# A LOW POWER PRESCALER, PHASE FREQUENCY DETECTOR, AND CHARGE PUMP FOR A 12 GHZ FREQUENCY SYNTHESIZER

A Thesis

by

EVAN LEE ESCHENKO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2007

Major Subject: Electrical Engineering

# A LOW POWER PRESCALER, PHASE FREQUENCY DETECTOR, AND CHARGE PUMP FOR A 12 GHZ FREQUENCY SYNTHESIZER

### A Thesis

by

## **EVAN LEE ESCHENKO**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Approved by:

Chair of Committee, Kamran Entesari Committee Members, May Boggess

Jose Silva-Martinez

Peng Li

Head of Department, Costas Georghiades

December 2007

Major Subject: Electrical Engineering

#### **ABSTRACT**

A Low Power Prescaler, Phase Frequency Detector, and Charge Pump for a 12 GHz

Frequency Synthesizer. (December 2007)

Evan Lee Eschenko, B.S., Texas A&M University

Chair of Advisory Committee: Dr. Kamran Entesari

A low power implementation of a CMOS frequency synthesizer at 12 GHz is an important step to improve the efficiency of a wireless transceiver in this frequency band. Since synthesizers are often employed as reference frequency sources such as local oscillators for up or down-conversion in communications system, their design is especially important for high performance transceiver applications. CMOS PLLs operating at high frequencies consume large amounts of power for proper operation, making power efficiency a top priority in transciever implementation. In response, this thesis presents a low power phase and frequency detector with True Single Phase Clocking by employing the .18µ TSMC process with a 1.8 V supply voltage. A conventional but extremely power efficient nano-watt charge pump is also implemented for additional power savings. Furthermore, a state of the art 16/17 prescaler using Current Mode Logic (CML) D-Flip Flops, CMOS inverters, and transmission gates has been optimized for maximum power savings. The prescaler consists of a 4/5 synchronous core and a feedback loop which modulates the 4/5 core to produce a division ratio of 16/17. Instead of employing power hungry CML, the feedback circuit takes advantage of low power NOR and AND gates realized in Transmission Gate Logic (TGL) to reduce the power consumption. To the best of my knowledge, this technique has never been used in a high frequency prescaler before.

## **DEDICATION**

To my parents Hal and Lindy Eschenko, grandparents George and Maxine Bellos and my sister Tina Everett and her family and of course Thu Ho

#### **ACKNOWLEDGMENTS**

I would like to thank Dr. Kamran Entesari for his guidance and support throughout the course of my thesis work. The weekly meetings I had with him gave me invaluable insights into mixed signal design and helped me appreciate the joint effort that goes into the design of a complex system.

I would like to express my sincere gratitude to Dr. Jose Silva for strengthing my understanding of prescaler design. The numerous discussions I had with him have greatly contributed toward the successful completion of my thesis.

Also, I would to thank Dr. Peng Li and Dr. May Boggess for participating on my committee.

I am deeply thankful for all the support of my family and friends.

## **TABLE OF CONTENTS**

|                                                                                                                                                                                                                                                                   | Page             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ABSTRACT                                                                                                                                                                                                                                                          | iii              |

| DEDICATION                                                                                                                                                                                                                                                        | iv               |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                   | V                |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                 | vi               |

| LIST OF FIGURES                                                                                                                                                                                                                                                   | viii             |

| LIST OF TABLES                                                                                                                                                                                                                                                    | xii              |

| I INTRODUCTION                                                                                                                                                                                                                                                    | 1                |

| <ol> <li>Frequency Synthesizers and Their Building Blocks.</li> <li>Research Objectives</li> <li>Phase-Frequency Detectors</li> <li>Charge Pumps for Phase Locked Loop</li> <li>Dual-Modulus Prescaler</li> <li>Individual Block Design Considerations</li> </ol> | 1<br>4<br>4<br>5 |

| II DESIGN OF PHASE-FREQUENCY DETECTOR                                                                                                                                                                                                                             | 9                |

| <ol> <li>Gate Level Architecture</li> <li>Transistor Level Architecture</li> <li>Phase Detector Simulation Results</li> </ol>                                                                                                                                     | 11               |

| III DESIGN OF CHARGE PUMP                                                                                                                                                                                                                                         | 14               |

| <ol> <li>Gate Level Architecture</li></ol>                                                                                                                                                                                                                        | 15               |

| IV DESIGN OF DUAL-MODULUS PRESCALER                                                                                                                                                                                                                               | 24               |

| 1 Gate Level Architecture                                                                                                                                                                                                                                         | 24               |

|       |                                                 | Page |

|-------|-------------------------------------------------|------|

| 2.    | Gate Level Operation                            | 25   |

|       | 2.1 Divide by 4                                 |      |

|       | 2.2 Divide by 5                                 |      |

| 3.    | Transistor-Level Architecture                   |      |

|       | 3.1 Edge-Triggered D-Flip Flop Implementation   |      |

|       | 3.2 Feedback Logic Implementation               |      |

| 4.    | Prescaler Simulator Results                     |      |

|       | 4.1 Post Layout Simulations                     | 67   |

| 5.    | Measurement Results                             |      |

|       | 5.1 Test Conditions and Setup                   | 76   |

|       | 5.2 Chip Micrographs                            | 78   |

|       | 5.3 Measurement Information                     |      |

| 6.    | Comparison with Other High Frequency Prescalers |      |

| V S   | UMMARY AND CONCLUSIONS                          | 92   |

| REFER | RENCES                                          | 93   |

| VITA  |                                                 | 97   |

# LIST OF FIGURES

|           |                                                          | Page |

|-----------|----------------------------------------------------------|------|

| Figure 1  | Block Diagram for 24 GHz Frequency Synthesizer           | 2    |

| Figure 2  | Simplified Block Diagram of PLL                          | 4    |

| Figure 3  | Reset-able Phase-Frequency Detector                      | 9    |

| Figure 4  | True Single Phase Clocked PFD                            | 11   |

| Figure 5  | Input Waveform to PFD                                    | 12   |

| Figure 6  | Output Waveforms from PFD.                               | 13   |

| Figure 7  | Conceptual Charge Pump                                   | 14   |

| Figure 8  | Transistor Level Charge Pump                             | 15   |

| Figure 9  | Verification of Charge Pump Current                      | 18   |

| Figure 10 | Control Voltage Settling Waveform                        | 19   |

| Figure 11 | Phase Detector Output Waveforms while Test PLL is Locked | 20   |

| Figure 12 | Locked Waveforms                                         | 21   |

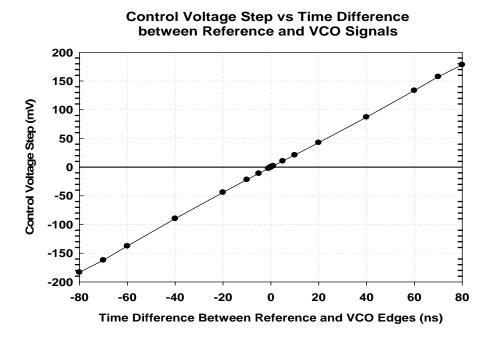

| Figure 13 | Change in VCO Control Voltage vs Waveform Edge Offset    | 22   |

| Figure 14 | Zoom of Figure 13                                        | 23   |

| Figure 15 | 16/17 Gate Level Prescaler Schematic                     | 24   |

| Figure 16 | Logic Levels in Core for Divide by 4 Mode                | 25   |

| Figure 17 | Simplified Schematic of Core for Divide by 4 Mode        | 25   |

| Figure 18 | Schematic of Logic Levels in Core for Divide by 5 Mode   | 26   |

| Figure 19 | Simplified Schematic of Core for Divide by 5 Mode        | 27   |

| Figure 20 | Output and Feedback Section                              | 28   |

| Figure 21 | Output of a NOR Gate with Inputs of 2 Frequencies        | 28   |

|                                                                         | Page |

|-------------------------------------------------------------------------|------|

| Figure 22 CML Master-Slave D-Flip Flop                                  | 29   |

| Figure 23 Gate Level D-Flip Flop                                        | 31   |

| Figure 24 CML D-Flip Flop with Merged CML NAND                          | 32   |

| Figure 25 Simplified Schematic of Circuit during Preamp Phase           | 34   |

| Figure 26 Simplified Schematic of Circuit during Latch or Holding Phase | 234  |

| Figure 27 Preamp Exponential Decay Term                                 | 39   |

| Figure 28 Actual Preamp Gain                                            | 40   |

| Figure 29 Selection of Normalized Latch Transconductance                | 41   |

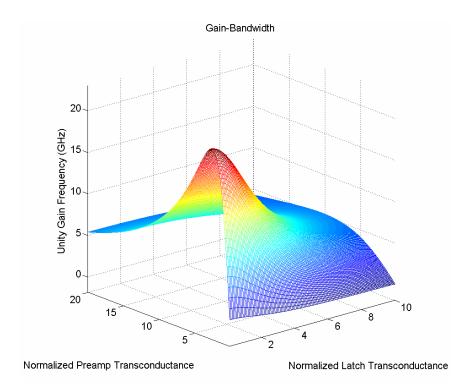

| Figure 30 Preamp Gain Bandwidth Drain Current=500 uA                    | 43   |

| Figure 31 Gain Bandwidth Drain Current=1 mA                             | 44   |

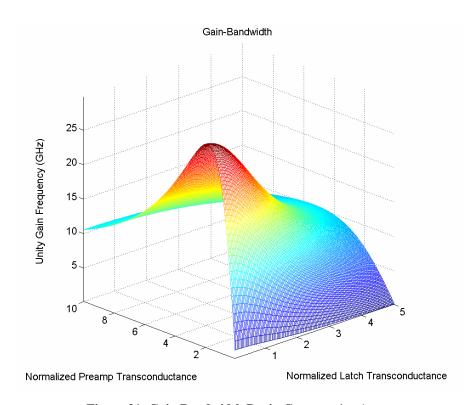

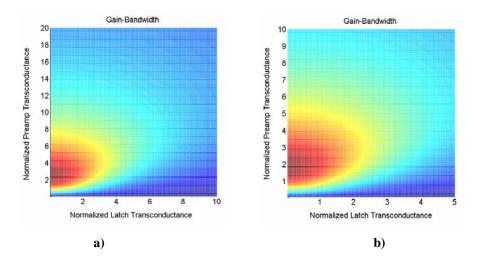

| Figure 32 Alternate Top Views of a) Figure 30 and b) Figure 31          | 45   |

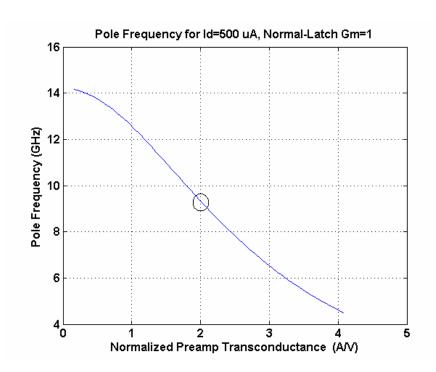

| Figure 33 Pole Frequency vs Normalized Preamp Transconductance          | 46   |

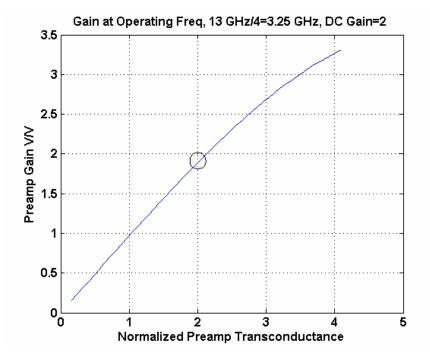

| Figure 34 Gain at Expected Operating Frequency                          | 47   |

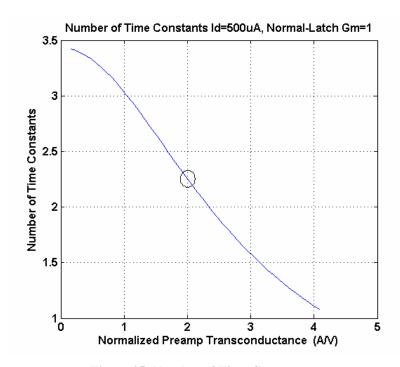

| Figure 35 Number of Time Constants                                      | 48   |

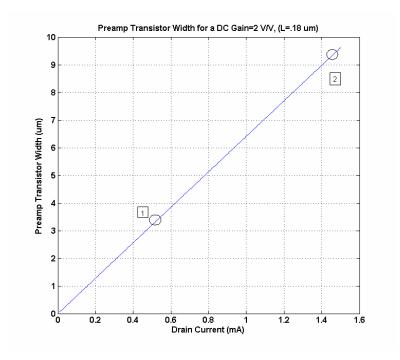

| Figure 36 Preamp Transistor Sizing (M3-M4)                              | 49   |

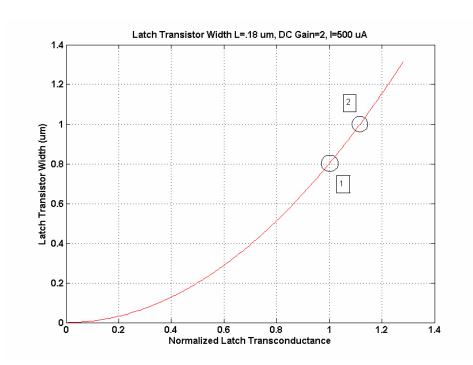

| Figure 37 Latch Width vs Latch Transconductance                         | 50   |

| Figure 38 Preamp Phase of 4/5 Core                                      | 52   |

| Figure 39 Gate Level Representation of Figure 40                        | 54   |

| Figure 40 Generic TGL OR Gate                                           | 54   |

| Figure 41 NOR Gate Modification 1                                       | 55   |

| Figure 42 Gate Level Representation of Figure 43                        | 56   |

| Figure 43 NOR Gate Modification 2                                       | 57   |

| Figure 44 Gate Level Representaion of Figure 45                         | 58   |

|                                                                           | Page |

|---------------------------------------------------------------------------|------|

| Figure 45 NOR Gate Modification 3                                         | 58   |

| Figure 46 Implemented TGL OR Gate with Inverter Buffers                   | 60   |

| Figure 47 Small Signal Model of TGL NOR Gate                              | 61   |

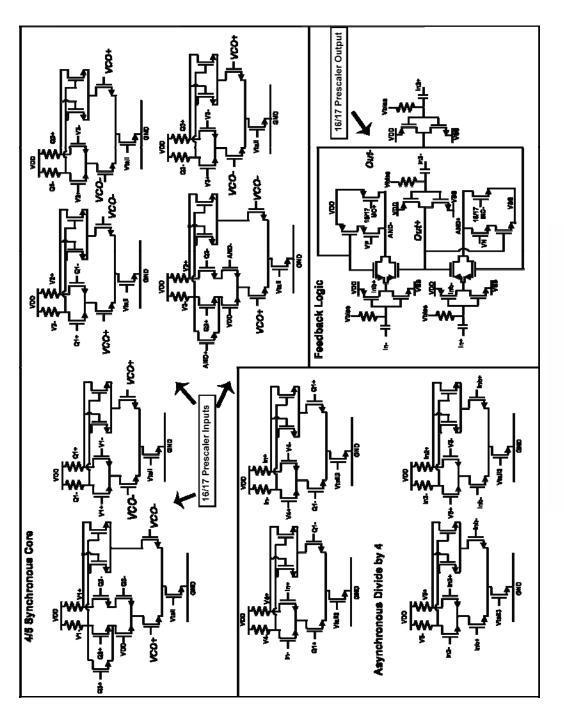

| Figure 48 Overall Schematic of 16/17 Prescaler                            | 65   |

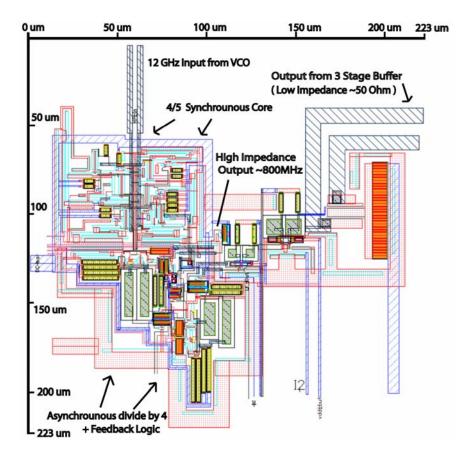

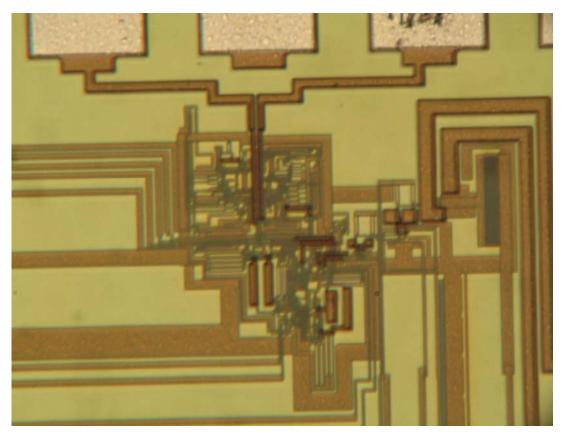

| Figure 49 Layout of 16/17 Prescaler                                       | 66   |

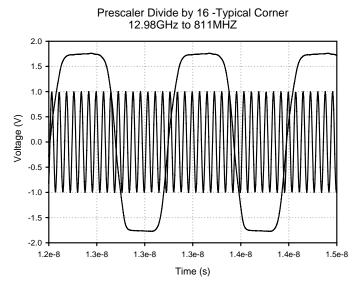

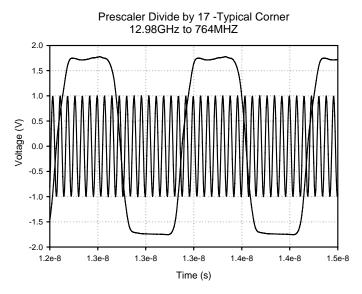

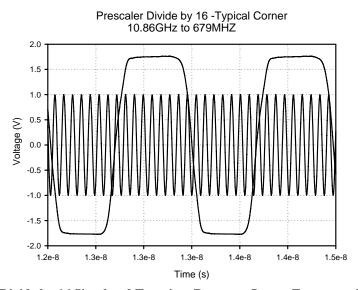

| Figure 50 Divide by 16 Simulated Transient Response-Upper Frequency Limit | 67   |

| Figure 51 Divide by 17 Simulated Transient Response-Upper Frequency Limit | 67   |

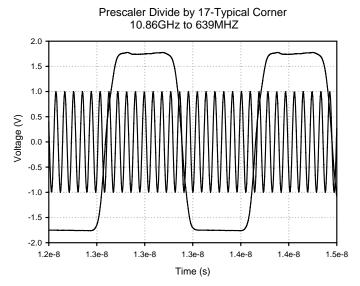

| Figure 52 Divide by 16 Simulated Transient Response-Lower Frequency Limit | 68   |

| Figure 53 Divide by 17 Simulated Transient Response-Lower Frequency Limit | 69   |

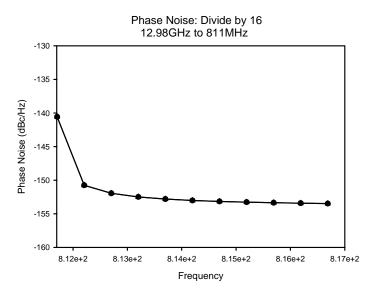

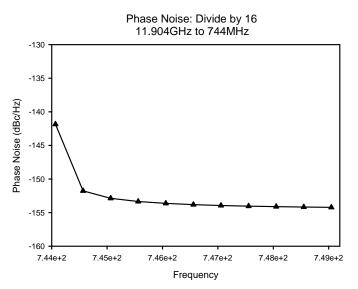

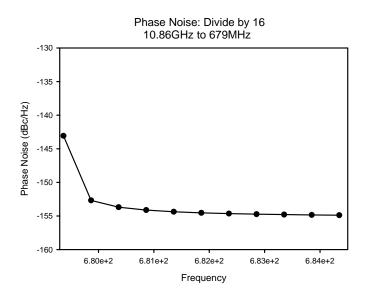

| Figure 54 Divide by 16 Simulated Phase Noise -Upper Frequency Limi        | t 70 |

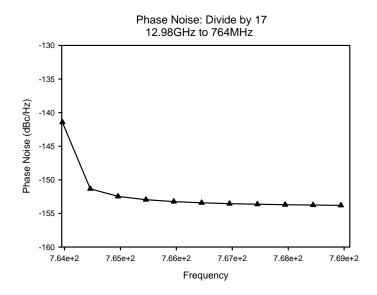

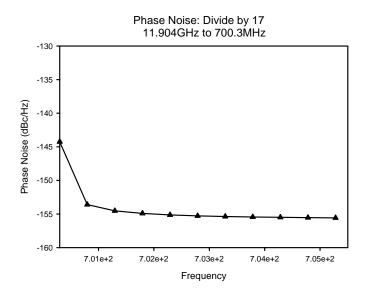

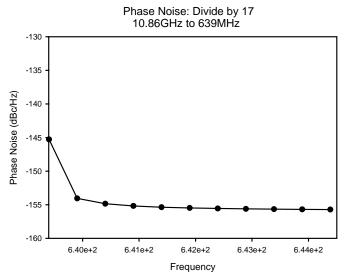

| Figure 55 Divide by 17 Simulated Phase Noise -Upper Frequency Limi        | t 70 |

| Figure 56 Divide by 16 Simulated Phase Noise-Center Band Frequency        | 771  |

| Figure 57 Divide by 17 Simulated Phase Noise-Center Band Frequency        | 771  |

| Figure 58 Divide by 16 Simulated Phase Noise-Lower Frequency Limi         | t 72 |

| Figure 59 Divide by 17 Simulated Phase Noise-Lower Frequency Limi         | t 72 |

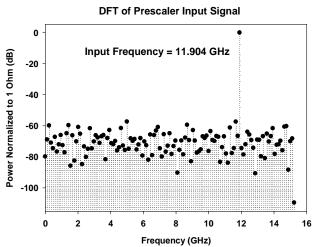

| Figure 60 Discrete Fourier Transform of the Input Signal                  | 73   |

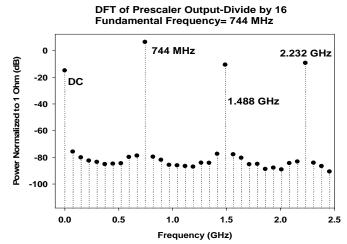

| Figure 61 DFT of the Output Signal during Divide by 16                    | 73   |

| Figure 62 DFT of Output Signal during Divide by 17                        | 74   |

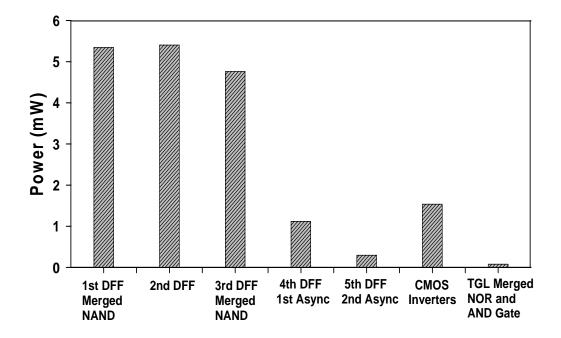

| Figure 63 Bar Graph of Power Consumption by Prescaler Sub-circuits        | 75   |

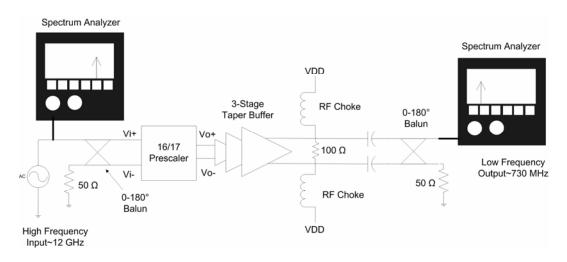

| Figure 64 Measurement Setup for the 16/17 Prescaler                       | 76   |

| Figure 65 3-Stage CMOS Output Buffer for On-Wafer Measurement             | 77   |

|                                                          | Page |

|----------------------------------------------------------|------|

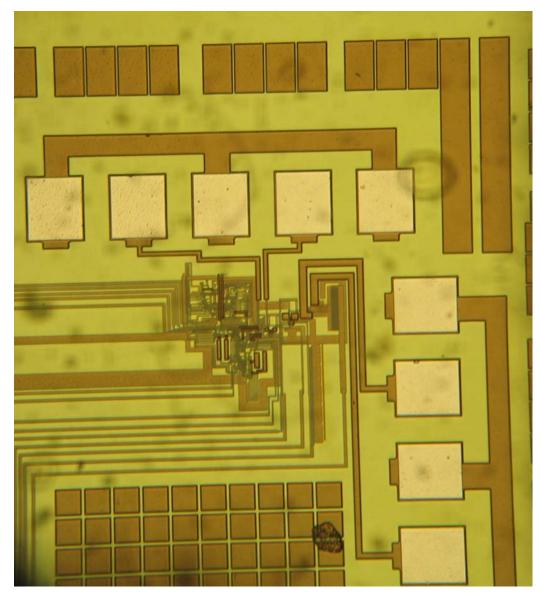

| Figure 66 Chip Micrograph #1                             | 78   |

| Figure 67 Chip Micrograph #2                             | 79   |

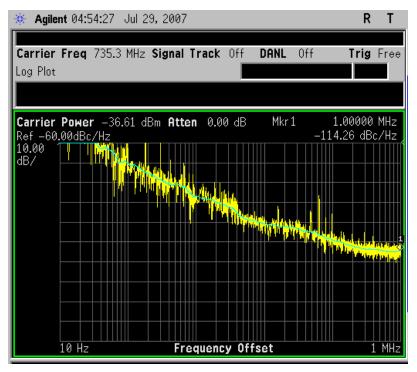

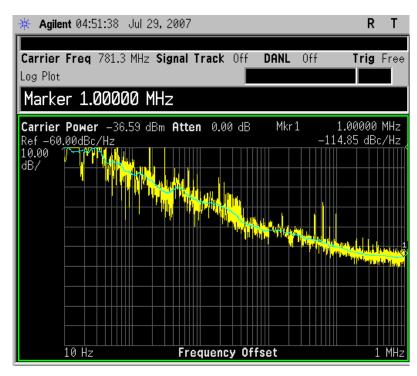

| Figure 68 Phase Noise in Divide by 17 fin=12.5 GHz       | 82   |

| Figure 69 Phase Noise in Divide by 16 Fin=12.5 GHz       | 83   |

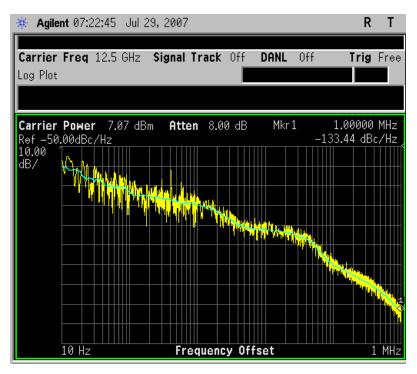

| Figure 70 Phase Noise of Frequency Source at 12.5 GHz    | 84   |

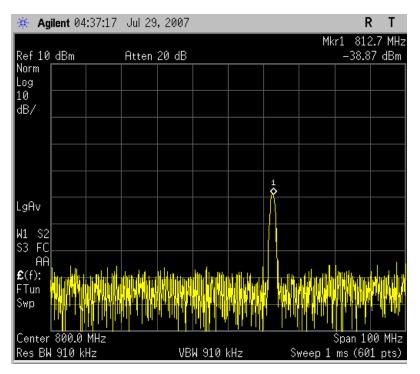

| Figure 71 Divide by 16, fin=13 GHz, fout=812.7 MHz       | 86   |

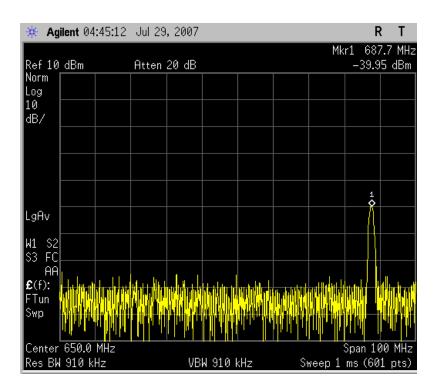

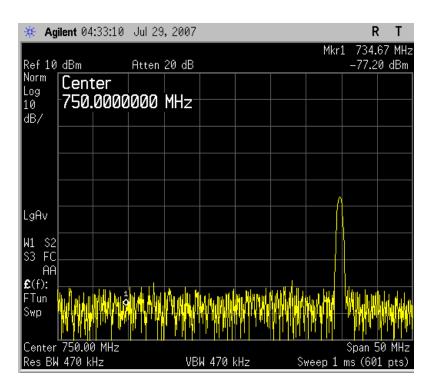

| Figure 72 Divide by 16, fin=11 GHz, fout= 687.7 MHz      | 87   |

| Figure 73 Divide by 17, fin=13 GHz, fout=764.7 MHz       | 88   |

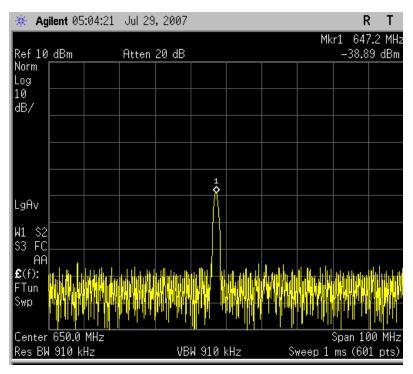

| Figure 74 Divide by 17, Divide fin=11 GHz fout=647.2 MHz | 89   |

# LIST OF TABLES

|          |                                                                       | Page |

|----------|-----------------------------------------------------------------------|------|

| Table 1  | Desired System Performance                                            | 2    |

| Table 2  | Required Block Specifications                                         | 6    |

| Table 3  | Transistor Sizes for Phase-Frequency Detector                         | 12   |

| Table 4  | Charge Pump Transistor Sizes                                          | 17   |

| Table 5  | Bit Sequence in Divide by 4 Mode                                      | 26   |

| Table 6  | Bit Sequence in Divide by 5 Mode                                      | 27   |

| Table 7  | Typical Values from Design Equations                                  | 51   |

| Table 8  | Typical Layout Values for D Flip Flops                                | 52   |

| Table 9  | Element Values for the Feedback Section after Post Layout Simulations | 64   |

| Table 10 | Post Layout Simulated Specifications for Prescaler                    | 74   |

| Table 11 | Raw Uncorrected Measurement Results                                   | 80   |

| Table 12 | 2 Buffer Corrected Measurement Results                                | 81   |

| Table 13 | 3 Comparision of Dual or Triple Modulus Prescalers                    | 90   |

#### I INTRODUCTION

## 1. Frequency Synthesizers and Their Building Blocks

Frequency synthesizers are found in a variety of circuits such as wireless communication transceivers [1]. They provide the stable reference frequency source for RF mixers and the central processing units found in all computers [2]. Without synthesizers, stable frequencies could not be produced higher than frequencies achievable from the excitation of crystals into oscillators. The frequency synthesizers can take a low frequency generated from a crystal oscillator and multiply it by an adjustable number to produce a much higher frequency[2]. The accuracy of frequency generated is very close to the high precision of a crystal oscillator. The frequency multiplication factor can be made adjustable to create communication transceivers with multiple channels [2-3]. Furthermore, synthesizers are used to synchronize clock signals between communication devices to allow digital information transfer[2].

## 2. Research Objectives

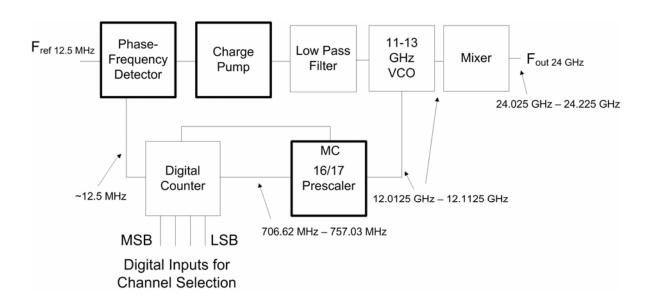

The primary objective of this thesis is to design a robust, low noise, high frequency prescaler, a phase frequency detector (PFD) and a low power and accurate charge pump as part of a larger project under Dr. Kamran Entesari, which entails an entire 24 GHz frequency synthesizer. The high frequency nature of the synthesizer calls for a phase-locked loop (PLL) implementation at the transistor-level for the .18u TSMC process with a 1.8 V supply voltage. All three blocks will strive for low power consumption and state of the art operation. The blocks must also satisfy the system level behavior for the 24 GHz ISM wireless band (24.025 GHz - 24.225 GHz). The system level analysis was performed by Dr. Gang Bu and is summarized in Table 1.

This thesis follow the style of *IEEE J. Solid-State Circuits*.

| Frequency Band      | 24.025 GHz – 24.225 GHz  |

|---------------------|--------------------------|

| Channels            | 9                        |

| Channel Spacing     | 25 MHz                   |

| Channel Frequencies | 24 GHz + n*25 MHz, n=1~9 |

| Settling time       | < 50 uS                  |

| Accuracy            | 20 ppm (480 KHz)         |

**Table 1: Desired System Performance**

Figure 1: Block Diagram for 24 GHz Frequency Synthesizer

The highlighted blocks in Figure 1 are the responsibility of this research project with specific emphasis on the 16/17 prescaler due to difficulty of implementing a prescaler at frequencies above 10 GHz with a .18 µm CMOS process. The PFD and charge pump are less challenging as they operate at much lower frequencies. The prescaler layout will be generated and simulated using Cadence, then fabricated and

tested on chip. The phase frequency detector and charge pump will be verified only through simulation.

## **Primary Objective**

Desired System Performance for all corners (fast, typical and slow)

## **Secondary Objectives**

1) Low Noise

Small Number of Noise Generating Components Limited Noise Bandwidth High Slew Rate

2) Low Power Consumption

Minimize DC Current usage

Arrange layout to minimize parasitics on signal path

Reduces required transconductance and therefore bias current

Avoid over-design of subcircuits with low performance requirements

Avoid over-design of subcircuits with low performance requireme

3) Small Chip Area

Use minimum size devices if possible

Small Input Capacitance to Reduce VCO Power Consumption

Multiple Stage Pre-amplifier

The following sections will introduce the individual blocks and their functions. The last section highlights some important practical considerations about the design of the individual blocks, which are deduced from the system level specifications.

#### 3. Phase-Frequency Detectors

The general function the phase-frequency detector (PFD) is to compare the input reference signal to the VCO output signal and output is a representation of the time or phase difference of the changes in the signals [4]. The primary measure of the effectiveness of a PFD is the size of the dead zone [5]. Dead zone can be defined as the situation where there is a difference between the VCO ouput signal and the input reference signal but the PFD output does not change. The effect of employing a PFD with a dead zone is reduced frequency stability manifested as sub reference spurs appearing in the frequency content of the VCO output. When the phase difference enters the dead zone, the VCO control voltage is not updated on for that cycle of the reference frequency. The usual periodic updating of the VCO control voltage results in a reference spurs which are located in the frequency spectrum a distance of one reference frequency away from the carrier [6].

### 4. Charge Pumps for Phase Locked Loop

The general function for the charge pump (CP) in a PLL is to provide a large open-loop gain by pumping charge into the loop filter [7]. The amount of charge pump is proportional to the amount of phase difference detected by the PFD. Since the capacitor is an open circuit for direct current (DC), charge accumulates very quickly and results in a large DC gain, which causes the final steady state phase error between the input and the output to be very small [8].

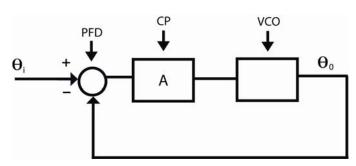

Figure 2: Simplified Block Diagram of PLL

A simplified diagram of a phase locked loop is shown Figure 2. Note that the low pass filter is considered as part of the charge pump. If *A* represents the open-loop gain of a phase-locked loop then the relationship between the input and output phase is shown in the following equation.

$$\frac{\theta_{out}}{\theta_{in}} = \frac{A}{1+A} \tag{1}$$

The theretorical DC gain for a charge pump based PLL is infinite however in practice this is impossible [9].

#### 5. Dual-Modulus Prescaler

A high frequency prescaler is arguably the most challenging block in phase-locked loop (PLL) design especially in the gigahertz range. Common benchmarks for performance are focused on wide input bandwidth for greater PLL acquisition range, low phase noise for PLL frequency stability and low power consumption for mobile applications[10-14]. LC injection locked dividers can provide very high frequency operation but their small locking bandwidth is impractical and comes at the large area cost of inductors [15-16]. Most low power dynamic dividers fail at high frequencies [17] and miller dividers are typically power hungry [18]. Therefore, a middle ground is found by employing current mode logic which balances speed with power [19].

Efficient high speed circuits can be realized by careful matching of the type of logic employed to the expected operating frequency. The proposed 16/17 prescaler has a feedback loop that operates at a much lower frequency then the core. For maximum efficiency, the core will be composed of CML while the feedback loop can take advantage of the much lower power TGL.

In PLL design, a low noise solution is of utmost importance because it will generate a more stable reference frequency. The phase noise of the prescaler can be minimized by maximizing the slew rate of the prescalar output stage [20]. Neither CML

nor TGL produce signals suitable for a maximum slew rail-to-rail output stage. CML does not provide rail to rail operation and TGL can just drive high impedance nodes because it merely passes or holds current with no current-producing capability in itself. The most efficient and natural choice for the output stage in this prescaler is employing CMOS inverters.

## 6. Individual Block Design Considerations

The phase locked loop system level behavior provides insight into how each block must operate for smooth functioning of the entire system. For instance, the phase frequency detector must operate within minimum frequency range (11.9 MHz to 13 MHz), the charge pump must provide a certain current flow (0 or +/- 40  $\mu$ A) and the prescaler must maintain a correct division ratio (16/17). Table 2 provides information regarding the different synthesizer block specifications under research for this thesis and a more detailed explanation follows the table.

**Table 2: Required Block Specifications**

| Parameter                                          | Value            |

|----------------------------------------------------|------------------|

| Charge Pump Current                                | 40 μΑ            |

| VCO Gain                                           | 500 MHz/V        |

| Range of Selectable Division Ratio From VCO to PFD | 961-969          |

| PFD Operating Frequency Range                      | 11.9-13 MHz      |

| Minimum Prescaler Division Ratio                   | 9/10             |

| Minimum Prescaler Input Range                      | 11 GHz to 13 GHz |

The charge pump current value is a result of the entire system-level phase locked loop analysis.

The selectable division ratio can be computed by dividing the desired VCO output frequency by the reference frequency. The target VCO output frequency is given at 12.0125 GHz and the desired channel spacing is 12.5 MHz due to the ISM band standard, leading to division ratios of 961 to 969.

For a reference frequency of 12.5 MHz, a VCO gain of 500 MHz/V and a power supply of 1.8 V, the maximum frequency seen by the phase-frequency detector can be computed by the following formula.

$$f_{\max@PFD} = \frac{f_{VCOFreeRunning} + (MaxSwingVCOControl \times VCOGain)}{MinimumDivisionRatio}$$

(2)

$$= \frac{12GHz + \left(.9V \times 500 \frac{MHz}{V}\right)}{961} = 12.96 MHz \tag{3}$$

The Max Swing on the VCO control line is set to .9 V because VCO control voltage is limited to values between zero and 1.8 V and the synthesizer is designed to operate at the center of the supply voltage. The maximum PFD operating frequency is close to the nominal operating reference frequency (12.5 MHz) and can be easily managed by most PFD architectures. To allow for some margin, the minimum PFD operating frequency will be set slightly higher than the previously calculated value to 13 MHz. Due of the relative ease in achieving this performance the main design considerations for the PFD are power consumption and chip area.

The prescaler input frequency range should be large enough to accept any frequency the VCO can generate so that the acquisition range limitation is due to VCO and not the prescaler. Ideally for this application, the VCO should have a free running frequency of approximately 12 GHz when the VCO control voltage is center between the power supply rails or Vdd/2. Also, the VCO control voltage is limited by the rails so the maximum VCO control voltage offset is Vdd/2. Therefore, the VCO gain determines the maximum variation in frequency. The maximum frequency change is .9 V times 500 MHz/V or 450 MHz. The expected VCO output frequencies are 12 GHz +/- 450 MHz or 11.55 GHz to 12.45 GHz, however to allow for some margin the prescaler bandwidth will be larger at approximately 11 to 13 GHz.

The minimum prescaler division ratio can be determined by researching typical operating frequencies for digital counters. Most reported counters operate at frequencies less than 2 GHz [17]. If the prescaler division ratio is set to 9/10 the highest output frequency the digital counter will see is 13 GHz divided by 9 or 1.44 GHz, which provides some margin for proper counter operation.

This thesis contains 3 main sections. Section I discusses the phase frequency detector behavior, section II explains the charge pump and finally section III is about the prescaler implementation. Each section contains subsections that explain in detail the design taken from the gate level through the transistor level and ending in simulation results for the PFD and charge pump and measurement results for the prescaler.

# II DESIGN OF PHASE-FREQUENCY DETECTOR

## 1. Gate Level Architecture

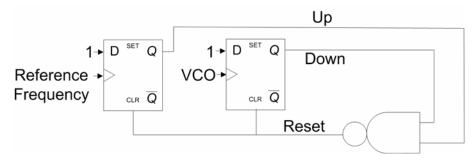

Figure 3: Reset-able Phase-Frequency Detector

In Figure 3, a digital D Flip Flop based phase detector is shown. A digital phase detector was chosen for this design because it provides low power consumption than analog based phase detectors [21] and most transistors in the circuit can be made with minimum size. The input reference frequency to the PLL is very low compared to the unity gain frequency of the technology process in most PLLs [17,19]. Because of this fact, phase frequency detectors can be implemented with minimal power and area resources and still provide a large margin in performance over required system specifications. An analog gilbert mixer phase frequency detector would provide a much higher maximum operating frequency [22] but this is not necessary and it only consumes additional power without noticable benefit.

The explanation of the general operation of the PFD begins by describing the initial state of the device. First, the Up and Down signals are reset to low or zero and assume both the reference frequency signal and the VCO signal are high or one. Additionally, the reference frequency waveform is slightly leading the VCO waveform. When a falling edge occurs on the reference frequency input, the high or one on the D input is transmitted to the Q output or Up. A short time later, the VCO waveform experiences a falling edge and the Q output or Down of the other flip flop is set. Once both Up and Down are high or one, the NAND gate experiences a transition to force the Reset signal to zero. The flip flop are designed so that zero on the Reset signal resets the Q outputs to zero.

### 2. Transistor Level Architecture

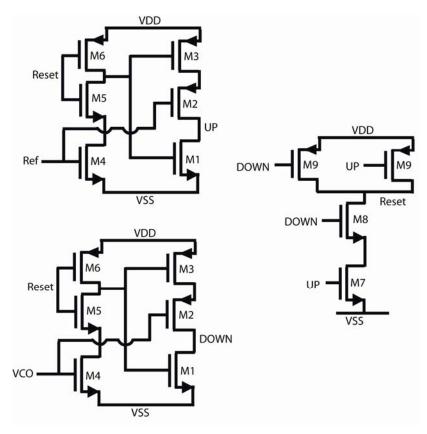

Figure 4: True Single Phase Clocked PFD

The PFD is implemented with True Single Phase Clocked logic as shown in Figure 4. The design strategy is to minimize the number of transistors and the amount of power consumed. However, not all of the transistors can be implemented with minimum width such as those involved in the reset operation. In Table 3, the transistor sizes for the PFD are given. Note that since the operating frequency of the PFD is quite low compared to the cutoff frequency of the technology process, most transistors can be made minimum size.

**Table 3: Transistor Sizes for Phase-Frequency Detector**

|    | W/L        |

|----|------------|

| M1 | 2.2u/.18u  |

| M2 | .27u/.18u  |

| М3 | .27u/.18u  |

| M4 | .27u/.18u  |

| M5 | .27u/.18u  |

| М6 | 1.35u/.18u |

| М7 | .27u/.18u  |

| M8 | .27u/.18u  |

| М9 | .54u/.18u  |

# 3. Phase Detector Simulation Results

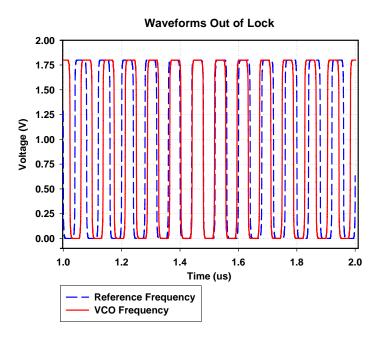

Figure 5: Input Waveform to PFD

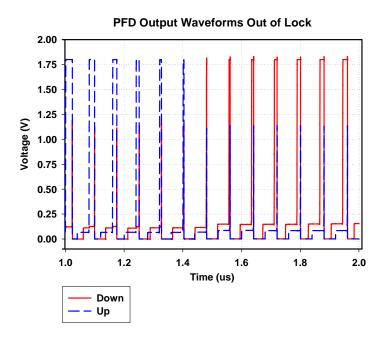

Figure 6: Output Waveforms from PFD

In Figure 5, we can notice that phase difference of the input waveforms of the input of the PFD changes with time. On the left side of the plot, the reference frequency leads the VCO frequency but on the right side, the VCO is leading the reference frequency. In order for the PLL to be driven to lock when the reference leads the VCO, the PFD must produce a wider pulse width on the up signal. This will cause the charge pump to raise the VCO control voltage which increases the VCO frequency. This increase in frequency will cause the VCO phase to accumulate faster than the reference phase. In a PLL, this will effectively reduce the current phase difference between the two signals.

It can be seen from Figure 6 that PFD output waveforms are correct in their relation to phase of the input signals. On the left side, the VCO would be pushed up to make up for the phase lag and on the right, we have the opposite. In the following section, the design of the charge pump will be discussed and the simulation of the joint operation of the PFD and charge pump will be shown.

### III DESIGN OF CHARGE PUMP

#### 1. Gate Level Architecture

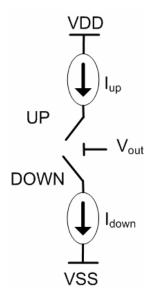

Figure 7: Conceptual Charge Pump

The basic idea of a charge pump is to add or subtract current from the  $V_{out}$  node. The charge pump circuit and the choice of impedance to ground at  $V_{out}$ , which is also the VCO control voltage determine the dynamics of the PLL, such as DC Loop gain and tracking bandwidth [23]. Ideally,  $I_{up}$  and  $I_{down}$  should be exactly equal and there are many literatures on methods to force current matching [24]. Circuit noise at  $V_{out}$  directly appears at the output spectrum of the VCO. To limit the effect of noise at the output spectrum, the bandwidth is usually limited at  $V_{out}$  with a second order low-pass filter [25].

# 2. Transistor Level Architecture

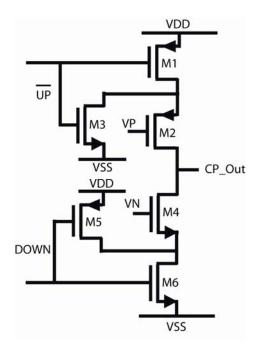

Figure 8: Transistor Level Charge Pump

The implemented architecture for the charge pump is shown in Figure 8. Notice there is a cascode transistor (M2 or M4) between the input transistor (M1 or M6) and the output node, CP Out. These cascode transistors raise the output impedance of the charge pump which makes the charge pump circuit perform more closely to an ideal current source. The two transistors on the left (M3, M5) are not necessary for rudimentary operation but they help to absorb some of the transient currents during switching [26]. M1 provides the charge up current and M2 acts as a cascode transistor because Vp is a DC bias voltage. This cascode transistor and the NMOS transistor with gate attached to the UP bar signal (M3) help to reduce the charge injected into the CP Out node. Charge injection effects due to the UP bar signal can be significant because this signal typically has a high slew rate. If these extra transistors are not included, the transient current flowing through the parasite capacitors will alter the charge at the high impedance output node, CP Out. This will significantly disrupt the output voltage at the CP Out node and should be minimized [27]. The bottom charge down (current sinking) section operates in a complemtary fashion to the top charge up (current sourcing) section. The ideal function of this block is to provide an ideal supply of current to or from the output node, CP Out. If a current source has a low output impedance then the supplied current will vary significantly with the node voltage at the output of the current source. This variation is undesirable because we would like to provide a stable and accurate current source with the charge pump. We do that by increasing the channel lengths of the cascode transistors (M2,M4) because this will result in a higher output impedance at the CP Out node.

**Table 4: Charge Pump Transistor Sizes**

|    | W/L        |

|----|------------|

| M1 | 1.35u/.18u |

| M2 | 1.11u/.36u |

| М3 | .27u/.18u  |

| M4 | .27u/.36u  |

| M5 | 1.35u/.18u |

| М6 | .27u/.18u  |

In Table 4, the transistor dimensions of the charge pump are shown.

### 3. Simulation Results

The charge pump and PFD were simulated in a phase locked loop similar to Figure 2. An ideal reference frequency source and an ideal VCO were used for the simulation. Also there was no divider in the feedback loop. This was done to minimize other circuit effects, making the PFD and CP performance more visible to inspection. The input reference frequency source is set to 10 MHz and since there is no divider in the feedback loop, the VCO should settle into phase lock at a frequency of 10 MHz.

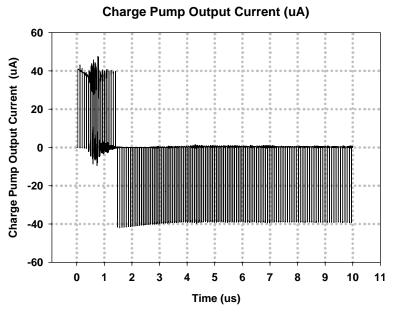

Figure 9: Verification of Charge Pump Current

In Figure 9, it is shown that the charge pump has been designed to produce a 40 uA current in either the positive or negative direction. This is the primary specification for the charge pump block as it directly affects the entire PLL loop gain. Even though the VCO, during the simulation, is already at a higher frequency, the initial falling edge of the VCO frequency was placed later than the initial falling edge of the reference frequency. In the other words, the initial phase of the system is such that the VCO frequency is lagging behind the reference frequency. This initial difference is detected by the PFD and fed through the charge pump which pumps positive current from top supply rail to force the VCO control higher. This causes an increase in VCO frequency in order to make up the initial phase difference. The phase difference is made up relatively quickly by the frequency difference and soon the VCO phase is leading the reference frequency phase. Once the VCO frequency leads in phase the current switches polarity and begins to reduce the VCO control voltage. This explains why the current switches polarity in Figure 9.

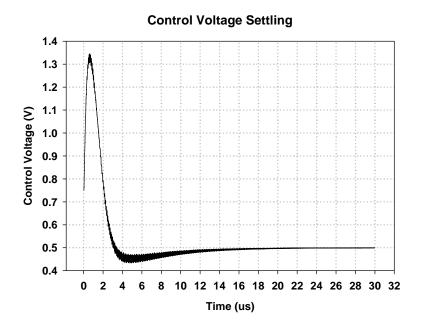

Figure 10: Control Voltage Settling Waveform

The VCO should lock to the same frequency as the input reference frequency. Since the VCO is ideal, the VCO control voltage is a direct represention of the VCO output frequency. Therefore, if the VCO control voltage is settled and not changing, then VCO output frequency is also stationary and the PLL is locked. In Figure 10, we can see that the VCO control voltage has settled which verifies the operation of the PFD and charge pump circuits together. The free running frequency of the VCO, when the control voltage is set to .9V, is 11 MHz. The VCO gain is 2.5 MHz per volt. In the figure, the voltage settles to .5 volts, this is expected because 2.5 MHz/V times .4 V is equal to 1 MHz and this is exactly the required correction to move the VCO frequency from 11 MHz to 10 MHz.

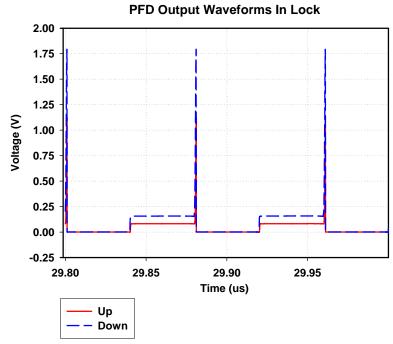

Figure 11: Phase Detector Output Waveforms while Test PLL is Locked

Notice in Figure 11, the up and down signals (the output of PFD) are raised at the same time and immediately reset. The small step visible on the graph is a characteristic of True Single Phase Logic operating at very low power. It could be minimized by using larger CMOS devices but that would increase power consumption. The small step is well below the 900mV threshold voltage of the following inverter and therefore has no to minimal effect on PFD and charge pump operation.

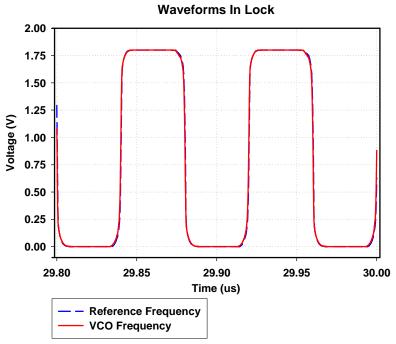

Figure 12: Locked Waveforms

In Figure 12, we can see the locked waveforms at the input and output of the PLL. There is no divider in the feedback loop so there is no static phase offset between the input and output.

Figure 13: Change in VCO Control Voltage vs Waveform Edge Offset

Figure 13 shows the amplitude of the step on the VCO control when a certain phase offset is detected. Notice phase is given in nanoseconds.

## **Zoom of Control Voltage Step vs Time Difference** between Reference and VCO Signals 100 o ∃ Control Voltage Step (uV) -200 -300 -400 -500 -600 -100 -50 0 50 100 Time Difference Between Reference and VCO Edges (ps)

Figure 14: Zoom of Figure 13

Figure 14 zooms the VCO control voltage to show the effect of a current mismatch in the charge pump. In this particular plot, when the VCO and reference frequency have zero phase offset there is still a slight negative voltage step. This implies that the NMOS charge down section is slightly overpowered compared to the PMOS charge up section. This effect can be eliminated by adjusting the cascode bias voltages in the charge pump.

### IV DESIGN OF DUAL-MODULUS PRESCALER

#### 1. Gate Level Architecture

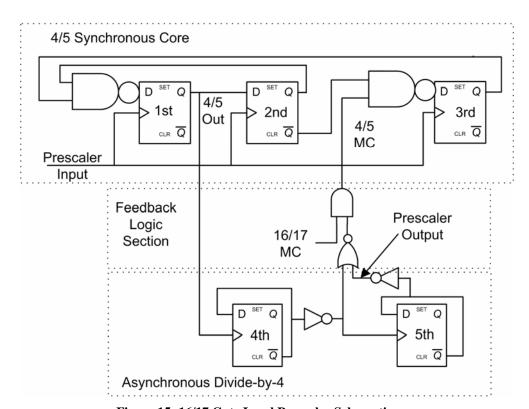

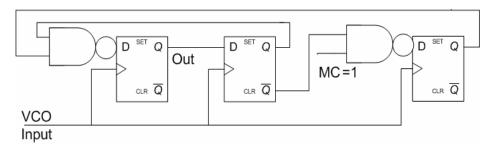

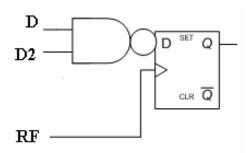

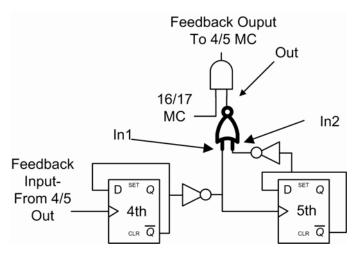

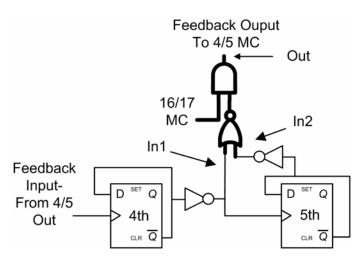

Figure 15: 16/17 Gate Level Prescaler Schematic

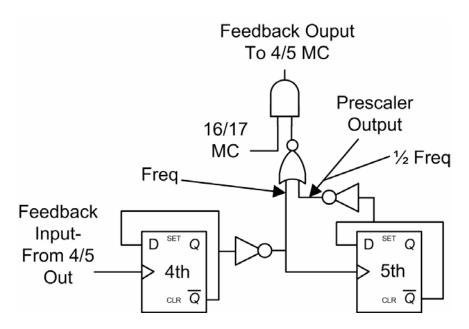

A 16/17 prescaler typically consists of a divide-by-4/5 synchronous core, a divide-by-4 asynchronous divider and a feedback logic section (Figure 15)[19]. The 4/5 MC signal controls how many DFFs the prescaler input signal must travel through and therefore determines the division ratio. When the 4/5 MC is held low, the core always divides the input signal by 4 which then travels through asynchronous divide-by-4 circuit, resulting in a total division ratio of 16. If the 4/5 MC signal is high, the core will divide by 5. If feedback is produced such that the core is modulated to divide-by-5 once and by 4 three times the resulting division ratio is 17.

## 2. Gate Level Operation

# 2.1 Divide by 4

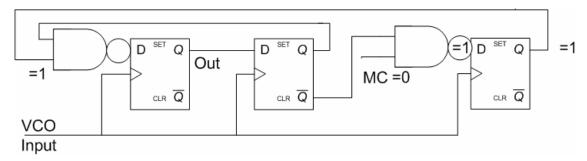

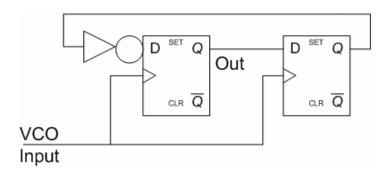

The 4/5 core is shown separate from the rest of the prescaler in Figure 16. Note here that during divde by 4 operation the output of the right most D Flip-Flop does not change and the circuit schematic can be simplified.

Figure 16: Logic Levels in Core for Divide by 4 Mode

In Figure 17, the simplified schematic is shown and it becomes clear that the 4/5 core resembles a shift register where the inversion of the last bit is fed into the first bit.

Figure 17: Simplified Schematic of Core for Divide by 4 Mode

The bit sequence of all the nodes is shown in Table 5. The 4 clock cycle bit sequence will continue indefintely, if MC is left at zero.

| MC=0         |       |    |    |      |       |    |            |  |  |  |

|--------------|-------|----|----|------|-------|----|------------|--|--|--|

| Clk<br>Cycle | NAND1 | Q1 | Q2 | Q2_b | NAND2 | Q3 | Cycle<br># |  |  |  |

| 1            | 1     | 0  | 0  | 1    | 1     | 0  |            |  |  |  |

| 2            | 1     | 1  | 0  | 1    | 1     | 1  | *1         |  |  |  |

| 3            | 0     | 1  | 1  | 0    | 1     | 1  | 2          |  |  |  |

| 4            | 0     | 0  | 1  | 0    | 1     | 1  | 3          |  |  |  |

| 5            | 1     | 0  | 0  | 1    | 1     | 1  | 4          |  |  |  |

| 6            | 1     | 1  | 0  | 1    | 1     | 1  | *1         |  |  |  |

| 7            | 0     | 1  | 1  | 0    | 1     | 1  | 2          |  |  |  |

| 8            | 0     | 0  | 1  | 0    | 1     | 1  | 3          |  |  |  |

| 9            | 1     | 0  | 0  | 1    | 1     | 1  | 4          |  |  |  |

Table 5: Bit Sequence in Divide by 4 Mode

# 2.2 Divide by 5

The 4/5 core is shown separate from the rest of the prescaler in Figure 18. Note here that during divde by 5 operation the output of the D Flip-Flop does change and now only the right NAND gate can be simplified.

Figure 18: Schematic of Logic Levels in Core for Divide by 5 Mode

In Figure 19, the simplified schematic is shown and it becomes clear that the 4/5 core resembles a shift register where the last bits are NANDed together and the result is fed into the first bit.

Figure 19: Simplified Schematic of Core for Divide by 5 Mode

In Table 6, the bit sequence of divide by 5 operation is shown.

MC=1 Clk Cycle # NAND1 Q2 Q2 b NAND2 Q3 Cycle Q1 \*1

Table 6: Bit Sequence in Divide by 5 Mode

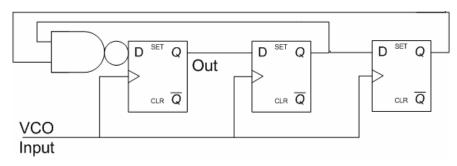

Figure 20: Output and Feedback Section

A topology that can provide both steady and modulated feedback and also be controlled with a single digital bit is shown in Figure 20.

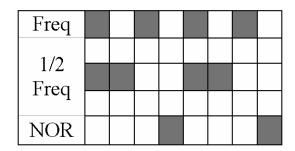

Figure 21: Output of a NOR Gate with Inputs of 2 Frequencies

Figure 21 shows the result of performing NOR operation for two digital signals when one signal is half the frequency of the other signal. The output of the NOR has the same frequency as the lower frequency section but the duty cycle is now 25% as

opposed to a usual duty cycle of 50%. The next section will present the Current Mode Logic D Flip-Flops at the transistor level.

#### 3. Transistor-Level Architecture

## 3.1 Edge-Triggered D-Flip Flop Implementation

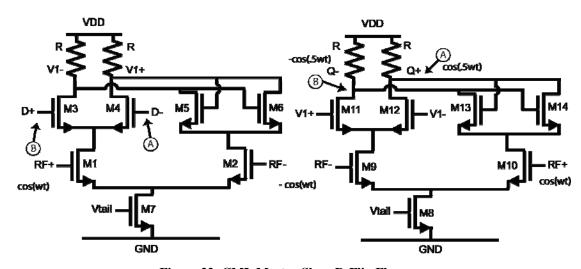

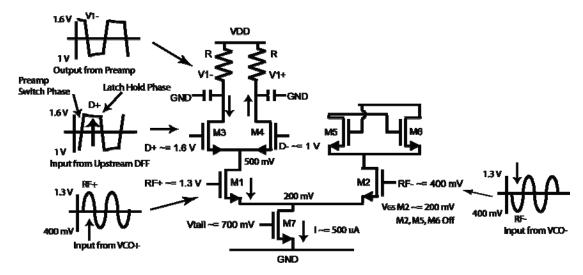

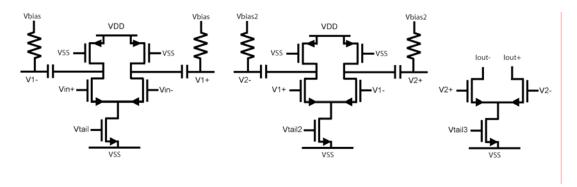

Figure 22: CML Master-Slave D-Flip Flop

Current mode logic is the choice for high speed mixed signal devices [11]. The constant current flow through the transistors biases the circuit a point where the transistors are already active and therefore can react quickly producing low time constants for maximum speed. The current mode logic architecture shown in Figure 22 eliminates slow PMOS transistors and their large parasitics as load elements and replaces them with either resistors with low parasitic or even inductors for maximum speed applications. One advantage of the differential nature of circuit is larger signal swing that results in a higher signal to noise ratio which is important to reduce phase noise in PLL design. Fortunately, extra power hungry common-mode feedback is not

necessary as circuit operates in a digital fashion with complete current switching from one side of the differential pair to the other during any transition.

The master-slave CML DFF is a well-studied topology but some important considerations are worthwhile to mention. The D-input differential pair must provide enough transconductance for complete current switching in one transition. The negative resistance formed by the cross-coupled pair can be small, even a gain slightly less than one is acceptable because input is periodic and voltage levels do not need to be stored for a long run of zeros or ones. Size minimization of this cross-coupled pair is necessary to reduce the capacitance at the output nodes (V1+/- and Q+/-) due to the relatively large gate-source capacitances.

The architecture is similar to a single balanced analog mixer and therefore transconductance of the RF input transistors should be maximized to reduce the effect of noise from the negative resistor, load resistors, and the differential pair. More transconductance in this stage also means more conversion gain ( $G_{conv}$ ) and therefore signal current ( $I_{RF}$ ) passing through M1 transfer to output nodes leading to wider bandwidths. Furthermore, amplitude of signal applied to the D input pair ( $V_{LO}$ ) can be increased by increasing the transconductance of the same D input pair in the previous DFF. A larger  $V_{LO}$  will improve noise immunity and also  $G_{conv}$ . As the transconductance in the bottom half of the circuit increases, the voltage bias point at the output nodes began to fall and less headroom is available for the transistors. To regain headroom, the pull up resistors can be made smaller at the cost of increased current flow and therefore power usage. A trade off arises between power consumption versus frequency response, specifically input bandwidth and maximum operating frequency. Careful selection of this trade-off is critical for optimal efficiency. The relationships are summarized in the following equations.

$$Bandwidth \propto G_{conv}$$

(4)

$$Gconv \propto I_{RF} \cdot V_{LO}$$

(5)

$$V_{LO} \propto gm_{D-input \ diff \ pair(M3-M4)}$$

(6)

$$I_{RF} \propto gm_{RF} pair(M1-M2)$$

(7)

Power Consumptio

$$n \propto I_{RF}$$

(8)

Output Noise Current

$$\propto \frac{1}{(V_{LO})^2}$$

(9)

Figure 23: Gate Level D-Flip Flop

Figure 24: CML D-Flip Flop with Merged CML NAND

Previously, it was shown that the 4/5 Prescaler needs 3 DFFs and 2 NAND gates. Recently reported work [10] has shown that the NAND gates can be merged with the DFFs as shown in Figure 23 to reduce power consumption, decrease delay and reduce complexity. The transistors that add the NAND functionality are M3a and M4b (Figure 24). However, this merged circuit introduces an asymmetry in the architecture. To remedy this asymmetry, we propose adding a degeneration transistor (M3b) in the master latch under the D input differential pair to the architecture (Figure 24). For further clarity, the gate of this degeneration transistor is connected to VDD. By adding this transistor, offsets can be prevented at the output nodes (V1+/-), an undesirable characteristic in the previously reported asymmetrical topology. Since CML logic does not have the wide rail to rail swings like CMOS logic and the signal travels around a loop in almost identical stages much like a ring oscillator, any offset in one stage can easily grow to disrupt the circuit. Close examination of the input section in the master latch shows that in NAND merging process, one side of the differential pair requires stacked transistors (M4, M4b) while the other side parallel transistors (M3, M3a). This causes the top stacked transistor to experience source degeneration and produces a disparity in inversion level and current flow. The final result is a fraction of a bit symbol

sitting on the output nodes (V1+/-), which is the input of the slave latch. However, the slave latch is designed for symmetrical inputs because this maximizes transconductance. The addition of source degeneration transistor (M3b) will ensure the input of the slave latch is fully symmetrical and truly differential, maximizing the efficiency of the slave latch. The DFFs in the feedback loop are both realized in the standard master-slave CML previously mentioned.

Before proceeding to the design equation section, it is important to note that there are two effects driving the output voltage as the signal propagates through the latch, the preamp step response in the first phase and the positive feedback during the second phase. We must maximize the preamp effect because it is the source of the switching and by doing this we can ensure the next stage already has a strong digital signal for the entire positive feedback phase which creates a predictable input for following circuit that happens to be another preamp. Indeed, the cross coupled pair only adds parasistics during the preamp phase and should be minimized to only flow enough current to delay the collapse of the output voltage by the pull-up resistors, during the second phase.

## 3.1.1 Design Equations for Current Mode Logic D-Flip Flop in Figure 22

#### 3.1.1.1 Latch Design Equations for Either Master or Slave

The D-flip flop latch is designed to provide the optimal drain current and transistor size ratio for maximum gain at the operating frequency. A single latch is analyzed in two phases, a preamp phase and a regeneration or latch phase. Both phases will be modeled as first order expontential neworks. First order approximations are a necessisty because higher order effects can only be well modeled on a computer. In the second phase of the latch, the regeneration phase, the output voltage must be held while the following stage senses the output voltage of the latch. The primary advantage of this analysis is providing the designer with an analytical procedure to calculate device sizes. When deciding among a variaty of possible transistor setups, the designer can be sure to select a setup that is most efficient for a given transistor size and power consumption.

First, we will show the linear small signal model of the circuit during each phase.

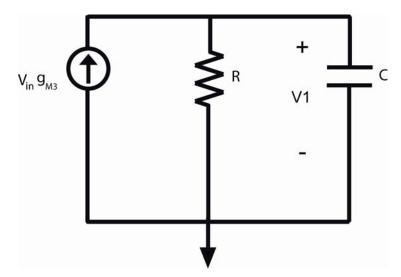

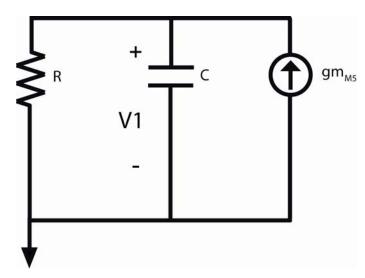

Figure 25: Simplified Schematic of Circuit during Preamp Phase

In Figure 25, the small signal model during the preamp phase is shown. Notice that the transconductance of the latch conductance is not present because the latch should be completely off.

Figure 26: Simplified Schematic of Circuit during Latch or Holding Phase

In Figure 26, the schemtic of the circuit during the latch phase is shown. Notice here that the transconductance of the preamp is not shown because it should be off during this phase. The next step is to translate the schematics into equations, but first we will define the time in each phase.

frequency of RF input signal =

$$F_{in}$$

(10)

$$T_{one\ phase} = \frac{1}{2F_{in}} \tag{11}$$

The frequency domain transfer function of the preamp is bascially a single-pole amplifier and is given by

$$V_{preamp} = V_{in} g m_{M3} \left( \frac{R}{RCs + 1} \right)$$

(12)

Where R is the load resistance at V1 in Figure 22 and C is the equivalent capacitance to ground at V1 in Figure 22. The C parameter varies significantly with transistor dimensions. The equivalent time domain representation is given by

$$V_{preamp} = V_{in} g m_{M3} R \left( 1 - e^{-t/RC} \right)$$

(13)

Plugging the length of the input preamp phase, we can calculate the expected voltage at the latch output,  $V_{preamp}$  or V1 in Figure 22, after the preamp cycle finishes. It is assumed that the input voltage is constant.

$$V_{preamp} = V_{in} g m_{M3} R \left( 1 - e^{\left( -\frac{1}{2F_{in}RC} \right)} \right)$$

(14)

The latch phase starts after the preamp phase so we will use the output voltage at the end of the preamp phase as the starting point for the regeneration phase. The frequency domain transfer function for the regeneration or holding phase is given by

$$V_{latch} = V_{preamp} \left( \frac{1}{s - \frac{\left(gm_{M5} - \frac{1}{R}\right)}{C}} \right)$$

(15)

Where C is the same as before. Notice how the transconductance of M5 and the conductance of R, the load resistor, work against each other. This means that depending on the value of each of these two parameters, the pole may be either positive or negative. The equivalent time domain representation is given by

$$V_{latch} = V_{preamp} e^{\left(\frac{t \left(gm_{M5} - \frac{1}{R}\right)}{C}\right)}$$

(16)

Here we see that depending on the two conductances, the output voltage at V1 may either increase or decrease during the latch phase. Plugging in the time period through which the latch operates on the output voltage we have,

$$V_{latch} = V_{preamp} e^{\left(\frac{gm_{M5} - \frac{1}{R}}{2F_{in}C}\right)}$$

(17)

We can substitute the preamp voltage in into to obtain the final two-phase latch output voltage at V1 in Figure 22.

$$V_{1} = V_{in}gm_{M3}R \left(1 - e^{\left(-\frac{1}{2F_{in}RC}\right)}\right)e^{\left(\frac{gm_{M5}-\frac{1}{R}}{2F_{in}C}\right)}$$

(18)

Leaving off the DC gain term,  $gm_{M3}R$ , the two exponential terms can be seperated into two terms as follows.

Latch Exponential Growth Term =

$$e^{\left(\frac{gm_{M5}-\frac{1}{R}}{2F_{in}C}\right)}$$

(20)

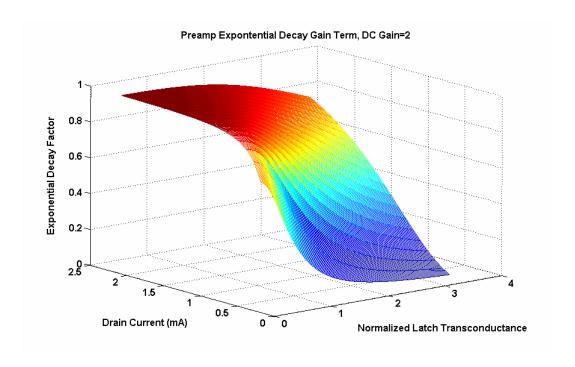

Optimization of the exponential terms is helpful in determining the effect of each subcircuit on the effective voltage gain for the overall latch. We will use MATLAB to evalutate each exponential term seperately for possible choices of drain currents and transconductances. The headroom of the transistor and DC gain of the preamp is held constant while current level and normalized latch transconductance are varied. The

normalized latch transconductane is a ratio of latch transconductance to resistor conductance. Establishment of device ratios is often more helpful when compared to absolute values because the device ratios provide a rule of thumb for the designer.

$$gm_{latch\_normalized} = \frac{gm_{latch}}{g_{resistor}} = (gm_{latch})R$$

(21)

Since we are varying the current, the device sizes must also vary accordingly to maintain DC gain and headroom and therfore the required transistor dimensions are calculated. We then use these dimensions along with process parameters obtained from MOSIS's website at www.MOSIS.org, for 0.18um TSMC to estimate the capacitive parasitics from transistors. Then from the parasitics, the time constants for each exponential are calculated. The actual time the circuit has in each phase for a 13 GHz input signal is 1/(2\*13e9). This actual time is normalized by the time constant, and the normalized result, which are the number of time constants, are plugged in to their respective expontential terms and plotted. This is a measure of the time domain performance for a particular transistor power and size setup. Note that we will use the term Latch to reference the cross-coupled negative resistor (M5-M6), because it is responsible for the latching or holding effect. The first plot is the premap exponential decay term and it shows the effect of device sizes in the cross coupled negative resistor. When the sizes are larger, the voltage regeneration is powerful but it is harder for the preamp to drive the voltage to the opposite polarity.

Figure 27: Preamp Exponential Decay Term

In Figure 27 the preamp gain clearly decreases as latch transconductance (transistor width) increases. The preamp transfer function is also highly dependent on current because as current increases the load resistance must reduce to maintain the output DC level fixed, which in turn reduces the time constant for the first section. On the drain current axis, the plot shows a sharp increase at about .5 mA and then saturates. An optimal choice would therefore be the region just when the plot saturates as further increase offers little benefit. It is clear that if only 70-80 percent of the signal is transferred, due to exponential decay term during the preamp phase, the preamp DC gain must be increased so that the gain is not less than unity. The following expressions show this relationship.

$$Av_{dc\ preamp} = \frac{1}{Exponential\ Decay\ Factor}$$

(22)

For example if exponential decay term is .5, the required DC preamp gain is

$$Av_{dc\ preamp} = \frac{1}{.5} = 2\frac{V}{V} = gm_{M3}R \tag{23}$$

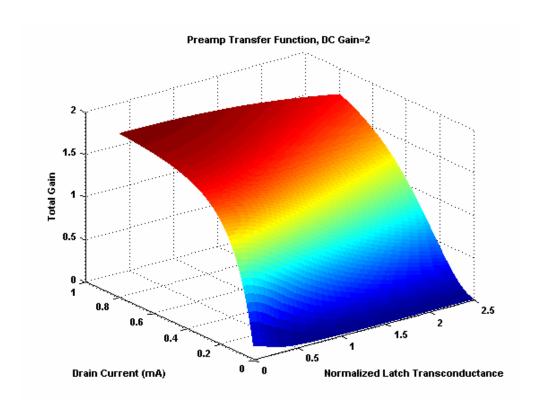

Figure 28: Actual Preamp Gain

The actual preamp gain, which is the combined effect of DC gain and exponential decay is shown in Figure 28. The gain is slightly reduced from the DC value of  $2\ V/V$  because of inadequate settling time.

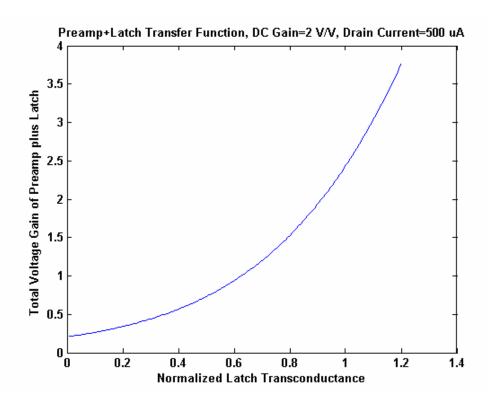

Figure 29: Selection of Normalized Latch Transconductance

In Figure 29, the overall gain of the preamp plus the latch is shown as a function of normalized latch transconductance. Note that the drain current is held at 500 uA, which was previously selected as an efficient choice for the preamp. From the graph, we can see that the output voltage is significantly attenuated when the normalized latch transconductance is small. This means that the pull up load resistors are causing the output voltage to collapse because the holding effect of the latch is too weak. To hold the output voltage of the latch exactly, the normalized latch transconductance should be equal to 1. This is true because if conductances are equal, then any charge flowing out of the node through the resistors is replaced by current flowing into the node through the latching transistors (M5-M6). We can verify on this graph that if the normalized latch transconductance is set to 1, then the overall gain will be approximately 2 V/V and this is exactly the gain of the preamp. This results in a transistor size that can be calculated by the following equation.

$$\frac{W}{L} = \frac{\left(gm_{latch}\right)^{2}}{2I_{D}u_{n}Cox} = \frac{\left(gm_{latch\_normalized}\right)^{2}R^{2}}{2I_{D}u_{n}Cox}$$

(24)

We now have an idea how to ratio out the transistor current and transistor aspect ratio for the latch.

This type of analysis is adequate for schematic simulation and determining approximate device sizes but during layout, the transistor parasitics will greatly increase the time constant of the output node. This translates into similiar latch regeneration design requirements because two types of parasitics, capacitive and resistive, tend to cancel the effect of each other on latch performance. Note that holding the voltage is enhanced with a longer time constant because of the increased capacitive effects. However, the resistive gate polysilicion parasitics form a voltage divider and attenuate the actual voltage on the input of the latch which decreases the holding ability of the latch. Therefore, for the latch, the two parasitic effects, capacitive and resistive cancel to some degree. For the preamp, both types of parasitics work against the switching effect of the preamp. This causes the preamp design requirements to become more strict because the output voltage must be driven with more current to sufficiently change the voltage in the time allocated. Therefore during layout, a designer should expect a similar to calculated value for the size of the cross coupled pair (M5-M6) but an increase in the size of the preamp transisors (M3-M4).

This concludes the latch design section. The following section will provide some traditional performance plots used by analog designers during amplifier design. This will serve as a verification of the previous analysis.

#### 3.1.1.2 Preamp Design Equations

#### 3.1.1.2.1 Gain Bandwith

The gain bandwidth is the most pertinant to preamp performance because the preamp will be mostly operating with low gain at a high frequency and also the gain

bandwidth determines the ultimate settling time. Gain bandwidth product can be calculated by the following expression. Note that C is same as before.

$$Gain \, Bandwidth = \frac{gm_{M3}}{2\pi \, C} [Hz] \tag{25}$$

Figure 30: Preamp Gain Bandwidth Drain Current=500 uA

Figure 30 shows the gain bandwidth of the preamp as a function of preamp and latch transconductances. This will given an idea of the optimal ratio between the preamp and the latch transconductance. The optimal parameters for maximum gain bandwidth are a normalized preamp transconductance of 2 and a normalized latch transconductance as small as allowable. The maximum unity gain frequency occurs around 15 GHz. Note that both the drain currents of the preamp and latch sections are set to 500uA and a

normalized preamp transconductance of 2 implies a DC gain of 2 V/V which agrees with the previous section.

Figure 31: Gain Bandwidth Drain Current=1 mA

Figure 31 shows the same plot when the drain current level is doubled. The gain of the preamp increases approximately 8 GHz compared to the first case, however, the expected operating frequency of the latch is only 3.25 GHz. Therefore, a preamp unity gain frequency around 20-25 GHz which is nearly 20 GHz higher seems to be overdesign. Although in a layout implementation, this may not be over-design. In any case, we will base the rest of the preamp performance plots on a drain current of 500 uA.

Figure 32: Alternate Top Views of a) Figure 30 and b) Figure 31

As further confirmation of the previous conclusion, Figure 32 shows top views of the previous 3-D mesh plots which reduces to a colored contour graph. It shows that the best value of the preamp transconductance should be in the vicinty of two times the conductance of a resistor. If the current is doubled to 1 mA, the best value of the preamp transconductance is still about 2 times the conductance of a resistor but the actual bandwidth increases. Therefore, we will keep for design values a drain current of 500 uA and set the normalized preamp transconductance to 2. This is because for any current level and for low normalized latch transconductances, this configuration is optimal. Note that if the normalized latch transconductance is less than one then the preamp circuit will maintain high Gain Bandwidth. On the other hand, if the preamp transconductance is less than 2, then the preamp circuit is under-powered and not optimal. One other thing to notice is that if normalized latch transconductance is equal to 1 or less then the preamp transconductance can be increased up to approximately 4 before gain bandwidth begins to drop significantly.

#### 3.1.1.2.2 Pole Frequency

The pole or 3-dB frequency can also be plotted for a given transistor setup.

$$|A_{v}(\omega)| = \frac{|gm_{preamp}R|}{\sqrt{1 + \left(\frac{\omega}{\omega_{3-dB}}\right)^{2}}} = \frac{|gm_{preamp}R|}{\sqrt{1 + (\omega RC)^{2}}}$$

(26)

$$f_{3-dB} = \frac{1}{2\pi RC} \left[ H_Z \right] \tag{27}$$

Figure 33: Pole Frequency vs Normalized Preamp Transconductance

With a drain current of 500  $\mu$ A, a normalized latch transconductance of 1 and normalized preamp transconductance of 2, the expected pole frequency is approximately 9 GHz as shown in Figure 33 which is well above the 3.5 GHz expected output frequency of the 4/5 synchronous prescaler core. We must now be sure that the gain at this frequency is at least unity plus some margin. The pole frequency is defined in the following equation.

$$A_{V}\left(\omega_{3-dB}\right) = \frac{gm_{M3}R}{\sqrt{2}}\tag{28}$$

Figure 34: Gain at Expected Operating Frequency

The expected gain at that pole frequency for our setup is approximately 1.8 V/V as shown in Figure 34 which is greater than the required 1 V/V by a factor of 1.8 giving some gain margin.

### 3.1.1.2.3 Preamp Time Constant

The number of time constants over which the preamp will have to settle is a time domain representation of the previous section results. This is true in the sense that these two calculations show the gain variation with frequency compared to DC gain value. The expression is given in the following equation.

Number of

$$\tau = \frac{2\pi}{2F_{in}RC} = \frac{\pi}{F_{in}RC}$$

(29)

In this expression, the input frequency is a given and the only design parameters are the load resistance and capacitance which are minimized with additional current.

**Figure 35: Number of Time Constants**

The number of time constants over which the preamp will be allowed to settle vs normalized preamp transconductance is shown in Figure 35. As expected, for a given current level, both the preamp and latch transconductances (transistor widths) should be minimized to allow the most number of time constants. For our previous design choices for transconductances, the circuit will have approximately 2.25 time constants to settle which should be sufficient to establish a valid digital symbol.

$$(1 - e^{-2.25}) = .89 (30)$$

Figure 36: Preamp Transistor Sizing (M3-M4)

In Figure 36, the required size of the transistor can be read right off the graph. Earlier we choose a normalized preamp transconductance of 2 which is equivalent to a DC gain of 2 V/V. We stated that the drain current should be .5 mA. The graph corresponds to a DC gain of 2 V/V and shows we should select a transistor width of just

over 3.5 µm at point 1. The preamp transistor sizing setup for the layout is shown at point 2 to highlight the large effect of layout extracted parasities on circuits operating at 3.25 GHz.

Figure 37: Latch Width vs Latch Transconductance

In Figure 37, the width of the latch transistor is chosen. The current is set to 500  $\mu$ A, the preamp transistors are sized such that the DC gain of the preamp is 2 V/V, and the length is minimum size. The design choice of a normalized latch transconductance of 1 can be realized if the latch transistors are .8  $\mu$ m wide as shown at point 1. The setup for layout is shown at point 2, which is a much smaller shift compared to the preamp. This disparity in layout size shift is expected as discussed previously in the conclusion of the latch design section.

**Table 7: Typical Values from Design Equations**

|             | 4/5 Core |  |

|-------------|----------|--|

| Input Freq  | 13 GHz   |  |

| Output Freq | 3.25 GHz |  |

| M3, M4      | 3.5 u    |  |

| M5, M6      | .8 u     |  |

| ld          | 500 A    |  |

| R           | 800 Ohms |  |

In Table 7, the calculated values of the most critical device sizes are shown. M1,M2 and M7 were not included because their drain node is attached to low impedance nodes. This means the time constants at those nodes is already very low and will not be the limiting factor in performance. This group of transistor should be sized large enough to flow enough current, about 500 uA to M3-M4 or M5-M6. This can easily be found in simulation. In this way, they are the power limiters of the circuit. If they are sized too small, operating bandwidth can suffer significantly. If sized too large, power consumption will be very high and the circuit will have greater than required bandwidth. The lower frequency D-flip flips are not arranged in ring oscillator fashion like the 4/5 core. Therefore, the load impedance of the the lower frequency dividers is very different which means the a new small signal model would have to be derived for the new circuit architecture and this task will be left to the reader.

Figure 38: Preamp Phase of 4/5 Core

In Figure 38, typical voltages and currents during the preamp phase are shown. Note that ideally, the sine wave input is converted into a square wave at lower frequency.

In Table 8, the actual transistor widths used in the final layout are given. All lengths are set to minimum which is .18  $\mu m$ .

**Table 8: Typical Layout Values for D Flip Flops**

|             | 4/5 Core | 1st Async | 2nd Async |  |

|-------------|----------|-----------|-----------|--|

| Input Freq  | 13 GHz   | 3.25 GHz  | 1.625 GHz |  |

| Output Freq | 3.25 GHz | 1.625 GHz | 812.5 MHz |  |

| M1, M2      | 15 u     | .9 u      | 1.2 u     |  |

| M3, M4      | 10 u     | 3 u       | 3 u       |  |

| M5, M6      | 1.08 u   | 1.9 u     | 4 u       |  |

| M7          | 50 u     | 40 u      | 40 u      |  |

| ld          | 1.4 mA   | 280 uA    | 85 uA     |  |

| R           | 850 Ohms | 3 kOhms   | 3.7 kOhms |  |

The values are for layout and therefore take into account a large number of parasitics. If these values were placed directly into Cadence simulator, the operating frequency band would be significantly shifted to higher frequencies. Notice from the table that the lower the frequency of operation, the larger the load resistor can be. A larger load resistor can provide sufficient voltage swing for the following circuit with less current. This explains the large power consumption disparity between the core dividers and the feedback dividers. The size of the M1.M2 differential pair determines the operating bandwidth of the divider because they act as the current source for the M3,M4 differential pair. If the M3,M4 differential pair can completely switch the current during one phase, then an increase in M3,M4 width will not provide any benefit but instead add parasitic capacitance. However increasing the width of M1, M2 will increases the available drain current for switching, which effectively reduces the output resistance of M3,M4 lowering the time constant at the output. Additionaly, the increase of M1,M2 width will increase the parasitic capacitance and the drains of M1,M2 but this effect is not important that node is already a low impedance node. This fact rises this question of why not make M1,M2 very wide for maximum bandwidth? The answer is a very wide M1, M2 will significantly load the preceding circuit which happens to be a VCO trying to achieve a very high operating frequency. Furthermore, due to the limited tuning range of the VCO, the VCO probably cannot produce frequencies in most of that maximum bandwidth.

This concludes the design section of the CML D. All optimal transistor sizes have been determined as a function of drain current.

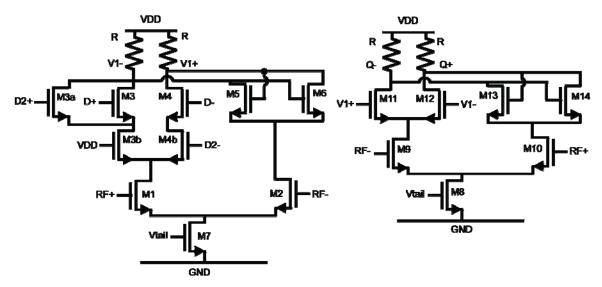

### 3.2 Feedback Logic Implementation

The implementation of the feedback logic will be discussed in the following pages. Most high frequency prescaler use current mode logic for the entire device [28]. This implementation will use transmission gate logic (TGL) to reduce the static power dissipation. We will first discuss the TGL NOR gate which is the heart of the feedback logic. Then we will proceed to add other parts of the logic until the entire logic section is discussed.

Figure 39: Gate Level Representation of Figure 40

In Figure 39, the highlighted NOR shows explictly what part will be under discussion first. The figure shows single-ended signals for clarity but the actual implementation is differential.

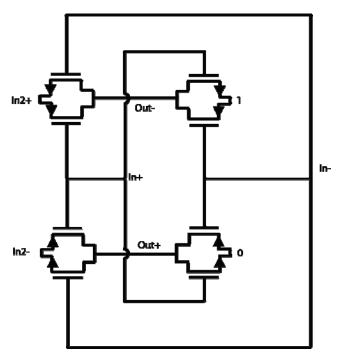

Figure 40: Generic TGL OR Gate

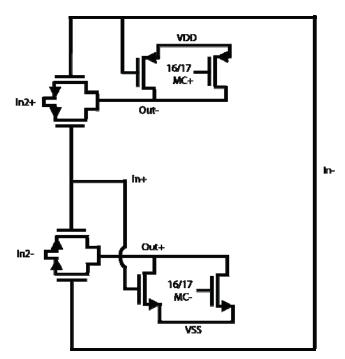

The basic operation of a generic differential TGL OR Gate (Figure 40) can be understood through a few key elements. Depending on the level of differential (In+/-) input the output (Out+/-) will be connected to either (In2+/-) or the power rails for a one. If (In+/-) is a one then the right TGs are open while the left TGs are closed and the output becomes a one. If (In+/-) is a zero, then the right TGs are closed while the left are open and the output follows the (In2+/-) input. The advantage of such a topology is the lack of static power dissipation as opposed to a CML NOR gate which would require differential pairs and tail currents. Since the operating frequency is 755 MHz in this section, the high speed of CML is not required. The circuit can also be configured as a NOR gate as shown in the gate level schematic by taking the differential outputs with opposite polarity.

The following pages will walk the reader through the step by step modifications made to the transmission gate logic NOR gate.

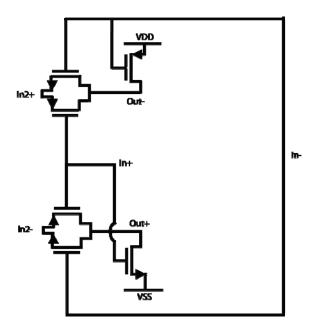

Figure 41: NOR Gate Modification 1

The first modification, shown in Figure 41, was noticing that the right hand transmission gates were connected to a supply rail. This means they are operating in a pull-up or pull-down mode as opposed to left hand transmission gates which are passing a bi-directional signal. Therefore, depending on which supply rail the source is connected to, one transistor can be eliminated from each transmission gate. The PMOS transistor, with source connected to the ground, and the NMOS transistor, with source connected to VDD, will never turn on and are unnecessary. Now, we will add the AND gate into our circuit, it is shown in Figure 42.

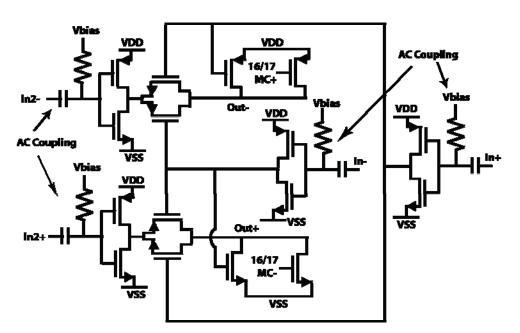

Figure 42: Gate Level Representation of Figure 43

Figure 43: NOR Gate Modification 2

After the first modification, we have a TGL NOR gate with no extra inactive transistors. If this NOR gate is placed into the prescaler directly, it would lead to a divide by 17 only divider with no way to change to divide by 16. There must a way to disconnect the NOR gate from the 4/5 core or at least force the output nodes of the NOR gate to the desired value in Figure 43. This is accomplished by adding two more transistors which are sized large enough to hold the NOR output voltage to a certain polarity. In Figure 43, the transistors with their gates attached to 16/17 MC +/- provide this functionality. Note that Figure 42 is a gate level representation of Figure 43. Forcing the 16/17 MC +/- signal to zero allows disconnection of modulated feedback and provides a constant zero feedback resulting in a division ratio of 16. Therefore, the 16/17 MC+/- signal controls the overall division ratio of the prescaler. The next section is about the inverters highlighted in Figure 44 and shown at transistor level in Figure 45.

Figure 44: Gate Level Represenation of Figure 45

Figure 45: NOR Gate Modification 3

These inverters serve as the overall prescaler output buffer, level shifter and amplifier from CML to TGL. They also decouple the output impedance of the CML divider from the input impedance of the TGL CMOS. To convert from low voltage swing CML to large voltage swing TGL, it is necessary to re-center the DFF output signal at VDD/2. CML requires transistors with highly inverted channels which leads to large overdrive voltages. This means that the DFF output signal is usually centered well above VDD/2, typically at 1.4 V. The ac coupling ensures the input of the CMOS inverters will be centered at VDD/2 or 900 mV. These CMOS inverters use very little static power, have the largest signal gain of any amplifer and create a better rail to rail signal for the TGL NOR gate output (Out-/+). The output of TGL (Out -/+) is applied directly to the high impedance input of the 4/5 core with no buffering. Transistor size in this section is as small as possible to minimize parasitics and chip area. However, the onresistance of the transmission gate is proportional to the width of the transistors and this places a restriction on their minimum sizes. Decoupling of the impedances is a critical feature because the operation of the divider is highly dependent on the load impedance of the divider. The load impedance is the input impedance of a transmission gate which intentionally varies greatly depending on whether it is on or off.

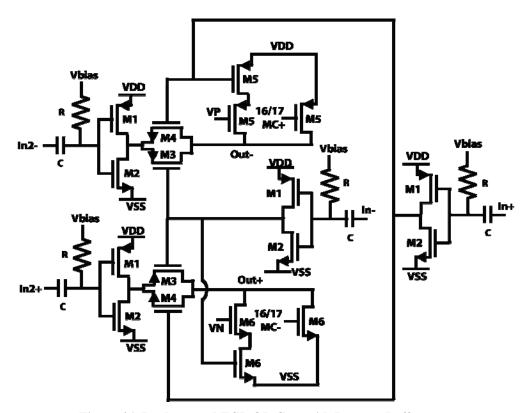

Figure 46: Implemented TGL OR Gate with Inverter Buffers

The final modification is included solely as a precaution to ensure NOR operation in the event that the fabrication process results in corner silicon. The cascode transistors M5,M6 are included to allow control over the driving strength of the pull up and pull down transistors, added in Figure 46. If the process is slow and the output voltage (Out-/+) cannot be effectively pulled up and/or pulled down, then the 4/5 core will not ever shift into divide by 5 mode resulting in divide by 16 mode only. However, if the process is fast and the output voltage is overdriven, then the 4/5 core will take too long to recover and return from divide by 5 mode. The net result is that instead of divide by 17 mode, the circuit will divide by 18. The adjustment can be performed by adjusting VN and VP. For instance, if the process is very slow VN will be set to VDD and VP will be set to VSS. If the process is fast then the VN can be decreased while VP is increased until the desired division ratio of 17 is achieved.

### 3.2.1 Design Equations for Feedback Logic Section

The inverters and transmission gates can be modelled by an inverter with a second order RC low pass filter as shown in Figure 47.

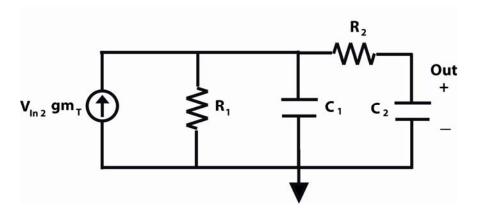

Figure 47: Small Signal Model of TGL NOR Gate

The input transconductance,  $gm_T$ , is the total transconductance of the NMOS and PMOS transistors, M1-M2, in the inverters. Note that this analysis neglects the  $C_{gs}$  and  $C_{gd}$  of the transmission gates for simplicity as the addition of two more capacitors to the model would result in a fourth order system.

$$\frac{Vo}{Vi} = \left(gm_{NMOS} + gm_{PMOS}\right) \left(\frac{\frac{s}{R_1C_1} + \frac{1}{R_1C_1R_2C_2}}{s^2 \frac{1}{R_1R_2} + s\left(\frac{1}{C_1R_2} + \frac{1}{C_2R_2} + \frac{1}{C_1R_1}\right) + \frac{1}{R_1C_1R_2C_2}}\right)$$

(31)

Where  $R_1$  is the total output resistance of the inverter on the In2- input and given by the following expression.