# PASSIVE AND ACTIVE CIRCUITS IN CMOS TECHNOLOGY FOR RF, MICROWAVE AND MILLIMETER WAVE APPLICATIONS

A Dissertation

by

# MOHAN KRISHNA CHIRALA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2007

Major Subject: Electrical Engineering

# PASSIVE AND ACTIVE CIRCUITS IN CMOS TECHNOLOGY FOR RF, MICROWAVE AND MILLIMETER WAVE APPLICATIONS

## A Dissertation

by

## MOHAN KRISHNA CHIRALA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Cam Nguyen

Committee Members, Edgar Sánchez-Sinencio

Chin B. Su

David A. Church

Head of Department, Costas N. Georghiades

December 2007

Major Subject: Electrical Engineering

#### ABSTRACT

Passive and Active Circuits in CMOS Technology for RF, Microwave and Millimeter

Wave Applications. (December 2007)

Mohan Krishna Chirala, B.E., Osmania University, India;

M.S., University of Cincinnati

Chair of Advisory Committee: Dr. Cam Nguyen

The permeation of CMOS technology to radio frequencies and beyond has fuelled an urgent need for a diverse array of passive and active circuits that address the challenges of rapidly emerging wireless applications. While traditional analog based design approaches satisfy some applications, the stringent requirements of newly emerging applications cannot necessarily be addressed by existing design ideas and compel designers to pursue alternatives. One such alternative, an amalgamation of microwave and analog design techniques, is pursued in this work.

A number of passive and active circuits have been designed using a combination of microwave and analog design techniques. For passives, the most crucial challenge to their CMOS implementation is identified as their large dimensions that are not compatible with CMOS technology. To address this issue, several design techniques – including multi-layered design and slow wave structures – are proposed and demonstrated through experimental results after being suitably tailored for CMOS technology. A number of novel passive structures - including a compact 10 GHz hairpin

resonator, a broadband, low loss 25-35 GHz Lange coupler, a 25-35 GHz thin film microstrip (TFMS) ring hybrid, an array of 0.8 nH and 0.4 nH multi-layered high self resonant frequency (SRF) inductors are proposed, designed and experimentally verified.

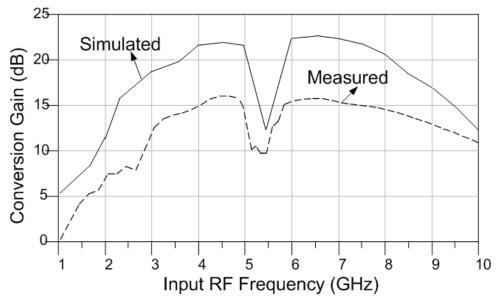

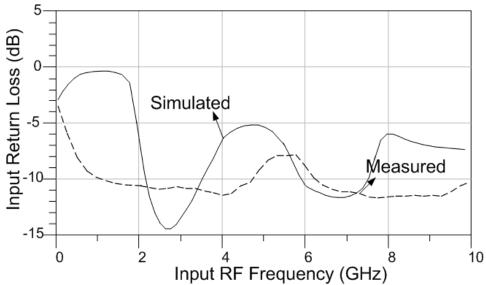

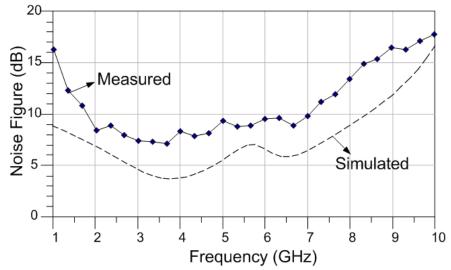

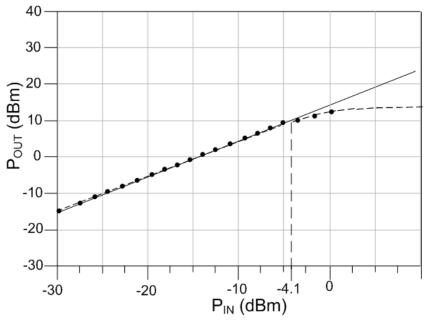

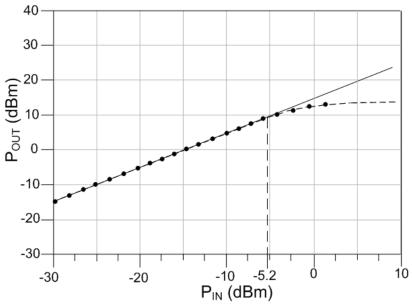

A number of active circuits are also designed and notable experimental results are presented. These include 3-10 GHz and DC-20 GHz distributed low noise amplifiers (LNA), a dual wideband Low noise amplifier and 15 GHz distributed voltage controlled oscillators (DVCO). Distributed amplifiers are identified as particularly effective in the development of wideband receiver front end sub-systems due to their gain flatness, excellent matching and high linearity. The most important challenge to the implementation of distributed amplifiers in CMOS RFICs is identified as the issue of their miniaturization. This problem is solved by using integrated multi-layered inductors instead of transmission lines to achieve over 90% size compression compared to earlier CMOS implementations. Finally, a dual wideband receiver front end sub-system is designed employing the miniaturized distributed amplifier with resonant loads and integrated with a double balanced Gilbert cell mixer to perform dual band operation. The receiver front end measured results show 15 dB conversion gain, and a 1-dB compression point of -4.1 dBm in the centre of band 1 (from 3.1 to 5.0 GHz) and -5.2 dBm in the centre of band 2 (from 5.8 to 8 GHz) with input return loss less than 10 dB throughout the two bands of operation.

To my mother, Indira Devi...

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to sincerely thank my advisor and committee chair, Dr. Cam Nguyen, who has taken the trouble of guiding me towards the end of my graduate studies at Texas A&M University and for having faith in my ability to perform research of high caliber in this intensely challenging field.

I would also like to thank my committee members, Dr. Edgar Sánchez-Sinencio, Dr. Chin B. Su and Dr. David A. Church, for their guidance and support, particularly during my preliminary examinations that led to a more definite shaping of my research work.

Thanks also go to my dear friends in Texas - my lab mates cum room mates Xin Guan and Rui Xu, not just for their technical discussions time and again but also for their friendship. My good friends - Alexandre Veniamin, Samuel Kokel, Marina Kovina and "Professor" Baski must be acknowledged for their friendship that has been tried and tested over the course of several years. My profound thanks are also due to Dr. Mahadevan Sridharan, president of Z~Communications, for giving me a full time employment opportunity in San Jose, CA. I also wish to thank the National Science Foundation that supported a part of my research work and the staff at the electrical engineering department of Texas A&M University, particularly Ms. Tammy Carda, for being extremely helpful on all departmental issues.

Finally, I would like to acknowledge my loving parents and my sister Yamini for their unwavering love and support.

# TABLE OF CONTENTS

|                                                     | Page |

|-----------------------------------------------------|------|

| ABSTRACT                                            | iii  |

| DEDICATION                                          | V    |

| ACKNOWLEDGEMENTS                                    | vi   |

| TABLE OF CONTENTS                                   | vii  |

| LIST OF FIGURES                                     | X    |

| LIST OF TABLES                                      | xvii |

| CHAPTER                                             |      |

| I INTRODUCTION                                      | 1    |

| 1.1 Research motivation                             | 2    |

| 1.2 Dissertation overview                           | 4    |

| II DISTRIBUTED PASSIVE CIRCUITS                     | 6    |

| 2.1 Overview of existing miniaturization techniques | 7    |

| 2.1.1 Couplers                                      | 7    |

| 2.1.2 Resonators                                    | 13   |

| 2.1.3 Inductors                                     | 19   |

| 2.2 Design of microwave structures in CMOS          | 22   |

| 2.2.1 Properties of silicon based substrates        | 23   |

| 2.2.2 Microstrip vs CPW                             | 25   |

| 2.3 The slow-wave theory                            | 27   |

| 2.3.1 Basic principles                              | 28   |

| 2.3.2 Existing slow wave structures                 | 30   |

| 2.3.3 Design of slow wave structures in CMOS        | 34   |

| 2.3.4 Principles of Defective UC-PBG                | 38   |

| 2.3.5 High-Q D-UCPBG Hairpin resonator              | 39   |

| 2.4 Multi-layered design techniques                 | 46   |

| 2.4.1 TFMS broadside coupled Lange coupler          | 47   |

| CHAPTER                                                         | Page |

|-----------------------------------------------------------------|------|

| 2.4.2 TFMS ring hybrid coupler                                  | 57   |

| 2.4.3 Vertically coiled inductors                               | 65   |

| 2.4.4 Complementary slow wave structures                        | 72   |

| 2.5 Applications of microwave passives in CMOS design           | 78   |

| 2.5.1 Balanced amplifiers                                       | 79   |

| 2.5.2 Mixers and phase shifters                                 | 81   |

| 2.5.3 Push-push voltage controlled oscillator                   | 83   |

| 2.3.3 Tush-push voltage controlled oscillator                   | 03   |

| III BROADBAND LOW NOISE AMPLIFIERS                              | 85   |

| 3.1 Concurrent dual wideband low noise amplifier                | 86   |

| 3.1.1 Principles of concurrent dual wideband LNAs               | 87   |

| 3.1.2 Amplifier design                                          | 92   |

| 3.1.3 Implementation and results                                | 93   |

| 3.2 Theory of distributed amplification.                        | 97   |

| 3.3 Overview of CMOS distributed low noise amplifiers           | 100  |

| 3.3.1 Design issues                                             | 101  |

| 3.3.2 Topologies                                                | 102  |

| 3.4 A DC-20 GHz distributed low noise amplifier                 | 103  |

| 3.4.1 Basic principles                                          | 104  |

| 3.4.2 Integration of inductors and transmission lines           | 106  |

| 3.4.3 Design                                                    | 107  |

| 3.4.4 Results                                                   | 110  |

| 3.5 An ultra-compact distributed LNA for UWB applications       | 112  |

| 3.5.1 Background and justification                              | 112  |

| 3.5.2 Integration issues in vertically coiled inductors         | 114  |

| 3.5.3 Amplifier design and layout                               | 119  |

| 3.5.4 Measurement results                                       | 120  |

| IV DISTRIBUTED VOLTAGE CONTROLLED OSCILLATORS                   | 125  |

| 4.1 Theory of distributed voltage controlled oscillators (DVCO) | 126  |

| 4.2 LC tank based VCOs Vs distributed VCOs                      | 129  |

| 4.3 Multi-stage DVCOs using inductors                           | 130  |

| 4.4 A 15 GHz CMOS DVCO with wide tuning range                   | 133  |

| 4.4.1 Design principles                                         | 133  |

| 4.4.2 Implementation and results                                | 136  |

| CHAPTER                                                | Page |

|--------------------------------------------------------|------|

| V DUAL BAND UWB RECEIVER SUBSYSTEM                     | 138  |

| 5.1 UWB communications                                 | 139  |

| 5.2 Multi-band receiver systems                        | 143  |

| 5.2.1 Heterodyne architecture                          | 143  |

| 5.2.2 Homodyne architecture                            | 144  |

| 5.2.3 Image reject architecture                        | 145  |

| 5.2.4 Concurrent narrow-band architecture              | 146  |

| 5.3 Dual band UWB receiver front end.                  | 148  |

| 5.3.1 Principles of concurrent dual band UWB front end | 149  |

| 5.3.2 Receiver architecture                            | 151  |

| 5.3.3 Front end design issues and specifications       | 153  |

| 5.4 Front end circuit blocks                           | 155  |

| 5.4.1 Concurrent dual wideband distributed LNA         | 155  |

| 5.4.2 High gain active BALUN                           | 163  |

| 5.4.3 Differential down conversion mixer               | 166  |

| 5.4.4 Buffer amplifier                                 | 169  |

| 5.5 Integration issues                                 | 170  |

| 5.6 Measurement results                                | 173  |

| VI CONCLUSIONS                                         | 178  |

| 6.1 Summary                                            | 178  |

| 6.2 Recommended future work                            | 179  |

| 6.2.1 Passives                                         | 179  |

| 6.2.2 Distributed actives                              | 180  |

| 6.2.3 Dual wideband receiver sub-system                | 181  |

| REFERENCES                                             | 182  |

| APPENDIX A                                             | 197  |

| APPENDIX B                                             | 200  |

| VITA                                                   | 202  |

# LIST OF FIGURES

| FIGURE                                  |                                                                                                            | Page |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------|------|

| 1.1 Estimated number                    | r of wireless subscribers in USA                                                                           | 2    |

|                                         | ar MMIC couplers (a) Ring hybrid (b) Wilkinson coupler and (d) Branchline coupler                          | 8    |

| • • • • • • • • • • • • • • • • • • • • | resonators (a) Uniform impedance (b) Stepped                                                               | 14   |

|                                         | ce resonators (a) quarter-wavelength $(\lambda_g/4)$ (b) half-<br>and (c) full wavelength $(\lambda_g)$ .  | 16   |

| . ,                                     | hairpin resonator (b) internally coupled hairpin type resonator with internal coupling.                    | 17   |

|                                         | ectors in CMOS (a) rectangular (b) octagonal and                                                           | 19   |

|                                         | actors in CMOS (a) vertically stacked (b) vertical                                                         | 22   |

| 2.7 Graphical represe                   | entation of (a) CMOS and (b) Duroid/RT substrates                                                          | 25   |

|                                         | ribution in a high impedance (a) Microstrip and OS.                                                        | 27   |

|                                         | wave lattices (a) circular (b) rectangular (c) rectangular                                                 | 30   |

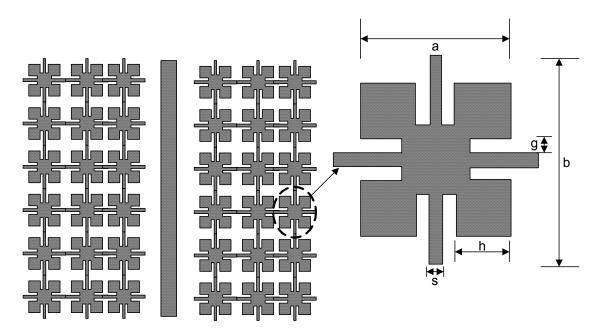

|                                         | s a CPW ground plane with the unit cell shown in the                                                       | 31   |

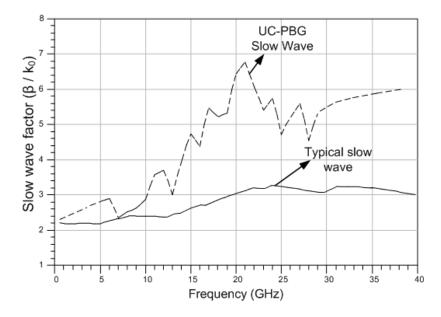

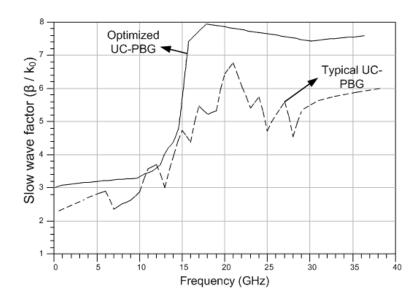

|                                         | vave factors of silicon substrate based UC-PBG structure l slow wave structure shown in figure 2.9 (c).    | 32   |

| gap on the slow w                       | JC-PBG reflecting the impact of strip length, width and vave factor. Also shown is the un-optimized UC-PBG | 35   |

| FIGU | FIGURE                                                                                                                                                                                                                                                                                |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

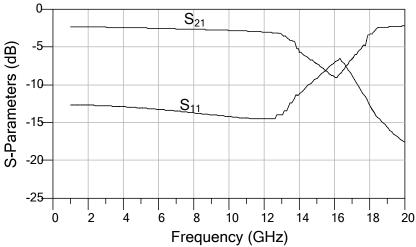

| 2.13 | Microstrip based UC-PBG structure. Metal 5 was used for the Microstrip line and Metal 1 for the UC-PBG ground plane                                                                                                                                                                   | 36 |

| 2.14 | S-parameters of the UC-PBG incorporating 50 $\Omega$ Microstrip line on a 5-metal layer CMOS technology.                                                                                                                                                                              | 37 |

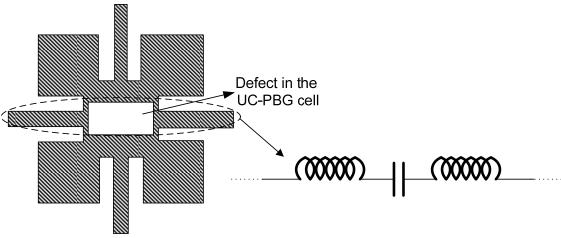

| 2.15 | Defect in the UC-PBG cell.                                                                                                                                                                                                                                                            | 38 |

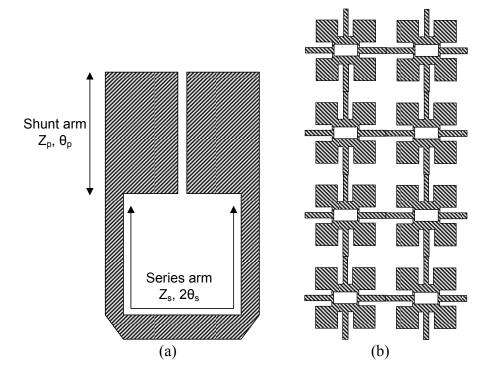

| 2.16 | (a) Hairpin resonator on top metal and (b) 2 x 4 D-UCPBG lattice as ground plane.                                                                                                                                                                                                     | 40 |

| 2.17 | Basic stepped impedance resonator.                                                                                                                                                                                                                                                    | 41 |

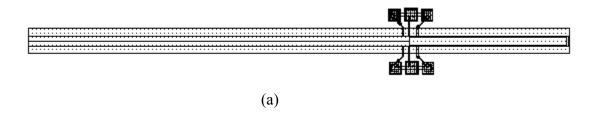

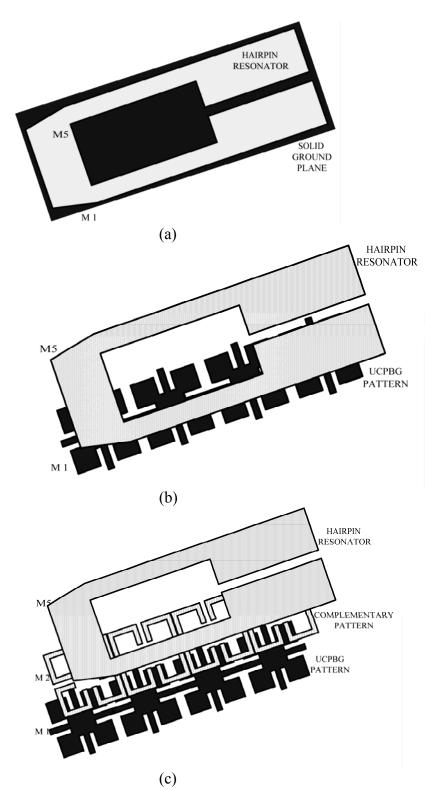

| 2.18 | Cadence layouts of the CMOS (a) solid-ground and (b)D-UCPBG ground hairpin resonators including on-wafer probe pads. The hairpin structure is on the top (Metal-5) and the D-UCPBG or solid ground is on the bottom (Metal-1), both connected to the on-wafer pads with CPW segments. | 43 |

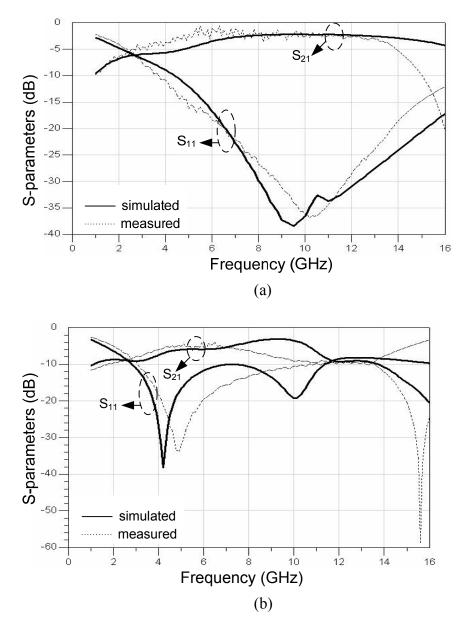

| 2.19 | Simulated and measured S-parameters of (a) solid ground plane based hairpin resonator and (b) D-UCPBG ground plane based hairpin resonator                                                                                                                                            | 44 |

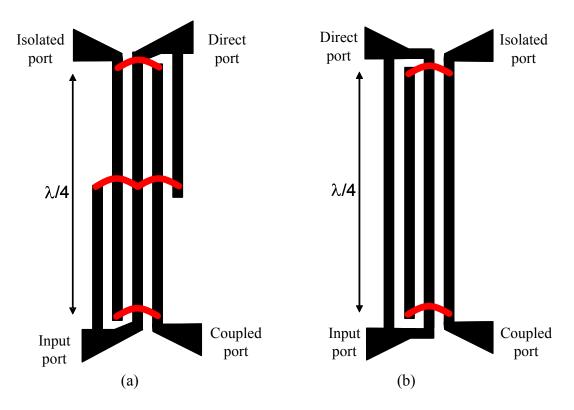

| 2.20 | (a) Folded and (b) un-folded Lange couplers with interconnections shown in red.                                                                                                                                                                                                       | 48 |

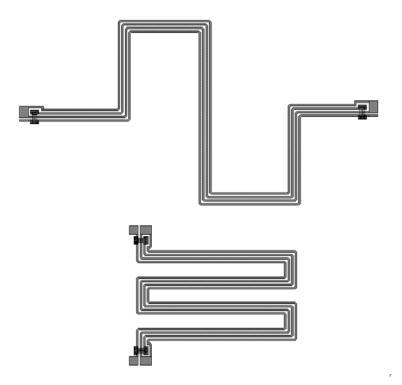

| 2.21 | Two different versions of silicon based Lange couplers with different kinds of aggressive meandering.                                                                                                                                                                                 | 49 |

| 2.22 | Layout of the proposed asymmetric broadside-coupled Lange coupler, with cross-section shown in the inset. The four fingers are implemented on the top four metal layers (M2-M5). The bottom metal layer (M1) is used as the ground plane.                                             | 50 |

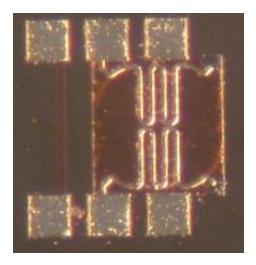

| 2.23 | Die photograph of the fabricated Lange coupler (217 x 185 μm without RF pads).                                                                                                                                                                                                        | 53 |

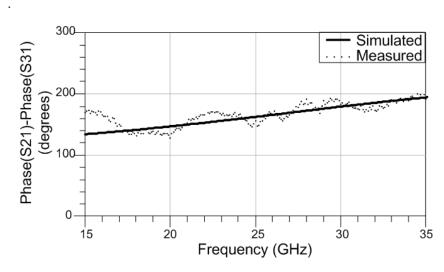

| 2.24 | Phase imbalance of the through and coupled ports. 1: input, 2: through, 3: coupled, and 4: isolated port.                                                                                                                                                                             | 54 |

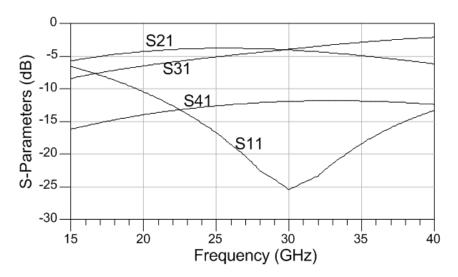

| 2.25 | Simulated S-parameters of the TFMS multi-layered Lange coupler. 1: input 2: through, 3: coupled, and 4: isolated port                                                                                                                                                                 | 55 |

| FIGU | JRE                                                                                                                                                                                                                                             | Page      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

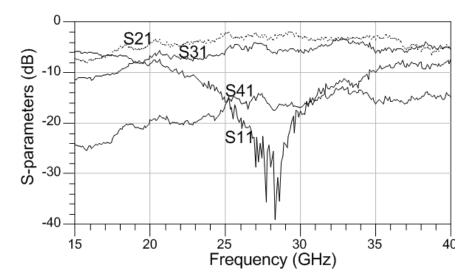

| 2.26 | Measured S-parameters of the TFMS multi-layered Lange coupler.  1: input, 2: through, 3: coupled, and 4: isolated port                                                                                                                          | . 55      |

| 2.27 | Ring hybrid structure implemented in FG-CPW incorporating a phase inverter. 1: isolation, 2: output, 3: input, and 4: output with 180° phase difference.                                                                                        | . 57      |

| 2.28 | Layout of a compact ring hybrid structure implemented in FG-CPW incorporating a phase inverter [51]. Each side measures 340 x 340 μm                                                                                                            | . 58      |

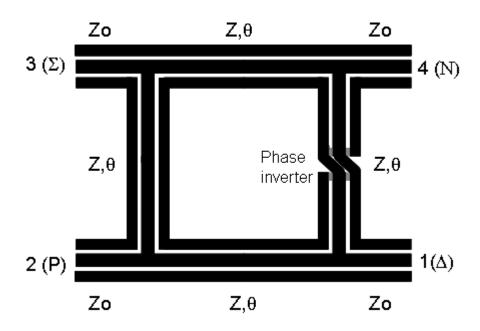

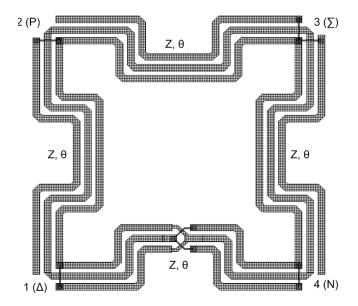

| 2.29 | An extremely compact multi-layered ring hybrid structure using TFMS microstrip lines.                                                                                                                                                           | . 59      |

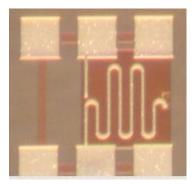

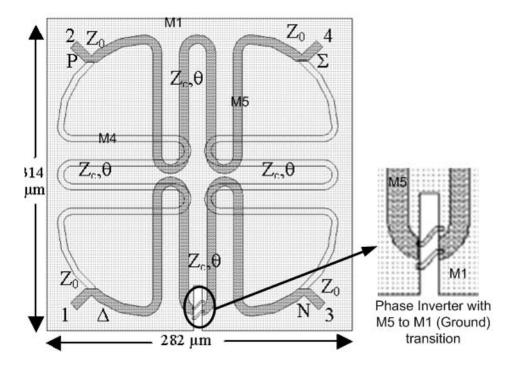

| 2.30 | Die photograph of the multi-layered ring hybrid coupler (314 x 282 μm without RF pads).                                                                                                                                                         | . 61      |

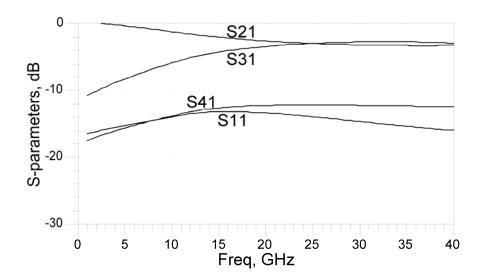

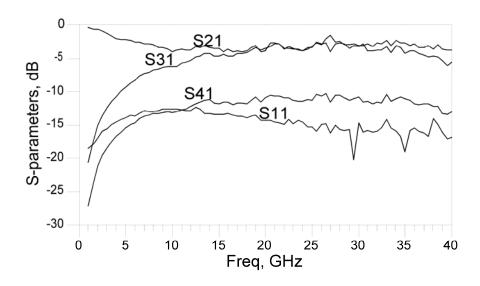

| 2.31 | Simulated S-parameters of the TFMS ring hybrid coupler.                                                                                                                                                                                         | . 62      |

| 2.32 | Measured S-parameters of the TFMS ring hybrid coupler.                                                                                                                                                                                          | . 63      |

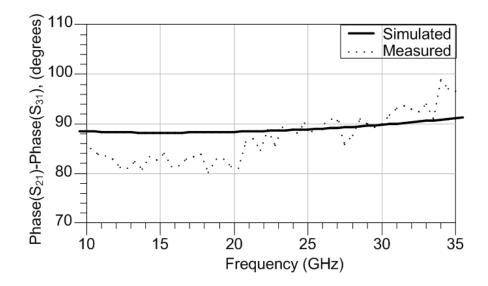

| 2.33 | Simulated and measured phase difference between coupled and inversion ports.                                                                                                                                                                    | . 63      |

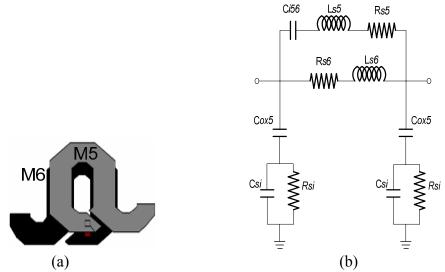

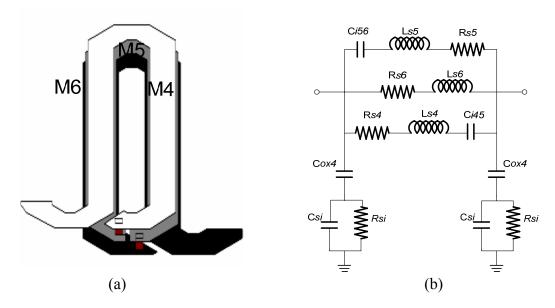

| 2.34 | (a) Two-layered inductor structure and (b) equivalent circuit                                                                                                                                                                                   | . 66      |

| 2.35 | (a) Three-layered inductor structure and (b) equivalent circuit                                                                                                                                                                                 | . 66      |

| 2.36 | (a) One-port model of the multi-layered inductor and (b) simplified one-port model of the multi-layer inductor for analyzing the inductor's self resonant frequency                                                                             | t<br>. 68 |

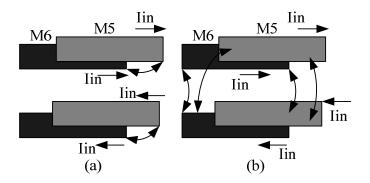

| 2.37 | (a) Positive and (b) negative mutual coupling in two-layered inductors                                                                                                                                                                          | . 71      |

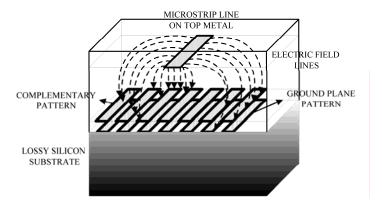

| 2.38 | Illustration of multi-layer slow wave pattern shielding the top metal passive structure from a lossy silicon substrate. Periodic parallel-strip patterns, different from those used in actual resonators, are used here for the sake of clarity | . 73      |

| 2.39 | Hairpin resonators with (a) solid ground plane (b) UC-PBG ground plane and (c) UC-PBG patterned ground plane with a complementary pattern on top                                                                                                | . 75      |

| FIGU | JRE                                                                                                                                                                                          | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

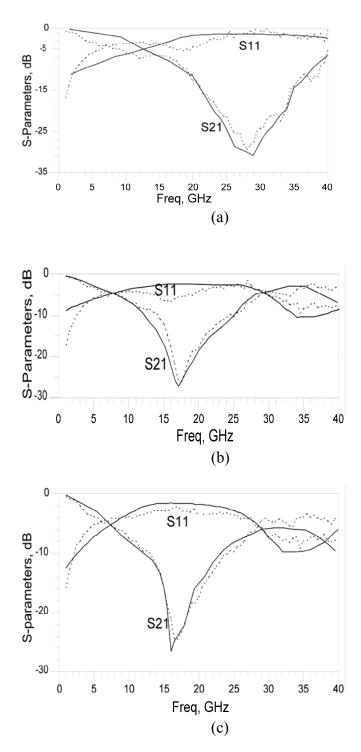

| 2.40 | S-parameters of the hairpin resonators with (a) solid, (b) UC-PBG, and (c) multi-layered UC-PBG ground planes. Solid and dotted lines indicate calculated and measured results, respectively | . 77 |

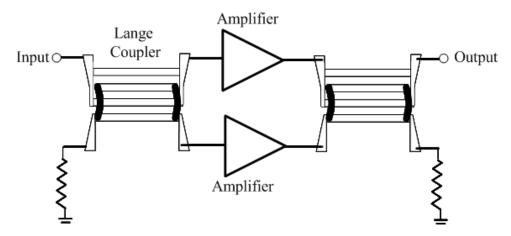

| 2.41 | Balanced amplifier topology using Lange couplers                                                                                                                                             | . 79 |

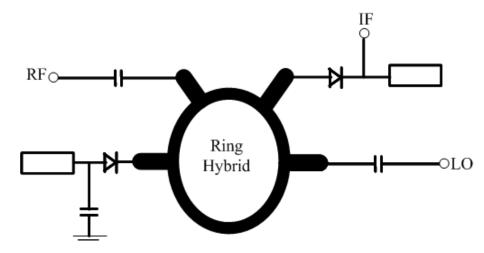

| 2.42 | Passive mixer topology using ring hybrid coupler for millimeter wave                                                                                                                         | 81   |

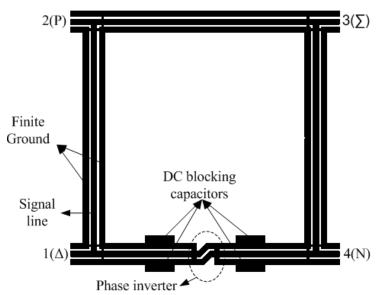

| 2.43 | A CMOS compatible DC isolated phase inverter for millimeter wave applications                                                                                                                | . 82 |

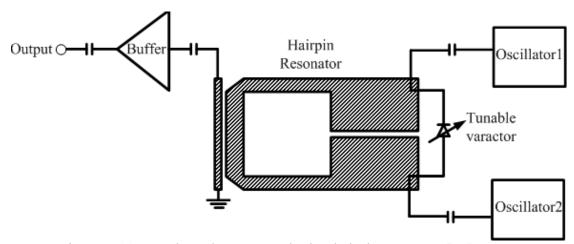

| 2.44 | A push-push VCO employing hairpin resonator                                                                                                                                                  | 83   |

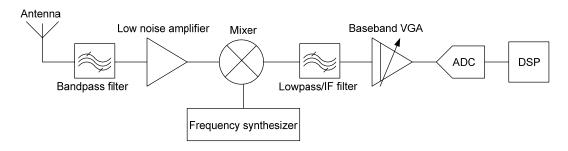

| 3.1  | Super-heterodyne receiver front-end                                                                                                                                                          | . 86 |

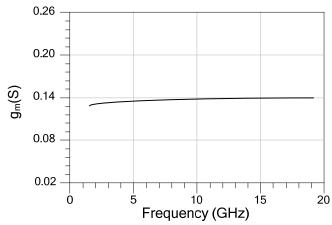

| 3.2  | Transconductance of common-source NMOS device with 100/0.25 aspect ratio biased in the saturation region                                                                                     | . 87 |

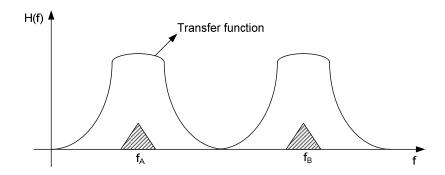

| 3.3  | Dual wideband LNA transfer function                                                                                                                                                          | . 88 |

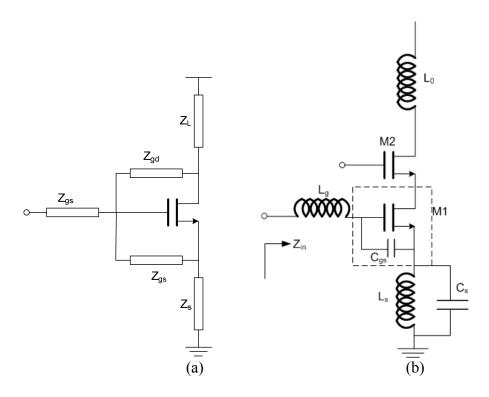

| 3.4  | (a) General schematic of a common source degenerated LNA (b) A Cascode source tuned LNA                                                                                                      | . 89 |

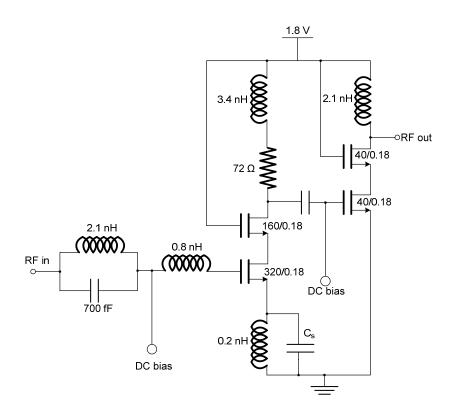

| 3.5  | Schematic of the cascode source tuned LNA                                                                                                                                                    | . 92 |

| 3.6  | Layout of the cascode source tuned LNA                                                                                                                                                       | 94   |

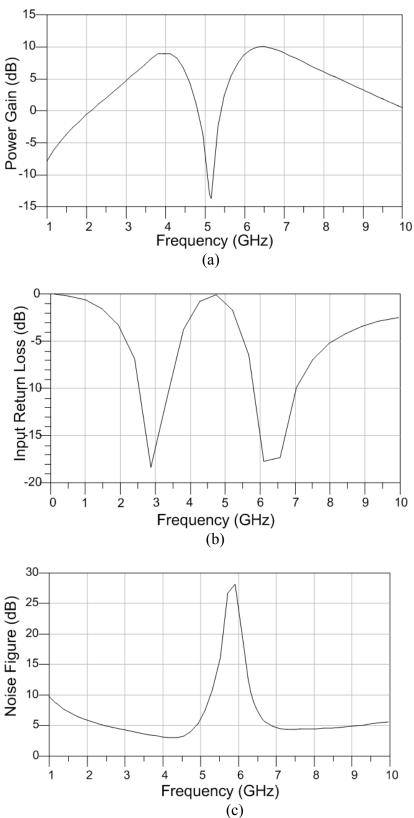

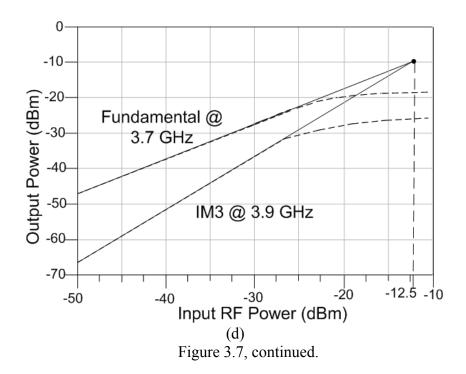

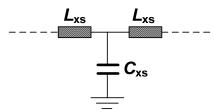

| 3.7  | Simulated performance of the LNA (a) power gain (b) input return loss (c) noise figure (d) simulated LNA response showing IIP3 in the first band                                             | . 95 |

| 3.7  | Continued                                                                                                                                                                                    | 96   |

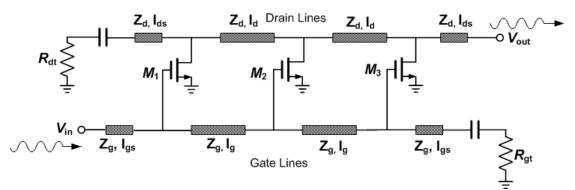

| 3.8  | Representation of a distributed amplifier employing transmission line segments                                                                                                               | . 98 |

| 3.9  | Unit cell of a distributed amplifier (x=d, g)                                                                                                                                                | 104  |

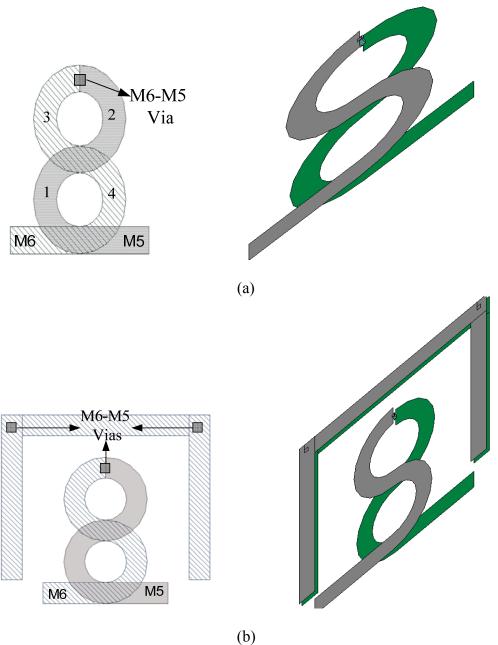

| 3.10 | (a) Novel octagonal multi-layered inductor and its 3-D view and (b) Inductor modified as a CPW transmission line with its 3-D view                                                           | 108  |

| FIGU | JRE                                                                                                                                           | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.11 | Layout of the 4-stage novel distributed amplifier employing transmission Lines and inductors                                                  | 109  |

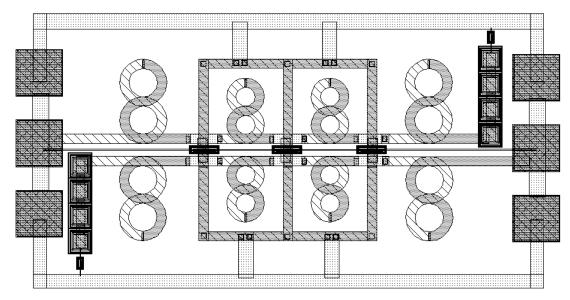

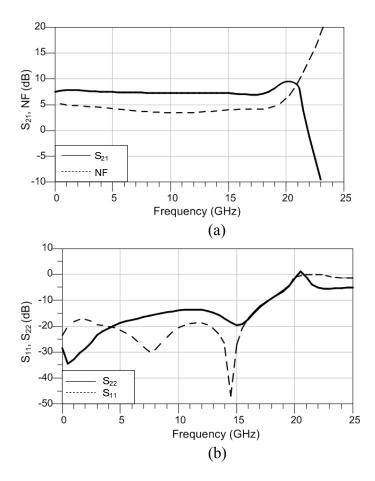

| 3.12 | Post layout simulation results of the novel multi-layered wideband LNA Showing (a) $S_{21}$ and noise figure (b) input and output return loss | 111  |

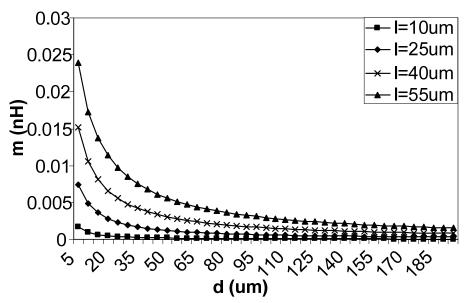

| 3.13 | Variation of mutual inductance with pitch for different metal lengths                                                                         | 114  |

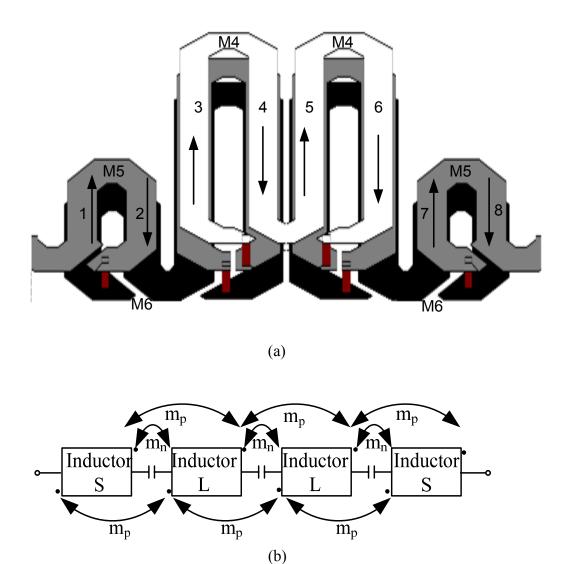

| 3.14 | (a) Integrated multi-layered inductor structure and (b) schematic representation of the above structure                                       | 115  |

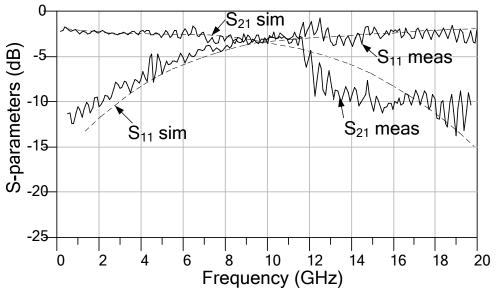

| 3.15 | S-parameters of the integrated inductor segment                                                                                               | 118  |

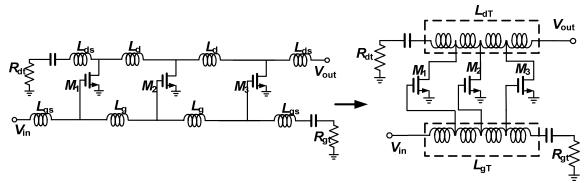

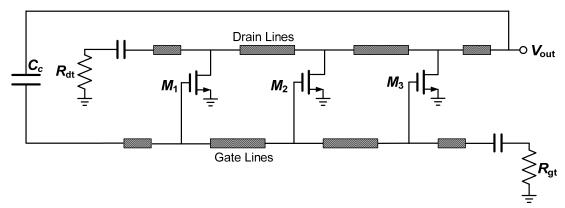

| 3.16 | Schematic of the modified distributed amplifier with 5-port inductor segments                                                                 | 119  |

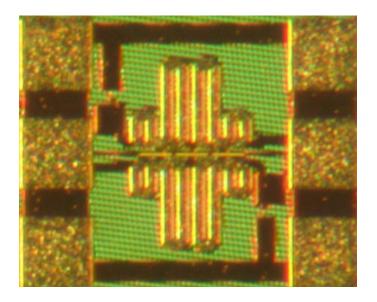

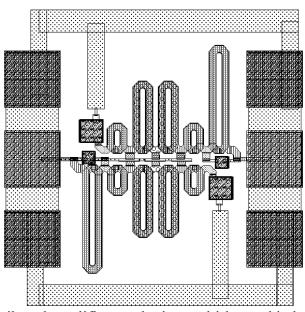

| 3.17 | Die photograph of the fabricated DA                                                                                                           | 120  |

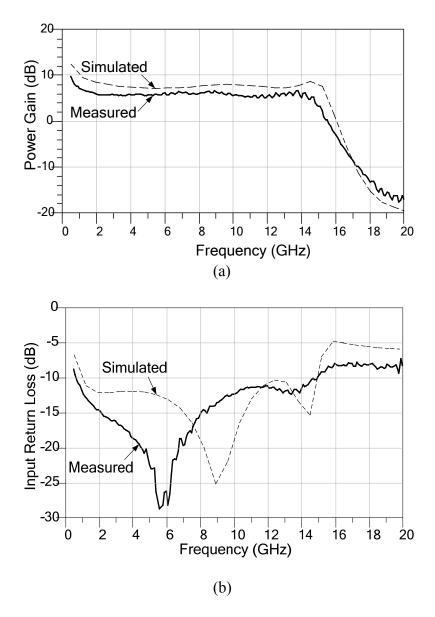

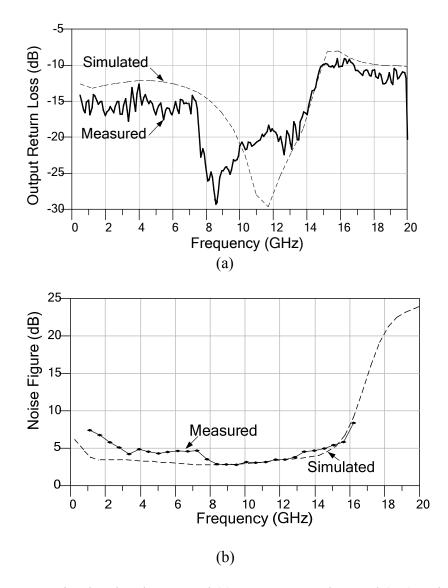

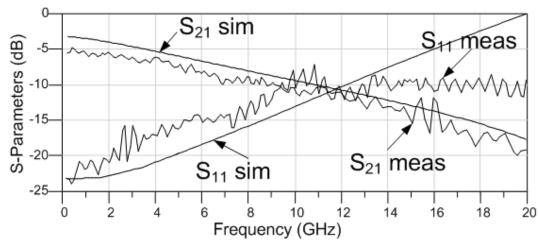

| 3.18 | Simulated and measured S-parameters of (a) power gain $(S_{21})$ and (b) input return loss $(S_{11})$                                         | 121  |

| 3.19 | Simulated and measured (a) output return loss and (S <sub>22</sub> ) and (b) noise figure (NF)                                                | 122  |

| 4.1  | Generalized concept of a distributed oscillator                                                                                               | 126  |

| 4.2  | (a) LC-tank based VCO and (b) distributed oscillator                                                                                          | 129  |

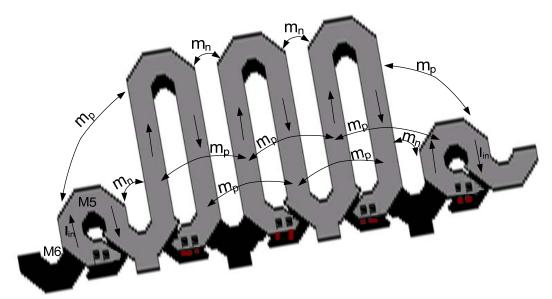

| 4.3  | Integrated inductor segment using multi-layered inductors                                                                                     | 134  |

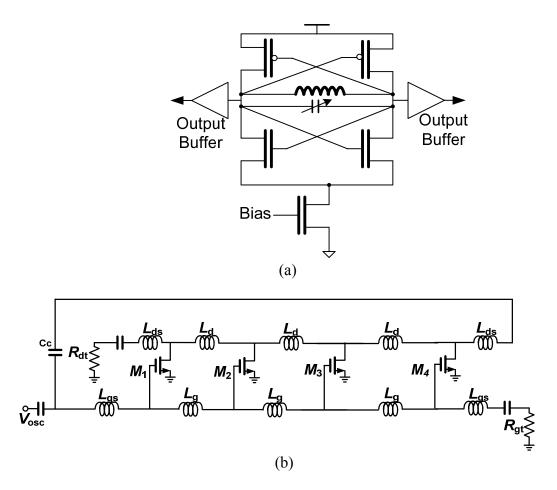

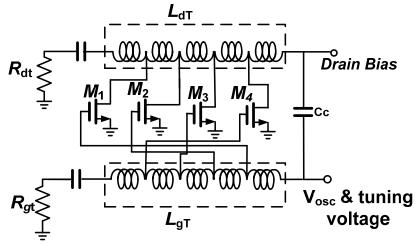

| 4.4  | Schematic of the multi-layered inductor based DVCO                                                                                            | 135  |

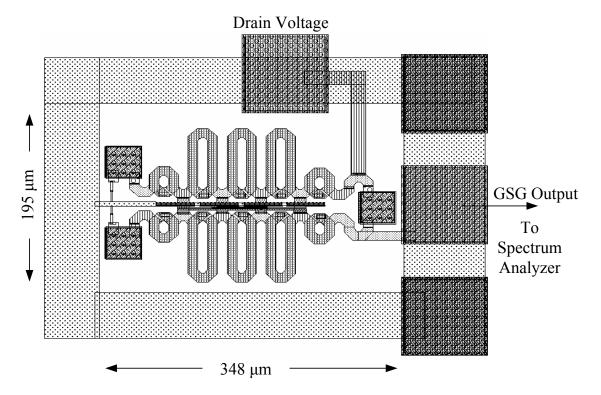

| 4.5  | Layout of the multi-layered inductor based DVCO                                                                                               | 136  |

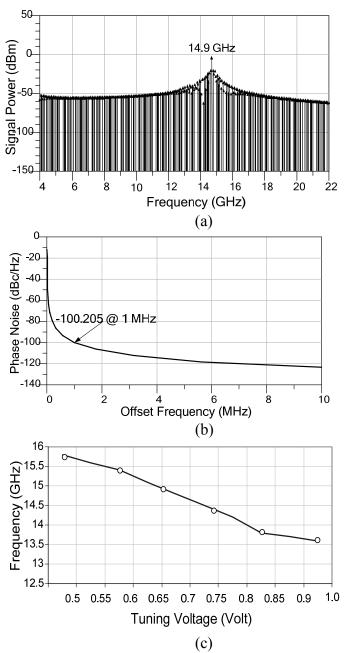

| 4.6  | Simulation results of the multi-layered inductor based DVCO (a) output spectrum (b) phase noise and (c) tuning range                          | 137  |

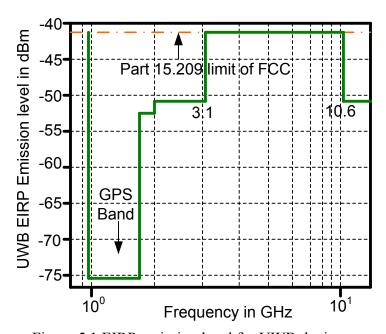

| 5.1  | EIRP emission level for UWB devices                                                                                                           | 140  |

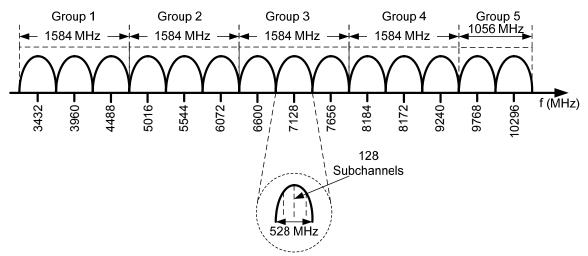

| 5.2  | Band plan for the multi-band OFDM approach                                                                                                    | 142  |

| FIGU | JRE                                                                                                                                        | Page  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

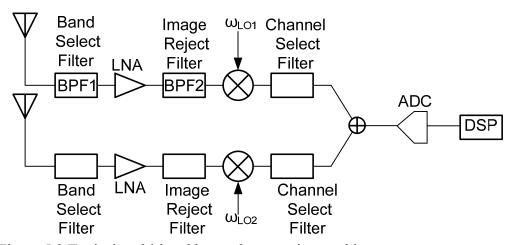

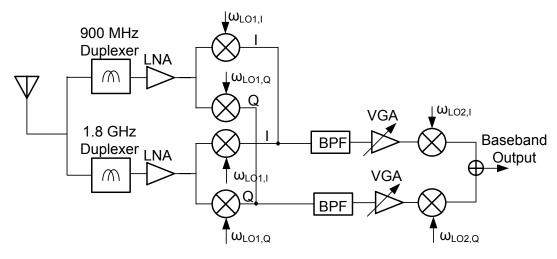

| 5.3  | Typical multi-band heterodyne receiver architecture                                                                                        | 143   |

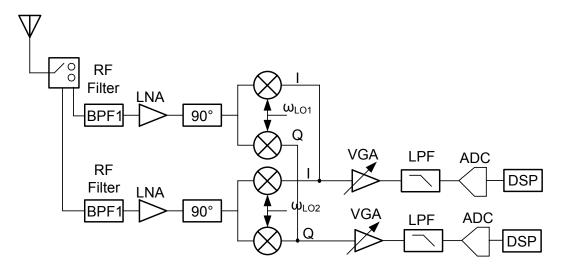

| 5.4  | Dual-band homodyne receiver architecture for WLAN applications                                                                             | . 145 |

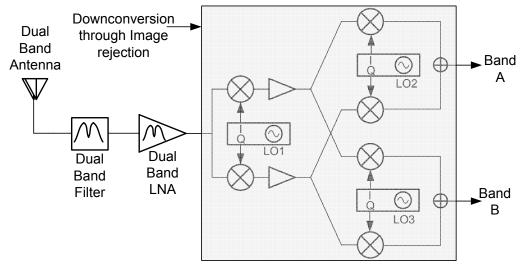

| 5.5  | Dual-band Image rejection receiver architecture                                                                                            | 146   |

| 5.6  | Concurrent dual-band receiver architecture for Bluetooth/WLAN applications                                                                 | . 147 |

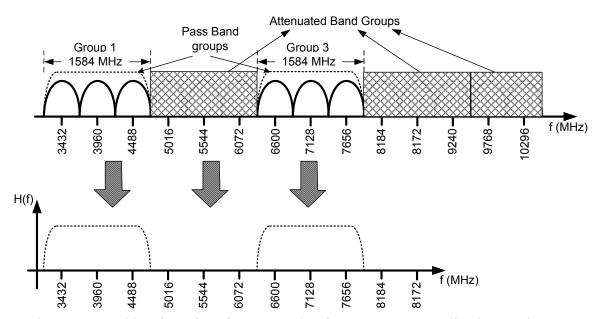

| 5.7  | Dual band receiver frequency plan for MB-OFDM applications and proposed dual band receiver front end transfer function                     | . 149 |

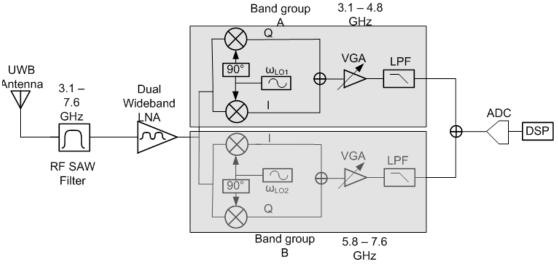

| 5.8  | Dual band UWB concurrent receiver architecture based on the homodyne principle                                                             | . 152 |

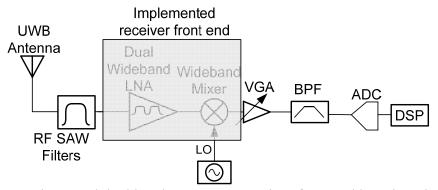

| 5.9  | Implemented dual band concurrent receiver front end based on the heterodyne principle                                                      | . 152 |

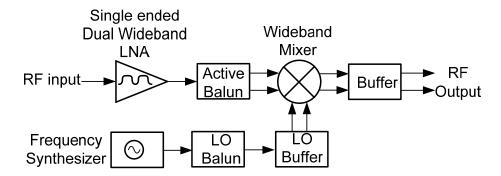

| 5.10 | Block diagram of the implemented dual wide band concurrent receiver front end. All components except the frequency synthesizer are on-chip | . 153 |

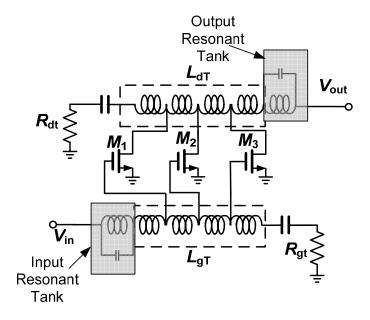

| 5.11 | Three stage concurrent distributed amplifier with integrated multi-layered inductors and resonant input and output tanks                   | . 156 |

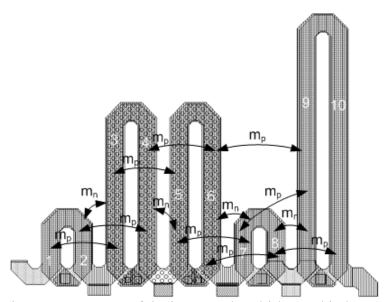

| 5.12 | Layout of the integrated multi-layered inductors including tank inductor and the positive and negative mutual coupling between segments    | . 157 |

| 5.13 | S-parameters of the integrated inductor segments of figure 5.12                                                                            | . 158 |

| 5.14 | Distributed amplifier employing multi-layered inductors and input/output resonant loads                                                    | . 159 |

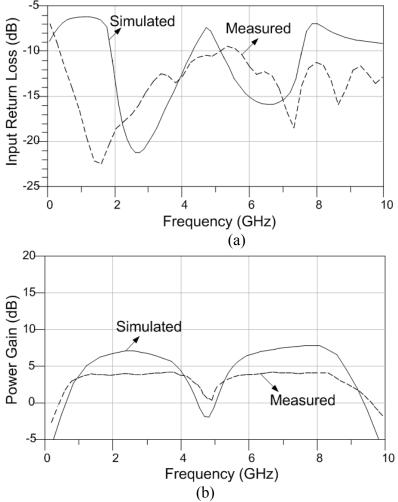

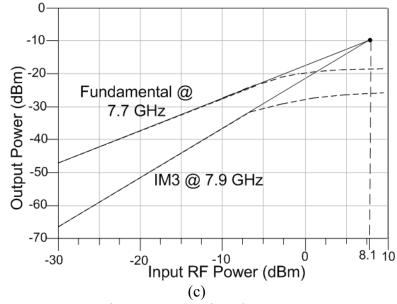

| 5.15 | (a) Input return loss and (b) power gain of the distributed wideband UWB Amplifier (c) simulated LNA IIP3 in the second band (5.8-7.8 GHz) | . 160 |

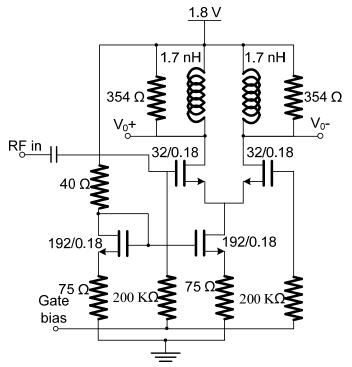

| 5.16 | Active balun schematic with component values                                                                                               | 163   |

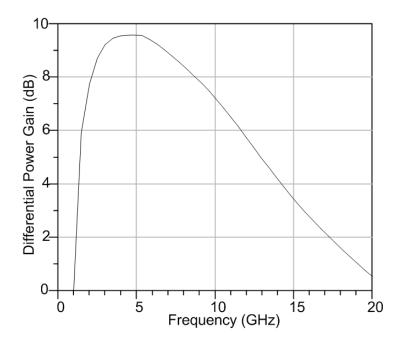

| 5.17 | Simulated differential power gain variation with frequency                                                                                 | 165   |

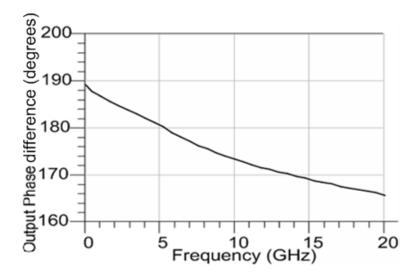

| 5.18 | Simulated phase difference between the two differential outputs                                                                            | 165   |

| FIGU | URE                                                                                                                                                                    | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

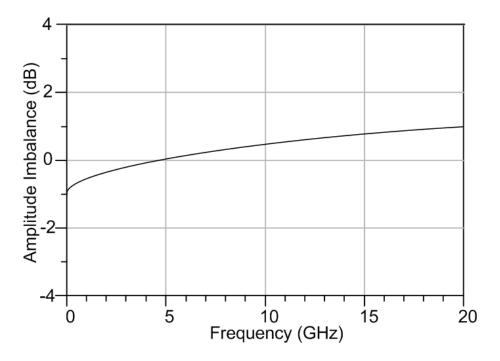

| 5.19 | Simulated amplitude imbalance at the balun output                                                                                                                      | 166  |

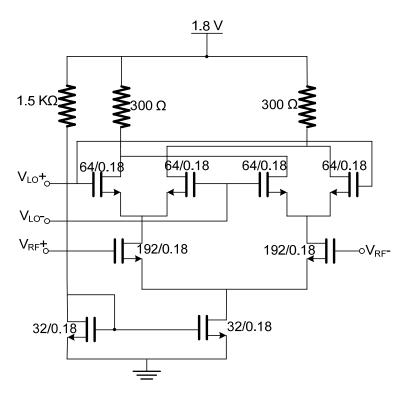

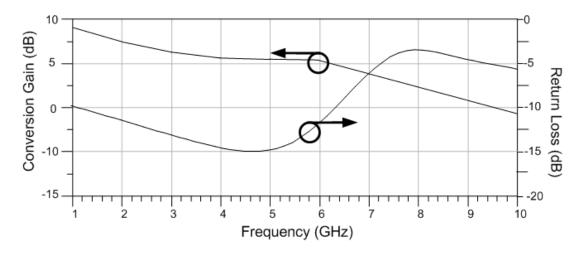

| 5.20 | Schematic of a double balanced Gilbert cell mixer for broadband operation and component values                                                                         | 167  |

| 5.21 | Simulated conversion gain and return loss at the RF port of the double balanced mixer                                                                                  | 168  |

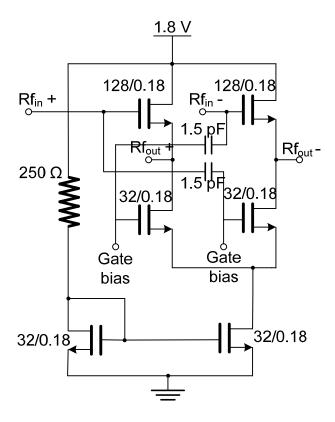

| 5.22 | Schematic of the differential buffer with component values                                                                                                             | 170  |

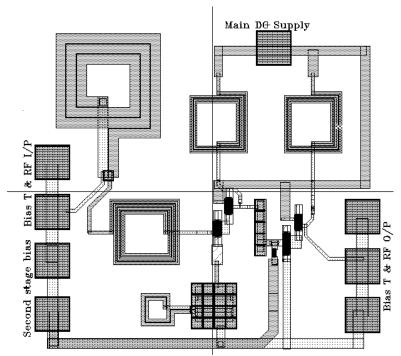

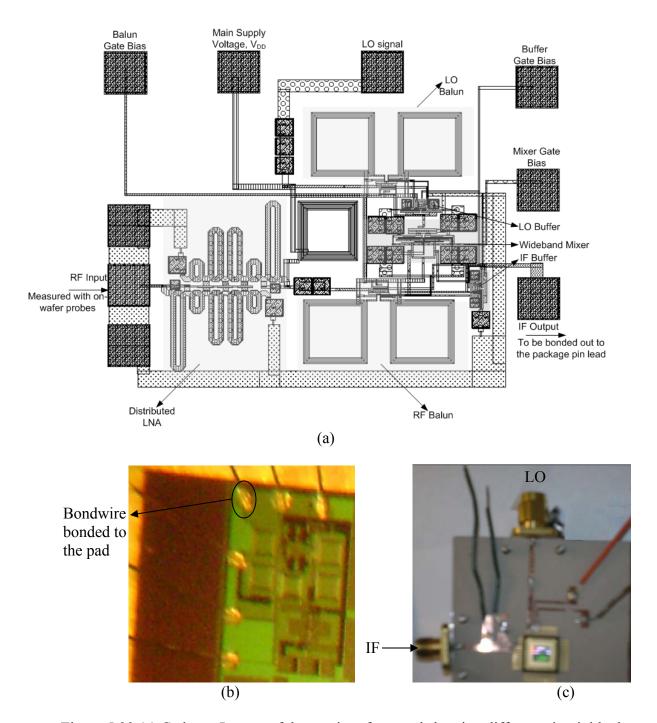

| 5.23 | (a) Cadence layout of the receiver front end showing different circuit blocks (b) packaged IC showing the bond wires and (c) PCB designed for measurement of front end | 172  |

| 5.24 | Conversion gain. LO frequency is varied from 500MHz to 9.5 GHz at a constant power of -10 dBm, IF=500 MHz and RF signal power = -15 dBm                                | 174  |

| 5.25 | Input matching. LO frequency varied from 500MHz to 9.5 GHz, IF=500 MHz, LO power=-10 dBm, RF power = -15 dBm                                                           | 174  |

| 5.26 | Noise figure. LO frequency varies from 500MHz to 9.5 GHz, LO power=-10 dBm, RF power = -15 dBm, IF=500 MHz                                                             | 175  |

| 5.27 | Maximum input 1-dB compression point at 4 GHz in the first band (3.5 GHz - 5 GHz). LO frequency is 3.5 GHz, while LO power is -10 dBm                                  | 175  |

| 5.28 | Maximum input 1-dB compression point at 6.5 GHz in the second band (5.8 GHz – 7.8 GHz). LO frequency is 6 GHz and LO power is -10 dBm                                  | 176  |

# LIST OF TABLES

| TABLE |                                                                                                    | Page |

|-------|----------------------------------------------------------------------------------------------------|------|

| 2.1   | Comparison of CMOS and Duroid substrates                                                           | 24   |

| 2.2   | Coupling and width estimation from EM analysis                                                     | 52   |

| 2.3   | Comparison with recently published microwave Lange couplers                                        | 56   |

| 2.4   | Comparison with microwave/millimeter wave ring hybrid couplers                                     | 64   |

| 2.5   | Two layered inductor calculations                                                                  | 71   |

| 3.1   | Transmission line parameters of the CPW structure for different spacing of the signal-ground lines | 106  |

| 3.2   | Comparison with transmission line based distributed amplifiers                                     | 112  |

| 3.3   | Comparison with recently published CMOS distributed amplifiers                                     | 123  |

| 4.1   | Performance of some recently reported silicon based DVCOs                                          | 131  |

| 5.1   | MB-OFDM receiver specifications                                                                    | 154  |

| 5.2   | Comparison of the receiver front end with recently published results                               | 177  |

#### CHAPTER I

#### INTRODUCTION

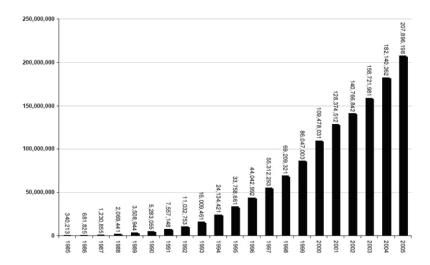

Over the course of the past decade, wireless industry has grown to be a highly versatile and diversified industry turning over revenues worth billions of dollars, with applications spanning across a wide swath of civilian and military domains. Several applications are being continuously updated to supplant existing tethered communication systems with wireless technology. Whether it is an EZ-tag that allows a much swifter automobile passage at freeways or ground penetration radar that helps detect hidden landmines, wireless industry has revolutionized modern life and made its presence ubiquitous. The flexibility and hands-free capability facilitated by Wireless appliances and tools has fuelled an unprecedented demand for a wide array of wireless devices. A modest idea of what an explosive growth this industry has witnessed could be gauged from Figure 1.1. Currently, there are over 218 million subscribers of wireless products in USA alone which is a five fold increase since the trend towards inexpensive products started gaining momentum and the market has been growing by at least 24 million each year in the past 2 years [1]. A wireless product is sold every second and a wireless access point is installed every four seconds in the United States of America. A significant reason for this unprecedented growth is the competitive pricing of wireless products. Such cost effectiveness has primarily been fuelled by lower cost per chip area facilitated by CMOS and related monolithic silicon technologies, whose benefit trickles

The style and format follow IEEE Transactions on Microwave Theory and Techniques.

down to the consumer.

At the same time, cost effectiveness alone wouldn't be a compelling reason without reasonable product performance. It is here that the role of an RF designer becomes clearly defined – it lies in the ingenuity to extract maximum circuit performance while striving to conserve chip area. The goal of the current dissertation is to achieve the same moderation required from RF designers - in balancing optimum circuit performance with reasonable chip area consumption.

Figure 1.1 Estimated number of wireless subscribers in USA (source CTIA [1]).

#### 1.1 Research motivation

Commensurate with the current trend of rapid wireless market expansion, the complications involved in the design of high frequency wireless circuits become more

difficult to specify with certainty. However, commercial applications that employ wireless products typically require a wide array of high performance, low cost and low power circuits though the design challenges vary from one application to another. Circuit specifications typically depend on their respective applications. Broadly, circuits catering to wireless communication related applications could be classified into two categories, depending on their frequencies of operation: (a) Front-end, the high frequency sub-system that performs signal amplification and down/up conversion (b) Back-end, the low frequency sub-system that performs signal extraction/generation. The front-end receiver sub-system is of particular interest owing to the challenges posed by the high frequency behavior of passives and active components of CMOS technology which tend to complicate optimal signal detection, extraction and regeneration. receiver front-end usually consists of a low noise amplifier (LNA), down-conversion mixer, frequency synthesizer, image rejection filters, intermediate frequency filters and amplifiers. Regardless of the nature of wireless applications, the challenges posed in the design of these high frequency wireless circuits, viz., the front-end sub-system components are common and directly related to the needs of the wireless market.

There were two prime motivations in conducting the current course of research. One was to develop high performance and extremely compact novel RF passive structures and front end circuits for Ultra Wideband (UWB), WLAN and the unlicensed Ka-band (26.5 GHz to 40 GHz) for Industrial, Scientific and Medical (ISM) applications. A second motivation was to contribute to the development of new wireless applications by developing a novel sub-system capable of *possible* multi-functional operation. A dual-

wide band concurrent receiver front-end sub-system is demonstrated, whose concept could be extended either to Ultra Wideband (UWB) or to multi-functional architectures serving multiple applications on the same chip.

To gist, regardless of the nature of wireless application, the design challenges of any wireless circuit are market oriented and are commonly subject to technological constraints that need to be carefully addressed by the designer.

#### 1.2 Dissertation overview

The current dissertation comprises of three broad segments – passive, active and subsystem. The following section on Passive structures includes novel topologies of 90° and 180° couplers, resonators and inductors. Chapter II discusses the design and development of CMOS-millimeter wave specific novel passive components. A variety of CMOS-specific miniaturization techniques were also developed and applied to these passive structures and are presented in detail. Chapter III details the design and development of wideband amplifiers, particularly distributed low noise amplifiers, which employ novel multi-layered inductor structures as well as integrated inductors and transmission lines. The LNAs including a DC-20 GHz broad band amplifier and an ultra-compact, low power UWB amplifier are both discussed elaborately in this chapter. A novel dual wide band amplifier with lumped element analog design principles is also demonstrated. A point worth mentioning here is that all the low noise amplifiers were designed considering their possible integration into a dual wideband sub-system. The subsequent chapter on VCOs discusses the general operational principles of multi-stage

distributed VCOs. Design issues related to the usage of artificial transmission lines in CMOS DVCOs are also discussed here and also the impact of multi-layered vertically coiled inductors on VCO performance. The fifth chapter discusses a novel dual-band UWB receiver sub-system. The circuit components, including a novel concurrent dual band distributed LNA, active baluns, dual balanced Gilbert cell mixer and output buffers are discussed along with system level issues in this section. The final chapter presents the recommended future work that could be carried out in each of these fields as well as a brief summary of the current work.

The dissertation has an extensive and ambitious scope aiming to cover a wide range of novel passive, active and front-end sub-system elements from DC till 40 GHz based applications. And because of such extensiveness, there could be a deliberation on the common factor binding such disparate circuits as a 90° Lange coupler and a dual wide-band low noise amplifier. It is here that it must be noted that the common binding factor lies in the similarity of the design premise in all implementations – of trying to develop high performance, miniaturized, low power consumption RF, microwave and millimeter-wave system and circuit blocks that are highly attractive to the wireless market. Another ambitious agenda was to successfully demonstrate the amalgamation of both analog and microwave design concepts – a useful trend that enables implementation of novel topologies for increasingly higher frequency related applications in CMOS.

#### **CHAPTER II**

#### DISTRIBUTED PASSIVE CIRCUITS

In this chapter, distributed passive circuits ranging from inductors to microwave couplers are discussed and several new design techniques are presented that improve their overall performance. Section 2.1 gives an overview of these passive components hitherto implemented in GaAs MMICs, need for miniaturization and a summary of all the important miniaturization techniques. Section 2.2 deals with the basics of CMOS microwave passive design while section 2.3 focuses on the theory and implementation of slow wave structures and the feasibility of its applicability to CMOS passive circuit miniaturization. A novel slow wave structure is also introduced here and its application to a hairpin resonator is also studied. Multi-layered design techniques form an important segment of discussion in section 2.4. A variety of microwave passive couplers miniaturized by multi-layer design techniques are presented and discussed in this section. The section also discusses the basic principles of multi-layered design and how the CMOS metal stack and the high resistive SiO<sub>2</sub> dielectric could be exploited for vertical design that facilitates substantial miniaturization. Finally, section 2.4 also presents a composite design technique that combines both slow wave and multi-layered design principles to achieve a novel 3-D complementary slow wave structure, which is shown to yield the benefits of both quality factor enhancement as well as circuit miniaturization, better than the 2-D planar slow wave. It can be noted that all the design techniques presented in this section, though implemented in CMOS, could be extrapolated to any monolithic IC technology where the size and performance of passives is a major concern. The final section discusses some possible applications for the designed CMOS microwave passives.

## 2.1 Overview of existing miniaturization techniques in MMICs

Since the discovery of Gunn effect [2] in 1962, development of GaAs based Monolithic Microwave Integrated Circuit (MMIC) components began at an extremely rapid pace. The first MMIC passive components were designed by Mehal et al [3] and Mao et al [4] who developed a series of couplers, phase shifters, mixers and diodes for millimeter wave applications up to 94 GHz. Since then, GaAs has been the workhorse of novel passive circuitry catering to the microwave and millimeter wave integrated circuit domain. The invention of MESFETs and PHEMTs in 1970s and 90s respectively, further contributed to the development of passive circuitry to complement the availability of excellent transistors with low transit carrier times and high resistance substrates. As a consequence, a number of monolithic passive design techniques are available in GaAs and this section provides an overview of those existing techniques.

## 2.1.1 Couplers

Couplers are typically passive components that perform power division or combination bearing an appropriate phase difference between their output terminals. During power division an input signal is divided into one or more signals of lesser power, either of equal or unequal power, usually accompanied with loss. Four port couplers that split the power equally between their outputs are called hybrids and exhibit

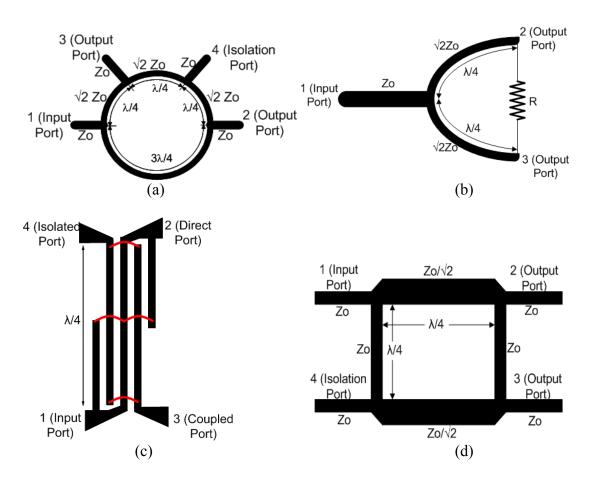

either 90° or 180° phase difference between the outputs [5]. In MMIC design, couplers are implemented in novel ways to conserve chip area and reduce their inherent losses. A list of popular MMIC based couplers is shown in figure 2.1. The ring hybrid is one of the most widely used 180° hybrid structures. It operates in either summation (in phase) or

Figure 2.1 Layouts of popular MMIC couplers (a) Ring Hybrid (b) Wilkinson Coupler (c) Lange Coupler and (d) Branchline Coupler.

difference (out of phase) modes. The layout shown in Figure 2.1(a) is of the difference mode, which splits the input signal equally and causes a 180° phase shift between the

two outputs. For the summation mode, the signal is typically applied at port 4 (currently labeled as the isolation port) to gain two signal outputs of similar phase but equally split. The main advantages of the ring hybrid are its ease of design, uni-planar configuration that facilitates easier fabrication and flexibility of operation while the prime disadvantages are its exorbitant size that makes it impractical even for RF frequencies in monolithic technologies and narrow bandwidth. Several techniques have been proposed in MMIC technologies to enhance the bandwidth and reduce the prohibitively large circuit dimensions of this coupler which are discussed in more detail in the coming section on the TFMS ring hybrid. Nonetheless, this circuit finds enormous applications in MMIC design – from active mixers to phase shifters.

The Wilkinson coupler [6] shown in figure 2.1 (b) is a three port 90° coupler, i.e., which can split input power equally, with excellent matching at all three ports and good isolation of input and output ports. It can also be designed for unequal power transfer and arbitrary phase difference as well. Its main strength lies in the ease of design and relatively moderate dimensions. However, for usage in RF applications, there is a possibility of loss in the resistor that leads to amplitude reduction. Furthermore, tighter coupling with very small insertion loss becomes exceedingly difficult to achieve with this coupler as it has been conceived as a power splitter and or power combiner rather than a low insertion loss, tight coupler.

This problem is overcome in a Lange coupler [7] that allows very tight coupling ratios. The 4-fingered, edge-coupled, folded version of the Lange coupler is shown in figure 2.1(c). This structure has the immediate advantage of tighter coupling and

extremely wide bandwidth through a completely uni-planar structure. The coupler works by forcing the even and odd mode phase velocities to be close to each other, which is achieved by creating equi-potential surfaces through inter-connects on alternate metal strips on an edge coupled structure. The Lange coupler is highly attractive for a variety of broadband RF and microwave applications if its quarter-wavelength dimension problem is solved. This is the subject of further discussion in the broadside coupled Lange structure.

The Branchline coupler introduced in figure 2.1(d) is the final structure which owes its popularity for being the simplest coupler to design and fabricate. When perfectly matched, power entering port 1 is evenly divided between ports 2 and 3, with a 90° phase difference between them. It is also a perfectly symmetrical structure that allows any port to function as an input. Its prime disadvantages that make it difficult for MMIC design are its inherently large chip area consumption. The coupler also suffers from very narrow bandwidths compared to the Lange, while occupying significantly larger area than the latter.

Among these different types of couplers mentioned above, two couplers are of particular interest to CMOS designers owing to their significant advantages for providing silicon based solutions for various microwave and millimeter wave applications. They are - the Lange coupler, which is a 90° hybrid and the ring hybrid, a 180° rat race coupler. The Lange coupler removes the problem associated with narrow bandwidths of the Branchline at the same time while facilitating a monolithic fabrication. It is a very tight coupling circuit and less than 3 dB coupling is easily

possible. Insertion losses less than 0.2 dB have been achieved even at millimeter wave frequencies, while facilitating several octaves of bandwidth, independent of technology. All these qualities prove extremely attractive to CMOS millimeter wave designers, where applications constantly demand greater bandwidths and low loss power combining or dividing circuits. On the other hand, the Ring hybrid can perform the role of single to differential conversion through its 180° phase difference between both of its output ports. It finds immediate applicability in CMOS Microwave design, for instance, through the super-heterodyne receiver architecture to ease the transition from a single ended LNA output to a differential input double balanced Gilbert cell mixer. By functioning as a Balun, it can be utilized in a wide variety of CMOS receiver circuit applications as well. However, the greatest obstacle in exploiting the circuit level applications of these immensely useful topologies is their prohibitively large size.

The above discussion makes it apparent that miniaturization of microwave passives is the biggest challenge in their CMOS implementation. The concept of exploring miniaturization techniques for microwave passives was in vogue ever since the first implementation of couplers in a monolithic IC technology by Waterman et al [8] and Brehm et al [9]. The reported dimensions were in excess of 1 x 3 mm even at millimeter wave frequencies. Lange couplers were among the first 90° hybrids to be fabricated owing to their uni-planar structure that do not necessitate additional procedures on the fabrication technique. Early miniaturization techniques involved only meandering that folded the coupler along its length without affecting the internal coupling between different turns of the coupler [8]. Multi-layered design techniques began to be utilized

for further scaling down the dimensions and circuits measuring 1 x 0.8 mm were reported by Robertson et al [10] for 0.1-12 GHz applications. Novel miniaturization techniques appeared around 1990s and involved utilizing lumped elements to mimic transmission line properties [11] which significantly scaled down dimensions. Yet, they suffered from inherent bandwidth limitations and could not span multiple decades of operation like their distributed counterparts. Multi-layered design techniques were proposed by [12]-[15] and began to be extensively used to scale down the size significantly as well as to increase the coupling of inter-digitated lines. Other notable techniques include periodic stub loading that creates either an inductive or capacitive periodic attenuation of the wave velocity, thereby causing an artificial slow wave impact [16]-[18], incorporating slow wave structures [19]-[20] and aggressive meandering [21]. Both capacitive and inductive loading are typically accomplished by short and open circuited stubs at microwave and millimeter wave frequencies. A variety of slow-wave structures particularly tailored for monolithic technologies, notably the Uni-Planar Compact Photonic Band Gap (UC-PBG) structure developed by Prof. Itoh et al [22], have been applied in GaAs to reduce wave propagation velocity, increase the effective dielectric constant and thus reduce circuit dimensions. However, slow wave design has not yet caught up with CMOS owing to the non-compatibility of dimensional requirements. Design complications also abound as slow wave structures need to satisfy physical properties and cannot comply with arbitrary miniaturization procedures. Aggressive meandering, while being the easiest of all, is more of a layout principle than

a design technique and can be used in addition to any of the above techniques to gain further miniaturization.

#### 2.1.2 Resonators

Traditionally, any structure that enables resonance or resonant behavior could be characterized as a resonator. A wide variety of resonators exist from 100 MHz to 100 GHz to satisfy a significant number of applications. In RF and millimeter wave circuit design, resonators perform several important functions like enabling oscillations inside local oscillators, diplexers and band pass filter components. Since the advent of monolithic circuit design, the basic resonator structures underwent a drastic change from bulk wave, surface acoustic wave (SAW), helical, dielectric and waveguide to coaxial and stripline resonators [23]. Bulk wave, SAW and helical resonators mostly operate below 1 GHz and handle diverse power requirements. Helical resonators are capable of handling larger powers than the other two. Dielectric resonators are mostly meant for RF and microwave applications and present exceptional characteristics – low loss and high quality factor. Yet, their reliance on exotic dielectric materials makes them unattractive for monolithic circuit implementation and also very expensive to realize in bulk. Waveguide resonators are among the oldest and most studied resonators and have proven valuable for applications more than 100 GHz. However, they too suffer from extremely large dimensions which makes them difficult to realize in monolithic technologies. Stripline and coaxial resonators, on the other hand, do not match either waveguide or dielectric resonators on the performance aspect. Yet, they are deemed very

useful by MMIC designers owing to their flexible, simple design procedures and relatively smaller dimensions. They are also technology independent, which makes them

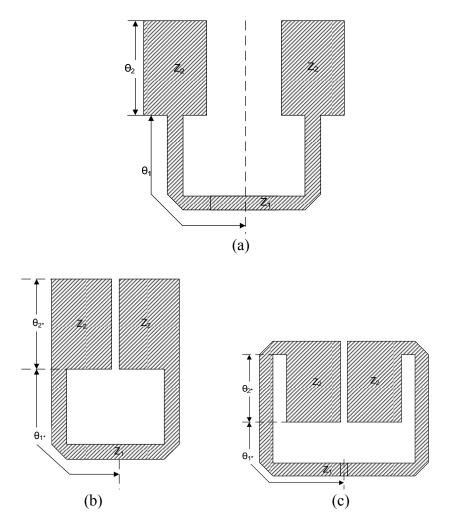

Figure 2.2 Types of Stripline resonators (a) Uniform Impedance (b) Stepped Impedance. [23]

less expensive to fabricate. Stripline resonators are more suited for monolithic design as they allow planar circuits.

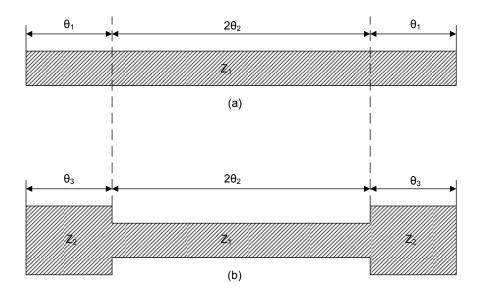

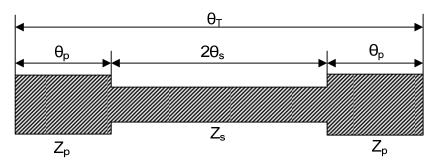

Stripline resonators could be broadly classified into Uniform Impedance Resonators (UIR) and Stepped Impedance Resonators (SIR). They are depicted in figure 2.2. The electrical length of the stepped branches in the SIR is related to the electrical length of the extended uniform arms of the UIR by the relation [23]:

$$\tan \theta_3 = \frac{Z_2}{Z_1} \tan \theta_1. \tag{2.1}$$

The uniform impedance resonator, while being very easy to design doesn't give designers many opportunities to introduce variations due to its limited design parameters. It also introduces spurious responses at integer multiples of fundamental resonant frequency. Stepped Impedance Resonators overcome these limitations by allowing greater design flexibility through its non-uniform impedance characteristics. Due to the availability of very powerful 2, 2.5 and 3 D Electro-magnetic simulators, the modeling and design of these resonators is very much simplified. Stepped impedance resonators have hitherto found several applications in filters, oscillators and mixers in MMIC design. Based on their electrical length, stepped impedance resonators are further classified into three classes - full, half and quarter wave length as shown in figure 2.3. The full wave length SIR is depicted as a circle in order to be area efficient. The half wavelength resonator could have both open and both short circuited ends. The quarter wavelength resonator is depicted with open ends in the figure, but it could also have short.

While full wavelength resonators are too large for monolithic IC implementation, quarter-wavelength SIRs inspite of having a significant size advantage over the half wavelength SIR, suffer from limited number of geometries and the convenience to tap the output in cross coupled structures that are used to generate negative resistance in CMOS design of voltage controlled oscillators, where such resonators could find potential application. Resonators like these are similar to distributed versions of typical RLC tank circuits. Their main practical disadvantage for CMOS design lies in the case of having an extremely low impedance terminal which is close to short at the resonant

Figure 2.3 Stepped Impedance Resonators (a) quarter-wavelength ( $\lambda_g/4$ ) (b) Half wavelength ( $\lambda_g/2$ ) and (c) Full wavelength ( $\lambda_g$ ). Each node is either open or short depending on the application.

frequency when the other terminal is a high impedance node. This could also causes problems in routing metal through the low impedance node. For microwave and

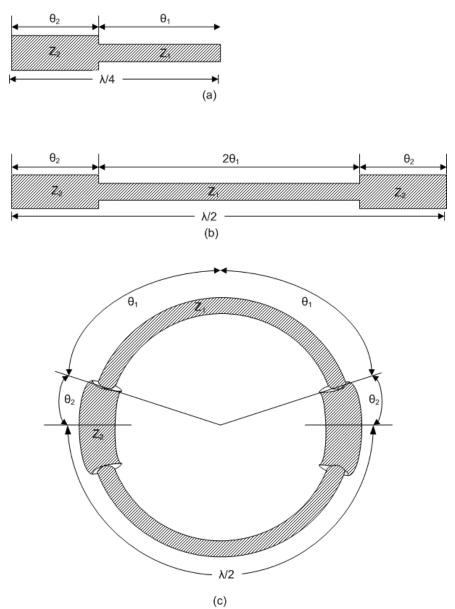

Figure 2.4 (a) Conventional hair pin resonator (b) internally coupled hairpin resonator (c) Ring type resonator with internal coupling. [23]

millimeter wave CMOS design, layout geometry flexibility is very important to enable high frequency routing between active devices and passive microwave structures. Half wavelength SIRs not only allow easier routing, a feature not available in quarter wavelength. The quarter wavelength resonator also tends to exhibit at least one low impedance node whenever the other end is left open. This becomes a practical problem at multi-GHz frequencies. Further, the half-wavelength resonators allow several different

geometries including hairpin, ring, etc, which gives the designer greater flexibility to tailor the functionality of the passives for specific circuit needs, depending on the application. Cristal et al [24] reported the first half wavelength resonators used a hairpin structure to implement a bandpass filter operating around 1.5 GHz. The structure had a uniform impedance and consisted of several mutually coupled hairpin structures. Stepped impedance resonators were first proposed by Makimoto et al [25] for designing bandpass filters at 900 MHz. The first attempt at miniaturization and practical high frequency application of half wavelength resonators was carried out by Sagawa et al [26] who developed an ultra compact hairpin split ring resonator which could be readily integrated in MMIC. Significant size reduction could be obtained by exploiting internal coupling between the resonator arms. Subsequently, miniaturized hairpin and other variants of half wavelength resonators have been widely used to design a variety of push-push oscillators [27], bandpass filters [26] and even as slow wave structures [28]. Currently, the sole miniaturization techniques applied to the traditional hairpin resonator has been to fold the structure internally. This internal coupled slow wave structure is depicted in figure 2.4 (c).

Structure (b) is explored in depth in section 2.2 as it could be of significant interest to CMOS designers at millimeter wave frequencies as a possible alternative to RLC tank circuits in NMOS-PMOS cross coupled voltage controlled oscillators (VCO). However, in its present form, the existing dimensions and inadequate miniaturization techniques do not make it compatible for CMOS implementation even at 30 GHz.

#### 2.1.3 Inductors

Contrary to the previous two categories of interest mentioned earlier, inductors have been exclusively researched in both performance and size aspects in CMOS more than any other passive structure in any other technology. Popular Silicon based spiral inductors meant for analog applications were first patented by A. E. Hubbard [29] and their multi-GHz behavior was first studied by Nguyen et al [30]. Numerous models exist in literature that quantify and characterize the three important performance factors of an inductor – the inductance, quality factor and self-resonant frequency, specifically for Radio frequency and microwave/millimeter wave applications. Quality factor is characterized by the following expression derived from the single port Y-parameters of a spiral coil:

$$Q = \frac{-\operatorname{Im}(Y_{11})}{\operatorname{Re}(Y_{11})} \,. \tag{2.2}$$

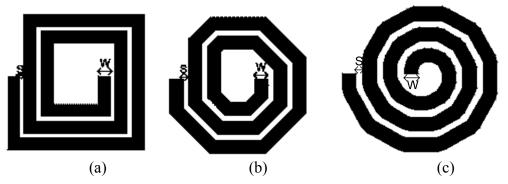

Figure 2.5 Planar spiral inductors in CMOS (a) Rectangular (b) Octagonal and (c) Circular.

An alternate expression is used to account for the finite Q values at the Self resonant frequency [31]:

$$Q = \frac{\omega_0}{\Delta \omega_{3dB}} \ . \tag{2.3}$$

with  $\Delta\omega_{3dB}$  being the 3-dB bandwidth measured around  $\omega_0$ . The self-resonant frequency, another important parameter, is defined as the frequency above which the extracted impedance becomes capacitive. Most communication circuits require higher quality factor values and higher self-resonant frequencies owing to the increasingly higher frequencies of circuit operation. The most widely used CMOS inductor structure is the planar spiral, which relies on mutual coupling between each turns to store magnetic energy. While it suffers from limited quality factors, it provides the best means to achieve a wide variety of inductances for different communication circuit applications. Different forms of planar spirals are shown in figure 2.5. The coil width 'w' and the spacing between the turns 's' are depicted in all cases.

The loss mechanisms in planar silicon based inductors are due to silicon substrate conductivity, substrate eddy current losses and current constriction in the turns of a multi-turn spiral and the spiral underpass capacitance [32], [33]. Subsequently, when the inductor structure is subject to miniaturization, these loss mechanisms must be taken into consideration as some miniaturization techniques might prove detrimental to the overall performance metrics.

Miniaturization of inductors is even more challenging than those of couplers and resonators because of their critical impact on key communication circuit blocks. The size reduction techniques employed for inductors in silicon have followed their microwave passive counterparts by exploiting the presence of multiple metal stacks in monolithic

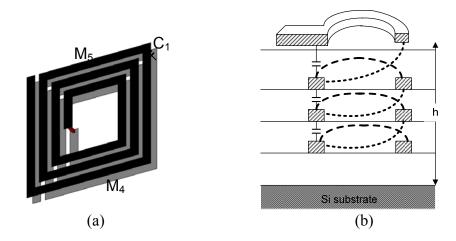

CMOS technology. Currently, vertically stacking, micro-machining and selective removal of lossy Si substrate and vertical solenoid are three prominent approaches to the design of miniaturized inductors. Vertically stacked inductors use a set of stacked planar inductors, implemented on different metal layers of a standard CMOS technology, to generate higher inductance without occupying much lateral chip area. A fractional increase in self resonant frequencies has also been reported [34]-[35]. Micro-machined inductors are typically fabricated using non-standard MEMS procedures on a standard silicon technology or on CMOS grade silicon wafers. They consume lower chip area and typically have extremely high quality factors, owing to the removal of lossy silicon substrate below the inductor [36]. However, this approach is the least preferred alternative owing to the extra cost incurred during the post-fabrication MEMS procedure. The vertical solenoid inductors are implemented in a helical form along the CMOS metal stack. The multiple turns of the inductor are each implemented on a different metal layer so as to build a vertical inductor structure that consumes little lateral chip area [37]. Higher quality factors and self-resonant frequencies have been reported using this design structure along with significant chip area consumption. Figure 2.6 shows the layouts of the two varieties of standard miniature inductors mentioned above.

Overall, existing miniaturization techniques for all the passive circuits mentioned in this section are still grappling with performance and cost optimization problems, while designers are constantly seeking new ideas to further reduce the chip area consumption and enhance their performance metrics. There is also a significant difficulty while trying

Figure 2.6 Miniaturized inductors in CMOS (a) Vertically stacked (b) Vertical Solenoid. M5 and M4 indicate metal layers 5 and 4.

to map the existing miniaturization techniques in well established MMIC technologies like GaAs into the newly developing CMOS technology due to the lossy nature of silicon substrate as well as the extremely small dimensions being required in CMOS technologies. These challenges along with some novel ideas that have been implemented for the first time in CMOS technologies are discussed in the subsequent sections of this chapter.

#### 2.2 Design of microwave structures in CMOS

CMOS based technologies pose a critical challenge in the design of microwave passive structures since size limitations are a major challenge to circuit designers even at millimeter wave frequencies. In this section, properties of the silicon substrate as well as

design considerations of how CMOS technology tends to influence microwave passive design are studied.

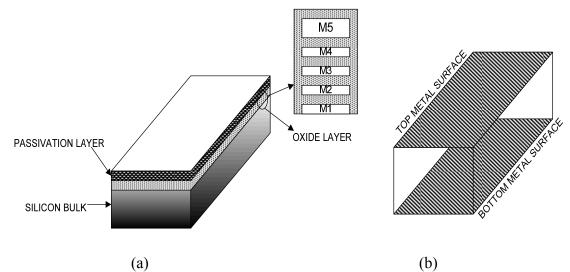

#### 2.2.1 Properties of silicon based substrates

The Silicon dioxide dielectric constant inside which all the metal layers of any standard CMOS technology are embedded is typically 3 times smaller than that of Duroid RT/6010 substrate laminate, a popular low loss substrate for developing microwave passives. Table 2.1 shows the comparison between a standard CMOS technology and a Duroid substrate. It shows the properties of the oxide and passivation layers, for the CMOS technology, as the metals are embedded inside the oxide layer. The structures of both the Duroid substrate and CMOS technologies are illustrated in figure 2.7. It should be noted that for quasi-TEM transmission lines like microstrip and CPW, which are extensively used in distributed topology based circuits; the role of silicon substrate is also crucial and as such its conductivity influences microwave passive circuit performance. The high conductivity of typical bulk silicon substrate which is about 12 S/m impacts inductor performance as well, leads to induction of large eddy currents in the substrate. The smaller dielectric constant within the oxide layer as well causes a significant reduction of metal width for microstrip transmission lines. The top metal thickness is only moderately thick which also poses additional problems of skin effect at millimeter wave and higher microwave frequencies.

Table 2.1 Comparison of CMOS and Duroid substrates

| Substrate Properties               | Typical CMOS technology | RT/Duroid       |

|------------------------------------|-------------------------|-----------------|

| Туре                               | Multi-layered           | Single          |

| Dielectric Constant                | 3.95-4.1                | 2.24-10.5       |

| Thickness                          | Few tens of micron      | At least 127 μm |

| Substrate Electrical  Conductivity | Prominent               | Negligible      |

| Loss tangent                       | 0.004-0.015             | 0.0009 to 0.002 |

| Top metal thickness                | Few Micron              | At least 19 μm  |

The smaller dielectric constant of the oxide is also counterproductive as it causes the effective wavelength to be larger for transmission lines. In spite of these apparent flaws, CMOS technology still holds some useful properties that could be exploited by microwave passive circuit designers. Firstly, successive technologies at the sub-micron gate length level are using thicker top metals that are placed much higher above the bottom metal. This is fuelled by the need for denser and more efficient power routing in digital circuits, which are typically integrated with the analog/RF blocks. Secondly, the electrical conductivity of the SiO<sub>2</sub> layer itself is quite small and it is in this layer that the major chunk of electric field is concentrated. Finally, the presence of passivation layers

Figure 2.7 Graphical representation of (a) CMOS and (b) Duroid/RT substrates.

above the oxide layer, further cushions the electric field from interfering with the outer environment, a facility not available in traditional monolithic substrates without additional fabrication procedures. Further more, the problems associated with the lossy and conductive silicon substrate could be easily alleviated by the designer's understanding of the substrate properties in CMOS as well as some by some time tested design techniques.

#### 2.2.2 Microstrip vs CPW

An important consideration in the design of microwave passive circuits lies in choosing which quasi-TEM transmission lines are to be preferred for implementing them. From the five metal CMOS technology shown in figure 2.7 (a), a microstrip line could be implemented using metals 5 (M5) and 1 (M1) while a (non-conductor backed)

CPW can be entirely implemented on M5. For microstrip lines, M1 could considered as the ground plane while M5 is used as the signal line, in order to extract the maximum substrate thickness from the technology. This is because having a larger substrate thickness allows usage of larger signal line widths to realize larger characteristic impedances, which is highly desirable since smaller metal widths usually face the problem of current crowding at high frequencies.

Microstrip transmission lines have the inherent advantage of easier routing and layout. However, their maximum impedances cannot go above  $100~\Omega$  for most submicron standard CMOS technologies as their widths become too narrow at higher impedances. CPW structures pose a difficulty in routing and tend to occupy greater chip area. But greater impedances are easily realizable through CPW than microstrip lines without risking narrower widths.

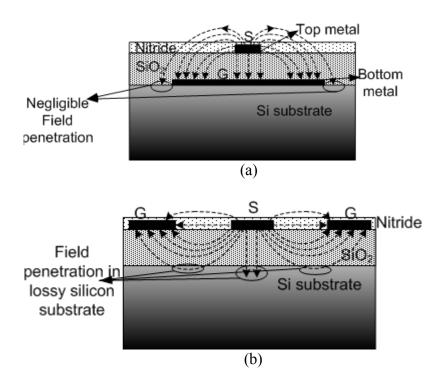

The clinching factor in favor of microstrip lines is that they tend to reduce the penetration of the electric field through the silicon substrate unlike the CPW which has significant field penetration. The electric field patterns of both these transmission lines are displayed in figure 2.8 for high characteristic impedance on a typical CMOS substrate. It is evident that the CPW segments risk greater silicon substrate penetration at higher impedances and as such might prove more lossy than microstrip lines at higher impedances which depend on having larger spacing between the signal and ground planes. The larger width advantage facilitated by CPW structures, therefore, could be replaced by a greater risk of silicon substrate field penetration. Thus, in this work, the microstrip transmission lines are the transmission lines of choice.

Figure 2.8 Electric field distribution in a high impedance (a) Microstrip and (b) CPW in CMOS.

#### 2.3 The slow wave theory

Slow wave techniques have been extensively used in non monolithic, multi-dielectric substrates to achieve frequency selective behavior in microwave passive circuits. Though the idea of creating a periodic change in dielectric constant is not new in itself, much of the initial focus was concentrated on slow wave transmission lines, which consisted of Metal-Insulator-Semiconductor (MIS) which had the intrinsic disadvantages of higher ohmic losses and lower impedances [38]. Moreover, with increasing demand for high frequency applications, need for higher impedance, low loss structures became the primary concern. Initial interest in slow wave structures was generated from photonic

crystals with slow wave characteristics [39] and subsequently, development of periodic band gap structures that emulate a similar behavior in the microwave domain [40]. These structures have much higher impedances and do not require any non-standard, exotic substrates for implementation. This section presents the theory of slow wave propagation resulting from such slow wave structures and discusses their applicability to miniaturization and performance enhancement of RF, microwave and millimeter wave CMOS based distributed passive circuits. A novel slow wave structure is also presented and its impact on a hairpin resonator is evaluated as well.

#### 2.3.1 Basic principles

Slow wave structures are 2 or 3-D periodic (and often, multi-layered) structures that prevent the propagation of Electro-magnetic waves within specific bands. This unique property of these structures offers designers an additional degree of freedom to control the EM behavior of a circuit. Mathematically, modeling an infinite periodic structure is much easier than a finite periodic structure owing to the occurrence of inhomogeneous modes in the latter. Since practical applications require only finite periodic structures, only they are of any significant interest to microwave engineers. In microwave circuits, finite periodic slow wave structures are designed in such a way that there would be an increase in the effective dielectric constant, which leads to reduction of group wave velocity. The periodicity of the slow wave pattern also leads to a complete attenuation of surface waves at some frequencies. A circuit operating subject to slow wave condition is bound by the stop band criterion [41]:

$$\beta.a = \pi \ . \tag{2.4}$$

wherein  $\beta$  is the phase constant at the center of the stop band and a is the lattice period of the periodically repeating slow wave structure. Several analytical approaches have been suggested to deal with the modeling challenges of finite periodic structures. One of the more feasible ways is to recursively extract the s-parameters of a finite periodic structure with n+2m repetitions from the ABCD matrices of the same structure with n+m and n repetitions as [43]:

$$\begin{bmatrix} A_{n+2m} & B_{n+2m} \\ C_{n+2m} & D_{n+2m} \end{bmatrix} = \begin{bmatrix} A_{n+m} & B_{n+m} \\ C_{n+m} & D_{n+m} \end{bmatrix} \begin{bmatrix} A_n & B_n \\ C_n & D_n \end{bmatrix}^{-1} \begin{bmatrix} A_{n+m} & B_{n+m} \\ C_{n+m} & D_{n+m} \end{bmatrix}.$$

(2.5)

However, this still requires a prior knowledge of the ABCD parameters of the previous stages. A further thorough analytical treatment requires the extraction of the entire behavior of the complex propagation constant through dispersion diagrams of the EM modes supported by the periodic structure. A modified Brillouin zone diagram could also gives insight into the range of frequencies attenuated by the structure [42].

Even though analytical approaches give much needed insight, a much simpler mechanism to design and model slow wave based structures is to use a full wave EM analysis through EM simulation software. It should be noted that the attenuation in the stop band depends on the dimensions of the slow wave structure. The pass band characteristics are also affected by the lattice dimensions as increasing the size tends to increase the effective dielectric constant and also leads to a variation in characteristic impedance and hence, greater mismatch. Therefore, by carefully understanding the impact of each of these parameters, the modeling challenge can be translated directly

from an EM based analytical approach to a parameter based simulation approach through a software tool.

#### 2.3.2 Existing slow wave structures

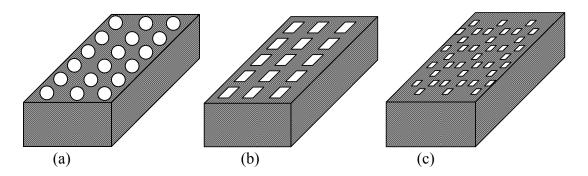

Since the first demonstration of slow wave structures as a viable technique to improve the performance and dimensions of microwave circuits in 1997, extensive studies have been undertaken to apply them to planar microwave circuit design using monolithic substrates. Figure 2.9 shows some traditional slow wave structures which require exorbitant dimensions and lattice spacing, making them incompatible for monolithic implementation.