# A FULLY INTEGRATED MULTI-BAND MULTI-OUTPUT SYNTHESIZER WITH WIDE-LOCKING-RANGE 1/3 INJECTION LOCKED DIVIDER UTILIZING SELF-INJECTION TECHNIQUE FOR MULTI-BAND MICROWAVE SYSTEMS

A Dissertation

by

SANG HUN LEE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

August 2012

Major Subject: Electrical Engineering

# A FULLY INTEGRATED MULTI-BAND MULTI-OUTPUT SYNTHESIZER WITH WIDE-LOCKING-RANGE 1/3 INJECTION LOCKED DIVIDER UTILIZING SELF-INJECTION TECHNIQUE FOR MULTI-BAND MICROWAVE SYSTEMS

## A Dissertation

by

# SANG HUN LEE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Cam Nguyen Committee Members, Aydin Karsilayan

Laszlo Kish

Binayak Mohanty

Head of Department, Costas N. Georghiades

August 2012

Major Subject: Electrical Engineering

#### ABSTRACT

A Fully Integrated Multi-Band Multi-Output Synthesizer with Wide-Locking-Range 1/3

Injection Locked Divider Utilizing Self-Injection Technique for Multi-Band Microwave

Systems. (August 2012)

Sang Hun Lee, B.S., Kwangwoon University, Korea;

M.S., Kwangwoon University

Chair of Advisory Committee: Dr. Cam Nguyen

This dissertation reports the development of a new multi-band multi-output synthesizer, 1/2 dual-injection locked divider, 1/3 injection-locked divider with phase-tuning, and 1/3 injection-locked divider with self-injection using 0.18-µm CMOS technology. The synthesizer is used for a multi-band multi-polarization radar system operating in the K- and Ka-band.

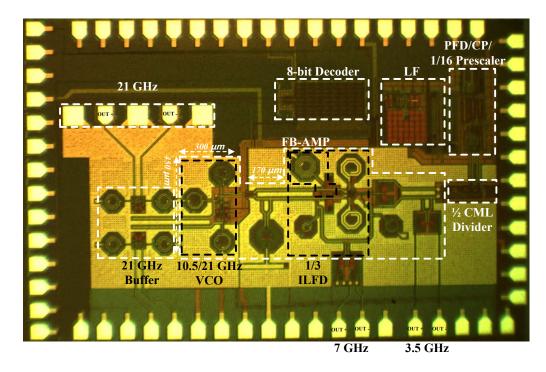

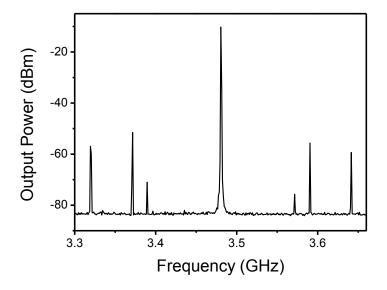

The synthesizer is a fully integrated concurrent tri-band, tri-output phase-locked loop (PLL) with divide-by-3 injection locked frequency divider (ILFD). A new locking mechanism for the ILFD based on the gain control of the feedback amplifier is utilized to enable tunable and enhanced locking range which facilitates the attainment of stable locking states. The PLL has three concurrent multiband outputs: 3.47-4.313 GHz, 6.94-8.626 GHz and 19.44-21.42-GHz. High second-order harmonic suppression of 62.2 dBc is achieved without using a filter through optimization of the balance between the differential outputs. The proposed technique enables the use of an integer-N architecture

for multi-band and microwave systems, while maintaining the benefit of the integer-N architecture; an optimal performance in area and power consumption.

The 1/2 dual-ILFD with wide locking range and low-power consumption is analyzed and designed together with a divide-by-2 current mode logic (CML) divider. The 1/2 dual-ILFD enhances the locking range with low-power consumption through optimized load quality factor ( $Q_L$ ) and output current amplitude ( $i_{OSC}$ ) simultaneously. The 1/2 dual-ILFD achieves a locking range of 692 MHz between 7.512 and 8.204 GHz. The new 1/2 dual-ILFD is especially attractive for microwave phase-locked loops and frequency synthesizers requiring low power and wide locking range.

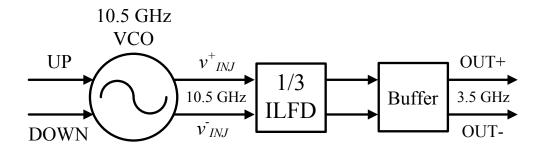

The 3.5-GHz divide-by-3 (1/3) ILFD consists of an internal 10.5-GHz Voltage Controlled Oscillator (VCO) functioning as an injection source, 1/3 ILFD core, and output inverter buffer. A phase tuner implemented on an asymmetric inductor is proposed to increase the locking range.

The other divide-by-3 ILFD utilizes self-injection technique. The self-injection technique substantially enhances the locking range and phase noise, and reduces the minimum power of the injection signal needed for the 1/3 ILFD. The locking range is increased by 47.8 % and the phase noise is reduced by 14.77 dBc/Hz at 1-MHz offset.

# DEDICATION

To my aunt, my brothers and sisters, and my lovely wife and son

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my doctoral advisor, Prof. Cam Nguyen, for his guidance, support, and encouragement throughout my research at Texas A&M University. His instructions are very valuable to my effort of developing the RF Synthesizer using injection locking for multiband microwave and millimeter-wave communication and radar systems. He believed in me from the beginning of the effort, and has been a constant source of encouragement throughout its duration. I thank to my committee members, Dr. Karsilayan, Dr. Kish, Dr. Mohanty, for their time and valuable suggestions. I also gained much from their course on broadband RF systems and low noise circuitry. The work presented in this dissertation could not have happened without helps and supports from many people.

I would like to thank my parents and my elder brother for their love, support and encouragement during these many years in the graduate school. Finally, I would like to express my love and gratitude to my beloved wife, Hyoeun Kim, son, Daniel Danhee Lee for the endless care and happiness brought throughout my degree studies.

This work was supported in part by the U.S Air Force Office of Science Research and in part by the U.S. National Institute of Justice.

# TABLE OF CONTENTS

|           |                                                                                                                                                                                                 | Page                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| ABSTRAC   | T                                                                                                                                                                                               | iii                                  |

| DEDICATI  | ON                                                                                                                                                                                              | V                                    |

| ACKNOW.   | LEDGEMENTS                                                                                                                                                                                      | vi                                   |

| TABLE OF  | CONTENTS                                                                                                                                                                                        | vii                                  |

| LIST OF F | IGURES                                                                                                                                                                                          | X                                    |

| LIST OF T | ABLES                                                                                                                                                                                           | xvi                                  |

| CHAPTER   |                                                                                                                                                                                                 |                                      |

| I         | INTRODUCTION                                                                                                                                                                                    | 1                                    |

| II        | BACKGROUND                                                                                                                                                                                      | 6                                    |

|           | 1. Principles of Phase-Locked Loop  A. Phase/Frequency Detector  B. Charge Pump and Loop Filter  C. Voltage Controlled Oscillator  D. Linear Model of PLL  E. Frequency Divider  2. Conclusions | 6<br>7<br>10<br>12<br>12<br>16<br>20 |

| III       | LOCKED 1/2 DIVIDER                                                                                                                                                                              | 21                                   |

|           | LOCKED 1/2 DIVIDER                                                                                                                                                                              | 21                                   |

|           | 1. Introduction                                                                                                                                                                                 | 21                                   |

|           | 2. Divide-by-2 Divider using Single-Injection                                                                                                                                                   | 26                                   |

|           | 3. Proposed Divide-by-2 using Dual-Injection                                                                                                                                                    | 29<br>29                             |

|           | A. The Proposed Concept of Dual-Injection  B. Design of Proposed Divide-by-2 Dual-ILFD                                                                                                          | 29<br>35                             |

|           | 4. Measured Results                                                                                                                                                                             | 40                                   |

|           | 5. Conclusion                                                                                                                                                                                   | 49                                   |

| CHAPTER |                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| IV      | A FULLY INTEGRATED 0.18-μm BiCMOS DIVIDE-BY-3                                                                                                                                                                                                                                                                                                                                                      |                                                |

|         | INJECTION-LOCKED FREQUENCY DIVIDER IMPLEMENTING                                                                                                                                                                                                                                                                                                                                                    |                                                |

|         | PHASE TUNING TECHNIQUE                                                                                                                                                                                                                                                                                                                                                                             | 50                                             |

|         | <ol> <li>Introduction</li> <li>Circuit Design and Analysis</li> <li>Measurement Results</li> <li>Conclusion</li> </ol>                                                                                                                                                                                                                                                                             | 50<br>52<br>58<br>64                           |

| V       | NEW DIVIDE-BY-3 INJECTION LOCKED FREQUENCY                                                                                                                                                                                                                                                                                                                                                         |                                                |

|         | DIVIDER UTILIZING SELF-INJECTION TECHNIQUE                                                                                                                                                                                                                                                                                                                                                         | 65                                             |

|         | <ol> <li>Introduction</li> <li>Circuit Design and Analysis</li> <li>Phase Noise Analysis of ILFD</li> <li>Measurement Results</li> <li>Conclusion</li> </ol>                                                                                                                                                                                                                                       | 65<br>67<br>70<br>71<br>80                     |

| VI      | A FULLY INTEGRATED MULTI-OUTPUT SYNTHESIZER FOR                                                                                                                                                                                                                                                                                                                                                    |                                                |

|         | MULTI-BAND MICROWAVE SYSTEMS                                                                                                                                                                                                                                                                                                                                                                       | 81                                             |

|         | <ol> <li>Introduction</li> <li>Limitations of Conventional Calibration Techniques</li> </ol>                                                                                                                                                                                                                                                                                                       | 81                                             |

|         | for Super-Harmonic-ILFD PLL  3. Proposed Architecture and Calibration Mechanism for Super-Harmonic-ILFD PLL.  4. Sub-Blocks of Triple-Band PLL  A. 10.5/21 GHz VCO and 21 GHz Buffer  B. 1/3 ILFD.  C. The Proposed Mode-Converter and Minimized Mismatch Gain/Phase for Differential Outputs.  D. 1/2 CML Divider, 1/16 Prescaler, PFD, CP, and LF.  E. Latched 8-bit Decoder for Digital Control | 84<br>87<br>90<br>93<br>96<br>99<br>101<br>102 |

|         | 5. Results                                                                                                                                                                                                                                                                                                                                                                                         | 102                                            |

|         | 6. Conclusion                                                                                                                                                                                                                                                                                                                                                                                      | 111                                            |

| CHA | APTER |                         | Page |

|-----|-------|-------------------------|------|

|     | VII   | SUMMARY AND CONCLUSIONS | 112  |

| REF | ERENC | CES                     | 115  |

| VIT | Δ.    |                         | 121  |

# LIST OF FIGURES

| FIGURE    |                                                                                                                                                                                       | Page |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 1.1  | Block diagram of a PLL                                                                                                                                                                | 2    |

| Fig. 2.1  | PLL as a negative feedback system                                                                                                                                                     | 6    |

| Fig. 2.2  | Transfer function of PFD                                                                                                                                                              | 8    |

| Fig. 2.3  | Block diagram of PFD using sequential method of 3 states: (a) schematic, (b) state machine                                                                                            | 8    |

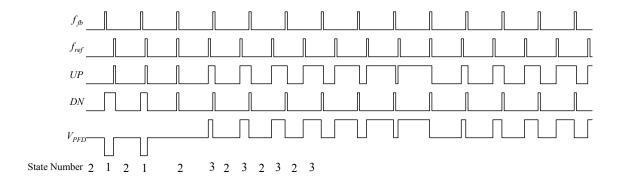

| Fig. 2.4  | The output signal of PFD using 3-state sequential method                                                                                                                              | 9    |

| Fig. 2.5  | The transfer function of PFD in dead zone                                                                                                                                             | 9    |

| Fig. 2.6  | Block diagram of PFD with gate delayed using inverters                                                                                                                                | 10   |

| Fig. 2.7  | Schematic of the charge pump (CP) with loop filter (LF)                                                                                                                               | 11   |

| Fig. 2.8  | Linear model of the PLL in Fig. 2.1                                                                                                                                                   | 13   |

| Fig. 2.9  | Modified loop filter (LF) for stabilization with R <sub>P</sub>                                                                                                                       | 14   |

| Fig. 2.10 | Transfer function and phase margin of a linear PLL model (a) without R <sub>p</sub> and (b) with R <sub>p</sub>                                                                       | 15   |

| Fig. 2.11 | CML frequency divider for 1/2 division: (a) block diagram using flip-flop, (b) schematic of each latch                                                                                | 17   |

| Fig. 2.12 | 2 Schematic of ILFD [24], [31]                                                                                                                                                        | 19   |

| Fig. 2.13 | Operation of ILFD: (a) phasor interpretation between $\omega_o$ and $\omega_i$ . $Z_{11}$ is the input impedance of the resonator, (b) phasor diagram between $i_{OSC}$ and $i_{INJ}$ | 19   |

| Fig. 3.1  | A conventional DILFD with single injection at NMOS: (a) schematic, (b) equivalent model using mixer, BPF, multiplier N, and (c) phasor diagram between $i_{OSC}$ and $i_{INJ}$        | 23   |

| FIGURE                                                                                                                                                                                                                                                                                                                              | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 3.2 Conventional 1/2 super-harmonic DILFD using single-injection: (a) circuit schematic, (b) output of divider (upper) with injection, $V_{INJ}$ (lower), and (c) phasor interpretation between $\omega_0$ and $\omega_i$ . Z11 is the input impedance of the resonator                                                        | 26   |

| Fig. 3.3 Behavioral model of the proposed 1/2 dual-ILFD                                                                                                                                                                                                                                                                             | 27   |

| Fig. 3.4 Schematic of the proposed 1/2 dual-ILFD. A 1/2 CML frequency divider is integrated with the dual-ILFD and used to compensate for the output voltage variation. The injection signal is via either a balun or divider                                                                                                       | 28   |

| Fig. 3.5 Equivalent circuit of resonator with external load R <sub>L</sub>                                                                                                                                                                                                                                                          | 30   |

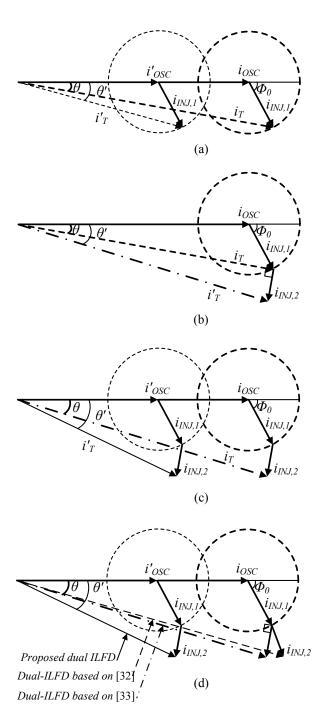

| Fig. 3.6 Phasor diagram for (a) single-injection vs. single-injection with reduced $i_{OSC}$ and hence reduced $Q_L$ , (b) single-injection vs. dual-injection, (c) dual-injection with and without reducing $i_{OSC}$ (equivalent to with and without optimized $Q_L$ ), and (d) proposed dual injection vs. other dual injection. | 33   |

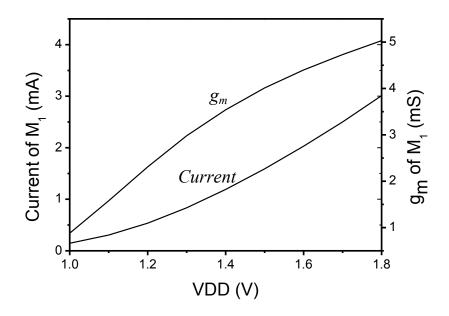

| Fig. 3.7 Simulation results of $1/2$ dual ILFD: current and $g_m$ of $M_1$                                                                                                                                                                                                                                                          | 37   |

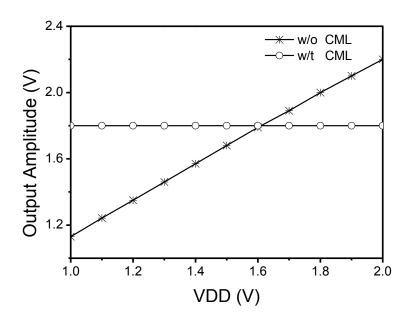

| Fig. 3.8 Output amplitude of 1/2 dual-ILFD versus <i>VDD</i>                                                                                                                                                                                                                                                                        | 37   |

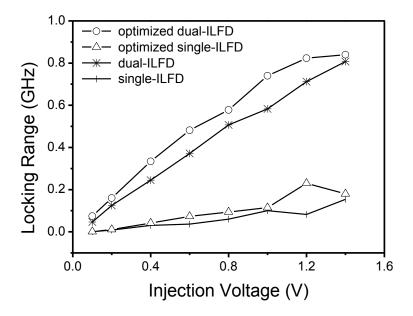

| Fig. 3.9 Locking range characteristics of the proposed 1/2 dual-ILFD versus injection voltage for different settings                                                                                                                                                                                                                | 39   |

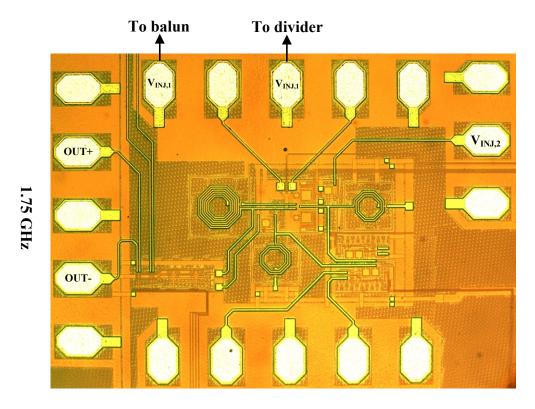

| Fig. 3.10 Die photograph of the $1/2$ dual-ILFD. Size: $0.8 \text{mm}^2$ (with pads), $0.156 \text{mm}^2$ (without pads). $V_{\text{INJ},1}$ is connected to either a balun or a divider                                                                                                                                            | 40   |

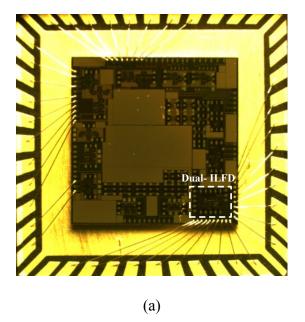

| Fig. 3.11 Microphotograph of the designed 1/2 dual-ILFD (a) packaged chip mounted on FR-4 PCB (b).                                                                                                                                                                                                                                  | 41   |

| Fig. 3.12 Measured kVCO and output power without injection                                                                                                                                                                                                                                                                          | 42   |

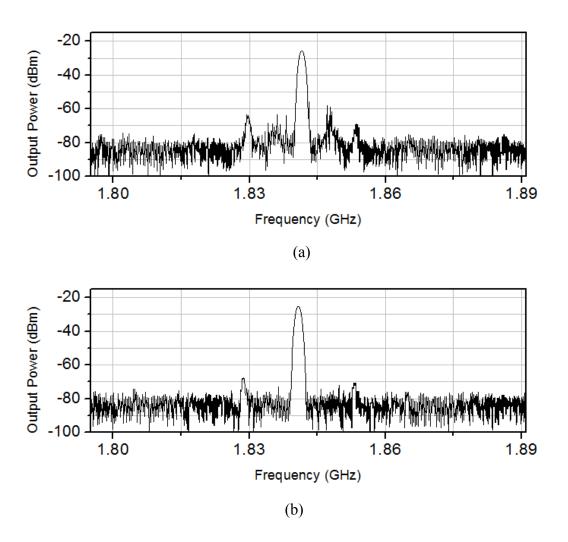

| Fig. 3.13 Measured output spectrum of (a) the free-running 1/2 dual-ILFD and (b) the locked 1/2 dual-ILFD                                                                                                                                                                                                                           | 43   |

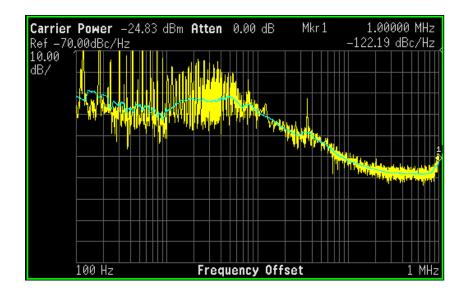

| Fig. 3.14 Measured phase noise of the locked 1/2 dual-ILFD                                                                                                                                                                                                                                                                          | 44   |

| FIGURE    |                                                                                                                                                        | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

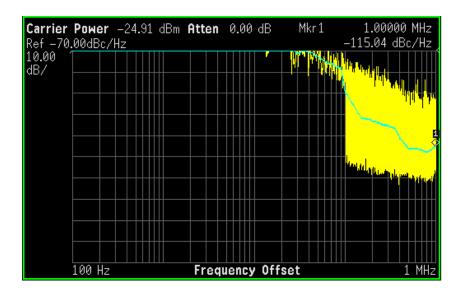

| Fig. 3.15 | Measured phase noise of the unlocked 1/2 dual-ILFD                                                                                                     | 45   |

| Fig. 3.16 | Measured phase noise of the locked 1/2 dual-ILFD                                                                                                       | 45   |

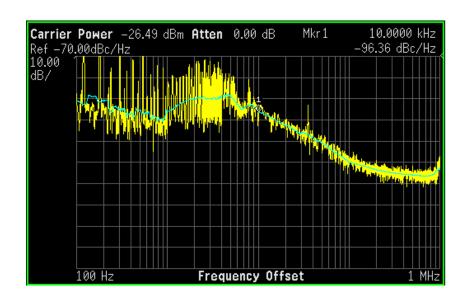

| Fig. 3.17 | Measured phase noise of the locked 1/2 dual-ILFD                                                                                                       | 46   |

| Fig. 3.18 | Measured phase noise of 7 GHz external source                                                                                                          | 46   |

| Fig. 3.19 | Measured locking range with single-injection and dual-injection for 1/2 function                                                                       | 47   |

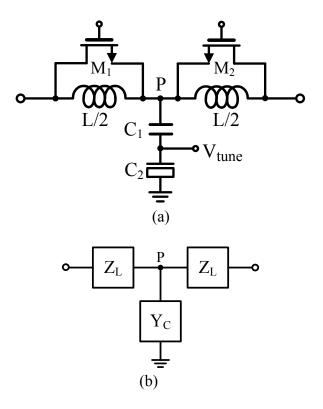

| Fig. 4.1  | (a) Block diagram model and (b) circuit schematic of the integrated divide-by-3 ILFD                                                                   | 51   |

| Fig. 4.2  | (a) Phase tuner and (b) its equivalent model                                                                                                           | 54   |

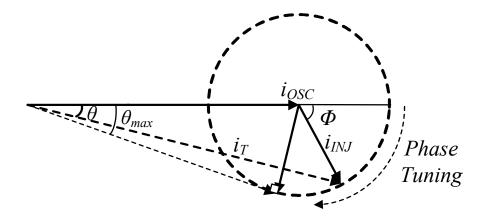

| Fig. 4.3  | Phase diagram between currents in the integrated ILFD                                                                                                  | 57   |

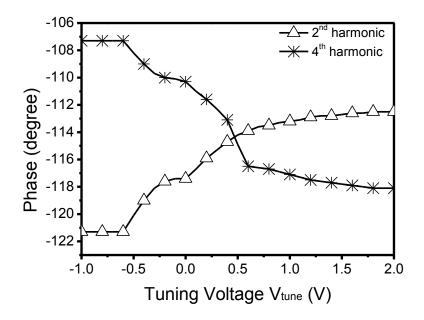

| Fig. 4.4  | Phase of the 2 <sup>nd</sup> and 4 <sup>th</sup> harmonic                                                                                              | 57   |

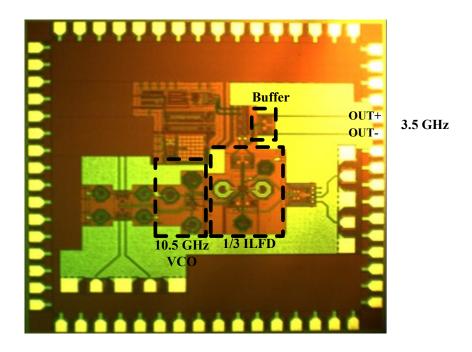

| Fig. 4.5  | Integrated ILFD with constituent components                                                                                                            | 59   |

| Fig. 4.6  | Die photograph of the integrated 1/3 ILFD. Size: 2mm² (with pads), 0.42mm² (without pads) for 1/3 ILFD chain, 0.25mm² (without pads) for 1/3 ILFD core | 59   |

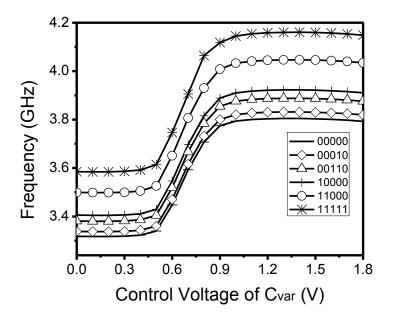

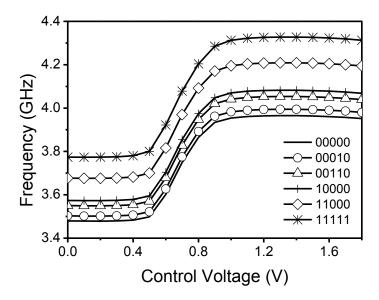

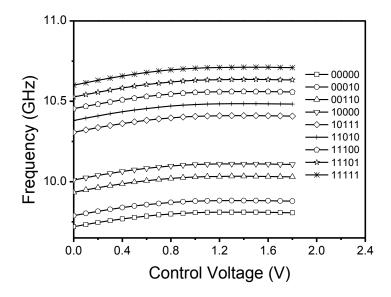

| Fig. 4.7  | Measured free-running frequency tuning range of the integrated 1/3 ILFD with 5-bit digital control                                                     | 61   |

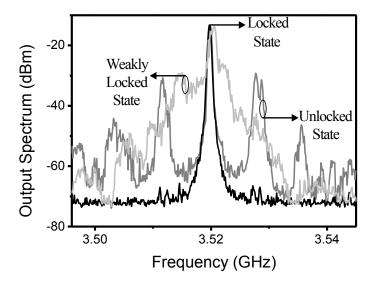

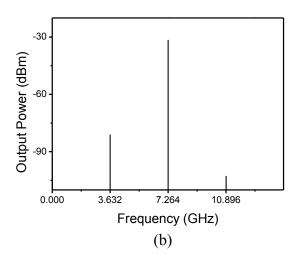

| Fig. 4.8  | Measured output spectrum in locked and unlocked states                                                                                                 | 61   |

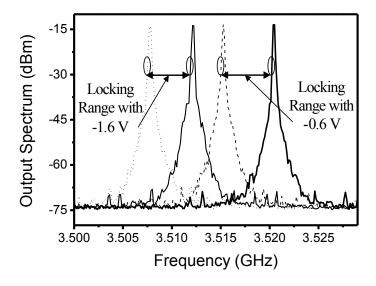

| Fig. 4.9  | Measured locking range for different phase tuning                                                                                                      | 62   |

| Fig. 4.10 | Microphotograph of the designed 1/3 ILFD (a) packaged chip mounted on FR-4 PCB (b).                                                                    | 63   |

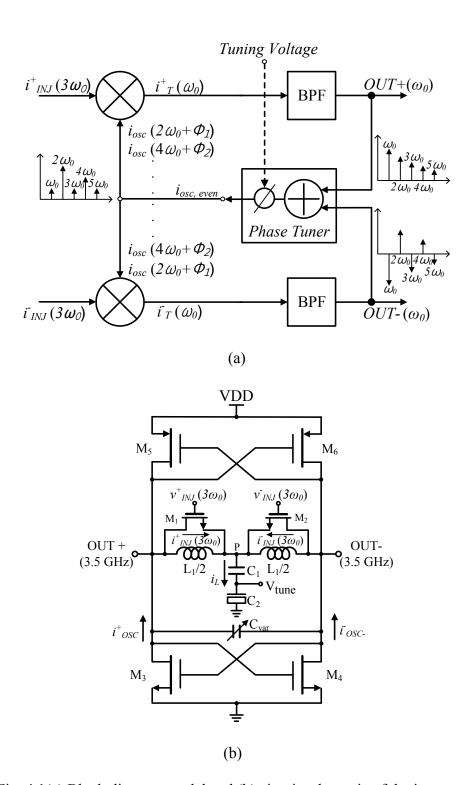

| Fig. 5.1  | Block diagram of the proposed divide-by-3 ILFD                                                                                                         | 66   |

| Fig. 5.2  | The schematic of the proposed divide-by-3 ILFD                                                                                                         | 67   |

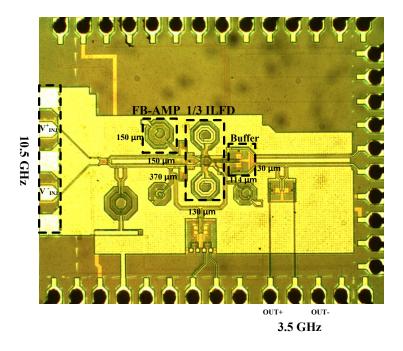

| Fig. 5.3  | Die photograph of the proposed 1/3 ILFD chain with gain-boosted amplifier                                                                              | 72   |

| FIGURE    |                                                                                                                           | Page |

|-----------|---------------------------------------------------------------------------------------------------------------------------|------|

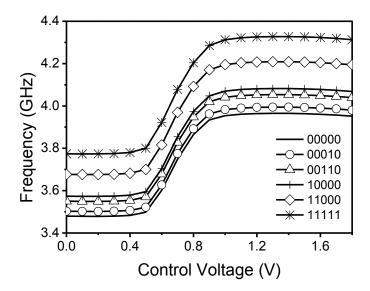

| Fig. 5.4  | Measured frequency tuning range vs. varactor control voltage for different capacitor arrays as noted in the digital codes | 73   |

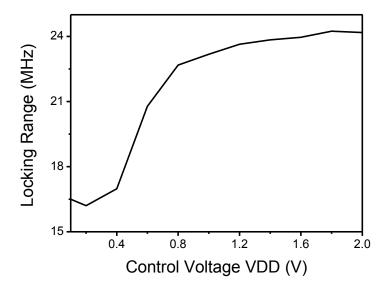

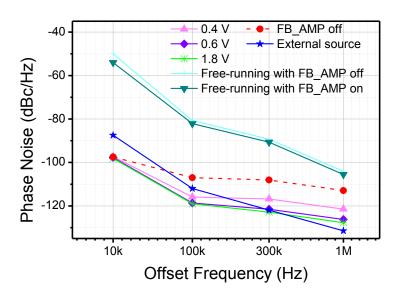

| Fig. 5.5  | Measured locking range vs. control voltage VDD of feedback amplifier under fixed capacitor array at 00110                 | 73   |

| Fig. 5.6  | Measured locking range for fixed capacitor array at setting 00110                                                         | 74   |

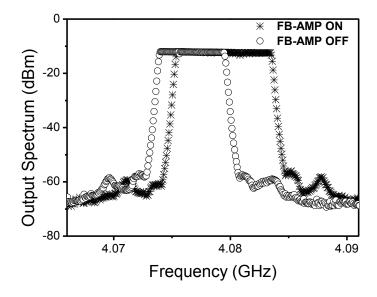

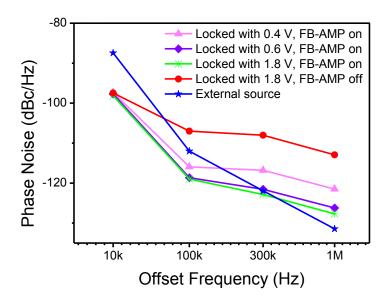

| Fig. 5.7  | Measured phase noise under fixed capacitor array at 00110                                                                 | 74   |

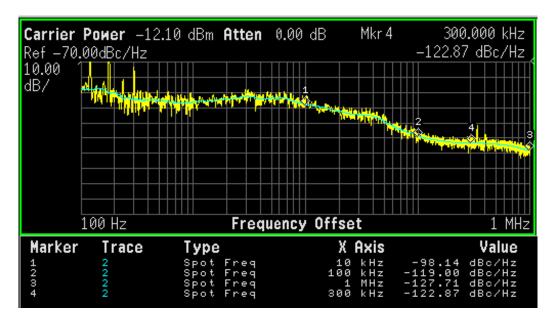

| Fig. 5.8  | Measured phase noise with feedback amplifier ON at 1.8-V control voltage for fixed capacitor array at 00110.              | 75   |

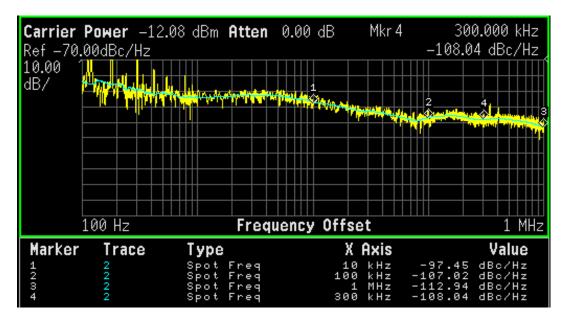

| Fig. 5.9  | Measured phase noise with feedback amplifier OFF at 1.8-V control voltage for fixed capacitor array at 00110              | 76   |

| Fig. 5.10 | Measured phase noise with feedback amplifier ON at 1.8-V control voltage for fixed capacitor array at 00110               | 77   |

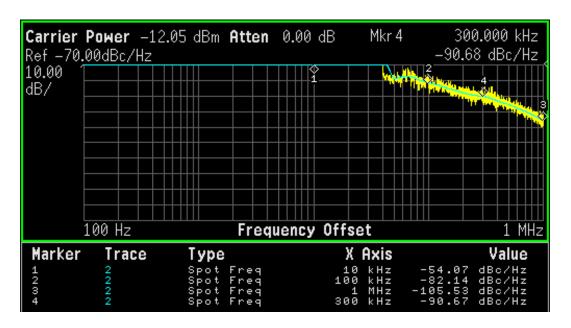

| Fig. 5.11 | Measured phase noise with feedback amplifier OFF at 1.8-V control voltage for fixed capacitor array at 00110              | 77   |

| Fig. 5.12 | Measured phase noise of the external 12.247 GHz injection source                                                          | 78   |

| Fig. 5.13 | Microphotograph of the designed 1/3 ILFD (a) packaged chip mounted on FR-4 PCB (b).                                       | 79   |

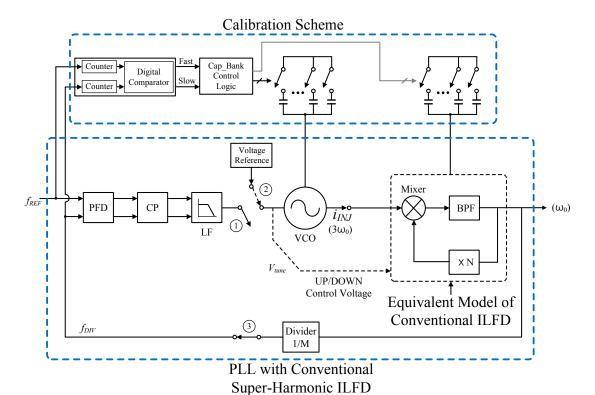

| Fig. 6.1  | Block diagram of PLL with conventional super-harmonic ILFD and calibration scheme for VCO frequency at coarse-locking     | 84   |

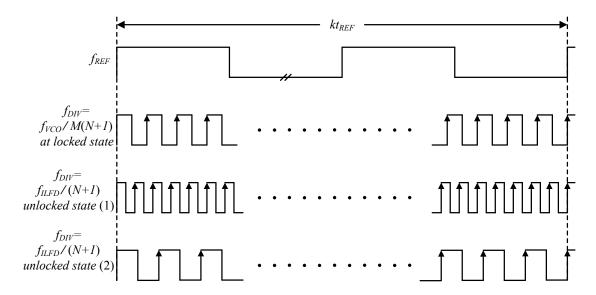

| Fig. 6.2  | Timing diagram of the frequency comparison techniques in ILFD PLL                                                         | 86   |

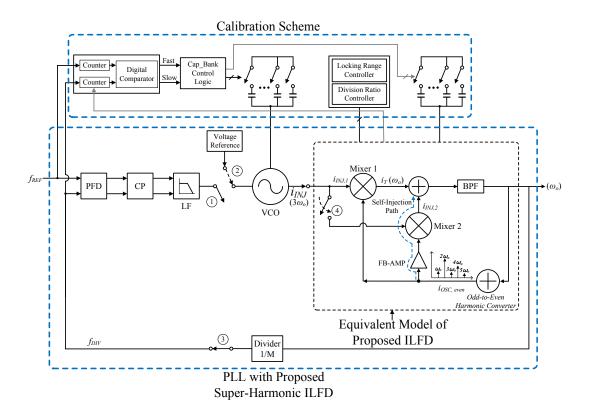

| Fig. 6.3  | Block diagram of the proposed ILFD PLL and calibration scheme for VCO frequency at coarse-locking                         | 88   |

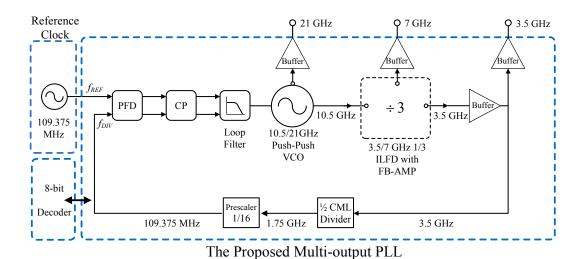

| Fig. 6.4  | Block diagram of the multi-output PLL integrating all, except the reference clock, on a single chip                       | 89   |

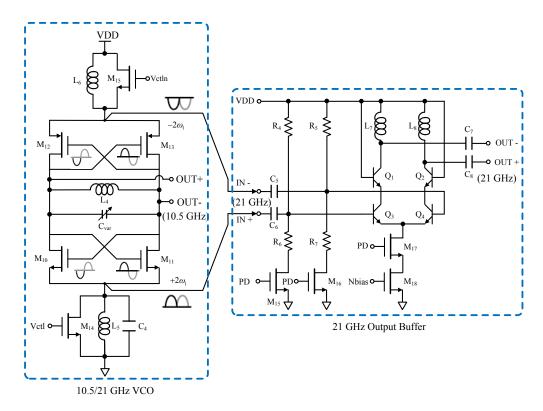

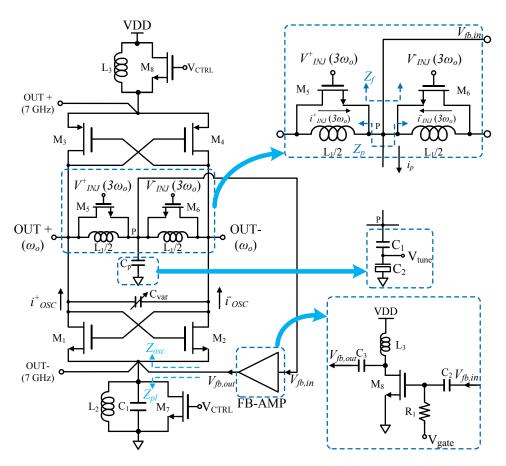

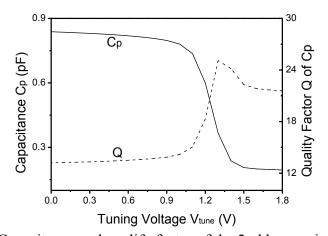

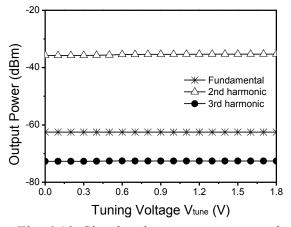

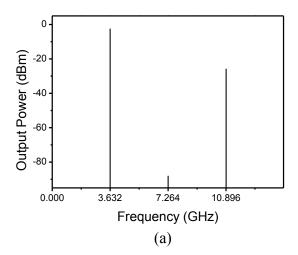

| Fig. 6.5  | Schematic of the 10.5/21-GHz push-push VCO and 21-GHz buffer                                                              | 91   |

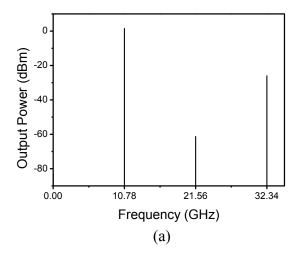

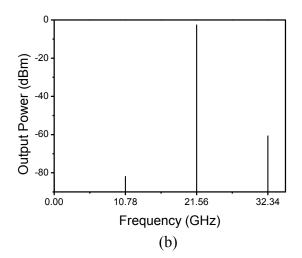

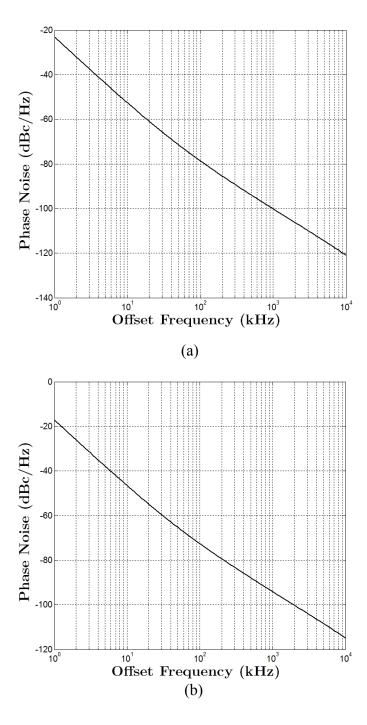

| 92 |

|----|

| 94 |

| 95 |

| 96 |

| 96 |

| 97 |

| 99 |

| )1 |

| )2 |

| )5 |

| )5 |

| 06 |

| 06 |

| 07 |

| )7 |

|    |

| FIGURE    |                                                                                                                           | Page |

|-----------|---------------------------------------------------------------------------------------------------------------------------|------|

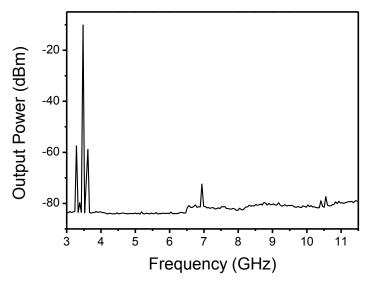

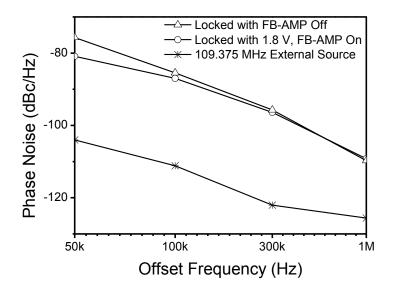

| Fig. 6.21 | Measured phase noise of the PLL                                                                                           | 108  |

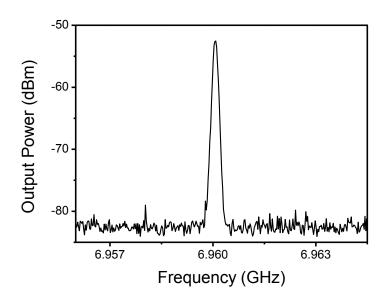

| Fig. 6.22 | Measured output spectrum of the PLL at the 7- GHz port. RBW: 100 kHz, VBW: 30 kHz, SPAN: 10 MHz, REF: -10 dBm, and ATT: 0 | 108  |

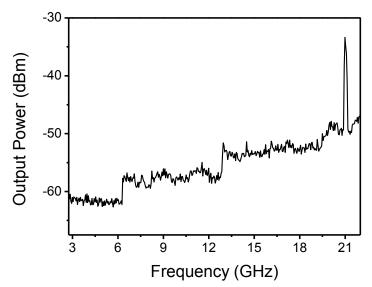

| Fig. 6.23 | Measured output spectrum of the PLL at the 21-GHz port. RBW: 3 MHz, VBW: 1 MHz, SPAN: 19.25 GHz, REF: 0 dBm, and ATT: 0   | 109  |

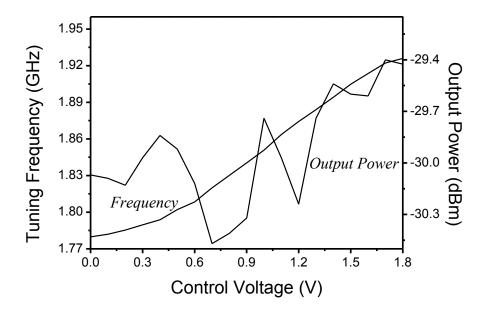

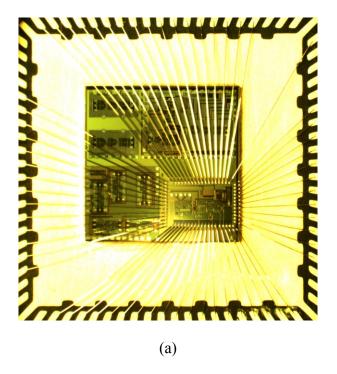

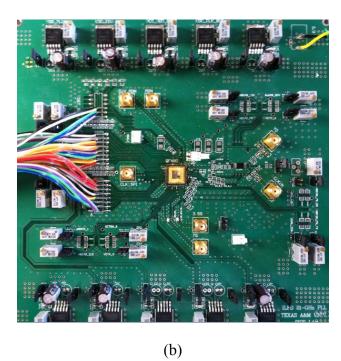

| Fig. 6.24 | Microphotograph of the designed ILFD PLL (a) packaged chip mounted on FR-4 PCB (b).                                       | 110  |

# LIST OF TABLES

| TABLE |                                                                        | Page |

|-------|------------------------------------------------------------------------|------|

| 2.1   | Comparison between divider types                                       | 16   |

| 3.1   | Comparison of measurement results between proposed ILFD and others     | 48   |

| 6.1   | Simulated results of harmonic suppression of the proposed ILFD         | 98   |

| 6.2   | Comparison of measurement results between proposed ILFD PLL and others | 109  |

## CHAPTER I

#### INTRODUCTION

Phase-locked loops (PLLs) have been introduced for synchronization of horizontal and vertical scans of television in early 1940s. It has become one of the most essential components in many electronic systems including televisions, radios, computers and communication systems, etc. PLL uses a control mechanism to reduce the phase error between the reference signal and the oscillator output while the loop is in a locked state. In early days, PLL was used in control systems such as motor speed control and so on and numerous research works have been conducted to improve the performance of PLL for the systems under high-noise environment. With the rapid development of radio communication systems since 1970s, PLLs have served important roles such as FM demodulation, synchronization, and frequency synthesis in the communication systems. Unlike the control systems, the communication systems are very susceptible to any noise sources since they determine the system fidelity and hence the quality of communications. Therefore, the spectral purity of the desired signal is one of the main concerns in building communication systems.

In communication systems, clean and stable periodic signal sources should be available for various functions such as signal transmission, generating a clock signal, calibrating a sampling clock, providing local oscillator (LO) signals, etc. PLL as a

Journal model is IEEE Transaction on Microwave Theory and Techniques.

frequency synthesizer can perform these functions inside systems. With the advances in semiconductor technology and IC fabrication process over the past few decades, people have been striving to integrate a frequency synthesizer together with whole transceiver subsystem on a single chip for cost-effectiveness and size reduction of the system. However, a major problem of an integrated PLL is the noise from the power supply, which is directly converted to phase noise at PLL. The noise from a power supply can enter a PLL directly via physical connections which can be reduced significantly by different design techniques like differential circuit implementation. The noise from a power supply and other nearby circuits can also arrive at the PLL through substrates, particularly the conductive Si substrate; this noise is difficult to reduce [1]-[4]. In order to improve power supply noise and common-mode noise rejection characteristics, the differential structure is commonly utilized for on-chip frequency synthesizer design [5]-

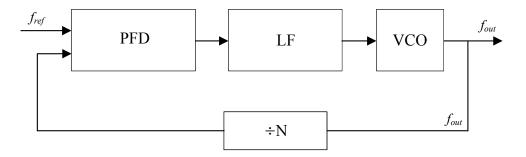

Fig. 1.1. Block diagram of a PLL

Figure 1.1 shows a conventional PLL structure working as a frequency synthesizer. The voltage-controlled oscillator (VCO) output signal is divided and its frequency  $f_{out}$  and phase are compared with those of a clean reference signal (at  $f_{ref}$ ) in a phase-frequency detector (PFD). Any misalignment in the frequency and phase between the two signals will be converted to voltage at the output of the PFD, which is filtered by the loop filter (LF). The output voltage of the LF tunes the VCO's free-running frequency until a perfect alignment of frequency and phase between the two signals occurs.

For proper phase and frequency locking, which is the main objective of PLL, a frequency divider denoted by ÷N in Fig.1.1 must be able to provide the same frequency as the reference frequency to the PFD. Frequency division can be performed in either analog or digital domains. Analog frequency dividers are usually used at high frequencies while digital frequency dividers are at relatively low frequencies for reduced power consumption.

Therefore, in microwave and, especially, millimeter-wave applications, analog type is preferred as an initial stage of the frequency division and then digital type of the frequency division follows. Among different types of frequency dividers, injection-locked frequency divider (ILFD) is getting more attention for its low power and high frequency operation [9]-[12]. However, ILFD typically suffers from narrow locking range over which a frequency division can be supported. In fully integrated PLL system, an internal VCO is used to supply the injection signal with limited output power, which

directly leads to the limited locking range. Therefore, a new ILFD design is necessary to overcome the limitation on locking range under relatively small injection power.

Conventional PLL is usually designed to produce a single frequency output at VCO, which is used as the LO signal for up/down conversion in carrier-based communication systems. However, there may be a need for systems supporting multiple frequency bands such as multi-band sensing applications. In that case, more than a single-frequency output should be available and hence PLL must be able to synthesize all frequencies required for multi-band systems. Typically, multiple VCOs are used to create multiple frequency outputs. However, it is challenging or may not be feasible to complete such systems at high frequencies under small DC power constraints. In order to overcome the difficulty, a push-push VCO structure, formed by combining two balanced outputs, is very attractive for generating multiple frequency outputs without consuming additional DC power. It can simultaneously generate both low and high frequencies with low speed ( $f_{max}$ ) transistors [13]-[16].

As introduced above, multi-band communication systems working "concurrently" over multiple bands provide significant advantages and have more capabilities compared to their single-band counterparts. Concurrent multiband systems allow communication and/or sensing to be performed at multiple frequencies simultaneously. To support these systems, concurrent multiband multi-output PLLs are needed, particularly, fully integrated CMOS/BiCMOS PLL's for complete systems on chips. The challenges for obtaining concurrent multiband multi-output in microwave CMOS PLLs using ILFD are the primary motivation of this research.

A new CMOS multiband multi-output PLL and three new ILFDs for microwave applications are proposed. Particularly, the multi-band PLL is based on the ILFD with feedback amplifier to enhance the locking range. It demonstrates an improvement in the locking range with low power and good phase noise characteristics.

The dissertation is organized into six chapters. Chapter II presents the background of PLL. Chapter III presents a rigorous analysis on the locking range of a dual-ILFD under the influence of dc-bias as well as injection signal. Chapter IV presents a wide locking range 1/3 ILFD design based on a new phase-tuning technique to improve the locking range. Chapter V presents a 1/3 ILFD design based on the self-injection technique. Chapter VI presents the concurrent multiband multi-output PLL utilizing the self-injection technique discussed in chapter V. Chapter VII draws the conclusions and provides the final remarks.

# CHAPTER II

# **BACKGROUND**

# 1. Principles of Phase-Locked Loop

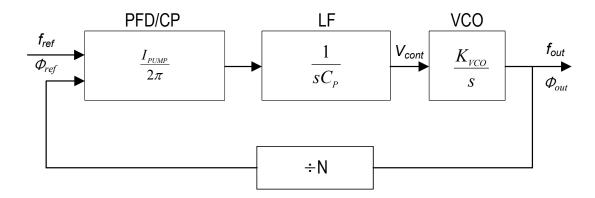

Conventional PLL is composed of the reference clock ( $f_{ref}$ ), phase frequency detector (PFD), charge pump (CP), loop filter (LF), and frequency divider (FD) as shown in Fig. 2.1. PFD determines the phase and frequency difference between the reference signal ( $f_{ref}$ ) and feedback signal ( $f_{fb}$ ) which is a divided-by-N version of  $f_{out}$ , and generates an error signal representing the phase/frequency difference. The output signal of the PFD is converted into current by the CP, which is low-pass filtered and converted into a control voltage ( $V_{cont}$ ) by the LF. Then, the output frequency of the

Fig. 2.1. PLL as a negative feedback system.

VCO  $(f_{out})$  is tuned by  $V_{cont}$  and divided by a factor of N to be compared with  $f_{ref}$  at the PFD. This procedure continues in a closed loop fashion until  $f_{out}$ =N· $f_{ref}$ . This is done in two steps. In the first step, the frequency difference between  $f_{ref}$  and  $f_{fb}$  is compared and adjusted until it becomes very small. In the second step, the phase error between the signals at  $f_{ref}$  and  $f_{fb}$  (i.e.,  $\Phi_{ref}$  -  $\Phi_{out}$ /N) is compared and adjusted until it is a constant, and hence the derivative of the phase error is zero, meaning that  $f_{out}$  is equal to N· $f_{ref}$ .

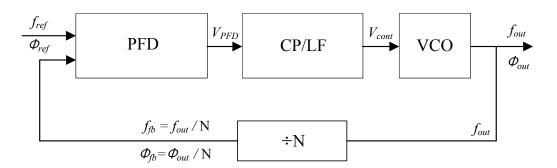

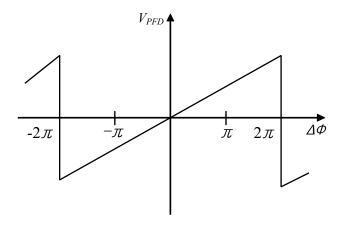

# A. Phase/Frequency Detector

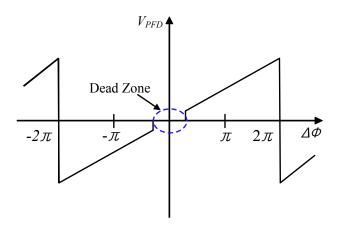

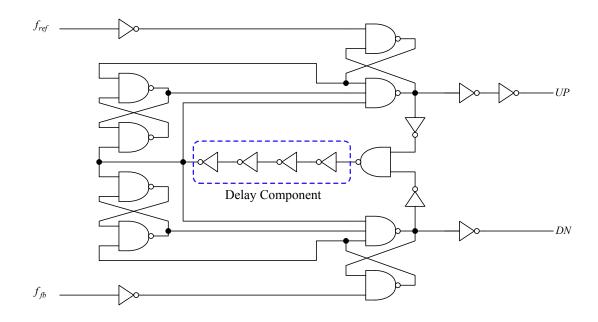

PFD produces an output signal having voltage proportional to the phase difference and frequency difference between the reference signal ( $f_{ref}$ ) and the output signal of the frequency divider ( $f_{fb}$ ). The transfer function of the PFD is shown in Fig. 2.2, where  $\Delta \Phi$  is the phase difference between the signals at  $f_{ref}$  and  $f_{fb}$ , which shows the phase dependence. Similar dependence is obtained for the frequency difference. The response manifests that the PFD has a (periodic) linear phase range within  $\pm 2\pi$ . When the PLL is in locked state (i.e., the output frequency fout is (ideally) equal to the desired frequency), the phase difference between  $f_{ref}$  and  $f_{fb}$  is normally very small and hence well within the PFD's linear operating region. Therefore, in the locked mode, the PFD is considered as a linear device. A PFD usually employs a memory device [17]-[18] such as flip flop and latch as shown in Fig. 2.3(a). The PFD state transitions and the events that cause these state transitions can be described using the state machine as shown in Fig. 2.3(b), where V↑ is a rising edge event of  $f_{fb}$  and R↑ is a rising edge event of  $f_{ref}$ . Each state of the PFD (state1, state2, and state2) yields a corresponding PFD output

Fig. 2.2 Transfer function of PFD.

Fig. 2.3. Block diagram of PFD using sequential method of 3 states: (a) schematic, (b) state machine.

Fig. 2.4. The output signal of PFD using 3-state sequential method.

Fig. 2.5. The transfer function of PFD in dead zone.

voltage. The output signal of PFD is according to the events of state machine as shown in Fig. 2.4. The most important factor to consider is a dead-zone effect in which the phase/frequency difference is not detected as shown in Fig. 2.5. Even though the input signal of PFD has a different phase and frequency compared to the reference signal, the system does not change the gain of the PFD (defined as the ratio between the output

voltage and the phase difference) and then the PLL loses the locking. To overcome this problem (due to finite gate delay), time delay is required to reset the time when UP/DOWN is 1 (high) in PFD. As seen in Fig. 2.6, there are delay components like an Inverter.

Fig. 2.6. Block diagram of PFD with gate delayed using inverters.

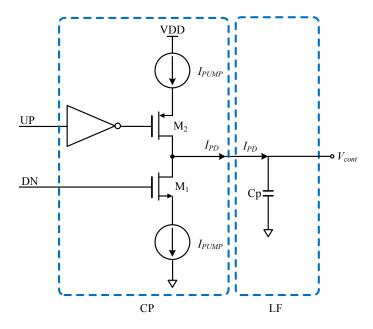

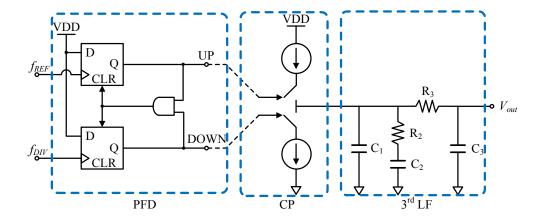

# B. Charge Pump and Loop Filter

CP takes the UP and DN outputs of the PFD as input signals and gives a single current output ( $I_{PD}$ ) [19]-[20]. Fig. 2.7 shows a simplified schematic of the CP and LF.

Fig. 2.7. Schematic of the charge pump (CP) with loop filter (LF).

When UP signal is in the "high" state, transistor  $M_2$  turns ON while transistor  $M_1$  is OFF, and the output current ( $I_{PD}$ ) has a positivity polarity. On the other hand, when the DN signal becomes high,  $M_1$  turns ON while  $M_2$  is OFF, and  $I_{PD}$  has a negative polarity. With the switching operations by  $M_1$  and  $M_2$  according to UP and DN signals, the charge pump output current can be expressed as [21]

$$\begin{split} I_{PD} &= \frac{I_{PUMP} - (-I_{PUMP})}{4\pi} \times \Delta \Phi \\ &= \frac{2I_{PUMP}}{4\pi} \times \Delta \Phi \\ &= \frac{I_{PUMP}}{2\pi} \times \Delta \Phi \\ &= K_{PD} \times \Delta \Phi \end{split} \tag{2.1}$$

where  $K_{PD}=I_{PUMP}/2\pi$  (amps/radian).

As seen in Fig. 2.7, the output current IPD of the CP is fed into the LF, which is a simple low-pass filter made by a shunt capacitor Cp, whose transfer function is simply given by

$$\frac{V_{cont}}{I_{PUMP}}(s) = \frac{1}{sC_p} \tag{2.2}$$

where  $s=j\omega$  is Laplace transform.

## C. Voltage Controlled Oscillator.

VCO (after the LF) generates a periodic output signal whose frequency depends on the applied control voltage ( $V_{cont}$ ) coming from the LF. Considering the VCO as a voltage-to-frequency converter for simplicity, its transfer characteristic can be written as

$$f_{out}(t) = K_{VCO}V_{cont} \tag{2.3}$$

where  $f_{out}(t)$  is the VCO output frequency and  $K_{VCO}$  is the gain of VCO in the unit of Hz/V. Integrating both sides of (2.3) versus time yields

$$\Phi_{out}(t) = K_{VCO} \int_0^t V_{cont} \quad or \quad \frac{\Phi_{out}}{V_{cont}}(s) = \frac{K_{VCO}}{s}$$

(2.4)

where  $V_{cont}$  is assumed as a constant, which has a DC value under ideal condition.

## D. Linear Model of PLL.

The PLL in Fig. 2.1 can be redrawn, considering each sub-block as a linear system, as a linear model shown in Fig. 2.8. The open-loop transfer function can be derived from Fig. 2.8 as

$$H(s)\big|_{open} = \frac{\Phi_{out}}{\Phi_{ref}}(s) = \frac{I_{PUMP}}{2\pi} \frac{K_{VCO}}{s^2}$$

(2.5)

The linear model in Fig. 2.8 also gives a closed-loop transfer function of

$$H(s)\big|_{closed} = \frac{\Phi_{out}}{\Phi_{ref}}(s) = N \cdot \frac{\frac{I_{PUMP}K'_{VCO}}{2\pi C_P}}{s^2 + \frac{I_{PUMP}K'_{VCO}}{2\pi C_P}}$$

(2.6)

where  $K'_{VCO} = \frac{K_{VCO}}{N}$ . The poles of the closed-loop transfer function are obtained from (2.6) as

$$s = \pm j \sqrt{\frac{I_{PUMP} K'_{VCO}}{2\pi C_P}}$$

(2.7)

Fig. 2.8. Linear model of the PLL in Fig. 2.1.

As described by (2.7), the closed-loop transfer function contains two imaginary poles, which suggests that the PLL system is unstable. In order to stabilize the system, an additional zero needs to be included in (2.6), which can be achieved by inserting

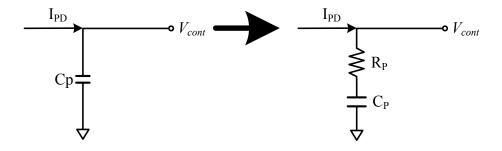

resistor  $R_P$  in series with  $C_P$  as shown in Fig. 2.9. With the added resistance ( $R_P$ ), the transfer function of the LF becomes

$$\frac{V_{cont}}{I_{PUMP}}(s) = \frac{1 + sR_pC_p}{sC_p}$$

(2.8)

where  $s=j\omega$ .

LF with zero R<sub>P</sub>

Fig. 2.9. Modified loop filter (LF) for stabilization with R<sub>P</sub>.

The closed-loop transfer characteristic of the PLL with modified LF can be written as

$$H(s)|_{closed} = N \cdot \frac{(1 + R_{p}C_{p}s) \frac{I_{PUMP}K'_{VCO}}{2\pi C_{p}}}{s^{2} + s \frac{I_{PUMP}K'_{VCO}}{2\pi} R_{p} + \frac{I_{PUMP}K'_{VCO}}{2\pi C_{p}}}$$

$$= N \cdot \frac{(1 + R_{p}C_{p}s)\omega_{n}^{2}}{s^{2} + 2s\zeta\omega_{n} + \omega_{n}^{2}}$$

(2.9)

where

$$\omega_n = \sqrt{\frac{I_{PUMP}K_{VCO}^{'}}{2\pi C_P}}$$

and  $\zeta = \frac{R_P}{2}\sqrt{\frac{I_{PUMP}C_PK_{VCO}^{'}}{2\pi}}$  with  $\omega_n$  being the natural

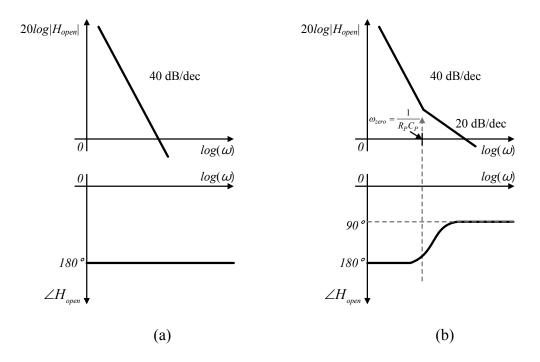

frequency and  $\zeta$  being the damping factor. Fig. 2.10 shows the open-loop transfer function of the linear PLL model shown in Fig. 2.8 without and with  $R_P$ . As shown in Fig. 2.10(a), the phase margin is zero and hence the PLL is unstable. On the other hand, as shown in Fig. 2.10(b), the addition of  $R_P$  creates a zero and produces a 90-deg phase margin, which stabilizes the system. However, it causes ripples (periodic fluctuations) on  $V_{cont}$ , which generates sideband spurious tones. To reduce sideband spurs as well as to provide the stability for PLL, therefore, it is common to insert additional poles and zeros at proper locations in PLL design [22].

Fig. 2.10. Transfer function and phase margin of a linear PLL model (a) without  $R_P$  and (b) with  $R_P$ .

# E. Frequency Divider

An external crystal oscillator is typically used as a reference source which has limited low frequency operation (up to a few hundreds of MHz) due to its physical property. On the other hand, the VCO typically has high frequency and hence the VCO output frequency needs to be divided until it is comparable to the reference frequency. Frequency division can be performed all in analog or digital domains, or combination of the two. Analog type frequency divider is normally used at the output of the VCO due to its high operation frequency with relatively low power consumption. There are different types of analog type frequency dividers such as current-mode logic (CML), true single-phase clock (TSPC), Miller type, and injection-locked (IL) type. The characteristics of each divider type are summarized in Table 2.1.

TABLE 2.1 Comparison between divider types

| Divider structure | Advantage                | Disadvantage                |

|-------------------|--------------------------|-----------------------------|

| CML               | High operating frequency | High power                  |

|                   | Good phase noise         |                             |

| TSPC              | Low power                | Limited operating frequency |

|                   |                          | Rail-to-rail swing          |

| Miller            | High operating frequency | High power                  |

|                   |                          | Poor phase noise            |

| IL                | High operating frequency | Narrow locking bandwidth    |

|                   | Low power                | _                           |

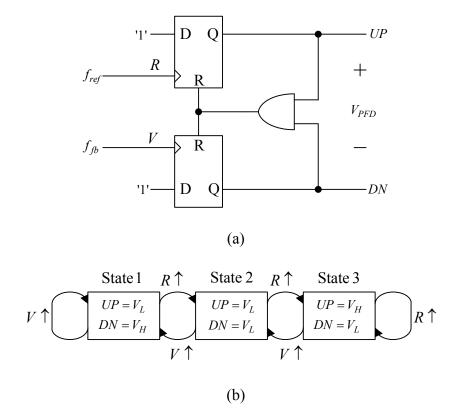

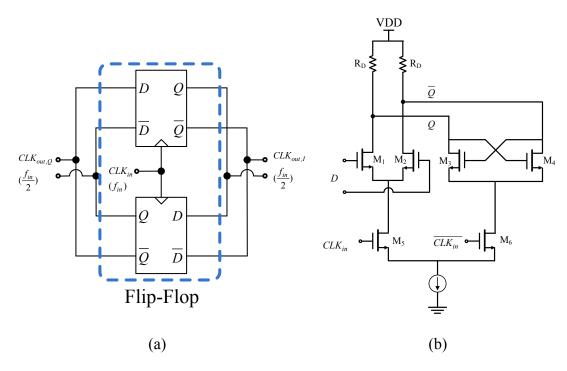

The CML divider is simply built with a D-flip-flop, where the output (Q) is feedback into the input (D) as shown in Fig. 2.11(a). The master-slave D-flip-flop is composed of differential circuit for each latch as shown in Fig. 2.11(b). It samples the input while  $M_1$  and  $M_2$  pair is activated, and holds the data by means of the cross-coupled  $M_3$  and  $M_4$ . At low frequencies, the latches locked the sampled data and wait until the next clock phase comes in. The loop gain of the positive feedback  $(M_3 - M_4)$  pair and  $R_D$  must exceed unity, and the output looks like a square wave under such a condition.

Fig. 2.11. CML frequency divider for 1/2 division: (a) block diagram using flip-flop, (b) schematic of each latch.

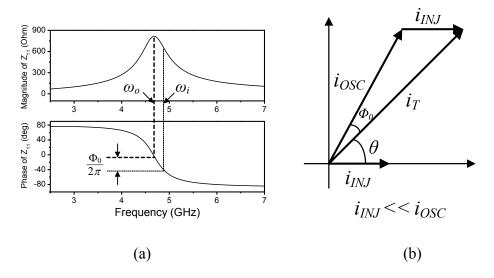

The injection-locked frequency divider can be implemented using tuned VCO (both LC VCO and ring VCO) resonating at a free-running frequency  $f_o$  [23]. Both LC VCO and ring VCO can be used to be a tuned VCO. A ring VCO has advantages of wide tuning range and small layout area compared to an LC VCO. However, an LC VCO typically exhibits superior performance in terms of phase noise, power consumption, and high frequency operating over a ring VCO. Fig. 2.12 shows the conceptual operation of injection locking in an oscillator. Assume that the required phase condition for oscillation is maintained and the total phase shift in the loop is zero at steady state. When the injection signal ( $i_{INJ}$ ) with the frequency of ( $\omega_i$ ) is applied, it causes a deviation in the free running frequency ( $\omega_o$ ) by  $\omega_i$  -  $\omega_o$ . Consequently a phase shift of  $\Phi_0/2\pi$  occurs in the resonator as shown in Fig. 2.13 and it forces the oscillation frequency to be  $\omega_i$  rather than  $\omega_o$ , where  $\Phi_0$  is the relative phase between the voltage and current in the resonator. The detailed explanation including a locking range is introduced in chapter III.

Fig. 2.12. Schematic of ILFD [24], [31].

Fig. 2.13. Operation of ILFD: (a) phasor interpretation between  $\omega_o$  and  $\omega_{i.}$  Z<sub>11</sub> is the input impedance of the resonator, (b) phasor diagram between  $i_{OSC}$  and  $i_{INJ}$ .

# 2. Conclusions

In this chapter, we have reviewed the principle of PLL design including PFD, CP, LF, frequency divider and VCO. It's transfer function and the linear model are briefly studied for the PLL itself. In the end, we have reviewed the ILFD and CML divider, for high frequency part and low frequency part in our design, respectively. This chapter presents as a basic knowledge for the design and analysis in later chapters. Circuit design and detailed analysis for each building block of the multi-band multi-output PLL will be discussed in the following chapters.

#### CHAPTER III

## LOW POWER WIDE-LOCKING-RANGE DUAL-INJECTION LOCKED 1/2 DIVIDER

#### 1. Introduction

Frequency divider is one of the most crucial building blocks in frequency synthesizer. Frequency divider is used for the frequency division of LO signals. Once divided, the phase and frequency of the divided signal is then compared with a reference signal. The reference signal is generally supplied by a crystal oscillator, whose maximum frequency is typically limited to only a few hundreds of MHz due to increased error at higher frequencies and limitation on physical material. To compare the low-frequency reference signal and high-frequency LO signal for tracking the phase and frequency, the LO signal needs to be divided until it has the same frequency with the reference signal.

Frequency divider can be categorized into 3 types: current- mode logic (CML), true single-phase clock (TSPC) type, and injection-locked (IL) type. The CML frequency divider is widely used in the PLL, accredited to its good input sensitivity. However, it generally requires high power and even higher power as the operating frequency increased [25], [26]. The TSPC frequency divider is limited to relatively low frequencies while having low-power characteristics [27]. Among the different divider types, the injection-locked frequency divider (ILFD) is popular since it can be designed to operate at high frequencies with low power consumption.

The frequency divider is based on Injection-Locked Oscillator. Injection-Locked Oscillator can be categorized into first-harmonic injection locked oscillator (FHILO), sub-harmonic injection locked oscillator (SBILO) and super-harmonic injection locked oscillator (SPILO) according to the injection frequency in (3.1) to (3.3). Especially, SPILO can be used as part of super-harmonic injection locked frequency divider (SPILD).

$$f_i = f_o$$

, for FHILO, (3.1)

$$f_i = \frac{1}{N} f_o$$

, for SBILO, (3.2)

$$f_i = N \times f_o$$

, for SPILO, (3.3)

where  $f_i$  is the injection frequency,  $f_o$  is the output frequency of injection-locked oscillator and N is the integer value for divide ratio.

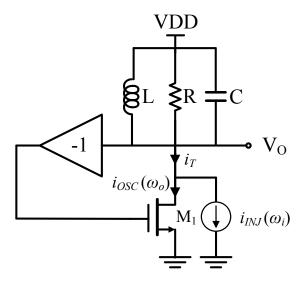

Fig. 3.1(a) shows a simple circuit schematic of a conventional direct injection-locked frequency divider (DILFD). The injection signal of frequency  $\omega_i$  is applied to the gate of the transistor M<sub>3</sub>. Due to the nonlinearities of an active device (M<sub>3</sub>), many intermodulation products are generated between the injection signal at  $(\omega_i)$  and output signal at  $(\omega_o)$ . For 1/2 frequency division, only the desired signal at  $(\omega_o) = \omega_i/2$  is extracted through the LC-resonator at the output.

Fig. 3.1 A conventional DILFD with single injection at NMOS: (a) schematic, (b) equivalent model using mixer, BPF, multiplier N, and (c) phasor diagram between  $i_{OSC}$  and  $i_{INJ}$ .

Fig. 3.1(b) shows an equivalent model of the DILFD shown in Fig. 3.1(a), which includes a band-pass filter (BPF) formed by the LC resonator, an  $N^{th}$  order multiplier (x N), and a mixer.

Fig. 3.1(c) shows a phasor diagram between the current of the cross-coupled pair  $i_{OSC}$  and injection current  $i_{INJ}$ , where  $\Phi_{\theta}$  is the relative phase between them. The locking range is enhanced as the angle  $\theta$  is increased, and the maximum locking range is achieved when  $\theta$  reaches  $\theta_{max}$  which happens when the angle between  $i_T$  and  $i_{INJ}$  is 90°.

Conventional DILFD generally has limited locking range. The locking range of DILFD can be increased to some extent by employing techniques such as shunt-peaking [28], [29], impedance matching at the injection device, frequency tuning using varactor and/or capacitor bank. etc. In super-harmonic dividers, the locking range is even narrower in case of higher-order division since the coefficients of the N<sup>th</sup> order harmonic of the injection signal ( $\omega_i$ ), which is contained in the series expansion of the injection signal, are smaller for higher order harmonics [30], [31].

In order to overcome the shortcomings of super-harmonic dividers, various works have been conducted to achieve a wider locking range while keeping the power consumption as low as possible [32]-[36]. Among them, dual-injection method was proposed to enhance the locking range using two injection signals having the same amplitude and phase [32]. The locking range is increased due to the increase of the amplitude of the injected signal resulting from the addition of the two injection signal amplitudes, as can be inferred from Fig. 3.1(c). In [33], the two injection signals are applied with 90° phase difference to obtain an increased locking range. However, the locking range cannot be maximized since the phase angle of the two injected signals is not optimal (i.e., not close to 90 degrees). The performance of the dual-ILFD's is fairly good in terms of locking range and power consumption. However, these papers do not

explain about the optimum phase angle between the injection signals, which maximizes the locking range. Also, the supply voltage (*VDD*) effect on the locking range is not presented.

A new dual-injection method is proposed to increase the locking range. The new dual-injection method can enhance the locking range by optimizing the quality factor (Q) of the combined transistors  $M_1$ ,  $M_2$  and  $M_3$ , the amplitude of the output cross-coupled current  $(i_{OSC})$ , and the phase angle between the injected signals. This chapter also analyzes the effects of the bias VDD on the Q and  $i_{OSC}$ , as well as the optimized phase angle between two injection signals, which ultimately affect the locking range. This chapter is organized as follows. Section 3.2 presents the operation of 1/2 DILFD using single-injection. Section 3.3 discusses the proposed dual-injection method for improving the locking range. Section 3.4 shows the simulation and measurement results, and Section 3.5 gives the conclusion.

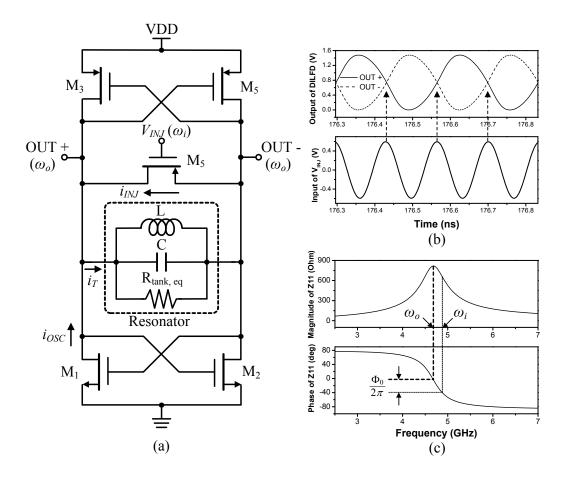

Fig. 3.2 Conventional 1/2 super-harmonic DILFD using single-injection: (a) circuit schematic, (b) output of divider (upper) with injection,  $V_{INJ}$  (lower), and (c) phasor interpretation between  $\omega_o$  and  $\omega_i$  Z11 is the input impedance of the resonator.

## 2. Divide-by-2 Divider using Single-Injection

DILFD is a frequency divider that can lock its frequency to the frequency of an externally applied signal or its harmonics. DILFD can be categorized into 3 different types by the division ratio: first- harmonic DILFD, sub-harmonic DILFD, and super-harmonic DILFD. Fig. 3.2(a) shows the schematic of a conventional super-harmonic

DILFD for divided-by 2. Since the injection signal is periodic, the output of the divider is periodically "short" and "open" as  $M_5$  turns ON and OFF by the injection signal ( $\omega_i$ ), respectively. Fig. 3.2(b) plots the transient results of the DILFD, which shows that the output frequency is divided by 2 ( $\omega_i$ /2) through the switching operation of  $M_5$ . The resultant total output current ( $i_T$  at  $\omega_o$ ) flows into the resonator.

In order to examine the locking range of the super-harmonic DILFD, we assume there exists the necessary for oscillation phase condition. For instance, the phase shift in the loop is zero in steady state. When an injection current  $(i_{INJ})$  is applied, a deviation from the free running frequency  $(\omega_o)$  by  $\omega_i$  -  $\omega_o$  results and, consequently, a phase shift of  $\Phi_0/2\pi$  occurs in the resonator as shown in Fig. 3.2(c) which results in frequency change, where  $\Phi_0$  is the relative phase between the voltage and current in the resonator. The resultant current  $(i_T)$  at the output varies according to  $i_{INJ}$  and the locking range  $\omega_i$  -  $\omega_o$  can be estimated as [37]

Fig. 3.3 Behavioral model of the proposed 1/2 dual-ILFD.

$$\omega_i - \omega_o = \frac{\omega_o}{2Q_L} \cdot \frac{i_{INJ}}{\sqrt{i_{OSC}^2 - i_{INJ}^2}}$$

(3.4)

where  $Q_L$  is the loaded quality factor of the LC tank with external elements such as transistors.

Fig. 3.4 Schematic of the proposed 1/2 dual-ILFD. A 1/2 CML frequency divider is integrated with the dual-ILFD and used to compensate for the output voltage variation. The injection signal is via either a balun or divider.

As can be seen in (3.4), the locking range can be increased by adjusting  $i_{INJ}$ , reducing Q, and/or decreasing  $i_{OSC}$ . Eq. (3.4) also indicates that  $i_{INJ}$  cannot be greater than  $i_{OSC}$ .  $i_{INJ}$  can be increased by using either the current reuse technique in [38] or dual-injection method in [32], [33] without consuming additional power. Reduced Q can be achieved by employing a resonator with lower Q. The relationship between reduced  $i_{OSC}$  and locking range is explained in section 3.

## 3. Proposed Divide-by-2 using Dual-Injection

## A. The Proposed Concept of Dual-Injection

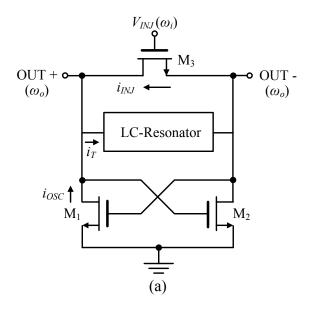

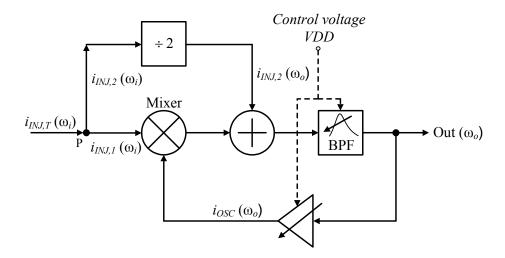

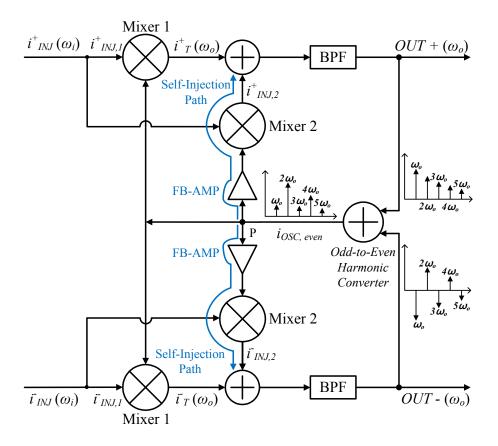

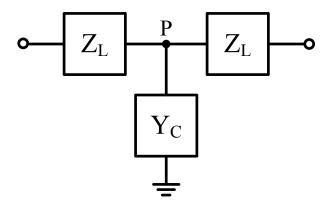

In the previous section, a 1/2 DILFD using single-injection method is discussed and its locking range is estimated as in (3.4). In order to increase the locking range, Dual-injection method is proposed. Fig. 3.3 shows an equivalent model for the proposed 1/2 dual-ILFD as shown in Fig. 3.4, which does not consume additional power as compared to a single-injection counterpart.

The new 1/2 dual-ILFD has two injection signals ( $i_{INJ,1}$ ,  $i_{INJ,2}$ ) and a control voltage (VDD) for optimizing  $Q_L$  and the amplitude of  $i_{OSC}$  needed for enhancing the locking range. The amplitude of  $i_{OSC}$  is controllable and it is modeled as a variable gain amplifier. The loaded  $Q_L$  is tunable and its resonant characteristic, and hence quality factor, can be modeled as a band-pass filter (BPF) response. An injection signal ( $i_{INJ}$ ) at  $\omega_i$  splits into  $i_{INJ,1}$  and  $i_{INJ,2}$  at node P through a balun or (equal-phase) divider depending on the device type used for injection in Fig. 3.3 and Fig. 3.4.  $i_{INJ,1}$  is injected into a mixer, which represents a MOSFET used for direct injection (such as  $M_5$  in Fig. 3.4), and it is

added to  $i_{OSC}$ .  $i_{INJ,2}$  is injected at the common-source node of a cross-coupled pair, and then added to the output current  $(i_{INJ,1} + i_{OSC})$ . At the output, only a desired output component  $(\omega_o)$  is obtained by filtering.

Fig. 3.5 Equivalent circuit of resonator with external load  $R_{\rm L}$ .

Similar to the single-injection case, the locking range under the dual-injection can be approximately estimated by

$$\omega_i - \omega_o = \frac{\omega_o}{2Q_L} \cdot \frac{i_{INJ}}{\sqrt{i_{OSC}^2 - i_{INJ}^2}}$$

(3.5)

where  $i_{INJ} = i_{INJ,1} + i_{INJ,2}$ . Note that summation between  $i_{INJ,1}$  and  $i_{INJ,2}$  is vector. From (3.5), the locking range can be enhanced by reducing  $Q_L$  and  $i_{OSC}$  as well as adjusting  $i_{INJ}$ . When the resonator is connected to an external load, the loaded quality factor  $(Q_L)$  can be expressed as

$$\frac{1}{Q_L} = \frac{1}{Q_E} + \frac{1}{Q} \tag{3.6}$$

where Q and  $Q_E$  represent the quality factor and external quality factor of the resonator, respectively.

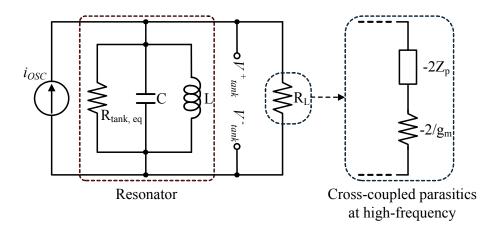

Fig. 3.5 shows an equivalent circuit of the resonator circuit with an external load  $R_L$ , where  $R_{tank,eq}$  is the effective resistance of the LC tank. The external load can be modeled as a series connection of the negative transconductance of the cross-coupled pair  $(-2/g_m)$ , where  $g_m$  is the transconducatnce for one pair, and the impedance due to parasitic capacitors at high frequency  $(-2Z_p)$ , where  $Z_p=1/(j2\omega_o C_p)$  with  $C_p$  being the parasitic capacitance at the common source node as seen in Fig. 3.4.

The external quality factor  $(Q_E)$  due to the cross-coupled pair can be expressed using its transconductance  $(g_m)$  and parasitic capacitance  $(C_p)$  as [39].

$$Q_{E} = \frac{g_{m}^{2}}{4 C_{p}^{2} \omega_{o}^{2}}$$

(3.7)

An optimization mechanism of  $Q_E$  can be deducted from (3.7). If the supply voltage (VDD) is decreased,  $I_{osc}$  (dc current) and  $i_{OSC}$  reduce accordingly. This will result in lower  $g_m$ , thus leading to reduced  $Q_E$ . Also, the voltage  $V_{tank}$ , across  $R_{tank,eq}$  decrease in a linear manner as  $i_{OSC}$  lowers according to:

$$i_{OSC} = \frac{V_{\tan k}}{R_{tank, eq}} \tag{3.8}$$

where the maximum amplitude of  $V_{tank}$  is VDD. Consequently, reducing VDD to an optimum point gives an optimum value for  $Q_E$  and thus  $Q_L$ .

To verify how and how much  $Q_E$  is changed by varying  $I_{osc}$ , we use the

fundamental current equations of MOSFET, neglecting the channel-length modulation effect, in the saturation region:

$$g_m = 2\sqrt{\beta \cdot I_{osc}} \tag{3.9}$$

$$I_{osc} \approx \beta \cdot [V_{GS} - V_T]^2$$

(3.10)

where  $V_T$  is the threshold voltage and  $\beta$  is  $0.5\mu_n C_{ox}(W/L)$ , with  $\mu_n$  being the mobility of the carriers in the channel,  $C_{ox}$  being the oxide capacitance, and W and L being the transistor width and length, respectively. The gate-source voltage  $(V_{GS})$  of the cross-coupled pair is equal to VDD/2, which is the output common mode level of the designed 1/2 dual-ILFD. Equating  $I_{osc}$  obtained from (3.9) and (3.10) with  $V_{GS} = VDD/2$  give

$$I_{osc} = \frac{g_m^2}{4\beta} \approx \beta \cdot \left[\frac{VDD}{2} - V_T\right]^2$$

(3.11)

The amplitude of  $I_{osc}$  in the designed 1/2 DILFD is minimum and maximum at the minimum ( $VDD_{min}$ ) and maximum ( $VDD_{max}$ ) value of VDD, respectively, according to (3.11). This leads to

$$\beta \cdot \left[ \frac{VDD_{\min}}{2} - V_T \right]^2 < I_{osc} \leq \beta \cdot \left[ \frac{VDD_{\max}}{2} - V_T \right]^2$$

(3.12)

Fig. 3.6 Phasor diagrams for (a) single-injection vs. single-injection with reduced  $i_{OSC}$  and hence reduced  $Q_L$ , (b) single-injection vs. dual-injection, (c) dual-injection with and without reducing  $i_{OSC}$  (equivalent to with and without optimized  $Q_L$ ), and (d) proposed dual injection vs. other dual injection.

In order to estimate the range of  $I_{osc}$ , we let  $V_T$  be 0.5 V and  $VDD_{max}$  be 1.8 V. We let  $VDD_{min}$  be 1.5 V, which is a reasonable value for guaranteeing oscillation. Substituting these values into (3.12) gives

$$0.0625 \cdot \beta \quad < \quad I_{osc} \quad \leq \quad 0.16 \cdot \beta \tag{3.13}$$

which shows a possible tuning range for  $I_{osc}$ .

We can see from (3.13) that  $I_{osc}$  can be reduced by about 60 % from the maximum. Correspondingly,  $g_m^2$  can be reduced by the same amount, leading to a reduction in  $Q_E$  as can be seen from (3.7). Therefore, according to (3.8) and (3.12), by reducing VDD to a certain minimum value,  $i_{OSC}$ , and hence  $Q_E$ , can be optimized to produce an enhanced locking range.

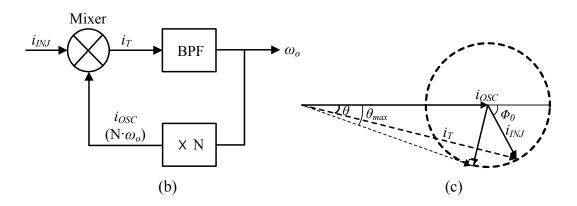

Fig. 3.6 shows the conceptual phase diagrams under different conditions. Fig. 3.6(a) illustrates the effect of increasing the deviation angle ( $\theta$ ) with respect to the locking range by decreasing  $i_{OSC}$ , which correspondingly results in reduced  $Q_L$  as we discussed earlier, for single injection. For reduced  $i_{OSC}$  (expressed as  $i'_{OSC}$ ) corresponding to reduced  $Q_L$ , the locking range can be increased by  $\theta'$ - $\theta$  while the total resultant current,  $i'_T$ , is lowered as compared to the original one,  $i_T$ . Fig. 3.6(b) compares the dualinjection with single-injection. The second injection signal ( $i_{INJ,2}$ ) is added to the resultant current ( $i_T$ ) after the first injection. When they bear a 90° phase difference, the effect of the second injection on the locking range is maximized. The effect of the dualinjection with the amplitude of  $i_{OSC}$  optimized, and hence  $Q_L$ , is shown in Fig. 3.6(c).

Fig. 3.6(d) shows that the locking range of the proposed 1/2 dual-ILFD can be extended further as compared to the other dual-injection methods [32], [33]. It is

manifested that a dual- injection with Q and  $i_{OSC}$  optimized will maximize the locking range of ILFD. This approach, however, has a disadvantage in that the output amplitude of the 1/2 dual-ILFD various as VDD and thus  $i_{OSC}$  is changed. In order to compensate for the output voltage variation, a CML divider is connected to the output of the 1/2 dual-ILFD to produce a constant output amplitude with respect to VDD adjustment. The detailed design of the dual-ILFD will be presented in the following section.

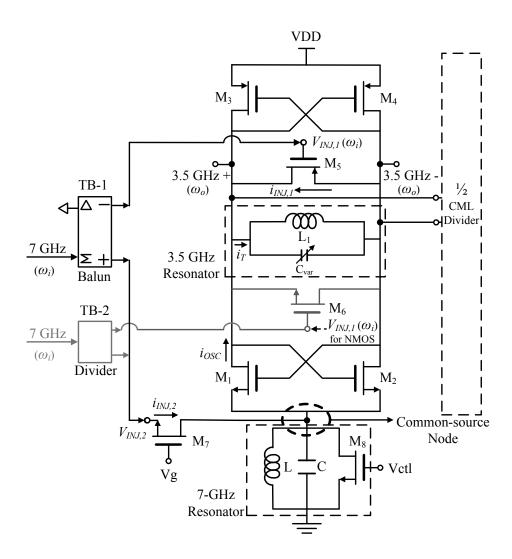

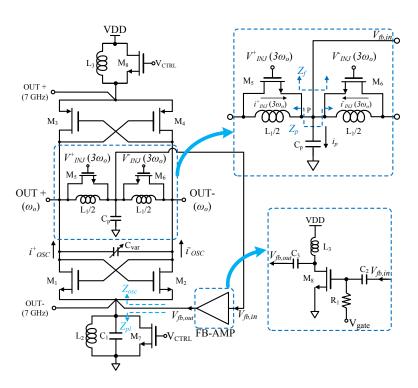

## B. Design of Proposed Divide-by-2 Dual- ILFD

Fig. 3.4 shows the schematic of the proposed 1/2 dual-ILFD. The VCO is operated at 3.5 GHz and consists of two complementary cross-coupled pairs and a 3.5-GHz LC resonator. The source and drain terminals of the N/PMOS are connected across the output terminals for direct injection. The 1/2 CML divider is connected at the output of the VCO. A 7-GHz signal is injected through the balun. The shunt-peaking resonator at 7 GHz is connected at the common source node of NMOS cross-coupled pair to create a high-impedance point at 7 GHz, forcing the 7-GHz injected signal to flow toward M<sub>1</sub> and M<sub>2</sub>. M<sub>8</sub> is connected in parallel with the resonator in order to control the impedance of the resonator by adjusting its gate bias voltage.

The operation of the proposed 1/2 dual-ILFD is as follows. Two injection signals  $(V_{INJ,1} \text{ and } V_{INJ,2})$  at 7 GHz  $(\omega_i)$  generated from a single external source through a balun are fed to  $M_5$  and  $M_7$ . Since these signals are 180° out of phase,  $M_5$  (PMOS) and  $M_7$  (NMOS) are turned on at the same time, thereby the resultant injection currents are constructively added at the output, effectively simulating the dual-injection. The injection current  $(i_{INJ,1})$  at  $M_5$  due to  $V_{INJ,1}$  flows between the output terminals of the

VCO.

The second injection  $V_{INJ,2}$  is applied to  $M_7$  according to common gate which is selected for broadband characteristics. When the 7 GHz signal is injected into the common source node through the common-gate device  $(M_7)$ , it mixes with one of the odd-harmonic products (10.5 GHz) generated by the switching differential pair  $M_1/M_2$  to produce a 3.5 GHz signal. This 3.5-GHz intermodulation product further increases the output signal at 3.5-GHz  $(\omega_o)$ . The corresponding drain current of  $M_7$  at 3.5 GHz splits into two branches at the common source node, which constitutes  $i_{INJ,2}$  at the output.

Fig. 3.7 plots  $g_m$  and the current of the cross-coupled pair  $(M_1)$  for different values of the control voltage VDD. As the control voltage is reduced,  $g_m$  and the current decrease which, as can be seen from (3.7), leads to reduced  $Q_E$ . This, in turn, results in reduced  $Q_L$  when VDD is decreased, and hence an increase in the locking range can be expected. The output amplitude, however, also decreases as VDD is lowered.

Fig. 3.7 Simulation results of 1/2 dual ILFD: current and  $g_m$  of  $M_1$ .

Fig. 3.8 Output amplitude of 1/2 dual-ILFD versus VDD.

This can be problematic if the 1/2 dual-ILFD is cascaded with other blocks such as prescaler or other divider, which is normal configuration in phase-locked loops. Suppose that a digital divider for obtaining a desired division ratio is connected in cascade with the proposed 1/2 dual-ILFD. In standard 0.18-m CMOS or BiCMOS process, the supply voltage is 1.8 V and the common mode DC voltage of the digital divider is normally set to be 0.9 V. It means that the (peak-to-peak) output voltage amplitude of the 1/2 dual-ILFD should be fixed at 1.8 V so that the output common level is 0.9 V. Since the output amplitude is different from 1.8V due to reduction as *VDD* is reduced, the common-mode output level of the 1/2 dual-ILFD becomes lower than 0.9 V, which affects the common-mode level of the next stage.

A 1/2 CML divider, instead of a simple DC level shifter, is then connected at the output of the dual-ILFD in order to provide constant output amplitude, regardless of the *VDD* variation. A 1/2 CML divider also provides an additional 1/2 division, hence relaxing additional division possibly needed in the next stage. Fig. 3.8 compares the output voltages of the proposed 1/2 dual-ILFD and without 1/2 CML divider versus *VDD*, which shows that a constant output for the proposed 1/2 dual-ILFD.

Fig. 3.9 plots the locking ranges versus injection voltage from a single external source at 7 GHz. Four cases are considered: single-ILFD and dual-ILFD without optimizing *VDD*, and optimized single-ILFD and dual-ILFD by changing *VDD*.

Fig. 3.9 Locking range characteristics of the proposed 1/2 dual-ILFD versus injection voltage for different settings.

The optimized locking range is obtained with lower VDD and, as we note earlier, this corresponds to lower  $Q_L$ . Therefore, we can see and verify the positive effects of optimizing e  $Q_L$  on the locking range of both dual-ILFD and single-ILFD. It can also be clearly seen that dual-injection method increases the locking range over the single-injection technique. The effect is more significant as the injection voltage level is increased. For example, the enhancement in the locking range is over 500-MHz at the injection voltage of 1 V while it is about 100 MHz at 0.2 V.

## 4. Measured Results

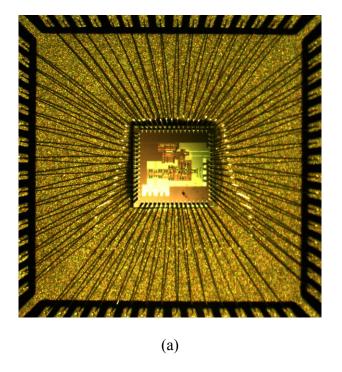

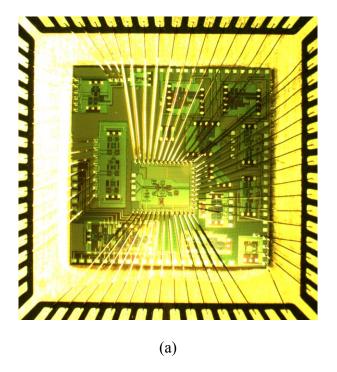

The designed 1/2 dual-ILFD was fabricated on a 0.18- $\mu m$  CMOS in BiCMOS process [40] and its die photograph is shown in Fig. 3.10.

Fig. 3.10 Die photograph of the 1/2 dual-ILFD. Size:  $0.8 \text{mm}^2$  (with pads),  $0.156 \text{mm}^2$  (without pads).  $V_{\text{INJ},1}$  is connected to either a balun or a divider.

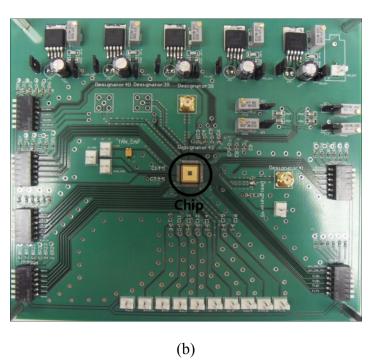

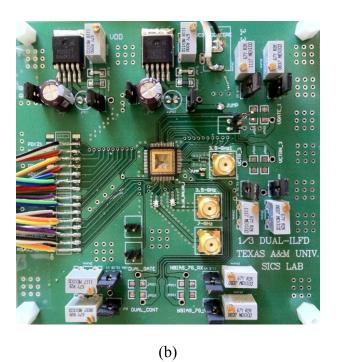

Fig. 3.11 Microphotograph of the designed 1/2 dual-ILFD (a) packaged chip mounted on FR-4 PCB (b).

The entire chip size is 0.8mm<sup>2</sup> while the core size of the 1/2 dual-ILFD (without the 1/2CML and pads) is 0.156mm<sup>2</sup>. The package of the design chip uses the 44-pin quad flat package (QFP) type and all bias are connected to the chip through wirebonding on the package mounted on FR-4 PCB as shown in Fig. 3.11.

To reduce the RF leakage through the bias line, the off-chip RF by-pass capacitor on the PCB is located as close as possible to the designed chip. The results of output spectrum are measured using HP 8692L Spectrum Analyzer. The result of phase noise is measured from Agilent E4446 Spectrum Analyzer. The current consumption of the designed 1/2 dual-ILFD with CML divider is 4.8 mA and that of the core 1/2 dual-ILFD is 2.93 mA with the supply voltage of 1.5 V.

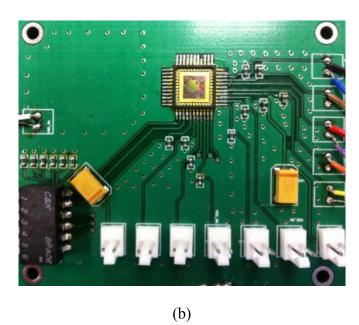

Fig. 3.12 Measured kVCO and output power without injection.

Fig. 3.12 shows the measured frequency range and output power without signal injection (free running) of the designed 1/2 dual-ILFD at the 1/2 CML output as a function of the control voltage of NMOS varactor. As can be seen, the output power varies little over the entire tuning range.

Fig. 3.13 Measured output spectrum of (a) the free-running 1/2 dual-ILFD and (b) the locked 1/2 dual-ILFD.

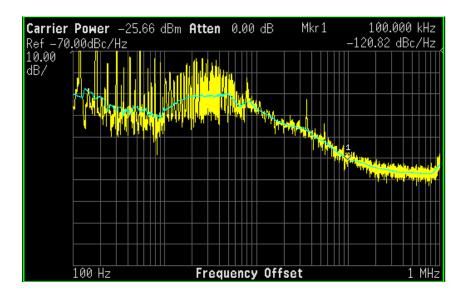

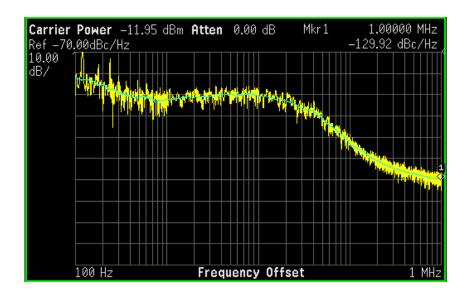

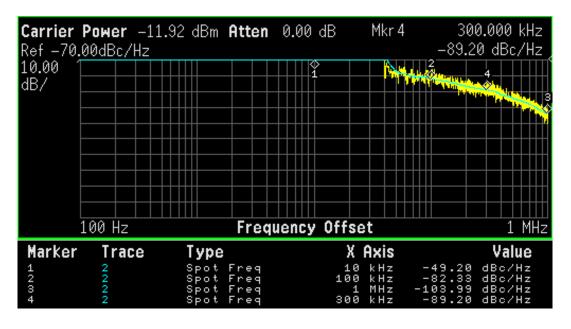

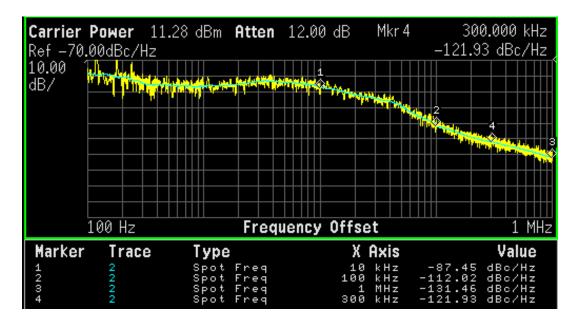

The free-running frequency without injection signal is 1.84 GHz at 0.9 V control voltage as shown in Fig. 3.12. The frequency changes from 1.78 to 1.9 GHz when the voltage of the NMOS varactor is tuned from 0 to 1.8. Fig. 3.13 shows the measured output spectrum of the free-running and locked 1/2 ILFD. As can be seen, the spurious signals are removed after the output signal is locked with the injected signal. Fig. 3.14 displays the measured phase noise of the designed 1/2 dual-ILFD, showing -122.19 dBc/Hz at 1MHz offset. As a comparison, the phase noise -115 dBc/Hz at 1 MHz offset without injection signal is shown in Fig. 3.15. The phase noise -96.36 dBc/Hz at 10 kHz offset with dual-injection is shown in Fig. 3.16 and -120.82 dBc/Hz at 100 kHz offset with dual-injection is shown in Fig. 3.17. The external injection source has -129.92 dBc/Hz at 1 MHz offset as shown in Fig. 3.18. All outputs are measured at output of 1/2

Fig. 3.14 Measured phase noise of the locked 1/2 dual-ILFD.

Fig. 3.15 Measured phase noise of the unlocked 1/2 dual-ILFD.

Fig. 3.16 Measured phase noise of the locked 1/2 dual-ILFD.

Fig. 3.17 Measured phase noise of the locked 1/2 dual-ILFD.

Fig. 3.18 Measured phase noise of 7 GHz external source.

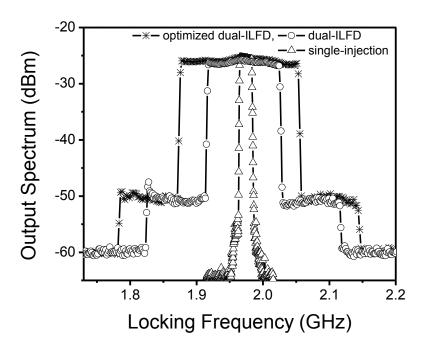

CML divider. In addition, the phase noise of ILFD may provide higher than 122.19 dBc/Hz if measured with a signal generator (injection signal) having better phase noise capability. The locking ranges with single-injection, and dual-injection without and with  $i_{OSC}$  and  $Q_L$  optimized are about 70 MHz, 502 MHz, and 692 MHz, respectively, and the flatness of the output spectrum is within 1 dB as shown in Fig. 3.19. The locking range of the proposed 1/2 dual-ILFD with optimized  $Q_L$  and  $i_{OSC}$  is extended almost 10 times better than that for the single-injection and about 27% more than the dual-injection without  $Q_L$  and  $i_{OSC}$  optimized.

Fig. 3.19 Measured locking range with single-injection and dual-injection for 1/2 function.

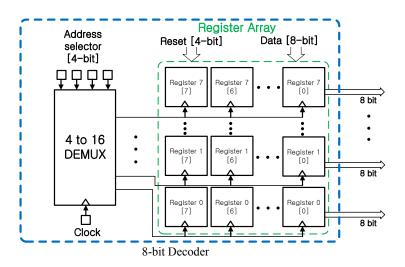

TABLE 3.1 Comparison of measurement results between proposed ILFD and others