# E-AMOM: AN ENERGY-AWARE MODELING AND OPTIMIZATION METHODOLOGY FOR SCIENTIFIC APPLICATIONS ON MULTICORE SYSTEMS

A Dissertation

by

CHARLES WESLEY LIVELY III

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2012

Major Subject: Computer Engineering

E-AMOM: An Energy-Aware Modeling and Optimization Methodology for Scientific Applications on Multicore Systems Copyright 2012 Charles Wesley Lively III

# E-AMOM: AN ENERGY-AWARE MODELING AND OPTIMIZATION METHODOLOGY FOR SCIENTIFIC APPLICATIONS ON MULTICORE SYSTEMS

#### A Dissertation

by

## CHARLES WESLEY LIVELY III

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Valerie Elaine Taylor Committee Members, Karen Butler-Purry

Eun Jung Kim

Tiffani Williams

Head of Department, Duncan Walker

May 2012

Major Subject: Computer Engineering

## **ABSTRACT**

E-AMOM: An Energy-Aware Modeling and Optimization Methodology for Scientific

Applications on Multicore Systems. (May 2012)

Charles Wesley Lively III,

B.S.E., Mercer University;

M.S., Texas A&M University

Chair of Advisory Committee: Dr. Valerie Elaine Taylor

Power consumption is an important constraint in achieving efficient execution on

High Performance Computing Multicore Systems. As the number of cores available on

a chip continues to increase, the importance of power consumption will continue to

grow. In order to achieve improved performance on multicore systems scientific

applications must make use of efficient methods for reducing power consumption and

must further be refined to achieve reduced execution time.

In this dissertation, we introduce a performance modeling framework, E-AMOM,

to enable improved execution of scientific applications on parallel multicore systems

with regards to a limited power budget. We develop models for each application based

upon performance hardware counters. Our models utilize different performance

counters for each application and for each performance component (runtime, system

power consumption, CPU power consumption, and memory power consumption) that

are selected via our performance-tuned principal component analysis method. Models

developed through E-AMOM provide insight into the performance characteristics of

each application that affect performance for each component on a parallel multicore system. Our models are more than 92% accurate across both Hybrid (MPI/OpenMP) and MPI implementations for six scientific applications.

E-AMOM includes an optimization component that utilizes our models to employ run-time Dynamic Voltage and Frequency Scaling (DVFS) and Dynamic Concurrency Throttling to reduce power consumption of the scientific applications. Further, we optimize our applications based upon insights provided by the performance models to reduce runtime of the applications. Our methods and techniques are able to save up to 18% in energy consumption for Hybrid (MPI/OpenMP) and MPI scientific applications and reduce the runtime of the applications up to 11% on parallel multicore systems.

# **DEDICATION**

This dissertation is dedicated to my loving and supportive parents, Charles W.

Lively Jr. and Irene S. Lively.

# **ACKNOWLEDGEMENTS**

Graduate school has been an enriching journey that has helped to shape my life and thought process. For this, I would first like to give thanks to my Lord and Savior Jesus Christ for guiding me through out this journey and in life. My mother, Irene, has been an endless source of encouragement and support since birth and I could never repay her for always encouraging my intellectual interests. My family and friends have been a great support system over the years and so I would like to thank them for always offering kind words of encouragement and support (Charles Lively Jr., Vidal Lively, Charles Beverley Jr., Courtney Carey, Jesse Dukes, Jacqueline Hodge, Carla Marsh, and Antoinette Davis)

I have to thank my academic family for support throughout this time. My advisor and mentor, Dr. Valerie Taylor, has taught me what it truly takes to be an excellent researcher through constant encouragement, hard work, and "refinement". I would also like to give thanks to my second advisor, Dr. Xingfu Wu, for always providing encouraging feedback and support. Special thanks are also in order for my past research group members Dr. Ayodeji Coker and Dr. Sameh Sharkawi.

# **NOMENCLATURE**

MPI Message Passing Interface

HPC High Performance Computing

DVFC Dynamic Voltage and Frequency Scaling

DCT Dynamic Concurrency Throttling

# **TABLE OF CONTENTS**

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| ABSTRAC    | CT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iii      |

| DEDICAT    | TION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | v        |

| ACKNOW     | /LEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vi       |

| NOMENC     | LATURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | vii      |

| TABLE O    | F CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | viii     |

| LIST OF I  | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X        |

| LIST OF T  | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XV       |

| 1. INTRO   | DDUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1        |

| 1.1        | Research Challenges on Multicore Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8        |

| 1.2<br>1.3 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11<br>16 |

| 2. PROP    | OSED PERFORMANCE MODELING SCHEME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27       |

| 2.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 2.2        | The state of the s | 30       |

| 2.3        | 11 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34       |

| 2.4        | Modeling Approaches Leveraged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37       |

| 3. PERFO   | ORMANCE-POWER TRADE-OFFS OF MPI AND HYBRID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| APPLI      | CATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50       |

| 3.1        | Parallel Multicore Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50       |

| 3.2        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52       |

| 3.3        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53       |

| 3.4        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68       |

|    |         |                                                            | Page |

|----|---------|------------------------------------------------------------|------|

| 4. |         | R-AWARE PERFORMANCE MODELS OF SCIENTIFIC CATIONS.          | 70   |

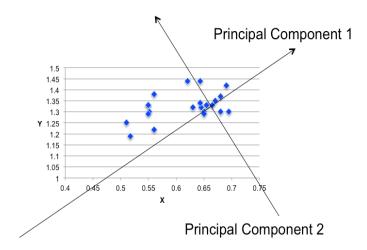

|    | 4.1     | Performance-Tuned Principal Component Analysis Methodology | 70   |

|    | 4.2     | HPC Applications                                           | 81   |

|    | 4.3     | Experimental Results                                       | 85   |

|    | 4.4     | Summary                                                    | 149  |

| 5. | OPTIM   | IZATION OF HYBRID AND MPI SCIENTIFIC APPLICATIONS          | 152  |

|    | 5.1     | Software-Based Power Reduction Methods                     | 152  |

|    | 5.2     | Optimization Methodology for Application Kernels           | 153  |

|    | 5.3     | Loop Optimizations                                         | 160  |

|    | 5.4     | Experimental Results                                       | 161  |

|    | 5.5     | Summary                                                    | 184  |

| 6. | SUMM    | ARY AND FUTURE WORK                                        | 185  |

|    | 6.1     | Summary                                                    | 185  |

|    | 6.2     | Future Work                                                | 186  |

| RE | EFEREN( | CES                                                        | 189  |

| VI | TA      |                                                            | 199  |

# LIST OF FIGURES

| FIGURI | Е                                                      | Page |

|--------|--------------------------------------------------------|------|

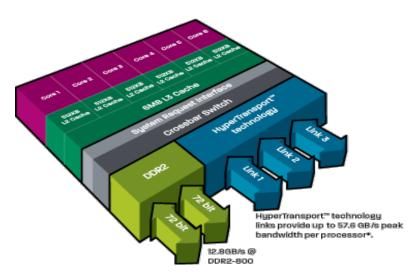

| 1      | Hex-Core AMD Opteron [60]                              | 2    |

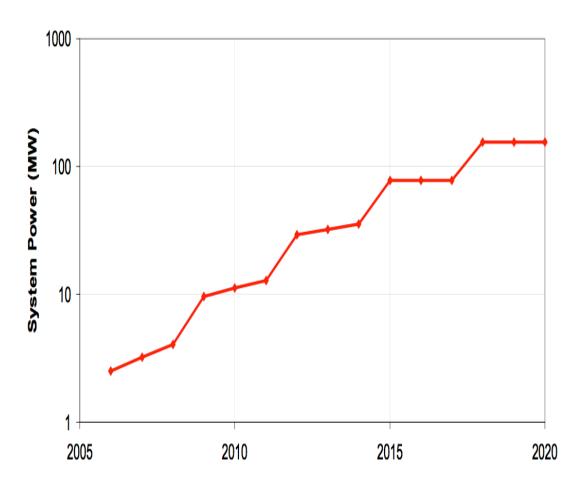

| 2      | Predicted Power Requirements for Exascale Systems [38] | 4    |

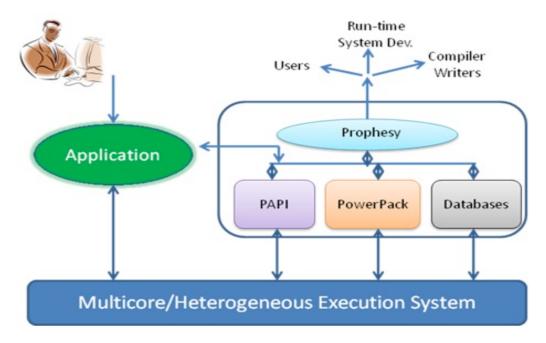

| 3      | Multiple Metrics Modeling Infrastructure [51]          | 12   |

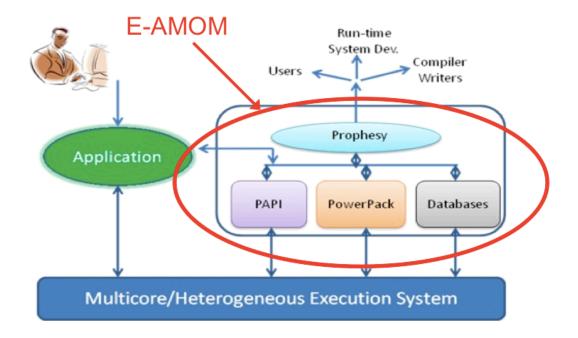

| 4      | Prophesy Framework [63]                                | 13   |

| 5      | PAPI Framework [56]                                    | 14   |

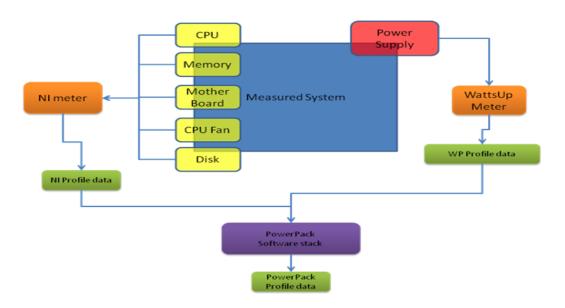

| 6      | PowerPack Framework                                    | 15   |

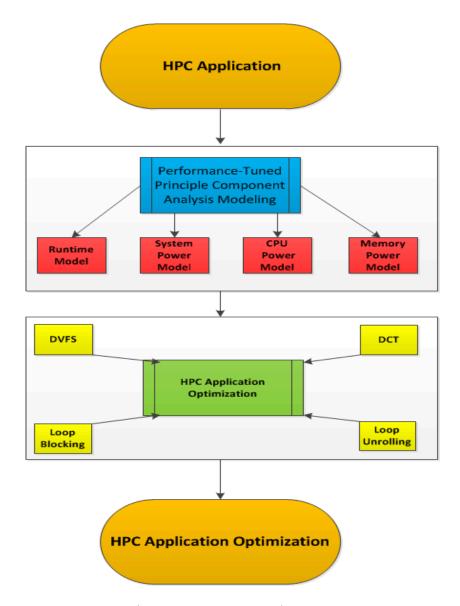

| 7      | E-AMOM Schema                                          | 29   |

| 8      | E-AMOM Integration into MuMMI                          | 30   |

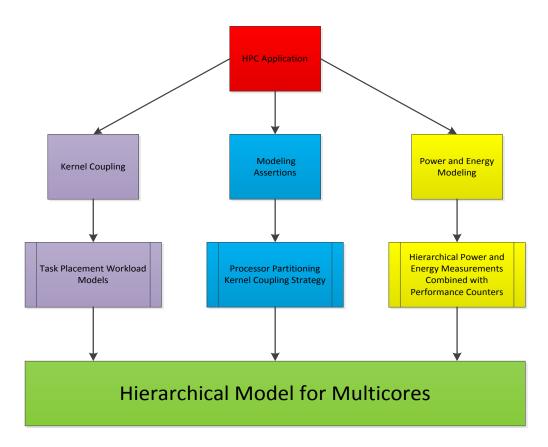

| 9      | Initial Hierarchical Multicore Modeling Framework      | 38   |

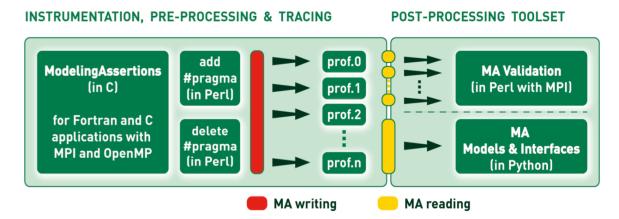

| 10     | Modeling Assertions Framework                          | 41   |

| 11     | Matrix-Matrix Multiply MA Profile                      | 42   |

| 12     | Matrix-Matrix Multiply Model                           | 43   |

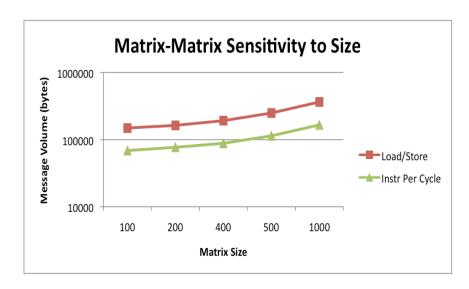

| 13     | Matrix-Matrix Sensitivity Analysis                     | 44   |

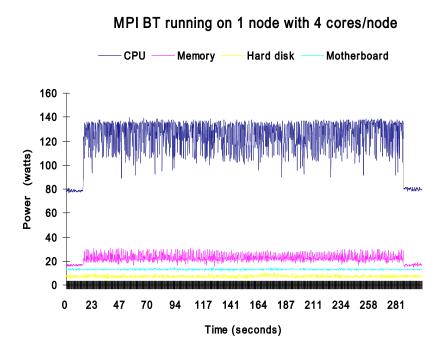

| 14     | Power for MPI BT Executed on 1 Node                    | 55   |

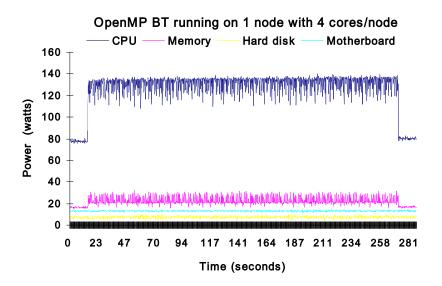

| 15     | Power for Hybrid BT on 1 Node                          | 56   |

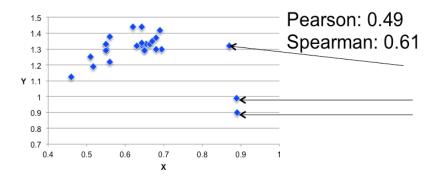

| 16     | Spearman and Pearson Correlation Comparison            | 72   |

| 17     | PCA Analysis Example                                   | 78   |

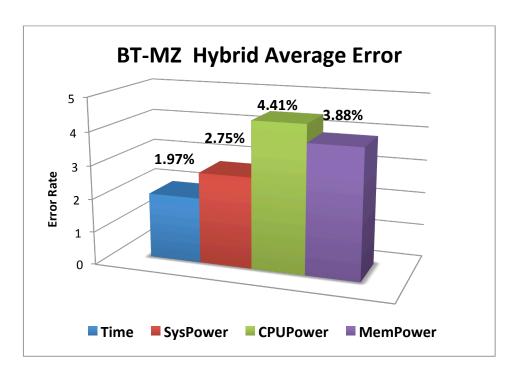

| 18     | Average Error of BT-MZ Hybrid                          | 87   |

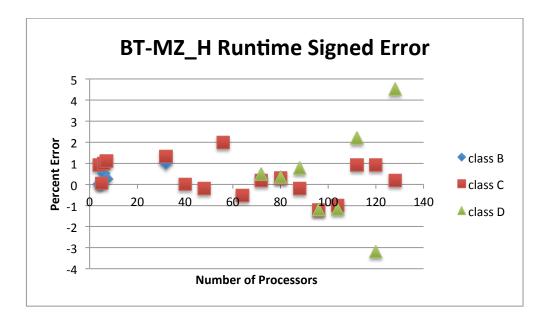

| 19     | Scatterplot of BT-MZ Hybrid for Runtime                | 88   |

|    |                                                          | Page |

|----|----------------------------------------------------------|------|

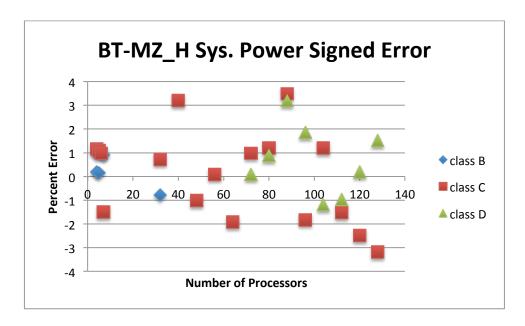

| 20 | Scatterplot of BT-MZ Hybrid for System Power Consumption | 89   |

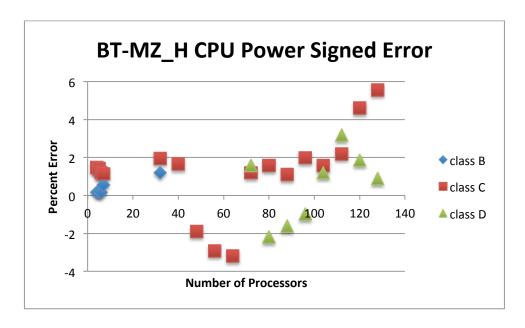

| 21 | Scatterplot of BT-MZ Hybrid for CPU Power Consumption    | 90   |

| 22 | Scatterplot of BT-MZ Hybrid for Memory Power Consumption | 91   |

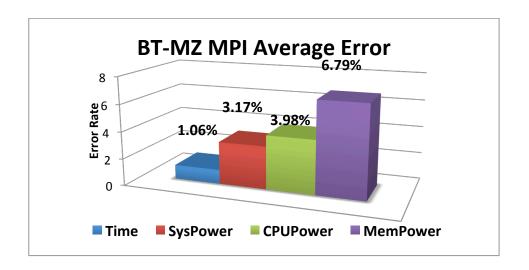

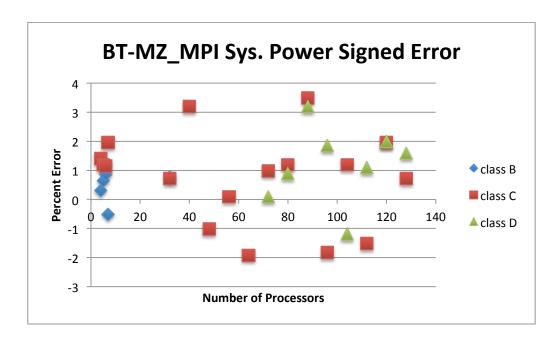

| 23 | Average Error of BT-MZ MPI                               | 92   |

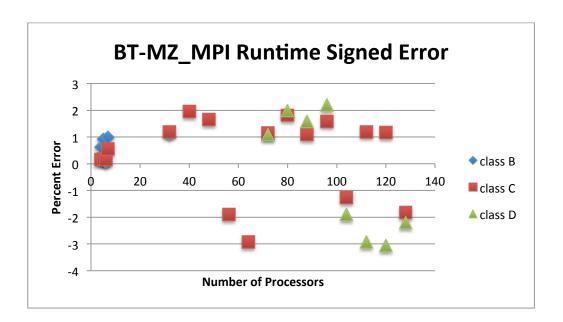

| 24 | Scatterplot of BT-MZ MPI for Runtime                     | 93   |

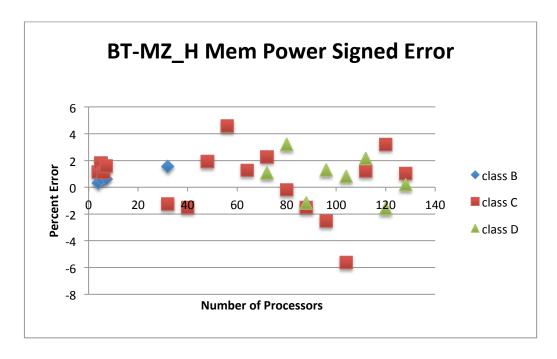

| 25 | Scatterplot of BT-MZ MPI for System Power Consumption    | 94   |

| 26 | Scatterplot of BT-MZ MPI for CPU Power Consumption       | 95   |

| 27 | Scatterplot of BT-MZ MPI for Memory Power Consumption    | 96   |

| 28 | Average Error of SP-MZ Hybrid                            | 97   |

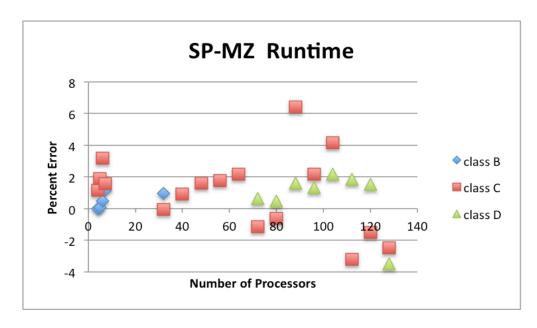

| 29 | Scatterplot of SP-MZ Hybrid for Runtime                  | 99   |

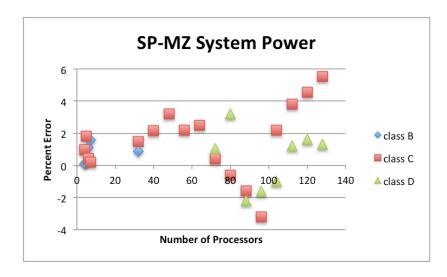

| 30 | Scatterplot of SP-MZ Hybrid for System Power Consumption | 100  |

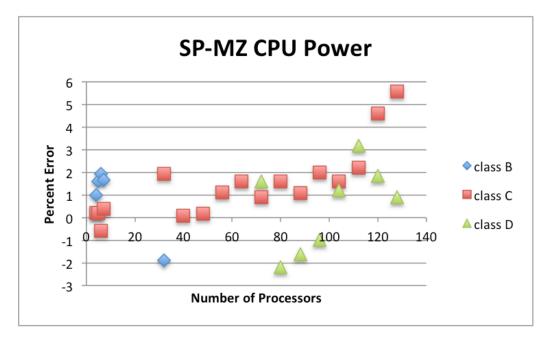

| 31 | Scatterplot of SP-MZ Hybrid for CPU Power Consumption    | 101  |

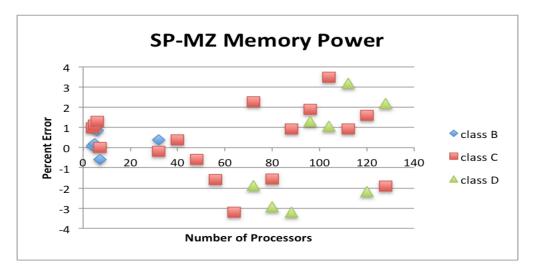

| 32 | Scatterplot of SP-MZ Hybrid for Memory Power Consumption | 102  |

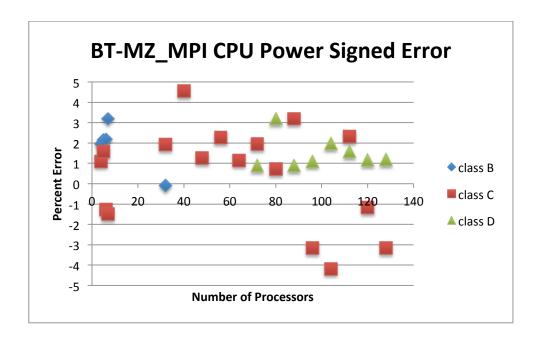

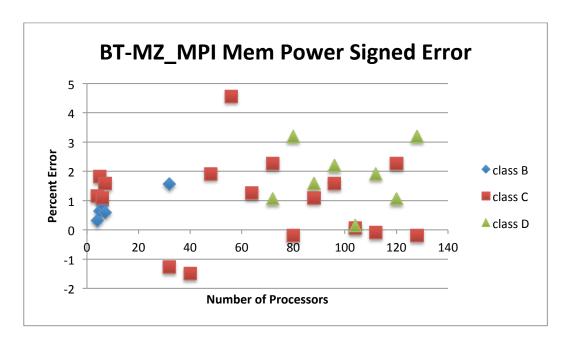

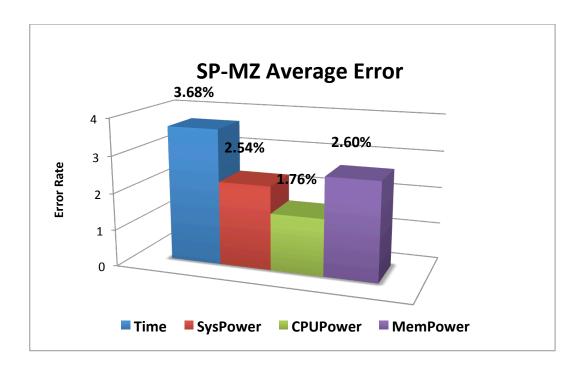

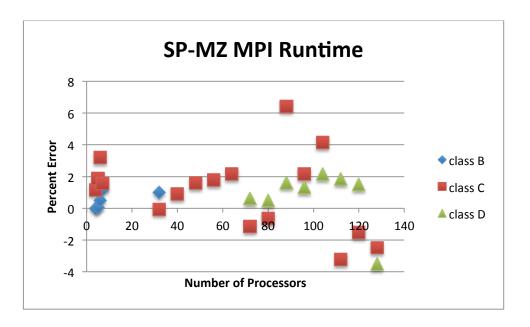

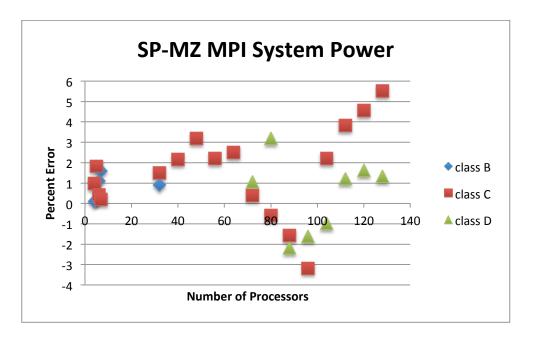

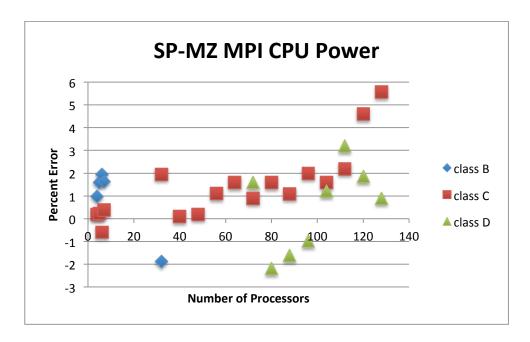

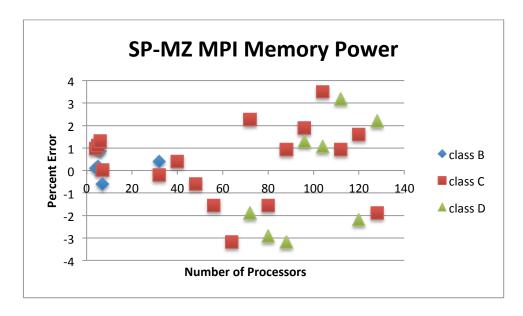

| 33 | Average Error of SP-MZ MPI                               | 103  |

| 34 | Scatterplot of SP-MZ MPI for Runtime                     | 104  |

| 35 | Scatterplot of SP-MZ MPI for System Power Consumption    | 105  |

| 36 | Scatterplot of SP-MZ MPI for CPU Power Consumption       | 106  |

| 37 | Scatterplot of SP-MZ MPI for Memory Power Consumption    | 107  |

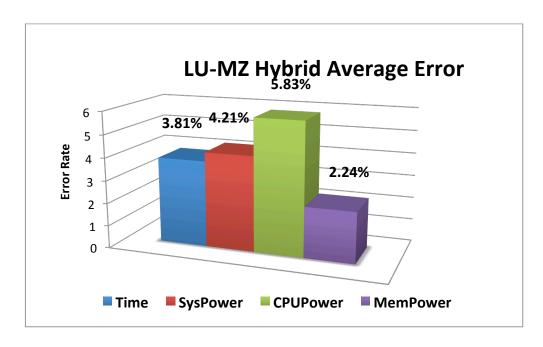

| 38 | Average Error of LU-MZ Hybrid                            | 109  |

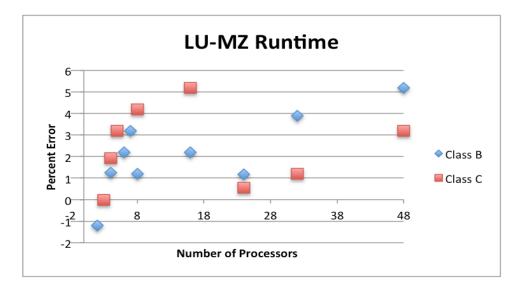

| 39 | Scatterplot of LU-MZ Hybrid for Runtime                  | 110  |

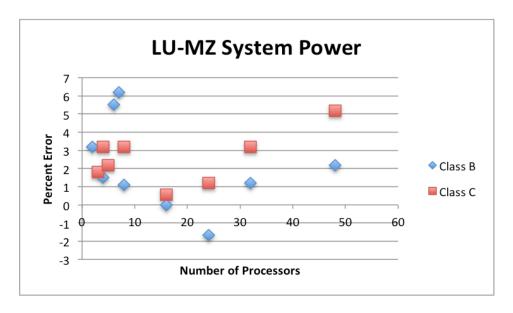

| 40 | Scatterplot of LU-MZ Hybrid for System Power Consumption | 111  |

|    |                                                          | Page |

|----|----------------------------------------------------------|------|

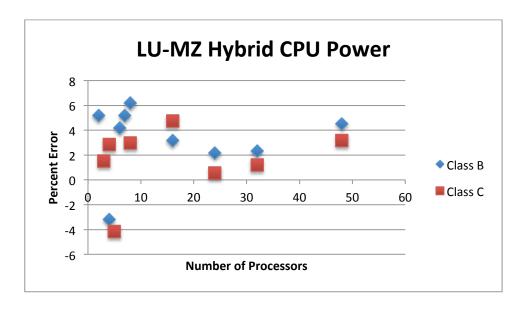

| 41 | Scatterplot of LU-MZ Hybrid for CPU Power Consumption    | 112  |

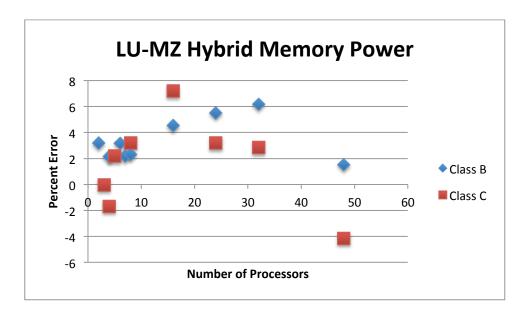

| 42 | Scatterplot of LU-MZ Hybrid for Memory Power Consumption | 113  |

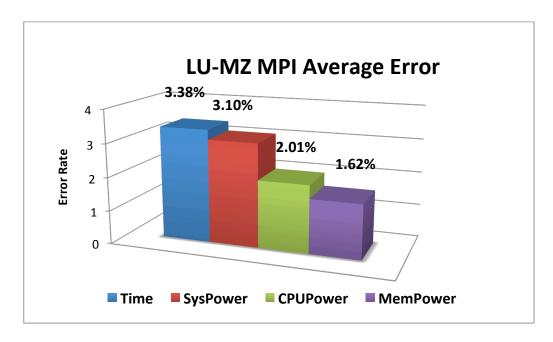

| 43 | Average Error of LU-MZ MPI                               | 115  |

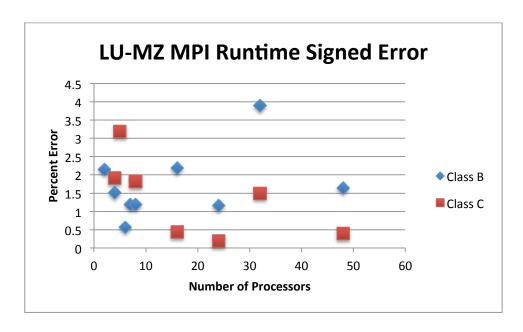

| 44 | Scatterplot of LU-MZ MPI for Runtime                     | 116  |

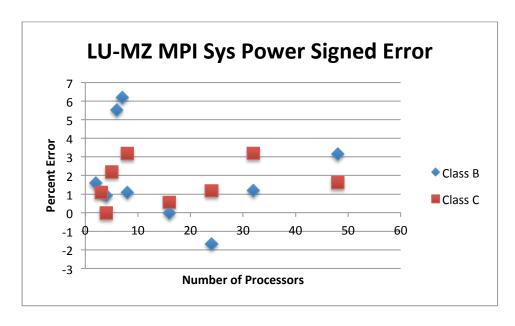

| 45 | Scatterplot of LU-MZ MPI for System Power Consumption    | 117  |

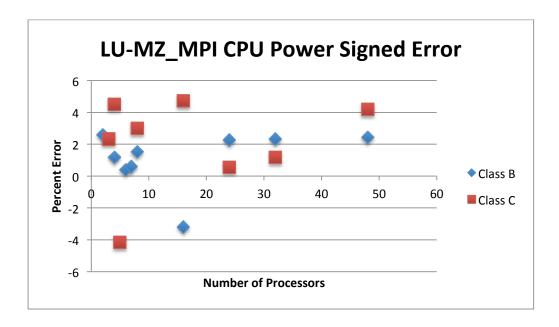

| 46 | Scatterplot of LU-MZ MPI for CPU Power Consumption       | 117  |

| 47 | Scatterplot of LU-MZ MPI for Memory Power Consumption    | 118  |

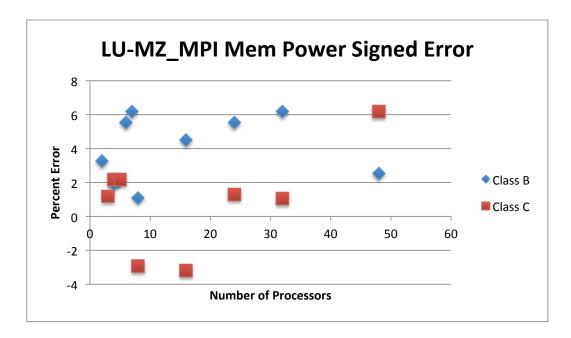

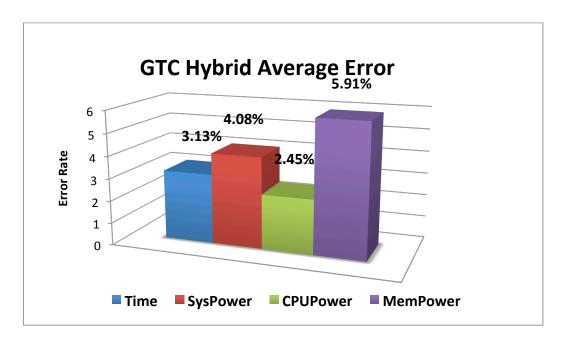

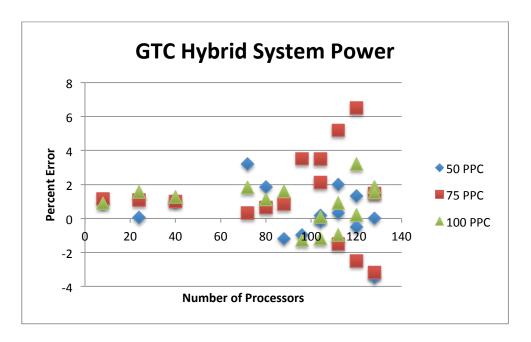

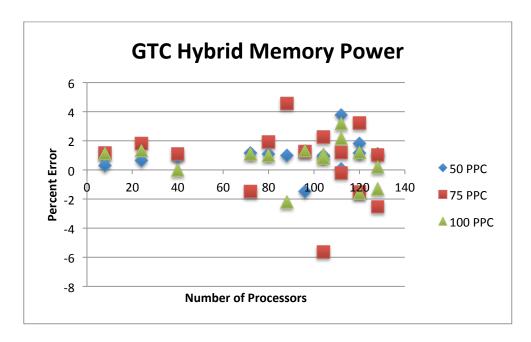

| 48 | Average Error of GTC Hybrid                              | 120  |

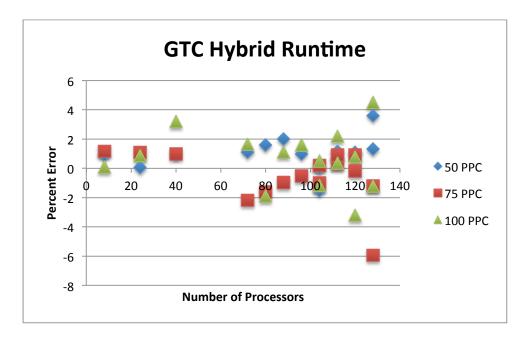

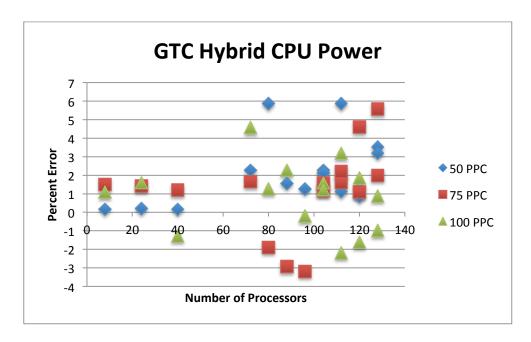

| 49 | Scatterplot of GTC Hybrid for Runtime                    | 121  |

| 50 | Scatterplot of GTC Hybrid for System Power Consumption   | 122  |

| 51 | Scatterplot of GTC Hybrid for CPU Power Consumption      | 123  |

| 52 | Scatterplot of GTC Hybrid for Memory Power Consumption   | 124  |

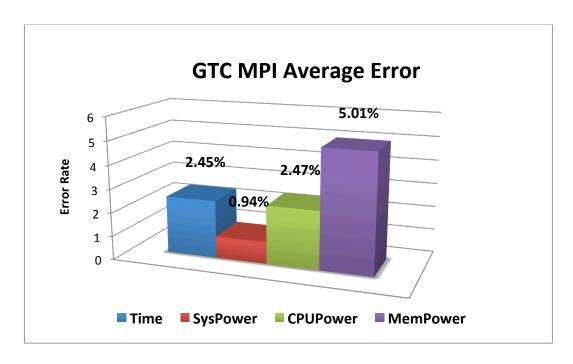

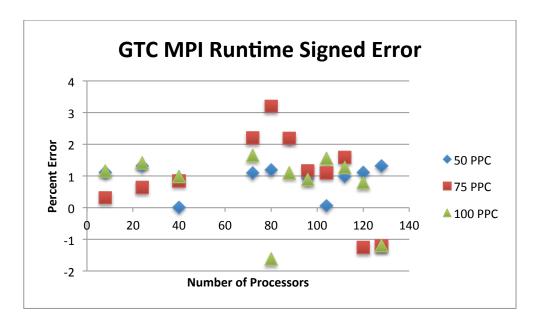

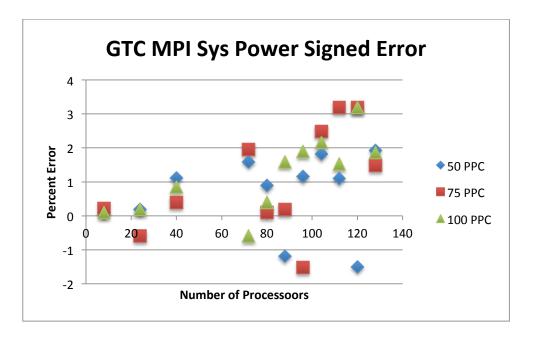

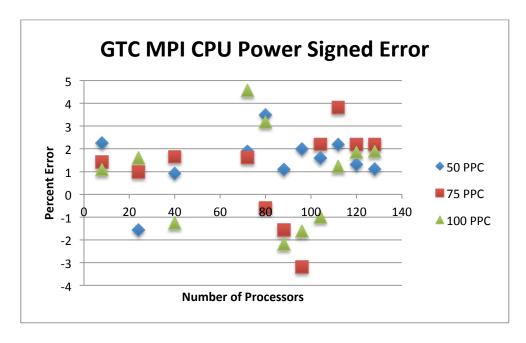

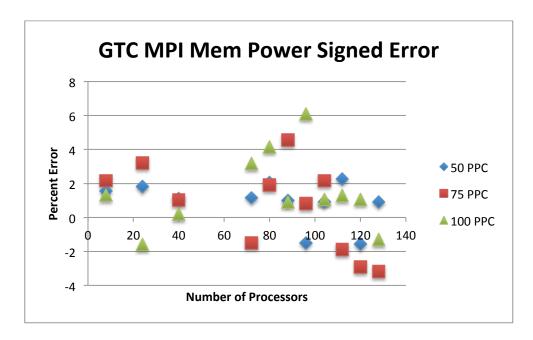

| 53 | Average Error of GTC MPI                                 | 125  |

| 54 | Scatterplot of GTC MPI for Runtime                       | 126  |

| 55 | Scatterplot of GTC MPI for System Power Consumption      | 127  |

| 56 | Scatterplot of GTC Hybrid for CPU Power Consumption      | 128  |

| 57 | Scatterplot of GTC Hybrid for Memory Power Consumption   | 129  |

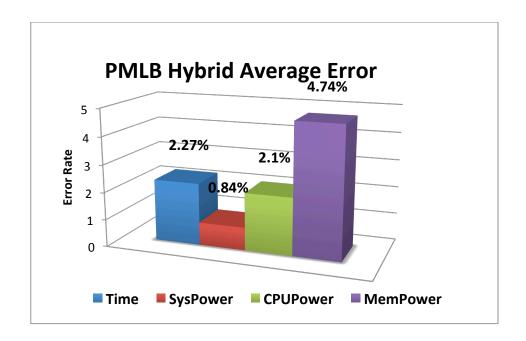

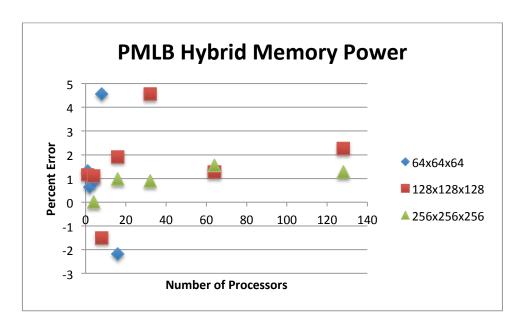

| 58 | Average Error of PMLB Hybrid                             | 130  |

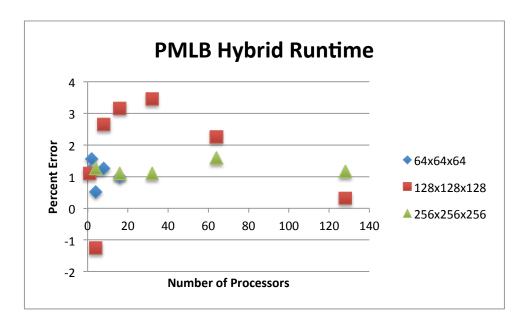

| 59 | Scatterplot of PMLB Hybrid for Runtime                   | 131  |

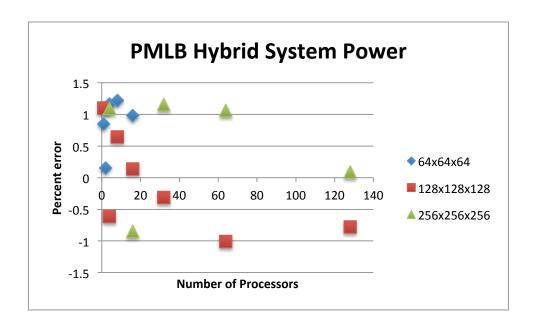

| 60 | Scatterplot of PMLB Hybrid for System Power Consumption  | 132  |

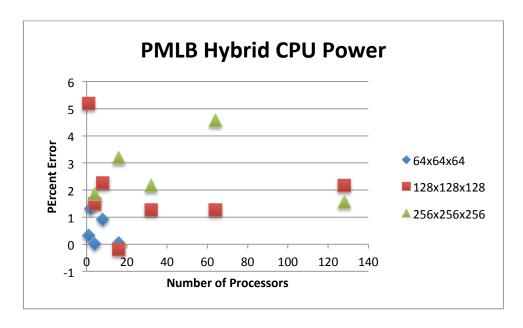

| 61 | Scatterplot of PMLB Hybrid for CPU Power Consumption     | 133  |

|    |                                                           | Page |

|----|-----------------------------------------------------------|------|

| 62 | Scatterplot of PMLB Hybrid for Memory Power Consumption   | 134  |

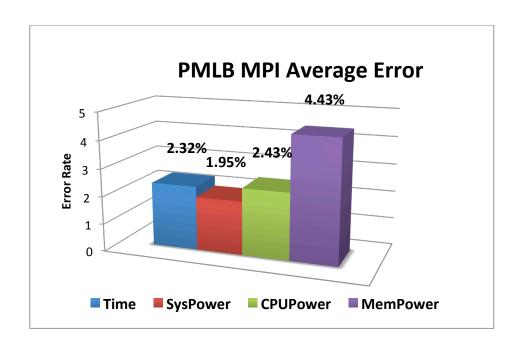

| 63 | Average Error of PMLB MPI                                 | 135  |

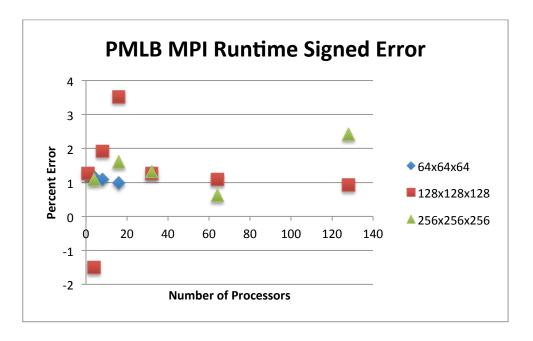

| 64 | Scatterplot of PMLB MPI for Runtime                       | 136  |

| 65 | Scatterplot of PMLB MPI for System Power Consumption      | 137  |

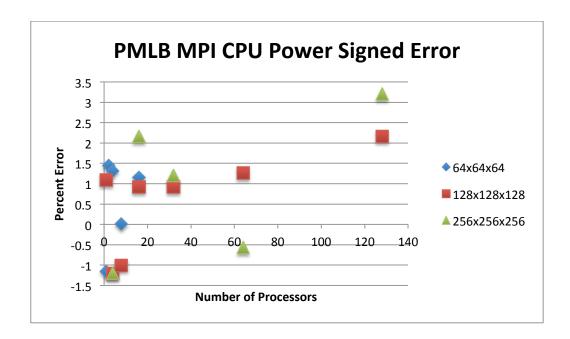

| 66 | Scatterplot of PMLB MPI for CPU Power Consumption         | 138  |

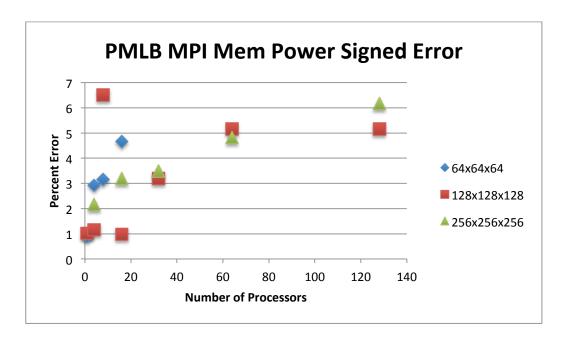

| 67 | Scatterplot of PMLB MPI for Memory Power Consumption      | 139  |

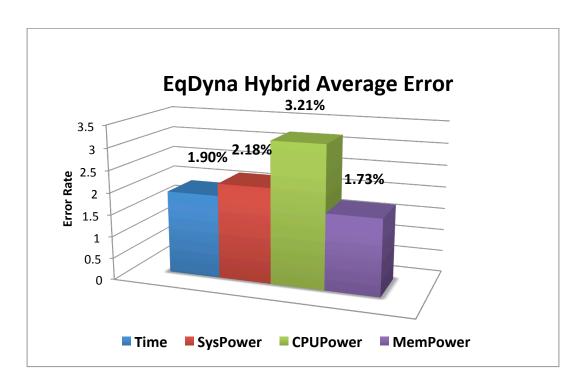

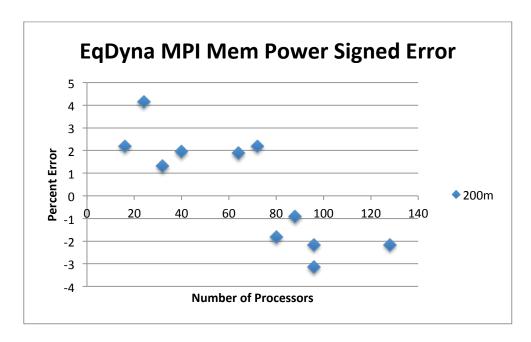

| 68 | Average Error of Parallel EqDyna Hybrid                   | 140  |

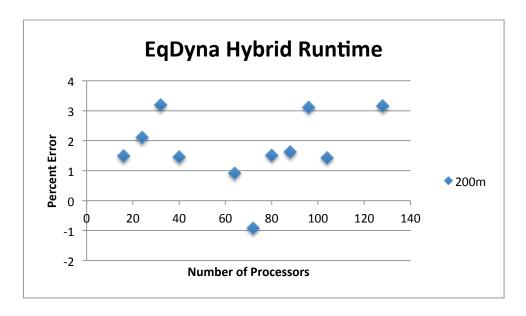

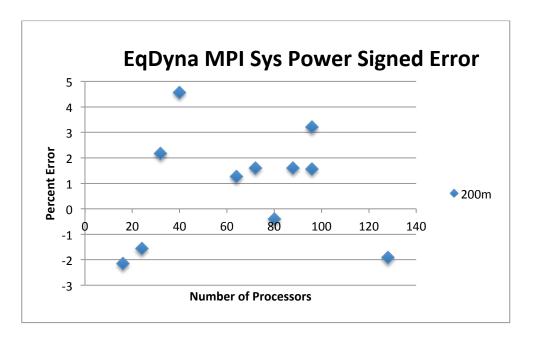

| 69 | Scatterplot of EqDyna Hybrid for Runtime                  | 141  |

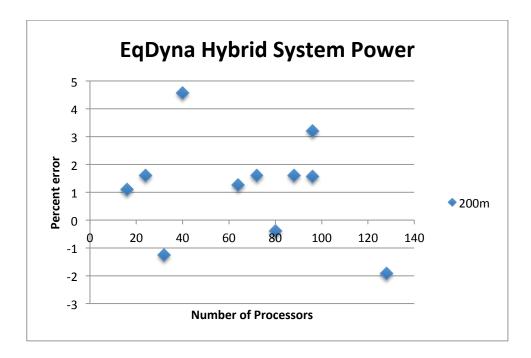

| 70 | Scatterplot of EqDyna Hybrid for System Power Consumption | 142  |

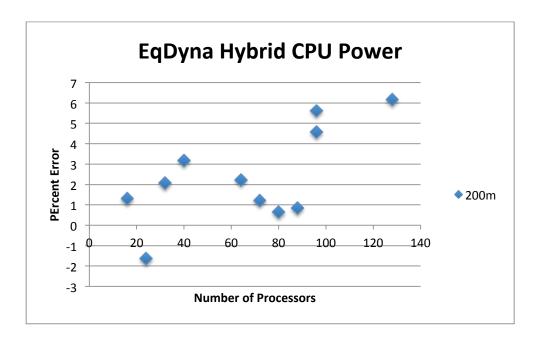

| 71 | Scatterplot of EqDyna Hybrid for CPU Power Consumption    | 143  |

| 72 | Scatterplot of EqDyna Hybrid for Memory Power Consumption | 144  |

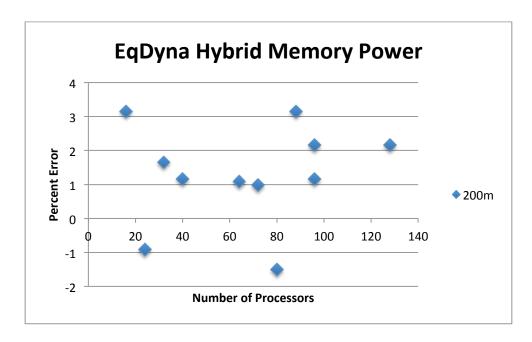

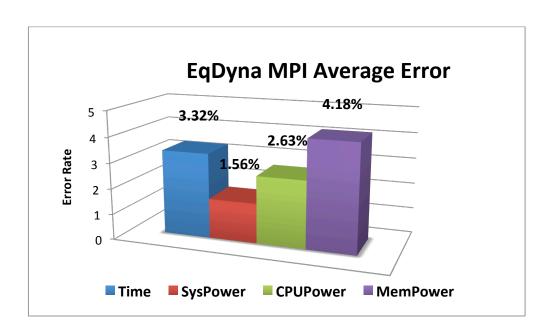

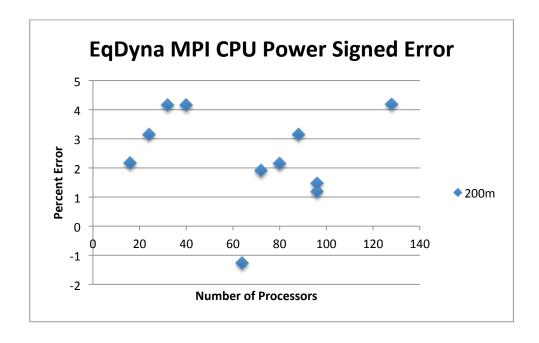

| 73 | Average Error of EqDyna MPI                               | 145  |

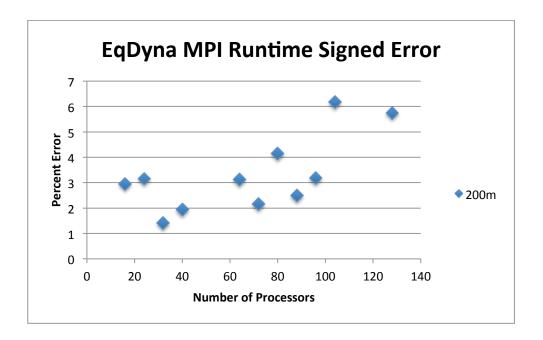

| 74 | Scatterplot of EqDyna MPI for Runtime                     | 146  |

| 75 | Scatterplot of EqDyna MPI for System Power Consumption    | 147  |

| 76 | Scatterplot of EqDyna MPI for CPU Power Consumption       | 148  |

| 77 | Scatterplot of EqDyna MPI for Memory Power Consumption    | 149  |

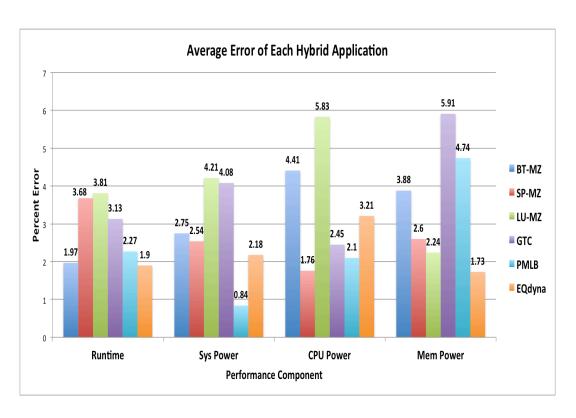

| 78 | Average Error of All Hybrid Applications                  | 150  |

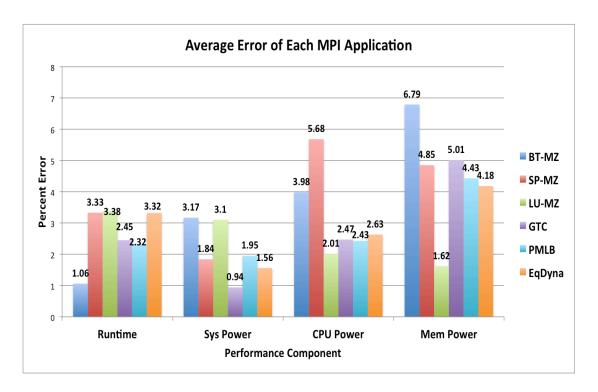

| 79 | Average Error of All MPI Applications                     | 151  |

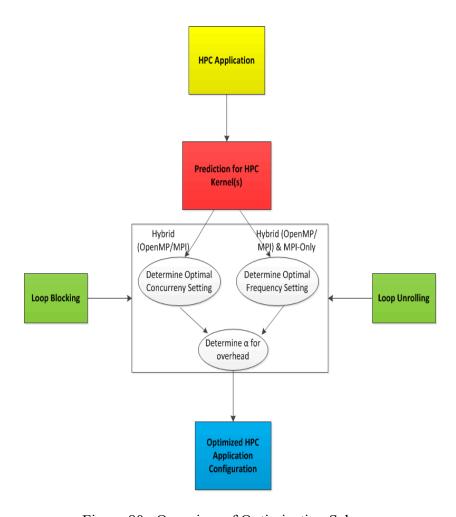

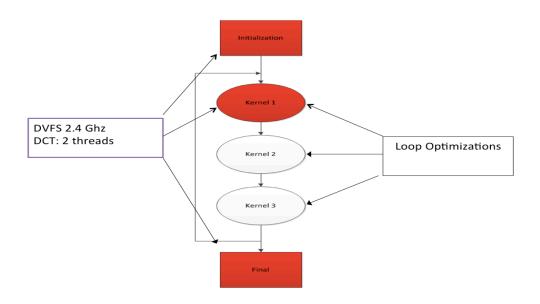

| 80 | Overview of Optimization Scheme                           | 156  |

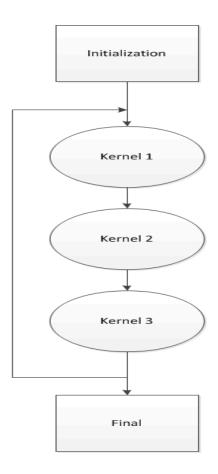

| 81 | Example Application Control Flow                          | 157  |

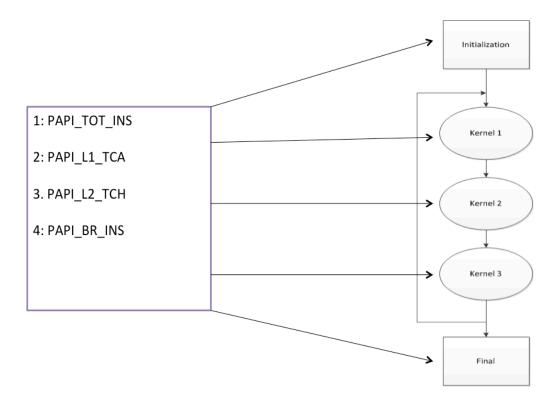

| 82 | Per Kernel Predictions for Applications                   | 159  |

|    |                                          | Page |

|----|------------------------------------------|------|

| 83 | Applying Optimizations to an Application | 162  |

# LIST OF TABLES

| TABLE |                                                                   | Page |

|-------|-------------------------------------------------------------------|------|

| 1     | Top 500 Supercomputers in the World (Top 500 List) [64]           | 3    |

| 2     | Hardware Performance Counters                                     | 32   |

| 3     | Kernel Coupling Values for M-M Kernel.                            | 47   |

| 4     | System Configuration of Dori                                      | 53   |

| 5     | Overview of HPC Applications                                      | 54   |

| 6     | Runtime and Energy Comparison for OpenMP and MPI BT on 1 Node     | 57   |

| 7     | Energy and Runtime Comparison of MPI and Hybrid BT                | 58   |

| 8     | Energy and Runtime Comparison of MPI and Hybrid PMLB Application  | 60   |

| 9     | Energy and Runtime Comparison of MPI and Hybrid GTC Application . | 62   |

| 10    | MPI and Hybrid BT on 4x4 (16 Cores) Using Frequency Scaling       | 64   |

| 11    | GTC Power Profiling on 4x4 (16 Cores) Using Frequency Scaling     | 66   |

| 12    | Function Comparison of GTC Using Frequency Scaling                | 67   |

| 13    | Reduced Performance Counters and Correlation Value                | 73   |

| 14    | Reduced Performance Counters and Regression Coefficients          | 75   |

| 15    | Reduced Performance Counters and Regression Coefficients-Step 5   | 76   |

| 16    | Final Multivariate Regression Model                               | 79   |

| 17    | Overview of HPC Applications                                      | 82   |

| 18    | Regression Coefficients for BT-MZ Hybrid                          | 86   |

| 19    | Regression Coefficients for BT-MZ MPI                             | 92   |

|    |                                                                     | Page |

|----|---------------------------------------------------------------------|------|

| 20 | Regression Coefficients for SP-MZ Hybrid                            | 97   |

| 21 | Regression Coefficients for SP-MZ MPI                               | 103  |

| 22 | Regression Coefficients for LU-MZ Hybrid                            | 108  |

| 23 | Regression Coefficients for LU-MZ MPI                               | 114  |

| 24 | Regression Coefficients for GTC Hybrid                              | 119  |

| 25 | Regression Coefficients for GTC MPI                                 | 125  |

| 26 | Regression Coefficients for PMLB Hybrid                             | 130  |

| 27 | Regression Coefficients for PMLB MPI                                | 135  |

| 28 | Regression Coefficients for Parallel EqDyna Hybrid                  | 140  |

| 29 | Regression Coefficients for Parallel EqDyna MPI                     | 145  |

| 30 | Performance of Hybrid BT-MZ Application and Optimization (Class C)  | 163  |

| 31 | Performance of Hybrid BT-MZ Application and Optimization (Class D)  | 164  |

| 32 | Performance of MPI BT-MZ Application and Optimization (Class C)     | 165  |

| 33 | Performance of MPI BT-MZ Application and Optimization (Class D)     | 166  |

| 34 | Performance of Hybrid SP-MZ Application and Optimization (Class C). | 167  |

| 35 | Performance of Hybrid SP-MZ Application and Optimization (Class D). | 168  |

| 36 | Performance of MPI SP-MZ Application and Optimization (Class C)     | 169  |

| 37 | Performance of MPI SP-MZ Application and Optimization (Class D)     | 170  |

| 38 | Performance of Hybrid LU-MZ Application and Optimization (Class C)  | 171  |

| 39 | Performance of Hybrid LU-MZ Application and Optimization (Class D)  | 172  |

| 40 | Performance of Hybrid GTC Application and Optimization (50ppc)      | 173  |

|    |                                                                   | Page |

|----|-------------------------------------------------------------------|------|

| 41 | Performance of Hybrid GTC Application and Optimization (100ppc)   | 174  |

| 42 | Performance of MPI GTC Application and Optimization (50ppc)       | 176  |

| 43 | Performance of MPI GTC Application and Optimization (100ppc)      | 177  |

| 44 | Performance of Hybrid PMLB Application and Optimization (128)     | 178  |

| 45 | Performance of Hybrid PMLB Application and Optimization (256)     | 179  |

| 46 | Performance of MPI PMLB Application and Optimization (128)        | 180  |

| 47 | Performance of MPI PMLB Application and Optimization (256)        | 180  |

| 48 | Performance of Hybrid EqDyna Application and Optimization (50ppc) | 182  |

| 49 | Performance of MPI EqDyna Application and Optimization (50ppc)    | 183  |

# 1. INTRODUCTION

In high performance computing, the current trend makes use of chip multiprocessors (multicore processors) for computing systems. The incorporation of uniprocessors in computing has reached both performance and physical limitations. For example, the processing speeds for uniprocessors are no longer able to scale with Moore's law [34]. Therefore, the use of multicore processors has been sought as an alternative avenue to maintain the gains in performance that have occurred previously in the computing field. Recently, interconnect technologies have posed limits on the capabilities of systems to continue the scaling of Moore's law.

It is expected that the number of cores available on a chip will continue to increase and the hierarchical nature of parallel systems will also continue to increase. As we move toward increased performance of high-performance parallel computing systems, it is expected that the complexity of the organization will increase as well as the power consumption [34][37]. In this work, we propose a methodology, called E-AMOM, to model and analyze the performance characteristics of scientific applications on high-end parallel systems with multicore processors.

Within the past decade, several chip manufacturers have introduced multicore processors. Since their introduction, multicore chips have been utilized in parallel computing environments by scientific laboratories, data centers, and academic chip, was introduced in 2001 with original clock speeds in the range of 1.1 Ghz to 1.3 Ghz. The

This dissertation follows the style of IEEE Trans. on Parallel and Distributed Systems.

first dual-core processor, the IBM POWER4 chip, was introduced in 2001 with original clock speeds in the range of 1.1 to 1.3 Ghz [33].

Later, Intel deployed its first dual-core chip, the Pentium D, in 2005 with clock speeds in the range of 3.0 – 3.2 Ghz [17]. In 2007 Intel introduced the world's first quad- core processor, Clovertown [18]. Currently, the use of multicores in computing has become the norm. Hence, there is a greater need to model how large-scale scientific applications perform and scale efficiently on these systems. Specifically, it remains to be understood what components of these emerging systems influence the achievable performance of large-scale scientific applications. Existing multicore compute systems can be configured hierarchically with multiple multicore chips within a node. These systems also utilize various levels of sharing for their memory subsystems.

Figure 1. Hex-Core AMD Opteron [60]

The configurations of current parallel compute systems provide an arrangement in hierarchical manner for accessing the memory subsystems. For example, the hex-core AMD Opteron processor, shown in Figure 1 [60], is used in the Jaguar Cray XT5 system, available at Oak Ridge National Laboratory. Each core on the processor has both a 128 KB L1 cache and 512KB L2 cache. A 2MB L3 cache is shared amongst all four cores on the quad-core Opteron. In addition, each node of the XT5 system contains two hex-core chips providing 12 processors per node.

Table 1. Top 500 Supercomputers in the World (Top 500 List) [64]

| Rank | Site                                                                   | Number<br>of Cores | Rmax<br>(Tflops) | Rpeak<br>(Tflops) | Power (KW) |

|------|------------------------------------------------------------------------|--------------------|------------------|-------------------|------------|

| 1    | RIKEN Advanced Institute<br>for Computational Science<br>(AICS), Japan | 705024             | 10510.00         | 11280.38          | 12659.9    |

| 2    | National Supercomputing  Center in Tianjin, China                      | 186,368            | 2566.00          | 4701.00           | 4040.00    |

| 3    | DOE/SC/Oak Ridge<br>National Laboratory, USA                           | 224,162            | 1759.00          | 2331.00           | 6950.60    |

| 4    | National Supercomputing  Centre in Shenzhen  (NSCS), China             | 120,640            | 1271.00          | 2984.30           | 2580.00    |

| 5    | GSIC Center, Tokyo Inst.<br>of Technology Japan                        | 73,278             | 1192.00          | 2287.63           | 1398.61    |

As parallel computing systems in HPC continue to incorporate more cores onto the system, the amount of power required to run these systems continues to be a major performance bottleneck [22]. Table 1 provides an overview of the power requirements of the top 5 supercomputing systems in the world based on rankings for the Top 500 list [64]. This table illustrates the power requirements that the top systems in the world currently required in order to run large-scale scientific applications.

Figure 2. Predicted Power Requirements for Exascale Systems [38]

Figure 2 outlines the predicted power requirements for future systems in high performance computing [38]. Power will be the leading contributor in energy costs as systems continue to grow at the exascale HPC level [34]. Costs are already a primary concern with existing supercomputing centers. For example, the expected upgrade to Oak Ridge National Laboratory's flagship machine will cost more than \$96 Million as a multiphase project. Projections indicate that for large-scale systems reducing the power consumption by 1 megawatt will result in \$1 million in savings per year [22].

As high performance computing systems become more complex and hierarchical in nature it is important that scientific applications are able to effectively make use of these systems. This dissertation provides a framework for achieving improved execution of an application on a high performance computing system given a limited power budget. Researchers and application developers need appropriate methods to understand how to improve the performance and power consumption of their application. Our modeling framework is useful to HPC users in the following ways:

- E-AMOM can be used to obtain the necessary application performance characteristics to determine application bottlenecks on a given system with regards to execution time and power consumption for the system, CPU, and memory components.

- E-AMOM can be used to improve the performance of the application with regards to applying DVFS and DCT to reduce power consumption and making algorithmic changes to improve power consumption.

- E-AMOM can be used by supercomputer schedulers to provide performance

predictions (about execution time and power requirements) for scheduling methods used with systems with a fixed power budget.

The contributions of this dissertation to the current literature of evaluating performancepower tradeoffs can be summarized in the following points:

- 1. We present a performance-tuned principal component analysis method for identifying application characteristics that affect performance of the application.

- 2. We present accurate performance models of Hybrid (MPI/OpenMP) and MPI implementations of scientific applications. Our models are able to accurately predict runtime and power consumption of the system, CPU, and memory components across different number of processors, frequency settings, concurrency settings, and application inputs.

- 3. Our models are used to determine appropriate frequency and concurrency settings for application kernels to reduce power consumption.

- 4. E-AMOM is used to optimize Hybrid and MPI scientific applications to improve cache utilization through loop blocking and loop unrolling techniques.

- 5. Our combined optimization strategy, developed in E-AMOM, is able to reduce energy consumption of Hybrid and MPI scientific applications by as much as 18% on multicore systems for six applications.

The publications resulting from this work are the following:

• Charles Lively, Xingfu Wu, Valerie Taylor, Shirley Moore, Hung-Ching

Chang, Chun-Yi Su and Kirk Cameron, *Power-Aware Predictive Models of Hybrid (MPI/OpenMP) Scientific Applications on Multicore Systems*, International Conference on Energy-Aware High Performance Computing(EnA-HPC2011), September 2011.

- Charles Lively, Xingfu Wu, Valerie Taylor, Shirley Moore, Hung-Ching Chang, and Kirk Cameron, Energy and Performance Characteristics of Different Parallel Implementations of Scientific Applications on Multicore Systems, International Journal of High Performance Computing Applications (IJHPCA), Volume 25 Issue 3, August 2011, pp. 342 350.

- Charles Lively, Sadaf Alam, Jeffrey Vetter, and Valerie Taylor, A Methodology for Developing High Fidelity Communications Models for Large-scale Applications on Multicore Systems, the 20th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD 2008), IEEE Computer Society Press, Oct. 29-Nov. 1, 2008, Campo Grande, Mato Grosso do Sol, Brazil.

The remainder of this section identifies the different requirements and challenges with respect to modeling and improving performance of scientific applications for reducing power consumption and provides a discussion about related work. The remainder of this dissertation is organized as follows: Section two provides an overview of E-AMOM and presents some background on the problem. Section three presents preliminary experimental results, which provide the motivation for our modeling and optimization framework. Section four presents the performance models of the Hybrid

and MPI applications and analysis. Section five discusses optimization techniques and presents optimization results of Hybrid and MPI scientific applications. The final section presents the summary and future work that will expand upon this dissertation.

# 1.1 Research Challenges on Multicore Systems

The importance of the detailed analysis of multicore systems and the applications that run on them is directly related to the continuous sustainability of improved performance as dictated by Moore's law [38]. If computing is to continue making the performance gains experienced during the 1990s, an explicit parallelism is needed in applications and architectures. Therefore, as the number of cores on multicore processors continue to grow there are a number of challenges that affect the performance of large-scale scientific applications are executed on multicore compute systems. These challenges include memory utilization, concurrency and locality, and power and energy utilization.

The issue of performance in scientific computing can be seen as the ability of an application to efficiently utilize a multicore compute system with respect to execution time, power and energy, and utilization of the memory subsystem. These challenges are the driving forces behind discovering new and better technologies [4]. These challenges present obstacles that must be addressed if multicore systems are able to reach their full potential for performance. The obstacles that these challenges present are explained in the following subsections.

#### 1.1.1 Energy and Power Challenge

As the utilization of multicore processors continues to increase the power consumption of these systems becomes a problem in maintaining stability of the system. Power in a multicore compute system consists of the power utilized by the CPUs, main memory, interconnects, and storage. Power utilized by main memory includes the total energy needed to refresh main memory, the number of independent accesses per second, and the data bandwidth needed to move accessed data. Additionally, the power required to move computational data through various interconnect levels, such as on-chip, between chips, within a node, and between nodes, can be in the order of 1-3 pJ [38].

Existing compute systems utilize ten's of thousands of processing cores that requires massive amounts of power [27]. Currently, the fastest supercomputing system in the world requires more than 12MWatts of power in order to achieve 10,510 Tflops, when such systems utilize such massive amounts of power this increases operating costs, and decreases the long-term lifecycle of the compute systems. Improving the power utilization of parallel systems that utilize multicore platforms will reduce overall maintenance costs, system failures, and increase the active time that the system can be used by researchers.

In this section, we discuss two topics that are of high importance for meeting the performance expectations of scientific applications with regards to energy and power consumption: power prediction and performance-power optimization.

#### 1.1.1.1 Power Prediction

Within the field, the ability to predict or accurately estimate the power consumption of scientific applications has posed a great challenge in multicore systems and emerging architectures. Determining the most efficient implementation to use for executing an application can be a cumbersome task that requires comparative analysis of the application's implementation for different datasets. In order, to predict and model the application one needs to understand the application characteristics that will affect performance of the application on the system.

In this dissertation, we address the power prediction challenge in parallel multicore systems modeling scientific applications using E-AMOM. We identify the application characteristics, through performance hardware counters, that affect power consumption of the application. In addition, we determine the similar and different characteristics between MPI and Hybrid implementations of an application that affect performance.

## 1.1.1.2 Power-Aware Optimization

Within the field, reducing the amount of power and energy consumed by a scientific application on multicore parallel systems poses a tremendous challenge. The amount of power required to run each of the fastest supercomputer systems for one year can exceed the power requirements of a city of 40,000 people [27]. In addition, it is expected that future exascale systems will be required at least 40 Gigaflops/Watt in order to maintain expected performance improvements for these systems [38].

In order to reduce power consumption novel methods must be utilized by both hardware vendors and application developers to reduce the power and energy requirements of scientific applications. Methods to reduce power consumption often employ using dynamic frequency and voltage scaling (DVFS) to reduce power and energy consumption [15][19][20][34][40][58]. However, additional methods must also be incorporated to further reduce the power consumption of an application, such as optimizing the application to better make use of the memory sub-system to reduce runtime and power consumption per workload. In this dissertation, will utilize DVFS and DCT to reduce power consumption on multicore systems and optimize the application using loop blocking and loop unrolling for further reduction in runtime and power consumption.

## 1.2 Modeling Infrastructure