# TIME-MODE ANALOG CIRCUIT DESIGN FOR NANOMETRIC TECHNOLOGIES

A Dissertation

by

# MOHAMED MOSTAFA ELSAYED

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

December 2011

Major Subject: Electrical Engineering

Time-Mode Analog Circuit Design for Nanometric Technologies

Copyright 2011 Mohamed Mostafa Elsayed

# TIME-MODE ANALOG CIRCUIT DESIGN FOR NANOMETRIC TECHNOLOGIES

A Dissertation

by

## MOHAMED MOSTAFA ELSAYED

# Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Committee Members, Edgar Sánchez-Sinencio Aydin Karsilayan Alexander Parlos Jun Zou Costas N. Georghiades

Head of Department,

December 2011

Major Subject: Electrical Engineering

#### ABSTRACT

Time-Mode Analog Circuit Design for Nanometric Technologies.

(December 2011)

Mohamed Mostafa Elsayed, B.Sc., Cairo University, Egypt;

M.Sc., Cairo University, Egypt

Chair of Advisory Committee: Dr. Edgar Sánchez-Sinencio

Rapid scaling in technology has introduced new challenges in the realm of traditional analog design. Scaling of supply voltage directly impacts the available voltage-dynamic-range. On the other hand, nanometric technologies with  $f_T$  in the hundreds of GHz range open opportunities for time-resolution-based signal processing. With reduced available voltage-dynamic-range and improved timing resolution, it is more convenient to devise analog circuits whose performance depends on edge-timing precision rather than voltage levels. Thus, instead of representing the data/information in the voltage-mode, as a difference between two node voltages, it should be represented in time-mode as a time-difference between two rising and/or falling edges. This dissertation addresses the feasibility of employing time-mode analog circuit design in different applications. Specifically:

1) Time-mode-based quantizer and feedback DAC of  $\Sigma\Delta$  ADC.

2) Time-mode-based low-THD 10MHz oscillator,

A Spur-Frequency Boosting PLL with -74dBc Reference-Spur Rejection in 90nm Digital CMOS.

In the first project, a new architectural solution is proposed to replace the DAC and the quantizer by a Time-to-Digital converter. The architecture has been fabricated in 65nm and shows that this technology node is capable of achieving a time-matching of 800fs which has never been reported. In addition, a competitive figure-of-merit is achieved.

In the low-THD oscillator, I proposed a new architectural solution for synthesizing a highly-linear sinusoidal signal using a novel harmonic rejection approach. The chip is fabricated in 130nm technology and shows an outstanding performance compared to the state of the art. The designed consumes 80% less power; consumes less area; provides much higher amplitude while being composed of purely digital circuits and passive elements.

Last but not least, the spur-frequency boosting PLL employs a novel technique that eliminates the reference spurs. Instead of adding additional filtering at the reference frequency, the spur frequency is boosted to higher frequency which is, naturally, has higher filtering effects. The prototype is fabricated in 90nm digital CMOS and proved to provide the lowest normalized reference spurs ever reported.

# DEDICATION

To my beloved parents, to my dear wife Shaimaa, to my sons Adam and Musa, and to all my family members for their love and support

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank Allah for all His bounties that He provided me through my life and my PhD. Without His guidance, I would have been lost in this life.

"My Lord! Grant me the power and ability that I may be grateful for Your Favors which You have bestowed on me and on my parents, and that I may do righteous good deeds that will please You, and admit me by Your Mercy among Your righteous slaves."

#### [Al-Naml: 27]

I would like to present my deep appreciation to my advisor Dr. Edgar Sánchez-Sinencio. In addition to being an academic advisor, Dr. Sánchez-Sinencio is a personal advisor for all his students. The environment that he provided me during my studies was really one of the great factors in the success of this dissertation. I would like also to thank Dr. José Silva-Martínez for providing precious advice and sharing his time and experience with me in the time-domain ADC project.

Special thanks also go to my ex-roommate, Mohammed Mohsen Abdul-Latif, not only for sharing an apartment together, but also for sharing a 13-year long journey of undergraduate and graduate studies. I thank him for all his help and support. Many thanks go also to all my colleagues especially Faisal Hussien and Mohamed Mobarak who made my transition from Egypt to College Station smooth. Special thanks are due to Mohammed El-Nozahi, Ahmed Amer, Ehab Abdulghany, Ahmed Helmy, Ramy Saad, Ayman Ameen and Ahmed Ragab for their numerous technical discussions and the good environment that they all helped to maintain in our group. Thanks also to my research colleagues Vijaykumar Dhanasekaran, Manisha Gambhir and Erik Pankratz.

I would like to present my sincere gratefulness to my wife, Shaimaa, for her continuous love, support, encouragement and patience and for her care of our little babies Adam and Musa. She provided me with the emotional support that I was really missing after leaving my family in Egypt.

Finally, words cannot express my endless thanks and gratitude for my parents, Prof. Mostafa Elsayed and Prof. Bothina Abdulfattah for all their love, help and support. May Allah reward them for all the good that they did for me.

# TABLE OF CONTENTS

| ABSTR  | RACT                                                                               | iii                                                         |

|--------|------------------------------------------------------------------------------------|-------------------------------------------------------------|

| DEDIC  | ATION                                                                              | v                                                           |

| ACKN   | OWLEDGEMENTS                                                                       | vi                                                          |

| TABLE  | E OF CONTENTS                                                                      | viii                                                        |

| LIST O | PF FIGURES                                                                         | xi                                                          |

| LIST O | PF TABLES                                                                          | xvi                                                         |

| СНАРТ  | ΓER                                                                                |                                                             |

| Ι      | INTRODUCTION                                                                       | 1                                                           |

|        | 1.1 Motivation1.2 Organization                                                     | 1<br>3                                                      |

|        | A 67DB DYNAMIC RANGE TIME-TO-DIGITAL CONVERTER<br>FOR TIME-MODE-BASED ΣΔ MODULATOR | 6                                                           |

|        | <ul> <li>2.1 Introduction to Time-to-Digital Converters</li></ul>                  | 6<br>7<br>8<br>10<br>12<br>12<br>14<br>15<br>16<br>22<br>22 |

|        | <ul> <li>2.2.2 Dive of FDC's Time Steps</li></ul>                                  | 22<br>28<br>34<br>34<br>38<br>39                            |

|     | 2.4.4 SR Latch.22.4.5 Reset Unit.22.4.6 Calibration Circuit.22.5 Jitter and Data Dependent Delay22.6 Layout Considerations and Experimental Results.22.7 Summary.2                                                                                                                                                                              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| III | A LOW THD, LOW POWER, HIGH OUTPUT-SWING TIME-<br>MODE-BASED OSCILLATOR VIA DIGITAL HARMONIC-<br>CANCELLATION TECHNIQUE                                                                                                                                                                                                                          |

|     | 3.1 Introduction.53.2 Background of Low THD Oscillators.53.3 Harmonic Cancellation Technique.53.3.1 Harmonic Cancellation Theory.63.3.2 System Level Design.63.4 Circuit Implementation.63.5 Performance Limitations.73.5.1 Amplitude and Phase Error Analysis.73.5.2 Even Harmonic Distortion Analyses.73.6 Measurement Results.83.7 Summary.8 |

| IV  | A SPUR-FREQUENCY BOOSTING PLL FOR LOW SPUR<br>FREQUENCY SYNTHESIZER                                                                                                                                                                                                                                                                             |

|     | 4.1 Introduction84.2 PLL Dynamics94.3 PLL Reference Spurs14.4 Low Spurs PLLs14.4.1 Gear-Shifting PLL14.4.2 Dead-Zone Controlled PLL14.4.3 Variable-K <sub>VCO</sub> PLL14.4.4 Multi-Path PFD-CP PLL14.4.5 Spur Suppression PLL Based on Sample-Reset Filter14.5 Spur-Frequency Boosting PLL1                                                    |

|     | 4.5.1 System Level Design14.5.2 Transistor Level Implementation14.5.2.1 PFD14.5.2.2 Divider14.5.2.3 Voltage-Controlled Oscillator14.5.2.4 Charge Pump1                                                                                                                                                                                          |

Page

|       | 4.5.2.5 Time-to-Voltage Converter | 132 |

|-------|-----------------------------------|-----|

|       | 4.5.2.6 Voltage-to-Time Converter | 140 |

|       | 4.5.3 PLL Implementation          | 147 |

|       | 4.5.4 Measurement Results         | 151 |

|       | 4.6 Summary                       | 156 |

| V     | CONCLUSIONS AND FUTURE WORK       | 157 |

| REFEI | RENCES                            | 159 |

| VITA. |                                   | 168 |

# Page

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

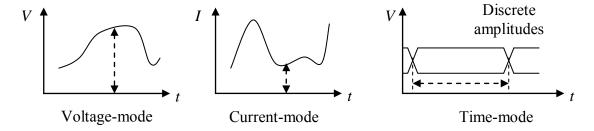

| 1.1    | Signal representation in the different modes.                                                                                                                                        | 3    |

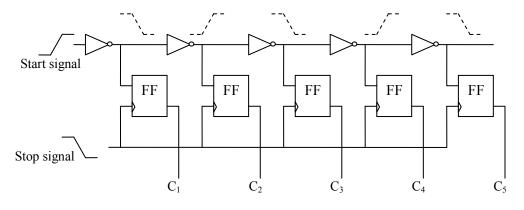

| 2.1    | Inverter chain based TDC.                                                                                                                                                            | 8    |

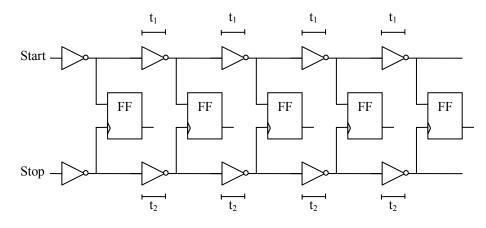

| 2.2    | Vernier line-based TDC                                                                                                                                                               | 10   |

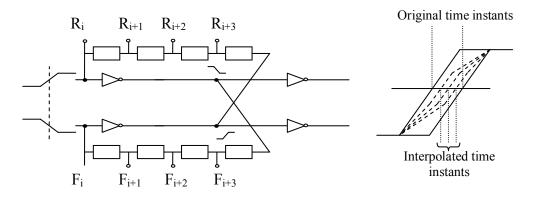

| 2.3    | Local passive interpolation TDC                                                                                                                                                      | 11   |

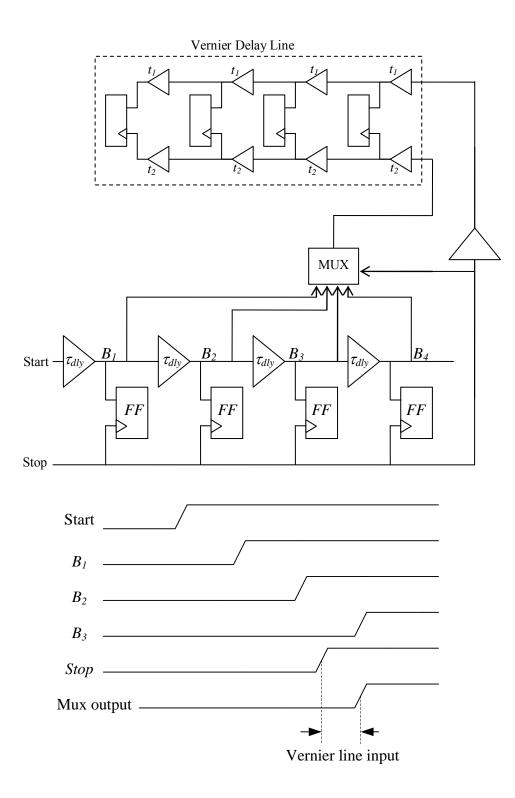

| 2.4    | Multistage TDC and its timing diagram.                                                                                                                                               | 13   |

| 2.5    | Reference recycling TDC [17].                                                                                                                                                        | 14   |

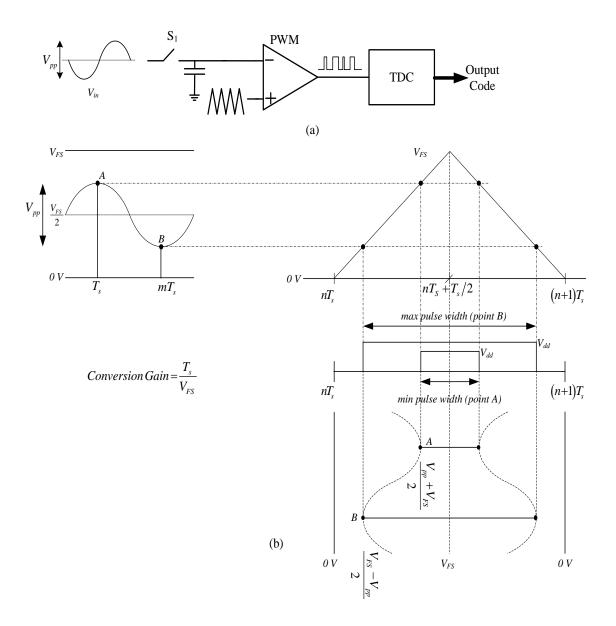

| 2.6    | (a) Open-loop time-mode-based ADC. (b) Timing diagram of the PWM                                                                                                                     | 18   |

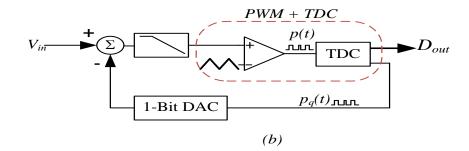

| 2.7    | Block diagrams of a) Voltage-mode $\Sigma\Delta$ modulator. b) Time-mode $\Sigma\Delta$ modulator.                                                                                   | 21   |

| 2.8    | TDC-based $\Sigma \Delta$ ADC : a) Block diagram. b) Timing diagram and $p_q(t)$ generation.                                                                                         | 23   |

| 2.9    | 9 M-Level feedback DAC: a) DAC output signal. b) Thermometric DAC architecture.                                                                                                      | 26   |

| 2.10   | Block diagram of the output code generation of the TDC                                                                                                                               | 31   |

| 2.11   | Uniform-delay wired-Nor architecture for the feedback pulse, $p_q(t)$ , generation.                                                                                                  | 32   |

| 2.12   | Block diagram of the different architectures for implementing 25 inputs <i>OR</i> gate of Fig. 6. a) 1-Level <i>OR</i> gate. b) 2-Levels <i>OR</i> gate. c) 3-Levels <i>OR</i> gate. | 33   |

| 2.13   | Relative jitter of the different OR gate architectures versus transistor's width                                                                                                     | 35   |

| 2.14   | Block diagram of the TDC with the feedback pulse generator                                                                                                                           | 36   |

| FIGURE |                                                                                                                                                                              | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

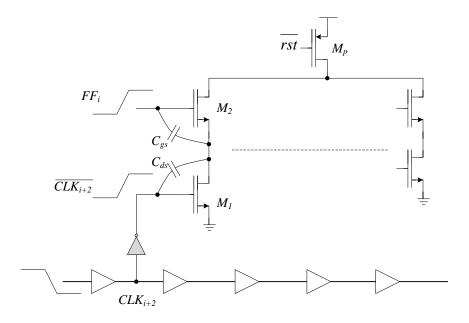

| 2.15   | Dynamic-logic-based delay cell (D): Transistor level implementation.                                                                                                         | 38   |

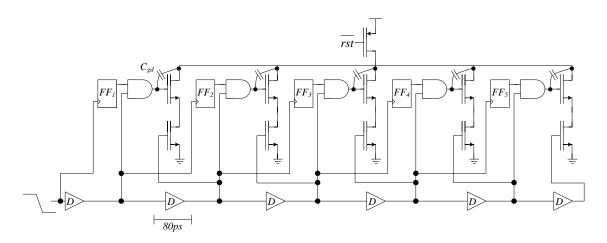

| 2.16   | Dynamic-logic-based flip flop ( <i>FF</i> ).<br>a) Transistor level implementation. b) Timing diagram when the input is captured. c) Timing diagram when the input is missed | 40   |

| 2.17   | Dynamic-logic-based OR gate                                                                                                                                                  | 41   |

| 2.18   | SR latch for the feedback pulse generation                                                                                                                                   | 42   |

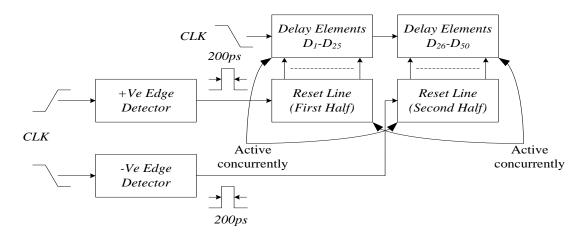

| 2.19   | Block diagram of the reset architecture of the TDC                                                                                                                           | 43   |

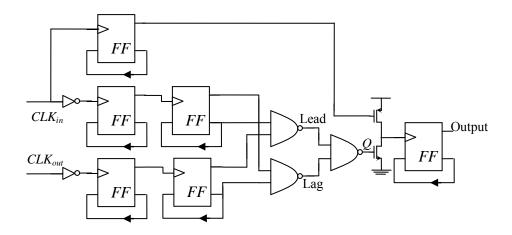

| 2.20   | Block diagram of the phase detector                                                                                                                                          | 44   |

| 2.21   | Effect of flip flop transition on the delay of the delay elements                                                                                                            | 47   |

| 2.22   | Effect of flip flop transition on OR gate response                                                                                                                           | 47   |

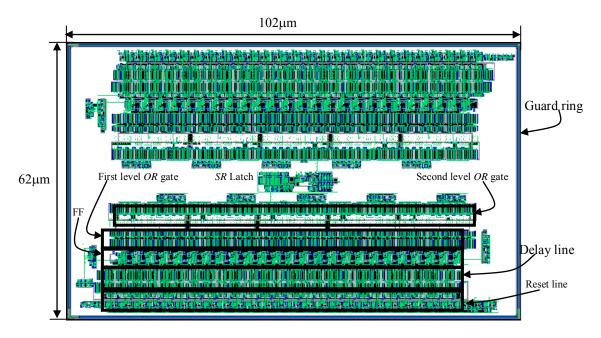

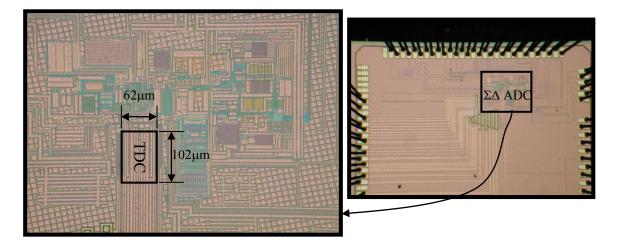

| 2.23   | Layout of the TDC                                                                                                                                                            | 49   |

| 2.24   | Chip micrograph                                                                                                                                                              | 49   |

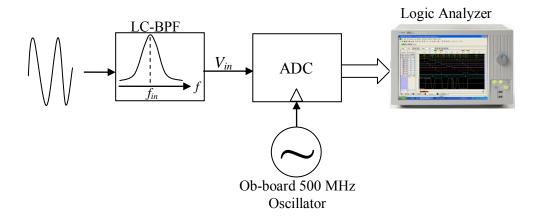

| 2.25   | Test setup for the measurement of the ADC                                                                                                                                    | 50   |

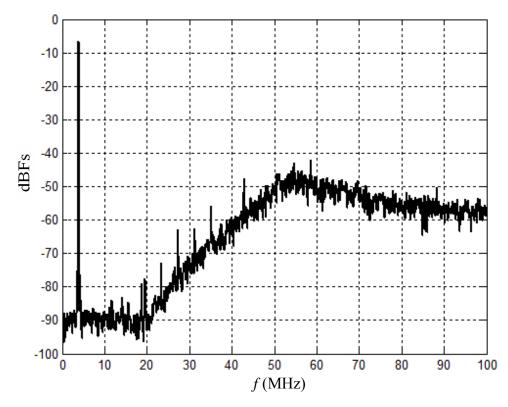

| 2.26   | Output spectrum for a -6dB input signal                                                                                                                                      | 50   |

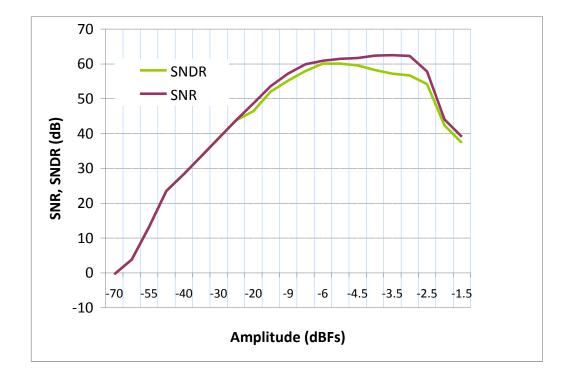

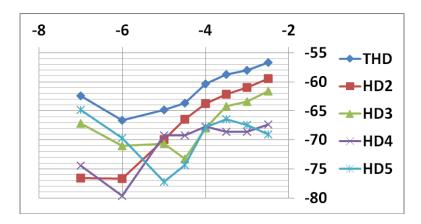

| 2.27   | SNR and SNDR of the ADC versus the input amplitude                                                                                                                           | 52   |

| 2.28   | HDk and the THD of the ADC versus the input amplitude                                                                                                                        | 53   |

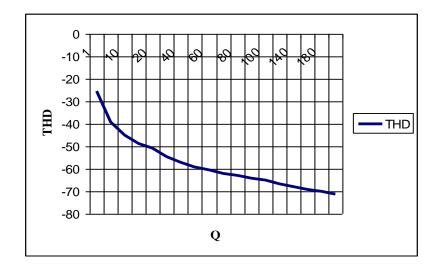

| 3.1    | THD of the oscillator versus the quality factor of a second order filter.                                                                                                    | 57   |

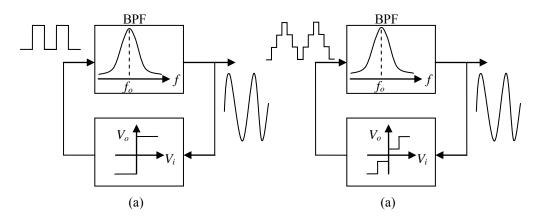

| 3.2    | Block diagram of (a) Conventional BPF-based oscillator.<br>(b) Multilevel-comparator-based oscillator                                                                        | 57   |

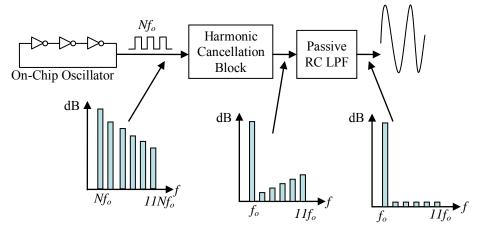

| 3.3    | Block diagram of the system                                                                                                                                                  | 59   |

| 3.4    | Block diagram of the proposed harmonic-cancellation-based oscillator.                                                                                                        | 61   |

| FIGURE |                                                                                                                             | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------|------|

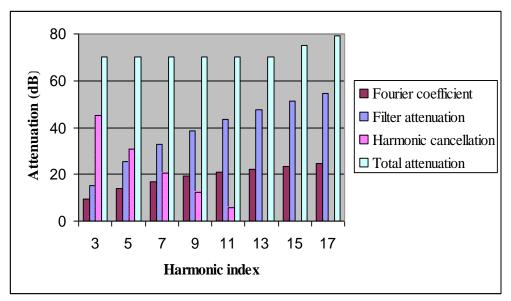

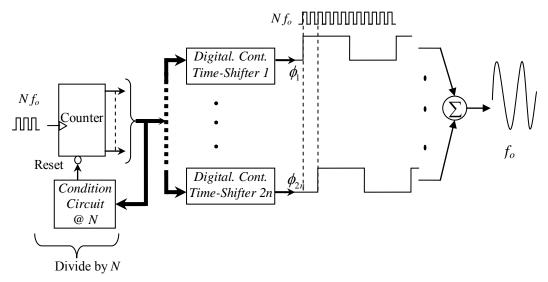

| 3.5    | Harmonics attenuation contributed by the different attenuation components of the oscillator system                          | 64   |

| 3.6    | Block diagram of the harmonic cancellation block.                                                                           | 64   |

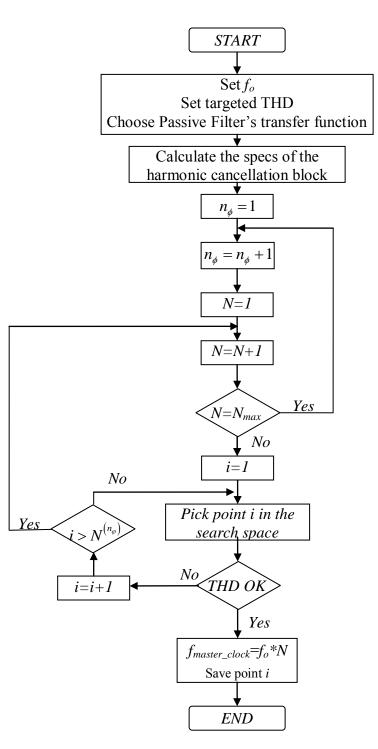

| 3.7    | Flow chart of the design procedure and the search algorithm for finding the appropriate time shifts                         | 66   |

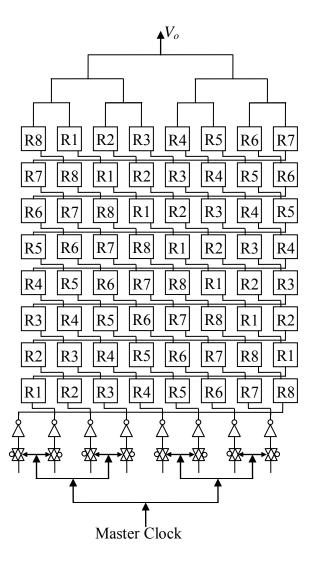

| 3.8    | Detailed block diagram of the oscillator                                                                                    | 67   |

| 3.9    | Clock routing and resistor-summer layout diagram                                                                            | 70   |

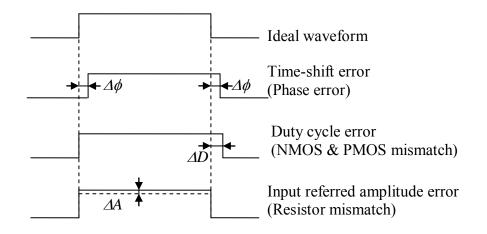

| 3.10   | Different types of the added signal errors                                                                                  | 72   |

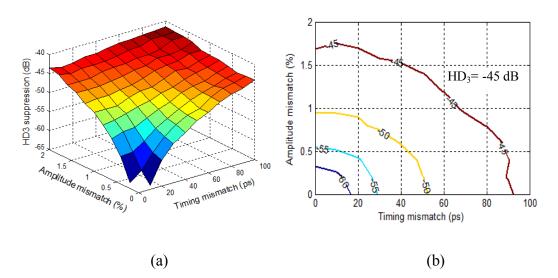

| 3.11   | Effect of timing and amplitude mismatches on HD <sub>3</sub> suppression. a) 3D plot. b) HD <sub>3</sub> Contour plot       | 74   |

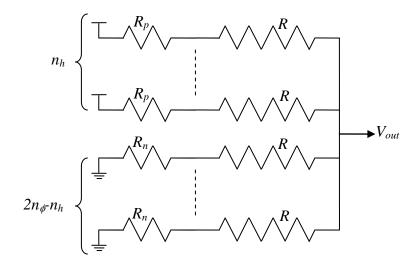

| 3.12   | PMOS/NMOS on-resistance switches mismatch.                                                                                  | 77   |

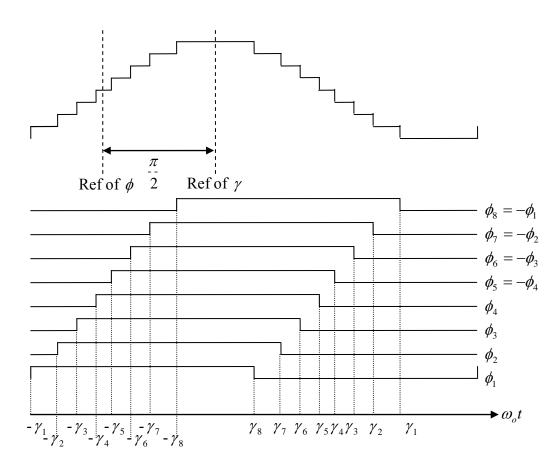

| 3.13   | Axis change from $\phi$ to $\gamma$                                                                                         | 78   |

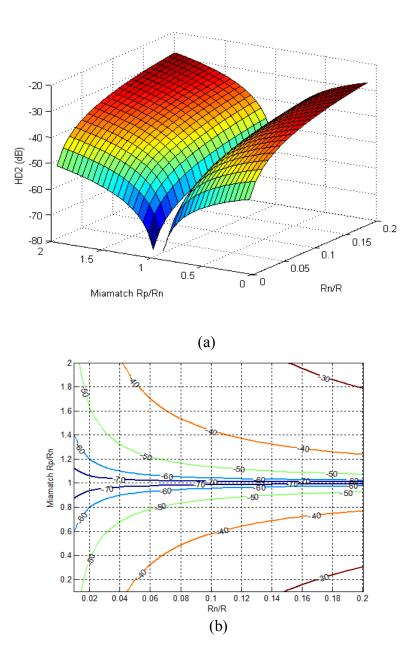

| 3.14   | On-resistance effect of the NMOS/PMOS transistors switches on HD <sub>2</sub> . a) 3D plot. b) HD <sub>2</sub> Contour plot | 80   |

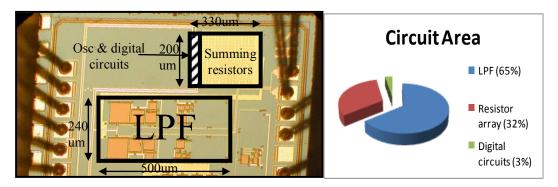

| 3.15   | Chip micrograph and area budgeting                                                                                          | 82   |

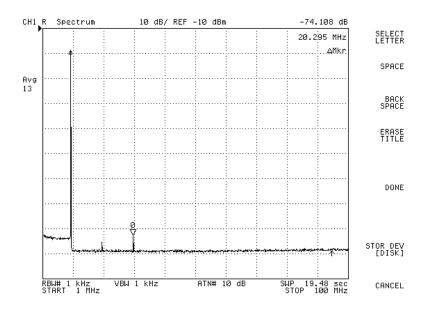

| 3.16   | Output spectrum of the pseudo-differential version of the oscillator at 10MHz.                                              | 83   |

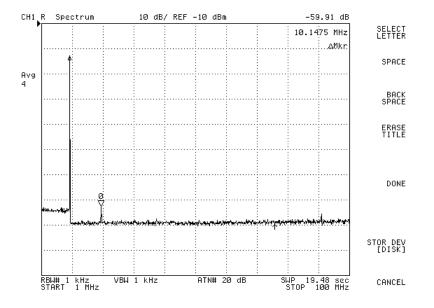

| 3.17   | Output spectrum of the single-ended version of the oscillator at 10MHz.                                                     | 84   |

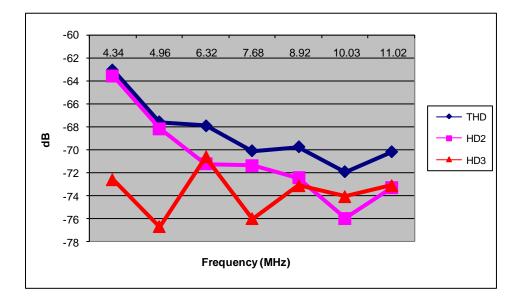

| 3.17   | HD <sub>2</sub> , HD <sub>3</sub> and THD of the differential output of the oscillator versus the output frequency          | 85   |

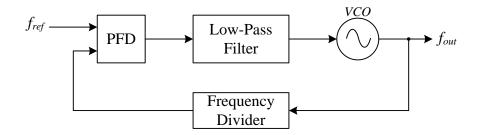

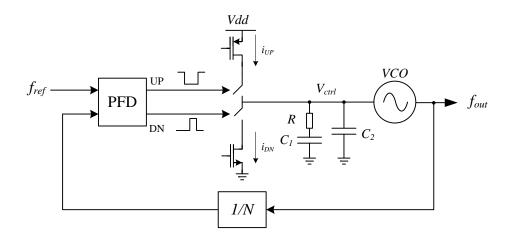

| 4.1    | Block diagram of a conventional PLL                                                                                         | 88   |

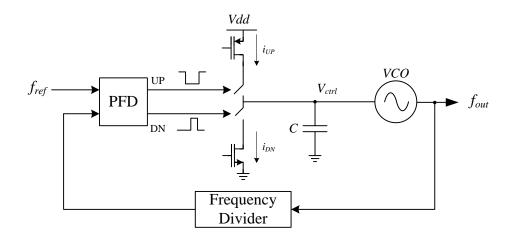

| 4.2    | Block diagram of the charge-pump-based PLL (CP-PLL)                                                                         | 90   |

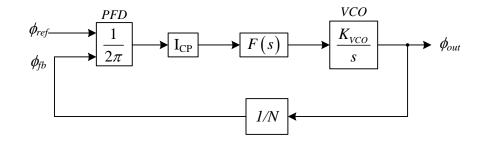

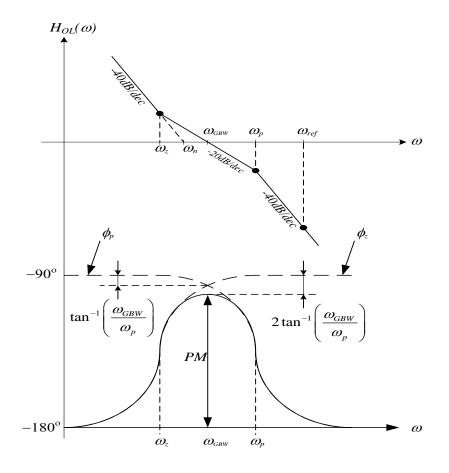

| 4.3    | Block diagram of the CP-PLL model                                                                                           | 92   |

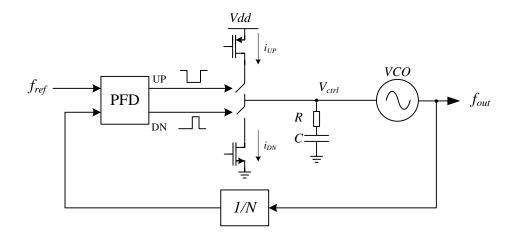

| 4.4    | Block diagram of the CP-PLL with the modified loop filter                                                                   | 93   |

| FIGURE |                                                                 | Page |

|--------|-----------------------------------------------------------------|------|

| 4.5    | Block diagram of the CP-PLL with the smoothing capacitor $C_2$  | 99   |

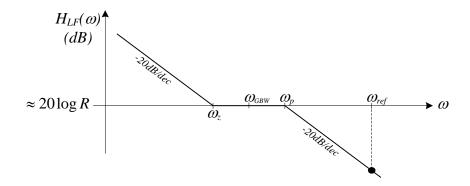

| 4.6    | Bode plot of a PLL                                              | 103  |

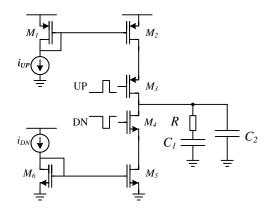

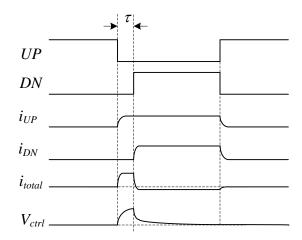

| 4.7    | Transistor level implementation of the charge pump              | 105  |

| 4.8    | Timing diagram of the current mismatches in CP-PLL              | 106  |

| 4.9    | Filtering characteristics of the loop filter                    | 108  |

| 4.10   | Block diagram of the dead-zone controlled PLL                   | 113  |

| 4.11   | Block diagram of the variable-KVCO PLL                          | 113  |

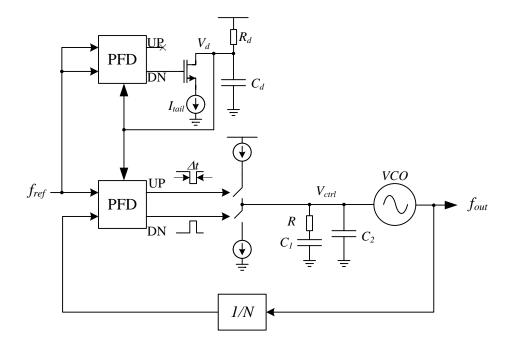

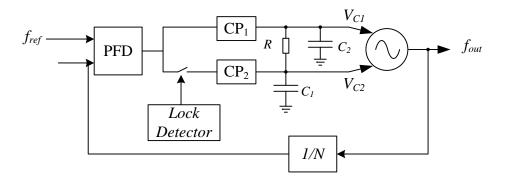

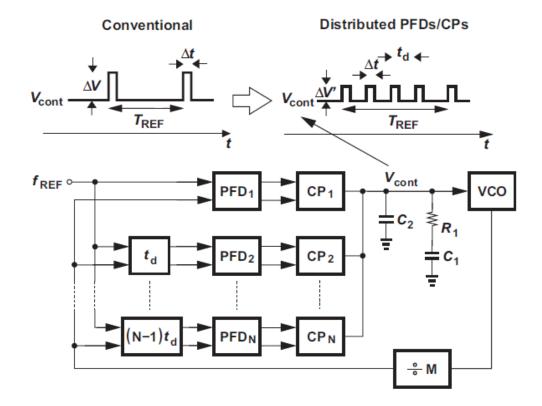

| 4.12   | Block diagram of the multi-path PFD-CP PLL [58]                 | 115  |

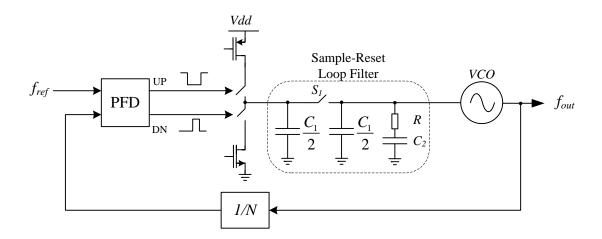

| 4.13   | Sample-based loop filter                                        | 116  |

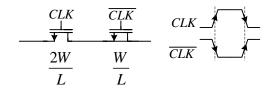

| 4.14   | Transmission gate with dummy switches                           | 118  |

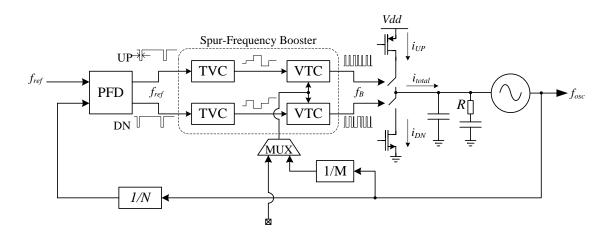

| 4.15   | Block diagram of the proposed SFB-PLL                           | 119  |

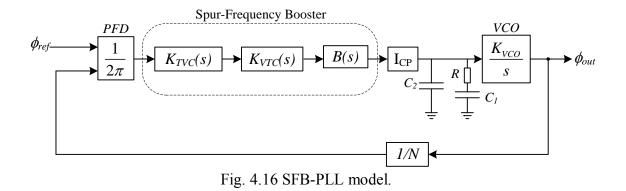

| 4.16   | SFB-PLL model                                                   | 121  |

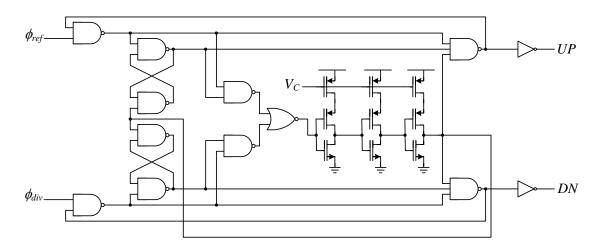

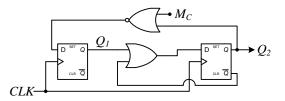

| 4.17   | Transistor level implementation of the phase-frequency detector | 124  |

| 4.18   | PFD minimum pulse width versus the control voltage              | 124  |

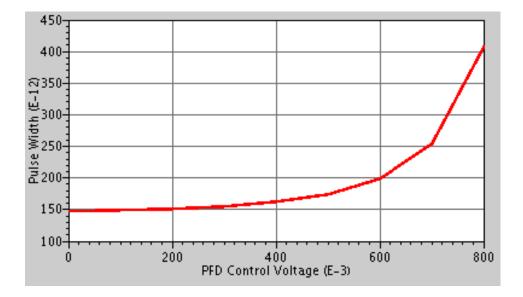

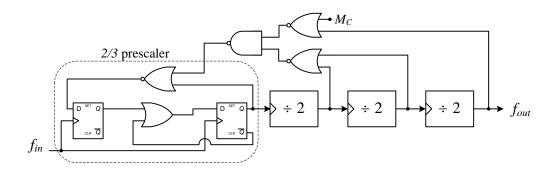

| 4.19   | Typical integer-N divider architecture in PLLs                  | 125  |

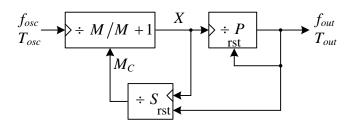

| 4.20   | Block diagram of a prescaler with $M=2$                         | 126  |

| 4.21   | Block diagram of a 16/17 prescaler                              | 127  |

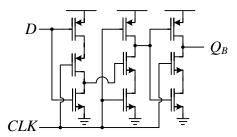

| 4.22   | Transistor level implementation of the TSPC D-FF                | 128  |

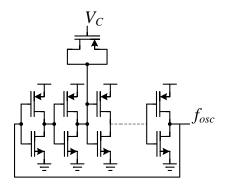

| 4.23   | Transistor level implementation of the VCO                      | 129  |

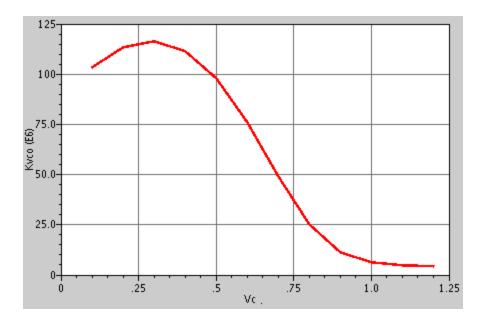

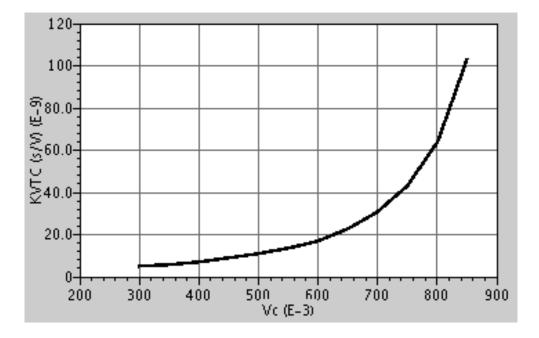

| 4.24   | VCO gain versus the control voltage                             | 130  |

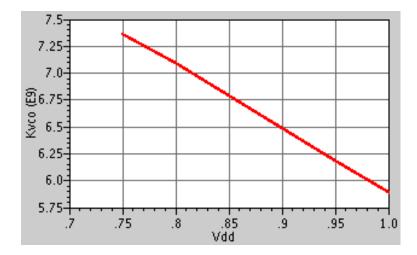

| 4.25   | VCO gain versus the supply voltage                              | 131  |

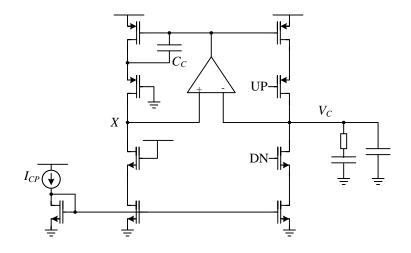

| 4.26   | Transistor level implementation of the CP                       | 132  |

| FIGURE |                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------|------|

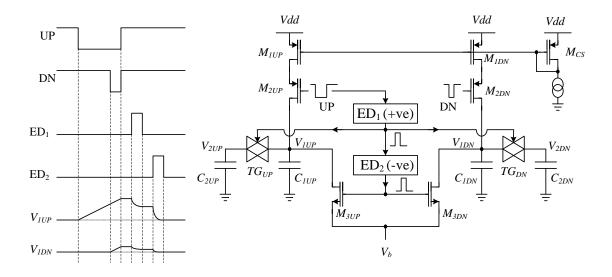

| 4.27   | Transistor level implementation of the TVCs                                             | 134  |

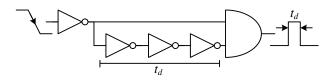

| 4.28   | Block diagram of a negative edge detector                                               | 134  |

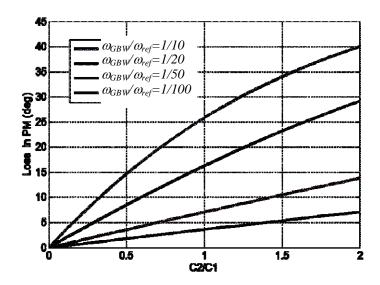

| 4.29   | Degradation of the phase margin versus the TVC capacitors ratio                         | 136  |

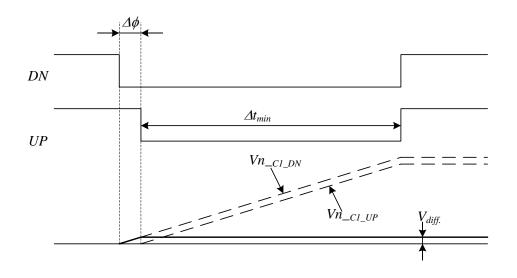

| 4.30   | Timing diagram for the effect of the current source noise on the performance of the TVC | 138  |

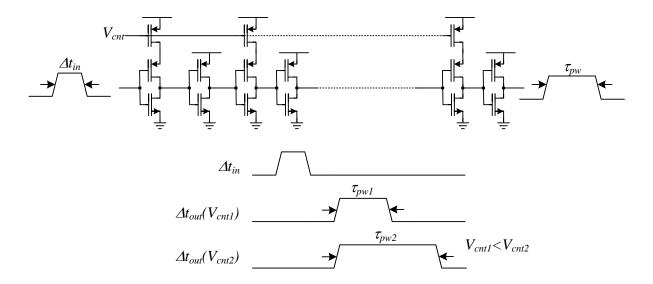

| 4.31   | Transistor level implementation of the delay line based VTC                             | 141  |

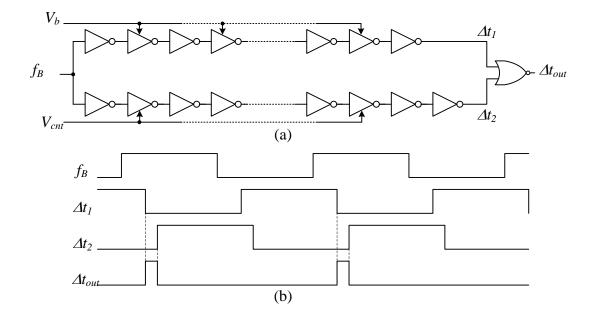

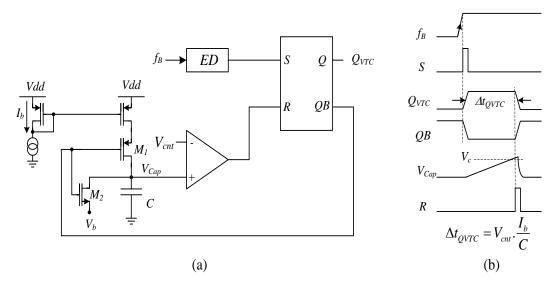

| 4.32   | Pseudo-differential delay-line-based VTC and its timing diagram                         | 143  |

| 4.33   | Gain of the inverter-based VTC versus the control voltage $V_{cnt}$                     | 144  |

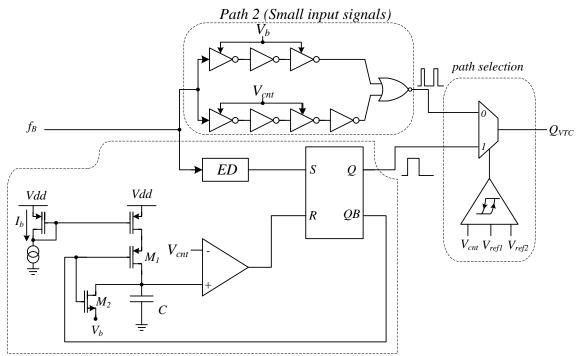

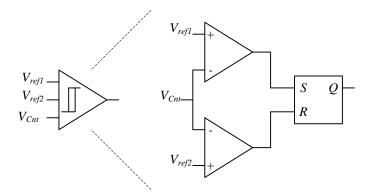

| 4.34   | Block diagram of the TVC-based VTC                                                      | 144  |

| 4.35   | Complete block diagram of the VTC                                                       | 146  |

| 4.36   | Block diagram of the comparator with hysteresis                                         | 146  |

| 4.37   | SFB-PLL model                                                                           | 148  |

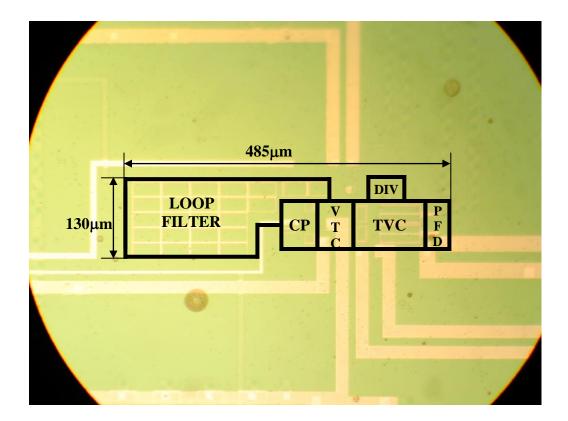

| 4.38   | SFB-PLL chip micrograph                                                                 | 152  |

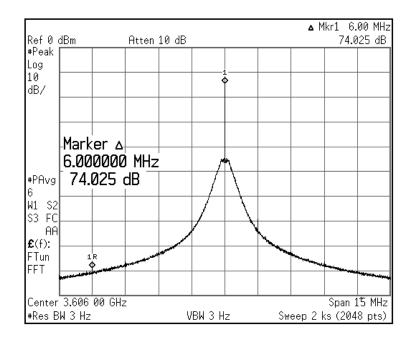

| 4.39   | SFB-PLL's output spectrum showing the reference spur at 6MHz offset.                    | 153  |

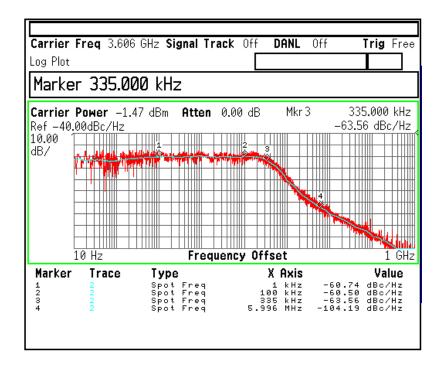

| 4.40   | Phase-noise plot of the SFB-PLL                                                         | 153  |

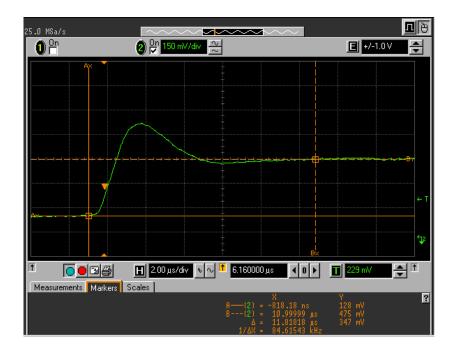

Transient response of the SFB-PLL showing a settling time of

11.8µsec.....

4.41

XV

154

# LIST OF TABLES

| TABLE |                                                                           | Page |

|-------|---------------------------------------------------------------------------|------|

| 2.1   | Comparison of the different TDC techniques                                | 16   |

| 2.2   | TDC measurement results compared with the state of the art TDCs           | 53   |

| 3.1   | Comparison of performance of the proposed approach with state-of-the-art. | 87   |

| 4.1   | Comparison between the different spur suppression techniques              | 118  |

| 4.2   | Truth table of a 2/3 prescaler                                            | 126  |

| 4.3   | SFB-PLL performance summary compared to the state-of-the-art PLLs.        | 155  |

#### CHAPTER I

#### INTRODUCTION

#### **1.1 Motivation**

Analog circuit design passed by many phases through the last century. Motivated by the invention of CMOS integrated circuits, many design techniques appeared to overcome the new challenges of the CMOS technology in which the dimensions scales down allowing the integration of larger systems. Gordan Moor predicted in 1975 that MOS device dimensions would continue to scale down by a factor of two every three years and the number of transistors per chip would double every one to two years [1]. As technology scales down by factor  $\alpha$ , the supply voltage, theoretically, scales down with the same factor. The aggressive reduction in the supply voltage and the moderate reduction in the device threshold voltage of CMOS technology have greatly affected the performance of CMOS voltage-mode circuits, typically reflected by a reduced dynamic range, increased propagation delay and reduced low noise margins [2]. Such scaling motivated the designers in sixties to introduce the current-mode circuit as a promising substitute for its voltage-mode counterpart [3].

This dissertation follows the style of IEEE Journal of Solid-State Circuits.

Signal representation in current-mode circuits depends on the value of the current flowing through certain branch. Consequently, it is upper limit is not constrained by the supply voltage as in the voltage- mode case in which the voltage signal must be less than the supply voltage except in some rare applications. In addition, high frequency operation favors current mode circuit topologies that are characterized by having lowimpedance-nodes compared to its voltage-mode counterpart. Thus, high frequency applications usually employ current-mode analog circuits and current-mode-logic (CML) to extend the operating bandwidth. On the other hand, low frequency applications continued to employ voltage-mode circuits since it usually consumes less power. However, rapid scaling in technology has introduced new challenges in the realm of traditional analog design. Scaling of supply voltage directly impacts the available voltage-dynamic-range. On the other hand, nanometric technologies with cutoff frequency  $f_T$  in hundreds of GHz range opens opportunities for time-resolution-based signal processing, which was not a viable option in previous technology nodes [4]. With reduced available voltage-dynamic-range and improved timing resolution, it is more convenient to device analog circuits whose performance depends on edge-timing precision rather than voltage levels. Thus, instead of representing the data/information in the voltage-mode, as a difference between two node voltages, or in current-mode, as a current flowing through certain branch, it should be represented in time-mode as a timedifference between two rising and/or falling edges. Fig. 1.1 shows the representation of the signals in voltage-mode, current-mode and time-mode. A major advantage of processing signals encoded in the time-mode is the digital-friendly nature of the system,

which scales down with the technology. In addition, migrating to smaller technologies is expected to improve the performance of the same time-mode-based design as timing resolution is improved.

The main circuit blocks in time-mode systems are the time-to-voltage and voltage-to-time converters which interface the time-mode circuits to the voltage-mode one. The first one can be considered as a charge pump that produces an output voltage that is proportional to the input pulse width while the later can be considered as a pulse-width-modulator (PWM) which generates an output pulse whose width is proportional to the input voltage.

Fig. 1.1 Signal representation in the different modes.

#### **1.2 Organization**

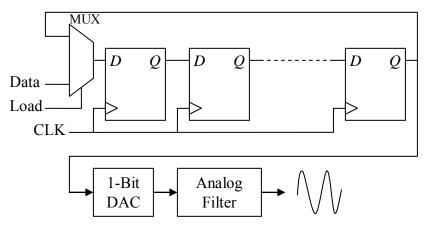

The dissertation includes novel design and implementation of three different blocks employing the time-mode concept discussed above. A time-to-digital converter (TDC) is proposed in chapter II to replace the multi-bit quantizer and the multi-bit feedback DAC of traditional voltage-mode  $\Sigma\Delta$  modulator. The proposed time-mode TDC makes the multi-bit  $\Sigma \Delta \square$  ADC digital friendly and more suitable for nanometric technologies. A pulse-width-modulator (PWM) converts the sampled-and-held voltage-sample to a time-pulse that the TDC generates a digital code corresponding its width. Simultaneously, the TDC provides a time-quantized feedback pulse for the  $\Sigma \Delta$  modulator, emulating the voltage-DAC in a conventional  $\Sigma \Delta$  ADC. Measurements show that the  $\Sigma \Delta$ -modulator achieves a dynamic range of 68dB and the TDC consumes 5.66mW at 250MHz event rate while occupying 0.006mm<sup>2</sup>.

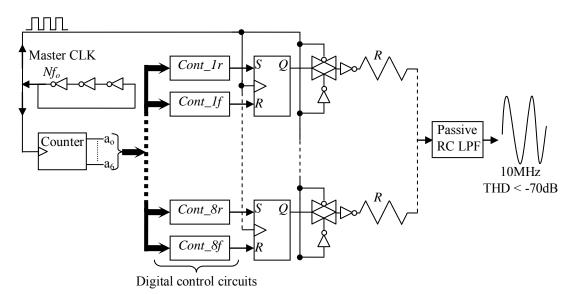

Chapter III proposed an architectural solution for designing and implementing low THD oscillators. A digital harmonic-cancellation-block is used to suppress the low frequency harmonics while a passive, inherently linear, filter is used to suppress the high frequency ones. The proposed technique eliminates the need for typical analog, high-Q BPF to suppress the harmonics. Thus, eradicates the effect of increasing device nonlinearities in the nanometric technologies by having pure digital solution. In addition, eliminating the need for high-Q band-pass-filter (BPF) releases the output swing from the constraints imposed by the linearity of the filter. Measurement results show -72dB THD at 10MHz along with a differential output swing of 228mV<sub>pp</sub>. As the performance depends solely on the timing precision of digital signals, the proposed oscillator is considered the best time-mode-based oscillator in literature.

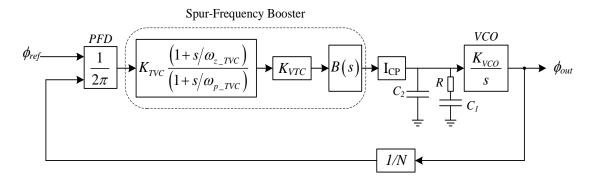

Chapter IV proposes an architectural solution for designing and implementing a low-reference-spurs PLL. A spur frequency-booster block is inserted between the PFD and the CP to boost the charge-pump input frequency. Hence, the reference-spurs theoretically vanish. The proposed technique adds additional degrees of freedom in the design of PLLs such that the spurs level can be reduced without sacrificing neither the loop bandwidth nor the voltage-controlled oscillator's gain. The prototype achieves -74dBc reference-spur suppression along with ( $K_{VCO}/f_{ref}$ ) ratio of 17 at a ( $f_{BW}/f_{ref}$ ) ratio of 1/20.

Finally, Chapter V concludes the work and explores the areas for future work.

#### CHAPTER II

# A 67DB DYNAMIC RANGE TIME-TO-DIGITAL CONVERTER FOR TIME-MODE-BASED $\Sigma\Delta$ MODULATOR\*

## 2.1 Introduction to Time-to-Digital Converters

The basic block that manipulates the data in time mode is the TDC. The TDC can be defined as a block that provides a digital code that corresponds to the width of the pulse (which is the data in time-mode case). Measuring the width of a digital pulse became an important technique for many applications. Although the very first work on CMOS TDC was targeting high energy physics, it became widely used in other electronic applications like PLL and time of flight-based systems [5-7]. The main TDC performance metrics are:

<sup>\*</sup>Reprinted, with permission, from M. M. Elsayed, V. Dhanasekaran, M. Gambhir, J. Silva-Martinez and E. Sánchez-Sinencio, "A 0.8ps DNL Time-to-Digital Converter with 250MHz Event Rate in 65nm CMOS for Time-Mode-Based ΣΔ Modulator" *IEEE J. Solid-State Circuits.*, vol. 46, no. 9, pp.2048-2098, Sept 2011. © 2011 IEEE and from V. Dhanasekaran, M. Gambhir, M. M. Elsayed, E. Sánchez-Sinencio, J. Silva-Martinez, C. Mishra, L. Chen, E. Pankratz "A 20MHz BW 68dB DR CT ΔΣ ADC Based on a Multi-Bit Time-Domain Quantizer and Feedback Element," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, Feb. 2009, pp. 174-175. © 2009 IEEE and from V. Dhanasekaran, M. Gambhir, M. M. Elsayed, E. Sánchez-Sinencio, J. Silva-Martinez, C. Mishra, L. Chen, E. Pankratz "A Continuous Time Multi-Bit ΔΣ ADC Using Time-Domain Quantizer and Feedback Element," *IEEE J. Solid-State Circuits.*, vol. 46, no. 3, pp.639-650, Mar 2011. © 2011 IEEE.

- 1- Differential-nonlinearity (DNL): defines as the difference between the actual time-step size and the ideal one.

- 2- Resolution: is the minimum time-step the TDC can resolve.

- 3- Latency: (or the conversion time): defined as the time the TDC requires after the signal is tracked till the digital output is available.

- 4- Dead time: is the minimum time required between two acquisitions.

- 5- Silicon area.

- 6- Power consumption.

Since different topologies were developed to improve the performance of TDCs, a short description of each topology will be presented followed by a comparison table for the TDC tradeoffs.

#### 2.1.1 Inverter-Chain-Based TDC[8-11]

The block diagram of the inverter-chain-based TDC is shown in Fig. 2.1. The basic idea is to propagate the start signal, the rising edge of the pulse to be measured, through a delay line whose elements consists of CMOS inverters connected to the input of a flip flop. While the signal propagates through the line the output of each inverter toggles and changes its state. When the stop signal triggers the flip flops, the state of the line is captured and the position of the propagating start signal is identified by applying *XOR* function on every two successive flip flop outputs. The output of the *XOR* is zero only at the position of the start signal.

Fig. 2.1 Inverter chain based TDC.

By knowing the position of the propagating start signal and the delay of the single cell, the width of the pulse can be calculated. The main advantage of the inverterchain-based TDC is the simplicity of the design and the conversion speed. On the other hand, the resolution is limited by one inverter delay which puts fundamental limit on the resolution of the circuit.

#### 2.1.2 TDC Based on Vernier Delay Line [12-14]

The second most commonly used TDC is the Vernier TDC. Vernier delay line overcomes the basic limitation of the inverter-chain-based TDC, the resolution, by employing two delay lines of different delays per inverter cell,  $t_1 > t_2$ , as shown in Fig. 2.2. The start signal propagates through the first line and changes the inputs of the flip flops while the stop signal propagates through the second line and captures the inputs of the flip flops. As the stop signal propagates faster than the start signal, at certain time and certain flip flop it will precede the start signal and trigger that flip flop to capture an

unchanged input (because the start signal is lagging the stop signal). Consequently, at the time that both edges are at the same stage the two successive flip flop outputs will be the same indicating that stop signal precedes the start signal at this stage. In this case the pulse width will be equal to:

$$T_{pulse} = N^*(t_1 - t_2) \tag{2.1}$$

where N is the number of flip flops that captured a changed input.

It can be seen from this equation that the resolution of the Vernier-based TDC is the difference between two inverter delays,  $(t_1-t_2)$ , instead of one inverter delay. In other words, the resolution enhancement factor is given by:

$$\alpha = (t_2/(t_1 - t_2))$$

(2.2)

On the other hand, the number of stages required to accommodate the same maximum pulse width is increased by  $\alpha$  compared to inverter-chain-based TDC. The number of stages required to accommodate a pulse width of *T* is given by  $N=T/(t_1-t_2)$ . In addition, having two active delay lines at the same time and increasing the delay line length by the resolution enhancement factor,  $\alpha$ , categorizes this technique as a power hungry one. One last disadvantage of this technique is the conversion latency. The latency is given by:

$$L=N.t_2 \tag{2.3}$$

Fig. 2.2 Vernier line-based TDC.

#### 2.1.3 Local Passive Interpolation TDC

This technique increases the resolution of the inverter-chain TDC while avoiding the latency of Vernier-based TDC. A conventional TDC is incorporated with local passive interpolators, LPI, between the successive delay elements to improve the resolution as shown in Fig. 2.3 [15]. Two delay lines are excited using differential input pulse while four-level passive interpolator is used to generate the intermediate crossings. The original crossings as well as the interpolated ones drive flip flop inputs that are triggered by the STOP signal. As shown in Fig.2.3, four resistors are used to interpolate two signals shifted by one inverter delay which improves the resolution by a factor of four.

Fig. 2.3 Local passive interpolation TDC

Area wise, this technique has less number of inverters, one fourth of Vernier TDC, but there is area overhead from the resistors and flip flops. Moreover, to have accurate interpolation, poly-silicon resistors are used which ends up with large area compared to Vernier TDC. From the mismatch point of view, the interpolation accuracy depends on the ratio between the four resistors rather than their absolute values. Since global mismatch does not affect the resistors ratios, this topology is considered a robust one. Finally, using less number of inverters in the delay line in this technique reduces the power consumption.

#### 2.1.4 Multistage TDC

This technique overcomes the disadvantage of having long Vernier line by using multistage pulse-quantization. A chain of buffers, similar to the conventional TDC, performs the coarse quantization while the fine quantization is performed using Vernier delay line as shown in Fig. 2.4 [16].

Since the maximum input-pulse-width to the Vernier line is set by the resolution of the conventional TDC, this technique is considered area and power efficient compared to Vernier-line-based TDC. Moreover, this technique surpasses Vernier TDC by having latency that is always less one buffer delay. On the other hand, it suffers two disadvantages. First, it is required to have two delay locked loops (DLL), instead of one, to calibrate the delay of each stage. Second, the MUX used to multiplex the first level signals induces dead zone in the signal leading to degradation in the overall resolution.

#### 2.1.5 Reference Recycling TDC

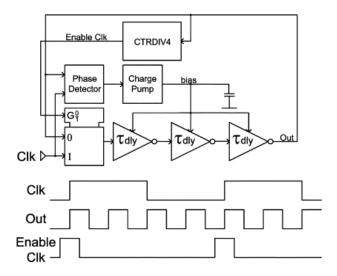

This technique overcomes the mismatch problem in long Vernier-delay-lines by employing short delay line and recycling the input pulse in the line many times as shown in Fig. 2.5 [17]. The signal, CLK, enters the delay line through the MUX, propagates through the delay line then the MUX recycles it again until another input pulse is applied. A DLL is used to adjust the total delay of the delay line such that the input clock period is integer multiple of the line's delay.

Fig. 2.4 Multistage TDC and its timing diagram.

Fig. 2.5 Reference recycling TDC [17].

Since the signal is recycled in the same delay line again and again, the layout is expected to be compact with reduced mismatch effect. In addition, this technique can be used concurrently with the LPI technique to improve the resolution.

## 2.1.6 Time Shrinking Delay Line TDC

In This technique single delay line digitizes the signal. The delay cells are designed such that the pulse shrinks while propagating through the line. The pulse also triggers flip flops connected to the delay element outputs and changes their state. As the pulse propagates through the line, the pulse width decreases until it vanishes. When the pulse vanishes, the remaining flip flops will not be triggered and its old state will be maintained indicating that the pulse vanished. The resolution in this technique depends on the shrinking of the pulse width when it propagates through one delay element. This allows a high resolution digitization of the input pulse. Similar to Vernier delay-linebased TDC, this technique suffers from the large latency [18].

#### 2.1.7 Pulse Stretching Converter

This technique improves the resolution of the conventional TDC by stretching the pulse then propagating it through the inverter chain delay line-based TDC. In this case the gain in the resolution is the stretching factor used to increase the pulse width. The stretching is performed by applying the input pulse to a CMOS switch that discharges a pre-charged capacitor with constant current until the pulse finishes. The capacitor is charged afterwards using smaller current. In this case the charging time will be proportional to the original pulse width and the proportionality factor, or the stretching factor, is the ratio between the discharging and charging currents. Unfortunately this technique leads to increased latency and poor DNL [19].

Table 2.1 summarizes the pros and cons of the aforementioned techniques. From the table it can be observed that there is a tradeoff between the resolution and the latency. Resolution defines the minimum time-step that the TDC can resolve while the latency limits the event rate of the input. In order to attain high resolution, the event rate will be sacrificed and vice versa. Consequently, the resolution and the bandwidth of the input should be compromised.

| TDC topology                    | Resolution | Latency  | Area            | Power    |

|---------------------------------|------------|----------|-----------------|----------|

| Inverter chain based TDC [8-11] | low        | low      | small           | small    |

| Vernier TDC [12-14]             | high       | large    | large           | large    |

| Local interpolation TDC [15]    | moderate   | low      | large           | small    |

| Multistage TDC [16]             | high       | moderate | moderate        | moderate |

| Reference recycling TDC [17]    | low        | low      | very<br>compact | small    |

| Time shrinking TDC [18]         | high       | large    | large           | large    |

| Pulse stretching TDC [19]       | moderate   | large    | large           | large    |

Table 2.1 Comparison of the different TDC techniques.

#### 2.2 TDC-Based ADC

The diagram in Fig. 2.6 (a) shows how a sinusoidal input of peak-to-peak amplitude of  $V_{pp}$  centered at  $V_{FS}/2$ , where  $V_{FS}$  is the full scale voltage, is digitized using time-mode circuits. The input signal is sampled-and-held at frequency  $f_s$  then a PWM block transforms the voltage-sample into a pulse-width which is digitized using the TDC. The transformation of the analog signal into the digital format is performed in the time-mode. The only part that is performed in voltage-mode is the pulse width modulation. In general, the same PWM design can be utilized as a front-end in time-mode systems to convert the signal from voltage-mode to time-mode prior to further processing.

Since the input signal is sampled at a frequency  $f_s$ , the zero-voltage input is mapped to a pulse width of  $T_s = 1/f_s$  while the full scale voltage input,  $V_{FS}$ , is mapped to a pulse of zero width. Consequently, the conversion gain of the PWM is given by

$$-T_s/V_{FS}$$

(s/V). Since the amplitude of the voltage-sample ranges from  $\frac{V_{FS}}{2}\left(1-\frac{V_{pp}}{V_{FS}}\right)$  to

$$\frac{V_{FS}}{2}\left(1+\frac{V_{pp}}{V_{FS}}\right), \text{ the width of the output pulse will range from } \frac{T_s}{2}\left(1+\frac{V_{pp}}{V_{FS}}\right) \text{to } \frac{T_s}{2}\left(1-\frac{V_{pp}}{V_{FS}}\right),$$

i.e. centered around  $T_s/2$ , as illustrated in Fig. 2.6 b) at points "B" and "A", respectively. Since the output pulse is symmetric and centered around  $T_s/2$ , the change in the outputpulse-width corresponding to the change of the input can be modeled as if there are two virtual sinusoids around  $T_s/2$ , as shown in Fig. 2.6 b) and the pulse width is modulated with the amplitude of the pulse. Such model will be useful when analyzing the effect of transistor mismatchs on the TDC performance. The amplitude of the PWM output pulse is  $V_{dd}$  in all cases but on Fig. 2.6 b) it is different, at points "A" and "B", just for clarity purposes. The output pulse is then digitized using a TDC.

A major issue that hinders the full utilization of the aforementioned time-mode ADC architecture is the trade off between the resolution of the TDC and both latency and dead-time. Latency, or the conversion time, is defined as the time the TDC requires after the signal is tracked till the digital output is available. The dead time is the minimum time required between two acquisitions. Both latency and dead time limit the maximum sampling frequency that can be used and, as a consequence, put an upper limit on the bandwidth of the ADC. On the other hand, the resolution is the minimum time step the TDC can resolve.

Fig. 2.6 a) Open-loop time-mode-based ADC. b) Timing diagram of the PWM.

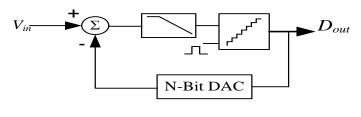

To achieve a high ADC dynamic range and a high signal-to-quantization-noiseratio (SQNR) a time-resolution of less than one gate delay may be required. This can be achieved using different techniques but will be at the expense of the latency and the dead time. Hence, the ADC bandwidth, which is limited by the latency, and SQNR, which is limited by the minimum time-resolution that the TDC can resolve, are compromised. To resolve this tradeoff, the concept of  $\Sigma\Delta$  modulator is adopted in time-mode designs [20]. Fig. 2.7 shows the analogy between the voltage-mode  $\Sigma\Delta$  modulator and its time-mode counterpart. The multi-bit quantizer and the multi-bit voltage-mode feedback DAC are replaced by a PWM and a modified TDC. The PWM transforms the input voltagesample into a pulse and the TDC generates a multi-bit digital output,  $D_{out}$ , that corresponds to the pulse-width and provides a time-quantized feedback pulse,  $p_q(t)$ which emulates the DAC output in traditional  $\Sigma\Delta$  modulators.

Owing to the over-sampling and noise shaping offered by the  $\Sigma \Delta$  loop architecture, the quantizer (TDC) is not required to have a number of levels in the order of the targeted SNR. On the other hand, the timing-accuracy of the feedback signal (the feedback pulse-width  $p_q(t)$ ) should be in the order of the targeted SNR or better. In other words, the error in the feedback signal  $p_q(t)$  should be less than a single bit as it will not be shaped by the loop filter. These two remarks can be mapped as specifications for the TDC as follows: First, the number of quantization steps of the TDC can be decreased compared to the open loop case, shown in Fig. 2.6 a), which means that we can use timequantization steps that are larger than one gate delay. That directly allows the use of TDC architectures with low latency and low dead-time. Thus, wide bandwidth ADC can be achieved. Second, the accuracy of the feedback signal, i.e. the width of the  $p_q(t)$ pulses, is proportional to the targeted SNR which puts a constrain on the DNL (timing mismatch) of the TDC steps. As a numerical example, assume a 10-bit ADC that is designed using the open loop architecture shown in Fig. 2.6 a). The time-quantization step of the TDC will be given by  $T_s/2^{10}$ . On the other hand if a third order  $\Sigma\Delta$  architecture with an over-sampling ratio (OSR) of 6 is used then the enhancement of the SQNR due to the loop filter is given by:

$$SQNR|_{\Sigma\Lambda} = 10\log\left(\frac{3(2L+1)M^{(2L+1)}}{2^{*}\pi^{2L}}\right) = 10\log\left(\frac{3^{*}7^{*}6^{7}}{2^{*}\pi^{6}}\right) = 34.86dB$$

(2.4)

Consequently, a 4.5 bits quantizer can be used to attain a 10-bits output. In other words, the time-quantization step of the quantizer can be as low as  $T_s/2^{4.5}$  which relaxes the resolution of the TDC.

On the other hand, the linearity of the feedback-pulse-width should be maintained higher than 10 bits which means that the DNL of the TDC should be better than 10 bits. In conclusion, by replacing the multi-bit voltage-mode feedback DAC by a TDC, the performance bottleneck is transformed to the timing-precision of the feedback pulse of the TDC,  $p_q(t)$ , rather than the absolute voltage levels of the DAC in a conventional voltage-mode  $\Sigma\Delta$  ADC. Since a reduced number of time-quantization steps is required compared to the open loop case, along with small latency to minimize the excess loop delay, inverter-chain-based TDC [8-11] is a suitable choice for time-mode based  $\Sigma\Delta$  modulators.

(a)

Fig. 2.7 Block diagrams of a) Voltage-mode  $\Sigma\Delta$  modulator. b) Time-mode  $\Sigma\Delta$  modulator.

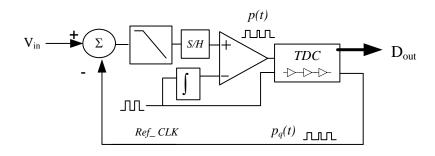

Fig. 2.8 shows how the time-quantized feedback pulse,  $p_q(t)$  is generated using an inverter-chain based TDC. The full scale input,  $[0, T_s]$ , is split, in time, into N timequantization steps using inverter-chain-based delay cells which is driven by the sampling clock. Assuming perfect matching between the delay cells, the time-quantization step  $T_Q$ is given by  $T_s/N$ . The edges of the time-quantized feedback pulse,  $p_q(t)$ , should be aligned to the edges of the delay cells outputs as shown in Fig. 2.8 b). Since the TDC directly drives the single-bit DAC, two relevant specifications are the signal-to-jitter ratio (SJR) of the feedback pulse and the maximum DNL of the TDC time-steps. Note that the 'signal' in this case corresponds to the pulse-width while the 'noise' corresponds to its jitter.

#### 2.2.1 Signal-to-Jitter Ratio (SJR)

Assuming a maximum input signal of  $-6dBFs (V_{pp} = V_{FS}/2)$ , where dBFs refers to the full scale input, and assuming that it is centered around  $V_{FS}/2$  and the PWM conversion gain is  $T_s/V_{FS}$  then the maximum feedback-pulse-width,  $p_{qmax}(t)$ , will be given by  $\frac{T_s}{2} \left[ 1 + \frac{V_{pp}}{V_{FS}} \right] = \frac{3T_s}{4}$  as shown in Fig. 2.8 b). Since the maximum pulse width corresponds to the peak-to-peak signal in the voltage domain, by analogy, its RMS value will be given by  $\frac{3T_s}{4} \cdot \frac{1}{2\sqrt{2}} = \frac{3T_s}{8\sqrt{2}}$ . Consequently, the signal-to-(pulse-width-jitter) ratio is given by:

is given by:

$$SJR = 10\log\left(\frac{\left(3T_s/8\sqrt{2}\right)^2}{\sigma_{j_-pw}^2}\right)$$

(2.5)

where  $\sigma_{j_{-pw}}$  is the standard deviation of the pulse-width jitter of the feedback pulse integrated over the frequency band of interest.

#### 2.2.2 DNL of TDC's Time Steps

If perfect matching between the delay cells in Fig. 2.8 b) is assumed, the DNL should be zero. Due to inevitable mismatches, the delay of the different steps will change introducing nonlinearities in the time-quantized feedback pulse  $p_q(t)$ . Since the input voltage-sample ranges from  $V_{FS}/4$  to  $3V_{FS}/4$  (assuming  $V_{pp} = V_{FS}/2$ ), the pulse width will change from  $T_s/4$ ,  $p_{qmin}(t)$ , to  $3T_s/4$ ,  $p_{qmax}(t)$ , as shown in Fig. 2.8 b). The

delay cells that are excited by the reference clock during the time intervals  $[0,T_s/8], [7T_s/8,T_s]$  will seldom interact with the output pulse width (black delay cells on Fig. 2.8 b)). Hence, their mismatch does not affect the performance.

Fig. 2.8 TDC-based  $\Sigma \Delta$  ADC: a) Block diagram. b) Timing diagram and  $p_q(t)$  generation.

On the other hand, the mismatch of the cells excited during the time interval  $[3T_s/8, 5T_s/8]$  (gray cells on the timing diagram) will contribute equally to all the pulse widths so their contribution will be transformed as offset in the pulse width rather than a harmonic distortion. Consequently, the time mismatches that contribute to THD are those of the cells who are active during the time intervals of  $[T_s/8, 3T_s/8]$  and  $[5T_s/8, 7T_s/8]$  (white cells on the timing diagram). Since the output pulse is symmetric and centered around  $T_s/2$  as shown in Fig. 2.6 b), in the following analysis a single side of the pulse-width will be considered then a 3 dB improvement in the THD will be included due to having the two sides at the output. Another observation is that the width of the time-quantized feedback pulse consists of the summation of the individual delays of the different delay cells where each delay cell represents one LSB. Consequently, the TDC can be considered as a time-mode thermometric DAC, where each delay cell corresponds to a time-mode 1-bit DAC. This observation will be useful when analyzing the harmonic distortion of the TDC.

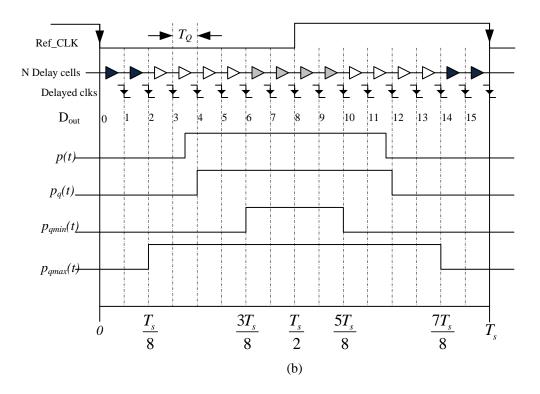

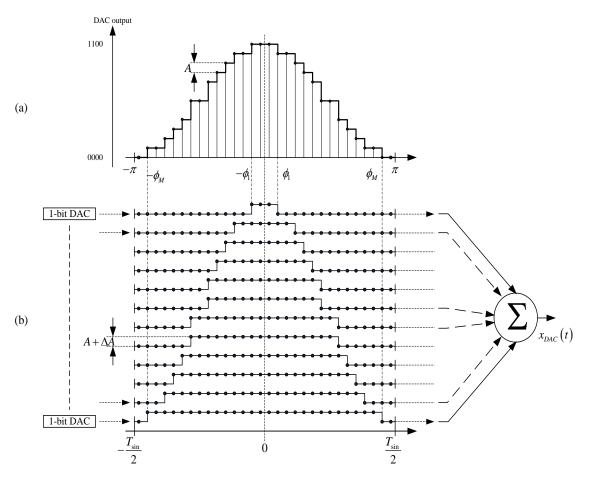

For simplicity of the harmonic distortion analysis, an M-level voltage-mode thermometric DAC consisting of M 1-bit DACs is considered then an analogy is performed to get the mismatch specification on the time-mode counterpart. Fig. 2.9 a) shows the output of an M-level (12-levels as an example) DAC for a one period of a digital sinusoidal signal of frequency  $\omega_{sin}$  with OSR of 15. Since the DAC architecture is a thermometric one, it can be represented as M 1-bit DACs followed by a summer as shown in Fig. 2.9 b). Each square wave signal, the outputs of the 1-bit DACs, can be expanded in terms of its harmonics using Fourier series:

$$x_{sq.(i)}(t) = \sum_{k=1}^{\infty} \frac{2}{\pi k} A \sin(k\phi_i) \cos(k\omega_o t)$$

(2.6)

where  $x_{sq.(i)}(t) = 1$  for  $|t| \le \frac{\phi_i}{\omega_{sin}}$ ,  $i = 1, ..., M$ ,  $0 < \phi_i < \pi$

Consequently, the M-level DAC output is given by the summation of the different square waves:

$$x_{DAC}(t) = \sum_{k=1}^{\infty} \left\{ \frac{2}{\pi k} \sum_{i=1}^{M} \left[ A \sin\left(k\phi_{i}\right) \right] \cos\left(k\omega_{o}t\right) \right\}$$

(2.7)

where *A* represents the step height in voltage-mode DAC, *k* is the harmonic index and  $\phi_i$  represents the phases of the different 1-bit signals.

To estimate the effect of the 1-bit DAC mismatches on the THD, a thirdharmonic-free and fifth-harmonic-free digital sinusoidal signal similar to the one shown in Fig. 2.9 a) is generated using the technique proposed in [21]. The condition to generate such input signal is

$$\sum_{i=1}^{M} \sin(k\phi_i) = 0 \text{ for } k = 3,5$$

(2.8)

If the above condition is satisfied, the third and fifth harmonics will vanish according to the equation of  $x_{DAC}(t)$  derived above in (2.7).

Fig. 2.9 M-Level feedback DAC: a) DAC output signal. b) Thermometric DAC architecture.

Assuming amplitudes mismatches in the different 1-bit DACs, the M-level DAC output, given in the ideal case by (2.7), will be given by

$$x_{DAC}(t) = \sum_{k=1}^{\infty} \left\{ \frac{2}{\pi k} \sum_{i=1}^{M} \left[ \left( A + \Delta A_i \right) \sin\left( k\phi_i \right) \right] \cos\left( k\omega_o t \right) \right\}$$

(2.9)

Thus, its third and fifth harmonic are no longer zero. The harmonic distortion of  $x_{DAC}(t)$  becomes:

$$HD_{k} = \frac{1}{k} \frac{\sum_{i=1}^{M} \left[ \left( 1 + \Delta A_{i} / A \right) \sin\left( k \phi_{i} \right) \right]}{\sum_{i=1}^{M} \left[ \left( 1 + \Delta A_{i} / A \right) \sin\left( \phi_{i} \right) \right]}$$

(2.10)

Since

$$\sum_{i=1}^{M} \sin(k\phi_i) = 0$$

for  $k = 3,5$  and  $\Delta A_i / A <<1$ , the expression can be simplified to

$HD_k \cong \frac{1}{Ak \sum_{i=1}^{M} \sin(\phi_i)} \sum_{i=1}^{M} \left[ \Delta A_i \sin(k\phi_i) \right], \quad k = 3,5$

(2.11)

Assuming a Gaussian distribution for the amplitude mismatches  $\Delta A_i$  with standard deviation  $\sigma_{\Delta A_i}$ , the distribution of  $HD_k$  will also be Gaussian with zero mean and standard deviation  $\sigma_{HD_k}$  as it is a summation of Gaussian distributions.

$$\sigma_{HD_k} = \frac{\sigma_{\Delta A_i}}{Ak \sum_{i=1}^{M} \sin(\phi_i)} \sqrt{\sum_{i=1}^{M} \sin^2(k\phi_i)}$$

(2.12)

For  $HD_k < B$ , then  $\sigma_{HD_k}$  should be < B/2 for a 95% yield ( $2\sigma$  on Gaussian distribution covers 95% of the area under the curve). Thus, the standard deviation of the mismatch will be given by:

$$\sigma_{\Delta A_i} < \frac{B}{2} Ak \frac{\sum_{i=1}^{M} \sin(\phi_i)}{\sqrt{\sum_{i=1}^{M} \sin^2(k\phi_i)}}$$

(2.13)

Consequently, once the system level simulations of the  $\Sigma\Delta$  modulator is performed and the maximum distortion of the DAC, *B*, and the time-quantization step in the TDC,  $T_Q$ which corresponds to *A* in voltage-mode DACs, are specified, both can be plugged in the above equation to obtain the maximum tolerable mismatch between the different timesteps which corresponds to the DNL of the TDC.

#### 2.3 System Level Design

The design of a TDC for the time-mode based  $\Sigma \Delta ADC$  requires system level simulations for the  $\Sigma\Delta$  modulator in order to extract the TDC specifications. System level simulations for the  $\Sigma\Delta$  modulator were performed targeting 10+ bits resolution over a bandwidth of 100kHz to 20MHz [20]. An OSR of 6.25 is used which corresponds to a sampling rate of 250MHz (sampling period  $T_s$ =4nsec). The signal-to-noise ratio of the TDC and its digital output buffer should be better than 72dB over the signal bandwidth. The TDC is required to have 50 quantization steps which correspond to a step size of 80ps. Since  $T_s$  is 4nsec, the standard deviation of the jitter of the timequantized feedback pulse width,  $\sigma_{_{_{i-pw}}}$ , must be kept less than 266fs for SJR >72dB according to equation (2.5). Finally, targeting 65dB THD assuming -3dBFs input implies a standard deviation of the delay of the different TDC steps of around 480fs according to equation (2.13) with  $\pm 40$  fs variations depending on the choice of the harmonic-free digital input signal (the choice of  $\phi_i$ ). However, system level simulations of the  $\Sigma \Delta$ modulator along with the TDC model indicate that the mismatch specifications can be relaxed to be around 800fs for a -3dBFs input.

The TDC in  $\Sigma\Delta$  modulator performs two main functions. First, it identifies the position of the rising and falling edges of the PWM signal with respect to the falling

edge of the PWM reference clock. Second, it emulates the multi-bit DAC operation by providing a time-quantized feedback pulse  $p_q(t)$ . Fig. 2.8 shows the timing diagram of a 16-level TDC-based  $\Sigma\Delta$  modulator. The TDC delivers the code representing the position of the rising and falling edges of the PWM signal, 4 and 12 on the diagram, and provides a time-quantized feedback pulse  $p_q(t)$  whose edges are aligned to the time-quantization steps as shown in Fig. 2.8 b). Some modifications are required for the TDC to generate the code with respect to the falling edge of the reference clock and to generate  $p_q(t)$ .

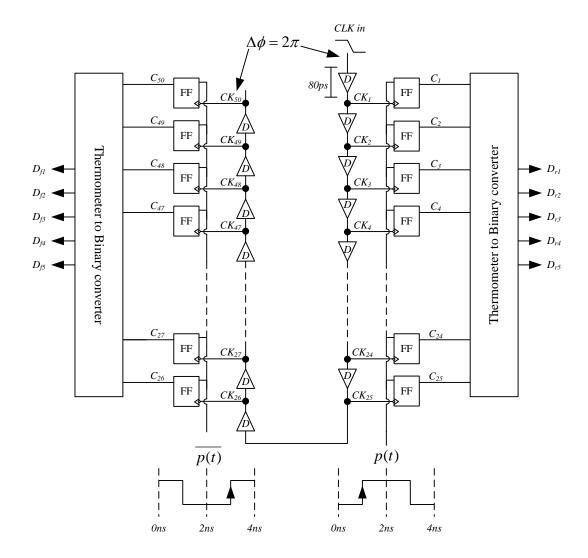

Fig. 2.10 shows the block diagram of the output code generation part of the TDC. A 50-cell inverter-based delay line is employed whose first half captures the rising edge of the input pulse while the second half captures its falling counterpart. The input signal, p(t), is applied to the inputs of the flip flops while the falling edge of the clock is applied to the delay line. As the clock propagates through the digital delay line it triggers the flip flops sequentially in 80ps steps to capture the input pulse in a thermometric fashion. To maintain the symmetry of the design, p(t) is inverted before being applied to the flip flops of the second half of the TDC such that the second set of flip flops captures the rising edge of  $\overline{p(t)}$ . A thermometer-to-binary converter is used to encode the thermometric output before it is further processed. Since the timing-precision of the feedback pulse,  $p_q(t)$ , is critical, the feedback-pulse-generation block must fulfill very demanding specifications. First, the width of the feedback pulse should be minimized to have minimum effect on the excess loop delay of the  $\Sigma\Delta$  loop. Third, the delay must be

constant to avoid data-dependent delay which distorts the signal. Finally, the jitter of the feedback pulse should be minimized to fulfill the targeted SNR of the system since the jitter is reflected as noise in the ADC output spectrum.

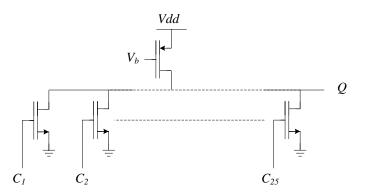

Since the flip flops in Fig. 2.10 are clocked through the delay elements, its outputs are aligned to the delay element outputs which are 80ps apart. The rising and falling edges of the feedback pulse can be generated by applying the *OR* operator on the first and second 25-outputs sets of the flip flops ( $C_1$  through  $C_{25}$  and  $C_{26}$  through  $C_{50}$ ) respectively. In this case the feedback pulse edges are aligned to the delay-element-output edges with one flip flop and *OR* gate delay. To ensure uniform delay from all inputs, ( $C_1$  through  $C_{25}$  and  $C_{26}$  through  $C_{50}$ ), to the output of the *OR* gate, the wired-NOR structure shown in Fig. 2.11 is used to generate the quantized signal  $p_q(t)$ .

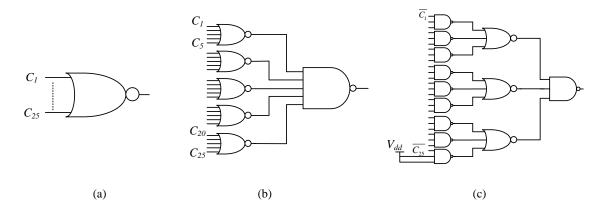

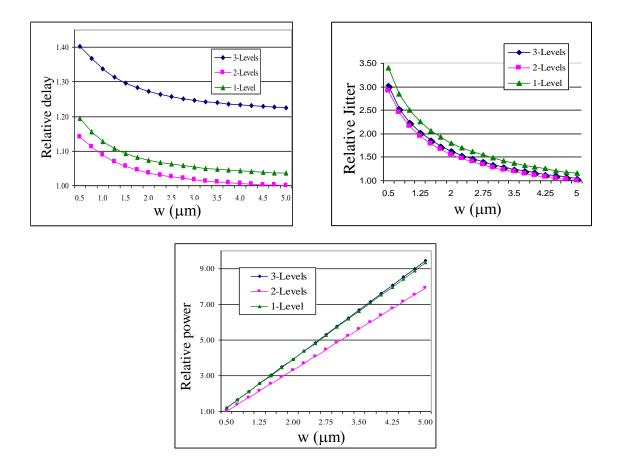

Many techniques can be used to implement 25-inputs *OR* operation in wiredstructure. The simplest one is to use a single *NOR* gate with 25 inputs as shown in Fig. 2.12 a). Other techniques are to use 2-levels or 3-levels *OR* operation as shown in Fig. 2.12 b) and c), respectively. The 2-level *OR* is implemented using *NOR-NAND* structure while the 3-level *OR* is implemented using *NAND-NOR-NAND* structures. Three factors should be considered when choosing the optimum *OR* implementation: delay, jitter and power consumption. For a fair comparison of these factors, all transistors are assumed to have the same current driving capability (charging/discharging currents are the same for all of them).

Fig. 2.10 Block diagram of the output code generation of the TDC (left side captures p(t) falling edge while the right side captures the rising edge).

The delay of digital circuit is roughly estimated by (Vdd/I)Cload where I is the current driving capability of the transistor. Since the design in Fig. 2.12 b) consists of two levels and in Fig. 2.12 c) consists of three levels, the corresponding delays of the three designs are approximately estimated to be:

$$t_{d1} = \frac{V_{dd}}{I} \left( 25C_{gdn} + C_{gdp} + C_{gg} \right) \approx \frac{V_{dd}}{I} C_{gd} \left( 26 + \frac{C_{gg}}{C_{gd}} \right)$$

$$t_{d2} = \frac{V_{dd}}{I} \left( 5C_{gd(n/p)} + C_{gd(p/n)} + C_{gg} \right) \approx 2 \approx \frac{V_{dd}}{I} C_{gd} \left( 12 + 2 * \frac{C_{gg}}{C_{gd}} \right)$$

$$t_{d3} = \frac{V_{dd}}{I} \left( 3C_{gd(n/p)} + C_{gd(p/n)} + C_{gg} \right) \approx 3 \approx \frac{V_{dd}}{I} C_{gd} \left( 12 + 3 * \frac{C_{gg}}{C_{gd}} \right)$$

(2.14)

where  $C_{gd}$  is the drain capacitance of the input and load transistors (assuming  $C_{gdp} = C_{gdn}$ ) and  $C_{gg}$  is the gate capacitance of the next stage. It can be observed that  $t_{d2}$  is always less than  $t_{d3}$  and is less than  $t_{d1}$  as long as  $C_{gg} < 14C_{gd}$ . From the power consumption point of view, the second design consumes minimum power as it achieves the least time delay and *I* is the same for the three designs.

Fig. 2.11Uniform-delay wired-Nor architecture for the feedback pulse,  $p_q(t)$  generation.

For the jitter analysis we assume that all transistors approximately have equal voltage-noise with standard deviation  $\sigma_n$ . The timing jitter is related to the voltage noise through the slew rate as follows:

$$J = \frac{v_n}{SR} = t_d \left(\frac{v_n}{\Delta V}\right)$$

(2.15)

Since the jitter is proportional to the delay, it is proportional to the load capacitance as follows:

$$J_{1}\alpha\left(26 + \frac{C_{gg}}{C_{gd}}\right), J_{2}\alpha\sqrt{2}*\left(6 + \frac{C_{gg}}{C_{gd}}\right), J_{3}\alpha\sqrt{3}*\left(4 + \frac{C_{gg}}{C_{gd}}\right)$$

(2.16)

From the above equations, it is clear that the jitter of the three designs depend on the ratio between gate-source capacitance and gate-drain capacitance.

Since the aforementioned analyses are approximate, transistor level simulations were performed to confirm that the quantitative analysis matches the trend of simulations. Fig. 2.13 shows the relative delay, jitter and power consumption of the three designs versus transistor width. It is clear that the 2-level architecture provides the best performance.

Fig. 2.12 Block diagram of the different architectures for implementing 25 inputs *OR* gate of Fig. 6.a) 1-Level *OR* gate. b) 2-Levels *OR* gate. c) 3-Levels *OR* gate.

## 2.4 Transistor Level Implementation

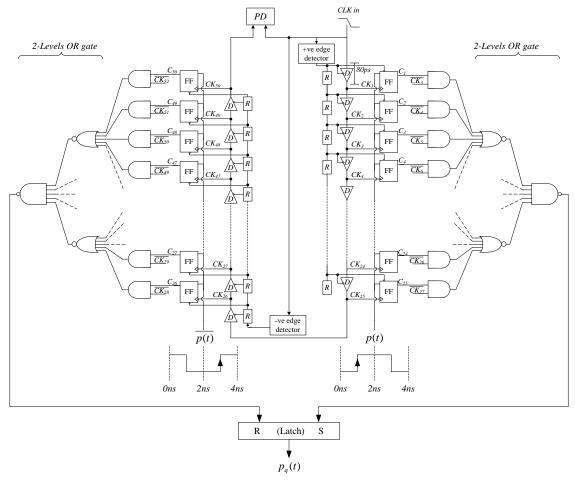

Fig. 2.14 shows the block diagram of the TDC with the feedback pulse generator. As shown in the figure, the TDC can be conceptually split into two main parts: one for the generation of output codes that correspond to the rising and falling edges of the input signals and a second part that generates the time-quantized rising and falling edges of the feedback pulse. The TDC block consists of six sub-blocks: delay cells (D), flip-flop (FF), 2-levels OR gate, SR latch and reset unit (R). In addition, a phase detector (PD) is used to adjust the total delay of the line to be 4ns The main design specifications are the timing jitter of the feedback pulse width and the timing mismatches of the time-quantized steps. In the following sections the implementation of the different blocks will be addressed such that the mismatch and jitter specifications are fulfilled.

## 2.4.1 Delay Cell

The bottleneck of the TDC is its jitter and mismatch performance. The jitter includes the jitter of the delay line (50 delay cells), 2-level *OR* gate, *SR* latch, feedback buffer and supply noise. On the other hand, the mismatch of the different delay elements is mapped as a distortion in the output spectrum.

As stated in section 2.3, 800fs of timing-mismatch/DNL of the delay cell and the *OR* gate is required to attain THD better than 65dB. This mismatch includes process variations, systematic design mismatch, periodic noise from the supply and metastability or data dependent delay. For critical sections, transistors' length is set as double the minimum length of the process to reduce the effect of PVT variations. Monte Carlo

simulations were used to provide a lower limit on the width such that the variation in the unit time-step is less than the targeted DNL.

Fig. 2.13 Relative jitter of the different OR gate architectures versus transistor's width.

Transistor's noise can be decreased by increasing the width of the transistor. By doubling the transistor width, a 3dB is gained in the noise as well as the timing-jitter. Unfortunately, the power consumption also doubles due to the increased capacitance in the circuit. In addition, *SR* does not improve significantly as both the driving capability of the transistor as well as the capacitive loading double. Moreover, increasing the power

consumption increases the supply noise and affects the timing precision of the neighboring circuits ending up with a degraded overall performance.

Fig. 2.14 Block diagram of the TDC with the feedback pulse generator  $(p_q(t))$ .

To overcome these drawbacks, innovative circuit techniques are employed to maintain the jitter within the required specifications. Assuming an *N*-inverters delay line and assuming uncorrelated noise sources, the total jitter of the line is given by:

$$J = \sqrt{N} \frac{v_n}{SR}$$

(2.17)

By increasing the *SR* by a factor *m* the number of required inverters to produce the same total delay will roughly increase by the same factor leading to:

$$J = \sqrt{N} \frac{v_n}{SR} \Longrightarrow J_{new} = \sqrt{mN} \frac{v_n}{SR^*m} = \frac{1}{\sqrt{m}} \left(\sqrt{N} \frac{v_n}{SR}\right)$$

(2.18)

As a rule of thumb, increasing the SR of the transitions by a factor m improves the jitter per unit delay by a factor  $\sqrt{m}$ . For example, having 8 transitions within 80ps provides 30% less jitter compared to having 4 transitions only. To increase the SR without doubling the width of the transistor, dynamic logic techniques are used. A dynamiclogic-based delay-cell is shown in Fig. 2.15 a). The main advantage of dynamic logic is that the driver transistor drives one load transistor instead of two. Theoretically the slew rate is improved by a factor of two and the number of stages is doubled per unit delay compared to the static CMOS delay line. Although the number of stages doubled, the power consumption will slightly increase as the pre-charging/pre-discharging transistors are designed using minimum length. For example, if  $L=2L_{min}$  is used for matching purposes in the static CMOS delay line, the same length can be used in the signal path in the dynamic-logic-based cell while the pre-charging/pre-discharging transistors are designed using  $L_{min}$ . Thus, their width is also divided by two without losing their current driving capability. Consequently, the total capacitance of the delay line, as well as the power consumption, increases by 25% only per unit delay compared to the static CMOS delay line.

Fig. 2.15 Dynamic-logic-based delay cell (D) a) Transistor level implementation. b) Timing diagram.

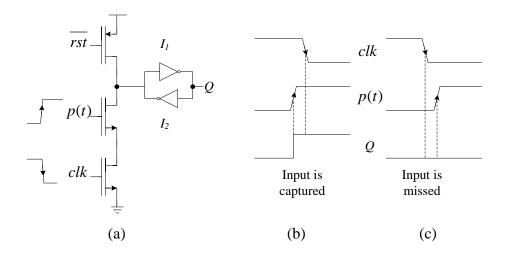

## 2.4.2 Flip Flop

Fig. 2.16 a) shows the dynamic-logic implementation of the flip flop while Fig. 2.16 b) and c) shows two timing diagrams in case of capturing/missing the data. The input signal, p(t), is normally low while the *CLK* is normally high. If the CLK falling edge leads p(t) as shown in Fig. 2.16 c) the output will not change. However, if the

rising edge of p(t) leads the falling edge of the CLK as shown in Fig. 2.16 b) the output node discharges and the flip flop captures the data. Static inverters,  $I_1$  and  $I_2$ , are designed to be unbalanced such that the transition of the output, Q, from low to high is enhanced.

Since the timing-precision of the feedback pulse is required to be better than 0.8ps, the metastability of the flip flop should be within that limit which is impractical. To overcome this problem, the output of the flip flop, that is triggered by  $CLK_n$ , is gated by another clock,  $\overline{CLK_{n+2}}$ , to leave time for the flip flop output to settle as shown in Fig. 2.14. In this case the flip flop output edges are still aligned to the outputs of the delay elements but the feedback pulse will be delayed by two time steps, 160ps, which adds to the total excess loop delay. To minimize the additional loop delay due to the *AND* stage, the *AND* gate is embedded in the two-levels *OR* gate.

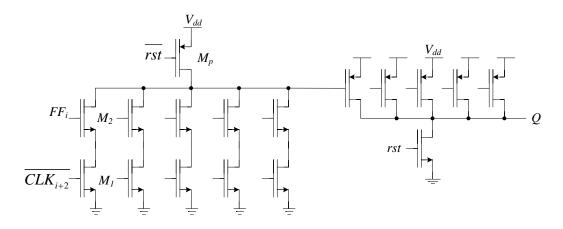

## 2.4.3 2-Levels OR Gate

The two-levels *OR* gate is implemented using a modified *NOR-NAND* structure to include the *AND* operation that gates the flip flop outputs as shown in Fig. 2.17. Dynamic logic ensures uniform and minimum delay for the different inputs. Transistor  $M_1$  acts as an *AND* gate while  $M_2$  is driven by the flip flop output. Five of such branches are connected in parallel to implement the 5-input *NOR* gate. The second level *NAND* gate is implemented using five *PMOS* transistors in parallel to ensure uniform delay.

Fig. 2.16 Dynamic-logic-based flip flop (*FF*). a) Transistor level implementation. b) Timing diagram when the input is captured. c) Timing diagram when the input is missed.

Since the delay of the FF depends on the time difference between the rising edge of the FF input and the falling edge of the clock, under certain conditions the FF output will change from low to high while setting in more than 160ps leading to a data dependent delay at the output of the OR gate. Simulation results indicate that such condition happens when the time difference between the FF input and the clock edge is within 40fs. Consequently, the SNR due to metastability, assuming a maximum input signal of -5dBFs is given by:

$$SNR = 20 \log \left( \frac{4ns}{2\sqrt{2} * 40 fs} \right) - 5 = 86 dB$$

(2.19)

where 4ns is the full scale of the TDC.

MonteCarlo simulations were used to provide the minimum limit on the transistor sizes such that DNL specifications are fulfilled. Simulations indicate that the

variations in the time step due to transistor mismatch in the different paths including the delay cell are around 0.78ps which fulfills the DNL specifications. A 1.2V supply was used in the design of the circuit.

Fig. 2.17 Dynamic-logic-based OR gate.

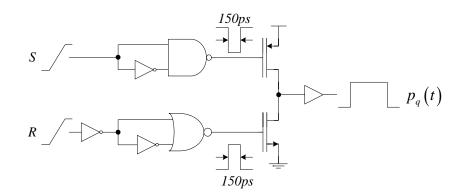

## 2.4.4 SR Latch

*SR* latch provides the feedback pulse of the *ADC*. Fig. 2.18 shows the block diagram of the circuit. The *set* input is driven by the *OR* gate of the first half of the TDC which detects the rising edge of the input signal while the *reset* input is driven by the *OR* gate of the second half that detects the falling edge. An edge detector detects the *set/reset* signals and generates a 150ps pulse that charges/discharges the high impedance output node to generate the feedback pulse. The output node is buffered using a static CMOS inverter to eliminate the leakage effect of the high impedance node.

#### 2.4.5 Reset Unit

The reset cell provides the reset signals to the dynamic-logic circuits. The TDC is split into two halves, one that handles the rising edge of the input pulse and one that handles its falling counterpart. Employing the fact that the two halves do not operate at the same time, the reset signal can be applied to the second half while the first half is handling the rising edge and vice versa as shown in Fig. 2.19. To prevent large instantaneous supply currents, the reset signal is applied sequentially to the 25 cells of each branch incorporating a static minimum-size delay-line as shown in Fig. 2.14.

Fig. 2.18 SR latch for the feedback pulse generation.

## 2.4.6 Calibration Circuit

Since the TDC is a time-mode circuit, it requires calibration in order to ensure that the total delay of the delay line is 4ns regardless of PVT variations. The delay is controlled through a voltage regulator that adjusts the supply voltage of the delay line. Fig. 2.20 shows the block diagram of the phase detector that detects the phase difference between the input and output clocks of the TDC. The input and the output clocks of the delay line are passed through two flip flops in order to ensure a 50% duty cycle then three NAND gates are used to implement XOR function. The outputs of the first two NAND gates indicate either the output clock is leading or lagging the input clock. The output of the XOR gate is used to discharge a high impedance node, Q, forcing it to toggle as long as the delay is not calibrated. The output is then divided by two in order to have a 50% duty cycle if the delay of the line is not 4ns. Simulations indicate that the accuracy of calibration is  $\pm 30$ ps which means that the gain error of each conversion level is less than  $\pm 600$  fs.

Fig. 2.19 Block diagram of the reset architecture of the TDC.

Fig. 2.20 Block diagram of the phase detector.

#### 2.5 Jitter and Data Dependent Delay

The clock and delay line jitter are mapped as noise floor in the ADC output spectrum and are required to be limited to 266fs as stated in section 2.3. The worst case jitter happens with a full scale input signal. In this case the rising edge is captured by the first stages of the TDC while the falling edge is captured by the very last stages. Consequently, the jitter of the 50 cells of the delay line affects the pulse width. On the other hand, the jitter of the *OR* gate, *SR* latch and the output buffer will affect both rising and falling edges. Simulation results indicate that the integrated jitter of the 50-cell delay line is around 160fs while the *OR* gate, *SR* latch and feedback buffer contribute with 90fs. Hence, the worst case RMS jitter is given by:

$$J_{tot} = \sqrt{J_{Delay\_line}^2 + \left(\sqrt{2} * J_{OR\_SR\_buf}\right)^2} = \sqrt{160^2 + \left(90\sqrt{2}\right)^2} = 205 fs$$

(2.20)

This timing jitter meets the system specs and leaves a margin for supply-induced jitter and noise injected from the substrate.

The second major issue in time-mode analog systems is the data-dependent delay, which is a variation in the time-quantized feedback pulse-width depending on the timing of the input signal. One cause of this phenomenon is the flip flop metastability. Another source of data-dependent delay is due to the use of dynamic logic gates. Feed-through from nearby switching circuits affect the high impedance nodes causing its output voltage to change. To overcome such problem, it is required to use static CMOS circuits to buffer the critical high impedance nodes. One example of this problem occurs when the flip flop outputs toggle and the switching feeds through to the high impedance nodes of the delay elements as shown in Fig. 2.21. When the flip flop output changes from low to high, the signal passes through the gate-source capacitance of  $M_2$  of the OR gate then through the drain-gate capacitance of  $M_1$ . Since the gate of  $M_1$  is a high impedance node, the voltage on the capacitance connected to this node changes its switching time by  $\Delta t_{cell}$ when the clock reaches this stage in the delay line. Consequently, if the rising edge of the input data happens at code  $C_{data}$ , the delay of the next (25- $C_{data}$ ) delay cells will change by: