# CALIBRATED CONTINUOUS-TIME SIGMA-DELTA MODULATORS

A Dissertation

by

CHO-YING LU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2010

Major Subject: Electrical Engineering

## CALIBRATED CONTINUOUS-TIME SIGMA-DELTA MODULATORS

### A Dissertation

by

## **CHO-YING LU**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

# Approved by:

Chair of Committee, Jose Silva-Martinez Committee Members, Aydin Karsilayan

Kai Chang

Alexander Parlos

Head of Department, Costas Georghiades

May 2010

Major Subject: Electrical Engineering

#### **ABSTRACT**

Calibrated Continuous-Time Sigma-Delta Modulators. (May 2010)

Cho-Ying Lu,

B.A., National Tsing Hua University, Taiwan;

M.S., National Tsing Hua University, Taiwan

Chair of Advisory Committee: Dr. Jose Silva-Martinez

To provide more information mobility, many wireless communication systems such as WCDMA and EDGE in phone systems, bluetooth and WIMAX in communication networks have been recently developed. Recent efforts have been made to build the all-in-one next generation device which integrates a large number of wireless services into a single receiving path in order to raise the competitiveness of the device. Among all the receiver architectures, the high-IF receiver presents several unique properties for the next generation receiver by digitalizing the signal at the intermediate frequency around a few hundred MHz. In this architecture, the modulation/demodulation schemes, protocols, equalization, etc., are all determined in a software platform that runs in the digital signal processor (DSP) or FPGA. The specifications for most of front-end building blocks are relaxed, except the analog-to-digital converter (ADC). The requirements of large bandwidth, high operational frequency and high resolution make the design of the ADC very challenging.

Solving the bottleneck associated with the high-IF receiver architecture is a major focus of many ongoing research efforts. In this work, a 6<sup>th</sup>-order bandpass continuous-

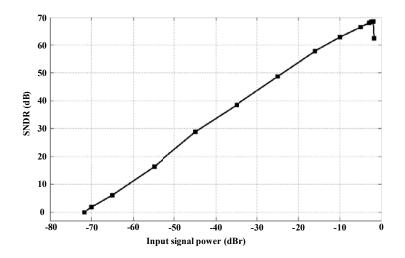

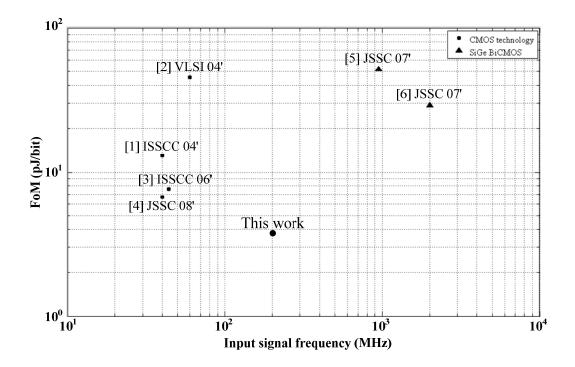

time sigma-delta ADC with measured 68.4dB SNDR at 10MHz bandwidth to accommodate video applications is proposed. Tuned at 200 MHz, the fs/4 architecture employs an 800 MHz clock frequency. By making use of a unique software-based calibration scheme together with the tuning properties of the bandpass filters developed under the umbrella of this project, the ADC performance is optimized automatically to fulfill all requirements for the high-IF architecture.

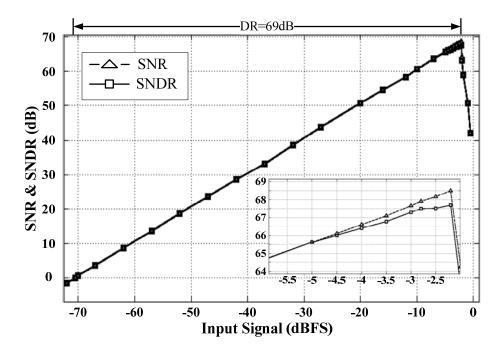

In a separate project, other critical design issues for continuous-time sigma-delta ADCs are addressed, especially the issues related to unit current source mismatches in multi-level DACs as well as excess loop delays that may cause loop instability. The reported solutions are revisited to find more efficient architectures. The aforementioned techniques are used for the design of a 25MHz bandwidth lowpass continuous-time sigma-delta modulator with time-domain two-step 3-bit quantizer and DAC for WiMAX applications. The prototype is designed by employing a level-to-pulse-width modulation (PWM) converter followed by a single-level DAC in the feedback path to translate the typical digital codes into PWM signals with the proposed pulse arrangement. Therefore, the non-linearity issue from current source mismatch in multi-level DACs is prevented. The jitter behavior and timing mismatch issue of the proposed time-based methods are fully analyzed. The measurement results of a chip prototype achieving 67.7dB peak SNDR and 78dB SFDR in 25MHz bandwidth properly demonstrate the design concepts and effectiveness of time-based quantization and feedback.

Both continuous-time sigma-delta ADCs were fabricated in mainstream CMOS 0.18um technologies, which are the most popular in today's consumer electronics industry.

# **DEDICATION**

# To my parents

To my dearest wife, Jihying Chang, and daughter, Ariel Lu

#### **ACKNOWLEDGEMENTS**

In coming to the final stage of my graduate studies, all my successful work reflects the relationships with many inspiring and gracious people I met during these years. I would like to contribute my thanks to all your priceless support.

First of all, I want to express my sincere appreciation to my advisor, Dr. Silva-Martinez, who is a generous mentor and inspiration. Without his endless support and encouragement, this dissertation would not have been possible. By sharing his strong knowledge in analog circuit design and showing me the appropriate attitude when doing research, he taught me how to be a scholar, an engineer, and a teacher. I will always remember his supervision and have him as an example, no matter in technical aspect or his personality.

I want to thank Dr. Aydin Karsilayan, Dr. Kai Chang, and Dr. Alexander Parlos for serving as my committee members and for their invaluable comments and suggestions to my research and my dissertation. The guidance and encouragement from Dr. Kai Chang assisted me a lot in planning my future career.

I would like to thank Dr. Edgar Sanchez-Sinencio and Dr. Sebastian Hoyos, instructors of in classes taken at Texas A&M University. Dr. Edgar Sanchez-Sinencio, the director of Analog and Mixed Signal center, enriches my knowledge and widens my perspective on analog circuit design in his classes. By teaching the class of analog-to-digital converter, my research topic, Dr. Sebastian Hoyos taught me all the required concepts of the circuit. He also spent his time reading my draft of a journal paper and gave me suggestions. Special mention and thanks goes to Dr. Peng Li, the instructor of

my first class at Texas A&M University. His encouragement relaxed my nervous feeling and gave me the confidence in my first semester studying in a foreign country.

I would like to thank Fabian Silva-Rivas, Praveena Kode, Marvin Onabajo, Venkata Gadde, Hsien-Pu Chen, Yung-Chung Lo, and Vijayaramalingam Periasamy, the colleagues cooperating with me in both my research projects. The contribution and inspiration from them helped me finishing my work and made the research a great and joyful learning experience. With their sharing of the cultures of different countries, I expanded my global view of the world and know how to work with the people from different countries without any misunderstanding. Special thanks to the secretary of the AMSC group, Ms. Ella Gallagher, for her kind help.

I would like to thank my mentor, Irene Deng, for her guidance and discussions during my internship at Texas Instruments. By teaching me how to build a career path in a company as an engineer, her suggestions will definitely help me be successful in my future career. I want to thank my colleague, Meng-Chang Lee. During my internship, he helped me a lot, not only in technical issues, but also my personal life in Dallas.

I would like to thank my friends, Hsien-Yun Hsu, Jiun-Yu Wu and Peter Yu, at Texas A&M University. Without their enrichment to my extracurricular life in this small town, it would be very difficult to release the pressure from the research.

Finally, I want to express my appreciation to my parents for their invaluable love and support and my wife, Jihying Chang, for always being my side with her unconditional love and for giving me the encouragement and motivation to make it through all the hard times during these years.

# TABLE OF CONTENTS

| ABSTRACT    | Γ                                                      |

|-------------|--------------------------------------------------------|

| DEDICATIO   | ON                                                     |

| ACKNOWL     | EDGEMENTS                                              |

| TABLE OF    | CONTENTS                                               |

| LIST OF FIG | GURES                                                  |

| LIST OF TA  | BLES                                                   |

| CHAPTER     |                                                        |

| I           | INTRODUCTION                                           |

|             | 1.1 Motivation                                         |

|             | 1.2 Research Contribution                              |

|             | 1.3 Dissertation Organization                          |

| II          | THE BOTTLENECK OF THE NEXT GENERATION                  |

|             | RECEIVERS: ANALOG-TO-DIGITAL CONVERTER                 |

|             | 2.1 Next Generation Receivers                          |

|             | 2.2 Common Receiver Architectures for Wireless         |

|             | Communication                                          |

|             | 2.3 Analog-to-Digital Converter (ADC)                  |

|             | 2.4 Conclusion                                         |

| III         | OVERSAMPLING ΣΔ ADC                                    |

|             | 3.1 Oversampling ΣΔ ADC                                |

|             | 3.2 Design Issues of A Continuous-Time ΣΔ ADC          |

|             | 3.3 Design Flow of A $\Sigma\Delta$ ADC                |

|             | 3.4 Literature Survey                                  |

| IV          | A SELF-CALIBRATED 6TH-ORDER 200MHZ IF BANDPASS         |

|             | ΣΔ MODULATOR WITH OVER 68DB SNDR IN 10MHZ<br>BANDWIDTH |

|             |                                                        |

|             | 4.1 Introduction                                       |

|       | 4.2 System Planning                                          |

|-------|--------------------------------------------------------------|

|       | 4.3 Circuit Implementation of critical blocks                |

|       | 4.4 Software-Based Calibration                               |

|       | 4.5 Experimental Results                                     |

|       | 4.6 Conclusion                                               |

|       | 4.7 Appendix A: Distortion Analysis of The Basic Closed-Loop |

|       | System                                                       |

|       | 4.8 Appendix B: System Simulation in Simulink                |

| V     | A 25MHZ BANDWIDTH 5TH-ORDER CONTINUOUS-TIME                  |

|       | LOWPASS SIGMA-DELTA MODULATOR WITH 67.7DB SNDR               |

|       | INTRODUCTION                                                 |

|       | 5.1 Introduction                                             |

|       | 5.2 System Planning                                          |

|       | 5.3 Level-to-PWM Converter                                   |

|       | 5.4 Complementary Injection-Locked Frequency Divider         |

|       | 5.5 3-Bit Two-Step Current-Mode Quantizer                    |

|       | 5.6 Circuit Implementation                                   |

|       | 5.7 Measurement Results                                      |

|       | 5.8 Conclusion                                               |

|       | 5.9 Appendix: Non-Linearity Analysis of Device Mismatch in   |

|       | The Proposed PWM Pulses                                      |

| VI    | CONCLUSION                                                   |

| DENIC | ES                                                           |

# LIST OF FIGURES

|            |                                                                                          | F |  |

|------------|------------------------------------------------------------------------------------------|---|--|

| Fig. 2.1.  | A next generation wireless device supporting multiple<br>Services                        |   |  |

| Fig. 2.2.  | The band distribution of different services.                                             |   |  |

| Fig. 2.3.  | The superheterodyne architecture of a receiver                                           |   |  |

| Fig. 2.4.  | The low-IF architecture of a receiver                                                    |   |  |

| Fig. 2.5.  | The direct conversion of a receiver                                                      |   |  |

| Fig. 2.6.  | The high-IF architecture of a receiver                                                   |   |  |

| Fig. 2.7.  | The software radio architecture of a receiver                                            |   |  |

| Fig. 2.8.  | The basic concept of an ADC                                                              |   |  |

| Fig. 2.9.  | The performance distribution of the Nyquist ADCs                                         |   |  |

| Fig. 2.10. | The quantization error distribution in frequency spectra                                 |   |  |

| Fig. 2.11. | Critical performance of an ADC                                                           |   |  |

| Fig. 2.12. | The power spectrum of a bandpass $\Sigma\Delta$ ADC                                      |   |  |

| Fig. 2.13. | The MIMO high-IF receiver architecture                                                   |   |  |

| Fig. 3.1.  | The operation of the traditional n-bit ADC                                               |   |  |

| Fig. 3.2.  | The system of the $\Sigma\Delta$ ADC                                                     |   |  |

| Fig. 3.3.  | The NTF and STF of the lowpass $\Sigma\Delta$ ADC with an ideal second order loop filter |   |  |

| Fig. 3.4.  | The effect of the system coefficients to the output quantization noise                   |   |  |

| Fig. 3.5.  | Block diagrams of two different sigma-delta ADCs                                         |   |  |

| Fig. 3.6.  | The aliasing effect of the sampling and hold circuit                                     |   |  |

| Fig. 3.7.  | Two different architectures of loop filter in $\Sigma\Delta$ ADC                         |   |  |

|            |                                                                                                  | Page |

|------------|--------------------------------------------------------------------------------------------------|------|

| Fig. 3.8.  | The comparison of STFs in CRFF and CRFB architectures                                            | 33   |

| Fig. 3.9.  | The architecture of a DT MASH $\Sigma\Delta$ ADC                                                 | 34   |

| Fig. 3.10. | Common DAC pulses                                                                                | 37   |

| Fig. 3.11. | A 2nd-order $\Sigma\Delta$ ADC with approximated quantizer model                                 | 39   |

| Fig. 3.12. | The phase portrait of a 2nd-order $\Sigma\Delta$ ADC                                             | 40   |

| Fig. 3.13. | The model of the non-lineairties from loop filter in a $\Sigma\Delta$ ADC                        | 41   |

| Fig. 3.14. | The model of the distortions from DAC in a $\Sigma\Delta$ ADC                                    | 43   |

| Fig. 3.15. | The source of device mismatch and the effect on the resolution of a 2-bit $\Sigma\Delta$ ADC.    | 43   |

| Fig. 3.16. | Four general different schemes to randomize or shape the Mismatch                                | 44   |

| Fig. 3.17. | The jitter effect on a square waveform.                                                          | 46   |

| Fig. 3.18. | The SJNR comparison between the systems with different sampling frequencies                      | 47   |

| Fig. 3.19. | The block diagram of a 6th-order single-bit $\Sigma\Delta$ ADC                                   | 49   |

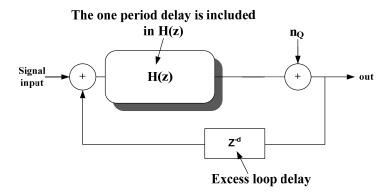

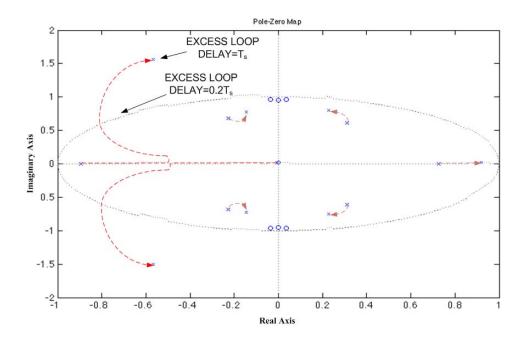

| Fig. 3.20. | The root locus of NTF of a 6th-order binary $\Sigma\Delta$ ADC under different excess loop delay | 50   |

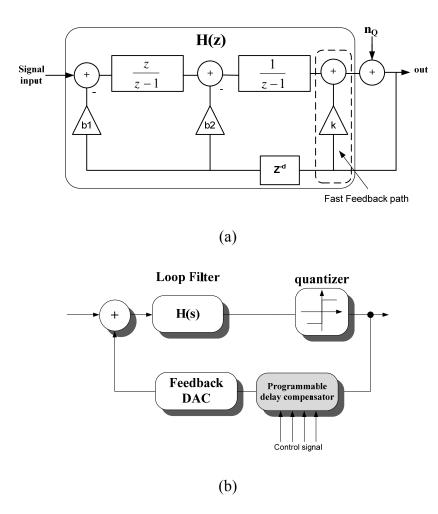

| Fig. 3.21. | Two methods to solve the issue of excess loop delay                                              | 52   |

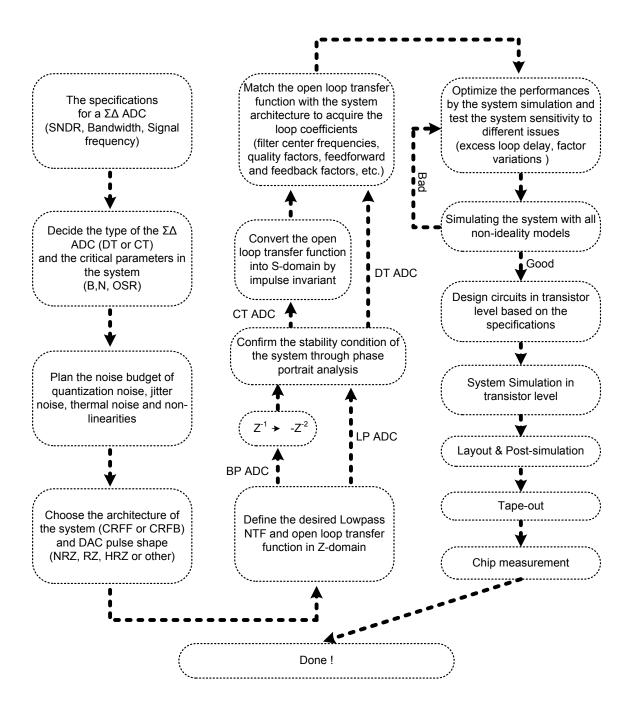

| Fig. 3.22. | Complete design flow of a $\Sigma\Delta$ ADC                                                     | 54   |

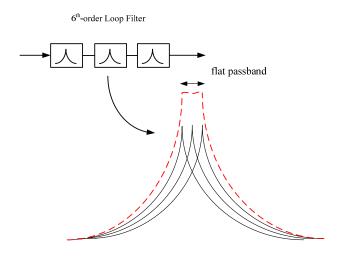

| Fig. 4.1.  | Pole-splitting technique                                                                         | 63   |

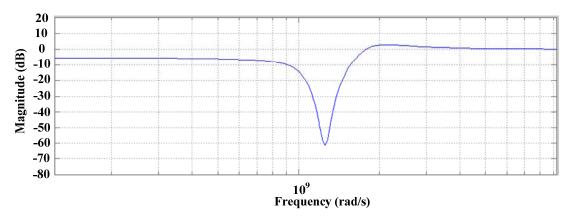

| Fig. 4.2.  | The frequency spectrum of the NTF                                                                | 65   |

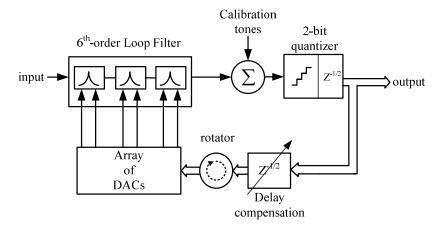

| Fig. 4.3.  | Block diagram of the 6th-order modulator architecture                                            | 66   |

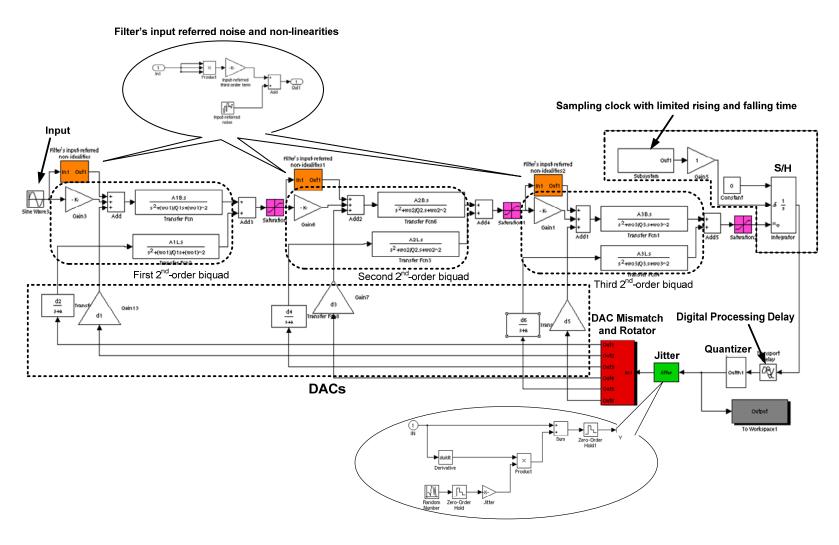

| Fig. 4.4.  | The Simulink model of the proposed modulator with all non-idealities                             | 68   |

|            |                                                                                                                                        | Page |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|------|

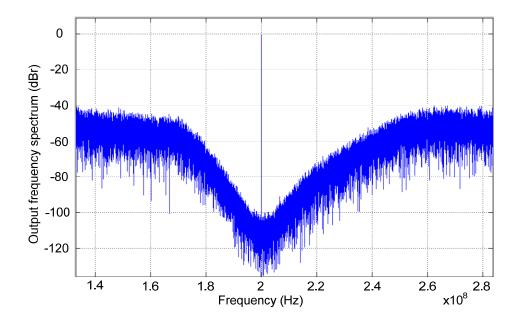

| Fig. 4.5.  | The output spectrum of the proposed architecture in Simulink                                                                           | 69   |

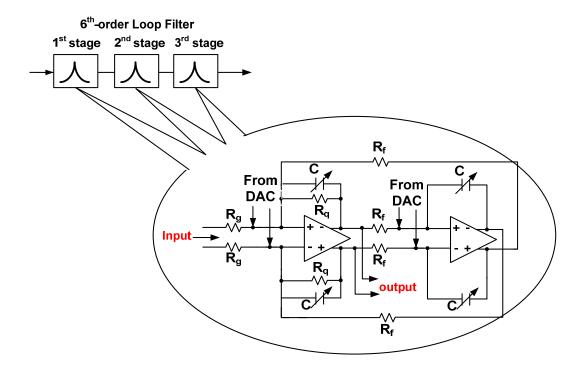

| Fig. 4.6.  | Active-RC type loop filter schematic                                                                                                   | 70   |

| Fig. 4.7.  | Block diagram of amplifier with feed-forward                                                                                           | 71   |

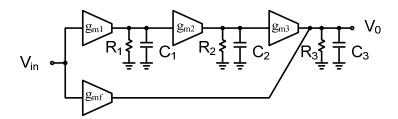

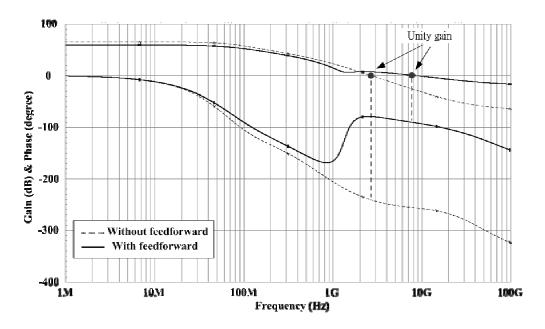

| Fig. 4.8.  | Frequency response for the proposed amplifier.                                                                                         | 73   |

| Fig. 4.9.  | Macromodel of the lossless integrator                                                                                                  | 76   |

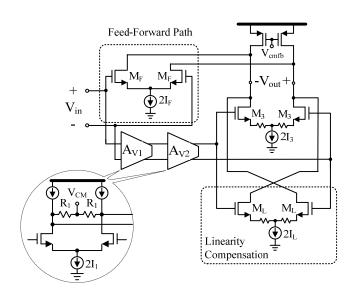

| Fig. 4.10. | Block diagram of amplifier with an additional linearity aid                                                                            | 79   |

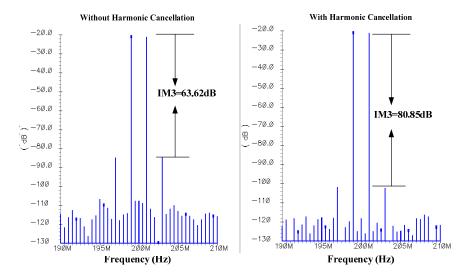

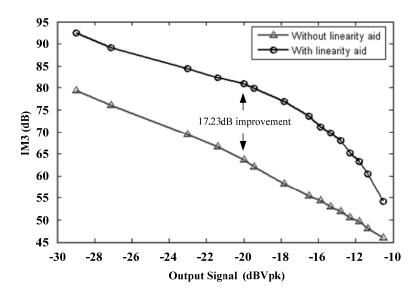

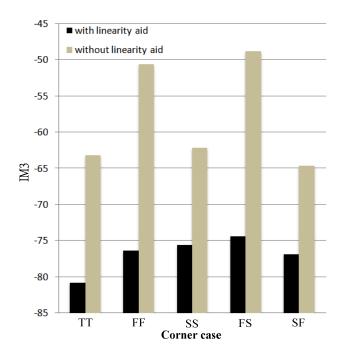

| Fig. 4.11. | IM3 performance of amplifier with and without linearity aid                                                                            | 81   |

| Fig. 4.12. | IM3 performance of $2^{nd}$ order filter in different output signal level .                                                            | 81   |

| Fig. 4.13. | Loop filter IM3 performance for different technology corners                                                                           | 82   |

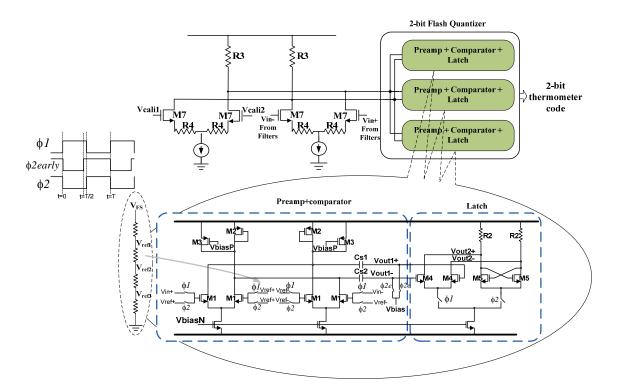

| Fig. 4.14. | Schematic of the summing amplifier with following comparators and latches                                                              | 84   |

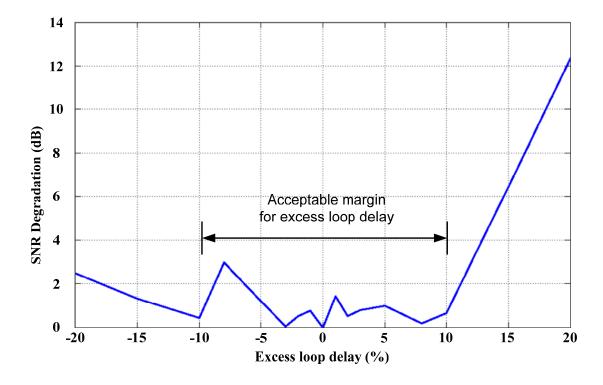

| Fig. 4.15. | SNR degradation in different level of excess loop delay                                                                                | 85   |

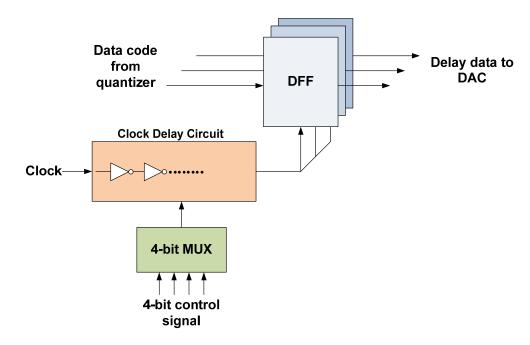

| Fig. 4.16. | The block diagram of the excess loop delay compensator                                                                                 | 86   |

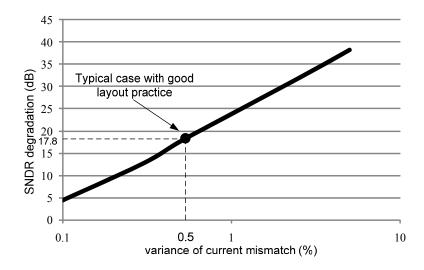

| Fig. 4.17. | SNDR degradation versus DAC current sources mismatch                                                                                   | 87   |

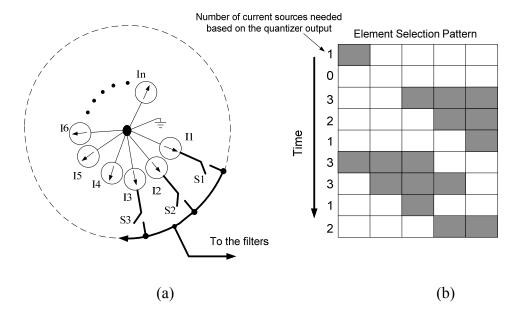

| Fig. 4.18. | Concept of data-weighted averaging using a 1-step clockwise rotator                                                                    | 88   |

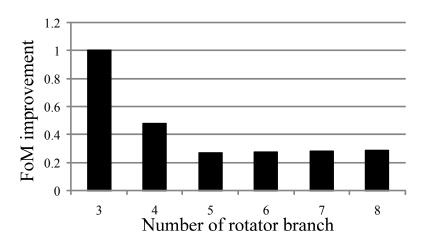

| Fig. 4.19. | FoM improvement under 0.5% current mismatch versus number of rotating branches                                                         | 89   |

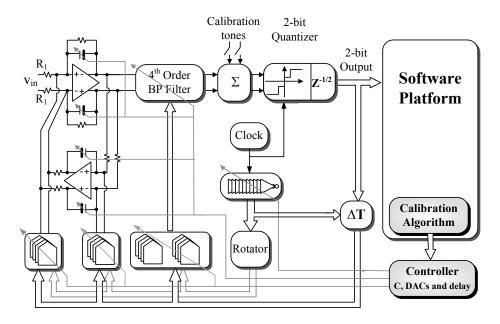

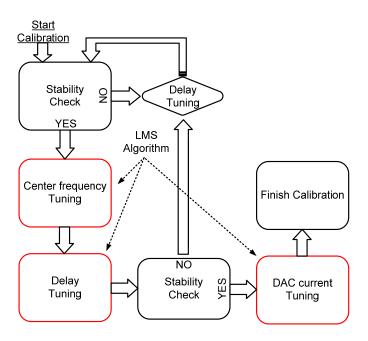

| Fig. 4.20. | Block diagram of the 6th order modulator architecture with the proposed software-based calibration                                     | 91   |

| Fig. 4.21. | The calibration flow chart                                                                                                             | 92   |

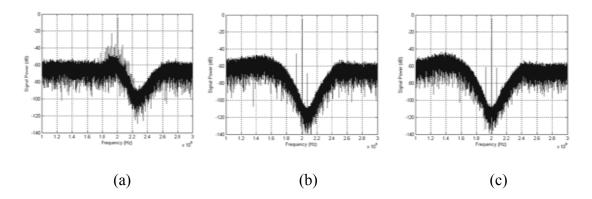

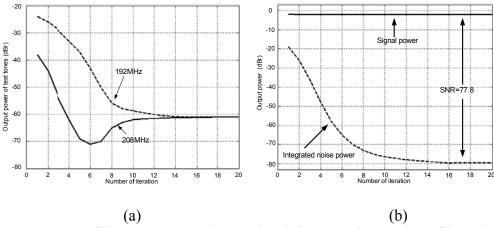

| Fig. 4.22. | The modulator calibration process                                                                                                      | 94   |

| Fig. 4.23. | Power of the test tones and SNR simulations vs. the number of iterations of the calibration scheme for PVT variations on the modulator | 94   |

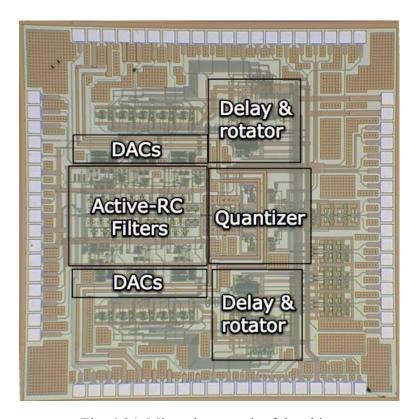

| Fig. 4.24. | Microphotograph of the chip                                                                                                                              |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

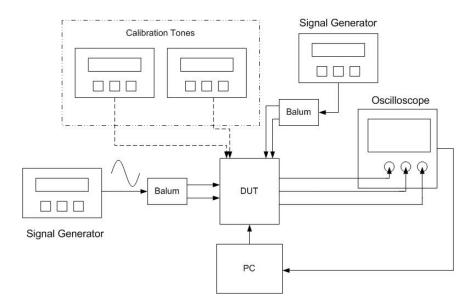

| Fig. 4.25. | The test-bench of the modulator measurement                                                                                                              |  |  |  |  |  |

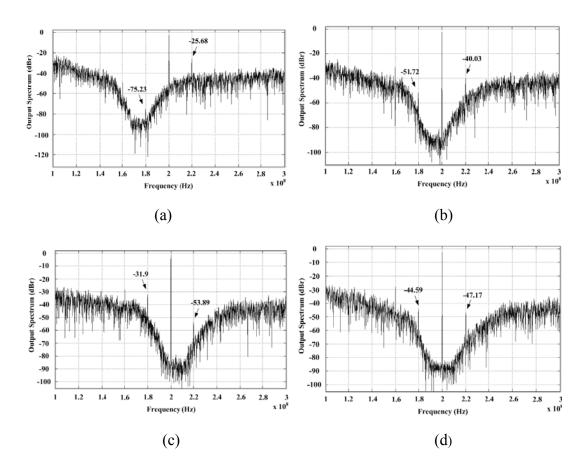

| Fig. 4.26. | Measured calibration process                                                                                                                             |  |  |  |  |  |

| Fig. 4.27. | Measured output spectrum with out-of-band input signal                                                                                                   |  |  |  |  |  |

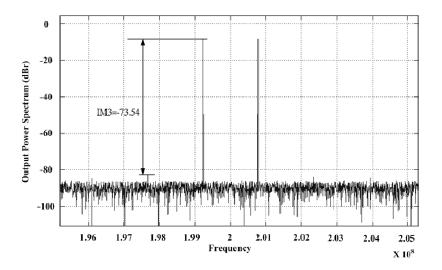

| Fig. 4.28. | Measured output spectrum in two-tone test                                                                                                                |  |  |  |  |  |

| Fig. 4.29. | SNDR versus input signal at 200MHz                                                                                                                       |  |  |  |  |  |

| Fig. 4.30. | FoM comparison versus center frequency of the BP $\Sigma\Delta$ modulators                                                                               |  |  |  |  |  |

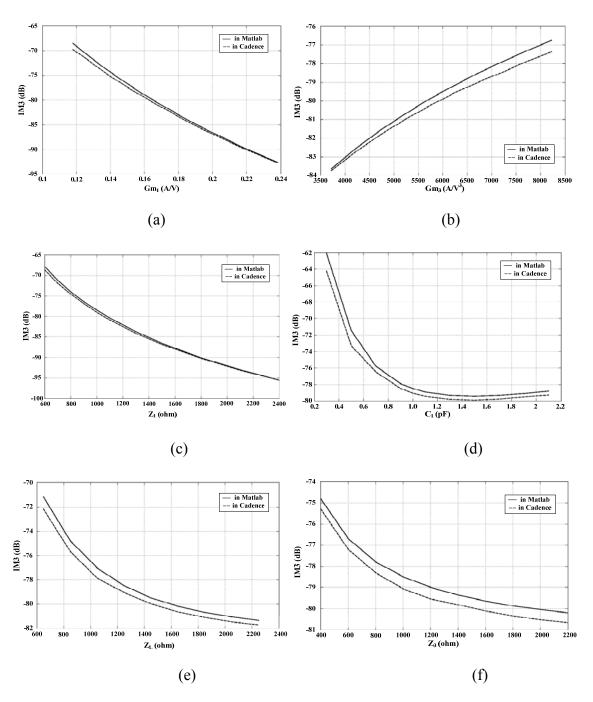

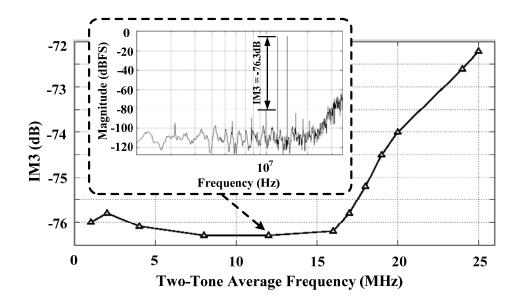

| Fig. 4.31. | The IM3 trend when sweeping.                                                                                                                             |  |  |  |  |  |

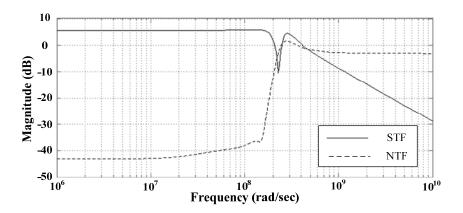

| Fig. 5.1.  | The plot of STF and NTF.                                                                                                                                 |  |  |  |  |  |

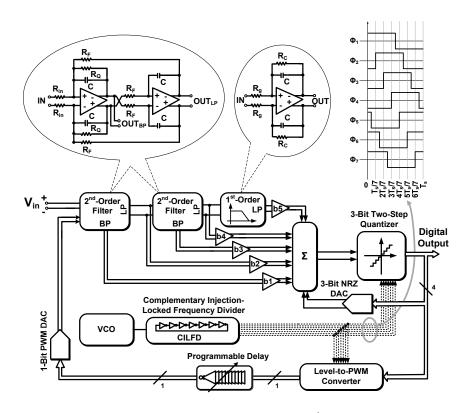

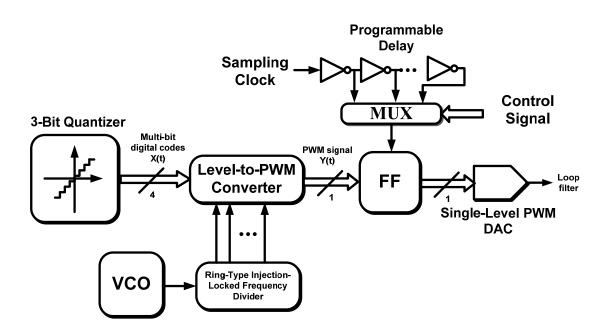

| Fig. 5.2.  | System architecture of the proposed 5th-order CT modulator                                                                                               |  |  |  |  |  |

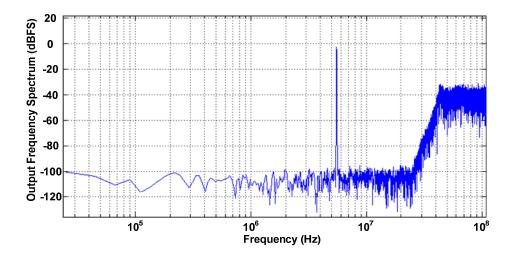

| Fig. 5.3.  | The simulated output spectrum of the proposed modulator                                                                                                  |  |  |  |  |  |

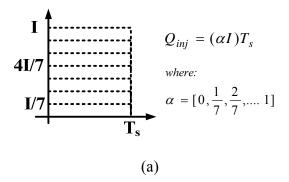

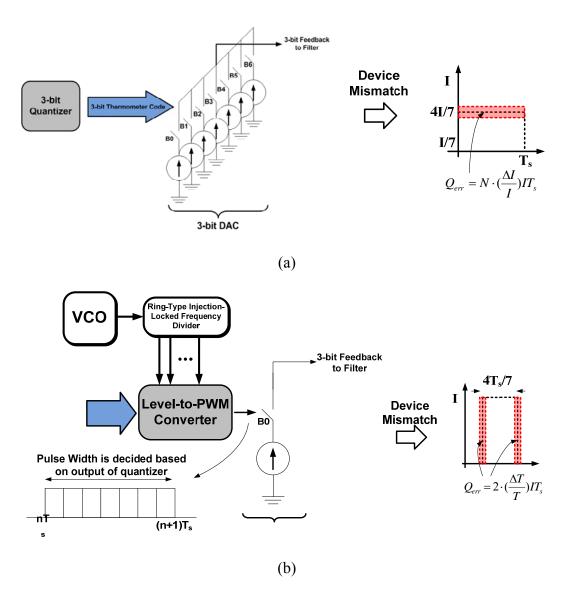

| Fig. 5.4.  | Multi-bit output                                                                                                                                         |  |  |  |  |  |

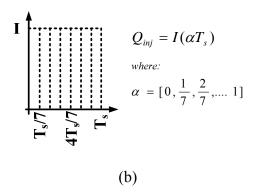

| Fig. 5.5.  | Level-to-PWM converter in the feedback path                                                                                                              |  |  |  |  |  |

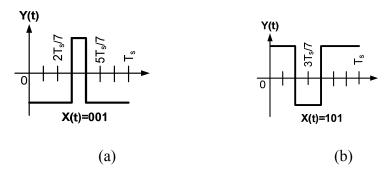

| Fig. 5.6.  | Example pulse shapes for two quantizer output codes                                                                                                      |  |  |  |  |  |

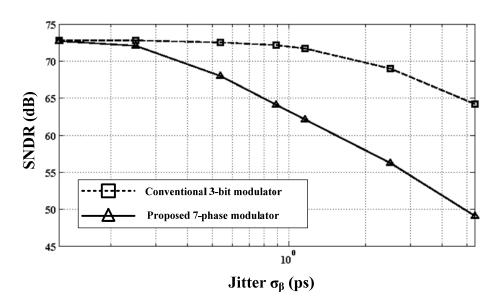

| Fig. 5.7.  | SNR (SQNR+SJNR) vs. jitter of the proposed modulator with the 7-phase feedback DAC compared to the conventional 3-bit modulator/DAC with 400MHz sampling |  |  |  |  |  |

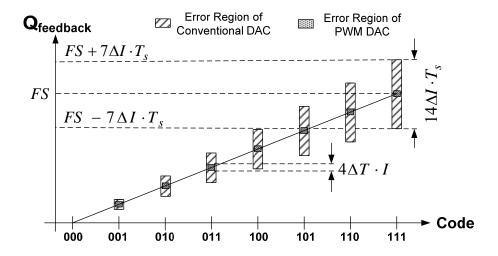

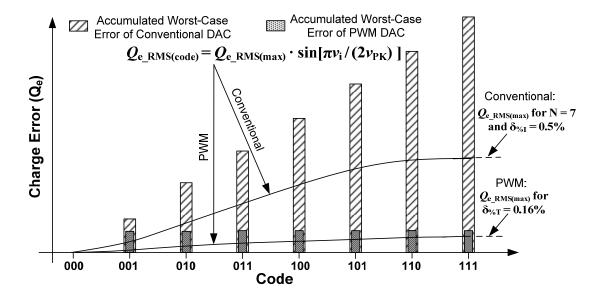

| Fig. 5.8.  | 3-bit DAC linearity error comparison: conventional vs. PWM                                                                                               |  |  |  |  |  |

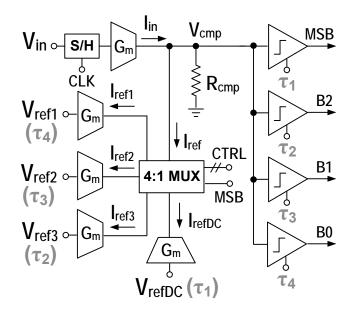

| Fig. 5.9.  | Single-ended equivalent block diagram of the quantizer                                                                                                   |  |  |  |  |  |

| Fig. 5.10. | Timing of the quantization decisions                                                                                                                     |  |  |  |  |  |

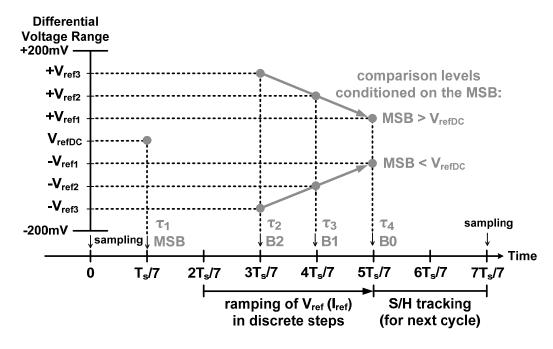

| Fig. 5.11. | Schematic of the amplifier employed in loop filter                                                                                                       |  |  |  |  |  |

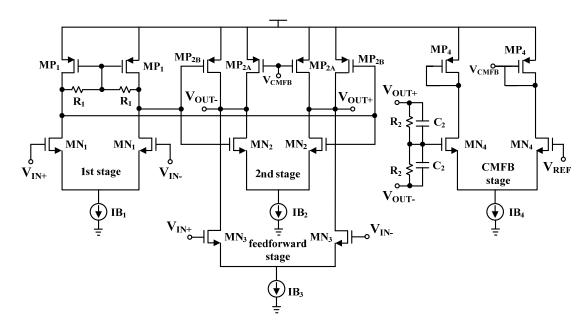

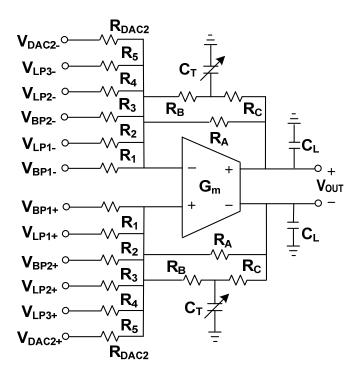

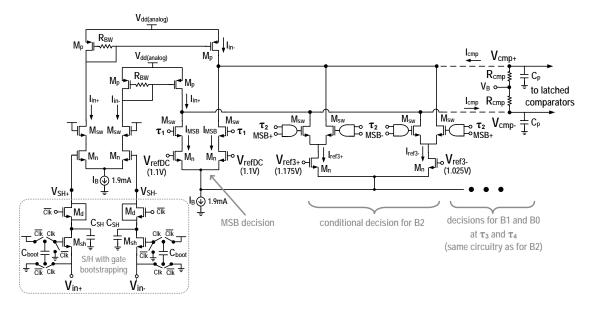

| Fig. 5.12. | Summing amplifier stage                                                                                                                                  |  |  |  |  |  |

| Fig. 5.13. | Simplified schematic of the current-mode quantizer core circuitry.                                                                                       |  |  |  |  |  |

|            |                                                                             | Page |

|------------|-----------------------------------------------------------------------------|------|

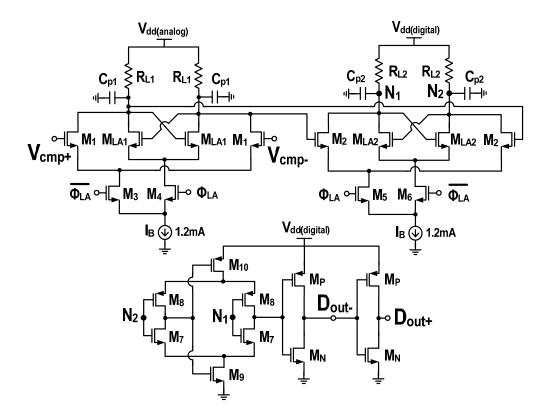

| Fig. 5.14. | Latched comparator schematic                                                | 134  |

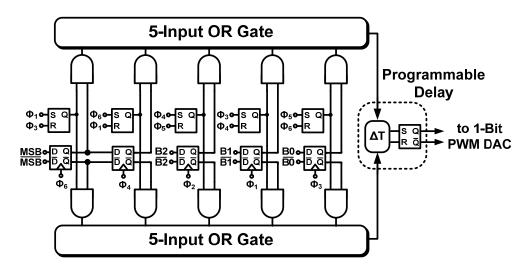

| Fig. 5.15. | Implementation of the level-to-PWM converter                                | 136  |

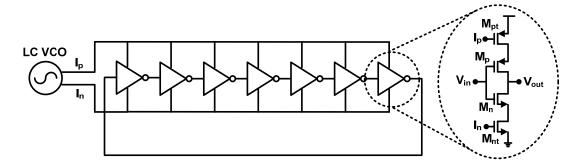

| Fig. 5.16. | Complementary injection-locked frequency divider (CILFD) diagram            | 137  |

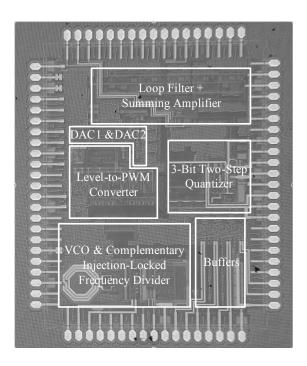

| Fig. 5.17. | Chip microphotograph. (2.6mm² area, excluding pads and ESD circuitry)       | 139  |

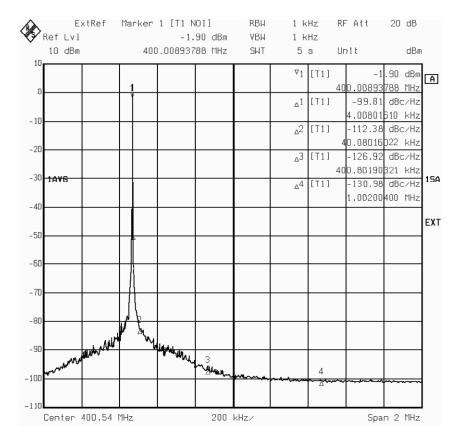

| Fig. 5.18. | Measured spectrum of one CILFD output.                                      | 140  |

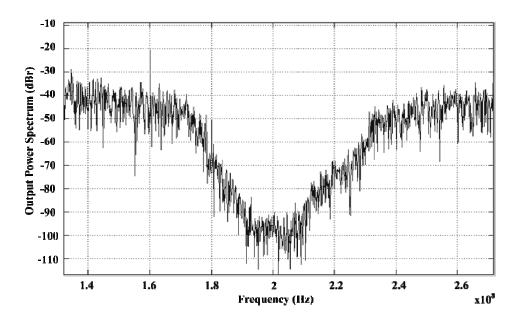

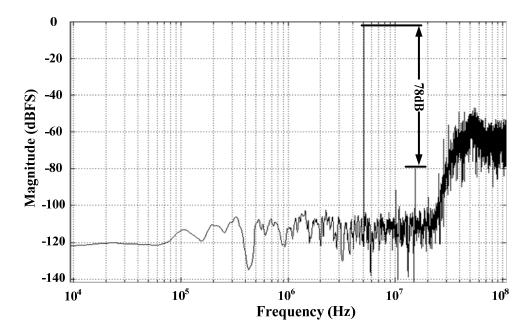

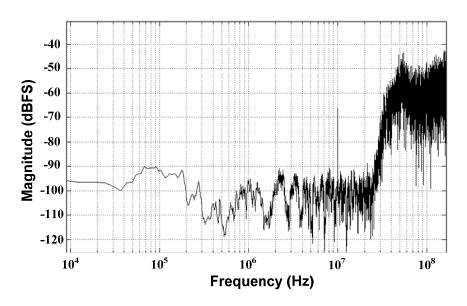

| Fig. 5.19. | Measured output spectrum of the modulator with a -2.2dBFS input at 5.08MHz  | 141  |

| Fig. 5.20. | Measured SNR and SNDR versus input signal power                             | 142  |

| Fig. 5.21. | IM3 vs. average frequency of two -5dBFS input tones separated by 2MHz       | 142  |

| Fig. 5.22. | Aliasing test: measured output spectrum with a -10dBFS input tone at 390MHz | 143  |

| Fig. 5.23. | The digital circuitries and device mismatch effect                          | 149  |

| Fig. 5.24. | Feedback charge error comparison.                                           | 150  |

# LIST OF TABLES

|           |                                                                                       | Page |

|-----------|---------------------------------------------------------------------------------------|------|

| Table 2.1 | The comparison of the receiver architectures.                                         | 16   |

| Table 3.1 | Literature survey of the reported $\Sigma\Delta$ ADCs                                 | 55   |

| Table 4.1 | The specifications of the CT BP $\Sigma\Delta$ modulator                              | 59   |

| Table 4.2 | Noise budget for different noise source                                               | 62   |

| Table 4.3 | Amplifier poles, zeros and gain                                                       | 73   |

| Table 4.4 | Detail values of components in the first filter                                       | 75   |

| Table 4.5 | Transistor devices and bias conditions for the sampling amplifier and 2-bit quantizer | 83   |

| Table 4.6 | Performance summary of the BP $\Sigma\Delta$ Modulator                                | 100  |

| Table 4.7 | Comparison with previously reported BP $\Sigma\Delta$ modulators                      | 102  |

| Table 4.8 | Default coefficients of the simulated integrator                                      | 106  |

| Table 5.1 | The specifications of the CT LP $\Sigma\Delta$ modulator                              | 111  |

| Table 5.2 | Noise budget for different noise source                                               | 112  |

| Table 5.3 | Pulse arrangement of the 7-phase time-domain feedback DAC signal                      | 120  |

| Table 5.4 | 3-bit quantization ranges and output codes                                            | 128  |

| Table 5.5 | Summary of the measured ADC performance                                               | 144  |

| Table 5.6 | Comparison with previously reported LP ΣΔ ADCs                                        | 145  |

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1 Motivation

With the recent developments on wireless communications, different wireless services are proposed year by year. With different definitions of signal power, signal bandwidth, signal frequency and coding methods in the standards, the required performance of the hardware for each one of these services is unique. For example, the receiver in GSM system has to have fast settling time due to the adoption of frequency hopped time-division multiple-access (TDMA) system. Nevertheless, by employing code-division multiple-access (CDMA) system, the timing requirement in WCDMA receiver is irrelevant. The noise and linearity performance in WCDMA is more important because of the higher required bit error rate (BER.) As a result, the conventional scheme building a multi-standard wireless device is to design different receiver modules for different wireless services. The solution is simple but the efficiency on power and area is low. Integrating as many wireless services as possible into a single chip-set is recently a trend for the semiconductor sector in order to cut down the cost of the products and raise the device competitiveness [1].

The software-defined radio receiver architecture (High-IF architecture) is a potential candidate to realize the multi-standard receiver [2]. With no DC offset and the relaxed image problem, this architecture eases the front-end circuit specifications. However, the requirements of large bandwidth (≥ 10MHz for video communication), high operational

This dissertation follows the style and format of IEEE Journal of Solid-State Circuits.

frequency (> 100MHz for high-IF receiver) and high resolution ( $\geq$  11bits for video communication) make the design of the ADC very challenging. None of the reported ADCs can match these three specifications perfectly in the architecture at this moment. In this research, therefore, the design of a continuous-time sigma-delta ( $\Sigma\Delta$ ) ADC to overcome the bottleneck of the software-defined radio receiver is addressed.

Unlike a discrete-time  $\Sigma\Delta$  ADC with immunity to the process, voltage, temperature (PVT) variations by using capacitor ratios to determine the system coefficients, one of the critical issues of a continuous-time  $\Sigma\Delta$  ADC is its high sensitivity to the variations due to the demands on RC time constants. These variations drastically degrade the performance of the ADCs or even break the stability conditions. Therefore, either manual or automatic calibration is definitely needed after fabrication. In this dissertation, an efficient software-based automatic calibration technique is proposed to recover the system performances from the PVT variations.

In order to maintain the resolution of continuous-time  $\Sigma\Delta$  ADCs, increasing sampling frequency and employing multi-bit quantizer and DACs are now essential due to the growth of the signal bandwidth in wireless services. The device mismatch issue in multi-level DACs threatens the system's linearity and degrades the ADC's resolution. Although there are different reported solutions to either pseudo-randomize or shape the mismatch, the reduced delay margin in the digital feedback path due to the increase of sampling frequency makes the solutions inadequate to improve the linearity of broadband ADCs. Hence, to implement continuous-time  $\Sigma\Delta$  ADCs with wide bandwidth and high resolution, a new technique to alleviate the non-linearity issue with minimal delay requirements and power consumption has to be proposed.

#### 1.2 Research Contribution

To overcome the limitations on current software-radio defined receiver architectures by employing a wide-band, high-speed, high-resolution continuous-time  $\Sigma\Delta$  ADC are some of the objectives in this research. A 6<sup>th</sup>-order bandpass continuous-time  $\Sigma\Delta$  ADC is implemented in TSMC 0.18um CMOS technology to acquire 10MHz bandwidth for video applications. The distortion issues due to the input stage filter are cautiously analyzed and a two-integrator type active-RC filter is designed with remarkable linearity performance. Since the sensitivity of continuous-time  $\Sigma\Delta$  ADCs to PVT variations is a critical issue, a robust unique software-based calibration technique is proposed to efficiently calibrate the system. By injecting two test tones at the input of the quantizer to measure the noise transfer function, the output noise level of the ADC is detected by software and minimized by tuning the system coefficients. The measured bandpass continuous-time  $\Sigma\Delta$  ADC achieves 68.4dB SNDR at 10MHz bandwidth with 160mW power consumption. The resulted figure-of-merit (FoM) of 3.72pJ/bit out perform all the currently reported bandpass continuous-time  $\Sigma\Delta$  ADCs.

To alleviate the non-linearity issues from device mismatches of the conventional multi-level DACs is also one of the core objectives of this research. The techniques are employed for the design of a 25MHz bandwidth 5<sup>th</sup>-order lowpass continuous-time  $\Sigma\Delta$  ADC. With oversampling ratio equal to eight, instead of using a 3-bit conventional quantizer and DAC, the 3-bit time-domain quantizer and DAC are proposed to achieve the required resolution at a 25MHz bandwidth.

By using a pulse-width modulation (PWM) scheme with appropriate pulse shape arrangement in digital feedback path, an inherently linear single-level DAC is employed and hence the current source mismatch problem is relaxed. Although the use of pulse-width modulation in continuous-time  $\Sigma\Delta$  ADCs is not a novel concept introduced in this dissertation, the detail analysis on jitter behavior of the time-domain DAC and non-linearity issue because of timing mismatch are for the first time addressed. The jitter noise sensitivity of the ADC is eased with the implementation of complementary injection-locked frequency divider, which can achieve the required reference clocks with improved jitter noise performance. Fabricated in Jazz 0.18um CMOS technology, the measurement of the proposed lowpass continuous-time  $\Sigma\Delta$  ADC results in 67.7dB peak SNDR and 78dB SFDR at the ADC output. By using only the cheapest technology, the 444fJ/bit FoM is comparable to the state-of-arts, which are implemented in more advanced technologies.

# 1.3 Dissertation Organization

In order to fully understand the design issues of a continuous-time  $\Sigma\Delta$  ADC for wireless communication applications, the advantages and limitations of different receiver architectures are analyzed and compared in Chapter II. In addition, the comparison between Nyquist ADCs and oversampling ADCs are addressed in Chapter II. An overview of the continuous-time  $\Sigma\Delta$  ADCs is given in Chapter III, where the design issues and design strategies are explained. The survey of currently reported works identifies the implementation trends of  $\Sigma\Delta$  ADCs.

Chapter IV presents a 10MHz bandwidth  $6^{th}$ -order bandpass continuous-time  $\Sigma\Delta$  ADC with 200MHz operational frequency and 800MHz sampling frequency for software-defined radio receiver architectures. A proposed unique calibration scheme to overcome the lack of accuracy of continuous-time  $\Sigma\Delta$  ADCs is well explained in this chapter. The design of a 25MHz bandwidth  $5^{th}$ -order lowpass continuous-time  $\Sigma\Delta$  ADC with a time-domain two-step 3-bit quantizer and feedback DAC for zero-IF architecture is described in Chapter V. The advantages of the pulse-width modulation are specified and the limitations of the scheme are fully discussed. The design flow, circuit implementation, and measurement results of both aforementioned continuous-time  $\Sigma\Delta$  ADCs are presented in their own chapters. Finally, Chapter VI depicts the conclusions of this dissertation.

#### **CHAPTER II**

# THE BOTTLENECK OF THE NEXT GENERATION RECEIVERS: ANALOG-TO-DIGITAL CONVERTER

#### 2.1 Next Generation Receivers

Due to the demand for high-performance radio frequency (RF) integrated circuit design in the past decades, a system-on-chip that enables integration of analog and digital parts on the same die has becoming the trend of the microelectronics industry. Also, many different standards have been developed for different wireless applications. The cell phones segment includes standards like GSM, CDMA, UMTS, GPRS, TDMA, DECT, EDGE, IS-95 etc. The wireless local area network for laptops, desktops and PDA's include standards like Bluetooth, for the Personal Area Network (PAN); WiFi for the Local Area Network (LAN); 802.16 for the Metropolitan Area Network (MAN) and IEEE 802.20 for the Wide Area Network (WAN). As a result, a major requirement of the next generation wireless devices is to support multiple standards in the same chip-set, as shown in Fig. 2.1. This would enable a single device to support multiple applications and services and also improve the total power consumption, form factor and device competitiveness.

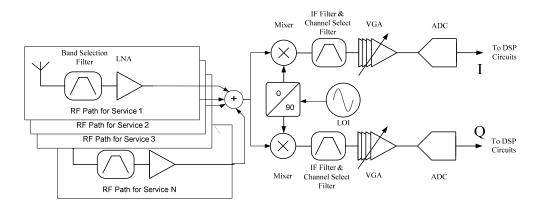

Fig. 2.1. A next generation wireless device supporting multiple services.

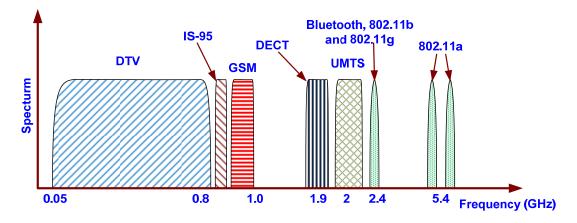

As the frequency spectrum in Fig. 2.2 shows, different services employ different radio frequency bands to build the communication between stations and mobile devices. In order to support multiple standards, the receiver within the next generation wireless device has to be able to select the preferred channel and process them accurately.

Fig. 2.2. The band distribution of different services.

The first design step is to determine the receiver architecture. Since there are several receiver architectures available, the detailed and thorough research on these architecture solutions, including all the advantages and drawbacks, is necessary to find the most potential candidate for the realization of next generation receivers. Section 2.2 discuss the operational concepts and the characteristics of each one of different receiver architectures and identify the best choice for the next generation receiver.

The Analog-to-Digital Converter (ADC) is the last block in the front-end of the wireless architectures. The main function of ADCs is to digitalize analog signals such that the following digital-signal-processing (DSP) circuits can process the signal and demodulate the wanted information through robust, flexible, and reliable software. In section 2.3, we will compare the different ADC architectures and point out the performance limitations. In section 2.4 we will make a conclusion on the observations on the receiver architectures and ADCs and determine the best choices for the realization of wideband receivers.

#### 2.2 Common Receiver Architectures for Wireless Communication

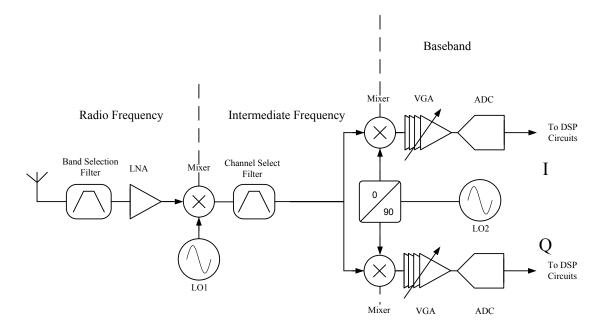

## 2.2.1 Superheterodyne architecture

This is the most traditional system architecture of a receiver in wireless communication. The main concept was introduced by Edwin Armstrong in 1918. As depicted in Fig. 2.3, when antenna captures the signal, the unwanted blockers and interferences are filtered out by the band selection filter and the signal is amplified by a low-noise amplifier (LNA.) This band selection filter is an external component with a very high Q. In order to reduce the difficulty in processing the signal, the desired channels are down-converted to the intermediate frequency (IF) from the original radio frequency (RF) usually in a range of 800MHz to 8GHz depending on the services. The channel select filter will select the required channel of the system and reject the adjacent channels and the un-desired high frequency spectral components produced by the mixer. The second mixer down-converts the cleaned signal to the baseband with I-Q paths, which have 90 degree phase difference between each other. The variable-gain amplifier (VGA) reduces the signal power range based on its flexible gain. At the last, the ADC converts the analog signal to the digital domain such that the digital signal processor (DSP) circuits can operate the signal and demodulate the information.

In this architecture, because there are many blocks needed to process the signal into the acceptable signal power level and frequency, the total power consumption is much higher than other solutions. Besides, when wanting to integrate multiple standards into single device, the only solution of this architecture is to duplicate the whole receiving path. Therefore, the power dissipation increases drastically. Nevertheless, this

architecture has been popular for many years since this is the easiest solution comparing with other architectures.

Fig. 2.3. The superheterodyne architecture of a receiver.

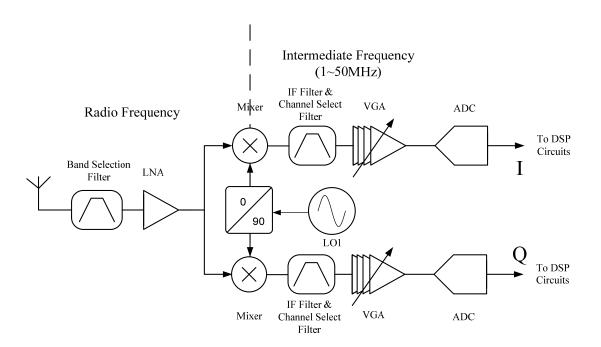

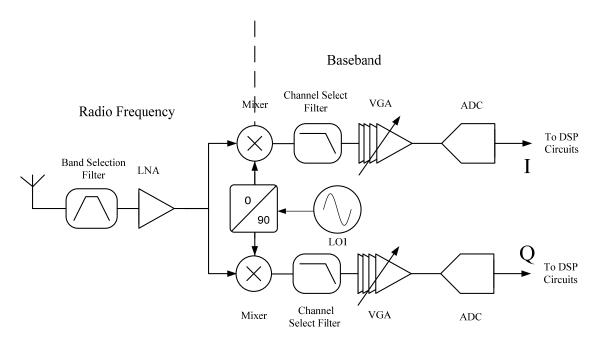

## 2.2.2 Low-IF architecture

Instead of employing two down-conversions, the low-IF architecture down-converts the signal only once to decrease the number of blocks and thus reduce the overall power dissipation of the receiver as depicted in Fig. 2.4. In addition, by lowering the IF frequency, the power consumption of each IF block can be reduced.

The image effect in this architecture is a critical issue since the IF is lowered. Based on the concept of mixing, when there are a signal at frequency of  $f_{sig}$  and a reference clock at frequency  $f_{LO}$  from LO, the output of mixer will generate a tone at  $f_{IF}=f_{sig}-f_{LO}$  and hence complete the down-conversion of the signal. However, if there is an interference locating at  $2f_{LO}-f_{sig}$ , (=  $f_{sig}-2f_{IF}$ ) it can be demonstrated that this interference will also fall into the frequency of  $f_{sig}-f_{LO}$  after mixing. The interference overlapping

with signals is very difficult to be rejected. The best way to prevent this effect is to attenuate the interference at  $f_{\text{sig}}$ - $2f_{\text{IF}}$  before mixer. However, since the IF frequency is only few MHz in low-IF architecture, this image interference may be the adjacent channel signal of the wireless system, which might has higher power than the desired channel. The purpose to eliminate this strong image interference results in a very power-hungry external bandpass RF filter. This is not a wanted solution in system-on-chip (SoC) applications. Other solutions, such as Hartley architecture [3] and Weaver architecture [4], were proposed in order to eliminate the image problem after mixer by taking the advantage of phase difference between IQ signals. However, the solutions are more expensive and the gain and phase mismatch limit the rejection of the image.

Fig. 2.4. The low-IF architecture of a receiver.

#### 2.2.3 Direct conversion architecture

The direct conversion or zero-IF architecture, plotted in Fig. 2.5, down-converts the RF signal to baseband directly. By choosing the LO frequency equal to the desired signal frequency, there is no image issues in this architecture. The power of the receiver is now further reduced since the desired channel is centered at DC after mixer.

Although the image problem is thoroughly solved, the extra issues from flicker noise, DC offset and IIP2 constraint the performance of the architecture. Since the circuits after mixer work at baseband, the flicker noise dominates the noise performance and threatens the system. An additional emphasis on this flicker noise has to be done when designing baseband circuits. DC offset issues are the results of the self-mixing where the reference signal from LO leaks to antenna and is received with signals. Since the frequency of reference signal and the desired signal are the same, it is impossible to distinguish them. To enhance the isolation of the mixer from LO port to RF port is normally the solution to alleviate the problem. In addition, if there are two blockers close to each other in frequency, the second-order intermodulation of Mixer and LNA will produce an undesired tone at baseband and affect the quality of the baseband signal. As a consequence, the even-order intermodulation performance of the LNA and Mixer are critical parameters in direct conversion architectures. The Mixer's isolation between RF and output ports is critical as well.

Fig. 2.5. The direct conversion of a receiver.

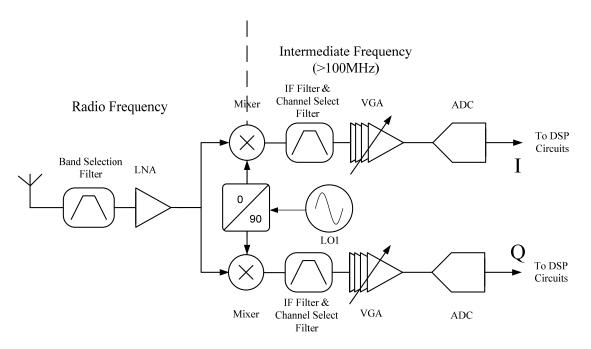

# 2.2.4 High-IF architecture (software-defined radio architecture)

Fig. 2.6 shows the architecture of a High-IF receiver. Similar to the low-IF architecture, the high-IF architecture down-converts the signal to the intermediate frequency and then digitalizes it. The high-IF radio presents several unique properties by digitalizing the signal at few hundred MHz. The baseband operations, such as baseband conversion and channel filtering, are more robust and power efficient in digital domain and fewer analog blocks would require to be replicated for each standard. Neither the image effect presenting in Low-IF architecture nor the DC offset issues in direct conversion will degrade the performance of the system. This architecture relaxes the specifications for most of the front-end building blocks but not for the ADC. The demands of wide bandwidth, high signal frequency and high resolution make this ADC a bottleneck when developing this architecture. Although there have been many reported papers for these specifications, none of them can fulfill the requirements perfectly.

Fig. 2.6. The high-IF architecture of a receiver.

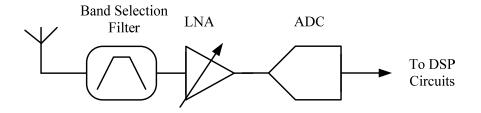

#### 2.2.5 Software radio architecture

Regarding the software radio, it is a concept proposed in 1991 to minimize the use of analog blocks due to the uncertainty of the analog circuits by digitalizing the signal at RF. As illustrated in Fig. 2.7, the signal is digitalized directly after a programmable LNA. This architecture is not only robust due to the entire signal processing in the digital domain but also suitable for multiple standard applications since all the signals from different standards can be processed by the same receiving path by running different software. In order to cover all the signal power ranges from sensitivity to maximum possible power in different applications, the LNA has to be programmable and the ADC has to achieve enough dynamic range at GHz range of signal frequency. Due to the huge barrier on the LNA and ADC requirements it is not economical to implement it. The

power consumption of the solution may be huge even with the most advanced technologies.

# Radio Frequency

Fig. 2.7. The software radio architecture of a receiver.

### 2.2.6 The comparison of the architectures

Table 2.1 compares the characteristics of all the receiver architectures. Based on the considerations on design issues, multi-standard compatibility and design difficulty, it is obvious that direct conversion and high-IF architectures are the most appropriate candidates to be employed in the next generation receiver. Indeed, the direction conversion architecture is the most popular architecture in many different applications nowadays. Many solutions are proposed to solve the issues from DC offset and flicker noise. The IIP2 of LNAs and Mixers in the architecture also keep being improved with the advances of circuit design techniques. Regarding the high-IF architecture, the development is constrained solely by the ADC where the operational speed of the circuit is a bottleneck. Fortunately, with the evolvement of the CMOS technologies, the f<sub>T</sub> frequency of the devices achieves about 200GHz; this will definitely assist overcoming

the bottleneck of ADCs and thus relax the limitation of the High-IF architecture development.

Table 2.1 The comparison of the receiver architectures

|                          | Multiple<br>standard<br>compatibility | Power<br>Consumption | DC-<br>offset | Image<br>effect | IQ<br>mismatch | Complexity |

|--------------------------|---------------------------------------|----------------------|---------------|-----------------|----------------|------------|

| Superhete -rodyne        | -                                     | ++                   | -             | +               | +              | -          |

| Low-IF                   | +                                     | +                    | -             | ++              | +              | +          |

| Direct<br>Conversio<br>n | ++                                    | -                    | ++            | -               | +              | +          |

| High-IF                  | ++                                    | +                    | -             | +               | -              | ++         |

| Software<br>Radio        | ++                                    | ++                   | -             | -               | -              | +++        |

### 2.3 Analog-to-Digital Converter (ADC)

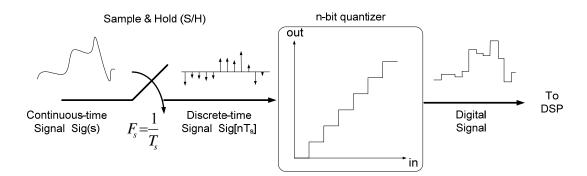

# 2.3.1 The basic concept of an ADC

The natural signal is analog but the digital signal is robust and efficient. When the analog signal travels through the air and is detected by a receiver, ADCs are required in order to digitalize the analog signal and take the advantages of the digital processing. The basic concept of an ADC, shown in Fig. 2.8, is to sample the analog signal with sampling frequency  $F_s$  and then quantize this sampled discrete-time signal into digital bits. Since there are always errors between the original signal and the quantized signal due to the limited number of bits in the quantizer, the average of the error is named quantization noise. A general signal-to-quantization noise (SQNR) equation in (2.1) can predict the resolution performance of an ADC [5].

$$SQNR = 6.02n + 1.76 \tag{2.1}$$

where n means the number of bits of a quantizer.

Fig. 2.8. The basic concept of an ADC.

## 2.3.2 Nyquist ADC and oversampling ADC

There are several ADC architectures that could be used for broadband communications. Overall, there are two main categories to classify these ADCs according to the ratio between the sampling frequency and signal bandwidth: Nyquist ADCs and Oversampling ADCs.

As described by equation (2.2) and (2.3), in Nyquist ADCs the sampling frequency [6] can be as low as twice the signal bandwidth to avoid series aliasing effect.

Oversampling ADCs employ a sampling frequency larger than twice of signal bandwidth.

$$\frac{f_{SNyquist}}{f_{BW}} = 2 \tag{2.2}$$

$$\frac{f_{soversampling}}{f_{BW}} > 2 \tag{2.3}$$

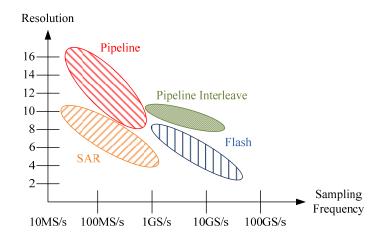

There are many different types of Nyquist ADCs. Fig. 2.9 illustrates the performance distribution on the resolution and sampling frequency of currently relevant Nyquist ADCs. The pipeline ADCs have the highest resolution but the slowest operational speed because of the employment of the cascaded quantizer stages. The flash ADCs have the fastest operational speed since the architectures are composed by a single quantizer stage. However, the resolutions of the flash ADCs are limited because the circuit complexities are proportional to 2<sup>bit</sup>. The requirements of the ADC in a high-IF receiver architecture demand on both high resolution (> 12bits) and high operational speed (≥ 800MHz sampling frequency). Therefore, there is no potential candidate of Nyquist ADCs that can fulfill the requirements of the ADC in high-IF architecture. In addition, since all the Nyquist ADCs are lowpass ADCs, the bandwidth of the ADC has to cover the bandwidth from DC to the desired high-IF frequency. However, the desired signal

bandwidth is usually in the range of 1MHz to 25MHz depending on the standard used. This will waste all other bandwidth as well as the power of the ADCs.

Fig. 2.9. The performance distribution of the Nyquist ADCs.

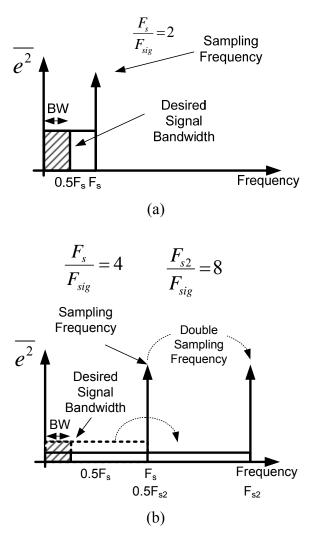

Unlike Nyquist ADCs, oversampling ADC has many inherent advantages especially for the high-IF application. As shown in Fig. 2.10 (a), when using a quantizer with sampling frequency equal to twice of the signal bandwidth BW, the rms quantization noise is  $\frac{1}{12}LSB^2$  where LSB is least significant bit of the quantizer. In oversampling ADCs with the same quantizer, by doubling the sampling frequency from  $F_s$  to  $F_{s2}$  ( $F_{s2}$ =2 $F_s$ ), the rms quantization noise is the same but is spread into more frequency range. If the quantization noise is considered as the only noise source to the ADC, the integrated in-band noise power becomes  $v_n(rms) = \sqrt{e^2 \cdot BW}$ . A 3dB resolution is improved when doubling the sampling frequency [7]. Therefore, in general, oversampling ADCs perform better resolution due to this characteristic. However, due to the employment of close loop system, the operational speed of an oversampling ADC is not as fast as that of a flash ADC. Fortunately, the speed of  $\Sigma\Delta$  ADCs nowadays keeps

increasing thanks to the higher frequencies achievable with advanced technologies. Despite the resolution performance, [8] has already achieved 1GHz bandwidth and 40GHz sampling frequency by using SiGe BiCMOS technology. As a result, the  $\Sigma\Delta$  ADC is the best candidate in the application with high-IF receiver architecture. The design strategies of the high-IF  $\Sigma\Delta$  ADC will be depicted in Chapter III.

Fig. 2.10. The quantization error distribution in frequency spectra (a)Nyquist ADC (b) Oversamping ADC.

# 2.3.3 ADC performance

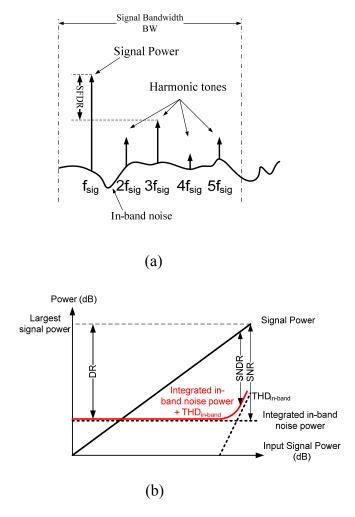

To judge the performance of an ADC, SQNR, SNR, IM3, peak SNDR, SFDR and DR are the most critical indicators. Fig. 2.11 (a) illustrates the general output power spectrum of an ADC. By injecting an input signal, the output of the ADC is composed by the signal, noise, and harmonic distortions. Thermal noise from transistors or resistors, quantization noise from a quantizer and jitter noise from the sampling clock all contribute to the overall noise performance. The harmonic distortions are generated due to the non-linear behavior of the circuits. The relation between power of those components and input signal power is depicted in Fig. 2.11 (b). Basically, the integrated in-band noise power is fixed and the total in-band harmonic distortion (THD<sub>in-band</sub>) increases when input signal power grows. Signal-to-noise ratio (SNR) is defined as the ratio between signal power and integrated in-band noise power. The harmonic tones should be excluded when computing SNR. The SNDR (signal-to-noise-and-distortion ratio) is defined as the power difference between the signal power and integrated in-band noise power plus THD<sub>in-band</sub> in most of ADCs. SFDR is spurious-free dynamic range which is the power difference between signal and the largest harmonic tone or intermodulation tone as shown in Fig. 2.11(a); dynamic range (DR) means the power range of the input signal where the upper limit and lower limit are the largest allowable power that would not saturate the system and the power level equal to the integrated inband noise power, respectively, as shown in Fig. 2.11 (b). IM3 is the power difference between signal and third intermodulation tones when employing two-tone test. Overall, SNDR and DR are the most critical indicators showing all the performance related to non-idealties of an ADC and the working range of the signal power.

Fig. 2.11. Critical performance of an ADC (a) output frequency spectrum (b) output power component v.s. input signal power.

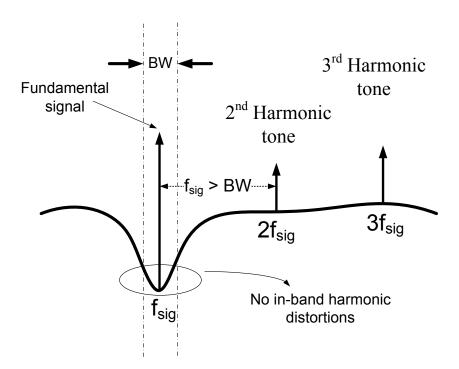

However, as depicted in Fig. 2.12, because the signal frequency is much higher than signal bandwidth ( $f_{sig} > BW$ ) in the case of bandpass  $\Sigma\Delta$  ADCs, harmonic tones ( $2f_{sig}$ ,  $3f_{sig...}$ ) will not fall into the desired bandwidth. The definition of the typical SNDR is invalid in this case since there is no in-band harmonic distortion. A new definition of SNDR for bandpass  $\Sigma\Delta$  ADCs is considered as equation (2.4) in order to maintain its indication on performance related to both in-band noise and non-linearities.

$$SNDR_{\text{bandpass }\Sigma\Delta \text{ ADCs}} = \frac{Power_{signal}}{Power_{niose} + Power_{third intermodulation tones @ two-tone test}}$$

(2.4)

where the power of third intermodulation tones should be measured under the condition that total power of two input signals in two-tone test is equal to the largest allowable signal level.

Fig. 2.12. The power spectrum of a bandpass  $\Sigma\Delta$  ADC.

#### 2.4 Conclusion

Due to its inherent characteristics, the high-IF architecture is one of the candidates with potential to realize the next generation receiver, which has to be able to support multiple services into a single chip. An architecture called multi-input, multi-output antenna (MIMO) high-IF architecture shown in Fig. 2.13 has been proposed to further relax the requirements of front-end RF circuits and simultaneously enhance the compatibility of this architecture to multiple standards.

However, the high-IF architecture bottleneck is the high requirements of the ADC. A bandwidth to accommodate the widest signal bandwidth in the different services, a signal frequency operating at IF frequency (> 100MHz), and a demanding resolution (> 11bit) of the ADC make the ADC design very challenging. The oversampling ADC, or called  $\Sigma\Delta$  ADC, seems to have the potential to fulfill these requirements efficiently over other ADC architectures.

Therefore, in order to design a  $\Sigma\Delta$  ADC to accommodate the requirements in the high-IF receiver architecture, Chapter III will go through the basic concepts and design issues to be considered.

Fig. 2.13. The MIMO high-IF receiver architecture.

#### **CHAPTER III**

#### **OVERSAMPLING ΣΔ ADC**

#### 3.1 Overview of $\Sigma\Delta$ ADC

## 3.1.1 Fundamentals on $\Sigma\Delta$ ADC

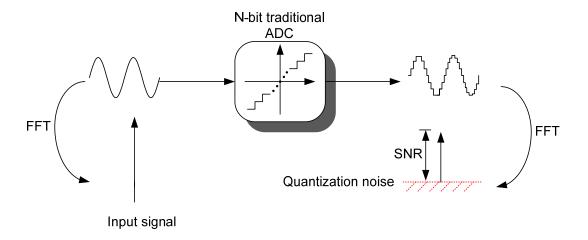

Sigma-delta ADCs can perform high resolution without the need of high-bit quantizer by forming a close-loop system with an embedded loop filter. Suppose there is the traditional flash n-bit ADC shown in Fig. 3.1. When the digitization is performed by the ADC, there are errors when comparing the original continuous-time input and the quantized output. The quantization noise appears at the ADC output and limits the signal-to-noise ratio performance (suppose there is no other noise source than quantization noise) as follows [7]:

$$SNR_{qutization} = 6.02 * n + 1.76 \tag{3.1}$$

Fig. 3.1. The operation of the traditional n-bit ADC.

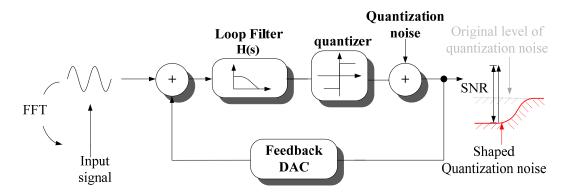

In  $\Sigma\Delta$  ADCs, a close loop system composed by the loop filter, n-bit quantizer, and

feedback DAC is constructed as depicted in Fig. 3.2. There are still quantization errors but these can be minimized due to the oversampling effect. The quantization noise is modeled as a noise source after the quantizer. However, unlike the case of the traditional ADC, the quantization noise will be shaped by the transfer function of the close loop system since the input signal is injected in a different node.

Fig. 3.2. The system of the  $\Sigma\Delta$  ADC.

Based on the feedback theory, the transfer function for the quantization noise, defined as noise transfer function (NTF), is approximated as

$$NTF = \frac{1}{1 + H(s)} \tag{3.2}$$

if the loop is linearized and assuming that the gain of the quantizer and DAC is unity. By using H(s) with high passband gain, the quantization noise will be further reduced. Regarding the input signal, the transfer function for the input signal (STF) is obtained as

$$STF = \frac{H(s)}{1 + H(s)} \tag{3.3}$$

It can be observed that the signal appears at the output of the system without any

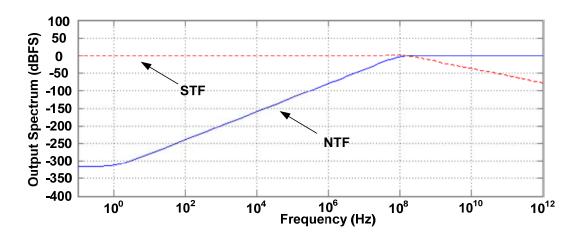

attenuation in the band of interest. Fig. 3.3 shows the NTF and STF of a  $\Sigma\Delta$  ADC if an ideal second order lowpass loop filter is employed. The gain of the STF is equal to one while that of NTF is about zero. The high-pass NTF (in lowpass  $\Sigma\Delta$  ADCs) or bandreject NTF (in bandpass  $\Sigma\Delta$  ADCs) allow us to obtain better SNR without employing the quantizers with higher resolution or same SNR by using lower bit quantizers. Therefore, the resolution of  $\Sigma\Delta$  ADCs depends not only on the resolution of the quantizer, but also on the filter's order and the sampling frequency, which are described in section 2.3.2.

Fig. 3.3. The NTF and STF of the lowpass  $\Sigma\Delta$  ADC with an ideal second order loop filter.

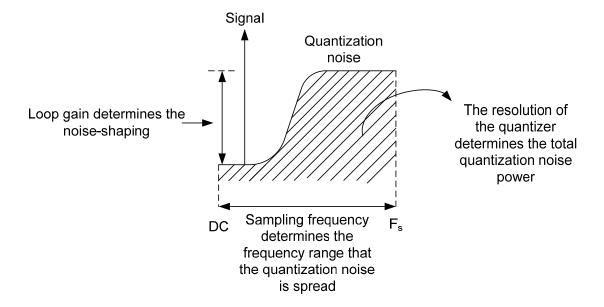

As a conclusion, in a  $\Sigma\Delta$  ADC, the attenuation of the quantization noise demands on the loop gain, the total quantization noise power is determined by the resolution of the quantizer, and the sampling frequency (F<sub>s</sub>) spreads the total quantization noise power into the frequency range of DC to F<sub>s</sub> as shown in Fig. 3.4. [9] analyzed the relation between the SNR of a  $\Sigma\Delta$  ADC and these three system parameters and obtained the equation (3.4):

Fig. 3.4. The effect of the system coefficients to the output quantization noise.

$$SNR_{max} = 10\log_{10}(\frac{1.5(N+1)OSR^{N+1}}{\pi^N}) + 6.02(B-1)$$

(3.4)

where N means the order of the bandpass loop filter (it will be 2N for the order of the lowpass loop filter), OSR is the oversampling ratio, which is  $f_{sampling}/(2 \cdot signal\ bandwidth)$ , and B is the bit number of the quantizer and feedback DACs. Increasing these parameters can improve the resolution of the  $\Sigma\Delta$  ADC. However, there are always trade-off issues behind all optimization procedures. These the issues will be discussed in section 3.2.

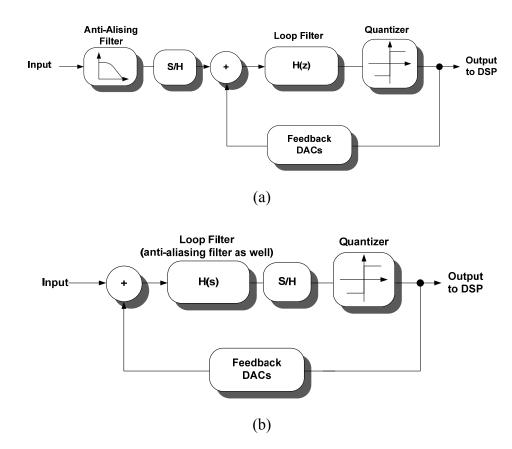

# 3.1.2 The comparison between the discrete-time $\Sigma\Delta$ ADC and the continuous-time $\Sigma\Delta$ ADC

$\Sigma\Delta$  ADCs are mainly divided into two different categories based on the location of the sample-and-hold (S/H): discrete-time (DT) and continuous-time (CT) ADCs. Fig. 3.5 shows the block diagrams of these two architectures. For discrete-time type, because S/H

locates at the input stage, switch-capacitor filter is normally employed to process the discrete-time signal. The continuous-time ADC employs continuous-time loop filter since the S/H locates after the filter.

Fig. 3.5. Block diagrams of two different sigma-delta ADCs (a) discrete-time (b) continuous-time.

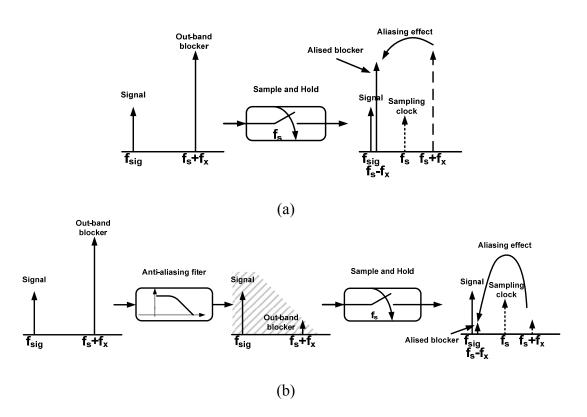

Based on the high precision of the capacitor ratio in technologies and the low feedback charge at the switching instant in switch-capacitor DACs, low sensitivities to process variations and jitter noise are the greatest advantages of the discrete-time  $\Sigma\Delta$  ADC because of the usage of the switch-capacitor filters and DACs. However, since the filter is after the signal sampler, an additional anti-alias filter before the ADC is needed

to prevent the aliasing effect. The total power consumption is therefore increased because of this additional anti-alias filter. Fig. 3.6 (a) presents the aliasing effect in the S/H. If an out-band blocker with the frequency of  $f_s+f_x$  is injected into a S/H with sampling frequency of  $f_s$ , the aliasing effect will move this out-band blocker to the frequency of  $f_s-f_x$ . This aliased blocker is thus in the band of interest and degrades the system performance. An additional anti-aliasing filter can attenuate the out-band blockers in advance and alleviate the aliasing effect as depicted in Fig. 3.6 (b).

Fig. 3.6. The aliasing effect of the sampling and hold circuit (a) without anti-aliasing filter (b) with anti-alias filter.

In addition, the speed of switch-capacitor (SC) filter is also constrained lower than few hundred MHz due to the operation fundamentals. In sampling phase, the input voltage needs to charge the sampling capacitor. The time-constant from the on-resistance of the switches and the sampling capacitor constraints the charge speed. In amplification phase, the amplifier needs certain time to react the large step at the input due to its limited bandwidth. The processing time in these two phases determines the operational speed of a SC filter. As a consequence, discrete-time  $\Sigma\Delta$  ADCs are performed for low frequency applications based on the current technologies and circuit design techniques. For continuous-time type, the S/H is located after the loop filter. The filter operates as an anti-alias filter. Besides, the speed of the filter can be up to GHz range based on the topology and the realization. Therefore, in most of the bandpass  $\Sigma\Delta$  ADC applications, continuous-time type is the choice to achieve the specifications [10].

- 1. The speed limit: the speed of DT  $\Sigma\Delta$  ADC is limited by the amplifier's bandwidth and slew rate and the settling time during each transition. In contrast, the CT  $\Sigma\Delta$  ADC operates continuously without any transition and the requirement of the amplifier's bandwidth is relaxed.

- 2. The need of extra anti-aliasing filter in front of ADC: The DT  $\Sigma\Delta$  ADC requires an additional anti-aliasing filter before the S/H to attenuate the power of the outband blockers that will alias back into baseband. In CT  $\Sigma\Delta$  ADC, the loop filter can perform as the anti-alias filter because of its S/H.

With a decision on the categories of  $\Sigma\Delta$  ADCs, next step is to determine the architecture of the loop filter.

## 3.1.3 The architecture of the loop filter: CRFF and CRFB

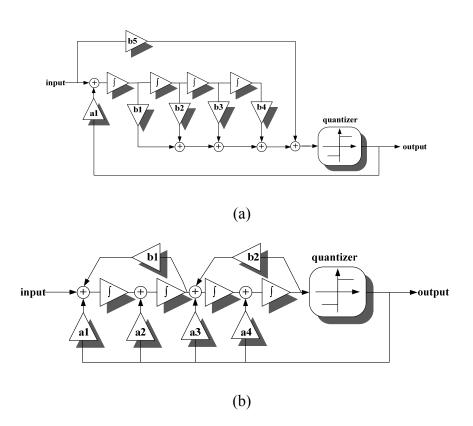

Based on the architecture of the loop filter,  $\Sigma\Delta$  ADCs can be also divided into two different topologies: the cascade of resonators with feed forward (CRFF) and the cascade of resonators with feedback (CRFB). These two topologies can be implemented in both discrete-time and continuous-time domains.

Taking a  $4^{th}$ -order CT  $\Sigma\Delta$  ADC for example, Fig. 3.7 shows two different architectures. In CRFF architecture all the output of the integrators feed forward to the input of the quantizer and there is an additional path directly from input to the quantizer. In CRFB, instead of feed-forward paths, there are feedback paths between integrators and DACs. Both architectures have enough degree of freedom to control the desired STF and NTF, and both have their own advantages and drawbacks.

In CRFF, synchronization issues are minimum since there is only one feedback DAC. The input signal is directly passed to the input of the quantizer through b5 path in CRFF making the swing of the internal nodes between integrators smaller and relaxing the linearity requirement of the filters. However, the design of the adder in front of the quantizer in CRFF is a challenge especially in the application with high sampling frequency. The adder is connected to several resistive and capacitive loads but the bandwidth requirement is extremely large to prevent excessive loop delay. In addition, with non-ideal integrators in the ADCs, the out-band blocker rejection is minimized in CRFF due to the b1 feedforward path. Fig. 3.8 depicts the difference of the out-band blocker rejections in  $2^{nd}$ -order  $\Sigma\Delta$  ADCs with CRFF and CRFB architectures by comparing their STFs. Both ADCs have the same NTF.  $2^{nd}$ -order and  $1^{st}$ -order out-band blocker attenuations are achieved in CRFB and CRFF architectures respectively. In

currently reported works, both architectures are popular based on the different applications and different considerations.

Fig. 3.7. Two different architectures of loop filter in  $\Sigma\Delta$  ADC (a)CRFF (b)CRFB.

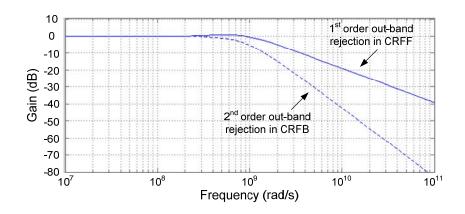

Fig. 3.8. The comparison of STFs in CRFF and CRFB architectures.

## 3.1.4 Multi-stage noise-shaping (MASH)

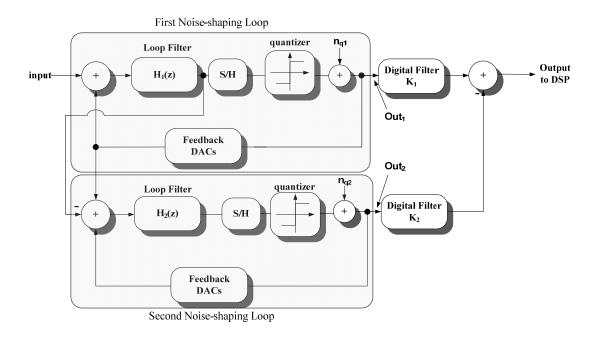

The MASH architecture was developed to achieve higher resolution. In this architecture, by cascading the noise-shaping loop, the actual order of noise-shaping can be higher than that of each individual loop. The DT architecture is plotted in the Fig. 3.9.

Fig. 3.9. The architecture of a DT MASH  $\Sigma\Delta$  ADC.

The main concept of the  $\Sigma\Delta$  ADC is to shape the quantization noise of the first loop again by employing a second loop. Suppose the quantization noise in the first loop and the second loop are  $n_{q1}$  and  $n_{q2}$ , respectively. The output of the quantizer in first loop and that in the second loop will be given as

$$Out_1 = STF_1 \cdot input + NTF_1 \cdot n_{q1}$$

(3.5)

$$Out_2 = STF_2 \cdot n_{a1} + NTF_2 \cdot n_{a2} \tag{3.6}$$

By designing the digital filters  $K_1$  and  $K_2$  with the relation as below

$$K_1 \cdot NTF_1 = K_2 \cdot STF_2 \tag{3.7}$$

A solution that  $K_1=k\cdot STF_2$  and  $K_2=k\cdot NTF_1$  (k is a constant) is able to be reached from (3.7). As a result, the overall output will be

$$Out = K_1 \cdot Out_1 - K_2 \cdot Out_2 = k \cdot STF_1 \cdot STF_2 \cdot input - k \cdot NTF_1 \cdot NTF_2 \cdot n_{g2} \quad (3.8)$$

The quantization noise in the first loop is perfectly cancelled out while that in the second loop is noise-shaped by NTF<sub>1</sub> and NTF<sub>2</sub>. If second order loops are used, the overall noise-shaping is now fourth order. In the ideal case, this is an excellent solution that an architecture achieves the same noise-shaping with less order loop filter and thus better stability condition.

However, under PVT variations, the equation (3.7) may not be satisfied. (3.9) presents the output of the ADC with variations. NTF<sub>1</sub>' and STF<sub>2</sub>' are the actual transfer functions composed by NTF<sub>1</sub>+NTF<sub>1 $\Delta$ </sub> and STF<sub>2</sub> NTF<sub>2 $\Delta$ </sub>, respectively. The terms of NTF<sub>1 $\Delta$ </sub> and STF<sub>2 $\Delta$ </sub> are the errors due to PVT variations. The output of the ADC is now as

$$Out = K_1 \cdot Out_1 - K_2 \cdot Out_2 = k \cdot \left(STF_1 \cdot STF_2 \cdot input + NTF'_1 \cdot STF_2 \cdot n_{q1}\right) - k \cdot \left(NTF_1 \cdot STF'_2 \cdot n_{q1} + NTF_1 \cdot NTF_2 \cdot n_{q2}\right)$$

(3.9)

An additional term of  $k \cdot (STF_2NTF_{1\Delta}-NTF_1STF_{2\Delta}) \cdot n_{q1}$  in the overall output results in more serious degradation on quantization noise performance of the  $\Sigma\Delta$  ADC as depicted in (3.10).

$$Out = k \cdot STF_1 \cdot STF_2 \cdot input - k \cdot NTF_1 \cdot NTF_2 \cdot n_{q2} + k \cdot n_{q1} (STF_2 \cdot NTF_{1\Delta} - NTF_1 \cdot STF_{2\Delta})$$

(3.10)

The issue is called noise leakage and is the dominant problem when designing a MASH architecture. Typically, 5% coefficient mismatch results in 6dB SNR degradation in a MASH21  $\Sigma\Delta$  ADC [11]. Normally DT MASH  $\Sigma\Delta$  ADC is more popular than CT MASH architecture since the switch-capacitor filters can achieve higher design accuracy than any other analog filters. This accuracy will help the system to hold the relation in equation (3.7). Therefore, in high speed applications, the MASH architecture is not a proper option for the  $\Sigma\Delta$  ADCs.

## 3.1.5 DAC pulse selection

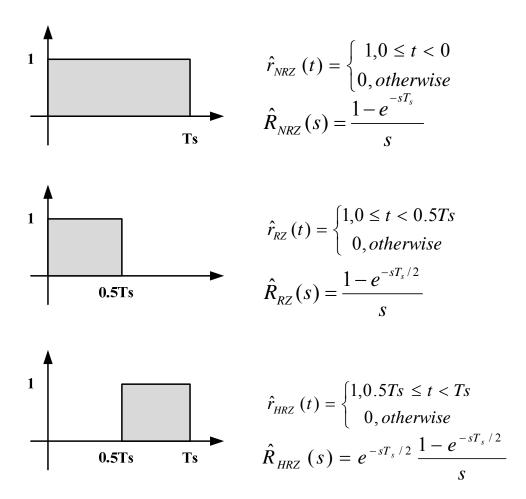

There are mainly three typical DAC pulses used in the continuous-time  $\Sigma\Delta$  ADCs: return-to-zero (RZ), half-delayed-return-to-zero (HRZ), and non-return-to-zero (NRZ). The waveform of these three DAC pulses and the describing equations are depicted in Fig. 3.10 [10].

Every DAC pulses result in different s-domain transfer function when processing impulse invariant to convert the desired Z-domain NTF. Due to the characteristics of different pulses, these three kinds of DAC pulses have different sensitivities to jitter effects and excess loop delay. For example, as will be demonstrated in the following sections, the NRZ presents less sensitivity to jitter effects but is more sensitive to the excess loop delay; the RZ is worse on jitter but performs better with excess loop delay while the HRZ has poor performances on both jitter effect and excess loop delay. The detail of the reasons in these effects will be discussed in the jitter and excess loop delay sections. Therefore, before designing a  $\Sigma\Delta$  ADC, an important decision on DAC pulses is definitely required based on the specifications and applications on jitter effect and excess loop delay.

Fig. 3.10. Common DAC pulses.

#### 3.2 Design Issues of A Continuous-Time $\Sigma\Delta$ ADC

The  $\Sigma\Delta$  ADC achieves high resolution without employing a high-bit quantizer by noise-shaping the quantization noise with the loop filter. However, the quantization noise is not the only noise source presented in the loop. Other noise sources and non-linearities from the components in the system would affect the performance and degrade the system resolution. Being aware of all the physical sources of related non-idealities and currently reported solutions would help developing new techniques to alleviate the issues.

### 3.2.1 Stability

Stability is always an issue in closed loop systems. Especially when increasing the order of the loop filter to achieve better resolution, the stability of the closed loop system is threatened by additional zeros and poles [12]. To check the stability of the system, the phase portrait technique can be utilized in both CT and DT  $\Sigma\Delta$  ADC architectures since a  $\Sigma\Delta$  ADC is a non-linear close loop system [13].

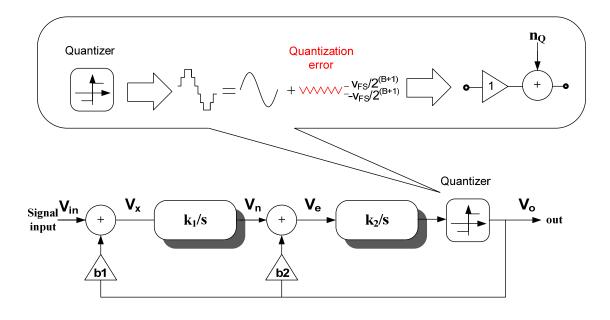

Suppose there is a  $2^{nd}$ -order  $\Sigma\Delta$  ADC as shown in Fig. 3.11 where the quantizer is modeled as an unity gain stage with the addition of the quantization error term  $n_Q$  due to its operational characteristics. Vin, Vx, Vn, and Ve are the voltage of different nodes in the system. Under the assumption of sinusoidal wave operation in the quantizer, the  $n_Q$  can be model as

$$n_q = \frac{8}{\pi^2} \cdot \frac{v_{FS}}{2^{(B+1)}} (\sin(w_s t) - \frac{1}{9} \sin(3w_s t) \cdot \dots)$$

(3.11)

Based on the loop analysis, an ODE equation can be obtained as

$$v_e = k_1 v_{in} - b_1 \frac{16}{\pi^2} \frac{v_{FS}}{2^{(B+1)}} \cdot OSR \frac{16}{\pi^2} \frac{v_{FS}}{2^{(B+1)}} + f_s \cdot OSR - b_2 v_e - b_1 k_1 \cdot v_e$$

(3.12)

Fig. 3.11. A 2nd-order  $\Sigma\Delta$  ADC with approximated quantizer model.

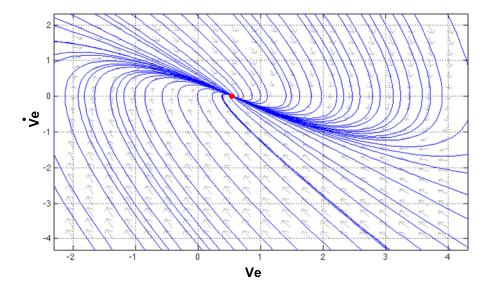

From (3.12), all the coefficients such as the full scale and bit number of the quantizer, OSR, sampling frequency, the amplitude of input signal, and the feedback parameters will determine the stability condition of the system. Commands "dfield7" or "pplane7" in Matlab can help solving (3.12) with different initial conditions and the result is depicted in Fig. 3.12. From Fig. 3.12, since all lines are converged into a point, it presents that the  $2^{nd}$ -order  $\Sigma\Delta$  ADC with 2-bit quantizer, 40 of OSR, and 800MHz sampling frequency is stable.

Fig. 3.12. The phase portrait of a 2nd-order  $\Sigma\Delta$  ADC.

For the higher order  $\Sigma\Delta$  ADC, the phase portrait analysis can be used as well and the higher order ODE equation from the system will be obtained. By plotting the speed of error versus error magnitude as Fig. 3.12, the stability conditions of the system with different system coefficients and different initial conditions can be estimated. Thus, the sufficient stability condition can be achieved during the system planning phase. The simulation-based stability check in the system simulation phase is also recommended to confirm the system stability.

#### 3.2.2 Non-linearities

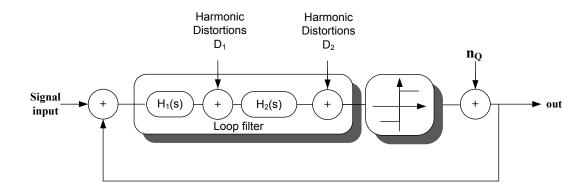

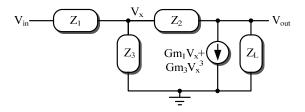

In a single-bit  $\Sigma\Delta$  ADC, the sources of non-linearities are basically from the non-linearities of the loop filter. As shown in Fig. 3.6, either CRFF or CRFB has integrators in the loop filter. The non-linear Op-amps within the integrators contribute the harmonic distortions, which degrade the resolution of the ADC. By assuming there are two filter stages in loop filter, Fig. 3.13 models the distortion contribution of each filter stage as extra terms D1 and D2.

Fig. 3.13. The model of the non-linearities from loop filter in a  $\Sigma\Delta$  ADC.

The closed loop transfer function for  $D_1$  and  $D_2$  thus can be determined as below.

$$\frac{out}{D_1} = \frac{H_2(s)}{1 + H(s)} \tag{3.13}$$

$$\frac{out}{D_2} = \frac{1}{1 + H(s)} = NTF \tag{3.14}$$

(3.13) and (3.14) show that the distortions of the second stage are noise-shaped as the quantization noise and that of the first stage are partially noise-shaped by the loop; this

makes the non-linearity of the first filter stage dominate the linearity performance of a  $\Sigma\Delta$  ADC.

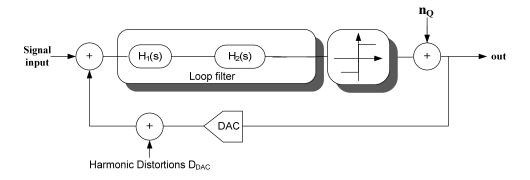

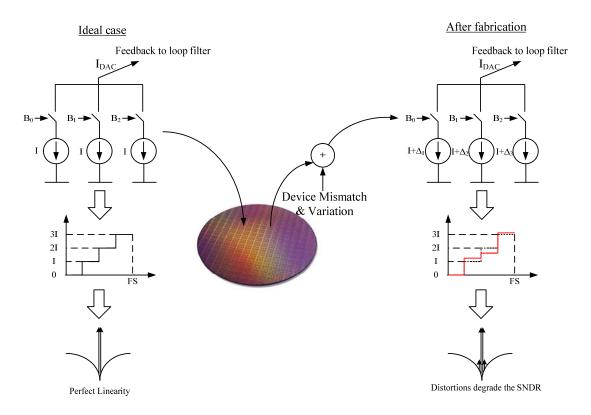

If increasing the bit number of the quantizer, another critical linearity issue appears: the unit current source mismatch in multi-level DACs. This mismatch generate the distortions D<sub>DAC</sub> at the output of the DAC as depicted in Fig. 3.14. Since the DAC is connected to the input stage, DDAC will pass through the system as input signal and degrades the performance of the ADC. Taking a 2-bit  $\Sigma\Delta$  ADC with switch current DACs as shown in Fig. 3.15, there are three identical current sources controlled by the thermometer code from the output of the quantizer to produce a four-level feedback. In ideal case, the current of the current sources are identical and, hence, there is no distortion in the two-tone test of a  $\Sigma\Delta$  ADC. However, random static mismatches between devices are presented in all the components and transistors in the chip; this mismatch changes the current flowing on current sources by random errors  $\Delta_1, \ \Delta_2, \ \Delta_3.$ The differences between levels of the feedback are no longer identical and thus the static mismatch introduces the distortions into the system. This non-linearity from the DAC feeding the signal back to the input stage is not noise-shaped by the closed loop and the signal-to-noise-and-distortion ratio (SNDR) of the system is hence degraded. Therefore, without a solution for this issue, the improvement on ADC resolution by increasing the number of bits in the DAC and quantizer is limited.

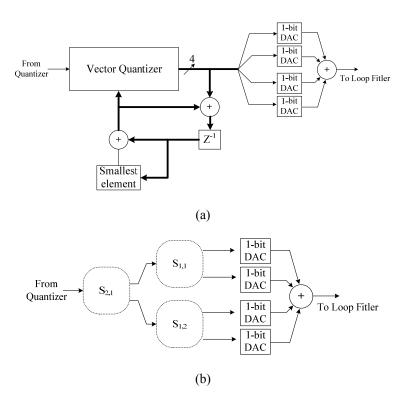

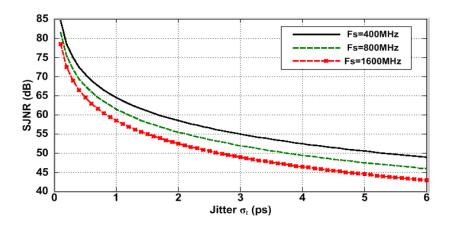

To alleviate this issue, several solutions have been reported; e.g. noise-shaping dynamic element matching loop (NSDEM) [14], tree-structure DEM [15], Dataweighted algorithm (DWA [16]) or butterfly shuffler [17]. These techniques either randomize or shape the non-linearity, as shown in Fig. 3.16.

Fig. 3.14. The model of the distortions from DAC in a  $\Sigma\Delta$  ADC.

Fig. 3.15. The source of device mismatch and the effect on the resolution of a 2-bit  $\Sigma\Delta$  ADC.

By building a close loop system in DACs, NSDEM (Fig. 3.15 (a)) technique employs noise-shaping DACs in a  $\Sigma\Delta$  ADC to attenuate the non-idealities from the DACs including the distortions. Tree-structure DEM (Fig. 3.15 (b)), DWA (Fig. 3.15(c)) and Butterfly shuffler (Fig. 3.15 (d)) all uses the switches or shifters controlled by the pseudo-random codes generated by the digital logic circuitry to randomly connect the DACs to different output codes from the quantizer. This randomization translates the static errors (distortions) into dynamic errors (white noise) and hence, the SNDR is improved when the distortions dominate the ADC resolution. The threat to the system stability is the common issue of these four techniques due to the delay contribution from the extra processing in the feedback path.

Fig. 3.16. Four general different schemes to randomize or shape the mismatch (a) NSDEM (b) tree-structure DEM.

Fig. 3.16. Continued (c) DWA (d) butterfly shuffler.

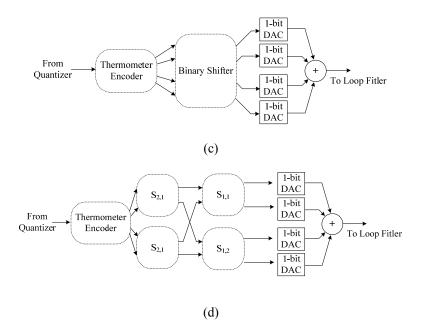

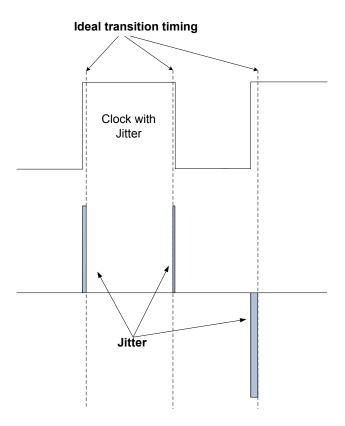

# 3.2.3 Jitter effect