# HIGH GAIN TRANSFORMERLESS DC-DC CONVERTERS FOR RENEWABLE ENERGY SOURCES

A Thesis

by

## NICHOLAS AARON DENNISTON

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

May 2010

Major Subject: Electrical Engineering

# HIGH GAIN TRANSFORMERLESS DC-DC CONVERTERS FOR RENEWABLE ENERGY SOURCES

## A Thesis

by

## NICHOLAS AARON DENNISTON

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Approved by:

Co-Chairs of Committee, Prasad Enjeti

Shehab Ahmed

Committee Members, Shankar Bhattacharyya

Chanan Singh

Emil Straube

Head of Department, Costas Georghiades

May 2010

Major Subject: Electrical Engineering

#### **ABSTRACT**

High Gain Transformerless DC-DC Converters

for Renewable Energy Sources. (May 2010)

Nicholas Aaron Denniston, B.S., Texas A&M University

Co-Chairs of Advisory Committee: Dr. Prasad Enjeti

Dr. Shehab Ahmed

Renewable energy sources including photovoltaic cells, fuel cells, and wind

turbines require converters with high voltage gain in order to interface with power

transmission and distribution networks. These conversions are conventionally made

using bulky, complex, and costly transformers. Multiple modules of single-switch,

single-inductor DC-DC converters can serve these high-gain applications while

eliminating the transformer.

This work generally classifies multiple modules of single-switch, single-inductor

converters as high gain DC-DC converters transformers. The gain and efficiency of both

series and cascade configurations are investigated analytically, and a method is

introduced to determine the maximum achievable gain at a given efficiency. Simulations

are used to verify the modeling approach and predict the performance at different power

levels. Experimental prototypes for both low power and high power applications

demonstrate the value of multiple module converters in high gain DC-DC converters for

renewable energy applications.

iii

# **DEDICATION**

To my family, for giving me everything I needed to succeed.

#### ACKNOWLEDGEMENTS

I would like to thank my committee co-chairs, Dr. Prasad Enjeti and Dr. Shehab Ahmed, and my committee members, Dr. Chanan Singh, Dr. Shankar Bhattacharya, and Dr. Emil Straube, for their guidance and support throughout the course of this research. Thanks go to Dr. Ahmed Massoud for his suggestions and guidance throughout my work, and to Dr. Jeehoon Jung for his valuable revisions and comments. I would also like to extend my gratitude to Qatar Foundation for providing the support and funding for my studies abroad.

Thanks also go to my colleagues and fellow students at the SEEC lab in Qatar and at the Power Electronics lab in College Station, especially Cole Dietert for his help in transferring much needed equipment and Ahmed Salah for his insights into my research.

I would also like to thank the technical staff at TAMU-Q, especially Rick Carusi for making my mechanical nightmares disappear and Abdallah Al-Mardawi for the numerous suggestions and assistance that were invaluable to the completion of my work.

Finally, thanks to my family and to my fiancée – for your unfailing support, and for never asking if I was finished with my thesis yet.

## **NOMENCLATURE**

BB Buck-boost

CCCS Current-controlled current source

CCM Continuous conduction mode

DCM Discontinuous conduction mode

EAR Equivalent averaged resistance

ESR Equivalent series resistance

FC Fuel cell

$f_S$  Switching frequency

HVDC High voltage direct current

$i_x$ ,  $v_x$  Instantaneous current, voltage of node x

$I_x$ ,  $V_x$  Average current, voltage of node x

$I_{x-rms}$ ,  $V_{x-rms}$  Root-mean-square value of current, voltage of node x

pu Per-unit value

PV Photovoltaic

PWM Pulse-width modulation

*RF* Ripple factor

$r_x$  Resistance (actual) of branch x

$r_X$  Equivalent averaged resistance of branch x

SCR Silicon-controlled rectifier (thyristor)

# **TABLE OF CONTENTS**

|             |                                                                                                                                                               | Page                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ABSTRACT    |                                                                                                                                                               | iii                        |

| DEDICATION  | ON                                                                                                                                                            | iv                         |

| ACKNOWL     | EDGEMENTS                                                                                                                                                     | V                          |

| NOMENCL     | ATURE                                                                                                                                                         | vi                         |

| TABLE OF    | CONTENTS                                                                                                                                                      | vii                        |

| LIST OF FIG | GURES                                                                                                                                                         | ix                         |

| LIST OF TA  | BLES                                                                                                                                                          | xi                         |

| CHAPTER     |                                                                                                                                                               |                            |

| I           | INTRODUCTION                                                                                                                                                  | 1                          |

|             | 1.1. Renewable energy sources 1.2. Limitations of conventional boost converters 1.3. Survey of existing research 1.4. Research objective 1.5. Thesis outline  | 1<br>3<br>5<br>7<br>9      |

| II          | CONDUCTION LOSS MODELING                                                                                                                                      | 11                         |

|             | 2.1. Principle of energy conservation 2.2. Per-unit system 2.3. Conduction losses in CCM converters 2.4. Conduction losses in DCM converters 2.5. Conclusions | 11<br>14<br>14<br>17<br>19 |

| HAPTER  |                                                                  | Page |

|---------|------------------------------------------------------------------|------|

| III     | MULTIPLE MODULE CONVERTER SYSTEMS                                | 20   |

|         | 3.1. Description                                                 | 20   |

|         | 3.2. Cascade modeling                                            |      |

|         | 3.3. Series modeling                                             | 27   |

|         | 3.4. Simulations and performance comparison                      | 31   |

|         | 3.5. Conclusions                                                 |      |

| IV      | A DCM-OPERATED HIGH GAIN CONVERTER FOR                           |      |

|         | LOW POWER APPLICATIONS                                           | 35   |

|         | 4.1. Introduction                                                | 35   |

|         | 4.2. DCM modeling.                                               | 37   |

|         | 4.3. Conduction losses in DCM                                    | 41   |

|         | 4.4. DCM design procedure                                        | 45   |

|         | 4.5. Design example                                              |      |

|         | 4.5.1. Simulation results                                        |      |

|         | 4.5.2. Experimental results                                      |      |

|         | 4.6. Conclusions                                                 | 57   |

| V       | HIGH GAIN CONVERTER CONFIGURATIONS FOR HIGHER POWER APPLICATIONS | 59   |

|         |                                                                  |      |

|         | 5.1. Introduction                                                |      |

|         | 5.2. Design example and simulation                               |      |

|         | 5.3. Evaluation of multiple module approach in HVDC converters   |      |

|         | 5.3.1. Conventional HVDC converter                               |      |

|         | 5.3.2. Full-bridge converter                                     |      |

|         | 5.3.3. Multiple module cascade boost converter                   |      |

|         | 5.3.4. Multiple module series hybrid converter                   |      |

|         | 5.3.5. Discussion                                                | 73   |

|         | 5.4. Prototype circuits                                          |      |

|         | 5.5. Conclusions                                                 | 80   |

| VI      | CONCLUSIONS                                                      | 81   |

|         | 6.1. Summary of work                                             | 81   |

|         | 6.2. Future work                                                 | 83   |

| EFERENC | CES                                                              | 84   |

| ITA     |                                                                  | 88   |

# LIST OF FIGURES

| FI | GURE |                                                                                        | Page |

|----|------|----------------------------------------------------------------------------------------|------|

|    | 1    | Boost gain (CCM) vs. duty cycle D                                                      | 4    |

|    | 2    | Definition of ripple factor (RF)                                                       | 13   |

|    | 3    | CCM boost converter model with averaged parasitic elements reflected into diode branch | 16   |

|    | 4    | Generalized CCM boosting converter DC model with parasitic losses                      | 16   |

|    | 5    | Branch currents in DCM                                                                 | 17   |

|    | 6    | Generalized DCM boosting converter DC model with parasitic losses                      | 19   |

|    | 7    | Multiple module converter configurations                                               | 21   |

|    | 8    | Multiple module cascade converters                                                     | 22   |

|    | 9    | Practical multiple module series boost converter                                       | 27   |

|    | 10   | Multiple module series BB and series hybrid converters                                 | 28   |

|    | 11   | Simulation results for pu CCM multiple module converters: gain and efficiency          | 32   |

|    | 12   | DCM series hybrid synchronous converter                                                | 37   |

|    | 13   | Current-controlled current source model of PWM switch in DCM                           | 39   |

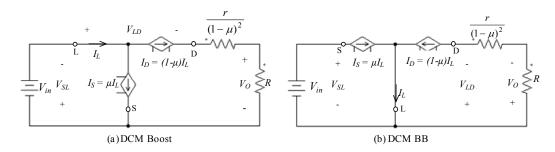

|    | 14   | DC averaged models for DCM synchronous boosting converters                             | 40   |

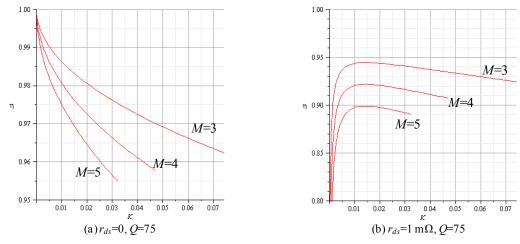

|    | 15   | Determining optimal <i>K</i> for maximum efficiency in DCM synchronous operation       | 44   |

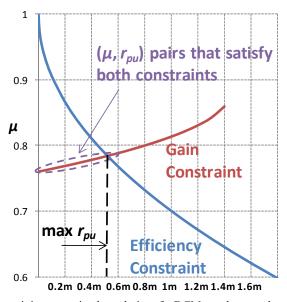

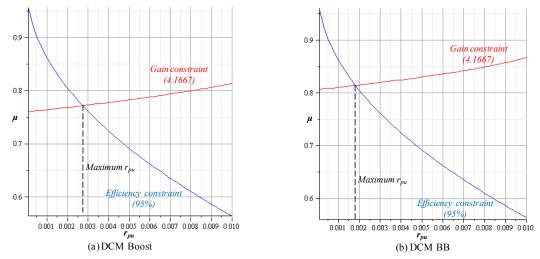

|    | 16   | Determining operating boundaries of a DCM synchronous boost converted                  | r 46 |

|    | 17   | Determining maximum allowable MOSFET resistances for design example                    | 49   |

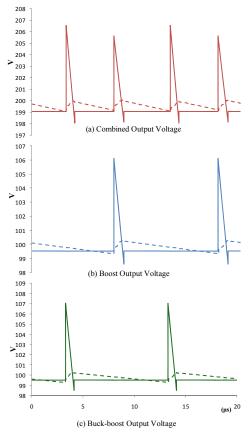

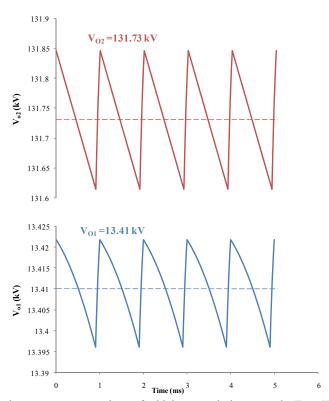

|    | 18   | DCM synchronous series hybrid (Fig. 12) simulated output voltages (Level 0)            | 52   |

| FIGURI | 3                                                                                   | Page |

|--------|-------------------------------------------------------------------------------------|------|

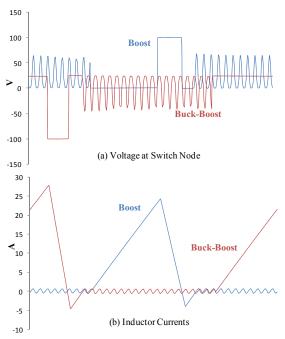

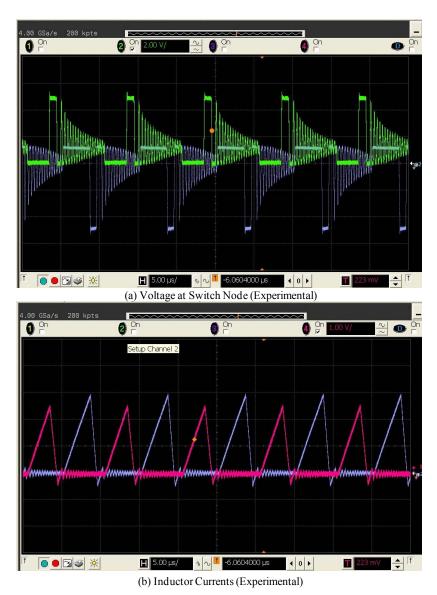

| 19     | Simulated oscillation at switch node from MOSFET drain-source capacitance (Level 2) | 54   |

| 20     | Oscillation at switch node from MOSFET drain-source capacitance (experimental)      | 56   |

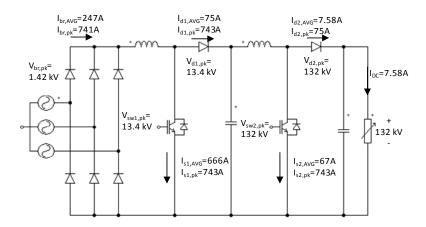

| 21     | High voltage multiple module cascade boost converter for high power design example  | 62   |

| 22     | Simulated converter output voltages for high power design example                   | 65   |

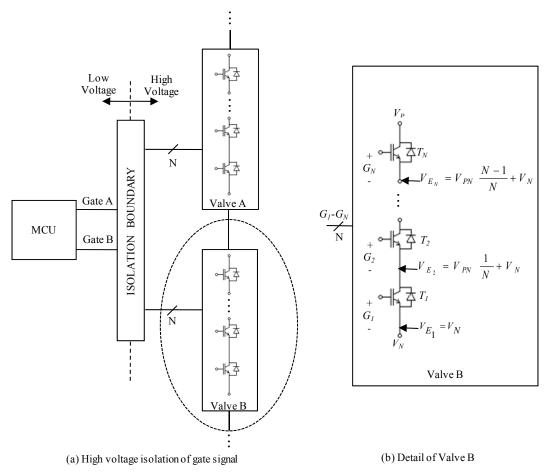

| 23     | Gate drive isolation for valves                                                     | 68   |

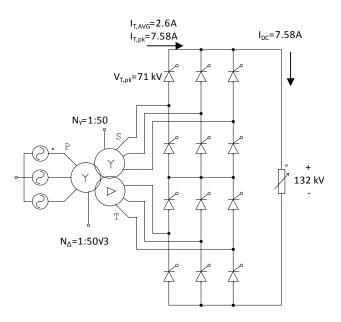

| 24     | Conventional HVDC (Approach A)                                                      | 69   |

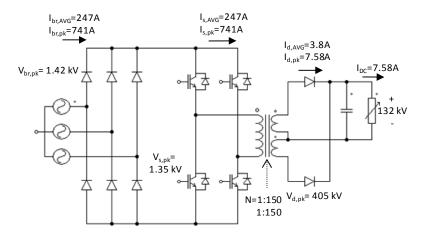

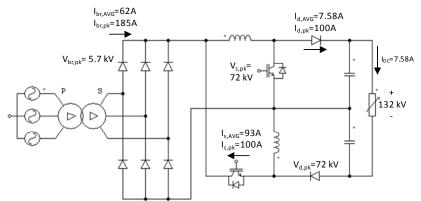

| 25     | Full-bridge converter (Approach B)                                                  | 70   |

| 26     | Multiple module cascade boost converter (Approach C)                                | 71   |

| 27     | Multiple module series hybrid converter (Approach D)                                | 73   |

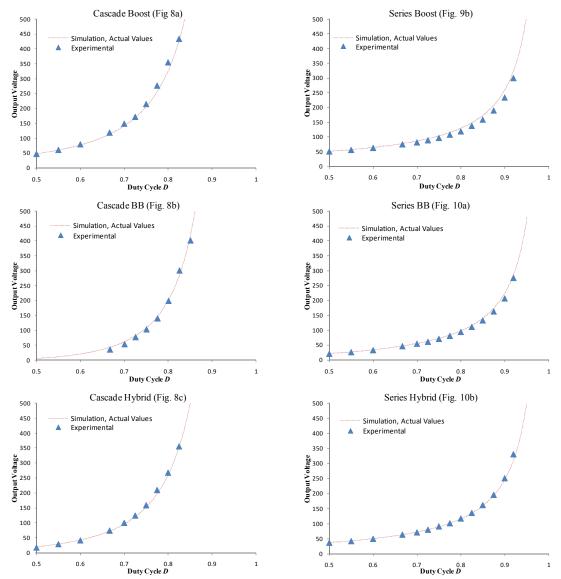

| 28     | Experimental output voltages of low power multiple module converter prototypes      | 79   |

## LIST OF TABLES

| ΓABLE |                                                                                                                        | Page |

|-------|------------------------------------------------------------------------------------------------------------------------|------|

| 1     | Cascade CCM converters: maximum duty cycles and gains for 95% efficiency                                               | 25   |

| 2     | Series CCM converters: maximum duty cycles and gains for 95% efficiency                                                | 29   |

| 3     | Simulation circuit parameters for pu CCM converters                                                                    | 32   |

| 4     | Comparison of simulated and calculated results for maximum duty cycles in pu CCM converters at $\eta$ =95%, $RF$ =0.50 | 33   |

| 5     | Summary of pu CCM multiple module configurations                                                                       | 34   |

| 6     | Gain and efficiency equations for DCM synchronous boosting converters                                                  | 41   |

| 7     | Design specifications for DCM series hybrid synchronous converter (Fig. 12)                                            | 48   |

| 8     | Procedure to determine circuit parameters for design example                                                           | 50   |

| 9     | Summary of losses in simulated DCM converter (Fig. 12) with electrolytic capacitors                                    | 51   |

| 10    | Summary of experimental results for DCM synchronous series hybrid converter (Fig. 12)                                  | 56   |

| 11    | Converter specifications for high power design example (Fig. 21)                                                       | 62   |

| 12    | Component values for high power design example (Fig. 21)                                                               | 64   |

| 13    | Comparison of calculated and simulated results for high power design example (Fig. 21)                                 | 65   |

| 14    | Comparison of HVDC approaches: device ratings, device counts, isolation levels                                         | 74   |

| 15    | Prototype circuit parameters and device data                                                                           | 76   |

#### **CHAPTER I**

#### INTRODUCTION

## 1.1 Renewable energy sources

The supply and conversion of energy is of critical importance to the safety and sustainability of human life. For years fossil fuels such as coal and oil have formed the backbone of the energy supply chain, but the rapid growth of both population and energy demand has exposed the limitations of these fuels. Fossil fuels are a limited resource, and it is widely accepted that most easily extracted reserves will be exhausted within about thirty years. Additionally, the combustion of fossil fuels releases greenhouse gasses such as carbon dioxide which are believed to contribute to global warming. Presently most oil reserves are found in politically instable regions, and developed nations spend large amounts of money in both defense spending and foreign aid to ensure secure fuel supplies from these regions. The myriad economic, environmental, and political challenges inherent to fossil fuels have sparked great interest in renewable energy sources (RES) such as photovoltaic energy, fuel cells, and wind power.

It is estimated that the amount of solar energy that strikes this planet daily is more than one thousand times the current global energy demand [1]. Solar energy can be converted to electrical energy with photovoltaic (PV) cells, which are specialized semiconductors that generate electrical current when irradiated with light. PV cells can be connected in series to generate higher voltages and paralleled to generate higher curr-

This thesis follows the style of *IEEE Transactions in Power Electronics*.

ents, but manufacturing and materiel restrictions limit the number of cells that can be combined. PV cells exhibit a power source characteristic, so the output voltage of a PV assembly varies inversely with the current drawn by the connected load; a 24 V nominal cell will provide 48 V at light loads but only 24 V at full rated power. The low output voltage and its wide fluctuation present challenges in the design of power electronics converters that interface the PV cell to the grid.

Fuel cells (FC) are electrochemical devices that use a chemical reaction to convert hydrogen fuel into electrical energy. Hydrogen is drawn into a membrane where it is split into protons and electrons. The electrons are collected as electrical energy and used in an external circuit; on their return, the electrons combine with the protons and atmospheric oxygen to create water and heat. No toxic byproducts or greenhouse gasses are produced in the reaction, and the efficiency of the reaction is much higher than that of the internal combustion engine. Each cell produces electrical voltages on the order of 1 V, so several cells must be combined in series to create useful voltages. However, mechanical challenges in providing equal fuel and air flows limit the number of cells that can be combined. Like PV cells, fuel cells also exhibit a power source characteristic with a similar 2-to-1 output voltage variation over the full power range.

Wind power is a more mature technology, and more than 100 GW of capacity has been installed throughout the world. Wind energy is used as a prime mover to generate electrical power from rotating machines. While most PV and FC assemblies generate voltages on the order of tens of volts, wind turbines can be designed to generate voltages above one thousand volts. While this voltage can be easily integrated in small

amounts at the distribution level, many countries (Denmark, Spain, Germany, etc.) are turning to wind power to supply large percentages of their electrical energy usage. These large blocks of power can be moved much more efficiently at transmission level voltages on the order of hundreds or thousands of kilovolts, so power electronics converters with large DC conversion ratios are needed to interface wind farms with the grid.

All three of the methods discussed above generate electrical energy using clean, renewable energy without generating toxic byproducts or combustion gasses, and they are available throughout the globe without regard to national wealth or politics. These sources provide power at low voltage and high current (compared to output levels), and the large currents result in high semiconductor conduction losses that reduce efficiency. All three sources, whether for portable power or stationary bulk generation, also require power electronics converters with large DC conversion ratios in order to interface with the AC grid. This thesis discusses the design of power electronic converters that can interface renewable energy sources to the grid with high efficiency.

#### 1.2 Limitations of conventional boost converters

The ideal voltage transfer characteristic of the well-known single switch boost converter can be derived from inductor volt-second balancing as I/(I-D) where D is the switch duty cycle. This ideal gain is reduced due to parasitic losses in semiconductor on-resistances, diode forward voltages, and inductor DC resistances. Fig. 1 shows the voltage gain of the conventional continuous conduction mode (CCM) boost converter plotted vs. D for several values of inductor DC resistance r (expressed as a percentage of

load resistance). For practical values of r in the low power range (between 1% and 5%) the maximum gain is limited to less than 5 V/V.

Fig. 1. Boost gain (CCM) vs. duty cycle D. Increasing inductor resistance quickly limits achievable gain.

Two problems with the voltage transfer function of the conventional boost converter are evident from Fig. 1:

1. The *1/(1-D)* characteristic requires large duty cycles for large voltage boosts. Large duty cycles are a problem at high frequencies when the switch may not have sufficient time to turn off before the start of the next switching period.

Parasitics such as inductor DC resistances limit gain at large duty cycles and result in low converter efficiencies. The dissipated energy causes heating and requires additional thermal management.

Many applications requiring high gain use transformers to provide additional voltage boosting. The transformer also provides galvanic isolation between input and output. While the general shape of the transfer characteristic is identical to Fig. 1, the magnitude is boosted by the turns ratio n of the transformer. This allows the converter to operate at a smaller duty cycle which in turn reduces conduction losses. The additional gain provided by the turns ratio is balanced by other design challenges. While properly designed transformers can reduce the voltage stress on the primary side switch, the voltage stress on the secondary diode is increased by the same factor. High frequency transformer cores introduce additional loss mechanisms, and ensuring tight couplings between primary and secondary windings becomes very difficult for large n. Uncoupled (leakage) inductance induces voltage spikes across semiconductors that must be managed with complicated or lossy snubber circuitry to avoid switch failure. Transformers are costly, complex, and bulky and make up a substantial portion of both circuit volume and circuit cost. In applications that do not require galvanic isolation it is highly desirable to eliminate the transformer entirely.

## 1.3 Survey of existing research

Several high gain transformerless DC-DC converters have been reported in the literature. An approach discussed in several proposed converters uses coupled inductors to extend gain, assist in turning off rectifier diodes, or both. Wai et al. [2] propose a

boost converter with a coupled inductor that provides both additional gain and regenerative snubbing. Wuhua et al. [3] propose a converter using a complicated coupled inductor to provide high gains and lossless snubbing. Wai et al. [4] propose a multiple-input converter for fuel cell vehicles that uses coupled inductors to provide additional gain and alleviate reverse recovery problems. Although these converters are called transformerless, the coupled inductors operate much like transformers with all of the associated benefits and disadvantages. Gain can be enhanced and switch stress can be reduced through proper choice of n, but diode stresses increase by the same factor. The circuits require complicated snubbers to alleviate the leakage energy of the coupled inductors which add to component counts and complexity. The design of coupled inductor magnetics is no less complicated than that of multiple-output, high-frequency transformers; inter-winding coupling must be very tight to minimize leakage inductances and avoid core saturation.

Luo et al. [5-7] describe an alternative series of high gain DC-DC converters known as Luo converters. Starting with either an inverse-SEPIC converter or a buckboost converter with output filter, Luo adds sets of capacitors, inductors, and diodes to reach high gains at low duty cycles. The low duty cycles allow greater converter efficiency even after accounting for the losses in the additional series elements, but both the component count and the converter order increase dramatically. The large number of components, multiple series semiconductor drops, and complicated small signal response appear to limit the practical applications of Luo converters.

Recent research has examined combinations of basic converter configurations. Ayyanar [8] and Giri [9] describe general input-output connections using multiple basic converter modules, although their work focuses mostly on ISOP (input-series, outputparallel) connections for large voltage step-down ratios. Vorperian [10] presents results of a 10kV-to-400V step-down converter using multiple low-voltage DC-DC forward converter modules. These approaches provide modularity, which increases reliability and simplifies maintenance; however, these approaches all use multiple high frequency isolation transformers to allow arbitrary series and parallel connections of the converter outputs. Palma et al. [11] and Duran-Gomez et al. [12] propose series connections of a single-level or two-level boost converter and an identical buck-boost converter to increase gain without additional circuit complexity. The combination of a boost converter and a buck-boost converter allows the use of a shared neutral and removes the need for transformer isolation when connecting the outputs in series. Cascade connections of multiple converters have been reported for some time, including the cascaded boost converter for server applications reported by Huber and Jovanovic in [13]. These latter three converters appear well suited for extension to general high gain transformer-less converters.

## 1.4 Research objective

The purpose of this research is to investigate the use of multiple modules of series- or cascade-connected transformerless DC-DC converters to provide the high voltage gain needed to interface renewable energy sources to electrical grids. Each multiple module converter arrangement will be analyzed generally in a per-unit system,

and semiconductor voltage and current stresses will be compared. Factors limiting gain and efficiency will be identified, and strategies for mitigating these factors will be discussed. The use of the multiple module approach for renewable energy sources will be studied in both low-power and high-power applications.

Low-power renewable energy applications use low voltage FC or PV sources that supply energy to a standard AC power interface such as a laptop power supply. Many standard PV or FC modules haves full load output voltages of 24 V, but a single-phase 120 V<sub>rms</sub> inverter requires a DC input of 200 V – a gain of more than 8 V/V. This work investigates the use of a series-connected multiple module converter operated in discontinuous conduction mode (DCM) to provide the necessary gain. The steeper voltage transfer characteristic of DCM operation results in larger gains at lower duty cycles, reducing conduction losses. DCM operation also allows the switch to turn on at zero current and the diode to turn off at zero current, reducing switching losses. The rectifier diode is replaced with a MOSFET synchronous rectifier to eliminate diode reverse recovery losses and to further reduce conduction losses. A series-connected multiple-module DCM converter is shown that achieves a gain of 8.33 V/V with low conduction losses.

In high-power applications renewable energy sources are connected to the grid and can supply large blocks of power. High voltage transmission reduces current-induced ( $I^2R$ ) losses in transmission lines and converters, and DC transmission allows power to be moved to distant demand centers more efficiently than AC transmission. The low per-unit parasitic elements and long switching periods available in high power

applications allow the use of CCM converters with large duty cycles. It is shown that multiple module configurations can achieve high gains at high efficiencies in these applications. The advantages of series- and parallel-connected multiple module configurations in high power HVDC transmission are demonstrated through simulations, comparisons to conventional approaches, and low-power prototypes achieving gains of up to 29 V/V.

#### 1.5 Thesis outline

Chapter I of this thesis introduces the challenges inherent in extracting usable electrical energy from renewable energy sources. The disadvantages of the conventional CCM boost converter are identified, and existing approaches to overcoming these disadvantages are presented.

Chapter II discusses the importance of efficiency in renewable applications and introduces the principle of energy conservation [14] to accurately model conduction losses in non-ideal single-switch boosting converters. Generalized models including conduction losses in CCM and DCM converters are developed that include effects of non-zero inductor current ripple.

Chapter III introduces the proposed multiple module approach. The series connection and the cascade connection are defined, and the six configurations of single-switch boosting converters are presented. Voltage gain and efficiency equations incorporating parasitic losses are derived in the per-unit system for each of the six configurations. Design considerations balancing gain and efficiency are developed, and the performance of the six configurations is compared through simulation. It is shown

that cascade converters can provide high gain, but efficiency falls off quickly at large duty cycles. It is also shown that series converters provide less gain, but high efficiency can be maintained over a wider range of duty cycles.

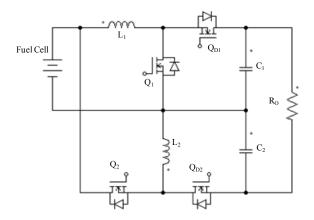

Chapter IV applies the concepts of the multiple module approach to low-power renewable energy sources. A series converter in DCM operation is used to overcome the poor slope of the CCM voltage transfer characteristic, and the output rectifier diodes of each converter are replaced with synchronous rectifiers to increase the efficiency. Full DC transfer functions including parasitic losses are derived using the principle of energy conservation and verified via simulation. A design procedure is developed based on efficiency and gain targets. Experimental results are shown for a converter that achieves a gain of 8.33 V/V at 200 W.

Chapter V applies the concepts of the multiple module approach to high-power wind energy generation. A design example is presented for a high voltage DC transmission (HVDC) application. The multiple module approach is then compared to other HVDC approaches and is shown to perform well in terms of component counts, voltage isolation levels, reliability, and semiconductor stresses. Experimental results from low power prototypes reaching gains up to 29 V/V are presented.

Chapter VI summarizes the results of the thesis, presents general conclusions on the applications of compound converters, and identifies areas of future study to advance the work.

#### **CHAPTER II**

#### CONDUCTION LOSS MODELING

## 2.1 Principle of energy conservation

In this chapter a method of accurately modeling conduction losses and efficiency is introduced. Efficiency is an important characteristic in high-gain renewable energy applications. Inefficient conversion of energy from renewable sources increases the number of sources needed to meet energy demand with a corresponding increase in cost. Heat from losses increases device failure rates and reduces reliability. For renewable sources in remote locations reduced reliability is a major concern. Thermal strategies for safely dissipating heat increase the size and cost of a converter. All of these concerns can be mitigated by high efficiency converters. Accurate models of conduction losses are essential for accurate predictions of converter accuracy.

Modeling strategies for DC-DC converters fall into two main categories: state-space averaging [15, 16] and averaged-circuit modeling [17, 18]. Both analysis techniques assume no ripple in the average inductor current when modeling parasitic losses like inductor DC resistances. Because losses are caused by rms currents, not average currents, and the rms value of terminal currents is always greater than or equal to the average value, the no-ripple assumption underestimates the losses incurred. While the errors from the no-ripple assumption are relatively small in CCM where the average and rms currents are close in value, this approach severely underestimates losses in DCM where the rms current is significantly larger than the average current. In both

cases, more accurate conduction loss models will provide better predictions of converter performance.

The principle of energy conversion [14] provides a powerful tool for accurately modeling conduction losses in DC-DC converters. The principle of energy conservation is used in averaged-circuit modeling to include non-zero ripple effects by replacing a parasitic element with an equivalent element. The equivalent element dissipates the same power when carrying the average current that the actual element dissipates when carrying the rms current. The equivalent element is used in place of the actual element for calculating DC transfer functions, small-signal transfer functions, and efficiencies.

Eq. (1) expresses the power relationship used in the principle of energy conservation and can be used to derive the equivalent averaged resistance (EAR) for any mode of operation by substituting in the correct relationship between average and rms currents. Note that parasitic elements modeled by an ideal DC voltage source, such as diode forward voltages, dissipate power only according to average currents and will not transform under this relationship.

$$I_{x,rms}^2 r_x = I_x^2 r_{x,EAR} \tag{1}$$

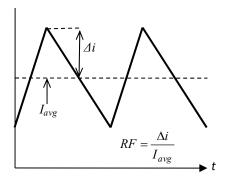

To apply the principle of energy conservation the relationship between the terminal average currents and rms currents must be known. For example, this relationship is given in CCM by (2), where the ripple factor RF is defined as the peak ripple amplitude divided by the average value (Fig. 2). The subscript 'x' is either L for inductor, S for switch, or D for diode. From (1-2), the EAR in CCM is given by (3). This resistance allows the effect of non-zero ripple current to be more accurately modeled.

Fig. 2. Definition of ripple factor (RF).

$$I_{x,rms} = I_x \sqrt{1 + \frac{RF^2}{3}} \tag{2}$$

$$r_{x,EAR} = \left(1 + \frac{RF^2}{3}\right) r_x \tag{3}$$

The principle of energy conservation also allows parasitic resistances from one branch to be reflected into a common circuit branch and summed. Eq. (1) can again be used for this reflection by replacing  $r_x$  with the EAR of (3) and observing the relationships between rms and average terminal currents. For the boost and buck-boost converters operating in CCM the average currents are related by (4), and the rms currents are related by (5). Note that all rms quantities in CCM are defined in terms of the average inductor current. Henceforth actual resistances will be designated with lower-case subscripts  $(r_s, r_{ds})$ , and an EAR will be designated with upper-case subscripts  $(r_s, r_{DS})$ . Resistances reflected from branch A to branch B will be designated as  $r_{A \rightarrow B}$ .

$$I_{L} = \frac{1}{D}I_{S} = \frac{1}{1 - D}I_{D} \tag{4}$$

$$I_{L,rms} = \sqrt{1 + \frac{RF^2}{3}} I_L = \frac{1}{\sqrt{D}} I_{S,rms} = \frac{1}{\sqrt{1 - D}} I_{D,rms}$$

(5)

The reflected EAR can be found from the substitution of (4) and (5) into (1). For example, the equivalent EAR of the switch on-resistance  $(r_S)$  in the inductor branch can be found by replacing  $r_S$  with  $r_S$  and  $r_{S,EAR}$  with  $r_{S,L}$  in (1). The EAR of the switch on-resistance  $(r_S)$  reflected to the inductor branch  $(r_{S,L})$  is then found from (1) and (5) by inspection as  $Dr_S$ .

## 2.2 Per-unit system

The per-unit (pu) system allows circuits of different power levels and operating voltages to be compared easily. Transforming a circuit into an equivalent representation in the per-unit system changes the device parameters, electrical quantities, and losses from absolute magnitudes into relative magnitudes. All quantities of interest in a circuit are normalized according to the input power and voltage, which are defined as the base quantities and are taken as equal to 1.

Once the base quantities have been determined, all other voltages and currents of interest are divided by the base quantity to give a normalized value. These normalized values can be directly compared to normalized values from other pu circuits without regard to actual voltage and current values; this allows the performance and losses of different circuits to be compared by inspection.

## 2.3 Conduction losses in CCM converters

The single-switch converters that provide boosting of the input voltage are the boost converter and the buck-boost converter, and they are henceforth referred to

collectively as the boosting converters. To demonstrate the use of the principle of energy conservation, the equivalent averaged parasitic elements will be determined for the boosting converters operating in CCM. The EARs will then be reflected into the diode branch. The following assumptions are made:

- 1. Diodes are modeled as a forward voltage  $V_f$ .

- 2. Switches are IGBTs and are modeled as a forward voltage  $V_f$ .

- 3. Inductor losses are modeled as a resistance  $r_l$ .

- 4. Switching and core losses are neglected.

- 5. Converters operate in continuous conduction mode (CCM).

- 6. The pu system is used with a normalized input voltage of 1 and a normalized input power of 1.

The EAR  $(r_L)$  of the inductor resistance  $r_l$  can be calculated from (1) and from the relationship between the average and rms current values in CCM given by (2) as shown in (3). Because the IGBT and diode are modeled as a DC voltage, they are not affected by ripple current; therefore, both elements are modeled with an equivalent averaged forward drop  $V_F = V_f$ . Now that the rms behavior has been encapsulated into averaged elements, the IGBT drop and inductor EAR can be reflected into the diode branch using the average current relationships. The calculations are shown in (6-7).  $V_{F,S}$  represents the forward drop of the IGBT in the switch branch, and  $V_{F,S \to D}$  represents this value reflected into the diode branch. Similarly,  $r_L$  represents the EAR of the inductor in the inductor branch, and  $r_{L,D}$  represents this value reflected into the diode branch.

$$V_{F,S}I_S = V_{F,S\to D}I_D \quad \to \quad V_{F,S\to D} = V_{F,S}\frac{I_S}{I_D} \quad \to \quad V_{F,S\to D} = V_{F,S}\frac{D}{1-D} \tag{6}$$

$$r_L I_L^2 = r_{L \to D} I_D^2 \to r_{L \to D} = r_L \frac{I_L^2}{I_D^2} \to r_{L \to D} = \frac{r_L}{(1-D)^2}$$

(7)

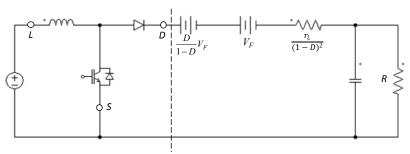

Fig. 3 shows the reflection of the equivalent averaged parasitic elements into the diode branch for a CCM boost converter. The portion of the circuit to the left of the dotted line is made up only of ideal elements, while the portion to the right (neglecting the capacitor) includes all parasitic elements in series with the load impedance. In a DC analysis the portion to the left of the dotted line is replaced with a CCM PWM switch model [17], and the inductor and capacitor are replaced by a short circuit and an open circuit, respectively. The voltage at the dotted line would then be given by the ideal gain of the boosting converter. This voltage can be treated generally as  $M_{ideal}V_{in}$  in the boosting converters without regard to the converter type as shown in Fig. 4.

Fig. 3. CCM boost converter model with averaged parasitic elements reflected into diode branch.

Fig. 4. Generalized CCM boosting converter DC model with parasitic losses.

#### 2.4 Conduction losses in DCM converters

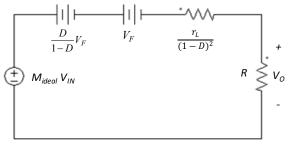

Converters operate in DCM when the inductor current falls to zero before the start of the next period. This mode of operation adds a third state where the current is zero in both the switch and the diode; additionally, the diode conduction interval becomes a function both of the switch conduction interval and of the load. The branch currents are shown in Fig. 5 where  $DT_S$  is the conduction interval of the switch and  $D_2T_S$  is the conduction interval is  $(D+D_2)T_S$ .

Fig. 5. Branch currents in DCM. All DCM current waveforms have triangular shapes.

The relationships between the average and rms values of each terminal current must be determined to calculate the parasitic EARs. Then the relationship between the average terminal currents must be determined to allow reflection of EARs into appropriate branches. The conduction losses in DCM boost and buck-boost converters will be modeled according to the following assumptions:

- 1. Converters operate in DCM.

- 2. Switches are MOSFETs and are modeled as a resistance  $r_{ds}$ .

- 3. MOSFET synchronous rectifiers are used in place of diodes and are modeled with a resistance  $r_{ds}$ .

- 4. Inductor losses are modeled as a resistance  $r_l$ .

Based on Fig. 5 the average and rms currents are given by (8) and (9), respectively. The EARs shown in (10) are obtained by substituting (8) and (9) into (1).

$$I_L = \frac{1}{2}i_{pk}(D + D_2)$$

$I_S = \frac{1}{2}i_{pk}D$   $I_D = \frac{1}{2}i_{pk}D_2$  (8)

$$I_{Lrms} = i_{pk} \sqrt{\frac{D+D_2}{3}} \qquad I_{Srms} = i_{pk} \sqrt{\frac{D}{3}} \qquad I_{Drms} = i_{pk} \sqrt{\frac{D_2}{3}}$$

(9)

$$r_{S} = \frac{4}{3} \frac{1}{D} r_{dS}$$

$$r_{D} = \frac{4}{3} \frac{1}{D_{2}} r_{dS}$$

$$r_{L} = \frac{4}{3} \frac{1}{D + D_{2}} r_{l}$$

(10)

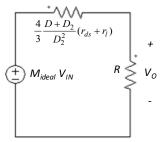

The next step is to reflect the switch and inductor EARs into the same branch, where they can be series-combined into a single parasitic resistance. Using (8) and (10) to reflect all resistances into the diode branch gives (after some algebra) the expression in (11). Using reasoning similar to the analysis of Section 2.3, the DCM boosting converters can be generally modeled as shown in Fig. 6. In Chapter IV a DCM modeling approach is presented that simplifies the expression of (11) into a form similar to (7).

$$r = \frac{4}{3} \frac{D + D_2}{D_2^2} (r_l + r_{ds}) \tag{11}$$

Fig. 6. Generalized DCM boosting converter DC model with parasitic losses.

## 2.5 Conclusions

In this chapter the importance of efficiency in renewable applications was discussed, and the principle of energy conservation was introduced to accurately model conduction losses. It was shown that increased losses from rms currents containing ripple can be modeled by using equivalent averaged parasitic elements. The relationships between average and rms terminal currents are developed for CCM and DCM converters, and the EARs are derived for both cases. Generalized models for the CCM and DCM converters considered in this work that incorporate parasitic elements are introduced.

#### **CHAPTER III**

#### MULTIPLE MODULE CONVERTER SYSTEMS

## 3.1 Description

Renewable energy sources often require high gain DC-DC converters to interface with the electric grid. Traditionally high gain DC-DC conversion has required transformer-based conversion. In low power applications, where operating frequencies are not limited by switching losses, the transformer is much smaller than a line-frequency transformer. However, the large turns ratios required for high gain require complex winding arrangements, and the converter must withstand large transient spikes from imperfect coupling between windings. Transformers in high power converters with limited operating frequency are much larger and still experience the same complexity and transient issues. Many renewable applications do not require galvanic isolation, so eliminating the transformer is highly desirable from cost and size perspectives.

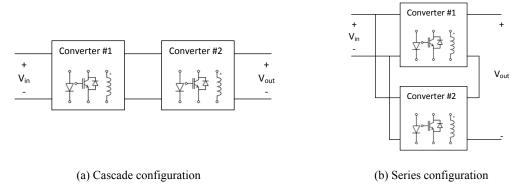

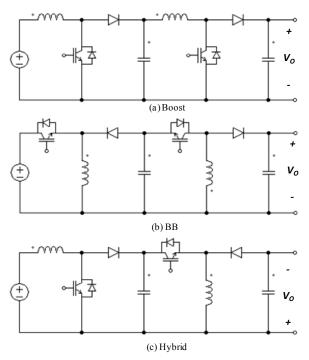

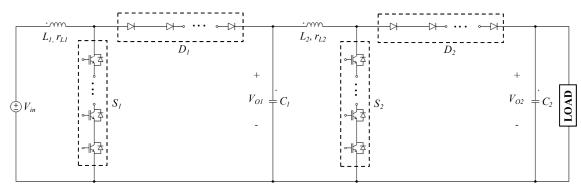

Multiple module DC-DC converters can provide high voltage gain and high efficiency while eliminating the transformer and its accompanying drawbacks. Converters can be arranged in cascade, where the output of the first converter becomes the input of the second (Fig. 7a), or in series, where the converter outputs are connected in series while the input source is shared (Fig. 7b). The multiple module approach is quite general, and many combinations of converter types and operating modes can be used. However, single-switch, single-inductor boosting converters (boost and buckboost) are especially suited for multiple module operation due to their simplicity and low

parts count. These converters also provide inherent voltage clamping; the voltage across the non-conducting semiconductor is clamped to a fixed voltage by the conducting semiconductor. The two types of single-switch boosting converters can be combined in three possible configurations for both series and cascade multiple module converters: boost/boost, buck-boost/buck-boost, and boost/buck-boost. These converters are referred to in this work as the boost, BB, and hybrid converters, respectively.

In this chapter expressions for gains and efficiencies are developed for the six converters introduced above, and the performances are compared. Parasitic losses are incorporated for better accuracy using the principle of energy conservation as discussed in Chapter II. Although the base analysis is independent of the type and operation mode of the base converters, for clarity the gain and efficiency expressions are extended to the specific examples of CCM converters using high-power IGBTs as the active switch and high-power diodes as the passive switch as in Section 2.3. Analysis will be extended to low-power DCM synchronous converters in Chapter IV.

Fig. 7. Multiple module converter configurations. Each converter is a single-inductor, single-switch converter.

## 3.2 Cascade modeling

The cascade configuration shown in Fig. 7a connects the output of the first converter to the input of the second converter. Each converter processes the full input power and must be rated accordingly. The three combinations of cascade multiple module converters are shown in Fig. 8. Each converter is characterized by a gain M, an input power P, and an output voltage  $V_O$ . This general characterization allows the converter gains and efficiencies to be derived without specifying the type of each converter as discussed in Chapter II. The converter module connected directly to the input source is designated as converter 1.

Fig. 8. Multiple module cascade converters.

To derive an equation for the total converter gain the loss elements are assumed equal on a pu basis for each converter. Converter 1 has a smaller pu output resistance  $(R_{O1pu}=V_{O1}^2/P=M_1^2)$  than Converter 2  $(R_{O2pu}=V_{O2}^2/P=M_1^2M_2^2)$ , so the parasitic resistance of the stage 1 has equal pu magnitude but smaller absolute magnitude than that of stage 2. It is also assumed that each converter is operated at the same duty cycle; while this assumption is not required, it simplifies the resulting equations for comparison purposes. Based on these assumptions the gain of the general cascade converters is given by (12), and the efficiency is given for the special case of CCM converters with IGBT switches and rectifier diodes in (13).  $M_i$  refers to ideal converter gain,  $\eta_i$  refers to the converter efficiency,  $V_{F,pu}$  refers to the pu IGBT/diode drop, and  $r_{L,pu}$  refers to the pu EAR of the inductor.

$$M_{casc} = M_1 M_2 \eta_1 \eta_2 \tag{12}$$

$$\eta_{i} = \left(1 - \frac{V_{F,pu}}{M_{i}(1-D)}\right) \left(\frac{1}{1 + \frac{r_{L,pu}}{(1-D)^{2}}}\right)$$

(13)

This equation neglects the increase in load that is seen by the first converter due to second stage parasitic resistance, but from substitution of Fig. 4 into the circuits of Fig. 8 it can be shown that, for small parasitic elements, this effect is only significant for D very near 1. At large enough duty cycles the parasitic resistance of the second stage dominates the load resistance, and the efficiency of the first stage approaches 50% (assuming equal pu resistances for each stage) while the efficiency of the second stage

approaches zero. For equal stage pu resistances of 0.001 and for D=0.9 there is less than 1% difference in stage efficiencies when neglecting this loading effect.

From (13), the combined IGBT/diode loss term is independent of duty cycle in CCM boost converters ( $M_i=1/(1-D)$ ). In CCM BB converters ( $M_i=D/(1-D)$ ) the combined IGBT/diode term is inversely dependent on D; however, for large gain ( $D\approx1$ ) the losses are approximately independent of duty cycle. The pu forward voltages are often negligible in high power devices; for example, the Eupec DD400S33K2C 3.3kV 400A IGBT shows a worst-case forward drop of 3.5V [19]. For a base input voltage of 1000V the pu forward voltage is only 0.0035 (0.35%). In the remainder of the analysis the combined IGBT/diode term will be neglected.

If the ripple factors in each converter are assumed equal, the  $\eta_1\eta_2$  term becomes  $\eta^2$  for any combination of converters. If the losses from the forward drop  $V_F$  are neglected, (13) can be solved for D as in (14) for converters operating in CCM. This equation gives the maximum cascade duty cycle in CCM that can achieve a specified efficiency under a constraining parasitic resistance.

$$D_{\text{max},casc} = 1 - \sqrt{r_{L,pu} \frac{\eta^{1/2}}{1 - \eta^{1/2}}}$$

(14)

The maximum duty cycle for an efficiency of 95% ( $D_{max}$ ) is calculated in Table 1 for different parasitic resistances and ripple factors using (14), where  $M_{tot}$  represents the overall gain of the CCM cascaded stages at this duty cycle. Small parasitic resistances and ripple factors extend the range of D over which high efficiencies can be achieved.

Table 1 Cascade CCM converters: maximum duty cycles and gains for 95% efficiency

| $r_{L, pu}$ | RF  |           | Boost<br>(Fig. 8a) | BB<br>(Fig. 8b) | Hybrid<br>(Fig. 8c) |

|-------------|-----|-----------|--------------------|-----------------|---------------------|

|             |     | $D_{max}$ |                    | 0.558           |                     |

| 0.005       | 20% | $M_{tot}$ | 4.627              | 1.443           | 2.584               |

|             |     | $D_{max}$ |                    | 0.543           |                     |

| 0.005       | 50% | $M_{tot}$ | 4.328              | 1.278           | 2.352               |

|             |     | $D_{max}$ |                    | 0.517           |                     |

| 0.005       | 80% | $M_{tot}$ | 3.865              | 1.032           | 1.997               |

|             |     | $D_{max}$ |                    | 0.802           |                     |

| 0.001       | 20% | $M_{tot}$ | 23.137             | 14.9            | 18.567              |

|             |     | $D_{max}$ |                    | 0.796           |                     |

| 0.001       | 50% | $M_{tot}$ | 21.642             | 13.705          | 17.222              |

|             |     | $D_{max}$ |                    | 0.784           |                     |

| 0.001       | 80% | $M_{tot}$ | 19.323             | 11.874          | 15.145              |

The assumption in Table 1 of equal ripple factors for each CCM converter requires closer examination. Ripple factor equations are derived from inductor volt-seconds in (15), where  $f_s$  is the switching frequency. For  $D\approx 1$  the expressions are identical.

$$RF = \begin{cases} \frac{V_{IN}^2}{2f_s LP} D & (boost) \\ \frac{V_{IN}^2}{2f_s LP} D^2 & (buck - boost) \end{cases}$$

(15)

Converter 2 sees an input voltage that is  $M_I$  times larger than converter 1, so the inductance of converter 2 must be  $M_I^2$  times larger to maintain the same ripple factor. From an electrical perspective, the volt-seconds of the second inductor are increased by a factor of  $M_I$  while the allowable change in current is reduced by the same factor; this requires the inductor to compensate for both factors and increase by  $M_I^2$ . In very high gain converters the inductance of converter 2 may be impractically large, and a

compromise must be made between increased ripple factor and decreased inductor size. In this case the efficiency terms in (12) must be evaluated separately. Table 1 shows, however, that the effects of ripple factor decrease as parasitic resistances decrease. Converters with extremely small parasitic resistances can tolerate larger rms currents (large RF) because the  $I_{rms}^2r$  losses remain small; with sufficiently small parasitic resistances, increased rms currents due to large RF will not result in poor efficiency.

Cascade converters offer potential for large gains due to the multiplicative effect, but the efficiency losses compound quickly for the same reason. The entire input power is processed twice, and the losses quickly become a limiting factor with large parasitic resistances. Interleaving can be applied to reduce parasitic resistances and inductor sizes while increasing reliability. The individual modules can allow larger ripple factors for decreased inductor sizes, or the inductances can be held constant to increase overall efficiency. In either case the physical inductor size is reduced due to the smaller current magnitudes. The ability to interleave converters is a major strength of the multiple module approach, especially in high-power applications where reliability concerns often vastly outweigh cost concerns. If one interleaved module fails, the converter can operate at a reduced rating instead of failing entirely. The failed unit can be replaced without bringing the entire converter offline.

Cascade converters suffer from other practical issues. Converter 1 experiences intermediate voltage stresses and large current stresses while converter 2 experiences large voltage stresses and small current stresses. This will likely require the use of semiconductors with different ratings in the converters and will increase inventory

requirements because of limited component interchangeability. Control is also difficult because of the interaction between converters, and the first converter must be operated at a lower bandwidth to maintain stability.

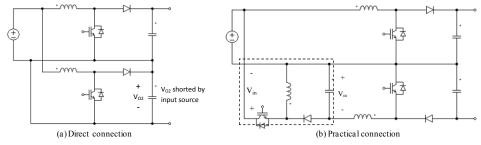

## 3.3 Series modeling

The series configuration shown in Fig. 7b connects the inputs of the converters in parallel and the outputs in series. Practically, only the series hybrid converter can be directly connected in this fashion. Fig. 9a shows a directly connected series boost converter where the output of the bottom converter is shorted to the input return. The series BB converter experiences the same effect when directly connected. This effect can be eliminated with the addition of a cascaded buck-boost converter between the input source and the bottom converter as shown in Fig. 9b. The additional converter acts as a voltage inverter and operates at  $D\approx0.5$  for M=-1. The efficiency loss of the cascaded converter is minimal (assuming negligible losses from forward drops) due to the small duty cycle; for example, the second term of (13) for a buck-boost converter evaluates to 99.5% for a 0.001 pu inductor resistance and 100% ripple factor operated at D=0.5.

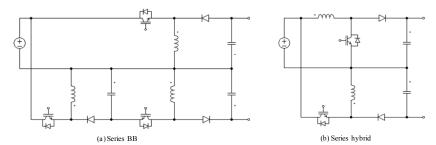

Fig. 9. Practical multiple module series boost converter. Additional BB converter in (b) inverts the input voltage.

The series BB and series hybrid converters are shown in Fig. 10. The series hybrid benefits from the inversion properties of the bottom buck-boost converter because the source neutral can be shared between both converters without an additional buckboost converter. Each converter in the multiple module arrangement provides half the voltage gain and processes half the input power. The top converter is referred to as converter 1, and the bottom converter is referred to as converter 2. The additional inverting buck-boost converter in the series boost and series BB converters is neglected in the efficiency analysis. Each converter is characterized by a gain M, an input power P, and an output voltage  $V_O$ . This general characterization allows the converter gains and efficiencies to be derived without specifying the type of each converter as discussed in Section 2.3. The gain of the series converters is derived in (16) using the same assumptions found in Section 3.2, and the efficiency expression is expanded for the special case of CCM converters with IGBTs as active switches and diodes as passive switches in (17). The factoring of (16) for series hybrid converters requires that the diode efficiency terms are approximately equal  $(D\approx1)$ ; at lower duty cycles the efficiency of the buck-boost converter will be less, and this factoring will not be exact.

Fig. 10. Multiple module series BB and series hybrid converters.

$$M_{series} = (M_1 + M_2)\eta \tag{16}$$

$$\eta = \left(1 - \frac{V_{F,pu}}{M_i(1-D)}\right) \left(\frac{1}{1 + \frac{r_{L,pu}}{(1-D)^2}}\right)$$

(17)

Neglecting forward drops, (17) is solved for *D* to determine the maximum duty cycle for a specified efficiency in (18) for CCM boosting converters. The maximum duty cycle for 95% efficiency is calculated in Table 2 for different parasitic resistances and ripple factors. Small parasitic resistances and ripple factors extend the duty cycle range over which high efficiency can be achieved. The ripple factor equations of (15) are also valid for series converters. The inductors, however, are (approximately) equal in each converter because the converters see the same input voltage.

$$D_{\text{max,series}} = 1 - \sqrt{r_{L,pu} \frac{\eta}{1 - \eta}} \tag{18}$$

Table 2

Series CCM converters: maximum duty cycles and gains for 95% efficiency

|             | 2570 efficiency |           |                    |                  |                      |

|-------------|-----------------|-----------|--------------------|------------------|----------------------|

| $r_{L, pu}$ | RF              |           | Boost<br>(Fig. 9b) | BB<br>(Fig. 10a) | Hybrid<br>(Fig. 10b) |

|             |                 |           | (1 15. 70)         | · · · ·          | (115. 100)           |

| 0.005       | 20%             | $D_{max}$ |                    | 0.690            |                      |

| 0.003       | 2070            | $M_{tot}$ | 6.124              | 4.224            | 5.174                |

| 0.005       | 50%             | $D_{max}$ |                    | 0.679            |                      |

| 0.003       | 30%             | $M_{tot}$ | 5.923              | 4.023            | 4.973                |

| 0.005       | 80%             | $D_{max}$ |                    | 0.66             | <u>-</u>             |

| 0.005       | 80%             | $M_{tot}$ | 5.596              | 3.696            | 4.646                |

| 0.001 20%   | $D_{max}$       |           | 0.861              |                  |                      |

| 0.001       | 20%             | $M_{tot}$ | 13.693             | 11.793           | 12.743               |

| 0.001       | 50%             | $D_{max}$ |                    | 0.857            |                      |

| 0.001       | 30%             | $M_{tot}$ | 13.243             | 11.343           | 12.293               |

| 0.001       | 80%             | $D_{max}$ |                    | 0.848            |                      |

| 0.001       | 80%             | $M_{tot}$ | 12.514             | 10.614           | 11.564               |

|             |                 |           |                    |                  | ·                    |

The gain of series converters is lower than the gain of cascade converters because of the additive effect, but series converters offer many advantages. Each converter processes only half the input power, and the total input power is only processed once (as opposed to twice in the cascade converters). The gains in efficiency allow a larger range of duty cycle operation. For example, data from Tables 1 and 2 for r=0.005 show that the maximum gain at 95% efficiency in the series converters is higher than that of the cascade converters due to the larger available range of duty cycles. This advantage disappears at lower parasitic resistances.

Semiconductors in series converters experience only half the total voltage stress, a decided advantage in high voltage converters where several switches must be combined in series to withstand the rated voltage. Semiconductors in both converters have identical ratings, reducing the inventory requirements. Control is decoupled, and independent controllers can be used. This independent operation allows a variation of boosting and control strategies beyond the basic operation described here. One possible control scheme in high power applications is based on a series hybrid converter. The boost converter would provide the majority of the gain at a low switching frequency to minimize switching losses. The buck-boost converter would operate at a higher switching frequency and fine tune the gain in response to fast load transients. This control scheme would offer fast transient response while minimizing switching losses. Another option involving the series hybrid is to operate the two converters at equal gains instead of equal duty cycles. The bottom buck-boost converter must be operated at a

greater duty cycle, so the efficiency terms can no longer be factored as in (17); however, at large duty cycles and small parasitics the additional losses are negligible.

## 3.4 Simulations and performance comparison

The multiple module converters discussed in this chapter were simulated in the SIMPLIS simulator from Transim to verify the modeling assumptions. High power CCM converters with IGBT switches and rectifier diodes were chosen as the base converters. All component values were normalized with a base input voltage of 1 and a base input power of 1. IGBT and diode forward drops ( $V_F$ ) of 0.0015 pu and an inductor DC resistance of 0.001 pu were specified for the parasitic elements. A 1 kHz switching frequency was selected to be consistent with the high power converters specified.

Inductances were chosen using (15) to limit RF to 50% at maximum duty cycle ( $D\approx1$ ) and were held constant for all duty cycles. Capacitances were chosen to limit output voltage ripple caused by inductor current ripple to 2% peak-to-peak at minimum duty cycle (50%) via (19); they were then held constant for all duty cycles. The pu circuit parameters are listed in Table 3. Note that these values are pu values and would be scaled based on the actual application; therefore, the relative magnitude of the parameters is more instructive than the absolute magnitude of the parameters.

$$C = \frac{\Delta Q/V}{\Delta V/V} = \frac{I_0 DT_S/V}{\Delta V/V} = \frac{DT_S}{R(\Delta V/V)}$$

(19)

Voltage and efficiency data was obtained with a parametric sweep of the duty cycle. To maintain a constant input power the pu output resistance  $(M_i^2)$  was defined as an expression evaluated at each sweep point. The parasitic resistances were then set as percentages of this value.

| Table 3     |                                                     |       |          |               |  |  |

|-------------|-----------------------------------------------------|-------|----------|---------------|--|--|

| Simula      | Simulation circuit parameters for pu CCM converters |       |          |               |  |  |

| All Conv    | Cascade Series                                      |       |          |               |  |  |

| All Conv    | All Converters                                      |       | (Fig. 8) | (Fig. 9b, 10) |  |  |

| $f_S$       | 1 kHz                                               | $L_1$ | 1.2 mH   | 2.5 mH        |  |  |

| $r_{L, pu}$ | 0.001                                               | $L_2$ | 350 mH   | 2.5 mH        |  |  |

| $V_{F,pu}$  | 0.0015                                              | $C_1$ | 24 mF    | 100 uF        |  |  |

| RF          | 50%                                                 | Ca    | 6 mF     | 100 nF        |  |  |

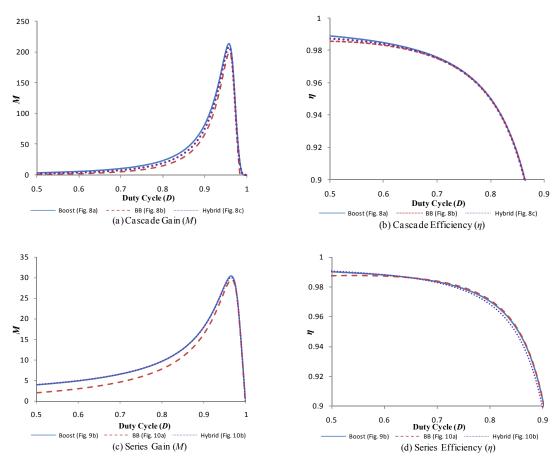

The simulated gains and efficiencies for the six multiple module high-power CCM converters are shown in Fig. 11. The converters within a class demonstrated similar efficiencies, so a restricted range is displayed to highlight the small differences.

Fig. 11. Simulations results for pu CCM multiple module converters: gain and efficiency.

Fig. 11a shows that the three multiple module cascade converters have similar gains, especially at large duty cycles, and validates the factoring introduced in (13). The peak voltage gain is over 200, but the efficiency (Fig. 11b) at this duty cycle is low. The converters using at least one BB converter show a lower efficiency at small duty cycles due to the effect of diode forward voltage as discussed in Chapter II.

Fig. 11c shows the gains of the three multiple module series converters. Note that in the simulation of the series-hybrid converter the two converters are operated at equal gains instead of equal duty cycles. This configuration reaches the same gain as the series-boost with only a slight loss of efficiency (Fig. 11d). The fall-off in efficiency at large duty cycles is due to increased inductor losses from the larger buck-boost duty cycle required to maintain equal gains. The maximum gain for the series converters is approximately 30, or less than one-sixth of the cascade gain, but high efficiency is achieved over a larger range of duty cycles. As in the cascade converters the series-BB converter slightly underperforms in both gain and efficiency; however, it does offer source inversion. Table 4 shows excellent agreement between the simulation results and the calculations from Tables 1 and 2.

Table 4

Comparison of simulated and calculated results for maximum duty cycles in pu CCM converters at  $\eta$ =95%, RF =50%

|                          | $D_{max}$ , calc. | $D_{max}$ , sim. | M, calc. | M, sim |

|--------------------------|-------------------|------------------|----------|--------|

| Cascade Boost (Fig. 8a)  | 0.796             | 0.800            | 23.14    | 23.76  |

| Cascade BB (Fig. 8b)     | 0.796             | 0.800            | 14.90    | 15.20  |

| Cascade Hybrid (Fig. 8c) | 0.796             | 0.800            | 18.57    | 19.00  |

| Series Boost (Fig. 9b)   | 0.857             | 0.854            | 13.70    | 13.02  |

| Series BB (Fig. 10a)     | 0.857             | 0.855            | 11.79    | 11.21  |

| Series Hybrid (Fig. 10b) | 0.857             | 0.854            | 13.70    | 13.02  |

#### 3.5 Conclusions

In this chapter the multiple module approach was introduced. Large voltage gains can be achieved by connecting multiple single-switch DC-DC converters in cascade or in series. Models including parasitic conduction losses were presented for each multiple module configuration, and general transfer functions were derived without referencing the base type of the converters. It was shown that cascade connections provide high gain, but the efficiency falls off quickly at large duty cycles. Parasitic elements must be minimized in order to take full advantage of the gain potential of cascade converters. It was shown that series converters provide less gain, but high efficiency can be maintained over a wider range of duty cycles. Both configurations can provide increased reliability and reduced parasitic losses through interleaving. Gain and efficiency were verified with pu simulations of high-power CCM converters. The performance of the pu CCM multiple module converters is summarized in Table 5.

Table 5 Summary of pu CCM multiple module configurations

| Summary of pu CCM multiple module configurations |                                           |         |            |                 |                   |  |

|--------------------------------------------------|-------------------------------------------|---------|------------|-----------------|-------------------|--|

| Configuration                                    | M                                         | Gain    | Efficiency | $L_2/L_1$ ratio | Source Inversion? |  |

| Cascade boost (Fig. 8a)                          | $\left(\frac{1}{1-D}\right)^2 * \eta^2$   | Highest | Low        | $M_I^2$         | No                |  |

| Cascade BB (Fig. 8b)                             | $\left(-\frac{D}{1-D}\right)^2 * \eta^2$  | High    | Low        | $M_I^2$         | No                |  |

| Cascade hybrid (Fig. 8c)                         | $-D\left(\frac{1}{1-D}\right)^2*\eta^2$   | Higher  | Low        | $M_I^2$         | Yes               |  |

| Series boost (Fig. 9b)                           | $\left(\frac{2}{1-D}\right)*\eta$         | Medium  | Highest    | 1               | No                |  |

| Series BB (Fig. 10a)                             | $\left(\frac{-2D}{1-D}\right) * \eta$     | Lowest  | Medium     | 1               | Yes               |  |

| Series hybrid (Fig. 10b)<br>(equal gains)        | $\left(\frac{2}{1-D_{boost}}\right)*\eta$ | Medium  | High       | 1               | Either            |  |

#### **CHAPTER IV**

# A DCM OPERATED HIGH GAIN CONVERTER FOR LOW POWER APPLICATIONS

### 4.1 Introduction

Renewable energy sources such as photovoltaic cells and fuel cells are low-voltage, high-current energy sources. The output characteristics follow a constant power curve where output voltage decreases as load current increases. The voltage output from a single cell is on the order of 1 to 2 volts, and modules are created by combining several cells in series. At the relatively low power levels of consumer modules (from a few watts to a few kilowatts), module output voltages are limited to a few tens of volts by size constraints and engineering challenges such as fuel and coolant distribution. The output voltage typically varies on a 2:1 scale from no-load to high-load, so power electronics converters are required to provide steady output voltages for single-phase inversion and grid connection. These converters face their greatest challenge at full load when the cell output voltage is at its minimum and the input current is at its maximum. At low power levels the pu semiconductor losses are larger than those found in high power converters, and high efficiency is difficult to reach.

Traditionally, high-frequency transformers have been used to provide large voltage gains at the cost of greater bulk, increased semiconductor stresses, and leakage spikes that must be managed. Low-power conventional single-switch converters operating in CCM cannot provide large voltage gains due to large pu parasitic elements

that limit gain at large duty cycles. Additionally, converters in these power ranges are normally operated at high switching frequencies to reduce component sizes. This restricts the maximum duty cycle so that semiconductors have enough time to turn off fully. These considerations eliminate CCM single-switch transformerless converters from consideration.

Discontinuous conduction mode (DCM) exhibits a voltage gain characteristic with a steeper slope at low duty cycles, allowing large gains to be reached at small duty cycles. Inductor sizes decrease, which improves transient response, but the larger peak currents cause increased conduction losses. Careful optimization is needed to balance the efficiency gains from reduced duty cycles and the efficiency losses from increased peak currents. Further efficiency gains are made possible by the low output voltages in single-phase applications; lower voltages allow rectifier diodes to be replaced with MOSFET synchronous rectifiers. Reverse recovery effects are eliminated, and conduction losses now depend on the MOSFET on-resistance instead of a constant voltage drop. DCM also has the beneficial effect of turning off the output rectifier at zero current and turning on the active switch at zero current, reducing switching losses. A careful design can manage the conduction losses while benefitting from reduced switching losses, and high efficiencies can be achieved at low power levels.

This chapter investigates the use of a multiple module DCM-operated series hybrid converter (Fig. 12) to interface low power, low voltage renewable sources to the grid. The converter will provide the DC link necessary for single-phase inversion. A complete DC model is presented that uses the principle of energy conservation to

accurately model parasitic effects, and a design procedure is developed. Modeling will be verified through simulation and an experimental prototype of a 200W, 24V-to-200V converter.

Fig. 12. DCM series hybrid synchronous converter.

## 4.2 DCM modeling

In DCM the inductor current falls to zero before the end of the switching period, introducing a third state of circuit operation. Many different DCM modeling approaches have been presented, including state-space methods [16], sampled data methods, and circuit-averaging methods [18]; the methods are summarized and compared by Sun in [20], and an averaged model including the dependency of the diode conduction time  $D_2$  on switch duty ratio  $D_1$  (D in this work) is presented. In [21] Reatti introduces a variation of the model of [20] using only controlled current sources which appears functionally identical to Sun's model. This current-controlled current source (CCCS)

model lends itself well to the principle of energy conservation due to its explicitly defined terminal currents.

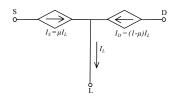

The CCCS model is shown in Fig. 13. The switch and diode are replaced by this three-terminal model with connections made at the location of the switch (S), diode (D), and inductor (L). The peak current can be expressed in terms of terminal voltages from inductor volt-seconds as in (20).  $T_S$  is the switching period, and  $V_{xy}$  is the voltage between terminals x and y where each terminal is S, D, or L. The relationship in (20) is approximate because it neglects the reduction in inductor volt-seconds from parasitic element drops, but the effects of these elements are negligible in a well-designed converter. The parameter  $\mu$  is defined in (21) and represents the ratio of the switch conduction interval to the inductor conduction interval. It is the DCM analog to D.

$$i_{pk} = \begin{cases} \frac{DT_S}{L} V_{SL} \\ \frac{D_2 T_S}{L} V_{LD} \end{cases}$$

(20)

$$\mu = \frac{D}{D + D_2} = \frac{1}{1 + \frac{V_{SL}}{V_{LD}}} \tag{21}$$

$D_2$  can be determined from the equation for  $I_L$  in (8) and from (20) as shown in (22). This result is identical to the duty cycle constraint given in [20]. Substituting (22) into (21) results in an equation for  $\mu$  that is dependent on the switch on-time, circuit parameters, and terminal voltages and currents (23). The parameter K [22] is a direct measure of the "depth" of DCM operation and is defined as 2L/RT. The terminal current expressions in Fig. 13 are obtained by substituting (20) and (23) into (8).

$$\boldsymbol{D_2} = \frac{2LI_L}{\boldsymbol{DT_SV_{SI}}} - \boldsymbol{D} = \frac{KRI_L}{\boldsymbol{DV_{SI}}} - \boldsymbol{D}$$

(22)

$$\mu = \frac{D^2 T_S}{2L} \frac{V_{SL}}{I_L} = \frac{D^2}{KR} \frac{V_{SL}}{I_L}$$

(23)

Fig. 13. Current-controlled current source model of PWM switch in DCM.

The definition of  $\mu$  in (21) can be used to simplify the combined EARs in synchronous DCM converters given in (11) in Section 2.4. For consistency with the previous references, the combined resistance is reflected into the inductor branch by multiplying by  $(1-\mu)^2$  and using (21) to eliminate  $D_2$ , resulting in (24). This equation for r is the DCM analog of  $r_L$  in (7) for synchronous converters.

$$r = \frac{4}{3} \frac{\mu}{D} (r_l + r_{ds}) \tag{24}$$

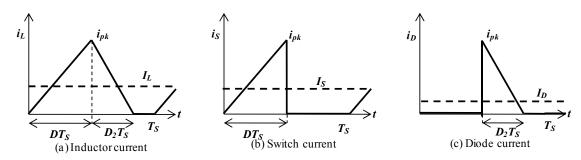

The PWM switch model of Fig. 13 is substituted point for point into the DC models for a boost converter and a buck-boost converter (Fig. 14) to derive the voltage transfer characteristic in the presence of parasitic resistances. The output voltage of the boost converter (Fig.14a) is given by a voltage divider across ( $V_{DL}+V_{LS}$ ); the polarity is reversed because the current sources are oriented opposite to the original model. Similarly, the output voltage of the buck-boost converter (Fig. 14b) is given by a voltage divider across  $V_{LD}$ . After using (21) to express  $V_{LD}$  as a function of  $V_{SL}$  (the input source in both converters) and  $\mu$ , the gain and efficiency of each converter can be written

generally as (25) and (26).  $M_{CCM}(D \rightarrow \mu)$  represents the ideal CCM gain equation of each converter with D replaced by  $\mu$ , and  $\eta$  is the efficiency.

Fig. 14. DC averaged models for DCM synchronous boosting converters.

$$M = M_{CCM}(D \to \mu)\eta \tag{25}$$

$$\eta = \frac{1}{1 + \frac{r}{R(1 - \mu)^2}} = \frac{1}{1 + \frac{r_{pu}}{(1 - \mu)^2}} \tag{26}$$