# MODELING AND SIMULATION OF ADVANCED NANO-SCALE VERY LARGE SCALE INTEGRATION CIRCUITS

A Dissertation

by

YING ZHOU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2010

Major Subject: Computer Engineering

# MODELING AND SIMULATION OF ADVANCED NANO-SCALE VERY LARGE SCALE INTEGRATION CIRCUITS

A Dissertation

by

# YING ZHOU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Weiping Shi Committee Members, Jiang Hu

Krzysztof A. Michalski

Vivek Sarin

Head of Department, Costas N. Georghiades

May 2010

Major Subject: Computer Engineering

#### ABSTRACT

Modeling and Simulation of Advanced Nano-Scale Very Large Scale Integration

Circuits. (May 2010)

Ying Zhou, B.S.; M.S., Xi'an Jiaotong University, China Chair of Advisory Committee: Dr. Weiping Shi

With VLSI(very large scale integration) technology shrinking and frequency increasing, the minimum feature size is smaller than sub-wavelength lithography wavelength, and the manufacturing cost is significantly increasing in order to achieve a good yield. Consequently design companies need to further lower power consumption. All these factors bring new challenges; simulation and modeling need to handle more design constraints, and need to work with modern manufacturing processes. In this dissertation, algorithms and new methodology are presented for these problems: (1) fast and accurate capacitance extraction, (2) capacitance extraction considering lithography effect, (3) BEOL(back end of line) impact on SRAM(static random access memory) performance and yield, and (4) new physical synthesis optimization flow is used to shed area and reduce the power consumption.

Interconnect parasitic extraction plays an important role in simulation, verification, optimization. A fast and accurate parasitic extraction algorithm is always important for a current design automation tool. In this dissertation, we propose a new algorithm named HybCap to efficiently handle multiple planar, conformal or embedded dielectric media. From experimental results, the new method is significantly faster than the previous one, 77X speedup, and has a 99% memory savings compared with FastCap and 2X speedup, and has an 80% memory savings compared with PHiCap for complex dielectric media.

In order to consider lithography effect in the existing LPE(Layout Parasitic Extraction) flow, a modified LPE flow and fast algorithms for interconnect parasitic extraction are proposed in this dissertation. Our methodology is efficient, compatible with the existing design flow and has high accuracy.

With the new enhanced parasitic extraction flow, simulation of BEOL effect on SRAM performance becomes possible. A SRAM simulation model with internal cell interconnect RC parasitics is proposed in order to study the BEOL lithography impact. The impact of BEOL variations on memory designs are systematically evaluated in this dissertation. The results show the power estimation with our SRAM model is more accurate.

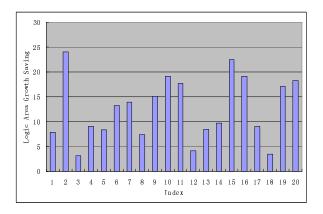

Finally, a new optimization flow to shed area blow in the design synthesis flow is proposed, which is one level beyond simulation and modeling to directly optimize design, but is also built upon accurate simulations and modeling. Two simple, yet efficient, buffering and gate sizing techniques are presented. On 20 industrial designs in 45nm and 65nm, our new work achieves 12.5% logic area growth reduction, 5.8% total area reduction, 10% wirelength reduction and 770 ps worst slack improvement on average.

To My Family

#### ACKNOWLEDGMENTS

I wish to express my great thanks to my advisor Professor Weiping Shi. Dr. Shi is a wonderful teacher, has taught me a lot of fundamental VLSI design automation and parasitic extraction knowledge, and shared his professional manner of conducting research. I am very thankful to him for all the time he devoted to scientific discussions with me, as well as for his constant encouragement. Finally, I truly appreciate all his support for my life and work. Especially, he showed his understanding after my daughter was born. Many thanks to my committee members, Dr. Vivek Sarin, Dr. Jiang Hu, and Dr. Michalski; I gained a lot of useful knowledge from them.

Many thanks to Dr. Vivek Sarin for introducing the linear algorithm, which gave me more knowledge of matrix. Many thanks to Dr. Michalski for introducing the electromagnetic theory, which provides a strong theory backup for my research. Many thanks to Dr. Jiang Hu for the great courses on physical design. Many thanks to Dr. Peng Li for introducing the modeling and simulation to me. Many thanks to Dr. Charles Alpert of the IBM Austin Research Lab for opening another window to my life-understand gate-sizing, overall physical design flow. Many thanks to all of my colleagues, Dr. Nam, Dr. Cliff Sze, Dr. Natarajan Viswanathan, Dr. Jarrod Ray, David Papa, who provided a lot of help with my work. Many thanks to Dr. Rouwaida Kanj, and Dr. Sani Nassif for the useful discussion and comments on the work about BEOL effect on SRAM yield analysis. Many thanks to Dr. Frank Liu for the useful discussion and help on the work about lithography impact on interconnect extraction.

I would like to express my gratefulness to all my officemates during my stay at Texas A&M University. Especially, thanks to Xiang Lu for learning Candence Tools.

Thanks to Shu Yan and Yang Yi for very useful discussions in interconnect extraction. Thanks to Chent-Ta Chiang for the course work discussion and introducing LaTex and many useful hints on that. Thanks to all the people in Zachary room 111, who give me the wonderful and unforgettable memories in my life. Without my friends in room 111, my life would not be so plentiful.

I wish to thank my parents and parents-in-law for their constant encouragement and support. After my daughter was born, they came to the US and helped us take care of Sophia for more than one year. Many thanks to my husband Zhuo Li. He is not only my husband, but also my good friend and mentor in my work. Without his support and encouragement, I could not finish my study and dissertation.

# TABLE OF CONTENTS

| CHAPTER |                                                                                                                   | Page     |

|---------|-------------------------------------------------------------------------------------------------------------------|----------|

| I       | INTRODUCTION                                                                                                      | 1        |

|         | A. Technique Trend and Background                                                                                 | 1<br>4   |

| II      | FAST CAPACITANCE EXTRACTION IN MULTILAYER, CONFORMAL AND EMBEDDED DIELECTRIC USING HYBRID BOUNDARY ELEMENT METHOD | 8        |

|         |                                                                                                                   | 8        |

|         | A. Background                                                                                                     | 11       |

|         | 1. Equivalent Charge Method (ECM)                                                                                 | 12       |

|         | 2. Multilayer Green's Function Method                                                                             | 13       |

|         | 3. HybCap Algorithm                                                                                               | 14       |

|         | 4. Correctness                                                                                                    | 15       |

|         | C. Kernel Independent Preconditioned Solver                                                                       | 17       |

|         | D. Ground Plane and Reflective Wall                                                                               | 18       |

|         | E. Experimental Results                                                                                           | 19       |

|         | 1. Multilayer Green's Function                                                                                    | 19       |

|         | 2. Reflective Walls with Ground Plane                                                                             | 22       |

|         | 3. Conformal/Embedded Dielectric and Reflective Walls F. Conclusion                                               | 23<br>23 |

| III     | INTERCONNECT PARASITICS EXTRACTION CONSID-                                                                        |          |

|         | ERING PHOTO-LITHOGRAPHY EFFECTS                                                                                   | 28       |

|         | A. Background                                                                                                     | 28       |

|         | B. New LPE Methodology                                                                                            | 29       |

|         | C. Lithography Simulation                                                                                         | 30       |

|         | D. 3D Extraction                                                                                                  | 33       |

|         | 1. Surface Discretization                                                                                         | 34       |

|         | 2. Side Wall Layer Selection                                                                                      | 37       |

|         | 3. Shape Correction                                                                                               | 43       |

|         | 4. Resistance Extraction                                                                                          | 46       |

|         | 5. Inductance Extraction                                                                                          | 48       |

|         | E. Conclusion                                                                                                     | 48       |

| CHAPTER |                                                                               | Page  |

|---------|-------------------------------------------------------------------------------|-------|

| IV      | THE IMPACT OF BEOL LITHOGRAPHY EFFECTS ON THE SRAM CELL PERFORMANCE AND YIELD | . 50  |

|         | A. Background                                                                 | . 51  |

|         | <ol> <li>SRAM RC Model</li> <li>RC Extraction for SRAM Cell</li> </ol>        |       |

|         | C. The Methodology for SRAM Performance Analysis                              |       |

|         | D. BEOL Impact Analysis with New Methodology                                  |       |

|         | 1. BEOL Impact on SRAM Read Delay                                             | . 57  |

|         | 2. BEOL impact on Stability                                                   | . 59  |

|         | 3. Misalignment Impact on SRAM Performance                                    | . 61  |

|         | E. Conclusion                                                                 | . 64  |

| V       | A SLEW BASED $C_{EFF}$                                                        | . 65  |

|         | A. Background                                                                 | . 65  |

|         | B. $C_{eff}$ for an RC Network for 10% Point                                  | . 68  |

|         | C. Equivalent Output Resistance                                               | . 73  |

|         | D. Detailed Comparison                                                        | . 77  |

|         | E. Statistical Comparison                                                     |       |

|         | F. Conclusion                                                                 | . 82  |

| VI      | AREA AWARE PHYSICAL SYNTHESIS FLOW                                            | . 83  |

|         | A. Background                                                                 | . 83  |

|         | 1. Buffer Insertion                                                           | . 85  |

|         | 2. Gate Sizing                                                                |       |

|         | 3. Our Contribution                                                           | . 90  |

|         | B. Overview of Existing Physical Synthesis Flow                               |       |

|         | C. Iterative EVE                                                              |       |

|         | D. Area Efficient Timing Driven Gate Sizing                                   |       |

|         | E. New Area Efficient Optimization Flow                                       |       |

|         | G. Experiments                                                                |       |

|         | 1. Iterative EVE vs Single EVE                                                |       |

|         | 2. Timing Driven Gate Sizing                                                  |       |

|         | 3. Overall Flow Comparison                                                    |       |

|         | H. Conclusion                                                                 |       |

| VII     | CONCLUSION AND SUMMARY                                                        | . 105 |

| CHAPTER    | Page |

|------------|------|

| REFERENCES | 109  |

| VITA       | 118  |

# LIST OF TABLES

| TABLE |                                                                                                                        | Page |

|-------|------------------------------------------------------------------------------------------------------------------------|------|

| I     | Experimental results for the structure shown in Fig. 6                                                                 | 24   |

| II    | Experimental results for industrial test case shown in Fig. 7                                                          | 25   |

| III   | Experimental results for reflective boundary walls and ground plane.                                                   | 26   |

| IV    | Experimental results for conformal/embedded dielectric, reflective boundary walls, ground plane and planar dielectrics | 27   |

| V     | Capacitance comparison between lithography simulated and layout for two elbow conductors                               | 33   |

| VI    | Resistance comparison between lithography simulated and layout for two elbow conductors                                | 33   |

| VII   | Capacitances error with the different number of etching layers                                                         | 43   |

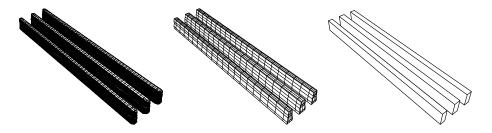

| VIII  | Capacitances with new LPE methodology for three parallel buses                                                         | 46   |

| IX    | Resistance comparison between new and old LPE methodologies for 1x1 elbow example                                      | 48   |

| X     | Inductance with new LPE strategy for 1x1 elbow example                                                                 | 48   |

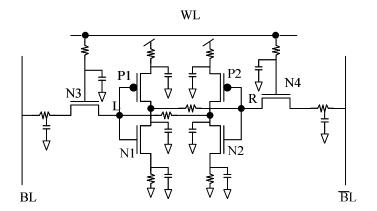

| XI    | The relative RC value among all layouts in one piece of SRAM cell                                                      | 57   |

| XII   | SRAM yield analysis. Yield is in sigma                                                                                 | 64   |

| XIII  | The variables used in the statistical simulation                                                                       | 78   |

| XIV   | The QOR comparison for iterative EVE                                                                                   | 99   |

| XV    | The QOR comparison for area efficient gate sizing                                                                      | 100  |

| XVI   | The QOR comparison of baseline and new flow                                                                            | 104  |

# LIST OF FIGURES

| FIGURI |                                                                                                                                                                                                                                                                       | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | The lithography challenge                                                                                                                                                                                                                                             | 2    |

| 2      | Image distortion due to lithography effect                                                                                                                                                                                                                            | 2    |

| 3      | The conductors buried in multilayer dielectric. Planar dielectric structures are XY plane. Embedded dielectric structures are a closed rectangular box region. Conformal dielectric structure is often modeled by embedded dielectric overridden by interconnect meta | l. 9 |

| 4      | Multiconductor system conformal/embedded in a multilayer di-<br>electric region. Black boxes are conductors, grey boxes are con-<br>formal/embedded dielectrics and dotted lines represent planar<br>dielectric-planar dielectric interfaces                          | 16   |

| 5      | Multiconductor system with reflective walls                                                                                                                                                                                                                           | 18   |

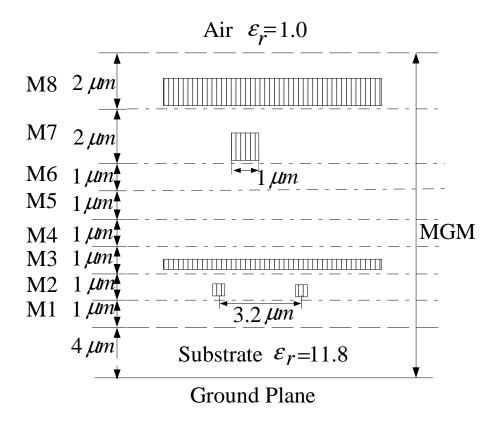

| 6      | Crossing bus with planar structure. Shade boxes are conductors and dotted lines represent planar dielectric-planar dielectric interfaces.                                                                                                                             | 20   |

| 7      | Example with 48 conductors and 8 dielectric layer                                                                                                                                                                                                                     | 21   |

| 8      | Conformal/embedded dielectric case. Shade boxes are conductors, green box is conformal/embedded dielectrics and dotted lines represent planar dielectric-planar dielectrics interfaces                                                                                | 22   |

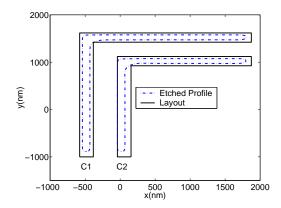

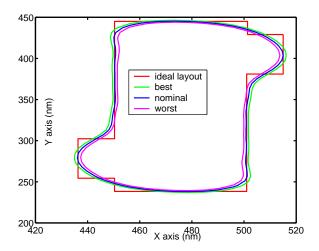

| 9      | The etched profile vs. layout (top view)                                                                                                                                                                                                                              | 28   |

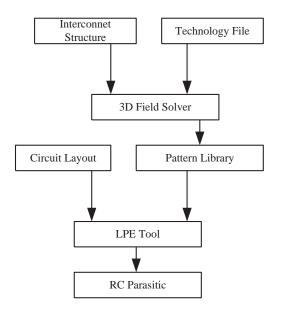

| 10     | Traditional LPE methodology                                                                                                                                                                                                                                           | 30   |

| 11     | New LPE methodology                                                                                                                                                                                                                                                   | 31   |

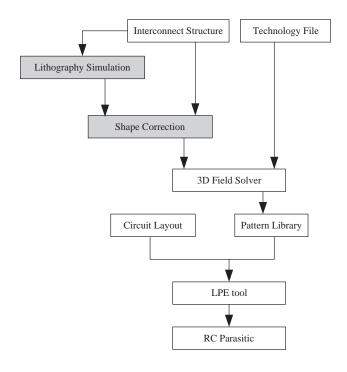

| 12     | 3D profile for elbow conductor                                                                                                                                                                                                                                        | 32   |

| 13     | Two cases to connect four points                                                                                                                                                                                                                                      | 35   |

| 14     | One example discretization for elbow-shape conductor                                                                                                                                                                                                                  | 36   |

| FIGURI | E                                                                                                        | Page |

|--------|----------------------------------------------------------------------------------------------------------|------|

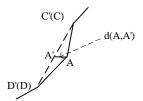

| 15     | Original points and projected points in a cross section view of one side wall surface                    | . 38 |

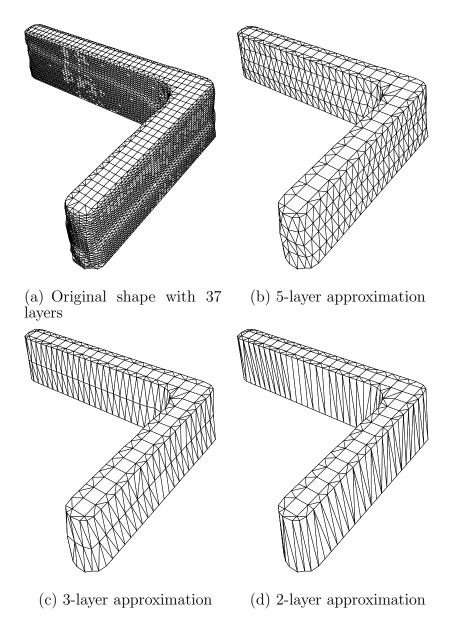

| 16     | One example approximation for elbow-shape conductor                                                      | . 42 |

| 17     | One examples for three parallel buses                                                                    | . 46 |

| 18     | Resistance computation model                                                                             | . 47 |

| 19     | Different lithographic profiles from the same layout profile of SRAM with different depth of focus (DOF) | . 52 |

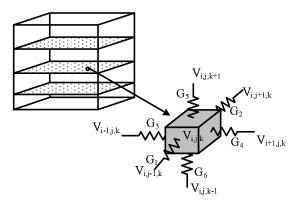

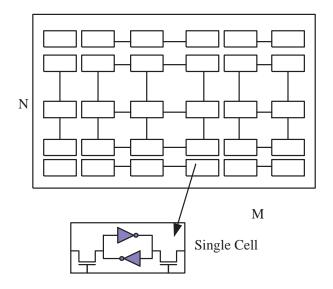

| 20     | SRAM MXN array                                                                                           | . 53 |

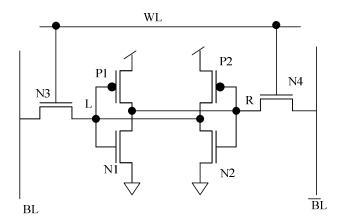

| 21     | 6 transistor SRAM schematic                                                                              | . 54 |

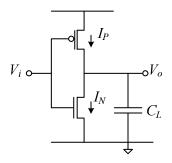

| 22     | 6 transistor SRAM schametic with RC network                                                              | . 55 |

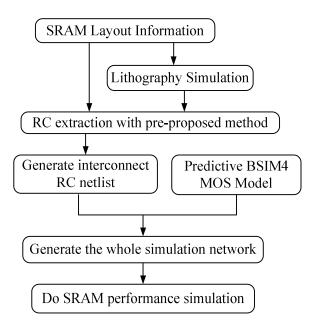

| 23     | The methodology flow for SRAM performance and yield analysis for BEOL variations                         | . 56 |

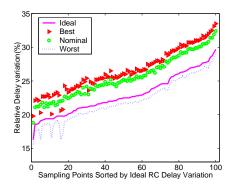

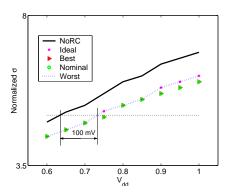

| 24     | Relative delay variation of ideal, best, nominal and worst RC model vs. basic NoRC model                 | . 58 |

| 25     | Relative delay varitation of best, nominal and worst. The reference model is ideal RC model              | . 58 |

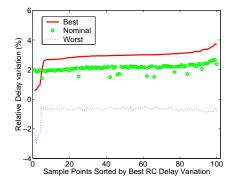

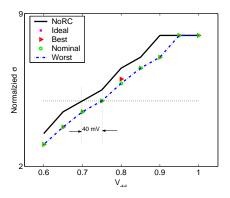

| 26     | Read yield of noRC, ideal RC, best RC, nominal RC and worst RC model                                     | . 59 |

| 27     | Stability yield for noRC, ideal RC, best RC, nominal RC and worst RC model                               | . 60 |

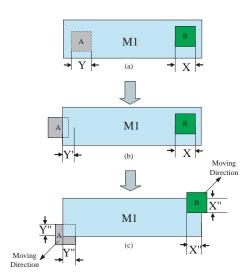

| 28     | Misalignment                                                                                             | . 61 |

| 29     | Resistance vs. misalignment distance                                                                     | . 62 |

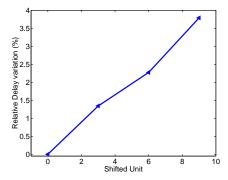

| 30     | The effect of misalignment on the read delay $\tau_R$ variation. The reference model is idea RC model    | . 63 |

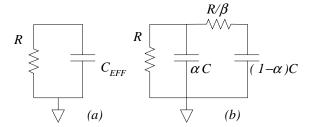

| 31     | One and two-stage RC circuit.                                                                            | . 68 |

| FIGURE |                                                                                                                                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

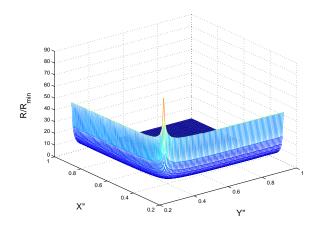

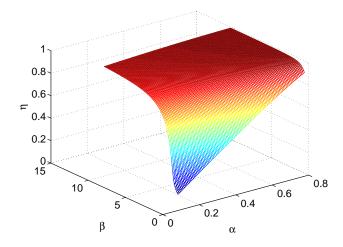

| 32     | $\eta$ vs. $\alpha$ and $\beta$ when we compute $0.1V_{DD}$ based effective capacitance.                                                                                                               | 71   |

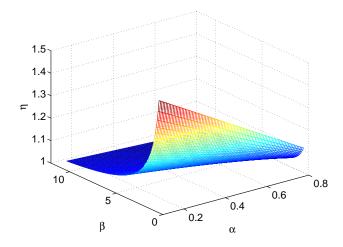

| 33     | $\eta$ vs. $\alpha$ and $\beta$ when we compute $0.5V_{DD}$ based effective capacitance.                                                                                                               | 72   |

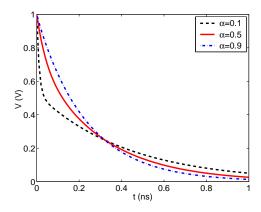

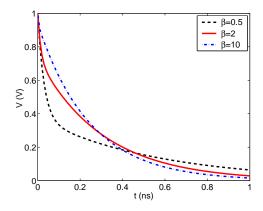

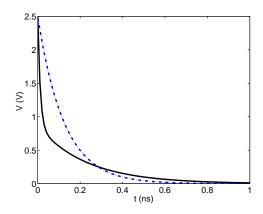

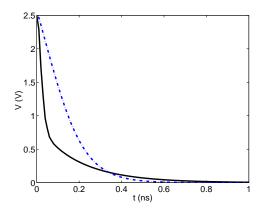

| 34     | The output waveform vs. $\alpha$ . $\beta = 1$                                                                                                                                                         | 73   |

| 35     | The output waveform vs. $\beta$ . $\alpha = 0.2$                                                                                                                                                       | 74   |

| 36     | Comparsion of Eq. $(5.5)$ and the solution of Eq. $(5.4)$                                                                                                                                              | 75   |

| 37     | CMOS inverter circuit                                                                                                                                                                                  | 75   |

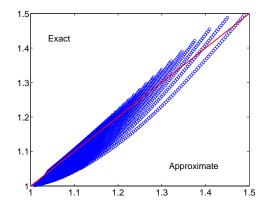

| 38     | Inverter vs. effective capacitance                                                                                                                                                                     | 78   |

| 39     | Pi section vs. effective capacitance                                                                                                                                                                   | 79   |

| 40     | Inverter driving Pi section vs. effective capacitances                                                                                                                                                 | 80   |

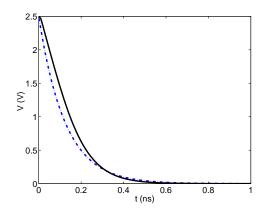

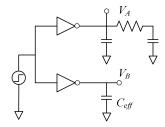

| 41     | Circuit used for statistical comparison                                                                                                                                                                | 80   |

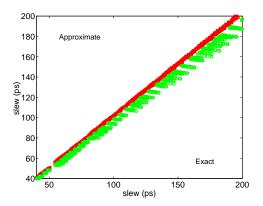

| 42     | Slew at $V_A$ and $V_B$ . Red squres represent our method. Green circules represent the single delay based effective capacitance method.                                                               | 81   |

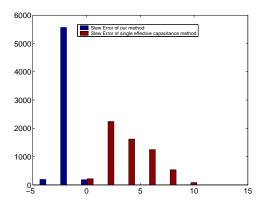

| 43     | Histogram of percentage slew error                                                                                                                                                                     | 81   |

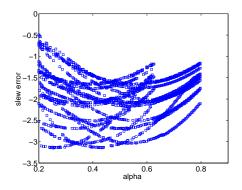

| 44     | Percentage slew error vs. $\alpha$                                                                                                                                                                     | 82   |

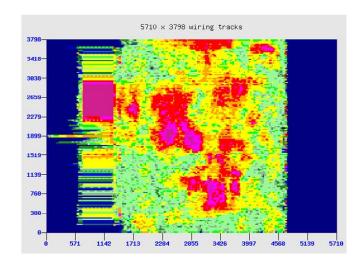

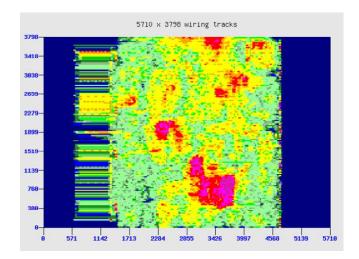

| 45     | Horizontal congestion from timing driven physical synthesis flow                                                                                                                                       | 85   |

| 46     | Horizontal congestion from area efficient physical synthesis flow                                                                                                                                      | 86   |

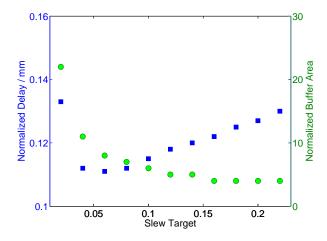

| 47     | Slew constrait (ns) vs. buffer area relationship is shown in green dots. Slew constraint (ns) vs. signal delay per mm relationship is shown in blue squares                                            | 87   |

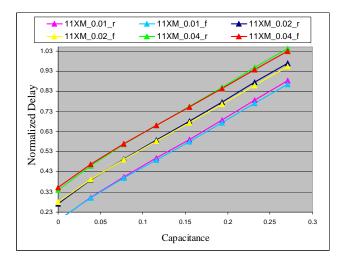

| 48     | Delay vs. cap for a buffer in 45 nm node. Three different input slew values, 10, 20 and 40 ps, are used here. 11XM_0.2_r refers to 11X driving strength buffer, 20 ps input slew and the rising inputs | 88   |

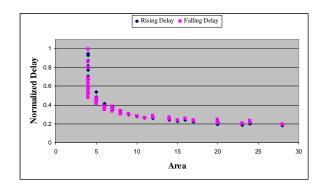

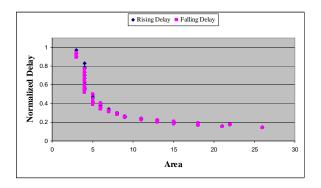

| 49     | Delay vs. area for a buffer library in 65 nm node                                                                                                                                                      | 89   |

| 50     | Delay vs. area for a buffer library in 45 nm node                                                                                                                                                      | 89   |

| FIGURI | $\Xi$                                              | Page  |

|--------|----------------------------------------------------|-------|

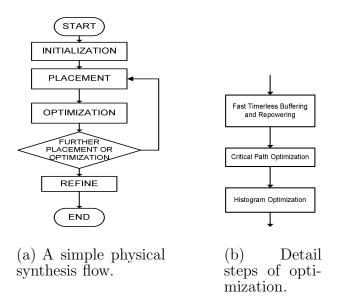

| 51     | Flow diagram.                                      | . 91  |

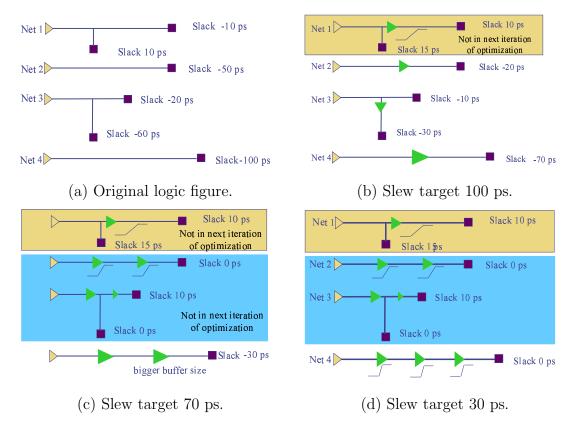

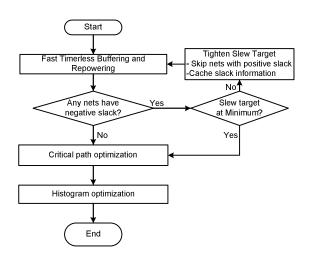

| 52     | A simple example for iterative EVE                 | . 92  |

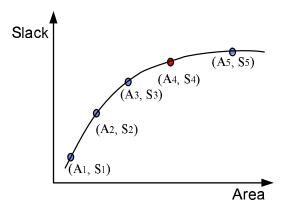

| 53     | Area aware gate sizing                             | . 96  |

| 54     | New optimization flow                              | . 97  |

| 55     | Logic area growth saving compared to baseline flow | . 101 |

## CHAPTER I

#### INTRODUCTION

### A. Technique Trend and Background

As Moore's Law predicts, the number of transistors on Integrated Circuit is doubled every 24 months. So it has become a key benchmark for semiconductor development. Integration level, cost, speed, power, compactness and functionality obey the Moore's Law. From ITRS (The International Technology Roadmap for Semiconductors) [1], the minimum feature size used to fabricated the integrated circuit exponentially decreases during last four decades.

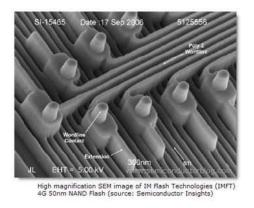

During the feature size shrinking, design automation company need face more challenges. Optical lithography is one of them. Optical lithography has been the mainstream technology for volume manufacturing since the earliest days of the microelectronics industry. And it is expected to continue as such through the 32 nm half-pitch technology generation. The minimum half pitch is proportional to the wavelength, and inversely proportional to the numerical aperture (NA). And depth of focuse is proportional to the wavelength, and inversely proportional to  $NA^2$  [1]. In order to get the clearly printed image, the smaller wavelength, and higher NA imaging systems are required. Just as Chris A. Mack, vice president of KLA-Tencor, notes that optical lithography is encountering stiff challenges when moving to deep submicron production. He indicates that conventional dry lithography is encountering a bottleneck, as the numerical aperture (NA) approaches 0.9.

There are many new RET(resolution enhancement technique) such as off-axis illumination (OAI), phase shifting masks (PSM), and optical proximity corrections

The journal model is *IEEE Transactions on Automatic Control*.

Fig. 1. The lithography challenge.

(OPC) are being used with imaging systems at 193 nm wavelength. Also including 157nm, extreme ultraviolet (EUV) lithography are in development. The ITRS 2005 update seems to have come to a conclusion. It thinks the 193nm scanner (including the use of wet scanners) will be the mainstream solution at the next two technology nodes shown in Fig. 1 [2]. If one day water-based immersion technology can be extended in its application, the use of fluid rather than air for lithography will be the star technology for the 32nm and 22nm environments.

Fig. 2. Image distortion due to lithography effect.

Fig. 2 are the STEM image from Intel. With OAI technique, we still can see the wiggle on the metal boundary. It is obvious that the difference exists, especially around the corners. The traditional LPE methodology can not model and extract the litho/etch effects of nano-scale interconnect, including feature size shrinking, subwavelength of light, pattern-dependent effect, etc. To do so would force designer and manufacturers to make a change in entire design flow. Here, we propose a new LPE methodology considering lithographic effect compatible with the existing design flow to solve this problem.

SRAM cell is the main part of memory processor. What does lithographic distortion impact SRAM performance? In traditional SRAM performance analysis, the internal cell short interconnect effect has been neglected. all previous work only study the front end of line (FEOL) such as  $V_{dd}$ ,  $V_{th}$  on SRAM performance. With the feature size shrinking beyond 65 nm, the transistor size and signal wire dimensions continues to decrease with the result of the unit wire capacitance and resistance become bigger. Here we proposed a SRAM RC model to consider the internal RC impact on SRAM performance. Also with this SRAM RC model, we study the lithography effect on SRAM performance.

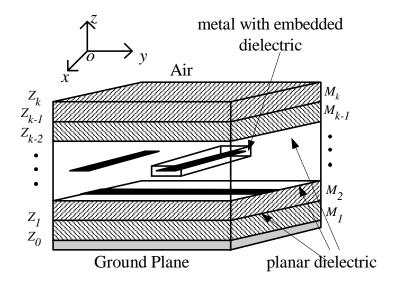

Except for the lithography challenge due to the technology scaling advances beyond 65nm, the increased wire delay dominance due to finer wire width makes design closure an increasingly challenging problem, a lot of advanced technique skill is used to solve design closure problem. In modern technology, there are over 40 layers of dielectric, etch stop, shield and substrate. Most dielectric structures are planar, but embedded and conformal are also common.

Accurate and fast layout parasitic extraction will help designers a lot during timing verification and signal integrity analysis. It is a big challenge to have a fast scalable algorithm for capacitance extraction to meet the industrial practical requirement while dramatically reducing the extraction time, memory usage and the number of the iterations. Traditionally, the dielectric structures are handled by either equivalent charge method (ECM) such as FastCap [3] or PHiCap [4], or multilayer Green's function method (MGM) such as  $IES^3$  [5] and HiCap [6]. Some other efficient methods, such as p-FFT [7] and FastImp [8], do not handle multilayer dielectric. In order to solve this problem, we propose a Hybrid algorithm for Capacitance extraction (HybCap) based on boundary element method.

As ITRS predicts, the density per chip is exponentially increased. The supply voltage will go to 0.4 V in 2016. Small area and low power design is the mainstream in the modern technology. During physical synthesis flow, what is the best way to realize small area and lower power design goal? We proposed an area efficient physical synthesis flow which is embedded in IBM physical synthesis flow.

#### B. Contribution

All of my work can be classified into three categories, namely (a) methodology, (b) extraction algorithm, (c) circuit simulation and modeling.

(a) Methodology. In this part work, I have two contributions. The first is about new Layout Parasitic Extraction (LPE) methodology. since the image distortion due to the technology limitation can not be neglected, lithography effect should be considered during Layout Parasitic Extraction flow. However, the tradition LPE flow doesn't support the extraction with subwavelength-light, pattern-dependent, etc. We proposed a smart new LPE methodology which made a minor change to include lithography simulation into the tradition LPE flow. Meanwhile, the algorithms for capacitance and resistance extraction are also presented, respectively. Lithography simulation and shape correction steps including a smart dynamic programming based

layer selection scheme are inserted into the traditional LPE methodology to form new LPE methodology. Compared with the traditional methodology, the new methodology will get much more accurate results. The new algorithm significantly reduces the running time of the 3D capacitance solver while keep the good accuracy. As well, we proposed a algorithm on how to do shape approximation. The new methodology are very quick, efficient and compatible with the current flow very well. This technique may be a little outdate, but it is a good option for industry, academy 2 years ago. This work was published in ASPDAC07 and got the best paper award.

Another one is about efficient area aware physical synthesis flow. Due to the demand of the small area and low power design, we proposed this efficient area aware physical synthesis flow based on IBM current physical design and synthesis tool. Based on the observation, we have several techniques to improve the current IBM PDS flow:

- An area efficient iterative slew-tighten approach for slew driven buffering and gate sizing (iterative EVE);

- A simple area efficient timing driven gate sizing method for cell library designs; With those simple and efficient techniques, we got the overall successful results and improve the quality of run with IBM PDS tool.

- (b) Fast extraction algorithm named HybCap. Since the multilayer dielectric are widely used in modern industry, fast and accurate interconnect extraction is important for timing verification and signal integrity analysis. ECM( Equivalent Charge Method) is popularly used to solve this problem in Boundary Element Method( BEM). Multilayer Green's Function is another option to solve this problem based on Boundary Element Method. Here, we proposed a methodology named hybrid to do interconnect exaction in multilayer dielectric media. We have main two contributions.

One is that we implemented MGM with independent solver, and another is that we combine ECM and MGM together to solve the cases for complex dielectric structures, ground plane, reflective walls. The capacitance matrix of our algorithm shows good accuracy with well known field solvers when there are complex dielectric structure and reflective boundary walls. With the experimental results, our method can speed  $2x\tilde{5}x$  based on the complex of the interconnect structure, and save more than 80with less iteration number.

(c) Circuit modeling and simulation. This part includes two works. One is about BEOL(Back End of Line) impact on SRAM performance. A new SRAM parasitic analysis model is proposed to capture the internal cell interconnect parasitics RC network. Then we propose an SRAM performance/yield analysis flow which enables litho-aware parasitic extractions and simulation to the existing flows. With our proposed methodology, we can study the back-end-of-line(BEOL) variations on SRAM performance combined with FEOL(front-end-of-line) variations.

Another one is about slew  $C_{eff}$  model. With technology scaling, the ratio between the typical output resistance of the output stage of a cell and the interconnect resistance has been steadily rising, making the estimation of the single lumped-capacitance representation of interconnect load more complex. This was observed in [9] and an approach for computing an equivalent effective capacitance was proposed. However, one effective capacitance that captures the cell delay cannot accurately predict the slew at the cell output. For this problem, we present a new accurate and efficient approach to estimate the effective capacitance for the output slew of the cell based on a compact analytical model of MOS device operation. The modeling is done with two simple closed form formulas, which are easy to embedded in any STA tools.

The remainder of this dissertation is organized as follows:

- Chapter II : fast capacitance extraction with hybrid boundary element method

- Chapter III: a new methodology for interconnect parasitics extraction considering photo-lithography effects

- Chapter IV: the impact of BEOL Lithography Effects on the SRAM Cell Performance and Yield

- Chapter V: a Slew based  $C_{eff}$

- Chapter VI: area aware physical synthesis flow

## CHAPTER II

FAST CAPACITANCE EXTRACTION IN MULTILAYER, CONFORMAL AND EMBEDDED DIELECTRIC USING HYBRID BOUNDARY ELEMENT METHOD A. Background

Fast and accurate capacitance extraction is very important for timing verification and signal integrity analysis for digital and mixed-signal integrated VLSI chips. Roughly speaking, there are two categories to compute capacitances: 2D/2.5D library looked-up, where the layout is divided into sections and matched against a precharacterized library to derive the capacitance value, and 3D field solvers, where the electromagnetic field is solved to compute the capacitance either by integral equations or differential equations. The library method is faster, while the field solver method is more accurate. In this section, we are targeting on fast and accurate field solver since it is important to critical net and clock tree analysis and library generation. We use boundary element method (BEM) as the baseline, which is used by many field solvers such as [3][4][7][10][11].

When the technology shrinks, more dielectric layers are used. One example is shown in Fig. 3. In modern technology, there are over 40 layers of dielectric, etch stop, shield and substrate. Most dielectric structures are planar, but embedded and conformal are also common. It is a big challenge to have a fast scalable algorithm for capacitance extraction to meet the trend of increasing dielectric layers. Traditionally, the dielectric structures are handled by either equivalent charge method (ECM) such as FastCap [3] or PHiCap [4], or multilayer Green's function method (MGM) such as  $IES^3$  [5] and HiCap [6]. Some other efficient methods, such as p-FFT [7] and FastImp [8], do not handle multilayer dielectric.

Fig. 3. The conductors buried in multilayer dielectric. Planar dielectric structures are XY plane. Embedded dielectric structures are a closed rectangular box region. Conformal dielectric structure is often modeled by embedded dielectric overridden by interconnect metal.

For the equivalent charge method, dielectric-dielectric interfaces are modeled and discretized to satisfy the interface condition [3][4]. The free space Green's function is used to construct the linear system. The charge density on both the conductor-dielectric and dielectric-dielectric interfaces are solved by iterative methods and acceleration techniques. Capacitances matrix is derived accordingly. ECM works for any dielectric structures with proper geometry processing and the Green's function is simple. However, it requires additional unknown charges on the discretized dielectric-dielectric interfaces and ground planes, thus resulting linear system is much larger. As the number of layers increases, this method becomes impractical.

For multilayer Green's function method, the Green's function for a multilayer planar dielectric medium are derived either directly in spatial domain, i.e., image theory [12], or in spectral domain [5]. The linear system is constructed by the new Green's function and the charge density of each discretized panel on conductors are

solved. MGM generally results in much smaller linear system compared to ECM since it avoids the discretization of dielectric-dielectric interfaces. However, MGM only works for planar dielectric structures and requires the algorithm be kernel independent. In [13], an equivalent dielectric constant approach is used to approximate all planar dielectric layers to only 4 layers by empirical formulas. Then double image Green's function is used, which works well only for up to 4 layers as shown in the paper. However, it is shown in [13] that the equivalent dielectric constants approach has over 15% error when combine two dielectric layers with relative bigger difference in dielectric constant, which is common for sub-130 nm technology. Moreover, the method cannot handle dielectrics other than planar dielectric.

In this section, we propose a Hybrid algorithm for Capacitance extraction (HybCap) based on a kernel independent fast multipole accelerated BEM field solver [4]. The new method combines ECM and MGM, and works extremely efficient for complex dielectric structures. Some of the main features of the algorithms are shown as follows:

- A linear system is built by multilayer Green's function for conductors and the interfaces between conformal/embedded dielectric regions and other dielectric regions;

- The system is transformed to a sparse system and solved with efficient preconditioner;

- The ground plane and reflective wall are handled.

To the best of our knowledge, this is the first hybrid method based on BEM to handle planar, conformal/embedded dielectric, ground plane, and reflective boundary walls.

### B. Preliminaries

To compute the self and coupling capacitances, we need to compute the conductor surface charges, given certain conductor electrostatic potentials. In general, the surface charges satisfy the integral equation

$$\Phi(r) = \int_{S} \sigma(r')G(r,r')d\alpha', \qquad (2.1)$$

where r is the observation point, r' is the source point,  $\Phi(r)$  is the known conductor surface potential, S is the union of conductor-dielectric interfaces alone or the combination of conductor-dielectric interfaces and the dielectric-dielectric interfaces,  $\sigma$  is the charge density on S, G(r, r') is the Green's function,  $d\alpha'$  is the incremental conductor or dielectric surface area, and  $r' \in d\alpha'$ . Also additional electric displacement vector must satisfy Eq. (2.2) at dielectric-dielectric interfaces (interface conditions):

$$\varepsilon_a \frac{\partial \Phi_+(r)}{\partial n_a} = \varepsilon_b \frac{\partial \Phi_-(r)}{\partial n_a}, \tag{2.2}$$

where r is a point on the dielectric-dielectric interfaces,  $n_a$  is the normal to the dielectric interface at r that points into dielectric a;  $\varepsilon_a$  and  $\varepsilon_b$  are the permittivities of the corresponding dielectric regions;  $\Phi_+(r)$  is the potential at r approached from the  $\varepsilon_a$  side of the interface, and  $\Phi_-(r)$  is the analogous potential for the  $\varepsilon_b$  side.

Eq. (2.1) can be numerically solved. The (i, j) entry of the capacitance matrix is the free charge on the ith conductor when the potential of the jth conductor is 1 V and the other conductors are grounded.

Before the new hybrid method HybCap is proposed, let us first review ECM and MGM methods.

# 1. Equivalent Charge Method (ECM)

Equivalent charge method is first proposed in [14] for capacitance extraction and followed by many researchers. In this method, surface charge layers are placed at the conductor-dielectric and dielectric-dielectric interfaces, with charge densities  $\sigma_c(r)$  and  $\sigma_d(r)$ , respectively, and the dielectric medium is replaced with free space. Eq. (2.1) now becomes

$$\Phi_{ECM}(r) = \int_{S_c} \sigma_c(r') G_F(r, r') d\alpha'$$

$$+ \int_{S_d} \sigma_d(r') G_F(r, r') d\alpha',$$

(2.3)

where  $S_c$  is the union of conductor-dielectric interfaces and  $S_d$  is the union of dielectric-dielectric interface, and  $G_F = 1/(4\pi\varepsilon_0||r-r'||)$ , r is the observation point and r' is the source point. The interface condition on dielectric-dielectric interfaces becomes

$$\varepsilon_a \frac{\partial \Phi_{ECM+}(r)}{\partial n_a} = \varepsilon_b \frac{\partial \Phi_{ECM-}(r)}{\partial n_a}.$$

(2.4)

To numerically compute  $\sigma_c$  and  $\sigma_d$ , the standard Galerkin scheme is used. The conductor-dielectric and dielectric-dielectric interfaces are discretized into  $n = n_c + n_d$  small panels,  $S_1, S_2, \ldots, S_n$ , with  $n_c$  panels on conductor-dielectric interfaces and  $n_d$  panels on dielectric-dielectric interfaces.

A dense linear system is formed:

$$\begin{bmatrix} P_{cc} & P_{cd} \\ E_{dc} & E_{dd} \end{bmatrix} \begin{bmatrix} q_c \\ q_d \end{bmatrix} = \begin{bmatrix} v_c \\ 0 \end{bmatrix},$$

where  $q_c$  and  $q_d$  are the vector charges on the conductor-dielectric and dielectricdielectric interface panels, respectively, and  $v_c$  are the vector of potentials on conductor panels. The dimension of potential matrix P is  $(n_c + n_d)$ . In Galerkin method the (i, j) entry of  $P_{cc}$  and  $P_{cd}$  are defined as

$$p_{ij} = \frac{1}{A(S_i)A(S_j)} \int_{S_i} \int_{S_j} G_F(r_i, r_j) d\alpha_j d\alpha_i, \qquad (2.5)$$

where  $A(S_i)$  and  $A(S_j)$  are the area of panel  $S_i$  and  $S_j$ , respectively.

The entries of  $E_{dc}$  and off-diagonal entries of  $E_{dd}$  are defined as

$$e_{ij} = \frac{\partial}{\partial n_a} \frac{\varepsilon_a - \varepsilon_b}{A(S_i)A(S_j)} \int_{S_i} \int_{S_j} G_F(r_i, r_j) d\alpha_j d\alpha_i.$$

(2.6)

The *i*th diagonal entry  $e_{ii} = \frac{(\varepsilon_a + \varepsilon_b)}{2\varepsilon_0 A(S_i)}$ .

### 2. Multilayer Green's Function Method

For planar dielectric as shown in Fig. 3, where the permittivity within each layer is uniform in the x- and y- directions, we can derive the multilayer Green's function. Assume a point charge at r' in layer k, we have Poisson's equation:

$$\nabla^2 G_M(r, r') = -\frac{\delta(r - r')}{\varepsilon_k}. \tag{2.7}$$

Many works [12][15] [16] describe how to get the multilayer Green's function. No matter what methods they use, the Green's function must satisfy the continuous conditions  $G_{M+} = G_{M-}$  everywhere and boundary conditions

$$\varepsilon_a \frac{\partial G_{M+}(r)}{\partial n_a} = \varepsilon_b \frac{\partial G_{M-}(r)}{\partial n_a} \tag{2.8}$$

at dielectric-dielectric interfaces. In this section, we use the methods similar to [5] to compute multilayer Green's function.

If we use multilayer Green's function as integral equation approach's kernel, Eq. (2.1) becomes

$$\Phi_{MGM}(r) = \int_{S_c} \sigma(r') G_M(r, r') d\alpha', \qquad (2.9)$$

where  $S_c$  is just the conductor surface,  $\sigma$  is the charge density on  $S_c$ , r is the observation point and r' is the source point. The new linear system is  $P'_{cc}q'_c = v_c$ , where  $p'_{ij}$  is evaluated similarly to Eq. (2.5) with  $G_M$  as kernel now. It is well known that multilayer Green's function method doesn't need to consider the charge on dielectric-dielectric interfaces. The dimension of matrix  $P'_{cc}$  is  $n'_c$ , which is much smaller than that of the equivalent charge method which is  $n_c + n_d$  even though that  $n'_c$  is different from  $n_c$  in general. Note that the evaluation of  $p'_{ij}$  is slower than  $p_{ij}$  in free space due to its complicated formulas, which results in a little overhead of matrix construction.

# 3. HybCap Algorithm

When the dielectric is nonplanar such as the example shown in Fig. 3, we can not solve this problem with MGM only. On the other hand, we need substantially large memory and long running time with ECM alone. In this section, we present HybCap, which is hybrid capacitance extraction algorithm to take advantage of general dielectric geometry with ECM and smaller system memory of MGM.

# HybCap Algorithm includes the following steps:

- 1. Construct  $G_M$  based on given planar dielectric layers' information.

- 2. Change Eq. (2.1) and Eq. (2.2) to Eq. (2.10) and Eq. (2.11), respectively,

$$\Phi_{HybCap}(r) = \int_{S_c} \sigma_c(r') G_M d\alpha'

+ \int_{S_{cd}} \sigma_e(r') G_M d\alpha',$$

(2.10)

and

$$\varepsilon_a \frac{\partial \Phi_{HybCap+}(r)}{\partial n_a} = \varepsilon_b \frac{\partial \Phi_{HybCap-}(r)}{\partial n_a}.$$

(2.11)

where  $S_c$  is the union of conductor-dielectric interfaces and  $S_{ed}$  is the union of

conformal/embedded dielectric-dielectric (conformal/embedded dielectric-planar dielectric or conformal/embedded dielectric-embedded dielectric) interfaces. Note that Eq. (2.11) only applies to  $S_{ed}$ .

- 3. Construct Pq = v with Eq. (2.10) and (2.11) accordingly.

- 4. Solve the system with the kernel independent hierarchical algorithm such as PHicap [4].

- 5. Compute capacitance matrix.

#### 4. Correctness

**Theorem II.1.** Given a set of conductors, a layered planar dielectric structure, and rectangle regions of embedded dielectric, HybCap method produces the same result as ECM.

*Proof.* Based on the previous analysis,

$$\Phi_{ECM}(r) = \int_{S_c} \sigma_c(r') G_F(r, r') d\alpha'

+ \int_{S_{pd}} \sigma_d(r') G_F(r, r') d\alpha'

+ \int_{S_{ed}} \sigma_e(r') G_F(r, r') d\alpha',$$

(2.12)

$$\varepsilon_a \frac{\partial \Phi_{ECM+}(r)}{\partial n_a} = \varepsilon_b \frac{\partial \Phi_{ECM-}(r)}{\partial n_a},$$

(2.13)

where  $S_c$  is the union of conductor-dielectric interfaces,  $S_{pd}$  is the union of planar dielectric-planar dielectric interfaces,  $S_{ed}$  is the union of conformal/embedded dielectric-dielectric interfaces, the other terminologies are defined in previous sections, Eq. (2.13) applies on  $S_{pd}$  and  $S_{ed}$  in Eq. (2.12).

Based on the previous analysis, both MGM and ECM are satisfied with the same boundary continuous conditions which are  $\Phi_+ = \Phi_-$  and  $D_+ = D_-$ . In ECM, the electric potential comes from the charge on conductors and the polarization charge on dielectric interface. If we remove the polarization charge on planar dielectric interface, the potential due to the dielectric difference will lose. The potential calculated with Multilayer Green's Function consider the potential caused not only by uniform dielectric but also by the dielectric difference. Therefore, we don't need to consider the polarization charge on dielectric interface in MGM since multilayer Green's function already considers it. Above all, the potential computed by ECM and MGM will be same in planar dielectric. We substitute free space Green's function  $G_F$  with multilayer Green's function  $G_M$  in Eq. (2.12). Since  $G_M$  already consider the potential due to the planar dielectric difference, the second item of the right hand side of Eq. (2.12) is zero. Then Eq. (2.12) becomes Eq. (2.10). Thus, HybCap method is equivalent to ECM method.

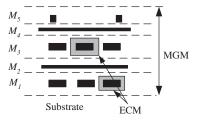

Fig. 4. Multiconductor system conformal/embedded in a multilayer dielectric region. Black boxes are conductors, grey boxes are conformal/embedded dielectrics and dotted lines represent planar dielectric-planar dielectric interfaces.

Note that in ECM, the whole dielectric medium is replaced by free space because the unknown charges are introduced at all dielectric boundary interfaces. In HybCap, however, each conformal/embedded dielectric region is replaced with the

planar dielectric surrounding the conformal/embedded dielectric. For the example shown in Fig. 4, where two dielectric boxes embeds in the layer  $M_1$  and  $M_3$ , HybCap first employs ECM for two conformal/embedded dielectric regions and use multilayer Green's function for the whole planar system after transforming.

The new linear system is as follows:

$$\begin{bmatrix} P_{cc} & P_{ce} \\ E_{ec} & E_{ee} \end{bmatrix} \begin{bmatrix} q_c \\ q_e \end{bmatrix} = \begin{bmatrix} v_c \\ 0 \end{bmatrix},$$

where  $q_c$  and  $q_e$  are the vector charges on the conductor-dielectric and conformal/embedded dielectric-dielectric interface panels, respectively, and  $v_c$  are the vector of potentials on conductor panels. Note that  $p_{ij}$  is directly derived by multilayer Green's function, and  $e_{ij}$  is the electrical filed intensity derived by the corresponding  $p_{ij}$ .

#### C. Kernel Independent Preconditioned Solver

With multilayer Green's function, kernel dependent BEM field solver, such as Fast-Cap [3] can not be used for hybrid method. HybCap algorithm uses PHiCap [4] as the underlying solver due to its kernel independence characteristic and efficient preconditioned solver. First, matrix P is hierarchically built on discretized panels of conductor-dielectric and conformal/embedded dielectric-dielectric interfaces with multilayer Green's function. Then the dense system Pq = v is transformed to an equivalent sparse system  $\tilde{P}\tilde{q} = \tilde{v}$ . An incomplete factorization preconditioner for  $\tilde{P}$  is computed next. Finally,  $\tilde{P}\tilde{q} = \tilde{v}$  is solved by preconditioned GMRES or CG method.

For a system with  $n_c$  conductor panels,  $n_p$  planar dielectric-planar dielectric interface panels, and  $n_e$  embedded/conformal dielectric-dielectric interface panels, the dimension of matrix P is  $n_c + n_e + n_p$  if ECM method is used alone. For HybCap algorithm, however, the dimension of matrix P could be from  $n_c + n_e$  to  $n_c + n_e + n_p - n_j$  de-

pending on the realistic chip structure assuming same discretization being performed (we can always model one or more planar dielectric-planar dielectric interfaces with ECM), where  $n_j$  is the minimum number of panels for one planar dielectric-planar dielectric interface among all k planar dielectric-planar dielectric interfaces.

# D. Ground Plane and Reflective Wall

Ground planes is a perfect electric conductor (PEC), which can be easily modeled. In [5], transmission line theory is used and the ground plane can be modeled as a short circuit line.

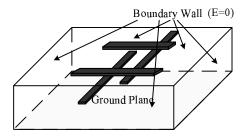

One example of the reflective walls (reflective boundary walls), also called Neumann boundary, is shown in Fig. 5. The normal of electric field on the reflective boundary walls is zero.

Fig. 5. Multiconductor system with reflective walls.

Reflective boundary walls can be easily modeled by our HybCap algorithm with treating reflective boundary walls as dielectric interfaces where  $\varepsilon_a = \varepsilon_i$  and  $\varepsilon_b = 0.0$

for panel i on the boundary. Now Eq. (2.10) changes to

$$\Phi_{HybCap}(r) = \int_{S_c} \sigma_c(r') G_M d\alpha'

+ \int_{S_{ed}} \sigma_e(r') G_M d\alpha'

+ \int_{S_{hw}} \sigma_b(r') G_M d\alpha',$$

(2.14)

where  $S_{bw}$  is the reflective boundary wall surfaces. We also need to add one more interface condition

$$\varepsilon_i \frac{\partial \Phi_{HybCap}(r_i)}{\partial n_i} = 0, \qquad (2.15)$$

where  $r_i$  is on the interface of reflective boundary walls. The linear system is rewritten as follows;

$$\begin{bmatrix} P_{cc} & P_{ce} & P_{cb} \\ E_{ec} & E_{ee} & E_{eb} \\ E_{bc} & E_{be} & E_{bb} \end{bmatrix} \begin{bmatrix} q_c \\ q_e \\ q_b \end{bmatrix} = \begin{bmatrix} v_c \\ 0 \\ 0 \end{bmatrix},$$

where  $q_b$  denotes the vector of charges on boundary panels,  $P_{cb}$  is the coefficient between conductor surface panels and boundary wall panels,  $E_{eb}$  is the coefficient between conformal/embedded dielectric-dielectric interface panels and boundary wall panels.  $E_{bb}$  evaluates self term and coefficient between boundary wall panels. Other symbols are same as previous. Solve this linear system, then we can derive the capacitance value.

#### E. Experimental Results

#### 1. Multilayer Green's Function

The experiments are executed on a 3.20GHz Intel Xeon CPU with 8GB memory. The average error  $E_{avg}$  in the capacitance matrix C' is defined as  $||C - C'||_F / ||C||_F$ , where

Fig. 6. Crossing bus with planar structure. Shade boxes are conductors and dotted lines represent planar dielectric-planar dielectric interfaces.

$||\cdot||_F$  denotes the Frobenius norm. In this case, there are only planar dielectric layers,  $\varepsilon_{substrate} = 11.8$ ,  $\varepsilon_{M_1,M_2,M_7} = 3.9$ ,  $\varepsilon_{M_3,M_4,M_8} = 7.0$ ,  $\varepsilon_{M_5,M_6} = 2.5$ , and  $\varepsilon_{Air} = 1.0$ . Layer M2 and M8 have two buses each whereas layer M3 and M7 have one conductor each. The other dimension is shown in Fig. 6.

We compare FastCap 2.0 [17], PHiCap [4] with HybCap. The comparison results are shown in Table I. From the table, HybCap is almost 300 times faster than FastCap with 99% memory saving. HybCap is almost 30 times faster than FastCap with 98% memory saving. With 10% of discretized panels, HybCap achieves very good accuracy.

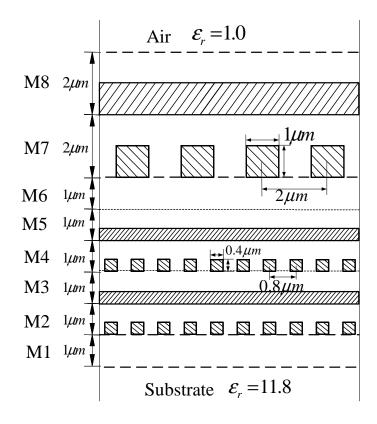

Another benchmark is an industrial test case containing eight layers of dielectric

Fig. 7. Example with 48 conductors and 8 dielectric layer.

and 48 conductors from [4] and we modified it by adding the ground plane on the bottom. The case structure is shown in Fig. 7. Metal conductors are shade regions. Relative permittivity of M1 is 3.9, M2-M6 is 2.5 and M7-M8 is 7.0. Layers M2-M5 have ten conductors each whereas layer M7 and M8 have four conductors each. The computation result is shown in Table II. FastCap can not solve these examples because of prohibitive time and memory requirement, therefore we compare HybCap with PHiCap. Few items are compared shown in Table II because of the number of the conductors. From Table II, HybCap is 5 times faster than PHiCap with 85% memory saving. The number of panels is almost 1/4 of PHiCap since no dielectric panels are modeled.

#### 2. Reflective Walls with Ground Plane

In this experiment, the example in Fig. 6 is added with reflective boundary walls. The boundary wall size is  $20 \times 20 \times 16 \ \mu m^3$ .

We compare our experimental results with FastCap and PHiCap. The comparison results are shown in Table III. The relative error is within 2% entries with 90 times speedup and 0.5% memory usage compared with FastCap and 2 times speedup and 20% memory usage compared with PHiCap.

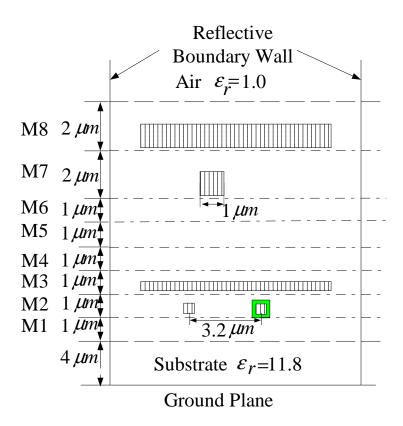

Fig. 8. Conformal/embedded dielectric case. Shade boxes are conductors, green box is conformal/embedded dielectrics and dotted lines represent planar dielectric—planar dielectrics interfaces.

# 3. Conformal/Embedded Dielectric and Reflective Walls

In this case, we consider the conformal/embedded dielectric, reflective boundary walls, ground plane and planar dielectric all together. The physical structure is shown in Fig. 8. The green area is the embedded dielectric. The boundary wall size is  $20\times20\times16\mu m^3$ . All of other parameters are same as the first case in section 1 and  $\varepsilon_{ed}=2.0$ .

The result is shown in Table IV. Compared with FastCap, HybCap gives about 70 times speedup and 99% memory saving. Compared with PHiCap, HybCap gives about 2 times speedup and 80% memory saving.

#### F. Conclusion

In this chapter, we present an efficient hybrid boundary element method for complex dielectric structures, ground plane, reflective walls. The new method optimally combines equivalent charge method and multilayer Green's function to meet the industrial practical requirement while dramatically reducing the extraction time, memory usage and the number of the iterations. The capacitance matrix of our algorithm shows good accuracy with well known field solvers when there are complex dielectric structure and reflective boundary walls.

Table I. Experimental results for the structure shown in Fig. 6.

| Table I. Experimental results for the structure shown in Fig. 6. |           |        |          |        |          |  |

|------------------------------------------------------------------|-----------|--------|----------|--------|----------|--|

| Capacitance                                                      | FastCap   | PHiCap |          | Ну     | bCap     |  |

| (aF)                                                             | (order=2) |        | Error(%) |        | Error(%) |  |

| $C_{11}$                                                         | 897.6     | 908.8  | 1.24     | 909.9  | 1.37     |  |

| $C_{22}$                                                         | 899.5     | 909.3  | 1.09     | 910.4  | 1.21     |  |

| $C_{33}$                                                         | 1168.0    | 1187.8 | 1.70     | 1177.4 | 0.80     |  |

| $C_{44}$                                                         | 1203.0    | 1214.0 | 0.91     | 1212.2 | 0.75     |  |

| $C_{55}$                                                         | 1308.0    | 1335.1 | 2.07     | 1324.3 | 1.25     |  |

| $C_{66}$                                                         | 1265.0    | 1287.8 | 1.80     | 1278.9 | 1.10     |  |

| $C_{12}, C_{21}$                                                 | 72.6      | 74.4   | 2.48     | 73.9   | 1.79     |  |

| $C_{13}, C_{31}$                                                 | 254.3     | 261.5  | 2.83     | 259.9  | 2.20     |  |

| $C_{14}, C_{41}$                                                 | 40.5      | 41.2   | 1.73     | 40.7   | 0.49     |  |

| $C_{15}, C_{51}$                                                 | 18.1      | 19.1   | 5.52     | 18.7   | 3.31     |  |

| $C_{16}, C_{16}$                                                 | 19.3      | 20.1   | 4.15     | 19.5   | 1.04     |  |

| $E_{avg}(\%)$                                                    | -         | 1.80   |          | 1      | 1.08     |  |

| Time(s)                                                          | 476.92    | 38.62  |          | 1.28   |          |  |

| Iteration                                                        | 14.7      | 2      |          |        | 1        |  |

| Memory(MB)                                                       | 4027.2    |        | 200      |        | 4.3      |  |

| Panel                                                            | 119296    | 16     | 58743    | 8      | 3316     |  |

Table II. Experimental results for industrial test case shown in Fig. 7.

| Capacitance      | PHiCap | HybCap |          |

|------------------|--------|--------|----------|

| (aF)             |        |        | Error(%) |

| $C_{11}$         | 854.1  | 854.9  | 0.09     |

| $C_{22}$         | 992.9  | 993.6  | 0.07     |

| $C_{33}$         | 1000.9 | 999.1  | 0.18     |

| $C_{12}, C_{21}$ | 299.0  | 297.7  | 0.43     |

| $C_{13}, C_{31}$ | 21.3   | 21.6   | 1.41     |

| $E_{avg}(\%)$    | -      | 3.4    |          |

| Time(s)          | 138.65 | 23.59  |          |

| Iteration        | 2.04   | 1.96   |          |

| Memory(MB)       | 330    | 48     |          |

| Panel            | 231559 | 63     | 54832    |

Table III. Experimental results for reflective boundary walls and ground plane.

| Capacitance      | FastCap   |        | HiCap    |        | ·bCap    |

|------------------|-----------|--------|----------|--------|----------|

| (aF)             | (order=2) |        | Error(%) |        | Error(%) |

| $C_{11}$         | 895.3     | 905.5  | 1.14     | 906.4  | 1.24     |

| $C_{22}$         | 896.7     | 907.0  | 1.17     | 907.5  | 1.20     |

| $C_{33}$         | 1159.0    | 1181.5 | 1.94     | 1170.7 | 1.01     |

| $C_{44}$         | 1188.0    | 1199.8 | 0.99     | 1199.3 | 0.95     |

| $C_{55}$         | 1229.0    | 1252.5 | 1.91     | 1244.9 | 1.29     |

| $C_{66}$         | 1155.0    | 1173.2 | 1.58     | 1169.5 | 1.26     |

| $C_{12}, C_{21}$ | 75.1      | 76.6   | 2.00     | 76.3   | 1.60     |

| $C_{13}, C_{31}$ | 258.4     | 266.6  | 3.17     | 264.4  | 2.32     |

| $C_{14}, C_{41}$ | 46.4      | 46.9   | 1.08     | 45.9   | 1.08     |

| $C_{15}, C_{51}$ | 26.6      | 27.7   | 3.76     | 26.8   | 0.75     |

| $C_{16}, C_{16}$ | 28.7      | 29.6   | 3.14     | 28.4   | 1.05     |

| $E_{avg}$ (%)    | -         | ]      | 1.78     | 1      | 1.18     |

| Time(s)          | 466.8     | 13.42  |          | 4.93   |          |

| Iteration        | 20.3      | 1.67   |          |        | 1        |

| Memory(MB)       | 2634.7    | 79     |          |        | 13.0     |

| Panel            | 123008    | 69     | 9583     | 19     | 9380     |

Table IV. Experimental results for conformal/embedded dielectric, reflective boundary walls, ground plane and planar dielectrics.

| Capacitance      | FastCap   | PF     | HiCap    | Ну     | bCap     |

|------------------|-----------|--------|----------|--------|----------|

| (aF)             | (order=2) |        | Error(%) |        | Error(%) |

| $C_{11}$         | 891.5     | 903.9  | 1.39     | 904.5  | 1.46     |

| $C_{22}$         | 702.5     | 691.9  | 1.27     | 693.6  | 1.27     |

| $C_{33}$         | 1120.0    | 1147.4 | 2.45     | 1135.9 | 1.41     |

| $C_{44}$         | 1187.0    | 1199.3 | 1.04     | 1198.7 | 0.99     |

| $C_{55}$         | 1228.0    | 1252.2 | 1.97     | 1244.7 | 1.36     |

| $C_{66}$         | 1154.0    | 1172.8 | 1.63     | 1169.1 | 1.31     |

| $C_{12}, C_{21}$ | 57.2      | 58.8   | 2.72     | 58.5   | 2.27     |

| $C_{13}, C_{31}$ | 268.5     | 271.1  | 0.97     | 268.9  | 0.15     |

| $C_{14}, C_{41}$ | 48.3      | 47.8   | 1.03     | 46.8   | 3.10     |

| $C_{15}, C_{51}$ | 27.9      | 28.4   | 1.79     | 27.4   | 1.79     |

| $C_{16}, C_{16}$ | 30.1      | 30.3   | 0.66     | 29.1   | 3.32     |

| $E_{avg}$ (%)    | -         | 6      | 2.65     | 6      | 2.13     |

| Time(s)          | 467.9     | 14.27  |          | 6.05   |          |

| Iteration        | 20.2      | 2      |          | 1      | 1.17     |

| Memory(MB)       | 3101.5    | 82     |          |        | 14       |

| Panel            | 123062    | 70     | 0529     | 20     | 0326     |

# CHAPTER III

# INTERCONNECT PARASITICS EXTRACTION CONSIDERING PHOTO-LITHOGRAPHY EFFECTS

## A. Background

As the feature sizes decrease, interconnect variation is playing a greater role in circuit performance. In [18], a process model for sensitivity to different variations is proposed for a clock tree. In [19], a methodology is proposed to model the effect of systematic intra-die variations on circuit performance. In [20], an integrated variation analysis technique is proposed that considers both the effects of systematic and random variation. In [21], with a variational order reduction technique, authors show that interconnect variation can cause up to 25% clock skew variability in a microprocessor design. All these studies are based on accurate parasitic extraction data. Therefore, efficient and accurate extraction of interconnect parasitics under process variation becomes increasingly important. Due to sub-wave lithography effects and process

Fig. 9. The etched profile vs. layout (top view).

variations, such as mask size, etching speed, temperature, exposure dose and focal

position variations, it is difficult to reliably print the image intended by the designer. Therefore, the features fabricated mismatch from those drawn in the layout. Fig. 9 shows the top view of the layout and etched profile simulated by PROLITH<sup>1</sup> of a pairs of elbow structures. It is obvious that the difference is significant, especially around the corners. In this example, the error of RC parasitic due to lithographic effect is 20%.

The traditional LPE methodology can not model and extract the litho/etch effects of nano-scale interconnect, including feature size shrinking, subwavelength of light, pattern-dependent effect, etc. To do so would force designer and manufacturers to make a change in entire design flow. In the rest part of this section, we propose a new LPE methodology considering lithographic effect compatible with the existing design flow.

#### B. New LPE Methodology

The traditional LPE methodology flow is illustrated in Fig. 10. First, the common interconnect structures and the technology files are input to the 3D field solver. The field solver generates a pattern library to be used for layout parasitic extraction (LPE) tools. LPE tools then read the circuit layout and the pattern library to compute the parasitics of the entire circuit. No process variations or lithography effects are considered in the traditional flow.

With advanced sub-wavelength lithography and etching technology, the distortion is so severe and unpredictable that litho/etching software are developed to simulate this complex process.

Considering the litho/etching effect, we embedded lithography simulation into

<sup>&</sup>lt;sup>1</sup>PROLITH is a trademark of KLA-Tencore Corporation.

Fig. 10. Traditional LPE methodology.

the LPE flow. Fig. 11 is the new methodology proposed in this section. Two new procedures are added into the new methodology: lithography simulation and shape correction. The shape correction algorithm is used to simplify the complicated geometry from lithography simulation, so that current LPE tools can handle the etched profile, such as shown in Fig. 9. It is clear that the new LPE methodology improves the accuracy of parasitic extraction, and fits well into the existing design flow.

# C. Lithography Simulation

Photo-lithography modeling and simulation have been used in the industry for about 30 years. Due to its speed and cost-effectiveness, lithography simulation is widely used to study the process development, determination of sensitivity to manufacture variables, mask design verification and yield analysis. Modern lithography simulation engine can provide accurate process models for the current lithography sequence. In

Fig. 11. New LPE methodology.

this section, we use 3D lithography simulator PROLITH version 8.1.2 provided by KLA-Tencor, to study the lithographic effect on interconnect. In our experiments, 90-nm technology is used with 193-nm UV light assumed as the lithographic light source.

The lithography simulation step of our new LPE methodology includes four steps. First, the typical 3D structures are selected from the interconnect library. Second, the proper masks with OPC are derived for lithography simulation, and determine the process window and optimization of the manufacture parameters. Third, based on the masks and proper processing parameters selected, the lithography simulation is carried out to produce the final 3D geometry of the interconnect structures. Finally, the lithography images are post-processed to a GDS2 format.

The outputs from lithography simulators PROLITH after processed are contours

at different elevation. In other words, the output are points in the X-Y plane, organized for different heights, which we call layers. Note that such layer definition is different from metal layer in the traditional way. For each metal layer, there are often several elevations. The output format for the profile in Fig. 9 is as follows:

| X     | У         | $\mathbf{Z}$ | layer |

|-------|-----------|--------------|-------|

| 480.5 | -1394.151 | 0            | 0     |

| 531.5 | -1398.848 | 0            | 0     |

| :     | :         | :            | :     |

| 480.5 | -1394.4   | -3           | 1     |

| 531.5 | -1399.1   | -3           | 1     |

| :     | :         | :            | :     |

We reconstruct the 3D profile for litho/etched conductors. The detail algorithm will be presented in next section. Fig. 12(a) and Fig. 12(b) show the original layout profile and the corresponding litho/etched profile, respectively.

Fig. 12. 3D profile for elbow conductor.

The litho/etched profile is no longer in rectangular shape and hence the current commercial LPE tools can not solve it. The difference of the extracted RC value between them can reach 20%. For example, in the layout shown in Fig. 9, Table V and VI shows the parasitics difference between simulated litho/etch and original layout profile. The parasitic capacitance and resistance considering lithographic effect

are very different from those of the original layout. Note that such difference will become much bigger for 65 and 45 nm technology.

Table V. Capacitance comparison between lithography simulated and layout for two elbow conductors.

| Capacitance      | Etched | Layout | Error |

|------------------|--------|--------|-------|

| (aF)             |        |        | (%)   |

| $C_{11}$         | 110.8  | 123.9  | 11.02 |

| $C_{22}$         | 93.9   | 105.9  | 11.91 |

| $C_{12}, C_{21}$ | 57.9   | 67.7   | 15.52 |

Table VI. Resistance comparison between lithography simulated and layout for two elbow conductors.

| Resistance | Etched | Layout | Error |

|------------|--------|--------|-------|

| $(\Omega)$ |        |        | (%)   |

| $R_1$      | 0.29   | 0.23   | 20.69 |

| $R_2$      | 0.23   | 0.18   | 21.74 |

# D. 3D Extraction

In the new LPE methodology, lithography simulation is inserted into the old LPE flow. However, it is a big challenge to accurately extract parasitics when the interconnect shape is no longer rectangular. In this section, a surface discretization algorithm, a dynamic programming based algorithm for selecting side wall layers, and a shape correction algorithm are introduced for the irregular shape interconnect capacitance extraction. An algorithm for resistance computation of irregular shapes is also proposed.

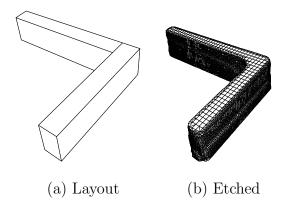

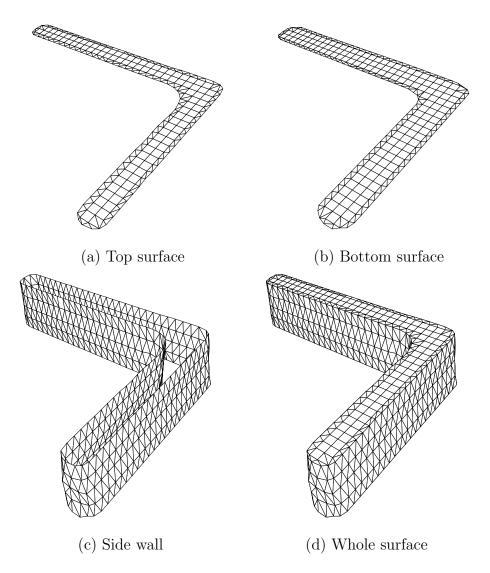

#### 1. Surface Discretization

BEM (Boundary Element Method) capacitance extraction algorithms are based on surface discretization which is easier to reconstruct the irregular interconnect shape after lithography simulation. Start from Possion's equation,  $\nabla^2 \Phi = \rho$ , where  $\Phi$  is the surface potential,  $\rho$  is the charge density in dielectric. Discretize the conductor surfaces into small panels and formulate the problem using a linear system Pq = V, where  $q \in \mathbb{R}^n$  is the vector of unknown panel charges,  $v \in \mathbb{R}^n$  is the vector of known panel potentials,  $P \in \mathbb{R}^{n \times n}$  is the potential coefficient matrix computed by Green's Function and boundary condition and n is the number of panels.

The first problem that we need to solve is how to discretize irregular shape interconnect surface, that is, how to do 3D reconstruction for the interconnect after lithography simulation. Here, we proposed a surface discretization algorithm for any 3D field solver based on the Boundary Element Method such as FastCap[22] [17], which can handle quadrilateral and triangular shape. In current extraction flow, FastCap is used. The discretization includes two parts: 1) constructing the side wall, and 2) constructing the top and bottom surfaces.

Based on the characteristics of lithography simulation result, we read the simulation output into vector L[n], where L[i] stores the head of a list of points on the ith layer, and n is the number of layers. To construct the side wall from the contours is not a trivial task. Here, to trade off the speed and accuracy, we present a simple yet effective algorithm. The main idea is to connect points in neighbouring layers L[i] and L[i+1] according to the following rules. If point A and B are in layer L[i], and point C and D are in layer L[i+1], as shown in Fig. 13. Let point A' be the projection of point A on the plane of i+1th layer. There are two cases which we need to deal with:

- 1. If line AB and CD are coplanar, then we can connect these four points in clockwise to form a quadrilateral ABDC as shown in Fig. 13(a).

- 2. If line AB and CD are not coplanar, then we can connect four points to form two triangles. If the distance AD is less than BC, then we generate two triangles  $\Delta ADC$  and  $\Delta ABD$  in clockwise shown in Fig. 13(b). Otherwise, we generate two triangles  $\Delta ABC$  and  $\Delta BCD$  as shown in Fig. 13(c).

Fig. 13. Two cases to connect four points.