# DESIGN AND ANALYSIS OF DYNAMIC THERMAL MANAGEMENT IN CHIP MULTIPROCESSORS (CMPS)

A Dissertation

by

IN CHOON YEO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2009

Major Subject: Computer Science

# DESIGN AND ANALYSIS OF DYNAMIC THERMAL MANAGEMENT IN CHIP MULTIPROCESSORS (CMPS)

A Dissertation

by

#### IN CHOON YEO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Eun Jung Kim Committee Members, Valerie E. Taylor Hank Walker

Peng Li

Head of Department, Valerie E. Taylor

December 2009

Major Subject: Computer Science

#### ABSTRACT

#### Design and Analysis of

Dynamic Thermal Management in Chip Multiprocessors (CMPs). (December 2009)

In Choon Yeo, B.S., Dongguk University;

M.S., Dongguk University

Chair of Advisory Committee: Dr. Eun Jung Kim

Chip Multiprocessors (CMPs) have been prevailing in the modern microprocessor market. As the significant heat is converted by the ever-increasing power density and current leakage, the raised operating temperature in a chip has already threatened the system's reliability and led the thermal control to be one of the most important issues needed to be addressed immediately in chip designs. Due to the cost and complexity of designing thermal packaging, many Dynamic Thermal Management (DTM) schemes have been widely adopted in modern processors.

In this study, we focus on developing a simple and accurate thermal model, which provides a scheduling decision for running tasks. And we show how to design an efficient DTM scheme with negligible performance overhead. First, we propose an efficient DTM scheme for multimedia applications that tackles the thermal control problem in a unified manner. A DTM scheme for multimedia applications makes soft realtime scheduling decisions based on statistical characteristics of multimedia applications. Specifically, we model application execution characteristics as the probability distribution of the number of cycles required to decode frames. Our DTM scheme for multimedia applications has been implemented on Linux in two mobile processors providing variable clock frequencies in an Intel Pentium-M processor and an Intel

Atom processor. In order to evaluate the performance of the proposed DTM scheme, we exploit two major codecs, MPEG-4 and H.264/AVC based on various frame resolutions. Our results show that our DTM scheme for multimedia applications lowers the overall temperature by 4 °C and the peak temperature by 6 °C (up to 10 °C), while maintaining frame drop ratio under 5% compared to existing DTM schemes for multimedia applications. Second, we propose a lightweight online workload estimation using the cumulative distribution function and architectural information via Performance Monitoring Counters (PMC) to observe the processes dynamic workload behaviors. We also present an accurate thermal model for CMP architectures to analyze the thermal correlation effects by profiling the thermal impacts from neighboring cores under the specific workload. Hence, according to the estimated workload characteristics and thermal correlation effects, we can estimate the future temperature of each core more accurately.

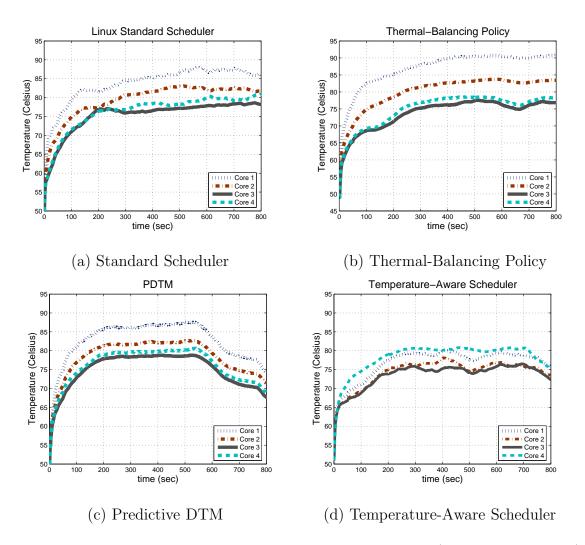

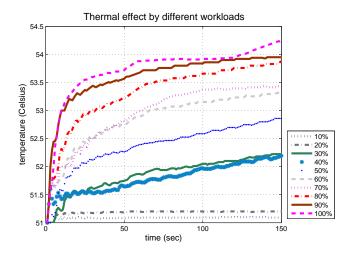

We implement a DTM scheme considering workload characteristics and thermal correlation effects on real machines, an Intel Quad-Core Q6600 system and Dell PowerEdge 2950 (dual Intel Xeon E5310 Quad-Core) system, running applications ranging from multimedia applications to several benchmarks. Experiments results show that our DTM scheme reduces the peak temperature by 8% with 0.54% performance overhead compared to Linux Standard Scheduler, while existing DTM schemes reduce peak temperature by 4% with up to 50% performance overhead.

To my family

#### ACKNOWLEDGMENTS

I am sincerely grateful to my advisor, Dr. Eun Jung Kim, for allowing me to conduct research with her. I am constantly amazed by her extraordinary ability to transform seeming unsolvable problems into a tractable form her infinite knowledge on subject matters, and her relentless attention to detail. Her exceptional commitment to research and strong demand for excellence have guided me this far. I am truly grateful to her insightful advice, her encouragement and constant motivation throughout this work.

I would also like to thank professors Valerie E. Taylor, Hank Walker, and Peng Li for their service on my advisory committee. Their insightful comments and constructive criticism helped me improve my research. In addition, I am deeply grateful to Dr. Kihwan Yum for giving me powerful advising during this study.

Furthermore, I would like to thank my friends and fellow students at Texas A&M University for numerous discussions about various issues related to research and lives. I sincerely thank current and former members of the High Performance Computer Lab for being supportive of me during this work. I also want to thank Seung-Ryong Kang, Young-Woo Ahn, Seung-Jin Sul for being great friends and for always being available whenever I need their assistance and help. I also thank to Chih-Chun Liu for being a great friend and for always being available whenever I need his assistance and help. All my friends at Texas A&M University have helped me in various ways during the years of my Ph.D. program. I thank them all, especially Sun-Hwan Jang, Jae-Woo Seo, Yoon-Jin Kim, Gun-Hee Jo, Ja-Ryeong Koo, Baik-Song Ahn, Heung-Ki Lee, and Ju-Young Jung.

Last, but not least, I would like to thank my parents and my family members

for their continuous support and encouragement. I am especially grateful to my wife for her endless support and love. Without her dedication and belief in me, this work would have been impossible.

## TABLE OF CONTENTS

| CHAPTER | I                                                                                                                                                                                                                                                                                                                | Page                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| I       | INTRODUCTION                                                                                                                                                                                                                                                                                                     | 1                                                  |

| II      | BACKGROUND AND RELATED WORK                                                                                                                                                                                                                                                                                      | 7                                                  |

|         | A. Dynamic Thermal Management in Single Core Architecture B. Dynamic Thermal Management in Multicore Architecture .                                                                                                                                                                                              | 7<br>8                                             |

| III     | EFFECTIVE DYNAMIC THERMAL MANAGEMENT FOR MPEG-4 DECODING                                                                                                                                                                                                                                                         | 12                                                 |

|         | A. Thermal Issues in Multimedia Applications  B. Overview of a Feedback Control  C. Advanced Feedback Controller Using GOP Information  D. Thermal Control Using GOP Information  E. DTM with the Advanced Feedback Controller  F. Experimental Results and Analysis  G. Conclusions                             | 13<br>14<br>17<br>20<br>23<br>26<br>27             |

| IV      | THERMAL-AWARE SCHEDULING BASED ON STATISTICAL CHARACTERISTICS OF MULTIMEDIA APPLICATIONS                                                                                                                                                                                                                         | 29                                                 |

|         | <ul> <li>A. The Problems of Multimedia Applications Processing</li> <li>B. The Workload of Multimedia Applications</li> <li>C. Thermal-Aware Scheduling for Multimedia Applications</li> <li>D. Application Characteristics Profiler for Multimedia Applications</li> <li>E. Experimental Environments</li></ul> | 31<br>33<br>36<br>38<br>42<br>44<br>44<br>47<br>52 |

| V       | PREDICTIVE DYNAMIC THERMAL MANAGEMENT FOR MULTICORE SYSTEMS                                                                                                                                                                                                                                                      | 55                                                 |

| CHAPTER |                                                                                                             | Page           |

|---------|-------------------------------------------------------------------------------------------------------------|----------------|

|         | <ul> <li>A. Predictive Thermal Model</li></ul>                                                              | 57<br>57<br>60 |

|         | 3. The predictive thermal model                                                                             | 61             |

|         | B. PDTM Scheduler                                                                                           | 62             |

|         | C. Experimental Results and Analysis                                                                        | 66<br>67       |

|         | <ol> <li>Digital thermal sensor for Intel quad-core</li> <li>Experimental results and analysis</li> </ol>   | 68             |

|         | D. Conclusions                                                                                              | 69             |

| VI      | TEMPERATURE-AWARE SCHEDULER BASED ON THERMAL BEHAVIOR GROUPING IN MULTICORE SYSTEMS                         | 70             |

|         | A. Thermal Behavior Group                                                                                   | 73             |

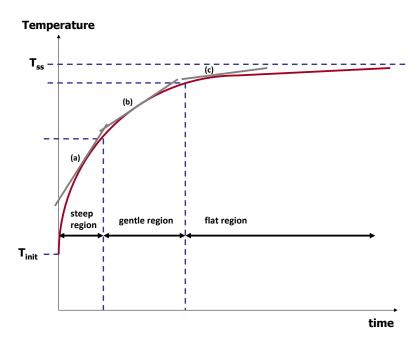

|         | tions' thermal pattern                                                                                      | 74             |

|         | 2. The region of the thermal behavior group                                                                 | 77             |

|         | B. Temperature-Aware Scheduler for Multicore Systems                                                        | 79             |

|         | C. Experimental Results and Analysis                                                                        | 82             |

|         | 1. 4-core system                                                                                            | 83<br>83       |

|         | 2. 8-core system                                                                                            | 84             |

| VII     | A THERMAL MODEL BASED ON WORKLOAD CHAR-                                                                     |                |

|         | ACTERISTICS USING CDF                                                                                       | 85             |

|         | A. A Representative Workload Estimation Based on CDF                                                        | 85             |

|         | 1. The definition of workload                                                                               | 86             |

|         | 2. The statistical representative to estimate workload $$                                                   | 86             |

|         | 3. Thermal parameters in CMP systems                                                                        | 88             |

|         | B. Thermal Mode Based on Workload                                                                           | 91             |

|         | 1. Prior thermal model of a single core                                                                     | 93             |

|         | 2. The thermal impacts contributed by different workloads                                                   |                |

|         | 3. New $T'_{ss}$ according to thermal correlation                                                           | 94             |

|         | <ul><li>4. New b' according to thermal correlation</li><li>5. Future temperature estimation model</li></ul> | 96<br>97       |

|         | C. A Proactive Correlation-aware Thermal Management                                                         | 100            |

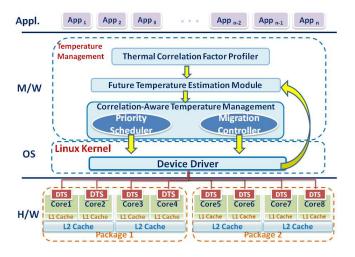

|         | 1. System overview                                                                                          | 100            |

|         | 2. Thermal-aware thread scheduler (TATS)                                                                    | 102            |

|         | D. Experimental Results and Analysis                                                                        | 104            |

| CHAPTER  |                                                                                           | Page       |

|----------|-------------------------------------------------------------------------------------------|------------|

|          | E. Conclusions                                                                            | 107        |

| VIII     | A THERMAL MODEL FOR CMPS CAPTURING WORK-LOAD CHARACTERISTICS AND NEIGHBORING CORE EFFECTS | 109        |

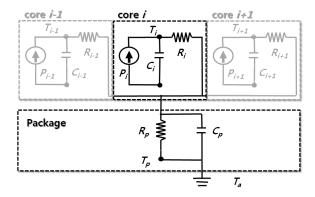

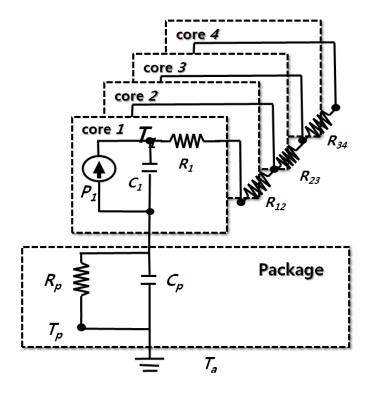

|          | A. The Lumped Thermal RC Model                                                            | 111<br>115 |

| IX       | CONCLUSIONS AND FUTURE WORK                                                               | 123        |

| REFERENC | CES                                                                                       | 126        |

| VITA     |                                                                                           | 131        |

### LIST OF TABLES

| TABLE |                                                                                                                                                          | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| I     | Experimental systems description                                                                                                                         | 42   |

| II    | The experimental multimedia data (Standard Definition)                                                                                                   | 43   |

| III   | The experimental multimedia data (High Definition)                                                                                                       | 43   |

| IV    | Environments parameters                                                                                                                                  | 67   |

| V     | A set of benchmarks list                                                                                                                                 | 67   |

| VI    | The result of thermal behavior group using $K$ -means clustering on 4-core system                                                                        | 76   |

| VII   | Experimental systems descriptions                                                                                                                        | 82   |

| VIII  | Each core's respective $T_{ss}$ and thermal parameter $b$ for a generated example process with 100% workload running in the Intel Quad Core Q6600 system | 92   |

| IX    | The thermal parameter $b$ and $T_{ss}$ according to workload in 4-core system                                                                            | 92   |

| X     | $T_{tc}$ and $b$ according to thermal correlation profiled for core 1                                                                                    | 96   |

| XI    | The ratio of $T_{ss}$ for cores in an Intel Quad-Core processor                                                                                          | 119  |

### LIST OF FIGURES

| FIGURE | $\Xi$                                                                                                                                                                     | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

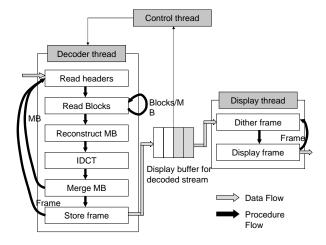

| 1      | MPEG process with display buffers                                                                                                                                         | 14   |

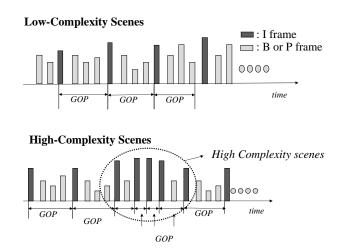

| 2      | Low complexity vs. high complexity scenes                                                                                                                                 | 18   |

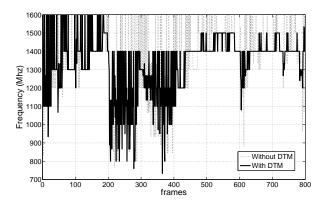

| 3      | Comparison with DTM and without DTM for frequency                                                                                                                         | 25   |

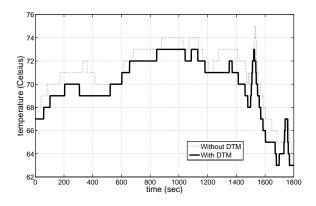

| 4      | Temperature comparison with and without DTM                                                                                                                               | 26   |

| 5      | Variance of temperature of high-complexity movies                                                                                                                         | 28   |

| 6      | Variance of temperature of mid- and low-complexity movies                                                                                                                 | 28   |

| 7      | The timing gap between decoding and displaying data using the buffer management                                                                                           | 32   |

| 8      | The workload of decoding and displaying multimedia data according to several codecs and frame resolutions                                                                 | 34   |

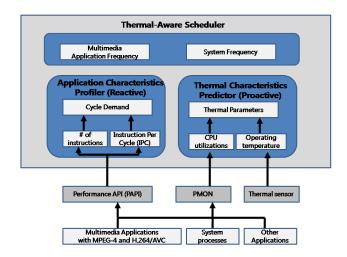

| 9      | TAS overview                                                                                                                                                              | 37   |

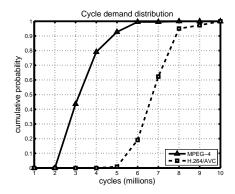

| 10     | The cumulative distribution function (cdf) of decoding frames in the multimedia application                                                                               | 40   |

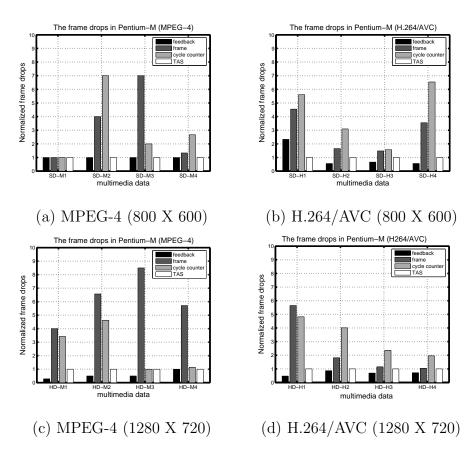

| 11     | The frame drop of standard definition multimedia data encoded by MPEG-4 and H.264/AVC in Intel Pentium-M processor                                                        | 45   |

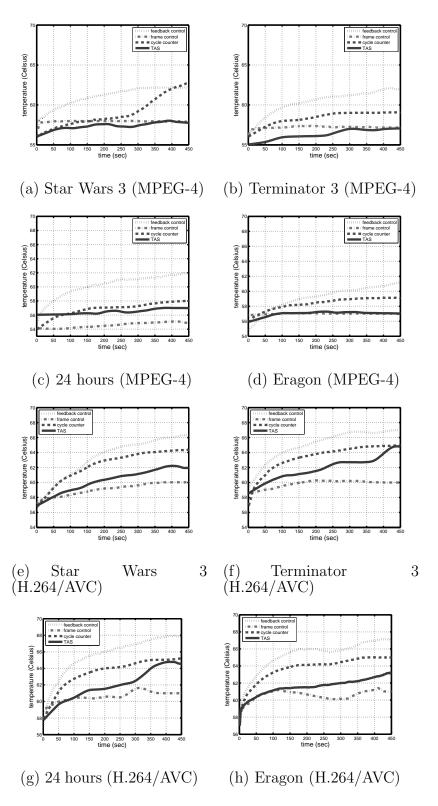

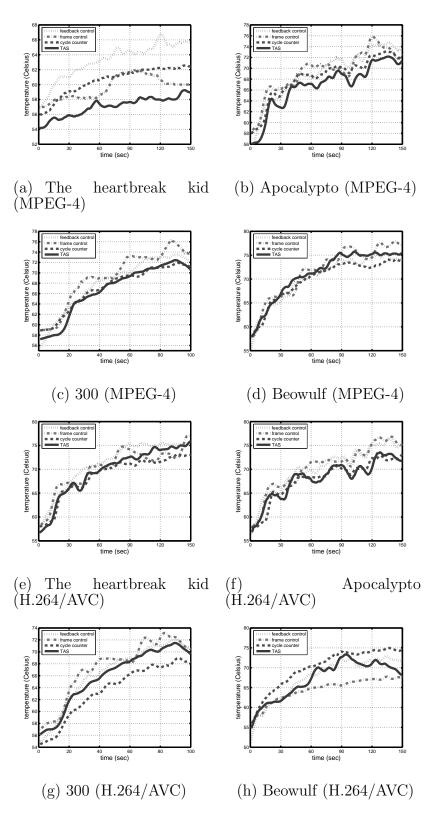

| 12     | Resulting temperatures with feedback, frame, cycle counter, and TAS in the standard definition multimedia data in Intel Pentium-M processor (frame resolution: 800 X 600) | 48   |

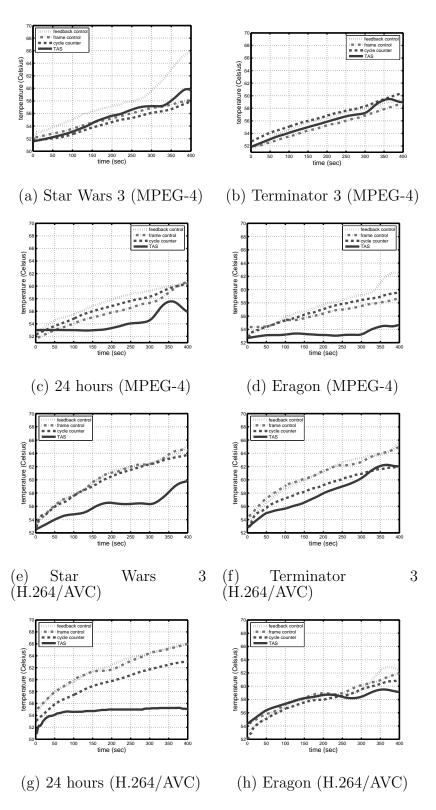

| 13     | Resulting temperatures with feedback, frame, cycle counter, and TAS in the high definition multimedia data in Intel Pentium-M processor (frame resolution: 1280 X 720)    | 49   |

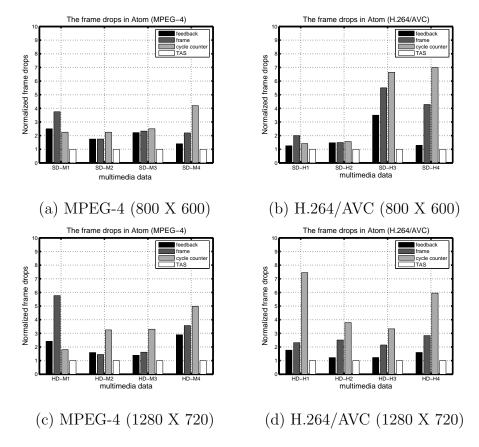

| 14     | The frame drop of standard definition multimedia data encoded by MPEG-4 and $\rm H.264/AVC$ in Intel Atom processor                                                       | 50   |

| FIGURI | E                                                                                                                                                                    | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

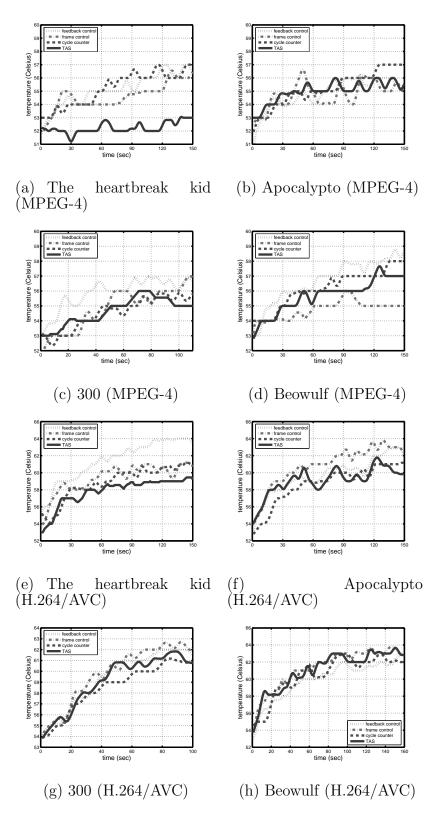

| 15     | Resulting temperatures with feedback, frame, cycle counter, and TAS in the standard definition multimedia data in Intel Atom processor (frame resolution: 800 X 600) | 53   |

| 16     | Resulting temperatures with feedback, frame, cycle counter, and TAS in the high definition multimedia data in Intel Atom processor (frame resolution: 1280 X 720)    | 54   |

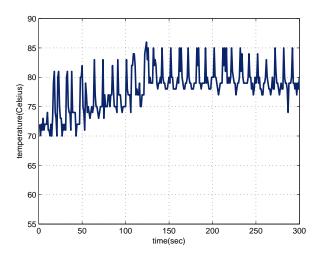

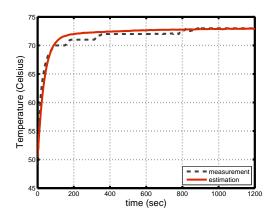

| 17     | Real temperature of one core on running bzip2 benchmark                                                                                                              | 58   |

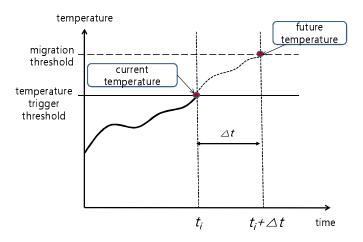

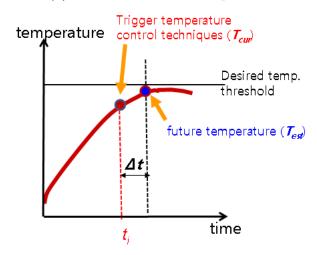

| 18     | The calculation of $\Delta t$ (migration time) using ABTM                                                                                                            | 60   |

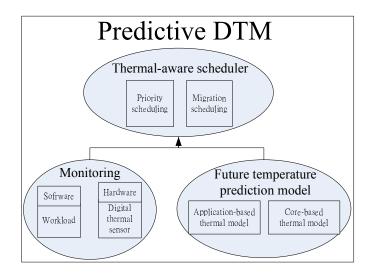

| 19     | System overview                                                                                                                                                      | 63   |

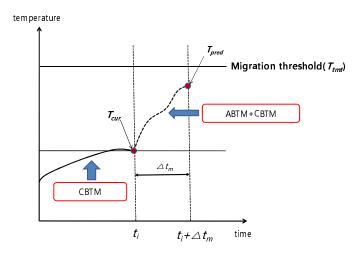

| 20     | PDTM utilizes ABTM and CBTM simultaneously to predict both short-term and long-term future temperature for multicore                                                 | 65   |

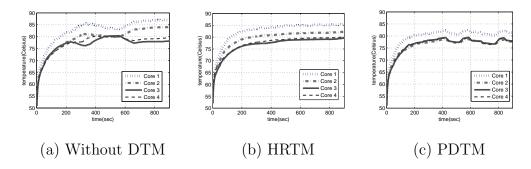

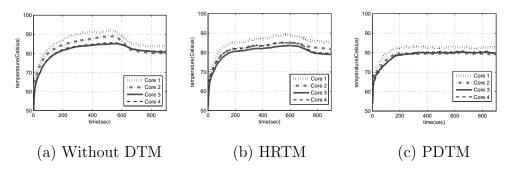

| 21     | Comparisons among without DTM, HRTM, and PDTM using libquantum benchmarks                                                                                            | 66   |

| 22     | Comparisons among without DTM, HRTM, and PDTM using bzip2 and libquantum benchmarks                                                                                  | 66   |

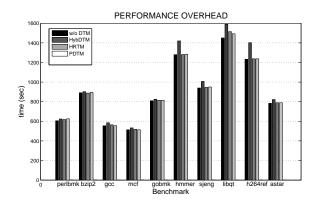

| 23     | Performance overhead: PDTM incurs only under 1% performance overhead in average while running single benchmark                                                       | 68   |

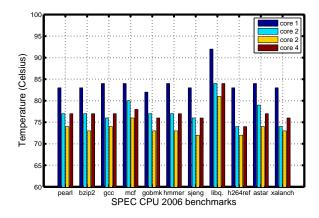

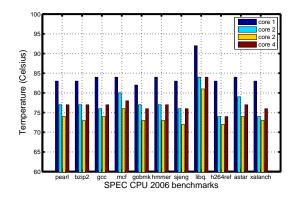

| 24     | $T_{ss}$ according to SPEC CPU 2006 benchmark suite                                                                                                                  | 72   |

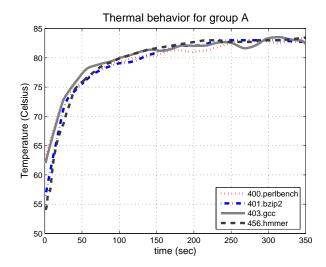

| 25     | Thermal behavior for Group A                                                                                                                                         | 74   |

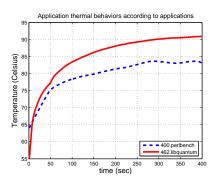

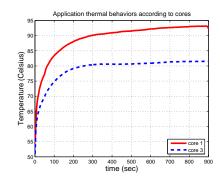

| 26     | The application thermal behavior according to applications and cores                                                                                                 | 75   |

| 27     | Slopes for the thermal pattern at runtime                                                                                                                            | 78   |

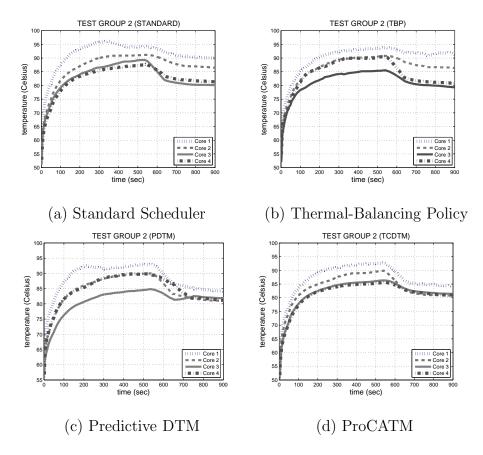

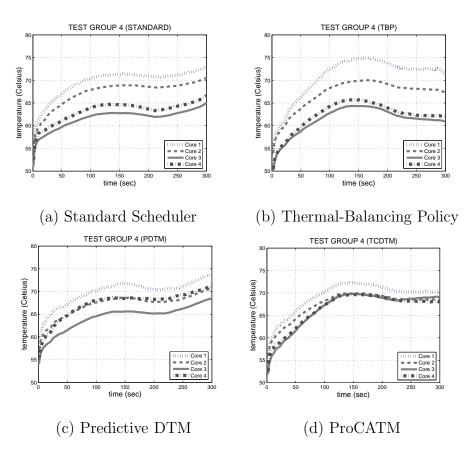

| 28     | DTM evaluations in 4-core system using test group 2 (bzip2 + libquantum)                                                                                             | 81   |

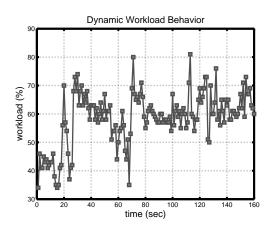

| 29     | The representative workload is 58% when the probability $(\rho)$ is 0.7 in dynamic workload behavior                                                                 | 88   |

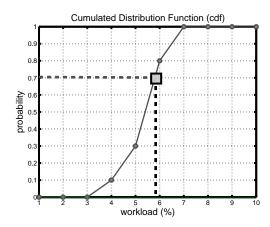

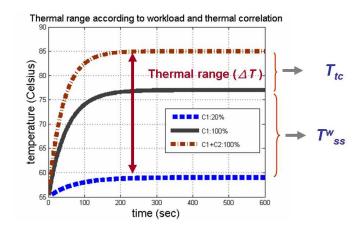

| 30     | Thermal effects by different workloads                                                                                                                               | 92   |

| FIGURI | ${\mathbb F}$                                                                                                                                                                                                                                                                      | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 31     | The thermal range $(\Delta T)$ using $T_{ss}^w$ and $T_{tc}$ to calculate $T_{ss}'$ for core 1                                                                                                                                                                                     | 94   |

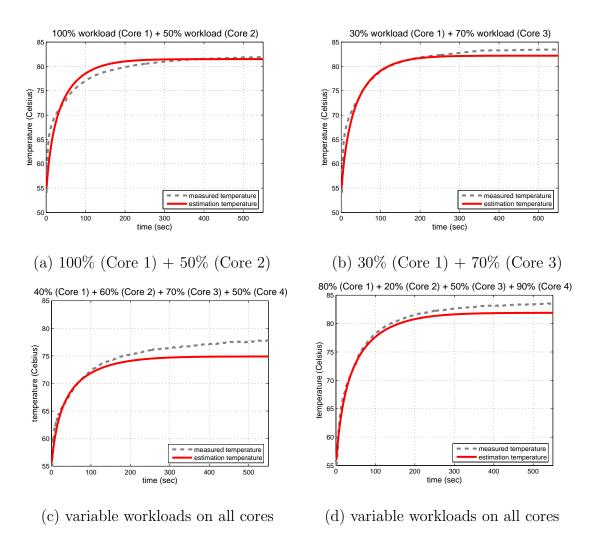

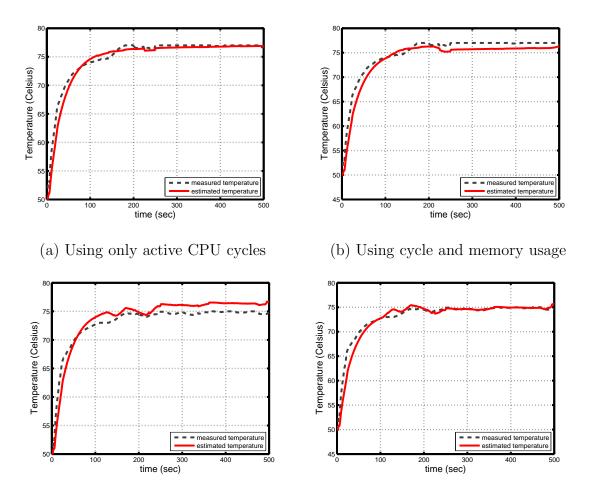

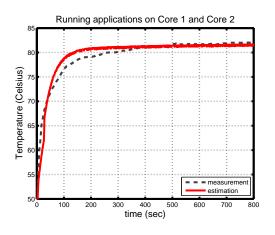

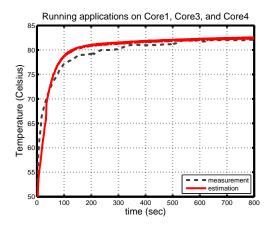

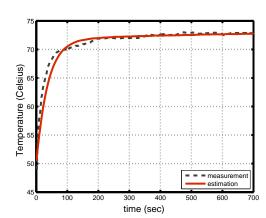

| 32     | Validation of improved thermal model with workload estimation and thermal correlation in static application. (Only core 1's temperature is drawn)                                                                                                                                  | 99   |

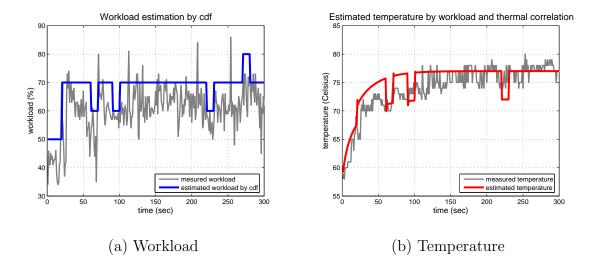

| 33     | Validation of new thermal model with fluctuant workload: whiling playing the <i>Transformer</i> movie, the Mplayer software would generate two threads. One is the X windows daemon with stable workload, and the other one is for decoding with fluctuant workload as shown above | 100  |

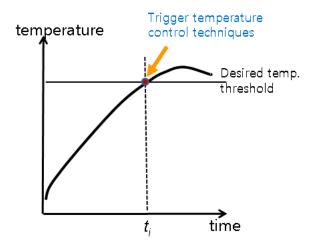

| 34     | The difference of thermal control based on current temperature and future temperature                                                                                                                                                                                              | 101  |

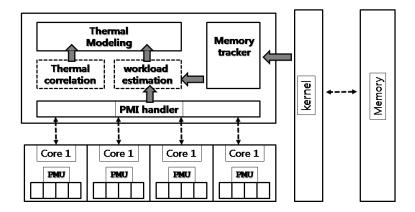

| 35     | ProCATM system architecture                                                                                                                                                                                                                                                        | 102  |

| 36     | DTM evaluation in Intel Quad Core Q6600 system for stable workload behaviors: $libquantum + vacation \dots \dots \dots \dots$ .                                                                                                                                                    | 104  |

| 37     | DTM evaluation in Intel Quad Core Q6600 for dynamic workload behaviors: Multimedia                                                                                                                                                                                                 | 106  |

| 38     | An extended lumped thermal RC circuit model for a single core in a CMP architecture                                                                                                                                                                                                | 111  |

| 39     | $T_{ss}$ of SPEC CPU 2006 benchmarks                                                                                                                                                                                                                                               | 112  |

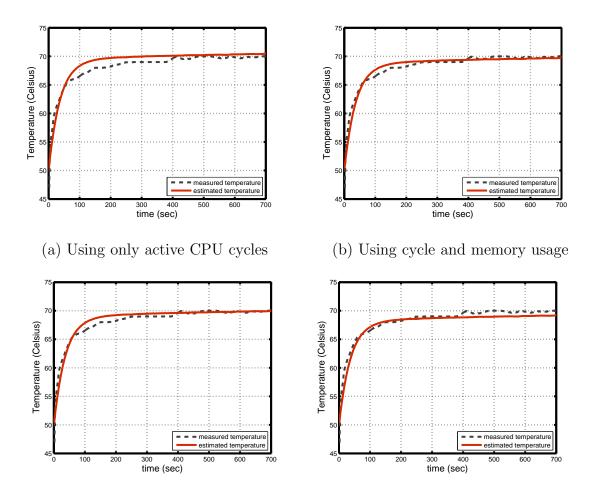

| 40     | Temperature tracking using architectural information in SPEC CPU integer benchmarks                                                                                                                                                                                                | 116  |

| 41     | Temperature tracking using architectural information in SPEC CPU floating-point benchmarks                                                                                                                                                                                         | 117  |

| 42     | The extended thermal model for CMP architecture                                                                                                                                                                                                                                    | 118  |

| 43     | The proposed platform                                                                                                                                                                                                                                                              | 120  |

| 44     | The comparisons between the estimated temperature considering workload characteristics and thermal correlation effects and the measured temperature in a CMP architecture                                                                                                          | 121  |

#### CHAPTER I

#### INTRODUCTION

Chip Multiprocessors (CMPs) have become the main trend in the design of new generation processors. CMP architectures include several cores within one single die area to increase their performance. Instead of pushing the limits of a processor's frequency, the demand for more capable microprocessors must be satisfied by other methods. However, decreased chip size and increased power-density produces a significant amount of heat, threatens system performance and reliability, and even increases power leakage. This heat dissipation is pushing the limits of current packaging technology and cooling solutions. Packages are designed for the worst typical behaviors and rely on Dynamic Thermal Management (DTM) techniques to control temperature at runtime. Therefore, over the past decade, chip design trends have shift to providing more effective thermal managements.

Brooks and Martonosi [1] state the key goals of DTM as: (1) providing inexpensive hardware or software responses, (2) reliably reducing power, and (3) impacting performance as little as possible. Although many hardware-based temperature control techniques, such as Dynamic Frequency and Voltage Scaling (DVFS) and clock gating, have been proposed and applied in modern processors, the demand for more efficient techniques is prevailing in modern microprocessors. [1, 2, 3, 4, 5, 6].

Although modern microprocessors can meet the computation requirement for multimedia data, the high definition multimedia data requires high computations, which converts into a huge amount of heat in modern embedded systems. Therefore, it is critical to keep the temperature of microprocessors under safe limits at runtime.

The journal model is IEEE Transactions on Networking.

In DTM schemes for modern processors, DVFS is a common method to control temperature. However, due to the nature of multimedia applications with different frame sizes and types in data, it is not easy to match their QoS requirements while temperature is under control. There have been a handful of studies on thermal managements for multimedia systems [7, 8, 9, 10, 4, 11]. However, according to our observations, these schemes tend to overestimate or underestimate multimedia application requirements. Their results inevitably lead to manage operating temperature high or degrade their performance. In order to compensate the tradeoff between QoS and temperature control, we derive application execution characteristics in various multimedia codecs such as MPEG-4 and H.264/AVC. The application execution characteristics can be represented by the probability distribution of cycle demand that is the number of cycles required to decode a frame. Using this representation, we estimate an adequate processor speed to execute multimedia applications for decoding frames at runtime. Then, we develop Thermal-Aware Scheduler (TAS) that takes optimal frequencies to avoid thermal emergencies while minimizing performance degradations in real environments. We experiment on Intels Pentium-M and Atom processors using various multimedia data encoded by MPEG-4 and H.264/AVC. Compared to feedback control scheme [10], Frame-based scheme [12] and cycle counter-based scheduler [13], TAS lowers average temperature by 6 °C and peak temperature by 10 °C or more, with maximum 5% frame drop ratio.

In DTM schemes for CMP architectures, a thread migration has been proposed to achieve thermal balance among cores without throttling the computation performance in CMP architectures. However, several studies are reactive to the increased chip temperature, while others, such as [4, 5], are proactive based on the predicted future temperature. The proactive DTMs are more effective in temperature control and preventing thermal emergencies, for they trigger the control schemes before the

core temperature reach the desired threshold. Since applications have used different functional units that can affect operating temperature, the temperature difference among applications can be up to 9 °C [2, 3]. In fact, the temperature difference between on-chip components can be as much as  $10 \sim 15$  °C [3]. Also, all applications do not result in the same heat dissipation pattern. In other words, there are significant variations in the thermal characteristics of different applications [3, 4] and different cores in the same chip.

Also, according to our observations, the temperature of a core varies by 2 °C to 16 °C depending on different levels of thermal correlation in a 4-core CMP system. The temperature of a component is highly correlated with those of other components in the same chip [14, 15, 16, 3]. The temperature model, capturing correlation effects in a uniprocessor, cannot be directly applied to that of a CMP, due to their potential heterogeneity where each core has an independent task to run. Furthermore, [14, 4] have already reported the significant variations in the thermal behaviors of different applications. Although there have been a handful of studies using simple workload models, such as average workload and Instructions Per Cycle (IPC), these studies measured the workload information offline for temperature managements [17, 18]. We believe that it is critical to develop an efficient and online application-based thermal model for DTM which is applicable to real world applications that have dynamic workload behaviors and distinct thermal contributions to the chip temperature. To demonstrate the proposed DTM scheme's scalability and efficiency, especially to satisfy the demand of thermal control in the recent server environments, we implement and evaluate our DTM scheme on real machines, an Intel Quad-Core Q6600 system and Dell PowerEdge 2950 (dual Intel Xeon E5310 Quad-Core) system, running applications ranging from multimedia applications to several benchmarks. For several applications with dynamic workload behaviors, experiments results show that our

DTM scheme reduces the peak temperature by 8% with 0.54% performance overhead compared to Linux Standard Scheduler, while existing DTM schemes reduce peak temperature by 4% with up to 50% performance overhead.

In summary, this thesis focuses on dynamic thermal managements in CMP architectures with negligible performance overhead. Specifically, the contributions of this thesis are follows:

- A near-optimal thermal management in various multimedia systems. We estimate multimedia applications' thermal characteristics using statistical approaches to be suitable for various multimedia codecs. A thermal-aware scheduler for multimedia systems provides soft realtime performance guarantees with statistical processor allocations.

- A better understanding of how the workload for running applications affects operating temperature in CMP architectures. We define the dynamic workload for running applications as a statistical function (cdf) and a workload characteristics function w(t) at a given interval time [t-1,t]. Also, the workload characteristics function consists of a positive factor and negative factors obtained by Performance Monitoring Counters (PMC). These analytical results provide a statistical approach to understand the temperature variations influenced by applications.

- Thermal correlation effects can explain how the heat transfer works in real CMP products. Thermal models for CMP architectures should consider the heat transfer among cores, which is defined as the thermal correlation effects. The thermal model, capturing thermal correlation effects in a uniprocessor, cannot be directly applied to the thermal model of CMP architectures due to the potential heterogeneity where each core has an independent task to run. We provide an

extended thermal model based on thermal correlation effects in CMP architectures.

- A measurement of temperature via Digital Thermal Sensor (DTS). In order to estimate temperature through Digital Thermal Sensor (DTS) in CMP architecture, we develop a specific device driver to access them at runtime. In a silicon die of CMP, each core has a unique thermal sensor that triggers independently. The trigger point of these thermal sensors is not programmable by software since it is set during the fabrication of the processor [19].

- Application-Based Thermal Management. Basically, an Application-Based Thermal Management (ABTM) consists of three major components: an application-based thermal model, a future temperature estimation, and a thermal-aware scheduler. We used a specific device driver for Linux to access the Digital Thermal Sensor (DTS) and measure each core's real temperature, and then used the temperature information in the future temperature estimation. Also, we used an application-based thermal model to exploit the thermal model according to each application's execution behavior. At the same time, the future temperature estimation utilizes the workload characteristics and thermal correlation effects to estimate the future temperature and the time left until the temperature reaches the migration threshold. Hence, the thermal-aware scheduler is able to react to the thermal emergency appropriately using the estimated information.

The rest of the thesis is organized as follows. In Chapter II, we describe background and related work of this thesis. In Chapter III, we propose an efficient thermal management for multimedia applications. We consider how the performance of a multimedia system is affected by the complexity of scenes, and then we find an appropriate frequency based on the information on scene complexity. In Chapter IV, we first derive

the applications' characteristics in various multimedia applications by transmitting MPEG-4 and H.264/AVC encoded by two different frame resolutions. By using those applications' characteristics, we estimate a frequency to execute multimedia applications which decode frames at runtime. In Chapter V, we present an advanced future temperature prediction model for each core. This allows us to estimate the thermal behavior considering both core temperature and applications temperature variations, and to take appropriate measures to avoid thermal emergencies. In Chapter VI, the proposed thermal-aware scheduler scheme utilizes an advanced future temperature prediction model for each core to estimate different thermal behaviors and measures the amount of time it takes for each core to reach the desired temperature threshold. In Chapter VII, we further model thermal correlation effects by profiling the thermal impacts from neighboring cores under the specific workload. Finally, in Chapter VIII, we propose a thermal model based on thermal correlation effects and online workload estimation using architectural information. In Chapter IX, we conclude this thesis and discuss future work.

#### CHAPTER II

#### BACKGROUND AND RELATED WORK

In this chapter, we review prior work in the areas of dynamic thermal managements.

#### A. Dynamic Thermal Management in Single Core Architecture

Several schemes using architecture adaptation provide Dynamic Thermal Management (DTM) solutions [1, 2]. Brooks and Martonosi suggested the fetch toggling to avoid thermal limit using the stall of instruction fetching [1]. Heo, et al. transformed the fetched computation into other duplicated unit during cooling down the overheated unit [2]. However, these schemes cannot satisfy the workload deadline in real-time. Especially, missed deadlines result in low performance in multimedia systems.

Skadron, et al. suggested several thermal management schemes including temperature-tracking [16], hybrid scheme [3], and feedback control [20, 10]. [16] used the temperature-tracking scheme to manage temperature based on frequency scaling, localized toggling, and computation migrations. [3] proposed a hybrid scheme combining fetch gating and DVFS. Also, a feedback control configures temperature based on feedback information [20, 10]. Since the approach introduced by Skadron, et al. does not take into account the complexity of scenes for multimedia, it cannot avoid the degradation of performance in multimedia applications with radical picture changes.

In [20], Mircea, et al. designed a thermal model using the thermal behavior, thermal resistances, and thermal capacitances within functional blocks at the architectural level. Many temperature researches have adopted this model. Althoug thermal behavior can be detected at runtime, this requires specific hardware, such as the built-in Performance Monitoring Counter (PMC) [21].

DTM schemes can be roughly grouped into two approaches: proactive schemes [4, 22, 8, 9, 23, 7] and reactive schemes [20, 24, 10]. In proactive schemes, the results of the previous task determine the speed of the multimedia system. Pouwelse, et al. estimated the decoding time per frame based on the offline information on decoding time and frame size [22, 8]. In [9], the Frame Data Computation Aware (FDCA) estimated the decoding time for incoming frames based on the information on decoding macro blocks. However, their method did not require any pre-profile information. [4] proposed predictive thermal management using profiled information, which showed the maximum performance under the thermal constraints. [23] presented an offline scheduling algorithm to save power with quality degradation.

In contrast, reactive schemes determine the speed of the system based on historical information. [24] designed a user-level power management, in which daemons configure the speed setting of the CPU using the characteristics of applications, such as soft real-time, interactive, and batch program. Also, [20, 10] designed feedback control in multimedia systems. Control modules change the level of frequency based on the occupancy of the display buffer. In [7], Son, et al. suggested two schemes including proactive and reactive. Their reactive scheme configured the frequency based on delay and drop frame rate, while the proactive scheme determined the frequency using the predicted decoding time based on the future GOP size. However, this scheme needs a profiling process before decoding a GOP.

#### B. Dynamic Thermal Management in Multicore Architecture

Nowadays, several thermal control techniques [1, 3] via hardware-based mechanisms, such as Dynamic Frequency Scaling (DFS), Dynamic Voltage Scaling (DVS), and clock gating, have been proposed and applied in modern processors. However, these

DTM mechanisms belong to temporal thermal control and bring high execution performance overhead. Therefore, as multicore systems become more popular, some software-based spatial thermal control mechanisms, such as [6, 17, 5], have been studied in a CMP system.

In [17], the proposed mechanism, called heat-and-run, has two key components: SMT thread assignment and CMP thread migration. Within heat-and-run the SMT thread assignment attempts to increase processor-resource utilization by co-scheduling threads which use complementary resources. The CMP thread migration moves threads away from overheated cores and assigns them to free SMT contexts on alternate cores. This maintains throughput while cooling the overheated cores. They evaluated their experiments in an extended Wattch simulator by running five threads within four cores. Heat-and-run thread assignment (HRTA) and heat-and-run thread migration (HRTM) achieve 9% higher average throughput than stop-go and 6% higher average throughput than DVS. Moreover, [25] confirmed that when performance is constrained by temperature, the performance gains brought by thread migration and the importance of limiting the migration frequency to reduce performance overhead. [17] proposed new migration method for temperature-constrained multicore in order to exchange threads whenever the simultaneous occurrence of a cold and a hot core is detected. The authors demonstrate that their method yields the same throughput as HRTM, but requires much fewer migrations. However, the performance overhead migrations cause is not further considered according to the application memory usage.

Mulas et al. show that the thread with less memory usage tends to migrate easier than other threads, thus reducing the performance overhead caused by migrations [6]. However, this study ignores the application workload behaviors are ignored. That implies that sets of running threads will migrate without considering the different thermal effects caused by various threads, while the core temperature reaches the

upper/lower temperature threshold. Furthermore, these studies are based on simulated results, and neglect thermal correlation among cores. The power dissipated by the rest of the chip is assumed to be negligible. Moreover, in this studies the migration action is triggered by the current temperature (when temperature is higher than the maximum allowed temperature).

Kumar et al. provide using HybDTM, a methodology for fine-grained, coordinated thermal management using both software (priority scheduling) and hardware (clock gating) techniques. HybDTM estimates temperature by using a regression-based thermal model based on Performance Monitoring Counters [26]. However, HybDTM cannot effectively reduce overheat temperature without noticeable performance overhead (9.9% performance overhead compared to cases without any DTM). This is why Performance Monitoring Counters cannot solely estimate real temperature. Also, both priority scheduling and clock gating generated high performance overhead. Most importantly, these proposed thermal management mechanisms make impractical assumptions and have only been evaluated by running benchmarks, which have stable application workloads and thermal behaviors. For example, HRTA cannot co-schedule threads without knowing the thread characteristics, such as Instructions Per Cycle (IPC) information and execution resources.

Liu et al. propose an application level power management, called Chameleon, for real-world user applications [24]. Chameleon consists of three components: (1) an OS interface that can be used by power-aware applications to measure their CPU usage, (2) a CPU scheduler that supports per-process CPU power settings and application isolation, and (3) a speed adapter that maps the CPU speed settings to the nearest speed supported by the hardware. However, the need for power-aware applications is impractical, since each application's source codes need to be modified. Otherwise, LongRun is used for the legacy applications. Even though this work deals with

power management, it inspired us to develop a scalable DTM for the real-world case and more specifically, to satisfy the demand for thermal control in the recent server environment.

Michaud et al. confirm that when performance is constrained by temperature, the performance gains from thread migrations [25]. It also demonstrates the importance of limiting the migration frequency to reduce performance overhead. Hence, several advanced DTM studies [17, 18, 6] advocate providing thermal fairness and reducing the peak temperature through temperature-aware thread migration schemes. However, as presented in [3], an accurate and practical dynamic model of temperature is needed to characterize accurately current and future thermal stress and application dependent behavior, as well as to evaluate architectural techniques for managing thermal effects. Moreover, estimating thermal behavior from the average of power dissipation is unreliable. Therefore, we propose to each application's thermal behavior by characterizing its workload through the statistic probability distribution and online workload estimation based on architectural information through Performance Monitoring Counters (PMC). Most importantly, Shang et al. introduce the thermal correlation effects in the on-chip networks [27]. We are motivated to model the thermal correlation effects from neighboring cores in the CMP systems from the architecture level and further present an adaptive and scalable DTM based on the thermal correlation effects for the CMP system.

#### CHAPTER III

# EFFECTIVE DYNAMIC THERMAL MANAGEMENT FOR MPEG-4 DECODING

In this work, we present Dynamic Thermal Management (DTM) based on a Dynamic Voltage and Frequency Scaling (DVFS) technique for MPEG-4 decoding to guarantee thermal safety while maintaining a quality of service (QoS) constraint. Although many low-power and low-temperature multimedia playback techniques have been proposed, most of them are impractical in real-time and have several restricting assumptions. Multimedia data consists of several frames requiring different decoding efforts. Since both temperature and performance of a multimedia system are affected by the complexity of scenes, our main idea is to use the information on scene complexity to find an appropriate frequency. In order to predict the complexity of the current scene, we extract information from the previous group of pictures (GOP) using feedback control with a display buffer. Experimental results with twelve movies show that our DTM scheme guarantees the threshold of temperature (70 °C) while maintaining 0% frame miss ratio. Also, the proposed DTM scheme decreases the average temperature by up to 13% without any additional hardware and playback latency.

The main contributions of this research are summarized as follows:

- Our DTM scheme estimates multimedia application's characteristics according to the complexity of the scene using GOP information and frame drop ratio.

- DTM with the advanced feedback controller provides soft realtime performance guarantees under thermal safety.

- Compared to the prior DTMs for multimedia applications such as feedback

control [10], Frame-based [12], the proposed DTM lowers temperature by 13% on average when running MPEG-4 data under 5% frame drop ratio.

#### A. Thermal Issues in Multimedia Applications

Thermal issues are becoming critical in multimedia systems to achieve high reliability. Although the speed of a modern microprocessor supports processing of the multimedia data in real-time, a multimedia system consumes lots of power for computation and cooling. General purpose computer systems consume over 25% of the power for energy management such as air conditioning, backup cooling and power delivery systems [1]. However, portable battery-operated devices cannot afford such high cooling power.

Without sufficient cooling, embedded systems suffer from long-time overheating and eventually cause the system to crash. However, reducing the voltage level causes the overall performance to slow down. Therefore, the best solution to reduce energy dissipation with dynamic voltage and frequency scaling (DVFS) techniques is to dynamically adjust the voltage scales, while maintaining the minimum required circuitry to accommodate workloads within appropriate computation time and throughput constraints [12]. Multimedia data consist of different frames with different deadlines to be displayed. MPEG frames are classified into three different coding types including intra (I), predictive (P), and bi-directional (B) that consume various power/energy, which leads to raise a different amount of temperature during decoding frames. In addition, a wide variety of frame sizes make it difficult to predict power consumption and to control temperature. Furthermore, since DVFS reduces the overall computation speed, it is likely to have some frames missing their deadlines. Therefore, it is challenging to find a right speed to control system temperature without quality degradation. In [10, 20], the authors suggested a feedback control from a display buffer

to find an adequate speed without quality degradation and to reduce the power consumption of MPEG decoding. However, they did not concern thermal problems and exploited only the buffer occupancy information that is not sufficient to control the speed for both performance and temperature. We observe that the required decoding time depends on the complexity of scenes that can be measured with the number of frames in a group of pictures (GOP), and those frames in a GOP require similar computation time for decoding. Therefore, the previous GOP information can be used to predict the computation power of a current frame. We propose an efficient Dynamic Thermal Management (DTM) scheme for a multimedia system to find an appropriate frequency for the available decoding and display buffer based on an advanced feedback control. Our scheme exploits the previous GOP information considering the trade-offs between the quality of data and thermal safety using a frequency efficient factor.

#### B. Overview of a Feedback Control

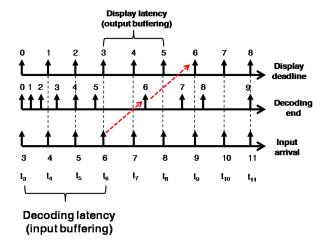

Fig. 1. MPEG process with display buffers

Fig. 1 shows the details of decoding procedures used in [20, 10]. After reading

a stream in 'Read headers' and 'Read Blocks' steps, a decoder thread decodes macro blocks at 'Reconstruct MD', 'IDCT', and 'Merge MB.' Finally, the decoder thread puts the decoded frame into a buffer for display. Then a display thread performs the steps of 'Dither' and 'Display' with the frames in the display buffer. The decoder thread executes CPU-intensive operations, while the display thread just displays the decoded frames. To obtain an adequate frequency for the decoding stream, a control thread checks the state of the display buffer. With the high occupancy in the display buffer, the control thread decreases the frequency, since the decoding elapsed time with the current frequency is too much faster than the display elapsed time. On the contrary, the low occupancy lets the control thread increase the frequency to meet the deadline of each frame. Therefore, the performance (i.e., the deadline of frames) should be considered in the low occupancy, while energy efficiency and thermal safety also should be considered in the high occupancy of the display buffer. To fulfill these two considerations, the control thread has to determine an optimal frequency without QoS degradation. Frames should be decoded sequentially and displayed on the display device with a constant playback interval denoted by  $t_{interval}$ . Although each frame can be decoded at a different elapsed time due to computation variations, each decoded frame in the display buffer are displayed at a uniform speed. To support the QoS requirement, the adjusted frequency should satisfy the following Equation (3.1)[10]:

$$\frac{\sum_{k=1}^{i} D_k}{i} \le t_{interval}, 1 \le i \le n, \tag{3.1}$$

where  $D_k$  is the decoding time for frame k, i means the number of frames in the display buffer, and n is the size of the display buffer. Note that for the consecutive frame, we do not have any information about the required decoding time. Without the display buffer, it is difficult to estimate the optimal frequency for decoding the frame. Also,

the display buffer with enough space for several frames can make a system determine the optimal frequency without frame misses. Lu et al. uses a feedback controller to adjust the frequency with the number of decoded frames in the display buffer within a region specified by  $\{B_l, B_h\}$ , where  $B_l$  is the lower threshold for the number of frames in the buffer and  $B_h$  is the higher threshold [10]. Using the feedback controller for decoding frames in the display buffer assumes that the decoder speed is adequate for decoding the frames as long as the number of the frames in the display buffer is within the specified region. However, there are two serious problems in the feedback controller with the display buffer. The first problem is that the feedback controller using the display buffer does not satisfy the deadline of all frames. The frequency is adjusted by the value based on the number of the frames in the display buffer within a region specified by  $\{B_l, B_h\}$ . This problem occurs with the movies containing several complicated scenes, such as Star Wars 3 and Terminator 3. For example, a high frequency may be required even though the occupancy of the display buffer seems to be sufficient to decode upcoming frames. In such cases, frames will be dropped if the the optimal frequency is only derived from the display buffer occupancy. Before decoding the next frame, we do not know how much time will be required for it. Without a buffer, we must use the most conservative estimate to set the decoding speed. But if there are some decoded frames already in the buffer between the decoder and the display device, we can apply a predictive operating frequency to be close to the optimum. Although the actual decoding time of the frames may vary greatly, its effect on the real-time constraint is hidden by the display buffer. In our approach, we always try to control the number of decoded frames in the buffer within a region specified by  $\{B_l, B_h\}$ , where  $B_l$  is the lower threshold for the number of frames in the buffer and  $B_h$  is the higher threshold. As long as the number of frames in the buffer is within the specified region, we assume that the current decoder speed is the right choice for decoding the frames; i.e. the average decode rate is equal to the display rate. However, if the actual number of frames in the buffer becomes higher or lower than the respective threshold, this means the current decoding speed is too fast or too slow, respectively. We apply a formal feedback controller to pull the number of frames back into the specified region by adjusting the decoding speed. The second problem is that the feedback controller using the display buffer cannot control the temperature to guarantee thermal safety. Without considering temperature constraints, the display buffer decides the optimal frequency using only its occupancy. This is a very critical problem in embedded systems, since most embedded systems do not have cooling systems such as a fan.

#### C. Advanced Feedback Controller Using GOP Information

The previous feedback control scheme uses the occupancy of display buffer between the decoder thread and the display thread to adjust the frequency of a processor to avoid the buffer underflow and overflow. However, although the occupancy of the display buffer is high, the frame may miss when the decoding time of the current frame is longer than the total display time the decoded frames in the display buffer. The relationship among the decoding time for each frame, the display interval and the occupancy of the display buffer is defined in Equation (3.2). Let  $D_i$  be a decoding time of  $frame_i$ . The decoding time  $D_i$  should be finished before all previous frames in the display buffer will be presented. Otherwise,  $frame_i$  will miss its deadline. Therefore,

$$D_i < n \cdot t_{interval},\tag{3.2}$$

where  $t_{interval}$  is the periodic display time in the display buffer and n is the occupancy of the display buffer.

Fig. 2. Low complexity vs. high complexity scenes

As shown in Fig. 2, the number of frames in a GOP decreases when pictures of scenes change rapidly. A single GOP has several frames which consists of I, B, and P frames. And for more complex scenes, the number of B and P frames decreases while only a single I frame is allowed for any GOP. Since the display interval time depends on frames per second (fps) and has a value between 25 msec and 30 msec, we calculate  $D_i$  of the frame that exceeds the display interval time,  $t_{interval}$ , in this situation. Therefore, the scene complexity can be estimated by adding these  $D_i$  values in a GOP.

For example, let's assume that frame  $f_n$  should be displayed at time  $t_n$  and  $f_{n+1}$  should be displayed at  $t_{n+1}$ . When frame  $f_n$  is ready to be displayed, there are four frames from  $f_{n-3}$  to  $f_n$  in the display buffer at time  $t_n$ . Also assume that a decoding time,  $D_{n+1}$  of  $f_{n+1}$  and  $D_{n+2}$  of  $f_{n+2}$  takes three times more than  $t_{interval}$ . Under these circumstances, all frames  $(f_{n-3} \sim f_{n+1})$  in the display buffer are displayed and the buffer will be empty since the next frame  $(f_{n+2})$  has not been decoded. In this case, the frame  $f_{n+2}$  is dropped. In order to avoid the future frames drop, the optimal frequency of  $f_{n+2}$  should be determined at time time  $t_n$ . However, it is difficult to

estimate the frequency for a future frame.

We propose a prediction scheme to find the adequate frequency using the information on decoding the previous GOP. According to our experiments, the frame decoding time depends on the complexity of scenes, which continues to exist in several consecutive frames. It means that frames in each GOP have similar complexity of scenes. Therefore, since the GOP consists of several frames, we can predict the optimal frequency of the current GOP using the information on the complexity of scenes in the previous GOP. If the complexity of the previous GOP is high, the complexity of the current GOP will be also high. Therefore, the complexity of the previous GOP can be used as a weight factor to determine the frequency of the current GOP. The weight factor  $(\alpha)$  is calculated as follows:

$$\alpha = \frac{\sum_{i=1}^{k} X_i D_i}{\sum_{i=1}^{k} D_i}, 1 \le i \le k,$$

(3.3)

where  $D_i$  is the decoding time of the  $frame_i$  and  $X_i$  is the indicator which is 1 or 0. With  $\alpha$ , the new frequency can be calculated as in Equation (3.4). Let  $freq_i$  be the frequency of the decoding time of the  $frame_i$ . The frequency of the current frame should be configured based on the number of previous frames which have taken less time than the threshold time for displaying that frame.

$$freq_i = (1 - \alpha) \cdot freq_{buf(i-1)} + \alpha \cdot freq_{max},$$

(3.4)

where  $freq_{buf(i-1)}$  is the frequency value to be calculated by the feedback control based on the occupancy of the display buffer.  $freq_{max}$  is the maximum frequency of the processor. Hence, the complexity of scenes can be estimated by the weighting factor,  $\alpha$ . For example, if the previous GOP has twelve frames and three frames among them have larger decoding time than the selected threshold value,  $\alpha$  is calculated as 0.25. It implies that 75% of decoding time of frames in the previous GOP is decoded within threshold and 25% decoding time of frames exceeds the threshold. According to Equation (3.4), the frequency of the current frame is adjusted to handle the frames with higher complexity based on the occupancy of the display buffer. Therefore, the frequency for decoding the current frame is selected by the information of the occupancy of the display buffer and the information of previous GOP. When the higher complexity of the previous GOP is, the higher frequency of the current frame is needed. Using this scheme, we can avoid the missed frames when the complexity of scenes is increased suddenly.

#### D. Thermal Control Using GOP Information

Although many studies has been focused on the relationship between frequency and power consumption, the relationship between frequency and temperature has to be formulated to find out the optimal frequency within thermal safety. Therefore, we consider a simple thermal model of the processor [28, 29] in that the relationship between processor's frequency and temperature is the basis for any frequency scaling scheme. By modeling the power dissipation or by increasing the input power, more precise models can be derived from this simple model [30].

We analyze Fourier's Law of heat conduction where the rate of heating or cooling is proportional to the difference in temperature between the object and the environment [30]. We define T(t) and P(t) as the temperature and the power at time t, respectively. Then we can use the Fourier's Law as the following [28, 29]:

$$T'(t) = P(t) - bT(t),$$

(3.5)

where b is a positive constant representing the power dissipation rate. Now, we define freq(t) as the processor frequency at time t. The power consumption of a processor is an increasing convex function of the frequency [28]. Most work assume that power and processor frequency are relevant as follows [28]:

$$P(t) = a(freq^{\gamma}(t)) \tag{3.6}$$

for some constants a and  $\gamma > 1$ . With an assumption that  $T_0 = 0$  (The initial temperature is the ambient one), through Equation (3.5), the solution to Equation (3.6) can be presented as [30]:

$$T(t) = \int_{t_0}^t a(freq^{\gamma}(\tau)e^{-b(t-\tau)})d\tau + T_0e^{-b(t-t_0)}.$$

(3.7)

Then, for the variation of the temperature, we deal with two cases of the variation at any point t [30]. The first case, when temperature is non-decreasing, by Equation (3.5) and Equation (3.6), can be derived like the following.

$$freq(t) \ge \left(\frac{b(T(t))}{a}\right)^{\frac{1}{\gamma}}.$$

(3.8)

The other case, when temperature is non-increasing, can be expressed as follows:

$$freq(t) \le \left(\frac{b(T(t))}{a}\right)^{\frac{1}{\gamma}}.$$

(3.9)

Therefore, we observe that scaling the frequency to change the temperature can be performed for the desired direction. Finally, we derive the following equation if we maintain the frequency constant at freq(t) = freqC during time interval  $[t_0, t]$ .

$$T(t) = \frac{a(freq_c^{\gamma})}{b} + (T(t_0) - \frac{a(freq_c^{\gamma})}{b})e^{-b(t-t_0)}.$$

(3.10)

$$dT/dt = -b(T(t) - \frac{a(freq_c^{\gamma})}{b})$$

(3.11)

In addition, the temperature variation by the frequency is based on the equations above (The initial temperature is 0. During [0,t], workload is executed at some frequency level and there is no workload to be executed in the interval [t,t']). Assuming  $\gamma=3.0$ , we can obtain the thermal parameter values for a and b. The values of a and b, are processor-specific but application-independent constants. Also, we can determine the thermal parameters, while observing the heating and cooling curves when we run an application which fully occupies the processor. After a long-time execution of the application, the infinite steady-state temperature value  $T(\infty)=T_s$  can be observed. Setting T(t)=T and  $a(freq_c^{\gamma})/b=T_s$ , Equation (3.5) and (3.6) is transformed as follows:

$$T = T_s + (T_{init} - T_s)e^{-bt}, (3.12)$$

where  $T_{init}$  is the initial temperature. Using  $T_s$  and sampling the temperature every millisecond, the rate of increase is plotted against  $(T - T_s)$  at each point. The resulting set of points is fitted to a straight line using least mean square error fitting. From Equation (3.12), the slope of this straight line represents the value of b. We obtain b = 0.016. By applying this value b to the relation, the value a is also obtained as a = 3.0E - 28. We used the thermal model above for the simulation. With the plotted temperature variations, we see the effects and decrease in temperature by the suggested DTM for MPEG-4 decoding. All the plots are based on real experimental data including the decoding times of each frame. There can be overestimation of temperature computation, because there can be many short processor idle durations even in the interval between the start and the finish of the decoding. We assume that there is no processor idle duration in the decoding period for a frame. However, even with this assumption, the relative temperature comparisons among four cases shows that the GOP-based DTM can decrease the processor temperature overall. Although

the temperature variation by the 1.0 GHz static frequency decoding is shown for the comparison, it is no good in terms of frame miss rate. We show the comparison of the frame miss rate by each method in later section.

#### E. DTM with the Advanced Feedback Controller

To maintain the temperature under the thermal safety, we should use a DTM scheme for the multimedia decoder. The new DTM scheme uses the accurate frequency from the previous GOP frequency. In our scheme, we decide the threshold of temperature to control the overall temperature during a decoder running. In order to decide the temperature threshold, we need the occupancy of the display buffer which can indicate the efficiency of the frequency for decoding the previous GOP.

$$e = \frac{\sum_{i=1}^{n} D_i}{n \cdot t_{\text{interval}}}, 0 < e \le 1, \tag{3.13}$$

where  $T_{emergency}$  is the maximum allowable temperature and is defined as 80 °C in our experiments. And  $T_{threshold}$  is the software threshold of temperature during decoding MPEG-4 stream. Therefore,  $\Delta T$  can be defined as the difference between an emergency temperature and software temperature threshold. The software temperature threshold is the factor that guarantees thermal safety. n is the total number of frames in the display buffer and  $t_{interval}$  is the period of displaying the frames. The e is the frequency efficient factor for decoding frames in the previous GOP only when  $D_i$  is equal to or less than  $t_{interval}$ . With the factor e, we decide the new software threshold of temperature as shown in Algorithm (1). If  $T_{current}$  exceeds  $T_{threshold}$ ,  $T'_{threshold}$  replaces  $T_{threshold}$ , and  $freq_{max}$  is also replaced by  $freq[T'_{threshold}]$ . Therefore,  $freq_i$  is determined to maintain the temperature under the thermal safety with Equation (3.4) because the determined  $freq_{max}$  is smaller than the previous  $freq_{max}$ .

## Algorithm 1 DTM algorithm

**Require:** Define Table[] for frequency according to threshold temperature

- 1: Determine a threshold temperature  $(T_{threshold})$ .

- 2:  $i \leftarrow GOP_i$

- 3: for i = 1 to  $GOP_{max}$  do

- 4: Calculate e in  $GOP_{i-1}$

- 5: Estimate a current temperature  $(T_{current})$ .

- 6: if  $T_{current} > T_{threshold}$  then

- 7:  $\Delta T \leftarrow T_{emergency} T_{threshold}$

- 8:  $T'_{threshold} \leftarrow T_{threshold} + (1-e) \cdot \Delta T$

- 9:  $index \leftarrow index + 1$

- 10:  $freq_{max} \leftarrow Table[index]$

- 11:  $freq_i \leftarrow (1-\alpha) \cdot freq_{i-1} + \alpha \cdot freq_{max}$

- 12: else if  $T_{current} < (T_{threshold} MIN)$  then

- 13:  $index \leftarrow index 1$

- 14:  $freq_{max} \leftarrow Table[index]$

- 15:  $freq_i \leftarrow (1-\alpha) \cdot freq_{i-1} + \alpha \cdot freq_{max}$

- 16: **end if**

- 17: end for

Fig. 3. Comparison with DTM and without DTM for frequency

For example, assuming  $T_{emergency}$  to be 80 °C and  $T_{threshold}$  to be 60 °C ,  $\Delta T$  is calculated as 20 °C . If e is 0.75 and the current temperature is over the current software temperature threshold, the new software temperature threshold can be adjusted to 64 °C . As a result,  $freq_{max}$  is decreased to the next low frequency by  $T_{threshold}$ . In this example,  $freq_{max}$  is adjusted from 1600 Mhz to 1400 Mhz when  $T_{threshold}$ is changed. This new software temperature threshold makes  $freq_{max}$  decrease the overall temperature. With this scheme, the adjusting temperature threshold can guarantee to maintain the overall system temperature. Also, the processor frequency can be efficiently adjusted at runtime, while taking into account the current thermal condition and the previous frequency. Fig. 3 shows the difference of  $freq_{max}$  of the case with DTM or without DTM. The DTM scheme can determine the lower frequency than other DVFS schemes without managing temperature because  $freq_{max}$  is changed through the temperature threshold. Fig. 4 shows the effect on the temperature in comparison with DTM and without DTM. The proposed scheme prevents the system temperature from reaching a dangerous level by controlling  $freq_{max}$  and maintaining the temperature within the steady state.

Fig. 4. Temperature comparison with and without DTM

## F. Experimental Results and Analysis

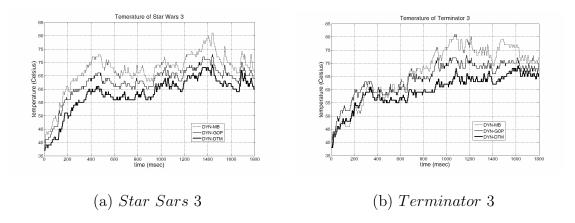

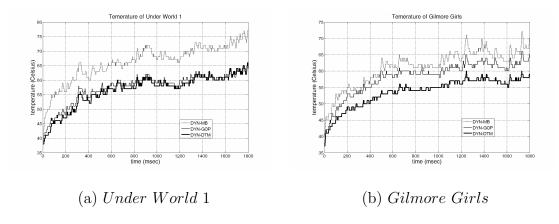

To demonstrate the benefits of our control algorithm, we compare three schemes in terms of the number of missing frame, frames per second (fps) and the variance of temperature. DYN-MB scheme stands for the feedback controller with the display buffer, DYN-GOP scheme is the feedback controller with the display buffer and the information of GOP. Finally, DYN-DTM is the feedback controller based on the previous GOP information with DTM. Although DYN-GOP and DYN-DTM use the information of the previous GOP, only DYN-DTM supports the dynamic thermal management. Fig. 5(a) and 5(b) describes the temperature variance in two movies, Star Wars 3 and Terminator 3, which have the higher-complexity data than any other movies. It is observed that the DYN-DTM scheme controls the temperature more precisely than the other two schemes. This is a reason why the thermal control in DYN-DTM uses the efficiency of frequency and temperature threshold. Another noticeable result is that DYN-DTM maintains the peak temperature to be at least 12% lower than other benchmark schemes. As shown in Fig. 5(a), there are the high-complexity scenes in the first part and the last part of this movie, while the middle part has relatively

lower complexity. Therefore, the DYN-DTM performs efficiently in the first and the last parts while maintaining the software temperature threshold at 70 °C. Fig. 5(b) also shows that DYN-DTM outperforms other two schemes even in multiple high-complexity scenes that are located at the middle of the movie. As a result, the proposed DYN-DTM scheme reduces the overall temperature up to 13% by using information from the previously decoded GOP and with dynamic thermal management. The most noticeable merit from this scheme is that it prevents all frames from exceeding the threshold temperature without dropping any frame at all.

#### G. Conclusions

In this work, we proposed a method to find a proper frequency using an advanced feedback controller for the available decoding and display buffer based on the information of the previous GOP. Also, our scheme efficiently adjusts the frequency using a frequency efficient factor, while keeping all frames from being dropped and maintaining thermal safety. We have implemented the proposed scheme on Linux and conducted benchmark testings. Experimental results prove that the proposed method does not drop any frames while the temperature is kept under the threshold. In other words, the proposed scheme suggests a solution for thermal constraints without any quality degradation for MPEG-4 decoding.

Fig. 5. Variance of temperature of high-complexity movies

Fig. 6. Variance of temperature of mid- and low-complexity movies

## CHAPTER IV

# THERMAL-AWARE SCHEDULING BASED ON STATISTICAL CHARACTERISTICS OF MULTIMEDIA APPLICATIONS

Dynamic Voltage and Frequency Scaling (DVFS) is a common method to control temperature in microprocessors. However, due to the nature of multimedia applications with different frame sizes and types in data, it is not easy to match their QoS requirements while temperature is under control. There have been handful studies on temperature management for multimedia applications [7, 8, 9, 10, 4, 11]. However, according to our observations, these schemes tend to overestimate or underestimate multimedia application requirements, which could result in false, inevitably leading to high operation temperature or performance degradation. In order to compensate the tradeoff between QoS and thermal control, in this work, we first derive application characteristics in various multimedia applications by transmitting MPEG-4 and H.264/AVC encoded by two different frame resolutions. The application characteristics can be represented by cycle demand, which is the number of cycles required to decode a frame. Using this representation, we estimate an adequate processor speed to execute multimedia application for decoding frames at runtime. Then, we propose Thermal-Aware Scheduler (TAS) that takes optimal frequencies to avoid thermal emergency while minimizing performance degradation in the embedded environments. To achieve this goal, TAS integrates DVFS feature into the traditional soft real-time scheduler.

Also, TAS can be classified into hybrid schemes to be integrated proactive and reactive approaches together. In the viewpoint of proactive approaches, TAS estimates temperature parameters to get accurate information for temperature according to applications' workload before running multimedia applications. Since those temperature parameters are related to processor and work as architecture specific factors, future temperature can be predicted more accurately using those temperature parameters. In the viewpoint of reactive approaches, TAS utilizes cycle demand distribution as application characteristics for multimedia applications, and those historical information helps the optimal frequency be decided for decoding next frames. As a result, TAS provides better solution to find the adequate frequency based on cycle demand distribution and predict the future temperature using profiled thermal parameters according to workload rather than using only one scheme between reactive and proactive schemes.

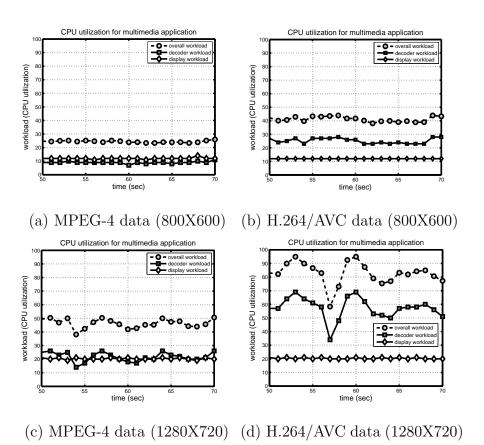

We experimented on an Intel's Pentium-M processor and Atom processor using various multimedia data encoded by MPEG-4 and H.264/AVC. Compared to feedback control DTM [10], Frame-based DTM [12] and cycle counter-based scheduler [31], TAS lowers average temperature by 6 °C and peak temperature by 10 °C or more, with maximum 5% frame drop ratio. Moreover, we also compare the predicted temperature by application thermal behavior to the estimated temperature by thermal sensors in Linux while playing movies.

The main contributions of this research are summarized as follows:

- We estimate multimedia applications' thermal characteristics using statistical approaches to be suitable for various multimedia codecs with only 2.5% error on average.

- TAS provides soft realtime performance guarantees with statistical processor allocations. Almost all deadlines of decoding and displaying frames in a lightly loaded real environments, and bounds the deadline miss ratio under the application-specific performance requirement (e.g., meeting 95% of deadlines) in a heavily loaded environment.

- Compared to the previous DTMs such as feedback control [10], Frame-based [12], and cycle counter scheduler [31], our proposed TAS lowers temperature by 10