# FILTER DESIGN CONSIDERATIONS FOR HIGH PERFORMANCE CONTINUOUS-TIME LOW-PASS SIGMA-DELTA ADC

A Thesis

by

VENKATA VEERA SATYA SAIR GADDE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2009

Major Subject: Electrical Engineering

# FILTER DESIGN CONSIDERATIONS FOR HIGH PERFORMANCE CONTINUOUS-TIME LOW-PASS SIGMA-DELTA ADC

## A Thesis

by

## VENKATA VEERA SATYA SAIR GADDE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

## Approved by:

Chair of Committee, Jose Silva-Martinez

Committee Members, Shankar P. Bhattacharyya

Aydin I. Karsilayan

Jay Porter

Head of Department, Costas N. Georghiades

December 2009

Major Subject: Electrical Engineering

#### ABSTRACT

Filter Design Considerations for High Performance Continuous-time Low-pass Sigmadelta ADC. (December 2009)

Venkata Veera Satya Sair Gadde, B. E., Birla Institute of Technology & Science, Pilani Chair of Advisory Committee: Dr. Jose Silva-Martinez

Continuous-time filters are critical components in the implementation of large bandwidth, high frequency, and high resolution continuous-time (CT) sigma-delta ( $\Sigma\Delta$ ) analog-to-digital converters (ADCs). The loop filter defines the noise-transfer function (NTF) and hence the quantization noise-shaping behavior of the  $\Sigma\Delta$  modulator, and becomes the most critical performance determining part in  $\Sigma\Delta$  ADC.

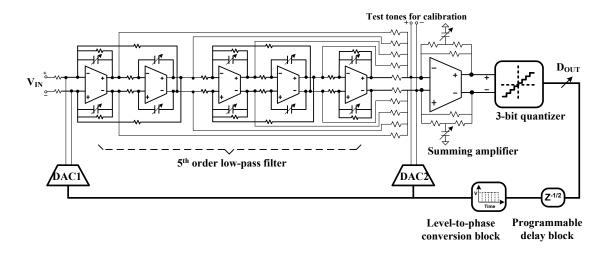

This thesis presents the design considerations for the loop filter in low-pass CT  $\Sigma\Delta$  ADC with 12-bits resolution in 25MHz bandwidth and low power consumption using 0.18µm CMOS technology. Continuous-time filters are more suitable than discrete-time filters due to relaxed amplifier bandwidth requirements for high frequency  $\Sigma\Delta$  ADCs. A fifth-order low-pass filter with cut-off frequency of 25 MHz was designed to meet the dynamic range requirement of the ADC. An active RC topology was chosen for the implementation of the loop filter, which can provide high dynamic range required by the  $\Sigma\Delta$  ADC. The design of a summing amplifier and a novel method for adjusting the group delay in the fast path provided by a secondary feedback DAC of the  $\Sigma\Delta$  ADC are presented in detail. The ADC was fabricated using Jazz 0.18µm CMOS technology.

The implementation issues of OTAs with high-linearity and low-noise performance suitable for the broadband ADC applications are also analyzed in this work. Important design equations pertaining to the linearity and noise performance of the Gm-C biquad filters are presented. A  $G_m$ -C biquad with 100MHz center frequency and quality factor 10 was designed as a prototype to confirm with the theoretical design equations. Transistor level circuit implementation of all the analog modules was completed in a standard  $0.18\mu m$  CMOS process.

To god

#### **ACKNOWLEDGEMENTS**

I would like to express my most sincere thanks to my advisor, Dr. Jose Silva-Martinez, who has been a great source of inspiration and support throughout my graduate studies. When I first approached him to start my research, he accepted me as his student in spite of my limited knowledge in analog and mixed signal design. The endless doubts from my side never seemed to bother him, and he patiently answered all my questions. The long discussions with him have helped me to understand different aspects of analog design, and I am greatly indebted to him for his guidance, encouragement and support during my graduate studies.

I would like to thank my committee members, Dr. Aydin I. Karsilayan, Dr. Shankar P. Bhattacharyya, and Dr. Jay Porter, for agreeing to serve on my committee and kindly sharing their academic experience. The courses I took in our AMSC group helped me to learn various aspects of IC design. Our secretaries, Ella Gallagher, Tammy Carda, and Jeanie Marshall, have always been a tremendous help in all aspects of administrative issues.

I would like to thank my colleagues in the AMSC group for the great discussions and help throughout my stay. Special mention goes to my project partners, Cho-Ying Lu, Marvin Onabajo, Fabian Silva-Rivas and Vijay who helped me during various phases of design and testing of the ADC. I want to express my deep gratitude to my friends, officemates, and other project partners in the AMSC group. I will never forget their constant support, sincere friendship and company during the long hours of work at school. Looking back on my career, I realize that I'm deeply indebted to all my teachers who have helped me to grow in both technical and personal aspects.

I'm always grateful for the love, encouragement and support from my family. One person who has made the greatest impact in my life is my uncle – Mr. Bhanuprasad. I would like to thank my parents, my sister and my uncle for their constant love, encouragement and their belief in me, which has been a great source of inspiration throughout my graduate studies.

# **TABLE OF CONTENTS**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iii                  |

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iv                   |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                | v                    |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |

| LIST OF TABLES.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |

| 1.1. Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1<br>4<br>5          |

| 2. PROPERTIES OF THE SIGMA-DELTA MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                      | 9                    |

| 2.1. Analog-to-digital conversion  2.2. Ideal sigma-delta modulator  2.3. Continuous-time and discrete-time sigma-delta modulators  2.4. Non-idealities in continuous-time sigma-delta modulators  2.4.1. Circuit noise  2.4.2. Non-linearity  2.4.3. Component mismatches  2.4.4. Excess loop delay  2.4.5. Clock jitter  2.5. Performance parameters of sigma-delta modulators  2.5.1. Signal-to-noise-and-distortion ratio (SNDR)  2.5.2. Dynamic range (DR) |                      |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22<br>23<br>25<br>27 |

| 4 DESIGN OF G <sub>m</sub> -C BIOUADRATIC FILTER                                                                                                                                                                                                                                                                                                                                                                                                                | 31                   |

|              |                                                                       | Page |

|--------------|-----------------------------------------------------------------------|------|

| 4            | -1. G <sub>m</sub> -C integrator                                      | 31   |

|              | .2. OTA architecture                                                  |      |

|              | 4.2.1. Noise analysis of G <sub>m</sub> -C-OTA integrator             | 35   |

|              | 4.2.2. Linearity analysis of G <sub>m</sub> -C-OTA                    |      |

|              | 4.2.3. OTA simulation results                                         |      |

| 4            | .3. The G <sub>m</sub> -C biquadratic cell                            | 41   |

|              | 4.3.1. Linearity analysis of the G <sub>m</sub> -C biquad             |      |

|              | 4.3.2. Noise analysis of the G <sub>m</sub> -C biquad                 |      |

| 4            | .4. Biquad simulation results                                         |      |

| 5. D         | DESIGN OF A 5 <sup>TH</sup> ORDER ACTIVE-RC LOW-PASS FILTER           | 56   |

| 5            | .1. Introduction                                                      | 56   |

|              | 5.1.1. Architectural considerations                                   |      |

|              | 5.1.2. Design considerations                                          |      |

| 5            | .2. Design of amplifier                                               |      |

|              | 5.2.1. Amplifier architecture                                         |      |

|              | 5.2.2. Amplifier circuit implementation                               |      |

|              | 5.2.3. Simulation results of the amplifier                            |      |

| 5            | 3. Second order filter realization.                                   |      |

|              | 5.3.1. Design considerations.                                         |      |

| 5            | .4. First-order integrator stage                                      |      |

|              | 5.5. Summing amplifier                                                |      |

|              | 5.5.1. Stability considerations                                       |      |

|              | 5.5.2. Summing amplifier design requirements                          |      |

|              | 5.5.3. Optimizing for group delay                                     |      |

|              | 5.5.4. Circuit implementation of summing amplifier                    |      |

|              | 5.5.5. Summing amplifier simulation results                           |      |

| 6. R         | RESULTS                                                               |      |

|              | 5.1. Preliminary experimental results of CT LP ΣΔ ADC                 |      |

| 6            | 5.2. Simulation results for the 5 <sup>th</sup> order low-pass filter | 92   |

| Ü            | 6.2.1. Simulation results for first stage of filter                   |      |

|              | 6.2.2. Simulation results for second stage of filter                  |      |

|              | 6.2.3. Simulation results for third stage of filter                   |      |

| 7. S         | SUMMARY AND CONCLUSIONS                                               |      |

|              | ERENCES                                                               |      |

| VIT /        |                                                                       | 109  |

| <b>1/II/</b> |                                                                       | 1110 |

# LIST OF FIGURES

|           |                                                                       | Page |

|-----------|-----------------------------------------------------------------------|------|

| Figure 1  | Different wireless applications and standards                         | 1    |

| Figure 2  | Generic block diagram of a wireless receiver                          | 2    |

| Figure 3  | Examples of discrete-time and continuous-time integrators             | 4    |

| Figure 4  | Classification of different ADC architectures based on resolution and |      |

|           | speed                                                                 | 7    |

| Figure 5  | Basic A/D conversion architectures                                    | 10   |

| Figure 6  | Power spectral density of quantization noise for ADC architectures    | 11   |

| Figure 7  | Block diagram of ideal sigma-delta modulator                          | 11   |

| Figure 8  | Typical STF and NTF for a lowpass $\Sigma\Delta$ modulator            | 13   |

| Figure 9  | The discrete-time and continuous-time sigma-delta modulators          | 14   |

| Figure 10 | Model of sigma-delta modulator with important noise sources           | 16   |

| Figure 11 | SNR degradation due to excess loop delay in CT ΣΔ ADC                 | 19   |

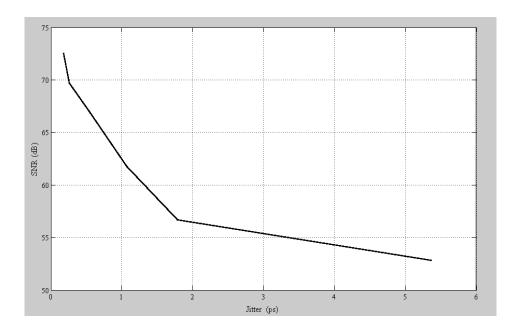

| Figure 12 | SNR degradation due to the effect of jitter in CT $\Sigma\Delta$ ADC  | 20   |

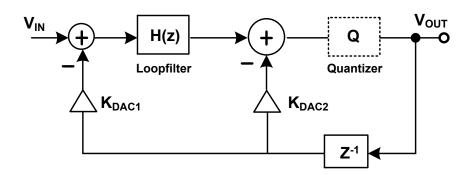

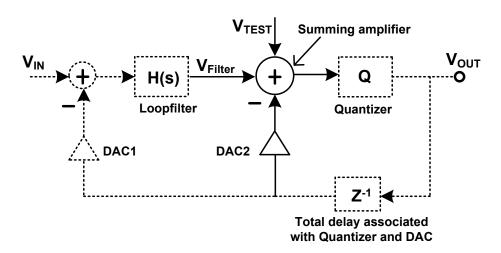

| Figure 13 | Simplified model of the continuous time sigma-delta modulator         | 24   |

| Figure 14 | Bode plot showing H(z) and Loop gain, G(z)                            | 25   |

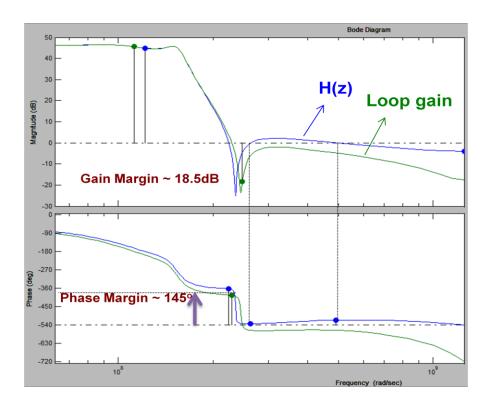

| Figure 15 | System level block diagram of CT LP ΣΔ ADC                            | 28   |

| Figure 16 | The NTF and the output spectrum of the CT LP SD ADC                   | 30   |

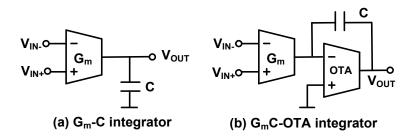

| Figure 17 | Popular Gm-C integrator architectures                                 | 31   |

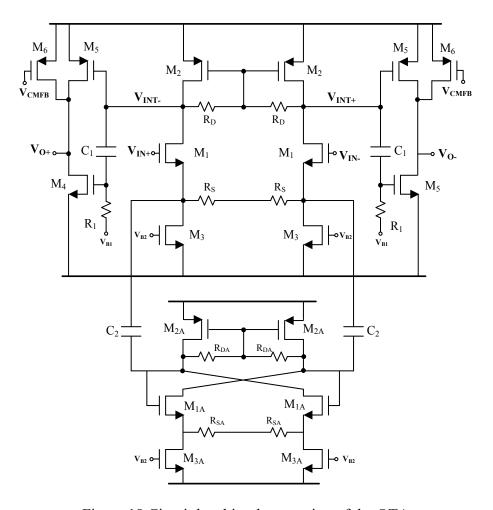

| Figure 18 | Circuit level implementation of the OTA                               | 34   |

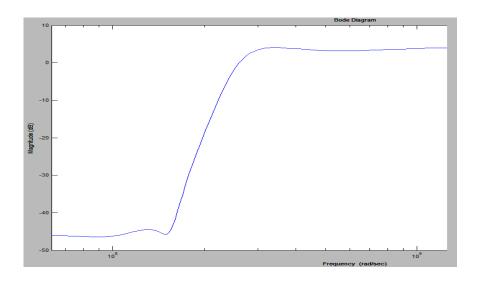

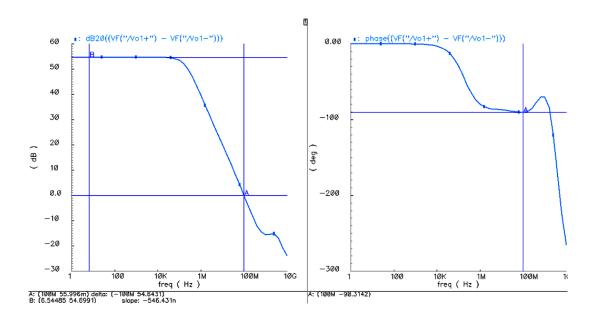

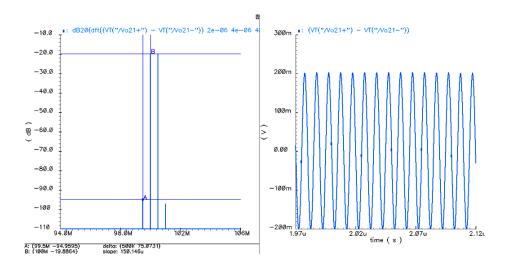

| Figure 19 | AC response showing DC gain and excess phase of the OTA               | 39   |

| Figure 20 | IM3 measurement for the stand alone OTA                               | 40   |

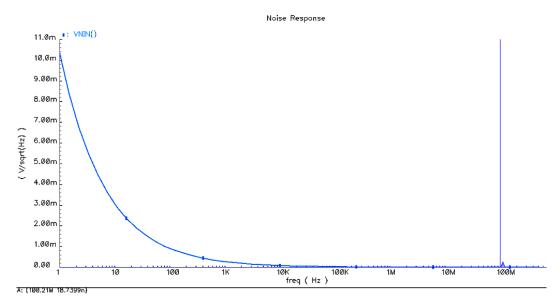

| Figure 21 | Input referred noise spectral density of the OTA                      | 40   |

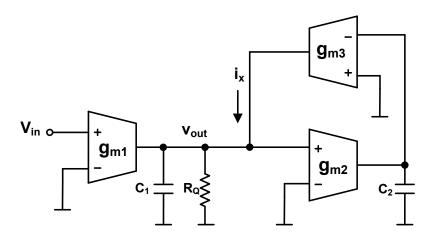

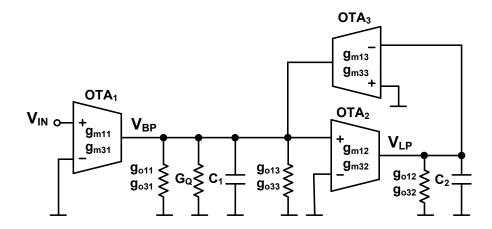

| Figure 22 | Schematic of the Biquadratic OTA-C filter                             | 41   |

| Figure 23 | Schematic of the Biquadratic OTA-C filter with non-linear elements    | 42   |

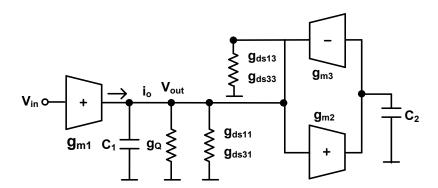

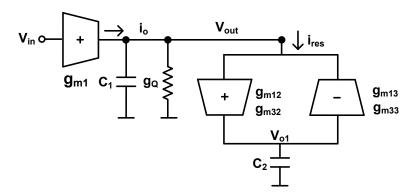

| Figure 24 | G <sub>m</sub> -C filter with ideal resonator.                        | 44   |

| Figure 25 | Gm-C biquad with non-linear output impedance of OTA                   | 44   |

|           |                                                                                    | Page |

|-----------|------------------------------------------------------------------------------------|------|

| Figure 26 | Gm-C biquad with non-idealities in resonator                                       | 45   |

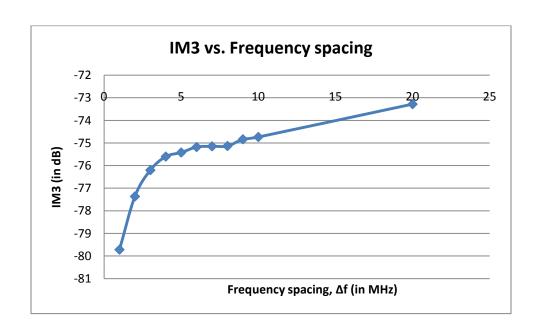

| Figure 27 | Dependence of IM3 on frequency of operation of G <sub>m</sub> -C biquad            | 48   |

| Figure 28 | Simulation results showing IM3 vs. Frequency spacing for G <sub>m</sub> -C         |      |

|           | biquad                                                                             | 49   |

| Figure 29 | Schematic of the Biquadratic OTA-C filter with noise sources                       | 50   |

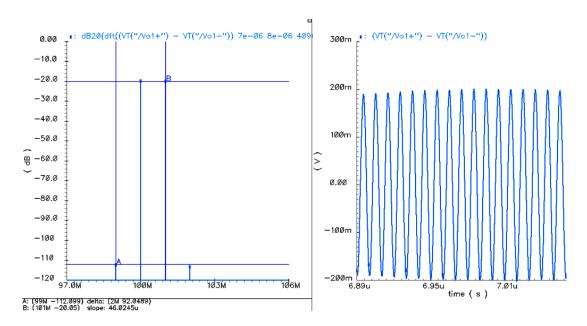

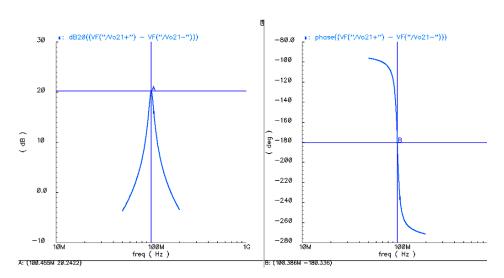

| Figure 30 | Magnitude and phase response of the G <sub>m</sub> -C band-pass biquad             | 53   |

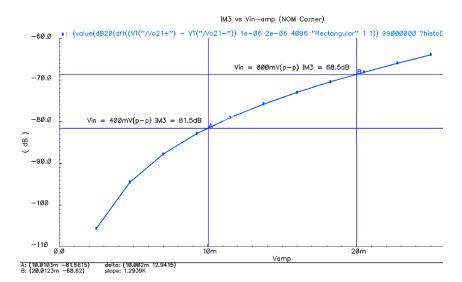

| Figure 31 | IM3 measurement for the G <sub>m</sub> -C biquadratic filter                       | 54   |

| Figure 32 | IM3 vs. input amplitude plot for the G <sub>m</sub> -C band pass filter, Peak gair | 1 =  |

|           | 20dB                                                                               | 54   |

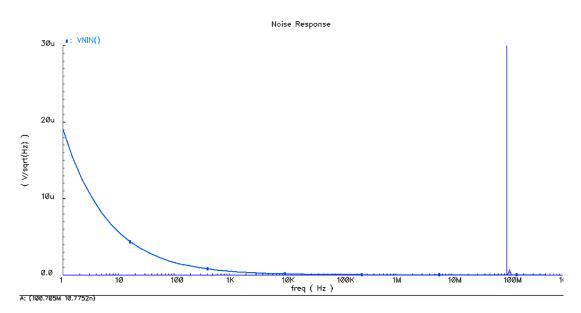

| Figure 33 | Input referred noise spectral density of the G <sub>m</sub> -C biquad              | 55   |

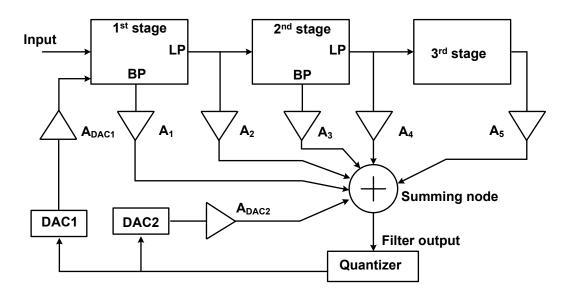

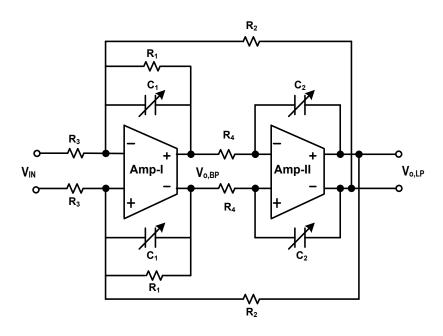

| Figure 34 | Feed-forward architecture of the 5 <sup>th</sup> order loop filter                 | 57   |

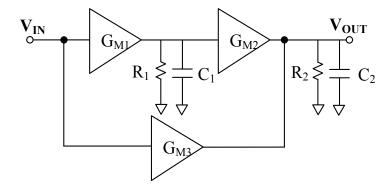

| Figure 35 | Block diagram of the amplifier with feed-forward compensation                      |      |

|           | technique                                                                          | 61   |

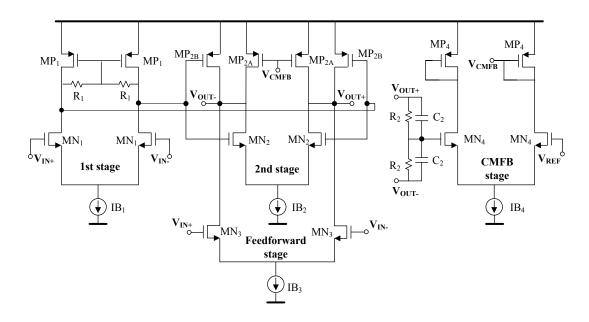

| Figure 36 | Schematic of the amplifier used in the loop filter                                 | 62   |

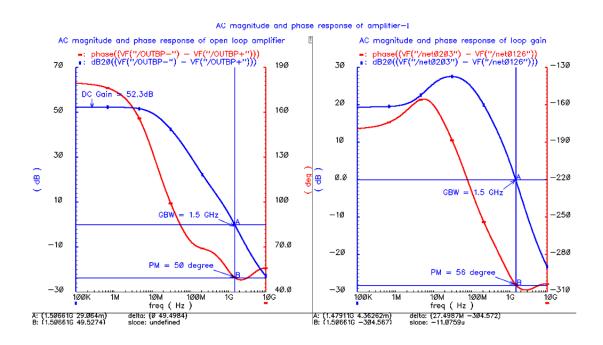

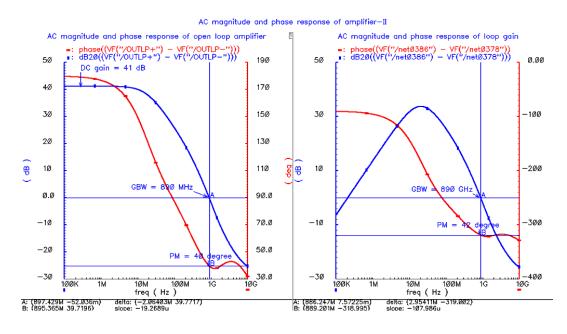

| Figure 37 | Simulated AC responses for amplifier I                                             | 65   |

| Figure 38 | Simulated AC responses for amplifier II                                            | 66   |

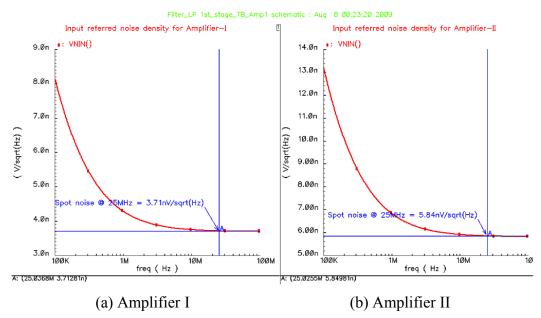

| Figure 39 | Input referred noise density of amplifier used in loop filter                      | 66   |

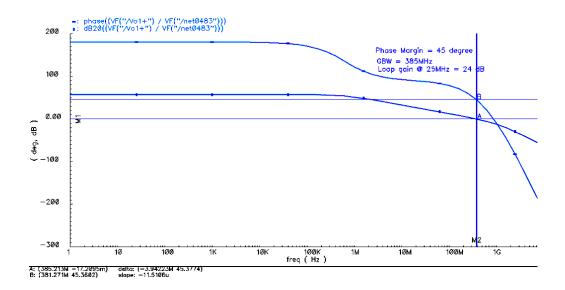

| Figure 40 | Common-mode loop AC magnitude and phase response                                   | 67   |

| Figure 41 | Step response of CMFB loop                                                         | 67   |

| Figure 42 | Two-integrator loop configurations                                                 | 68   |

| Figure 43 | Two-integrator loop biquad                                                         | 69   |

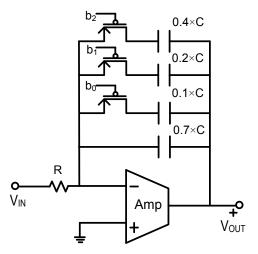

| Figure 44 | Capacitor tuning mechanism for a single-ended integrator stage                     | 71   |

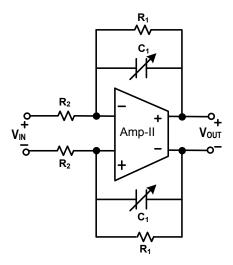

| Figure 45 | Third stage of the loop filter                                                     | 74   |

| Figure 46 | Block diagram showing the summing node in the $\Sigma\Delta$ modulator             | 76   |

| Figure 47 | Simplified representation of the summing amplifier stage                           | 77   |

| Figure 48 | The direct path formed by summing stage around the quantizer                       | 80   |

| Figure 49 | Block diagram of the summing amplifier stage                                       | 83   |

|           |                                                                                | Page |

|-----------|--------------------------------------------------------------------------------|------|

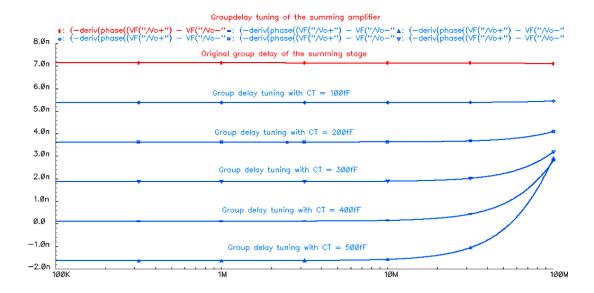

| Figure 50 | Tuning of group delay using C <sub>T</sub> in direct (fast) path               | 87   |

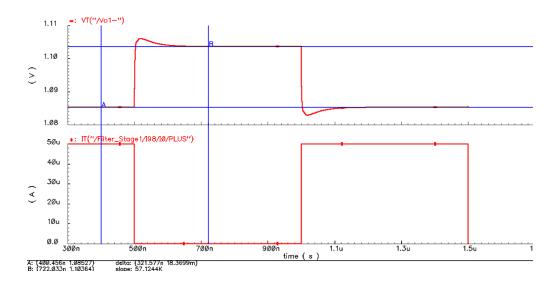

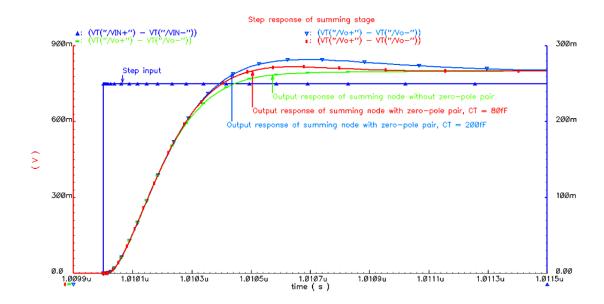

| Figure 51 | Step response of the amplifier stage                                           | 87   |

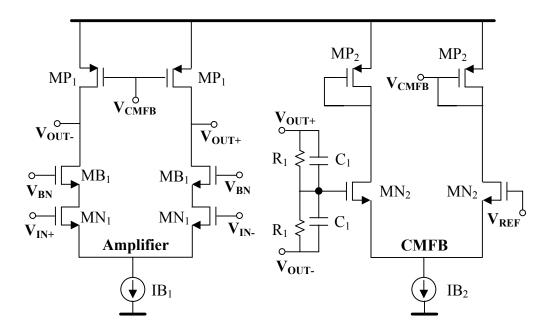

| Figure 52 | Schematic of the amplifier in loop filter                                      | 88   |

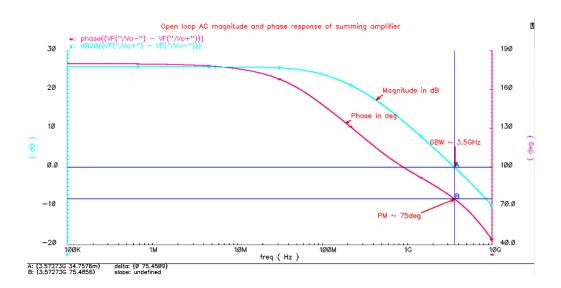

| Figure 53 | Open-loop AC response of the summing amplifier                                 | 90   |

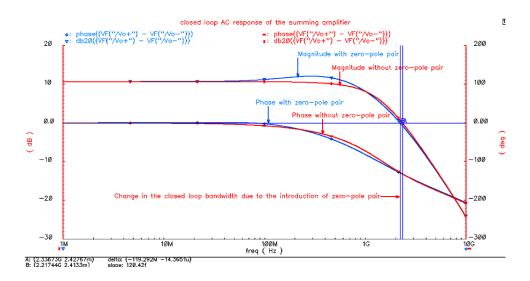

| Figure 54 | Closed-loop AC magnitude and phase response of the summing stage               | 90   |

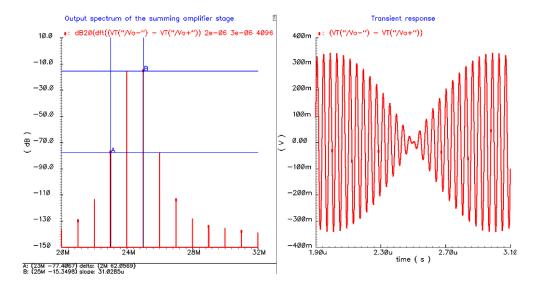

| Figure 55 | Linearity test of the summing amplifier, $V_{out} = 600 \text{mV}_{p-p}$ .     | 91   |

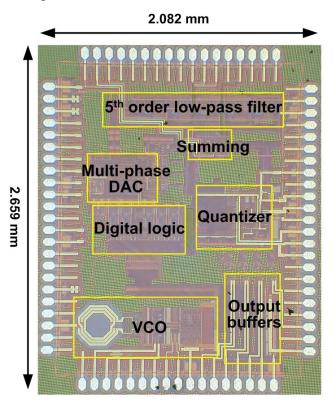

| Figure 56 | Chip micrograph of the CT LP SD ADC in 0.18µm CMOS technology                  | 92   |

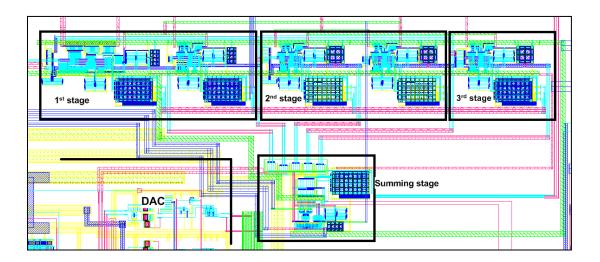

| Figure 57 | Layout of the fifth order low-pass filter                                      | 93   |

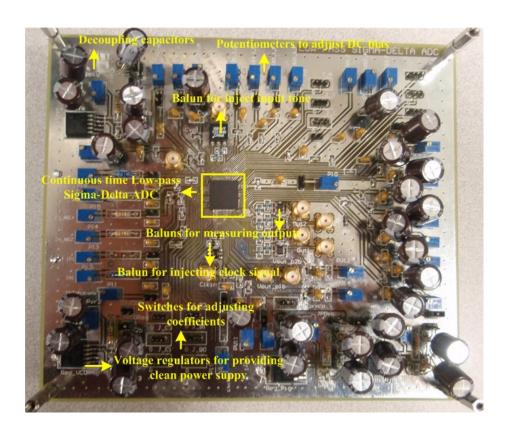

| Figure 58 | PCB test set-up for measuring the performance of CT LP SD ADC                  | 94   |

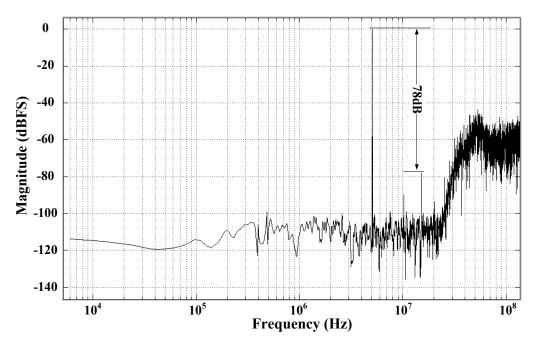

| Figure 59 | Output spectrum of CT LP SD ADC from experimental results                      | 94   |

| Figure 60 | AC magnitude and phase responses of open loop filter [H(s)]                    | 95   |

| Figure 61 | AC magnitude and phase responses of open loop filter transfer function         | ı    |

|           | [H(s)] and the effect of secondary DAC feedback [0.5+H(s)]                     | 96   |

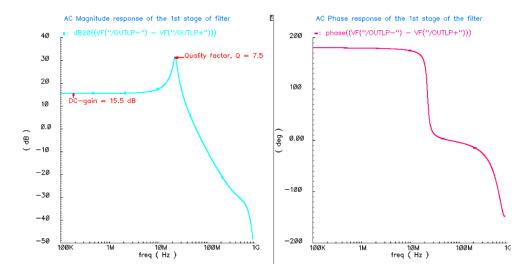

| Figure 62 | AC Magnitude and Phase response of the 1 <sup>st</sup> stage of the filter     | 97   |

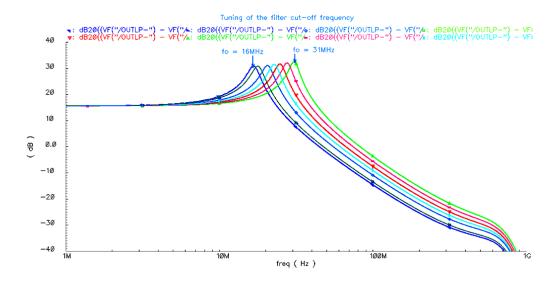

| Figure 63 | Tuning of cut-off frequency of first stage between 16MHz and                   |      |

|           | 31MHz                                                                          | 97   |

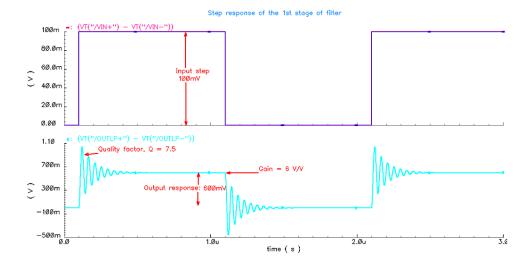

| Figure 64 | Step response of the first stage of the filter                                 | 98   |

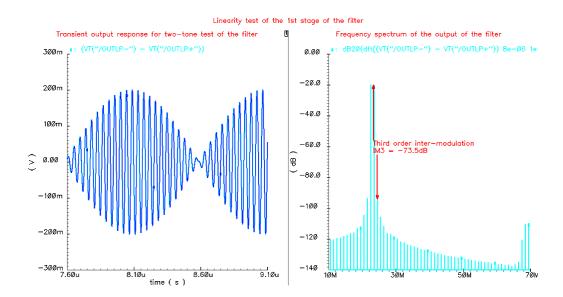

| Figure 65 | Linearity test of the first stage of the filter, $Vout = 400 \text{mV}_{p-p}$  | 98   |

| Figure 66 | Input-referred integrated noise of the first stage of the filter in 25MHz      |      |

|           | bandwidth                                                                      | 99   |

| Figure 67 | Input referred noise density of the first stage of the filter                  | 99   |

| Figure 68 | AC Magnitude and Phase response of the 2 <sup>nd</sup> stage of the filter     | 100  |

| Figure 69 | Tuning of cut-off frequency of second stage between 11.5MHz and                |      |

|           | 19.5MHz                                                                        | 100  |

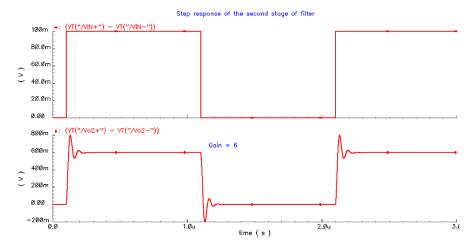

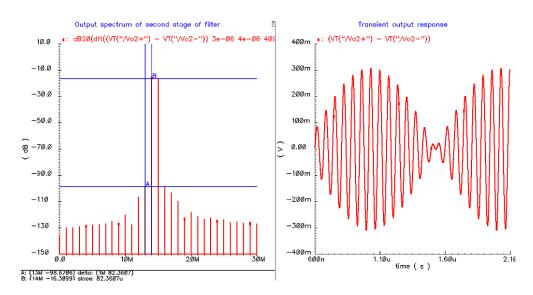

| Figure 70 | Step response of the second stage of the filter                                | 101  |

| Figure 71 | Linearity test of the second stage of the filter, Vout = $600 \text{mV}_{p-p}$ | 101  |

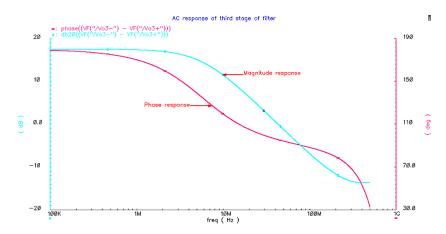

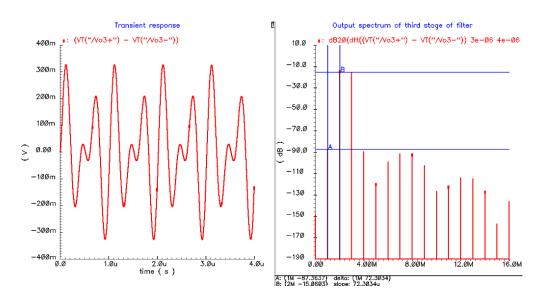

| Figure 72 | AC response of the third stage of the filter                                   | 102  |

|           |                                                                                      | Page |

|-----------|--------------------------------------------------------------------------------------|------|

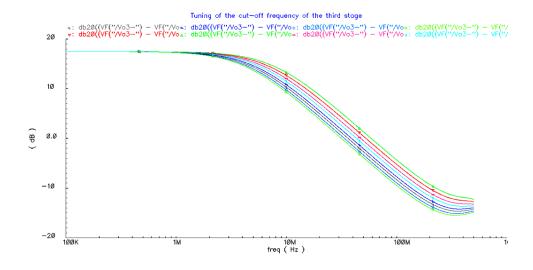

| Figure 73 | Tuning of cut-off frequency of third stage filter between 4.2MHz and                 |      |

|           | 7.8MHz                                                                               | 102  |

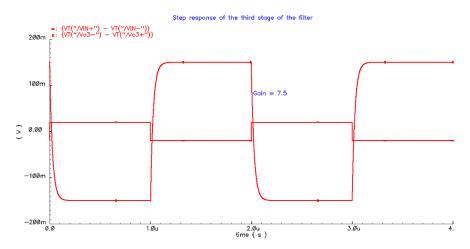

| Figure 74 | Step response of the third stage of the filter                                       | 103  |

| Figure 75 | Linearity test of the third stage of the filter, Vout = $600 \text{mV}_{\text{p-p}}$ | 103  |

# LIST OF TABLES

|          |                                                                            | Page |

|----------|----------------------------------------------------------------------------|------|

| Table 1  | Various parameters used in the realization of the filter transfer function | 27   |

| Table 2  | System level design parameters for low-pass $\Sigma\Delta$ ADC             | 29   |

| Table 3  | Transistor dimensions, device values and bias conditions for OTA           | 35   |

| Table 4  | Simulation results of the stand alone OTA                                  | 39   |

| Table 5  | Linearity test for Gm-C biquad (Quality factor = 10) for different input   |      |

|          | frequencies                                                                | 49   |

| Table 6  | Gm-C band pass filter simulation results.                                  | 52   |

| Table 7  | Gm-C band pass filter simulation results across process corners            | 53   |

| Table 8  | Performance requirements of each stage of the filter                       | 59   |

| Table 9  | Transistor dimensions, device values and bias conditions for amplifier I   | 63   |

| Table 10 | Transistor dimensions, device values and bias conditions for amplifier     |      |

|          | II                                                                         | 64   |

| Table 11 | Summary of performance parameters for amplifier I and II                   | 64   |

| Table 12 | Component values used in the implementation of first biquad of loop        |      |

|          | filter                                                                     | 72   |

| Table 13 | Important performance parameters of the first stage of filter              | 72   |

| Table 14 | Component values used in the implementation of second biquad of loop       |      |

|          | filter                                                                     | 73   |

| Table 15 | Important performance parameters for second stage of filter                | 73   |

| Table 16 | Component values used in the implementation of first biquad of loop        |      |

|          | filter                                                                     | 75   |

| Table 17 | Important performance parameters for third stage of filter                 | 75   |

| Table 18 | GBW requirement for summing amplifier                                      | 81   |

| Table 19 | Component values of summing amplifier stage of loop filter                 | 85   |

| Table 20 | Transistor dimensions, device values and bias conditions for amplifier     | 89   |

| Table 21 | Important performance parameters of the summing amplifier                  | 89   |

|          |                                                                           | Page |

|----------|---------------------------------------------------------------------------|------|

| Table 22 | Important performance parameters of the 5 <sup>th</sup> order loop filter | 95   |

#### 1. INTRODUCTION

#### 1.1 Motivation

The recent technological growth in the wireless communication industry indicates a strong need for ultra-high performance analog-to-digital converters (ADCs) for future wireless radios. Radio frequency (RF) and analog/mixed-signal technologies pay essential and critical role for the success of wireless communications industry. Single-chip multimode, multiband, and multi-standard wireless radio implementations are instrumental for advancing the state-of-the art wireless communication products. This would help the next generation receivers that require support for multiple service providers on a single wireless device [1].

Next generation wireless receivers need support for multiple standards on a single chip. Numerous communications standards have been introduced in the recent past. The most common wireless communication applications are shown in Fig. 1.

Figure 1 Different wireless applications and standards

This thesis follows the style and format of the IEEE Journal of Solid-State Circuits.

The cell phone communication standards include GSM (Global System for Mobile communications), GPRS (General Packet Radio Service), EDGE (Enhanced Data rate for GSM Evolution), CDMA (Code Division Multiple Access), AMPS (Advanced Mobile Phone Systems), UMTS (Universal Mobile Telecommunication System) etc. The standards used in communication networks include WLAN (Wireless Local Area Network), Bluetooth, WI-MAX (Worldwide Interoperability for Microwave Access) and UWB (Ultra Wide Band). The satellite communication standards include GPS (Global Positioning System) standard.

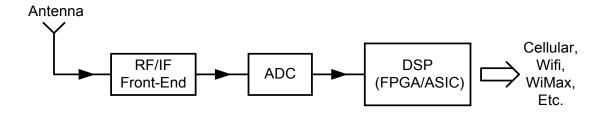

A generic block diagram of wireless receiver is shown in Fig. 2. The architecture of the wireless receiver defines the location of ADC in a receiver chain. If the ADC is placed close to the antenna, important functions such as filtering and frequency translation can be performed in digital domain, which reduces receiver's complexity and increases flexibility. Depending on the architecture of the receiver, the ADC needs to digitize an RF, intermediate-frequency (IF), or the baseband signal. Therefore, the location of ADC in a receiver affects the overall performance, complexity, power dissipation, size and cost of a wireless receiver. A flexible wireless radio should be able to deal with the narrowband / high-dynamic range requirements of cellular standards as well as the wideband / low-dynamic range requirements of WLAN and WiMAX standards, in combination with other standards like Bluetooth and digital video broadcasting-handheld (DVB-H). In this context, it becomes extremely important to explore the ADC architectures that enable reconfiguration and full integration in a RF transceiver.

Figure 2 Generic block diagram of a wireless receiver

The sigma-delta ( $\Sigma\Delta$ ) ADCs provide an effective way to implement high-performance ADCs without stringent matching requirements or calibration. They allow inherent trade-off between bandwidth and dynamic range. Therefore, they are suitable for multi-standard implementations of wireless radio as they provide a variable bandwidth and dynamic range. They lower the specifications for the anti-aliasing filter in front of the ADC. Also, the adjacent interferers fall into the same band as the shaped quantization noise and the digital filters can remove both quantization noise and interferers. Applications like WLAN and WiMAX require wideband ADCs that can digitize both the desired and adjacent-channel interferes, resulting in high dynamic range (DR) requirements. However, the high bandwidth and high dynamic range requirements make the real circuit implementation of  $\Sigma\Delta$  modulators challenging.

In the design of high performance sigma-delta modulators, the use of analog loop filters is unavoidable. The transfer function of the loop filter defines the quantization noise-shaping behavior of the  $\Sigma\Delta$  modulator. The stability of  $\Sigma\Delta$  modulator mainly depends on the location of poles and zeros in the loop filter. Hence, the loop filter becomes a major performance determining part in a  $\Sigma\Delta$  ADC. For applications requiring wide bandwidth and high resolution, the design of analog filters is becoming increasingly difficult.

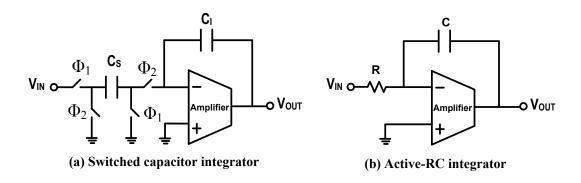

## 1.2 Overview of analog filters

Next generation communication systems require high dynamic range filters that can be integrated on the same chip. The technology and implementation techniques are very important issues to be considered in the design of loop filters in sigma-delta ADCs. The design of CMOS analog filters can broadly be divided into two categories, namely continuous-time and discrete-time techniques [2]. Switched-capacitor and switched-current techniques are examples of discrete-time or sampled-data implementations. The active RC filter, MOSFET-C filters and OTA-C filters are the popularly known continuous-time filter implementations. An integrator is the basic building block in the

implementation of analog filters. Example implementations of discrete-time and continuous-time integrators are shown in Fig. 3a and Fig. 3b respectively.

Figure 3 Examples of discrete-time and continuous-time integrators

#### 1.2.1 Discrete-time filters

Discrete-time filters use multiple clock phases that are non-overlapping in time. In switched capacitor techniques the main characteristics are determined by the clock frequency and the capacitor ratios. These two parameters are almost independent of the process and temperature variations. The high accuracy of the integrator time constant is the major advantage of discrete-time techniques. Furthermore, as the input of the opamp is a virtual ground node, the distortion is very low. In low frequency applications, the high dc gain and high gain-bandwidth of the CMOS operational amplifiers make these filters insensitive to the parasitic capacitors. However, these advantages of switched-capacitor filters are not necessarily maintained for high frequency applications. This is mainly due to the finite dc gain and finite gain bandwidth of the operational amplifiers, the finite resistance of the switches and the clock feed-through.

In high frequency applications the operational amplifier has to be fast enough to settle to the correct output within a half time period of the sampling clock. For a settling precision of 0.1%, the settling time should be higher than the gain-bandwidth of the operational amplifier at least by a factor 7. However, due to contribution of the feedback

factor even larger GBWs are required. In order to guarantee the stability of the closed loop system, the second pole of the operational amplifier should be placed around three times higher than the GBW. For high frequency applications, it is very difficult to satisfy these requirements. The dc gain of the opamp has to be high enough to minimize the signal swing at its input terminals. And, the circuit becomes parasitic insensitive and allows the total charge and discharge of the capacitors. Otherwise the precision of the filters is reduced and the harmonic distortion increases rapidly.

In general, sampled-data filters need an anti-aliasing filter to band limit the frequencies of the input signal. Due to the sampling, high frequency noise can be aliased on to the base band which increases the in band noise reducing the filter's dynamic range. In wireless applications, where in several information channels must be separated it is not possible to use sampled data filters due to aliasing effect. A filtering technique that avoids many of the disadvantages with discrete-time techniques is the continuous-time filtering technique.

## 1.2.2 Continuous-time filters

In the earlier generation of continuous-time filters the basic network elements were inductor, capacitor and resistor. With the evolution of the integrated circuits, the inductors have been replaced by equivalent networks composed of active devices and capacitors. The resulting topologies are called active RC filters. The active devices of the active RC filters are either OPAMPs or OTAs. Aliasing problems are not present in continuous-time filters, which is beneficial when having to handle large interferers. In continuous-time filters based on OTA-C techniques, integrator time constants depend on C/g<sub>m</sub> ratios. Due to the lack of virtual grounds and low impedance nodes, the time constants are not very well controlled. They are affected by the process, temperature variations and parasitic capacitors. In addition to these, the active filters are very sensitive to the OTA non-idealities including finite dc gain, finite bandwidth, parasitic poles and zeros.

The active RC filters use OPAMPs, resistors and capacitors as basic elements. In the present day CMOS technology, the resistors can be implemented either as diffused or poly-silicon resistors. The linearity of the polysilicon resistors is quite good enough and the accuracy of resistors ratios can be as good as 1%. But, the accuracy of the RC products can be as worse as 30%. The RC product is a strong function of both process and temperature variations. Unfortunately, the frequency of poles and frequency of zeros is determined by RC products. Typically, the quality factor of the filter is determined by resistors and/or capacitor ratios. Because the filters are more sensitive to variations in the frequency of the poles than the quality factors, the accuracy of the active RC filters is quite low. The accuracy of these filters can be improved by including certain kind of tuning, either on chip or externally.

## 1.3 Overview of analog-to-digital converter architectures

Digital circuits require very small area and provide extremely large dynamic range at very low cost. Hence, digital signal processing (DSP) has gained momentum in the present decade. However, the digital signal processors have to interface with the real analog world. Therefore, high performance data converters become critical for extremely fast paced improvements of DSP. As the digital signal processing is moved closer to the receiving antenna, the demands on the speed and dynamic range of the analog-to-digital converter become increasingly severe.

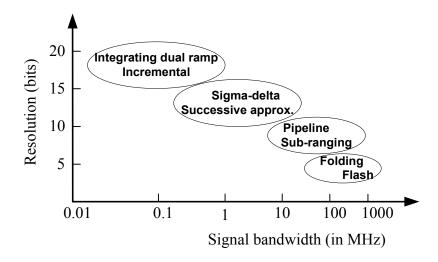

There are two broad classifications of ADCs based on the relation between the sampling frequency and the bandwidth of the input analog signal. They are Nyquist-rate and oversampled ADCs. As shown in Fig. 4, in data converters the speed is always traded with the resolution. Flash architectures are the fastest topology but they provide the lowest resolution. The folding, sub-ranging and pipeline ADC architectures are in the very high speed and medium to low resolution category. The successive approximation and sigma-delta ADCs provide high/medium speed and fall in high resolution category. The incremental and integrating dual ramp ADC architectures fall in the low speed and

very high resolution category [3]. Power consumption increases with increase in the sampling frequency. All the ADC architectures, except sigma-delta, fall under Nyquist rate category. The sigma-delta ADC is an example of oversampling ADC.

Figure 4 Classification of different ADC architectures based on resolution and speed

This thesis presents the design considerations for the loop filter in low-pass continuous-time sigma-delta ADC with 12-bits resolution in 25MHz bandwidth and low power consumption using  $0.18\mu m$  CMOS technology. The main target of this work is to identify and design a suitable filter architecture that satisfies the ADC system-level requirements. It involves designing loop filter that can provide signal-to-noise-and-distortion-ratio (SNDR) greater than 72dB. In this context, this thesis presents the implementation details of two popular filter realization topologies, namely,  $G_m$ -C and active-RC topology is preferred over its  $G_m$ -C counterpart due to the high linearity requirements.

## 1.4 Organization of the thesis

There are seven sections in the thesis. Section 1 provides a brief introduction to the architecture of generic wireless receiver and different communication standards. A brief note on the popular ADC architectures is presented. The importance of analog filters in the design of next generation wireless receivers is identified.

In section 2, properties of the ideal sigma-delta modulator are presented. The architectural differences between continuous-time and discrete-time sigma-delta ADCs are discussed. Some of the system level issues in the implementation of continuous-time sigma-delta modulators are explained. Various performance parameters of the sigma-delta ADCs are discussed in brief.

In section 3, system level design of 12-bit resolution, 25MHz input signal bandwidth continuous-time low-pass sigma-delta ADC is presented. The important system level considerations for determining the open loop filter transfer function of the sigma-delta modulator are presented. An overview of the system implementation is presented together with the behavioral simulation results.

In section 4, theory and simulation results of the  $G_m$ -C band pass filter are discussed. The linearity and noise performance of the OTA and the biquadratic cell are analyzed in a detailed manner. The simulations results for a biquad designed to operate at 100MHz center frequency with a quality factor of 10 are presented. It is shown that the linearity of the biquad depends on the frequency separation between the input-tones used for IM3 measurement.

In section 5, the design of a 5<sup>th</sup> order active low-pass filter for a continuous-time sigma-delta ( $\Sigma\Delta$ ) ADC is presented. The circuit implementation details of the amplifiers used in the integrator stages are presented. The design of a summing amplifier and a novel method for adjusting the group delay in the fast path provided by a secondary feedback DAC of the  $\Sigma\Delta$  ADC are presented in detail.

In section 6, the layout and simulation results of the 5<sup>th</sup> order active low-pass filter are presented. The chip micrograph, test setup and preliminary experimental results of the  $\Sigma\Delta$  ADC are presented in this section. Summary and conclusions are provided in section 7.

#### 2. PROPERTIES OF THE SIGMA-DELTA MODULATOR

This section gives an overview of the basic operation of ideal sigma-delta modulator. The architectural differences between continuous-time and discrete-time sigma-delta ADCs are discussed. Some of the system level implementation issues of continuous-time sigma-delta modulators are presented. Various performance parameters of the sigma-delta ADCs are discussed in brief.

## 2.1 Analog-to-digital conversion

The process of sampling a continuous time analog signal can be treated as multiplying the signal by a train of impulses spaced by  $T_s$  seconds.  $T_s$  represents the sampling time interval expressed as the inverse of sampling frequency,  $F_s$ . Mathematically, the time-domain representation of sampling operation of a continuous-time signal X(t) that produces a sampled output signal  $X_s(t)$  given by

$$X_{s}(t) = \sum_{n=-\infty}^{\infty} X(t) \, \delta(t-nT_{s})$$

(2.1)

where, n is an integer and  $\delta$  is the ideal impulse function. If X(f) represents the Fourier transform of X(t), the frequency domain representation of equation (2.1) can be obtained as

$$X_{s}(f) = X(f) \sum_{n=-\infty}^{\infty} \frac{1}{T_{s}} \delta(f - nF_{s})$$

(2.2)

From equation (2.2), it can be seen that the sampling operation modulates the input signal by carrier frequencies that are integer multiples of sampling frequency ( $F_s$ ,  $2F_s$ ,  $3F_s$  etc.). Since the real world signals are band-limited the maximum signal frequency ( $F_{sig}$ ) defines the minimum sampling rate requirement. As per Nyquist sampling theorem, the minimum sampling frequency required is twice the maximum signal bandwidth. The minimum sampling frequency that recovers the original signal

perfectly from sampled signal is commonly referred as Nyquist sampling rate which is expressed as

$$F_{\text{Nyquist}} = 2 * F_{\text{sig}} \tag{2.3}$$

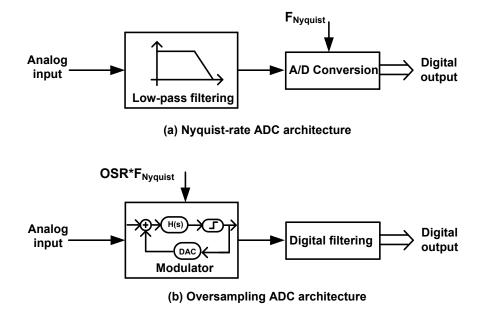

The conceptual diagrams showing the Nyquist-rate and the oversampling ADC architectures are presented in Fig. 5a and Fig. 5b respectively.

Figure 5 Basic A/D conversion architectures

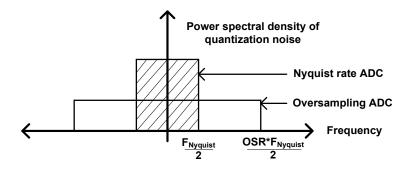

The sampling frequency of oversampled ADCs is much higher than the Nyquist sampling rate. The power of the quantization noise that originates from analog-to-digital conversion process spreads from DC to  $F_s/2$ . Therefore, the in band quantization noise power of the oversampling ADC is reduced by the oversampling ratio (OSR). For example, an oversampling ratio of 2 produces a 3-dB improvement in the signal-to-quantization-noise ratio. Spreading of quantization noise power in an oversampling ADC is exemplified in Fig. 6. Oversampling ratio is expressed in terms of sampling frequency and input signal bandwidth as  $OSR = F_s/2*F_{Sig}$ .

Figure 6 Power spectral density of quantization noise for different ADC architectures

## 2.2 Ideal sigma-delta modulator

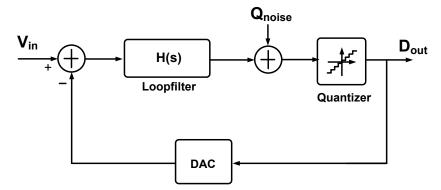

Oversampling and noise-shaping are the basic principles involved in the operation of sigma-delta analog-to-digital converters. The oversampling spreads the quantization noise over the entire sampling frequency and hence reduces the quantization noise floor in the signal bandwidth. The sigma-delta operation shapes the quantization noise such that the in-band noise is decreased while the out-of-band noise is increased. The conceptual diagram of  $\Sigma\Delta$  modulator is shown in Fig. 7. It consists of a loop filter followed by a quantizer, with a digital-to-analog converter (DAC) completing the negative feedback loop.

Figure 7 Block diagram of ideal sigma-delta modulator

The quantization noise ( $Q_{noise}$ ) is assumed as random or white noise which is additive. For small signal analysis of  $\Sigma\Delta$  modulator, a linear model is used and a unity gain transfer function is assumed for DAC and quantizer blocks. H(s) represents the transfer function of the loop filter, therefore, the signal transfer function (STF) and noise transfer function (NTF) of the  $\Sigma\Delta$  modulator are given in equations (2.4a) and (2.4b) respectively. Therefore, the modulator output ( $D_{out}$ ) can be expressed as given in equation (2.4c).

$$STF = \frac{D_{out}}{V_{in}} = \frac{H(s)}{1 + H(s)}$$

(2.4a)

$$NTF = \frac{D_{out}}{Q_{poise}} = \frac{1}{1 + H(s)}$$

(2.4b)

$$D_{out} = STF * V_{in} + NTF * Q_{noise}$$

(2.4c)

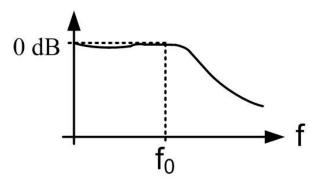

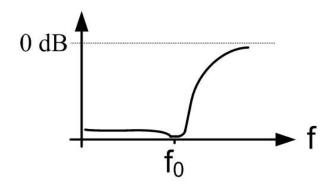

In case of a lowpass  $\Sigma\Delta$  modulator, a lowpass filter transfer function that provides high passband gain is used as H(s). The plots of STF and NTF transfer functions of  $\Sigma\Delta$  modulator employing a lowpass filter are depicted in Fig. 8a and Fig. 8b respectively.

Some of the important advantages of the sigma-delta ADCs can be summarized as follows. Since major portion of the sigma-delta ADC contains digital circuits, their integration with other digital circuitry becomes easy and the cost of implementation reduces. By nature, the sigma-delta modulators provide inherent anti-aliasing due to high oversampling ratio and inherent filtering. High resolution can be achieved using sigma-delta ADCs by exploiting the noise shaping characteristics of the modulator. Importantly, the noise shaping can be obtained without affecting the STF. These advantages make the sigma-delta modulators a good choice for implementing wireless radios.

(a) Signal Transfer function (STF)

(b) Noise Transfer function (NTF)

Figure 8 Typical STF and NTF for a lowpass  $\Sigma\Delta$  modulator

## 2.3 Continuous-time and discrete-time sigma-delta modulators

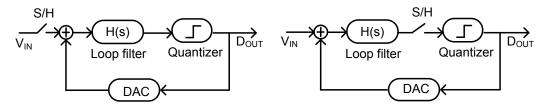

The sigma-delta modulators are classified into two types based on the location of the sample-and-hold (S/H) block. If the sampling operation is performed outside the sigma-delta loop the resulting modulator is called discrete-time modulator. And, if the sampling operation is performed inside the sigma-delta loop the resulting architecture is referred as continuous-time sigma-delta modulator. The loop filter of discrete-time sigma-delta modulators is implemented using switched-capacitor techniques and the loop filter of continuous-time sigma-delta modulator is implemented using continuous-time techniques. The conceptual diagrams of the discrete-time and continuous-time sigma-delta architectures are shown in Fig. 9a and Fig. 9b respectively.

(a) Discrete-time sigma-delta modulator (b) Continuos-time sigma-delta modulator

Figure 9 The discrete-time and continuous-time sigma-delta modulators

Switched capacitor (SC) circuits have been the dominant discrete-time (DT) techniques used for implementing the loop filters in SDMs. This is primarily due to the ease with which monolithic SC filters can be designed and their high-linearity. However, the amplifiers in SC filters require several time constants to settle and impose severe bandwidth requirements at high sampling frequencies [4], [5]. Therefore, continuous-time (CT) techniques have been introduced as an alternative for implementing loop filters for high bandwidth applications [6]. Sampling errors and out-of-band signals which alias into the passband are suppressed by the high in-band gain of the CT loop filter. The absence of sampling switches enables the circuit implementation of the CT filter in low-voltage technologies.

Besides the advantages with respect to large bandwidth and low-power consumption, CT loop filters are more difficult to design and simulate than SC filters. CT components show a higher variation with process-, supply-voltage, and temperature (PVT) spread. The linearity of the continuous time filters is limited due to the inherent non-linear behavior of MOS transistors. The conflicting requirements of low-power and low-noise makes filter design challenging at high frequencies. The over-sampling-ratio (OSR) of the  $\Sigma\Delta$  modulator is traded with the order of the loop filter to achieve high signal-to-quantization-noise ratio (SQNR) at high sampling frequencies. This introduces other issues in terms of stability and excess delay in the  $\Sigma\Delta$  modulator loop. Over the past few years of research in SDMs, it has been shown that CT implementation of ADCs can extend the input frequency range from a few hundreds of kilohertz up to a few tens of megahertz in a very power efficient manner [7]-[12].

The advantages of continuous-time sigma-delta modulators over their discretetime counterparts make them good candidates for future wireless communications [13], [14]. The sampling errors of the sample and hold (S/H) circuit are shaped as the quantization noise since the S/H is placed inside the loop. Also, the CT filter implementation suits well for the high frequency applications, as the sampling frequency is not limited by the charge transfer accuracy requirements. By nature, CT sigma-delta modulators are not sensitive to settling behavior. Contrary to CT modulators, in a DT modulator, large glitches appear on the op-amp virtual ground node of op-amp-RC integrators due to switching transient. Hence, the CT modulator achieves better linearity performance. Further to this, when the sigma-delta modulator is integrated into a complete wireless transceiver in baseline CMOS, glitches generated in DT modulators can potentially couple to other critical blocks of the receiver, such as voltage-controlled oscillators (VCO), LNA and mixers, and can seriously degrade the receiver sensitivity. However, the clock jitter of the feedback DAC in CT sigma-delta modulators is a main issue at high sampling frequency. Multi-bit sigma-delta implementations can circumvent this problem to certain extent.

The continuous-time modulator is obtained by replacing the discrete-time loop filter by continuous-time one. Therefore, the two modulators behave exactly the same. The mapping between CT and DT domain usually employs the impulse invariant transformation as we require the open loop impulse response to be similar [6]. This transformation maps the frequencies linearly from  $-\pi/(2T_s)$  to  $\pi/(2T_s)$  while other frequencies will be aliased. The z-domain transfer function of the loop filter is transformed into to s-domain transfer function for realizing the continuous-time filter. The impulse invariant transformation ensures that the properties of both the structures are the same in terms of performance.

## 2.4 Non-idealities in continuous-time sigma-delta modulators

The functionality of ideal  $\Sigma\Delta$  modulator described in previous section shows that high-dynamic range can be achieved using higher-order loop filter which provides sufficient pass-band gain that suppresses the in-band quantization noise. However, there are certain non-ideal effects to be considered with regards to circuit implementation. Some of the critical non-idealities of continuous-time sigma-delta modulators include circuit noise, distortion, component mismatches, clock jitter and excess loop delay.

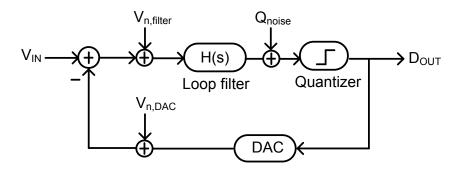

#### 2.4.1 Circuit noise

In practical CMOS circuit implementations, noise is introduced by active transistors and passive resistors. For high frequency and high bandwidth applications the thermal noise of transistors and resistors plays a crucial role in determining dynamic range performance. Since the loop filter is the very first block in the forward path of sigma-delta modulator, its nonidealities appear directly at the output spectrum. Similarly, the noise introduced by the feedback DAC is not shaped by the loop. The noise of loop filter and feedback DAC can be represented using the equivalent voltage noise sources  $V_{n,filter}$  and  $V_{n,DAC}$  respectively as shown in Fig. 10.

Figure 10 Model of sigma-delta modulator with important noise sources

Assuming that the quantizer and the DAC provide linear gain of one, the total input referred noise can be expressed as given in equation (2.5).

$$V_{n,in} = \frac{H(s)}{1 + H(s)} V_{n,filter} + \frac{H(s)}{1 + H(s)} V_{n,DAC} + \frac{1}{1 + H(s)} Q_{noise}$$

(2.5)

From equation (2.5), it can be seen that the quantization noise ( $Q_{noise}$ ) is shaped by the loop gain. However, the noise of the loop filter and feedback DAC see the same transfer function as that of the input signal (STF). Therefore, it is important to minimize circuit noise and distortion from filter and the feedback DAC. Other noise may come from clock jitter and power supply. For optimum dynamic range performance, the total circuit noise contribution must be less than the quantization noise floor of the  $\Sigma\Delta$  modulator.

## 2.4.2 Non-linearity

The inherent nonlinearities present in circuits introduce harmonic distortion in band and degrade the dynamic range of the ADC. Fully differential circuit implementations can eliminate even-order harmonics and the third order harmonic distortion is the most significant. The major contribution of distortion comes from the non-linear behavior of transistors in the loop filter. Any non-linearity of the loop filter directly appears at the output of the modulator as inter-modulation components. Increasing the saturation voltage of the input transistors reduces the distortion as much as possible. However, it will only help to some extent and is only valid for transistor operating in strong inversion. The suppression of harmonic distortion means increasing the linear range of operation of transistors which demands more power.

Nonlinearity of integrators used in the realization of the loop filter is one of the major factors limiting the achievable SNR of CT  $\Sigma\Delta$  ADC. The linearity requirements of the first stage of the filter are more critical for the overall performance of the modulator. DAC mismatch errors become another major source of nonlinearity in CT  $\Sigma\Delta$

modulators that use multi-bit quantization. The non-linearity of the DAC and first stage of filter are most critical because they are added directly to the input signal.

## 2.4.3 Component mismatches

The component mismatches change the frequency response of the loop filter transfer function in sigma-delta modulator. In case of a continuous-time filter, the location of poles and zeros is determined by the product of resistors and capacitors. However, RC product varies with process and temperature variations. Typically, a tuning circuitry and calibration scheme are used to achieve high resolution. Multi-bit quantizers are employed in sigma-delta modulators to improve the modulator resolution, to improve stability with higher order loop filters and to reduce clock jitter sensitivity. However, multiple levels of the quantizer can introduce non-linearity due to mismatches. Component mismatch errors between multiple DAC elements will directly appear at the input of the modulator without any noise shaping.

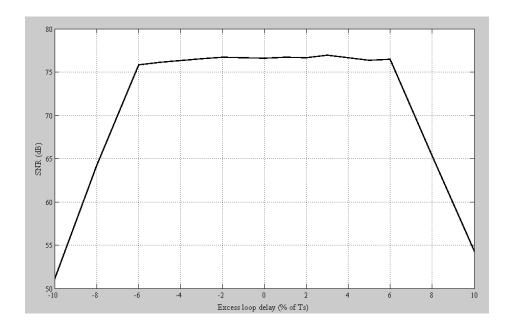

## 2.4.4 Excess loop delay

In a sigma-delta modulator the output of the quantizer drives the feedback DAC and the output of the DAC is fedback to the input of the filter. However, the transistors in DAC and comparator have finite response time. Therefore, there is a finite amount of delay from the sampling clock edge to the change in the output at the feedback node. This delay is commonly referred as excess loop delay and it is significant in continuous-time sigma-delta modulators. Excess loop delay changes modulator transfer function characteristics and affects the stability and dynamic range performance. Excess loop delay is a major concern in high frequency, large bandwidth sigma-delta modulators. Tunability can be incorporated into the coefficients of the loop filter to combat with the excess loop delay. The plot shown in Fig. 11 demonstrates the SNR degradation due to

excess loop delay in CT  $\Sigma\Delta$  ADCs. As it can be seen from figure, the system becomes sensitive to excess loop delay variations greater than  $\pm 6\%$  of the sampling time period.

Figure 11 SNR degradation due to excess loop delay in CT  $\Sigma\Delta$  ADC

## 2.4.5 Clock jitter

In continuous sigma-delta modulators the feedback mechanism is commonly implemented as integration of the feedback signal over a finite-time window. In most of the cases the feedback DAC produces rectangular current or voltage pulses. Any variation in the duty-cycle of the pulses appears as finite error in the integration. Since the clock jitter causes a random variation in the pulse width of the DAC, it adds a random phase noise to the output bit stream of the modulator. In other words, the timing uncertainty in the sampling clock causes an amplitude error in the continuous-time signal. However, this problem is not severe in discrete-time sigma-delta modulators based on switched capacitor filters. This is because of the exponential change transfer that happens between two capacitors in a given time window. Therefore, the clock jitter is a critical issue in sigma-delta modulators. The effect of jitter can directly be related

with the number of clock transitions required for producing DAC's output. Therefore, feedback DACs employing return-to-zero (RZ) mechanism produce low dynamic range performance as compared with the non-return-to-zero (NRZ) DACs. An analytical expression for upper limit to SNR due to jitter for a continuous-time sigma-delta modulator with Non-Return-to-Zero DAC is given below,

SNR =

$$10.\log \left[ \frac{V_{\text{in}}^2 \cdot \text{OSR. } 2^{2N} \cdot T_s^2}{8 \cdot \alpha \cdot \sigma_t^2} \right]$$

(2.6)

where,  $V_{in}$  is the amplitude of the input signal,  $\alpha$  is the value which describes the quantization error variation, OSR is the oversampling ratio, N is the number of quantization levels and jitter is assumed to be Gaussian random process with the standard deviation  $\sigma_t$  and the spectrum of the jitter is white. As the sampling frequency increases, the clock jitter becomes the dominant limit in the SNR performance of the ADC. And, SNR becomes proportional to OSR rather than OSR<sup>2N</sup>. SNR degradation due to the effect of increase in the jitter standard deviation in CT  $\Sigma\Delta$  ADC is shown in Fig. 12.

Figure 12 SNR degradation due to the effect of jitter in CT  $\Sigma\Delta$  ADC

## 2.5 Performance parameters of sigma-delta modulators

The performance of Nyquist rate ADC's is measured using time-domain statistical parameters like differential nonlinearity (DNL), integral nonlinearity (INL) etc. However, these errors have no practical meaning when it comes to oversampling sigma-delta modulators. The most important specification of sigma-delta modulators includes dynamic range, signal-to-noise-and-distortion-ratio, dynamic range and power consumption.

## 2.5.1 Signal-to-noise-and-distortion ratio (SNDR)

SNDR is the ratio of the maximum signal power to the total noise and distortion power in a specific band. In an ideal sigma-delta modulator, the total noise and distortion power is equal to the quantization noise power. However in practical circuit implementation the performance is degraded by the circuit noise and nonlinearity. The main noise contribution comes from thermal noise and flicker noise of transistors and other noisy elements. The nonlinear nature of circuits generates harmonics that can degrade the performance when they fall in band. The noise and distortion can be separately quantified using two different parameters signal-to-noise ratio (SNR) and signal-to-distortion ratio (SDR). For optimum performance, a good balance between SNR and SDR needs to be maintained in the design of sigma-delta modulator [15].

## 2.5.2 Dynamic range (DR)

The dynamic range of a sigma-delta modulator is defined as the ratio of the maximum input signal to the minimum input signal that can be applied. It is often specified as the resolution of the sigma-delta ADC. The relation between the dynamic range and resolution of a modulator is expressed as

Resolution (in bits) =

$$(DR(in dB) - 1.76)/6.02$$

(2.7)

#### 3. DESIGN OF CONTINUOUS-TIME SIGMA-DELTA MODULATOR

This section presents the details of the system level design of 12-bit resolution, 25MHz signal bandwidth continuous-time low-pass sigma-delta ADC. The important system level considerations that affect the stability of the modulator are considered for determining the transfer function of the open loop filter transfer function. An overview of the implementation of system is presented together with the behavioral simulation results.

#### 3.1 Introduction

The architecture of the continuous-time sigma-delta modulator mainly determines its performance. The important architectural level choices include order of the loop filter, single-loop or cascaded architectures, and, single-bit or multi-bit quantizer. Higher order sigma-delta modulators are more suitable for high-frequency, high-resolution applications because they relax the over-sampling requirements. A single loop implementation consumes less power than cascaded architectures. And, cascaded modulators need a precise matching between the analog and digital coefficients. Multi-bit implementation of the quantizer increases the SNR (6dB per each quantizer bit), but it may suffer from mismatches in the feed-back DAC. System level design of the sigma-delta modulator involves determining the loop transfer function, finding the proper loop topology and modeling various non-ideal effects to determine the specifications for each building block. In this work, a 5<sup>th</sup> order, single-loop and 3-bit quantizer architecture is chosen for the implementation of 25MHz bandwidth, 12-bit resolution continuous-time low-pass sigma-delta ADC.

### 3.2 Loop filter transfer function

The most common method to design a CT modulator is to first find the equivalent DT modulator loop filter and then transform it to continuous-time using impulse invariant transformation [16]. However, the design of loop filter transfer function of a continuous-time sigma-delta modulator has a strong dependence on the pulse shape of the feedback DAC. The analog loop filter used in continuous-time sigma-delta modulators requires large dynamic range due to significant peak to average ratio of the resulting signals [17]. Sigma-delta modulator with L<sup>th</sup> order noise transfer function (NTF) given by  $(1-z^{-1})^L$  can achieve dynamic range (DR) given by

DR (in dB) =

$$10 * \log_{10} \left[ \frac{3(2L+1)OSR^{2L+1}}{2\pi^{2L}} \right] + 6.02 * (N-1)$$

(3.1)

where, OSR is the oversampling ratio, L is the order of the modulator and N represents the number of bits in quantizer. For the desired wideband, high resolution modulator, the noise transfer function is more complex. And, the above equation gives a qualitative guidance on selecting the system parameters - OSR, L and N. Based on extensive MATLAB simulations, a fifth order, 3-bit topology is chosen with OSR of 8.

The transfer function of the loop filter is chosen to have Chebyshev type I response with order 5, peak-to-peak ripple equal to 0.5dB and pass-band edge frequency 24MHz. The Chebyshev type I response provides sharp pass-band to stop-band transition which is very important for suppressing the quantization noise in  $\Sigma\Delta$  modulators. The pass-band of the Chebyshev type I filter exhibits equiripple behavior. The order of the filter is equal to the number of reactive components needed to realize the filter. Elliptic filters provide even steeper roll-off by allowing ripple in the stop-band. This will however result in less suppression of quantization noise in the stop-band. The open loop filter transfer function used in low-pass  $\Sigma\Delta$  ADC to achieve a SQNR of 75dB with 25MHz bandwidth in SIMULINK is given in equation (3.2).

$$H(z) = \frac{1.838 z^{-1} - 4.992 z^{-2} + 5.781 z^{-3} - 3.137 z^{-4} + 0.7227 z^{-5}}{1 - 4.503 z^{-1} + 8.295 z^{-2} - 7.802 z^{-3} + 3.744 z^{-4} - 0.7331 z^{-5}}$$

(3.2)

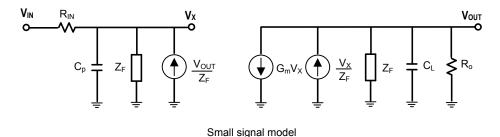

A simplified model of the continuous time sigma-delta modulator is shown in Fig. 13 using z-domain transfer function.  $K_{DAC1}$  and  $K_{DAC2}$  are the primary and secondary feedback DAC coefficients. H(z) represents the open loop filter transfer function. Modeling the quantization error as an input independent additive white noise, the system becomes linear and a small signal analysis can be used to describe the system behavior. Therefore, the input to output voltage transfer function is obtained as

$$\frac{V_{OUT}}{V_{IN}} = \frac{H(z)}{1 + z^{-1}[K_{DAC 1}H(z) + K_{DAC 2}]}$$

(3.3)

Figure 13 Simplified model of the continuous time sigma-delta modulator

The stability of the loop depends on the loop gain term in the denominator given by equation (3.4). Using equation (3.2) the loop gain can be computed as

Loop gain =

$$G(z) = z^{-1}[K_{DAC 1}H(z) + K_{DAC 2}]$$

(3.4)

$$G(z) = z^{-1} \frac{0.5 - 0.413z^{-1} - 0.845z^{-2} + 1.88z^{-3} - 1.26z^{-4} + 0.35z^{-5}}{1 - 4.50z^{-1} + 8.29z^{-2} - 7.80z^{-3} + 3.74z^{-4} - 0.73z^{-5}}$$

(3.5)

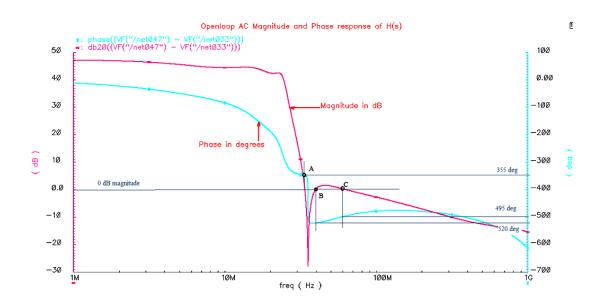

The Bode magnitude and phase response plots of the loop gain and open loop filter transfer function are shown in Fig. 14. The plot shows a phase margin of approximately 145 degrees and a gain margin of -18.5 dB.

Figure 14 Bode plot showing H(z) and Loop gain, G(z)

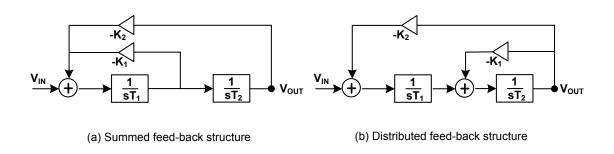

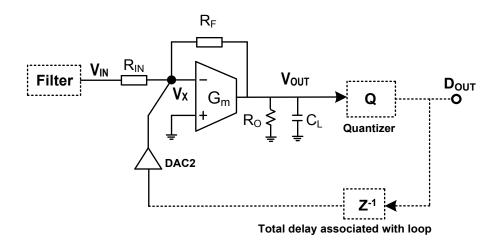

## 3.3 Modulator loop topology

The commonly used loop filter architectures for single stage modulators are of two kinds. One is cascade of integrators with distributed feed-back (CIFB) and the other is cascade of integrators with feed-forward summation (CIFF). The CIFB topology requires multiple DACs feeding back to the input of each integrator stage. Whereas, the CIFF topology requires only two accurate DACs and an additional summing stage to perform feed-forward summation of integrator outputs. However, the CIFB topology

offers better anti-aliasing behavior and is less susceptible to peaking in the signal transfer function.

The feed-forward architecture offers several advantages when compared to the feedback architecture. The signal swing at the internal nodes of the modulator is relaxed in case of feed-forward architecture. The performance requirements of the later stages can be relaxed when compared to the requirements of the former stages in feed-forward architecture. This helps in reducing the power consumed by the non-critical blocks. Therefore, the selection of the modulator loop topology greatly affects the circuit implementation of the loop filter. A feed-forward topology is selected for the implementation of the continuous-time sigma-delta modulator. The s-domain transfer function of the loop filter is obtained as equation (3.6) from impulse invariant transformation of the z-domain transfer function.

$$H(s) = \frac{5.25e6 (s^2 + 3.842e8 s + 8.821e16)(s^2 + 1.606e5 s + 5.567e16)}{(s + 3.58e7)(s^2 + 6.78e7 s + 1.1e16)(s^2 + 2.04e7 s + 2.37e16)}$$

(3.6)

The transfer function of the  $5^{th}$  order loop filter can be simplified to obtain  $2^{nd}$  order and  $1^{st}$  order transfer functions for ease of implementation. The complete filter transfer function is realized as the sum of three different filter blocks with feed-forward summation. Assuming that the operational amplifiers are ideal, the transfer function of the loop filter can be expressed as

$$\begin{split} H(s) &= K_{1} \left( \frac{A_{1} \frac{s}{\omega_{01}} + A_{2}}{1 + \frac{s}{\omega_{01} Q_{1}} + \frac{s^{2}}{\omega_{01}^{2}}} \right) + K_{2} \left( \frac{K_{1}}{1 + \frac{s}{\omega_{01} Q_{1}} + \frac{s^{2}}{\omega_{01}^{2}}} \right) \left( \frac{A_{3} \frac{s}{\omega_{02}} + A_{4}}{1 + \frac{s}{\omega_{02} Q_{2}} + \frac{s^{2}}{\omega_{02}^{2}}} \right) \\ &+ K_{3} \left( \frac{K_{1}}{1 + \frac{s}{\omega_{01} Q_{1}} + \frac{s^{2}}{\omega_{01}^{2}}} \right) \left( \frac{K_{2}}{1 + \frac{s}{\omega_{02} Q_{2}} + \frac{s^{2}}{\omega_{02}^{2}}} \right) \left( \frac{A_{5}}{1 + \frac{s}{\omega_{03}}} \right) \end{split}$$

where  $\omega_{o1}$ ,  $\omega_{o2}$  and  $\omega_{o3}$  are the cut-off frequencies of each filter stage.  $Q_1$  and  $Q_2$  represent the quality factor of first and second biquadratic sections.  $K_1$ ,  $K_2$  and  $K_3$

represent the low frequency gains of each stage. The coefficients  $A_1$ ,  $A_2$ ,  $A_3$ ,  $A_4$  and  $A_5$  are realized as ratio of resistors performing weighted addition of the outputs of the integrators. Table 1 summarizes the coefficient values.

Table 1 Various parameters used in the realization of the filter transfer function

| Coefficient   | Value                          | Coefficient    | Value  |

|---------------|--------------------------------|----------------|--------|

| $\omega_{01}$ | $2\pi \times 24.5 \times 10^6$ | K <sub>3</sub> | 7.7    |

| $\omega_{02}$ | $2\pi \times 16.7 \times 10^6$ | $A_1$          | 0.5685 |

| $\omega_{03}$ | $2\pi \times 5.71 \times 10^6$ | $A_2$          | 1.0369 |

| $Q_1$         | 7.5                            | $A_3$          | 0.5953 |

| $Q_2$         | 1.55                           | $A_4$          | 0.7611 |

| $K_1$         | 6                              | $A_5$          | 0.8743 |

| $K_2$         | 6                              |                |        |

## 3.4 Overview of system implementation

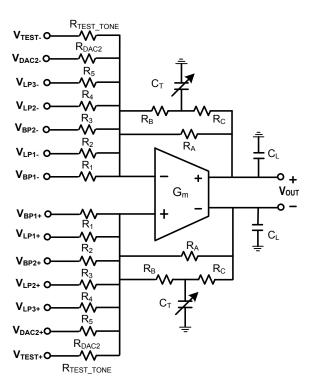

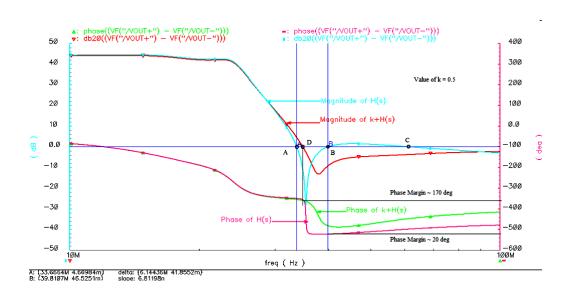

The system level block diagram of continuous-time lowpass sigma-delta (CT LP  $\Sigma\Delta$ ) ADC is shown in Fig. 15. Multiple feed-forward architecture is employed in the loop filter and two accurate feedback DACs are required in the feedback path [18]. The forward path consists of a fifth order Chebyshev lowpass filter and a three-bit quantizer to guarantee the desired signal-to-quantization-noise ratio (SQNR). The output of the quantizer is a digitized version of the filter's output with an embedded half-period delay ( $z^{-1/2}$ ). The output digital bit stream is in voltage mode and the programmable delay block provides another  $z^{-1/2}$  delay to complete the full one period delay required in the loop. The digital output,  $D_{out}$ , in voltage mode is converted into current by a time-variant single bit DAC and injected back into the filter to close the negative feedback loop. The multi-phase DAC uses a single unit element avoiding the mismatch errors that are common in multi-element implementations. However, the multi-phase DAC demands an accurate clock with low jitter performance. Hence, an LC-tank oscillator with injection-

locked frequency divider is implemented to provide a built-in reference clock with low phase noise. A secondary feedback DAC is employed to enhance the tolerance to the excess loop delay [9]. The delay in the secondary feedback loop formed by the summing amplifier, quantizer and the secondary DAC is critical for the stability of the system. Therefore, the summing amplifier needs to be very fast and demands more power. The group delay of the summing amplifier is enhanced by the introduction of a zero-pole pair in its feedback network. The important system level design parameters for low-pass  $\Sigma\Delta$  ADC are presented in Table 2.

Figure 15 System level block diagram of CT LP  $\Sigma\Delta$  ADC

Table 2 System level design parameters for low-pass  $\Sigma\Delta$  ADC

| Design parameter          | Value                 |

|---------------------------|-----------------------|

| Signal bandwidth          | 25 MHz                |

| Sampling frequency        | 400 MHz               |

| Over-sampling ratio (OSR) | 8                     |

| Order of noise shaping    | 5 <sup>th</sup> order |

| Quantizer resolution      | 3 bits                |

| Supply voltage            | 1.8 V                 |

| Targeted resolution       | 12 bits               |

| CMOS Technology           | 0.18µm                |

#### 3.5 Behavioral simulations of the system

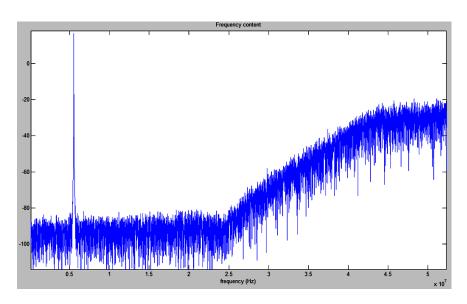

The expected NTF of the ADC and its output spectrum obtained from the 3-bit output data are shown in Fig. 16a and Fig. 16b respectively. The input signal is a sine wave at 5.533 MHz and the sampling frequency is 400 MHz. The measured SQNR at the output of the ADC is 74dB in 25MHz signal bandwidth. The SNR was calculated for 65536 samples and a step size of  $T_s/20$  ( $T_s$  is the time period of the sampling clock) is used for simulating the model, which ensures good accuracy for behavioral simulations.

One of the major challenges in the design of high performance CT LP  $\Sigma\Delta$  ADCs is the design of analog loop filter. In this case, demanding high-performance analog filters are needed to shape the in-band quantization noise and improve the overall SNDR of the system. The summing amplifier block is another critical block for the high speed operation. It needs large bandwidth to guarantee stability of the system by compensating for the excess loop delay introduced by the analog loop filter. This work mainly focuses on the implementation of the analog loop filter for 12-bit resolution 25MHz bandwidth CT LP  $\Sigma\Delta$  ADC.

(a) NTF of ADC

(b) Output spectrum of ADC

Figure 16 The NTF and the output spectrum of the CT LP SD ADC

# 4. DESIGN OF G<sub>m</sub>-C BIQUADRATIC FILTER

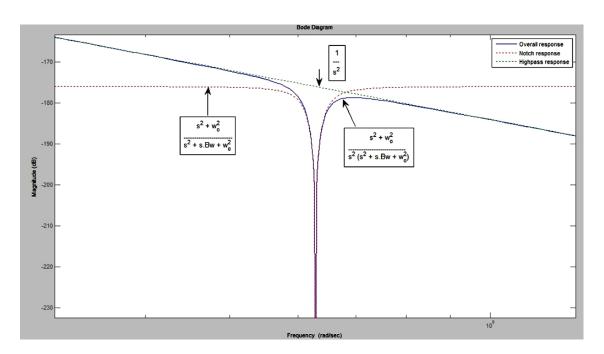

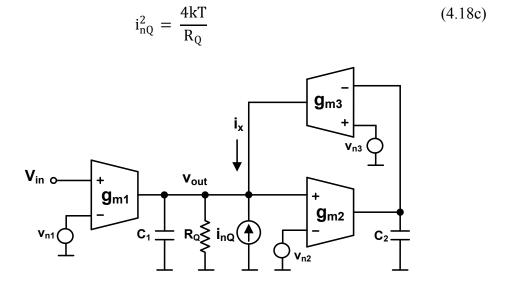

This section presents the theory and simulation results of the  $G_m$ -C band pass filter designed for high-performance continuous-time applications. The linearity and noise performance of the OTA and the biquadratic cell are analyzed in a detailed manner. The simulation results of the  $G_m$ -C biquad designed to operate at a center frequency of 100MHz and a quality factor of 10 are presented. Some important mathematical relations concerning noise and linearity of the  $G_m$ -C biquadratic structure are presented. It is shown that the linearity of the biquad depends on the frequency separation between the input-tones used for IM3 measurement. It is also shown quantitatively that the input referred noise power of the biquad is approximately 3 times that of the stand-alone OTA at the center frequency of the biquad.

## 4.1 G<sub>m</sub>-C integrator

Integrators are the basic building blocks used in continuous-time and discrete-time filters.  $G_m$ -C is the most popular technique used to implement integrators in high-frequency continuous-time filters.  $G_m$ -C integrators have robust stability due to their open-loop operation [19]. Integrators used in high speed continuous-time applications have small load capacitors and large transistors with high transconductance ( $\omega_o$  is proportional to  $g_m/C$ ). Therefore, parasitic capacitance can be a significant portion of the total capacitance value. As a result, the time constant of the integrator is sensitive to process and temperature variations.

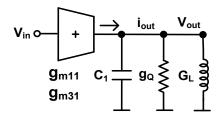

Figure 17 Popular G<sub>m</sub>-C integrator architectures

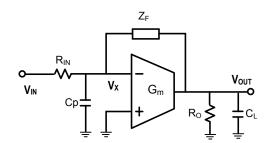

Two popular  $G_m$ -C integrator structures employed in high frequency continuous time filters are shown in Fig. 17. The basic  $G_m$ -C integrator which is obtained by loading a transconductor with a capacitor at the output is shown in Fig. 17a. Assuming that the  $G_m$ -cell has very high output impedance and the parasitic capacitance at the output node is negligible compared to the load capacitance, the voltage transfer function of the circuit is obtained as

$$\frac{V_{\text{OUT}}}{V_{\text{IN}+} - V_{\text{IN}-}} = \frac{g_{\text{m}}}{\text{sC}}$$

(4.1a)

If  $g_0$  is the finite output impedance and  $C_p$  is parasitic capacitance at the output node, the transfer function is obtained as

$$\frac{V_{\text{OUT}}}{V_{\text{IN}+} - V_{\text{IN}-}} = \frac{g_{\text{m}}}{g_{\text{o}}} \frac{1}{1 + s\left(\frac{C + C_{\text{p}}}{g_{\text{o}}}\right)}$$

(4.1b)

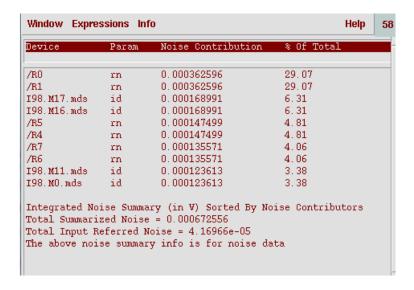

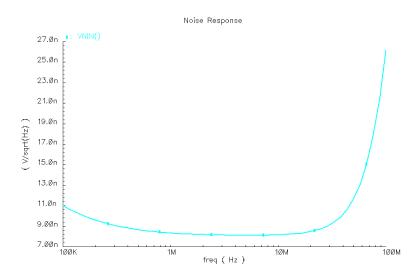

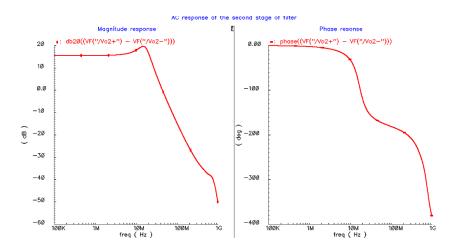

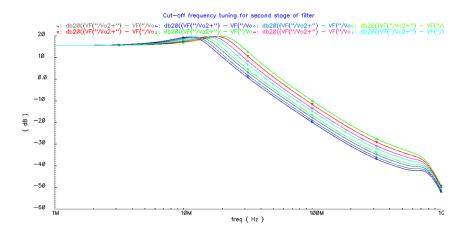

Therefore, the low-frequency gain of the  $G_m$ -C integrator depends on the transconductance  $(g_m)$  and the finite output impedance  $(r_o = 1/g_o)$  of the transconductor. To increase the dc gain of the integrator without increasing the power consumption, it may be required to use some kind of cascoding at the output of the  $G_m$ -cell. However, with the reduction in power supply voltages cascoding may reduce the output voltage swing capability of the integrator. Further to this, the time constant of  $G_m$ -C integrator is sensitive to parasitic capacitances.