# DESIGN FOR MANUFACTURING (DFM) IN SUBMICRON VLSI DESIGN

A Dissertation

by

KE CAO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

August 2007

Major Subject: Computer Engineering

# DESIGN FOR MANUFACTURING (DFM) IN SUBMICRON VLSI DESIGN

# A Dissertation

by

### KE CAO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

# Approved by:

Chair of Committee, Committee Members, Weiping Shi Duncan Walker

Duncan Walke Vivek Sarin

Head of Department, Costas N. Georghiades

August 2007

Major Subject: Computer Engineering

#### **ABSTRACT**

Design for Manufacturing (DFM) in Submicron VLSI Design. (August 2007)

Ke Cao, B.S., University of Science and Technology of China;

M.S., University of Minnesota

Chair of Advisory Committee: Dr. Jiang Hu

As VLSI technology scales to 65nm and below, traditional communication between design and manufacturing becomes more and more inadequate. Gone are the days when designers simply pass the design GDSII file to the foundry and expect very good manufacturing and parametric yield. This is largely due to the enormous challenges in the manufacturing stage as the feature size continues to shrink. Thus, the idea of DFM (Design for Manufacturing) is getting very popular. Even though there is no universally accepted definition of DFM, in my opinion, one of the major parts of DFM is to bring manufacturing information into the design stage in a way that is understood by designers. Consequently, designers can act on the information to improve both manufacturing and parametric yield. In this dissertation, I will present several attempts to reduce the gap between design and manufacturing communities: Alt-PSM aware standard cell designs, printability improvement for detailed routing and the ASIC design flow with litho aware static timing analysis. Experiment results show that we can greatly improve the manufacturability of the designs and we can reduce design pessimism significantly for easier design closure.

To my parents and my beloved wife, Shasha Luo

#### **ACKNOWLEDGMENTS**

Pursing a doctoral degree certainly is a long and difficult process, and it would not be possible without the help of numerous people. To them I wish to express my sincere gratitude. I would especially like to thank my advisor, Dr. Jiang Hu, for his generous time and commitment. Throughout my doctoral work he encouraged me to develop independent thinking and research skills. He continually stimulated my analytical thinking and greatly assisted me with scientific writing.

I am also very grateful for having an exceptional doctoral committee and wish to thank Dr. Weiping Shi, Dr. Duncan Walker and Dr. Vivek Sarin for their continual support and encouragement.

My thanks go out to the many fellow students in the Computer Engineering program, Chin-Ngai Sze (Cliff), Ganesh Venkataraman, Di Wu, Mankang Mai, Shu Yan, Zhuo Li, Xiang Lu and Ying Zhou. They made my routine student life much more enjoyable.

My research for this dissertation was made more practical and more extensive through the communications with some of the brightest people in the ASIC design and EDA industry. Thus I would like to thank Mr. Sorin Dobre at Qualcomm for the many hour-long discussions on the trends of various design methodologies including DFM, Dr. Puneet Gupta at Blaze-DFM for debating lithography aware design methodology, Mr. Bill Graupp at Mentor Graphics for developing design tool usability, Dr. Andrew Kahng at UCSD/Blaze-DFM for his encouragement and support.

Finally, I'd like to thank my family. My parents extended their unconditioned support to my decision to continue with the graduate program. I'm especially grateful to my wife, Shasha Luo, for her patience, her sacrifice, and for helping me keep my life in proper perspective and balance. I can not imagine going through graduate school without her being by my side.

# TABLE OF CONTENTS

| CHAPTER |                                                                                  | Page |

|---------|----------------------------------------------------------------------------------|------|

| I       | INTRODUCTION                                                                     | 1    |

|         | A. Alt-PSM Compliance and Composability for Standard Cell Layout                 | . 1  |

|         | B. Wire Sizing and Spacing for Lithographic Printability and Timing Optimization | . 3  |

|         | C. ASIC Design Flow Considering Lithography Induced Effects.                     | . 6  |

|         | D. Organization of the Dissertation                                              | . 8  |

| II      | ALT-PSM COMPLIANCE AND COMPOSABILITY FOR STAN-<br>DARD CELL LAYOUT               | 9    |

|         | A. Introduction                                                                  | . 9  |

|         | B. Library Cell Construction                                                     |      |

|         | 1. Layout Style                                                                  |      |

|         | 2. Transistor Placement                                                          |      |

|         | <ul><li>3. Routing</li></ul>                                                     |      |

|         | C. Cell Alt-PSM Composability                                                    |      |

|         | 1. Problem Formulation                                                           |      |

|         | 2. Algorithm                                                                     | . 24 |

|         | D. Standard Cell Library Design Flow                                             | . 26 |

|         | E. Experiments                                                                   | . 28 |

|         | 1. Standard Cell Construction                                                    |      |

|         | 2. Layout Modification                                                           |      |

|         | F. Conclusion                                                                    | . 30 |

| III     | WIRE SIZING AND SPACING FOR LITHOGRAPHIC PRINT-                                  |      |

|         | ABILITY AND TIMING OPTIMIZATION                                                  | 32   |

|         | A. Introduction                                                                  | . 32 |

|         | B. Problem Formulation                                                           | . 35 |

|         | C. Printability Model                                                            |      |

|         | 1. Aerial Image                                                                  |      |

|         | 2. Printability Function                                                         |      |

|         | D. Timing Driven Wire Sizing Considering Coupling Capacitance                    | . 42 |

| CHAPTER  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                       |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|          | E. Printability Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                         |

| IV       | ASIC DESIGN FLOW CONSIDERING LITHOGRAPHY INDUCED EFFECTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55                                                                         |

|          | A. Introduction B. Overview of Methodology 1. FEOL Lithography Variations 2. Calculation of Effective Transistor with Litho Effects 3. Calculation of Effective Transistor with Litho Effects 4. Calculation and Standard Cell Characterization 5. Calculation and Standard Cell Characterization 6. Experiment 7. Standard Cells 7. Calculation On BEOL 8. STA Comparison 9. Calculation On BEOL 9. 9 | 57<br>57<br>57<br>59<br>63<br>64<br>65<br>65<br>65<br>66<br>66<br>69<br>70 |

| V        | CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74                                                                         |

| REFERENC | ES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                                                         |

| VITA     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79                                                                         |

# LIST OF TABLES

| TABLE |                                                                                                                         | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------|------|

| I     | Experimental results for standard cell construction                                                                     | 28   |

| II    | Experimental results for standard cell modification                                                                     | 31   |

| III   | Benchmark circuit specification                                                                                         | 52   |

| IV    | Experimental results. # vio is the number of delay violations. $\Theta$ is the printability. # vio remains 0 in phase 2 | 53   |

| V     | Lithographic simulation results on average EPE                                                                          | 54   |

| VI    | Experimental results for standard cell characterization                                                                 | 72   |

| VII   | Leakage variability analysis                                                                                            | 73   |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                  | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

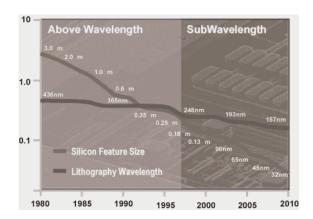

| 1      | Technology tread for transistor feature size                                                                                                                     | . 2  |

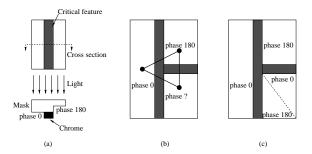

| 2      | (a) Alternating Phase Shifting Mask(Alt-PSM). (b) Phase conflict occurs for a T-shaped critical feature. (c) Phase conflict removal by splitting a phase region. | . 3  |

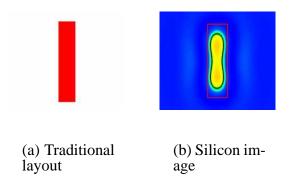

| 3      | Layout without OPC and its silicon image [14]                                                                                                                    | . 4  |

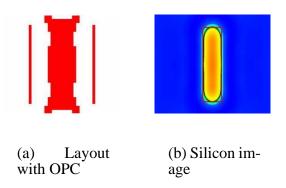

| 4      | Layout with OPC and its silicon image [14]                                                                                                                       | . 4  |

| 5      | OPC results in fractures in mask layout [15].                                                                                                                    | . 5  |

| 6      | Standard cell Alt-PSM composability                                                                                                                              | . 10 |

| 7      | Library cell layout style                                                                                                                                        | . 12 |

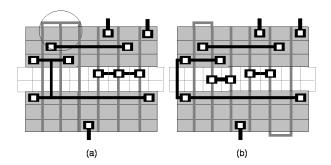

| 8      | Layout constraints examples                                                                                                                                      | . 19 |

| 9      | PSM aware library cell synthesis algorithm                                                                                                                       | . 22 |

| 10     | Phase conflict graph                                                                                                                                             | . 23 |

| 11     | Boundary nodes in phase conflict graph                                                                                                                           | . 23 |

| 12     | Phase conflict bipartite graph: empty dots represent boundary nodes, solid dots represent all other nodes                                                        | . 25 |

| 13     | Standard cell library design flow.                                                                                                                               | . 27 |

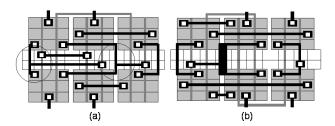

| 14     | (a) XOR gate layout: T joints in Metal 1 layer that pose phase conflict problem. (b) PSM clean layout.                                                           | . 29 |

| 15     | (a) 2 Input NOR gate layout with N-P pairs split in 3 fingers each: T joints in Poly. (b) PSM compliant and composable. layout                                   | . 30 |

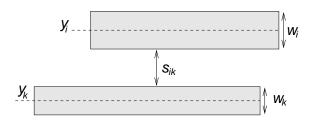

| 16     | Wire segment parameters                                                                                                                                          | . 35 |

| FIGURE |                                                                                                                   | Page |

|--------|-------------------------------------------------------------------------------------------------------------------|------|

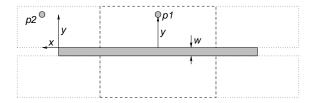

| 17     | Infinite line model in dashed bounding box. Semi-infinite line model in dotted boxes.                             | 39   |

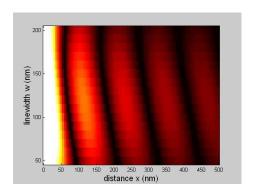

| 18     | Contour plot of complex field amplitude vs. feature linewidth and distance to feature for coherent illumination   | 40   |

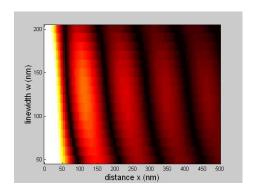

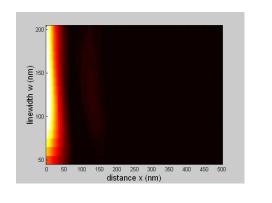

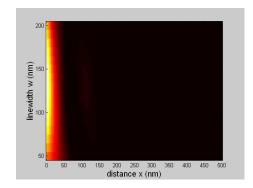

| 19     | Contour plot of light intensity vs. feature linewidth and distance to feature for partially coherent illumination | 41   |

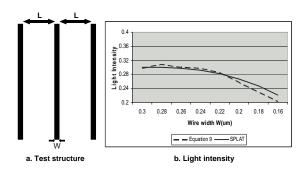

| 20     | Comparisons of light intensity calculations                                                                       | 41   |

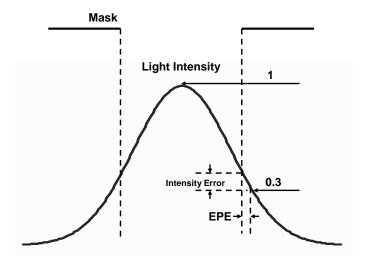

| 21     | Light intensity and EPE                                                                                           | 43   |

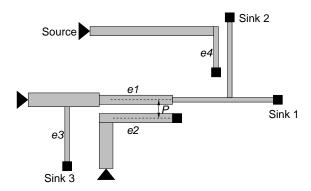

| 22     | Illustration on relative positions among nodes and edges                                                          | 46   |

| 23     | Timing driven wire sizing algorithm                                                                               | 48   |

| 24     | Printability optimization heuristic                                                                               | 50   |

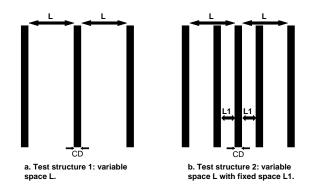

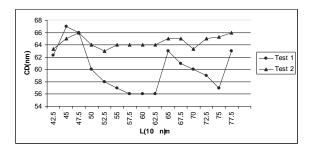

| 25     | Test structures for CD variations through pitch                                                                   | 58   |

| 26     | Critical dimensions of the two test structures when $L$ changes                                                   | 58   |

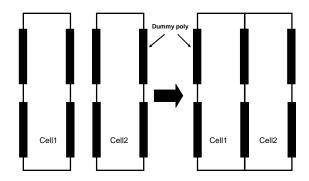

| 27     | Dummy poly of two neighboring cells can be merged                                                                 | 60   |

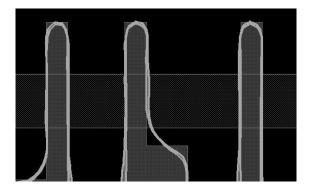

| 28     | Systematic poly gate CD variations from lithography                                                               | 60   |

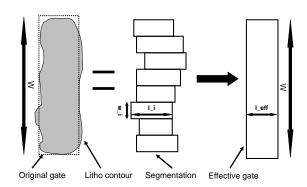

| 29     | Calculation of effective gate length for timing and leakage                                                       | 61   |

| 30     | Litho contours for routing metal                                                                                  | 64   |

| 31     | Convert litho contour to Manhattan polygon                                                                        | 66   |

| 32     | Litho aware standard cell characterization flow                                                                   | 67   |

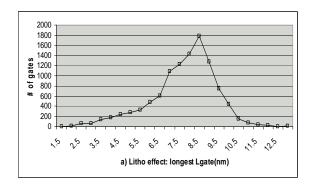

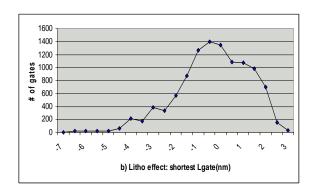

| 33     | Lithography induced Lgate deviation distribution: worst corner                                                    | 68   |

| 34     | Lithography induced Lgate deviation distribution: best corner                                                     | 68   |

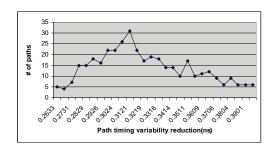

| 35     | Timing variability reduction for critical paths                                                                   | 70   |

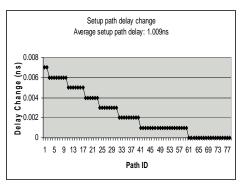

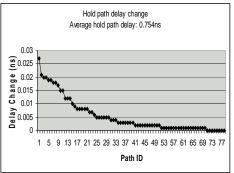

| 36     | Delay path timing changes                                                                                         | 73   |

#### CHAPTER I

#### INTRODUCTION

For an ASIC design, it used to be true that design and manufacturing are relatively independent of one another, with a set of design rules the only connection between the two. This configuration, however, is changing as VLSI technology scales towards deep submircon technology nodes. Manufacturing in sub-wavelength technology has become so challenging that we need to address some of the issues in design practice to improve manufacturing yield. At the same time, process variations in the advanced technologies cause either difficulty or unnecessary pessimism for design closure. Clearly, a mechanism is needed for modeling manufacturing processes accurately and bring the modeling into design space. Thus designer can effectively account for manufacturing realities to enhance manufacturing yield and at the same time reduce design pessimism. In this dissertation, I will attempt to present some of the new technologies to reduce the gap between design and manufacturing.

## A. Alt-PSM Compliance and Composability for Standard Cell Layout

Current VLSI technology has the minimum transistor feature size of 90nm and 65nm, which is remarkably below the lithography wavelength of 192nm. The technology trend for future indicates that this gap will become even larger as shown in Figure 1. In the subwavelength lithography, Resolution Enhancement Techniques(RET) [1] have been deployed to combat strong diffractive effects that cause severe mismatch between mask shapes and printed shapes. Phase Shifting Mask(PSM) is one of the common techniques in RET. PSM uses the destructive interference between two 180 degree out of phase lights to print shape edges.

The journal model is IEEE Transactions on Automatic Control.

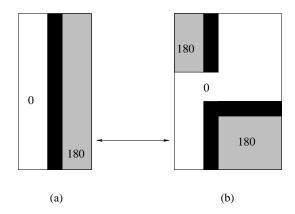

There are two types of PSM currently in use, Attenuated PSM(Att-PSM) and Alternating PSM(Alt-PSM). In Att-PSM, mask substrates are used to allow a small amount of the out of phase light to penetrate the normally opaque mask regions. In Alt-PSM, lights with opposite phases are shed on two sides of a thin critical feature. While Att-PSM poses less restriction in layout design than Alt-PSM does, Alt-PSM is easier to control in lithography process and the quality and the robustness of the printed image is better. Alt-PSM is currently being used in high performance VLSI designs in 90nm and 65nm technologies for its better critical dimension(CD) control of transistor gate poly. For routing metals of the standard cell, Att-PSM could be used instead of Alt-PSM as the requirement of CD control is not as rigorous. Alt-PSM may be the only option for Phase Shifting Mask of gate poly when VLSI technology further scales down 45nm and 32nm. The Alt-PSM technique is illustrated in Figure 2(a).

Fig. 1. Technology tread for transistor feature size.

Even though the Alt-PSM technique is carried out in the stage of mask design and lithography, it needs to be considered in circuit layout as well. For example, a T-shaped layout like in Figure 2(b) may make phase assignment infeasible. In [2], a region where a phase conflict occurs is split to enable Alt-PSM as shown in Figure 2(c). As the phases

Fig. 2. (a) Alternating Phase Shifting Mask(Alt-PSM). (b) Phase conflict occurs for a T-shaped critical feature. (c) Phase conflict removal by splitting a phase region.

of lights are opposite along two sides of the splitting line (the dashed line in Figure 2(c)), unwanted features may be left there and need to be trimmed by another exposure. The second exposure will increase the already expensive mask cost and cause misalignment risk. In [3,4], graph based algorithms are proposed to modify existing layout for Alt-PSM compliance. These algorithms can achieve global optimality, but demand large CPU time if they are applied on an entire chip layout. Furthermore, it is very complicated to modify layout at top level in standard cell based designs, considering both fixed IP designs and interactions between layout layers.

# B. Wire Sizing and Spacing for Lithographic Printability and Timing Optimization

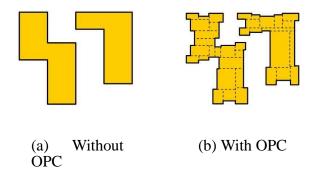

When lithography entered sub-wavelength regime, strong diffraction effect may cause significant discrepancy between photo-mask patterns and printed features. For example, a rectangle feature as in Figure 3(a) on photo-mask may result in printed feature with distortion as in Figure 3(b) on the silicon. A circuit layout with poor printability implies that it is difficult to make the printed features on wafers follow designed shapes without distortions. Currently, the printability of devices with sub-wavelength sizes is usually improved by using Resolution Enhancement Techniques (RET) [1,11–13] such as Optical Proximity Cor-

rection (OPC), Phase Shift Mask (PSM), Off Axis Illumination (OAI), and Sub-Resolution Assist Feature (SRAF), so as to overcome diffraction limit and process imperfections. For example, mask layout for printing the rectangle feature in Figure 3(a) becomes Figure 4(a) with OPC and SRAF. As a result, the printed feature on silicon (Figure 4(b)) becomes closer to the desired rectangle shape.

Fig. 3. Layout without OPC and its silicon image [14].

Fig. 4. Layout with OPC and its silicon image [14].

However, relying on RET alone is inadequate to harness the problem because of the following reasons.

The increasingly large gap between feature size and wavelength forces several aggressive RETs to be jointly applied and thereby compounds the already complicated mask design and increases mask cost drastically. An example in [15] is shown in

Figure 5 to demonstrate this problem. Compared to mask layout without OPC like Figure 5(a), the mask layout with OPC like Figure 5(b) increases mask data volume, mask writing time and therefore mask cost dramatically.

- The circuit complexity keeps growing and makes RET formidably challenging.

- RET deployments may be obstructed or even prohibited by an RET-unfriendly layout. Therefore, the sub-wavelength printability problem has to be considered also in circuit layout design to ensure manufacturability.

Fig. 5. OPC results in fractures in mask layout [15].

In practice, a lithography friendly and/or RET compliant layout is often obtained through either rule based or model based methodology level approaches. In rule based approaches, lithography friendliness and/or RET compliance are expressed as a set of recommended/hard design rules which are applied in detailed layout design such as detailed routing and layout compaction. This approach is fast and relatively easy to use. However, lithography and RET procedures are so complicated that it is very difficult to convey their requests fully through simple rules. In model based approaches, lithography and RET simulations are performed on a circuit layout and any observed problems are fed back to circuit designers for layout modification. The model based solutions are generally more reliable

than the rule based solutions, but the simulations are very time consuming and it usually takes several iterations to reach closure.

In order to overcome the weakness of the methodology level approaches, lithography friendliness and/or RET compliance need to be considered directly in circuit layout algorithms.

## C. ASIC Design Flow Considering Lithography Induced Effects

The International Technology Roadmap for Semiconductors (ITRS) projects that process variations present a critical challenge for both manufacturing yield and parametric yield of integrated circuit products. The process variations consist of systematic components and random components. The systematic variations represent both Front End Of Line (FEOL) and Back End Of Line (BEOL) parameter variations caused by predictable design and process procedures, such as CD (Critical Dimension) variations from different poly gate pitches and metal thickness variations occurred during Chemical Mechanical Planarization (CMP). Therefore, systematic variations behave deterministically in general.

In many existing design methodologies, people usually treat systematic variations together with random variations without differentiation. By handling both kinds of variations together in a process corner based methodology, people can conveniently circumvent relatively complex systematic variation models. However, such simplification usually causes unnecessary pessimism in process corner estimations especially when the systematic components account for a large portion of the overall variations. Indeed, it is reported in [27] that more than 50% of transistor gate length variations are due to systematic sources. As VLSI technology aggressively scales to 65nm and beyond, the influences from both systematic and random variations become greater and greater. The consequently expanding process corners force designers to set aggressive timing targets which intensify both design

productivity crisis and power crisis [26]. Therefore, significant pessimism in process corner estimations is no longer tolerable and systematic variations need to considered differently from random variations.

Among systematic variations, transistor gate length variation has perhaps the largest impact on circuit timing and power performance since it directly affects both transistor switching speed and leakage power [28]. Fortunately, gate length variation largely depends on lithography process and can be captured through lithography/OPC (Optical Proximity Correction) simulations. A pioneer work [29] tried to estimate gate length variations through computationally expensive aerial image process simulations. Recently, a post OPC extraction methodology was proposed [30] for timing analysis of critical paths in a design. In [30], it is found that timing critical paths are changed when post OPC extraction information is utilized. However, the overall timing performance of a circuit is not altered by this methodology. Another work [31] proposed a timing analysis methodology with awareness of lithography induced gate length variations according to different poly pitches. For a standard cell, three poly spacing ranges are considered for its four boundaries and thereby 81 variants are characterized for each cell. The timing characteristic of a cell instance in a layout is obtained by matching its surrounding layout pattern with one of the 81 variants. Others [13] proposed a Restricted Design Rule (RDR) concept. This approach imposes more stringent constriants on designs to enhance manufacturing yield. It basically trades off design area and possible performance loss for less design variability.

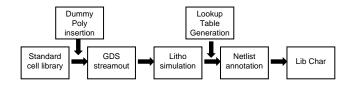

In this chapter, we present a new standard cell characterization methodology considering lithography effects, then we extend this discussion into BEOL to investigate the timing impact of lithography effects on routing metals. Based on these result, we propose a new litho-aware timing analysis flow which considers lithography induced effects on both gate length variations and interconnect wire width variations. In this methodology, the timing and power performance of a cell is based on layout shapes obtained from lithography and

OPC simulations and the interconnect wire width variations is considered with a lookup table.

# D. Organization of the Dissertation

The rest of the dissertation is organized as follows. In Chapter II, we present a technique for Alt-PSM compliant and composable standard cell library design. Chapter III contains a wire size and spacing technology for timing optimization and printability improvement. Chapter IV discusses a lithography aware ASIC design flow for standard timing analysis. Chapter V concludes this dissertation.

#### **CHAPTER II**

# ALT-PSM COMPLIANCE AND COMPOSABILITY FOR STANDARD CELL LAYOUT

Alternating Phase Shift Mask (Alt-PSM) has been identified as one of the important Resolution Enhancement Techniques (RET) solutions for manufacturing of high performance designs because of its superior Critical Dimension (CD) control of the printed features. To facilitate the use of Alt-PSM in VLSI deep submicron manufacturing, we developed a new methodology for Alt-PSM aware library cell generation. We proposed a two-way approach for library cell generation and a new library development flow that is very easy to incorporate into the current design flow. The methodology we proposed guarantees that the top level designs using our Alt-PSM aware library do not have poly layer phase errors, which is required for manufacturing with Alt-PSM.

#### A. Introduction

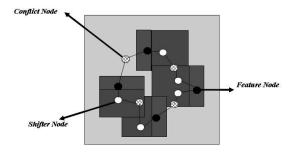

In standard cell designs, one speedup method is to exploit the repetition usage of library cells. The Alt-PSM compliance for each library cell does not need to be obtained repeatedly, it can be achieved once in library cell designs. However, due to the proximity effect, placing Alt-PSM compliant cells adjacent to each other may cause new phase conflict. For example, in Figure 6, when the two Alt-PSM compliant cells are placed next to each other, phase conflict will happen between the two regions indicated by the arrow.

We propose a two way approach for developing standard cell library with Alt-PSM compliance and composability. For smaller standard cells where placement of transistors has minimal impact on the electrical performance of the standard cell, we will construct the standard cell layout to be Alt-PSM compliant and Alt-PSM composable; for larger standard cells with fixed transistor placement and routing for performance optimization,

Fig. 6. Standard cell Alt-PSM composability.

we propose an optimal and efficient algorithm to modify the existing layout to achieve Alt-PSM compliance and composability.

For small standard cell construction, we consider the transistor placement and intracell routing at the same time so that the layout of poly layer and metal layer can match with each other. As an early classical work, Uehara and Cleemput [5] developed a graph based automatic cell layout system with a certain regular style. Recently, the minimum width version of the problem is tackled [6] with Boolean satisfiability(SAT) method [8]. We also propose to achieve Alt-PSM compliant and composable cell layout by using Boolean satisfiability. We transform the constraints for the standard cell synthesis to a SAT formulation and then use Siege SAT solver [7] to search for solution. Our formulation handles multiple sized transistors and considers transistor folding for large transistors.

For complicated standard cells, the placement of the transistors has been optimized for performance, we propose a network flow based algorithm to modify the existing layout for Alt-PSM composability with minimal cell area increase.

Our experiments show that Alt-PSM requirements can be satisfied efficiently at the IP development level. Block level and top level Alt-PSM compliance is guaranteed by our

methodology.

The paper is organized as follows: section 2 presents the SAT formulation for standard cell construction, section 3 provides the algorithm for standard cell layout modification. The experiment results are presented in section 4. Section 5 is the conclusions of this work.

# B. Library Cell Construction

For simple standard cells with small number of transistors, we use correct-by-construction approach for Alt-PSM compliant and composability. This section will present the SAT formulation for standard cell construction.

# 1. Layout Style

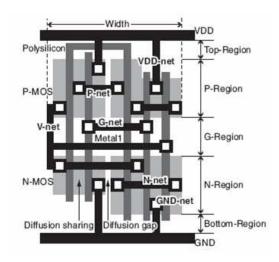

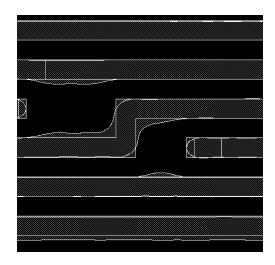

The layout style employed in this work follows the convention of [5, 6] and is illustrated by redrawing the example of [6] in Figure 7. The major characteristics of this style are summarized as follows.

- Transistors are placed in two rows, with PMOS at upper row and NMOS at bottom row.

- PMOS transistors are aligned with their bottom boundaries. NMOS transistors are aligned with their top boundaries.

- If a PMOS transistor and an NMOS transistor share the same GATE node, they are vertically aligned.

- The intra-cell routing uses only the poly layer and the Metal-1 layer.

- All nets connecting SOURCE/DRAIN nodes of PMOS are in P-Region.

- All nets connecting SOURCE/DRAIN nodes of NMOS are in N-Region.

- All nets connecting GATE nodes of are in G-Region, Top-Region or Bottem-Region.

- The VDD rail lies horizontally above the PMOS row and the GND rail lies horizontally below the NMOS row.

- No dogleg is employed.

Fig. 7. Library cell layout style.

It is not hard to see that this layout style is very regular and the constraints of regularity may sacrifice performance/area to certain degree.

### 2. Transistor Placement

This section describes the SAT formulation for transistor placement. Following the layout style mentioned in Figure 7 and placement formulation from [6], N PMOS transistors and N NMOS transistors need to be placed in minimum number of columns so that the resultant placement is PSM Clean and Composable. Each transistor's placement is defined by a set of boolean variables of length P, where  $P = \lceil logW \rceil$ , W being the number of columns. A

13

variable of unit length is needed to define flip of each transistor. We call the flip variable

as  $f_i$ . Total number of variables thus needed for placement is  $2N X(\lceil log W \rceil + 1)$ . The

placement constraints are:

**MOS Overlap Constraints:** Any two N/P transistors should not overlap in same col-

umn, i.e.

$$(x_n/x_{pi1} \oplus x_n/x_{pj1}) \lor (x_n/x_{pi2} \oplus x_n/x_{pj2}) \dots \lor (x_n/x_{pip} \oplus x_n/x_{pjp}) = 1; i \neq j;$$

(2.1)

where  $x_n/x_{pi1}, x_n/x_{pi2}...x_n/x_{pip}$  is the bit vector of length P defining placement of  $i^{th}$  N/P transistor.  $x_{nip} \oplus x_{njp} = 1$  means that the column number of the *ith* NMOS transistor has the same value at the  $p^{th}$  digit as that of the column number of the  $j^{th}$  NMOS transistor.

**Vertical Gate Constraint:** N and P transistor placed in same column must share the same gate connection.

$$\vee_{j \in G} \overline{((x_{ni1} \oplus x_{pj1}) \vee (x_{ni2} \oplus x_{pj2}) \dots \vee (x_{nip} \oplus x_{pjp}))} = 1; \tag{2.2}$$

where G is the set of P transistors having same gate as NMOS i. Basically, if there exists a PMOS transistor that shares the same gate connection with this NMOS transistor, this constraint aligns that PMOS transistor with the NMOS transistor. This configuration usually results in the most compact layout as the gate connection between P and N transistors can be made with the vertical poly. Similar expressions for NMOS transistor will provide the vertical gate constraint for PMOS transistors.

**Neighboring MOS Constraint:** transistors placed in neighboring columns must share

diffusions: For N transistors

$$GAP_n(i,j) \bigvee [\bigvee_{k=0}^{W-2} (C_n(i,k) \wedge C_n(j,k+1)] = 1$$

(2.3)

where  $GAP_n(i, j) = 0$  if NMOS j is placed right of NMOS i to share diffusion.

$$GAP_{n}(i,j) = \overline{f_{i}f_{j}}same_{ds}(i,j) \vee \overline{f_{i}}f_{j}same_{d}(i,j) \vee f_{i}\overline{f_{j}}same_{s}(i,j) \vee f_{i}f_{j}same_{sd}(i,j)$$

(2.4)

$same_{ds}(i,j) = 1$  if  $i^{th}$  MOSs' drain is same as  $j^{th}$ 's source.  $same_{sd}(i,j) = 1$  if  $i^{th}$  MOSs' source is same as  $j^{th}$ 's drain.  $same_{s}(i,j) = 1$  if  $i^{th}$  MOSs' source is same as  $j^{th}$ 's source.  $same_{d}(i,j) = 1$  if  $i^{th}$  MOSs' drain is same as  $j^{th}$ 's drain.

$f_i$  is the flip variable of MOS i.  $f_i$  is 0 if source is placed left of drain, 0 otherwise.  $C_n(i,k) = 1$  if N MOS i is placed at  $k^{th}$  column.

Similarly constraint is applied to all P transistors.

**Transistor Folding Constraints:** Smaller transistors resulting from splitting transistors larger than maximum allowable width should be placed together:

$$\bigvee_{k=0}^{W-B} \left[ C_n(i,k) \wedge C_n(i+1,k+1) \wedge \dots C_n(i+B-1,k+B-1) \right] = 1$$

(2.5)

where B is the number of fingers a larger transistor is split into.

Flip of neighboring folded transistors should be opposite to ensure that the fingers share diffusion areas :

$$(f_n(i) \oplus f_n(i+1)) \wedge (f_n(i+1) \oplus f_n(i+2)) \wedge \dots (f_n(i+B-2) \oplus f_n(i+B-1)) = 1$$

(2.6)

Here,  $f_n(i) \oplus f_n(i+1) = 1$  means that the diffusion area between two neighboring fingers of a folding transistor is either source or drain to both of the fingers, that in turn, indicates that the diffusion can be shared for these two fingers. Similar constraint is applies to PMOFETs

as well.

**PSM Constraint:** For all transistors that are not folded, distance between the one's having the same gate connection should be even:

$$Q_{ij}(x_{nip} \oplus x_{njp}) = 1 \tag{2.7}$$

where  $Q_{ij} = 1$  if gate i - j is connected, 0 otherwise.  $x_{nip}/x_{njp}$  is the least significant bit of placement vector of NMOS i/j. Similar constraint is applied for PMOS transistors. This constraint is illustrated by point 1 in Figure 8. It is important to point out that this constraint is not necessary for placement stage of the standard cell since the gate connection can also be made by a metal 1 routing. But if it can be satisfied in placement stage without area cost, it will help increase the routing options of the standard cell.

**Unused Column Constraint:** If  $W < 2^P$ , no transistor can be placed in columns with top  $2^P$  - W bit vectors.

$$(x_n/x_{pi1} \oplus u_{j1}) \vee (x_n/x_{pi2} \oplus u_{j2}) \vee ...(x_n/x_{piP} \oplus u_{jP}) = 1$$

(2.8)

where  $u_{j1}...u_{jP}$  is the unused column bit vector.

#### 3. Routing

This section explains the intra-cell routing. Basically, we need to find available routing tracks for each net that has to be connected through routing. We have followed the routing style from [7]. Let  $P_n, P_p, P_g$  and  $P_v$  be the number of boolean variable for N, P, G and V nets respectively. If  $W_n, W_p, W_g$  be the number of rows in N, P and G region and  $W_v$  the number of columns in G region, then  $P_n = \lceil log W_n \rceil$ ,  $P_p = \lceil log_2 W_p \rceil$ ,  $P_v = \lceil log_2 W_v \rceil$ , and  $P_g = \lceil log W_2(W_g + 2) \rceil$ . A connection between two gate terminals is called a Poly connec-

tion if the net is placed in Over/Under G Region, a Gate Net if in G Region.

**Poly Connection Constraints:** Poly connection between two gate terminals is considered as a single instance. Let  $x_{ij}$  represents the variable that assumes value of 1 if a gate connection i - j is necessary, otherwise 0. Let  $a_{ij}$  be 1 if gate connection i - j uses the G region, otherwise 0.All instances in a G-Net with multiple gate terminals are treated as separate G-Nets. For example in a G-Net with gate terminals i, j and k that need to be connected together.

There should not be redundant connections:

$$x_{ij} \wedge x_{ik} \wedge x_{ik} = 0 \tag{2.9}$$

Terminals i, j and k should be connected together:

$$(x_{ij} \wedge x_{jk}) \vee (x_{ij} \wedge x_{ik}) \vee (x_{ik} \wedge x_{jk}) = 1$$

(2.10)

**Net Overlap Constraints:** Any two nets i, j have overlapping intervals, can not be placed in same row.

$$(n_{i1} \oplus n_{j1}) \lor (n_{i2} \oplus n_{j2}) \dots \lor (n_{ip} \oplus n_{jp}) = 1; i \neq j; I_n(i) \cap I_n(j) \neq \emptyset$$

(2.11)

where  $n_{ip}$  is the  $p^{th}$  significant bit for the track assignment for net i in N region,  $I_n(i)$  is the range of column numbers that net i crosses. For example, a connection for net x has been made from two transistors in column 2 and column 5 respectively, then  $I_n(x) = 2, 3, 4, 5$ . Similar constraints apply for P and G regions.

**VDD/GND Constraints:** VDD connection will block the top metal track and GND connection will block the bottom metal routing track. If a N net has a GND in its interval

$I_n(i)$ , it can not be placed in lowest row in N Region. If a P net has a VDD in its interval  $I_P(i)$ , it can not be placed in highest row in the P region.

$$(n/p_{i1} \oplus L_1) \lor (n/p_{i2} \oplus L_2) \dots \lor (n/p_{ip} \oplus L_p) = 1; VDD/GND \in I_{n/p}(i/p)$$

(2.12)

where  $L_p$  is the  $p^{th}$  significant bit for the highest routing track in P region or the  $p^{th}$  significant bit for the lowest routing track in N region, depending on the n or p constraint used in the above equation.

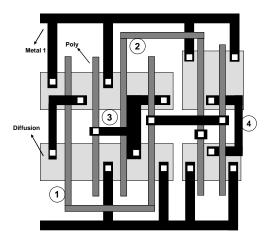

V-Net Pass Constraints: We defined V-net in Figure 7 as a net that has PMOS and NMOS drain connection made vertically by a metal connection. Obviously, a V-net is going to block horizontal metal tracks at the location where the PMOS and NMOS drain connection is made. For this reason, special constraints have to be considered for the V-nets routing to avoid short on different nets. If we assign the vertical drain connection of a V-net to be at a specific column, other V-nets along with all its gate terminals should not take that column assignment to avoid short of the two V-nets. This is illustrated in Figure 8 at point 3 and point 4, two V-nets do not across each other. This constraint is represented by:

$$A_{ij_{k1}} \oplus A_{ij_{k2}} = 0; k1, k2 \in I_{\nu}(i)$$

(2.13)

where  $A_{ij_{k1}}=1$  means the source-drain connection of V-net i is at the left of the column k1 that are spanned by another V-net j.  $I_{\nu}(i)$  is the range of column numbers that V-net i crosses.

For a G-net connection, it should not short with the vertical connection of the V-net drain connection for P and NMOS. A G-Net spans from column i to column j should be

span the column k where a drain connection of a V-net is made. i.e.

$$x_{ij}a_{ij}(G_{ik}\oplus G_{jk})=0; (2.14)$$

where  $G_{ik} = 1$  means column i is at the left of column k.  $a_{ij} = 1$  means that gate connection is done in G-region,  $a_{ij} = 0$  means that gate connection is done with poly routing at the top or bottom of the cell.

Also for a G-net that spans from column i to column j, it should not take the same routing track assignment as the horizontal portion of the V-net l if both of the nets span any same column. i.e.

$$x_{ij}a_{ij}(G_{ik} \oplus G_{jk})\overline{[(g_{ij1} \oplus g_{k1}) \vee ....(g_{ijPg} \oplus g_{kPg})]} = 0; k \in I_{\nu}(l)$$

(2.15)

Similar constraints apply for N nets and P nets.

Connections to gate terminals of two V-Nets if overlap, should not be placed in same row in G-Region. For any V-Net i with gate terminal j should not overlap another V-Net l with gate terminal k:

$$(A_{ik} \oplus A_{jk})\overline{[((g_{ij1} \oplus g_{kl1}) \vee ..(g_{iPg} \oplus g_{klPg}))]} = 0$$

(2.16)

Similar constraints apply in N region and P region as well to avoid short of two V-nets.

**Poly Routing Overlap Constraints:** For two different poly nets, namely poly net m which spans from column i to column j and poly net n which spans from column k and column k can not overlap with the poly connection made at the top or bottom of the cell:

$$x_{ij} \wedge x_{kl} \wedge \overline{a_{ij}} \wedge \overline{a_{kl}} \wedge \overline{[(g_{m1} \oplus g_{n1}) \vee ... (g_{mPg} \oplus g_{nPg})]} = 0; I_{poly}(m) \cap I_{poly}(n) \neq \emptyset$$

(2.17)

where  $g_{mp}$  is the  $p^{th}$  significant bit of the row number in top/bottom regions assigned to poly gate connection net m.  $I_{poly}(m)$  is the range of column numbers that poly net m crosses.

As we showed in Figure 2b, T-shaped poly connection creates a PSM phase error. The constraint to avoid this T-shape poly connection configuration is described as follows: two same poly nets with terminals i - j and k - l, both can not be placed in either over or under region. This constraint can be expressed as:

$$x_{ij} \wedge x_{kl} \wedge \overline{a_{ij}} \wedge \overline{a_{kl}} \wedge \overline{[(g_{ij1} \oplus g_{kl1}) \vee ... (g_{ijPg} \oplus g_{klPg})]} = 0$$

(2.18)

The example of this can be found in Figure 8. The gate connections at point 1 and point 4 in Figure 8 show that one of the gate connection is made with bottom poly routing track but the other connection is made with a metal 1 in G region.

Fig. 8. Layout constraints examples.

**Poly PSM Phase Error Constraint:** If all columns between two poly nets are occupied by transistor gates, the number of poly gates in such interval should be even. This constraint makes sure that there is no phase error generated when poly routing exists at the

top/bottom of the cell. It is further illustrated in Figure 8 as point 1.

$$x_{ij} \wedge x_{kl} \wedge \overline{a_{ij}} \wedge C_{ij} \wedge \overline{(l_{Pg} \oplus r_{Pg})} = 0$$

(2.19)

$C_{ij} = 1$  if all columns between i and j are occupied, 0 otherwise.  $l_{Pg}/r_{Pg}$  are the least significant bits of left/right column of a poly connection.

**Composibility Constraint:** For any two poly connections i - j (i < j) and k - l (k < l), the column numbers of one poly connection should have same least significant bit as other connection if all the intervals are occupied. Satisfying this constraint guarantees that phase assignment at top and bottom of the cell is going to be same, thus achieve Alt-PSM composability. An example of this situation is shown in Figure 8 as point 1 and 2.

$$x_{ij} \wedge \overline{a_{ij}} \wedge x_{kl} \wedge \overline{a_{kl}} \wedge \left[ C_{ik}(l_{pgi} \oplus l_{pgk}) \vee C_{il} \overline{(l_{pgi} \oplus l_{pgl})} \vee C_{jk} \overline{(l_{pgj} \oplus l_{pgk})} \vee C_{jl} (l_{pgj} \oplus l_{pgl}) \right] = 0$$

$$(2.20)$$

**Metal 1 Layer PSM Constraint:** To avoid T-type connections that introduce phase assignment problem in Metal 1 layer, the width of T's top can be increased to make it a non critical feature, thus preventing any phase error. In V-Nets with gate connections, such situations are very likely. To overcome this, if a V-Net has a T connection, the width of its vertical or source-drain connection is increased beyond critical size(see point 3 in Figure 8). To provide enough space and design rule compliance, both columns in vicinity of such V-Nets can not be occupied. At least one column should be empty.

$$\overline{V_{c-1} \wedge V_{c+1}} = 1 \tag{2.21}$$

where  $V_{c-1} = 1$  if the column before V-Net source-drain column is occupied, 0 otherwise.  $V_{c+1} = 1$  if the column after V-Net source-drain is occupied, 0 otherwise. However if V-Net with T connection is placed at column 0, column 1 should be unoccupied and similarly if

in last column, last but one should be empty.

#### 4. SAT Formulation Flow

The flow for generating standard cell with SAT formulation is shown in Figure 9.

## C. Cell Alt-PSM Composability

For complicated standard cells, the placement of the transistor is determined primarily by performance and area. While our previous approach does yield the smallest area for the standard cell design, it does not account for timing tradeoffs of the transistor placement. Thus we will use the following methodology for Alt-PSM compliant and composability: we use the method proposed by [4] to achieve Alt-PSM compliant and then we use the algorithm presented in this section to achieve Alt-PSM composability.

#### 1. Problem Formulation

We start by assuming that all standard cells are free of internal phase errors. It is then straightforward to derive the fact that if we can assign the boundary regions with the same phase for all standard cells, we create a standard cell library that is composable, i.e. putting any two standard cells together will not generate phase errors. Thus the Alt-PSM composability problem is described as follows:

Given standard cell design without phase errors, determine if the design is Alt-PSM composable. If not, find the minimum modification of the design in order to make it composable.

As in previous work of Alt-PSM [9], the relation of b < B holds, where b is the minimum spacing between two features defined by design rules, B is the minimum spacing for features with different phases between them. It is also commonly true that B < 2b.

```

Procedure: PSMPlaceRoute

Input: standard cell schematic netlist

Output: PSM compliant and composable standard

cell layout.

1. W \leftarrow \# \text{ NMOS } (\# \text{ PMOS})

2. Generate and solve CNF for placement constraints

3. While placement is UNSAT{

W \leftarrow W + 1

Generate & solve new CNF for placement.

4. Apply PSM constraint for Placement

5. If (solution is SAT) Retain placement

else

Revert to last satisfiable placement

6. Generate & solve CNF for routing constraints

7. While routing is UNSAT{

If routing not possible at W

W \leftarrow W + 1

Go back to 2

}

```

Fig. 9. PSM aware library cell synthesis algorithm.

Fig. 10. Phase conflict graph.

We construct the phase conflict graph according to [4] in Figure 10. In the graph, each feature is represented by a feature node, the region with 180 degree light is designated by a shifter node, and if space between two features is less than B, i.e. the two features are in phase conflict, there is a conflict node representing this situation. There exists an edge between a feature node and its associated shifter node, the shifter node and the conflict node. Also an edge between a feature node and the conflict node is added if there is no shifter node in that side of the feature. In case one feature is in phase conflict with multiple features, each phase conflict will be represented by a different conflict node and a different shifter node if the conflict occurs at the shifter side of the feature. The work of [4] has proved that this graph is planar. The layout is phase error free if the phase conflict graph is a bi-partite graph [4], i.e., there is no odd cycle in the graph.

Fig. 11. Boundary nodes in phase conflict graph.

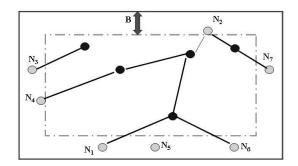

We define *critical boundaries* to be the boundaries of a cell that need the same phase for composability. Critical boundaries can be specified by designers, for a row based design, critical boundaries are the left and right side of the cell borders. In a conflict graph, for every feature node whose location is within a certain distance B to any critical boundary of the cell, we define another type of node - *boundary node*, it is either the feature node if the shifter of the feature node is pointing into the cell, or the shifter node of the feature otherwise. For example, assuming the phase conflict graph looks like Figure 11, if critical boundaries are the four boundaries of the cell, node N1-N7 are boundary nodes. We further define the *odd path* in a graph as a path composed by odd number of edges. For example, the path between N2 and N1 in Figure 11 is an odd path.

We want to point out an obvious observation: we can assign the same phase to all critical boundary *if and only if* there is no odd path existed between any two of the boundary nodes in the phase conflict graph. Another fact is that if there are multiple paths between two boundary nodes, either all of them are odd paths or none of them is an odd path, since there is no odd cycle in a conflict graph for a cell layout without phase error itself. Thus, the problem of cell composability is reduced to:

Given a phase conflict graph of a cell layout without phase errors, determine if odd path between any two boundary nodes exists. If so, determine a minimum change of layout that can remove such odd paths.

#### 2. Algorithm

For every edge in phase conflict graph, we define the *edge weight* as follows: For an edge that has a conflict node incident on it, if we traverse this edge in both directions, we will reach two feature nodes in phase conflict, we define the weight of the edge to be the silicon area penalty if we have to increase the spacing between those two features to remove the phase conflict. For all other edges, the edge weights are infinite.

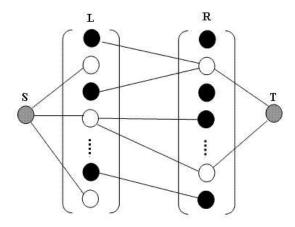

Fig. 12. Phase conflict bipartite graph: empty dots represent boundary nodes, solid dots represent all other nodes.

Since the original cell layout does not have any phase errors, the corresponding phase conflict graph is bi-partite, i.e. we can color the graph with two colors. Then, the nodes can be partitioned into two sets L and R, with all the edges between L and R. For any node x in L and node y in R, if they are connected in the conflict graph, the path from x to y is an odd path. For any two nodes x and y in the same set, the path from x to y can not be an odd path. Hence, the composability problem becomes to find the minimum edge weight cut to separate boundary nodes that belong to different sets. In Figure 12, the empty dots indicate boundary nodes and the solid nodes indicate all other nodes. We use the network flow model to separate the set of boundary nodes in subset L and those in subset R by introducing a source node S and a sink node T. We also add edges between S and all the boundary nodes in subset L and edges between T and all the boundary nodes in subset R, with all the added edges having infinite edge weights We then search for a minimum weight cut of S and T, the result will give us the minimum cut of the boundary nodes in L and R, which is the same as the minimum change of the layout for composability.

The optimality of this algorithm is obvious. If we cut all edges with finite weight, we can separate S from T, which implies that the minimum cut of S and T has to be finite, and

each edge that has been cut has a conflict node incident on it since the weight of the edge is infinite otherwise. Because all the cut that we make are necessary and the weight of the cut is minimized, this algorithm is optimal for the design. Note that the cut could also include an edge that has no boundary node incident on it, but it has to have a conflict node incident on it.

We analyze the complexity of this algorithm as follows: the generation of the conflict graph has the complexity of O(nlogn) as demonstrated in [4], with n being the number of features. The partitioning of the nodes into L and R sets has the complexity of O(n) as each feature needs to be processed only once. We use the Minimum Capacity Cut algorithm [10] as the S-T minimum cut algorithm, the capacity of each edge is the weight of the edge. This minimum cut algorithm takes time  $O(n^3)$ . Therefore, the complexity of our algorithm is  $O(n^3)$ . Since the number of feature in a typical standard cell is fairly small, the running time for our algorithm is quite reasonable.

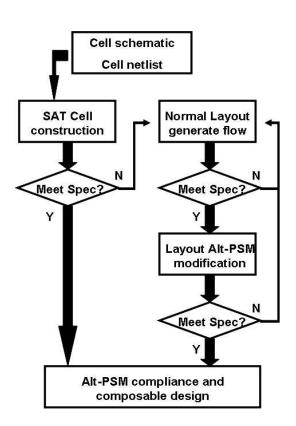

#### D. Standard Cell Library Design Flow

In Figure 13, we propose a standard cell design flow for Alt-PSM compliant and composability. We take the standard cell schematic or netlist and use the Alt-PSM aware cell construction flow to generate the layout of the cell, if the cell meets the performance specification, this is the final design. If not, we go through the normal design flow to generate the layout and try to modify the layout for Alt-PSM purposes, the final design also has to satisfy the performance specification.

Fig. 13. Standard cell library design flow.

# E. Experiments

#### 1. Standard Cell Construction

The constraints for Placement and Routing described above were transformed into SAT formulations and solved using Siege Variant 4 SAT Solver [7]. In additional to its fast run time, Siege SAT solver has the major advantage that its output depends on it's seed. This helps to avoid adding additional clauses during placement stage to suppress an existing placement result in order to get a new one.

Table I. Experimental results for standard cell construction.

| Ckt   | # trs | Pvars | Rvars Cols |   | CPU(s) |

|-------|-------|-------|------------|---|--------|

| and3  | 8     | 24    | 10         | 4 | 0.03   |

| and8  | 16    | 90    | 12         | 9 | 0.73   |

| aoi22 | 10    | 40    | 7          | 6 | 0.05   |

| nd2ab | 8     | 32    | 17         | 5 | 0.32   |

| nor2  | 4     | 48    | 21         | 6 | 0.23   |

| mux2  | 10    | 40    | 23         | 7 | 0.07   |

| nand3 | 6     | 40    | 14         | 5 | 0.12   |

| xor2  | 12    | 48    | 30         | 8 | 0.58   |

| cgi2  | 10    | 40    | 18         | 6 | 0.04   |

| nor5  | 10    | 40    | 3          | 5 | 0.08   |

| nor8  | 18    | 64    | 18         | 8 | 0.53   |

Our formulation has been implemented in 'C++' and experiments were conducted on Linux server with 2GB of RAM. A timeout of 3000s was used in our experiment. Table 1 lists some of the test cases used in our experimentation. The fist column gives the circuit

name, followed by the number of transistors in each circuit, the number of variables for Placement, number of variables for Routing, the resultant width in columns, and the time taken to get a satisfiable result. The number of rows in N/P region are assumed to be 3, for G region 2 and one row each in Over and Under G region. Apart from being of minimum width, the layouts generated by our formulation are PSM Compliant and Composable.

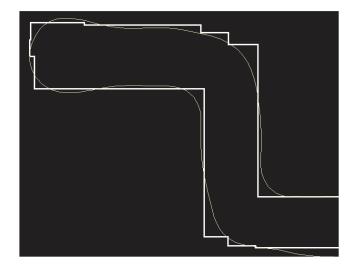

Figure 14 shows a comparison of layouts with and without PSM considerations in placement and routing phases for a 2 input XOR gate that uses 12 transistors. Two T junctions (highlighted by circles) can be noticed in Metal 1 Layer that are not PSM compliant. To avoid any phase conflict, the width of source-drain portion of the two V-Nets needs to increased beyond critical feature size. This is shown in Figure 14(b). Without any increase in area, we generate a PSM clean layout. Figure 15 compare the layouts for a 2 input NOR gate with each transistor split into 3 fingers each. Again T junctions in POLY layer are removed to get a PSM compliant and composable layout.

Fig. 14. (a) XOR gate layout: T joints in Metal 1 layer that pose phase conflict problem. (b) PSM clean layout.

## 2. Layout Modification

We ran the algorithm on a selected set of test cells. All test cells are pre-processed so that they are Alt-PSM compliant before applying our algorithm. This pre-process is done

Fig. 15. (a) 2 Input NOR gate layout with N-P pairs split in 3 fingers each: T joints in Poly. (b) PSM compliant and composable. layout

manually as typical standard cells require only minor changes for Alt-PSM compliance. Table 2 shows the area increment comparison of our algorithm and the method of applying blank area around the cells. We used the minimum poly spacing b=0.16 unit length and phase conflict spacing B=0.32 unit length.

The comparison shows area savings of our approach. For the library cells that will be placed into the design for multiple times, the total area saving for Alt-PSM designs will be significant.

## F. Conclusion

We have proposed a two-way approach to generate Alt-PSM aware standard cell library. Our SAT based methodology results in Alt-PSM clean standard cells with minimum area while our cell modification based methodology generates Alt-PSM clean standard cells with minimum impact on cell performance. We introduced a new Alt-PSM aware standard cell design flow. Using our approach, the generated standard cell library can be used directly in the place and route environment without any concerns of poly layer Alt-PSM phase errors.

Table II. Experimental results for standard cell modification.

| Cell              | #           | Initial            | Area increase                 | Area increase                |

|-------------------|-------------|--------------------|-------------------------------|------------------------------|

|                   | of          | area               | with                          | with blank                   |

|                   | transistors | (um <sup>2</sup> ) | composable                    | area                         |

|                   |             |                    | processing (um <sup>2</sup> ) | insertion (um <sup>2</sup> ) |

| Balanced AND      | 8           | 4.76               | 0.21                          | 1.50                         |

| Divider           | 99          | 46.99              | 3.86                          | 8.03                         |

| Scanable D-Latch  | 54          | 21.42              | 0.041                         | 4.08                         |

| Clock Gating      | 56          | 29.04              | 0.041                         | 5.26                         |

| 2:1 Multiplexer   | 12          | 4.76               | 0.12                          | 1.50                         |

| Boundary Scan Reg | 68          | 34.28              | 0.21                          | 6.06                         |

| Scanable DFF      | 64          | 39.04              | 0.22                          | 6.80                         |

| Average           | 52          | 25.76              | 0.67                          | 4.75                         |

#### **CHAPTER III**

# WIRE SIZING AND SPACING FOR LITHOGRAPHIC PRINTABILITY AND TIMING OPTIMIZATION

The printability problem due to strong diffraction effects poses a serious threat to the progress of VLSI technology. A circuit layout with poor printability implies that it is difficult to make the printed features on wafers follow designed shapes without distortions. The development of Resolution Enhancement Techniques (RET) can alleviate the printability problem but cannot reverse the trend of deterioration. Moreover, over-usage of RET may dramatically increase photo-mask cost and increase the cycle time for volume production. Thus, there is a strong demand to consider the sub-wavelength printability problem in circuit layout designs. However, layout printability optimization should not degrade circuit timing performance. In this chapter, we introduce a wire sizing and spacing method to improve wire printability with minimal adverse impact on interconnect timing performance. A new printability model is proposed to handle partially coherent illuminations. The complex printability and timing optimization problem is solved in a 2-phase approach. The difficulty of the printability optimization due to its multimodal nature is handled with a sensitivity based heuristic. A coupling aware timing driven continuous wire sizing algorithm is also provided. Lithographic simulation results show that our approach can improve the printability in term of EPE (Edge Placement Error) by 20% - 40% without violating timing, wire width and spacing constraints.

# A. Introduction

There are previous works to address DFM issues within design environment. In [3,4], the Alternating PSM compliance is modeled as a graph problem and layout modification algorithms are developed to achieve Alternating PSM compliance with minimum cost change

where the cost can be defined in term of area or timing. Compared with Alternating PSM compliance, the other RET procedures are very difficult to be abstracted into concise models that can be easily embedded in automatic layout algorithms. Recently, the work of [14] circumvents the difficult RET abstraction issue by optimizing interference intensity instead. This is based on the observation that a reduced interference intensity can alleviate the workload of RET and the interference intensity model is relatively easier to be obtained. An OPC friendly maze routing algorithm is proposed in [14] using the interference intensity model. An RET aware routing algorithm based on fast litho simulation is proposed in [16].

In layout printability optimizations, conventional design objectives such as timing performance cannot be ignored since timing performance heavily depends on physical layout in today's interconnect dominated technology [17]. In this chapter, we focus on the wire sizing problem which plays an important role on affecting timing performance and we combine wire sizing and spacing to improve printability of the design. There are many previous works on wire sizing but mostly for timing optimization alone. The work of [17] attempts to minimize a weighted sum of sink delays for a Steiner tree. A sensitivity based wire sizing heuristic is reported in [18]. A dynamic programming based simultaneous buffer insertion and wire sizing algorithm is proposed in [19] to achieve timing-area tradeoff for a Steiner tree. A circuit-wise gate sizing and wire sizing method based on local refinement is developed in [20]. In [21], the circuit-wise simultaneous gate sizing and wire sizing problem is solved optimally using Lagrangian relaxation. A simultaneous wire sizing and spacing algorithm considering coupling capacitance is introduced in [22].