# EXTENSIBLE MICROPROCESSOR WITHOUT INTERLOCKED PIPELINE STAGES (eMIPS), THE RECONFIGURABLE MICROPROCESSOR

A Thesis

by

# RICHARD NEIL PITTMAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

May 2007

Major Subject: Computer Engineering

# EXTENSIBLE MICROPROCESSOR WITHOUT INTERLOCKED PIPELINE STAGES (eMIPS), THE RECONFIGURABLE MICROPROCESSOR

A Thesis

by

# RICHARD NEIL PITTMAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

Approved by:

Chair of Committee, Committee Members,

Head of Department,

Jyh-Charn Liu Duncan M. Walker Norman Guinasso Valerie E. Taylor

May 2007

Major Subject: Computer Engineering

# ABSTRACT

Extensible Microprocessor without Interlocked Pipeline Stages (eMIPS), the Reconfigurable Processor. (May 2007) Richard Neil Pittman, B.S., Texas A&M University Chair of Advisory Committee: Dr. Jyh-Charn Liu

In this thesis we propose to realize the performance benefits of applicationspecific hardware optimizations in a general-purpose, multi-user system environment using a dynamically extensible microprocessor architecture. We have called our dynamically extensible microprocessor design the Extensible Microprocessor without Interlocked Pipeline Stages, or eMIPS.

The eMIPS architecture uses the interaction of fixed and configurable logic available in modern Field Programmable Gate Array (FPGA). This interaction is used to address the limitations of current microprocessor architectures based solely on Application Specific Integrated Circuits (ASIC). These limitations include inflexibility, size, and application specific performance optimization. The eMIPS system allows multiple secure extensions to load dynamically and to plug into the stages of a pipelined central processing unit (CPU) data path, thereby extending the core instruction set of the microprocessor. Extensions can also be used to realize on-chip peripherals, and if area permits, even multiple cores. Extension instructions reduce dramatically the execution time of frequently executed instruction patterns. These new functionalities we have developed can be exploited by patching the binaries of existing applications, without any changes to the compilers.

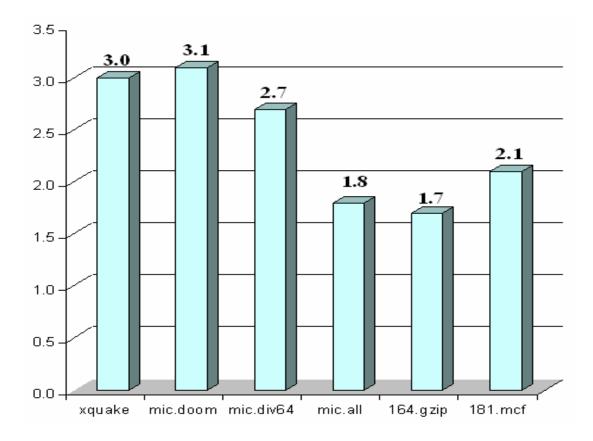

A FPGA based workstation prototype and a flexible simulation system implementating this design demonstrates speedups of 2x-3x on a set of applications that include video games, real-time programs and the SPEC2000 integer benchmarks. eMIPS is the first realized workstation based entirely on a dynamically extensible microprocessor that is safe for general purpose, multi-user applications. By exposing the individual stages of the data path, eMIPS allows optimizations not previously possible. This includes permitting safe and coherent accesses to memory from within an extension, optimizing multi-branched blocks, and throwing precise and restart able exceptions from within an extension.

This work describes a simplified implementation of an extensible microprocessor architecture based on the Microprocessor without Interlocked Pipeline Stages (MIPS) Reduced Instruction Set Computer (RISC) architecture. The concepts and methods contained within this thesis may be applied to other similar architectures. Given this simplified prototype we look forward to propose how this architecture will be expanded as it matures.

# DEDICATION

To my wife

# ACKNOWLEDGEMENTS

I would like to thank my committee chair, Dr. Jyh-Charn (Steve) Liu, for his guidance and support throughout the course of this research and my years in the graduate program. I would also like to thank my committee, Dr. Duncan M. Walker and Dr. Norman Guinasso, for their help with this work.

Thank you to my friends, colleagues, faculty and staff of the Department of Computer Science at Texas A&M University for making the last eight years of my life so memorable. I hope that I gave back at least half of what I received in my interactions with all of you.

I would also like to extend my gratitude to Alessandro Forin of Microsoft Research who provided tremendous support at every stage of this research project. The tools and previous work I had the privilege to build upon, allowed me to explore a problem that might have been overwhelming otherwise.

Finally, thank you to my family for their support through it all. Thank you to my wife for showing me that sometimes when you get stuck, you to take a few steps back. Thank you to my mother for always believing in me. Thank you to my brother and sister for supporting me as only they can. Thank you to my grandmother for always being there when I need to someone to talk to. Thank you to my in-laws for their emotional support for my wife and me.

# NOMENCLATURE

| ALU   | Arithmetic Logic Unit                   |

|-------|-----------------------------------------|

| API   | Application Program Interface           |

| ASIC  | Application Specific Integrated Circuit |

| CAM   | Content Addressable Memory              |

| CPU   | Central Processing Unit                 |

| DPS   | Digital Signal Processor                |

| eMIPS | Extensible MIPS                         |

| GUI   | Graphic User Interface                  |

| FPGA  | Field Programmable Gate Array           |

| FPU   | Floating Point Unit                     |

| HDL   | Hardware Description Language           |

| IC    | Integrated Circuit                      |

| ID    | Instruction Decode                      |

| IDE   | Integrated Drive Electronics            |

| IE    | Instruction Execute                     |

| IF    | Instruction Fetch                       |

| ISA   | Instruction Set Architecture            |

| JTAG  | Joint Test Action Group                 |

| LUT   | Look-up Table                           |

| MA    | Memory Access                           |

| MIC        | Microsoft Invisible Computing                                  |

|------------|----------------------------------------------------------------|

| MIPS       | Microprocessor without Interlocked Pipeline Stages             |

| MMU        | Memory Management Unit                                         |

| OS         | Operating System                                               |

| PC         | Program Counter                                                |

| PIO        | Parrallel Input/Output Interface                               |

| PLI        | Programming Language Interface                                 |

| RAM        | Random Access Memory                                           |

| RI         | Reserved Instruction                                           |

| RISC       | Reduced Instruction Set Computer                               |

| SRAM       | Static Random Access Memory                                    |

| System ACE | System Advanced Configuration Environment                      |

| TBUF       | Tristate Buffer                                                |

| TISA       | Trusted Instruction Set Architecture                           |

| USART      | Universal Serial Synchronous Asynchronous Receiver Transmitter |

| VHDL       | Very High Speed Integrated Circuit Hardware Description        |

|            | Language                                                       |

| WB         | Writeback                                                      |

# **TABLE OF CONTENTS**

| ABSTRACTiii                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEDICATIONv                                                                                                                                                                                                                                    |

| ACKNOWLEDGEMENTSvi                                                                                                                                                                                                                             |

| NOMENCLATURE                                                                                                                                                                                                                                   |

| TABLE OF CONTENTS ix                                                                                                                                                                                                                           |

| LIST OF FIGURES                                                                                                                                                                                                                                |

| 1 INTRODUCTION                                                                                                                                                                                                                                 |

| 2 BACKGROUND                                                                                                                                                                                                                                   |

| 2.1Shortcomings of Modern ASICS52.2MIPS Instruction Set102.3FPGA Architecture122.3.1Partial Reconfiguration of Xilinx FPGA162.3.2System ACE Compact Flash Solution232.3.3eMIPS and the FPGA252.4Profiling and Identification of Basic Blocks27 |

| 3DYNAMICALLY EXTENSIBLE PROCESSORS333.1The 'Classic' RISC CPU333.2The eMIPS Architecture363.3Execution Data Paths: MIPS vs. eMIPS393.4The eMIPS Workstation41                                                                                  |

| 4 IMPLEMENTATION                                                                                                                                                                                                                               |

| 4.1       Challenges       48         4.1.1       Scaling       48         4.1.2       Area Challenges       50         4.1.3       Pipeline Issues       52         4.1.4       Exception Processing       56                                 |

# PAGE

|   | 4.2   | eMIPS System Components           | 57  |

|---|-------|-----------------------------------|-----|

|   | 4.2.1 |                                   |     |

|   | 4.2.2 |                                   |     |

|   | 4.2.3 | 3 Extensions                      | 60  |

|   | 4.2.4 | 4 Pipeline Arbiter                | 67  |

|   | 4.2.5 |                                   |     |

| 5 | TES   | STING AND VERIFICATION            | 75  |

| 6 | RES   | SULTS                             | 83  |

| 7 | FUT   | TURE OF eMIPS                     | 88  |

|   | 7.1   | CAM Based Decoding                |     |

|   | 7.2   | Multiple Instruction Dispatch     |     |

|   | 7.3   | Multi-Core eMIPS Microprocessors  |     |

|   | 7.4   | From eMIPS to eARM, ePowerPC, etc |     |

| 8 | REL   | LATED WORK                        |     |

| 9 | CON   | NCLUSION                          | 103 |

| R | EFERE | ENCES                             | 105 |

| V | TTA   |                                   | 125 |

# **LIST OF FIGURES**

| FIGURE PAG |                                                                     |    |

|------------|---------------------------------------------------------------------|----|

| 1          | Xilinx ML401 Evaluation Board with Virtex 4 LX25                    | 15 |

| 2          | Logical Connections of Signals Across Region Boundary               | 18 |

| 3          | TBUF Based Bus Macro                                                | 19 |

| 4          | LUT Based Bus Macro                                                 | 20 |

| 5          | System ACE File Structure                                           | 24 |

| 6          | A Basic Block Augmented with an Extension Instruction               | 29 |

| 7          | Block Diagram of a Typical Pipelined CPU Architecture               | 34 |

| 8          | Block Diagram of the eMIPS Architecture                             | 37 |

| 9          | The eMIPS Workstation, Concept                                      | 42 |

| 10         | Required Additions to the OS-Managed Protected State, Processes and |    |

|            | Processors                                                          | 43 |

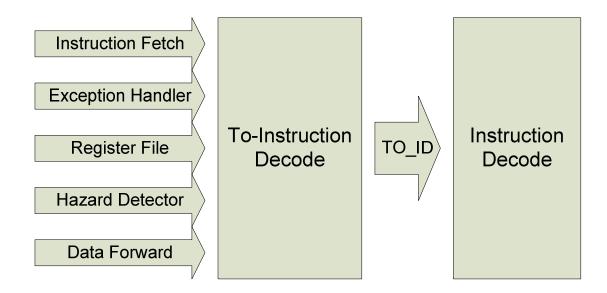

| 11         | Input Coupling Bus Module                                           | 51 |

| 12         | Pipeline Arbitration Hardware                                       | 53 |

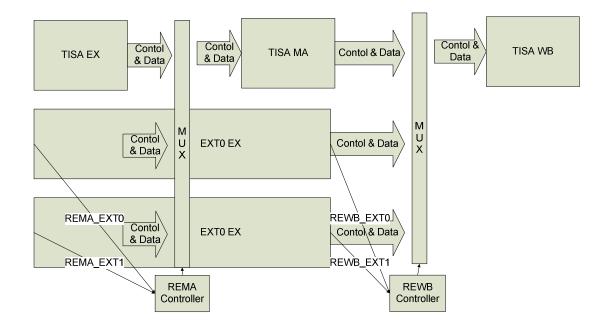

| 13         | Data Path Reentry Hardware                                          | 55 |

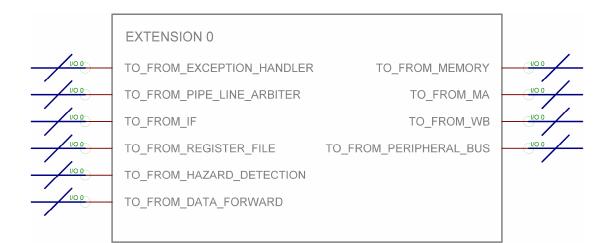

| 14         | eMIPS Extension Interfaces                                          | 61 |

| 15         | Example Memory Map for an eMIPS Microprocessor System               | 70 |

| 16         | Peripheral Types and Associated Tags                                | 72 |

| 17         | Atmel EB63 Evaluation Board                                         | 76 |

| 18         | Peripherals for the ML401 Board                                     | 77 |

# FIGUREPAGE19Testing eMIPS with Giano7820The TestGenerator Environment8021Execution Counts of Individual Basic Blocks in XQuake, on the Xbox3608422Speedups from Extension Instructions8523eMIPS on the Virtex4 XC4LX25 FPGA Device8624Instruction Decoding with a CAM89

## **1 INTRODUCTION**

Most contemporary microprocessors, e.g., MIPS, ARM and PowerPC, etc., are based on a RISC architecture, in which a fixed set of assembly instructions are defined based on the analysis of software benchmarks, costs and hardware technologies. The vast majority of those microprocessors are fabricated as Application Specific Integrated Circuits, or ASIC, for best performance in terms of speed and chip area. In an ASIC microprocessor the instruction set is optimized statistically, therefore the temporal and spatial locality of a particular software application cannot be considered individually. Adding co-processing units to a microprocessor is a common approach to remedy the limitations of an instruction set architecture, but this approach faces the same problem that the coprocessor architecture cannot be easily customized for each software application.

In this thesis we propose an Extensible MIPS architecture, or eMIPS, which allows an application designer to identify heavily executed software regions, or basic block patterns, so that extension instructions and their execution units can be synthesized based on optimized execution flows in those basic blocks. The fixed instruction areas can be implemented using the ASIC technology, but the extension instructions and their execution units are based on configurable logic, so that they can be configured before program run time to optimize the computations.

This thesis follows the style of IEEE Transactions on Computers.

Integrated architectures that support an ASIC processor interfaced with programmable fabrics are available in the embedded marketplace, e.g., the Xilinx Vertex IV and V FX series [ 49 ][ 58 ][ 51 ]. However, the general issue of using instruction extensions in a general-purpose, multi-user application environment is an open issue being addressed in this thesis. Additionally, those architectures do not allow the programmable logic to interact with the individual stages of the pipeline and therefore are only usable for larger-grain optimizations. Unlike the typical instruction compaction techniques which would be targeted for a particular architecture, in eMIPS we aim to identify the computing needs of basic block patterns and leverage the unused instruction space together with the necessary execution units to improve the overall performance. With relatively small additions of configurable logic to existing processor, the extension instruction architecture allows optimization of individual software applications at a fine granularity that cannot be achieved otherwise.

To validate our concepts, the partial reconfiguration feature supported by modern FPGAs (Virtex series from Xilinx Inc. [49][51][58][52] and the Stratix series from Altera [3]) is used for prototype implementation, and the interactive hardware-software development processes for eMIPS are realized using an integrated simulation/development environment called Giano [ 37 ][ 22 ]. The MIPS R4000 processor is chosen as the Trusted Instruction Set Architecture, or TISA, to guarantee that at cold start the microprocessor has a secure and known instruction set and hardware state. The unused operation codes of the R4000 instruction set can be used for the extension instructions.[ 32 ] We designed the instruction decoder, data paths, and the pipeline interlock mechanisms, and implemented them on an FPGA board to validate the eMIPS architecture. The field programmable logic fabrics are partitioned into areas for either dedicated functions, or extension logic. Through the partial reconfiguration technique, only the region that needs to be reconfigured is updated with its configuration file while the TISA operations and other extensions remain unchanged. The Xilinx ML401 Evaluation board has enough peripherals that we could create a complete eMIPS workstation and experiment with a multi-user application environment.

Real software programs are complied into their binary images, their basic block patterns identified and then encoded into Extension instructions to evaluate the performance gains. We used several software systems, ranging from an object oriented real-time operating system for embedded applications, video games, and the SPEC2000 benchmarks. Experimental results show substantial performance gains for both large and small software systems, with overall application speedup factors of 2x-3x using a very small number of extension instructions per application.

The eMIPS system makes the following specific contributions. eMIPS is the first realized workstation based entirely on a dynamically extensible processor that is safe for general purpose, multi-user applications. By exposing the individual stages of the data path, eMIPS allows optimizations not previously possible. This includes permitting safe and coherent accesses to memory from within an extension, optimizing multi-branched blocks, and throwing precise and restart able exceptions from within an extension.

The remainder of this thesis is structured as follows. Section 2 gives an overview of all relevant background information including FPGA architecture and software profiling. The eMIPS architecture is introduced, including software support, in Section 3. Section 4 lays out the challenges and implementation of the eMIPS prototype. The testing and verification processes are discussed in Section 5. Experimental results are reported in Section 6. In Section 7, future avenues available for exploration and development are discussed. Section 8 presents related work and Section 9 concludes the thesis.

# 2 BACKGROUND

The following section provides information supporting the motivation of this thesis and places the claims made within into perspective. Section 2.1 makes the argument that the design paradigms based solely on ASIC technology approach their limits and that eMIPS has the potential to provide continued growth in microprocessor design. The selection of the MIPS instruction set and explanation of RISC pipelines is provided in Section 2.2. An overview of the FPGA technology features utilized in the eMIPS prototype is given in Section 2.3. Finally, Section 2.4 presents a summary of the software profiling on which the eMIPS architecture is based.

### 2.1 SHORTCOMINGS OF MODERN ASICS

Most of the modern available microprocessors implement the Reduced Instruction Set Computer architecture, or RISC, which is based on fixed instruction sets. Many different types of RISC microprocessors populate the market based on these different sets of instructions including, MIPS, ARM and PowerPC to name some of the more popular. These microprocessors are realized in the form of application specific integrated circuits, or ASIC, made up of logic fixed at design time that cannot be altered after the chip fabrication process is complete.

When designing instruction sets, computer engineers attempt to capture all the instructions necessary to cover the largest space of potential applications, while keeping

in mind factors such as size, cost and power. This set of instructions form the blue print for the instruction set architecture, or ISA, to be implemented on the new microprocessor. Despite all efforts, the quest for the 'optimal fixed instruction set architecture' is an impossible one. The space of applications to which the designers apply general purpose microprocessors evolves constantly. In addition, the trends that govern this evolution shift periodically in response to changes in consumer lifestyles and demands. For example, the need to process more audio and video data has led to extensions for all of the available RISC architectures. Therefore, the selection of instructions for a 'general purpose' microprocessor designed to meet the demands of today's market place may be ill equipped to handle the applications of future markets.

We can also argue that the quest for the 'optimal general purpose' microprocessor for today's market does not make sense anymore, especially in the embedded market place. In the embedded market, system designers work within the strictest constraints of size, cost and power. The systems they design apply to a specialized and significantly reduced space of potential applications. In this context, a 'general purpose' microprocessor is inefficient and under-utilized when the majority of applications never use a large subset of the capabilities it provides. For instance, many embedded systems rarely if ever use floating point operations but many 'general purpose' microprocessors include them.

For these applications, a popular solution is to use custom microprocessors with reduced instruction sets but with customized instructions added specifically for the intended application space. This requires redesigning the microprocessor architecture and fabricating custom microprocessors for each of the desired application domains; still they suffer from the inflexibility previously discussed. Therefore, manufacturers cannot offset the cost in design and fabrication of the new custom chip if the market for the given application is not large enough. As demonstrated in this discussion, the problem of this inflexible 'general purpose' microprocessor architecture becomes a severe hindrance. What is needed in the embedded application space and potentially in all areas of microprocessor hardware design is a new technology that can provide for flexibility and customization, allowing the microprocessors to evolve with their target markets at all stages of their life cycles.

The classical microprocessors have grown exponentially in speed and complexity while maintaining relatively constrained costs, in a fashion characterized by Moore's Law. Moore's Law states that the complexity of modern integrated circuits, or IC, with respect to cost doubles every two years. One may observe this trend as the various microprocessor manufacturers; including Intel and AMD, vie for supremacy in the market by delivering increasingly faster and more complex microprocessors. These new microprocessors include new features that augment their capabilities while maintaining fairly level costs over time. As manufacturers reach the limits of the physical constraints of the materials available in terms of speed, conductivity, size and reliability, they also reach the end of this level of growth under current microprocessor design paradigms.

The current trend in the quest for additional execution speed provides additional processing cores in the CPU and to parallelize the execution of as much of the software as possible. This paradigm has potential, but its effectiveness has been limited by the

difficulties involved in parallelizing software that was written for sequential execution, resulting in cumbersome dependencies. These dependencies require changes in the software design paradigms if this approach means to reach its full potential.

The extensions of the eMIPS microprocessor depart from the current techniques for attaining microprocessor execution speedups and flexibility in that to fully realize their benefits, it does not require any changes in software design and it is hidden from developers at the software level. To utilize the extensions, only minimal changes are required at the assembly/binary level. Performing instruction compaction using extensions in eMIPS improves performance by up to three times in most cases when compared to systems of a similar architecture without extensions.

The software design techniques for multi-core systems must become more mature before applications can take full advantage of the large-grain parallelism they offer. When this happens, the eMIPS technology can be leveraged to realize even greater speedups by providing multiple customized processor cores executing in parallel. Each processor core may additionally execute the instruction blocks that it is best suited for. If the chip area devoted to the extensions is abundant we can use the eMIPS architecture to realize a more complex and more adaptable multiprocessing system by allowing extensions to include additional complete data paths, or some other custom processor design. These additional data paths can be loaded on-demand to increase overall throughput. In this way we can convert the eMIPS into a multi-core system when the system is under heavy computational demand. When the system is lightly loaded the extension data paths are disabled to save energy or reconfigured to be used for more specialized purposes.

The eMIPS architecture also addresses the waste associated with including functions in systems where they are never used. The extensions of the eMIPS architecture do not load when the microprocessor powers up. The fixed logic system only includes the minimum functionality (system management, reconfiguration support, load, store, arithmetic and logical functions); the extensions provide any additional functions required by the applications running on the microprocessor. For instance, the floating point, the media or vector co-processors can be loaded only if and when software applications use them. When applications do not require these functions the extensions are not loaded, providing for potentially large power savings because the unused Extension slots may have their clocking resources and power disabled to reduce the power consumption. Area savings are also possible because not all extensions need to be present at all times, as is the case instead for an ASIC implementation. This waste reduction may increase by dynamically loading and unloading not only the co-processors but also the on-chip peripherals that are part of an embedded microcomputer. Rather than including all possible peripherals in the ASIC we can load them on an extensible microprocessor as extensions, again with power and area reductions.

The standard RISC architecture lacks the infrastructure to allow for the kind of flexibility and extensibility possible through the use of eMIPS. This new extensible instruction set computer architecture provides this infrastructure. The FPGA is partitioned into fixed and reconfigurable regions. The fixed logic region constitutes the base functionality of the processor including security sensitive resources such as the system coprocessor and the systems used by the microprocessor to control its configuration. The extensions to the base processor make up the reconfigurable region of the FPGA. The architecture provides the flexibility and adaptability lacking in the RISC architecture.

### 2.2 MIPS INSTRUCTION SET

The Microprocessor without Interlocked Pipeline Stages, or MIPS, instruction set [ 32 ][ 30 ] provides a good example of a modern Reduced Instruction Set Computer instruction set architecture, or RISC ISA, although it is but one of many. There are other RISC ISA available such as the ARM and PowerPC that arguably could be better than the MIPS ISA. Unfortunately, these ISA fall under proprietary controls that removes them from consideration in research projects such as this. The MIPS documentation for the MIPS R16000 is widely available and by residing in the public domain where most other instruction sets are proprietary, it makes MIPS an ideal choice for research in microprocessor architecture and design. The MIPS instruction set architecture like all fixed RISC architectures has experienced growth, modification and expansion in order to keep up with the changing needs of the microprocessor market. The architecture is currently in its ninth generation with the MIPS R16000 [ 32 ]. For this reason, the MIPS R4000 was chosen as the basis of the eMIPS processor. In order to consider a device a MIPS microprocessor, all the basic instructions must be implemented. Software compiled using this base instruction set must run on the eMIPS microprocessor and

existing compilers for high-level programming languages that target the R4000 should remain usable without change.

The MIPS architecture is pipelined to provide improved throughput at higher clock frequencies. One can increase the clocking frequency by breaking the instruction execution within the processor into stages that require less time to execute. Each stage of the pipeline works on different instructions at different times and then passes the instruction to the next stage to continue execution. After the pipeline is full, the microprocessor completes execution of one instruction per clock cycle just like the non-pipelined version except at a much higher clock rate. This architecture results in a net increase in throughput despite the overhead that the architecture experiences with flow control, hazards and exceptions. The time to fill the pipeline is negligible.[ 30 ]

The classic implementation of the RISC pipeline architecture [ 30 ] includes five pipeline stages: Instruction Fetch (IF), Instruction Decode (ID), Instruction Execute (IE), Memory Access (MA) and Writeback (WB). The functions of these stages are as follows:

- Instruction Fetch (IF) Update the program counter, or PC, and fetch the instruction located in memory at the address stored in the PC. [30]

- Instruction Decode (ID) Using wired logic, decode the instruction passed from IF into control signals that control the remainder of the pipeline. Read any data required by the instruction from the general purpose register file. Test branch conditions and calculate the memory location of the next instruction to be executed if a branch is taken. [30]

- Instruction Execute (IE) Using an Arithmetic Logic Unit, or ALU, and other special purpose logic perform operations on data based on the control signals passed from ID. [ 30 ]

- Memory Access (MA) In case of a load or store instruction, the output of IE is used as the memory location to be read from or written to. Otherwise, the output of IE is passed through. [ 30 ]

- Writeback (WB) In the event a register in the general purpose register file is modified by the instruction, the output of MA is written to the desired register.

[ 30 ]

To realize greater throughput at higher frequency, some microprocessor implementations have utilized as many as eight pipeline stages. The deeper the pipeline is the greater the overhead in the event of a branch event, hazards and exceptions on execution. To further offset this overhead, microprocessor designers have developed a variety of features, including branch predictors and speculated execution. These features have highly complex implementations and exist beyond the scope of this project. For this reason, the architecture of the eMIPS microprocessor omits these features and has just the basic five pipeline stages. [ 30 ]

### 2.3 FPGA ARCHITECTURE

The Field Programmable Gate Array, or FPGA, is a digital semiconductor device often used for prototyping. Developers use FPGA in prototyping for their ability to configure or program their electrical interconnects to realize an expansive space of

applications from glue logic to application coprocessors. As the name indicates, developers are free to apply modifications to the design implemented on the FPGA in the field, after deployment. Developers synthesize the configurations from a Hardware Description Language (HDL), like Verilog or Very High Speed Integrated Circuit Hardware Description Language (VHDL), for the targeted FPGA device. Eventually, the configuration file downloads to the chip through an interface such as Joint Test Action Group, or JTAG. This flexibility comes with a price. The configurable logic of the FPGA experiences significantly lower performance, currently clocking at frequencies up to 500 MHz, than the modern ASIC, currently clocking at frequencies over 3 GHz. [49] [51] [58] Despite this limitation, FPGA technology has evolved to the point where developers can implement fixed logic microprocessors with performance levels competitive with their ASIC counterparts in the embedded market. These future microprocessors will have the advantage that they can be dynamically updated after deployment to meet new demands. This approach to microprocessor design leads to a new class of microprocessors termed the "dynamically extensible microprocessor".

Some of the new 'state of the art' FPGA, which have come to market in recent years, have added features that further augment their flexibility and power. First, modern FPGA, such as the Virtex series from Xilinx Inc. [49][51][58] and the Stratix series from Altera Corp.[2][4], have included a feature called 'dynamic partial reconfiguration'. FPGA that include this feature may have their configurations partitioned and later allow individual partitions within the design to continue operations while a new configuration downloads to another partition.[56][55][52][57] FPGA

configuration solutions allow for FPGA to be configured at runtime by other devices or by themselves. An example of one of these solutions is the System ACE Compact Flash solution. This is an IC chip set that provides five interfaces: JTAG to host workstation, JTAG to FPGA, external to a Compact Flash chip, and Control from either the microprocessor or the FPGA. Using these interfaces a system can configure one or multiple FPGA using the JTAG from a workstation or reading a configuration from the compact flash and streaming it to the FPGA on the JTAG chain.[ 54 ]

Using modern FPGAs it is possible to partition the FPGA into sections containing a standard fixed logic processor core with interconnects to blocks termed extensions. These extensions contain customized instructions. To use these extensions the processor core includes functionality that loads, modifies and enables these extensions while the fixed logic continues to function without interruption. In this way, the dynamically extensible processor, using a library of extensions from which it can draw, adapts to the changing application needs in the field. Using the configuration solution with hardware and software support allows for self extension of the system. By using these dynamically reconfigurable FPGA, an "extensible central processing unit" becomes possible. The eMIPS project described in this document argues that such a device is feasible today and proves this thesis by means of an example prototype implementation.

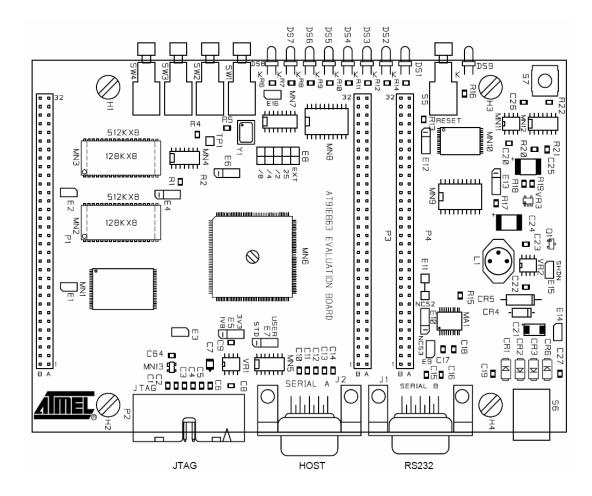

Fig. 1. Xilinx ML401 Evaluation Board with Virtex 4 LX25[51]

The FPGA selected for the development and experimentation of this project is the Xilinx Virtex IV product line. The Virtex series rates among the most powerful FPGA devices in the market in terms of density, feature set and speeds. These FPGA clock commonly at frequencies of 100 MHz but their specifications indicate they could operate at much higher frequencies. The specifications claim 500 MHz. These frequencies fall significantly short of modern ASIC frequencies approaching multiple gigahertzes but the FPGA continue to grow in speed with each new generation. The Virtex IV FPGA comes in three distinguishable types denoted by LX, SX and FX. Each flavor includes a set of special features to allow developers to select an FPGA with the feature set that best fits their application domain. The Virtex IV LX targets logic design applications. For this reason, the Virtex IV LX provides the largest number of logical blocks for implementation. Given the floor planning requirements of partial reconfiguration, having more logic area to work with is preferred. Therefore, the implementation of the eMIPS processor targets the Xilinx ML401 Evaluation board with the Virtex LX25 shown in Fig. 1.[ 51 ][ 58 ][ 49 ][ 60 ]

### 2.3.1 PARTIAL RECONFIGURATION OF XILINX FPGA

Xilinx has supported partial reconfiguration since its Virtex FPGA and that feature continues in the more modern Virtex IV and Spartan III. [56][55][52] Despite the continued support of this feature on their hardware, Xilinx continues to underemphasize this feature in the tool suite, the ISE Foundation. Xilinx recently released the latest release of the ISE, release 8.2i.[49] In the past, hardware designers performed the partial reconfiguration design flow using command line instructions to the tools in the ISE. Xilinx did not integrate the design flow into the graphical user interface, or GUI of the ISE Project Navigator. This results in a large amount of tedious repetitive steps one must perform to run the design flow. Project management and organization becomes crucial, a large set of files is required for each stage of the design flow. In the last year, Xilinx made a greater effort to provide tool support for partial reconfiguration and to make it more accessible to developers. A new tool that Xilinx has developed is called Planahead and attempts to provide improved floor planning utilities and to integrate the partial reconfiguration design flow into a project structure managed by a GUI. Planahead currently has limited availability in an advanced access beta program. [56][55][52]

The smallest reconfigurable unit of the FPGA configuration fabric is called the 'frame'. When partitioning the FPGA into different independently reconfigurable and static regions the boundaries between these regions must coincide with the boundaries of these 'frames'. Multiple frames may be grouped together into a single rectangular region. Regions cannot be smaller than a 'frame'. In the Virtex and Virtex II architectures a frame constituted a column of logic cells called slices that spanned the height of the chip. In the Virtex IV, a column of sixteen slices makes up the 'frame'. In this way, each column of the Virtex IV contains multiple frames. In the LX25, which has 192 rows of slices, each column contains twelve frames. This architecture provides the Virtex IV the advantage of allowing for rectangular regions in the form of tiles on the FPGA configuration fabric as opposed to strictly columns as in the previous architectures.[ 56 ][ 55 ][ 52 ]

Hardware designers must also consider the routing of signals crossing the boundaries of the various regions. Only the region containing the reconfigurable module changes when reconfiguration occurs. The remaining configuration fabric remains unchanged. Therefore any inconsistency from one configuration to the next will result in unpredictable results.

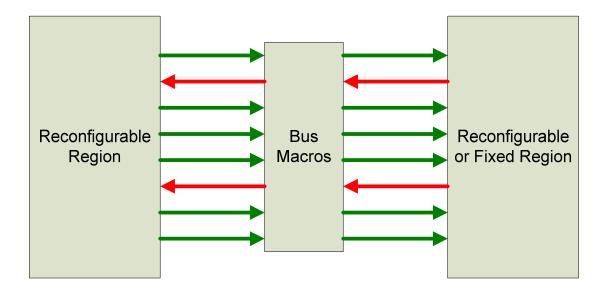

Fig. 2. Logical Connections of Signals Across Region Boundary [ 52 ]

One potential inconsistency can occur when a signal crosses the module boundaries. Consider for instance the case of a signal that crosses the boundary and in one configuration the signal routes through row four but the same signal is routed in row five in another configuration. When the system undergoes reconfiguration, the signal will not line up on the boundary where the reconfiguration occurred, therefore cutting the signal. To prevent this inconsistency we can restrict the routing of such signals to fixed locations along the region boundaries. This is done by passing the signals through a 'bus macro' or a hard pre-routed macro as seen in Fig. 2. The bus macros are positioned on the module boundary and force the routing program to route the signal through a given location in each configuration. For the eMIPS processor, bus-macros are placed between the interfaces of the fixed instruction set logic and the dynamic extensions. [56][55][52]

Fig. 3. TBUF Based Bus Macro [ 56 ]

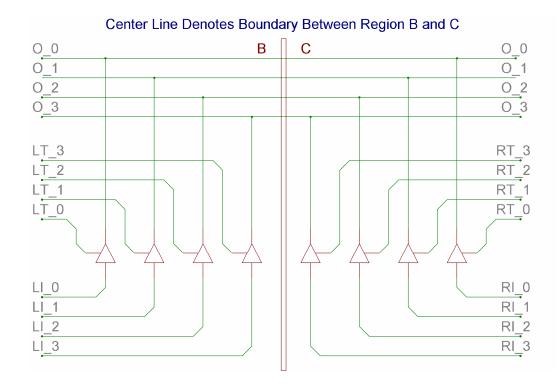

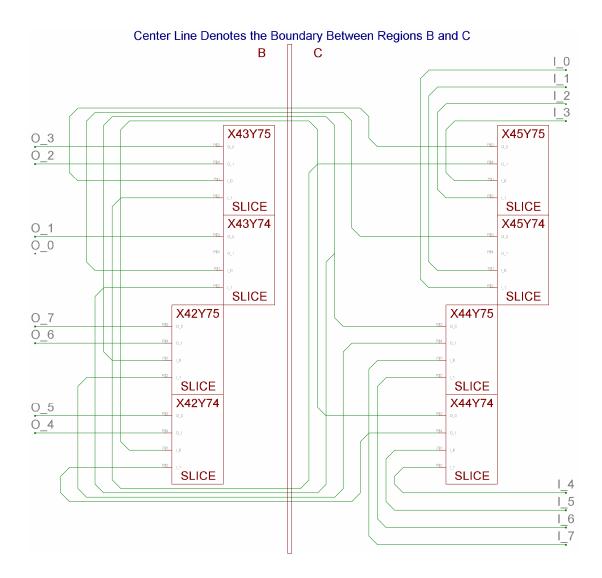

In the Virtex and Virtex II architectures Xilinx provided 'bus macros' based on tri-state buffers, or TBUF. Fig. 3 shows an example of a TBUF-based bus macro used to interface two modules, module B and module C. TBUFs are not included in the Virtex IV and Xilinx provided no alternative 'bus macros' when the device was released. Researchers intending to do partial reconfiguration created 'bus macros' of their own during this time using the Xilinx FPGA Editor.[ 53 ] Most of these bus macros ended up being based on look-up tables, or LUT. Researchers and developers would use the FPGA Editor tool available in the Xilinx ISE to route and generate these hard macros. Fig. 4 shows an example of a LUT-based bus macro.[ 56 ][ 55 ][ 52 ]

Fig. 4. LUT Based Bus Macro [ 52 ]

When Xilinx released Planahead in beta, they also released LUT based 'bus macros' for all their products including the partial reconfiguration feature. Planahead takes the required routing consistency a step further by recording the routing of all fixed logic that passes through reconfigurable regions in a routing database. Planahead incorporates these routing patterns in the place-and-route phase of compilation, so that the reconfigurable regions will maintain consistency. [56][52]

The partial reconfiguration design flow includes four phases as documented by Xilinx. These phases are Design Entry, Initial Budgeting, Active Module, and Final Assembly. Full details can be found in [ 52 ][ 55 ][ 56 ]. The following is a brief description of each phase:

- Design Entry This phase involves setting up the project by targeting the desired FPGA device, decide on design partitioning and performing some design planning. Before Planahead, this phase also included manually setting up the project directory structure. Planahead now handles this in project setup. In large projects including multiple engineers, this phase is usually carried out by the team lead. [ 52 ][ 55 ][ 56 ]

- Initial Budgeting In this phase the design engineers write the top level module and implementation constraint files. The constraint files include information such as pin assignments, area definitions, assignment of modules to areas and clocking constraints. The top level module defines the ports of the design and instantiates

all second level modules and defines their interfaces to each other and to the system ports. This top level should be minimal in its contents. There should be as little logic in this layer as possible and contain only the modules that will be implemented at this layer. Any top level logic that is present goes through place and route and this data is written to the routing database for future use. In most cases, a team lead also carries out this phase. [ 52 ][ 55 ][ 56 ]

- Active Module Design engineers execute this phase of the design flow for each module instantiated in the top level in parallel. The team lead assigns hardware designers to implement the different modules using the interface outlined in the top level written in the previous phase. In the case of reconfigurable modules, hardware designers implement two or more versions of this module. In some cases, designers write module level constraints into the implementation constraint file. The Planahead tool synthesizes each module independently of the rest of the design and performs place and route within the region designated for it while taking the contents of the routing database into account. [ 52 ][ 55 ][ 56 ]

- Final Assembly This is the final phase of the design flow. In this phase, the team lead collects the module implementation of each module from the hardware designers and uses Planahead to integrate them together. The team lead creates a floor plan of the system for each possible configuration or combination of modules. Using these floor plans Planahead completes any additional place and route required and generates configurations files for the desired default

configuration and other configuration files for the reconfigurable regions that change dynamically. [ 52 ][ 55 ][ 56 ]

We used these phases in the eMIPS project. Through Planahead the eMIPS processor was synthesized, floor planned, components placed, signals routed, and configuration files generated.

### 2.3.2 SYSTEM ACE COMPACT FLASH SOLUTION

The System Advanced Configuration Environment, or System ACE [ 54 ], attempts to fill a niche for pre-engineered configuration solutions of multiple FPGA systems. The system applies to the eMIPS microprocessor's need to control and modify its extensible microprocessor architecture. System ACE works through the interaction of four interfaces: JTAG to host workstation, JTAG to FPGA, compact flash and control from a microprocessor or FPGA. Using the host JTAG interface a configuration file can be downloaded manually to the system and used to configure one or multiple FPGA. This feature is excellent for debugging. It allows the developer to download test configurations and run code before including the new configuration in the system. When configuring the system from the host JTAG the System ACE reads the bits stream on the host interface and transfers it to the system JTAG chain it controls. After the configuration design completes and the system is ready for deployment, system controlled configuration can be performed via microcontroller or FPGA control. In the case of a single FPGA system, like the eMIPS microprocessor, the microprocessor interface can be integrated in the FPGA to allow it to control its own configuration. The

compact flash is a portable, permanent storage device that stores the configuration files and inserts into a reader integrated with the System ACE. Using the control interface the FPGA or microprocessor can initiate configuration of the system by selecting a configuration file stored in the compact flash that the System ACE drives on the system JTAG chain. The System ACE also provides an interface similar to Integrated Drive Electronics, or IDE, disk interface commonly found on workstations to allow the controller to read and write to the compact flash. [54]

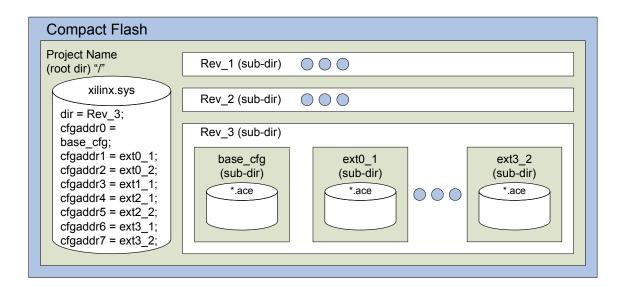

Fig. 5. System ACE File Structure [54]

The System ACE controller interface provides a three bit configuration selection input to allow the controller to select one of eight potential configurations. Note that the compact flash can store more than eight configurations, as illustrated in Fig. 5. The configurations are grouped into sets of no more than eight and placed in directories on the compact flash. In the root directory there exists a file called 'xilinx.sys'. This file tells System ACE which directory containing configuration files should be considered 'active'. The controller can only use configuration files from the 'active' directory. The 'xilinx.sys' file also assigns to each file the numerical designation zero through seven for the configuration selection. To change which set of configurations is considered active, one must change the assignment in the 'xilinx.sys' file. System software can do this dynamically using the IDE interface to the compact flash.[ 54 ]

#### 2.3.3 eMIPS AND THE FPGA

This implementation of the eMIPS microprocessor uses the dynamic partial reconfiguration feature of the Xilinx FPGA to implement the dynamic loading of extensions to the core microprocessor architecture. During the design phase, the core microprocessor architecture resides in the fixed logic region of the FPGA configuration. The configurable partition(s) constitute the area dedicated to the loading of extensions after the processor has begun operation. After design implementation completes, the process produces a binary file containing the default configuration. Later the process generates the binary configuration files used to alter the configuration of the extension slots. The process uses the default configuration and the hardware description of the extension as a starting point. At power up, the default configuration contains the implementation of the core microprocessor architecture and the region allocated for the extensions is empty, or actually contains the minimum logic needed to prevent the

synthesis tool from removing it during optimization. When the microprocessor starts an application that requires an extension, it loads the extension using a JTAG chain provided by the System ACE Compact Flash solution.

The System ACE Compact Flash solution provides the functionality needed for the Xilinx FPGA to control and change its configuration. The System ACE Compact Flash solution includes a JTAG configuration chain capable of dynamically configuring the extensions of the microprocessor. The microprocessor stores the default configuration and the extensions in the compact flash card interfaced to the System ACE chipset. At power up, the System ACE Compact Flash solution reads the default configuration from the compact flash card and streams it on the JTAG chain implementing it on the FPGA. The microprocessor running on the FPGA requests changes to the extension configurations by requesting the loading of a configuration from System ACE through the microprocessor control interface. In this event, System ACE reads the requested extension configuration from the compact flash card. Then like the default configuration at power up, System ACE streams the configuration on the JTAG chain. In the case of a partial reconfiguration, the signals on the JTAG chain only modify the region of the FPGA where the extension is located. The remainder of the FPGA continues to function normally. Consequently, the microprocessor may continue to execute instructions while the configuration process alters the extension configuration. In this way, the microprocessor powers up using the default configuration and modifies its own configuration using the partial extension configurations stored in the compact flash card.

#### 2.4 PROFILING AND IDENTIFICATION OF BASIC BLOCKS

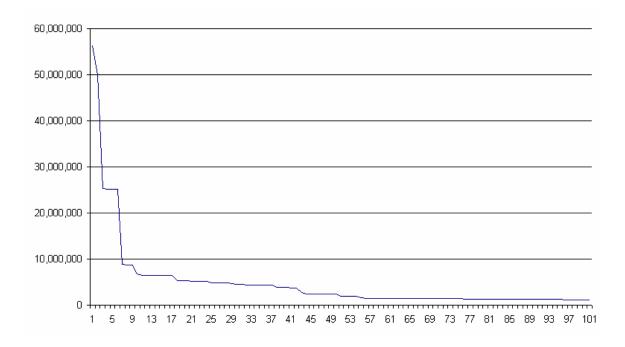

While CPU designers seek generality in their designs, all application programs spend most of their execution time in small sections of the code that make up the executable file image. This observation holds regardless of platform or application, from personal computers to embedded systems to entertainment consoles and devices. Analysis of software execution profiles revealed that in many cases the two to three most executed sequences of code in the applications program account for more than 80% of the total instruction execution count. Based on this observation, if we can somehow optimize the execution of these few select sequences we can attain an overall improvement of the performance of the entire application.[21]

These sequences are termed the "basic blocks" of the software application. Technically, a basic block is a sequence of instructions that ends in a (conditional) branch and is not branched-to anywhere but at the first instruction. In our work, the basic blocks are identified using the tools distributed with Microsoft Giano [ 37 ][ 22 ]. Giano has been used internally at Microsoft Corporation for system verification for some years now. The profiling tool outputs a database of basic block and basic block patterns that manifest in the (set of) application program(s). Roughly speaking, a basic block pattern is the set of all basic blocks that perform the same function but differ in their register assignments or in the embedded constants. Once the database is generated, it is updated by the simulator each time the profiled application is run. Each basic block is uniquely identified by a hash value; there are no duplicates in the database. Each entry also contains counters for the static and dynamic repetition counts of the basic block. The static count indicates how many times the basic block is repeated in the application binary itself, or possibly across more than one binary, according to the user's preference. The dynamic count is maintained by the execution simulator and counts the times the basic block has been actually executed during one or possibly more executions of the application. It is possible to obtain the distribution of dynamic counts against time by check pointing the database with a certain frequency. This can capture the behavior of programs that exhibit "phases" during their execution.[21]

In the practice, the basic block sequences are given to hardware design engineers as specifications. The hardware engineers create a hardware module that implements the semantics of that sequence in the most optimized way possible and in a manner that conforms to the extension interface of the microprocessor. Automatic generation of the extension appears feasible [ 61 ][ 25 ] but it is beyond the scope of this project and we will assume manual generation. The engineers create the design for the extension and generate the FPGA configuration file. The configuration file integrates into the application software package. When the application starts up on a platform that supports it the extension is loaded into a free extension slot, provided one is available. If the platform does not support extensions, or if the security settings of the platform disallow it or if the configuration file is damaged the extension instruction is ignored and the basic block sequence executes normally. The extension interfaces and configuration file generation are discussed in Section 4.2.3.

The implementation of the extension, including its use in the application, is abstracted or hidden at the software level. No change to the higher level compiler is necessary. After the basic block is identified, implemented and encoded into an extension instruction, another tool independent of the compiler augments the executable image. The tool scans the assembly binary image for occurrences of the basic block pattern identified in the profile database. The tool encodes the new extension instruction to match the register assignments and constants, and inserts the new extension instruction immediately before the instance of the basic block pattern. In this way, the software developers are not aware of the hardware acceleration and need not be aware of it. [21]

| ext1 | a0,t1,40   | Extension    |

|------|------------|--------------|

|      |            | Instruction  |

| sll  | t1,t1,1    | Basic Block  |

| srl  | t3,t0,31   | Instructions |

| or   | t1,t1,t3   |              |

| sll  | t0,t0,1    |              |

| srl  | t3,a0,31   |              |

| or   | t0,t0,t3   |              |

| sll  | a0,a0,1    |              |

| srl  | t3,a1,31   |              |

| or   | a0,a0,t3   |              |

| sltu | t3,t1,a2   |              |

| beq  | zero,t3,40 |              |

| sll  | a1,a1,1    |              |

Fig. 6. A Basic Block Augmented with an Extension Instruction

Fig. 6 shows the basic block that was found to be the most frequently executed during testing of the Giano profiling and simulation tool. This basic block was the dynamically most frequent one; it was not the statically most frequent. It was only through actual execution profiling that we found it to be the best candidate for optimization. Simple inspection of the binary code base pointed to a completely different basic block. The first instruction in Fig. 6 is the extension instruction, inserted before the basic block itself. The basic block is part of a software implementation of a 64-bit division. It shifts left by one the 128-bit number contained in the register quad t0-t1-a0-a1, then makes a conditional branch depending on register t1 being greater than register a2. [21]

The extension instructions must conform (at least in part) to the instruction format restrictions of the ISA from which they are derived. In the case of the MIPS ISA, instructions consist of a 32-bit value including an op code, up to two operand registers and a destination register or data immediate. If this single instruction must replace a potentially long sequence of several instructions with as many as two operands per instruction, one destination and data, the question becomes how to encapsulate all that information into a 32 bit instruction. One way is to leverage the relationships that exist between operands, destinations and immediate values. For instance, if the register operand of one instruction is the same as the destination of a previous instruction it only needs to be encoded once. Scratch registers need not be encoded, for each instance in Fig. 6 we can skip the scratch register t3. Notice though that in the implementation of the extension care should be taken to maintain the same semantics as the original sequence and to write the new value to the register file even if nothing else uses it.

When registers differ, the relationships between register numbers can be built into the instruction decoding phase of the extension. For instance, if there are two registers used by different instructions in a sequence but the second is always one away from the first, the extension designers only require one of the register numbers to encode both of them. In Fig. 6 this is the case both for t0-t1 and for a0-a1-a2. It is up to the binary patching tools to verify that these constraints are met. Encoding of destination registers can be performed in the same way. In the case of immediate values, if the value is the same every time the block is executed, then this may be encoded directly into the extension. This is not the case in the example of Fig. 6 and the immediate field must be used, reducing the number of available slots for register numbers by one. [21]

Similar relationships can be identified amongst operand registers to reduce the number of bits (register numbers and the like) needed to encode the required data in the instruction format. If hardware designers cannot reduce the required register numbers to two operands and one destination they could violate the ISA rules and use any of the bits other-than the op code as they see fit. The only penalty is that a disassembler will not be able to provide any meaningful decoding of the extension instruction. Yet another possibility is to further break up the sequence into two or more extension instructions. More information, including the means to automatically identify patterns of instruction sequences and applying such patterns to modify executable binaries is presented in [21].

Using the eMIPS means of execution acceleration requires no change in software design or practice. Modifications are applied, after the software development process is complete, to the finished product. This is in sharp contrast to multi-core parallel systems that require parallelization of the software design at the highest levels to benefit from the hardware feature. Future business models for platform manufacturers that utilize these microprocessors include independent services to profile and augment application software binaries with an extension to fully utilize hardware acceleration. [21]

# **3 DYNAMICALLY EXTENSIBLE PROCESSORS**

The eMIPS processor is a 'dynamically extensible microprocessor' because it is based on a new, extensible architecture. The architecture is extensible because it allows additional logic to interface and interact with the basic data path at all stages of the pipeline. The additional logic, which we term extensions, can be loaded on-chip dynamically during execution by the microprocessor itself. The architecture therefore possesses the unique ability to extend its own ISA at run-time. To explain this more in detail, we will first describe the 'classical' RISC CPU architecture in Section 3.1 and then show where the eMIPS microprocessor architecture departs from it in Section 3.2 and Section 3.3. The overall functioning of a complete system based on an eMIPS microprocessor is then described in Section 3.4.

#### 3.1 THE 'CLASSIC' RISC CPU

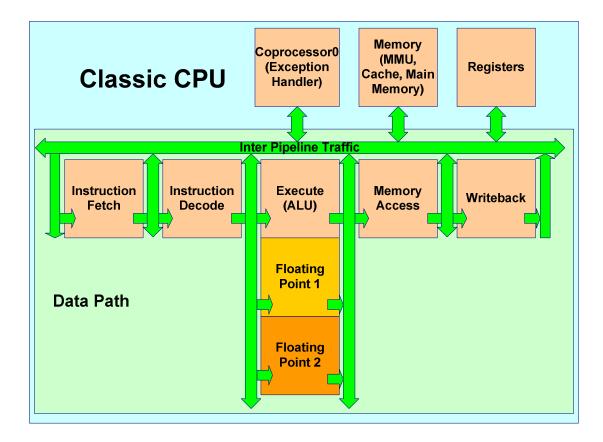

Fig. 7 presents a block diagram of a 'classic' RISC CPU organization, including five pipeline stages, a general purpose register file, a memory interface that includes the interface to the peripherals and a system coprocessor. The five pipeline stages include Instruction Fetch (IF), Instruction Decode (ID), Instruction Execute (IE), Memory Access (MA) and Writeback (WB). The stages are as described in Section 2.2.

Fig. 7. Block Diagram of a Typical Pipelined CPU Architecture

It is important to note the inclusion in this organization of two Floating Point Units, or FPU, depicted as operating in parallel with the IE block. Execution of floating point arithmetic and other coprocessor operations require considerably longer execution times to complete than most integer operations performed by the Arithmetic Logic Unit, or ALU, inside of the IE block. These FPU operate on data in register files that are independent of the general purpose register file used by the rest of the CPU. Independence of the data in these units removes potential conflicts and dependencies, and allows these functional units to execute in parallel with the rest of the CPU. Parallel execution limits the latency effects of these floating point operations to those tasks dependent on their outputs. The presence of two FPU in the diagram denotes the established practice of including multiple instances of functional units on a single CPU to achieve a higher rate of instruction throughput. Several other functional units available in modern high-performance microprocessors have been omitted from this diagram for simplicity. These functional units go beyond the scope of this project and have been omitted from the design.[ 30 ][ 32 ]

Fig. 7 depicts the FPU using different colors to signify that it differs from the other blocks in important ways. In the first place, unlike the other blocks in the diagram the CPU does not require these units to function correctly. Floating point operations could be performed in software, using the ALU, although at a significant execution time penalty. Many applications in embedded systems never use floating point operations and it is fairly common to omit these functional units from simpler microprocessors. The omission results in smaller chips, lower power and reduced costs for the embedded market. In the second place, system software has the capability of disabling access to these functional units when switching between software tasks and of restricting use of these units to particular tasks. When restricting access to the FPU the state of the FPU is preserved across context switches for the benefit of that particular task. This eliminates the swapping of the FPU register file in and out to memory and increases overall system performance. [ 30 ][ 32 ]

## **3.2 THE eMIPS ARCHITECTURE**

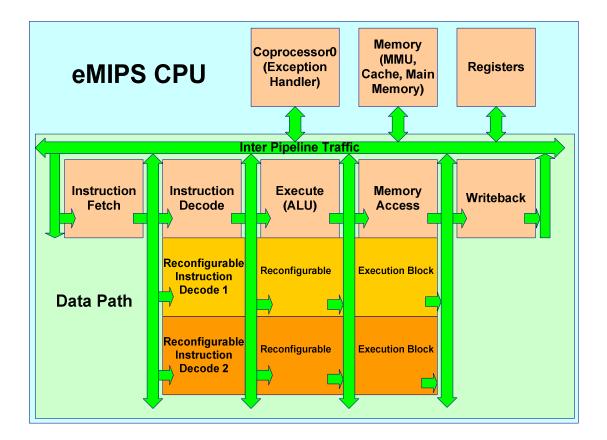

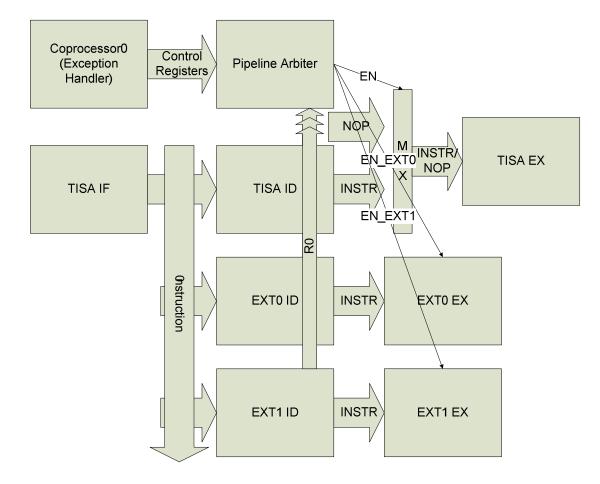

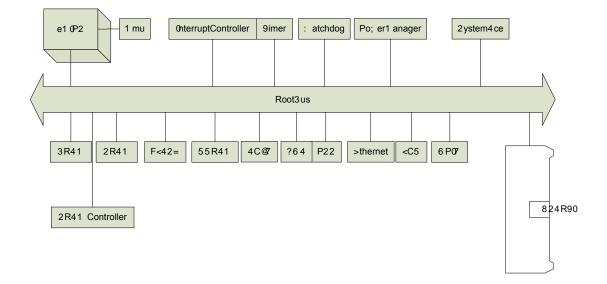

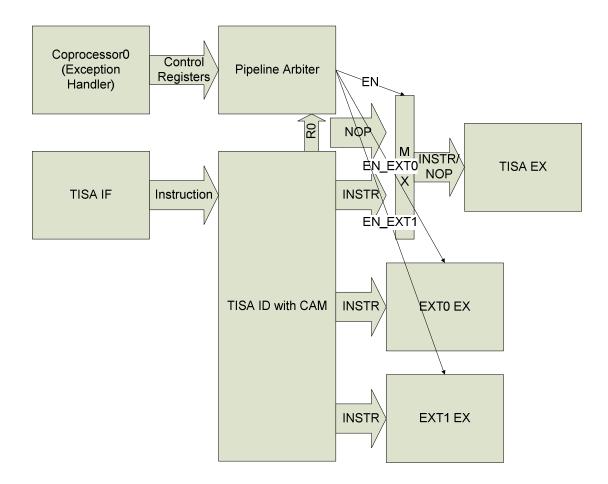

Fig. 8 presents a block diagram of the eMIPS CPU organization. The pipeline stages, general purpose register file and memory interface match those depicted for the 'classic' CPU and are depicted in lighter color in the diagram. These pipeline stages constitute the Trusted ISA or TISA, the core portion of the architecture that is required for initial operation and to provide a level of trust in the functioning of the CPU. These blocks cannot be removed or disabled and must be present at startup of the system. These blocks constitute the fixed partition of the architecture and include all resources that are of a security sensitive nature, such as the system coprocessor. The TISA also includes all the facilities for self-extension, including instructions for loading, unloading, disabling and controlling the unallocated blocks in the microprocessor. At a functional level the pipeline blocks operate similarly to the 'classic' CPU, except their interconnections with respect to each other and other blocks differs. Their implementations differ as well and this will be explained later.

In place of the FPU, Fig. 8 shows two sets of blocks labeled "Extensions". These extensions distinguish the eMIPS architecture from the established RISC architecture from which it is derived. Through the extensions the eMIPS CPU overcomes two major shortcomings of the RISC architecture; inflexibility and inability to evolve with changing needs. Using the partial reconfiguration design flow described in Section 2.3.1, the processor is partitioned into fixed and reconfigurable regions. The TISA is included in the fixed region; the extensions are included in the reconfigurable regions and are interconnected with the TISA by means of the bus macros described in Section 2.3.1. By

implementing different extensions for the reconfigurable regions, it becomes possible to adapt the functionality of the CPU. The CPU may apply these adaptations after deployment, dynamically while the applications continue executing.

Fig. 8. Block Diagram of the eMIPS Architecture

Examples of possible extensions include but are not limited to FPU, Digital Signal Processors, or DSP, encryption coprocessors, vector processors and the

application specific instructions of Section 2.4. Using application execution profiling, engineers identify the extension instructions and implement them as hardware modules synthesized for the target device. More than one extension instruction might be included in a single extension. A successful implementation of an extension instruction runs in fewer clock cycles than the original instruction sequence it replaces. If the instruction is executed a sufficient number of times, even a single clock cycle reduction in execution could significantly improve performance.

Let us compare an extension with the FPU available in the 'classic' architecture. In the first place, in the eMIPS context a FPU is indeed implemented as an extension. The second difference between the FPU and the extension is that the extension is not available as a CPU resource at power up, because extensions are only loaded and unloaded dynamically during execution by the TISA. A third difference is that the blocks of an extension overlap with ID, IE and MA whereas the FPU only overlap with IE. The extension blocks must overlap with ID in order to recognize their instructions. The extension may not require access to memory and therefore can extend into the MA block of the pipeline as well. In this way, if an extension instruction only requires two clock cycles to complete but does not access memory, no stall is necessary and it can pass its outputs to WB to update the necessary registers without creating any pipeline bubbles.

The diagram of Fig. 8 depicts only two extension blocks but more can be included, depending on space and other limitations imposed by the physical chip. If

Moore's Law continues to hold we can project that tens and possibly even hundreds of extensions might be available in future chips.

## 3.3 EXECUTION DATA PATHS: MIPS VS. eMIPS

In the case of the 'classic' RISC CPU architecture, the IF block fetches the instruction indicated by the current value of the program counter, or PC. That instruction passes to the ID block that decodes the instruction into the appropriate control signals for the remainder of the pipeline. If the ID does not recognize the instruction, the ID throws a Reserved Instruction, or RI, exception to the system coprocessor. The ID also calculates the next PC based on the current PC and the instruction being decoded. In the case of a non-branching instruction, the next PC is the current PC plus four. In the case of a branch, the ID tests the branch condition. If the branch condition is true, the next PC is the current PC plus an offset, otherwise it is the same as a standard instruction. In the case of a jump, the next PC is the current PC plus an offset or the content of a register. For all instructions, the ID fetches operand data from the general purpose register file. Using the control signals and data from the ID block, the remainder of the pipeline executes the decoded instruction. In the case of an operation instruction, the IE block modifies the operands fetched by ID using the operation indicated by the instruction decoding. In the case of a load or store instruction, the IE calculates the address to be loaded or written to and passes it to the MA block. Using the address calculated by the IE, the MA loads the contents of that address from memory or modifies it using data read from a register in ID. For operation instructions, the MA block passes the result of IE directly to WB. Finally, if the instruction modifies a register, WB writes the new value of the register to the general purpose register file.

The eMIPS follows a similar execution path for instructions included in the TISA. For instructions not in the TISA, the processor departs from this execution path in the ID phase where the ID blocks of the extensions operate in parallel with the one in the TISA. After the IF block fetches the current instruction from memory, the instruction is sent in parallel to the ID blocks of the TISA and of each extension. Each ID of the extensions attempts to decode the instruction in parallel. If the TISA recognizes the instruction, the execution path is the same as the previous example of the 'classic' CPU. In the case that none of the ID blocks recognize the instruction, a RI exception will be throw to the system coprocessor like the 'classic' CPU model.

If one of the extensions recognizes the instruction, its ID requests to take over execution of the instruction. The arbitration logic sends a NOP to the TISA pipeline stages and to those of the other extensions. The arbitration logic also passes control of the read ports of the general purpose register file to the ID of the extension that recognized the instruction. The ID of the extension that recognized the instruction finishes decoding the instruction and passes the operand data from the register file and control signals to the IE block of the extension. In general, the instruction decoding may be implemented in logic but for a more flexible design a content addressable memory, or CAM, is preferred. The IE block of the extension may span the IE and MA block of the TISA, allowing it an additional clock cycle of execution time to complete the designated operation. When operations require additional clock cycles an IE of the extension sends a signal to the hazard detection unit of the TISA to stall the processor until the extension has completed operations. The IE of the extension completes execution of its implemented instruction and passes the results to the WB block of the TISA. Other issues exist in arbitrating between the TISA and the extensions, as well as controlling this more complex data path. These issues will be identified and addressed in Section 4.

#### 3.4 THE eMIPS WORKSTATION

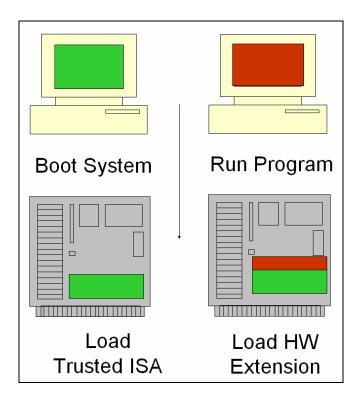

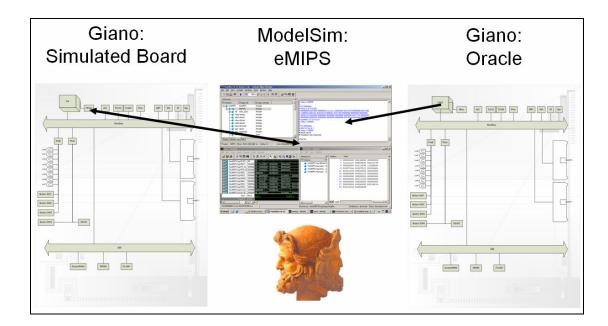

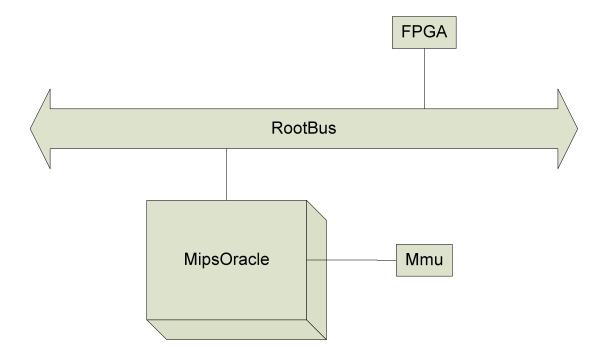

Fig. 9 illustrates the two ways in which a workstation based on the eMIPS microprocessor differs from a regular workstation. In the first place, at power up time the TISA is loaded in the FPGA if it is implemented as the default configuration. If it is implemented in fixed logic this step is not necessary. If the step is necessary, a secure component verifies the validity and integrity of the configuration file and loads it on the FPGA [9]. In the second place, when a user starts a program that uses an extension the Operating System, or OS, asks the TISA to verify and load the extension configuration file and enables it for that particular process. Other processes can later share the extension. For those extensions that are in fact peripherals the corresponding software entity is a device driver. A multi-core extension is loaded directly by the OS, automatically as appropriate.

Fig. 9. The eMIPS Workstation, Concept

When the execution comes to a basic block accelerated by an extension, the extension will execute its optimized extension instruction and skip the block that the instruction replaced. If for any reason the extension is not available the extension instruction is ignored and the software executes normally. To accomplish this evolution of the eMIPS microprocessor within a system some software support is required. Some of this software support was described in Section 2.4, namely the software profiling tools used to identify the basic blocks to be implemented as extensions. Additional changes to the OS software are required to control the loading of extensions and to activate them when they are available.

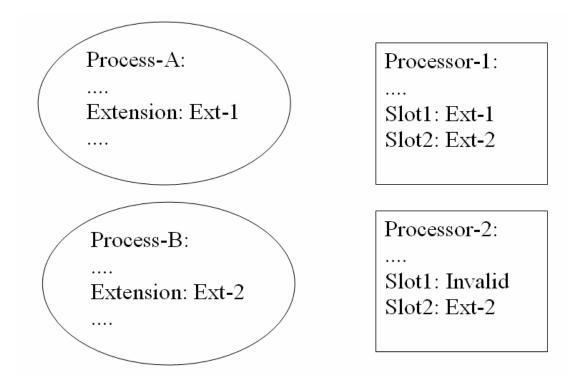

The OS is notified of the extension requirements at application loading time, either explicitly by invoking some Application Program Interface (API), or implicitly by information contained in the executable file image. The OS keeps track of the extension information on a per-process and per-processor basis, as part of its protected state. Fig. 10 depicts the additional state that is required for a dual-multiprocessor using the extensible processor of Fig. 8. Notice that it is necessary to keep track of which extension is loaded in which slot of each available processor, as is depicted in Fig. 10. This knowledge is necessary to load extensions from different application programs at the same time.

Fig. 10. Required Additions to the OS-Managed Protected State, Processes and Processors

The OS loader is the module responsible for providing the extension data to the OS, at application launch time. The loader can be used to help sharing extensions among applications. Every extension instruction is defined by the binary patching tool using op codes that all start at some value and progress in the same manner. This leads with certainty to collisions between op codes among independently developed extensions. What the loader can do instead is to modify the op codes in a newly loaded image such that they minimize the conflict with other previously loaded images. Fig. 10 shows the effects of this optimization. Because Process-A and Process-B use different op codes they could both be scheduled on Processor-1 without incurring any management trap, and Process-B can be scheduled on both processors. If we try to schedule Process-1 on Processor-2 we will instead incur a trap.

An extensible CPU has only a limited number of slots for currently-loaded extensions. The actual number could be as small as depicted in Fig. 8 or much larger, but it will always be finite. The OS is the arbiter that manages this limited resource on behalf of the application program(s), sharing it in an efficient manner. This management problem is similar to the problem of handling a FPU and the state left in it by multiple application programs. Well known algorithms can be applied here, with one crucial difference. In the FPU case execution cannot proceed unless the coprocessor is made available because there is state left in it and only the FPU is capable of executing the floating-point instructions. In the case of extensions, we are subject to neither of these constraints. In the first place, the application state is held in the general purpose registers and not in a special unit, unless the extension provides extra register state, which is a special case similar to the floating-point case. Notice that the extension configuration file is not changeable and does not need to be preserved across context switches. Secondly, the code of the original basic block is still available; therefore the OS has the option of skipping the extension instructions and simply falling-through to the original code. This is the reason why we require the extensible microprocessor to leave it to software to decide whether to trap or not on an extension instruction.

Having the option to continue execution "without the coprocessor" opens the door to new and more elaborate software management algorithms, some ideas are as follows. The operating system could exclusively assign the resource to the application that is observed to make the most use of it or is selected by a human user; and/or disable all extensions on interrupts, assuming that interrupt service routines will not make use of them, or to guarantee predictable response times; and/or load as many extensions as there are available slots and fall-back to the non optimized basic blocks otherwise; and/or use a least-recently-used algorithm to handle what is effectively a cache of extension data.

Executable images that use extensions can potentially pose a security threat to the guest OS. A certification authority, such as the OS vendor must sign such images to attest to their safety. If the extension uses the technique described in Fig. 6 there is no security threat because the semantic of the extension instruction is the same as the block of instructions it replaces. Nonetheless, certification is still required to prove that the extension configuration file does indeed match the intended semantics.

## **4 IMPLEMENTATION**

One way to realize the eMIPS processor is to start from an existing data path implementation and to modify it as indicated in Section 3.3. Xilinx and other FPGA manufacturers provide examples of so called "soft-core" microprocessors, which are also easily retarget able to different devices. Unfortunately, implementing the interconnections between the individual pipeline stages of the eMIPS microprocessor data path and the extensions requires access to the inputs and outputs of each pipeline stage. Due to the proprietary nature of soft-core microprocessors used in FPGA system designs this is not readily available. For this reason, it becomes necessary to implement a full MIPS data path from scratch to provide these needed connections for the TISA.