## INSTRUMENTATION FOR PARALLEL MAGNETIC RESONANCE IMAGING

A Dissertation

by

# DAVID GERALD BROWN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2005

Major Subject: Electrical Engineering

## INSTRUMENTATION FOR PARALLEL MAGNETIC RESONANCE IMAGING

### A Dissertation

by

### DAVID GERALD BROWN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Steven M. Wright Committee Members, Robert D. Nevels

Andrew K. Chan Gerard L. Cote

Head of Department, Costas N. Georghiades

December 2005

Major Subject: Electrical Engineering

#### **ABSTRACT**

Instrumentation for Parallel Magnetic Resonance Imaging. (December 2005)

David Gerald Brown, B.S., Texas A&M University

Chair of Advisory Committee: Dr. Steven M. Wright

Parallel magnetic resonance (MR) imaging may be used to increase either the throughput or the speed of the MR imaging experiment. As such, parallel imaging may be accomplished either through a "parallelization" of the MR experiment, or by the use of arrays of sensors. In parallelization, multiple MR scanners (or multiple sensors) are used to collect images from different samples simultaneously. This allows for an increase in the throughput, not the inherent speed, of the MR experiment. Parallel imaging with arrays of sensor coils, on the other hand, makes use of the spatial localization properties of the sensors in an imaging array to allow a reduction in the number of phase encodes required in acquiring an image. This reduced phase-encoding requirement permits an increase in the overall imaging speed by a factor up to the number of sensors in the imaging array. The focus of this dissertation has been the development of cost-effective instrumentation that would enable advances in the state of the art of parallel MR imaging.

First, a low-cost desktop MR scanner was developed (< \$13,000) for imaging small samples (2.54 cm fields-of view) at low magnetic field strengths (< 0.25 T). The performance of the prototype was verified through bench-top measurements and phantom imaging. The prototype transceiver has demonstrated an SNR (signal-to-noise

ratio) comparable to that of a commercial MR system. This scanner could make parallelization of the MR experiment a practical reality, at least in the areas of small animal research and education.

A 64-channel receiver for parallel MR imaging with arrays of sensors was also developed. The receiver prototype was characterized through both bench-top tests and phantom imaging. The parallel receiver is capable of simultaneous reception of up to sixty-four, 1 MHz bandwidth MR signals, at imaging frequencies from 63 to 200 MHz, with an SNR performance (on each channel) comparable to that of a single-channel commercial MR receiver. The prototype should enable investigation into the speed increases obtainable from imaging with large arrays of sensors and has already been used to develop a new parallel imaging technique known as single echo acquisition (SEA) imaging.

# **DEDICATION**

This work is dedicated to my loving wife, Laura, and our son, Thomas.

#### **ACKNOWLEDGMENTS**

The author wishes to thank the many persons and agencies who have helped to make this work possible. Among these are faculty advisors, colleagues, corporations, funding agencies, and family. There is too little room to mention everyone's contributions in detail here, but the most significant have been highlighted in the paragraphs below.

First among these contributors is Dr. Steven M. Wright of the Department of Electrical Engineering at Texas A&M University. Dr. Wright served as the chair of the author's doctoral committee and was his principal advisor. Without his advice, support, and the equipment/ facilities which he provided at the Magnetic Resonance Systems Lab (MRSL), it would have been impossible to conduct the research described in these pages.

Another invaluable resource has been Dr. Jay Porter of the Department of Engineering Technology at Texas A&M University. Dr. Porter provided his expertise in LabVIEW programming and a great deal of his own time to develop the control software for the desktop MR scanner. In addition, Dr. Porter generously provided the services of several of his students in the fabrication of the active shim set that was used on the desktop imaging system's magnet.

The author also wishes to thank his many colleagues at the MRSL who have assisted him during the course of this research. In particular, the author wishes to acknowledge David Spence for all of his help in the initial development of the desktop MR imaging system. Mr. Spence was responsible for developing the gradient amplifier system and was always available as a sounding board in the initial design process. Likewise, the

author wishes to thank Jason Payne, Hyokwon Nam, Dan Spence, Krishna Kurpad, Ed Jeter, Emilio Esparza-Coss, and Jorge Rosas, who helped in the repetitive (and often tedious) process of assembling the prototype 64-channel parallel receiver system.

IGC, Inc. is also gratefully acknowledged for its generous donation of a 0.16 T, whole body, permanent magnet. The IGC magnet was used as a testbed for the development of RF coils, gradient coils, and shims sets during the desktop MR imaging project.

Next, the author wishes to thank the State of Texas Higher Education Coordinating Board (grant no. 000512-0189-1997) for its support. From the spring of 1998 to the spring of 2001, this grant provided much of the funding required to develop the low-cost desktop MR imaging system.

The author also wishes to thank the Department of the Army and its National Medical Technology Testbed agency (Dept. of the Army DAMD17-97-2-7016) for its support. From the spring of 2001 to the winter of 2002, this grant provided funding for the development of the 64-channel parallel receiver prototype.

Last, but not least, the author wishes to thank his wife and family for their unending support, extensive patience, and unwavering belief in his ability to complete the work undertaken in this dissertation.

# **TABLE OF CONTENTS**

|         |                                                                                                                                                                                                                                                  | Page        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| ABSTR.  | ACT                                                                                                                                                                                                                                              | iii         |

| DEDICA  | TION                                                                                                                                                                                                                                             | v           |

| ACKNO   | WLEDGMENTS                                                                                                                                                                                                                                       | vi          |

| TABLE   | OF CONTENTS                                                                                                                                                                                                                                      | viii        |

| LIST OF | TABLES                                                                                                                                                                                                                                           | xii         |

| LIST OF | FIGURES                                                                                                                                                                                                                                          | xiii        |

| СНАРТІ  | ER                                                                                                                                                                                                                                               |             |

| I       | INTRODUCTION                                                                                                                                                                                                                                     | 1           |

|         | I.1 Problem Statement I.1.1 Parallelization of the MR Experiment I.1.2 Array Imaging Techniques                                                                                                                                                  | 2           |

|         | I.2 Research Objectives I.2.1 Aim 1: Build a Low-Cost Desktop MR Scanner I.2.2 Aim 2: Design a Digital MR Receiver I.2.3 Aim 3: Implement a 64-Channel Parallel MR Receiver I.2.4 Aim 4: Characterize the Performance of the 64-Channel Receiver | 7<br>8<br>8 |

|         | I.3 Dissertation Organization                                                                                                                                                                                                                    | 8           |

| II      | BACKGROUND THEORY                                                                                                                                                                                                                                | 11          |

|         | II.1 NMR Theory                                                                                                                                                                                                                                  | 12<br>12    |

|         | II.2 MR Imaging Basics                                                                                                                                                                                                                           |             |

|         | II.2.1 Encoding Spatial Information in the NMR SignalII.2.2 Pulse Sequences                                                                                                                                                                      |             |

| CHAPTI | ER                                                      | Page |

|--------|---------------------------------------------------------|------|

|        | II.2.3 Received Signal                                  | 21   |

|        | II.2.4 Image Reconstruction                             | 22   |

|        | II.2.5 Image Resolution                                 | 22   |

|        | II.2.6 Relaxation Processes and Steady-State Transverse |      |

|        | Magnetization                                           |      |

|        | II.2.7 Signal-to-Noise Ratio for the MR Signal          | 24   |

|        | II.3 MR Receiver Theory                                 | 25   |

|        | II.3.1 Nyquist Criterion for Sampled Signals            | 26   |

|        | II.3.2 MR Signal Detection                              |      |

|        | II.3.3 Demodulation Methods                             | 27   |

|        | II.3.4 Quadrature versus Single Phase Detection         |      |

|        | II.3.5 Single-Channel Receiver Architectures for MRI    |      |

|        | II.3.6 Undersampling Issues for the Digital Receiver    |      |

|        | II.3.7 Receiver Architectures for Parallel MR Imaging   | 50   |

|        | II.4 MR Receiver Performance Metrics                    |      |

|        | II.4.1 Noise Figure                                     |      |

|        | II.4.2 Dynamic Range                                    |      |

|        | II.4.3 Image SNR                                        |      |

|        | II.4.4 Interchannel Isolation                           |      |

|        | II.4.5 Channel-to-Channel Gain Variation                | 65   |

|        | II.5 Summary                                            | 65   |

| III    | A LOW-COST DESKTOP MR SCANNER                           | 66   |

|        | III.1 System Implementation                             | 66   |

|        | III.1.1 System Requirements                             | 66   |

|        | III.1.2 System Design                                   | 73   |

|        | III.2 System Evaluation                                 | 113  |

|        | III.2.1 Performance Summary                             | 113  |

|        | III.2.2 System Cost                                     | 114  |

|        | III.2.3 SNR Comparison                                  |      |

|        | III.2.4 2D Imaging                                      |      |

|        | III.2.5 3D Imaging                                      | 119  |

|        | III.3 Summary                                           | 125  |

| IV     | A SCALABLE. SINGLE-CHANNEL DIGITAL MR RECEIVER          | 126  |

| CHAPT | ER                                                      | Page |

|-------|---------------------------------------------------------|------|

|       | IV.1 System Design Methods                              | 126  |

|       | IV.1.1 System Requirements                              |      |

|       | IV.1.2 System Design                                    |      |

|       | IV.1.3 Design Verification                              |      |

|       | IV.2 Summary                                            | 154  |

| V     | DESIGN OF THE 64-CHANNEL PARALLEL MR RECEIVER           | 155  |

|       | V.1 64-Channel Parallel Receiver System Requirements    | 155  |

|       | V.2 64-Channel Parallel Receiver Design                 | 156  |

|       | V.2.1 MR Scanner Interface                              |      |

|       | V.2.2 64-Channel Preamplifier                           |      |

|       | V.2.3 Main Receiver                                     |      |

|       | V.2.4 Acquisition Control Computer                      |      |

|       | V.3 Summary                                             | 166  |

| VI    | PERFORMANCE CHARACTERIZATION OF THE 64-CHANNEI RECEIVER |      |

|       | RECEIVER                                                | 107  |

|       | VI.1 Design Verification                                | 167  |

|       | VI.1.1 Channel Bandwidth                                |      |

|       | VI.1.2 Operating Frequency Range                        |      |

|       | VI.1.3 Noise Figure                                     |      |

|       | VI.1.4 Dynamic Range                                    |      |

|       | VI.1.5 Interchannel Isolation                           | 185  |

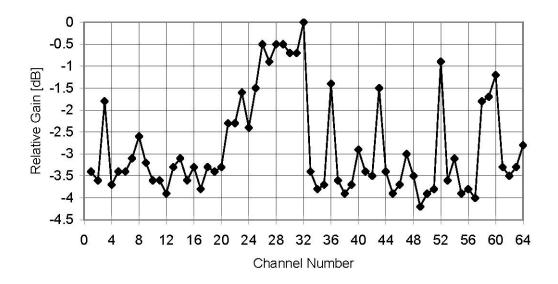

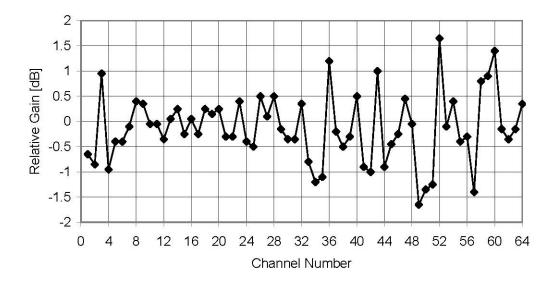

|       | VI.1.6 Channel- to-Channel Gain Variation               | 189  |

|       | VI.1.7 System Cost                                      | 191  |

|       | VI.2 Summary                                            | 193  |

| VII   | DIGITIZER SYNCHRONIZATION TECHNIQUES FOR                |      |

|       | CORRECTION OF THE PHASE JITTER ARTIFACT                 |      |

|       | IN MR RECEIVERS                                         | 195  |

|       | VII.1 The Phase Jitter Problem                          | 195  |

|       | VII.2 Oversampling                                      | 200  |

|       | VII.2.1 Oversampling Theory                             |      |

|       | VII 2 2 Oversampling Limitations                        | 203  |

| CHAPTE | CHAPTER                                                       |     |

|--------|---------------------------------------------------------------|-----|

|        | VII.3 Fourier Time-Shifting                                   | 204 |

|        | VII.3.1 Fourier Time-Shifting Theory                          |     |

|        | VII.3.2 Acquisition Trigger Integration Circuit               |     |

|        | VII.3.3 Fourier Time-Shifting Algorithm                       | 213 |

|        | VII.3.4 Fourier Time-Shifting Synchronization on the 64-Chann |     |

|        | Receiver                                                      |     |

|        | VII.3.5 Limitations of the Fourier Time-Shifting Technique    | 219 |

|        | VII.4 Synchronous Clock Synthesis                             | 219 |

|        | VII.4.1 Clock Synthesis Theory                                |     |

|        | VII.4.2 Digitizer Synchronization on the 64-Channel Receiver  |     |

|        | via Clock Synthesis                                           | 221 |

|        | VII.4.3 Clock Synthesis Limitations                           |     |

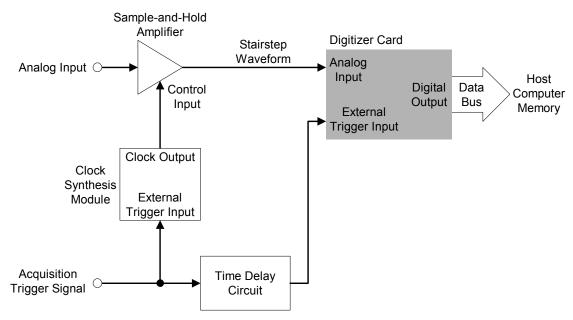

|        | VII.5 Pre-Sampling                                            | 224 |

|        | VII.5.1 Pre-Sampling Theory                                   |     |

|        | VII.5.2 Pre-Sampling Limitations                              |     |

| VIII   | CONCLUSION AND FUTURE WORK                                    | 232 |

|        | VIII.1 Conclusions                                            | 232 |

|        | VIII.1.1 Desktop MR Imaging System                            |     |

|        | VIII.1.2 64-Channel Parallel MR Receiver System               |     |

|        | VIII.2 Future Work                                            | 236 |

|        | VIII.2.1 Desktop MR System                                    |     |

|        | VIII.2.2 64-Channel Parallel MR Receiver System               |     |

|        | VIII.3 Summary                                                | 254 |

| REFERE | NCES                                                          | 255 |

| VITA   |                                                               | 260 |

# LIST OF TABLES

| ΓΑΒLΕ |                                                                                                         | Page |

|-------|---------------------------------------------------------------------------------------------------------|------|

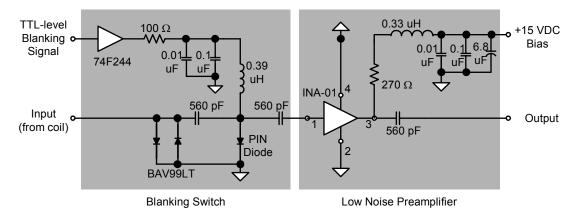

| Ι     | Active PIN Diode Blanking Switch Performance<br>Summary at 6.75 MHz                                     | 95   |

| II    | Active PIN Diode Blanking Switch Performance<br>Summary at 9.15 MHz                                     | 96   |

| III   | Desktop MR System Cost Analysis                                                                         | 114  |

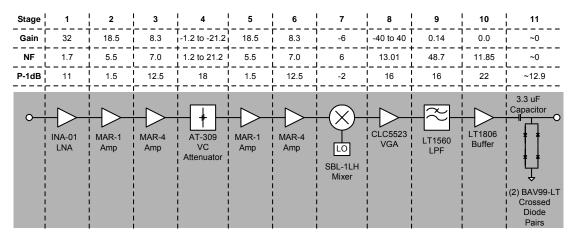

| IV    | Gain, Noise Figure, and Output 1 dB Compression Point Values for the Single-Channel Receiver Components | 146  |

| V     | Average Interchannel Isolation Data for the 4-Channel RF to IF Submodules                               | 189  |

| VI    | 64-Channel Prototype Receiver Operating Frequency Limiting Components                                   | 242  |

# LIST OF FIGURES

| FIGU | RE                                                                                                                                       | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1    | An example of a 2D Fourier encoded pulse sequence for MR imaging                                                                         | 20   |

| 2    | Block diagram for an ideal analog mixer with an output bandpass filter                                                                   | 28   |

| 3    | Undersampling of a bandpass signal                                                                                                       | 31   |

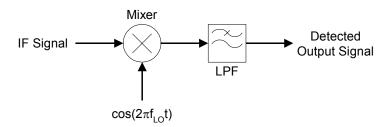

| 4    | Single phase sensitve detection architecture                                                                                             | 31   |

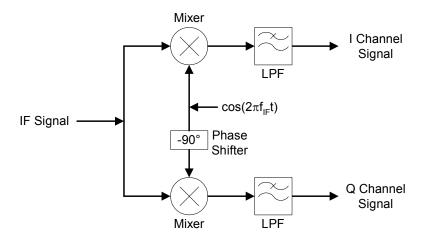

| 5    | Quadrature phase sensitive detector architecture                                                                                         | 31   |

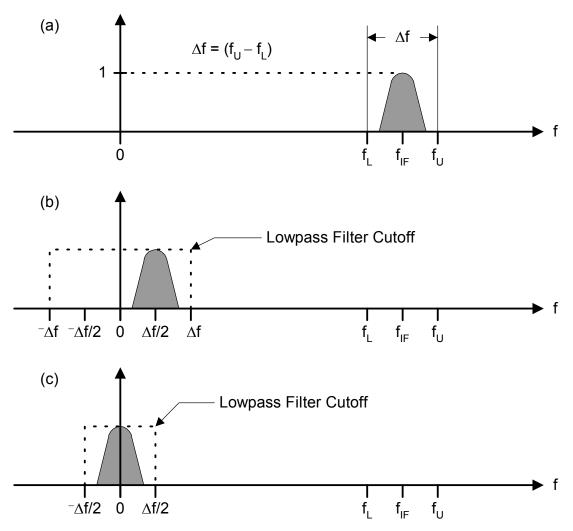

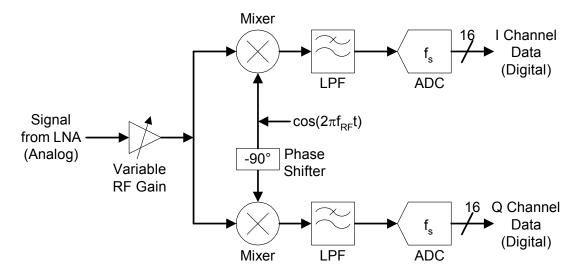

| 6    | Frequency domain comparison of single phase and quadrature phase sensitive detection of a hypothetical, IF frequency, MR signal          | 32   |

| 7    | Block diagram for a direct conversion analog receiver.                                                                                   | 35   |

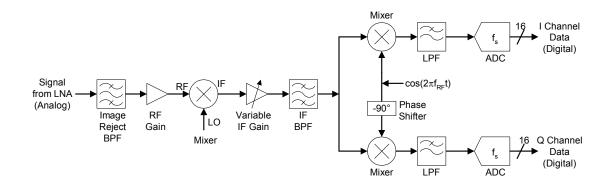

| 8    | Block diagram for a multiple conversion analog receiver                                                                                  | 40   |

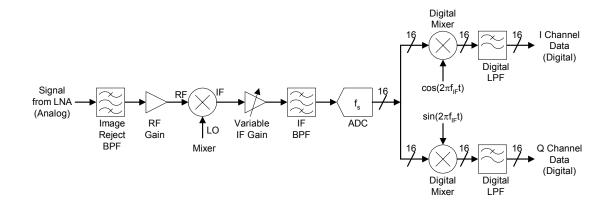

| 9    | Block diagram for a single conversion digital receiver.                                                                                  | 43   |

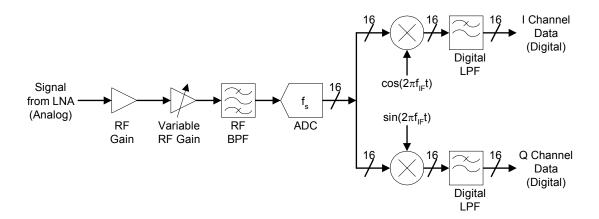

| 10   | Block diagram for a direct digital receiver.                                                                                             | 45   |

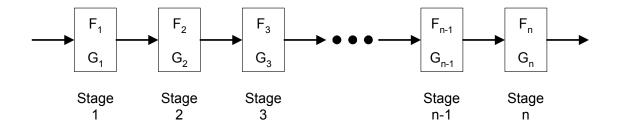

| 11   | Noise figure parameters for an n-stage cascaded system.                                                                                  | 54   |

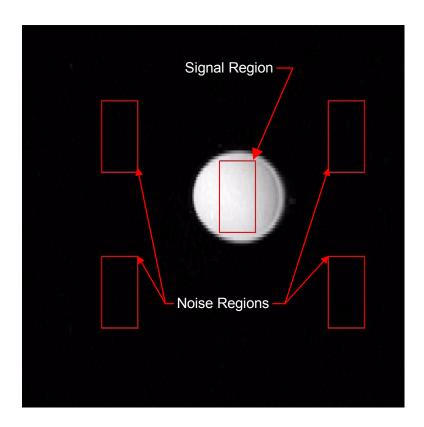

| 12   | Example of the location of signal and noise averaging regions for the calculation of image SNR on an image of a cylindrical test phantom | 64   |

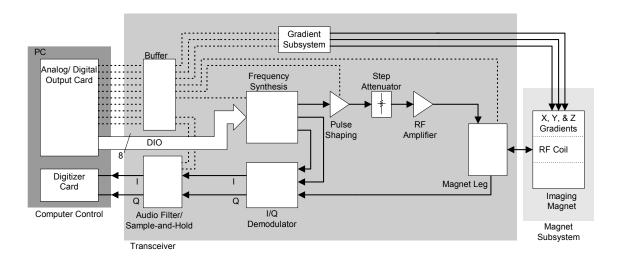

| 13   | Block diagram of the desktop MRI system                                                                                                  | 74   |

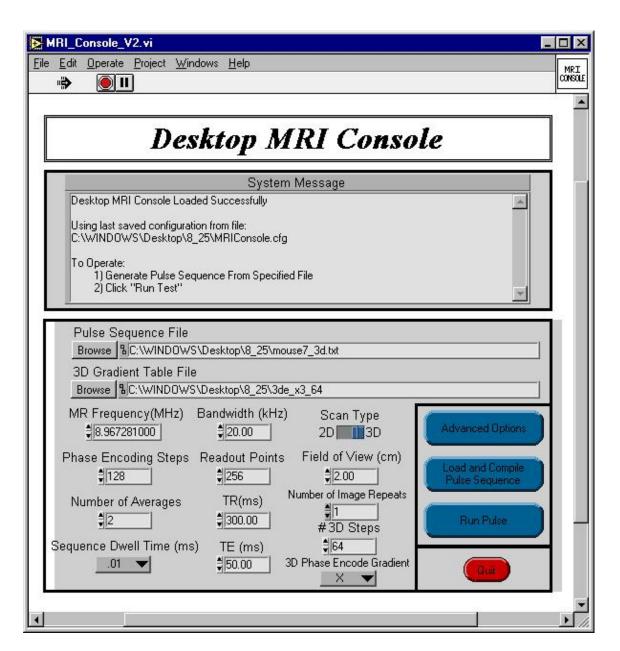

| 14   | Main MR control console window                                                                                                           | 77   |

| 15   | Typical pulse sequence file                                                                                                              | 79   |

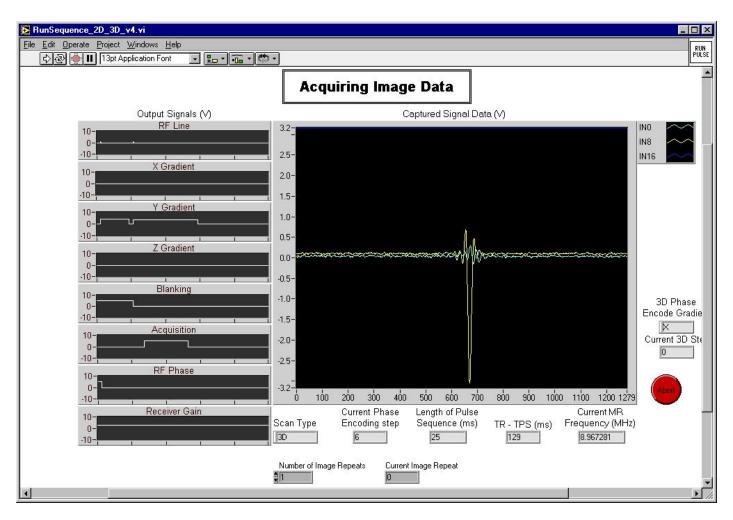

| 16   | Image acquisition window.                                                                                                                | 80   |

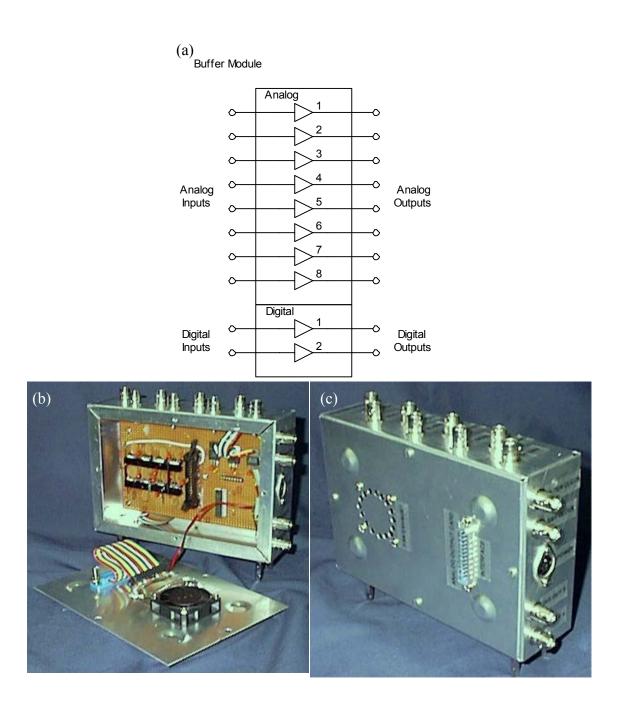

| 17   | Analog and digital buffer module                                                                                                         | 82   |

| 18   | Pictures of the frequency synthesis and RF pulse shaping modules                                                                         | 83   |

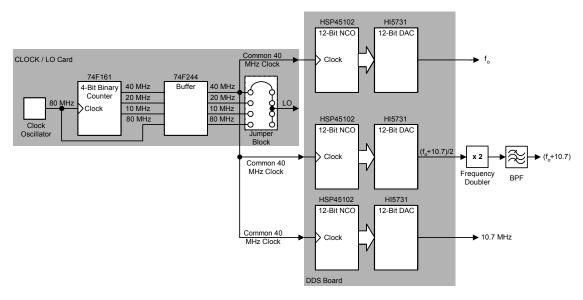

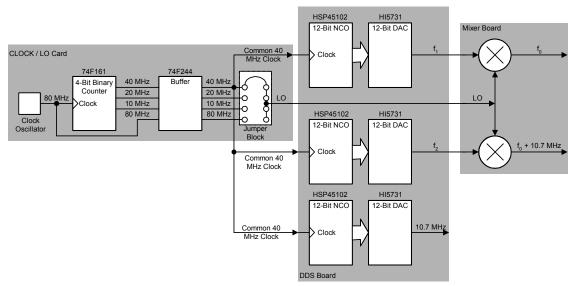

| 19   | Frequency synthesis module schematic                                                                                                     | 85   |

| FIGU | RE                                                                                                | Page |

|------|---------------------------------------------------------------------------------------------------|------|

| 20   | Frequency synthesis module schematic with the external mixing module                              | 86   |

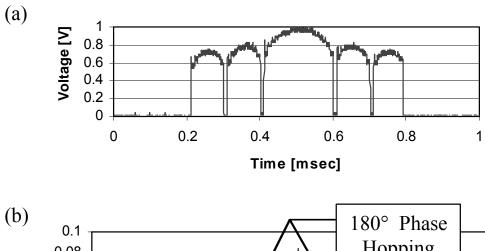

| 21   | Performance of the pulse shaping module as measured with a Tektronix TDS-220 digital oscilloscope | 90   |

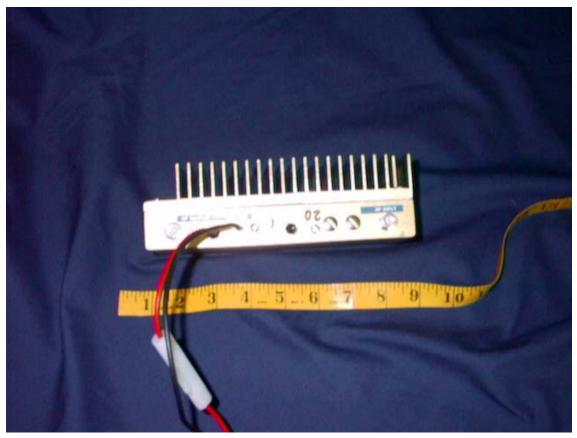

| 22   | RF power amplifier from Henry Radio                                                               | 91   |

| 23   | Magnet leg module                                                                                 | 92   |

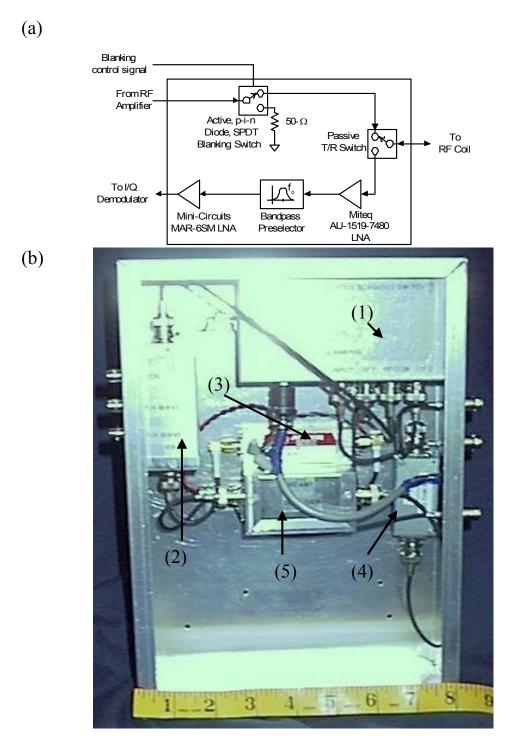

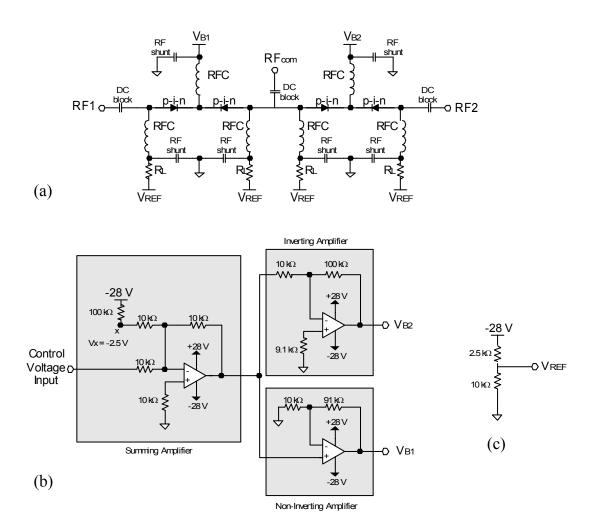

| 24   | PIN diode blanking switch circuit diagrams                                                        | 94   |

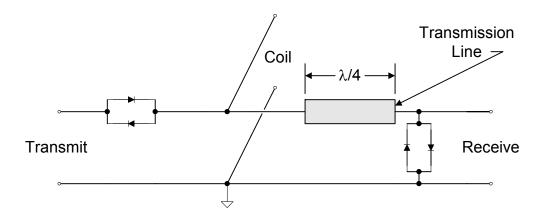

| 25   | Passive quarter-wavelength transmit/ receive (TR) switch                                          | 97   |

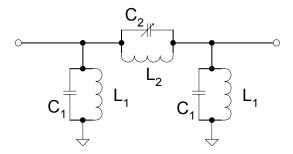

| 26   | Bandpass preselect filter schematic                                                               | 99   |

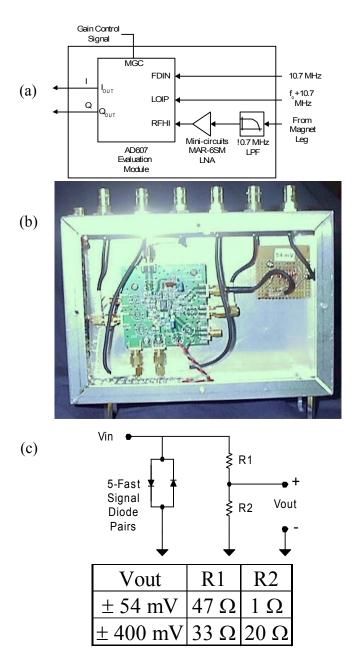

| 27   | I/Q demodulation block                                                                            | 100  |

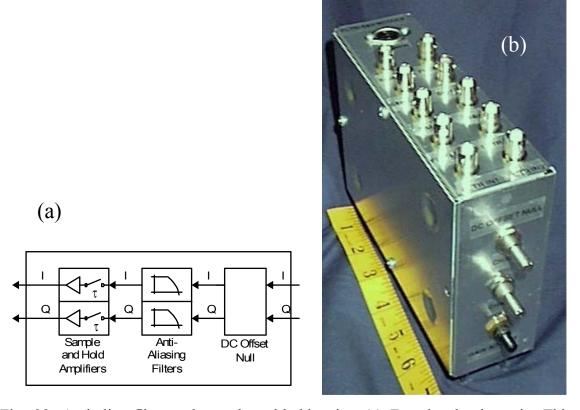

| 28   | Anti-alias filter and sample-and-hold unit                                                        | 103  |

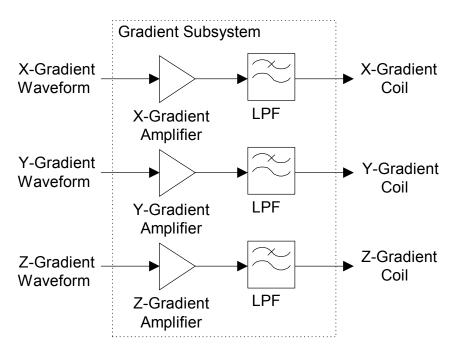

| 29   | Gradient subsystem block diagram                                                                  | 106  |

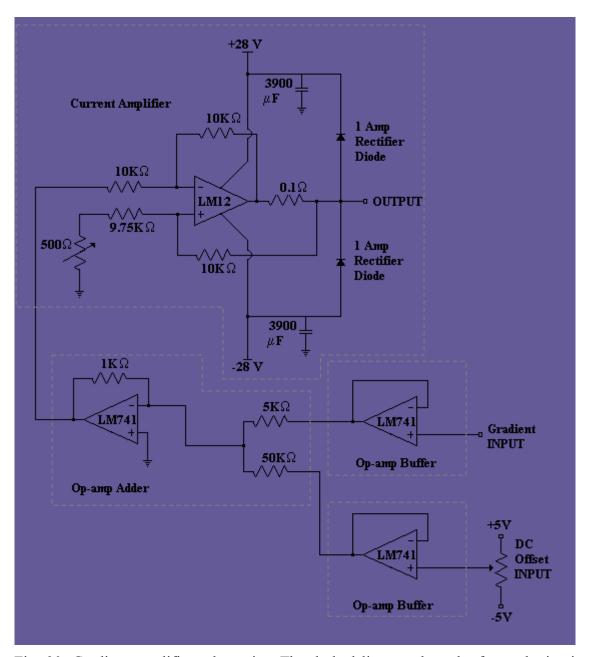

| 30   | Gradient amplifier schematic                                                                      | 107  |

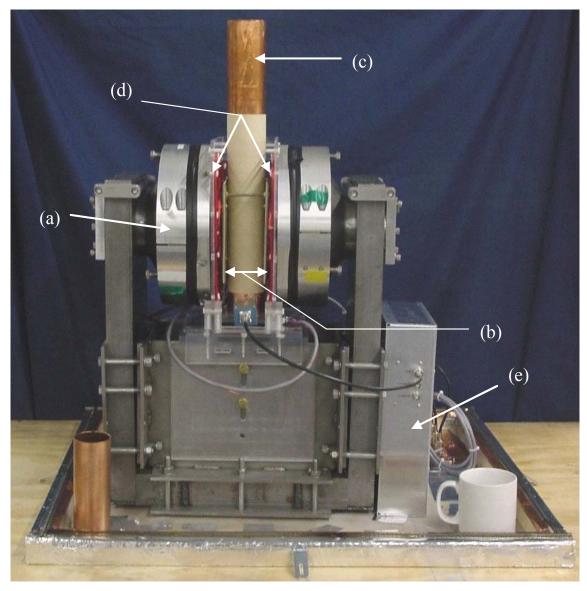

| 31   | Desktop MR scanner magnet subsystem                                                               | 108  |

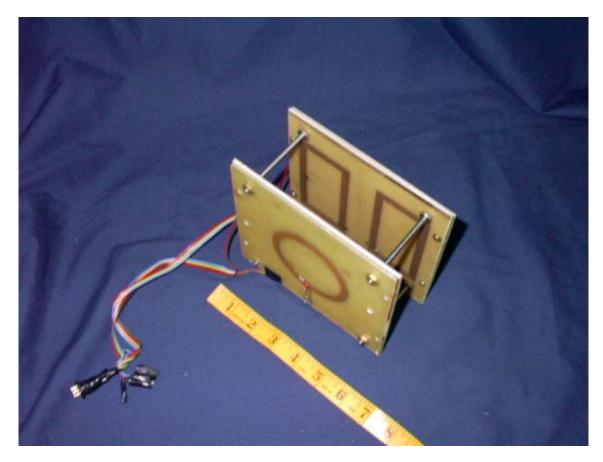

| 32   | Gradient coil set                                                                                 | 111  |

| 33   | RF imaging coil and shield assembly                                                               | 112  |

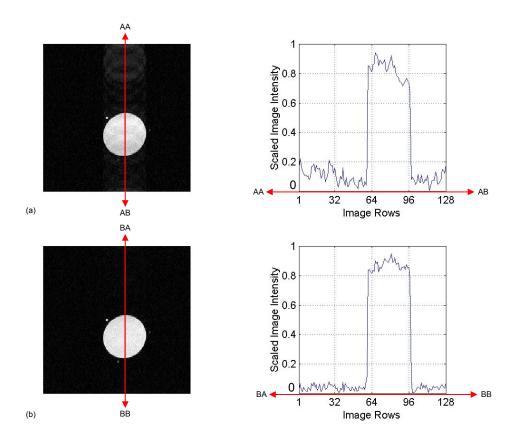

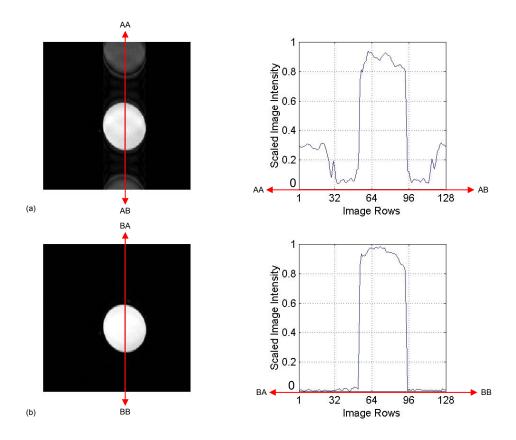

| 34   | SNR comparison images between the desktop MR system and a Varian SIS-85 commercial scanner        | 116  |

| 35   | 2D slice select image results from the desktop MR scanner                                         | 118  |

| 36   | 3D imaging phantom constructed for use on the desktop MR system                                   | 120  |

| 37   | 3D spin echo images of the test phantom                                                           | 120  |

| 38   | Thirty central slices out of 64 axial slices from the 3D spin echo data set                       | 121  |

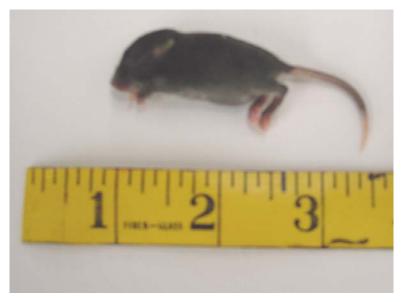

| 39   | A "fresh frozen" juvenile mouse phantom                                                           | 123  |

| FIGURE |                                                                                                                                                                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

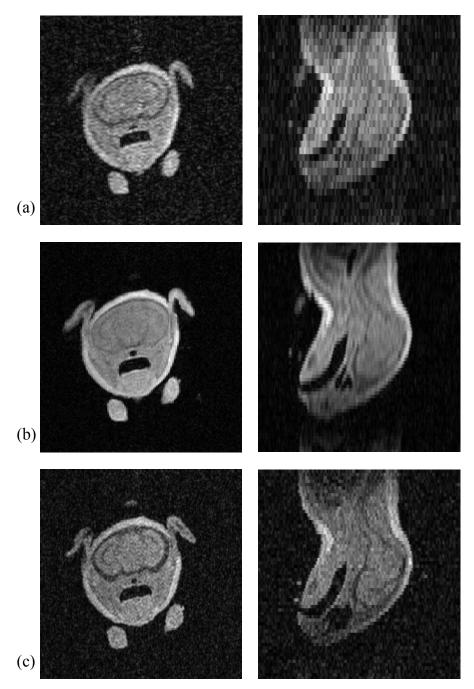

| 40     | 3D spin echo (TE/TR = 9.4 ms/ 300 ms) image data sets of a "fresh frozen" juvenile mouse acquired from the desktop MR system                                                                                                                | 124  |

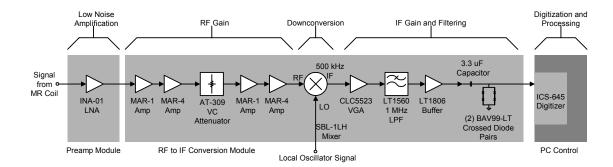

| 41     | Schematic for the single-channel receiver                                                                                                                                                                                                   | 133  |

| 42     | Low-noise preamplifier circuit                                                                                                                                                                                                              | 135  |

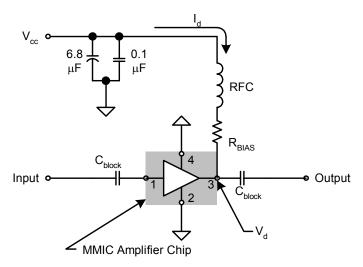

| 43     | Standard connection schematic for MMIC amplifier chips                                                                                                                                                                                      | 137  |

| 44     | Gain, noise figure, and output 1 dB compression points for each stage of the single-channel receiver prototype prior to the digitizer                                                                                                       | 145  |

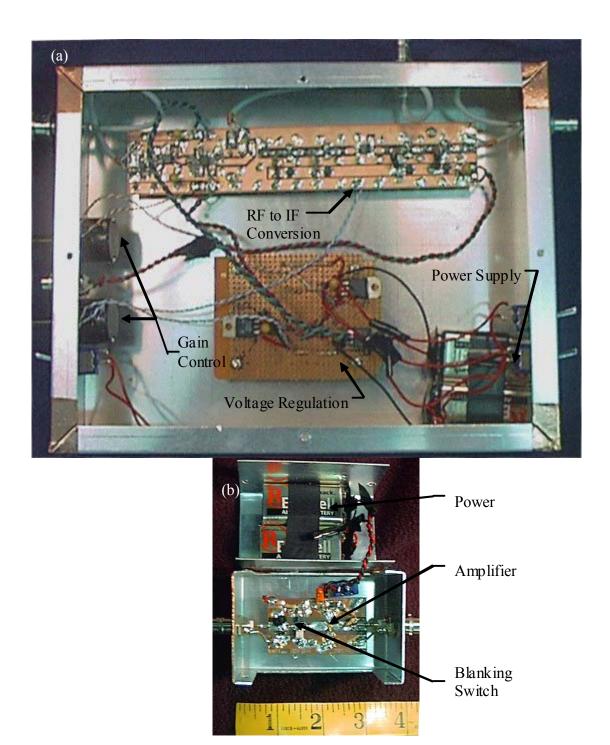

| 45     | Single channel receiver prototype                                                                                                                                                                                                           | 149  |

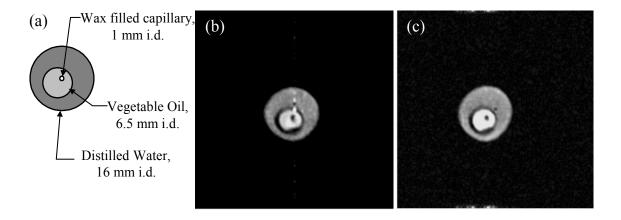

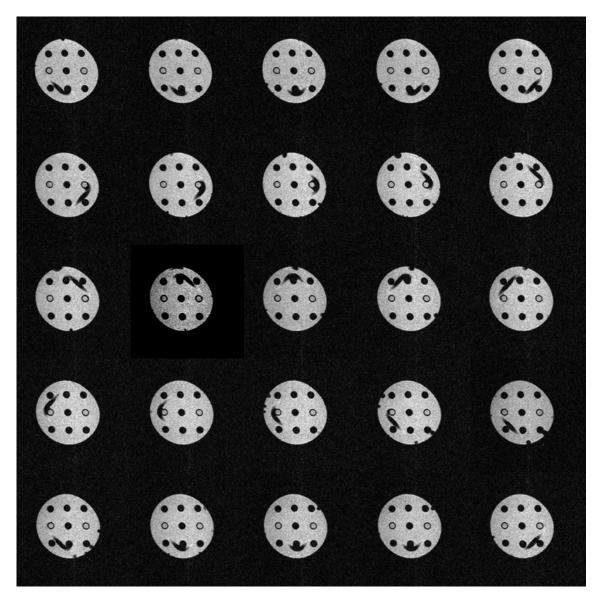

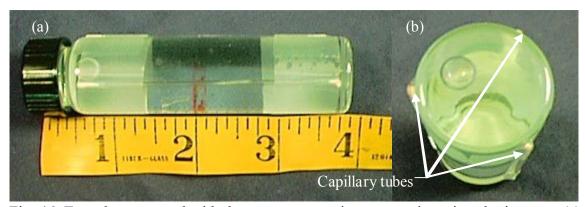

| 46     | Test phantom used with the prototype receiver to acquire spin echo images                                                                                                                                                                   | 151  |

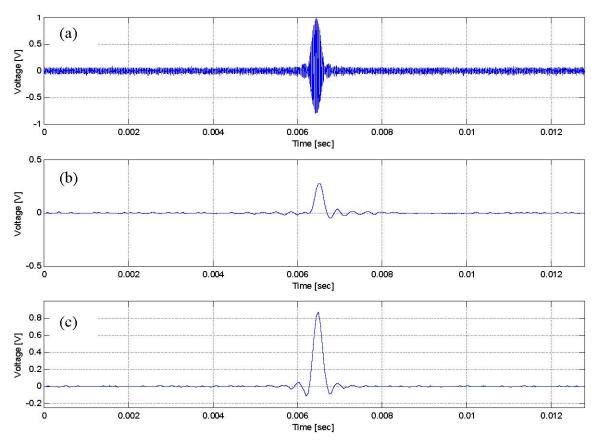

| 47     | A standard spin echo (center line of k-space, TE/ TR = 28 ms/ 300 ms, 20 kHz spectral width, 75 mm FOV, 256 point, 12.8 ms acquisition) received with the prototype receiver on a GE Omega 4.7 T/ 33 cm bore magnet system                  | 152  |

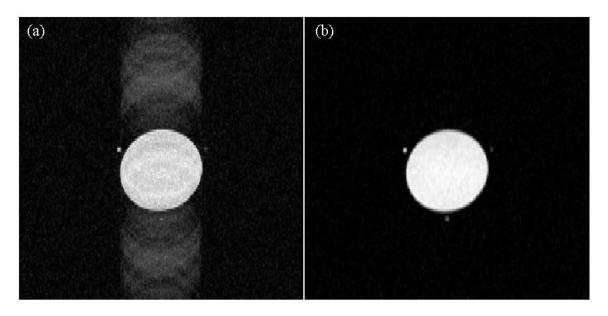

| 48     | Standard spin echo images (TE/ TR = 28 ms/ 300 ms, 20 kHz spectral width, 75 mm FOV, 2 mm slice thickness, 256 × 128 point acquisition) received with the prototype receiver and the GE Omega receiver on a 4.7 T/ 33 cm bore magnet system | 153  |

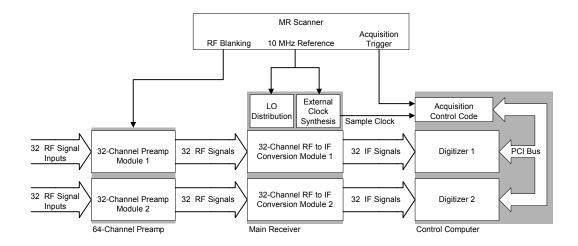

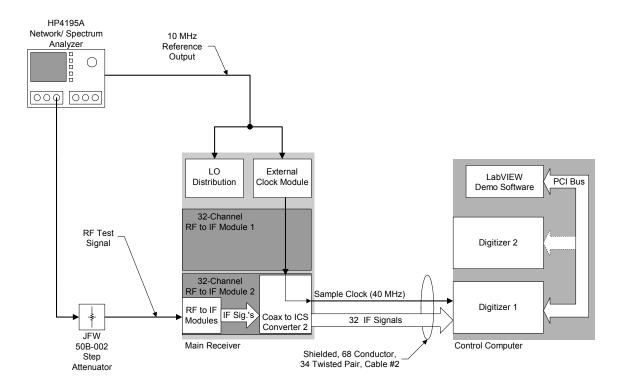

| 49     | Layout of the 64-channel receiver system                                                                                                                                                                                                    | 158  |

| 50     | The prototype 64-channel receiver system mounted in a 35-in. tall, 19-in. shock-mount rack                                                                                                                                                  | 158  |

| 51     | A 19-in. chassis containing one of the two, 32-channel RF to IF conversion modules                                                                                                                                                          | 162  |

| 52     | One of the eight, 4-channel RF to IF conversion submodules used in each 32-channel RF to IF conversion module                                                                                                                               | 162  |

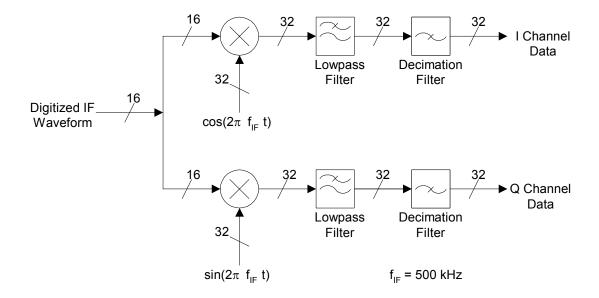

| 53     | A block diagram of the digital demodulation process for the digitized IF signal data                                                                                                                                                        | 165  |

| FIGUI | FIGURE                                                                                                                                                                                                                                             |     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

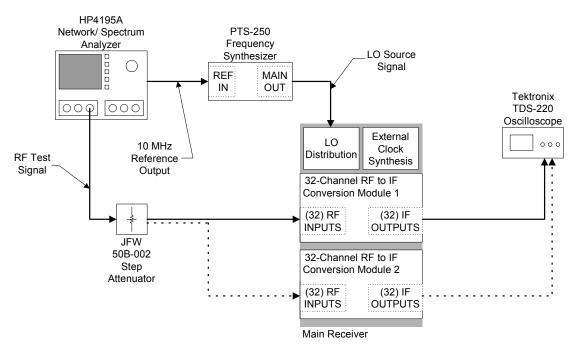

| 54    | Diagram of the apparatus used to test the bandwidth of the channels in the 64-channel receiver                                                                                                                                                     | 169 |

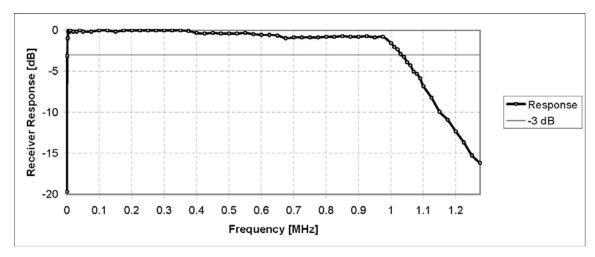

| 55    | Plot of typical bandwidth response of the channels in the 64-channel receiver                                                                                                                                                                      | 171 |

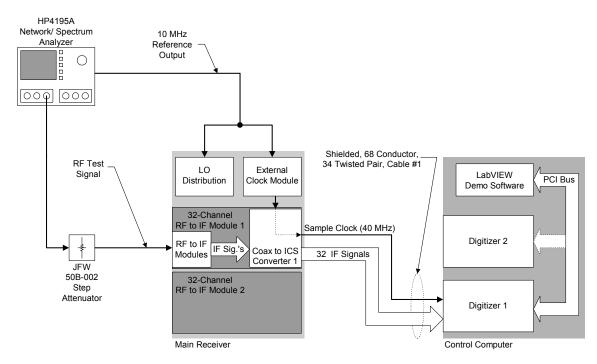

| 56    | Schematic diagram of the operating range test for the 64-channel receiver                                                                                                                                                                          | 173 |

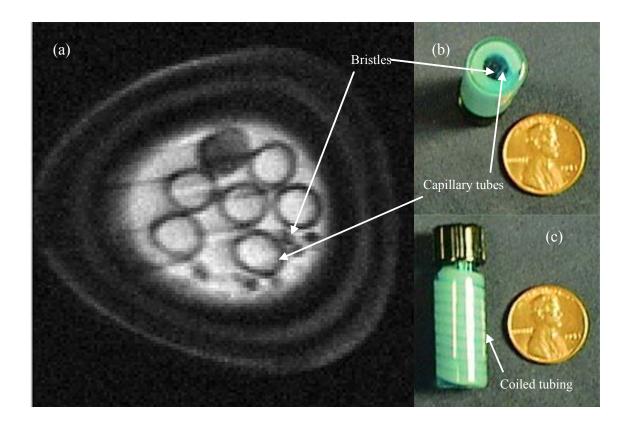

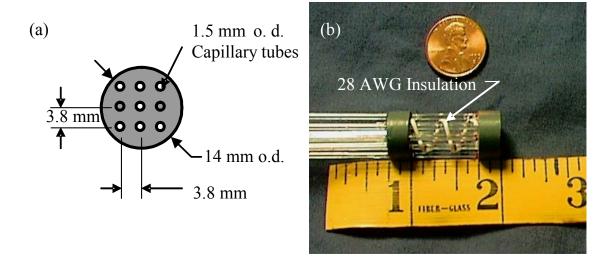

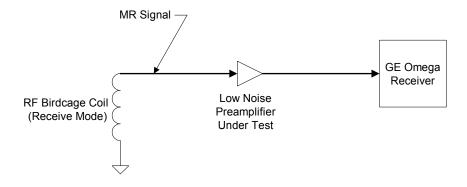

| 57    | Schematic of the test apparatus used to evaluate the noise performance of the 64-channel receiver preamplifier circuits using image SNR methods                                                                                                    | 176 |

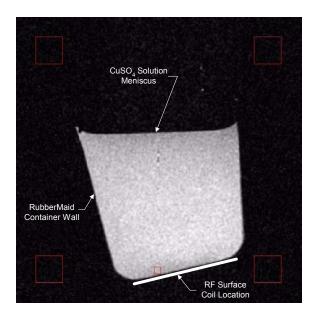

| 58    | A reference image of the preamplifier noise performance test phantom obtained using the birdcage coil for both transmit and receive, the Miteq preamp with the Omega receiver, and the same imaging sequence as the actual noise performance tests | 178 |

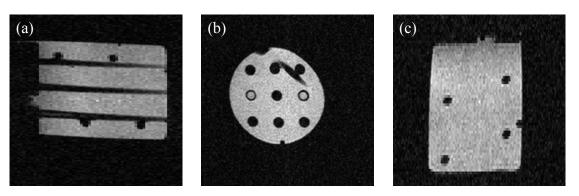

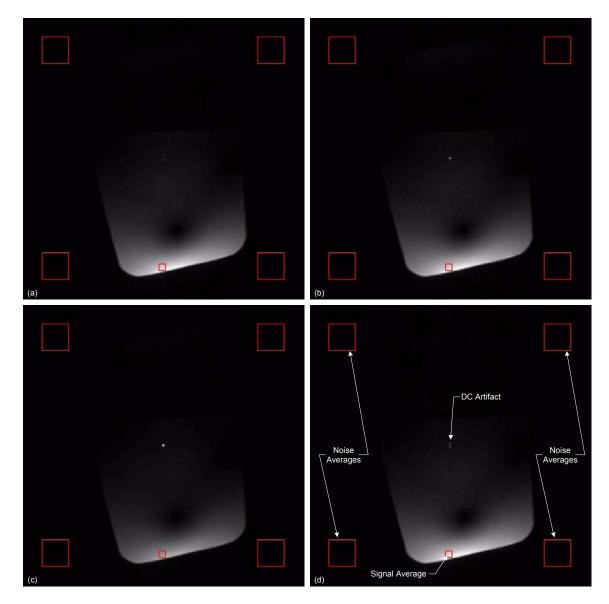

| 59    | Representative images from the preamplifier noise performance tests                                                                                                                                                                                | 179 |

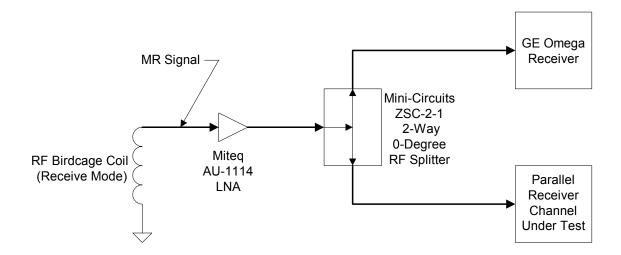

| 60    | Test arrangement for performing the image SNR comparison tests with a commercial receiver                                                                                                                                                          | 181 |

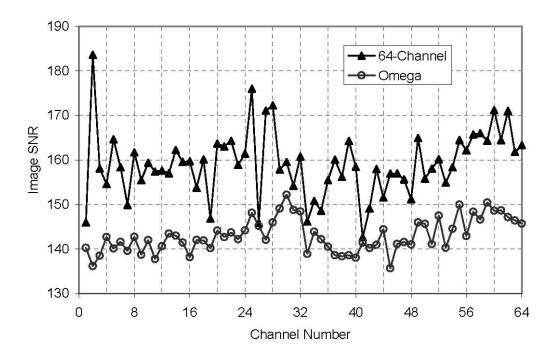

| 61    | Plot of the results of the image SNR comparison tests between the 64-channel receiver and a commercial MR system receiver                                                                                                                          | 181 |

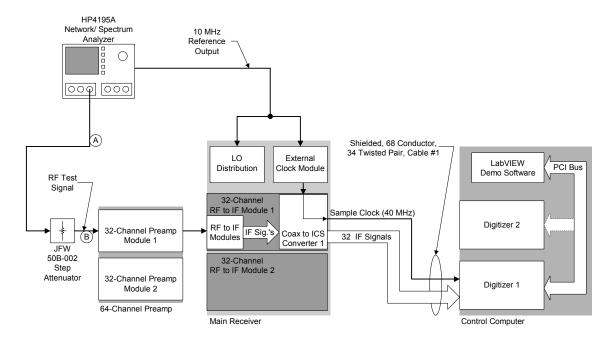

| 62    | Equipment setup for measuring the dynamic range of the first thiry-two channels in the parallel receiver                                                                                                                                           | 183 |

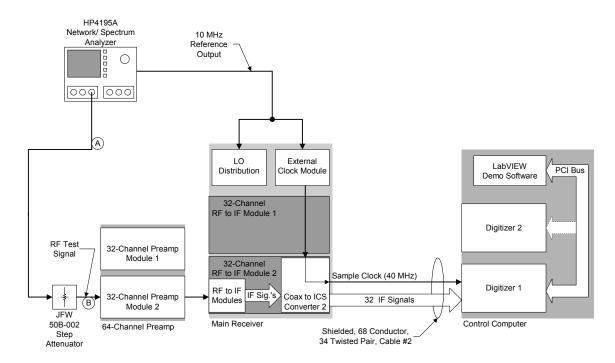

| 63    | Equipment setup for measuring the dynamic range of the second thiry-two channels in the parallel receiver                                                                                                                                          | 184 |

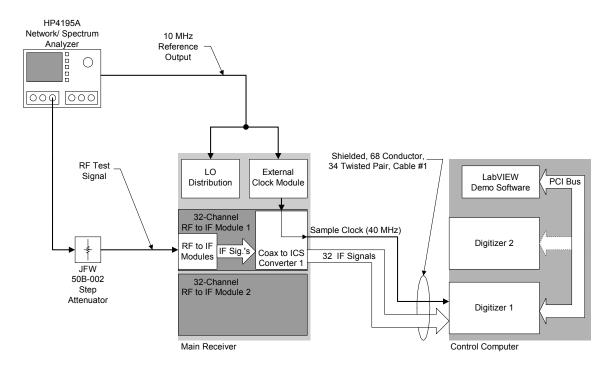

| 64    | Test schematic for the interchannel isolation and channel-to-channel gain variation tests for RF to IF Module 1                                                                                                                                    | 187 |

| 65    | Test schematic for the interchannel isolation and channel-to-channel gain variation tests for RF to IF Module 2                                                                                                                                    | 188 |

| 66    | Plot of the gain variation test results for each of the sixty-four receiver channels                                                                                                                                                               | 192 |

| FIGURE |                                                                                                                                                                                                   | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 67     | Plot of the gain variation test results for each of the sixty-four receiver channels scaled by varying the VGA control network fine adjustment potentiometer on each 4-channel RF to IF submodule | 192  |

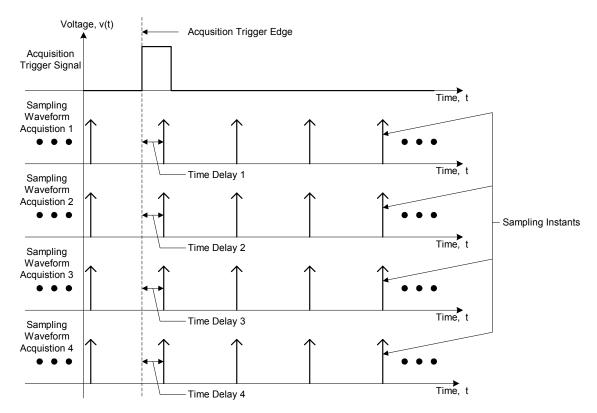

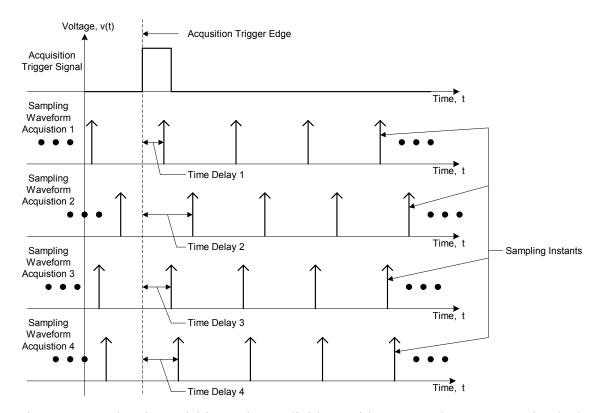

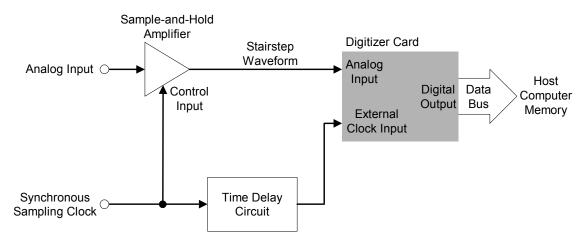

| 68     | MR Signal acquisition using a synchronous digitizer                                                                                                                                               | 197  |

| 69     | MR Signal acquisition using a digitizer with an asynchronous sample clock                                                                                                                         | 199  |

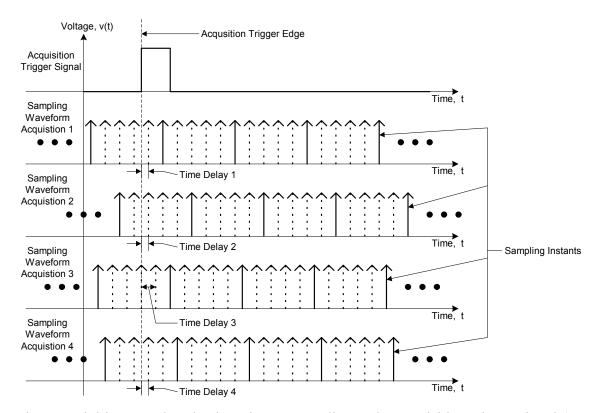

| 70     | Digitizer synchronization via oversampling                                                                                                                                                        | 202  |

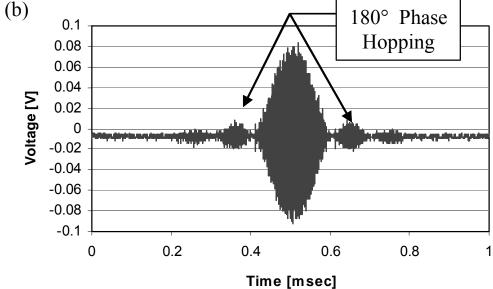

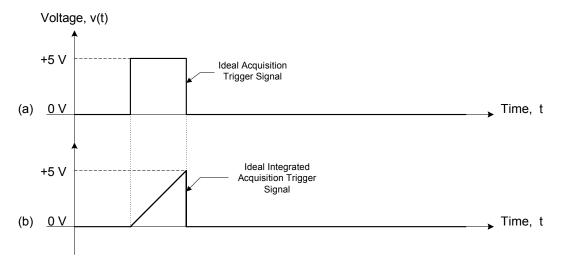

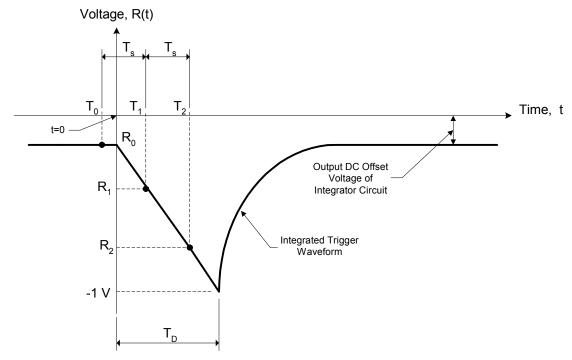

| 71     | Plots of (a) an ideal acquisition trigger signal and (b) an ideal, integrated acquisition trigger signal                                                                                          | 207  |

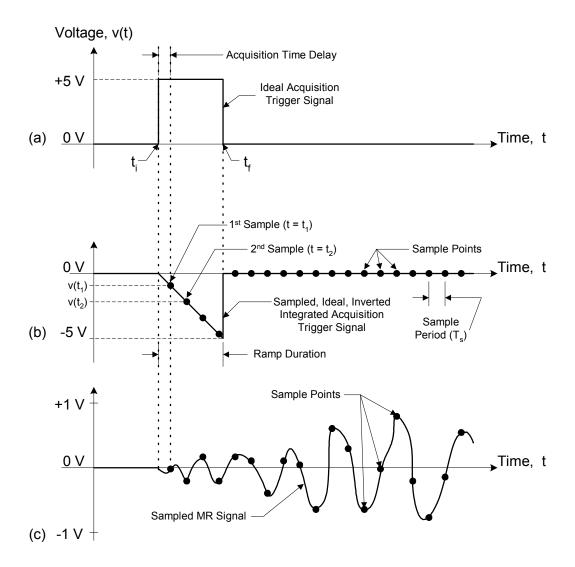

| 72     | The acquisition time delay for the simultaneous digitization of an integrated acquisition trigger signal and an MR signal                                                                         | 208  |

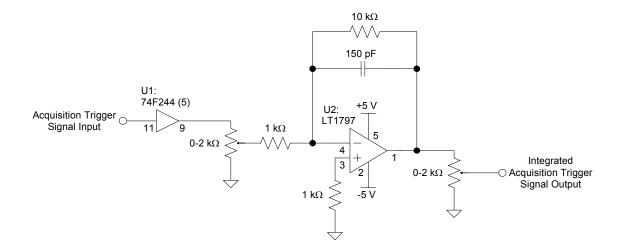

| 73     | Schematic diagram for the acquisition trigger integration circuit                                                                                                                                 | 211  |

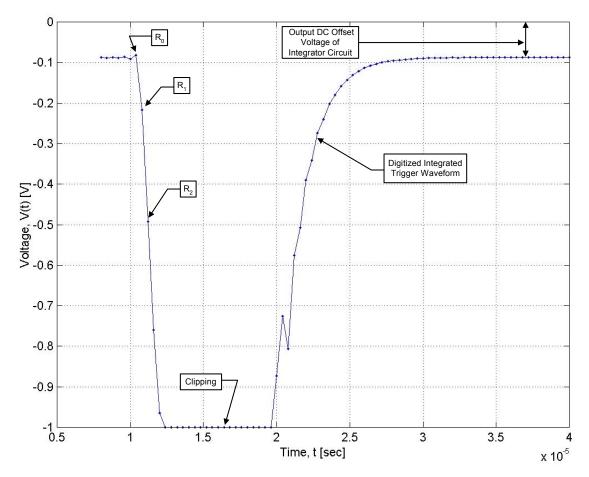

| 74     | Plot of one of the actual, digitized, integrated acquisition trigger signals used to implement digitizer synchronization by Fourier time-shifting on the 64-channel receiver                      | 212  |

| 75     | Diagram of the important parameters for the Fourier time-shifting synchronization algorithm                                                                                                       | 215  |

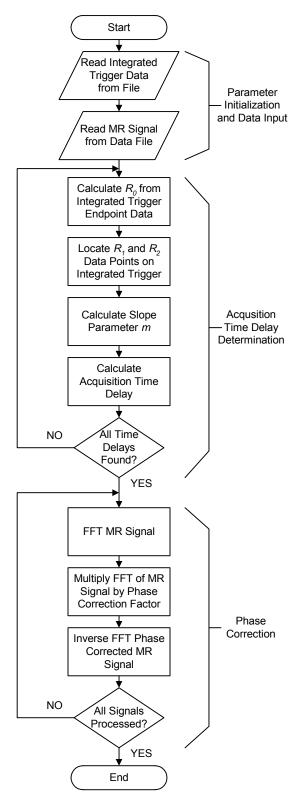

| 76     | Flow chart for the Fourier time-shifting synchronization algorithm                                                                                                                                | 216  |

| 77     | Verification of the Fourier time-shifting synchronization technique                                                                                                                               | 218  |

| 78     | Verification of the clock synthesis synchronization technique on the 64-channel receiver prototype                                                                                                | 222  |

| 79     | The input and output waveforms for an ideal sample/ track and hold circuit                                                                                                                        | 225  |

| 80     | Implementation of pre-sampling using synchronization to the acquisition trigger signal from the MR scanner                                                                                        | 228  |

| 81     | Implementation of pre-sampling using synchronization to the master clock on the MR scanner                                                                                                        | 230  |

#### **CHAPTER I**

#### INTRODUCTION

Reduction of imaging time has long been an important concern in magnetic resonance imaging (MRI). Shorter scan times have many benefits, including increased patient comfort, reduction of motion artifacts, and lower cost. Until recently, the primary method for increasing imaging speed in MRI has been to improve gradientbased imaging technology. This has been done to increase both the power and speed with which magnetic field gradient pulses can be applied to a sample. However, high speed gradient imaging methods are restricted by guidelines imposed by the FDA which limit the application of magnetic field gradients and radio-frequency (RF) energy to the patient in order to prevent bio-effects [1]. It turns out that the high switching speeds and large amplitude gradient pulses now achievable on most commercial MR scanners can cause unwanted peripheral nerve stimulation [1-3]. Additionally, the increase in imaging speed has increased the duty cycle of the RF energy applied to the patient during a scan. This higher RF duty cycle can lead to patient heating [1]. These limitations have led to the inception of alternative approaches for increasing imaging speed, such as parallel MR imaging.

#### I.1 Problem Statement

Parallel imaging is one method for increasing imaging speed without using rapidly

This dissertation follows the style and format of the *Institute of Electrical and Electronic Engineers (IEEE) Transactions on Biomedical Engineering*.

switched, high strength gradient fields. In MRI, parallel imaging may be performed in two different ways. The first is to use multiple MR scanners or multiple sample RF coils to "parallelize" the MR experiment. This method enables different samples to be scanned at the same time [4]. While this does not reduce actual imaging time for a given sample, it does increase sample throughput and thereby reduces the total imaging time required to scan multiple samples. The second parallel imaging method involves the use of arrays of receive coils to reduce the number of phase encoding steps required to scan a sample. The elements of a receive array have B-field patterns which are sensitive primarily to MR signals from regions of a sample near the coil. Hence, the signals received by a particular element of the array are known, *a priori*, to be within a specified region near that array element. This information may be used to decrease the amount of time required to scan a particular sample by eliminating or reducing phase encode steps.

# I.1.1 Parallelization of the MR Experiment

In small animal imaging, large quantities of research animals (50 to 100 or more) must be imaged at regular time intervals to monitor the progression of new disease treatments. Using a clinical, whole body scanner to perform this task is both prohibitively expensive and time-consuming. One way to get around this obstacle is through the parallelization of the MR experiment by using either multiple, independent MR scanners or multiple sample RF coils within a single whole body MR scanner [4]. This would allow multiple animals (or other samples) to be imaged simultaneously. As a result, the overall scan time for large numbers of samples is reduced by increasing the throughput of the MR imaging experiment.

#### I.1.1.1 Multiple MR Scanners

Parallel imaging via multiple MR scanners would be useful for increasing the speed (i.e., throughput) of small animal imaging studies, were it not for the high cost and complexity of MR system hardware. Recently, however, advances in the consumer electronics industry have led to the availability of low-cost RF integrated circuits with remarkable capability. These range from single chip receivers to direct digital synthesis (DDS) chipsets. Such components have the ability to dramatically reduce the cost of the MR transceiver instrumentation. When combined with commonly available PC-based data acquisition cards and compact, low-field imaging magnets, these new RF circuits have the potential to form a new class of inexpensive desktop MR instruments. These low-cost MR scanners could be used to make parallel imaging with multiple MR scanners a practical reality.

# I.1.1.2 Multiple Sample MR Coils

A second approach to the parallelization of the MR imaging experiment involves the use of RF coils capable of simultaneously imaging multiple samples. The idea of using a multiple sample RF coil for imaging laboratory mice has been the subject of some interest in the MRI community. In 2000, a group at the University of Toronto began developing a multiple-sample RF coil for simultaneously scanning up to sixteen mice at 7 T [5, 6]. At about the same time, a four sample RF coil was developed by a colleague in the Magnetic Resonance Systems Laboratory (MRSL) here at Texas A&M University for imaging mice at 1.5 T in the Department of Diagnostic Radiology at the University of Texas M. D. Anderson Cancer Center in Houston [7, 8]. This coil consisted of four,

lowpass, trombone birdcage coils mounted together inside a cross-shaped RF shield assembly. Both of these groups have shown that multiple coil RF coils have the potential for increasing the throughput of the MR imaging experiment via parallelization.

# I.1.2 Array Imaging Techniques

MR imaging is used to obtain an image of a sample that has been placed within a static magnetic field. This image is formed by the application of a series of RF and static magnetic field gradient pulses (a pulse sequence) which interact with the nuclear magnetic dipoles, or spins, contained within the sample. Pulse sequences are used to scan the spatial frequency space, or k-space, of a sample's spins. With traditional gradient based imaging techniques, to acquire an  $N \times M$  pixel image, N scans of k-space, called phase encode lines, must be acquired sequentially. Here, M is the number of readout points which is determined by the strength of the gradient pulse applied during the signal acquisition portion of each line of k-space. Since it takes a finite amount of time, TR, to perform each scan, it takes a total time of  $N \cdot TR$  to acquire an  $N \times M$  pixel image. The goal of parallel imaging with arrays of receive coils is to reduce the number of phase encode lines required to form a given  $N \times M$  pixel image.

The idea of using an array of multiple, independent receive coils to reduce MR imaging time was first introduced in 1987 by two different groups [9, 10]. Indeed, Hutchinson and Raff went so far as to claim that a full  $N \times M$  image could be acquired entirely without phase encoding by placing N closely spaced, small receive coils around a sample [10]. The main problem with this completely parallel imaging method was that

receiving an image from N receive coils required a receiver with at least N channels. By the mid-1990's no MR system manufacturer had produced a receiver with more than four channels; hence, the method proposed by Hutchinson and Raff was regarded as impractical and largely abandoned in favor of fast gradient based imaging.

By the late 1990's, fast gradient based imaging techniques were rapidly approaching the FDA imposed safety limits. This led to a revival of interest in parallel imaging with arrays; however, MR system manufacturers were still providing receivers with only a limited number of channels. For this reason, several partially parallel imaging (PPI) techniques came about which reduced imaging time not by eliminating phase encoding, but by reducing the number of phase encode steps required to take an image. In 1989, the idea of using MR arrays to perform partially parallel k-space scans was first proposed by Kelton, *et al.* [11]. In 1997, Sodickson released the SMASH technique for rapid MR imaging with arrays [12]. Roughly a year later, in 1999, Preussman published the SENSE method [13] which is essentially a refined version of the algorithm first proposed by Kelton. Since then, other PPI methods have been introduced, such as PILS and GRAPPA [14, 15]. All of these methods use arrays of receive coils to reduce the number of phase encode steps needed to acquire an image.

To date, SMASH (or SiMultaneous Acquisition of Spatial Harmonics) and SENSE (or SENSitivity Encoding) remain the most common partially parallel imaging techniques. Both of these techniques increase imaging speed by reducing the number of phase encoding steps needed to encode an image. In SMASH reconstruction the coil sensitivity patterns for each element in an array and the reduced k-space scan data are

used to synthesize the phase encode lines which were "skipped" in the initial scan. Using the SMASH technique, total scan time may be reduced at most by a factor equal to the number of coils in the array. However, it must be noted that at high acceleration factors (i.e., as the acceleration factor approaches the number of coils in the array), the SNR in the reconstructed image degrades significantly. In SENSE, a set of *N* aliased images are acquired from an *N*-element receive array. The sensitivity patterns for each element in the array are used to form a set of linear equations which relate the aliased images from each coil to the unaliased full field-of-view image. Solving this set of equations performs an "unwrapping" of the data in the image domain to yield the desired image. Like SMASH, the SENSE technique can be used to reduce scan time by at most a factor equal to the number of coils in the array. So, the amount by which these techniques can reduce imaging time is limited by the number of receiver channels available on a particular MR scanner.

It is clear that to increase imaging speed any further with partially parallel techniques, larger arrays of receive coils must be used. However, these larger arrays require a parallel receiver with enough channels to support them. When the work for this dissertation was begun in early 1998, the largest MR receiver reported in the literature had only sixteen channels [16], and no commercial MR system could support more than eight receiver channels. Thus, for scan times to be reduced any further by partially parallel imaging methods, it was determined that a dedicated MR receiver for parallel imaging was needed. Such a receiver would support a minimum of 64-channels,

enabling both fully parallel imaging and partially parallel imaging with high acceleration factors.

## I.2 Research Objectives

The primary objective of this work is to identify cost-effective methods for implementing parallel MR imaging. To accomplish this goal, four specific aims have been defined. These aims encompass two methods for parallel MR imaging: parallel imaging via multiple low-cost MR scanners and parallel imaging with arrays of receive coils. (The third method, parallelization by multiple sample MR coils, has been excluded from this dissertation as it has been undertaken by a colleague within the MRSL.) The first aim investigates the former method for parallel MR imaging, while the last three aims deal with the latter. Accomplishment of the four aims will enable the overall research objective to be met.

# I.2.1 Aim 1: Build a Low-Cost Desktop MR Scanner

In order to develop an understanding of the intricacies of the MR receiver, a prototype desktop MR scanner will be constructed. The scanner will be capable of imaging small volumes with high resolution on dedicated, low-field MR magnets. The scanner will be based upon a conventional analog transceiver design and will be built from off-the-shelf sub-systems to lower system cost. The prototype will demonstrate the feasibility of inexpensive, low-field MR scanners as a new-class of general use laboratory instrument for non-clinical applications.

#### I.2.2 Aim 2: Design a Digital MR Receiver

A cost-effective, single-channel MR receiver will be designed to serve as a building block for a highly parallel MR receiver system. The receiver will be suitable for imaging small volumes with surface coils at 4.7 T. The performance of the receiver will be comparable to that of commercial analog receivers. Finally, the single-channel receiver design must be easily scaled up to form a 64-channel receiver.

#### I.2.3 Aim 3: Implement a 64-Channel Parallel MR Receiver

A prototype receiver for parallel imaging will be implemented based upon the single-channel design of Aim 2. The parallel imaging receiver will be low in cost, have 64-channels total, and will easily interface to any commercial MR scanner.

# I.2.4 Aim 4: Characterize the Performance of the 64-Channel Receiver

The 64-channel system will be fully characterized to establish how well it meets the requirements for a cost-effective parallel imaging MR receiver. The bandwidth, operating frequency range, noise performance, dynamic range, interchannel isolation, gain variation between channels, and system cost will all be determined for the receiver. As part of the noise performance characterization, the signal-to-noise ratio of the receiver will be compared to that of a single-channel commercial scanner.

### I.3 Dissertation Organization

This dissertation has been organized to follow the completion of the research objectives detailed in section I.2. As such the dissertation has been divided into eight chapters. The first two chapters supply the motivation and required background theory for this work. Next, Chapters III through VII describe how each of the four main

research objectives was satisfied. Finally, in Chapter VIII, conclusions are drawn from the research and suggestions for future work are made. The contents of each chapter will be described in the next paragraphs.

Chapter I presents the problem statement, research objectives, and an outline of the dissertation. The outline has been provided to assist the reader in identifying the location of relevant information within the dissertation. Chapter II conveys the principles necessary for understanding the methods used to design cost-effective instrumentation for parallel MR imaging. These include a brief description of NMR theory, the basics of MR image formation, the received MR signal, the design of the MR receiver, and performance metrics for MR receivers.

Chapter III details the process by which the low-cost, desktop MR scanner was developed to satisfy the first research objective. The desktop scanner prototype was developed during a three year period from spring of 1998 to spring of 2001 as part of a grant from the State of Texas Higher Education Coordinating Board (no. 000512-0189-1997). The chapter begins with the initial design requirements which drove the design of the prototype desktop system. Then, the overall system design for the desktop scanner is presented. Finally, an evaluation of the desktop scanner is given which includes a performance summary, an evaluation of the desktop system cost, an SNR comparison to a commercial scanner, and a demonstration of system performance during 2D and 3D MR imaging.

Chapters IV through VI together present the design, implementation, and characterization of a dedicated, 64-channel receiver for parallel MR imaging. The

receiver was developed to fulfill research aims 2 through 4. Actual work on the 64-channel receiver prototype was carried out during an 18 month period from the spring of 2001 to winter of 2002 as part of a one year grant from the National Medical Technology Testbed (Dept. of the Army DAMD17-97-2-7016). Chapter IV presents the design of a scalable, single-channel, digital MR receiver. In Chapter V, the implementation of the 64-channel parallel MR receiver system is described. Then, in chapter VI, the characterization of the 64-channel prototype is presented.

Chapter VII presents methods for correcting the phase jitter problem that is commonly encountered in MR receivers. As such, it first describes the nature of phase jitter. Then, four techniques are presented for eliminating the phase jitter problem. Each of the four techniques has been used to accomplish the four research aims detailed in section I.2.

Finally, in Chapter VII, conclusions are drawn from the results of the primary research objectives. This is followed by suggestions for future work on both the desktop MR scanner and the 64-channel receiver.

#### **CHAPTER II**

#### **BACKGROUND THEORY**

In this chapter, the essential theoretical background for the work undertaken within this dissertation will be presented. As such, the key elements of NMR theory will first be briefly outlined to provide a basis for a discussion of MR imaging. Next, the basic operating principles underlying MR image formation will be discussed. Particular emphasis will be placed upon the equation of the MR signal that is received in a typical imaging experiment. This MR signal equation will lead to a description of the operation and design of the MR receiver. Finally, the methods used to characterize the performance of an MR receiver will be discussed. All of these topics should provide the reader with an understanding of the principles required to design instrumentation for parallel MR imaging. (The reader should note that it is not the author's intention to present anything more than a brief sketch of the fundamental principles which serve as a basis for the instrumentation required to perform parallel MR imaging with arrays of sensor coils. The theory of NMR and MR imaging has been widely discussed in great detail elsewhere in the literature.)

#### **II.1 NMR Theory**

The phenomenon of nuclear magnetic resonance (NMR) in bulk materials was first reported by Bloch in 1946 [17]. The theory of NMR has several key components which include the properties of nuclear spin and magnetic dipole moment, the Larmor frequency, bulk magnetization of nuclei within a static magnetic field, and the emission

of the free induction decay signal. This section will provide a brief introduction to the NMR phenomenon and these principle components.

## II.1.1 Nuclear Spin and Magnetic Dipole Moment

Atomic nuclei which possess either an odd number of protons, neutrons, or both have certain magnetic properties which include both spin and a magnetic dipole moment. There are several nuclei in nature which meet this qualification, including  $^{1}$ H,  $^{13}$ C, and  $^{31}$ P. (The hydrogen nucleus (or proton),  $^{1}$ H, is of primary importance to MRI due to its natural abundance in biological tissues; hence, the hydrogen proton will be assumed in all discussions of NMR theory contained within this dissertation unless otherwise specified.) When any of these nuclei are placed within a static magnetic field they assume one of (2I+1) possible energy states, known as spin states. Each of these spin states has an associated magnetic dipole moment. (The variable I is known as the spin number and represents the total angular momentum of a nucleus. In general, I is always some positive integer multiple of  $\frac{1}{2}$ .)

# II.1.2 Larmor Frequency

In the presence of a static magnetic field,  $B_0$ , the magnetic dipole moment,  $\mu$ , of each nucleus will experience an aligning torque,  $\tau$ , due to the static field (2.1). (For the purpose of this dissertation, the direction of the static magnetic field will always be assumed to be in the positive z-direction.) Under the influence of this torque, the magnetic dipole moment of the nucleus will precess, in a left-handed fashion, about the main magnetic field. This, in turn, will cause the z-component of each nuclear magnetic dipole moment vector to align itself either parallel or anti-parallel to the applied

magnetic field. The precession frequency of the nuclear magnetic dipole, or spin, is given by the Larmor relation (2.2) [18, 19]. In (2.2),  $\omega_0$  [rad/s] is known as the Larmor (or resonant) frequency of the nucleus,  $B_0$  [T] is the strength of the static magnetic field flux, and  $\gamma$  [rad·T<sup>-1</sup>·s<sup>-1</sup>] is the gyromagnetic ratio. For the hydrogen proton, the gyromagnetic ratio,  $\gamma$ , is known to be  $2\pi\cdot42.578\cdot10^6$  rad·T<sup>-1</sup>·s<sup>-1</sup>.

$$\vec{\tau} = \vec{\mu} \times \vec{B}_0 \tag{2.1}$$

$$\omega_0 = \gamma \cdot B_0 \tag{2.2}$$

## II.1.3 Bulk Magnetization

Since the hydrogen nucleus has a spin number of  $\frac{1}{2}$ , it has only two possible spin states. When a sample containing a collection of hydrogen protons is not in the presence of a static magnetic field (and is in thermal equilibrium), there is no magnetic potential energy associated with either spin state. In this case, the population of spins is equally distributed between the two spin states. However, when a static magnetic field is applied to this same sample, each spin state has an associated magnetic potential energy. For the hydrogen proton, the energy for each spin state,  $E_m$  [J], is given by (2.3) [18]. In (2.3), m is the energy level and  $\hbar = h/2\pi$ , where h is Planck's constant (6.63×10<sup>-34</sup> [J·s]). The two spin states are additionally differentiated by the orientation of the z-component of their respective magnetic dipole moments. The nuclear magnetic dipoles in the spin  $\frac{1}{2}$  state (i.e., m is  $\frac{1}{2}$ ) have a potential energy  $E_{\frac{1}{2}}$  and align themselves parallel to the direction of the static magnetic field. The spins in the  $-\frac{1}{2}$  state, on the other hand, have an energy of  $E_{-\frac{1}{2}}$  and tend to align themselves anti-parallel to the static magnetic field. A slightly higher proportion of spins in the sample will occupy the spin  $\frac{1}{2}$  state since it

has a lower magnetic potential energy. Thus, if there are total of N spins contained within a sample, summation of the magnetic dipole moment vectors,  $\bar{\mu}_i$ , for all the spins (2.4) will result in a net magnetization vector,  $\bar{M}_0$ , that lies in the direction of the static field [18]. The magnitude of this net magnetization vector,  $M_0$  [J/T/m<sup>3</sup>], for a sample consisting of N hydrogen protons is given in (2.5), where k is the Boltzmann constant (i.e.,  $1.3807 \times 10^{-23}$  [J/K]), T is the sample temperature [K], and the remaining variables have been previously defined [18].

$$E_m = -m\hbar\gamma B_0 \qquad m = \pm I = \pm \frac{1}{2} \tag{2.3}$$

$$\vec{M}_0 = \sum_{i=1}^{N} \vec{\mu}_i \tag{2.4}$$

$$M_0 = \frac{N\gamma^2 \hbar^2 B_0}{4kT}$$

(2.5)

## II.1.4 Free Induction Decay Signal

Once the magnetic dipole moment vectors of all the nuclei in a sample have aligned with the static field, an equilibrium condition is reached and the net magnetization vector  $(\bar{M}_0)$  will be aligned with the static field  $(\bar{B}_0)$ . The net magnetization vector (and the spins associated with it) may then be tipped away from alignment with the static magnetic field (and into a plane transverse to the static field) by the application of an external time-varying magnetic field,  $B_I$ . This  $B_I$ -field must be orthogonal to the static field and have a frequency content that spans the Larmor frequency for the spins in the sample.

The angle that forms between the static magnetic field  $(B_0)$  and the net magnetization vector  $(M_0)$  during the application of the  $B_I$  field is known as the "tip" angle. When the tip angle is 90°, the entire net magnetization vector is tipped into the transverse plane. Now, if the applied  $B_I$  field is a square pulse (2.6) with duration,  $\tau_p$  [s], then the tip angle,  $\alpha$  [rad], is given by (2.7) [18]. In (2.7) the term  $B_{Ieff}$  [T] is the effective  $B_I$ -field in the rotating frame. In the special case where the applied  $B_I$  field is a linearly polarized square pulse, the magnitude of  $B_{Ieff}$  may be specified by (2.8).

$$B_{1}(t) = \begin{cases} B_{1}\cos(\omega_{0}t) & 0 \le t \le \tau_{p} \\ 0 & elsewhere \end{cases}$$

(2.6)

$$\alpha = (\gamma B_{1eff}) \tau_p \tag{2.7}$$

$$B_{leff} = \frac{B_1}{2} \tag{2.8}$$

After the  $B_I$  field has been applied, the net magnetization vector will again relax back to its equilibrium state while continuing to precess about the main  $B_0$  field at the Larmor rate. The relaxation process, known as "spin-lattice" or " $T_1$ " relaxation, may be described by the exponential relation of (2.9). In (2.9), the z-component of the net magnetization vector,  $M_z$ , is given as a function of time, t [s]. Here, the time constant of the relaxation process is  $T_I$  [s]. Finally,  $M_z^0$  is the net magnetization in the direction of the static field at time t = 0. (Note: If the sample is at its equilibrium state at time t = 0, then the term  $M_z^0$  will be given by the net magnetization ( $M_0$ ) of (2.5).)

$$M_z(t) = M_z^0 (1 - e^{-t/T_1})$$

(2.9)

The precession of the net magnetization vector in the transverse (or x-y) plane will induce an emf (at the Larmor frequency of the nuclei within the sample) inside any tuned RF pickup coil whose polarization vector is also orthogonal to the static magnetic field. This induced voltage is known as a free induction decay signal (or fid), and it serves as the basis for both NMR spectroscopy and MR imaging.

The voltage of the fid signal as a function of time, v(t), has the form of a decaying sinusoid and may be described by (2.10) [18]. Here, t is time [s], j is simply the imaginary number ( $\sqrt{-1}$ ),  $\omega_{\theta}$  is the Larmor frequency of the spins [rad/s], and  $\Delta V$  is the volume of the sample [m<sup>3</sup>]. The  $M_{xy}^0$  term denotes the magnitude of the net magnetization vector in the transverse plane immediately after the RF excitation has been applied. The  $e^{-t/T_2}$  term describes the "spin-spin" or "T<sub>2</sub>" relaxation process. T<sub>2</sub>relaxation is used to describe the loss of signal coherence due to a dephasing of the spins which compose the transverse plane magnetization vector. Finally,  $B_{It}$  [T/A] is the effective sensitivity of the detector coil (2.11) [18]. In (2.11), the  $\vec{B}_1$  term denotes the flux density vector that would be produced by the detector coil if it were operated in transmit mode, the  $I_I$  term indicates the amount of current necessary to produce  $\vec{B}_1$ , and  $\hat{

ho}_{\scriptscriptstyle M}$  is the unit polarization vector for the net magnetization of the spins in the transverse plane. The unit polarization vector (2.12) for the transverse plane magnetization is circularly polarized due to the fact that the net magnetization precesses about the zdirected static field  $(B_0)$ . (The terms  $\hat{a}_x$  and  $\hat{a}_y$  are just unit vectors in the direction of the x- and y-axes, respectively.)

$$v(t) = j\sqrt{2}\omega_0 \Delta V B_{1t} M_{xv}^0 e^{-t/T_2} e^{j\omega_0 t}$$

(2.10)

$$B_{1t} = \left(\frac{\vec{B}_1}{I_1}\right) \bullet \hat{\rho}_M \tag{2.11}$$

$$\hat{\rho}_M = \frac{\hat{a}_x + \hat{a}_y}{\sqrt{2}} \tag{2.12}$$

# **II.2 MR Imaging Basics**

The principle of using static magnetic field gradients to encode spatial information into the frequency content of the received NMR signal was first introduced by Lauterbur in 1973 [20]. This idea may be used to obtain an image of a sample that has been placed within a homogeneous, static magnetic field. An MR image is formed by the application of a series of RF and static magnetic field gradient pulses at specified time intervals (a pulse sequence) which interact with the nuclear magnetic dipoles, or spins, contained within the sample. This interaction causes a map or image of the spins within an object to be encoded in the NMR signals. In this section the method by which spatial information is encoded into the NMR signal will be presented. A typical MR pulse sequence will then be described to show how an MR image may be formed using standard 2D Fourier encoding techniques. This will be followed by a description of the MR signal that is received from the imaging sample during the pulse sequence. Afterwards, the MR image reconstruction process will be summarized. Finally, the resolution of the MR image will be presented and equations will be given for determining the signal-to-noise ratio of the received MR signal.

#### II.2.1 Encoding Spatial Information in the NMR Signal

The spins for a particular nucleus (such as the hydrogen proton) all have the same gyromagnetic ratio. When a sample is placed in a homogeneous, static magnetic field,  $B_{\theta}$  [T], (which is assumed to be z-directed) the spins of all the hydrogen protons will have nearly the same precession frequency. (Note: There will be slight variations in this precession frequency throughout the sample due to varying amounts of shielding from local electrons within the molecules that the hydrogen protons inhabit.) If a linear gradient in the static magnetic field is then applied to the sample under investigation, the spins along that field gradient will precess about the main field at different frequencies. For example, if a z-directed magnetic field gradient,  $G_x$  [T/m], is applied along the xaxis of the sample, the spins along the x-axis will experience a linear variation in their Larmor frequencies governed by (2.13). It is easy to see that if additional, z-directed, linear, static magnetic field gradients ( $G_v$  [T/m] and  $G_z$  [T/m]) are imposed along the yand z-axes over the region containing a sample, the position of each spin within the sample will be mapped to a unique frequency (2.13). In (2.13) and (2.14), position is denoted by x, y, and z [m] while  $\omega_0$  and  $\gamma$  are as given in section II.1. It turns out that by selectively applying the static magnetic field gradients  $(G_x, G_y, \text{ and } G_z)$  at specified intervals during the time period in which a series of time-varying  $B_1$  field pulses are applied to a sample (a series of events known as a pulse sequence), the spatial location of that sample's spins may be encoded in the received NMR signal. This encoding of the position to frequency is what is used in MRI to generate an image of the spins contained within a particular sample.

$$\omega(x) = \gamma(B_0 + G_x x) = \omega_0 + \gamma G_x x \tag{2.13}$$

$$\omega(x, y, z) = \gamma \left(B_0 + G_x x + G_y y + G_z z\right) = \omega_0 + \gamma G_x x + \gamma G_y y + \gamma G_z z \tag{2.14}$$

# II.2.2 Pulse Sequences

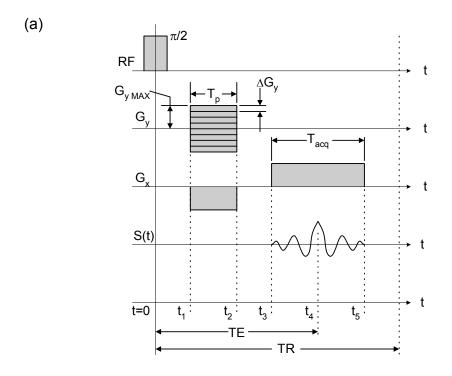

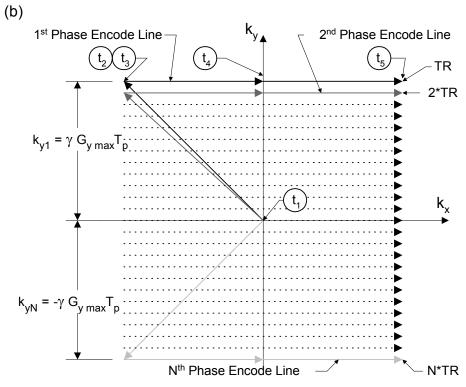

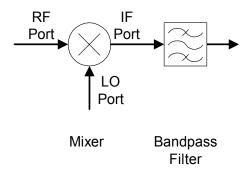

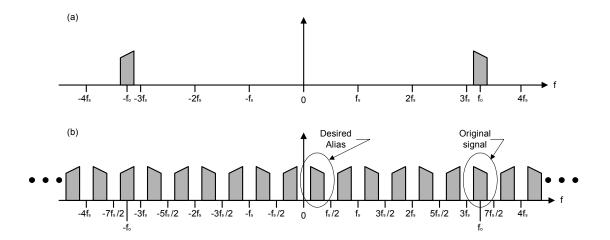

Pulse sequences are used to collect the MR image data by scanning the spatial frequency space, or k-space, of a sample's spins. As an example, a simple, 2D Fourier encoded, gradient echo pulse sequence (Fig. 1a) and its corresponding traverse of k-space (Fig. 1b) has been shown. In order to acquire an  $N \times M$  pixel image using this gradient echo sequence, N scans of k-space, called phase encode lines, must be acquired sequentially. A single line of k-space is acquired every time the pulse sequence is run from time t = 0to t = TR (Fig. 1a). The received NMR signal, a gradient echo in this case, is digitized in the time period from  $t = t_3$  to  $t = t_5$  which has a duration of  $T_{acq}$ . Note that the center of the received echo signal occurs at time TE (or the "echo time"). M (the number of readout points in the final image) is determined by the strength of the gradient pulse  $(G_x)$ applied during the signal acquisition, the length of the acquisition period, and the bandwidth of the pulse sequence. All of k-space is scanned by repeating the pulse sequence while changing the length of the step in  $k_{\nu}$  (Fig. 1b) that occurs between time t  $= t_1$  and  $t = t_2$ . This change in the length of the  $k_v$ -step is accomplished by varying the strength of the y-gradient pulse,  $G_v$  (Fig. 1a), from  ${}^+G_{v max}$  to  ${}^-G_{v max}$  in N steps of size  $\Delta G_{\nu}$  (called phase encoding). Since it takes a finite amount of time (TR or the "repetition time") to scan each line of k-space, a total time of (N·TR) is required to acquire an  $N \times M$  pixel image.

Fig. 1. An example of a 2D Fourier encoded pulse sequence for MR imaging. (a) A simple, 2D Fourier encoded gradient echo pulse sequence. (b) The k-space scan resulting from the pulse sequence in (a).

#### II.2.3 Received Signal

During a 2D Fourier encoded MR imaging experiment, an NMR signal is acquired for every line of k-space that is scanned. This signal is picked up as an induced emf in an RF detector coil that has been tuned to the resonant frequency of the spins within the imaging sample. The received MR signal itself may be represented by (2.15) assuming that the imaging sample consists of a thin slice of spins in the x-y plane with a constant slice thickness. (A thorough derivation of the signal received in a 2D Fourier encoded MR imaging experiment is widely available in the literature [14]-[15] and will not be given here.) In (2.15) the MR image is represented by the function I(x,y) which incorporates the effects of T2 relaxation, transverse magnetization, and the sensitivity of the receive RF coil (which all vary with position over the imaging sample) as well as constant multiplicative factors due to the Larmor frequency and the slice thickness [18]. Additionally,  $T_{pe}$  is the duration of the phase encode gradient pulse while the remaining variables in (2.15) remain as previously defined in (2.2) and (2.14). It should be noted that by performing a change of variables according to (2.16) and (2.17), the expression of (2.15) can be rewritten in (2.18) as a function of the k-space coordinates  $k_x$  [rad/m] and  $k_v$  [rad/m]. Equation (2.18) shows that the received MR signal  $S(k_x, k_y)$  consists of an information signal that has been modulated by a complex carrier with a frequency of  $\omega_0$ . Finally, it should be noted that the information signal is actually just the 2D Fourier Transform of the image function I(x,y).

$$S(t) = \left[ \iint_{slice} I(x, y) e^{j\gamma G_x x t} e^{j\gamma G_y y T_{pe}} \partial x \partial y \right] \cdot e^{j\omega_0 t}$$

(2.15)

$$k_{x} = \frac{\omega_{0} \cdot G_{x} \cdot t}{B_{0}} = \gamma \cdot G_{x} \cdot t \tag{2.16}$$

$$k_{y} = \frac{\omega_{0} \cdot G_{y} \cdot T_{pe}}{B_{0}} = \gamma \cdot G_{y} \cdot T_{pe}$$

(2.17)

$$S(k_x, k_y) = \left[ \iint_{slice} I(x, y) e^{jk_x x} e^{jk_y y} \partial x \partial y \right] \cdot e^{j\omega_0 t}$$

(2.18)

# II.2.4 Image Reconstruction

The signals received during a 2D Fourier encoded MR imaging experiment contain the Fourier Transform of the MR image modulated by a complex carrier signal. In order to reconstruct the image from these signals, two operations must be performed. First, the signals must be demodulated in order to remove the complex carrier. Mathematically, this may be performed by simply multiplying the received signals by a complex exponential (2.19); however, the demodulation of the received signals is more involved in actual practice (this will be discussed in section II.4.2). Second, an inverse 2D Fourier Transform must be performed on the demodulated signals to reconstruct the MR image of the sample (2.20).

$$S_{de \bmod}(k_x, k_y) = S(k_x, k_y) \cdot e^{-j\omega_0 t} = \iint_{slice} I(x, y) e^{jk_x x} e^{jk_y y} \partial x \partial y$$

(2.19)

$$I(x,y) = \iint S_{de \bmod}(k_x, k_y) e^{-jk_x x} e^{-jk_y y} \partial k_x \partial k_y$$

(2.20)

# II.2.5 Image Resolution

In a Fourier encoded MR imaging experiment each line of k-space is acquired and stored in a 2D matrix having N rows (i.e., one for each phase encode line) and M

columns (i.e., the signal is digitized and a total of M readout points are collected). The MR image is then reconstructed by performing an  $N \times M$ , 2D, inverse discrete Fourier Transform (2D-IDFT) on the k-space data set. For faster reconstruction, N and M are generally chosen to be powers of 2 so that fast Fourier Transforms (FFT's) may be used to reconstruct the final image. The resolution and field-of-view in the final MR image is given by (2.21) and (2.22). The terms  $FOV_x$  and  $FOV_y$  [m] refer to the fields-of-view along the x- and y-axes. Also,  $\Delta x$  and  $\Delta y$  [m] give the resolution in the x and y plane of the image space while  $\Delta k_x$  and  $\Delta k_y$  [rad/m] are the resolution in k-space. Finally,  $\Delta t$  [s] is the sample dwell time for the digitizer that acquires the MR signal and  $\Delta G_y$  [T/m] is the phase encode gradient step size.

$$FOV_{x} = M \cdot \Delta x = \frac{2\pi}{\Delta k_{x}} = \frac{2\pi}{\gamma \cdot G_{x} \cdot \Delta t}$$

(2.21)

$$FOV_{y} = N \cdot \Delta y = \frac{2\pi}{\Delta k_{y}} = \frac{2\pi}{\gamma \cdot \Delta Gy \cdot T_{pe}}$$

(2.22)

## II.2.6 Relaxation Processes and Steady-State Transverse Magnetization

During an MR imaging sequence, the received signal voltage level will vary from that of the fid signal (2.10) due to the presence of various relaxation processes which affect the behavior of the net magnetization vector. The two primary processes,  $T_1$ - and  $T_2$ -relaxation, have been previously discussed in section II.1.4. In addition to these two, there exist two other relaxation processes known as the  $T_2^*$ - and  $T_2^{**}$ -relaxations. These last two relaxations are actually just modifications of the  $T_2$ -relaxation process to include the effects of magnetic field inhomogeneities and magnetic field gradients. Hence, the  $T_2^*$ -relaxation process describes the dephasing of the transverse plane magnetization

$(M_{xy})$  due both to normal  $T_2$ -relaxation and to magnetic field inhomogeneities. Likewise,  $T_2^{**}$ -relaxation includes the effects of both  $T_2^{*}$ -relaxation and the dephasing from magnetic field gradients. As a general rule, the lengths of the time constants for the four relaxation processes have the following relationship:  $T_2^{**} \le T_2^{*} \le T_2 \le T_1$  [19].

Due to the actions of the various relaxation processes, the transverse plane magnetization of a sample during an MR pulse sequence will reach a steady-state value (usually within a few TR cycles) that is less than the net equilibrium magnetization (2.5) for that sample. Expressions for the steady-state transverse magnetization ( $M_{xy}$ ) for different pulse sequences are tabulated in the literature [18]. Of particular interest for this work are the steady state transverse magnetizations for the spin echo and gradient echo imaging sequences which are given in (2.23) and (2.24), respectively. (The terms  $\alpha$  and  $M_z^0$  have been previously defined in section II.1.4. Likewise, the terms TR and TE have been defined in section II.2.2.) Note that the steady-state transverse magnetization for a gradient echo sequence has the same form as that of the spin echo at a tip angle of  $90^{\circ}$ .

$$M_{xy} = M_z^0 (1 - e^{-TR/T_1}) e^{-TE/T_2}$$

(2.23)

$$M_{xy} = M_z^0 \frac{(1 - e^{-TR/T_1})e^{-TE/T_2^*} \sin \alpha}{(1 - \cos \alpha \cdot e^{-TR/T_1})}$$

(2.24)

# II.2.7 Signal-to-Noise Ratio for the MR Signal

An important characteristic of the received MR signal is its voltage signal-to-noise ratio, SNR<sub>v</sub>. This may be calculated by dividing the received signal voltage by the noise voltage. The received signal voltage level during an imaging pulse sequence (2.25) may

be found by taking the magnitude of the of the fid signal from (2.10). In this case, however, the value of the transverse magnetization immediately after the RF pulse,  $M_{xy}^0$ , is replaced by the steady-state transverse magnetization,  $M_{xy}$  (refer to section II.2.6). The primary source of noise in the NMR experiment is due to thermal resistance (or Johnson or Nyquist) noise. The r.m.s. level of thermal noise may be found from (2.26) [21], where k is the Boltzmann constant [J/K], T is the absolute temperature of the noise resistance [K], B is the noise bandwidth [Hz], and B is the resistance of the noise source  $[\Omega]$ . Finally, the voltage SNR of the received MR signal may be computed (2.27).

$$V_{signal} = \sqrt{2}\omega_0 \Delta V M_{xy} B_{1t} \tag{2.25}$$

$$V_{noise} = \sqrt{4kTBR} \tag{2.26}$$

$$SNR_{v} = \frac{V_{signal}}{V_{noise}} = \frac{\sqrt{2}\omega_{0}\Delta VM_{xy}B_{1t}}{\sqrt{4kTBR}}$$

(2.27)

### **II.3 MR Receiver Theory**

The design of the receiver is key in MR imaging as it has a major influence on the quality of the final image. This section will explore several factors which play an important part in the theory and design of the MR receiver. These will include the Nyquist criterion for sampled data, MR signal detection, three methods for performing demodulation, a comparison of quadrature and single phase sensitive detectors, the four main single-channel receiver architectures for MR imaging, how to successfully undersample with a digital receiver, and the two primary receiver architectures for parallel MR imaging using arrays of sensors.

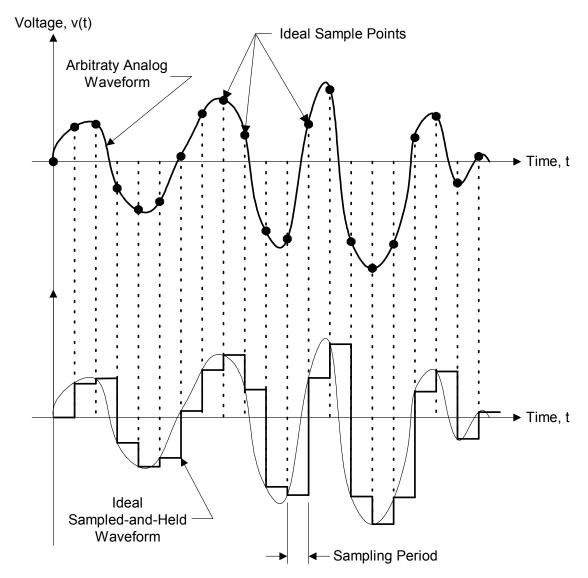

#### II.3.1 Nyquist Criterion for Sampled Signals