# NONLINEARITY AND NOISE MODELING OF OPERATIONAL TRANSCONDUCTANCE AMPLIFIERS FOR CONTINUOUS TIME ANALOG FILTERS

A Thesis

by

# ARUN RAMACHANDRAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

May 2005

Major Subject: Electrical Engineering

# NONLINEARITY AND NOISE MODELING OF OPERATIONAL TRANSCONDUCTANCE AMPLIFIERS FOR CONTINUOUS TIME

# **ANALOG FILTERS**

# A Thesis

by

# ARUN RAMACHANDRAN

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

Approved as to style and content by:

Edgar Sánchez-Sinencio (Chair of Committee)

> Takis Zourntos (Member)

> Gerard L. Cote (Member)

Jose Silva-Martinez (Member)

Steven M. Wright (Member)

Chanan Singh (Head of Department)

May 2005

Major Subject: Electrical Engineering

# ABSTRACT

Nonlinearity and Noise Modeling of Operational Transconductance Amplifiers for Continuous Time Analog Filters. (May 2005)

Arun Ramachandran, B.En., Birla Institute of Technology and Science-Pilani, India;

M.S., Birla Institute of Technology and Science-Pilani, India

Chair of Advisory Committee: Dr. Edgar Sánchez-Sinencio

A general framework for performance optimization of continuous-time OTA-C (Operational Transconductance Amplifier-Capacitor) filters is proposed. Efficient procedures for evaluating nonlinear distortion and noise valid for any filter of arbitrary order are developed based on the matrix description of a general OTA-C filter model . Since these procedures use OTA macromodels, they can be used to obtain the results significantly faster than transistor-level simulation. In the case of transient analysis, the speed-up may be as much as three orders of magnitude without almost no loss of accuracy. This makes it possible to carry out direct numerical optimization of OTA-C filters with respect to important characteristics such as noise performance, THD, IM3, DR or SNR. On the other hand, the general OTA-C filter model allows us to apply matrix transforms that manipulate (rescale) filter element values and/or change topology without changing its transfer function. The above features are a basis to build automated optimization procedures for OTA-C filters. In particular, a systematic optimization procedure using equivalence transformations is proposed. The research also proposes suitable software implementations of the optimization process. The first part of the research proposes a general performance optimization procedure and to verify the process two application type examples are mentioned. An application example of the proposed approach to optimal block sequencing and gain distribution of 8<sup>th</sup> order cascade Butterworth filter (for two variants of OTA topologies) is given. Secondly the modeling tool is used to select the best suitable topology for a 5<sup>th</sup> order Bessel Low Pass Filter. Theoretical results are verified by comparing to transistor-level simulation with

CADENCE. For the purpose of verification, the filters have also been fabricated in standard 0.5µm CMOS process.

The second part of the research proposes a new linearization technique to improve the linearity of an OTA using an Active Error Feedforward technique. Most present day applications require very high linear circuits combined with low noise and low power consumption. An OTA based biquad filter has also been fabricated in  $0.35\mu$ m CMOS process. The measurement results for the filter and the stand alone OTA have been discussed. The research focuses on these issues.

# ACKNOWLEDGMENTS

I wish to express my sincere gratitude to my advisor, Professor Dr. Edgar Sánchez-Sinencio, for his guidance and support in all my academic endeavors at Texas A&M University. His creativity, insight into circuit design, and ability to keep me focused on the whole picture helped me a lot in my research. His sincere dedication to his teachings and his work inspires me a lot. I wish to thank him for not making me feel out of place at any point of time during my stay at Texas A&M University.

I wish to thank Dr. José Silva-Martinez for his constant guidance and encouragement in my thesis work. I have always relished the number of serious discussions we have had during the course of my research.

A special mention of thanks to Dr. Slawomir Koziel and Dr. Antonio Torralba, two visiting faculties from Poland and Seville, Spain, respectively, with whom I had the chance to interact, exchange ideas and learn a lot during my research. I am always indebted to them for the amount of knowledge I gained from them.

I am deeply indebted to Dr. Ugur Cilingiroglu who has always been a source of my inspiration during my academic stay at Texas A&M University. I have enjoyed and relished every lecture of his.

I wish to express my sincere gratitude to my committee members Dr. Takis Zourntos, Dr. Steven M. Wright, Dr. Gerard L. Cote, for being a part of my thesis committee and for sparing their time and valuable suggestions on my research work

A special note of thanks to Ms. Ella Gallagher, who has always been more than a friend to me. I have never missed home in her presence. She keeps giving me the courage and encouragement and she always installed the notion that we are here to achieve something. I owe a lot to her for this valuable lesson.

I wish to thank all my fellow graduate students here at the Analog and Mixed Signal Center for all their support during my stay here. We have shared a lot of information on the technical and cultural fronts. I thank them for the opportunity given to me learn about the various cultures across the globe. I wish to acknowledge my roommates and friends here at Texas A&M University, who are not a direct part of the AMSC group, for having stood by me in all that I have done. I shall ever be indebted to them.

I could not have achieved this but for the help, guidance and blessings of my parents, my sister, her husband and my wonderful and most adorable niece Mytreyi. They have always believed that I could do it.

Words of thanks will not suffice to express my sincere gratitude to Bhagawan Sri Sathya Sai Baba, who has been the divine light within me. In my own words "Koti Pranams Swami".

# **TABLE OF CONTENTS**

| ABSTRA    | СТ                                                                                                                           | iii      |

|-----------|------------------------------------------------------------------------------------------------------------------------------|----------|

| ACKNOW    | LEDGMENTS                                                                                                                    | v        |

| TABLE O   | F CONTENTS                                                                                                                   | vii      |

| LIST OF F | FIGURES                                                                                                                      | X        |

| LIST OF 7 | TABLES                                                                                                                       | xvi      |

| CHAPTER   | R                                                                                                                            |          |

| Ι         | INTRODUCTION                                                                                                                 | 1        |

|           | <ul><li>1.1. Motivation and Background</li><li>1.1.1. Digital Filters</li><li>1.1.2. Sampled-Data Filters</li></ul>          | 2<br>3   |

|           | <ul><li>1.1.3. Continuous Time Filters</li><li>1.2. Continuous Time Analog Filters</li><li>1.2.1. Passive Filters</li></ul>  | 5        |

|           | 1.2.1.1. RLC Filters<br>1.2.1.2. Surface Acoustic Filters<br>1.2.1.3. MEMS Filters                                           | 7<br>8   |

|           | 1.2.2. Active Filters<br>1.2.2.1. Active-RC Filters<br>1.2.2.2. OTA-C Filters                                                | 10<br>11 |

|           | 1.2.2.3. MOSFET-C Filters<br>1.2.2.4. Current Mode Filters                                                                   | 13<br>14 |

|           | <ul><li>1.3. Filter Design Procedure</li><li>1.3.1. Filter Specifications</li><li>1.3.2. The Approximation Problem</li></ul> | 19       |

|           | <ul> <li>1.3.3. Filter Class</li> <li>1.3.4. Filter Topology</li> <li>1.2.4.1. Coccede Terrelegy</li> </ul>                  | 21       |

|           | <ul><li>1.3.4.1. Cascade Topology</li><li>1.3.4.2. Leapfrog Topology</li><li>1.3.4.3. Summed-feedback Topology</li></ul>     | 23       |

|           | 1.3.4.4. LC Ladder Simulation         1.4. Active Blocks Design Considerations                                               | 25<br>25 |

|           | <ul><li>1.4.1. Noise</li><li>1.4.2. Non-Linearity</li><li>1.5. Organization</li></ul>                                        | 27       |

|           |                                                                                                                              |          |

| II  | NONLINEARITY AND NOISE MODELING OF OTA-C FILTERS                                                                                         | .34                                                                                                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|     | 2.1. Motivation and Background                                                                                                           | .34                                                                                                   |

|     | 2.1.1. Transconductor Amplifier                                                                                                          |                                                                                                       |

|     | 2.1.2. Differential Input Operational Transconductor Amplifiers                                                                          |                                                                                                       |

|     | 2.1.2.1. Macromodel of the OTA                                                                                                           |                                                                                                       |

|     | 2.1.3. Simple Applications of OTA                                                                                                        |                                                                                                       |

|     | 2.1.3.1. Voltage Amplifier / Integrator                                                                                                  |                                                                                                       |

|     | 2.1.3.2. Voltage Variable Resistor                                                                                                       |                                                                                                       |

|     | 2.1.3.3. Voltage Summation                                                                                                               |                                                                                                       |

|     | 2.1.3.4. Integrator                                                                                                                      |                                                                                                       |

|     | 2.1.4. Non Idealities of OTA                                                                                                             |                                                                                                       |

|     | 2.1.4.1. Non-Linearity of the OTA                                                                                                        |                                                                                                       |

|     | 2.1.4.2. Capacitor Non-Linearity                                                                                                         |                                                                                                       |

|     | 2.2. Proposed Generalized Non-Linearity and Noise Modeling Approach                                                                      |                                                                                                       |

|     | 2.2.1. A General Structure of a Gm-C (OTA-C) Filter                                                                                      |                                                                                                       |

|     | 2.2.2. Dynamics of Nonlinear OTA-C Filters                                                                                               |                                                                                                       |

|     | 2.2.3. Noise Analysis in General OTA-C Filters                                                                                           |                                                                                                       |

|     | 2.2.4. Verification of the Nonlinearity and Noise Analysis Tool                                                                          |                                                                                                       |

|     | 2.2.5. Performance Optimization of OTA-C Filters                                                                                         |                                                                                                       |

|     | 2.3. Conclusion                                                                                                                          |                                                                                                       |

| III | A LINEARIZED CMOS OTA USING ACTIVE ERROR<br>FEED-FORWARD TECHNIQUE                                                                       | .96                                                                                                   |

|     |                                                                                                                                          |                                                                                                       |

|     | 3.1. Motivation and Background                                                                                                           |                                                                                                       |

|     | 3.1. Motivation and Background<br>3.1.1 Linearization Techniques                                                                         | .96                                                                                                   |

|     | 3.1.1 Linearization Techniques                                                                                                           | .96<br>.97                                                                                            |

|     | 3.1.1 Linearization Techniques<br>3.1.1.1 Source Degeneration                                                                            | .96<br>.97<br>100                                                                                     |

|     | 3.1.1 Linearization Techniques      3.1.1.1 Source Degeneration      3.1.1.2 Attenuation                                                 | .96<br>.97<br>100<br>100                                                                              |

|     | 3.1.1 Linearization Techniques         3.1.1.1 Source Degeneration         3.1.1.2 Attenuation         3.1.1.3 Combination of Techniques | .96<br>.97<br>100<br>100                                                                              |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>100<br>103<br>106                                                                |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>100<br>103<br>106<br>107                                                         |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>100<br>103<br>106<br>107<br>110                                                  |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>100<br>103<br>106<br>107<br>110                                                  |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>103<br>106<br>107<br>110<br>111                                                  |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>103<br>106<br>107<br>110<br>111<br>115<br>116                                    |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>100<br>103<br>106<br>107<br>110<br>111<br>115<br>116                             |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>103<br>106<br>107<br>110<br>111<br>115<br>116<br>118<br>120                      |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>103<br>106<br>107<br>110<br>111<br>115<br>116<br>118<br>120                      |

|     | <ul> <li>3.1.1 Linearization Techniques</li></ul>                                                                                        | .96<br>.97<br>100<br>100<br>103<br>106<br>107<br>110<br>111<br>115<br>116<br>116<br>118<br>120<br>121 |

| CHAPTER                                      | Page |

|----------------------------------------------|------|

| 3.3.7 Measurement Results<br>3.4. Conclusion |      |

| IV CONCLUSION                                |      |

| REFERENCES                                   | 140  |

| APPENDIX A                                   |      |

| APPENDIX B                                   | 165  |

| VITA                                         | 170  |

# LIST OF FIGURES

| Fig. 1.1. A typical digital processing system                                      |

|------------------------------------------------------------------------------------|

| Fig. 1.2. A typical digital filtering example                                      |

| Fig. 1.3. Sampling of a continuous time waveform                                   |

| Fig. 1.4. A switched-capacitor (SC) filter application4                            |

| Fig. 1.5. Wide range of filter applications                                        |

| Fig. 1.6. A classical second order low pass RLC filter7                            |

| Fig. 1.7. Simple transversal SAW filter9                                           |

| Fig. 1.8. Unity gain Sallen and Key low pass filter11                              |

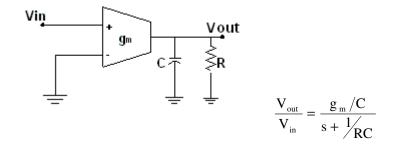

| Fig. 1.9. Simple low pass OTA-C filter with a fixed pole and adjustable gain13     |

| Fig. 1.10. Voltage mode to current mode transformation                             |

| Fig. 1.11. Non-inverting current mode integrator14                                 |

| Fig. 1.12. Data flow for continuous time filter design procedure                   |

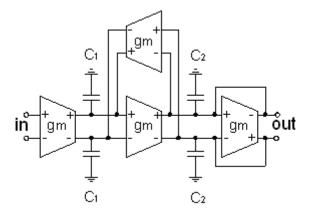

| Fig. 1.13a. OTA-C biquad section                                                   |

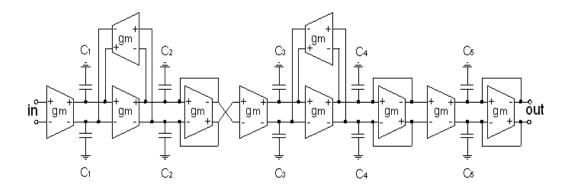

| Fig. 1.13b. 5 <sup>th</sup> order Bessel OTA-C filter (cascade 2:2:1)              |

| Fig. 1.14. Leapfrog topology23                                                     |

| Fig. 1.15. Summed-feedback topology                                                |

| Fig. 1.16. Follow-the-leader feedback (FLF) topology                               |

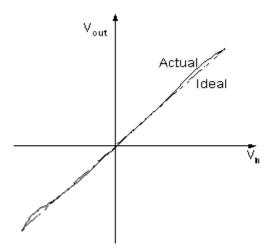

| Fig. 1.17. Input/output characteristic of a nonlinear system                       |

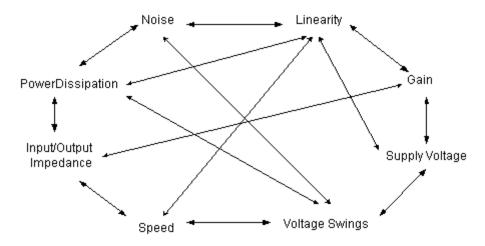

| Fig. 1.18. Analog design octagon showing the relation between various parameters31 |

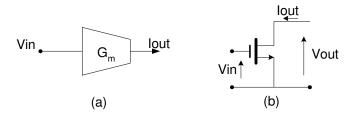

| Fig. 2.1. (a) Transconductor cell (b) Simple MOS transconductor cell               |

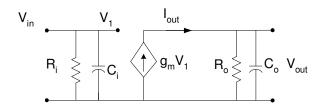

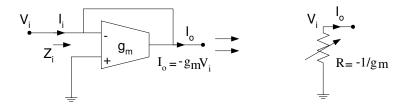

| Fig. 2.2. Macromodel of transconductor cell in Fig. 2.1b                                                                                                      | 37 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

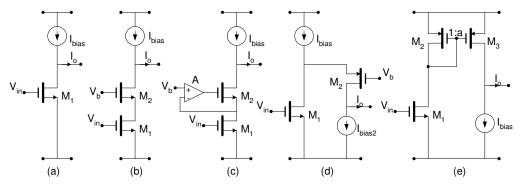

| Fig. 2.3. Single input transconductor implementations: (a) Simple negative, (b) Cas-ode, (c) Enhanced, (d) Folded-cascode, (e) Simple positive transconductor |    |

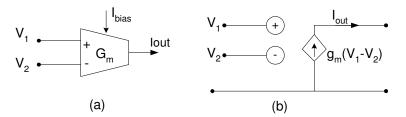

| Fig. 2.4. (a) OTA symbol, (b) Ideal equivalent circuit                                                                                                        | 40 |

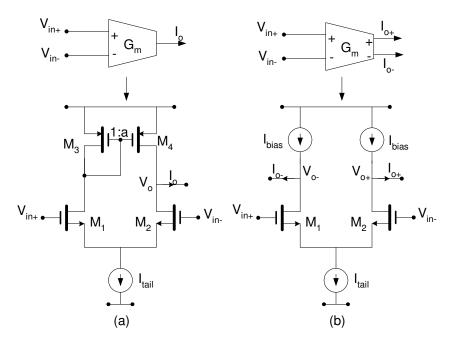

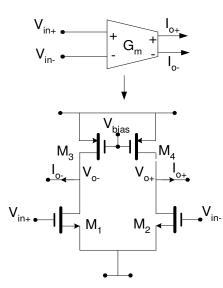

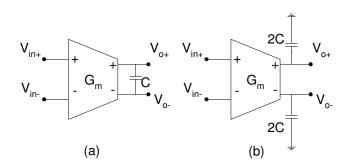

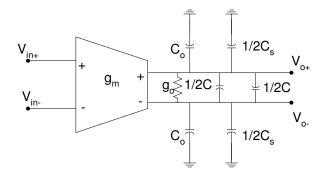

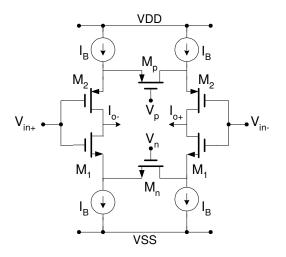

| Fig. 2.5. (a) Single ended differential OTA, (b) conventional fully differential OTA                                                                          | 41 |

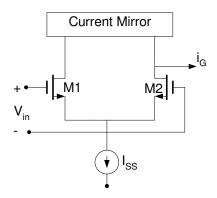

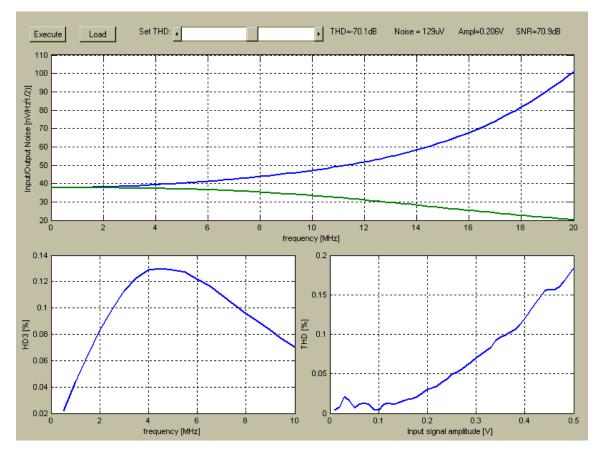

| Fig. 2.6. A simple pseudo-differential OTA                                                                                                                    | 42 |

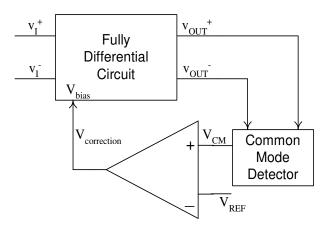

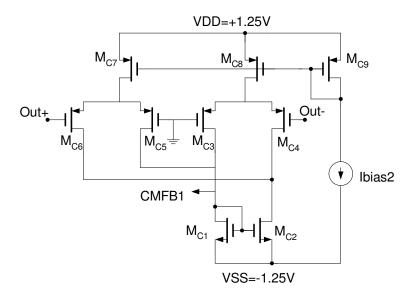

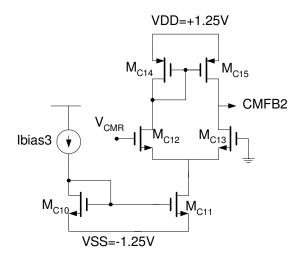

| Fig. 2.7. Conventional common mode feedback (CMFB) loop                                                                                                       | 43 |

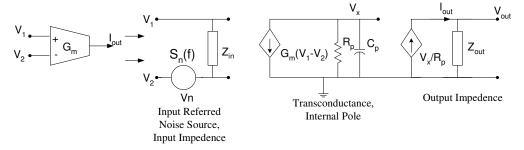

| Fig. 2.8. Non-linear OTA macro model                                                                                                                          | 44 |

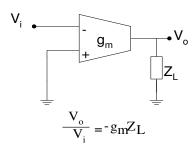

| Fig. 2.9. OTA with load                                                                                                                                       | 46 |

| Fig. 2.10. Grounded voltage variable resistor                                                                                                                 | 46 |

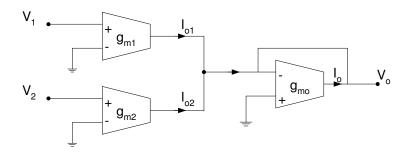

| Fig. 2.11. Voltage summation                                                                                                                                  | 47 |

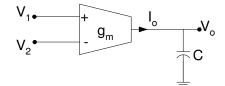

| Fig. 2.12. First order integrator                                                                                                                             | 48 |

| Fig. 2.13. Integrator with (a) floating capacitors, (b) grounded capacitors                                                                                   | 48 |

| Fig. 2.14. Parasitic capacitors associated with OTA-C structure                                                                                               | 49 |

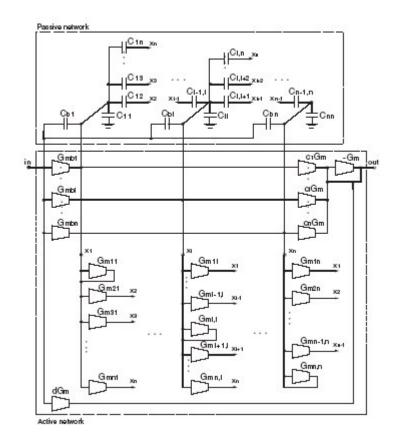

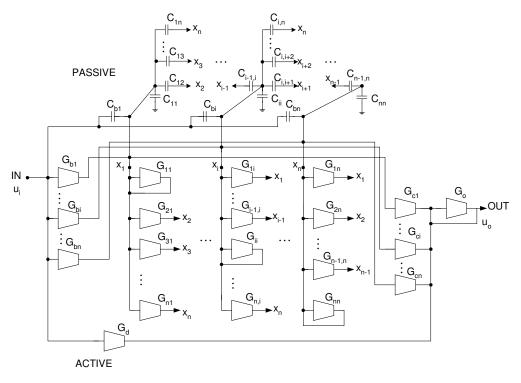

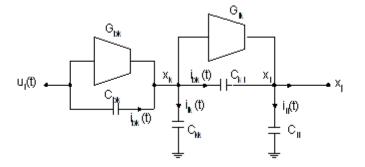

| Fig. 2.15. The general structure of a voltage mode Gm-C filter                                                                                                | 54 |

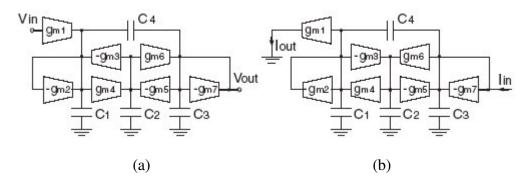

| Fig. 2.16. Third order Elliptic Gm-C filter (a) voltage mode and (b) current mode                                                                             | 57 |

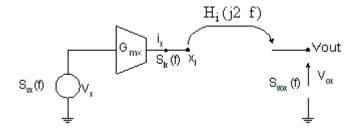

| Fig. 2.17. Generalized structure of OTA-C filter                                                                                                              | 59 |

| Fig. 2.18. Structure for notation representation                                                                                                              | 60 |

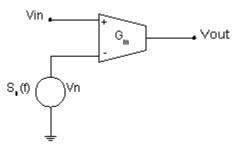

| Fig. 2.19. Noise representation in an OTA with an equivalent voltage source                                                                                   | 65 |

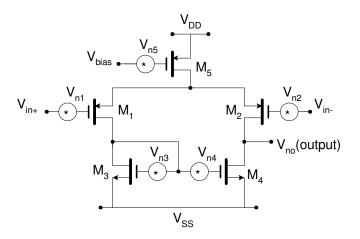

| Fig. 2.20. A CMOS input stage with voltage noise sources                                                                                                      | 66 |

| Fig. 2.21. | Noise contributions of an individual filter transconductor to the output noise of the filter                                                                                                   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.22. | Simple differential pair71                                                                                                                                                                     |

| Fig. 2.23. | 3 <sup>rd</sup> order Butterworth low pass filter (leap frog structure)72                                                                                                                      |

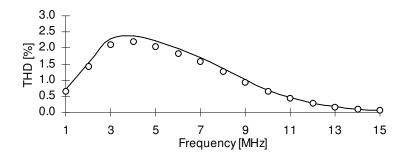

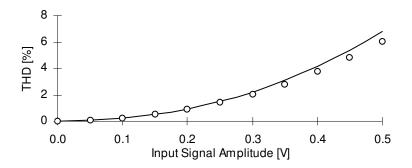

| Fig. 2.24. | THD vs. frequency for 3 <sup>rd</sup> order low pass filter in Fig. 2.23 with 0.3V input amplitude: theoretical data (line), and simulation (points)                                           |

| Fig. 2.25. | THD vs. input signal amplitude for 3 <sup>rd</sup> low pass filter in Fig. 2.23 with 5MHz sine wave: theoretical data (line), and simulation (points)72                                        |

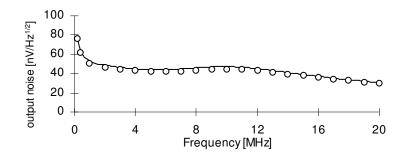

| Fig. 2.26. | Output noise spectrum vs. frequency for 3 <sup>rd</sup> low pass filter in Fig. 2.23: theoretical data (line), and simulation (points)73                                                       |

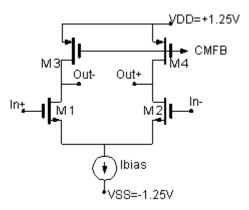

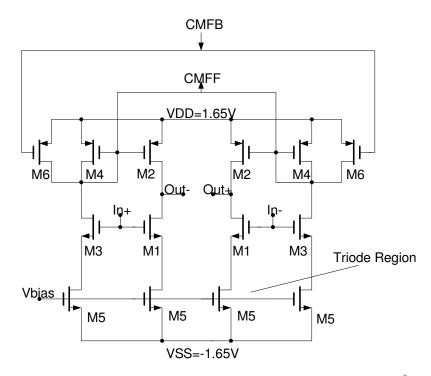

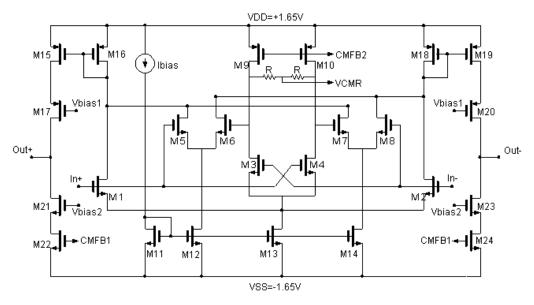

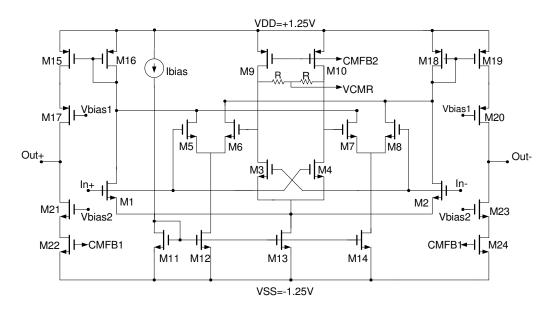

| Fig. 2.27. | Fully balanced fully symmetric pseudo differential OTA [75]74                                                                                                                                  |

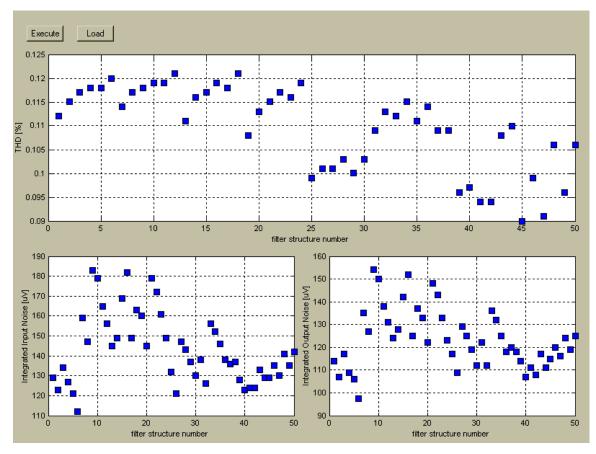

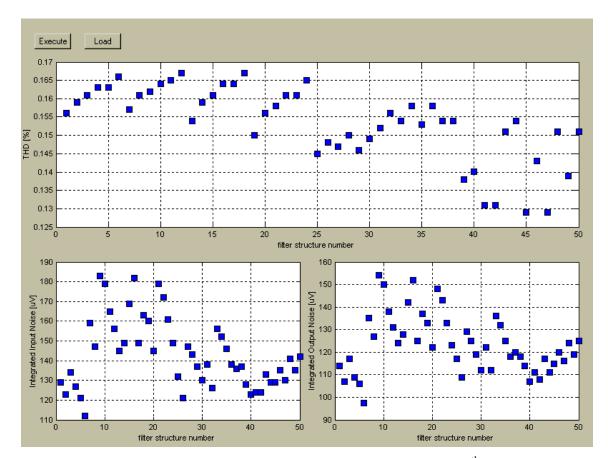

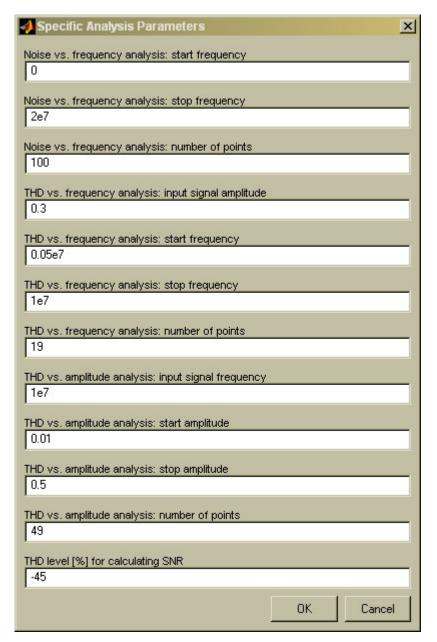

| Fig. 2.28. | Output window of the modeling tool showing the performance of the various structures for THD and noise                                                                                         |

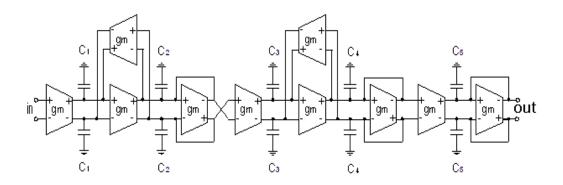

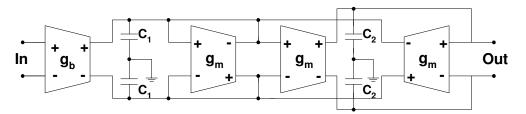

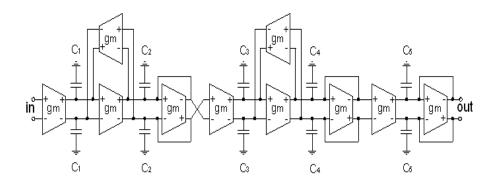

| Fig. 2.29. | Cascade structure for the 5 <sup>th</sup> order Bessel filter (2:2:1)77                                                                                                                        |

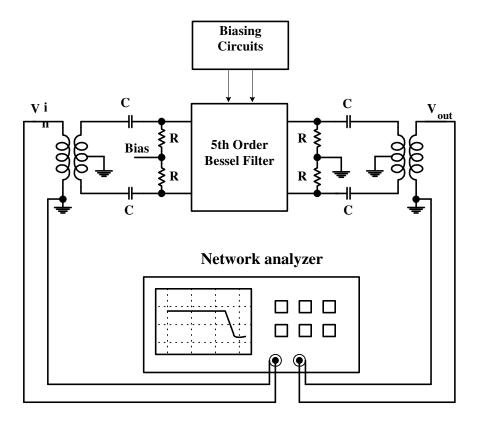

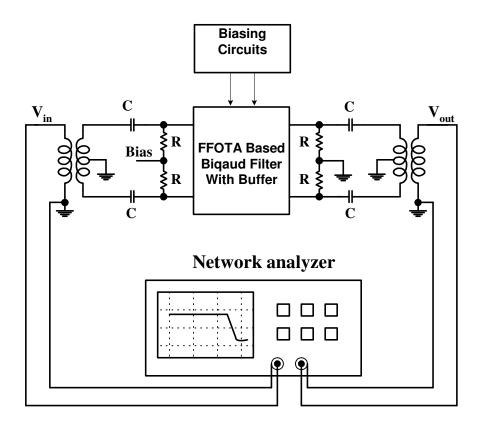

| Fig. 2.30. | Set-up for transfer function measurements                                                                                                                                                      |

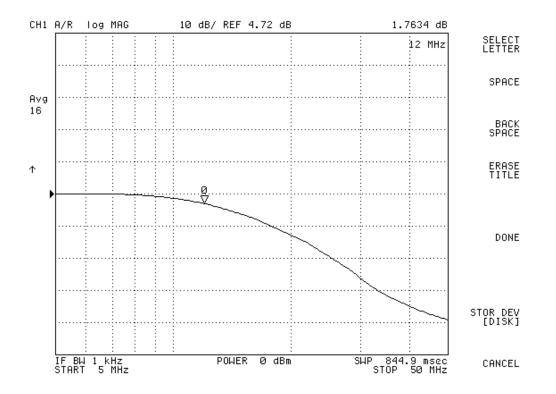

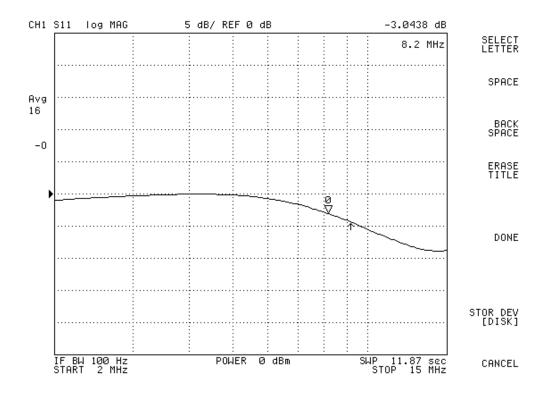

| Fig. 2.31. | Filter transfer function for the 5 <sup>th</sup> order Bessel low pass filter -cascade structure using OTA shown in Fig. 2.27 [75]                                                             |

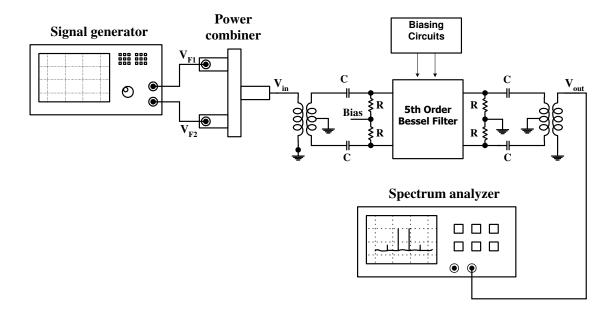

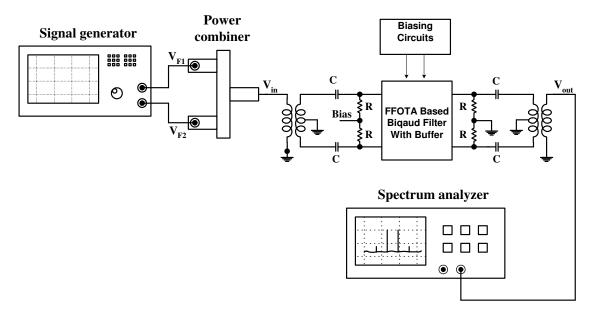

| Fig. 2.32. | Set-up to measure intermodulation distortion using the spectrum analyzer 80                                                                                                                    |

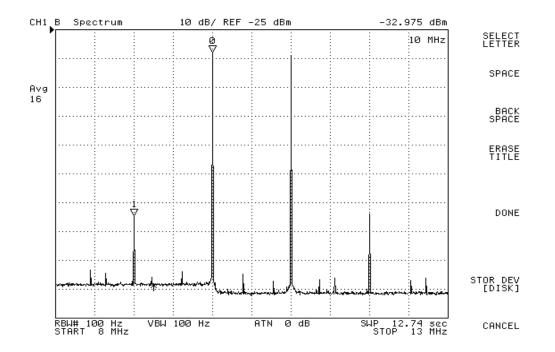

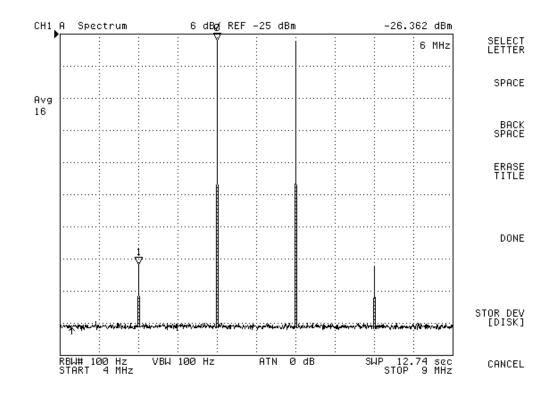

| Fig. 2.33. | Two tone measurement results for IM3 at 10MHz and 11MHz for a 0.5V input amplitude for the 5 <sup>th</sup> order Bessel filter                                                                 |

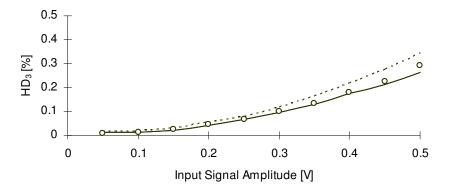

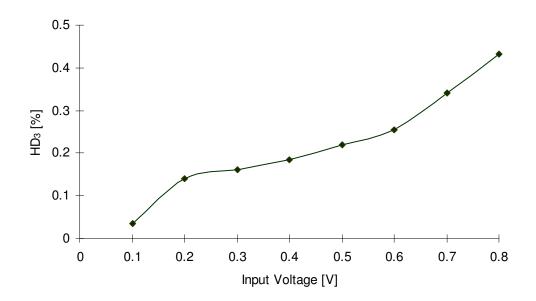

| Fig. 2.34. | HD <sub>3</sub> vs. input signal amplitude for filter in Fig. 2.29 with 10MHz sine wave: theoretical data (solid line), SPICE simulation (points), and experimental measurements (dashed line) |

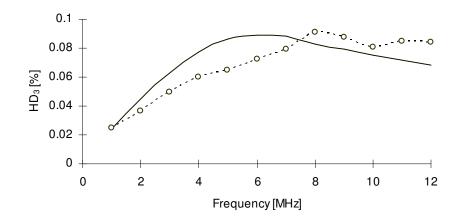

| Fig. 2.35. | HD <sub>3</sub> vs. input signal frequency for filter in Fig. 2.29 for an input signal amplitude of 0.25 V: theoretical (solid line), experimental (dashed line)82                             |

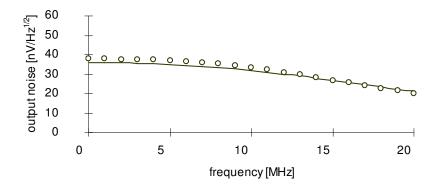

| Fig. 2.36. Output noise spectrum vs. frequency for filter in Fig. 2.29: theoretical data (solid line), and Spice simulation (points) |      |

|--------------------------------------------------------------------------------------------------------------------------------------|------|

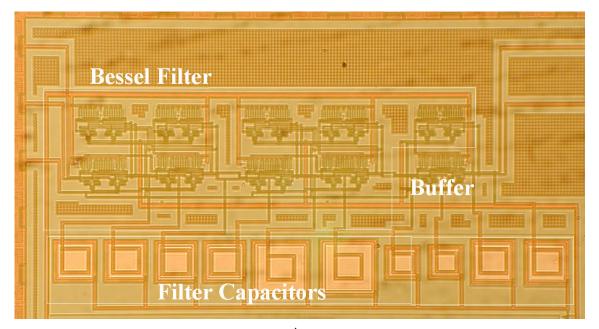

| Fig. 2.37. Micro photograph of the 5 <sup>th</sup> order Bessel low pass filter (cascade)                                            | 84   |

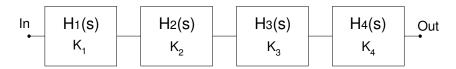

| Fig. 2.38. Block diagram of $8^{th}$ order cascade filter (K <sub>i</sub> =H <sub>i</sub> (0))                                       | 88   |

| Fig. 2.39. Fully differential biquad used in the filter of Fig. 2.38                                                                 | 88   |

| Fig. 2.40. Variant I- simple differential pair                                                                                       | 90   |

| Fig. 2.41. Variant II – linearized OTA [75]                                                                                          | 90   |

| Fig. 2.42. Variant III- linearized OTA [78]                                                                                          | 91   |

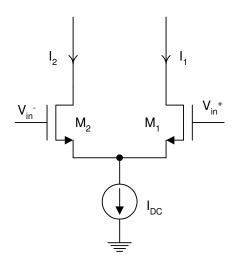

| Fig. 3.1. Simple differential pair                                                                                                   | 98   |

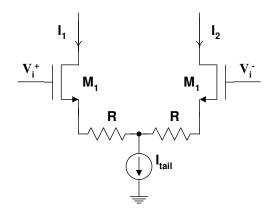

| Fig. 3.2. Linearization using source degeneration                                                                                    | .100 |

| Fig. 3.3. Linearization using series of differential pairs                                                                           | .101 |

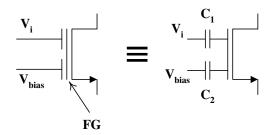

| Fig. 3.4. Linearization using floating gates [88]                                                                                    | .102 |

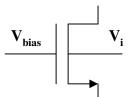

| Fig. 3.5. Linearization using bulk driven transistor [89]                                                                            | .103 |

| Fig. 3.6. Linearization technique using voltage division, source degeneration, cross coupling                                        | .104 |

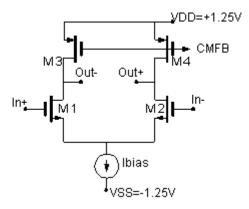

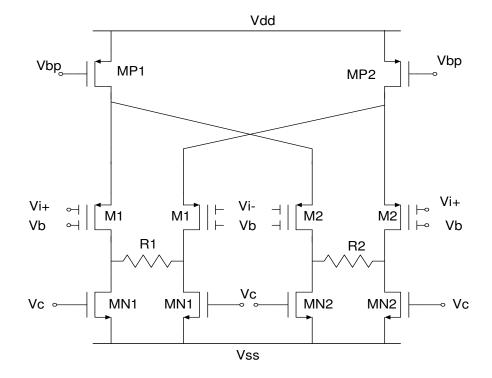

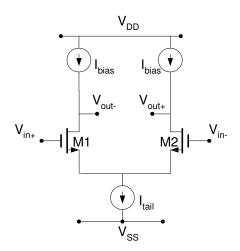

| Fig. 3.7. Fully balanced, fully symmetric pseudo-differential OTA [75]                                                               | .105 |

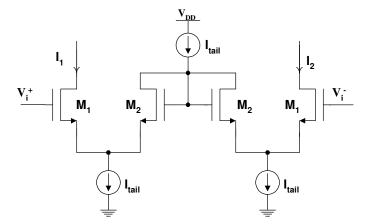

| Fig. 3.8. Complimentary differential pair OTA                                                                                        | .106 |

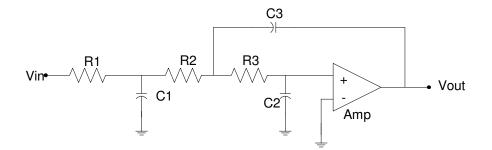

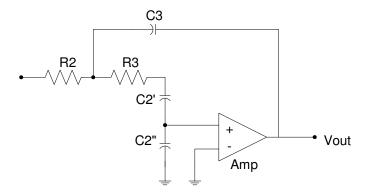

| Fig. 3.9. 3 <sup>rd</sup> order filter for VDSL applications                                                                         | .108 |

| Fig. 3.10. Signal attenuation at the input of the amplifier                                                                          | .109 |

| Fig. 3.11. Linear OTA for the VDSL filter                                                                                            | .109 |

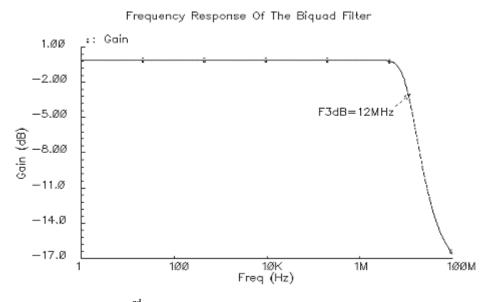

| Fig. 3.12. 3 <sup>rd</sup> order Butterworth filter's magnitude response                                                             | .113 |

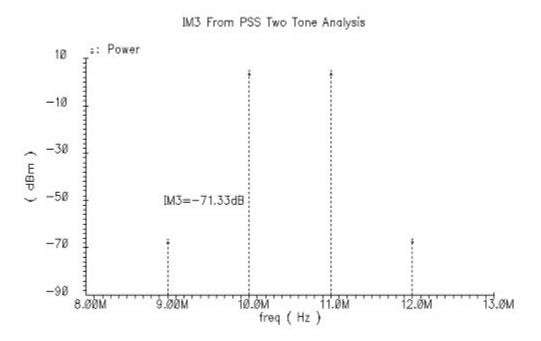

| Fig. 3.13. Two tone analysis results for IM3 simulation for two equal tones of 1Vpp at 10MHz and 11MHz for the 3 <sup>rd</sup> order filter                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

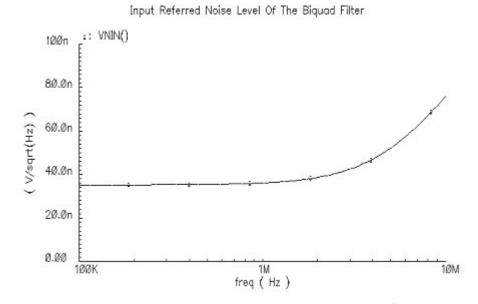

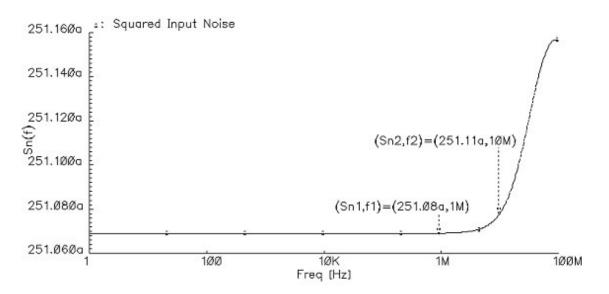

| Fig. 3.14. Input referred noise spectral density for the 3 <sup>rd</sup> order filter                                                                               |

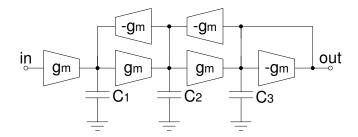

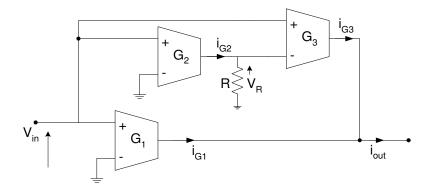

| Fig. 3.15. Three block feed-forward transconductance amplifier                                                                                                      |

| Fig. 3.16. Simple CMOS differential pair transconductor                                                                                                             |

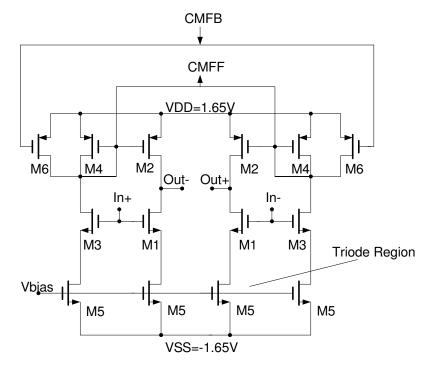

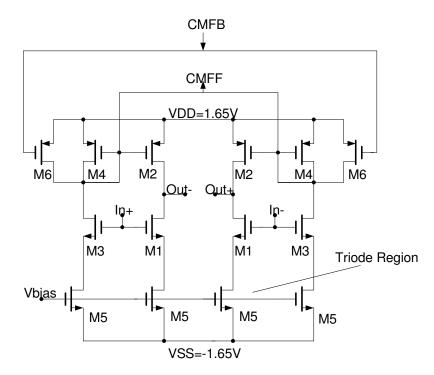

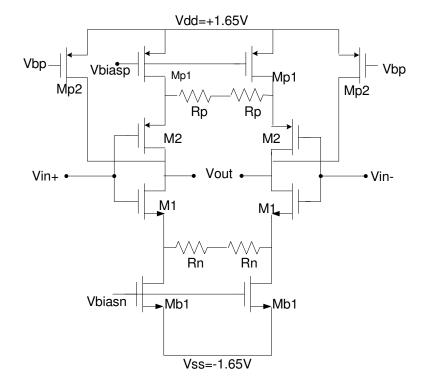

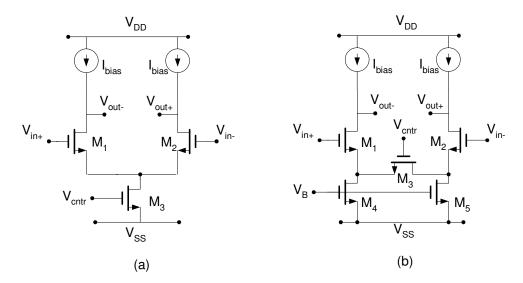

| Fig. 3.17. Linearized CMOS OTA based on active-error feedforward technique [78].12                                                                                  |

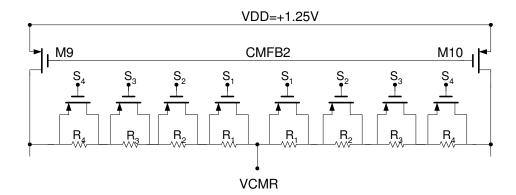

| Fig. 3.18. Output common mode feedback circuit (CMFB1)                                                                                                              |

| Fig. 3.19. Common mode feedback for the resistor biasing circuit (CMFB2)12.                                                                                         |

| Fig. 3.20. Tuning circuitry for the OTA124                                                                                                                          |

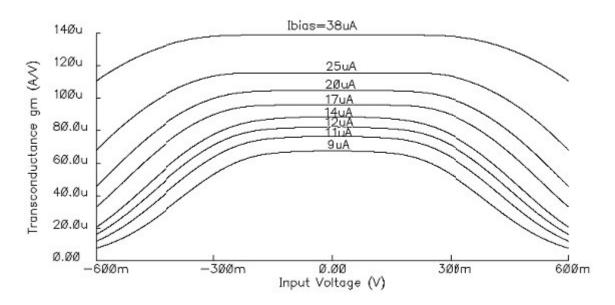

| Fig. 3.21. Gm tuning from $70\mu A/V-140\mu A/V$ , of the OTA, using the biasing current123                                                                         |

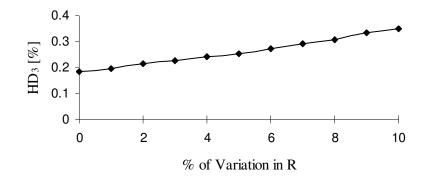

| Fig. 3.22. Variations in HD <sub>3</sub> vs. % variations of the resistor values                                                                                    |

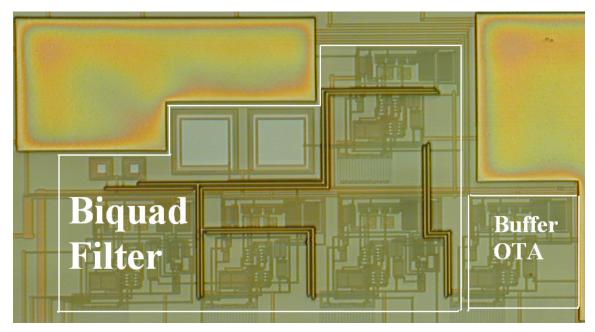

| Fig. 3.23. Chip micrograph of the biquad filter along with the buffer OTA127                                                                                        |

| Fig. 3.24. Set-up to measure intermodulation distortion (IM <sub>3</sub> , IM <sub>5</sub> )127                                                                     |

| Fig. 3.25. Set-up for transfer function measurements                                                                                                                |

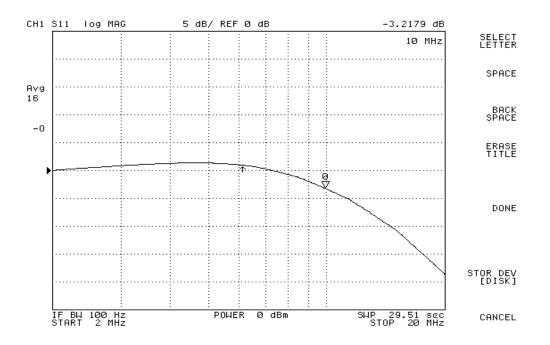

| Fig. 3.26. Biquad filter transfer characteristic- magnitude response                                                                                                |

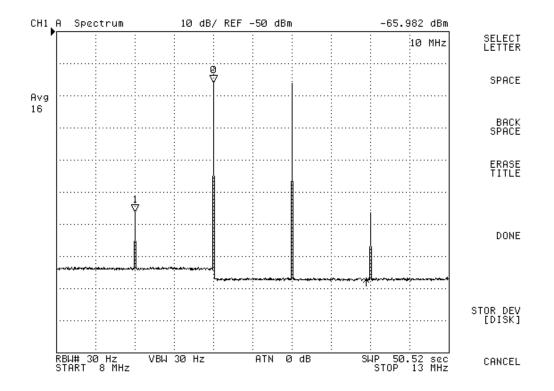

| Fig. 3.27. $IM_3$ measurement for two equal tones of 0.6V at 10MHz and 11MHz130                                                                                     |

| Fig. 3.28. Biquad filter's magnitude response for a 2KΩ resistor at the output of the buffer                                                                        |

| Fig. 3.29. Two tone measurement results for two equal tones of 0.5V amplitude at $6MHz$ and $7MHz$ for the biquad filter with $2K\Omega$ at the output of buffer132 |

| Fig. 3.30. $HD_3$ vs. input amplitude for an input signal at 10MHz for the biquad filter 133                                                                        |

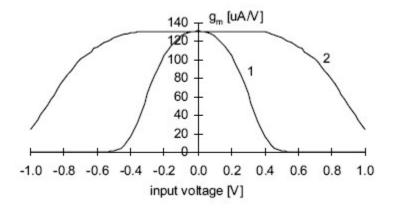

| Fig. 3.31. Transconductance vs. input voltage (a) simple differential pair,<br>(b) with linearization                                                               |

xiv

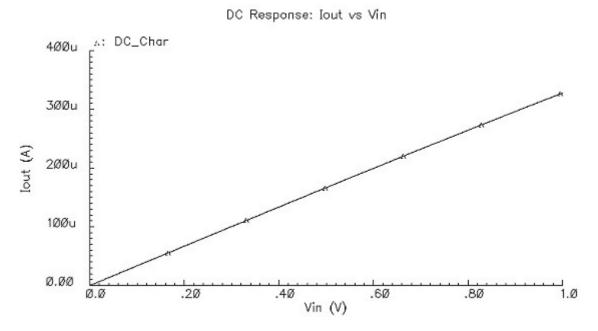

| Fig. A.1. Non-linear DC characteristic: input-output relation for the OTA [75]154                  |

|----------------------------------------------------------------------------------------------------|

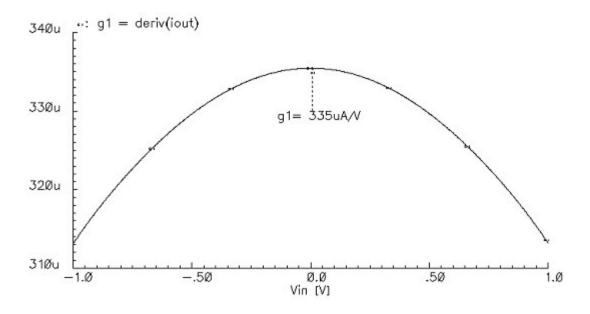

| Fig. A.2. Extraction of $g_1$ from the nonlinear DC characteristic of the OTA [75]155              |

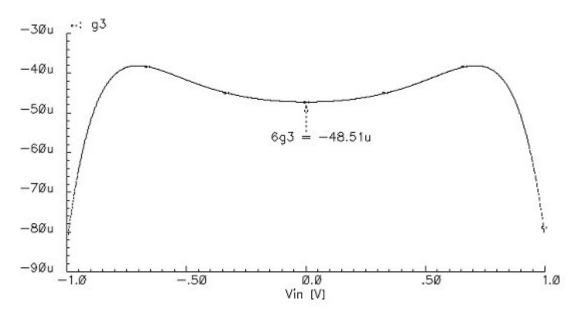

| Fig. A.3. Extraction of $g_3$ from the nonlinear DC characteristic of the OTA [75]156              |

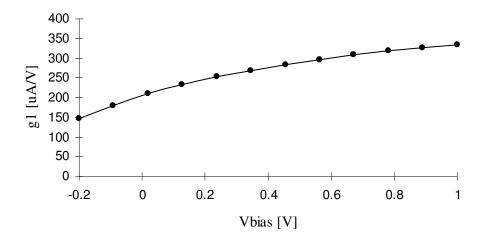

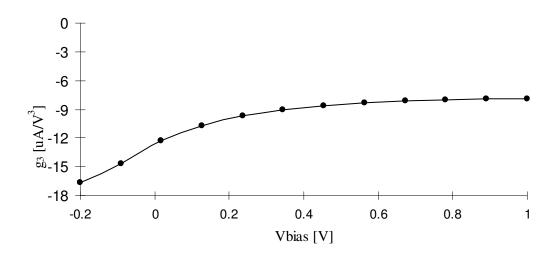

| Fig. A.4. Variation of $g_1$ with respect to $V_{bias}$ for the linear OTA [75]158                 |

| Fig. A.5. Variation of $g_3$ with respect to $V_{bias}$ for the linear OTA [75]158                 |

| Fig. A.6. Noise simulation in CADENCE to extract the noise parameters159                           |

| Fig. A.7. Cascade implementation of the 5 <sup>th</sup> order Bessel filter using OTA [75]160      |

| Fig. A.8. Input menu of the modeling tool161                                                       |

| Fig. A.9. THD and noise results for all the 50 structures of the 5 <sup>th</sup> order filter162   |

| Fig. A.10. Input menu to analyze a particular structure                                            |

| Fig. A.11. Output window for a single structure analysis164                                        |

| Fig. B.1. Simple differential pair with a tail current source166                                   |

| Fig. B.2. OTA g <sub>m</sub> -tuning (a) tail current adjustment (b) source degeneration167        |

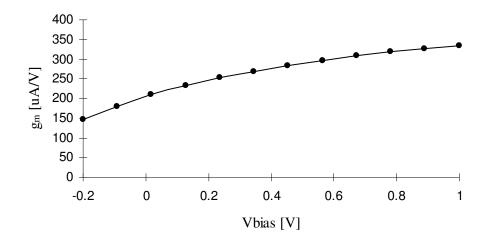

| Fig. B.3. Variation of g <sub>m</sub> with respect to V <sub>bias</sub> for the linear OTA [75]168 |

# LIST OF TABLES

| Page                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------|

| Table 1.1. Comparison of Filter Categories    16                                                                               |

| Table 1.2. Comparison of the Continuous Time Filter Types                                                                      |

| Table 1.3. Comparison of Filter Topologies    25                                                                               |

| Table 2.1. Transconductance for Various Modes of Operation                                                                     |

| Table 2.2. Properties of Simple (Single Input/ Single Output) Transconductors                                                  |

| Table 2.3. Parameters for OTA Used in the 5 <sup>th</sup> Order Bessel Filter [75]75                                           |

| Table 2.4. Performance Comparisons Among the Structures for the 5 <sup>th</sup> Order Bessel      Filter                       |

| Table 2.5. Parameters for Reference Filter Combination H1H2H3H492                                                              |

| Table 2.6. Optimization Results for the 8 <sup>th</sup> Order Cascade Filter (in Fig. 2.38) Using         Variant I OTA        |

| Table 2.7. Optimization Results for the 8 <sup>th</sup> Order Cascade Filter (in Fig. 2.38) Using         Variant II OTA [75]  |

| Table 2.8. Optimization Results for the 8 <sup>th</sup> Order Cascade Filter (in Fig. 2.38) Using         Variant III OTA [78] |

| Table 3.1. Attenuation Factors for Different Techniques    103                                                                 |

| Table 3.2. Amplifier Simulation Results    112                                                                                 |

| Table 3.3. Filter Simulation Results    112                                                                                    |

| Table 3.4. Comparison of VDSL Results                                                                                          |

| Table 3.5. Filter Performance Parameters    134                                                                                |

| Table 3.6. Comparison of This Work with Published Material    135                                                              |

|                                            | Page |

|--------------------------------------------|------|

| Table A.1. Nonlinear Parameters Extraction | 157  |

# **CHAPTER I**

# **INTRODUCTION**

#### **1.1. Motivation and Background**

Real-world signals contain both wanted and unwanted information. Therefore, some kind of electronic signal filtering technique must separate the two before processing and analysis can begin. Every electronic design project produces signals that require electronic signal filtering, processing, or amplification, from simple gain to the most complex digital-signal processing (DSP). As mentioned, in any system that interfaces with the real world, the quantity to be measured and later processed is always contaminated with noise and interferes. A filter is usually used in order to eliminate the unwanted noise and reject the surrounding interferes. Although we are living in a digital age, any system that interfaces with the real world, i.e., the analog world, will find use for continuous-time filters.

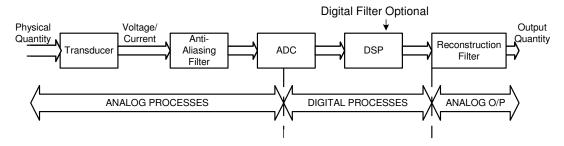

Some of the common applications of filters are in communication systems [1]-[3], bio-medical systems [4] etc, where it is essential to eliminate or separate the useful information from the noise signals. A typical digital processing system is shown in Fig. 1.1. The physical quantity to be processed is converted to an electrical signal (current or voltage) via a transducer. This signal is then converted to a digital signal via an analog to digital converter (ADC) for further processing by the digital signal processor (DSP). The physical quantity, which is measured, is mixed with the noise signals present inherent in the environment, noise from the transducer circuits etc. These noise signals have some high frequency components. According to Nyquist theory and to avoid aliasing, the input signal must be band-limited before the analog to digital (A/D) conversion.

This thesis follows the style and format of IEEE Journal of Solid-State Circuits.

This is achieved by a low-pass filter (anti-aliasing filter) that limits the bandwidth of the signal to half the sampling rate of the ADC. The processed digital signal coming out of the DSP is converted back to an analog signal via a low-pass reconstruction filter. Both the anti-aliasing filter and the reconstruction filter are analog filters operating in continuous-time.

Fig. 1.1. A typical digital processing system

The filter circuit used in any application can be of three different types depending on the type of signals handled. The general types of filters used in most applications are digital filters, continuous-time filters (Analog) and sampled-data filters.

## **1.1.1 Digital Filters**

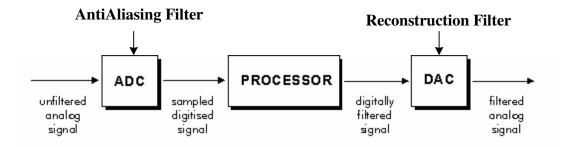

A digital filter [5] uses a digital processor to perform numerical calculations on sampled values of the signal. The processor may be a general-purpose computer such as a PC, or a specialized DSP chip. The analog input signal must first be sampled and digitized using an ADC. The resulting binary numbers, representing successive sampled values of the input signal, are transferred to the processor, which carries out numerical calculations on them. These calculations typically involve multiplying the input values by constants and adding the products together. If necessary, the results of these calculations, which now represent sampled values of the filtered signal, are output through a DAC (digital to analog converter) to convert the signal back to analog form. In a digital filter, the signal is always represented by a sequence of numbers, rather than a voltage or current. Fig. 1.2 shows the basic setup of such a system. Fig. 1.2 combines the anti-aliasing filter and ADC together and the reconstruction filter with that of the DAC to focus more on the digital filtering block.

Fig. 1.2. A typical digital filtering example

## 1.1.2 Sampled-Data Filters

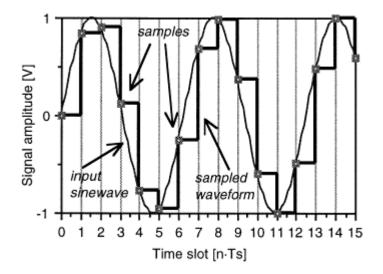

Sampled-data filters do not work with the digital representation of the signal samples, as digital filters do, they rather operate on samples of the signal itself. But both the digital filters and sampled-data filters are characterized in the Z-domain. Thus these filters are discontinuous in time but continuous in processed data values. The best-known example of such an approach is that of switched-capacitor (SC) filters. An SC filter is a continuous-amplitude, sampled-data system. This means that the amplitude of the signals can assume any value within the possible range in a continuous manner. On the other hand, these values are assumed at certain time instants and then they are held for the entire sampling period. Thus, the resulting waveforms are not continuous in time but look like a staircase. Fig. 1.3 describes how an input continuous time signal can be sampled. The sampling operation extracts from the continuous-time waveform the values of the input signal at the instant  $n \cdot Ts$  (n = 1, 2, 3, ...), where Ts is the sampling period (Ts = 1/Fs).

Fig. 1.3. Sampling of a continuous time waveform

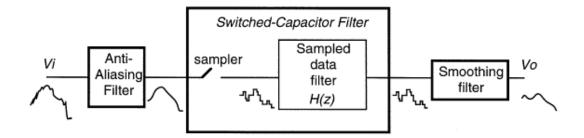

The switched capacitor filter can be used in an application [6]-[7] similar to those shown in Fig. 1.1 and 1.2. Fig. 1.4 shows the usage of SC filter in the standard application example. Due to the sampling operation involved, continuous-time (CT) anti-aliasing filter and reconstruction (smoothing) filter are still needed in those kinds of switched-capacitor systems. However these CT filters are not required to have a high accuracy.

Fig. 1.4. A switched-capacitor (SC) filter application

### **1.1.3 Continuous Time Filters**

An analog filter is any filter, which operates on continuous-time signals. In particular, Linear Time Invariant (LTI) analog filters can be characterized by their (continuous) differential equation. Instead of a difference equation as in digital and SC filters, analog filters are described by a differential equation. Instead of using the *z* transform to compute the transfer function, CT systems use the Laplace transform. In the real world, analog filters are usually electrical models, or "analogues", of mechanical systems working in continuous time. If the physical system is linear and time-invariant (LTI) (e.g. consisting of elastic springs and masses which are constant over time), an LTI analog filter can be used to model it. Before the widespread use of digital computers, physical systems were simulated on so-called ``analog computers." An analog computer was much like an analog synthesizer providing modular building-blocks (``integrators") that could be patched together to build models of dynamic systems.

Filters can be also categorized according to the relative size (depending on the frequency of operation) of the elements used with respect to the wavelength of the signal into two categories: Distributed [8] and Non-distributed filters. In a non-distributed [9] (lumped) filter, the physical dimensions of the used elements (resistance, inductance, or capacitance) are negligible compared to the wavelength of the fields associated with the signal. Thus they are considered as simple elements concentrated within the boundaries of the corresponding physical element. This is in contrast to the distributed filter, in which the physical elements have dimensions comparable to the wavelength of the fields associated with the signal and hence it is represented by a combination of physical elements.

## **1.2. Continuous Time Analog Filters**

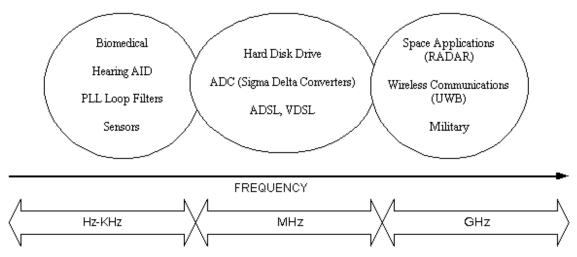

The main focus of this research is the design issues of continuous-time integrated filters. High frequency continuous-time filters have been widely used, in recent years for various applications, especially for medium dynamic range applications, in cases where high speed and/or low power dissipation are needed. Those applications, as shown in Fig. 1.5, include video signal processing [10], hard-disk drive read channels [11], loop filters for phase-locked loops [12], and radio frequency wireless communication systems [13]. The low frequency applications include those filters used in the bio-medical applications [14] like Hearing-Aid etc. and also the filters used for seismic systems [15].

Fig. 1.5. Wide range of filter applications

Using digital filters is not feasible for high frequency applications because they are very power hungry at high frequencies, i.e.,  $power=f_{clock}V_{DD}^2/2$ . Although switched capacitor filters can have good linearity and dynamic range properties, they are not suitable for those kinds of applications either. This is mainly due to their limited ability to process high frequency signals due to the sampling operation. The sampling frequency should be chosen larger than the filter bandwidth to avoid inaccurate filter frequency response. That requires the use of operational amplifiers (OpAmps) with very wide bandwidths, to provide proper settling, demanding large currents; it is required that the unity gain frequency of the used operational amplifier be at least five times larger than the clock frequency used. Another bottleneck is the inability of real switches to operate at high frequency and at low voltages. Thus continuous-time filters became the only option in these types of applications. Continuous-time filters include two main categories: Passive filters and Active filters. A passive filter has all of its elements passive. Therefore, a passive filter may include among its elements resistors, capacitors, inductors and transformers. If the elements of the filter include amplifiers or negative resistances, this is called active.

#### **1.2.1.** Passive Filters

The passive filters are those, which do not employ active blocks like the OpAmps, OTA and other active blocks. They are built using passive elements like resistors, capacitors and inductors. They include three main topologies: RLC filters [16], Surface acoustic filters [17-18], and MEMS filters [19].

## 1.2.1.1. RLC Filters

Classic RLC filters built with resistors, inductors, and capacitors are still much in use in today's systems. They were first used to meet the needs of the early voice applications from the early 1920s. Although high performance on-chip resistors and capacitors can be fabricated in one or more forms in all IC processes, the performance of on-chip inductors is still unsatisfactory in silicon processes. Furthermore for low frequency applications, the area of the on-chip inductor is prohibitive. This renders RLC filters unsuitable for implementation in an integrated form in silicon technologies.

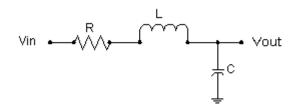

Fig. 1.6. A classical second order low pass RLC filter

$$H(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{\omega_o^2}{s^2 + \frac{\omega_o}{Q}s + \omega_o^2}$$

(1.1)

Fig. 1.6 shows a classical example of a second order low pass RLC filter. Equation (1.1) gives the basic transfer function of the simple RLC filter. The terms  $\omega_0$  is the filter's characteristic frequency and Q is the quality factor of the second order low pass filter and they are equal to  $\omega_0^2 = 1/LC$  and  $Q = \omega_0 L/R$ . The inductors used in the passive circuits are lossy in nature. The quality factor of an inductor is limited by resistive losses in metal traces, and by induced currents in both metal strips and lossy Si substrate.

#### 1.2.1.2. Surface Acoustic Filters

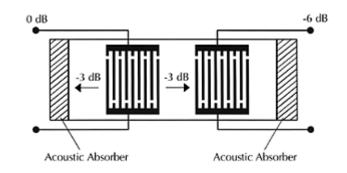

Surface acoustic wave (SAW) filters are applied extensively in today's communication equipment [17]. These high performance components have reached a key position in current communication technology assisting the efforts to increase the spectral efficiency of limited frequency bands for higher bit rates. A SAW filter consists of a piezoelectric substrate with metallic structures, such as inter-digital transducers (IDTs) and reflection or coupling gratings deposited on its plain-polished surface. It is based on propagating and/or standing micro-acoustic waves. Triggered by the piezoelectric effect, a microwave input signal at the transmitting IDT stimulates a microacoustic wave that propagates along the surface of the elastic solid [18]. The associated particle displacement of this SAW is bounded in the vicinity of the surface only. Vice versa, a SAW generates an electric charge distribution at the receiving IDT, causing a microwave electrical output signal to occur. SAW technology has evolved to the GHz range in recent years and now routinely covers the frequency range up to 3GHz. This frequency band is used as carrier frequency for many new wireless communication and sensor applications. SAW filters are not suitable for monolithic implementation and are usually implemented off-chip since silicon is not a piezoelectric material. Fig. 1.7 shows a simple transversal SAW filter configuration.

Fig. 1.7. Simple transversal SAW filter (Source: Triquint Semiconductor)

In its simplest form, a transversal SAW filter consists of two transducers with inter-digital arrays of thin metal electrodes deposited on a highly polished piezoelectric substrate such as Quartz or Lithium Niobate (Fig. 1.7). The electrodes that comprise these arrays alternate polarities so that an RF signal voltage of the proper frequency applied across them causes the surface of the crystal to expand and contract. This generates the Raleigh wave, or surface wave, as it is more commonly called. A Typical SAW filter's frequency of operations includes 0-250MHz. SAW filters finds its applications in most of the communication systems. They are also mostly compact devices.

#### 1.2.1.3. MEMS Filters

Micro-Electro-Mechanical Systems (MEMS) [19] are integrated circuit (IC) devices or systems that combine both electrical and mechanical components. MEMS are fabricated using typical IC batch-processing techniques with characteristic sizes ranging from nanometers to millimeters. RF MEMS are micro-electromechanical systems that interact with a radio frequency (RF) signal [20]. The integration/implementation of RF MEMS provides engineers with an additional integration option for better performance, smaller size, and lower cost in their designs. RF MEMS provide microwave and RF engineers with low insertion loss, high Q, small size, very low current consumption, and potentially low cost options to solving their design problems. The low insertion loss is

obtained by replacing the moderate losses associated with semiconductors with lower metallic losses. Cost and size reduction is the result of utilizing semiconductor batchprocessing techniques in RF MEMS manufacturing. Like existing semiconductor devices, the RF MEMS circuitry must be protected from the environment. But unlike semiconductors, the environmental protection is required due to either the mechanical movement and/or the mechanical fragility of the parts.

Some of the RF MEMS application devices belong to the general class of static devices, which includes transmission lines and resonators; active devices, such as switches and variable capacitors; and circuits, such as oscillators (fixed frequency and voltage controlled), and tunable filters.

Resonators (Filters) are a basic building block in frequency selective systems. Due to the diverse technologies involved and the low insertion loss associated with MEMS technology, several different resonator types exist. There are three types of resonant structures, demonstrated over widely different frequency ranges, mechanical (300 KHz to 100 MHz), cavity (greater than 20 GHz), and piezoelectric film (1.5 to 7.5 GHz) resonators.

#### **1.2.2.** Active Filters

Active filters are ubiquitous in electronic design today, performing signalfrequency manipulation and conditioning for audio, IF (intermediate frequency), and digital-signal processing. The success of active filters is due primarily to integration capability and the extensive body of theoretical knowledge. Although DSPs can outperform active filters in dynamic range, active filters can achieve good performance with significantly lower power demands.

Active filters [21] also use resistors and capacitors, but active devices capable of producing power gain replace the inductors. These devices can range from single transistors to integrated circuit (IC) -controlled sources such as the operational amplifier (OPAMP), and simpler devices, such as the operational transconductance amplifier (OTA) [22], the generalized impedance converter [23] (GIC), and the frequency-

dependent negative resistor [24] (FDNR). The general class of active filters includes the Active-RC filters, MOSFET-C, OTA-C, and Current mode types of filters.

## 1.2.2.1. Active-RC Filters

Despite the availability of active-filter ICs, most engineers still resort to RC (resistor/capacitor) active implementations consisting of operational amplifiers (OpAmp), resistors, and capacitors. Indeed, the popularity of RC active filters has not diminished since their heyday in the 1970s. They offer the opportunity to integrate complex filters on-chip, and do not have the problems that the relatively bulky, lossy, and expensive inductors bring in particular their stray magnetic fields that can provide unwanted coupling in a circuit or system.

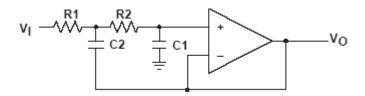

Fig. 1.8 shows the simplest form of active-RC architectures, the Sallen and Key [25] circuit (which uses a voltage amplifier, resistors, and capacitors). It has been around for a long time, yet research into active-RC filters still proceeds after all that time. Sallen

and Key types of filters are mainly used for designing high

$$Q\left(Q = \frac{\sqrt{R_1R_2C_1C_2}}{C_1(R_1 + R_2)}\right)$$

filters.

Larger Qs are attainable by using a positive feedback amplifier. If the positive feedback is controlled—localized to the cut-off frequency of the filter—almost any Q can be realized, limited mainly by the physical constraints of the power supply and component tolerances. Fig. 1.8 shows a unity gain amplifier used in this manner. Capacitor  $C_2$ , no longer connected to ground, provides a positive feedback path.

Fig. 1.8. Unity gain Sallen and Key low pass filter

OpAmps (active block represented by the triangular block in Fig. 1.8) are often the most critical elements in any RC-active-filter design and deserve much attention. Voltage-feedback OpAmps are still the mainstay of RC active filters, but currentfeedback topologies [26] offer gain that's independent of bandwidth, as well as good current outputs at high frequencies. With more designs concentrating on portable systems, low-voltage CMOS op amps offer rail-to-rail [27]-[28] voltage-handling capability down to power supply voltages of 3V or less.

Active-RC filters have been widely used in various low frequency applications in telecommunication networks, signal processing circuits, communication systems, control, and instrumentation systems. However, they cannot work at higher frequencies due to OpAmp frequency limitations, i.e. higher order poles are created which needs to be compensated, and are not suitable for full integration if large resistors are required. They are also not electronically tunable and usually have complex structures. The most successful approach to overcome these drawbacks is to replace the conventional OpAmp in active-RC filters by an OTA giving rise to OTA-C filters.

### 1.2.2.2. OTA-C Filters

Programmable high-frequency active filters can be achieved by incorporating the Operational Transconductance Amplifier-Capacitor filters (OTA-C). OTA-C filters also have simple structures, and can operate up to several hundreds of MHz. In recent years OTA-based high frequency integrated circuits, filters and systems have been widely investigated [22]. This is due to their simplicity, electronic tunability, and suitability for high frequency operation due to open loop configuration.

The OTA has been implemented widely in CMOS and bipolar and also in BiCMOS and GaAs technologies. The typical values of transconductances are in the range of tens to hundreds of  $\mu$ S in CMOS and up to mS in bipolar technology. The CMOS OTA, for example, can work typically in the frequency range of 50MHz to several 100MHz. Linearization techniques [29]-[30] make the OTA able to handle input signals of the order of nearly volts with nonlinearities of a fraction of one percent.

Although OTA-C filters have the potential to operate at relatively high frequencies (MHz range), the linear signal range of the used transconductance limits the dynamic range. Also the OTA-C filters become very power hungry at GHz range.

This research focuses on the modeling of these OTA blocks, designing new highly linear OTA blocks for continuous time analog filters. Chapters II and III describe the OTA in detail. Several design issues of the OTA-C filters are also discussed.

Fig. 1.9. Simple low pass OTA-C filter with a fixed pole and adjustable gain

Fig. 1.9 shows a typical example of a simple first order OTA-C circuit with a fixed pole, depending on the values of R and C, and an adjustable gain (adjusted using the transconductance  $g_m$  of the OTA.

#### 1.2.2.3. MOSFET-C Filters

Today among some of the most proven reliable filter structures are a class called MOSFET-C filters. The MOSFET-C method follows the standard OpAmp based active filter techniques as mentioned in the previous section. The main difference is that the method replaces the resistors used in the conventional active RC integrating and summing circuitry by MOSFET devices based in the triode region (linear/ohmic region), where the MOS device acts as a linear resistor.

#### 1.2.2.4. Current Mode Filters

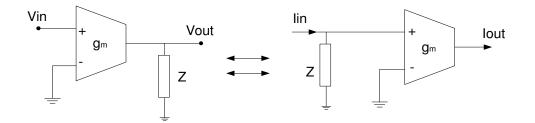

Most of the techniques mentioned in the previous sections were all voltage mode filters where the input is a voltage variable and the output is either voltage or current. The class of active filters whose inputs are mainly current variables are called collectively as Current Mode filters. For the fully current mode filters [31] the inputs and the outputs are current forms. Fig. 1.10 shows the current mode form of the first order filter whose voltage mode is shown in Fig. 1.9.

Fig. 1.10. Voltage mode to current mode transformation

Fig. 1.11. Non-inverting current mode integrator

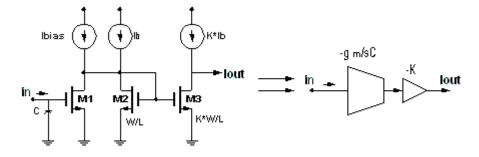

The most primitive form of the transconductance mode architecture is that of a simple inverting transistor. A simple MOS transistor (a NMOS for e.g.) produces a drain currents  $I_{ds}$  corresponding to the voltage input and also its transconductance  $g_m$

parameter. A current amplifier can be implemented using a simple current mirror. Fig 1.11 shows a simple non-inverting integrator in the current mode operation.

The performance comparisons between the voltage mode and current mode almost yield the same response. This might be due to inherent transconductance-mode of both the types. There are however few differences depending on the type of circuit design. In most of the papers proposing very fast current-mode circuits, open-loop current amplifiers are compared to results obtained with closed-loop voltage amplifiers [31]. Many of the amplifiers derived with a current-mode approach base on current mirrors and provide a specific, low gain without feedback around the amplifier. The typical low-gain voltage amplifier uses feedback around a high-gain amplifier. This feedback stabilizes the gain and reduces harmonic distortion, it also improves the terminal impedances of the amplifier.

The voltage-mode filter has ideally a high-impedance output and the currentmode filter has a high-impedance input. Therefore, on a real IC, the voltage mode circuit might need an output buffer, since a resistive load connected to the output node would otherwise change the transfer function, and the current-mode circuit might need an input buffer, since the input nodes must be driven by a high-resistance device. However, the noise of the current buffer is filtered, but not the noise of the voltage buffer, and the performance difference between the two filters is reduced to the performance difference between the circuits used to insert signals into the feedback loop and extract signals from it. The resulting performance difference is certainly small, and it is not a question of signal representation, but of transistor-level design.

Some of the research works indicates that the current-mode circuits are considered to be faster than voltage-mode circuits: although both would be similarly good from an ideal point of view. In general the advantages of current-mode circuits that are often cited in the literature, like a potential for reaching higher frequencies, lower power consumption, and smaller chip area, are in fact real, but the reason is not technical, and has nothing to do with choosing voltages or currents to represent signals. The reasons for the difference are mainly the design preferences of the proponents of the current-mode approach.

Tables.1.1 and 1.2 show a comparison of the various filter types.

Table 1.1. Comparison of Filter CategoriesParameterDigitalSampled-dataContinuous-timeFime samplesDiscreteDiscreteContinuous

| Time samples                          | Discrete    | Discrete    | Continuous               |

|---------------------------------------|-------------|-------------|--------------------------|

| Data samples                          | Discrete    | Continuous  | Continuous               |

| Need anti-aliasing and reconstruction | Yes         | Yes         | No                       |

| Mathematical Description              | Z-transform | Z-transform | S-transform<br>(Laplace) |

Table 1.2. Comparison of the Continuous Time Filter Types

| Parameter              | Active               |           | Passive RLC         |

|------------------------|----------------------|-----------|---------------------|

|                        | Active-RC            | OTA-C     |                     |

| Frequency of Operation | Upto a few 100of MHz | Upto GHz  | Upto a few MHz      |

| Block                  | OpAmp                | ΟΤΑ       | R, L and C          |

| Limitations            | Power consumption    | Linearity | Bulky inductors for |

|                        | OpAmp has frequency  | Power     | higher frequencies  |

|                        | Limitations          | Noise     |                     |

|                        | Tunability           | Tuning    |                     |

| Area                   | Less                 | Less      | Very large          |

| Silicon Integration    | Easy                 | Easy      | Difficult           |

#### **1.3. Filter Design Procedure**

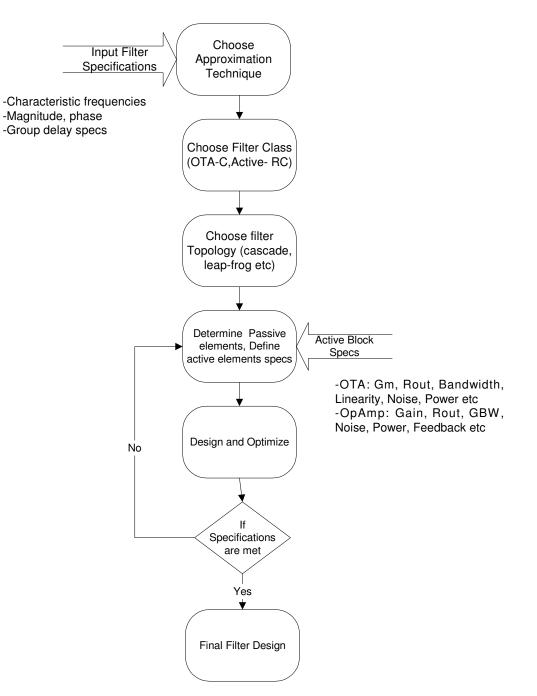

The design of a filter (be it continuous time, digital or sampled-data) involves a series of steps, which will end up in the final filter design to meet the required application. Depending on the application, the specifications of the filter needs to mentioned clearly. There are various ways of approaching the design procedure to achieve the specifications. To select the best approach depends on the choice of the appropriate system transfer function, which will satisfy the specifications. This process involves choosing the right approximation technique. With the filter transfer function chosen the next would be to choose the class of the filter type which needs to be used, be it Active-RC, OTA-C, MOSFET-C etc. Depending on the order of the filter chosen, possible filter implementations needs to be considered like the cascade [32], leap-frog [33], follow the leader feedback, multiple feedback loop [34] etc, if the order is more than 2. If the order is 2, the filter can be a simple biquad. The next step would be to define the passive element values and also the specifications of the active block in the circuit. Designing of the active block to match the specifications follows this step. The final step is to verify the complete filter functionality. Fig. 1.12 gives the data flow diagram for the continuous time filter design. Each of the steps are explained in detail in the following sub-sections.

Fig. 1.12. Data flow for continuous time filter design procedure

## **1.3.1. Filter Specifications**

Each application requires some specifications, which may be based on the magnitude, phase, and group delay specifications. Some of the filter specifications are explained in brief.

Magnitude Response: Magnitude Response is defined as the ratio of the output amplitude to the input amplitude versus frequency and is usually plotted on a log/log scale. Some of the magnitude specifications are maximum attenuation in the pass band, minimum attenuation in the stop band, the maximum allowable ripple etc.

Frequency Response: Along with the magnitude specifications are the frequency specifications. The frequency limit till which the filters need to perform is an important measure. A commonly used term is the "Corner" frequency, or the "3dB" frequency. It is defined as the frequency at which the magnitude response drops by 3dB from its desired level, in the case of low pass or high pass filter. The range of frequencies till this level would be termed as the pass band and the range of frequencies above/below, which the signal is totally attenuated, is termed as the stop band. In the case of band-pass filters or band-reject filters, the important specification is the center frequency and the bandwidth within which the signal is contained. Other frequency and magnitude related specification includes "Quality factor Q" of the filter, which is related to peaking factor around the corner frequency.

Phase Response/Group Delay Response: All non-ideal filters introduce a time delay between the filter input and output terminals. This delay can be represented as a phase shift if a sine wave is passed through the filter. The extent of phase shift depends on the filter's transfer function. For most filter shapes, the amount of phase shift changes with the input signal frequency. The normal way of representing this change in phase is through the concept of Group Delay, the derivative of the phase shift through the filter with respect to frequency.

Some of the other specifications of the filter which are not directly involved in choosing the filter transfer function, but are very critical factors are, Noise performance related to signal to noise ratio (SNR), Linearity performance defined using a term called

"Total Harmonic Distortion (THD)" and dynamic range, power consumption etc. These issues are dealt in detail in chapters II and III.

### **1.3.2.** The Approximation Problem

Solution of the approximation problem [35] is a major step in the design procedure of a filter. It is through the solution of this problem that the filter designer determines the filter function, the response that satisfies the above mentioned specifications. In practice, the specifications of a low pass filter are often given in terms of the cutoff frequency the maximum allowable deviation (error) in the passband, the stop band edge frequency, and the minimum attenuation in the stop band. In general, from those specifications, one is able to draw a frequency response magnitude plot. This plot can be approximated by a function that is then implemented using a low pass filter.

The approximation problem has been solved mathematically in various ways. Some of the best-known and most popular lows pass functions in the frequency domain for magnitude responses are: Butterworth, Chebyschev, Elliptic functions, Equal ripple delay and Bessel-Thomson function for phase response. With the aid of any of the computer programs that are available nowadays, such as Fiesta-II [35], one can obtain the appropriate approximating function for any particular specifications. Then, since these basic functions are low pass, a suitable frequency transformation is applied in order to obtain high pass, band pass, or band stop filters according to the requirement.

#### **1.3.3. Filter Class**

The next step in the filter design process is the selection of the appropriate filter classes i.e. the type of filter to be used, be it active-RC, OTA-C or MOSFET-C. This has been described in detail in the previous section. The best class of filter is chosen depending on the application. OTA-C is chosen for high frequency applications. Active-RC is chosen if the application has stringent noise and Signal to noise requirements etc. This thesis focuses on the application and usage of OTA-C filters for continuous time

analog applications. The specifications of the active and passive components of the filter are mentioned in the forth-coming sections.

# **1.3.4.** Filter Topology

The filter transfer function obtained from the approximation used, indicates the order of the filter required to meet the filter specifications. In cases, where the order of the filter is 2, a simple biquad (a second order filter) can be used to achieve the response. In most cases, the selectivity that is provided by a second order filter is not sufficient. Higher order filters are needed in order to satisfy the tough selectivity requirements in telecommunication systems, and many other applications. There are two main approaches to realize a high order filter; (1) to cascade second order stages without feedback (Cascade) [32] or through the application of negative feedback [34] (multiple-loop feedback MLF), and (2) simulation of passive LC ladder filters [36]. Selection of the filter topology would depend on some of issues like sensitivity and area available. Some of the filter topologies may not require many active elements; hence the effective silicon area and power can be reduced. Some of the known filter topologies are discussed below.

## 1.3.4.1. Cascade Topology

In this approach biquadratic second order sections are cascaded and the high order function is realized as the product of biquadratic factors. These sections are simply cascaded by connecting the output of each section to the input of the following one. This method has the advantage of simplicity in designing the filter, provided that the output of each section is very low impedance or the input of each section is very high impedance. Fig. 1.13a shows a simple biquad OTA-C filter and Fig. 1.13b shows a 5<sup>th</sup> order Bessel OTA-C filter designed by cascading two biquads and a first order filter.

Fig. 1.13a. OTA-C biquad section

Fig. 1.13b. 5<sup>th</sup> order Bessel OTA-C filter (cascade 2:2:1)

In the above approach there is no feedback between the biquadratic sections. However the second class of cascading techniques involves feedback across the biquadratic sections. In this approach multiple feedback is applied in a cascade connection of biquadratic sections. This leads to a better sensitivity performance of the overall circuit compared to the corresponding circuit obtained using the Cascade approach. This approach has two general topologies: the leapfrog topology [33], and the summed-feedback topology [34].

## 1.3.4.2. Leapfrog Topology

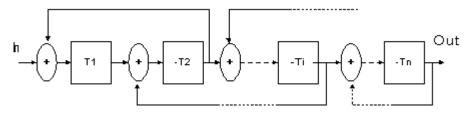

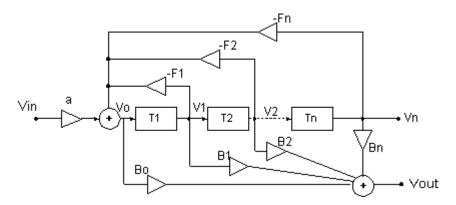

The leapfrog (LF) configuration is shown in Fig. 1.14. Each of the boxes named  $T_i$  realizes a second order losssless filter transfer function (biquad) except for the terminations at the input and output. The feedback loop always comprises of two sections; thus, inverting and non-inverting sections must alternate to keep the loop gains negative and the loops stable [33]. If the circuit is derived from a resistively terminated lossless ladder filter, as is normally the case,  $T_1$  and  $T_n$  are lossy and all the internal sections are lossless. A lossless block implies a function  $T_i$  with infinite Q, which may not be stable by itself, but the overall feedback connection guarantees stability. This topology is useful in the functional simulation of LC ladder filter.

Fig. 1.14. Leapfrog topology

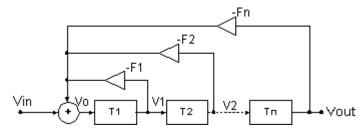

### 1.3.4.3. Summed-feedback Topology

The summed-feedback topology [34], as shown in Fig. 1.15, is not suitable for realizing any finite transmission zeros. To overcome this problem, one of two techniques can be used: (1) the multiple-or distributed-input technique, in which the input signal is also fed to the input of all cascading sections, or (2) the summation of the input signal and the output signals from all cascaded sections.

Fig. 1.15. Summed-feedback topology

There are three other design methods based on that topology: the primaryresonator block (PRB) [14] where all the used  $T_i$  stages are identical, the follow-theleader feedback (FLF) [37], and the shifted-companion form (SCF) [38]. Both the FLF and SCF methods are generalizations of the PRB method. The general block diagram of FLF [37] method is shown in Fig. 1.16. In this case,  $T_i$  can be first order low pass or high pass functions or alternatively second order biquadratic sections. The summation of the feedback voltages is responsible for the realization of the poles of the function, while the second summation is required for the realization of any finite transmission zeros.

Fig. 1.16. Follow-the-leader feedback (FLF) topology

# 1.3.4.4. LC Ladder Simulation

Simulating either functionally or using active elements to implement the inductances of the ladder can achieve simulation of passive resistively terminated lossless ladder networks. Functional simulation [36] is implemented by realizing the currents and node voltages in the ladder. The LC ladder simulation method is attractive, because it leads to active filters of lower sensitivities the other two approaches, i.e., Cascade and multiple loop feedbacks.

Table 1.3 gives an overall comparison of the various filter topologies.

| Туре          | Approach             | Sensitivity | Design              |  |

|---------------|----------------------|-------------|---------------------|--|

| Cascade       | Biquadratic sections | Bad         | Simple and easily   |  |

|               | are cascaded         |             | tunable             |  |

| Multiple-loop | Multiple feedback is | Good        | Complex             |  |

| feedback      | applied in cascade   |             | More critical nodes |  |

|               | of biquadratic       |             | due to feedback     |  |

|               | sections             |             |                     |  |

| LC ladder     | Simulation of        | Best        | Simple              |  |

| simulation    | passive lossless     |             |                     |  |

|               | ladder networks      |             |                     |  |

Table 1.3. Comparison of Filter Topologies

# **1.4.** Active Blocks Design Considerations

The next step, having defined the class and topology is the specification of the active and passive elements used in the filter design. The passive elements are chosen to minimize area consumed in actual silicon and other parasitics introduced. The active block needs further investigation. Some of the commonly mentioned active block

specifications for the case of an Active-RC filter are DC gain, output resistance, gain bandwidth product for the OpAmp used. The specifications for the case of OTA-C filters are the transconductance ( $g_m$ ) of the OTA, bandwidth, linearity, noise performance of the OTA etc. Apart from the specifications particular for the active block in the filter design, there are some performance criteria specific for the filter applications. Some typical analog filter performance criteria are transfer function accuracy, linearity, noise performance, power consumption, and silicon area.

#### 1.4.1. Noise