## A CAPACITOR-LESS LOW DROP-OUT VOLTAGE REGULATOR

# WITH FAST TRANSIENT RESPONSE

A Thesis

by

## ROBERT JON MILLIKEN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2005

Major Subject: Electrical Engineering

# A CAPACITOR-LESS LOW DROP-OUT VOLTAGE REGULATOR

# WITH FAST TRANSIENT RESPONSE

### A Thesis

# by

## ROBERT JON MILLIKEN

## Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

Approved by:

| Co-Chairs of Committee, | Jose Silva-Martinez    |

|-------------------------|------------------------|

|                         | Edgar Sanchez-Sinencio |

| Committee Members,      | Aydin Karsilayan       |

|                         | Prasad Enjeti          |

|                         | Michael Pilant         |

| Head of Department,     | Costas Georghiades     |

December 2005

Major Subject: Electrical Engineering

#### ABSTRACT

A Capacitor-less Low Drop-out Voltage Regulator with Fast Transient Response. (December 2005) Robert Jon Milliken, B.S., Iowa State University Co-Chairs of Advisory Committee: Dr. Jose Silva-Martinez Dr. Edgar Sanchez-Sinencio

Power management has had an ever increasing role in the present electronic industry. Battery powered and handheld applications require power management techniques to extend the life of the battery and consequently the operation life of the device. Most systems incorporate several voltage regulators which supply various subsystems and provide isolation among such subsystems. Low dropout (LDO) voltage regulators are generally used to supply low voltage, low noise analog circuitry. Each LDO regulator demands a large external capacitor, in the range of a few microfarads, to perform. These external capacitors occupy valuable board space, increase the IC pin count, and prohibit system-on-chip (SoC) solutions.

The presented research provides a solution to the present bulky external capacitor LDO voltage regulators with a capacitor-less LDO architecture. The large external capacitor was completely removed and replaced with a reasonable 100pF internal output capacitor, allowing for greater power system integration for SoC applications. A new compensation scheme is presented that provides both a fast transient response and full range ac stability from a 0mA to 50mA load current. A 50mA, 2.8V, capacitor-less LDO voltage regulator was fabricated in a TSMC 0.35um CMOS technology, consuming only 65uA of ground current with a dropout voltage of 200mV.

Experimental results show that the proposed capacitor-less LDO voltage regulator exceeds the current published works in both transient response and ac stability. The architecture is also less sensitive to process variation and loading conditions. Thus, the presented capacitor-less LDO voltage regulator is suitable for SoC solutions.

To my parents for their encouragement, love, and support

#### ACKNOWLEDGMENTS

I would like to first thank my advisors Dr. Jose Silva-Martinez and Dr. Edgar Sanchez-Sinencio for their expert knowledge and guidance throughout my entire Master's program at Texas A&M University. I would also like to thank my peers, namely Abraham Islas-Olimar, Julio Aaylas, Chad Marquart, Farmarz Bahmani, Artur Lewinski, Arun Ramachandran, Chinmaya Mishra, Alberto Valdes-Garcia, Feyza Berber, and Burak Kelleci for their input and moral support. I would also like to extend my thanks to Dr. Randall Geiger and Prof. Patterson from Iowa State University to whom I owe my acceptance and preparation towards achieving a Master of Science degree in electrical engineering. Finally, I would like to thank my family for all their love and support along my arduous journey in the electrical engineering profession. To my family, I owe them my current successes and the success that will follow in the future. Thank you.

# TABLE OF CONTENTS

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                       | iii                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                     | iv                                                       |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                | v                                                        |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                              | vi                                                       |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                | vii                                                      |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                 | x                                                        |

| I. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                | 1                                                        |

| <ul> <li>A. LDO Regulator Applications</li> <li>B. Conventional Linear and LDO Regulator Architectures</li> <li>C. LDO Regulator Characterization</li> <li>D. Capacitor-less LDO Voltage Regulators</li> </ul>                                                                                                                                                                                 | 1<br>4<br>7<br>12                                        |

| II. CAPACITOR-LESS LDO REGULATOR DESIGN                                                                                                                                                                                                                                                                                                                                                        | 21                                                       |

| A. Uncompensated Device Characterization<br>B. Design Architecture Strategy                                                                                                                                                                                                                                                                                                                    | 22<br>38                                                 |

| _ · _ · - · - · - · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| III. TRANSISTOR-LEVEL DESIGN AND SIMULATION                                                                                                                                                                                                                                                                                                                                                    | 58                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                | 58<br>61<br>74<br>78                                     |

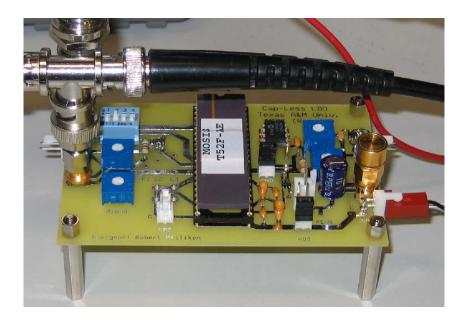

| III. TRANSISTOR-LEVEL DESIGN AND SIMULATION<br>A. Transistor-level Simulations<br>B. Statistical Analysis                                                                                                                                                                                                                                                                                      | 61<br>74                                                 |

| <ul> <li>III. TRANSISTOR-LEVEL DESIGN AND SIMULATION</li> <li>A. Transistor-level Simulations</li> <li>B. Statistical Analysis</li> <li>C. Final LDO Layout</li> <li>IV. EXPERIMENTAL RESULTS</li> <li>A. Test Board Design</li> <li>B. Transient Response</li> <li>C. High-Frequency Response</li> </ul>                                                                                      | 61<br>74<br>78                                           |

| <ul> <li>III. TRANSISTOR-LEVEL DESIGN AND SIMULATION</li> <li>A. Transistor-level Simulations</li> <li>B. Statistical Analysis</li> <li>C. Final LDO Layout</li> <li>IV. EXPERIMENTAL RESULTS</li> <li>A. Test Board Design</li> <li>B. Transient Response</li> </ul>                                                                                                                          | 61<br>74<br>78<br>80<br>80<br>81<br>86                   |

| <ul> <li>III. TRANSISTOR-LEVEL DESIGN AND SIMULATION</li> <li>A. Transistor-level Simulations.</li> <li>B. Statistical Analysis.</li> <li>C. Final LDO Layout.</li> <li>IV. EXPERIMENTAL RESULTS</li> <li>A. Test Board Design</li> <li>B. Transient Response.</li> <li>C. High-Frequency Response.</li> <li>D. Comparison of Results.</li> </ul>                                              | 61<br>74<br>78<br>80<br>80<br>81<br>86<br>89             |

| <ul> <li>III. TRANSISTOR-LEVEL DESIGN AND SIMULATION</li> <li>A. Transistor-level Simulations.</li> <li>B. Statistical Analysis.</li> <li>C. Final LDO Layout.</li> <li>IV. EXPERIMENTAL RESULTS.</li> <li>A. Test Board Design</li> <li>B. Transient Response.</li> <li>C. High-Frequency Response</li> <li>D. Comparison of Results.</li> </ul>                                              | 61<br>74<br>78<br>80<br>80<br>81<br>86<br>89<br>91       |

| <ul> <li>III. TRANSISTOR-LEVEL DESIGN AND SIMULATION</li> <li>A. Transistor-level Simulations.</li> <li>B. Statistical Analysis.</li> <li>C. Final LDO Layout.</li> <li>IV. EXPERIMENTAL RESULTS.</li> <li>A. Test Board Design</li> <li>B. Transient Response.</li> <li>C. High-Frequency Response.</li> <li>D. Comparison of Results.</li> <li>V. CONCLUSION</li> <li>REFERENCES.</li> </ul> | 61<br>74<br>78<br>80<br>80<br>81<br>86<br>89<br>91<br>92 |

# LIST OF FIGURES

|                                                                                                                  | Page |

|------------------------------------------------------------------------------------------------------------------|------|

| Fig. 1. Cell phone power management application                                                                  | 2    |

| Fig. 2. Cell phone battery characteristics                                                                       | 3    |

| Fig. 3. High efficiency linear regulation.                                                                       | 4    |

| Fig. 4. Linear voltage regulator topologies                                                                      | 4    |

| Fig. 5. AC pole locations without compensation                                                                   | 5    |

| Fig. 6. Conventional LDO regulator compensation                                                                  | 6    |

| Fig. 7. LDO regulator parameters                                                                                 | 8    |

| Fig. 8. Capacitor-less LDO voltage regulator                                                                     | 13   |

| Fig. 9. Pole locations for uncompensated capacitor-less LDO voltage regulator                                    | 14   |

| Fig. 10. Equivalent circuit for fast load transients                                                             | 16   |

| Fig. 11. Power efficiency tradeoff.                                                                              | 17   |

| Fig. 12. Capacitor-free LDO voltage regulator                                                                    | 18   |

| Fig. 13. LDO compensation with C <sub>F1</sub> .                                                                 | 18   |

| Fig. 14. LDO regulator with pole/zero tracking.                                                                  | 19   |

| Fig. 15. Basic capacitor-less LDO concept                                                                        | 20   |

| Fig. 16. Pass transistor design                                                                                  | 23   |

| Fig. 17. AC open-loop simulation circuit.                                                                        |      |

| Fig. 18. AC open-loop block diagram test circuit                                                                 | 27   |

| Fig. 19. Feedback circuit with parasitic capacitor, C <sub>F1</sub>                                              |      |

| Fig. 20. Pass transistor small signal analysis.                                                                  |      |

| Fig. 21. Pass transistor output resistance models                                                                |      |

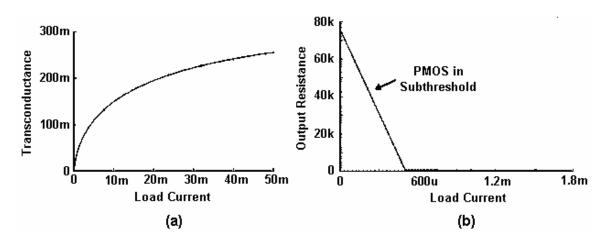

| Fig. 22. Pass transistor load-dependent DC operating points:<br>(a) transconductance (b) output resistance.      | 32   |

| Fig. 23. Uncompensated LDO AC response                                                                           |      |

| Fig. 24. Uncompensated LDO AC parameters verses I <sub>out</sub> :<br>(a) output pole frequency (b) phase margin | 34   |

| Fig. 25. Uncompensated AC response simulated in CADENCE.                                                         |      |

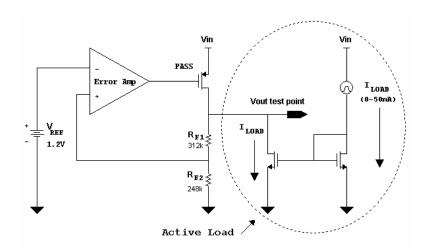

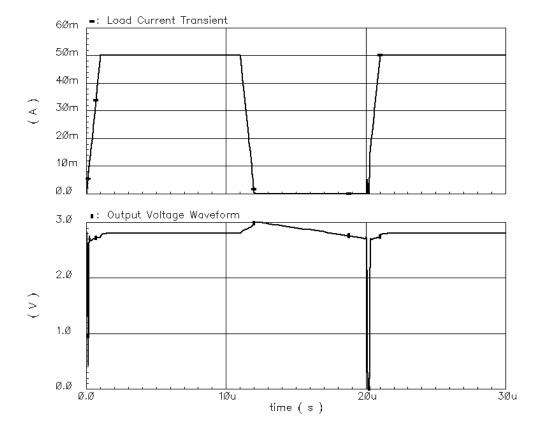

| Fig. 26. Close-loop uncompensated LDO load transient test circuit.                                               |      |

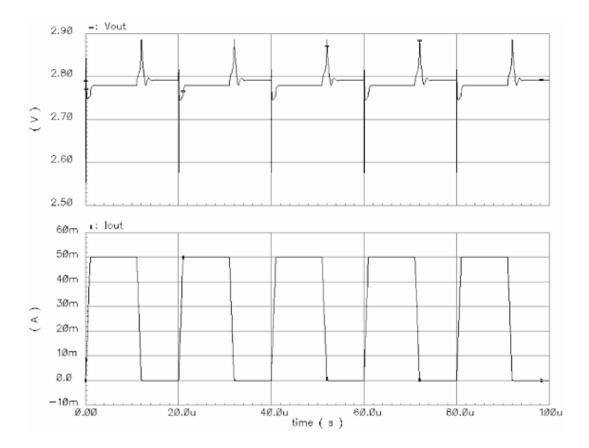

| Fig. 27. 0 to 50mA load transient response.                                                                      |      |

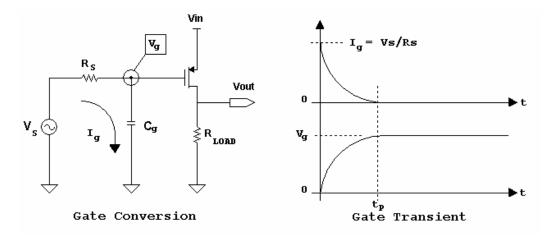

| Fig. 28. Pass transistor gate transient effect                                                                   |      |

|                                                                                                                  |      |

|          |                                                                                                                                      | Page |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|------|

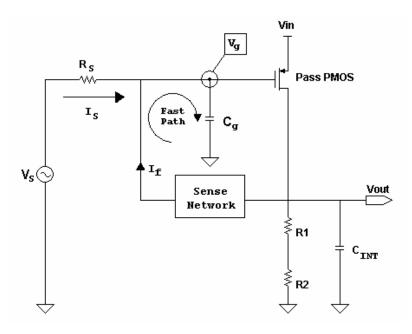

| Fig. 29. | Fast transient path general concept                                                                                                  |      |

| Fig. 30. | Basic capacitive differentiator.                                                                                                     | 40   |

| Fig. 31. | Addition of differentiator fast path                                                                                                 | 41   |

| Fig. 32. | Differentiator voltage mode AC response                                                                                              |      |

| Fig. 33. | Simplest coupling network                                                                                                            | 43   |

| Fig. 34. | Proposed coupling network.                                                                                                           |      |

| Fig. 35. | Differentiator charge analysis                                                                                                       |      |

| Fig. 36. | Proposed topology: simplified circuit diagram.                                                                                       |      |

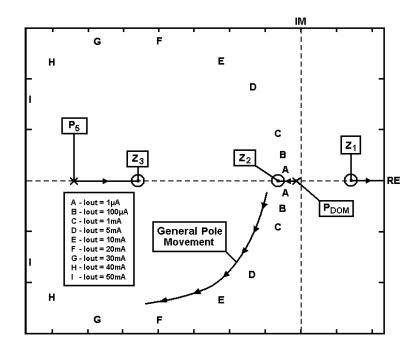

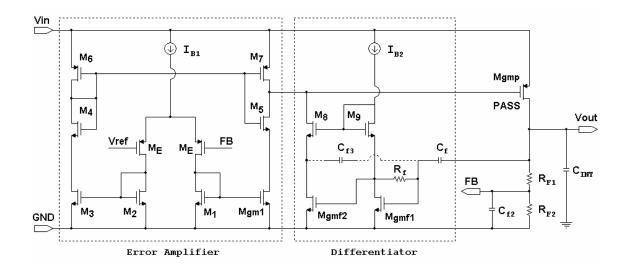

| Fig. 37. | Proposed capacitor-less LDO voltage regulator: Open-loop schematic                                                                   |      |

| Fig. 38. | Differential equivalent circuit diagram.                                                                                             |      |

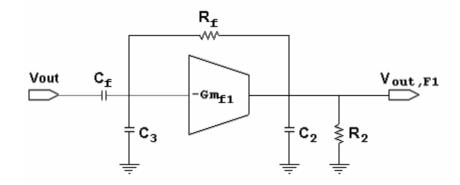

| Fig. 39. | <ul> <li>(a) General differentiator pole movement with gm<sub>f1</sub></li> <li>(b) Differentiator open-loop AC response.</li> </ul> |      |

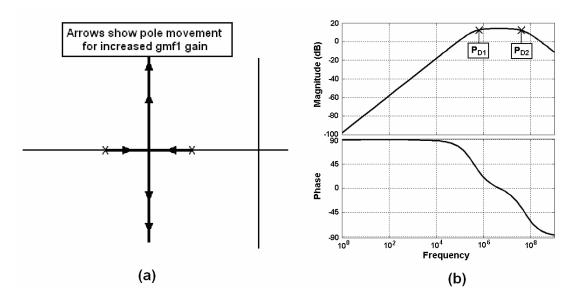

| Fig. 40. | Differentiator closed-loop pole movement with changing load current                                                                  |      |

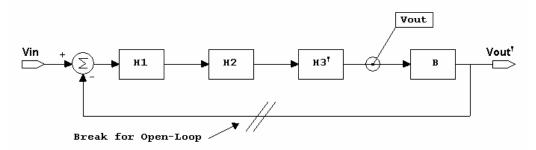

| Fig. 41. | Modified block diagram.                                                                                                              |      |

| Fig. 42. | Complete root locus showing closed-loop pole movement for both load current variations and feedback factor, $\beta$                  |      |

| Fig. 43. | Stability constraint for the differentiator's complex close-loop poles                                                               |      |

| Fig. 44. | MATLAB simulation: Open-loop AC response for $I_{OUT} = 0$ mA                                                                        |      |

| Fig. 45. | Proposed capacitor-less LDO transistor-level design                                                                                  |      |

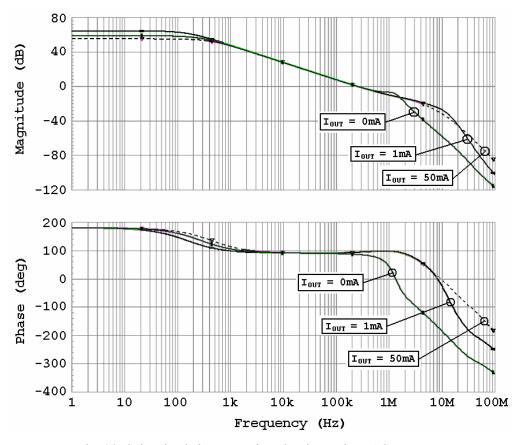

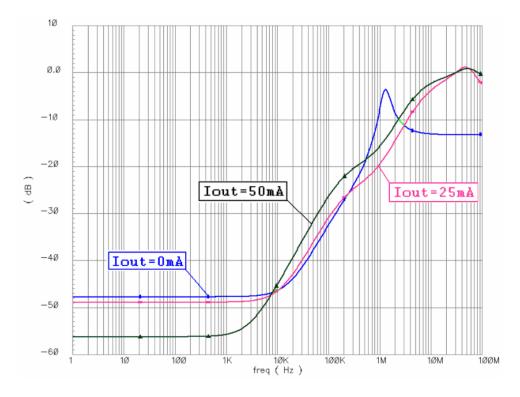

| Fig. 46. | Spice simulation: Transistor-level open-loop AC response.                                                                            | 60   |

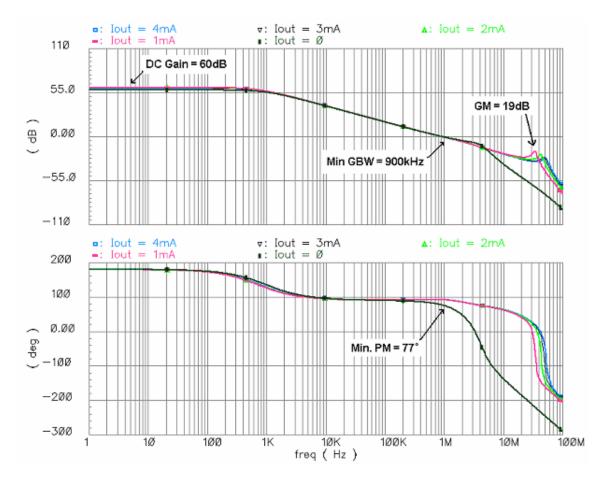

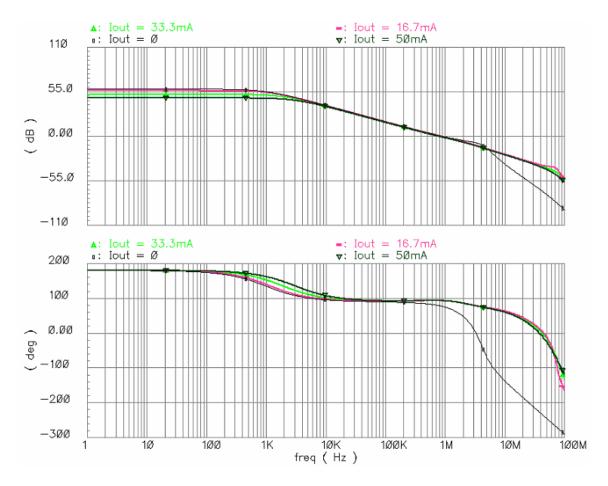

| Fig. 47. | Low output current open-loop AC response for $I_{out} = 0 \sim 4mA$                                                                  |      |

| Fig. 48. | Full range open-loop AC response for $I_{out}$ = 0 $\sim$ 50mA                                                                       |      |

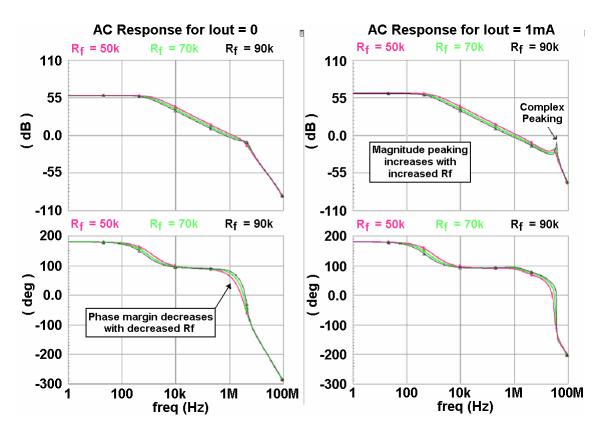

| Fig. 49. | Variation in compensation resistor, R <sub>f</sub> .                                                                                 | 64   |

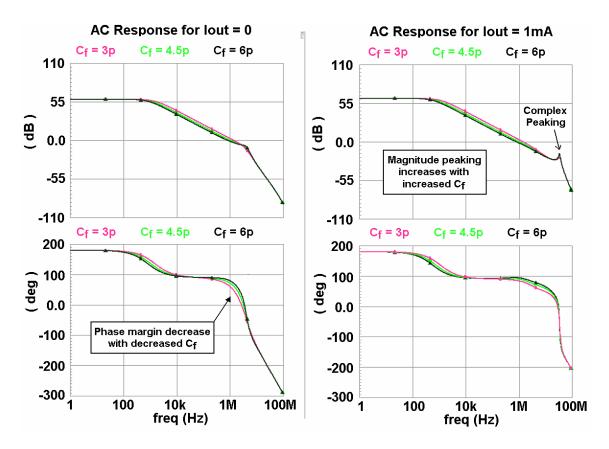

| Fig. 50. | Variation in compensation capacitor, C <sub>f</sub> .                                                                                |      |

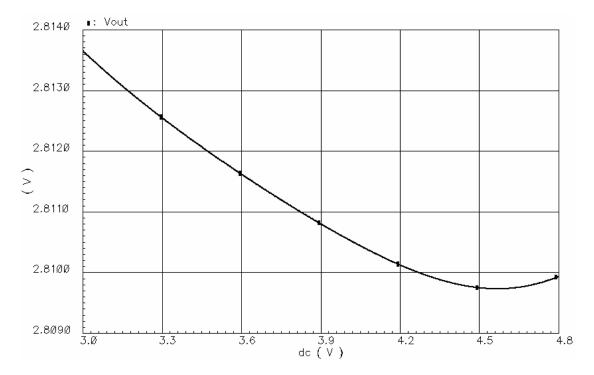

| Fig. 51. | Line regulation for $I_{out} = 0mA$                                                                                                  |      |

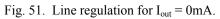

| Fig. 52. | Load regulation for Vin = 3V                                                                                                         |      |

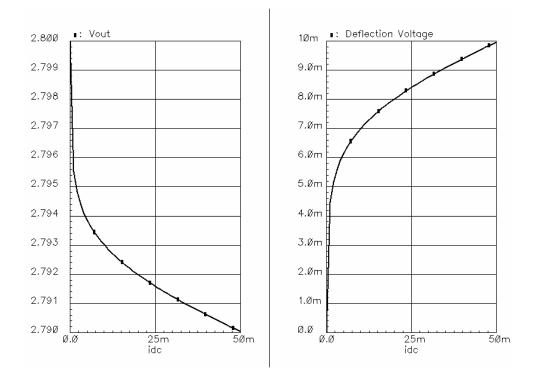

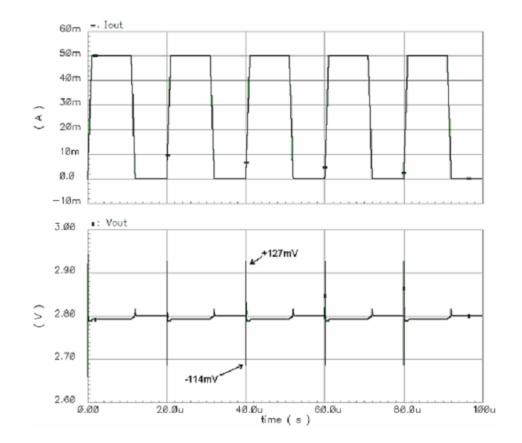

| Fig. 53. | Full load transient response (without Cf2 and Cf3)                                                                                   | 67   |

| Fig. 54. | Load transient response for zero to full load with $C_{f2}$ and $C_{f3}$                                                             |      |

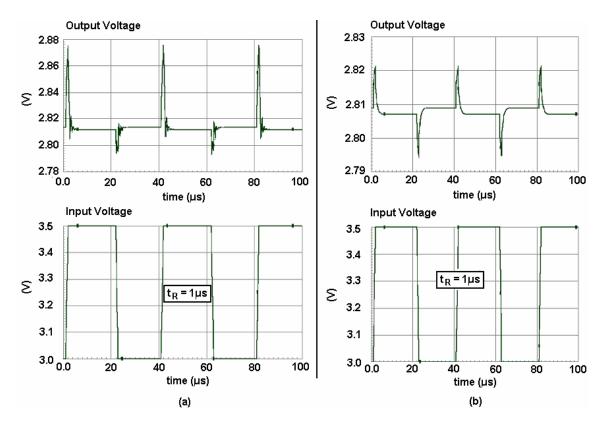

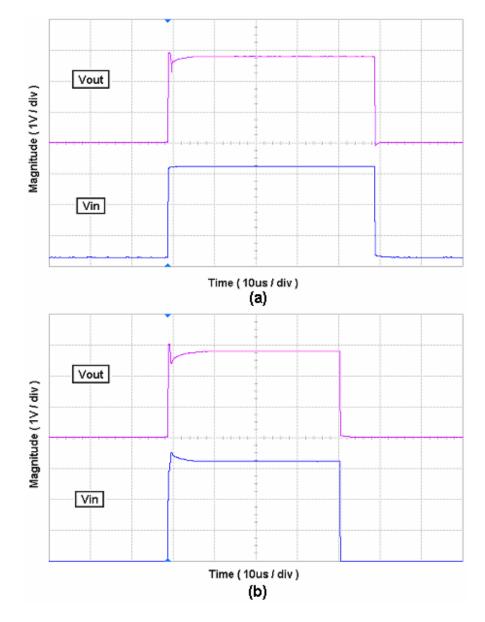

| Fig. 55. | Line transient response for $I_{out}$ set to $0mA$ (a) and $1mA$ (b).                                                                | 69   |

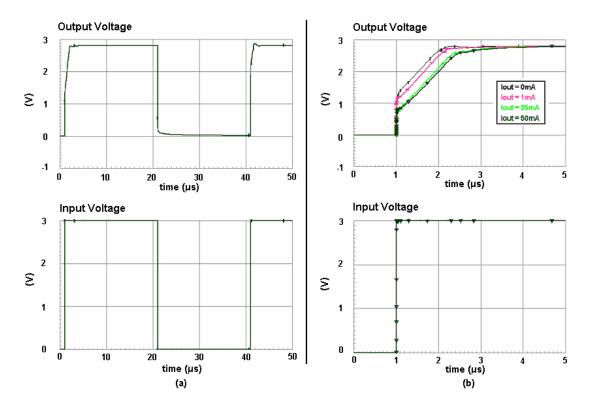

| Fig. 56. | Turn-on settling time for various output current conditions:<br>(a) full pulse and (b) expanded view.                                |      |

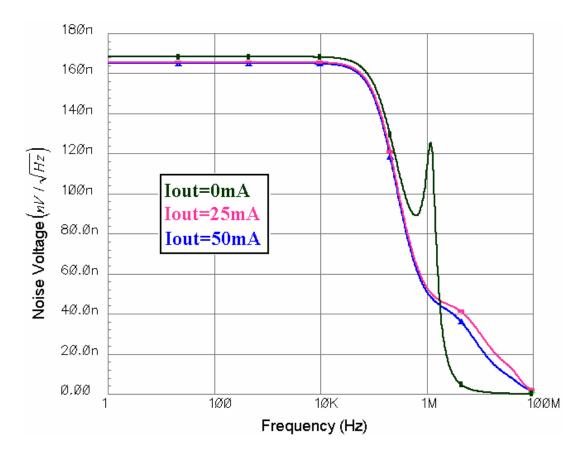

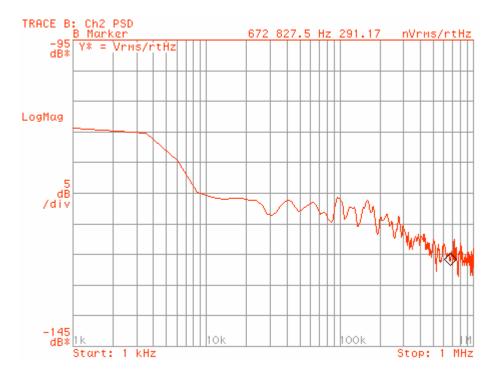

| Fig. 57. | Equivalent output noise for various loading conditions.                                                                              | 71   |

|          |                                                                                                                                                                                                                            | Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

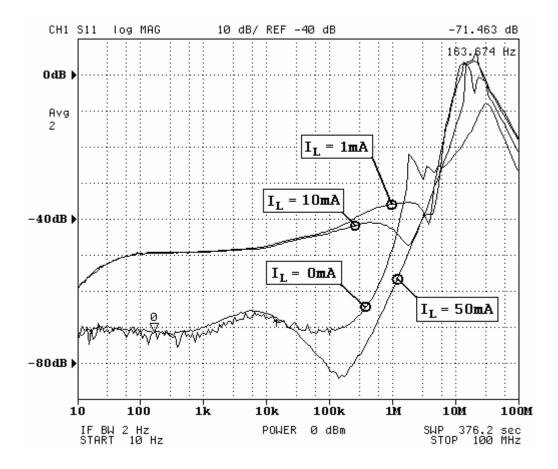

| Fig. 58. | PSRR measurement for various output current conditions.                                                                                                                                                                    | 73   |

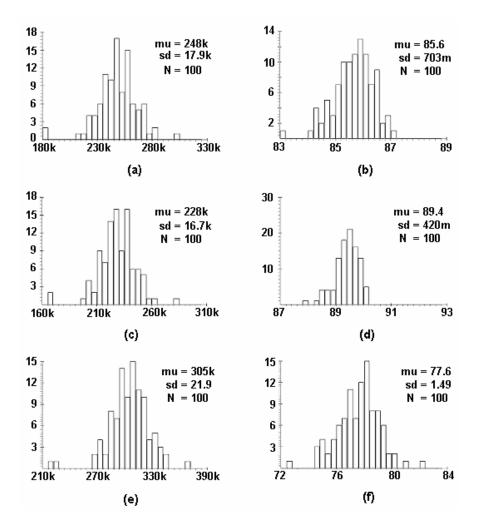

| Fig. 59. | Process variation for $I_{OUT} = 0mA$ : nominal GBW<br>(a) and phase margin (b), $C_f$ and $R_f + 20\%$ of nominal GBW<br>(c) and phase margin (d), and $C_f$ and $R_f - 20\%$ of nominal GBW<br>(e) and phase margin (f). | 74   |

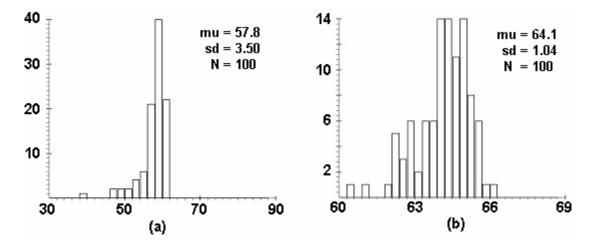

| Fig. 60. | Process variation on DC gain for $I_{OUT} = 0$ mA (a) and 1mA (b)                                                                                                                                                          |      |

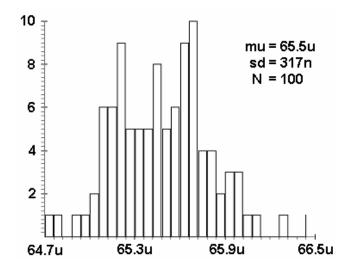

| Fig. 61. | Process variations effects on dc quiescent current.                                                                                                                                                                        |      |

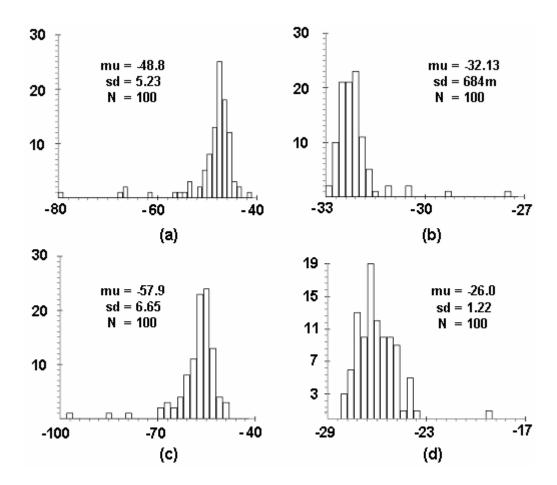

| Fig. 62. | Process variation on PSRR for $I_{out} = 0$ mA at 1Hz<br>(a) and 100kHz (b) and for $I_{out} = 50$ mA at 1Hz (c) and 100kHz (d)                                                                                            | 76   |

| Fig. 63. | Process variation on DC steady-state output voltage for I <sub>out</sub> set to 0mA (a), 1mA (b), 10mA (c) and 50mA (d).                                                                                                   | 77   |

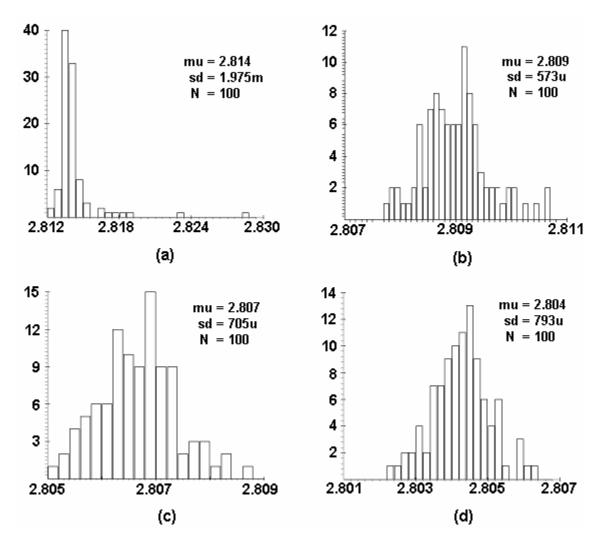

| Fig. 64. | Final layout in TSMC 0.35µm CMOS technology.                                                                                                                                                                               | 78   |

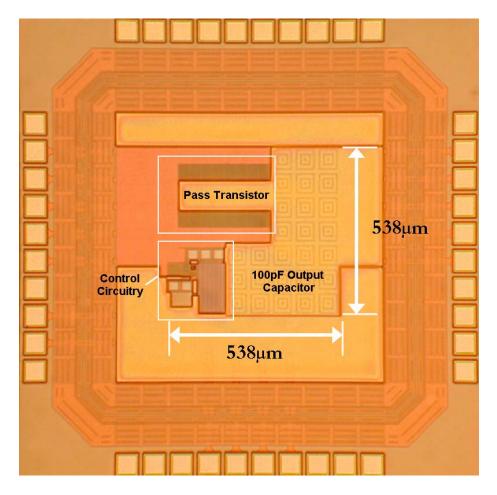

| Fig. 65. | Final populated test board and setup.                                                                                                                                                                                      |      |

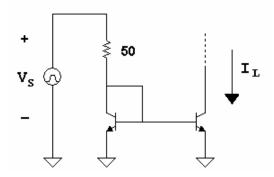

| Fig. 66. | Transient load current generator                                                                                                                                                                                           |      |

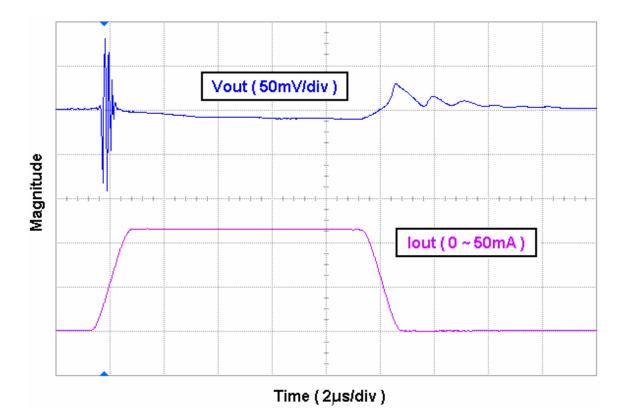

| Fig. 67. | Transient response for a 0mA to 50mA load transient with $V_{IN} = 3V$                                                                                                                                                     |      |

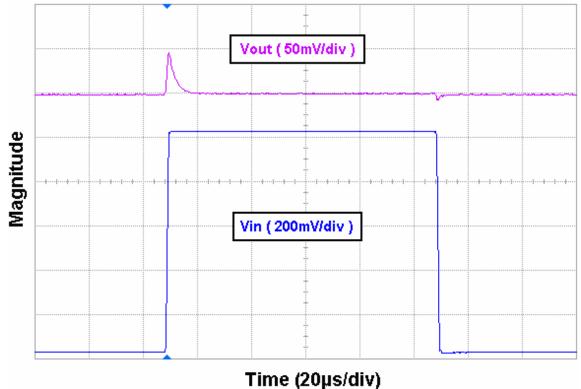

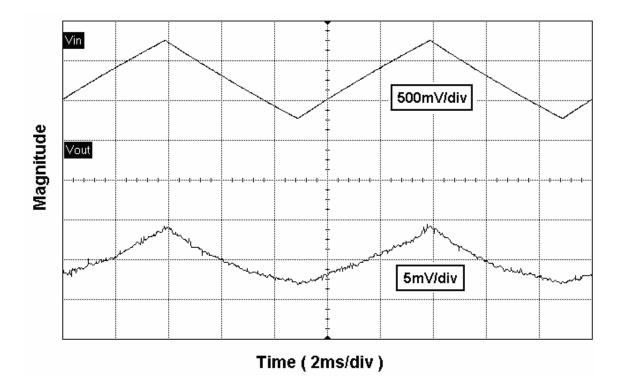

| Fig. 68. | Experimental line transient response with $I_{out} = 0mA$                                                                                                                                                                  |      |

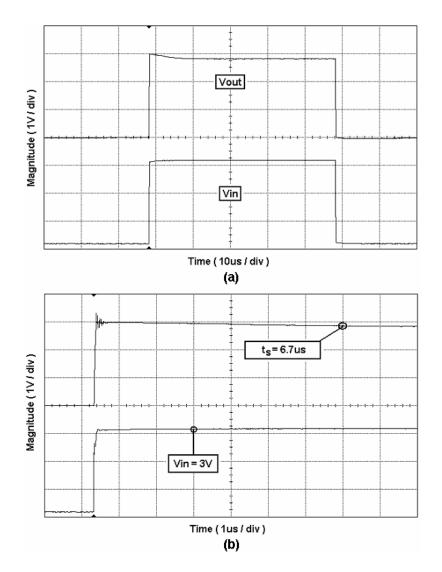

| Fig. 69. | Turn-on settling time for $I_{OUT} = 0$ mA: full pulse (a) and expanded view (b)                                                                                                                                           |      |

| Fig. 70. | Turn-on settling time for $I_{OUT} = 10mA$ (a) and $I_{OUT} = 50mA$ (b)                                                                                                                                                    |      |

| Fig. 71. | PSRR for various loading conditions.                                                                                                                                                                                       |      |

| Fig. 72. | Line ripple rejection at 100Hz.                                                                                                                                                                                            |      |

| Fig. 73. | Noise Spectrum for 50mA output current.                                                                                                                                                                                    |      |

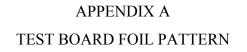

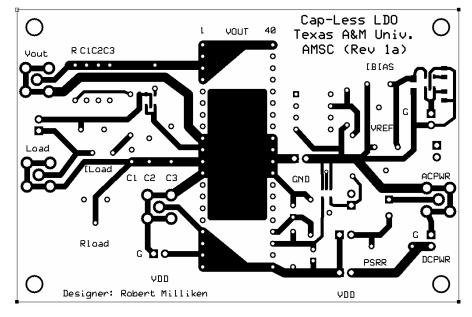

| Fig. 74. | Top layer of PCB                                                                                                                                                                                                           | 94   |

| Fig. 75. | Bottom layer of PCB from top view                                                                                                                                                                                          | 94   |

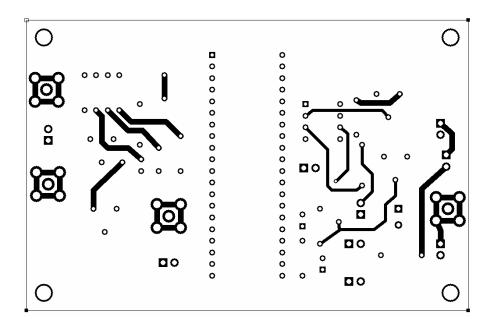

| Fig. 76. | Test board schematic diagram.                                                                                                                                                                                              | 95   |

# LIST OF TABLES

# Page

| TABLE I.    | Capacitor-less LDO Specification                | .21  |

|-------------|-------------------------------------------------|------|

| TABLE II.   | TSMC 0.35 Data: Run T4CU                        | .24  |

| TABLE III.  | Pass Transistor Dimensions                      | . 24 |

| TABLE IV.   | Amplifier Block Small Signal Transfer Functions | . 30 |

| TABLE V.    | AC Response Test Circuit Parameters             | . 33 |

| TABLE VI.   | Load Dependent Poles and Zeros                  | .36  |

| TABLE VII.  | Differentiator Simplifications                  | . 50 |

| TABLE VIII. | Design Guide                                    | . 59 |

| TABLE IX.   | Fabricated Circuit Parameters                   | .61  |

| TABLE X.    | Integrated Output Noise: 1Hz ~ 100kHz           | . 72 |

| TABLE XI.   | Simulated Worst Case Parameters                 | . 73 |

| TABLE XII.  | Final LDO Comparison                            | . 90 |

#### I. INTRODUCTION

Industry is pushing towards complete system-on-chip (SoC) design solutions including power management. The study of power management techniques has increased dramatically within the last few years corresponding to the vast increase in the use of portable, handheld battery operated devices [1]. Power management seeks to improve the device power's efficiency resulting in prolonged battery life and operating time for the device. A power management system contains several subsystems including linear regulators, switching regulators, and control logic. The control logic changes the attributes of each subsystem; turning the outputs on and off as well as changing the output voltage levels, to optimize the power consumption of the device.

The presented research focuses on low drop-out (LDO) voltage regulators. LDO regulators are an essential part of the power management system that provides constant voltage supply rails. They fall into a class of linear voltage regulators with improved power efficiency. LDO voltage regulators have several inherent advantages over conventional linear voltage regulators making them more suitable for on-chip power management systems [2].

A power management system usually contains several LDO regulators and switching regulators. The conventional LDO voltage regulator requires a relatively large output capacitor in the single microfarad range. Large microfarad capacitors can not be realized in current design technologies, thus each LDO regulator needs an external pin for a board mounted output capacitor. The presented research proposes to remove the large external capacitor, eliminating the need for an external pin. Removing the large output capacitor also reduces the board real estate and the overall cost of the design and makes it suitable for SoC applications.

#### A. LDO Regulator Applications

LDO voltage regulators compose a small subset of the power supply arena. LDO voltage regulators are used in analog applications that generally require low noise, high accuracy power rails. Voltage regulators provide a constant voltage supply rail under all loading conditions.

This thesis follows the style of the IEEE Journal of Solid-State Circuits.

These conditions include fast current transients and rapid changes in the load impedance. Most hand-held, battery-powered electronics feature power-saving techniques to reduce power consumption. Circuits that are not performing tasks are temporarily turned off lowering the overall power consumption. The LDO voltage regulator, therefore, must respond quickly to system demands and power up connected circuits within a few system clock cycles, typically 1 to 2  $\mu$ s.

#### 1. Cell Phones

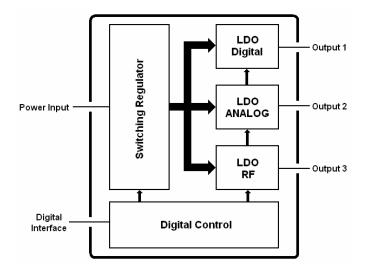

A typical cell phone power management IC is shown in Fig. 1. The purposed LDO regulator topology would be used for the RF/Analog power supplies. These require ultra low noise and a linear output. The LDO regulators are usually placed after switching regulators to improve their efficiency. The RF/analog blocks require LDO regulators with output currents up to 50 mA. They also require turn-on settling times around 2 µs.

Fig. 1. Cell phone power management application.

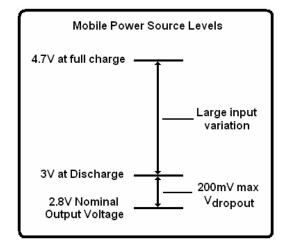

Most cell phones use a 1 cell Li-ion battery supply. The maximum output voltage for a Li-ion battery is typically 4.2V at full charge. At the onset of battery dropout, the battery supplies 2.92V. Thus, the circuits must operate below roughly 3V. Fig. 2 shows the typical voltage

headroom at full battery discharge. To improve power efficiency, most system blocks are optimally design to operate with 2.8V power rails.

Fig. 2. Cell phone battery characteristics.

The proposed capacitor-less LDO was design to replace current RF/analog LDO regulators that require a large external output capacitor. These blocks operate at 2.8V and consume approximately 32 mA of current. Dropout voltage is a defining characteristic of an LDO regulator and defines the minimum voltage drop across the control element, usually a large common-source output transistor or pass transistor. The dropout voltage of the regulator can not exceed 200 mV to operate at the full battery discharge condition. The typical RF standby current is 50  $\mu$ A and the RF/analog needs 65dB of power-supply-rejection-ratio (PSRR) at 217Hz.

#### 2. High-Efficiency Linear Regulation

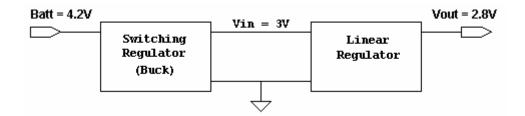

Linear regulators suffer from poor efficiency. The efficiency is inversely proportional to the voltage drop across the control element. Typically, linear regulators are cascaded after switching regulators. Switching regulators have the ability to buck or boost the input voltage to any desired output voltage with near 100% efficiency. Therefore, the voltage drop across the control element can be reduced which in turn increases the power efficiency of the linear regulator. Fig. 3 shows a linear regulator cascaded after a switching regulator.

Fig. 3. High efficiency linear regulation.

Without the switching regulator, the voltage drop across the linear regulator ( $V_{IN} - V_{OUT}$ ) would drastically increase. The switching regulator is designed to minimize the voltage drop across the linear regulator during loading conditions. Charge pumps can also be used to reduce the size and cost of the switching regulator.

#### B. Conventional Linear and LDO Regulator Architectures

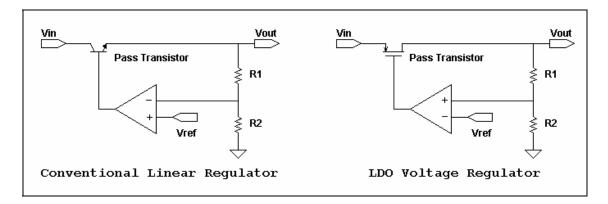

Linear voltage regulators come in two different topologies: conventional linear regulators and LDO voltage regulators [3]. The only topological difference arises from the orientation of the pass element. The conventional linear voltage regulator uses a source follower in either a single transistor realization or a Darlington BJT configuration. The LDO regulator on the other hand uses a single transistor in a common-source configuration operating in saturation. The two configurations are shown in Fig. 4.

Fig. 4. Linear voltage regulator topologies.

Both linear regulators operate using the same feedback mechanism. The output voltage is sensed through feedback resistors  $R_1$  and  $R_2$ . An error amplifier then compares the scaled output voltage to a reference voltage. The error signal is fed to the pass transistor and forms the negative feedback path.

Transistor orientation plays a major role in the operation and the stabilization of the linear voltage regulator. The conventional linear regulator requires gate drive voltages in excess of the input voltage making it cumbersome for low voltage applications. Conventional linear regulators are being used in some low-voltage applications but necessitate the use of charge pump gate drives. LDO voltage regulators overcome the necessary voltage headroom by operating the pass transistor in a common-source configuration. The  $V_{DS}$  saturation voltage of the pass transistor limits the regulator operation. The drop-out voltage or  $V_{DSAT}$  is a function of the maximum output current and the size of the pass transistor.

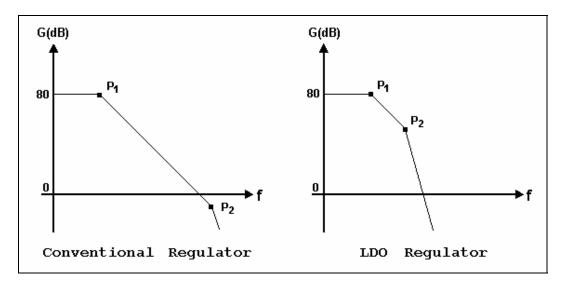

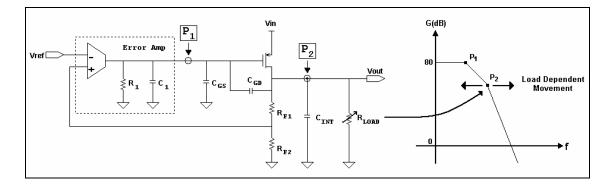

As mentioned earlier, the transistor orientation affects the stability of the regulator. Typical small signal AC responses for both architectures are shown in Fig. 5. The conventional linear regulator is inherently stable due to the low output impedance of the source follower. The first pole,  $P_1$ , acting as the dominant pole, is generated from the error amplifier output impedance. The output pole,  $P_2$ , moves with the load impedance but resides at much higher frequency.

Fig. 5. AC pole locations without compensation.

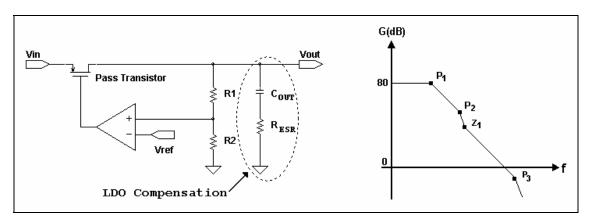

LDO voltage regulators can operate in low voltage applications without the need of charge pumps, but they are inherently unstable. The large output capacitor and high output impedance create the dominant pole,  $P_1$ . This dominant pole, however, is located in close proximity to the error amplifier output pole,  $P_2$ . Thus, the LDO regulator's stability can not be guaranteed and will most likely be unstable. LDO regulators must be internally or externally compensated for guaranteed stability. Typical LDO regulators use the electro-static resistance (ESR) of the output capacitor to reach stability. The ESR creates a zero, that when placed in the vicinity of  $P_2$ , can add phase necessary to maintain stability. Fig. 6 shows the use of capacitor ESR.

Fig. 6. Conventional LDO regulator compensation.

The ESR also creates a pole,  $P_3$ . The regulator stability depends heavily on the value of ESR. As ESR is decreased, the location of  $Z_1$  moves to the right and consequently has no effect on phase margin. On the other extreme, when ESR is increased significantly, the associated pole,  $P_3$ , moves below the gain-bandwidth, and the LDO regulator becomes unstable. A given LDO regulator must be given a range of stable capacitor ESR, otherwise the LDO regulator will be unstable.

Several recent publications have sought to eliminate the dependence on ESR. They exploit the use of internal compensation, either by creating an internal zero or adaptively modulating the location of the dominate pole. The presented research seeks to push one step further by eliminating the large external output capacitor altogether. The research begins with

the basic fundamental properties of linear regulators. This forms the foundation and direction to realize capacitor-less LDO voltage regulators.

#### C. LDO Regulator Characterization

LDO voltage regulators and all other voltage regulators ideally have constant output voltage regardless of supply voltage or load current variations. Voltage regulator specifications generally fall into three categories: static-state or steady-state specifications, dynamic-state specifications, and high-frequency specifications [4]. All the equations presented consider only CMOS LDO voltage regulators, but the same basic principles relate to most other linear voltage regulators.

#### 1. Static-state Specifications

The static-state parameters include the line regulation, the load regulation, and the temperature coefficient effects. The line and load regulation specifications are usually defined for a given LDO regulator and measure the ability to regulate the steady-state output voltage for given line and load steady-state values. The temperature coefficient defines the combined performance of the voltage reference and the error amplifier offset voltage.

Line Regulation defines the ratio of output voltage deviation to a given change in the input voltage. The quantity reflects the deviation after the regulator has reached steady-state. A general line regulation equation is given in equation 1.

$$\frac{\Delta V_{OUT}}{\Delta V_{IN}} \approx \frac{g_{mp} r_{op}}{A\beta} + \frac{1}{\beta} \left( \frac{\Delta V_{REF}}{\Delta V_{IN}} \right)$$

(1)

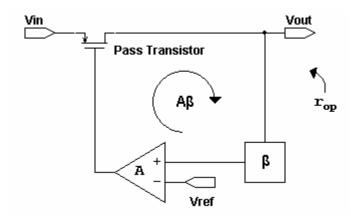

Line regulation depends on the pass transistor transconductance,  $g_{mp}$ , the LDO output resistance,  $r_{op}$ , the LDO loop gain, A $\beta$ , and the feedback gain,  $\beta$ . Fig. 7 below illustrates the LDO parameters.

Fig. 7. LDO regulator parameters.

Smaller output voltage deviation for a given dc change in input voltage corresponds to a better voltage regulator. To increase the line regulation, the LDO regulator must have a sufficiently large loop gain. These quantities become clear in the LDO regulator design discussion.

Load regulation is a measure of output voltage deviation during no-load and full-load current conditions. The load regulation is related to the loop gain, A $\beta$ , and the pass transistor output impedance,  $r_{op}$ . This relation is given in equation 2.

$$LR_{load} = \frac{\Delta V_O}{\Delta I_O} = \frac{r_{op}}{1 + A\beta}$$

(2)

The load regulation improves as the loop-gain increases and the output resistance decreases. The load regulation only applies to the LDO regulator steady-state conditions and does not include load transient effects.

The temperature coefficient defines the output voltage variation due to temperature drift of the reference and the input offset voltage of the error amplifier. The temperature coefficient is given in equation 3.

$$TC = \frac{1}{V_{OUT}} \cdot \frac{\partial V_{OUT}}{\partial Temp} \approx \frac{1}{V_{OUT}} \cdot \frac{\Delta V_{TC}}{\Delta Temp} = \frac{\left[\Delta V_{TC\,REF} + \Delta V_{TC\,VOS}\right] \cdot \frac{V_{OUT}}{V_{REF}}}{V_{OUT} \cdot \Delta Temp}$$

(3)

The output voltage accuracy improves as the error amplifier offset voltage is reduced and the reference voltage temperature dependence is minimized.

The LDO regulator's dropout voltage determines the maximum allowable current and the minimum supply voltage. These specifications, dropout voltage, maximum load current, and minimum supply voltage, all depend on the pass transistor parameters. A particular LDO design typically specifies the maximum load current and the minimum supply voltage it can tolerate while maintaining pass transistor saturation. Equation 4 relates the LDO dropout voltage to device parameters were  $I_{LOAD}$  is the maximum sustainable output current.

$$V_{dropout} = I_{LOAD} \cdot R_{ON} = V_{DSAT, PMOS}$$

(4)

The pass transistor dimensions are designed to obtain the desired  $V_{DSAT}$  at the maximum load current,  $I_{LOAD}$ .

#### 2. Dynamic-state Specifications

The LDO regulator dynamic-state specifications specify the LDO regulator's ability to regulate the output voltage during load and line transient conditions. The LDO regulator must respond quickly to transients to reduce variations in output voltage. Dynamic-state specifications, unlike steady-state specifications, depend on the large signal LDO regulator capabilities. The most significant capability is the charging and discharging of parasitic capacitance and the parasitic capacitor feed-through.

Load transients define the LDO regulator's ability to regulate the output voltage during fast load transients. The largest variations in output voltage occur when the load-current steps from zero to the maximum specified value. The ability of the LDO to regulate the output voltage

during a large current transient depends on the closed-loop bandwidth, the output capacitance, and the load-current. The output voltage variation is modeled in equation 5.

$$\Delta V_{out} = \frac{I_{\max} \cdot \Delta t}{C_{out}} \tag{5}$$

$I_{max}$  is the maximum specified output current,  $\Delta t$  is the LDO response time, and  $C_{out}$  is the LDO output capacitance.  $\Delta t$  is approximately the reciprocal of the LDO closed-loop bandwidth. A large output capacitor and large closed-loop bandwidth improve the load regulation. Conventional LDO regulators inherently have large output capacitors and therefore will have better load regulation verses capacitor-less LDO regulators.

Parasitic capacitors also cause slewing effects that degrade LDO regulator's load transient response. The gate capacitance of the pass transistor can be significant and places strain on the error amplifier. If the slew rate at the gate of the pass transistor is much slower than the gain-bandwidth product, significant transient voltage spikes appear at the output voltage node during fast load transients. This effect becomes more pronounced with capacitor-less LDO regulators.

Ripple-rejection-ratio specifies the ability for the regulator to rejected input signals from the output node. This parameter measures the small-signal gain from the input voltage to the output voltage. The ripple rejection ratio is given in equation 6.

$$ripple \ rejection = 20 \log_{10} \frac{output \ ripple \ voltage}{input \ ripple}$$

(6)

The ripple-rejection-ratio is typically determined for lower frequencies within the gainbandwidth product. Large input voltage transient spikes can cause larger output voltage variations than predicted by the ripple-rejection-ratio. The deviation is due to large signal effects, mainly capacitor slewing.

#### 3. High-frequency Specifications

Power-supply-rejection-ratio (PSRR) and regulator output noise can be categorized as high-frequency specifications. Both parameters are small signal parameters and are plotted verses frequency. Most LDO regulators specify PSRR at certain frequencies as well as spot noise at a particular frequency greater than the gain-bandwidth product [5].

PSRR defines the LDO regulator's ability to reject high-frequency noise on the input line. PSRR is a function of pass transistor parasitic capacitances and is proportional to the reciprocal of the loop gain. The error amplifier plays a major role in improving PSRR [5]. The combined individual error amplifier PSRR and the individual pass transistor PSRR is desired to sum to zero at the output voltage node. The design techniques to minimize PSRR are studied later on in the text.

Output noise is primarily defined by the input stage transconductance. The subsequent stages do not add significant noise to the output. Maximizing the input transistors' size lowers the output noise. The optimal noise figure is dependent on each particular design and a general analysis lacks sufficient information.

#### 4. LDO Regulator Efficiency

The LDO regulator efficiency is determined by three parameters: ground current, load current, and pass transistor voltage drop. The total no-load quiescent current consumption for the entire LDO regulator circuitry is defined as the ground current. Equation 7 relates the LDO regulator power efficiency.

$$Eff = \frac{V_{out} \cdot I_{LOAD}}{V_{in} \cdot (I_{GND} + I_{LOAD})}$$

(7)

There are two cases for power efficiency, one for small load currents and one for large load currents. The relation reduces to equation 8 for small load currents.

$$Eff \approx \frac{I_{LOAD}}{I_{GND} + I_{LOAD}}$$

(8)

Thus, ground current affects the LDO regulator efficiency much more at very low load currents. The longevity of battery life for low current applications can be significantly increased by reducing the quiescent ground current. At the other extreme, for very large load currents, the power efficiency is solely dependent on the pass transistor voltage drop, shown in equation 9.

$$Eff \approx \frac{V_{out}}{V_{in}} \tag{9}$$

The efficiency of the linear regulator approaches 100% as the output voltage approaches the input voltage. This scenario, however, requires an infinitely large pass transistor but would result in an infinite gate capacitance. Clearly, there is a trade-off between efficiency and the speed of the LDO regulator.

#### 5. Specification Trade-offs

All the LDO regulator specifications are interrelated and lead to important tradeoffs. The largest among all other specifications is efficiency, stability, and transient response. The optimization, especially with tight constraints, becomes very convoluted. The tradeoffs will be more apparent when designing the LDO regulator.

#### D. Capacitor-Less LDO Voltage Regulators

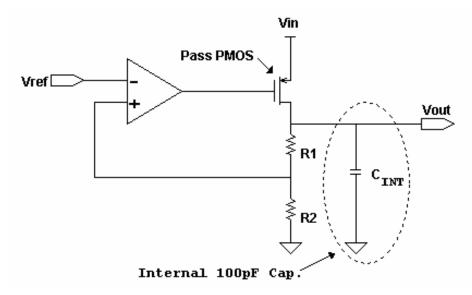

The basic linear voltage regulator architectures and their properties have been discussed. Research continues on conventional LDO regulators but recent research is focusing on capacitorless LDO voltage regulators [2]-[10]. As mentioned before, removing the output capacitor on LDO regulators allows SoC designs to fully incorporate power management systems with multiple LDO voltage regulators. Removing the external capacitor also reduces board real estate and system costs. The basic capacitor-less LDO voltage regulator is shown in Fig. 8.

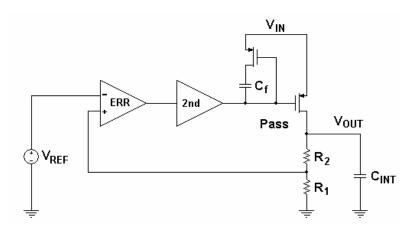

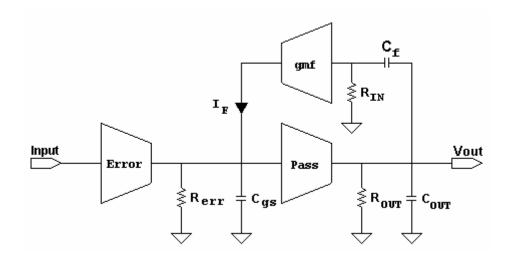

Fig. 8. Capacitor-less LDO voltage regulator.

The capacitor-less LDO regulator still has an internal output capacitor but it is much smaller than those used by conventional LDO voltage regulators. Current industrial capacitor-free LDO regulators decrease the required external capacitor by a factor of 10 or so, but they still use a 0.1 microfarad external capacitor. The presented research purposes the complete removal of the external capacitor and its replacement with a small internal capacitor. The internal capacitor is maximized as much as possible but is constrained by chip size dimensions and current CMOS technology. Typical capacitor values fall in the range of a few hundred picofarads.

#### 1. Initial Capacitor-less LDO Regulators Pole Locations

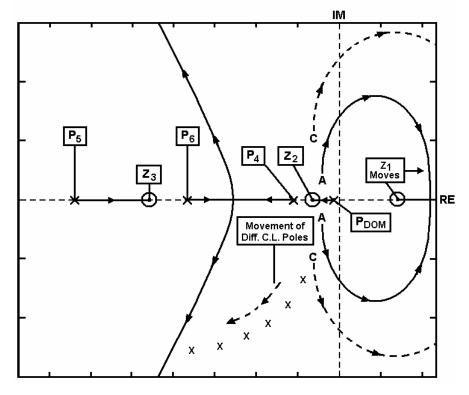

Most of the conventional LDO specifications are greatly affected when the external capacitor is reduced by several orders of magnitude. The most significant side effect is stability degradation. The uncompensated capacitor-less LDO has two major poles, the error amplifier output pole,  $P_1$ , and the load dependent output pole,  $P_2$ . Fig. 9 shows the relative pole location.

Fig. 9. Pole locations for uncompensated capacitor-less LDO voltage regulator.

The standalone error amplifier has a pole located at relatively high frequency. The equivalent pass transistor input capacitance adds significant capacitance to the error amplifier output impedance. The location of  $P_1$  is given by equation 10.

$$\omega_{P1} = \frac{1}{R_1 \cdot (C_1 + C_{GS} + A_{Pass}C_{GD})}$$

(10)

The pass transistor is very large in order to reduce  $V_{DSAT}$ . Therefore,  $C_{GS}$  and  $C_{GD}$  are extremely large, in the tens of picrofarads.  $C_{GD}$  also forms a Miller capacitor which increases the effective input capacitance by the gain of the pass transistor. The pass transistor has a typical gain of 20dB or 10V/V at low load currents. The Miller capacitor can increase the effective pass transistor input capacitor to a few hundred picofarads. Thus, the pole, P<sub>1</sub>, resides at low frequencies of typically a few kilohertz. The gain of the pass transistor changes with varying load current. P<sub>1</sub> is therefore load dependent but less so than P<sub>2</sub>. The first tradeoff is between efficiency and stability. The large output current efficiency is inversely proportional to the pass transistor's  $V_{DSAT}$ . Smaller  $V_{DSAT}$  increases the effective input gate capacitance and consequently decreases the error amplifier pole frequency, increasing the burden on the error amplifier. The second pole,  $P_2$ , is located at the LDO's output. The output resistance decreases for increasing load current.  $P_2$  is directly proportional to the load current and is load dependent. The location of  $P_2$  is given by equation 11.

$$\omega_{P2} = \frac{1}{\left(R_{OUT} // R_{LOAD}\right) \cdot C_{INT}}$$

(11)

High load current pushes the output pole,  $P_2$ , to higher frequency, and the capacitor-less LDO regulator is usually stable. At low currents, the effective load resistance increases significantly.  $P_2$  is pushed to lower frequency in close proximity to the error amplifier pole. Stability cannot be guaranteed due to the decreased phase margin. The uncompensated capacitor-less LDO regulator is not stable at low currents, especially at the no-load condition.

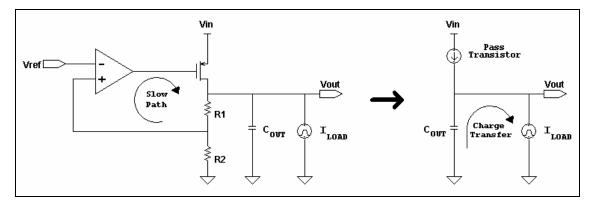

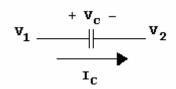

#### 2. Transient Response Attributes

The large external capacitor is used on conventional LDO regulators and linear regulators in general to improve the transient load regulation [2],[6] and [8]. The output capacitor stores potential energy equivalent to the output voltage. The ideal capacitor can deliver instantaneous current and has infinite bandwidth, assuming its source resistance in zero. The transfer of charge from the capacitor to the load corresponds to a drop in output voltage. Equation 12 gives a relationship for this voltage difference.

$$\Delta V_{OUT} = \frac{\Delta Q}{C_{OUT}} \tag{12}$$

Thus, the change in output voltage is inversely proportional to the output capacitance. The output voltage ripple for a given load transient is reduced by increasing the output capacitance. This relationship becomes much more apparent when the load transients are much faster than the

gain-bandwidth product, which is usually the case. Fig. 10 illustrates this situation in a conventional LDO voltage regulator.

Fig. 10. Equivalent circuit for fast load transients.

The gain-bandwidth is much slower than the load transient and the pass transistor gate voltage can be assumed constant throughout the load transient. The circuit diagram to the right of Fig. 10 has substituted a constant current source for the pass transistor. Then the output voltage is only determined by equation 12 and equation 5. The capacitor-less LDO regulator does not have the advantages of a large external capacitor. Instead, the constant current source in Fig. 10 must be replaced with high speed adaptive current source.

The pass transistor has a very large transconductance, but the large effective input capacitance limits its transient speed. The effective input gate capacitance is driven by the error amplifier. In order for the error amplifier to drive large capacitive loads, the quiescent bias current must be increased. Slewing occurs at the pass transistor gate given by equation 13.

$$SR = \frac{I_{bias,error}}{C_{GS,eff}}$$

(13)

The error amplifier output stage bias current only effects the slew rate in equation 13, and the  $C_{GS,eff}$  is the total effective input gate capacitance of the pass transistor. Conventional LDO

regulators typically use an error amplifier with a class AB output stage. This lowers the output impedance and increases the drive capability of the error amplifier. The fundamental problem still exists; the power must be increased to drive larger pass transistors. This forms the second inherent tradeoff, the power efficiency is directly proportional to the transient response. A third tradeoff exists between large-current power efficiency and low-current efficiency. The large current efficiency is improved by reducing  $V_{DSAT}$ . The effective pass transistor input gate capacitance is increased, however; the ground current or bias current must be increased for acceptable load transient response. The tradeoff is shown in Fig. 11.

Fig. 11. Power efficiency tradeoff.

The capacitor-less LDO regulator is design for a specific application where the nominal operating point is known. Clearly, the pass transistor forms the backbone of the LDO regulator and consequently defines most of the design tradeoffs.

#### 3. Previous Academic Works

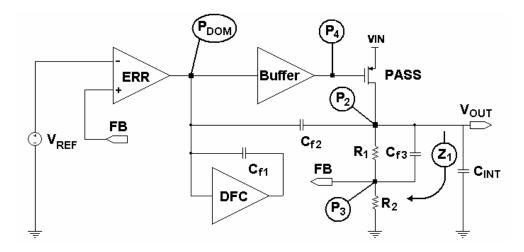

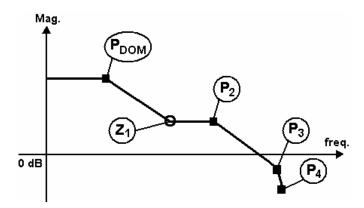

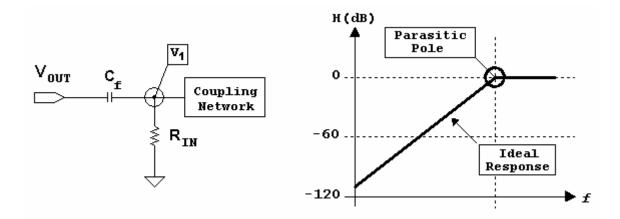

Only a few works have been published in the IEEE regarding capacitor-less LDO regulators [4], [11], and [12]. To date, there have been no works published in IEEE journals that demonstrate a completely stable common-source LDO regulator with no external capacitor. They all have problems either tracking the output pole variation or have problems with high impedance loads. The first work used a DFC analog block to create a fix internal dominant pole [4]. The circuit architecture is shown in Fig. 12.

Fig. 12. Capacitor-free LDO voltage regulator.

A zero and a pole are created with compensation capacitor  $C_{F1}$ . The zero is used to cancel the output pole. The parasitic pole,  $P_f$ , must be placed past the unity-gain frequency. The compensation technique is shown in Fig. 13.

Fig. 13. LDO compensation with  $C_{F1}$ .

Two problems arise with this architecture. First, the pole created with  $C_{F1}$  is limited by the selection of feedback resistors and will most likely be relatively close to  $Z_f$ . This greatly reduces the effect of the cancellation zero. Second, the zero is fixed and does not move with the load dependent output pole. This pole moves well over a decade, and the stability at no-load

condition is most likely unstable. The capacitor-free LDO regulator using this concept was unstable for loads smaller than 5mA.

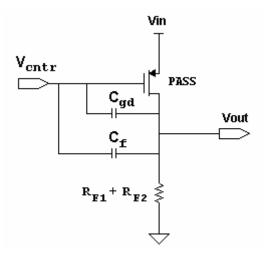

The second work [10] moves in the right direction using pole-zero tracking frequency compensation. The structure is shown in Fig. 14.

Fig. 14. LDO regulator with pole/zero tracking.

They use a variable zero created by a linear resistor. This structure is also not completely stable over the entire output current range. The resistance does not have enough tunable range due to its weak function of the load current.

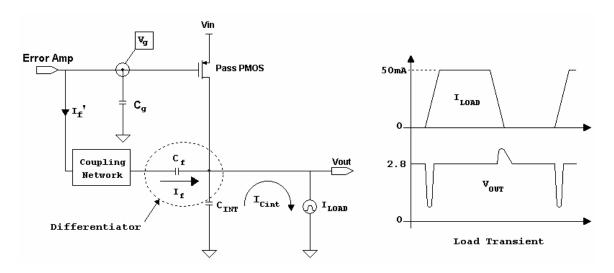

#### 4. Capacitor-less LDO Design Direction

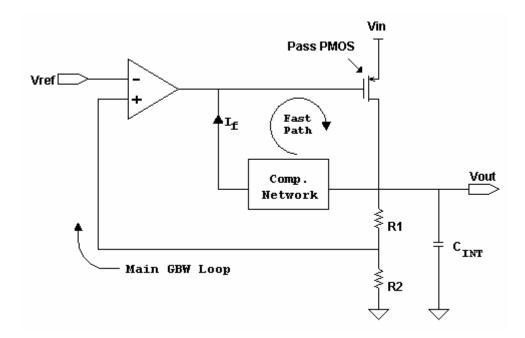

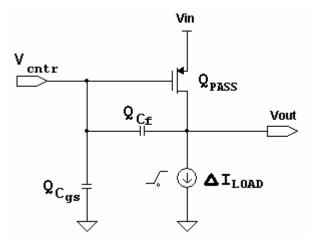

A new structure was needed to compensate the capacitor-less LDO while maintaining good load transient response and stability at low load currents. The transient response is dependent on the speed of the pass transistor and not the output capacitor. A fast transient path from the LDO output to the gate of the pass transistor was required since the system gain-bandwidth was relatively low in frequency. The capacitor-less LDO stability at low load currents was the second major problem. The initial idea sought to apply adaptive techniques to compensate the output pole and possibly the error amplifier output pole. The basic concept is shown in Fig. 15.

Fig. 15. Basic capacitor-less LDO concept.

The concept in Fig. 15 uses a fast path to improve the transient response. A compensation network is needed to stabilize the new fast transient system. The main feedback loop determines the capacitor-less LDO's gain-bandwidth product and is the main mechanism that replenishes the energy in the output capacitor, restoring the output voltage to the correct steady-state level. The fast path is an internal negative feedback loop with very high bandwidth, much greater than the overall gain-bandwidth product. The fast path senses any load current variation and mirrors and amplifies the signal directly into the gate of the pass transistor.

The concept in Fig. 15 formed the basis of research and design for the final capacitorless LDO voltage regulator. A specific application was selected for the design, and the capacitor-less LDO was designed to approach most of the conventional LDO specifications. This leads to the formal design analysis discusses in Section II.

#### II. CAPACITOR-LESS LDO REGULATOR ANALYSIS

The capacitor-less LDO regulator design targets the cell phone and handheld device market. Each of these designs uses a power management IC to improve the battery life longevity and usually contain several LDO voltage regulators, shown in Fig. 1 in Section I. The proposed capacitor-less LDO voltage regulator would most likely replace the analog/RF and audio power supplies. Based on the current specification for these LDO regulator applications, the proposed capacitor-less LDO specification was developed as shown in Table I.

# TABLE I CAPACITOR-LESS LDO SPECIFICATION

| PARAMETER       | VALUE                  |

|-----------------|------------------------|

| Gain Bandwidth  | $1 \sim 2 \text{ MHz}$ |

| Settling Time   | < 2 µs                 |

| Loop Gain       | $\sim 100 \text{ dB}$  |

| GND Current     | < 150 µA               |

| Dropout Voltage | 200 mV                 |

| Output Current  | $0 \sim 50 \text{ mA}$ |

| PSRR            | < -40dB @ 100kHz       |

| Output Noise    | $< 20 \ \mu V$         |

| Line Regulation | 0.01%                  |

| Load Regulation | 0.02%                  |

| Technology      | TSMC 0.35µ CMOS        |

|                 |                        |

The chosen capacitor-less LDO specification is competitive with current conventional LDO voltage regulators with the exception of the transient response and high frequency response, accounting for the reduced output capacitance. This formed the basis for the LDO design, and the device characterization soon followed.

The capacitor-less LDO design must incorporate two important criteria: stability and fast transient response. There were two possible angles of attack. The first method starts by stabilizing the LDO regulator and then optimizing the stability for fast transient response. The second method first optimizes the fast transient response and then stabilizes the fast transient

LDO regulator. It was found easier to apply the second method and start by adding a fast transient path.

The uncompensated capacitor-less LDO regulator had to be characterized first before any new topologies were developed. This included the complete characterization of poles, DC gains, and fixed device parameters. Also, the uncompensated transient response was needed to determine slewing issues and relative circuit speed. The capacitor-less LDO regulator was inherently unstable for DC output currents lower than approximately 5mA. However, a test circuit was constructed to measure the slewing effects. The pass transistor's subthreshold saturation region also played a major role in the LDO operation. These effects are all summarized in the following section, Uncompensated Device Characterization.

#### A. Uncompensated Device Characterization

The pass transistor determines the maximum output current and the dropout voltage. These parameters are essentially fixed throughout the LDO operation. The pass transistor could be designed before a new topology was constructed. Thus, the LDO compensation and the fast transient path are in place to compensate the effects of the large pass transistor.

The first section discusses the pass transistor design process. Following the design of the pass transistor, the LDO is characterized for both AC response and transient response. The results from the uncompensated device characterization were directly applied to the final proposed capacitor-less LDO topology.

#### 1. Pass Transistor Design

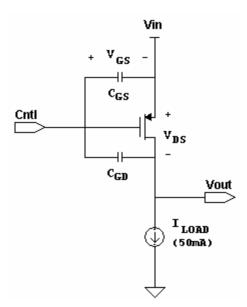

The dropout voltage of the capacitor-less LDO was selected to be 200mV for a maximum load current of 50mA based on current LDO regulator requirements. In device parameters, the pass transistor is designed to deliver a drain current of 50mA while maintaining a saturation voltage,  $V_{DS} \ge V_{GS} - V_T$ , of 200 mV or less. The pass transistor stage is shown in Fig. 16.

Fig. 16. Pass transistor design.

First order approximations were used to find the rough device dimensions. This relationship is shown in equation 14.

$$V_{dropout} = V_{DSAT} = \sqrt{\frac{2I_{MAX}}{\mu_p C_{OX} W / L}}$$

(14)

$I_{MAX}$  defines the maximum output current, forcing the dimensions of the pass transistor, W/L, for a desired minimum  $V_{DROPOUT}$ . The variables  $\mu_p$ , hole mobility, and  $C_{OX}$ , the gate capacitance per unit area, are device technology parameters and are given in Table II. The device parameters in Table II were used to design the pass transistor. Equation 14 was rearranged to find the pass transistor device dimensional ratio, W/L, shown in equation 15.

$$\left[\frac{W}{L}\right]_{PASS} = \frac{2I_{MAX}}{\mu C_{ox} V_{DSsat}^2} = 37.8 \times 10^3$$

(15)

| PARAMETER      | VALUE                    |

|----------------|--------------------------|

| $V_{TP}$       | 0.58 V                   |

| $V_{TN}$       | -0.74 V                  |

| $\mu_p C_{OX}$ | $180.2 \ \mu A/V^2$      |

| $\mu_n C_{OX}$ | $66.00 \mu \text{A/V}^2$ |

TABLE II

#### TSMC 0.35 DATA: RUN T4CU

The ratio found in equation 15 was very large. The channel length was minimized to reduce the gate capacitance  $C_{GS}$ . The minimum length is 400nm, set by the TSMC 0.35µm CMOS process. This forces the pass transistor width to 15,000µm or 15mm. BSIM3 computer simulations were used to verify and fine tune the pass transistor dimensions. Table III shows the calculated and simulated pass transistor parameters to yield a 200mV dropout voltage at 50mA load current.

# TABLE III

#### PASS TRANSISTOR DIMENSIONS

| CALCULATED                 | SIMULATED                   |

|----------------------------|-----------------------------|

| W = 15mm                   | W = 16mm                    |

| L = 400 nm                 | L = 400 nm                  |

| $C_{GS} = 19.1 \text{ pF}$ | $C_{GS} = 20.18 \text{ pF}$ |

| $C_{GD} = 5.0 \text{ pF}$  | $C_{GD} = 3.84 \text{ pF}$  |

CADENCE simulations show that the actual dimensional ratio of the pass transistor must be at least 40,000. Unfortunately, this means that for a device of minimum length, the required width must increase to 16mm instead of the calculated 15mm width. Such a large device introduces significant parasitic capacitances into the network, notably the gate-source capacitance  $C_{GS}$ . As mentioned previously in this report, large gate capacitance along with variable low-frequency load impedance makes stabilizing a capacitor-less LDO difficult. The gate-source capacitance of this PMOS pass-transistor measured 20pF. The Miller effect with  $C_{GD}$  further increases the effective gate capacitance. Equation 16 relates the total effective gate capacitance.

$$C_{GS,eff} \cong C_{GS} + (1 + A_{pass}) \cdot C_{GD} = C_{GS} + (1 + G_{m,pass}R_{O,pass}) \cdot C_{GD}$$

(16)

The effective pass transistor gate capacitance approaches 100pF. Thus, the Miller capacitor contributes most of the effective gate capacitance while varying with load conditions.

Pass transistor subthreshold operation is another major concern. For large variations in the load current, the PMOS transistor will undergo a transition from operating in the saturation region to operating in the subthreshold saturation region. The pass transistor exhibits an exponential relationship while operating in subthreshold in contrast to the nominal square law relationship. The relationship is shown in the equation 17.

$$I_D \cong I_{DO} \left[ \frac{W}{L} \right] e^{(qV_{GS}/nkT)} \tag{17}$$

Subthreshold operation produces a significantly slower response. This may cause significant degradation in the voltage regulation for applications where the load current drops to low current levels in a short span of time. This degradation in load regulation can only be counteracted by providing more current to the LDO, improving the speed of the circuit. This is especially true during subthreshold operation.

The pass transistor constitutes the only fixed predetermined capacitor-less LDO component. The other components, including the error amplifier, feedback gain, fast transient path, and the compensation network, are molded around the fixed pass transistor. Next, the newly designed pass transistor was simulated using a generic control loop.

#### 2. Uncompensated AC Response

The pole locations were determined over the entire desired operating range of 0 to 50mA, using the generic control loop. The pass transistor transconductance and output impedance were simulated in CADENCE over the output current operating range. The simulated pass transistor

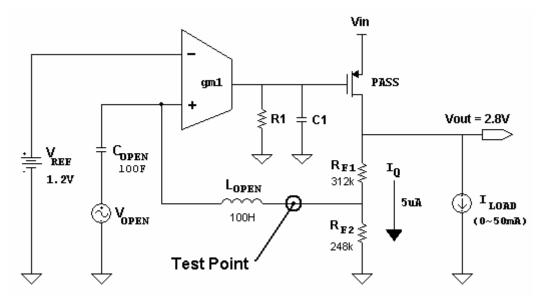

data could then be used in MATLAB for a more robust AC simulation. The control loop is shown in Fig. 17.

Fig. 17. AC open-loop simulation circuit.

The transconductance, gm1, and the output impedance,  $R_1$  and  $C_1$ , form the error amplifier. The feedback resistors,  $R_{F1}$  and  $R_{F2}$ , were designed to yield an output voltage of 2.8V. Equation 18 relates the reference voltage,  $V_{REF}$ , to the output voltage assuming infinite loop gain.

$$V_{OUT} = V_{REF} \cdot \left(1 + \frac{R_{F1}}{R_{F2}}\right) \tag{18}$$

The output voltage is defined by the feedback resistor ratio and the input reference voltage. The absolute resistance determines the pass transistor quiescent current,  $I_Q$ . Standard BiCMOS bandgap reference output is 1.24V in a range of -40°C to 80°C. Thus, the input reference voltage of 1.24V was used throughout the capacitor-less LDO regulator design.

$L_{OPEN}$  forms a DC feedback path, blocking most of the AC components. This allows for an open-loop AC response measurement at the test point shown in Fig. 17. The DC feedback loop through  $L_{OPEN}$  sets the DC operating points for the LDO that would normally occur during closed-loop operation.  $C_{OPEN}$  couples the AC test signal to the amplifier loop without affecting the LDO's DC operating points. Both  $L_{OPEN}$  and  $C_{OPEN}$  are very large, 100H and 100F respectively. This allows the AC measurement down to very low frequencies.

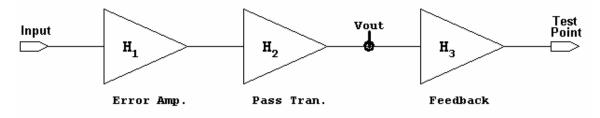

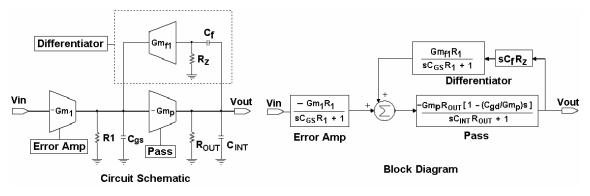

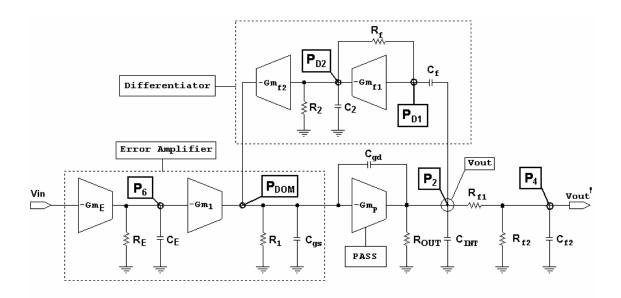

A block diagram was used to simulate the open-loop LDO AC response. The uncompensated LDO was divided into separate amplifier blocks shown in Fig. 18.

Fig. 18. AC open-loop block diagram test circuit.

$H_1$ ,  $H_2$ , and  $H_3$  represent the error amplifier, the pass transistor, and the feedback gain, respectively. The pass transistor was already designed based on the desired dropout voltage and the maximum load current. This left the error amplifier and the feedback gain to be designed. Feedback resistors,  $R_{F1}$  and  $R_{F2}$ , were designed to draw  $5\mu A$  of current through the pass transistor. The current through the series-connected feedback resistors is solely determined by the output voltage. Equation 19 defines the series relationship of  $R_{F1}$  and  $R_{F2}$ .

$$R_{F1} + R_{F2} = \frac{V_{OUT}}{I_{O,pass}} = \frac{2.8V}{5\mu A} = 560k\Omega$$

(19)

Equation 20 was then used to find the absolute resistor values, combining equation 18 and the results from equation 19.

$$R_{F2} = \frac{V_{REF}}{V_{OUT}} \left( R_{F1} + R_{F2} \right) = \left( \frac{1.24}{2.8} \right) \cdot 560k\Omega = 248k\Omega$$

(20)

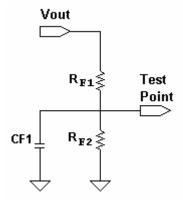

This forces the resistance of  $R_{F1}$  to 312k. A parasitic capacitor was also incorporated into the feedback gain section. This capacitor was used to simulate the effects of the error amplifier input capacitance and any parasitic capacitance associated with resistor layout. The addition of the capacitor is shown in Fig. 19.

Fig. 19. Feedback circuit with parasitic capacitor, C<sub>F1</sub>.

The feedback gain transfer function was divided into two components, the DC gain and the AC gain characteristics. Equation 21 gives the small signal transfer function for gain block  $H_3$ .

$$H_{3} = \left[\frac{R_{F2}}{R_{F1} + R_{F2}}\right]_{DC} \cdot \left[\frac{1}{1 + s(R_{F1} / / R_{F2}) \cdot C_{F1}}\right]_{AC}$$

(21)

Thus, the parasitic capacitor,  $C_{F1}$ , only contributes a pole. The location of the feedback pole resides at relatively high frequency. Nonetheless,  $C_{F1}$  can affect the phase margin and the fast transient response.

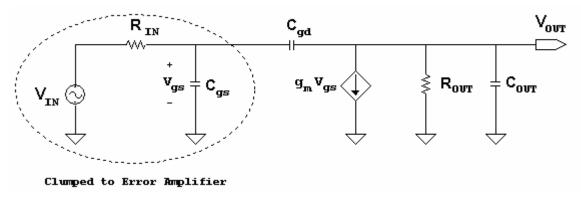

The pass transistor stage,  $H_3$ , forms a common source amplifier. Fig. 16 showed the complete pass transistor circuit including the parasitic capacitors,  $C_{GS}$  and  $C_{GD}$ . This circuit was used to form a small signal model, shown in Fig. 20.

Fig. 20. Pass transistor small signal analysis.

The pass transistor input impedance was merged with the error amplifier.  $H_3$  represents the rest of the pass transistor circuit elements. Preliminary inspection indicates  $H_3$  had one pole and one zero. Equation 22 forms the nodal analysis at the pass transistor output with  $V_{GS}$  as the input.

$$\frac{v_{out}}{R_{out}} + sC_{OUT}v_{out} + (v_{out} - v_{gs})sC_{gd} + v_{in}g_m = 0$$

(22)

Equation 22 was rearranged to form the output transfer function in equation 23.

$$\frac{v_{out}}{v_{gs}} = \frac{-g_m R_{out} \left(1 - s \frac{C_{gd}}{g_m}\right)}{s(C_{out} + C_{gd})R_{out} + 1}$$

(23)

Both a pole and a zero appeared in the transfer function reflecting the preliminary inspection. The transfer function for  $H_1$  followed similar results as  $H_2$  but without the feed-forward zero. Table IV lists the rest of the small signal characterization and the poles and zeros for the amplifier blocks given in Fig. 18.

| BLOCK          | TRANSFER FUNCTION                                                                                                               | POLE/ZERO                                                          |

|----------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| $H_1$          | $TF = \frac{g_{m1}R_1}{1 + sR_1C_1}$                                                                                            | $p_1 = \frac{1}{R_1 C_1}$                                          |

| H <sub>2</sub> | $TF = \frac{-g_{mp}R_{out}\left(1-s\frac{C_{gd}}{g_{mp}}\right)}{s(C_{out}+C_{gd})R_{out}+1}$                                   | $p_{2} = \frac{1}{R_{OUT}C_{OUT}}$ $z_{1} = \frac{g_{mp}}{C_{gd}}$ |

| H <sub>3</sub> | $TF = \left[\frac{R_{F2}}{R_{F1} + R_{F2}}\right]_{DC} \cdot \left[\frac{1}{1 + s(R_{F1} / / R_{F2}) \cdot C_{F1}}\right]_{AC}$ | $p_3 = \frac{1}{R_{F1}  / /  R_{F2} \cdot C_{OUT}}$                |

TABLE IV

AMPLIFIER BLOCK SMALL SIGNAL TRANSFER FUNCTIONS

Amplifiers  $H_1$  and  $H_2$  are characterized by a simple first order transconductance transfer function.  $H_1$  forms the error amplifier module, where  $C_1$  constitutes the error amplifier output capacitance in parallel with the effective pass transistor gate capacitance. The effective pass transistor gate capacitance was derived in equation 16. Equation 24 forms the complete error amplifier output pole.

$$\omega_{P1} = \frac{1}{R_1 C_1} = \frac{1}{R_1 [C_{error} + C_{GS} + (1 + G_{m, pass} R_{O, pass}) \cdot C_{GD}]}$$

(24)

$H_3$  forms the pass transistor common source amplifier with  $g_{mp}$  equaled to the pass transistor transconductance.  $R_{OUT}$  in pass transistor amplifier block,  $H_3$ , combines several circuit

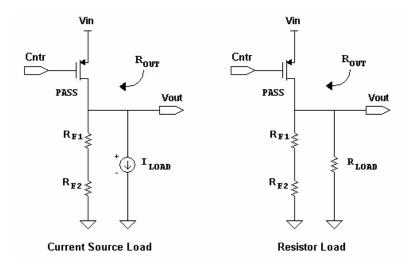

parameters. There are two different methods of modeling  $R_{OUT}$  based on loading conditions. The load can either be modeled as a resistor or as a current source. Fig. 21 shows the two different methods for modeling the pass transistor output impedance.

Fig. 21. Pass transistor output resistance models.

The pass transistor output resistance is formed from the parallel combination of the feedback resistors,  $R_{F1}$  and  $R_{F2}$ , the transistor output resistance, and the load resistance. Equation 25, using a current source load, and equation 26, using a resistor load, model the two forms of pass transistor output resistance.

$$R_{OUT} = (R_{O, pass} // R_{F1} + R_{F2} // R_{O, current})$$

(25)

$$R_{OUT} = (R_{O,pass} // R_{F1} + R_{F2} // R_L)$$

(26)

Resistive loading decreases the output impedance with respect to a current source load, and effectively pushes the output pole to higher frequencies. Resistive loading was used for the simple uncompensated AC response but was later changed to a current source for the final design. The error amplifier was design to yield an overall gain of 100dB. Simulations showed

that the pass transistor provides roughly 20dB of gain at the zero load current condition. Thus, the error amplifier requires 80 dB of gain. The error amplifier was also design to produce the dominant system pole around 100Hz, yielding a gain-bandwidth product of 1MHz for a single pole system. Equation 27 exemplifies the procedure for determining  $R_1$  and  $C_1$ .

$$C_1 = \frac{1}{R_1 p_1} = \frac{1}{10M\Omega \cdot (100Hz \cdot 2\pi)} = 0.159nF$$

(27)

$R_1$  was arbitrarily set to 10M $\Omega$ , forcing the effective error amplifier output capacitance,  $C_1$ , to 1.59nF. The error amplifier transconductance,  $g_{m1}$ , was determined by equation 28.

$$gm1 = \frac{A_{DC,error}}{R_1} = \frac{10,000V/V}{10M\Omega} = 1000\mu A/V$$

(28)

Finally, the pass transistor amplifier parameters were extracted from a BSIM3 simulation. Fig. 22 shows the simulation results. All the AC circuit parameters are tabulated in Table V.

Fig. 22. Pass transistor load-dependent DC operating points: (a) transconductance (b) output resistance.

| ERROR AMPLIFIER       |          | PASS TRANSISTOR  |                |  |

|-----------------------|----------|------------------|----------------|--|

| DC Gain               | 80 dB    | W/L              | 16mm/400nm     |  |

| Gm <sub>1</sub>       | 1000µA/V | Gm               | Variable       |  |

| <b>R</b> <sub>1</sub> | 10MΩ     | R <sub>out</sub> | Variable       |  |

| $C_1$                 | 0.159nF  | I <sub>Q</sub>   | 5μΑ            |  |

| Pole                  | 100Hz    | C <sub>OUT</sub> | 100pF          |  |

| FEEDBACK              |          | VOLTAGE LEVELS   |                |  |

| В                     | 0.443    | V <sub>REF</sub> | 1.24V          |  |

| R <sub>F1</sub>       | 312kΩ    | V <sub>IN</sub>  | 3.0V           |  |

| R <sub>F2</sub>       | 248kΩ    | V <sub>OUT</sub> | 2.8V           |  |

| C <sub>F1</sub>       | 1pF      | I <sub>OUT</sub> | $0 \sim 50 mA$ |  |

## TABLE V

#### AC RESPONSE TEST CIRCUIT PARAMETERS

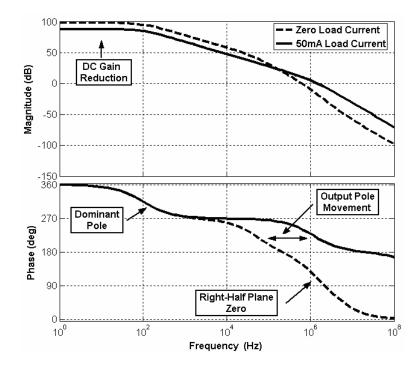

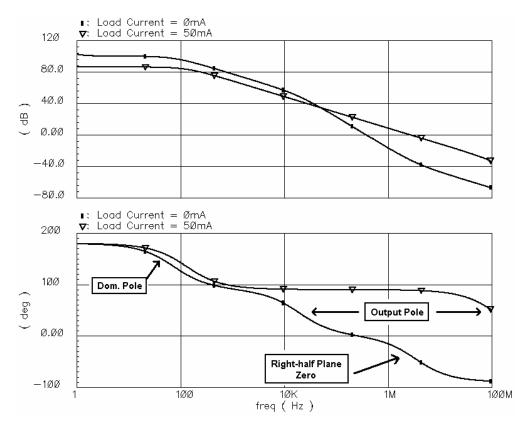

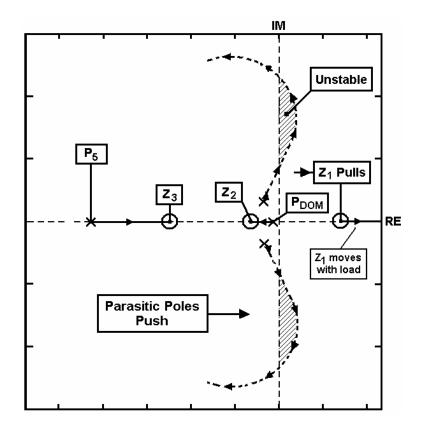

All the amplifier blocks were combined together to yield equation 29. A computer simulation determined the system poles and the AC Bode plots for various loading conditions. Fig. 23 illustrates the pole movement for the uncompensated capacitor-less LDO regulator. The AC bode diagram was simulated for both zero load current and a 50mA load current. The load dependent pass transistor gain adjusts the overall DC gain by roughly 10dB.

$$\frac{V_{out}}{V_{in}} = \left(\frac{g_{m1}R_1}{1+R_1C_1s}\right) \cdot \left(\frac{-g_{mp}R_{out}\left(1-s\frac{C_{gd}}{g_{mp}}\right)}{s(C_{out}+C_{gd})R_{out}+1}\right) \cdot \left(\frac{R_{F2}/(R_{F1}+R_{F2})}{1+s(R_{F1}//R_{F2})C_{F1}}\right)$$

(29)

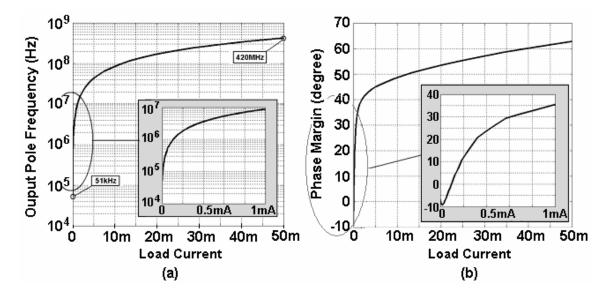

In a single pole system, the DC gain adjustment changes the gain-bandwidth product. Very small load currents push the gain-bandwidth to higher frequency, increasing the difficulty in stabilizing the LDO regulator. Secondly, the output pole movement is very large. Thus, a pole-zero cancellation scheme becomes very tedious and cumbersome. Fig. 24 displays the pass transistor output pole and phase margin verses the LDO load current. The pass transistor output pole varies over several decades from 51kHz to 420MHz. This large variation in pole movement

causes large fluctuations in phase margin. Most of the variations are absorbed between zero load current and approximately 1mA of load current.

Fig. 23. Uncompensated LDO AC response.

Fig. 24. Uncompensated LDO AC parameters verses I<sub>out</sub>: (a) output pole frequency (b) phase margin.

Fig. 25. Uncompensated AC response simulated in CADENCE.