## ANALOG-TO-DIGITAL INTERFACE DESIGN FOR WIRELESS RECEIVERS

A Dissertation

by

## BO XIA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

December 2004

Major Subject: Electrical Engineering

## ANALOG-TO-DIGITAL INTERFACE DESIGN FOR WIRELESS RECEIVERS

A Dissertation

by

## BO XIA

#### Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved as to style and content by:

Edgar Sánchez-Sinencio (Chair of Committee)

> Aydin Karsilayan (Member)

Eva Sevick-Mauraca (Member)

José Silva-Martínez (Member)

> Scott Miller (Member)

Chanan Singh (Head of Department)

December 2004

Major Subject: Electrical Engineering

#### ABSTRACT

# Analog-to-Digital Interface Design for Wireless Receivers. (December 2004) Bo Xia, B.S., Shanghai Jiao Tong University, Shanghai, China Chair of Advisory Committee: Dr. Edgar Sánchez–Sinencio

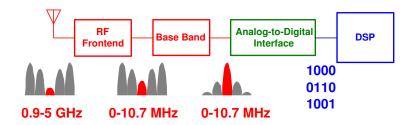

As one of the major building blocks in a wireless receiver, the Analog-to-Digital Interface (ADI) provides link and transition between the analog Radio Frequency (RF) frontend and the baseband Digital Signal Processing (DSP) module. The rapid development of the radio technologies raises new design challenges for the receiver ADI implementation. Requirements, such as power consumption optimization, multistandard compatibility, fast settling capability and wide signal bandwidth capacity, are often encountered in a low voltage ADI design environment. Previous research offers ADI design schemes that emphasize individual merit. A systematic ADI design methodology is, however, not sufficiently studied. In this work, the ADI design for two receiver systems are employed as research vehicles to provide solutions for different ADI design issues.

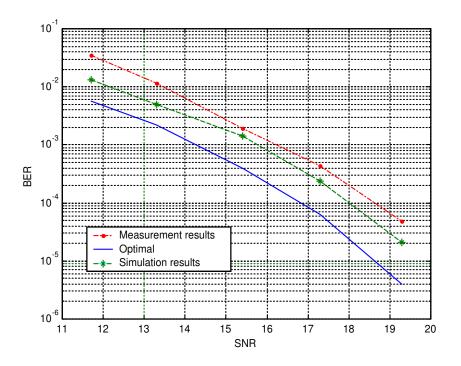

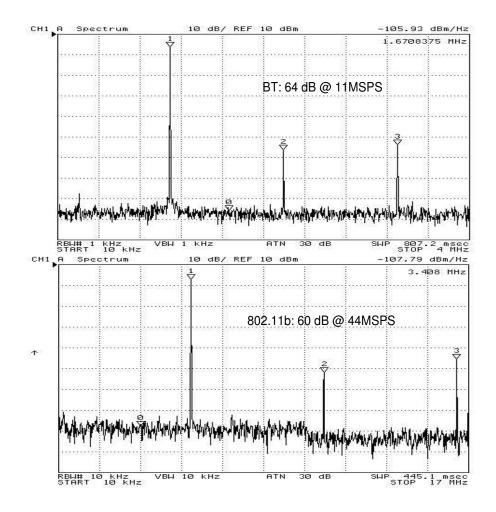

A zero-crossing demodulator ADI is designed in the  $0.35\mu m$  CMOS technology for the Bluetooth receiver to provide fast settling. Architectural level modification improves the process variation and the Local Oscillation (LO) frequency offset immunity of the demodulator. A 16.2dB Signal-to-Noise Ratio (SNR) at 0.1% Bit Error Rate (BER) is achieved with less than 9mW power dissipation in the lab measurement. For ADI in the 802.11b/Bluetooth dual-mode receiver, a configurable time-interleaved pipeline Analog-to-Digital-Converter (ADC) structure is adopted to provide the required multi-standard compatibility. An online digital calibration scheme is also proposed to compensate process variation and mismatching. The prototype chip is fabricated in the 0.25 $\mu m$  BiCMOS technology. Experimentally, an SNR of 60dB and 64dB are obtained under the 802.11b and Bluetooth receiving modes, respectively. The power consumption of the ADI is 20.2mW under the 802.11b receiving mode and 14.8mW under the Bluetooth mode.

In this dissertation, each step of the receiver ADI design procedure, from system level optimization to the transistor level implementation and lab measurement, is illustrated in detail. The observations are carefully studied to provide insight on receiver ADI design issues. The ADI design for the Ultra-Wide Band (UWB) receiver is also studied at system level. Potential ADI structure is proposed to satisfy the wide signal bandwidth and high speed requirement for future applications. To my beloved parents, brother and wife

#### ACKNOWLEDGMENTS

I will always consider my experience of the past five years in the Analog and Mixed-Signal Center as one of the most wonderful and enjoyable parts of my life. I am so deeply indebted to many people during the work leading to this dissertation. First of all, I would like to express my sincere gratitude to Dr. Edgar Sánchez-Sinencio, who has encouraged and guided me through all my research work. As a true advisor to me, he tutored me not only in the area of academic study but also in the matters in my personal life. I will benefit from his precious and generous advices lifelong.

I am grateful to Dr. José Silva-Martínez, Dr. Aydin Karsilayan and Dr. Scott Miller. They always leave their doors open for me whenever I encountered technical problems or need their suggestion on my work. I also want to thank the other committee member, Dr. Eva Sevick-Mauraca for her valuable comments on my research.

I owe my gratitude to Alexander H. Reyes, Sherif Embabi, Yong-In Park and other design engineers in Texas Instruments, Inc. Their technical advices and insights are really valuable to the success of this research.

I would say thanks to the Bluetooth and Chameleon research teams, which include Wenjun Sheng, Alberto Valdes-Garcia, Sung Tung Moon, Ari Valero-Lopez, Chunyu Xin, Ahmed Emira and Ahmed Nader Mohieldin. I am so fortunate to be able to work with such a group of extraordinary colleagues and genuine friends. The hard time and laughter we shared together are truly memorable. Their talent and persistence assured our achievements in these two projects. Especially, Alberto, whom I have been working so closely with, has contributed a very important part of the work in this dissertation. Thanks also go to the other professors and students in the Analog and Mixed Signal Center for the fruitful technical discussion, in particular, Dr. Ugur Cilingiroglu, Shouli Yan, Wei Zhuo, Siangtong Tan, Jianhong Xiao, Xiaohua Fan, Keliu Shu, Jinghua Li and Shanfeng Chen. I am also grateful to Ella Gallagher, the secretary of the center. Her contagious enthusiasm, warm sense of humor and positive attitude is a valuable treasure of the group.

The last people to mention are the most important ones in my life, my family. The accomplishment of this work would not be possible without them. My parents and brother are the great source of support and encouragement to my research and life. My beloved wife, Xin Tan, always inspires me with her love and companionship. I cannot adequately express the love and gratitude I feel for them.

## TABLE OF CONTENTS

# CHAPTER

| Ι   | INTRODUCTION                                                                                                      | 1             |

|-----|-------------------------------------------------------------------------------------------------------------------|---------------|

|     | <ul><li>A. Research Motivation and Goals</li></ul>                                                                | $\frac{1}{3}$ |

| II  | ADI DESIGN IN THE WIRELESS RECEIVER SYSTEMS                                                                       | 4             |

|     | <ul> <li>A. The Development and Trends in the Wireless Technologies</li> <li>1. Power Conscience Design</li></ul> | 4<br>4<br>5   |

|     | Requirement                                                                                                       | 6 7           |

|     | <ol> <li>Technology Scaling and SoC Requirement</li> <li>Wide Band Digital Modulation</li> </ol>                  | 7             |

|     | 6. Challenges in the ADI Design                                                                                   | 7             |

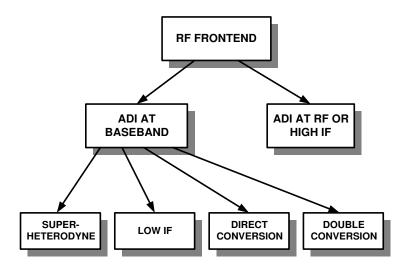

|     | B. Wireless Receiver Systems                                                                                      | 8             |

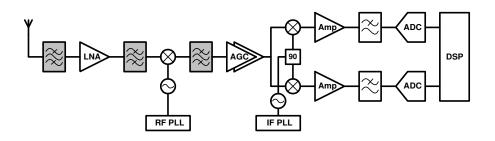

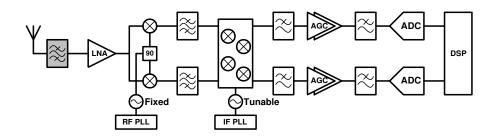

|     | 1. Wireless Receiver Architectures                                                                                | 8             |

|     | 2. ADI in a Wireless Receiver                                                                                     | 12            |

|     | C. ADI Design Approaches                                                                                          | 13<br>16      |

| III | BLUETOOTH, 802.11B/BLUETOOTH DUAL-MODE AND                                                                        |               |

|     | ULTRA-WIDE BAND RECEIVER SYSTEMS                                                                                  | 19            |

|     | A. The Wireless Standards                                                                                         | 19            |

|     | B. Design of a Wireless Receiver                                                                                  | 22            |

|     | C. System Level Considerations in the Bluetooth Receiver                                                          | 2.4           |

|     |                                                                                                                   | 24            |

|     | <ol> <li>Summary of the Bluetooth Radio Specification</li> <li>Bluetooth Data Packets</li></ol>                   | $25 \\ 27$    |

|     | 3. The Low-IF Bluetooth Receiver Architecture                                                                     | 21<br>29      |

|     | D. System Level Considerations in the 802.11b/Bluetooth                                                           | _0            |

|     | Dual-mode Receiver Design                                                                                         | 31            |

|     | 1. Summary of the 802.11b Radio Specification $\ldots$                                                            | 31            |

|     | 2. 802.11b Data Packets                                                                                           | 33            |

IV

| 3. The Direct Conversion Architecture for the                                             |            |

|-------------------------------------------------------------------------------------------|------------|

| 802.11b/Bluetooth Dual-Mode Receiver                                                      | 33<br>27   |

| E. System Level Considerations in UWB Receiver Design                                     | 37         |

| <ol> <li>Summary of the UWB Radio Specification</li></ol>                                 | 37         |

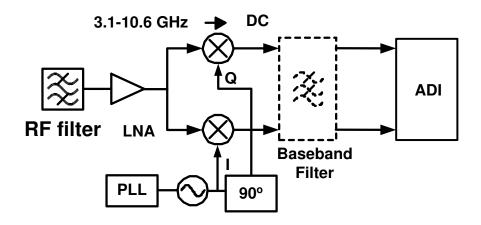

| 3. Direct Conversion UWB Receiver Architecture                                            | $40\\43$   |

| F. ADI Design in the Bluetooth and                                                        | 40         |

| 802.11b/Bluetooth Receiver                                                                | 45         |

| G. ADI Design in the UWB Receiver                                                         | 49         |

|                                                                                           |            |

| ADI DESIGN FOR THE LOW-IF BLUETOOTH RECEIVER .                                            | 55         |

| A. The Characteristics of Bluetooth GFSK Modulation                                       |            |

| and Its Detection $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 55         |

| 1. Bluetooth GFSK Signal                                                                  | 55         |

| 2. The Detection of the Bluetooth GFSK Signal                                             | 60         |

| B. ADI Design Approach for the Low-IF                                                     |            |

| Bluetooth Receiver                                                                        | 67         |

| 1. ADC+AGC Approach for the low-IF                                                        |            |

| Bluetooth Receiver                                                                        | 67         |

| 2. Single ADC Approach for the low-IF Bluetooth                                           |            |

| Receiver                                                                                  | 69         |

| 3. Hardware Demodulator of the ADI for the low-IF                                         |            |

| Bluetooth Receiver                                                                        | 70         |

| 4. The Selection of the ADI Structure for the low-IF                                      |            |

| Bluetooth Receiver                                                                        | 72         |

| C. Zero-Crossing Detector Circuit Design                                                  | 73         |

| 1. Architectural Improvement in the                                                       |            |

| Zero-Crossing Detector                                                                    | 74         |

| 2. Circuit Implementation of the Zero-Crossing Detector                                   | 76         |

| D. Demodulator Lowpass Filter                                                             | 83         |

| E. LO Frequency Offset Cancellation                                                       | 88         |

| 1. Proposed Frequency Offset Cancellation Structure                                       | 88         |

| 2. Circuit Implementation of the DC Offset Cancel-                                        | 00         |

| lation Structure                                                                          | 92<br>100  |

| F. Decision Circuit                                                                       | 100<br>101 |

| G. Bluetooth ADI Design Testing and Verification                                          | 101        |

| S a star                                                                                  | 101 $103$  |

| 2. Experimental Results                                                                   | 109        |

| V  | ADI DESIGN FOR THE DIRECT CONVERSION<br>802.11B/BLUETOOTH DUAL-MODE RECEIVER                                                        | 107          |

|----|-------------------------------------------------------------------------------------------------------------------------------------|--------------|

|    | A. The Characteristics of 802.11b Modulation Formats and                                                                            | 101          |

|    | Their Detection                                                                                                                     | 107          |

|    | 1.    802.11b    Baseband    Signal    Signal                                                                                       | 107          |

|    | 2. The Detection of the 802.11b Baseband Signal                                                                                     | 107          |

|    |                                                                                                                                     | 111          |

|    | B. ADI Design Approach for the Direct Conversion                                                                                    | 114          |

|    | 802.11b/Bluetooth Dual-Mode Receiver                                                                                                | $114 \\ 119$ |

|    |                                                                                                                                     |              |

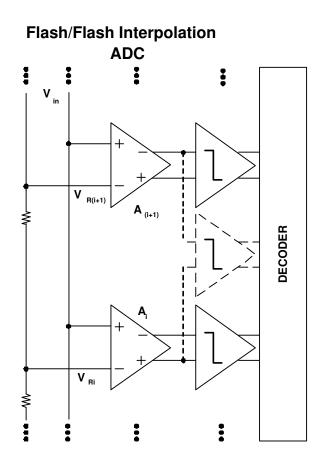

|    | 1. Flash/Flash Interpolation ADC                                                                                                    | 120<br>122   |

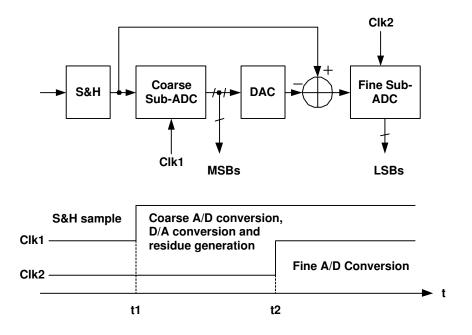

|    | 2. Two-step ADC $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$                                             |              |

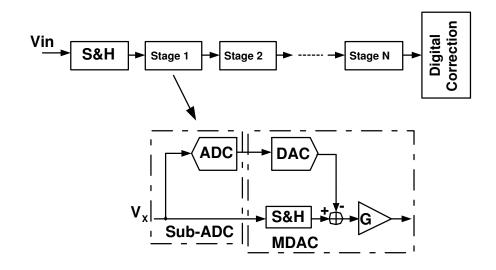

|    | 3. Pipeline ADC $\dots \dots \dots$ | 123          |

|    | 4. $\Sigma\Delta$ ADC                                                                                                               | 126          |

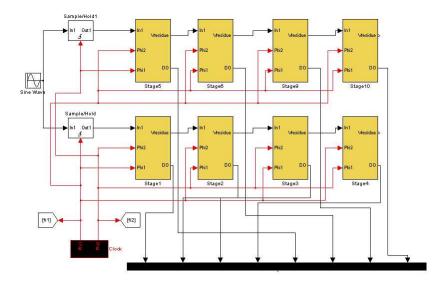

|    | D. Configurable Time-Interleaved Pipeline ADC Structure                                                                             | 129          |

|    | 1. Selection of Proper ADC Architecture for                                                                                         | 100          |

|    | 802.11b/Bluetooth Dual-Mode Receiver                                                                                                | 130          |

|    | 2. Pipeline ADC Branch in the Configurable                                                                                          |              |

|    | Time-Interleaved ADC                                                                                                                | 133          |

|    | E. Non-Idealities in the Time-Interleaved Pipeline ADC                                                                              | 136          |

|    | 1. Design Concerns in the Time-Interleaved ADC                                                                                      | 137          |

|    | 2. Design Requirement for the Frontend S&H Circuit $\therefore$                                                                     | 141          |

|    | 3. Design Challenges in the Pipeline ADC and Re-                                                                                    |              |

|    | quirements for the Sub-Stages                                                                                                       | 143          |

|    | F. System Level Modelling and Simulation of the ADC                                                                                 | 146          |

| VI | CIRCUIT IMPLEMENTATION AND VERIFICATION FOR                                                                                         |              |

|    | THE ADC DESIGN IN THE 802.11B/BLUETOOTH DUAL-                                                                                       |              |

|    | MODE RECEIVER                                                                                                                       | 149          |

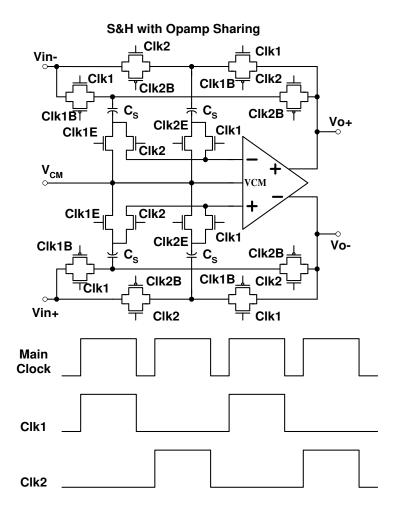

|    | A. Sample and Hold Circuit                                                                                                          | 149          |

|    | 1. Specs Derivation                                                                                                                 | 149          |

|    | 2. Circuit Implementation                                                                                                           | 154          |

|    | 3. Simulation Results                                                                                                               | 156          |

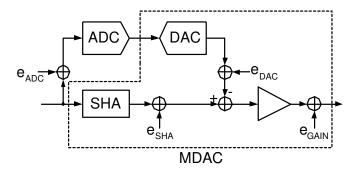

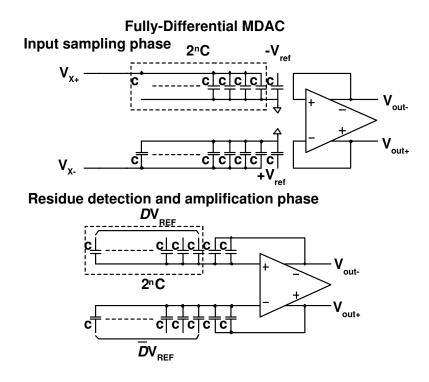

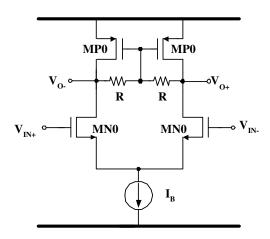

|    | B. MDACs                                                                                                                            | 157          |

|    | C. Sub-ADCs                                                                                                                         | 163          |

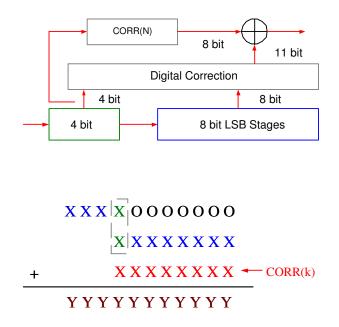

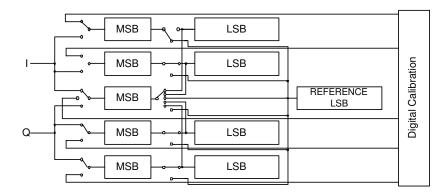

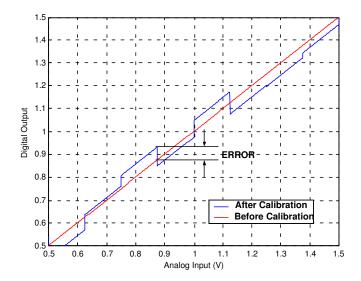

|    | D. Digital Calibration and Correction                                                                                               | 168          |

|    | 1. Digital Calibration                                                                                                              | 169          |

|    | 2. On-line Digital Calibration Scheme                                                                                               | 105          |

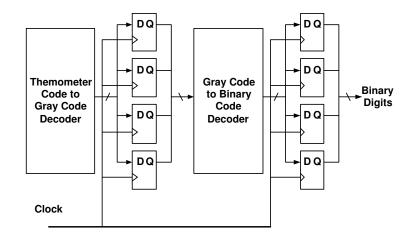

|    | 3. Thermometer Code to Binary Decoder                                                                                               | 174          |

|    | Si Incimente code to Dinary Decoder                                                                                                 |              |

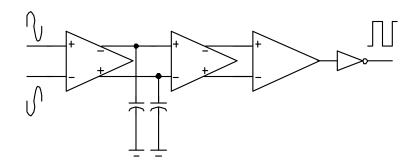

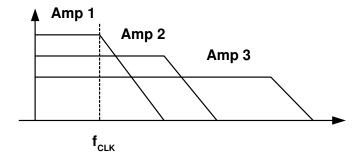

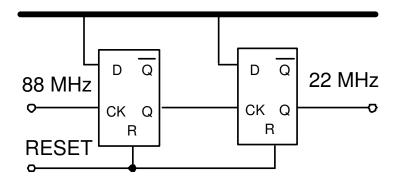

| E. Low Jitter Clock Re-Generation Circuit                  | 176 |

|------------------------------------------------------------|-----|

| F. $802.11b/Bluetooth ADI Design Testing and Verification$ | 180 |

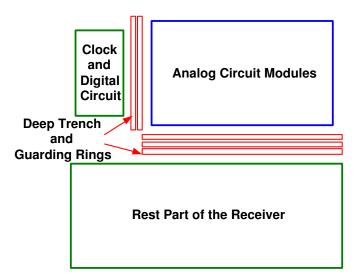

| 1. ADC Layout Design and Consideration                     | 183 |

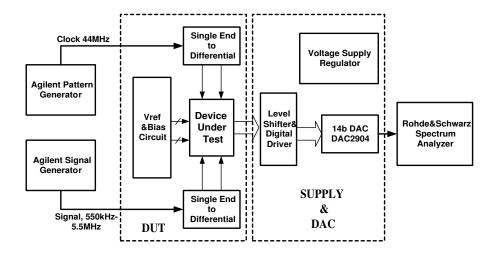

| 2. Testing Setup and Print Circuit Boards (PCBs) Design    | 185 |

| 3. Measurement Results                                     | 188 |

| VII CONCLUSION                                             | 195 |

| A. Summary                                                 | 195 |

| B. Insights on the Receiver ADI Design                     | 196 |

| REFERENCES                                                 | 200 |

| APPENDIX A                                                 | 210 |

| APPENDIX B                                                 | 221 |

| APPENDIX C                                                 | 225 |

| νιτα                                                       | 226 |

## LIST OF TABLES

| TABLE |                                                                                   | Page |

|-------|-----------------------------------------------------------------------------------|------|

| Ι     | The comparison between different receiver ADI design approaches                   | 15   |

| II    | Summary of existing wireless standards                                            | 21   |

| III   | Summary of the Bluetooth radio specification                                      | 26   |

| IV    | Major specs for the low-IF Bluetooth receiver                                     | 31   |

| V     | Summary of the 802.11b radio specification                                        | 32   |

| VI    | Major specs for the 802.11b/Bluetooth dual-mode receiver                          | 35   |

| VII   | RF specifications for the multi-band UWB                                          | 38   |

| VIII  | Baseband data modulation specifications for the multi-band UWB                    | 41   |

| IX    | 802.11b and BT ADI design requirements                                            | 45   |

| Х     | Reported ADI designs for Bluetooth and 802.11b receivers $\ . \ . \ .$ .          | 48   |

| XI    | ADC specification for a UWB receiver                                              | 51   |

| XII   | The truth table of the SR latch                                                   | 79   |

| XIII  | The specs and simulation results for the voltage subtractor OpAmp .               | 93   |

| XIV   | The transistor size and capacitor, resistor value used in the voltage substractor | 94   |

| XV    | The transistor size for the folded-cascode OpAmp                                  | 97   |

| XVI   | The specs and simulation results for the folded cascode OpAmp                     | 98   |

| XVII  | The simulation and measurement results for the Bluetooth GFSK Demodulator         | 105  |

| XVIII | DPSK encoding table                                                               | 108  |

| XIX    | DQPSK encoding table                                                         | 108 |

|--------|------------------------------------------------------------------------------|-----|

| XX     | 5.5 Mbit/s CCK encoding table                                                | 110 |

| XXI    | 11 Mbit/s CCK encoding table                                                 | 111 |

| XXII   | ADC specs                                                                    | 119 |

| XXIII  | ADC architectures and their targeting applications $\ . \ . \ . \ .$ .       | 129 |

| XXIV   | Circuit block requirements for the time-interleaved pipeline ADC $$ .        | 146 |

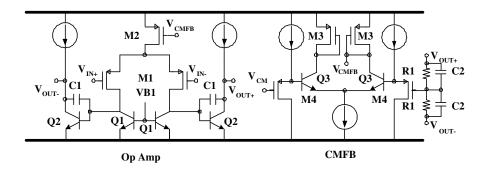

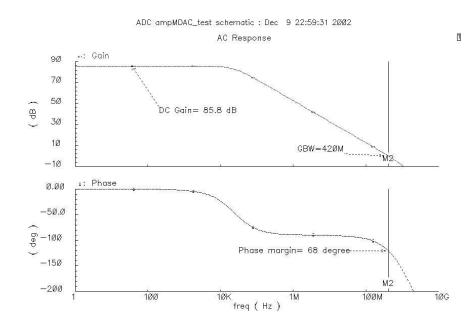

| XXV    | The circuit design parameters of the S&H OpAmp $\ \ . \ . \ . \ . \ .$       | 156 |

| XXVI   | The summary of specs and simulated results for the S&H OpAmp                 | 159 |

| XXVII  | The summary of specs for the MDAC OpAmp                                      | 162 |

| XXVIII | The summary of specs and simulated results for the sub-ADC circuit           | 169 |

| XXIX   | The circuit parameters for the clock re-generation circuit. $\ldots$ .       | 181 |

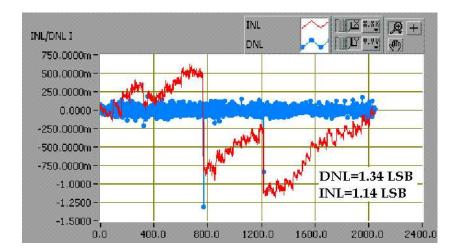

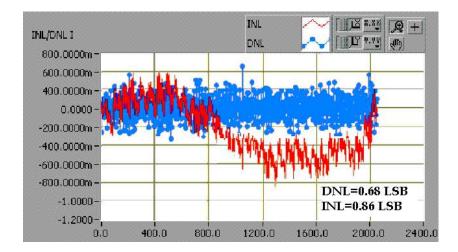

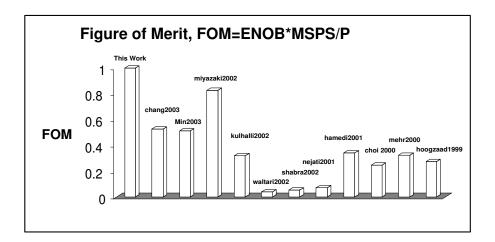

| XXX    | The summary of the experimental results of the time-interleaved pipeline ADC | 193 |

| XXXI   | The comparison of power figure of merit                                      | 194 |

## LIST OF FIGURES

| FIGUR | E                                                                                | Page |

|-------|----------------------------------------------------------------------------------|------|

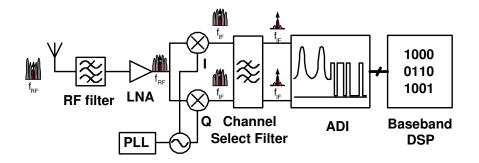

| 1     | The general model of a wireless receiver                                         | 2    |

| 2     | Wireless receiver architectures                                                  | 9    |

| 3     | Super-heterodyne receiver architecture                                           | 10   |

| 4     | Wideband IF double conversion receiver architecture                              | 10   |

| 5     | General block diagram of the direct conversion and low-IF receiver architectures | 11   |

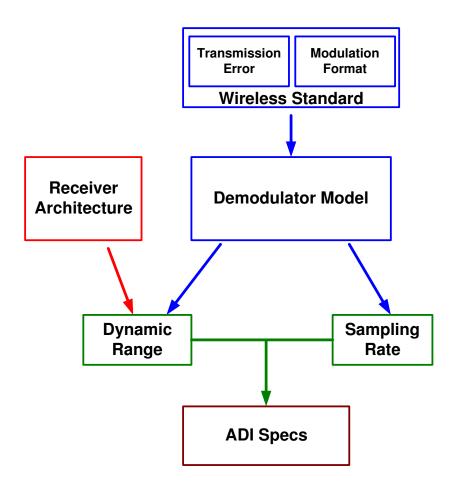

| 6     | Specs derivation for ADI design                                                  | 18   |

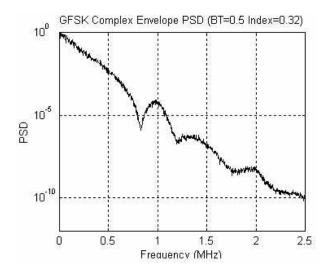

| 7     | Power spectrum of a Bluetooth baseband signal                                    | 27   |

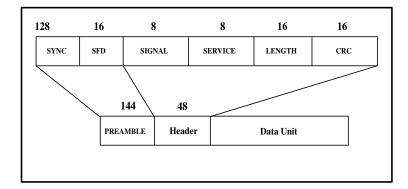

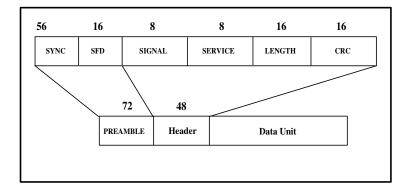

| 8     | Standard Bluetooth packet format                                                 | 28   |

| 9     | Bluetooth access code format                                                     | 29   |

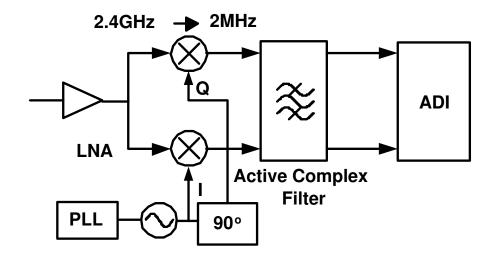

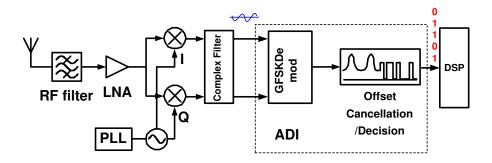

| 10    | The block diagram of a low-IF Bluetooth receiver                                 | 30   |

| 11    | The 802.11b long data packet format                                              | 33   |

| 12    | The 802.11b short data packet format                                             | 34   |

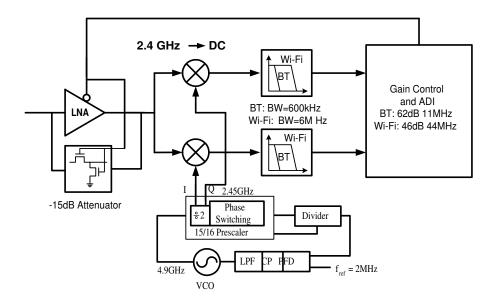

| 13    | The block diagram of a 802.11b/Bluetooth dual-mode receiver                      | 36   |

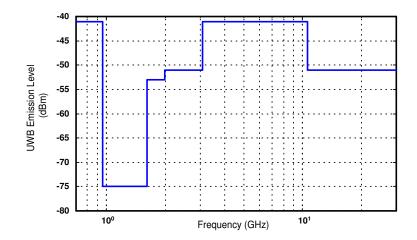

| 14    | Indoor UWB spectral mask                                                         | 38   |

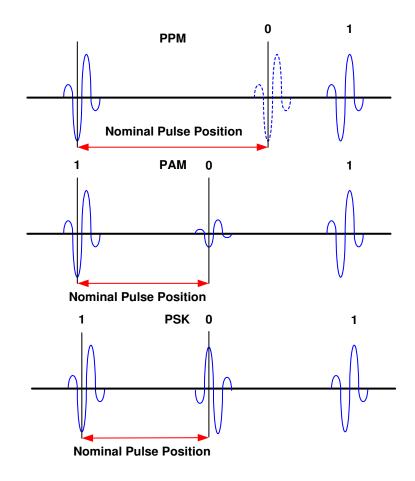

| 15    | UWB modulated signal in time domain                                              | 41   |

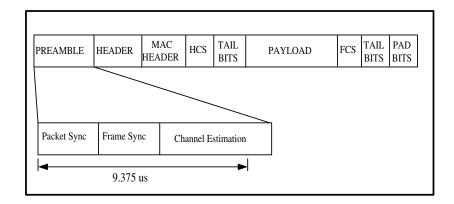

| 16    | UWB data packet format                                                           | 43   |

| 17    | The block diagram of a UWB receiver                                              | 44   |

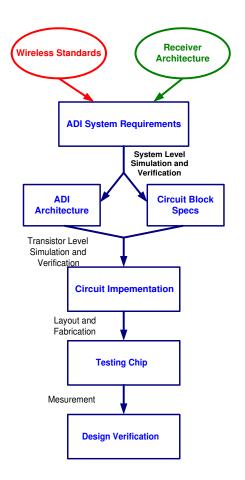

| 18    | The ADI design flow                                                              | 46   |

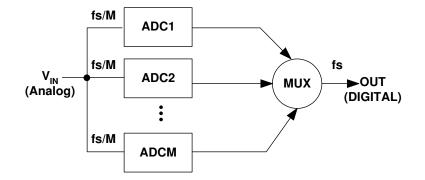

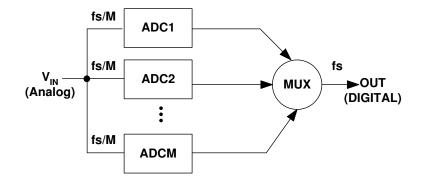

| 19 | The block diagram of a time-interleaved ADC $\hdots$                                    | 52 |

|----|-----------------------------------------------------------------------------------------|----|

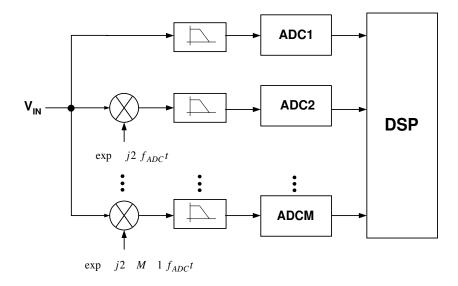

| 20 | The block diagram of a frequency channelized ADC                                        | 53 |

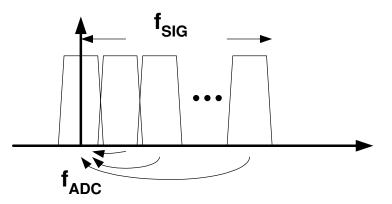

| 21 | Frequency domain explanation for the frequency channelized ADC $$ .                     | 54 |

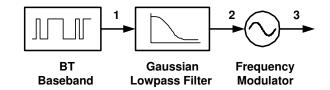

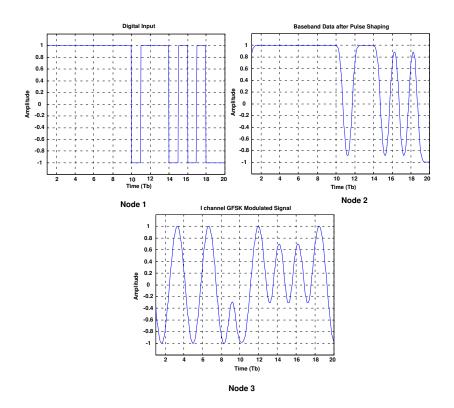

| 22 | The block diagram of a GFSK modulator                                                   | 55 |

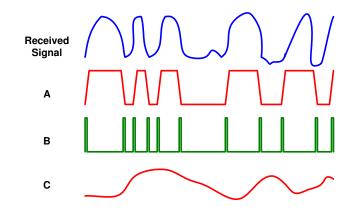

| 23 | The time domain signal waveform at internal nodes of a typical GFSK modulator           | 56 |

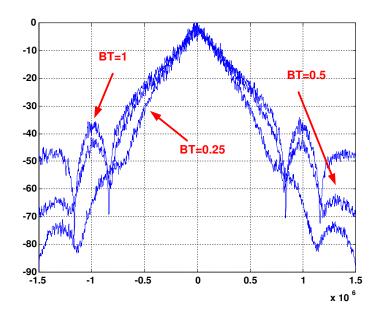

| 24 | The power spectrum density of the GFSK signal with different $BT{\rm s}$ .              | 58 |

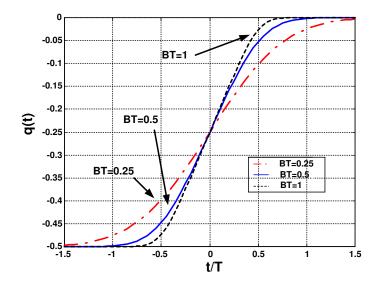

| 25 | The $q(t)$ of the GFSK signal with different $BT$ s                                     | 59 |

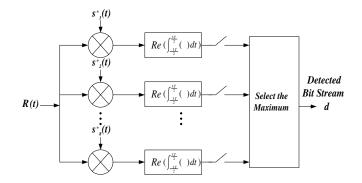

| 26 | The block diagram of an optimum non-coherent GFSK detector $\ . \ .$                    | 61 |

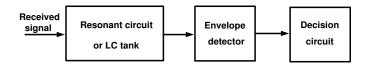

| 27 | The block diagram of a frequency discriminator                                          | 62 |

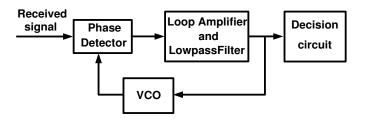

| 28 | The block diagram of a PLL based demodulator                                            | 63 |

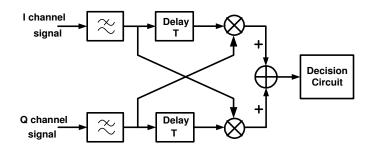

| 29 | The block diagram of a delay line discriminator                                         | 64 |

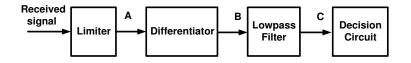

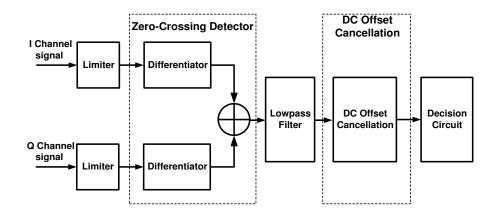

| 30 | The block diagram of a zero-crossing detector                                           | 65 |

| 31 | The transient voltage changes in the zero-crossing detector                             | 65 |

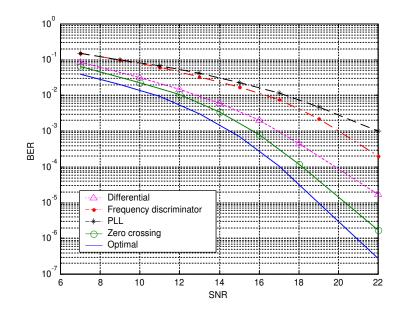

| 32 | Matlab simulated BER performances of different demodulators $\ . \ .$                   | 66 |

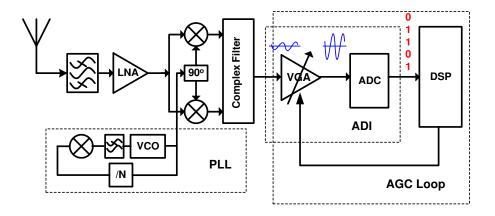

| 33 | The block diagram of a Bluetooth receiver using AGC+ADC ADI structure                   | 68 |

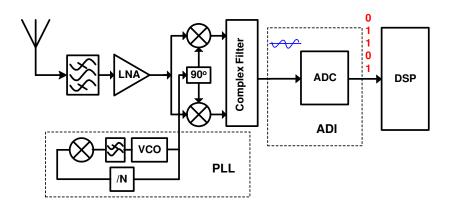

| 34 | The block diagram of a Bluetooth receiver using single ADC ADI structure                | 70 |

| 35 | The block diagram of a Bluetooth receiver using single analog demodulator ADI structure | 71 |

| 36 | The ADI architecture for the Bluetooth low-IF receiver                                  | 73 |

| 37 | The proposed zero-crossing detector for Bluetooth GFSK signal $\ . \ .$                 | 74 |

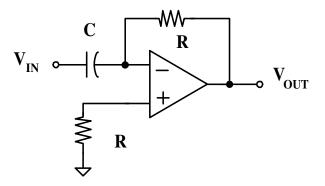

| 38 | Analog differentiator                                                                   | 74 |

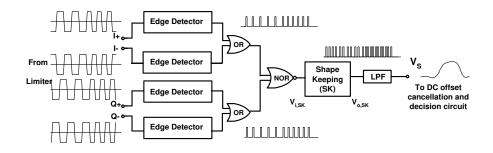

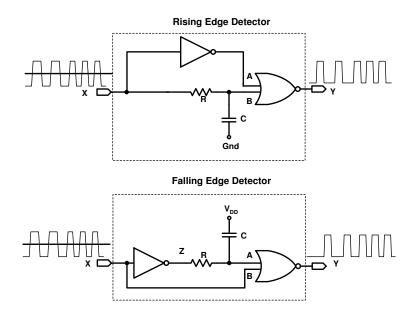

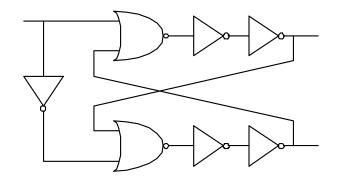

| 39 | One-shot zero-crossing detectors                                                              | 78 |

|----|-----------------------------------------------------------------------------------------------|----|

| 40 | Internal node voltage transient response of the edge detector                                 | 79 |

| 41 | Shape keeping one-shot circuit                                                                | 81 |

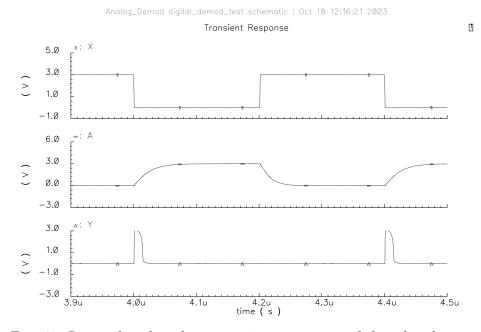

| 42 | The internal node voltage transient response of the shape keeping one-shot                    | 82 |

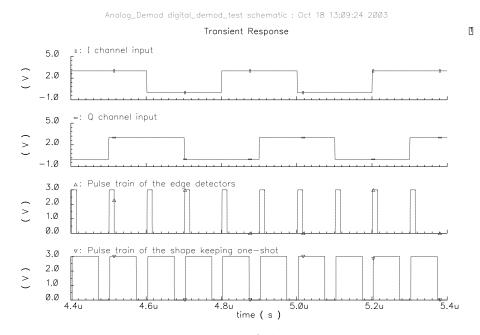

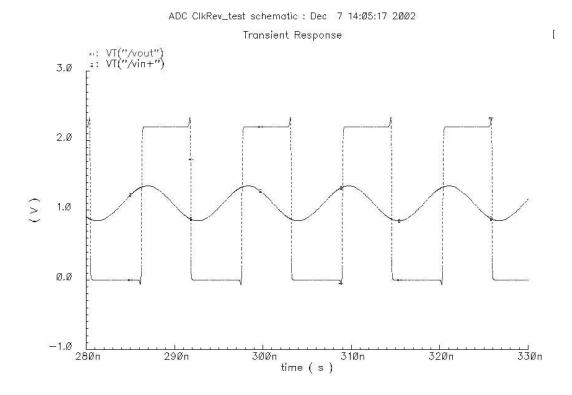

| 43 | Transient response of the zero-crossing detector                                              | 82 |

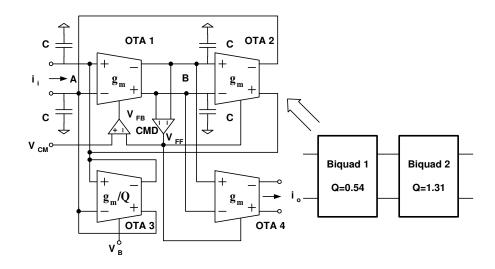

| 44 | The demodulator lowpass filter and the schematic of the biquads $~$                           | 83 |

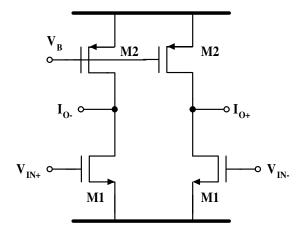

| 45 | The schematic of the pseudo differential OTA                                                  | 84 |

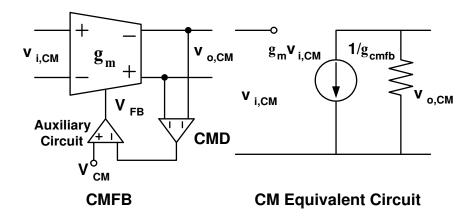

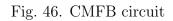

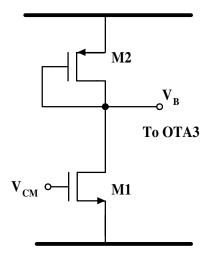

| 46 | CMFB circuit                                                                                  | 85 |

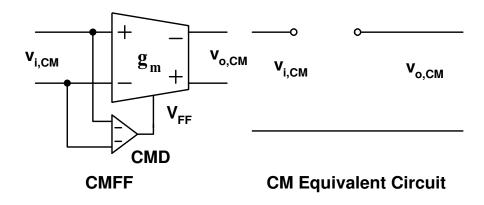

| 47 | CMFF circuit                                                                                  | 85 |

| 48 | The CMD and its auxiliary circuits                                                            | 86 |

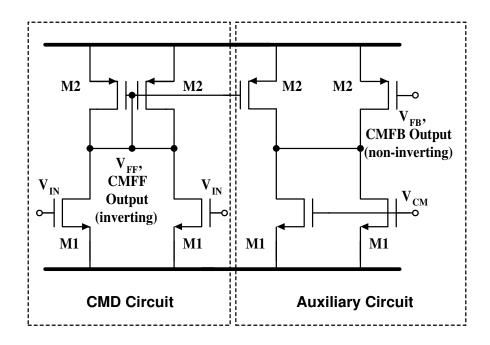

| 49 | The biasing circuit for OTA3                                                                  | 86 |

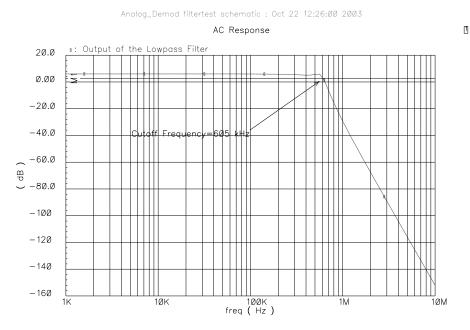

| 50 | The frequency response of the demodulator lowpass filter                                      | 87 |

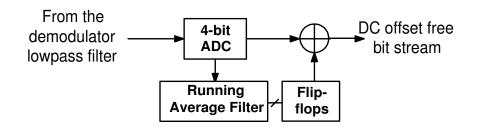

| 51 | Digital domain DC offset cancellation circuit                                                 | 89 |

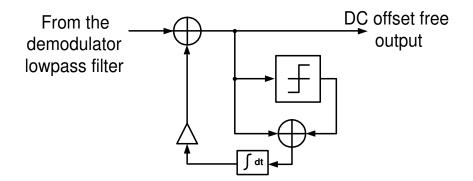

| 52 | Adaptive DC offset cancellation circuit                                                       | 90 |

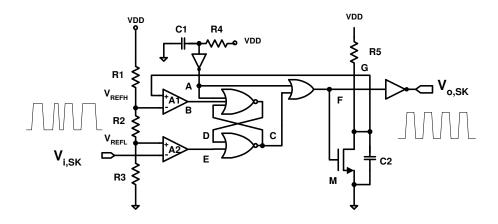

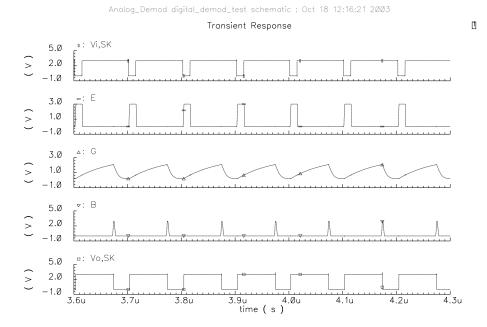

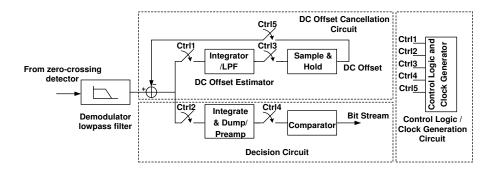

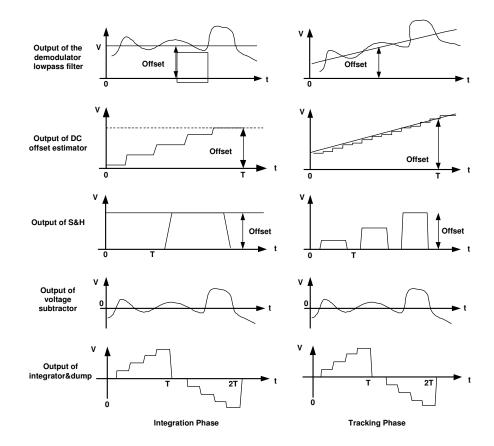

| 53 | Proposed DC offset cancellation and decision circuit $\ldots \ldots \ldots$                   | 91 |

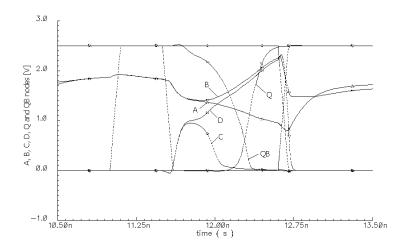

| 54 | The time domain waveform at each node of the DC offset cancel-<br>lation and decision circuit | 91 |

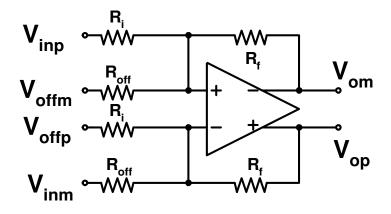

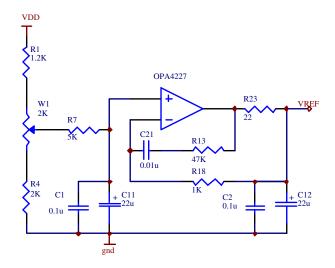

| 55 | Adaptive DC offset cancellation circuit                                                       | 93 |

| 56 | Two-stage-OpAmp used in the voltage subtractor                                                | 94 |

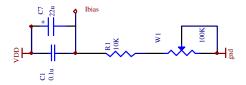

| 57 | DC offset estimator                                                                           | 96 |

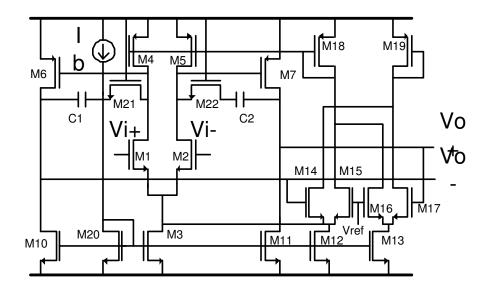

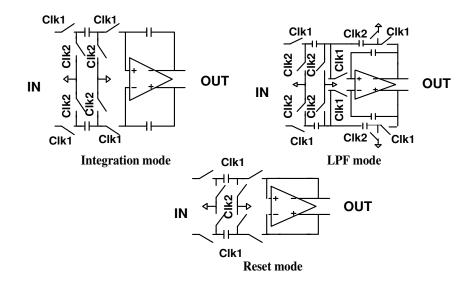

| 58 | The operating modes of the DC offset estimator                                                | 96 |

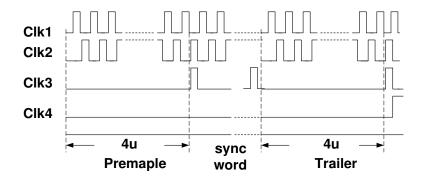

| 59 | Clock phases in the DC offset estimator                                                       | 97 |

| 60 | The folded-cascode OpAmp used in the DC offset estimator $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 98  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

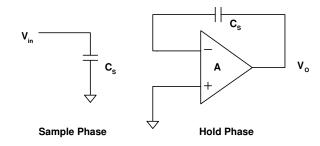

| 61 | The sample and hold circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 |

| 62 | The decision circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101 |

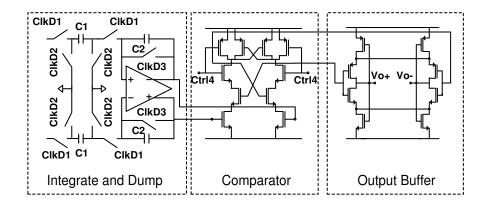

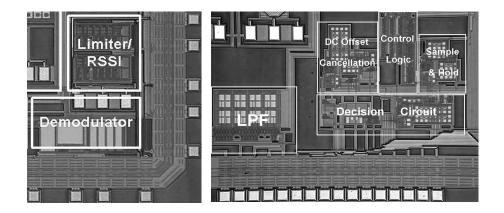

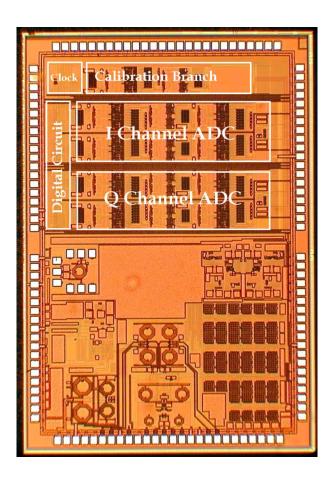

| 63 | The die microphotograph of GFSK demodulator and LO frequency offset cancellation circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 102 |

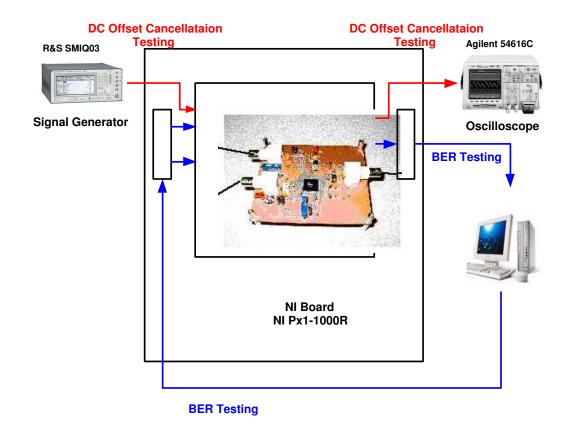

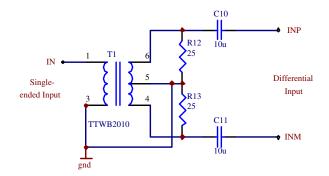

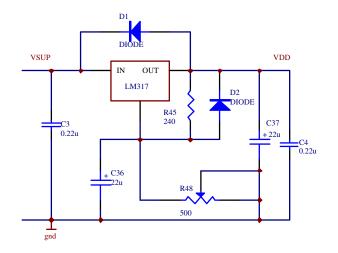

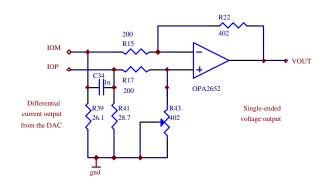

| 64 | Testing setup for the proposed GFSK demodulator and its DC offset cancellation circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102 |

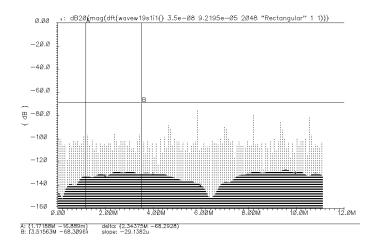

| 65 | The measured BER performance of the zero-crossing demodulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 104 |

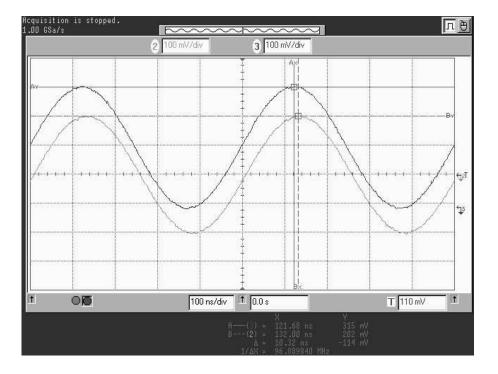

| 66 | The performance testing for the DC offset cancellation circuit $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 105 |

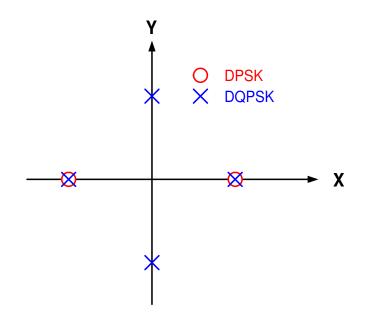

| 67 | Phase of the DPSK and DQPSK modulated signal $\ . \ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 109 |

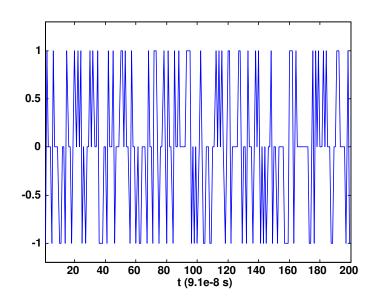

| 68 | The pulse sequence of 11 Mbits CCK modulated signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112 |

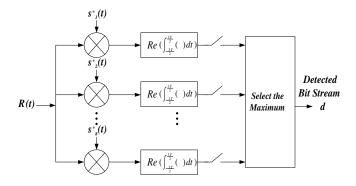

| 69 | The general block diagram of an optimum non-coherent detectors for the 802.11b baseband signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 113 |

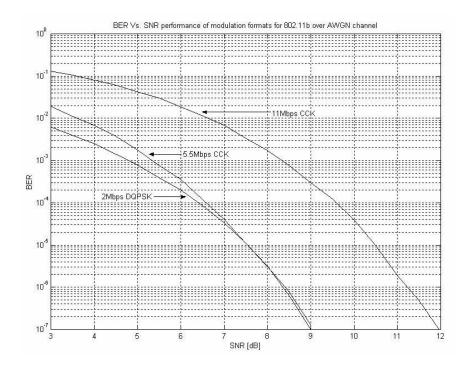

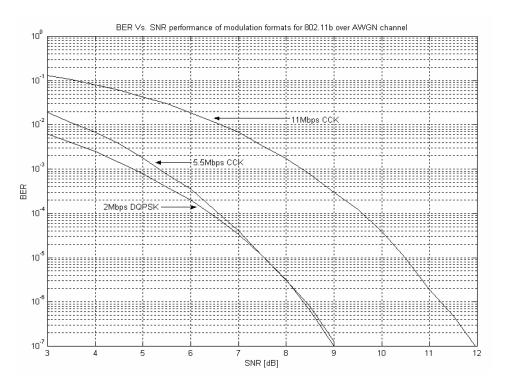

| 70 | SystemView simulated BER performances of optimum non-coherent demodulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 113 |

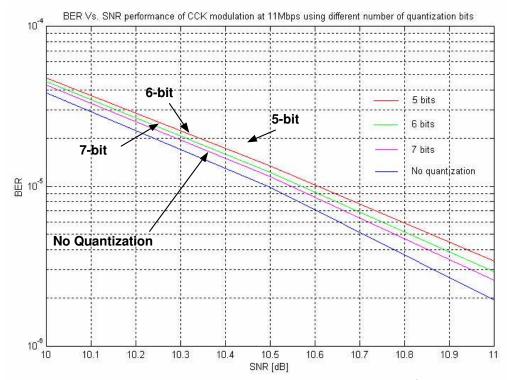

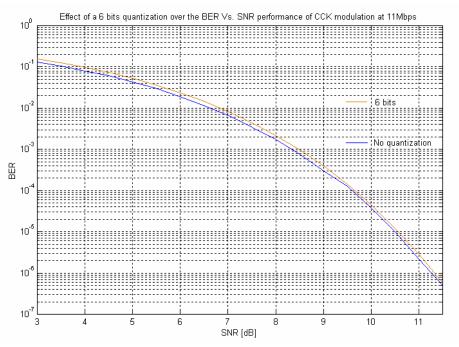

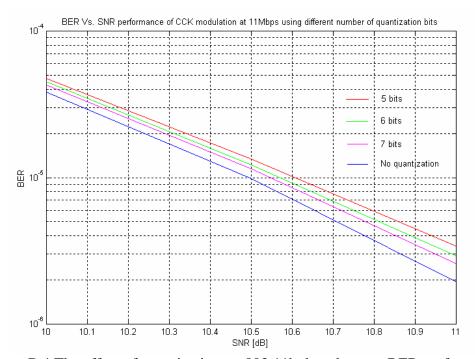

| 71 | The effect of ADC quantization noise on the 802.11b 11Mbit/s CCK signal demodulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 116 |

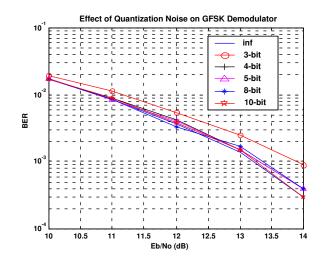

| 72 | The effect of ADC quantization noise on the Bluetooth GFSK signal demodulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 117 |

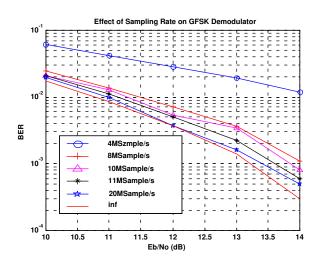

| 73 | The effect of sampling rate on the Bluetooth signal demodulation $\ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 117 |

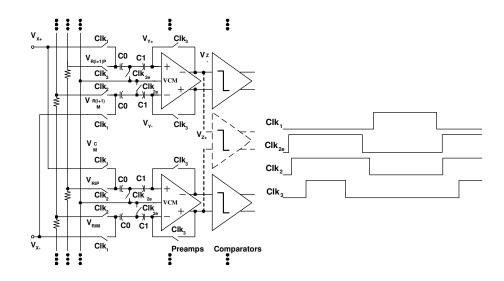

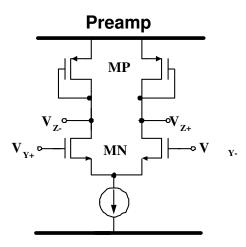

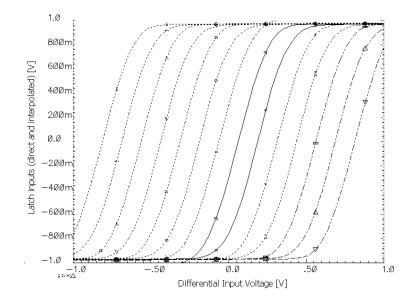

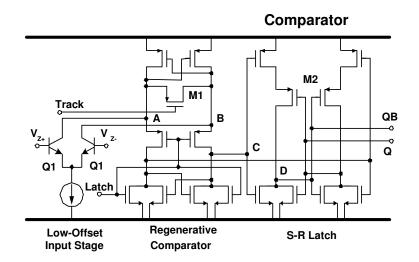

| 74 | The schematic of a flash/flash interpolation ADC $\ . \ . \ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 121 |

| 75 | Block diagram of a two-stage ADC ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 123 |

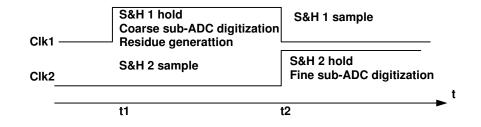

| 76 | Clock diagram of a two-step pipelined ADC $\hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots \hfill \hfill \ldots \hfill \hfill \ldots \hfill \hfill \ldots \hfill \hfill \hfill \hfill \ldots \hfill \$ | 124 |

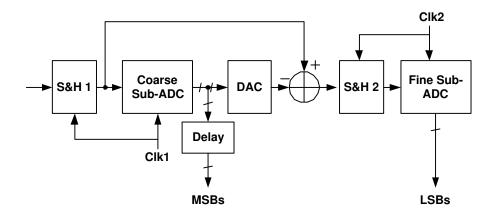

| 77 | Schematic of a two-step pipelined ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125 |

| FIGUI | RE |

|-------|----|

|-------|----|

| 78 | Schematic of a multi-stage pipelined ADC                                                                            | 126 |

|----|---------------------------------------------------------------------------------------------------------------------|-----|

| 79 | Block diagram of a $\Sigma\Delta$ ADC $\ldots$                                                                      | 127 |

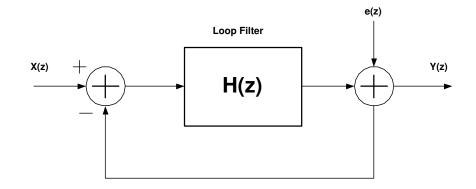

| 80 | Linear model of a $\Sigma\Delta$ modulator                                                                          | 128 |

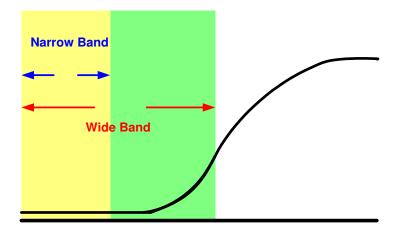

| 81 | Noise transfer function of a $\Sigma\Delta$ modulator                                                               | 131 |

| 82 | The block diagram of a time-interleaved ADC                                                                         | 132 |

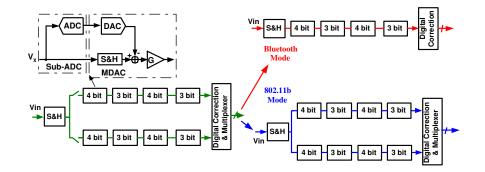

| 83 | Configurable time-interleaved pipeline ADC for 802.11b/ Blue-<br>tooth dual-mode receiver                           | 133 |

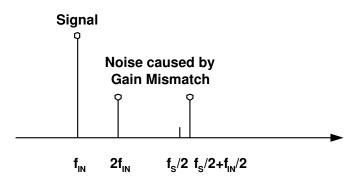

| 84 | Spectrum of a 2-branch time-interleaved ADC output with a sinusoidal input and gain mismatch between the branches   | 139 |

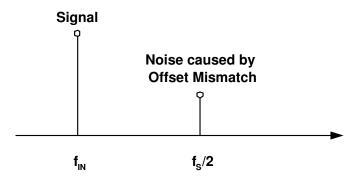

| 85 | Spectrum of a 2-branch time-interleaved ADC output with a sinusoidal input and offset mismatch between the branches | 140 |

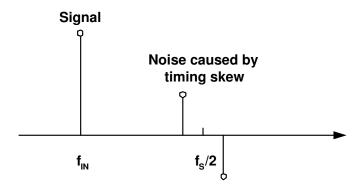

| 86 | Spectrum of a 2-branch time-interleaved ADC output with a sinusoidal input and timing skew between the branches     | 140 |

| 87 | Error model of a stage in the pipeline ADC                                                                          | 143 |

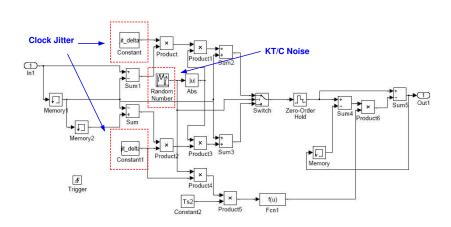

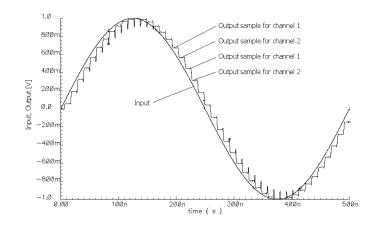

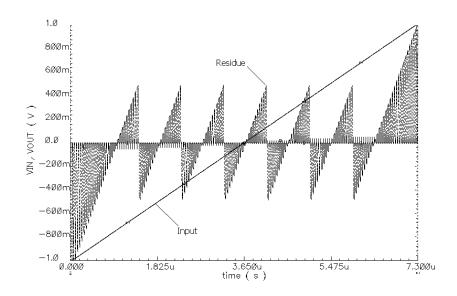

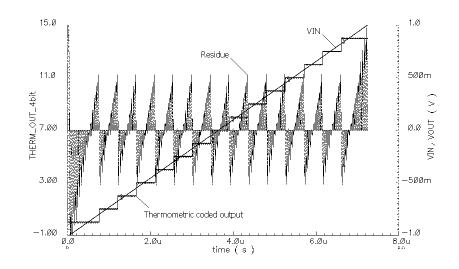

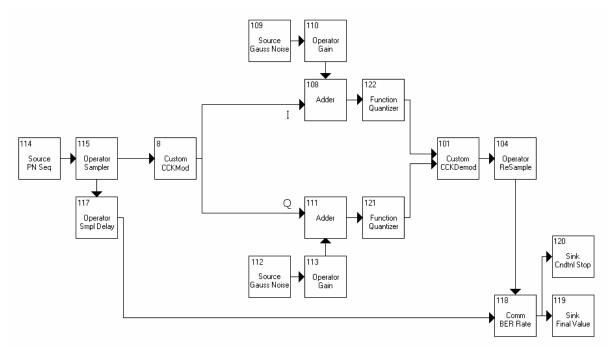

| 88 | Simulink model for pipeline ADC system level verification $\ldots \ldots$                                           | 147 |

| 89 | Simulink model for the S&H circuit                                                                                  | 148 |

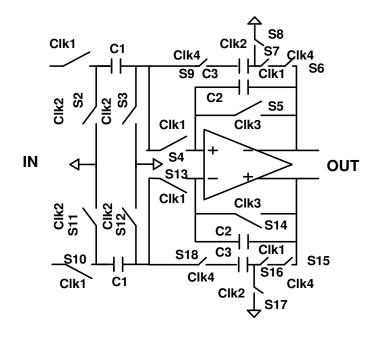

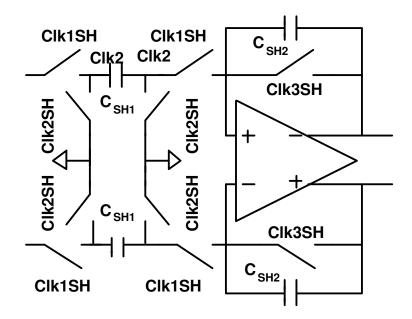

| 90 | The schematic and clock arrangement for the S&H circuit $\ .$                                                       | 150 |

| 91 | The schematic of the S&H circuit in different phase                                                                 | 151 |

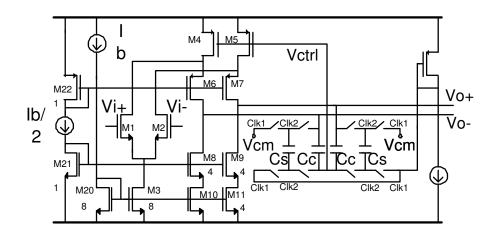

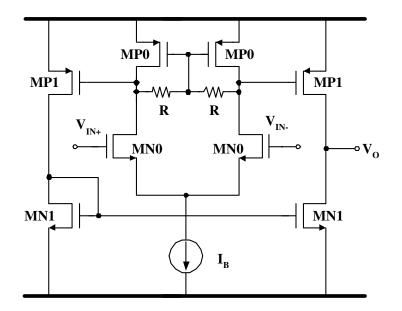

| 92 | The schematic of the OpAmp used in S&H and MDACs $\ . \ . \ .$ .                                                    | 154 |