# MACHINE LEARNING TECHNIQUES FOR PERFORMANCE PREDICTION AND DIAGNOSIS OF VLSI DESIGNS

# A Dissertation

by

# ERICK MAURICIO CARVAJAL BARBOZA

Submitted to the Graduate and Professional School of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Chair of Committee, Jiang Hu Co-Chair of Committee, Paul Gratz

Committee Members, Ulisses Braga Neto

Duncan Walker

Head of Department, Miroslav Begovic

December 2021

Major Subject: Computer Engineering

Copyright 2021 Erick Mauricio Carvajal Barboza

#### **ABSTRACT**

As the cost of scaling-down the manufacturing process of integrated circuits grows larger and its performance gains become smaller, designs must grow in complexity in order to achieve expected performance improvements. As this complexity grows, the development of automation tools for design, validation, and debug is critical. The number of machine learning-based techniques aiming to improve available tools has grown rapidly in recent years, as machine learning has proven an extraordinary capability of extracting knowledge from data and handling complicated non-linear behaviors, which makes it the best approach to mimic a human manual process among mathematical or algorithmic options. The work presented in this dissertation aims to evaluate the application of machine learning techniques in two different areas of the integrated circuit design process: pre-routing timing prediction and performance debugging of microprocessor cores.

The strategy proposed for pre-route timing prediction is based on machine learning models that predict the post-routing timing using only placed, but un-routed circuit databases. This strategy prevents over-design due to pessimistic timing estimations, as well as it saves time by reducing the need of multiple design iterations caused by the use of inaccurate timing estimations to guide circuit optimizations such as gate resizing, logic restructuring, or threshold voltage assignment leading to design violations once routing is executed. The obtained results show that our models achieve a prediction quality on-par with a sign-off static timing analysis commercial tool, with a  $3\times$  speedup.

For the performance debug of microprocessor cores task, we focus on bugs that affect the generation-by-generation performance improvement in new designs. This task is very challenging due to the lack of an accurate golden performance model, unlike its functional counterpart. In addition, there is a limited visibility of the performance on intermediate steps of the design, and overall, the debugging infrastructure is lacking, which makes this problem even more challenging. Currently this process is executed on a highly manual manner, which requires large amounts of time to fully characterize a bug. Therefore, automated techniques for performance debugging are

essential to keep-up the performance gains obtained by new microarchitectural designs. In this dissertation, we focus on detecting the presence of a performance bug and localizing the microarchitectural unit on which the bug might be, more detailed debugging is left for future work. Our proposed techniques achieved up to a 91.5% of bug detection, and up to a 98% top-3 (out of 16 possible) bug localization accuracy on bugs with average IPC impact > 1%.

# DEDICATION

To Tía Maru and Abuelo Victor, up in heaven.

To my mother, my father, and especially to my wife.

#### **ACKNOWLEDGMENTS**

I would like to thank Dr. Jiang Hu, not only for his academic advice and support, but also for believing in me during trying times and for motivating me to push forward, without him this thesis would have never happened. I would also like to thank Dr. Paul Gratz, whose guidance to navigate the world of Computer Architecture has been essential.

I am also very thankful to Dr. Mahesh Ketkar and Dr. Michael Kishinevsky from Intel Labs. Not only were they amazing mentors throughout my research at Texas A&M, but they also provided me with the amazing opportunity to intern with them. Even with all the complications due to COVID-19, they were always eager to help.

I would also like to thank my committee members, Dr Braga Neto and Dr Walker for their helpful suggestions and comments.

Finally, I would also like to thank the University of Costa Rica for giving me the opportunity to do my graduate studies abroad, and specially Dr. Lochi Yu, for guiding me towards my academic path.

#### CONTRIBUTORS AND FUNDING SOURCES

#### **Contributors**

This work was supported by a dissertation committee consisting of Professor Jiang Hu and Professor Paul Gratz of the Department of Electrical and Computer Engineering, who served as co-advisors, and Professor Ulisses Braga Neto of the Department of Electrical and Computer Engineering and Professor Duncan Walker of the Department of Computer Science and Engineering.

The work in Chapter 2 was advised by Dr. Jiang Hu of Texas A&M University. Some test cases for this chapter were prepared by Nischal Shukla of Texas A&M University. This work was published in [1].

The work in Chapter 3 was advised by Dr. Jiang Hu, and Dr. Paul Gratz of Texas A&M University, and Dr. Mahesh Ketkar, and Dr. Michael Kishinevsky of Intel Labs. The work on performance bug detection shown in that chapter was published in [2].

# **Funding Sources**

Graduate study was partially supported by Semiconductor Research Corporation (SRC) Tasks 2810.021 and 2810.022 through UT Dallas' Texas Analog Center of Excellence (TxACE), Semiconductor Research Corporation (SRC) Task 2902.001, and the University of Costa Rica, "Graduate Studies Abroad for UCR Faculty" Scholarship.

# NOMENCLATURE

AMAT Average Memory Access Time

AUC Area Under the Curve

CBC Counter-Based Classification

CNN Convolutional Neural Network

CPI Cycles Per Instruction

CTS Clock Tree Synthesis

FF Flip-Flops

FNR False-Negative Rate

FPR False-Positive Rate

GAN Generative Adversarial Network

GBT Gradient Boosted Trees

HDL Harfware Description Language

IC Integrated Circuits

IPC Instructions committed Per Cycle

ITC International Test Conference

LSTM Long Short-Term Memory

MAE Mean Absolute Error

ML Machine Learning

MLP Multi-Layer Perceptron

MSE Mean Squared Error

P2BC Performance Prediction error-Based Classification

PERT Program Evaluation and Review Technique

RC Resistor-Capacitor

RF Random Forest

RMAE Relative Mean Absolute Error

RMSE Relative Mean Squared Error

ROC Receiver Operating Characteristic

RRMSE Relative Root Mean Squared Error

STA Static Timing Analysis

SVM Support Vector Machine

TNR True-Negative Rage

TNS Total Negative Slack

TPR True-Positive Rate

VHDL Very High-Speed integrated circuit Hardware Description

Language

VLSI Very-Large Scale Integration

# TABLE OF CONTENTS

|     |               | Pag                                                | ge          |

|-----|---------------|----------------------------------------------------|-------------|

| ΑE  | BSTR.         | ACT                                                | ii          |

| DE  | EDIC <i>i</i> | ATION                                              | iv          |

|     | NTT 10        |                                                    |             |

| AC  | CKNO          | OWLEDGMENTS                                        | V           |

| CC  | ONTR          | IBUTORS AND FUNDING SOURCES                        | vi          |

| NO  | OMEN          | NCLATURE v                                         | / <b>ii</b> |

| TA  | BLE           | OF CONTENTS                                        | ix          |

|     |               |                                                    |             |

| LI  | ST OF         | F FIGURES x                                        | ίi          |

| LIS | ST OI         | F TABLESx                                          | iv          |

| 1.  | INTI          | RODUCTION AND MOTIVATION                           | 1           |

|     | 1.1           | Pre-routing timing prediction                      | 1           |

|     | 1.2           | Performance debugging of microprocessor cores      |             |

|     |               |                                                    | 4           |

|     |               |                                                    | 4           |

|     | 1.3           | Thesis statement                                   | 4           |

|     | 1.4           | Summary of contributions                           | 4           |

| 2.  | PRE           | -ROUTING TIMING PREDICTION                         | 6           |

|     | 2.1           | Background                                         | 6           |

|     |               | -                                                  |             |

|     |               | 2.1.2 Timing models                                |             |

|     | 2.2           | Prior work                                         |             |

|     | 2.3           | Machine learning for pre-routing timing prediction | 9           |

|     |               | 2.3.1 Problem formulation                          | 9           |

|     |               | 2.3.2 Methodology overview                         | 11          |

|     |               |                                                    | 12          |

|     |               |                                                    | 13          |

|     |               |                                                    | 15          |

|     | 2.4           | 1                                                  | 16          |

|     | 2.5           |                                                    | 17          |

|     |               | 2.5.1 Net slew and delay estimation quality        | 17          |

|    |     | 2.5.2   | Impact of the customized loss function on the neural network prediction      |          |

|----|-----|---------|------------------------------------------------------------------------------|----------|

|    |     |         | accuracy                                                                     | 19       |

|    |     | 2.5.3   | Path slack prediction accuracy                                               |          |

|    |     | 2.5.4   | Critical path classification accuracy                                        | 23       |

|    |     | 2.5.5   | Implementation quality ranking                                               | 25       |

|    | 2.6 | Conclu  | usion                                                                        | 26       |

| 3. | PER | FORM    | ANCE DEBUGGING OF MICROPROCESSOR CORES                                       | 27       |

|    | 3.1 | Backg   | round                                                                        | 27       |

|    | 3.2 | Prior v | vork                                                                         | 30       |

|    |     | 3.2.1   | Performance modelling                                                        | 31       |

|    |     | 3.2.2   | Performance counters for power prediction                                    | 31       |

|    |     | 3.2.3   | Microprocessor performance bug detection                                     | 32       |

|    |     | 3.2.4   | Microprocessor performance bug localization                                  | 33       |

|    |     | 3.2.5   | Performance bugs in other domains                                            | 33       |

|    | 3.3 | Machi   | ne learning for performance debugging                                        | 34       |

|    |     | 3.3.1   | Performance probe design                                                     | 35       |

|    |     |         | 3.3.1.1 Microbenchmark extraction                                            | 35       |

|    |     |         | 3.3.1.2 Performance counters as ML features                                  | 37       |

|    | 3.4 | Mach    | ine learning for performance bug detection                                   | 38       |

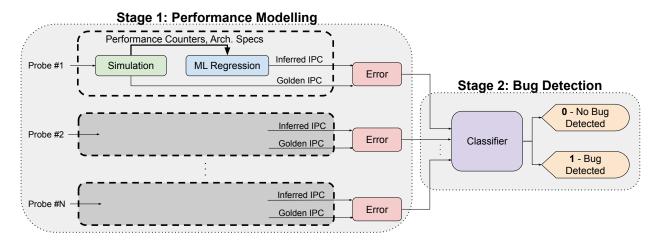

|    |     | 3.4.1   | Problem formulation for the bug detection task                               |          |

|    |     | 3.4.2   | Methodology overview for the bug detection task                              | 39       |

|    |     | 3.4.3   | Baseline single-stage naïve bug detection approach                           | 39       |

|    |     | 3.4.4   | Two-stage bug detection approach                                             | 40       |

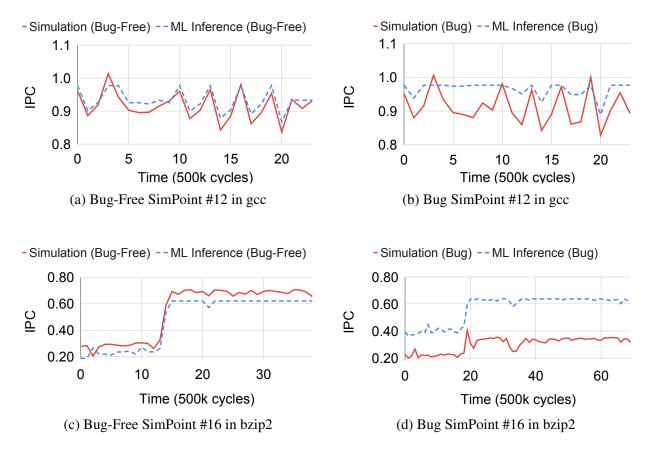

|    |     |         | 3.4.4.1 Stage 1: Performance inference                                       | 41       |

|    |     |         | 3.4.4.2 Stage 2: Bug detection classifier                                    | 43       |

|    |     | 3.4.5   | Experimental setup for bug detection                                         | 48       |

|    |     |         | 3.4.5.1 Probe setup                                                          | 48       |

|    |     |         | 3.4.5.2 Simulated architectures                                              |          |

|    |     |         | 3.4.5.3 Implemented bugs                                                     | 58       |

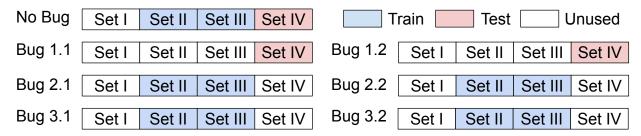

|    |     |         | 3.4.5.4 Train and test data organization for the bug detection task          | 60       |

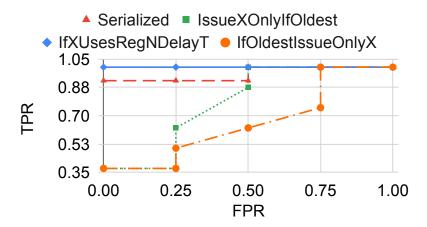

|    |     | 3.4.6   | Bug detection results                                                        | 61       |

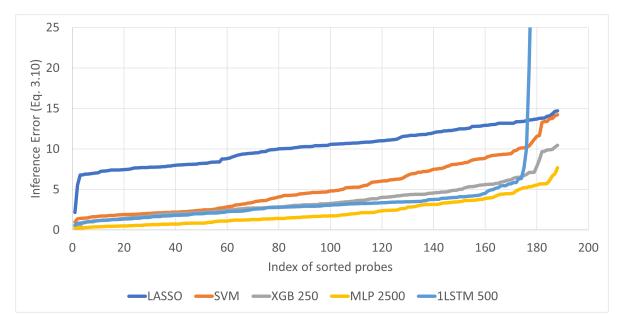

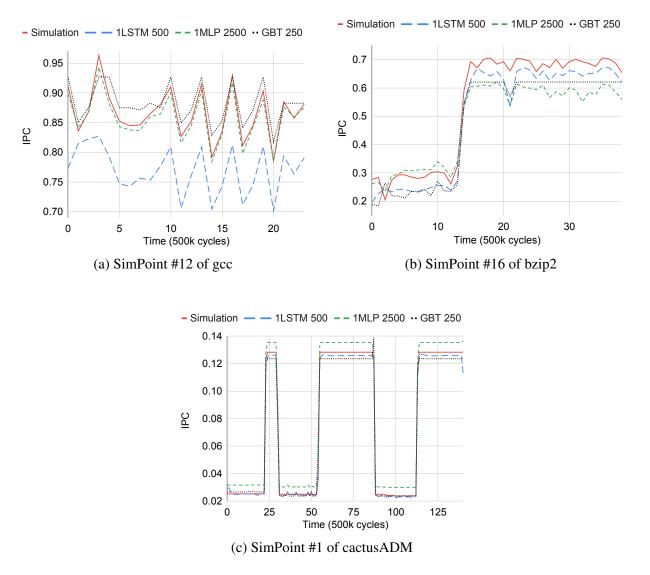

|    |     |         | 3.4.6.1 IPC estimation                                                       | 62       |

|    |     |         | 3.4.6.2 Bug detection accuracy                                               | 67       |

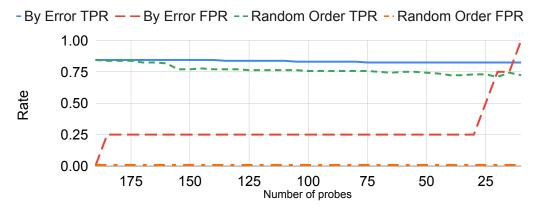

|    |     |         | 3.4.6.3 Impact of the number of probes on bug detection                      | 70       |

|    |     |         | 3.4.6.4 Impact of the counter selection mechanism on bug detection           | 71       |

|    |     |         | 3.4.6.5 Impact of the time step size on bug detection                        | 72       |

|    |     |         |                                                                              | 73       |

|    |     |         | 3.4.6.7 Impact of the usage of microarchitecture design parameter as fea-    | 71       |

|    |     |         | $\epsilon$                                                                   | 74       |

|    |     |         | 3.4.6.8 Impact of the number of training microarchitectures on bug detection | 75       |

|    | 2 5 | Mook    |                                                                              | 75<br>76 |

|    | 3.5 |         | e i                                                                          | 76<br>76 |

|    |     | 7. ). I | ETODICHI TOLIHUTAHOH TOLIHIC DUQ TOCAHZAHOH TASK                             | 70       |

|    | 3.5.2     | Methodo    | ology overview for the bug localization task                       | 77  |

|----|-----------|------------|--------------------------------------------------------------------|-----|

|    | 3.5.3     |            | ance bug localization via Counter-Based Classification (CBC)       |     |

|    | 3.5.4     | Perform    | ance bug localization via Performance Prediction error-Based Clas- |     |

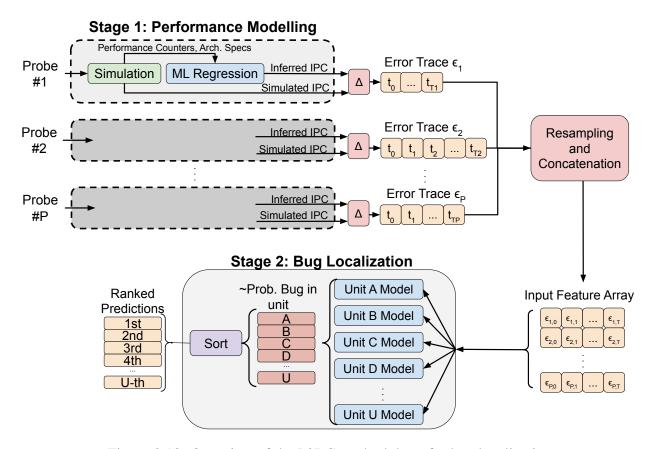

|    |           | sification | n (P2BC)                                                           | 80  |

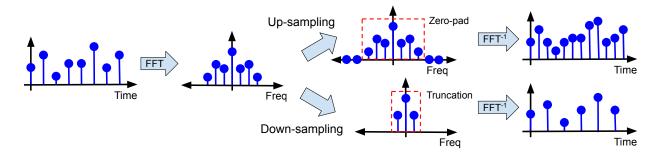

|    |           | 3.5.4.1    | Stage 1: Performance modeling                                      | 81  |

|    |           | 3.5.4.2    | Stage 2: Error-based bug localization                              | 83  |

|    | 3.5.5     | Trade-of   | ffs between CBC and P2BC                                           | 83  |

|    | 3.5.6     | Ensemb     | le of methods                                                      | 84  |

|    | 3.5.7     | Experim    | nental setup for bug localization                                  | 85  |

|    |           | 3.5.7.1    | Probe setup                                                        |     |

|    |           | 3.5.7.2    | Simulated architectures                                            | 85  |

|    |           | 3.5.7.3    | Implemented bugs                                                   | 96  |

|    |           | 3.5.7.4    | Training and test data organization for the bug localization task. | 99  |

|    | 3.5.8     | Bug loca   | alization results                                                  | 100 |

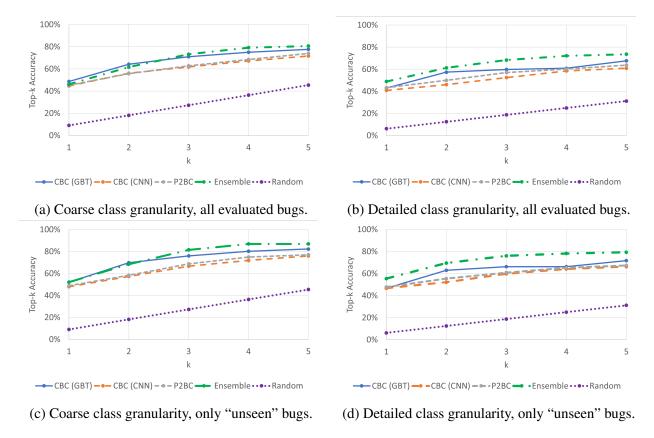

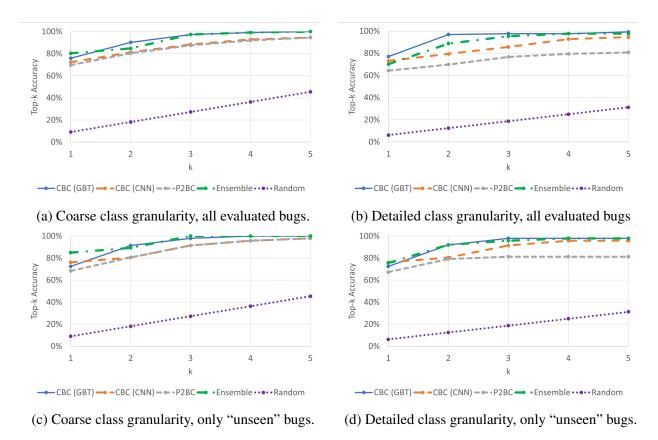

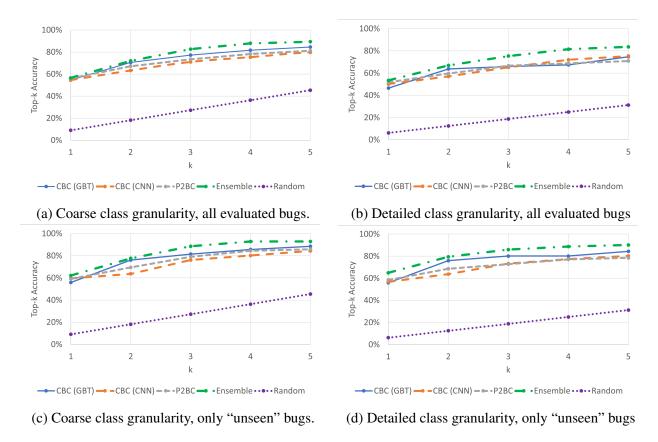

|    |           | 3.5.8.1    | Bug localization overall accuracy                                  | 101 |

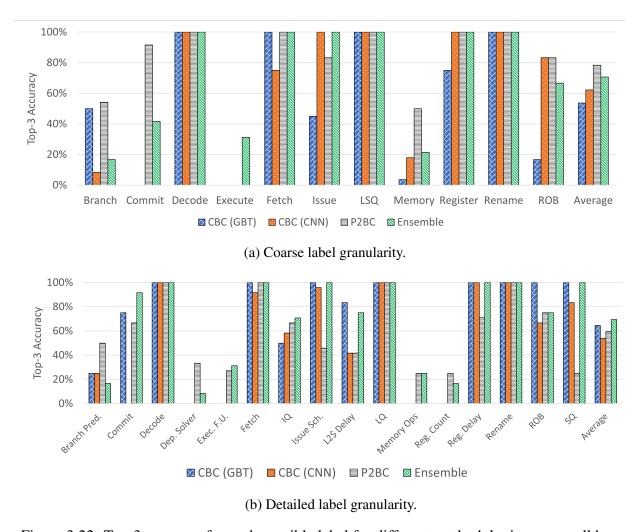

|    |           | 3.5.8.2    | Bug localization accuracy per microarchitectural unit              | 103 |

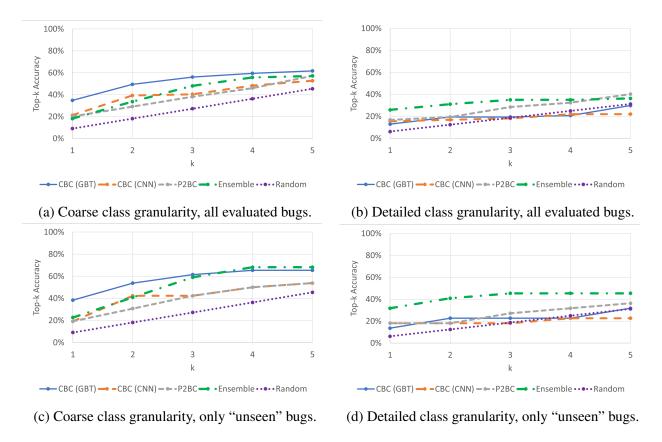

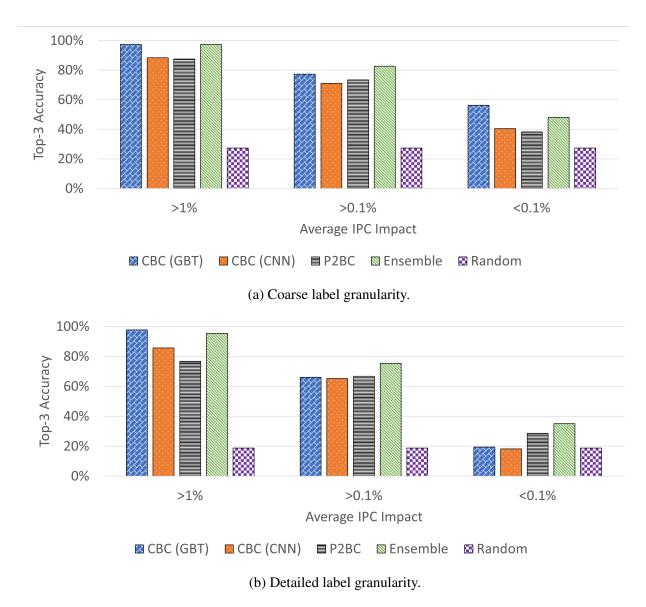

|    |           | 3.5.8.3    | Bug localization accuracy per impact bin                           | 104 |

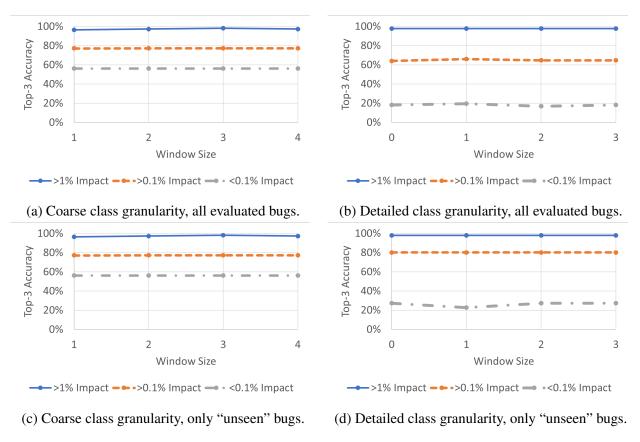

|    |           | 3.5.8.4    | Impact of the window size on bug localization                      | 108 |

|    |           | 3.5.8.5    | Impact of the number of probes on bug localization                 | 110 |

|    |           | 3.5.8.6    | Handling of bug-free cases                                         | 111 |

|    |           | 3.5.8.7    | Potential debugging time speedup                                   | 112 |

|    | 3.6 Conc  | lusion     |                                                                    | 114 |

| 4. | CONCLUS   | SION       |                                                                    | 116 |

|    | 4.1 Futur | e Work     |                                                                    | 117 |

| RI | FERENCE   | S          |                                                                    | 118 |

# LIST OF FIGURES

| FIGURI | E P                                                                                                                                                                                 | age |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1    | Pessimism of a commercial tool in pre-routing timing estimation                                                                                                                     | 2   |

| 2.1    | Simplified diagram of the design flow for integrated circuits                                                                                                                       | 6   |

| 2.2    | An example circuit for timing estimation                                                                                                                                            | 10  |

| 2.3    | Timing prediction methodology structure flow                                                                                                                                        | 11  |

| 2.4    | Timing prediction data extraction flow.                                                                                                                                             | 14  |

| 2.5    | Error distribution of sink delay predictions.                                                                                                                                       | 19  |

| 2.6    | Neural network prediction versus PrimeTime results on net sink delay                                                                                                                | 20  |

| 2.7    | Path slack predictions of circuit "b22" for different methods compared to sign-off timer (PrimeTime) results.                                                                       | 21  |

| 2.8    | ROC curves for critical path classification.                                                                                                                                        | 25  |

| 3.1    | Speedup of Skylake simulation with and without performance bugs, normalized against Ivy Bridge simulation                                                                           | 29  |

| 3.2    | IPC by SimPoints in 403.gcc for Skylake architecture.                                                                                                                               | 37  |

| 3.3    | Overview of a naïve approach for bug detection. Multiple instances of this classifier are implemented, one per application, and the final result is produced by a voting mechanism. | 40  |

| 3.4    | Overview of the two-stage methodology for bug detection                                                                                                                             | 41  |

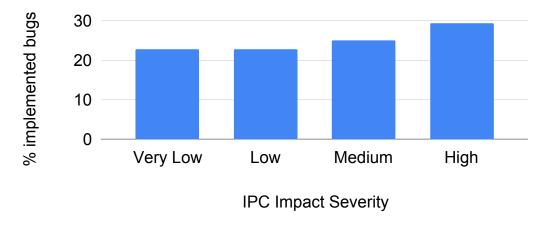

| 3.5    | Average IPC impact distribution of bugs injected for performance bug detection                                                                                                      | 61  |

| 3.6    | Example of the training and testing data split used for performance bug detection                                                                                                   | 62  |

| 3.7    | Distribution of IPC inference error for different ML engines.                                                                                                                       | 64  |

| 3.8    | Examples of ML-based IPC inference and simulated IPC on bug-free microarchitectures.                                                                                                | 65  |

| 3.9    | Comparison of IPC estimations between microarchitectures with and without performance bugs obtained by using ML model GBT-250.                                                      | 66  |

| 3.10 | ROC curves for GBT-250 on different bug types using rule-based classifier                                                      | 69  |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

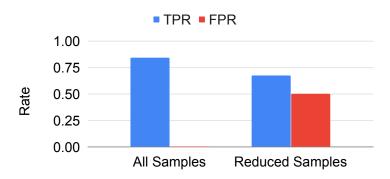

| 3.11 | Impact of the number of available probes on the bug detection results                                                          | 71  |

| 3.12 | Impact of the counter selection method on the bug detection results                                                            | 72  |

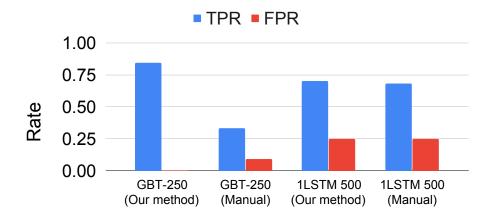

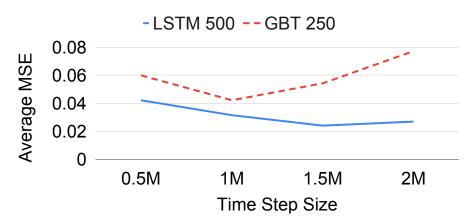

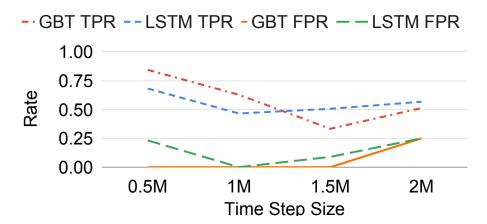

| 3.13 | Impact of the time step size on bug detection measured by the average MSE across all probes.                                   | 72  |

| 3.14 | Impact of the time step size on bug detection measured by the TPR and FPR                                                      | 73  |

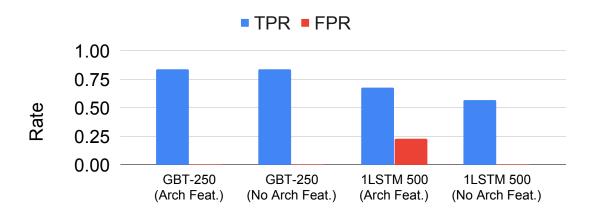

| 3.15 | Impact of the usage of microarchitecture design parameter as features on bug detection.                                        | 74  |

| 3.16 | Impact of the number of training microarchitectures on bug detection                                                           | 75  |

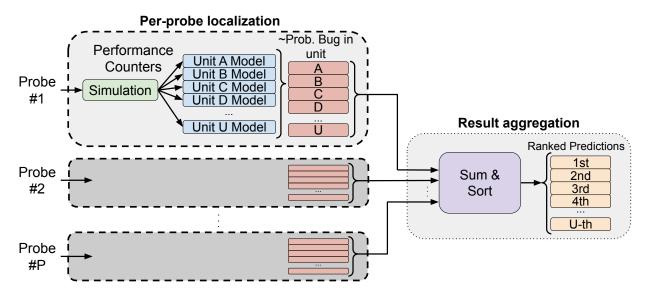

| 3.17 | Overview of the CBC methodology for bug localization.                                                                          | 78  |

| 3.18 | Overview of the P2BC methodology for bug localization.                                                                         | 80  |

| 3.19 | Fourier-based resampling methodology.                                                                                          | 82  |

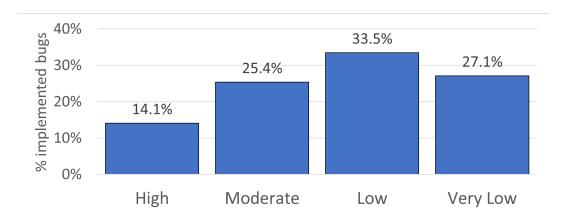

| 3.20 | Average IPC impact distribution of bugs injected for performance bug localization                                              | 99  |

| 3.21 | Top- <i>k</i> bug localization accuracy for different methodologies                                                            | .02 |

| 3.22 | Top-3 accuracy for each possible label for different methodologies across all bugs 1                                           | 03  |

| 3.23 | Top- $k$ localization accuracy for different methodologies in bugs with average IPC impact $> 1\%$ .                           | .05 |

| 3.24 | Top- $k$ localization accuracy for different methodologies in bugs with average IPC impact $> 0.1\%$                           | .06 |

| 3.25 | Top- $k$ localization accuracy for different methodologies in bugs with average IPC impact $<0.1\%$                            | .07 |

| 3.26 | Top-3 localization accuracy on different IPC impact level bugs for different methodologies considering all then evaluated bugs | .08 |

| 3.27 | Impact of window size on top-3 localization accuracy                                                                           | .09 |

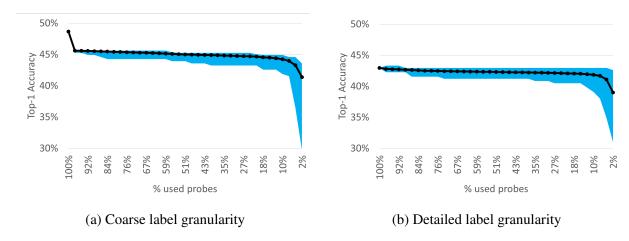

| 3.28 | Impact of the number of available probes on the top-1 localization accuracy across all evaluated bugs                          | 10  |

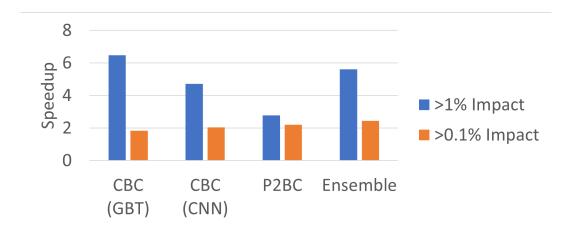

| 3.29 | Speedup gained in debugging time by using the proposed bug localization methodologies                                          | 14  |

# LIST OF TABLES

| BLE                                                                                             | ΓABLE | age |

|-------------------------------------------------------------------------------------------------|-------|-----|

| 2.1 Net slew and delay prediction results for multiple machine learning engines                 | 2.1   | 17  |

| 1                                                                                               | 2.2   | 18  |

| 2.3 Results on total negative slack separated by circuit design on the benchmark                | 2.3   | 22  |

| 1 2                                                                                             | 2.4   | 24  |

|                                                                                                 | 2.5   | 26  |

|                                                                                                 | 3.1   | 49  |

| 3.2 Core specifications of the architectures used to evaluate the bug detection mechanisms      | 3.2   | 50  |

|                                                                                                 | 3.3   | 51  |

| Port organization of the architectures used to evaluate the bug detection mechanisms. 5         | 3.4   | 52  |

| 3.5 Architecture partitioning for train / test of detection methodologies                       | 3.5   | 57  |

| 3.6 IPC modelling runtime and error statistics                                                  | 3.6   | 63  |

| Bug detection results for multiple ML engines when exclusively bug-free train data is used. 6   | 3.7   | 68  |

| used to train. Bug 1 refers to "If XOR is oldest in IQ, issue only XOR" and Bug 2               | 3.8   | 69  |

| 3.9 Impact of the window size on performance bug detection                                      | 3.9   | 74  |

| 3.10 Core specifications of the architectures used to evaluate the bug localization mechanisms. | 3.10  | 87  |

| Cache specifications of the architectures used to evaluate the bug localization mechanisms.      | 88 |

|--------------------------------------------------------------------------------------------------|----|

| Port organization of the architectures used to evaluate the bug localization mechanisms.         | 89 |

| Performance bug types injected to gem5 and their corresponding locations for both granularities. | 96 |

#### 1. INTRODUCTION AND MOTIVATION

With the ever-growing complexity of integrated circuits (ICs), the development of efficient automation tools in areas such as design, validation, and debugging is vital. In recent years, the number of machine learning (ML)-based techniques aiming to improve state-of-the-art tools has grown at a fast pace and has proven its value across a wide variety of problem formulations in almost every step of the IC design flow [3]. This dissertation proposes and evaluates the application of machine learning-based techniques that aim to improve two design aspects, specifically timing prediction for IC designs using pre-routing information, and performance debugging of microprocessor cores at microarchitectural level.

# 1.1 Pre-routing timing prediction

During the cell placement stage of the IC design flow, several optimizations, such as logic restructuring, gate resizing, and threshold voltage assignment, need to be executed in order to achieve the required timing and power specifications. All these optimization procedures require accurate estimations of the circuit timing, however, since routing information is essential for these, it is very challenging to achieve a satisfactory solution at early design stages.

To overcome this issue, designers typically employ one of two options:

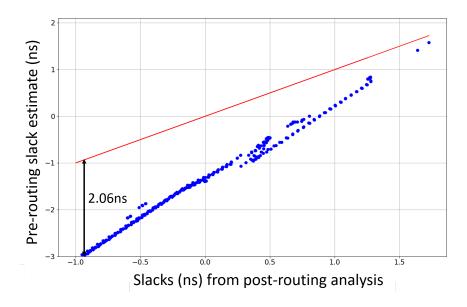

1. To be overly-cautious, and use pessimistic estimations of the timing, this is to ensure that no violations will occur once routing is performed. An example of a commercial tool slack estimation on pre-routing databases is shown in Figure 1.1. The figure corresponds to a circuit with about 25k nets and 500 Flip-Flops (FFs). In the figure, the x-axis represents the worst path slack, as calculated by a post-routing sign-off tool, and the y-axis shows the worst path slack, as calculated by a commercial tool using a placed, but un-routed database. Each dot in the figure represents a different FF. Therefore, the red line indicates a perfect match between pre-routing estimation and post-routing sign-off analysis. In this example, the worst-case slack is over-estimated by more than 2ns. Such pessimism causes over-design

for area and power and wastes optimization time.

Figure 1.1: Pessimism of a commercial tool in pre-routing timing estimation. Reprinted from [1] © 2019 IEEE.

2. To run the whole flow, and iterate back to fix cell placement if the specifications were not met at routing. In this case, each iteration required will significantly increase the design turn-around time, and there is no guarantee that design convergence will be achieved after a certain number of iterations.

Taking all this into consideration, the goal of our research is to develop a machine learning model, that is able to perform accurate and fast predictions of the post-routing timing using placed, but un-routed circuit databases [1]. This will aid designers by reducing the design turn-around time, without incurring in over-design penalties.

# 1.2 Performance debugging of microprocessor cores

During the design of a new microprocessor, the process of verification and validation are typically the ones consuming most of the engineer's time and effort. These procedures can be divided

into two very distinct disciplines, namely, functional and performance verification. Functional verification handles design correctness and has received significant attention in the literature. Although challenging, it has the advantage of having known correct outputs to compare against. On the other hand, performance verification, which handles generation-by-generation workload performance improvement, lacks an exact golden reference for comparison. This is because it remains very difficult to model the interactions among different units in the highly complex microprocessor designs and accurately represent how they affect the system performance. The process of debugging also suffers from the very limited visibility on intermediate points, exposed mostly by performance counters, and the lack of a good debugging infrastructure. Currently, performance verification is conducted mostly through manual techniques that rely on rough estimates of performance gain expected by microarchitectural changes [4]. Such manual processes are not only very lengthy but also error prone.

Although simulation studies may provide an approximation of how long a given application might run on a real system, prior work has shown that these performance estimates will typically diverge from real systems performance [5, 6, 7]. Thus, the process to detect and analyze performance bugs is, in practice, via tedious and complex manual analysis, often taking large periods of time to isolate and eliminate a single bug. For example, consider the case of the Xeon Platinum 8160 processor snoop filter eviction bug [8]. Here the performance regression was more than 10% on several benchmarks. The bug took several months of debugging effort before being fully characterized. In a competitive environment where time to market and performance are essential, there is a critical need for more automated mechanisms that help designers to do performance debugging.

As an early work in this space, we have limited the focus of this dissertation mainly to the microprocessor core, which is the most complex component on the system, although the methodology could be further generalized to other units, such as memory systems or interconnect. In order to maintain tractability, we divided this problem into two main tasks, as described below.

# 1.2.1 Performance bug detection

The goal of this task is to develop an automated machine learning-based performance bug detection flow that uses information extracted from legacy designs to tell the designers whether a new design has a performance bug or not.

# 1.2.2 Performance bug localization

The goal of this task is to expand the methodology implemented for bug detection so that we not only provide the designers with a yes or no answer regarding bug presence, but also provide insight regarding which microarchitectural unit of the processor is the one with the performance bug.

#### 1.3 Thesis statement

This dissertation aims to advance the state-of-the-art automation techniques available for two specific tasks in the performance prediction and diagnosis of VLSI designs area. The first tackles performance at the logic level, in the form of static timing analysis and path slack predictions, the second one, at a higher level, tackles detection and localization of microarchitecture level bugs affecting the total runtime of some applications.

The proposed methodologies for both of these tasks are based on Machine Learning methodologies, which has proven to be an extraordinary method to extract knowledge from data, and handle very complicated non-linear behaviors, making it the best approach to mimic a human manual process among other mathematical or algorithmic options.

#### 1.4 Summary of contributions

Throughout this dissertation, we present several machine-based techniques for performance prediction and diagnosis of VLSI designs, in particular, the main contributions of this work are:

1. The first study on the usage of machine learning for pre-routing timing prediction is conducted [1]. For this study, several machine learning engines are investigated, and a set of input features required for the timing prediction is obtained. The results of this study achieve

pre-routing timing predictions with an accuracy that is comparable to post-routing sign-off timers.

- 2. The first study on the usage of machine learning for automatic detection of performance bugs in microprocessor cores [2]. For this study, multiple strategies and machine learning techniques are evaluated, and it is found that a two-stage approach provides the best results. This method detects 91.5% the evaluated core performance bugs that lead to a ≥ 1% IPC degradation with 0% false positives.

- 3. The first study on the usage of machine learning for automatic localization of performance bugs in microprocessor cores. For this study, multiple methodologies are evaluated, and it is found that the best performing methodology identifies the correct bug location as the most likely option in ~ 75% of the cases and achieves over 98% accuracy when a list of the three most likely options (out of 16 possible) is provided for bugs with an average IPC impact of >1%. Further, for bugs with impact over 0.1% the top-3 accuracy is over 75%. Moreover, our techniques can handle false alarms generated by bug detection.

#### 2. PRE-ROUTING TIMING PREDICTION 1

# 2.1 Background

# 2.1.1 Integrated circuits design flow

As the number of transistors that manufacturers are able to fit into a chip grows, the complexity of the flow required to design an integrated circuit increases. Due to this complexity, the IC industry heavily relies on the usage of design automation software.

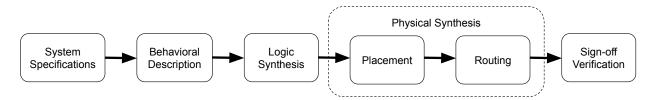

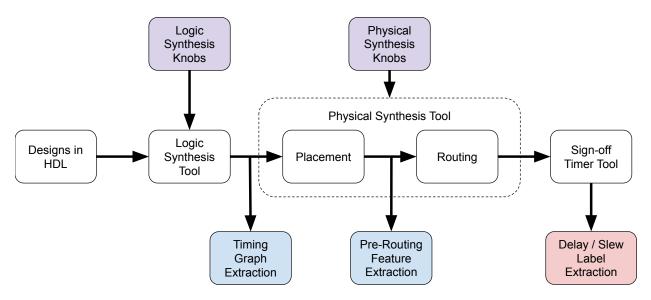

Figure 2.1 shows a diagram of simplified design flow for digital circuits, keeping only the most important steps. Even though the diagram shows a unidirectional flow, the design process usually requires iterating back over several steps, until a solution meeting all the design constraints and specifications is obtained.

Figure 2.1: Simplified diagram of the design flow for integrated circuits.

Each of the steps in Figure 2.1 corresponds to a complex task, which involves several subprocedures that are not covered in detail in this dissertation, as they are out of the scope of this work. However, a brief description of these steps is provided below:

1. **System Specifications:** This step defines the design functionality, provides a list of features that must be included in the design, and technical specifications such as clock frequency,

<sup>&</sup>lt;sup>1</sup>©2019 IEEE. Reprinted, with permission from E. Carvajal Barboza, N. Shukla, Y. Chen and J. Hu, "Machine Learning-Based Pre-Routing Timing Prediction with Reduced Pessimism", *ACM/IEEE Design Automation Conference (DAC)*, 2019.

power consumption, and several others depending on the purpose of the design and its target market.

- Behavioral Description: Once the major characteristics of the design have been determined, these are translated into behavioral models of the design, usually written in a hardware description language, such as VHDL or Verilog.

- 3. **Logic Synthesis:** During this step, the behavioral description of the design is transformed into a digital circuit by listing every logic gate, sequential elements, and their corresponding connectivity. This description is usually known as a "netlist". Due to the high complexity of this procedure, automated tools are usually used for this process. Along with the transformation, several timing, power, and area optimizations also take place at this step [9].

- 4. **Physical Synthesis:** In this step, the netlist generated by the logic synthesis is further transformed into a physical design by deciding where each logic gate will be placed and what trajectory each interconnection will follow. Both placement and routing are very complex tasks, usually requiring several iterations to achieve a satisfactory result. Several specifications, such as performance, power consumption, and heat distribution rely heavily on the quality of the solution obtained at this stage.

- 5. **Sign-off Verification:** In this step the design is evaluated using more detailed, and therefore slower models. This allows for better accuracy in the results and higher confidence in the timing, power, and reliability metrics. Once all the checks in this step have passed, the design is ready for manufacturing.

# 2.1.2 Timing models

Briefly speaking, there are two kinds of timing models that are often employed for logic and physical synthesis of integrated circuits:

1. A sign-off model that evaluates if a circuit design satisfies timing specifications. It estimates gate delay using lookup tables [10] or current source model; these models consider slew-

rates, and the wire delay estimation uses high-order models [11]. Additionally, sign-off timing analysis tools consider many details such as rising/falling switching, crosstalk, false paths, and simultaneous switching.

2. A relatively fast model that is often invoked within synthesis and optimizations. In this case, a gate is modeled as an RC switch, wires are modeled as RC trees, and the delay is computed using the Elmore method [12].

To obtain an overall estimation of the timing in the design, the gate and wire delays are collected using addition/subtraction and max/min operations through PERT traversals [13] to obtain signal arrival time, required arrival time, and slack at each node in a circuit.

For timing estimation at placement, and before routing, gate delay can be obtained using signoff models while wire delay is greatly simplified because the routing information is not available.

For example, the source-sink delay of a net can be estimated using an analytical formula based on

their distance [14]. Such pre-routing models are not very accurate, as they do not consider potential

wire detours due to congestion avoidance or the impact produced by the metal layer assignment.

Moreover, without wire parasitic information, the higher-order interconnect model has no ground

to carry out accurate delay computation.

#### 2.2 Prior work

There have been a few previous works aiming to apply machine learning methodologies for timing analysis, but they are targeted for applications in different contexts from our work. For example, the work by Kahng *et al.* in 2014 [15] aims to guide the gate sizing and threshold voltage assignment in post-routing timing recovery and power optimization. For this, a set of machine learning models that estimate wire delay and slew are used on iterative static timing analysis to achieve a more accurate estimation of endpoint slack without the need to constantly re-run the sign-off tool timing models due to adjustments on gate sizing or threshold voltage swapping. In this work, the ML is used to learn weights that are later applied to the delay and slew results obtained by multiple analytical models.

Han et al. [16] studied several machine learning techniques, including random forest and SVM to overcome the discrepancy between different commercial timing analysis tools. The proposed methodology correlates path slack between different timing tools across multiple technology nodes and designs, reducing the range of divergence by over  $5.5\times$ . In particular this approach was evaluated by correlating two different signoff tools, as well as a signoff tool with a design implementation tool.

The work by Kahng *et al.* in 2015 [17] makes use of neural network and SVM techniques to estimate the effect of coupling capacitance in timing analysis without the need to run commercial timing analysis tools in signal integrity mode. This work achieved worst-case error reductions of up to 55ps.

In work done by Chan *et al.* in 2016 [18], boosting and SVM are applied to the floorplanning stage to predict timing failures of embedded memories. The high uniformity of embedded memory circuits allows for such early timing failure predictions, unlike the case of other circuits where the structure is not as well-defined.

More recently, work by Lu [19] uses conditional generative adversarial networks (GAN) to optimize the clock tree synthesis (CTS) outcome via reinforcement learning. This methodology extracts features from placement images and uses a GAN to test combinations of input settings to be used during the clock tree synthesis flow and determine whether they will outperform the designs obtained automatically by the commercial tools.

Overall, there is no previous work on machine learning-based pre-routing timing prediction for circuit optimizations at the placement stage, to the best of our knowledge.

# 2.3 Machine learning for pre-routing timing prediction

# 2.3.1 Problem formulation

Given an un-routed, but placed circuit database, the goal of this work is to develop an accurate and fast model that is able to predict the post-route slack of every path in the design. This will aid designers by providing results with post-routing sign-off tool quality at early stages of the design,

preventing the need of multiple iterations or over-designing.

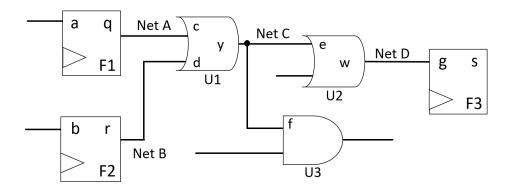

The proposed methodology consists of a machine learning model able to predict net delay using information that is readily available at pre-routing stages. The model performs the predictions on a per-net basis. In other words, the delay model will provide a prediction of the delay between the input pin of a driver gate and the sink pin of the receiver gate. Using Net 'D' of Figure 2.2 as an example, our model will predict the delay to pin 'g', incorporating the delay of driver gate 'U2', as well as the delay due to the wire between pins 'w' and 'g'. In the case of multi-fanout drivers, as is the case of Net 'C', our model will predict two separate delays, one to pin 'e' and another to pin 'f', and just as in the previous case, both of these timing predictions will incorporate the delay of the driver gate 'U1' and their delay produced by the wire.

Figure 2.2: An example circuit for timing estimation.

Once the delay of all source-sink pairs has been calculated, PERT traversals [13] are applied on the circuit graph, which is extracted from the design netlist. This is done so that more useful metrics for designers, such as arrival time, required arrival time, and path slack can be obtained.

Our model does not differentiate among the different input pins of a single driver gate (pins 'c' and 'd' of cell 'U1'). The different arrival times of the pins are considered only during the PERT traversal. This strategy allows our model to perform a single prediction for multi-input gates with the expense of minor approximation. For similar reasons, our model does not differentiate between

rising and falling delays, it only predicts the delay for the worst case.

# 2.3.2 Methodology overview

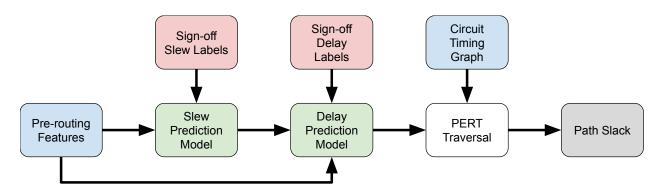

An overview of the proposed methodology is depicted in Figure 2.3. In the figure, the blue boxes correspond to inputs to our methodology, obtained in the pre-routing stages of the design flow. The red boxes indicate labeled data, which is required only during training phases. The gray box indicates our final output.

Figure 2.3: Timing prediction methodology structure flow.

The proposed methodology takes as input features a set of data extracted from pre-routing databases, a detailed explanation of the features used as inputs to the ML models implemented for this methodology is given in Section 2.3.3. The features are used in two different machine learning models:

• Slew prediction model: We define the slew rate as the signal transmission time, which means that a sharp signal transition will have small slew. Slew information is vital for an accurate timing estimation, but it usually requires a thorough timing analysis in order to produce accurate results. For this reason, we developed a dedicated net slew model, which predicts the slew rate at every sink pin by using the pre-routing features. This model is trained using labeled data obtained with a sign-off timer tool.

• **Delay prediction model:** This model takes the pre-routing features along with the information predicted by the slew model mentioned above. This model is the one in charge of generating the delay predictions for every net on the design. To train it, labeled data obtained with a sign-off timer tool is used.

Once the delay predictions of every net in the design have been performed, a circuit timing graph, extracted from the design netlist, is used in order to perform the PERT traversals [13]. This method will then produce the path slack information, which is ultimately the most important metric for circuit designers.

### 2.3.3 Model features

The pre-routing features correspond to the data that will be used as inputs to the machine learning model so that a prediction can be performed. A good set of input features is critical for the accuracy of the model. The features used for the delay model are elaborated as follows:

- **Driver capacitance:** The driver output capacitance is proportional to its driving strength.

Larger values indicate faster drivers and therefore smaller delays. This value can be extracted from the standard cell library being used for the design.

- **Sink capacitance:** The sink input pin capacitance is proportional to the load seen by the driver. Larger values indicate more load and therefore larger delays. The proposed model uses two different features to represent this information:

- 1. The **target sink capacitance**, which corresponds only to the capacitance of the input pin to which the delay is being predicted.

- 2. The **total sink capacitance**, which corresponds to the sum of the input capacitance of every sink pin connected to the net.

Going back to the example of Figure 2.2, when predicting the delay to pin 'e' in Net 'C', the target sink capacitance will correspond only to the capacitance provided by pin 'e', while the

total sink capacitance will also include the capacitance added to Net 'C' due to pin 'f'. This value can also be extracted from the standard cell library that is used to generate the design

- **Distance between driver and target sink:** The horizontal and vertical distances between the driver gate and the target sink are proportional to the wire delay, especially when buffers are inserted in long nets [14].

- Context sink locations: In multi-fanout nets, when the proposed model is applied to determine the delay between the source gate and the target sink, every other sink connected to the same net is called a "context sink". As an example, in Net 'C' of Figure 2.2, when the delay to sink pin 'e' is being predicted, sink pin 'f' serves as a context sink. These context sinks not only contribute to the total load capacitance, but their locations can also affect routing, buffering, and therefore delay to the target sink. Since the number of context sinks varies among nets, but the evaluated machine learning models require a fixed size input, the context sink locations are approximated by providing the model with statistical signatures. One is the median position of all context sink, which provides the model with information of roughly, how far away these are from the driver. Another one is the standard deviation of the locations in both dimensions, this indicates to the model how spread they are, which correlates with the corresponding interconnect tree size.

- **Driver input slew:** The slew information is obtained via a dedicated machine learning model, as explained in Section 2.3.2. As the number of input pins varies from gate to gate, and the evaluated machine learning models require a fixed input size, only the maximum slew across every input pin of the driver gate is considered. For example, when the slew model is applied to Net 'C' at Figure 2.2, it will provide estimations for sink pins 'e' and 'f', these will later be used to estimate the delays of Net 'D' and the net driven by gate 'U3'.

#### 2.3.4 Data extraction

In order to extract the data required for the training and testing of this methodology the flow described in Figure 2.4 is followed.

Figure 2.4: Timing prediction data extraction flow.

In detail, the steps are described below:

- Designs are described in a behavioral manner in a Hardware Description Language, such as Verilog or VHDL.

- 2. Using a commercial logic synthesis tool, the behavioral description is transformed into a netlist, which enumerates the logic gates, sequential elements, and their connections. To augment the dataset, the logic synthesis tool is executed multiple times with different values on some of the tool knobs such as mapping effort, dynamic power optimization, static power optimization, clock gating, maximum fanout, maximum load capacitance, maximum transition time, among others. From the resulting netlists, the circuit timing graph that will be used for the PERT traversals is extracted, this is required in order to obtain each path slack.

- 3. Each of the generated netlists is then processed by a commercial physical synthesis tool, which transforms the netlist into a physical layout design. As in the previous step, the dataset is augmented by running this step multiple times changing some of the tool knobs, such as maximum utilization, congestion effort, timing optimization, signal integrity optimization, among others. Physical synthesis is usually done in two separate steps: placement and

routing. After the first stage is done, the data that will be used as features by the proposed model is extracted. For the intended application usage, once here, and before running the routing, the machine learning model is used to obtain timing estimations, and fixes can be applied by the designers to address the issues with the current implementation. However, to gather training data for the model, the rest of the flow is executed, so that the labels can be extracted.

4. Finally, a sign-off timing analysis tool is executed, and the slew and delay data is extracted, so that they can be used as labels to train the machine learning models.

# 2.3.5 Customized loss function neural network

When performing timing estimations designers prefer to estimate delays higher than what they actually are, so that they err on the cautious side. For that reason, in this section, a custom loss function in the neural network model is proposed, so that the models learn to follow the same cautious behavior. Commonly, Neural Networks use Mean Squared Error (MSE), described by Equation 2.1, as its loss function.

$$MSE = \frac{1}{N} \sum_{i=0}^{N} (\hat{y}_i - y_i)^2$$

(2.1)

Here  $y_i$  represents the actual value,  $\hat{y_i}$  represents the value estimated by the model, while N represents the total number of samples. This metric is symmetric, and the same loss weight will be applied to both positive and negative errors. However, since designers would prefer to have estimations that are higher than the actual value (positive error values), an asymmetric MSE is implemented as described by Equation 2.2.

Asymmetric MSE = MSE +

$$\frac{1}{2n} \sum_{i=0}^{n} (|\hat{y}_i - y_i| - \hat{y}_i + y_i)^2$$

(2.2)

Note that, for positive errors  $(\hat{y}_i \geq y_i)$  the loss function is equal to the regular MSE, while for negative errors  $(\hat{y}_i < y_i)$  the asymmetric MSE is equal to two times the MSE. Thus, this loss

function forces the model to prevent predictions that under-estimate the delay. A comparison on the accuracy of this method is shown in Section 2.5.2

# 2.4 Experimental setup

The experimentation was performed on benchmark circuits from ITC'99 [20], in particular the selected designs are b11, b12, b13, b14, b17, b20, b21, and b22. The ITC'99 benchmarks are written in VHDL language. These designs go through the logic synthesis procedures using Synopsys Design Compiler, and the generated netlist is then feed to Cadence Encounter to perform the physical synthesis. The physical synthesis includes steps such as cell placement, buffer insertion, and routing. For labeled data generation, a subset of the routing solutions are fed to Synopsys PrimeTime, which is considered a sign-off analysis tool.

By modifying some knobs on the logic and physical synthesis tools, as described in Section 2.3.4, 40 different implementations of each of the b11, b12, b13, b14, b20, and b21 circuits are obtained (240 different circuit implementations in total). From these, 20 of each circuit are used as part of the training set for the ML models (120 different circuit implementations in total). The other half of these, along with 20 different implementations of b17 and b22 are used to test the models (160 implementations in total). This allows to evaluate the performance of the models in designs that the models have seen before, as well as designs that are completely new for the models.

The circuits are implemented using the NanGate 45nm standard cell library [21]. Although the proposed methodology is able to work on designs that have not been seen by the models before, the models learn the behavior of the specific standard cell library on which they are trained, therefore, if a different library is used, the models will need to be re-trained.

The machine learning models were implemented, trained, and tested using Python [22]. The Lasso Linear Regression [23] and Random Forest [24] models were implemented using the Scikit-Learn library [25], while the Neural Networks were implemented using Keras [26]. Besides these machine learning models, a commercial tool on pre-routing timing prediction is used to compare the obtained results.

#### 2.5 Results

This section presents the results of multiple evaluations performed to the ML-based timing estimation methodology proposed here.

# 2.5.1 Net slew and delay estimation quality

In this section, the quality of the machine learning models on individual net delay and slew prediction is evaluated. Please note that testing data includes 20 different implementations of designs b11, b12, b13, b14, b20, and b21; although the model was trained using these designs, every implementation used for testing is slightly different to the ones used for training. All 20 implementations of designs b17 and b22 are completely new to the model since these designs were not included for the training.

The evaluated machine learning engines are Lasso Linear Regression [23], Random Forest [24] and Artificial Neural Networks [27]. In the case of the latter, two different variants were tested, the first one uses Mean Squared Error (MSE) as its loss function, while the second variation uses the custom loss function explained in Section 2.3.5. The results obtained on the testing designs for different machine learning engines are presented on Table 2.1.

Table 2.1: Net slew and delay prediction results for multiple machine learning engines.

|                         | Slew pre    | diction              | Delay prediction |                      |  |

|-------------------------|-------------|----------------------|------------------|----------------------|--|

| Method                  | Correlation | MSE                  | Correlation      | MSE                  |  |

| Lasso Regression        | 0.739       | $1.4 \times 10^{-3}$ | 0.710            | $1.9 \times 10^{-3}$ |  |

| Neural Network (MSE)    | 0.861       | $7.6 \times 10^{-4}$ | 0.891            | $5.7 \times 10^{-4}$ |  |

| Neural Network (Custom) | 0.856       | $8.1 \times 10^{-4}$ | 0.882            | $6.1 \times 10^{-4}$ |  |

| Random Forest           | 0.974       | $1.0 \times 10^{-4}$ | 0.971            | $1.8 \times 10^{-4}$ |  |

| Commercial tool         | 0.909       | $3.8 \times 10^{-4}$ | 0.947            | $3.7 \times 10^{-3}$ |  |

On Table 2.1, both Pearson's correlation factor and MSE are calculated with respect to the post-routing analysis obtained using Synopsys PrimeTime, as that metric is considered the "Ground Truth". These results are averaged across all testing circuits and weighted by the number of end-

points, *i.e* the number of flip-flops and primary outputs. Therefore, large circuits carry relatively large weights.

The results show that the proposed models for slew prediction have an accuracy on-par with the estimations provided by the pre-routing commercial tool. However, the pre-routing commercial tool has a much larger MSE than the obtained by the proposed machine learning models in terms of delay prediction. In particular, it can be seen that the proposed method produces the least MSE and highest correlation when Random Forest is used. Not only is Random Forest far more accurate than the other machine learning engines evaluated, but the achieved error is an order of magnitude lower than the error from the pre-routing commercial tool. A detailed circuit by circuit comparison between the Random Forest model and the commercial tool is provided in Table 2.2.

Table 2.2: Comparison of net skew and delay prediction results between random forest and a commercial tool.

|         |        |       | Slew prediction               |             |                       |             | Delay prediction      |             |                       |             |

|---------|--------|-------|-------------------------------|-------------|-----------------------|-------------|-----------------------|-------------|-----------------------|-------------|

|         |        |       | Random forest Commercial tool |             |                       | rcial tool  | Randor                | n forest    | Comme                 | rcial tool  |

| Circuit | # nets | # FFs | MSE                           | Correlation | MSE                   | Correlation | MSE                   | Correlation | MSE                   | Correlation |

| b11     | 926    | 30    | $1.69 \times 10^{-6}$         | 0.998       | $2.29 \times 10^{-5}$ | 0.976       | $6.18 \times 10^{-5}$ | 0.986       | $1.71 \times 10^{-3}$ | 0.966       |

| b12     | 2409   | 121   | $1.69 \times 10^{-6}$         | 0.999       | $1.67 \times 10^{-4}$ | 0.948       | $9.71 \times 10^{-5}$ | 0.968       | $1.84 \times 10^{-3}$ | 0.992       |

| b13     | 586    | 53    | $1.42 \times 10^{-6}$         | 0.999       | $3.69 \times 10^{-5}$ | 0.979       | $9.62 \times 10^{-5}$ | 0.954       | $1.54 \times 10^{-3}$ | 0.987       |

| b14     | 28828  | 247   | $5.25 \times 10^{-6}$         | 0.999       | $6.49 \times 10^{-4}$ | 0.854       | $7.57 \times 10^{-5}$ | 0.989       | $4.02 \times 10^{-3}$ | 0.967       |

| b17     | 31084  | 1407  | $1.11 \times 10^{-4}$         | 0.962       | $1.79 \times 10^{-4}$ | 0.919       | $3.39 \times 10^{-4}$ | 0.924       | $2.91 \times 10^{-3}$ | 0.980       |

| b20     | 18907  | 494   | $9.62 \times 10^{-5}$         | 0.978       | $4.48 \times 10^{-4}$ | 0.912       | $1.41 \times 10^{-4}$ | 0.980       | $3.44 \times 10^{-3}$ | 0.937       |

| b21     | 25034  | 494   | $1.16 \times 10^{-4}$         | 0.967       | $3.83 \times 10^{-4}$ | 0.937       | $2.09 \times 10^{-4}$ | 0.972       | $3.41 \times 10^{-3}$ | 0.967       |

| b22     | 45354  | 709   | $1.15 \times 10^{-4}$         | 0.974       | $3.72 \times 10^{-4}$ | 0.910       | $1.72 \times 10^{-4}$ | 0.976       | $4.72 \times 10^{-3}$ | 0.922       |

Results on Table 2.2 show that the slew predictions of the random forest model are slightly better than the commercial tool estimations in every circuit, both for correlation, as well as MSE. In terms of net delay prediction, the random forest model achieves MSE that are at least one order of magnitude smaller than the commercial tool, even on designs b17 and b22, which were not used for training.

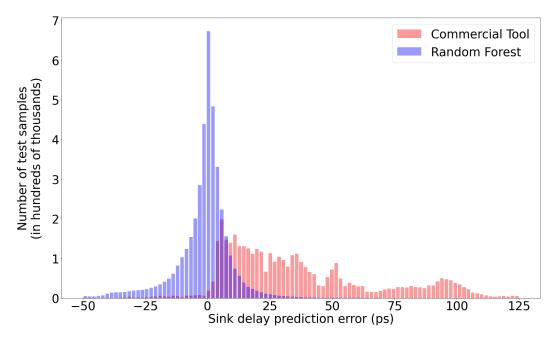

A histogram depicting the distribution of the error on net delay predictions is shown in Figure 2.5. The figure clearly shows the advantage of the proposed random forest model over the commercial tool. The random forest predictions have not only smaller errors but also a smaller variation. By contrast, the estimations by the commercial tool are very pessimistic and the errors are largely spread.

Figure 2.5: Error distribution of sink delay predictions.

# 2.5.2 Impact of the customized loss function on the neural network prediction accuracy

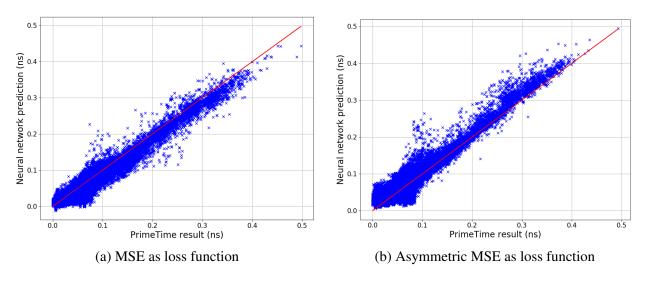

To evaluate the impact of using the asymmetric MSE as loss function, both variations of Neural Networks (regular MSE and custom MSE) were trained and tested using identical network architectures and well as identical train and test sets. The only difference between them is the loss function. The results of this experiment are shown in Figure 2.6. In the figure, the x-axis shows the net delay as calculated by PrimeTime, a post-routing sign-off timer tool, the y-axis shows the delay estimated using the corresponding NN. Each dot in the figure represents a different source-sink pair. Therefore, the red line indicates a perfect match between the ML prediction and the post-routing sign-off analysis.

It can be seen that the custom loss function forces the predictions to shift upwards, and therefore reduces the number of under-estimated delays. From the 90,010 source-sink pairs on the test set,

Figure 2.6: Neural network prediction versus PrimeTime results on net sink delay.

only a 22.06% is underestimated when the asymmetric loss function is used, while a 75.26% is underestimated when the regular MSE is used as loss function. Despite the improvement from the custom loss function, the overall accuracy achieved by the neural network model is not as good as that of random forest-based model. This method was evaluated exclusively on Neural Networks because the libraries implementing the other ML engines do not allow for custom loss functions.

# 2.5.3 Path slack prediction accuracy

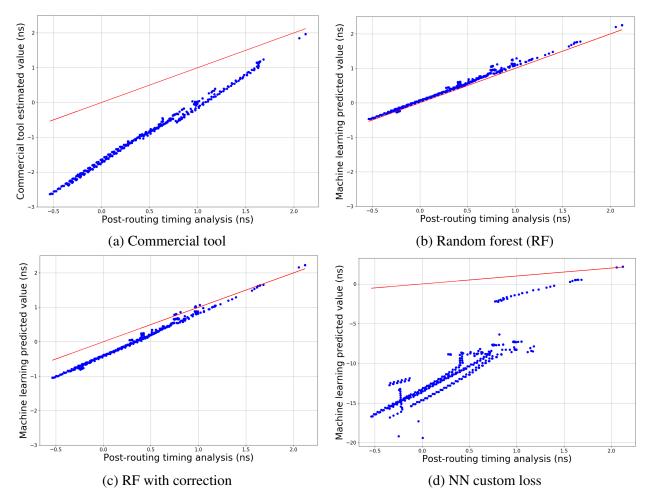

Although having accurate predictions of the delay of every net in the design is important, even more significant is to have accurate predictions of the slack available at each endpoint in a design. This is because, ultimately this will be the determining factor to identify timing violations. To illustrate this, endpoint (either flip-flops or primary outputs) slack predictions from different methods are compared for one implementation of circuit b22 and the results are plotted in Figure 2.7. In the figure, the x-axis shows the path slack as calculated by PrimeTime, which is considered the "ground-truth", since it is a post-routing sign-off timer tool, the y-axis shows the slack predicted by using the corresponding ML engine. Each dot in the figure represents a different endpoint. Therefore, the red line indicates a perfect match between the ML prediction and the post-routing sign-off analysis estimation.

Figure 2.7: Path slack predictions of circuit "b22" for different methods compared to sign-off timer (PrimeTime) results.

Note that circuit "b22" is not included in the training data, and therefore none of the nets of this design were used to train the model. The goal of this plot is to illustrate slack predictions on different paths of a design, and how accurate the ML engines can be. Although here we show only results for one implementation of "b22", the results on other circuits and implementations are similar to these.

Figure 2.7a shows that the pre-routing commercial tool estimations are quite pessimistic for slack prediction, its MSE across this design is 2.023. Figure 2.7b shows that the random forest-based prediction is much closer to the perfect match with a MSE of 0.012, which is more than  $150 \times$  smaller than the commercial tool.

However, one disadvantage of the random forest model is that, as it can be seen in Figure 2.7b, there are multiple paths for which the predicted slack is greater than what it is in reality, which could lead to functional issues when the circuit runs at the specified speed. To avoid this, a scaling-based correction was implemented. What this methodology does is simply to multiply the obtained maximum arrival time of each endpoint by a factor  $\alpha>1$ , which will make the predictions larger, and therefore the slack predictions become more pessimistic, pushing down the slack curve as shown in Figure 2.7c for  $\alpha=1.15$ . Even after this correction, the MSE is still at 0.114, which is still  $>15\times$  lower than that from the commercial tool. The result in Figure 2.7d confirms that neural network is quite inferior in slack prediction.

The overall slack predictions results are summarized in Table 2.3 for PrimeTime (which constitutes the "Ground Truth"), the Random Forest models (both with and without scaling factor), as well as the pre-route commercial tool. The quality of the results is measured by comparing the Total Negative Slack (TNS). It can be seen that the result from random forest prediction is much closer to PrimeTime than the commercial tool prediction. The error of TNS prediction is consistently one order of magnitude lower than the pre-route commercial tool on every circuit. The results normalized against the PrimeTime TNS are also shown in this table.

Table 2.3: Results on total negative slack separated by circuit design on the benchmark.

|         | PrimeTime | Ran    | dom forest | Random f | forest w/ correction | Comn    | nercial tool |

|---------|-----------|--------|------------|----------|----------------------|---------|--------------|

| Circuit | TNS       | TNS    | Normalized | TNS      | Normalized           | TNS     | Normalized   |

| Circuit | (ns)      | (ns)   | TNS MSE    | (ns)     | TNS MSE              | (ns)    | TNS MSE      |

| b11     | -0.14     | -0.49  | 3.50       | -1.37    | 9.79                 | -5.33   | 38.07        |

| b12     | -0.90     | -2.94  | 3.27       | -5.51    | 6.12                 | -22.42  | 24.91        |

| b13     | -0.04     | -0.35  | 8.75       | -1.20    | 30.00                | -5.78   | 144.50       |

| b14     | -9.05     | -12.01 | 1.33       | -40.37   | 4.46                 | -143.86 | 15.90        |

| b17     | -7.73     | -0.56  | 0.07       | -10.14   | 1.31                 | -367.79 | 47.58        |

| b20     | -48.46    | -69.38 | 1.43       | -151.63  | 3.13                 | -412.09 | 8.50         |

| b21     | -17.48    | -27.82 | 1.59       | -85.71   | 4.90                 | -299.29 | 17.12        |

| b22     | -22.23    | -18.08 | 0.81       | -68.21   | 3.07                 | -383.27 | 17.24        |

| Average | -13.25    | -16.45 | 1.24       | -45.52   | 3.44                 | -204.98 | 15.47        |

In terms of runtime, on average, across the 160 design implementations (20 implementations per circuit  $\times$  8 circuits) for testing, the random forest-based timing prediction is  $30\times$  faster than PrimeTime and only  $3\times$  slower than the commercial pre-routing timing estimation.

#### 2.5.4 Critical path classification accuracy

The most important application of timing analysis or slack prediction is to identify the timing critical paths where additional optimization effort is needed. In practice, designers often apply additional guard-band to avoid missing any potentially critical paths. For example, a path is considered critical when its slack is smaller than a threshold  $\theta > 0$ . In this experiment, a  $\theta = 15ps$  is used and then machine learning prediction is applied in order to classify if the path with minimum slack at each endpoint is critical or not. The following are a couple of commonly used metrics for evaluating classification accuracy.

- TPR (True Positive Rate): the ratio of the number of truly critical paths correctly identified by a classifier versus total number of truly critical paths. This captures the percentage of actual critical paths the method is able to detect. A perfect TPR is 1.

- TNR (True Negative Rate): the ratio of the number of truly non-critical paths correctly identified by a classifier versus total number of truly non-critical paths. A perfect TNR is 1.

- FPR (False Positive Rate): 1 TNR.

- FNR (False Negative Rate): 1 TPR.

The TPR and TNR results from random forest-based classification (with and without correction) and the pre-route estimations provided by the commercial tool are shown in Table 2.4. It can be seen that random forest reaches TPR of 1 for all circuits except b17. There could be two reasons for this: (1) b17 is not part of the training data, therefore results with slightly less accuracy are expected or (2) b17 is an intrinsically difficult case, the large errors obtained by the commercial tool hint that the second reason might be true.

Table 2.4: Results on circuit slack and critical path classification divided by circuit design on the benchmark.

|                  | PrimeTime  | R          | andom | forest |      | Random     | forest | w/ corre | ection | Co         | mmerc | ial tool |      |

|------------------|------------|------------|-------|--------|------|------------|--------|----------|--------|------------|-------|----------|------|

| Circuit          | # critical | # critical | TPR   | TNR    | ROC  | # critical | TPR    | TNR      | ROC    | # critical | TPR   | TNR      | ROC  |

|                  | paths      | paths      |       |        | area | paths      |        |          | area   | paths      |       |          | area |

| b11              | 4          | 8          | 1.00  | 0.86   | 0.94 | 15         | 1.00   | 0.55     | 0.74   | 28         | 1.00  | 0.02     | 0.29 |

| b12              | 24         | 34         | 1.00  | 0.90   | 0.98 | 41         | 1.00   | 0.81     | 0.94   | 114        | 1.00  | 0.96     | 0.72 |

| b13              | 4          | 10         | 0.97  | 0.84   | 0.93 | 26         | 1.00   | 0.43     | 0.75   | 42         | 1.00  | 0.03     | 0.37 |

| b14              | 39         | 45         | 1.00  | 0.97   | 0.99 | 78         | 1.00   | 0.77     | 0.90   | 150        | 1.00  | 0.36     | 0.71 |

| b17              | 49         | 10         | 0.19  | 1.0    | 0.50 | 57         | 0.92   | 0.99     | 0.89   | 759        | 1.00  | 0.44     | 0.80 |

| b20              | 116        | 166        | 1.00  | 0.86   | 0.99 | 166        | 1.00   | 0.61     | 0.90   | 330        | 1.00  | 0.31     | 0.68 |

| b21              | 53         | 93         | 1.00  | 0.90   | 0.99 | 184        | 1.00   | 0.66     | 0.94   | 343        | 1.00  | 0.33     | 0.69 |

| b22              | 73         | 74         | 0.89  | 0.99   | 0.94 | 148        | 1.00   | 0.86     | 0.96   | 459        | 1.00  | 0.32     | 0.63 |

| Average          | 45         | 55         | 0.88  | 0.91   | 0.91 | 99         | 0.99   | 0.71     | 0.88   | 278        | 1.00  | 0.35     | 0.61 |

| Weighted Average | -          | -          | 0.86  | 0.96   | 0.98 | -          | 0.99   | 0.85     | 0.97   | -          | 1.00  | 0.38     | 0.85 |

It can also be observed that the commercial tool has much lower TNR than random forest. Its TNR results indicate that the number of false alarms is usually over 60%, which lead to considerable over-design and wastes precious engineer time. The random forest-based classification achieves satisfactory results, even on design b22, which is not included in the training data. The results in Table 2.4 also confirm the importance of the correction for random forest model. Without the correction, the TPR of random forest b17 is very low. The average results in the last row of Table 2.4 are weighted according to the number of endpoints of each circuit. As such, large circuits carry more weight in the average results.

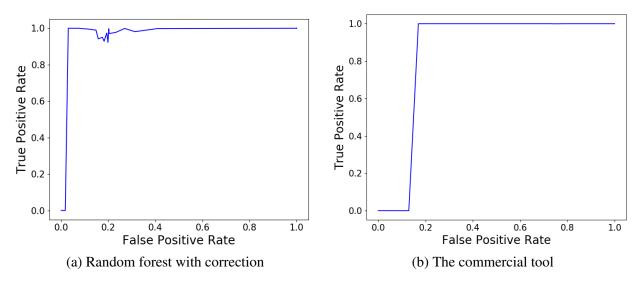

Evidently, TPR and TNR are affected by the value of threshold  $\theta$ . When  $\theta$  becomes large, TPR increases and TNR decreases. The Receiver Operating Characteristic (ROC) curve is a way to evaluate classification accuracy for different threshold values. In ROC curves, the x-axis shows the FPR, while the y-axis indicates the TPR. A perfect classifier would reside on the point (0,1). Figure 2.8 shows the ROC curves for the classifications obtained using random forest with correction (Figure 2.8a) as well as the pre-route commercial tool (Figure 2.8b). The oscillations in Figure 2.8a are due to the fact that the slack estimate of the machine learning model is occasionally optimistic.

An overall numeric metric for an ROC curve is the area under the ROC curve. A random guess would obtain an ROC area of 0.5, while a perfect classifier can achieve ROC area 1. The ROC area

results for all test cases are also listed in Table 2.4. The ROC areas from random forest is 0.97 in the weighted average, which is remarkably higher than the 0.85 from the commercial tool.

Figure 2.8: ROC curves for critical path classification.

Another purpose of the timing prediction is to identify non-critical paths, which are those from which timing can be sacrificed in order to reduce power consumption. Experiments were conducted to identify those paths with a slack > 100ps. In this classification, the random forest model with correction can correctly identify 79% of the truly non-critical paths while the pre-route commercial tool can identify only 34% of them. Finding more non-critical paths will help the designer with considerable power savings.

### 2.5.5 Implementation quality ranking

Another application of the timing prediction is to compare design implementations of the same circuit and determine which implementation is superior. In this experiment, the TNS is used to rank the 20 implementations of each circuit. Table 2.5 shows the ranking of the highest ranked implementation (with respect to the actual TNS obtained using PrimeTime) that can be found on the top-3 ranked of either random forest or the pre-route commercial tool. The random forest-

based ranking can often pick the actual best implementation among its top-3 choices, including b17, which is not used in training data. On average, the ranking results from the random forest model is better than that from the commercial tool.

Table 2.5: Best rank circuit implementation found in estimated top-3 using pre-routing ML estimation method.

| Circuit | Commercial tool | Random forest with correction |

|---------|-----------------|-------------------------------|

| b11     | 1st             | 1st                           |

| b12     | 1st             | 1st                           |

| b13     | 4th             | 1st                           |

| b14     | 7th             | 4th                           |

| b17     | 2nd             | 1st                           |

| b20     | 3rd             | 1st                           |

| b21     | 10th            | 11th                          |

| b22     | 2nd             | 4th                           |

| Average | 4th             | 3rd                           |

#### 2.6 Conclusion

In this chapter, the first systematic study, to the best of our knowledge, on a machine learning approach for pre-routing timing prediction, was presented and evaluated. Model feature selection and several different machine learning engines were investigated. Extensive experiments on benchmark circuits show that the proposed machine learning model can largely reduce the pessimism and improve the accuracy of pre-routing prediction compared to a commercial tool.

# 3. PERFORMANCE DEBUGGING OF MICROPROCESSOR CORES 1

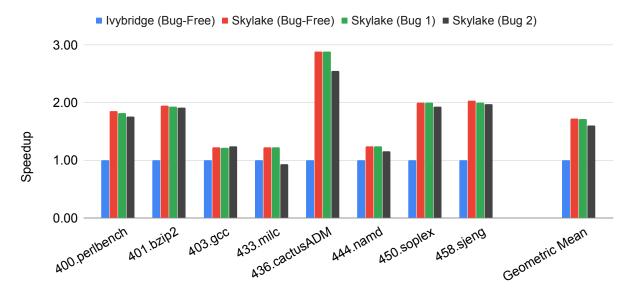

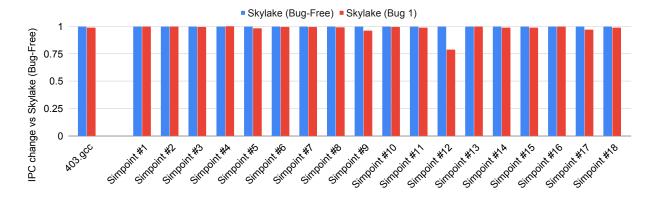

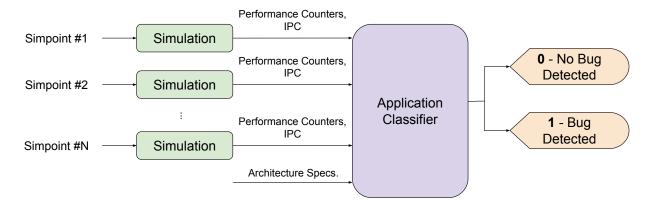

## 3.1 Background