# EFFICIENT INTERCONNECTION NETWORK DESIGN FOR HETEROGENEOUS ARCHITECTURES

A Dissertation

by

#### JIAYI HUANG

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Eun Jung Kim Committee Members, Daniel A. Jiménez

Dilma Da Silva

Jiang Hu

Head of Department, Scott Schaefer

August 2020

Major Subject: Computer Engineering

Copyright 2020 Jiayi Huang

#### **ABSTRACT**

The onset of big data and deep learning applications, mixed with conventional general-purpose programs, have driven computer architecture to embrace heterogeneity with specialization. With the ever-increasing interconnected chip components, future architectures are required to operate under a stricter power budget and process emerging big data applications efficiently. Interconnection network as the communication backbone thus is facing the grand challenges of limited power envelope, data movement and performance scaling. This dissertation provides interconnect solutions that are specialized to application requirements towards power-/energy-efficient and high-performance computing for heterogeneous architectures.

This dissertation examines the challenges of network-on-chip router power-gating techniques for general-purpose workloads to save static power. A voting approach is proposed as an adaptive power-gating policy that considers both local and global traffic status through router voting. In addition, low-latency routing algorithms are designed to guarantee performance in irregular power-gating networks. This holistic solution not only saves power but also avoids performance overhead.

This research also introduces emerging computation paradigms to interconnects for big data applications to mitigate the pressure of data movement. Approximate network-on-chip is proposed to achieve high-throughput communication by means of lossy compression. Then, near-data processing is combined with in-network computing to further improve performance while reducing data movement. The two schemes are general to play as plug-ins for different network topologies and routing algorithms.

To tackle the challenging computational requirements of deep learning workloads, this dissertation investigates the compelling opportunities of communication algorithm-architecture co-design to accelerate distributed deep learning. MultiTree allreduce algorithm is proposed to bond with message scheduling with network topology to achieve faster and contention-free communication. In addition, the interconnect hardware and flow control are also specialized to exploit deep learning communication characteristics and fulfill the algorithm needs, thereby effectively improving

the performance and scalability.

By considering application and algorithm characteristics, this research shows that interconnection networks can be tailored accordingly to improve the power-/energy-efficiency and performance to satisfy heterogeneous computation and communication requirements.

# DEDICATION

To my loving family

To the past, the current and the future

#### **ACKNOWLEDGMENTS**

Without the support of many people, this dissertation would not have been possible. First and foremost, I would like to express my heartfelt gratitude to my advisor, Prof. Eun Jung (EJ) Kim. Since the first day, her continuous encouragement has inspired me to go through the ups and downs along this journey. Her inspiring guidance, generous support and continuous trust has motivated new directions and perspectives in interconnection networks, leading to the success of this research. In addition to her technical expertise, EJ has also offered me advice on my pursuit of career goals, I am truly indebted to her.

Many thanks to my committee members and collaborators. I am thankful to Prof. Ki Hwan Yum for his suggestions and efforts in shaping this research. I am grateful to Prof. Daniel A. Jiménez, Prof. Dilma Da Silva and Prof. Jiang Hu for the insightful feedback and the mentoring they have provided for my research and career development. Daniel has always been an enthusiastic consultant and supporter for my research and career. It has been a great honor to organize the CSE System Seminar with Dilma and Prof. Chia-Che Tsai. The collaboration with Prof. Abdullah Muzahid and Prof. Chia-Che Tsai has been an enjoyable time in the last two years. Thank you. I also thank Greg Diamos, my internship mentor, for introducing me to deep learning for systems research and teaching me the methodology for achieving one's long-term vision.

It would not have been a wonderful graduate life without friends. First, thanks to my HPC research group mates, especially Pritam and Sungkeun who have made my office life very colorful through chit-chat, debates and jokes. Thanks to Kyung Hoon for his encouragement and feedback on my research. I also appreciate the efforts that Ram, Shilpa and Rahul have contributed to this research. Thanks to Di, Mengyuan, Zelun, Jay, Jasmine, Captain, Xinxin, Wangie, and Ocean who have been supporting me since we started graduate studies together. To my bros and sis back home in China, Kow-Leng, Tsong-Tow, Low-Chu, Gem-Fay, Huk-Yen, Sa, Chuanjiang, Zetao and Guanyao, who have always been my listeners and supporters since high school and college.

I am also grateful to the teachers and mentors who have been guiding and supporting me along

my education journey. I am thankful to my junior high teacher Mr. Yanan Wang for teaching me how to take the leadership and responsibilities to lead the team to achieve the goals. Many thanks to my high school teachers Ms. Chuangqun Kuang, Ms. Michelle Xiao and Mr. Jianxin Yang. Ms. Kuang and Ms. Xiao are not only great mentors but also very close friends who have been consistently encouraging me with care and trust since high school.

Last and most importantly, my deepest appreciation to my dearest family. Papa, Mama, my twin brother Jiayue and my sister-in-law Lijuan, as well as my adorable nephew Shuoshuo, whose birth has filled the family with love and joys, thank you all for your unconditional love and support. Without you, this dissertation would not have been possible.

#### CONTRIBUTORS AND FUNDING SOURCES

#### **Contributors**

This work was supported by a dissertation committee consisting of Professors Eun Jung Kim (advisor), Daniel A. Jiménez and Dilma Da Silva of the Department of Computer Science and Engineering, and Professor Jiang Hu of the Department of Electrical and Computer Engineering.

In Chapter 3, the FLOV routing algorithm was derived in part by Ningyuan Wang and the FLOV+ routing algorithm was conducted in part by Shilpa Bhosekar while they were Masters students at Texas A&M University. Part of the results in Chapter 3 was published in 2017 in the proceedings of IEEE International Parallel & Distributed Processing Symposium (IPDPS) [1]. The remaining results of Chapter 3 were submitted to IEEE Transactions on Computers for publication while writing the dissertation. The synthetic simulation results in Chapter 4 were in part collected by Rahul Boyapati while he was a doctoral student at Texas A&M University. The analysis in Chapter 4 was published in the proceedings of International Symposium on Computer Architecture (ISCA-44) in 2017 [2]. The simulation framework used in Chapter 5 was co-developed with Pritam Majumdar, Ramprakash Reddy Puli, and Sungkeun Kim. The results in Chapter 5 were published in 2019 in the proceedings of International Symposium on High Performance Computer Architecture (HPCA-25) [3]. The materials in Chapter 6 were under submission to a conference while writing this dissertation.

All other work conducted for the dissertation was completed by the student independently.

#### **Funding Sources**

Graduate study was supported by Teaching Assistantships from the Department of Computer Science and Engineering, Texas A&M University and research grant CCF-1423433 from National Science Foundation, as well as a Dissertation Fellowship from Texas A&M University Office of Graduate and Professional Studies.

## NOMENCLATURE

NoC Network-on-Chip

VC Virtual Channel

Flit Flow Control Digit

CMP Chip-Multiprocessors

ISA Instruction Set Architecture

FLOV Fly-Over Mechanism

NI Network Interface

MC Memory Controller

FPGA Field-Programmable Gate Array

ASIC Application-Specific Integrated Circuit

SoC System on a Chip or System-on-Chip

APPROX-NOC Approximate Network-on-Chip

AVCL Approximate Value Compute Logic

VAXX Value Approximation Mechanism

HMC Hybrid-Memory Cube

NDP Near-Data Processing

PIM Processing-in-Memory

DNN Deep Neural Network

ART Active-Routing Mechanism

MULTITREE MultiTree All-Reduce Algorithm

# TABLE OF CONTENTS

|     |                                 | Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ge                                                  |

|-----|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| AB  | STR                             | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ii                                                  |

| DE  | DICA                            | ATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | iv                                                  |

| AC. | KNO                             | OWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | v                                                   |

|     |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

| CO  | NTR                             | IBUTORS AND FUNDING SOURCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | vii                                                 |

| NO  | MEN                             | NCLATURE v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | /iii                                                |

| TA] | BLE                             | OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ix                                                  |

| LIS | Т ОЕ                            | F FIGURES x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iii                                                 |

| LIS | Т ОЕ                            | F TABLESxv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | vii                                                 |

| 1.  | INTI                            | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                   |

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | The Problem: Heterogeneous Communication Requirements  1.1.1 Low-Power Interconnect in Dark Silicon  1.1.2 High-Throughput Communication for Big Data Applications  1.1.3 Performance Scaling of Communication for Distributed Deep Learning.  The Solution: Communication Specialization  1.2.1 Low-Power Network-on-Chip for General-Purpose CMP  1.2.2 Disruptive Computing Paradigms for Big Data Movement  1.2.3 Algorithm-Architecture Co-Design for Distributed Deep Learning  Thesis Statement  Contributions  Dissertation Organization | 1<br>2<br>3<br>3<br>4<br>5<br>5<br>5<br>6<br>6<br>8 |

|     | 2.1<br>2.2<br>2.3               | 2.1.2 Routing Algorithm 2.1.3 Flow Control 2.1.4 Router Microarchitecture 2.1.5 Network-on-Chip (NoC) NoC Power Problem and Router Power-Gating in Dark Silicon.                                                                                                                                                                                                                                                                                                                                                                                 | 9<br>10<br>10<br>11<br>12<br>13<br>13               |

|    | 2.4  | Near-Data Processing and In-Network Computing                     | 17  |

|----|------|-------------------------------------------------------------------|-----|

|    | 2.5  | Distributed Deep Learning and All-Reduce Collective Communication |     |

|    |      | 2.5.1 Data-Parallel DNN Training                                  |     |

|    |      | 2.5.2 All-Reduce Operation                                        |     |

|    |      | 2.5.3 All-Reduce Algorithms                                       | 22  |

| 2  | DED  | FORMANCE AWARE NOC DOWER CATING                                   | 2.4 |

| 3. | PEK  | FORMANCE-AWARE NOC POWER-GATING                                   | 24  |

|    | 3.1  | FLOV Router Microarchitecture                                     |     |

|    | 3.2  | Adaptive FLOV Power-Gating Policy                                 | 25  |

|    |      | 3.2.1 Restricted FLOV (R-FLOV)                                    |     |

|    |      | 3.2.2 Generalized FLOV (G-FLOV).                                  |     |

|    |      | 3.2.3 Adaptive FLOV through Router Voting                         |     |

|    | 3.3  | Dynamic Routing Algorithms                                        | 33  |

|    |      | 3.3.1 FLOV Routing Algorithm                                      | 34  |

|    |      | 3.3.2 FLOV+ Routing Algorithm                                     | 36  |

|    | 3.4  | Experimental Evaluation                                           | 40  |

|    |      | 3.4.1 Experimental Methodology                                    | 40  |

|    |      | 3.4.2 Throughput and Power Consumption                            | 42  |

|    |      | 3.4.3 Power-Gating Case Studies                                   | 43  |

|    |      | 3.4.3.1 Performance                                               | 45  |

|    |      | 3.4.3.2 FLOV Routing versus FLOV+ Routing                         | 49  |

|    |      | 3.4.3.3 Power Consumption                                         |     |

|    |      | 3.4.4 Reconfiguration Overhead Analysis                           | 51  |

|    |      | 3.4.5 Real Workload Evaluation                                    |     |

|    |      | 3.4.6 Area Overhead Analysis                                      | 52  |

|    | 3.5  | Summary                                                           | 53  |

| 4. | ۸ DD | PROXIMATE COMMUNICATION FOR HIGH-THROUGHPUT NOC                   | 51  |

| 4. | AFF  | ROAIMATE COMMUNICATION FOR HIGH-THROUGHFUT NOC                    | J4  |

|    | 4.1  | Challenges in NoC Approximate Communication                       |     |

|    | 4.2  | APPROX-NOC Framework                                              |     |

|    |      | 4.2.1 Architectural Overview                                      |     |

|    |      | 4.2.2 Approximation Logic Design                                  |     |

|    | 4.3  | APPROX-NOC Implementation                                         |     |

|    |      | 4.3.1 Frequent-Pattern Mechanism                                  | 60  |

|    |      | 4.3.1.1 FP-VAXX Implementation                                    |     |

|    |      | 4.3.2 Dictionary-Based Mechanism                                  | 61  |

|    |      | 4.3.2.1 DI-VAXX Implementation                                    | 62  |

|    |      | 4.3.3 Latency Overhead                                            | 65  |

|    | 4.4  | Evaluation                                                        | 65  |

|    |      | 4.4.1 Methodology                                                 | 65  |

|    |      | 4.4.2 Results and Analyses                                        | 67  |

|    |      | 4.4.2.1 Performance Analysis                                      | 68  |

|    |      | 4.4.2.2 Throughput Analysis                                       | 71  |

|    |      | 1 1 2 Sansitivity Studies                                         | 72  |

|    |       |        | 4.4.3.1 Error Threshold                               | . 73  |

|----|-------|--------|-------------------------------------------------------|-------|

|    |       |        | 4.4.3.2 Approximable Packets Ratio                    | . 74  |

|    |       | 4.4.4  | Full System Impact Analysis                           | . 74  |

|    |       | 4.4.5  | Power Consumption and Area Overhead                   |       |

|    | 4.5   | Summ   | ary                                                   |       |

| 5. | RED   | OUCINO | G DATA MOVEMENT VIA IN-NETWORK COMPUTING              | . 79  |

|    | 5.1   | Active | -Routing Architecture                                 | . 79  |

|    |       | 5.1.1  | Architectural Overview                                | . 79  |

|    |       |        | 5.1.1.1 Three-Phase Packet Processing                 | . 81  |

|    |       |        | 5.1.1.2 Memory Access Patterns                        | . 83  |

|    | 5.2   | Impler | mentation                                             | . 84  |

|    |       | 5.2.1  | Programming Interface and ISA Extension               | . 84  |

|    |       | 5.2.2  | Network Interface                                     | . 85  |

|    |       | 5.2.3  | Active-Routing Engine                                 | . 86  |

|    |       |        | 5.2.3.1 Packet Processing Unit                        | . 87  |

|    |       |        | 5.2.3.2 Flow Table                                    |       |

|    |       |        | 5.2.3.3 Operand Buffers                               |       |

|    |       |        | 5.2.3.4 ALU                                           |       |

|    |       |        | 5.2.3.5 Putting It All Together                       |       |

|    |       | 5.2.4  | Integrity Considerations                              |       |

|    |       |        | 5.2.4.1 Virtual Memory                                |       |

|    |       |        | 5.2.4.2 Cache Coherence                               |       |

|    |       | 5.2.5  | Enhancements in Active-Routing                        |       |

|    | 5.3   |        | dology                                                |       |

|    |       | 5.3.1  | System Modeling and Configuration                     |       |

|    |       | 5.3.2  | Workloads                                             |       |

|    | 5.4   |        | ation                                                 |       |

|    |       | 5.4.1  | Performance                                           |       |

|    |       | J1     | 5.4.1.1 Speedup                                       |       |

|    |       |        | 5.4.1.2 Update Offloading Roundtrip Latency           |       |

|    |       |        | 5.4.1.3 Data Movement                                 |       |

|    |       | 5.4.2  | Power and Energy                                      |       |

|    |       | S2     | 5.4.2.1 Power Consumption                             |       |

|    |       |        | 5.4.2.2 Energy Consumption                            |       |

|    |       |        | 5.4.2.3 Energy-Delay Product.                         |       |

|    |       | 5.4.3  | Dynamic Offloading: A Case Study                      |       |

|    | 5.5   |        | ary                                                   |       |

|    | A T C |        |                                                       |       |

| 6. |       |        | IM/ARCHITECTURE CO-DESIGN FOR DISTRIBUTED DEEP LEARN- | . 103 |

|    | 6.1   | MultiT | Free All-Reduce Algorithm                             | 103   |

|    | 0.1   | 6.1.1  | MULTITREE Insights                                    |       |

|    |       | 0.1.1  | 6.1.1.1 Why All-Reduce Trees?                         |       |

|    |       |        |                                                       |       |

|    |       |        | 6.1.1.2 Why Topology Awareness?                       | 104 |

|----|-------|--------|-------------------------------------------------------|-----|

|    |       | 6.1.2  | MULTITREE All-Reduce Algorithm                        | 104 |

|    |       |        | 6.1.2.1 Algorithm Description                         | 104 |

|    |       |        | 6.1.2.2 Complexity Analysis                           | 109 |

|    |       |        | 6.1.2.3 Concentrated and Indirect Networks Support    | 109 |

|    |       |        | 6.1.2.4 Bandwidth and Latency Comparisons             |     |

|    |       | 6.1.3  | An Example                                            | 110 |

|    | 6.2   | Archit | ectural Supports                                      | 111 |

|    |       | 6.2.1  | Wide Network Interface for MULTITREE                  |     |

|    |       | 6.2.2  | Message-based Flow Control for Big Gradient Exchanges | 114 |

|    | 6.3   | Metho  | dology                                                |     |

|    |       | 6.3.1  | System Modeling and Configuration                     |     |

|    |       | 6.3.2  | Workloads                                             |     |

|    | 6.4   | Evalua | ation                                                 | 120 |

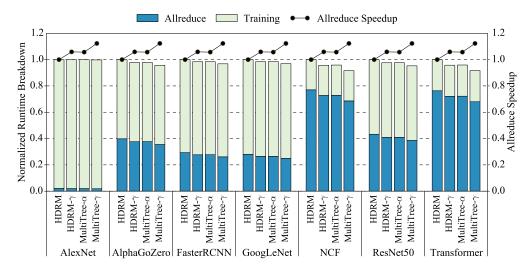

|    |       | 6.4.1  | Performance                                           | 120 |

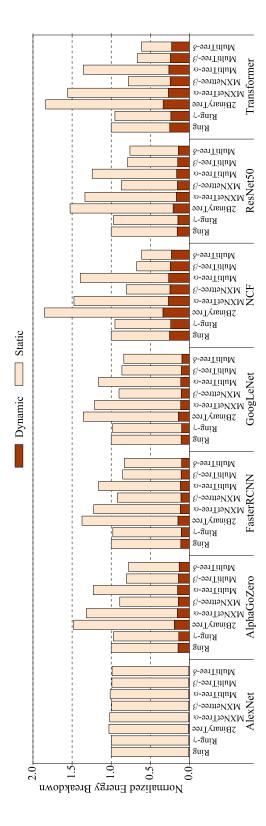

|    |       | 6.4.2  | Energy Consumption                                    |     |

|    |       | 123    |                                                       |     |

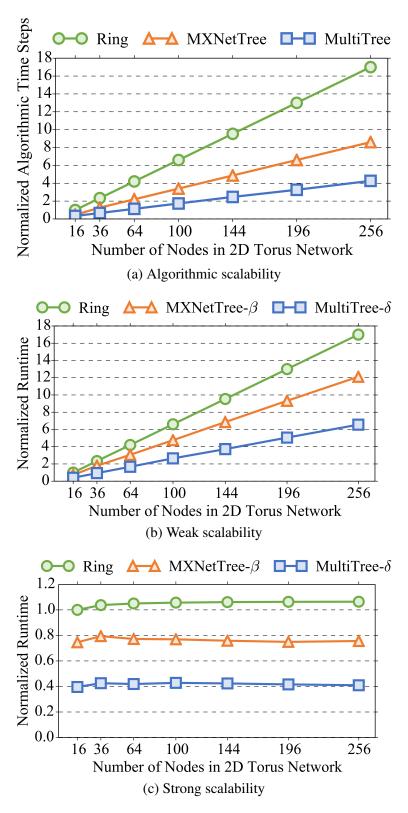

|    |       |        | 6.4.3.1 Algorithmic Scalability                       |     |

|    |       |        | 6.4.3.2 Weak Scalability                              | 124 |

|    |       |        | 6.4.3.3 Strong Scalability                            |     |

|    | 6.5   | Discus | ssions                                                |     |

|    |       | 6.5.1  | Broader Applications                                  | 126 |

|    |       | 6.5.2  | Limitations                                           | 126 |

|    |       | 6.5.3  | Opportunities                                         | 127 |

|    | 6.6   | Summ   | ary                                                   |     |

| 7. | CON   | NCLUS  | IONS                                                  | 128 |

|    | 7.1   | Disser | tation Summary                                        | 128 |

|    | 7.2   | Future | Directions                                            | 130 |

|    |       | 7.2.1  | Approximate Communication                             |     |

|    |       | 7.2.2  | In-Network Computing                                  |     |

|    |       | 7.2.3  | Topology Specialization                               |     |

| RF | EFER1 | ENCES  |                                                       | 133 |

# LIST OF FIGURES

| FIGURI | E                                                                                                                                                                                                                                                                           | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

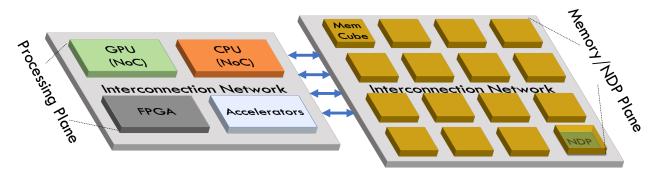

| 1.1    | A heterogeneous system architecture example                                                                                                                                                                                                                                 | 1    |

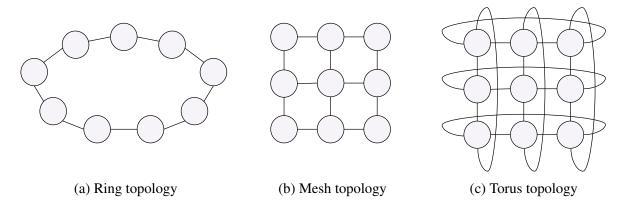

| 2.1    | Three topology examples: ring (a), mesh (b), and torus (c)                                                                                                                                                                                                                  | 9    |

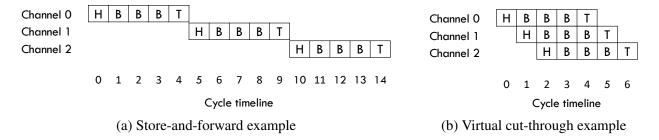

| 2.2    | Flow control examples at low load without contention: store-and-forward flow control (a) and virtual cut-through flow control (b). Figures are redrawn and adapted from examples in [40], where H indicates head flit, B and T stand for body and tail flits, respectively. | 11   |

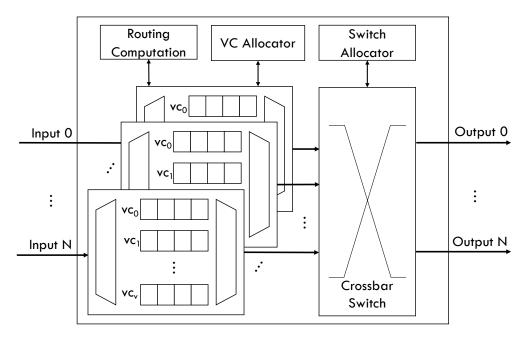

| 2.3    | Virtual-channel router microarchitecture.                                                                                                                                                                                                                                   | 12   |

| 2.4    | Traditional 5-stage router pipeline followed by link traversal                                                                                                                                                                                                              | 13   |

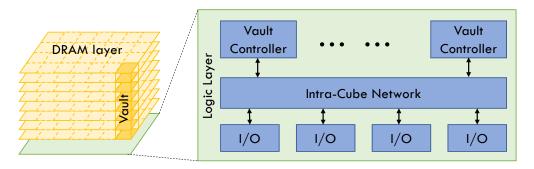

| 2.5    | Hybrid memory cube.                                                                                                                                                                                                                                                         | 17   |

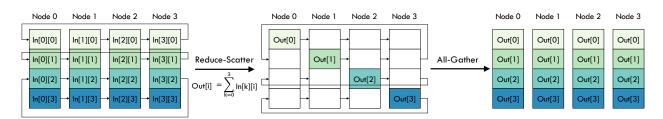

| 2.6    | Reducde-scatter and all-gather in Ring All-Reduce.                                                                                                                                                                                                                          | 21   |

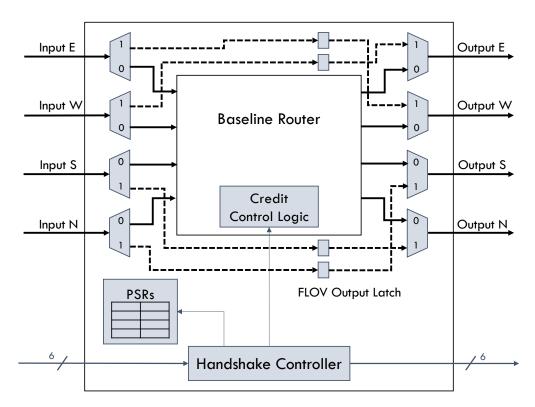

| 3.1    | A block diagram of the FLOV router microarchitecture.                                                                                                                                                                                                                       | 25   |

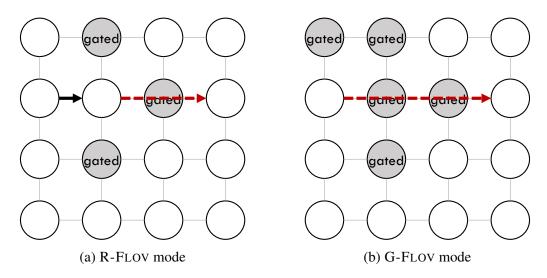

| 3.2    | Examples of R-FLOV (a) and (b) G-FLOV with power-gated routers. The gray 'gated' circle indicates a power-gated router.                                                                                                                                                     | 26   |

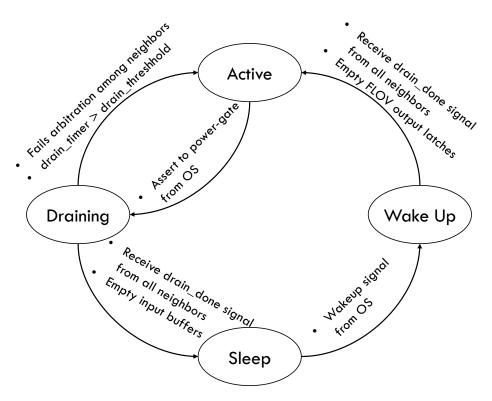

| 3.3    | A state transition diagram for the power status of a router.                                                                                                                                                                                                                | 27   |

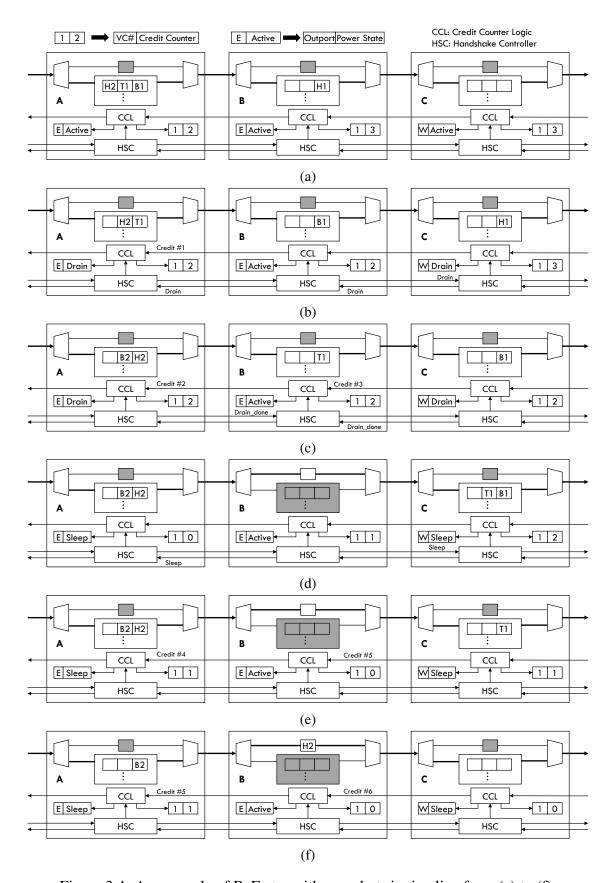

| 3.4    | An example of R-FLOV with snapshots in timeline from (a) to (f)                                                                                                                                                                                                             | 29   |

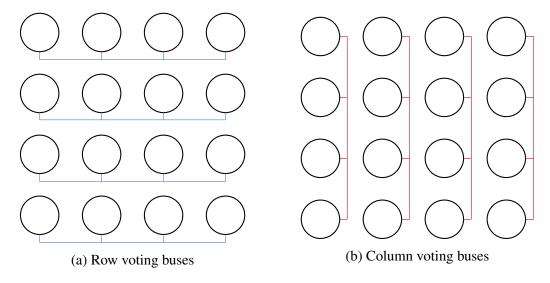

| 3.5    | Two-bit voting buses for rows (a) and columns (b) of adaptive FLOV power-gating policy.                                                                                                                                                                                     | 32   |

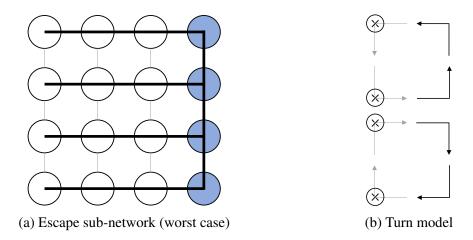

| 3.6    | Worst case of escape sub-network is shown in (a), which uses always-on routers at the last column; and turn model is shown in (b).                                                                                                                                          | 34   |

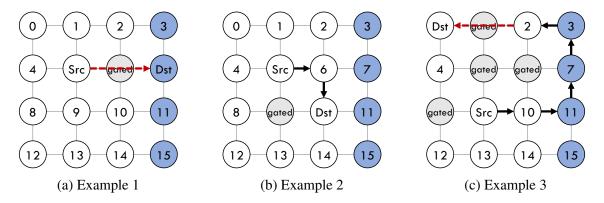

| 3.7    | FLOV routing algorithm examples 1 (a), 2 (b), and 3 (c). The gray 'gated' circles indicate power-gated routers. 'Src' and 'Dst' represent source and destination                                                                                                            | 36   |

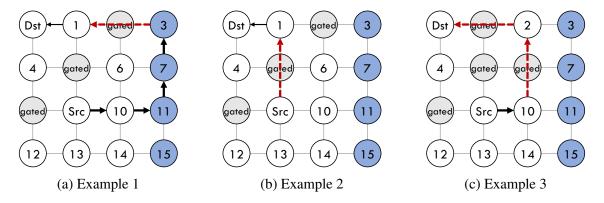

| 3.8    | Routing algorithm examples: example 4 (a) uses FLOV Routing while example 5 (b) and 6 (c) use FLOV+.                                                                                                                                                                        | 39   |

| 3.9  | Load-latency curves (left) and power consumption (right) under uniform random traffic with 50% cores power-gated for $4\times4$ (a), $6\times6$ (b), $8\times8$ (c), and $10\times10$ (d) mesh networks. | 41 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

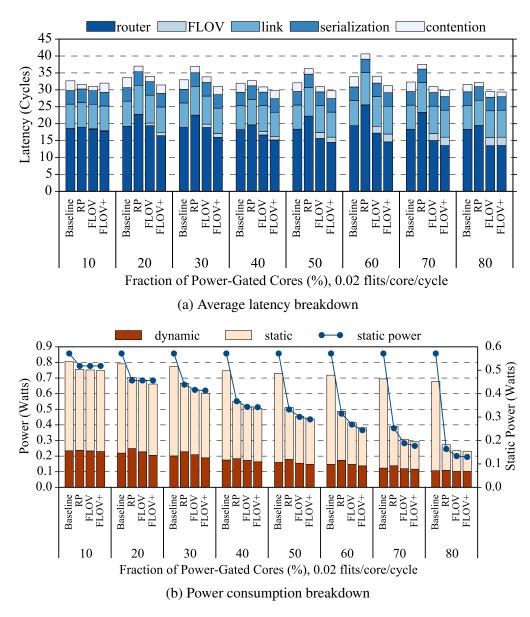

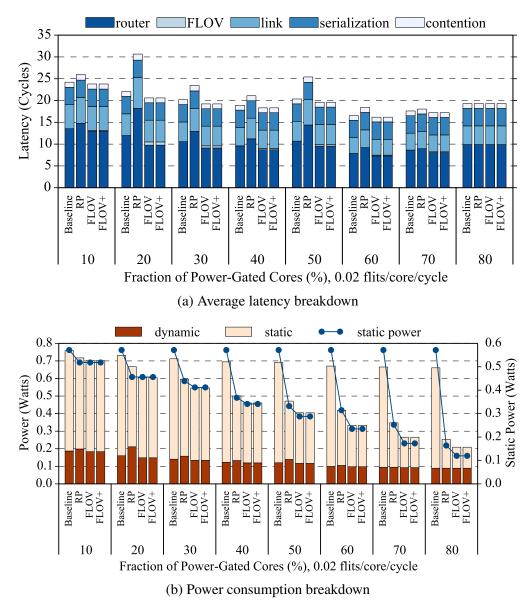

| 3.10 | Average latency breakdown (a) and power comparison breakdown (b) for injection rates of 0.02 flits/node/cycle with Uniform Random traffic pattern                                                        | 44 |

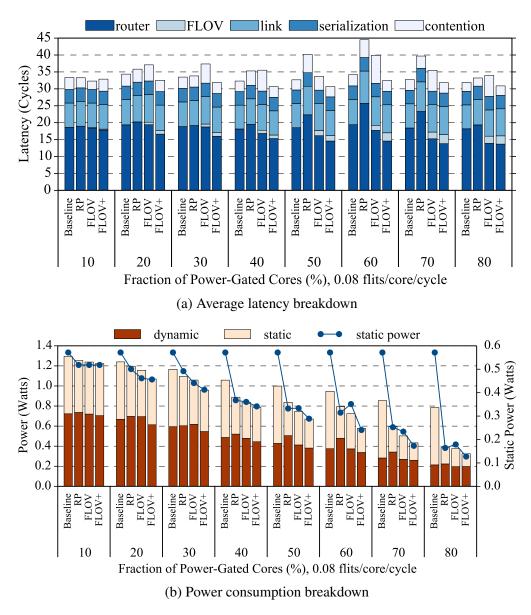

| 3.11 | Average latency breakdown (a) and power comparison breakdown (b) for injection rates of 0.08 flits/node/cycle with Uniform Random traffic pattern                                                        | 45 |

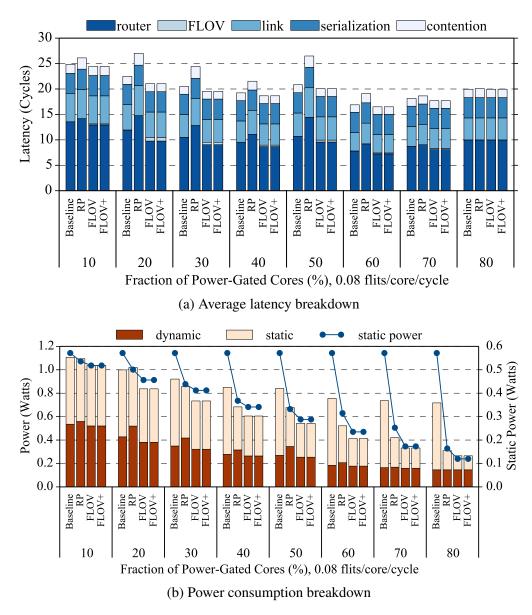

| 3.12 | Average latency breakdown (a) and power comparison breakdown (b) for injection rates of 0.02 flits/node/cycle with Tornado traffic pattern.                                                              | 46 |

| 3.13 | Average latency breakdown (a) and power comparison breakdown (b) for injection rates of 0.08 flits/node/cycle with Tornado traffic pattern.                                                              | 47 |

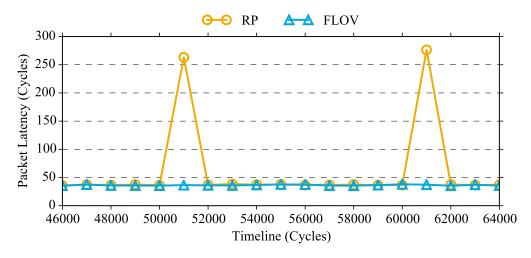

| 3.14 | Reconfiguration overhead of RP and comparison with FLOV                                                                                                                                                  | 50 |

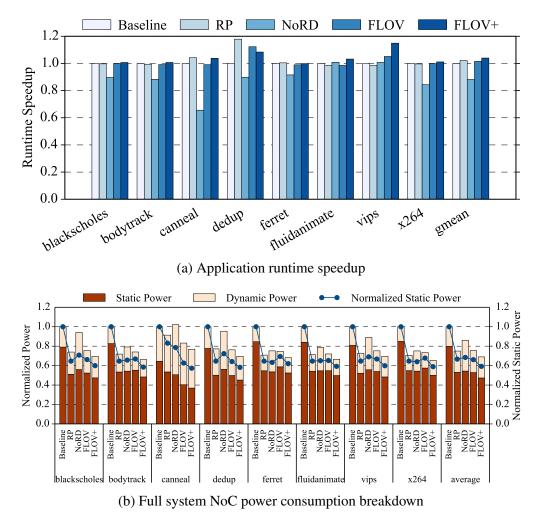

| 3.15 | Full system simulation results: application runtim speedup (a), and normalized NoC power consumption (b) over Baseline.                                                                                  | 50 |

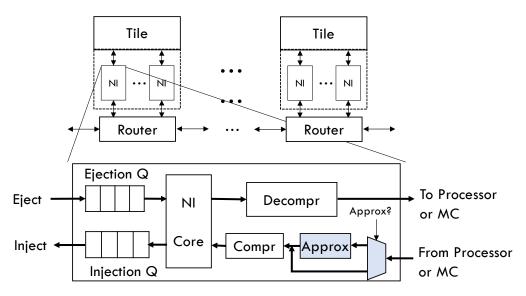

| 4.1  | APPROX-NoC architectural overview.                                                                                                                                                                       | 55 |

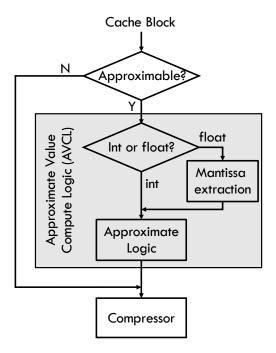

| 4.2  | APPROX-NoC operation flowchart                                                                                                                                                                           | 56 |

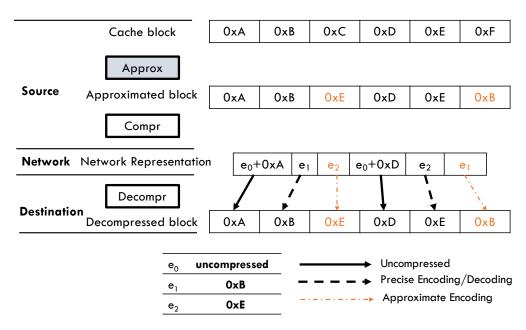

| 4.3  | Compression and decompression of a 6-word cache block                                                                                                                                                    | 57 |

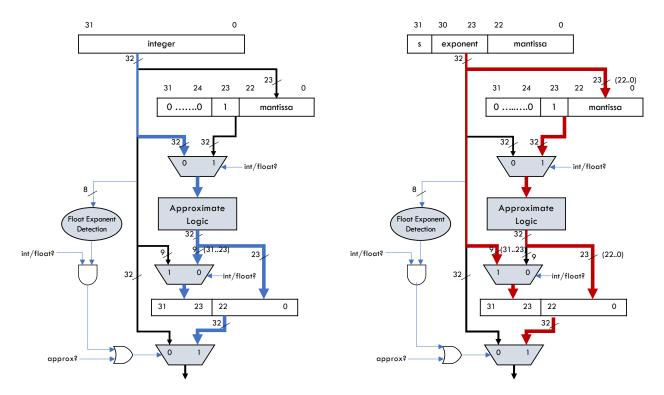

| 4.4  | Approximate value compute logic.                                                                                                                                                                         | 58 |

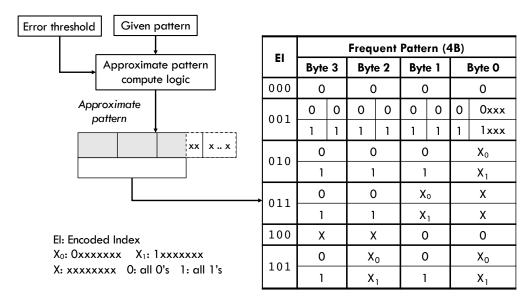

| 4.5  | Frequent pattern compression [134].                                                                                                                                                                      | 60 |

| 4.6  | FP-VAxx microarchitecture.                                                                                                                                                                               | 61 |

| 4.7  | The encoder PMT at Node 3 and the decoder PMT at Node 6                                                                                                                                                  | 63 |

| 4.8  | DI-VAXX microarchitecture.                                                                                                                                                                               | 63 |

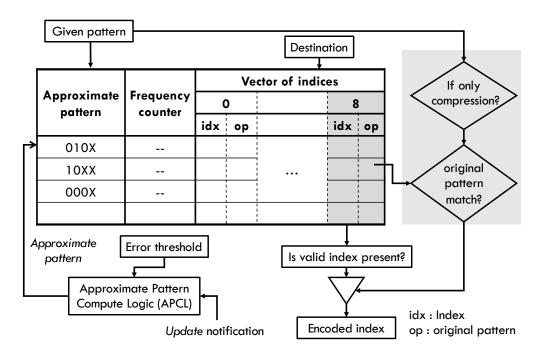

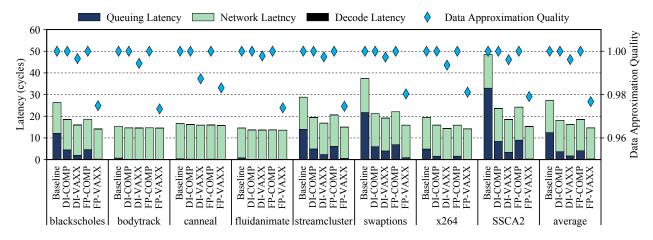

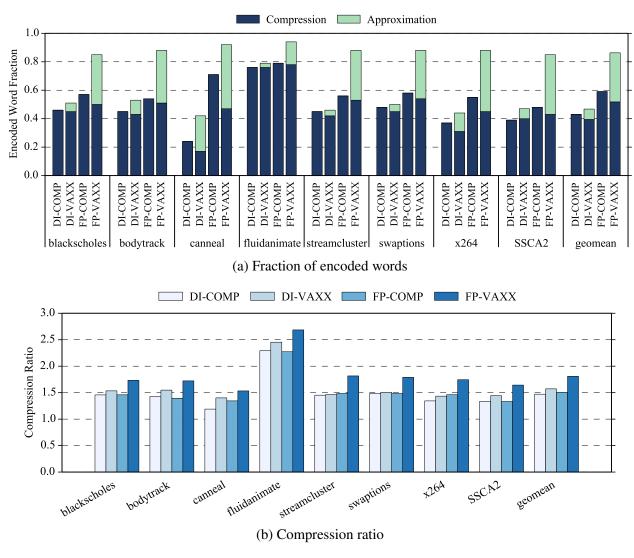

| 4.9  | Average packet latency breakdown and overall approximation quality                                                                                                                                       | 67 |

| 4.10 | Fraction of encoded words breakdown to exact compression and approximation (a) and compression ratio improvement of VAXX (b)                                                                             | 69 |

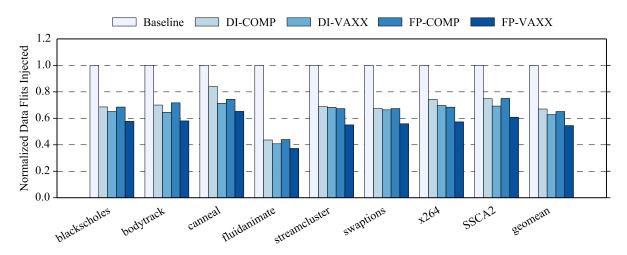

| 4.11 | Reduction in number of injected flits.                                                                                                                                                                   | 69 |

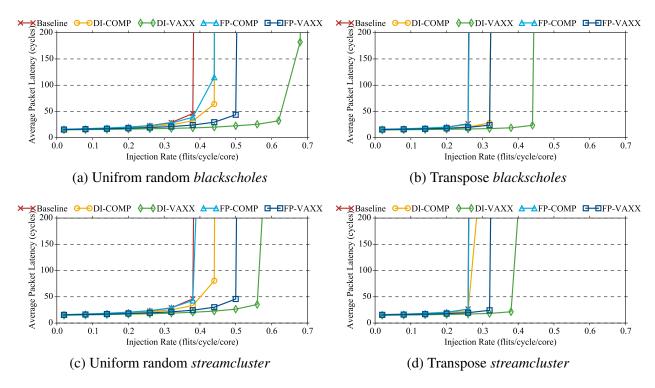

| 4.12 | Throughput analysis with different benchmark data traces under uniform random and transpose traffic patterns                                                                                             | 71 |

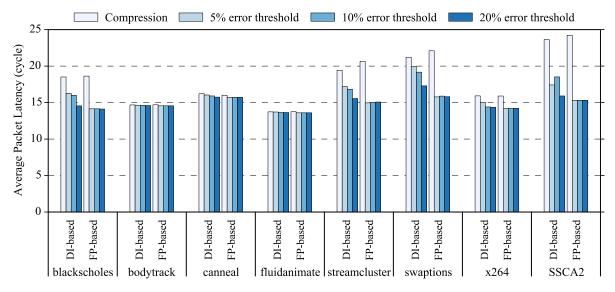

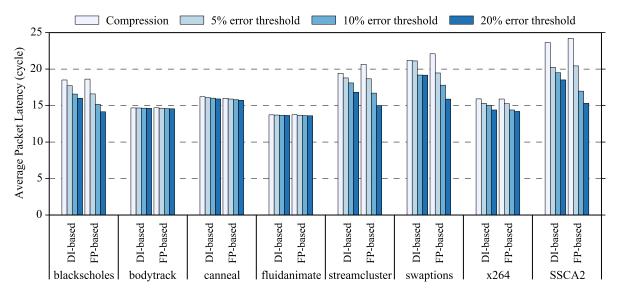

| 4 13 | Error threshold sensitivity analysis                                                                                                                                                                     | 72 |

| 4.14 | Approximable packets ratio sensitivity analysis.                                                                                                                                                                      | 73  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

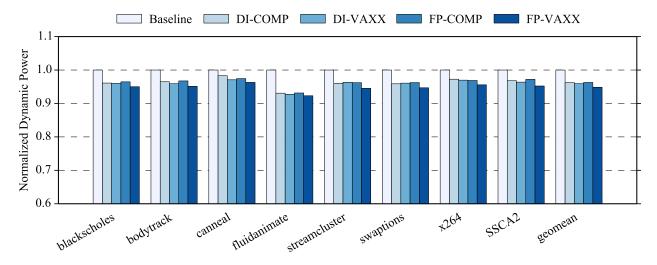

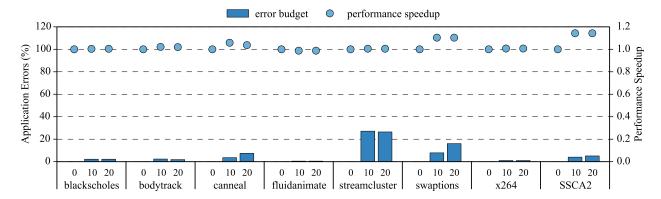

| 4.15 | Dynamic power consumption normalized to Baseline                                                                                                                                                                      | 74  |

| 4.16 | Application output accuracy and normalized performance                                                                                                                                                                | 75  |

| 4.17 | Approximate versus precise output of bodytrack.                                                                                                                                                                       | 76  |

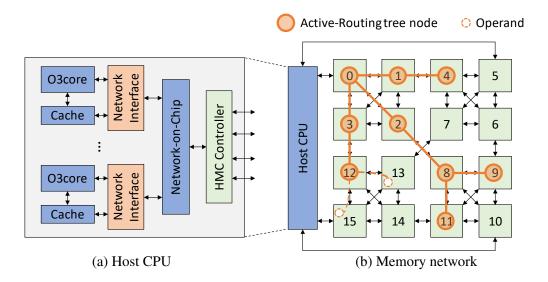

| 5.1  | System configuration with (a) a host CPU connected to (b) a Memory network with an <i>Active-Routing</i> example                                                                                                      | 80  |

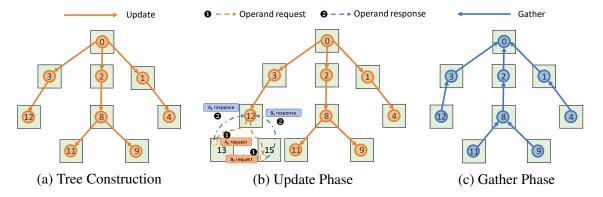

| 5.2  | Active-Routing consists of three phases: (a) Active-Routing Tree Construction on-<br>the-fly; (b) near-data processing in Update Phase; and (c) network aggregation<br>along the Active-Routing Tree in Gather Phase. | 81  |

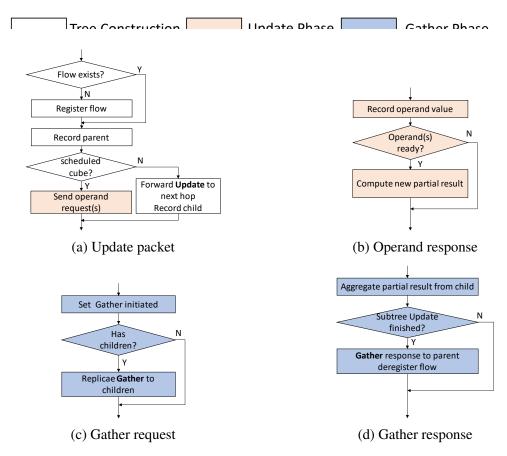

| 5.3  | Active packet processing flow chart for (a) update packet, (b) operand response packet, (c) gather request packet and (d) gather response packet                                                                      | 82  |

| 5.4  | Pseudocode of thread worker for parallel <i>pagerank</i>                                                                                                                                                              | 85  |

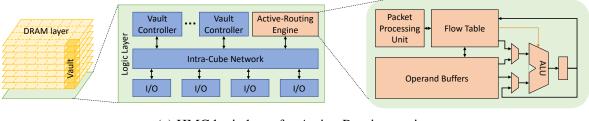

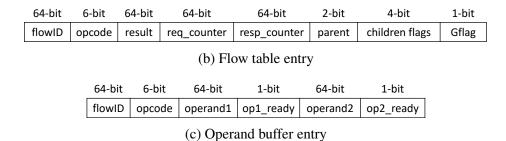

| 5.5  | Active-Routing microarchitecture: (a) engine implementation in HMC logic layer with (b) flow table entry and (c) operand buffer entry.                                                                                | 86  |

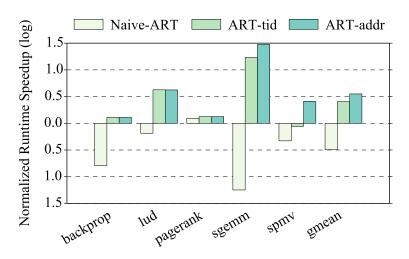

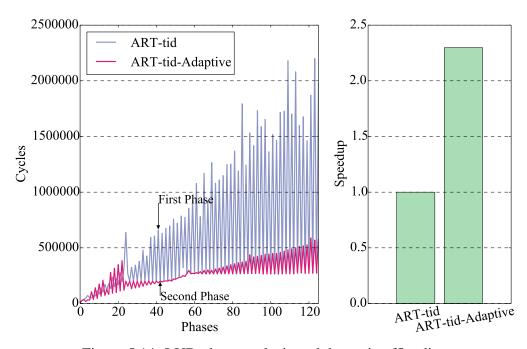

| 5.6  | Runtime speedup of ART variants over HMC Baseline.                                                                                                                                                                    | 90  |

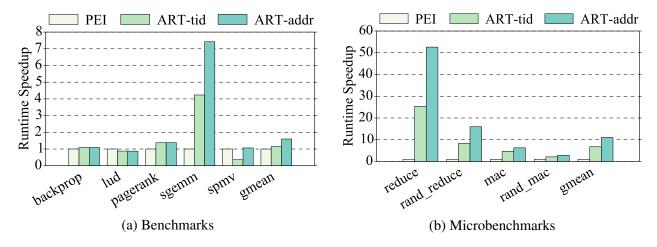

| 5.7  | Runtime speedup over PEI.                                                                                                                                                                                             | 94  |

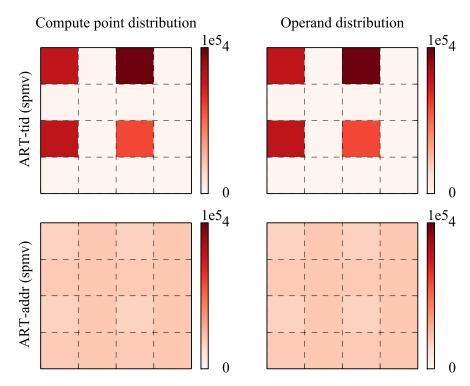

| 5.8  | SPMV compute point and operand distribution.                                                                                                                                                                          | 95  |

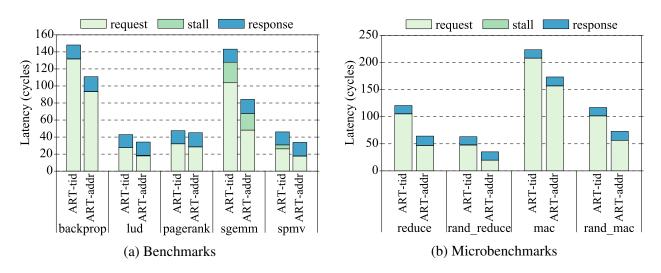

| 5.9  | Update round-trip latency breakdown into request, stall and response latency                                                                                                                                          | 96  |

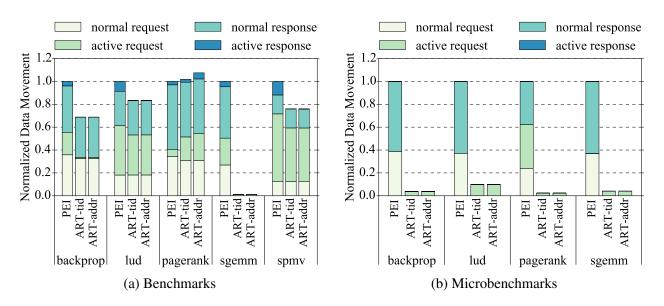

| 5.10 | On/off-chip data movement normalized to PEI.                                                                                                                                                                          | 97  |

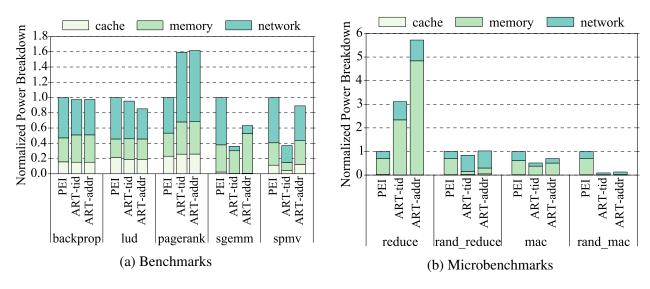

| 5.11 | Normalized power consumption over PEI.                                                                                                                                                                                | 98  |

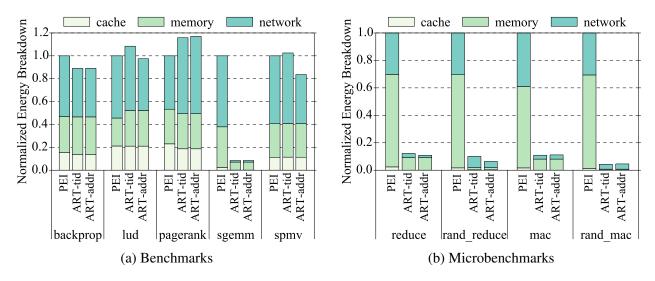

| 5.12 | Normalized energy consumption over PEI.                                                                                                                                                                               | 99  |

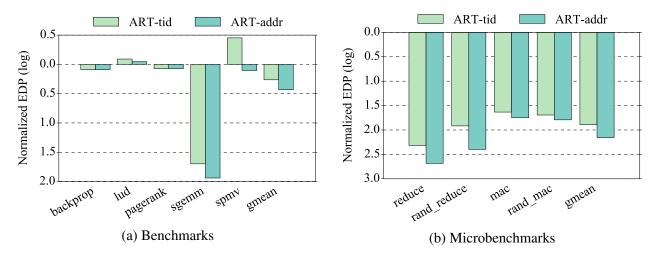

| 5.13 | Logarithmic scale of normalized energy-delay product (EDP) over PEI                                                                                                                                                   | 101 |

| 5.14 | LUD phase analysis and dynamic offloading                                                                                                                                                                             | 102 |

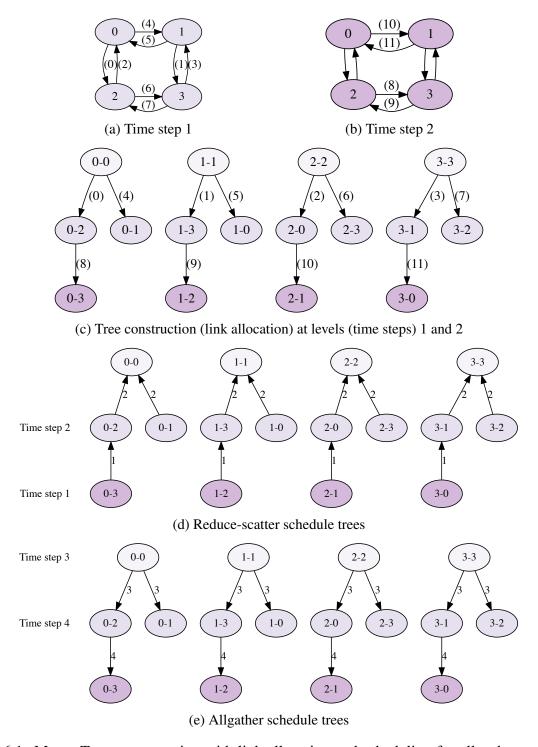

| 0.1  | munication of a $(2\times2)$ mesh network. Node n in tree T is denoted as $(2\times2)$ and label $(1)$ of an edge is the allocation sequence of that link while label t of an edge is the communication time step between the two nodes: link allocation sequence of the topology graph for level 1 (time step 1) (a); when no more links are available for the predecessor levels 0 and 1, a new link topology graph is used for allocation for level 2 (time step 2) (b); the tree construction process indicated by edge labels (c); the constructed reduce-scatter schedule trees (d) and all-gather schedule trees (e). |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

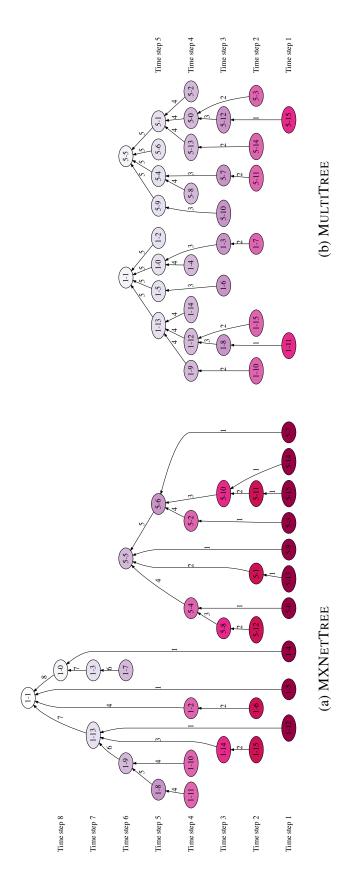

| 6.2  | Reduce-scatter schedules of all-reduce trees 1 and 5 of a $(4\times4)$ 2D-Torus network constructed by MXNETTREE (a) and MULTITREE (b), where a tree node $(T-n)$ indicates accelerator $n$ in tree $T$ and the edge label denotes the scheduled communication time step                                                                                                                                                                                                                                                                                                                                                     |

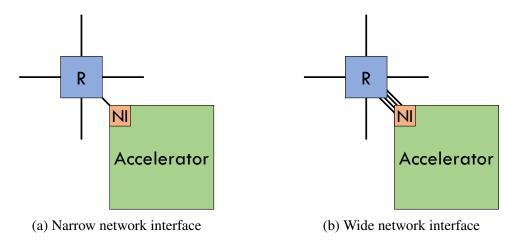

| 6.3  | Conventional narrow network interface (a) and wide network interface dedicated for MULTITREE (b), where R is router and NI is network interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

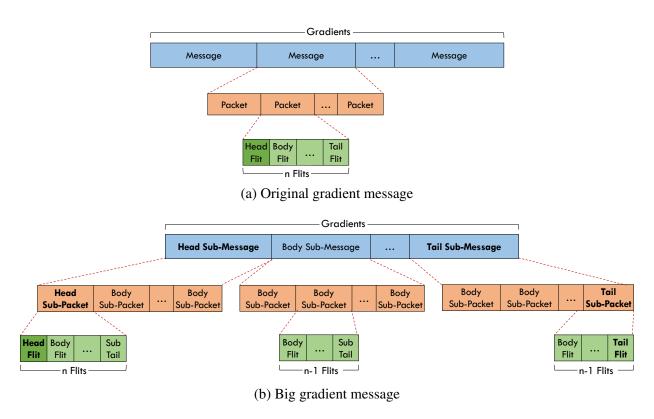

| 6.4  | Original many messages with small packets of gradients (a) and big message with large packet of full gradients (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

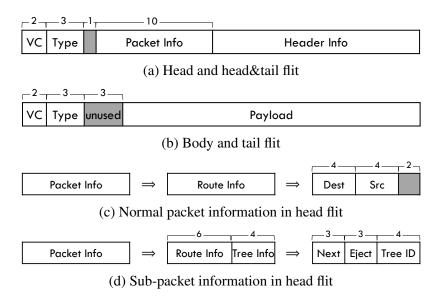

| 6.5  | Flit formatting in a $(4\times4)$ Torus network for head and head&tail flit (a), body and tail flit (b), packet information in head flit for normal packet (c) and sub-packet (d) 113                                                                                                                                                                                                                                                                                                                                                                                                                                        |

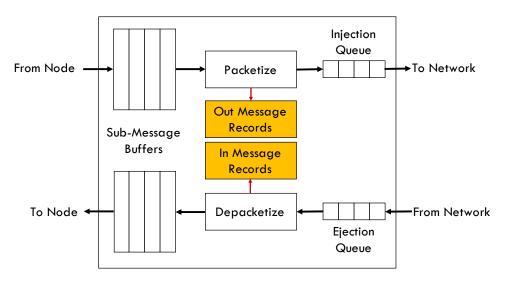

| 6.6  | Augmented network interface for sub-message and sub-packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

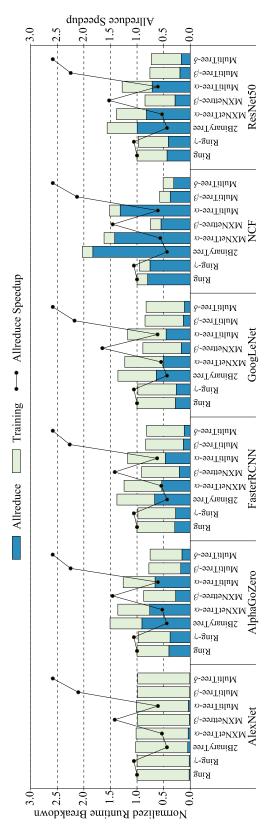

| 6.7  | Runtime breakdown of training and all-reduce (primary) and all-reduce speedup (secondary) normalized to RING in $4\times4$ Torus network ( $\alpha$ : without architectural support, $\beta$ : with wide network interface, $\gamma$ : with message-based flow control, $\delta$ : with both wide network interface and message-based flow control)                                                                                                                                                                                                                                                                          |

| 6.8  | Dynamic and static energy consumption normalized to RING in $4\times4$ Torus network ( $\alpha$ : without architectural support, $\beta$ : with wide network interface, $\gamma$ : with message-based flow control, $\delta$ : with both wide network interface and message-based flow control).                                                                                                                                                                                                                                                                                                                             |

| 6.9  | Runtime breakdown of training and all-reduce (primary) and all-reduce speedup (secodnary) normalized to HDRM in 32-node $4\times8$ BiGraph network ( $\alpha$ : without architectural support, $\gamma$ : with message-based flow control)                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.10 | Algorithmic scalability (a), weak scalability with fixed per node 375 KB model size (b) and strong scalability with fixed problem size of 32 MB model size (c) normalized to 16-node performance of RING ( $\beta$ : with wide network interface, $\delta$ : with both wide network interface and message-based flow control)                                                                                                                                                                                                                                                                                                |

# LIST OF TABLES

| Page | 3                                      | TABLE |

|------|----------------------------------------|-------|

| 40   | FLOV System Configuration              | 3.1   |

| 66   | APPROX-NOC System Configuration        | 4.1   |

| 92   | Active-Routing System Configuration    | 5.1   |

| 93   | Workloads                              | 5.2   |

| 114  | Packet and Flit Types                  | 6.1   |

| 117  | MULTITREE System Configuration         | 6.2   |

| 118  | Baselines and MultiTree Configurations | 6.3   |

#### 1. INTRODUCTION

The physics limitations of semiconductor technology and grand computational requirements of emerging applications have inspired computer architecture to evolve to heterogeneous systems as shown in Figure 1.1, embracing general-purpose CPUs, specialized accelerators and disruptive computation paradigms such as approximation and near-data processing (NDP). On the one hand, such a system needs to operate under a stricter power budget due to the end of Dennard Scaling [4] and diminution of Moore's Law [5]. On the other hand, the onset of big data and deep learning applications urge future architectures to process humongous data efficiently. With the ever-increasing interconnected chip components, interconnection networks as the communication backbone is facing the enormous challenges of limited power envelope, data movement and performance scaling issues. Thus, it is demanding to design efficient interconnect solutions to tackle these multifaceted challenges for future heterogeneous architectures.

## 1.1 The Problem: Heterogeneous Communication Requirements

The mixture of general-purpose workloads and emerging big data applications running on heterogeneous architectures show distinct characteristics. General-purpose programs exploit data locality and deep cache hierarchy with very low average communication rate, overusing power for light traffics. In contrast, big data applications, such as graph processing and machine learning, have large memory footprint with low data reuse rate and requires tremendous communication

Figure 1.1: A heterogeneous system architecture example.

bandwidth to fulfill the substantial data movement demands. Furthermore, the immense advances in distributed deep learning show long-lasting communication data streams, which is very dissimilar to random short messages in conventional workloads. These diverse characteristics show heterogeneous communication requirements and reveal different inefficiency in terms of power utilization, data movement, and performance scaling on the current interconnect solutions.

#### 1.1.1 Low-Power Interconnect in Dark Silicon

Scalable networks-on-chip (NoCs) have become the *de fecto* interconnection mechanism in large-scale chip multiprocessors (CMPs). Not only are NoCs devouring a large fraction of the on-chip power budget, but static NoC power consumption is becoming the dominant component as technology scales down. General-purpose programs running on CMPs typically have low communication traffics [6], making the standby leakage a waste of the power envelop. Therefore, it is essential to reduce static NoC power consumption for power-efficiency in dark silicon. Power-Gating as an effective static power saving technique can be used to power off inactive routers. However, packet deliveries in irregular power-gated networks suffer from detour or waiting time overhead to either route around or wake up power-gated routers. Previous research has proposed to power-gate routers attached to inactive cores in a centralized manner [7], leading to high overhead for network reconfiguration. Other research has introduced a bypass ring network to route packets even in disconnected power-gated networks [8]. However, it can introduce long latency with too many detours. In addition, they either make power-gating decision depending on the local traffic or the average global traffic, thereby either losing the big picture of the whole network or missing details of independent routers. As a consequence, they introduce performance overhead and has limited power saving. Thus, it is essential to provide a solution that captures both global and local status for power-gating decision, meanwhile achieving more power saving and low-latency packet deliveries.

## 1.1.2 High-Throughput Communication for Big Data Applications

The explosion of data availability and the demand for faster data analysis have led to the emergence of applications exhibiting large memory footprint and low data reuse rate. These workloads, ranging from graph processing to neural networks [9, 10], require significant data movement throughout the memory hierarchy, posing heavy stress on the communication fabrics. Furthermore, due to the gap between dense CPU computation power and deficient data supply, computer systems fail to achieve their peak computational capability. Therefore, architectural innovations are imperative to reduce data movement for substantial improvements in terms of system performance as well as energy efficiency. Prior research has adopted compression in network-on-chip to increase the throughput for communication [11, 12, 13]. However, these compression techniques are not adequate to provide the demanding throughput for big data. Other work has proposed various techniques to reduce data movement with near-data processing by moving computation near data-resident locations. In-place computation in cache uses bit-line SRAM circuit technology to transform existing cache elements to active very large vector computational units, avoiding moving data between different levels in the cache hierarchy [14, 15, 16, 17]. Processing-in-memory (PIM) has also enabled computation in the memory for data processing [18, 19, 20, 21, 22]. Although effectively reducing data movement, these approaches miss the opportunity of in-network optimization for further improvement. Thus, network level optimizations are needed to reduce data movement during communication.

#### 1.1.3 Performance Scaling of Communication for Distributed Deep Learning

With the movement of artificial intelligence, deep learning has been transforming the land-scape of computing from applications to hardware. The onset of big data era and rapid advances of accelerator architectures have enabled deep neural networks (DNNs) to achieve superhuman accuracy on complex real-world problems [10, 23, 24, 25, 26]. State-of-the-art DNN models have tens to hundreds of millions of parameters, requiring billions of compute operations and hundreds of megabytes of storage and bandwidth. Recent work projects that orders of magnitude growth

of dataset and model size are required to exceed human-level accuracy, which will take weeks to train a single epoch for language modeling [27]. As data keep exploding and DNNs evolve to be larger and deeper, it is crucial to provide scalable solutions to fulfill the trend in grand computing requirements. To this end, accelerator pod with hundreds to thousands of processors have been deployed to train these giant DNNs in a parallel and distributed manner [28, 29, 30]. During the iterative distributed training, all-reduce communication is frequently invoked for gradients synchronization, dominating the communication time and stalling the computations of the next training epoch. Widely used all-reduce algorithms either suffer from contention or long latency, resulting in resource under utilization [31, 32, 33]. Although communication algorithms are optimized in theory, they lack hardware support for coordination and communication scheduling, and thus, miss potential optimization opportunity to further improve performance. Furthermore, the fine-grained flow control and arbitration designed for general purpose network can be inefficient to support such large gradient exchanges, resulting in poor performance and huge energy/power overhead. Comparing to the significant investment in computation acceleration, little attention has been paid to communication, which can quickly become a bottleneck for large-scale distributed training.

#### 1.2 The Solution: Communication Specialization

Along the wave of heterogeneous computing, specialization has been broadly practiced in computation acceleration tailored to various applications, such as CPU for general-purpose programs, GPU for graphics and TPU for deep learning. In contrast, specialized communication has not been widely investigated. With the divergent application domains and their heterogeneous communication requirements, the one-for-all interconnect solution is no longer efficient for their multifaceted characteristics. To keep up with the improvement of computation efficiency, communication specialization is urgently needed to tackle the challenges of power-/energy-efficiency, data movement and performance scaling accordingly. Thus, this dissertation proposes four specialized interonnect solutions for these problems as an attempt towards efficient communication in terms of power/energy and performance.

## 1.2.1 Low-Power Network-on-Chip for General-Purpose CMP

In general, since general-purpose programs have average light traffic loads, NoC static power consumption is a large waste of the total on-chip power budget. Static power consumption for the chip is also increasing drastically, while the feature size becomes smaller and the operating voltage gets closer to the near-threshold level [34]. Therefore, it is highly desirable to achieve power-efficient NoC designs for future CMPs. This dissertation proposes *Fly-Over* (FLOV), a voting approach for adaptive router power-gating, targeting for low-power NoCs for general-purpose CMPs. The adaptive power-gating policy works in synergy with low-latency routing algorithms in the irregular power-gating network. Such a holistic solution not only saves power but also avoids performance overhead.

#### 1.2.2 Disruptive Computing Paradigms for Big Data Movement

Data movement has posed significant pressure on the communication backbone of modern processors due to the emergence of big data applications. Thus, it is crucial to provide communication solutions that can move data efficiently. Many of these applications, such as machine learning, image/video processing and pattern recognition have approximation in nature in their algorithm designs for either faster convergence or result estimations [35, 36, 37]. These workloads also have compute kernels that operate reduction over myriads of data. Therefore, this research exploits the error tolerance of these applications and proposes APPROX-NOC for approximate communication with lossy compression to improve the data content locality for higher compression rate, effectively improving communication throughput. In addition, by leveraging near-data processing, this dissertation proposes *Active-Routing*, an in-network computing architecture that maps compute kernels to the memory network for data-flow style processing, further reducing data movement compared to state-of-the-art processing-in-memory approach.

#### 1.2.3 Algorithm-Architecture Co-Design for Distributed Deep Learning

Large-scale distributed deep learning training has enabled developments of more complex deep neural network models to learn from larger datasets for sophisticated tasks. In particular, distributed stochastic gradient descent intensively invokes all-reduce operation for gradient update, which dominates communication time during iterative training epochs. As computations are significantly accelerated through specialization, communication can soon become the bottleneck in distributed deep learning. To tackle this problem, this dissertation proposes MULTITREE All-Reduce algorithm and co-designs the architecture to satisfy algorithmic requirements. The algorithm takes topology and resource utilization into account for efficient and scalable all-reduce scheduling. Moreover, the interconnection network is specialized with heterogeneous bandwidth provisioning of injection/ejection and network channels in addition to flow control to cope with the algorithm in synergy.

#### 1.3 Thesis Statement

Specializing interconnection networks tailored to heterogeneous architectures and workloads is an effective approach to achieve power-/energy-efficient, high-throughput and accelerated communication.

#### 1.4 Contributions

This dissertation addresses the grand challenges of power-/energy-efficiency, data movement and performance scaling issues of communication in heterogeneous architectures using interconnect specialization. The main contributions of this research are the following.

- This research increases the understanding of the key factors that affect power saving and performance effects in designing router power-gating policy. The proposed routing algorithm achieves best-effort minimal route to avoid performance degradation. The proposed FLOV voting approach is well balance in the knowledge of local and global traffic status for adaptive power-gating decisions to achieve more static power saving while guaranteeing network throughput. This voting policy can be applied to other distributed power-gating schemes for performance-aware power optimizations.

- This research is the first study that introduce approximate computing to networks-on-chip for high-throughput communication provisioning. The proposed APPROX-NOC exploits

approximate data similarity in communication and translates it to high compression rate to reduce traffic loads in NoCs. Its approximate engine implements fast approximation logic that guarantees error tolerance within budget, making it suitable to work synergistically with other computation and memory approximation techniques in the same system. Furthermore, the proposed approximation module can be used in a plug-and-play fashion with any underlying data compression mechanisms.

- This research examines the first in-network computing idea in near-data processing to minimize the data movement in emerging memory networks. The proposed *Active-Routing* architecture maps compute kernels to the memory network for data-flow style processing by exploiting the pattern of aggregation over intermediate results of arithmetic operators. It seeks to schedule computations at routers attached to memory so as to take advantage of the massive bandwidth and parallelism in memory. Meanwhile, it dynamically builds topology-oblivious Active-Routing trees and leverages the network concurrency to optimize reduction operations along the routing path. This research demonstrates the promising potential for in-network computing with data-flow processing.

- This research is among the first studies that co-designing algorithm and architecture to accelerate communication for large-scale distributed deep learning. This work identifies the inefficiency in recent all-reduce algorithms and the opportunity of communication algorithm-architecture co-design. The proposed MULTITREE All-Reduce algorithm couples tree construction and communication scheduling, with topology and global link utilization awareness, to efficiently coordinate concurrent tree communications. The co-designed interconnection network is specialized to satisfy the fan-in/out of trees in the algorithm. In addition, the large size of gradients in deep learning is exploited by a simplified flow control and arbitration for better effective bandwidth utilization. This research is the first work to exploit characteristics of large-scale deep learning for communication acceleration.

## 1.5 Dissertation Organization

The rest of the dissertation is organized as follows. Chapter 2 introduces the fundamental concepts in interconnection network and network-on-chip (NoC) to lay down a foundation for the discussion of this research, and survey the literature of related work. Chapter 3 presents the voting-based adaptive NoC power-gating policy and its routing algorithm, designed for general-purpose CMPs. To minimize data movements for big data applications, Chapters 4 and 5 present two specialized interconnect solutions, approximate communication and in-network computing, respectively. Chapter 6 co-designs communication algorithm-architecture to accelerate communication for large-scale distributed deep learning. Finally, Chapter 7 concludes this dissertation with a discussion of the future research directions.

#### BACKGROUND AND LITERATURE SURVEY

This chapter presents the fundamental concepts of interconnection networks to facilitate the discussions of this dissertation with a literature review of the related work in the areas of low-power networks-on-chip, approximate computing, near-data processing, distributed deep learning and all-reduce collective communication, respectively.

#### 2.1 Interconnection Network Basics

An interconnection network consists of router nodes and link channels as a communication fabric for interconnecting multi nodes in a system or multicores in in chip multiprocessors (CMPs). The construction of an interconnection network includes its network topology, routing algorithm, flow control protocol and router microarchitecture implementation. The important performance metrics for interconnection network evaluation is latency and throughput. Latency, or average packet latency defines the average time for sending a packet from one node to another while throughput defines the maximum traffic load the network can sustain for a traffic pattern before indefinite queuing or congestion happens at the end node.

Figure 2.1: Three topology examples: ring (a), mesh (b), and torus (c).

## 2.1.1 Topology

Network topology defines the connections between the router nodes and provides the possible paths between the nodes. Topology also determines how well the contention can be handled on various traffic patterns. Figure 2.1 shows three widely used topologies. The ring network shown in Figure 2.1a has minimum path diversity and hence has limited network throughput and high latency for most of the traffic patterns. Figure 2.1b shows a mesh network topology that has more choices at each node compared to ring, thereby improving performance. In Figure 2.1c, a torus network is showed to have lower network diameter and more path diversity than both ring and mesh. So it can deal with contention better to achieve lower latency and higher throughput.

## 2.1.2 Routing Algorithm

Given a network topology, an important factor that affects the performance is the routing algorithm that determines the packet traversal path(s) between two nodes. In general, there are two classes of routing algorithms, deterministic and adaptive routing. Deterministic routing algorithms are simpler to implement in hardware while limiting to a single choice for routing between two nodes. In contrast, adaptive routing has more path diversity for routing packets, thereby tending to have higher network throughput. One of the important issues needs to be handled in routing design is deadlock, where packets in the network are holding resources and waiting for resources held by others in a circular way indefinitely. Two classic mechanisms for deadlock handling are deadlock recovery [38] and deadlock avoidance [39]. In deadlock recovery, routing deadlocks are identified by detection techniques, then escape resources are provided to the deadlocked packet, therefore, circular dependence is mitigated to break the deadlock. A common deadlock detection technique is timeout mechanism to detect *possible* deadlock in the network. In deadlock avoidance mechanism, deadlock can be avoided by always providing choice from the a deadlock-free escape routing subfunction. So a packet can always go to the deadlock-free escape path when it is blocked.

Figure 2.2: Flow control examples at low load without contention: store-and-forward flow control (a) and virtual cut-through flow control (b). Figures are redrawn and adapted from examples in [40], where H indicates head flit, B and T stand for body and tail flits, respectively.

#### 2.1.3 Flow Control

Flow control manages how the resources, including buffers and links, are used by the packets along the route. The smallest unit that recognized by flow control methods is *flit control digit (flit)*. So, a packet usually consists of one or more flits. Since buffered routers are considered in this dissertation, we focus on buffer-based flow control. In packet-switching networks, a router needs to make sure downstream buffer availability before sending the packet. The reserved buffer lane can only be used by the reserving packet before it receives the last flit of the packet, which releases the reservation. Well-known packet-buffer flow control methods are store-and-forward and virtual cutthrough. In store-and-forward, as the name suggests, the whole packet is received and stored before being forwarded to the next hop. And before sending packets, buffer space for the whole packet should be reserved in next hop. However, even when the buffers in the next hop are available, flits have been received are holding unnecessarily the buffers while waiting for the remaining flits for the same packet, as shown in Figure 2.2a. In virtual cut-through switching, received flits can start transmission as long as the buffer for the whole packet has been reserved in the next hop [41]. Figure 2.2b shows the timeline diagram for packet transmission using virtual cut-through flow control at low traffic load. Virtual cut-through make it possible to send flit earlier and recycles flit buffers faster, thus improving network latency and throughput. Wormhole flow control, a flit-buffer based method, relaxes the restriction on buffer reservation, where flits can be transmitted as long as there is a free flit buffer in the reserved lane [42]. Therefore, wormhole flow control can reduce the

Figure 2.3: Virtual-channel router microarchitecture.

buffer requirements even with buffer size smaller than packet size. Virtual-Channel flow control, a more advanced flit-buffer based technique, associates multiple virtual channels (flit buffer lanes) with the same physical channel. Therefore, it remove the head-of-line blocking issue and increases the physical channel bandwidth utilization, thereafter improving network throughput.

#### 2.1.4 Router Microarchitecture

Router microarchitecture is the implementation of a router switch. Figure 2.3 shows a typical virtual-channel router microarchitecture. The datapath includes the input virtual channels (VCs) and a switch crossbar switch connecting the input VC to the output ports. The incoming flits are stored in the input VC, and the routing computation unit computes the route and assigns the output port in packet basis. Then the VC allocator assigns the packet an output VC, which is associated with the downstream input VC. When the buffer resources are allocated, the switch allocator assigns the switch time in flit basis by configuring the connection of the crossbar to setup the datapath. In general, router traversals are pipelined to increase the clock frequency. Figure 2.4 shows a traditional router with five pipeline stages followed by link traversal, including buffer

| Head Flit         | Buffer Write | Routing<br>Computation | VC Allocation | Switch<br>Allocation | Switch<br>Traversal  | Link Traversal      |                |

|-------------------|--------------|------------------------|---------------|----------------------|----------------------|---------------------|----------------|

| Body or Tail Flit |              | Buffer Write           |               |                      | Switch<br>Allocation | Switch<br>Traversal | Link Traversal |

Figure 2.4: Traditional 5-stage router pipeline followed by link traversal.

write (BW), routing computation (RC), VC allocation (VC), switch allocation (VA), and switch traversal (ST). Only the head flit experiences all the stages while remaining flits skip the RC and VA stages because output port and VC have been determined in packet basis. Lookahead routing and speculation of VA and SA can be performed to reduce the executed pipeline stages [43]. If misspeculation happens, the flit falls back to the normal pipeline.

#### 2.1.5 Network-on-Chip (NoC)

Network-on-Chip (NoCs) are on-chip interconnection networks in silicon that interconnect execution cores, slices of cache, memory and IO controllers. The design specifications of NoCs are more constrained in terms of power and area compared to its off-chip counterpart. Therefore, flit-buffer flow control is used so that buffer depth can be less than a packet size to reduce both area and power consumption. In terms of performance, link latency is the dominant component in off-chip network while router latency becomes the major portion for NoCs due to the on-chip fast wire signaling. In consequence, router latency is critical to the performance in NoCs. Therefore, speculation and pipeline are mostly applied to router datapath to reduce the latency.

#### 2.2 NoC Power Problem and Router Power-Gating in Dark Silicon

Scalable Networks-on-chip (NoCs) such as 2D meshes, are *de facto* communication fabrics in these large CMPs. Studies show that NoCs consume a significant portion, ranging from 10% to 36%, of the total on-chip power [44, 45, 46]. Therefore, it is highly desirable to achieve power-efficient NoC designs for future CMPs. Static power consumption for the chip is also increasing drastically, while the feature size becomes smaller and the operating voltage gets closer to the near-threshold level. Previous studies show that the percentage of static power in the total NoC

power consumption increases from 17.9% at 65nm, to 35.4% at 45nm, to 47.7% at 32nm and to 74% at 22nm [47, 48]. Based on this trend, as we reach towards sub-10nm feature sizes, static power can become the major portion in NoC power consumption. Power-gating is an effective circuit technique to mitigate the worsening impact of on-chip static power consumption by cutting off supply current to idle chip components. Prior research has applied power-gating to NoCs for static power saving. In the rest of this subsection, we review the previous research related to power and performance issues of NoC power-gating.

Fine-grained Interconnect Power-Gating. Significant research has applied power-gating techniques in NoCs [49, 50]. Several fine-grained interconnect component power-gating techniques were proposed [51, 52, 53, 54]. Kim et al. introduced a dynamic link shutdown (DLS) technique together with dynamic voltage scaling to save link energy [55]. Soteriou et al. presented a power-aware network that reduces static power consumption by monitoring the link utilization and power-gating the underutilized links [51]. Matsutani et al. applied the power-gating technique to control the power supply of different components individually in an ultra fine-grained way [52]. Kim et al. proposed a buffer organization to adaptively adjust active buffer size by power-gating [53]. Parikh et al. introduced power-aware routing and topology reconfiguration to minimize detours while selected components in routers are power-gated [54]. These approaches work well to reduce the static power consumption, however, they only power-gate certain components (e.g. input buffer) of a router and requires additional circuits.

Coarse-grained NoC Router Power-Gating. Coarse-grained router power-gating has been broadly studied as well. In [56], lookahead routing is utilized to wake up sleeping routers two hops in advance to hide the wakeup latency. However, as clock frequency increases, wake up latency cannot be totally hidden. Chen et al. introduced Power Punch, a non-blocking power-gating scheme that wakes up powered-off routers along the path of a packet in advance, thereby preventing the packet from suffering router wakeup latency [57]. Zhan et al. presented a mechanism that can activate powered down cores for performance gains while considering thermal aware floor planning, and they also explored topological/routing support [58]. Catnap power-gates physical