# MEMRISTOR ENGINEERING: MODELING, FABRICATION, AND CHARACTERIZATION

A Dissertation

by

# ALEXANDRE YASUO YAMAMOTO

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | H. Rusty Harris     |

|---------------------|---------------------|

| Committee Members,  | Jun Kameoka         |

|                     | Peng Li             |

|                     | M. Suhail Zubairy   |

| Head of Department, | Miroslav M. Begovic |

December 2019

Major Subject: Electrical Engineering

Copyright 2019 Alexandre Yasuo Yamamoto

### ABSTRACT

Memristors are the predicted fourth fundamental passive element of circuits, connecting a previously missing relationship between charge q and flux-linkage  $\phi$ . It was first fabricated by a team led by Stanley Williams in 2008 and since many examples have been fabricated, but there is still much debate over how to properly model these devices, what is the physical mechanism for their behavior and even whether or not current examples can be considered the theoretical Memristor predicted by Leon Chua in 1971.

This dissertation shows that barriers preventing injection of charges to the switching medium are likely the cause of exponential terms in model, and this phenomenological cause for the differences found between manufactured devices and the theoretical device can be simply translated by diodes in series with an "ideal" Memristor. These non-idealities can be modeled by devices familiar to circuit designer such as diodes, and by using common tools such as SPICE, an effective model is provided for simulation of Memristors.

To try and clear the confusion over what an ideal Memristor is, a new unit of memristance is proposed, being named after Leon Chua: the Chua [Ch], representing the SI units of  $\Omega/C$ . It is shown that this new way of describing Memristors by their own merit is valid and derives from the same reciprocity that suggested the existence of the device in the first place, being validated against several fabricated examples. This theory also explains some difficulties in measuring these devices, namely the fact that measurement and forming of the memristance are not completely independent and the fact that there is an inverse square dependency with the area; effectively explaining why memristive devices were found only when process nodes shrunk enough that the effects were more obvious.

Finally, this work proposes a structure that is simultaneously a HEMT and a Memristor, and cannot simply be explained by an association of one of each device; this is because the threshold voltage of the transistor appears to change proportionally to the state variable of the Memristor, effectively correlating the devices and causing an amplification of the change in resistance of the memristor. This fact enables the creation of a memristive synapse that could be used in future neuromorphic circuitry, being more efficient than currently proposed 1T1M circuits.

# DEDICATION

To my mother and father, who gave me life; and to my wife, who gave me reasons to live it.

#### ACKNOWLEDGMENTS

I owe the greatest thanks of all to my mother, Ana Virginia de Moraes, and my father, Lauro Koichi Yamamoto; they supported all of my weird choices throughout my life and didn't disown me when I decided to go to graduate school. I also cannot understate the support given to me by my wife, Emily Nicole Bartz, for being such a wonderful person and companion in this journey. None of this would ever be possible without their support and love.

To my advisor, Dr. H. Rusty Harris, I am thankful for all of the guidance and good laughs I had. Your always upbeat guidance provided an excellent environment to conduct research, and allowed me to reach a level of teaching and research I wasn't aware I was capable of. Thank you for pushing me out of my comfort zone.

As for my committee, I would like to thank Dr. Peng Li for the help with my early research career and the flexibility shown at the end of it. To Dr. Jun Kameoka, I owe gratitude for being such a good teacher and for showing me by example on how to be a good instructor. I would also like to thank Dr. Suhail Zubairy for being receptive on the idea of Memristors and providing such good feedback and encouraging words during my preliminary examination.

Additionally, this section would never be complete without my lab-mates. Michael Babb, you have helped me a lot throughout my time here with suggestions on my research despite having a herculean task of your own and I only wish I could have helped you as much as you helped me. William Baker, thank you so much for all the hard work you put in, both with helping the research and providing a very casual and fun atmosphere in the lab. Abhiram Dinavahi, thank you for all the help with theory and definitely thank you for willing to take over from where I left off; I truly believe the field will be better off with you in it. Sravani Jaligama, I appreciate all of the talks we had and all the words of encouragement you have given me. Jung Hwan, you are a truly awesome person and an inspiration for me; I honestly have no idea how you keep it all together with the incredibly hard work and dedication you have shown to me. I thank you for the example you have given me. Shuvodip, thank you for the laughs and the companionship during your time

here. Jae Woo, thank you for teaching me how Aggiefab works and the ins and outs of most obscure equipment in the fab. Feyza Berber, thank you for teaching me how to stand my ground and providing a new angle of view of academia. Andrew Schall, thank you for showing me where my previous research can lead; you have provided me many reasons to believe in myself and on the future of my work. Chen Gong, thank you for showing me how productive a graduate student can be in such a short time.

To Larry Rehn, Gregory Jordan, Etan Morse, Sam Mote, Chelsey Bullock, Jim, Dennis, and all others in Aggiefab that just kept the place running, thank you for all the support and hard work in keeping all machines working so I could fabricate my devices. Robert Atkins, thank you so much for keeping the academic laboratories in check and for all the support during my years as a TA of ECEN472. You made my work that much more enjoyable and classes would not have run smoothly without your help.

Due to space constraints, I decided to only thank those who were most present during my time at Texas A&M university. I do wish to thank all of those who have crossed my life up to this point; Know that I remember and am thankful to all of you.

Finally I would like to thank my dog and cat for simply existing in my life. Thank you Dr. Turing and Monseigneur Baudrillard for being there for me through thick and thin.

## CONTRIBUTORS AND FUNDING SOURCES

# Contributors

This work was supported by a dissertation committee consisting of Professors Harlan Rusty Harris, Jun Kameoka, and Peng Li of the Department of Electrical and Computer Engineering and Professor Muhammad Suhail Zubairy of the Department of Physics.

The data analyzed for the Tungsten-doped Memristor was provided in part by Michael Everett Babb of the Department of Electrical Engineering. The HEMT used for the analysis in chapter 6 was fabricated by Derek Wade Johnson.

All other work conducted for the dissertation was completed by the student independently.

## **Funding Sources**

Graduate study was supported by a teaching assistantship from Texas A&M University.

# NOMENCLATURE

| 1T1M       | 1-Transistor-1-Memristor                                       |

|------------|----------------------------------------------------------------|

| 2DEG       | 2-Dimensional Electron Gas                                     |

| BOE        | Buffered Oxide Etch                                            |

| CF         | Conductive Filament                                            |

| D          | Switching medium thickness                                     |

| HEMT       | High Electron Mobility Transistor                              |

| $I_S$      | Diode Saturation Current                                       |

| $I_d$      | HEMT Drain current                                             |

| $I_g$      | HEMT Gate current                                              |

| $I_s$      | HEMT Source current                                            |

| LOR        | Lift-Off Resist                                                |

| MIIM       | Metal-Insulator-Insulator-Metal                                |

| MIM        | Metal-Insulator-Metal                                          |

| MIS        | Metal-Insulator-Semiconductor                                  |

| MOS        | Metal-Oxide-Semiconductor                                      |

| n          | Diode Ideality Factor                                          |

| $R_{INIT}$ | Memristor initial resistance                                   |

| $R_{ON}$   | ON-state resistance                                            |

| $R_{OFF}$  | OFF-state resistance                                           |

| ReRAM      | Resistive Random-access Memory                                 |

| SI         | Système International d'unités (International System of Units) |

| SV      | State Variable         |

|---------|------------------------|

| $\mu_V$ | Drift velocity         |

| $V_0$   | Diode built-in voltage |

| $V_T$   | HEMT Threshold voltage |

| $V_d$   | HEMT Drain voltage     |

| $V_g$   | HEMT Gate voltage      |

| $V_s$   | HEMT Source voltage    |

| w       | State Variable         |

# TABLE OF CONTENTS

| AE | BSTR                            | ACT                                                                                                                | ii             |

|----|---------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------|

| DE | EDICA                           | ATION                                                                                                              | iv             |

| AC | CKNC                            | WLEDGMENTS                                                                                                         | v              |

| CC | ONTR                            | IBUTORS AND FUNDING SOURCES                                                                                        | vii            |

| NC | OMEN                            | VCLATURE                                                                                                           | viii           |

| TA | BLE                             | OF CONTENTS                                                                                                        | x              |

| LI | ST OI                           | F FIGURES                                                                                                          | xii            |

| LI | ST OI                           | F TABLESx                                                                                                          | viii           |

| 1. | INT                             | RODUCTION                                                                                                          | 1              |

|    | 1.1<br>1.2<br>1.3               | The Tail End of Moore's Law<br>Non-Von Neumann Computing<br>Purpose of This Work                                   | 3              |

| 2. | MEN                             | MRISTOR                                                                                                            | 5              |

|    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Physical Device Discovery<br>Memristance Mechanisms<br>Forming Cycle<br>Density<br>Current Modeling and Simulation | 9<br>11<br>13  |

| 3. | NON                             | N-IDEALITY AND MODELING                                                                                            | 15             |

|    | 3.1<br>3.2<br>3.3               |                                                                                                                    | 21<br>23<br>27 |

| 4. | MEN                             | MRISTANCE CHARACTERIZATION                                                                                         | 37             |

|    | 4.1<br>4.2<br>4.3               | Symmetry Between Fundamental Circuit Elements<br>Memristor Linearity<br>Alternative Memristance Calculation Method |                |

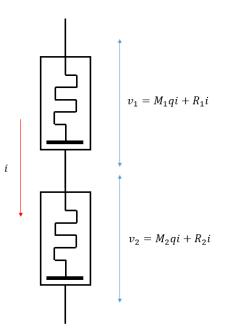

|    | 4.4  | Associa | ation of Memristors                                              | 50  |

|----|------|---------|------------------------------------------------------------------|-----|

|    |      | 4.4.1   | Series Association of Memristors                                 | 50  |

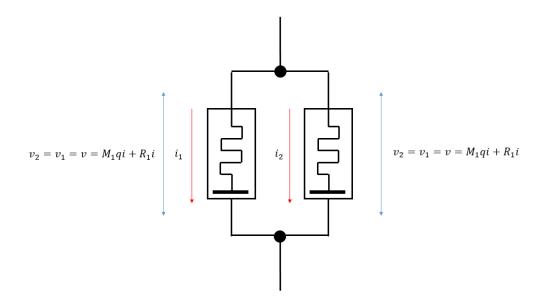

|    |      | 4.4.2   | Parallel Association of Memristors                               | 52  |

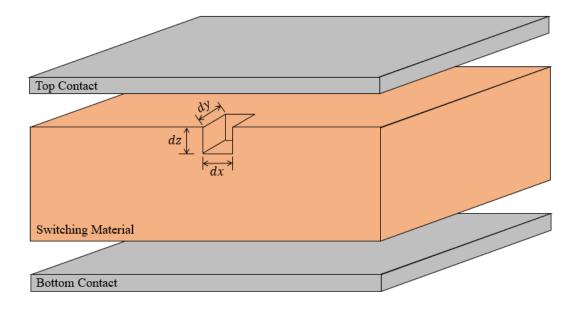

|    |      | 4.4.3   | Volumetric Analysis of Memristance                               | 54  |

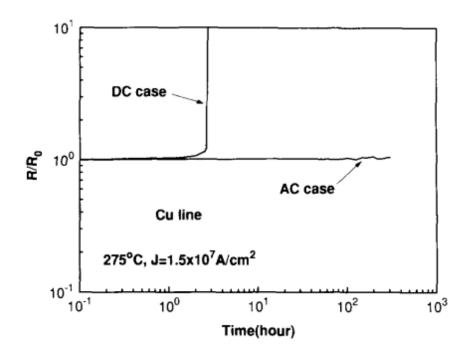

|    |      | 4.4.4   | Large Size Memristors: Electromigration as Memristance Mechanism | 56  |

|    |      | 4.4.5   | Conductive Filament Analysis                                     | 58  |

|    | 4.5  | Linear  | Memristor Model Validation                                       | 59  |

|    |      | 4.5.1   | Single Memristor Simulations                                     | 60  |

|    |      | 4.5.2   | Series Memristor Simulations                                     |     |

|    |      | 4.5.3   | Parallel Memristor Simulations                                   | 62  |

|    |      | 4.5.4   | Parasitics Effect on Memristance Measurement                     | 63  |

|    |      |         |                                                                  |     |

| 5. | TES  | TING M  | IEMRISTANCE                                                      | 65  |

|    | 5.1  | MIM C   | Crossbar Memristor                                               | 65  |

|    | 5.2  |         | ercial Samples                                                   |     |

|    | 5.3  |         | eterar sumpres                                                   |     |

|    | 5.5  | 5.3.1   | Fabricated MIM Crossbar Memristor                                |     |

|    |      | 5.3.2   | Carbon-doped Chalcogenide                                        |     |

|    |      | 5.3.3   | Tungsten-doped Chalcogenide                                      |     |

|    |      | 5.3.4   | Overall Picture                                                  |     |

|    |      | 5.5.1   |                                                                  | , , |

| 6. | MEN  | ATRAN   | SISTOR - 1T1M STRUCTURE                                          | 79  |

|    | 6.1  | Device  | Structure                                                        | 79  |

|    | 6.2  |         | stance                                                           |     |

|    |      |         |                                                                  |     |

| 7. | CON  | ICLUSI  | ON AND OUTLOOK                                                   | 88  |

| пт |      |         |                                                                  | 00  |

| КĿ | FERI | LINCES  |                                                                  | 90  |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

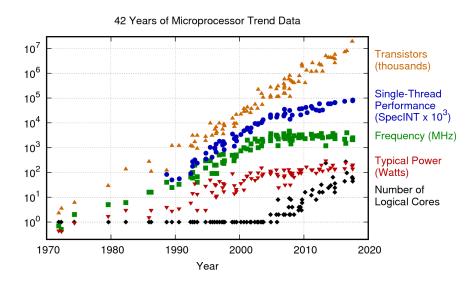

| 1.1    | Trends in microprocessors until 2017 showing exponential transistor count growth while other performance figures start to plateau. Reprinted from [11] with permission under MIT License.                                                                                                                                                                                                                                                                                                 | 2    |

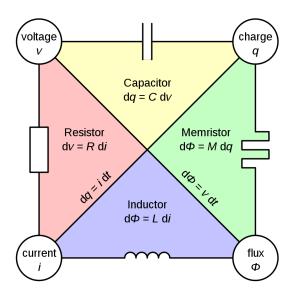

| 2.1    | Graph illustrating how passive devices connect charge, current, flux and voltage.<br>Art by Parcly Taxel used under CC-BY-SA 3.0                                                                                                                                                                                                                                                                                                                                                          | 5    |

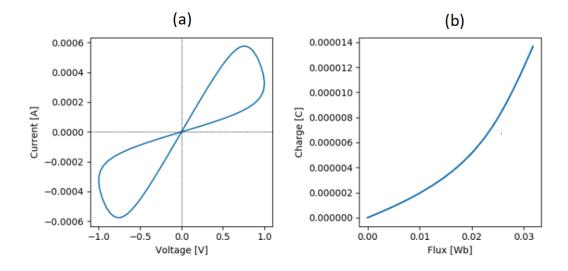

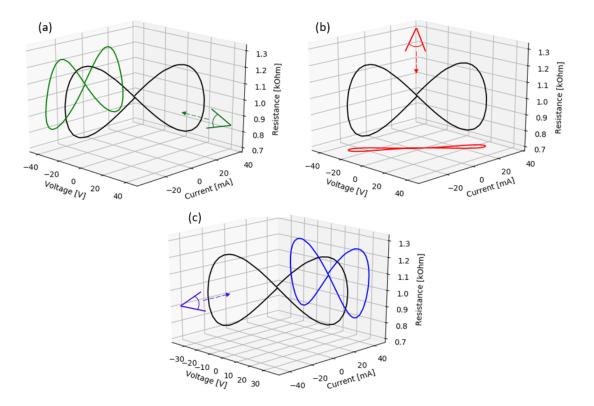

| 2.2    | (a) <i>i</i> - $v$ plane of a Memristor, showing the pinched hysteresis at the origin and symmetric hysteresis areas in the first and third quadrant. (b) $q$ - $\phi$ plane of the same Memristor, showing non-linearity.                                                                                                                                                                                                                                                                | 6    |

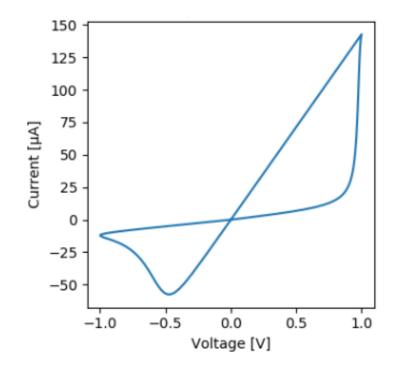

| 2.3    | <i>i-v</i> plot of a simulation of the first fabricated Memristor.                                                                                                                                                                                                                                                                                                                                                                                                                        | 8    |

| 2.4    | Sketch structure of the first fabricated Memristor                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8    |

| 2.5    | (a) Sketch of a simple memristive device depicting an oxygen-deficient layer and its boundary. The location of the boundary $w$ relative to the total thickness $D$ is dubbed State Variable (SV). (b) Analogy with a potentiometer.                                                                                                                                                                                                                                                      | 9    |

| 2.6    | (a) and (b) $i$ - $v$ plot of a typical forming cycle for a metal-oxide Memristor. (c) Process sketch showing an initial middle layer going from insulator to switching medium due to application of a breakdown voltage.                                                                                                                                                                                                                                                                 | 12   |

| 3.1    | Illustration of non-linearities present in many fabricated devices. (1) Non-linear current-voltage relationship in saturation. (2) Pinch point away from origin. (3) Asymmetry of hysteresis loops between quadrants. (4) High leakage currents that do not change SV. (a) Low cost Memristor based on $TiO_2$ , adapted from [21]. (b) $TaO_X$ Memristor, adapted from [71]. (c) Memristor crossbar array, adapted from [72]. (d) Memdiode for neuromorphic circuitry, adapted from [70] | 15   |

| 3.2    | Band diagrams of a MIM Memristor. (a) Work function mismatch causing direct tunneling under certain bias conditions. (b) Work function mismatch causing a barrier to appear for injection of charges through the switching medium.                                                                                                                                                                                                                                                        | 16   |

| 3.3    | Simulations of a diode in series with a Memristor. (a) Circuit representation. (b) First quadrant response for varying built-in potentials: from left to right, 0.3V, 0.5V, 0.7V and 1V. (c) First quadrant response for varying ideality factors                                                                                                                                                                                                                                         | 17   |

| 3.4  | Simulations of a diode in parallel with a Memristor. (a) Circuit representation. (b) Response for varying built-in potentials: from left to right, 0.3V, 0.5V, 0.7V and 1V. (c) Response for varying ideality factors                                                                                                                                                                                                                                         | 19 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Simulations of a combination of diodes with a Memristor. (a) Diode in parallel with Memristor. (b) Diode in parallel with Memristor-diode                                                                                                                                                                                                                                                                                                                     | 20 |

| 3.6  | Full device model for fabricated Memristors including parasitic diodes                                                                                                                                                                                                                                                                                                                                                                                        | 21 |

| 3.7  | Illustration of the parallel leakage path on the diode curve and first approximations for parasitics variables. Upper inset shows the equivalent circuits and lower inset shows impact of changing ideality factor on parallel diode                                                                                                                                                                                                                          | 22 |

| 3.8  | Memdiode for neuomorphic applications fit. (a) Fit overlaid in original published data adapted from [70] for comparison. (b) Simulation in LTSpice using the proposed model showing separate branch currents. In this case $n_{D_{S_1}} = 1.7$ , $V_{0_{D_{S_1}}} = 0.75V$ , $n_{D_{P_1}} = 1.6$ , $V_{0_{D_{P_1}}} = 1.2V$ , $R_{ON} = 7k\Omega$ , $R_{OFF} = 800k\Omega$ , $\mu_v = 0.8ncm^2s^{-1}V^{-1}$ .                                                 | 23 |

| 3.9  | Crossbar array for neuromorphic applications fit. (a) Fit overlaid in original published data adapted from [72] for comparison. (b) Simulation in LTSpice using the proposed model. In this case $n_{D_{S_1}} = 1.5$ , $V_{0_{D_{S_1}}} = 0V$ , $R_{ON} = 800k\Omega$ , $R_{OFF} = 1M\Omega$ , $\mu_v = 0.5ncm^2 s^{-1}V^{-1}$                                                                                                                                | 24 |

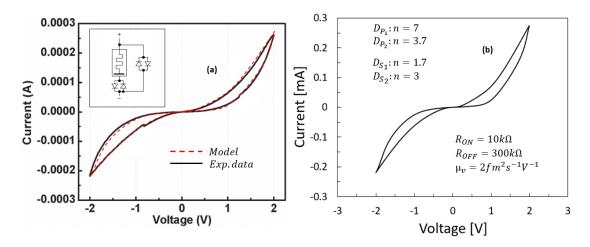

| 3.10 | Low cost titanium oxide Memristor fit. (a) Fit overlaid in original published data adapted from [21] for comparison. (b) Simulation in LTSpice using the proposed model. In this case $n_{D_{P_1}} = 7$ , $V_{0_{D_{P_1}}} = 0V$ , $n_{D_{P_2}} = 3.7$ , $V_{0_{D_{P_2}}} = 0V$ , $n_{D_{S_1}} = 1.7$ , $V_{0_{D_{S_1}}} = 0V$ , $n_{D_{S_2}} = 3$ , $V_{0_{D_{S_2}}} = 0V$ , $R_{ON} = 10k\Omega$ , $R_{OFF} = 300k\Omega$ , $\mu_v = 20pcm^2s^{-1}V^{-1}$ . | 25 |

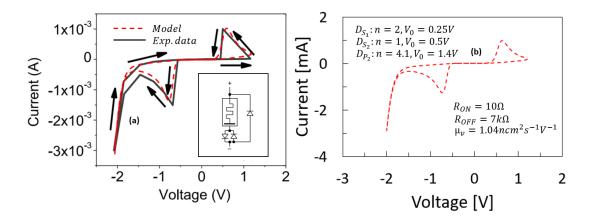

| 3.11 | MIM Memristor fit. (a) Fit overlaid in original published data adapted from [71] for comparison. (b) Simulation in LTSpice using the proposed model. In this case $n_{D_{S_1}} = 2$ , $V_{0_{D_{S_1}}} = 0.25V$ , $n_{D_{S_2}} = 1$ , $V_{0_{D_{S_2}}} = 0.5V$ , $n_{D_{P_2}} = 4.1$ , $V_{0_{D_{P_2}}} = 1.4V$ , $R_{ON} = 10\Omega$ , $R_{OFF} = 7k\Omega$ , $\mu_v = 1.04ncm^2s^{-1}V^{-1}$                                                                | 26 |

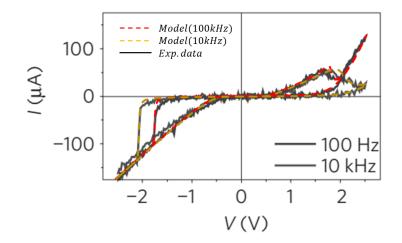

| 3.12 | Current-Voltage characteristic of a fitted ferroelectric Memristor adapted from [79].<br>Dashed lines show the simulated model                                                                                                                                                                                                                                                                                                                                | 27 |

| 3.13 | Methodology for calculating hysteresis area in a quadrant. Arrow points to max-<br>imum excitation voltage. (a) Integration of first half of positive swing (zero to<br>maximum voltage). (b) Integration of second half of positive swing (maximum<br>voltage back to zero). (c) Resulting hysteresis area due to simple subtraction of areas.                                                                                                               | 28 |

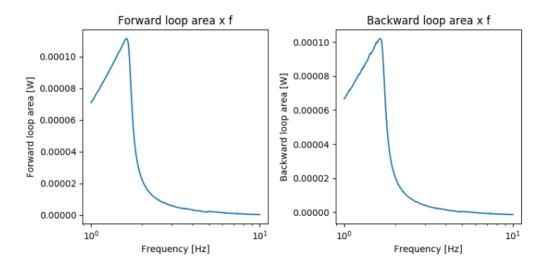

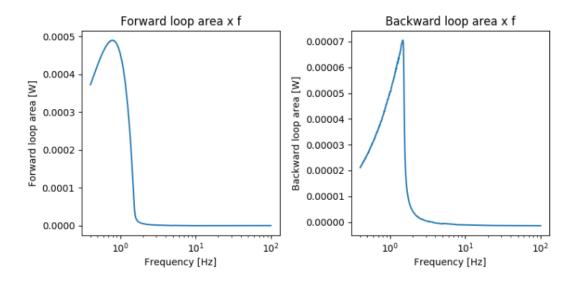

| 3.14 | Magnitude of hysteresis area versus frequency for a Memristor.                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

| 3.15 | Magnitude of hysteresis area versus frequency for a Memristor which exhibits many non-idealities such as saturation.                                                                                                                                     | 29 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

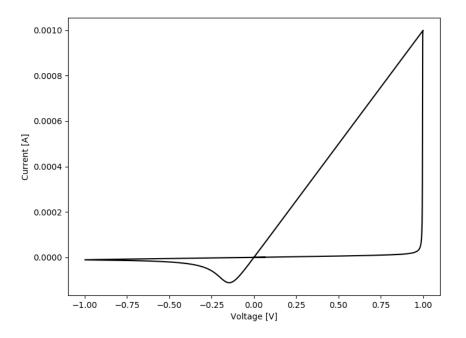

| 3.16 | <i>i-v</i> curve for a frequency of 1Hz for Memristor of Fig. 3.15                                                                                                                                                                                       | 30 |

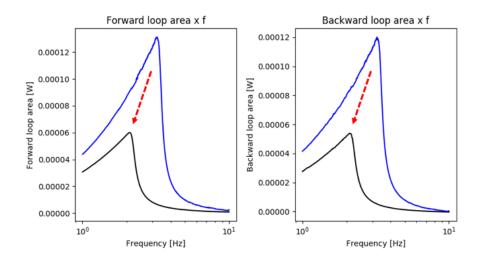

| 3.17 | Magnitude of hysteresis area versus frequency for the Memristor of Fig. 3.14 altered by anti-parallel diodes of $n = 1$ in series with it                                                                                                                | 31 |

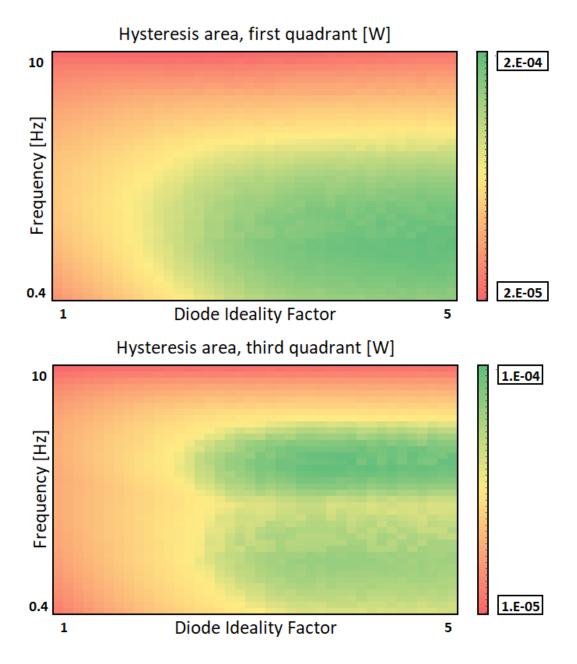

| 3.18 | Result of the simulation showcasing hysteresis area change because of anti-parallel diodes in series with a Memristor.                                                                                                                                   | 32 |

| 3.19 | Result of the simulation showcasing hysteresis area change because of anti-parallel diodes in parallel with a Memristor                                                                                                                                  | 33 |

| 3.20 | Result of the simulation showcasing pinch point change for a variety of ideality factors. (a) Circuit being simulated. (b) Simulation result. (c) Zoom of pinches with arrow pointing to pinch.                                                          | 34 |

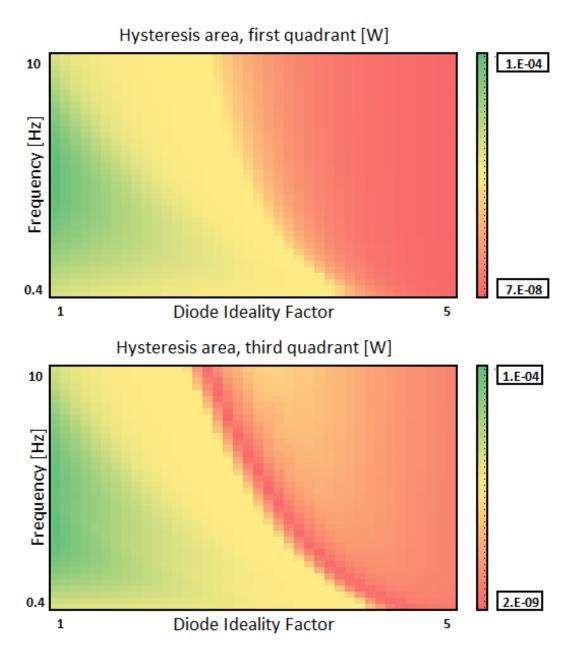

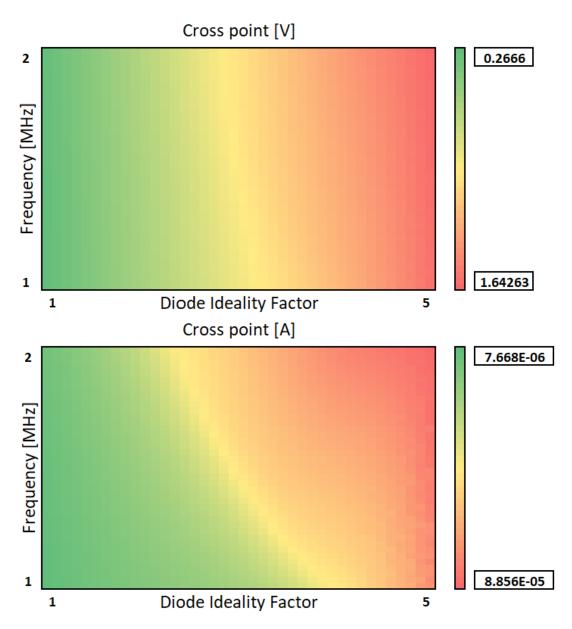

| 3.21 | Result of the simulation showcasing pinch point change as function of series diodes ideality factor and driving frequency.                                                                                                                               | 35 |

| 4.1  | (a) <i>i</i> - $v$ plane of a NTC thermistor that self-heats, showing hysteresis. (b) $q$ - $\phi$ plane of the same thermistor.                                                                                                                         | 37 |

| 4.2  | (a) $i$ - $v$ plane of a capacitor with an initial condition of 0.5V. (b) Conductance- $i$ plane of the same capacitor.                                                                                                                                  | 38 |

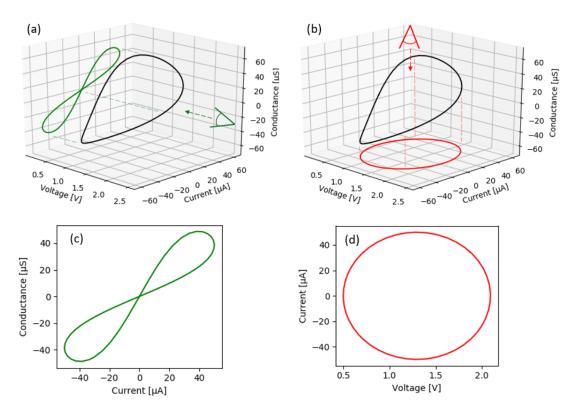

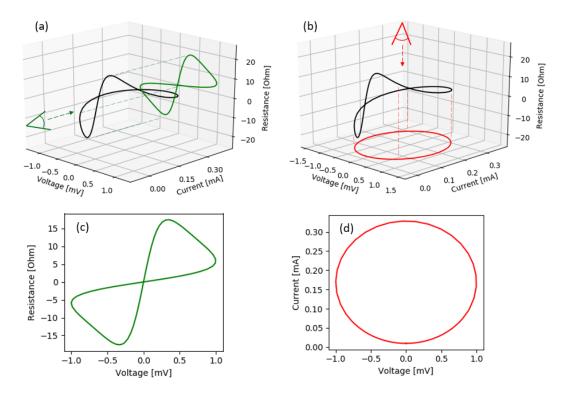

| 4.3  | <ul> <li>(a) 3D plot of a capacitor showing projection in Conductance-<i>i</i> plane. (b) 3D plot of a capacitor showing projection in <i>i</i>-v plane. (c) Conductance-<i>i</i> plane projection.</li> <li>(d) <i>i</i>-v plane projection.</li> </ul> | 39 |

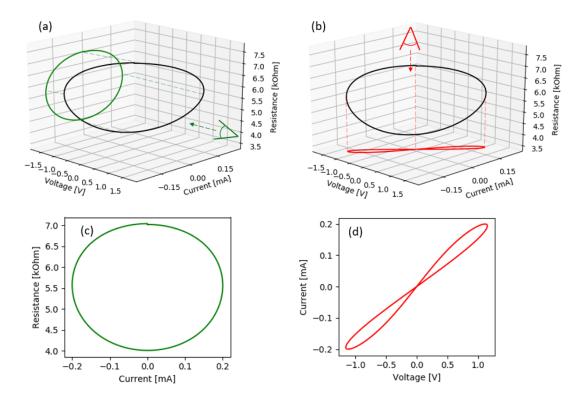

| 4.4  | (a) 3D plot of an inductor showing projection in $\Omega$ - <i>i</i> plane. (b) 3D plot of an inductor showing projection in <i>i</i> - <i>v</i> plane. (c) $\Omega$ - <i>i</i> plane projection. (d) <i>i</i> - <i>v</i> plane projection.              | 40 |

| 4.5  | (a) 3D plot of a Memristor showing projection in $\Omega$ - <i>i</i> plane. (b) 3D plot of a Memristor showing projection in <i>i</i> - <i>v</i> plane. (c) $\Omega$ - <i>i</i> plane projection. (d) <i>i</i> - <i>v</i> plane projection.              | 41 |

| 4.6  | (a) 3D plot of a NTC thermistor showing projection in $\Omega$ - <i>i</i> plane. (b) 3D plot of a NTC thermistor showing projection in <i>i</i> - <i>v</i> plane. (c) 3D plot of a NTC thermistor showing projection in $\Omega$ - <i>v</i> plane.       | 42 |

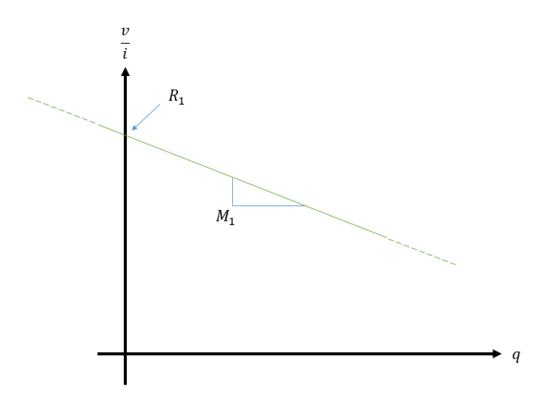

| 4.7  | Ideal memristor showing linearity.                                                                                                                                                                                                                       | 44 |

| 4.8  | Practical memristor showing linearity region and saturation regions.                                                                                                                                                                                     | 45 |

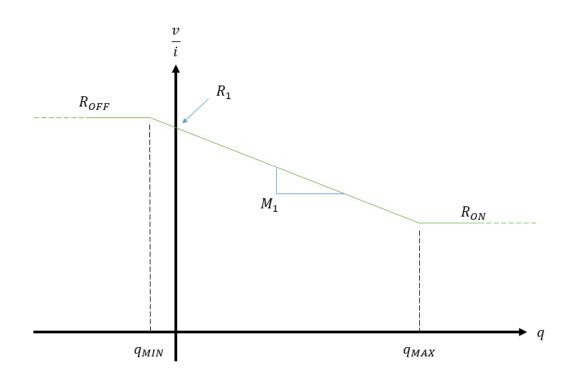

| 4.9  | $\Omega$ -I plane of an ideal Memristor showing instantaneous resistance change                                                                                                                                                                          | 47 |

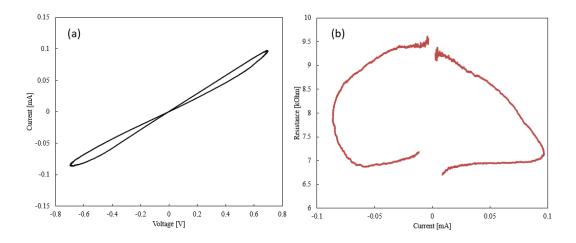

| 4.10 | (a) $i$ - $v$ and (b) $\Omega$ - $i$ plane of a manufactured Memristor                                                                                                                                                                                       | 47 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

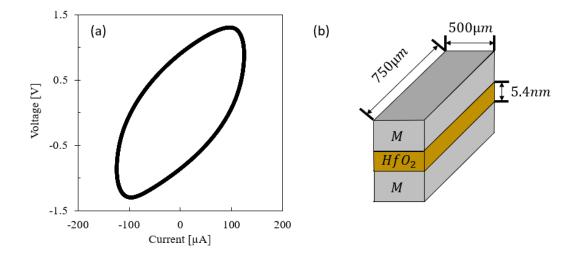

| 4.11 | (a) <i>i</i> - <i>v</i> curve of the parallel plate capacitor shown in (b)                                                                                                                                                                                   | 48 |

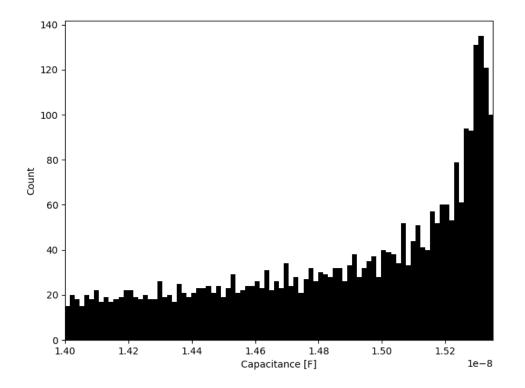

| 4.12 | Histogram of detected capacitances showing peak at $15.3nF$                                                                                                                                                                                                  | 49 |

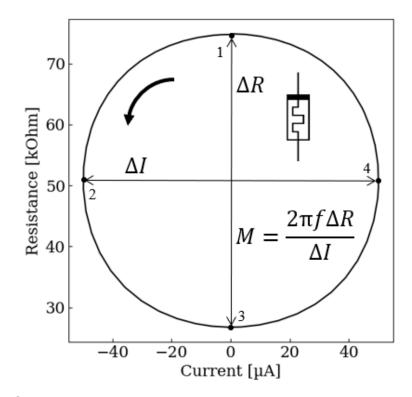

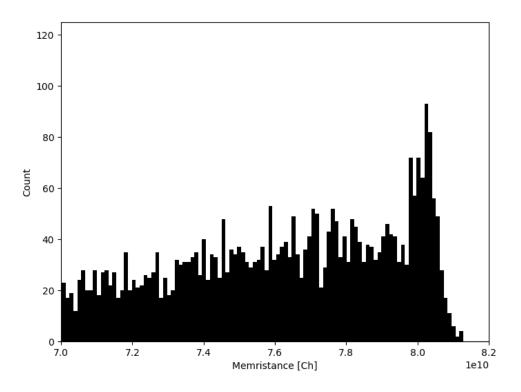

| 4.13 | Histogram of detected memristances showing peak at 8GCh                                                                                                                                                                                                      | 50 |

| 4.14 | Series association of memristors                                                                                                                                                                                                                             | 51 |

| 4.15 | Equivalent Memristor arising from the series association of Memristors with char-<br>acteristics $M_1q + R_1$ and $M_2q + R_2$                                                                                                                               | 52 |

| 4.16 | Parallel association of two identical Memristors                                                                                                                                                                                                             | 52 |

| 4.17 | Parallel association of <i>n</i> identical Memristors.                                                                                                                                                                                                       | 53 |

| 4.18 | Memristor MIM structure showing "quantized" memristance block removed                                                                                                                                                                                        | 55 |

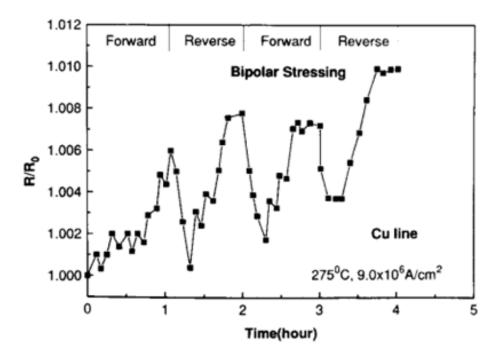

| 4.19 | Copper interconnect subject to a DC and 1MHz AC current over time. Reprinted with permission from [84].                                                                                                                                                      | 57 |

| 4.20 | Copper interconnect subject to a AC current over time showing linear dependence between charge and resistance. Reprinted with permission from [84]                                                                                                           | 58 |

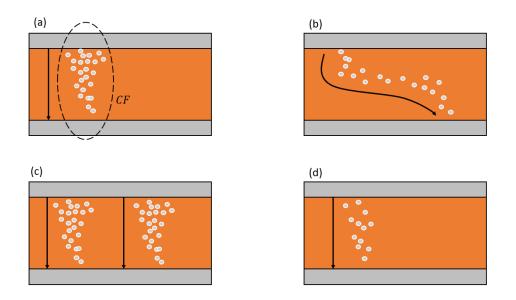

| 4.21 | (a) Memristor structure showing single CF. (b) Longer CF. (c) Multiple CF. (d) Single CF with lower mobile ions.                                                                                                                                             | 59 |

| 4.22 | Memristor test setup on LTSpice.                                                                                                                                                                                                                             | 60 |

| 4.23 | (a) <i>i</i> - $v$ curve of the simulated Memristor using Biolek's model. (b) $\Omega$ - $q$ curve of the same memristor showing linear and saturation region                                                                                                | 61 |

| 4.24 | (a) $i$ - $v$ curve of the simulated Memristor using Biolek's model for three different variations in test parameters. (b) $\Omega$ - $q$ curve of the same Memristor showing linear and saturation region for three different variations in test parameters | 61 |

| 4.25 | (a) <i>i</i> - $v$ curve of the simulated Memristors in series using Biolek's model. (b) $\Omega$ - $q$ curve of the same Memristors showing linear and saturation region                                                                                    | 62 |

| 4.26 | (a) <i>i</i> - <i>v</i> curve of the simulated Memristors in parallel using Biolek's model. (b) $\Omega$ - <i>q</i> curve of the same Memristors showing linear and saturation region                                                                        | 63 |

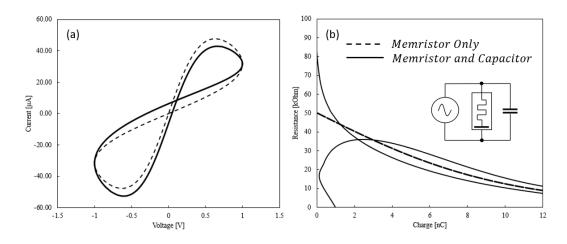

| 4.27 | (a) <i>i</i> - <i>v</i> curve of the simulated Memristors with and without a $1nF$ parallel capacitor at $1kHz$ . (b) $\Omega$ - <i>q</i> curve of the same configurations                                                                                   | 64 |

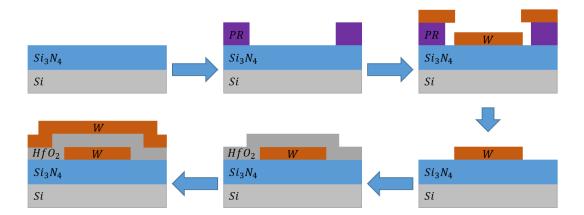

| 5.1  | Sketch of fabrication sequence. Not to scale                                                                                                                                                                                                                 | 65 |

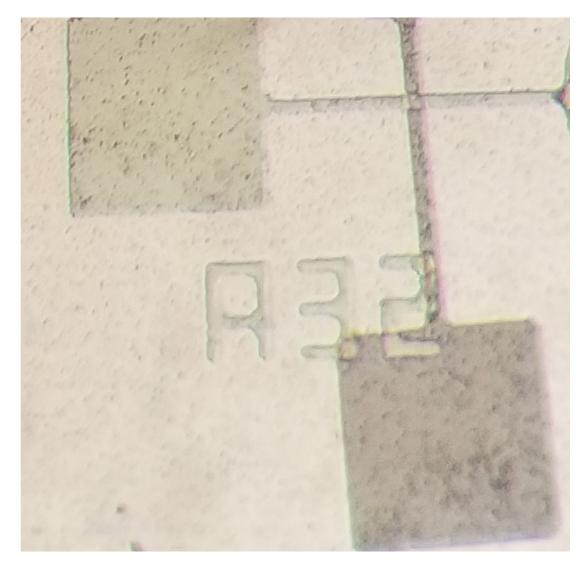

| 5.2  | Fabricated crossbar structure with contact pads for probing                                                                                                                                                                                                  | 66 |

| 5.3  | Two packaged memristor devices with eight Memristors each. Top: Tungsten doped Chalcogenide. Bottom: Carbon doped Chalcogenide                                                                 | 67 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

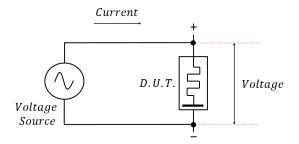

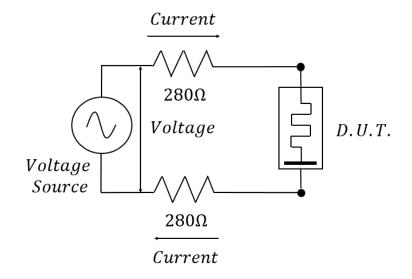

| 5.4  | Circuit of the test setup                                                                                                                                                                      | 68 |

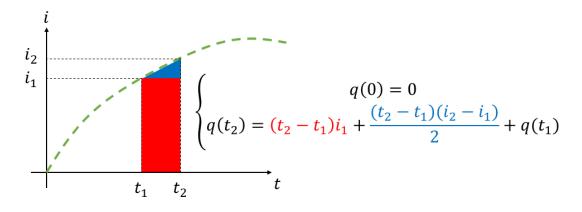

| 5.5  | Methodology for the calculation of history of charge through the device                                                                                                                        | 69 |

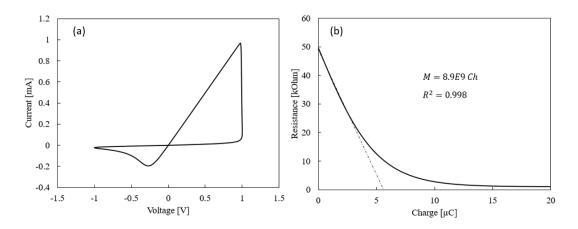

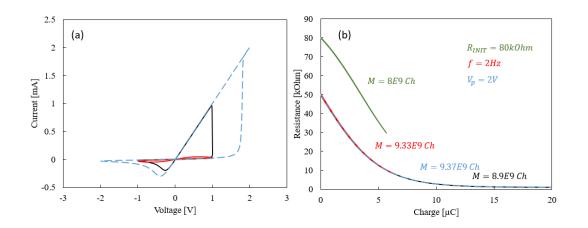

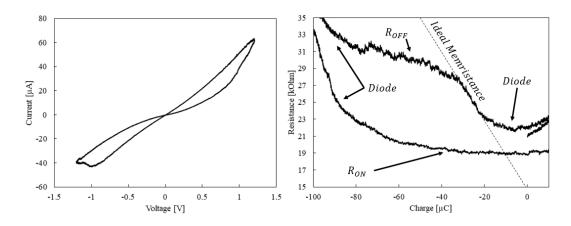

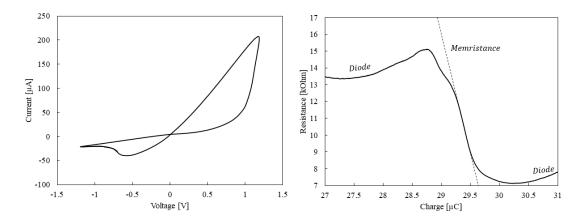

| 5.6  | (a) $i$ - $v$ curve of the fabricated MIM Memristor. (b) $\Omega$ - $q$ curve of the same Memristor showing linear region, saturation regions and other non-idealities                         | 69 |

| 5.7  | <ul> <li>(a) <i>i-v</i> curve of the fabricated MIM Memristor corrected to remove non-idealities.</li> <li>(b) Ω-q curve of the same Memristor showing linear regions of same slope</li> </ul> | 70 |

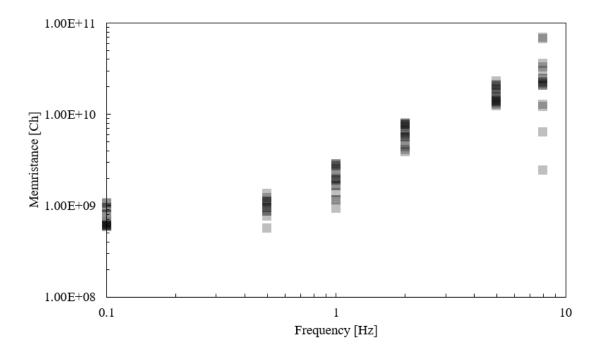

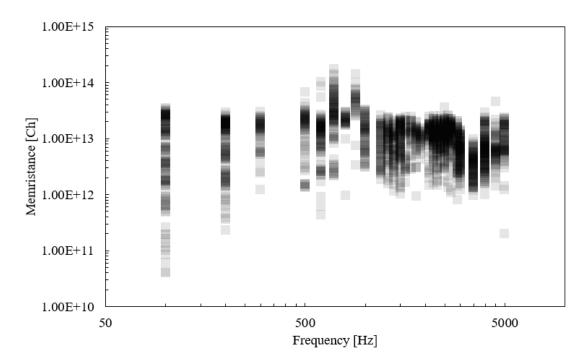

| 5.8  | Analysis of memristance as measured using a sinusoidal voltage source in multiple frequencies for the fabricated MIM Memristor.                                                                | 71 |

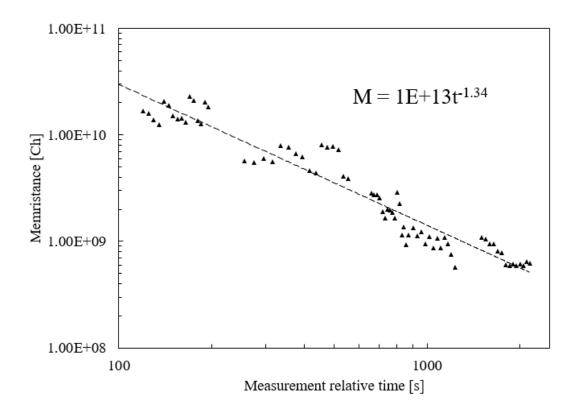

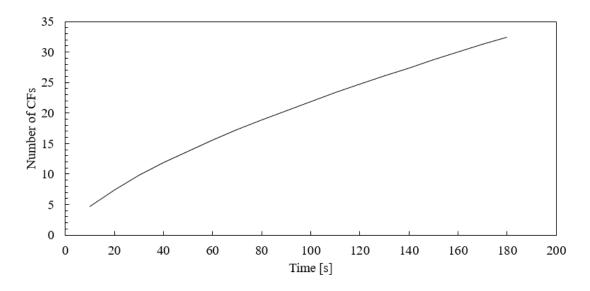

| 5.9  | Time variance of memristance due to the formation of new conduction paths re-<br>sulting in lower memristance.                                                                                 | 72 |

| 5.10 | Number of new channels as a function of time                                                                                                                                                   | 73 |

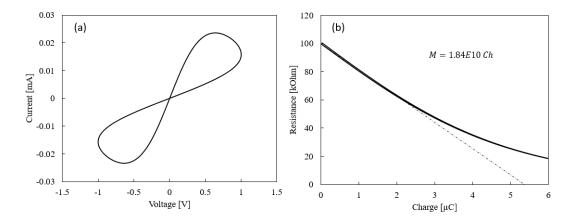

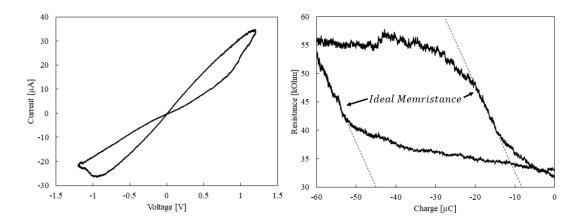

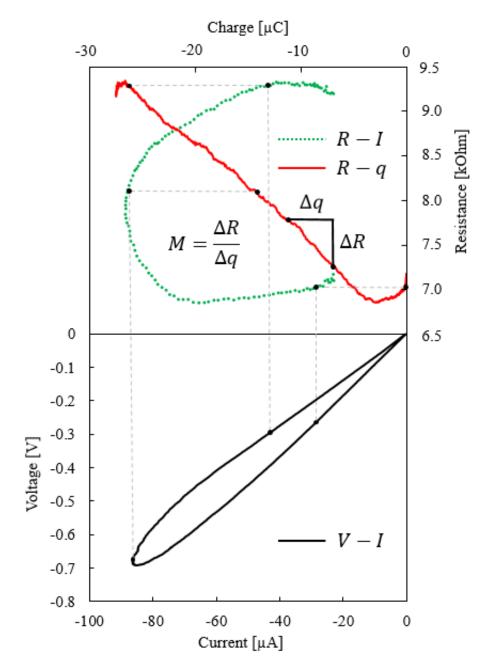

| 5.11 | (a) $\Omega$ - <i>i</i> and $\Omega$ - <i>q</i> curve of the Carbon Knowm device. (b) <i>i</i> - <i>v</i> curve of the same Memristor for the third quadrant                                   | 74 |

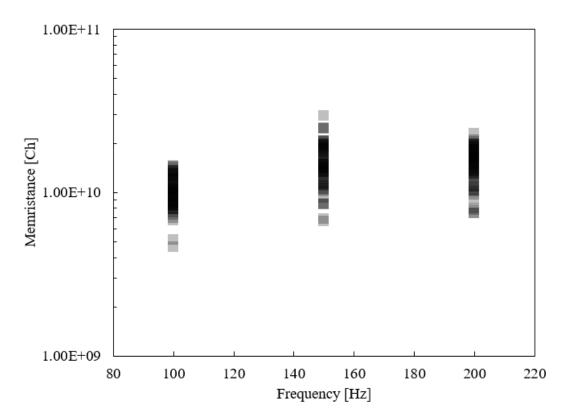

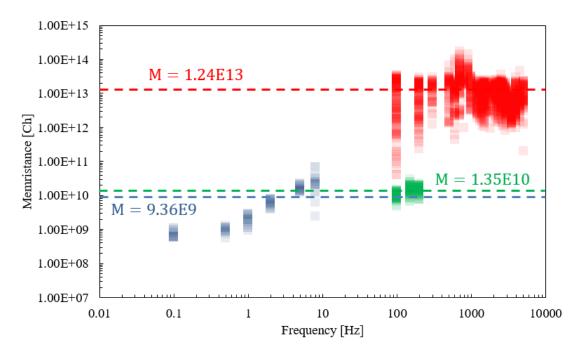

| 5.12 | Analysis of memristance as measured using a sinusoidal voltage source in multiple frequencies for the Carbon-doped chalcogenide device.                                                        | 75 |

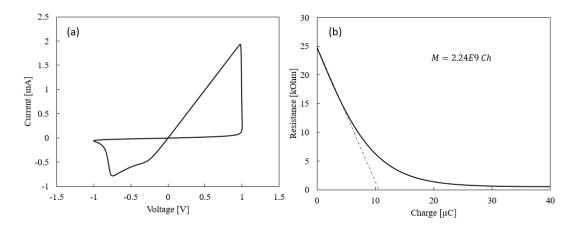

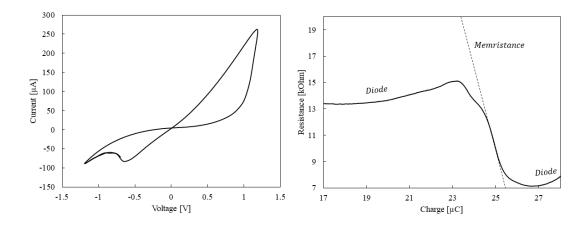

| 5.13 | (a) $i\text{-}v$ curve of the Tungsten Knowm device. (b) $\Omega\text{-}q$ curve of the same Memristor                                                                                         | 76 |

| 5.14 | (a) Corrected <i>i</i> - <i>v</i> curve of the Tungsten Knowm device. (b) $\Omega$ - <i>q</i> curve of the same Memristor corrected.                                                           | 76 |

| 5.15 | Analysis of memristance as measured using a sinusoidal voltage source in multiple frequencies for the Tungsten-doped chalcogenide device.                                                      | 77 |

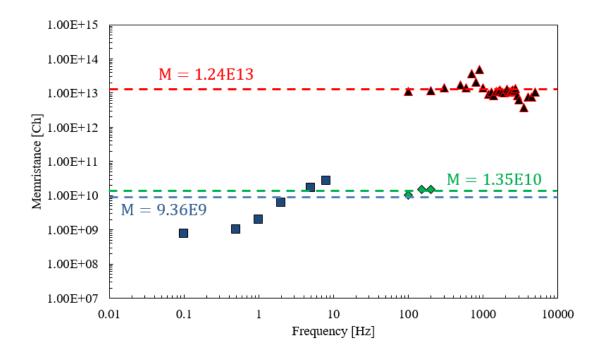

| 5.16 | Analysis of mean measured memristance in multiple frequencies for all devices, with every measurement of Memristance shown.                                                                    | 78 |

| 5.17 | Analysis of mean measured memristance in multiple frequencies for all devices, with average of Memristance measurements for every frequency shown                                              | 78 |

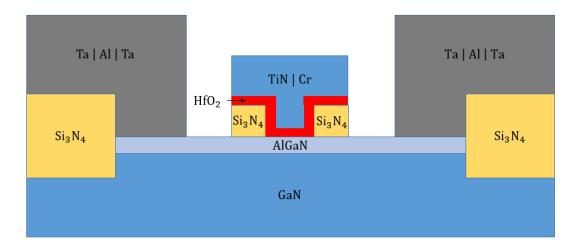

| 6.1  | Sketch of fabricated HEMT device with metal-oxide gate insulator                                                                                                                               | 80 |

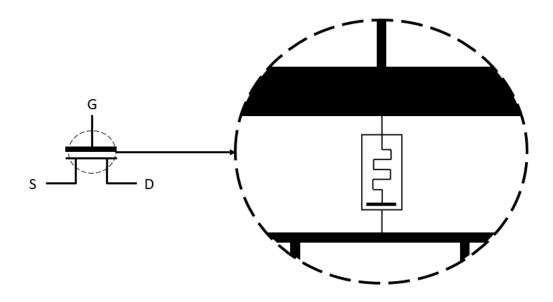

| 6.2  | Position of the Memristor inside of the HEMT after forming cycle                                                                                                                               | 81 |

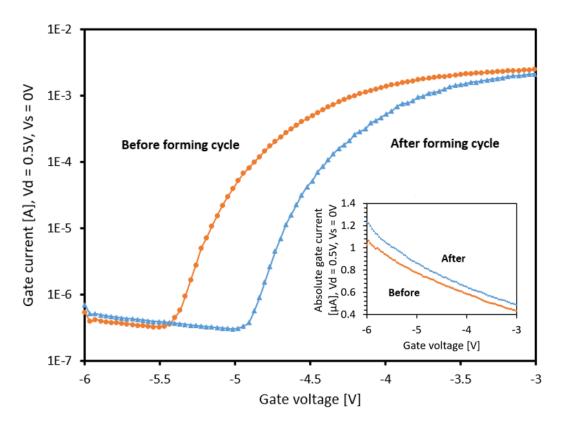

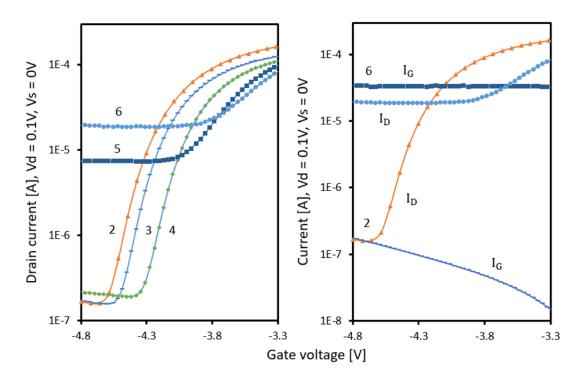

| 6.3  | Semilog plot of $I_d$ - $V_g$ for the HEMT before and after a single forming cycle. Inset: gate current versus voltage showing increase in leakage currente after forming                      | 82 |

| 6.4 | Second forming cycle.                                                                                                                                                                                                                                                                                                                | 83 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.5 | Semilog plots of $I_d$ - $V_g$ for the HEMT showcasing threshold voltage and gate leak-<br>age modification with further forming cycles. Numbers indicate amount of forming<br>cycles applied before measurement                                                                                                                     | 83 |

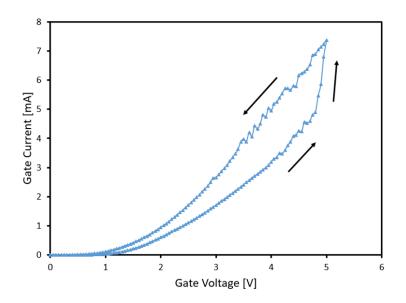

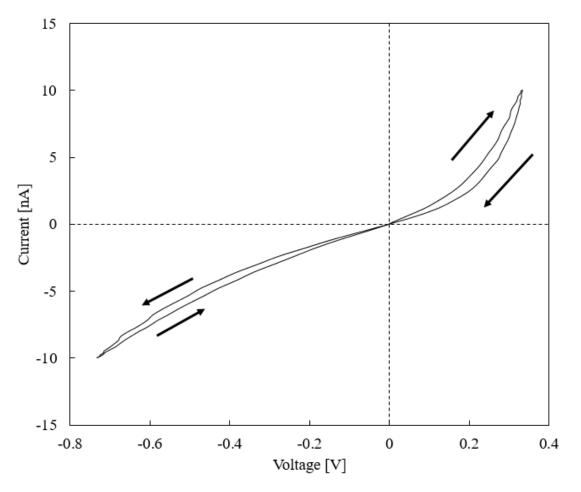

| 6.6 | Memristance <i>i</i> - <i>v</i> for the HEMT. Source and Drain were tied and used as a second contact                                                                                                                                                                                                                                | 84 |

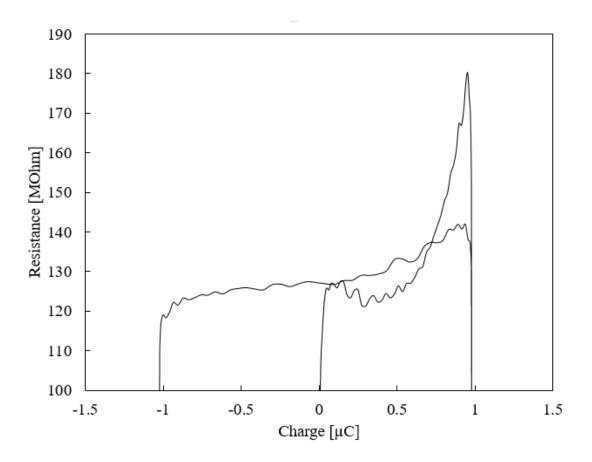

| 6.7 | Memristance $\Omega$ -q for the HEMT. Source and Drain were tied and used as a second contact.                                                                                                                                                                                                                                       | 85 |

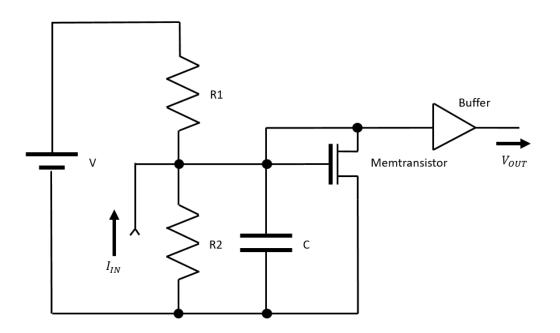

| 6.8 | Neuromorphic circuit that generates spikes proportional to input current $I_{IN}$                                                                                                                                                                                                                                                    | 86 |

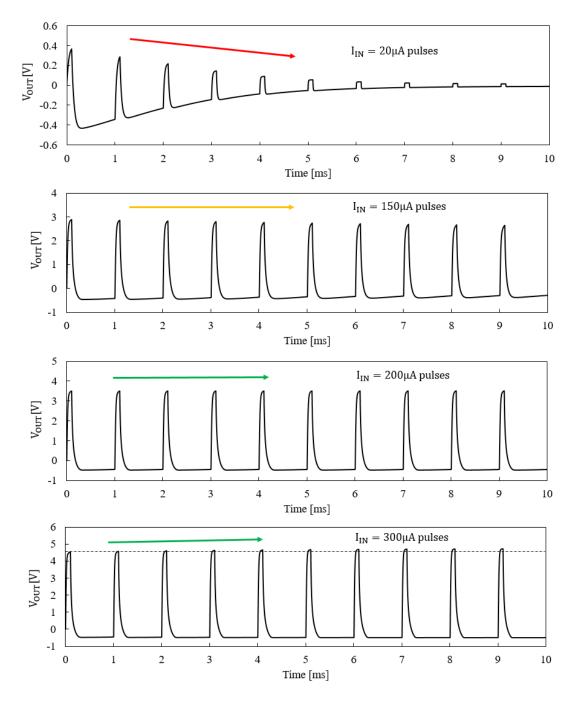

| 6.9 | Results of exciting the neuromorphic circuit of Fig. 6.8 with $I_{IN}$ pulses of magnitude $20\mu A$ , $150\mu A$ , $200\mu A$ , and $300\mu A$ . For this simulation: $C = 1nF$ , $R1 = R2 = 1M\Omega$ , and $V = -10V$ . Dotted line in last graph added to show position of first peak, illustrating that peak size is increasing | 87 |

# LIST OF TABLES

| TABLE | P                                      | age |

|-------|----------------------------------------|-----|

|       |                                        |     |

| 2.1   | Comparison between memory technologies | 13  |

### 1. INTRODUCTION

Modern day computing was made possible due to many interesting properties of silicon. For many years the increase in transistor density [1] coupled with other techniques has enabled an exponential speedup in processing power; this has provided us the ability to solve more and more complex problems while at the same time improving accessibility due to the reduced costs.

One area that has greatly benefited from the growth in computing power is machine learning [2], which has the ambitious goal of solving any problems that a human would be capable of while being faster and more efficient (a very useful reference of the current state of the art is given by Steve Furber [3], comparing large scale neuromorphic systems to the human brain). It could be argued that computers are already more efficient than humans for a variety of tasks (such as playing chess [4]), but currently that is not true of *every* task. As a superficial analysis we can look at the raw computational power of a human brain in operations per second: estimates put that value between  $10^{12}$  to  $10^{14}$  operations per second [5].

Comparing that to the amount of instructions per second of a modern processor (around  $10^{11}$ ) the value does not seem much larger, but the current computational paradigm requires many instructions to mimic a single brain operation. Comparing the number of instructions needed for a single synapse (around 100 floating point operations [6]) yields a much lower bound of  $10^8$  synapses for a single modern day processor and  $10^{11}$  for large scale systems. Since a human brain typically contains  $10^{15}$  synapses [3] we are currently still at least six orders of magnitude away from obtaining the same complexity as a human brain in a single chip; there is also the added complexity of efficiency, since a human brain consumes around 20W of power, which is also orders of magnitude lower than the power used by artificial systems [3].

## 1.1 The Tail End of Moore's Law

Smaller and application specific machine learning algorithms have had significant progress with the computational power already available in numerous areas from speech recognition to autonomous vehicles [7]. Still demand for larger algorithms and the introduction of new paradigms is more than enough to push for larger processing capabilities and memory densities; in the past this hasn't been much of an issue since we were comfortable in the knowledge that transistor density was still progressing at an exponential pace. For the past few decades Eq. 1.1 defined the transistor count:

$$T_N \approx T_0 2^{\frac{N}{2}}.\tag{1.1}$$

In this equation  $T_N$  is the number of transistors at year n and  $T_0$  is the number of transistors at year zero. In the coming years this may no longer be the case [8, 9, 10, 11]: the enhancement in transistor density is starting to reach fundamental physical limitations. There is still room for improvement; we've been pushing these limits for some time now and keep developing clever new ways to stack more computational power in less area, and the graph in Fig. 1.1 shows that the transistor count keeps increasing to this date, due mainly to the increase in the number of cores, while all other performance aspects have started to reach their maximum level.

Figure 1.1: Trends in microprocessors until 2017 showing exponential transistor count growth while other performance figures start to plateau. Reprinted from [11] with permission under MIT License.

Thus it is starting to look like that this stacking will sooner rather than later reach its limit and we will need emerging technologies to keep the processing power increasing in an exponential fashion without having an improvement in device density.

#### **1.2** Non-Von Neumann Computing

How we build the vast majority of our computation devices also has a role in this issue. The Von Neumann architecture [12] has shaped computers as we know them; under this paradigm data operations are severely limited by the necessity of fetching the data and the instruction separately, to then after the operation have to save the data back. This limitation is known as the Von Neumann bottleneck [13, 14] and a report places that there are algorithms for which the majority of the time a CPU will actually be waiting for the memory [15]. It is important to mention that many of the machine learning algorithms are also bound by this architecture even though the originating point - the neuron - does not abide by it; this has inspired many designs for neuromorphic computing [16, 17] that can operate on data directly.

To solve some of these problems it was proposed that the Memristor could be applied to new paradigms in computation [18]. It exhibits switching speeds as low as nanoseconds [19] (and in a few cases even below that [20]), reliability [19], cost [21, 22], extremely low switching energy [23], and density [22, 24] that already have found applications not only in neuromorphic computing [25], but in many other fields [26, 27, 28, 29].

#### **1.3** Purpose of This Work

The groundwork for understanding Memristors was provided by Leon Chua in 1971 [30], by outlining constraints and providing examples (albeit done with the help of active components) of what should be the fourth fundamental passive element in circuit theory. His original work was interpreted and reproduced since to narrow the classification some [31, 32], but there is still much debate on what exactly is a Memristor [33, 34] going sometimes as far as say that no examples have been found or that the Memristor itself is not a fundamental passive circuit element. Efforts of modeling the electrical characteristics of fabricated devices have also been met with mixed

success [35, 36, 37, 38].

This work aims to provide a new understanding of how to describe Memristors and to solidify how to engineer and model them; both for specific application design and to understand phenomenological effects that change its behavior. It starts by reviewing the current state of the art in the area and some of the major applications, followed by how currently manufactured structures differ from a hypothetical ideal case; then it explores how to model those differences, what should the ideal case be, and outline the idea for memristance units. Finally, it proposes a novel memristive structure that can act as a Memtransistor - a transistor with a Memristor - that has an underlying High Electron Mobility Transistor (HEMT) which allows it to produce more compact and fast electronic neural networks.

#### 2. MEMRISTOR

In 1971, Leon Chua [30] noticed that from the standpoint of circuits there are four fundamental variables: current *i*, voltage *v*, charge *q* and flux-linkage  $\phi$ . Relations between these are well-known for most cases; between voltage and current we have the resistor, between charge and voltage we have the capacitor and between the flux-linkage and current we have the inductor. There is then a void between flux-linkage and charge: thus Chua postulated that a device must exist to fill it. Fig. 2.1 shows the relationship between the fundamental variables and the circuit elements that connects them.

Figure 2.1: Graph illustrating how passive devices connect charge, current, flux and voltage. Art by Parcly Taxel used under CC-BY-SA 3.0.

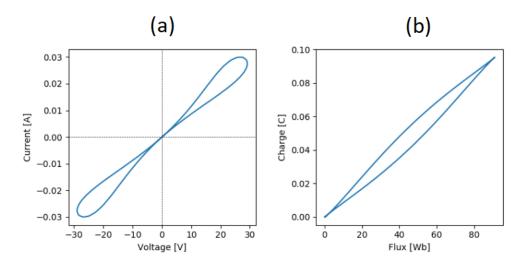

Chua postulated that this device could be charge-controlled or flux-controlled. The former device would display a relation between flux-linkage and charge dictated by  $M(q) = \frac{d\phi(q)}{dq}$  and the latter  $W(\phi) = \frac{dq(\phi)}{d\phi}$ . These constituent equations give rise to many characteristics that can be used to identify Memristors [31, 39, 32], of which the most known is the pinched hysteresis loop

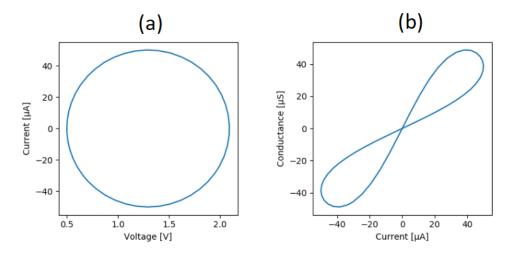

present in the voltage-current plane. The cause for this is a change in resistance due to the history of charge and/or flux-linkage through the device, which is why the device is dubbed "memory resistor". This hysteresis loop is also known as a "figure 8", shown in Fig. 2.2(a). Additionally the charge-flux-linkage plane is required to not be linear as shown in Fig. 2.2(b).

Figure 2.2: (a) *i*-*v* plane of a Memristor, showing the pinched hysteresis at the origin and symmetric hysteresis areas in the first and third quadrant. (b) q- $\phi$  plane of the same Memristor, showing non-linearity.

The applications of this device as memory are very obvious [40, 41], but there are many other functions it can perform: chaotic circuits [42, 43, 44] and cryptography [45, 46] are some of the examples. A particular interest for this work however are its applications in neuromorphic computing [47, 48, 49].

This is because it is reasonable to expect that fundamental elements have good integration densities; in principle it would be easier to achieve greater densities, for instance, of resistors and capacitors than it would be of an amplifier (since one amplifier contains multiple fundamental elements). Thus if a Memristor (or small set of Memristors) can represent a single synapse [49] then such devices manufactured to current transistor density levels would far outpace current machine learning algorithms performed in a classical computer, driving many on this field of research.

## 2.1 Physical Device Discovery

The initial theory allowed for a particularly large margin in implementation; it mostly outlined features that would be present in such device leaving most of the constituent equations open and awaiting development. Chua even demonstrated practical implementations of circuits that displayed memristive qualities but they were active, making use of amplifiers and other non-linear devices. Thus since the original proposal of such a device in 1971 researchers were working on developing a two-terminal passive Memristor, with the first major breakthrough appearing in 2008 when a device [50] was fabricated that complied with all of the constraints and thus is called the first Memristor. It is noting that the *i*-v curve of this device looked very different from the expected result illustrated by Fig. 2.2(a); major differences include the existence of an upper and lower boundary for possible instant resistances ( $R_{OFF}$  and  $R_{ON}$  respectively) and a sharp transition between these two boundaries. These cause the original "figure 8" curve to resemble more the triangular plot of Fig. 2.3.

Figure 2.3: *i*-*v* plot of a simulation of the first fabricated Memristor.

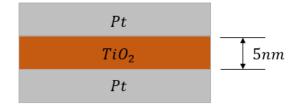

This device, whose structure is shown in Fig. 2.4, was built using a MIM structure of two platinum contacts separated by a titanium dioxide medium. The mechanism for memristance in this device is believed to be oxygen vacancies [50] contained in the insulator, introduced by its joule heating; since it is then the material responsible for the appearance of a memristance, it is referred to as the *switching medium*.

Figure 2.4: Sketch structure of the first fabricated Memristor.

### 2.2 Memristance Mechanisms

To better understand the causes for these differences one must first understand the mechanism for memristance. There is still some debate to all of the factors that can cause this change in resistance [33, 51, 52, 53, 54] and even to whether all of them can be considered memristance as defined by Chua [33, 34, 54], but many metal oxide Memristors1 operate under the theory that oxygen vacancies are created in the oxide [50] and their drift (or movement of the boundary between stoichiometric and oxygen-deficient oxide) causes a variation in instant resistance between two terminals.

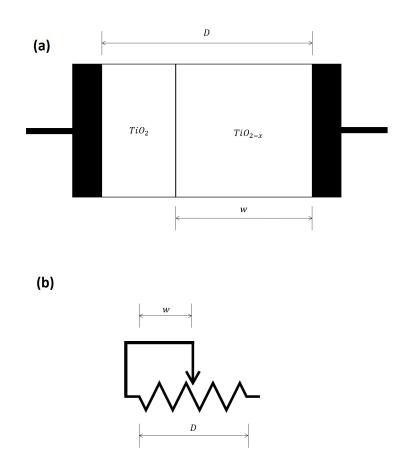

Figure 2.5: (a) Sketch of a simple memristive device depicting an oxygen-deficient layer and its boundary. The location of the boundary w relative to the total thickness D is dubbed State Variable (SV). (b) Analogy with a potentiometer.

The SV w is then the independent variable whose evolution controls all of the aspects of a Memristor. In this particular case, the SV is simply the position of the boundary between stoichiometric and oxygen-deficient layers as seen in Fig. 2.5(a) and a useful analogy is to think of this device as a potentiometer with a center contact having a position w relative to the total length of the resistive strip D which changes as current flows in the potentiometer itself.

In this scenario and considering a resistive strip which provides a linear change in resistance relative to the distance of the center contact to the extremities, the *i*-v characteristic of the potentiometer would be as in Eq. 2.1, where  $R_{total}$  is the maximum resistance and t is time.

$$v = \frac{w(t)}{D} i R_{total}.$$

(2.1)

There are two main predicted methods that cause a change in w: the history of charge q and the history of flux-linkage  $\phi$  through the device. In the former case we then aptly classify the Memristor as *charge controlled* and in the latter *flux controlled*. The vast majority of demonstrated devices appear to be charge controlled and the apparent scarcity of truly passive and magnetic controlled Memristors has led to claims that no Memristor has been found yet [33]. These rebuttals will be discussed at a later chapter.

In the case of the charge controlled Memristor then, the SV and consequently the instant resistance is a function of the history of the charge that has gone thorough the device, arriving then at Eq. 2.2.

$$\begin{cases} v = R(w(t))i. \\ w(t) = f(q(t)). \end{cases}$$

(2.2)

The evolution of R(w(t)) is heavily dependent on its type; for linear ionic drift for instance, Eq. 2.3 fully describes the Memristor by simply multiplying the charge through the device by a factor which depends on the total thickness of the switching layer and the mobility of the dopant  $\mu_V$ .

$$\begin{cases} v = R(w(t))i. \\ R(w(t)) = \left[\frac{R_{ON}w(t)}{D} + R_{OFF}\left(1 - \frac{w(t)}{D}\right)\right]. \\ \frac{dw(t)}{dt} = \frac{\mu_V R_{ON}i(t)}{D} \implies w(t) = \frac{\mu_V R_{ON}q(t)}{D}. \end{cases}$$

(2.3)

Many other mechanisms for memristance have been documented: the previous example concerns drift of ions - more specifically oxygen vacancies [55] - through an amorphous  $TiO_2$  film, but memristance has been also observed as the change in a conductive filament which can be formed by Joule heating [56, 57] or electrochemical redox [58, 59], metal-dopant movement inside chalcogenides [60], trapping of metallic nanoparticles in a polymer [61], conformational changes in single molecules [62], and Mott transitions of an insulator [63]. It is important to stress at this point that each of these mechanisms produces a different evolution of the state variable (due to different phenomenological mechanisms) and thus they have different governing equations; no one global model existed to this point that describes the Memristor.

### 2.3 Forming Cycle

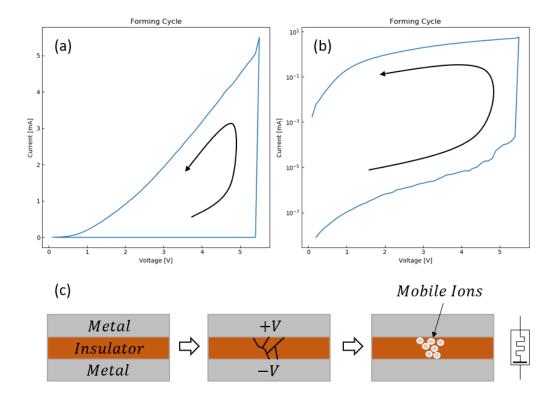

In certain cases, the switching medium require activation after the fabrication process using a cycle referred to as a forming cycle (FC). During this cycle a high voltage with a low compliance current is applied to the Memristor in order to inject enough energy via Joule heating into the oxide layer such that oxygen atoms are freed from the insulator and can then move depending on the history of charge through the device. An example of such cycle is shown in Fig. 2.6.

Figure 2.6: (a) and (b) i-v plot of a typical forming cycle for a metal-oxide Memristor. (c) Process sketch showing an initial middle layer going from insulator to switching medium due to application of a breakdown voltage.

In some devices, the FC is reversible by applying an even larger power: this higher temperature instead of creating defects and freeing dopants actually anneals the device and returns it to the original insulating state. These are denominated *unipolar* since switching between high and low resistance state can be accomplished with a signal that does not need to change polarity. As for *bipolar* devices, in general the forming cycle is irreversible; once done, the original insulating characteristic of the switching medium cannot be obtained again and resistance change is simply due to reversing the polarity (and thus the drift) of the applied field. In principle nothing prevents a device of being able to operate both as a unipolar and bipolar device, though usually only one mode of operation is chosen. Devices that do not require a FC are denominated forming-free. For the remainder of this work, unless otherwise noted, Memristors are either forming-free or are being

tested after the forming cycle has been applied to the devices.

### 2.4 Density

The simplicity and versatility of the structure allows it to achieve great densities, reported being as high as  $3.125 \ Gbit/mm^2$  [64]; this is an improvement of more than an order of magnitude from DRAM, which for a 20nm process can achieve a density of around  $0.15 \ Gbit/mm^2$  [65]. Table 2.1 compares current integration density of Memristors as used in memory versus other technologies.

| Technology                      | DRAM                    | SRAM                    | NAND Flash              | ReRAM (Memristor)    |

|---------------------------------|-------------------------|-------------------------|-------------------------|----------------------|

| Feature size [nm]               | 20 [65]                 | 10 [66]                 | 12 [67]                 | 35 [64]              |

| Density [Gbit/mm <sup>2</sup> ] | 0.15 [65]               | $\approx 0.02$ [66]     | 2 [67]                  | 3 [64]               |

| Read time [ns]                  | < 10 [68]               | < 10 [68]               | 25000 [68]              | $\approx 10$ [68]    |

| Write time [ns]                 | < 10 [68]               | < 10 [68]               | 200000 [68]             | $\approx 10$ [68]    |

| Endurance [cycles]              | > 10 <sup>15</sup> [68] | > 10 <sup>15</sup> [68] | > 10 <sup>15</sup> [68] | 10 <sup>5</sup> [68] |

| Retention time                  | 16ms [68]               | N/A                     | years                   | years [68]           |

Table 2.1: Comparison between memory technologies.

These performance figures that can already be achieved in memory applied to neuromorphic chips would represent a fantastic improvement in computational power.

## 2.5 Current Modeling and Simulation

In order to properly design systems that utilize Memristors it is necessary to model their behavior accurately. This is also particularly important since a proper model will also account for and explain the underlying physical effects responsible for the appearance of a memristance. There are currently many models for Memristors, as each model attempts to fit and explain a particular memristance mechanism [35]; one that stands out models the change in instant resistance measured as being bounded and non-linear [36, 69]. This changes Eq. 2.3 to Eq. 2.4 where p is a positive integer:

$$\begin{cases} x(t) = \frac{w(t)}{D}, \\ v = R(x)i, \\ R(x) = \left[ R_{ON}w(t + R_{OFF}(1 - x)) \right], \\ \frac{dx(t)}{dt} = \frac{\mu_V R_{ON}i(t)f(x)}{D}, \\ f(x) = 1 - (2x - 1)^p. \end{cases}$$

(2.4)

This window function f(x) guarantees that the velocity of mobile ions approaches zero as the state variable approaches either limit. This model explains the relation between the change in resistance, movement in the boundary of a doped region, and applied current to a level that has it being considered one of the main models for a Memristor. Biolek [36] further solidified its adoption by providing a translation from this mathematical model to SPICE, enabling a widely-used tool to be applied to these new devices.

### 3. NON-IDEALITY AND MODELING

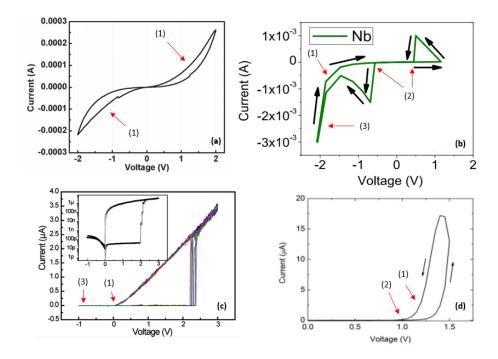

Despite being widely accepted, the Biolek model fails to fit to many fabricated Memristors that do not display the expected current-voltage plane "figure 8" but still check when compared against the expected fingerprints [31]. Some examples are shown in Fig. 3.1 and exhibit four main characteristics that illustrate the necessity for an expansion of this model: pinch point not at origin [70, 71], non-linear current-voltage relationship in saturation [70, 72, 71, 21], asymmetry of hysteresis loops between quadrants [70, 72, 71], and high leakage currents that do not appear to change the SV[70, 71].

Figure 3.1: Illustration of non-linearities present in many fabricated devices. (1) Non-linear current-voltage relationship in saturation. (2) Pinch point away from origin. (3) Asymmetry of hysteresis loops between quadrants. (4) High leakage currents that do not change SV. (a) Low cost Memristor based on  $TiO_2$ , adapted from [21]. (b)  $TaO_X$  Memristor, adapted from [71]. (c) Memristor crossbar array, adapted from [72]. (d) Memdiode for neuromorphic circuitry, adapted from [70].

Some of these behaviors were individually explained by previous models [38, 35, 73]; all of them contain non-linear behavior but in general these models make an effort to fit to experimental data observed from fabricated devices, at times neglecting the physical effect that introduces these non-linearities. As a consequence, their major shortcoming is not being able to fit to a variety of devices and driving conditions, being constrained to a single fabricated device under specific bias. Of particular interest is the fact that many of these models have exponential terms in them resembling the current-voltage characteristics of a diode. This is because by analyzing the structure of most Memristors, MIM with two different metals and a metal oxide as an insulator, one arrives at the band diagram shown in Fig. 3.2.

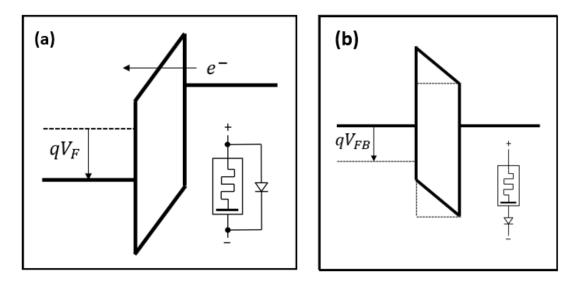

Figure 3.2: Band diagrams of a MIM Memristor. (a) Work function mismatch causing direct tunneling under certain bias conditions. (b) Work function mismatch causing a barrier to appear for injection of charges through the switching medium.

These non-linearities are a consequence of the ability of charges to move in and out of the switching layer and between contacts. The structure of the device then plays a major role in how these leakage and non-idealities show in the Memristor: thinner insulating layers will exhibit direct tunneling of charges from one contact to the other as seen in Fig. 3.2(a). In both in the case of CF or

dopant drift Memristors, at least one of the contacts will be further from the portion of the insulator with the mobile species; this effectively introduces a diode in series with an ideal Memristor, as seen in Fig. 3.2(b). Additionally, a work function mismatch may introduce asymmetries between positive and negative bias (effectively causing different diodes to appear depending on the bias and thus, an asymmetry in the format of the hysteresis).

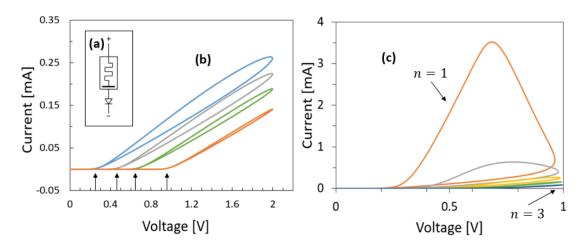

The presence of these parasitics will heavily alter the i-v characteristics of a Memristor. A similar study was done using passive elements [74], showcasing how the hysteresis area may change due to the addition of capacitors and inductors at different frequencies. That study never included or attempted to explain the non-linear phenomenon however, so it is useful then to explore the effects of various diode configurations with a Memristor. For the following cases the Biolek [36] model was used since it is a very good representation of a non-linear dopant drift, the mechanism which is believed to be the cause for the memristance in metal-oxide switching layers. The first case of interest is where there is an asymmetry to the Memristor structure that results in a diode in series as pictured in Fig. 3.3(a).

Figure 3.3: Simulations of a diode in series with a Memristor. (a) Circuit representation. (b) First quadrant response for varying built-in potentials: from left to right, 0.3V, 0.5V, 0.7V and 1V. (c) First quadrant response for varying ideality factors.

This is the case for when the Memristor is fabricated with top and bottom electrodes with a

large work function mismatch, if the distance between electrodes is large enough such that there is always a layer in the switching medium which remains insulating (and thus charges must tunnel to the conductive part), for Memristors with a complex structure such as MIIM or Chalcogenides so that charges only affect the switching layer after a certain bias, or for which the mechanism of memristance is a Mott transition. This is because a large potential is required to move switching material charges or to activate relevant transitions. A direct consequence is that if the mismatch is large enough the device will operate only in the first quadrant (unipolar) since no reverse current takes place; in such cases, another mechanism must be present in order to relax the Memristor back to its original state. For instance, in Mott transition Memristors that mechanism is simply the cooling of the switching medium by removing the bias; in some other unipolar devices the CF is destroyed via Joule heating induced by a large stimulus.

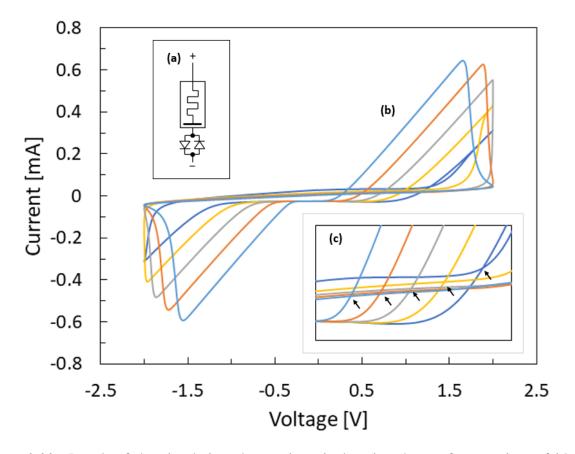

What can be seen then in Fig. 3.3(b) is that the built-in voltage  $V_0$  of the series diode has a major impact in the perceived pinch point of the current-voltage plane. The larger the  $V_0$ , the further away from the origin the pinch point will be in the first quadrant; not only that, but it also obviously causes a voltage drop that limits charge and flux at the ideal Memristor such that the hysteresis area is smaller for the same driving voltage. Fig. 3.3(c) showcases the impact of different ideality factors. Higher ideality factors strangle the available flux and current for the memristive device, lowering significantly the hysteresis area. Of note is that ideality factors higher than 2 were simulated; this is due to the fact that when fitting to practical devices, many times these values were observed. This has been observed before in both Si [75, 76, 77] and GaN [78] with a variety of causes, so it is reasonable to assume that devices that were not manufactured specifically to be diodes could have such high ideality factors. One can extend this analysis for a second anti-parallel diode, where the curves will extend to the third quadrant with similar effects.

In some cases the switching material is thin enough (or the bias large enough) such that charges can pass through it without affecting the SV, acting as a leakage current. This situation is best represented by the parallel diode shown in Fig. 3.4(a).

Figure 3.4: Simulations of a diode in parallel with a Memristor. (a) Circuit representation. (b) Response for varying built-in potentials: from left to right, 0.3V, 0.5V, 0.7V and 1V. (c) Response for varying ideality factors.

Once again due to the asymmetric characteristic of the parasitic property, changes in a single quadrant are seen while another quadrant is largely unaffected. The largest impact of a parallel diode is the existence of a secondary path for charges to pass which do not alter the SV of the Memristor. This causes significant alteration on the shape of the hysteresis area in a manner which is inversely proportional to the ideality factor and can cause one to incorrectly identify when the Memristor is changing states; the rise in current is usually associated with the Memristor "turning on" (changing to a lower resistance state), while one can clearly see from Fig. 3.4 (b) and (c) that for various cases, even though the state variable is at a point where it hasn't started changing yet, current is already at significant levels.

Similarly to the case in Fig. 3.3, hysteresis area is significantly altered and an assymetry is introduced between the first and third quadrant. It is possible to neglect the effects of this parasitic however by simply driving the device at levels below where tunneling would occur.

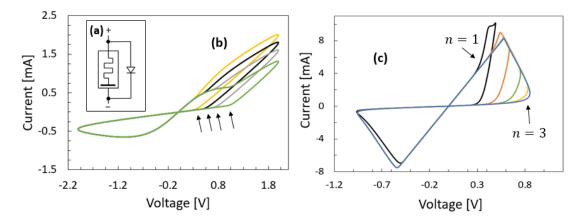

While devices have been observed that can be explained by either only a series diode or a parallel diode, in many cases a combination of both is more adequate. Fig. 3.5 shows two possible combinations of two diodes that result in significant change in the shape and magnitude of the hysteresis area.

Figure 3.5: Simulations of a combination of diodes with a Memristor. (a) Diode in parallel with Memristor. (b) Diode in parallel with Memristor-diode.

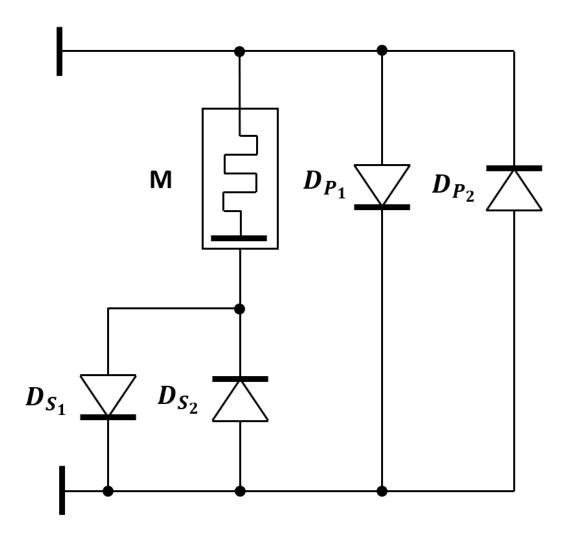

The reader can utilize the knowledge acquired from these simulations to extrapolate for other cases where the alterations are on the third quadrant; all that is necessary is to switch the polarity of the diodes being used. Multiple different combinations of diodes can be used to explain the nonidealities in a Memristor, but there is a format which phenomenologically explains them while remaining relatively simple and effective. It is shown in Fig. 3.6. In it, there are four diodes: two  $(D_{S_1} \text{ and } D_{P_1})$  are responsible for the changes in the first quadrant (positive bias) while the other two  $(D_{S_2} \text{ and } D_{P_2})$  are responsible for changes in the third quadrant (negative bias).  $D_{P_1}$  and  $D_{P_2}$  represent the tunneling current that passes from one metal contact to another in a MIM structure without changing the SV of the switching medium; in general they should be similar diodes, but use of different metals and geometries for each contact may cause them to be significantly different.  $D_{S_1}$  and  $D_{S_2}$  represent the barrier that exists between each contact and the mobile ions in the switching medium; these will almost always significantly different from each other since usually one contact will be closer to the mobile ions than the other. All of these parasitics are largely affected by all of the process in manufacturing a Memristor, including the forming cycle. The same device subject to a different forming cycle should see differences in the parasitic components.

Figure 3.6: Full device model for fabricated Memristors including parasitic diodes.

### 3.1 Fitting Procedure

To validate the model one can use it to simulate various fabricated devices. Fitting to experimental data is done by iteratively modifying all of the parasitic diodes and comparing the result to the original data: there are five parameters that should be used for the Memristor ( $R_{ON}$ ,  $R_{OFF}$ ,  $R_{INIT}$ ,  $\mu_V$ , and D) and three for each parasitic diode ( $V_0$ ,  $I_S$ , and n). The leakage conduction path diodes  $D_{P_1}$  and  $D_{P_2}$  are usually the easiest to fit since they do not alter the state variable and thus appear outside of the hysteresis area. Fig. 3.7 shows how the high currents at the peaks of voltage actually correspond very closely to the parallel conduction path.

Figure 3.7: Illustration of the parallel leakage path on the diode curve and first approximations for parasitics variables. Upper inset shows the equivalent circuits and lower inset shows impact of changing ideality factor on parallel diode.

Both  $V_0$  for the diodes and  $R_{ON}$  and  $R_{OFF}$  (or at times  $R_{INIT}$ ) for the Memristor can be defined closely from the *i*-*v* plot as well. All other variables are defined iteratively by analyzing the error between the simulation and the empirical data and doing a gradient descent for each in turn. It is worth mentioning that this method did not always converge, requiring at times manual fitting by trial and error.

#### 3.2 **Resulting Fits**

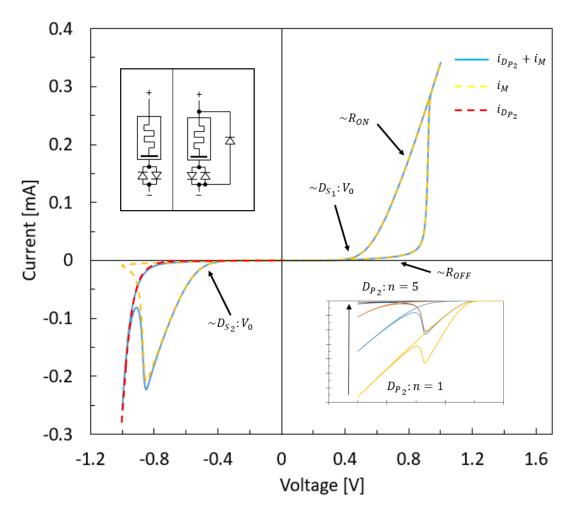

Using this model and fitting methodology, Fig. 3.8 shows a Memristor fabricated with  $Nb_2O_5$  for use in neuromorphic circuitry. It showcases how the pinch point is not only away from zero but actually extends all the way to the threshold, exactly as a diode would. For clarity and to further the understanding of how the diodes change the device, the individual currents through both branches are shown as well as the current of the overall device. One can see how a single diode in series with the Memristor fails to explain the device, requiring a second diode in parallel.

Figure 3.8: Memdiode for neuomorphic applications fit. (a) Fit overlaid in original published data adapted from [70] for comparison. (b) Simulation in LTSpice using the proposed model showing separate branch currents. In this case  $n_{D_{S_1}} = 1.7$ ,  $V_{0_{D_{S_1}}} = 0.75V$ ,  $n_{D_{P_1}} = 1.6$ ,  $V_{0_{D_{P_1}}} = 1.2V$ ,  $R_{ON} = 7k\Omega$ ,  $R_{OFF} = 800k\Omega$ ,  $\mu_v = 0.8ncm^2s^{-1}V^{-1}$ .

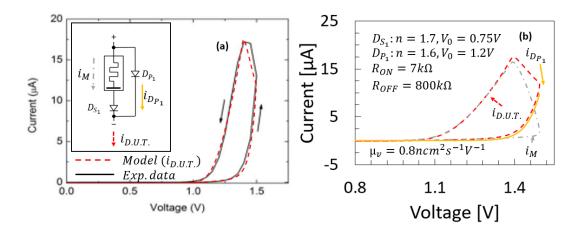

For unipolar Memristors, only a single quadrant has a hysteresis. This is the case of Fig. 3.9, where the asymmetry in the switching material and electrodes can be explained by placing a single "ideal" Memristor in series with a diode. It is important to note in these cases that other methods must be available to modify the state variable of the Memristor back to the original state if it is intended for the device to switch between states. To better illustrate this Fig. 3.9 shows in green how a bipolar Memristor without a the series diode has a hysteresis area in the third quadrant which

"resets" the SV back to the initial state. The presence of the diode (and thus of hysteresis only on the first quadrant) imply that there is no way to force reverse current and thus return the Memristor to that state if the switching medium is bipolar.

Figure 3.9: Crossbar array for neuromorphic applications fit. (a) Fit overlaid in original published data adapted from [72] for comparison. (b) Simulation in LTSpice using the proposed model. In this case  $n_{D_{S_1}} = 1.5$ ,  $V_{0_{D_{S_1}}} = 0V$ ,  $R_{ON} = 800k\Omega$ ,  $R_{OFF} = 1M\Omega$ ,  $\mu_v = 0.5ncm^2 s^{-1}V^{-1}$ .

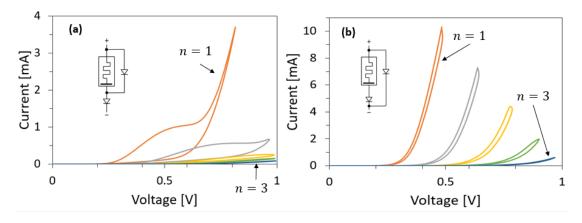

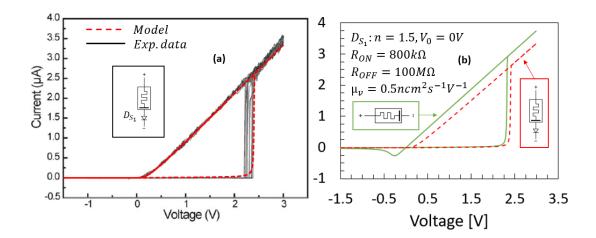

Fig. 3.10 shows a Memristor fabricated with two W electrodes and a  $TiO_2$  switching material; this shows how since the device is more symmetric hysteresis now shows in the first and third quadrant making the Memristor *bipolar*. Thus diodes are needed for both forward and reverse conduction, and while the expectation would be for both sets of diodes to be identical because of symmetry, the top and bottom electrodes do not have the same area. This leads to the differences seen in the parameters.

Figure 3.10: Low cost titanium oxide Memristor fit. (a) Fit overlaid in original published data adapted from [21] for comparison. (b) Simulation in LTSpice using the proposed model. In this case  $n_{D_{P_1}} = 7$ ,  $V_{0_{D_{P_1}}} = 0V$ ,  $n_{D_{P_2}} = 3.7$ ,  $V_{0_{D_{P_2}}} = 0V$ ,  $n_{D_{S_1}} = 1.7$ ,  $V_{0_{D_{S_1}}} = 0V$ ,  $n_{D_{S_2}} = 3$ ,  $V_{0_{D_{S_2}}} = 0V$ ,  $R_{ON} = 10k\Omega$ ,  $R_{OFF} = 300k\Omega$ ,  $\mu_v = 20pcm^2s^{-1}V^{-1}$ .