# POWER MANAGEMENT ICS FOR INTERNET OF THINGS, ENERGY HARVESTING AND BIOMEDICAL DEVICES

A Dissertation

by

## XIAOSEN LIU

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Edgar Sánchez-Sinencio

Committee Members, Prasad Enjeti

Kamran Entesari Alexander G. Parlos

Head of Department, Miroslav M. Begovic

August 2016

Major Subject: Electrical Engineering

Copyright 2016 Xiaosen Liu

#### **ABSTRACT**

This dissertation focuses on the power management unit (PMU) and integrated circuits (ICs) for the internet of things (IoT), energy harvesting and biomedical devices. Three monolithic power harvesting methods are studied for different challenges of smart nodes of IoT networks. Firstly, we propose that an impedance tuning approach is implemented with a capacitor value modulation to eliminate the quiescent power consumption. Secondly, we develop a hill-climbing MPPT mechanism that reuses and processes the information of the hysteresis controller in the time-domain and is free of power hungry analog circuits. Furthermore, the typical power-performance tradeoff of the hysteresis controller is solved by a self-triggered one-shot mechanism. Thus, the output regulation achieves high-performance and yet low-power operations as low as 12 μW. Thirdly, we introduce a reconfigurable charge pump to provide the hybrid conversion ratios (CRs) as  $1\frac{1}{3}$ × up to 8× for minimizing the charge redistribution loss. The reconfigurable feature also dynamically tunes to maximum power point tracking (MPPT) with the frequency modulation, resulting in a two-dimensional MPPT. Therefore, the voltage conversion efficiency (VCE) and the power conversion efficiency (PCE) are enhanced and flattened across a wide harvesting range as 0.45 to 3 V. In a conclusion, we successfully develop an energy harvesting method for the IoT smart nodes with lower cost, smaller size, higher conversion efficiency, and better applicability.

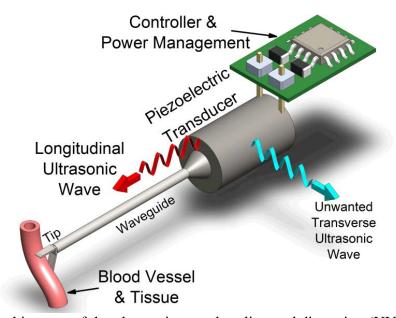

For the biomedical devices, this dissertation presents a novel cost-effective automatic resonance tracking method with maximum power transfer (MPT) for piezoelectric transducers (PT). The proposed tracking method is based on a band-pass filter (BPF) oscillator, exploiting the PT's intrinsic resonance point through a sensing bridge. It guarantees automatic resonance tracking and maximum electrical power converted into mechanical motion regardless of process variations and environmental interferences. Thus, the proposed BPF oscillator-based scheme was designed for an ultrasonic vessel sealing and dissecting (UVSD) system. The sealing and dissecting functions were verified experimentally in chicken tissue and glycerin. Furthermore, a combined sensing scheme circuit allows multiple surgical tissue debulking, vessel sealer and dissector (VSD) technologies to operate from the same sensing scheme board. Its advantage is that a single driver controller could be used for both systems simplifying the complexity and design cost. In a conclusion, we successfully develop an ultrasonic scalpel to replace the other electrosurgical counterparts and the conventional scalpels with lower cost and better functionality.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my advisor Dr. Edgar Sánchez-Sinencio. His knowledgeable advices and wise judgement helped me to become a professional researcher. He also gives me generous support, sufficient financial support and a lot of academic opportunities, which are vital for my achievements.

I would like to thank my committee members, Dr. Prasad Enjeti, Dr. Kamran Entesari, Dr. Alexander G. Parlos, and Dr. Ohannes Eknoyan, for their guidance and support throughout the course of this research. Their insightful opinions encourage me to improve my research continuously.

Thanks also go to the department faculty and staff for making my time at Texas

A&M University a great experience: Dr. Jose Silva-Martinez, Dr. Sam Palermo, Tammy

Carda, Melissa Sheldon, Anni Brunker, and Ella Gallagher.

I want to extend my gratitude to the Intel, Covidien, and Medtronic Corporation.

Their generous funding and technical supports greatly enhance the research of our group.

I would like to specifically thank: Lilly Huang, Krishnan Ravichandran, James Gilbert,

Daniel A. Friedrichs, and Keith Malang. The research collaborations between us are my exciting memory.

In the Analog & Mixed Signal Center, I would like to sincerely thank my colleague students: Joselyn Torres, who is the shepherd leading me into the track of mixed signal IC design, Adrian I. Colli-Menchi, with whom I successfully achieved the biomedical project and finalize a patent. My deepest gratitude goes to Salvador Carreon,

Congyin Shi, Jiayi Jin, Kyoohyun Noh, Chen Li, Mohamed Ali Abouzied Jr, Jun Yan, Johan Estrada, Jorge Zarate, and Fernando Lavalle.

I also want to gratefully thank the professors during my bachelor and master program: Dr. Linhui Cai from Nanjing Normal University, Dr. Xiaohan Sun, Dr. Guoliang Du, Dr. Yongming Tang from Southeast University, Dr. Kevin J. Chen, Dr. Wing-Hung Ki from Hong Kong University of Science & Technology. Without your academic advices and training, I can never go to study in Texas A&M University.

Finally, I would like to thank my mother and father, Huailin Gong and Yunlin Liu, for their strong encouragement, and my wife, Haoling Zhang for her patience and unconditional love. Thanks to my daughter Yimu, who reminds me every day what the important things in life are.

## NOMENCLATURE

BPF Band-pass Filter

CP Charge Pump

CR Conversion Ratio

CLK Clock

EH Energy Harvesting

FSL Fast Switching Limit

IC Integrated Circuit

MFB Multiple Feedback

PFM Pulse-frequency Modulation

PMU Power Management Unit

PT Piezoelectric Transducer

PWM Pulse-width Modulation

RF Radio Frequency

SMPC Switched Mode Power Converter

SSL Slow Switching Limit

VCE Voltage Conversion Efficiency

PCE Power Conversion Efficiency

UVSD Ultrasonic Vessel Sealing and Dissecting

# TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii                                         |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                               | iv                                         |

| NOMENCLATURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vi                                         |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vii                                        |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xi                                         |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | xx                                         |

| 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                          |

| 1.1 Internet of Things and the Hardware Bottleneck 1.2 Characteristics of Energy Sources 1.2.1 Photovoltaic Cell 1.2.2 Thermoelectric Generator 1.2.3 Piezoelectric Transducer 1.2.4 Radio Frequency Electromagnetic Wave 1.3 Design Challenges of the Energy Harvesting 1.3.1 Maximum Power Point Tracking Technique 1.3.2 Impedance Tuning 1.3.3 Fully Integration 1.3.4 Output Regulation 1.3.5 Charge Redistribution Loss 1.4 IoT and Hardware Applications 1.5 Conclusion | 3<br>6<br>11<br>13<br>14<br>15<br>16<br>17 |

| 2 DC-DC POWER MANAGEMENT TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24                                         |

| 2.1 Inductor-based SMPC  2.1.1 Principle and Electrical Model  2.1.2 Pulse-width Modulation  2.2 Switched Capacitor SMPC                                                                                                                                                                                                                                                                                                                                                       | 24<br>26<br>30                             |

| <ul> <li>2.2.1 Principle and Electrical Model</li> <li>2.2.2 Equivalent Resistance of Switched Capacitor DC-DC Converters</li> <li>2.2.3 Dickson Charge Pump &amp; Gate Control</li> </ul>                                                                                                                                                                                                                                                                                     |                                            |

|   | 2.2.4 Serial-parallel, Fibonacci, and Doubler Charge Pump        | 35 |

|---|------------------------------------------------------------------|----|

|   | 2.2.5 Mathematical Analysis and Dynamic Behavior                 |    |

|   | 2.2.6 Design Consideration and Procedure of Voltage Doubler      | 39 |

|   | 2.3 Low Dropout Regulator                                        | 41 |

|   | 2.4 Conclusion                                                   | 44 |

| 3 | THE STATE-OF-THE-ART MAXIMUM POWER POINT TRACKING                | 45 |

|   | 3.1 Current Sensing MPPT                                         | 45 |

|   | 3.1.1 Architecture of the Proposed Energy Harvesting System      |    |

|   | 3.1.2 Energy Efficient MPPT with the Hill-Climbing Algorithm     |    |

|   | 3.1.3 Capacitor Value Modulation                                 |    |

|   | 3.1.4 Efficiency Limit by the Charge Redistribution Loss         |    |

|   | 3.2 Energy Efficient MPPT                                        |    |

|   | 3.2.1 Architecture of the Energy Harvester with Time-domain MPPT | 52 |

|   | 3.2.2 3× Charge Pump with CVM                                    |    |

|   | 3.2.3 Hysteresis Output Regulation                               | 56 |

|   | 3.2.4 Time-domain Quantization for MPPT                          | 58 |

|   | 3.2.5 Hill-Climbing Algorithm                                    |    |

|   | 3.3 Two-dimensional MPPT                                         | 62 |

|   | 3.3.1 Architecture of the Proposed Energy Harvester              | 62 |

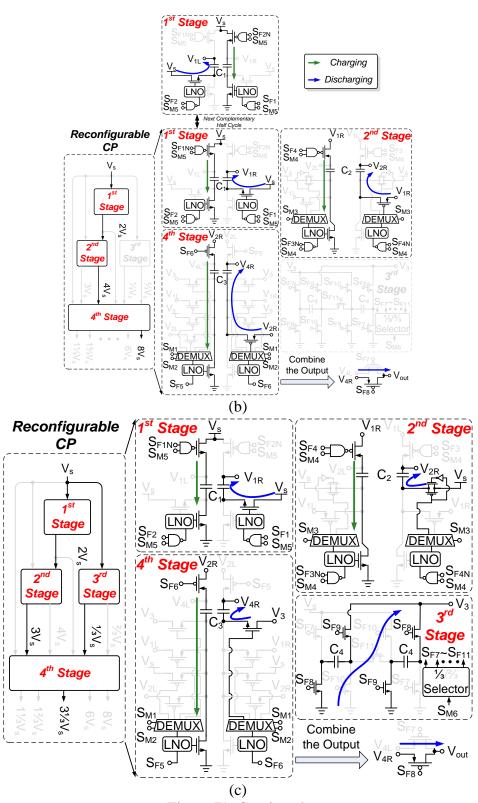

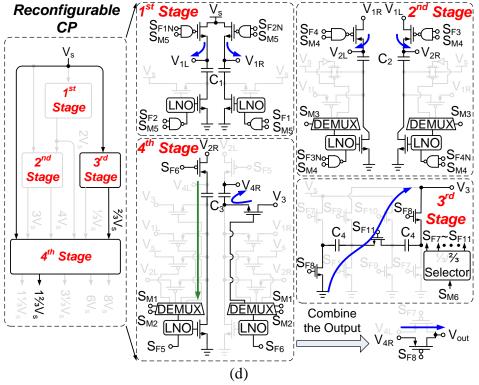

|   | 3.3.2 Charge Redistribution Loss and Reconfigurable Charge Pump  | 63 |

|   | 3.3.3 Constant-on Time Regulation and Power Sensing              | 66 |

|   | 3.3.4 Principle of the Two-Dimensional MPPT                      | 69 |

|   | 3.4 Conclusion                                                   | 71 |

| 4 | CIRCUIT DESIGN TECHNIQUES AND IMPLEMENTATIONS                    | 73 |

|   | 4.1 EH System with Current Sensor and CVM MPPT                   | 73 |

|   | 4.1.1 Circuit Implementation & Design Procedure                  | 73 |

|   | 4.1.1.1 Nested Voltage Tripler                                   |    |

|   | 4.1.1.2 MPPT Mechanism and FSM Design                            | 77 |

|   | 4.1.1.3 Ultra-Low Power Current Sensing Technique                | 79 |

|   | 4.1.1.4 MPPT Processing Circuit                                  |    |

|   | 4.1.1.5 Digital Programmable Capacitor Bank of CVM               | 83 |

|   | 4.1.2 Measurement Results                                        |    |

|   | 4.1.3 Conclusion                                                 | 91 |

|   | 4.2 EH System with Hysteresis Regulation and Time-domain MPPT    | 91 |

|   | 4.2.1 Circuit Implementation & Design Procedure                  |    |

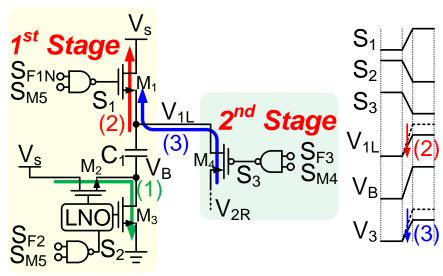

|   | 4.2.1.1 Compact Nested Voltage Doubler                           |    |

|   | 4.2.1.2 Startup & Auxiliary Bias Circuit                         |    |

|   | 4.2.1.3 Hysteresis Controller                                    | 96 |

|   | 4.2.1.4 Implementation of FSM and TDC Converter                  | 98 |

|   | 4.2.2 Measurement Results                                        | 99 |

| 4.2.3 Conclusion                                                | 107 |

|-----------------------------------------------------------------|-----|

| 4.3 EH System with Two-Dimensional MPPT                         | 108 |

| 4.3.1 Circuit Implementation & Design Procedure                 | 108 |

| 4.3.1.1 Reconfigurable 3-stage Voltage Doubler                  | 109 |

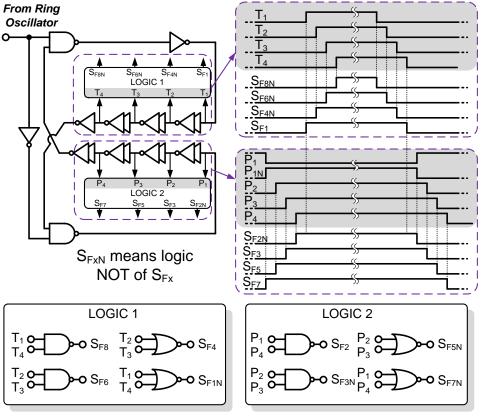

| 4.3.1.2 Non-overlapping Switching Signal Planning               | 113 |

| 4.3.1.3 Constant-on Regulation                                  | 115 |

| 4.3.1.4 Two-channel S/H MPPT Arbiter                            | 116 |

| 4.3.1.5 Finite-state Machine                                    | 118 |

| 4.3.2 Measurement Results                                       | 120 |

| 4.3.3 Conclusion                                                |     |

| 4.4 EH System with a Single-cycle MPPT without Storage Capacito |     |

| 4.4.1 Motivation and Innovation                                 |     |

| 4.4.2 Single-cycle Regulation and MPPT                          |     |

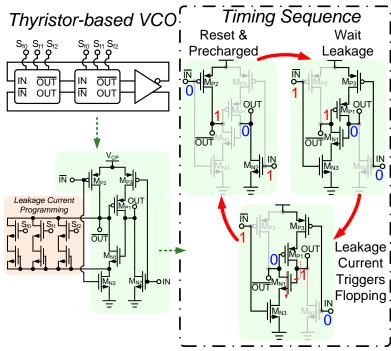

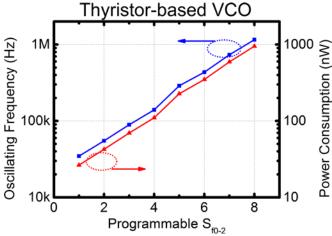

| 4.4.3 Thyristor-based VCO                                       | 134 |

| 4.5 Conclusion                                                  | 136 |

| 5 DOWED MANAGEMENT FOR ELECTRICAL COALREL                       | 120 |

| 5 POWER MANAGEMENT FOR ELECTRICAL SCALPEL                       | 138 |

| 5.1 Background of UVSD System                                   | 138 |

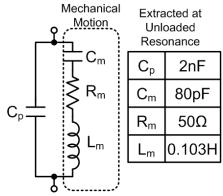

| 5.1.1 Characteristics of the PT                                 | 138 |

| 5.1.2 Design Challenges                                         |     |

| 5.2 Discrete Version: Automatic Resonance Tracking Technique    |     |

| 5.2.1 Motional Current Sensing Bridge                           |     |

| 5.2.2 Automatic Resonance Tracking Scheme                       |     |

| 5.2.2.1 Architecture of the Proposed Scheme                     |     |

| 5.2.2.2 Automatic Resonance Tracking with the BPF Oscillator    |     |

| 5.2.2.3 Amplitude Control                                       |     |

| 5.2.3 Ultrasonic VSD System Implementation                      | 149 |

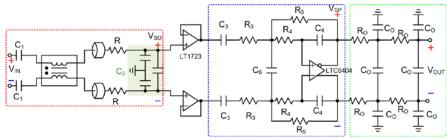

| 5.2.3.1 BPF Oscillator Implementation                           | 150 |

| 5.2.3.2 Amplitude Control Circuits                              | 151 |

| 5.2.3.3 Stability of the UVSD with the PI Compensator           | 152 |

| 5.2.4 Experimental Results                                      |     |

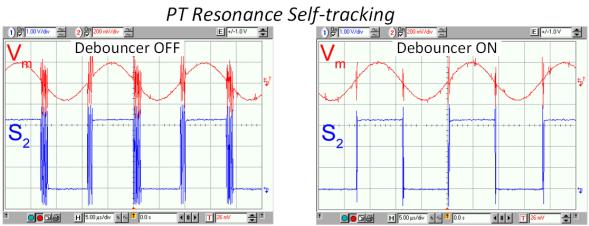

| 5.2.4.1 Power Regulation with Various References                | 155 |

| 5.2.4.2 Experimental Results in Glycerin                        |     |

| 5.2.4.3 Accuracy of the Automatic Resonance Tracking            | 160 |

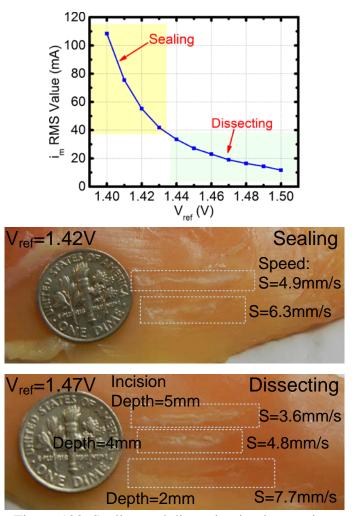

| 5.2.4.4 Experimental Results in Chicken Tissue                  | 161 |

| 5.3 Integrated Version: IC Implementation                       |     |

| 5.3.1 Sliding-mode Power Management Architecture                | 162 |

| 5.3.2 Monolithic Integration and Measurement Results            |     |

| 5.4 Conclusion                                                  |     |

| 6 SIGNAL PROCESSING FOR UNIFIED RF AND UVSD SYSTEM.             | 172 |

|                                                                 |     |

| 6.1 Background                                                  | 172 |

| 6.1.1 Motivation                                            | 172 |

|-------------------------------------------------------------|-----|

| 6.1.2 Challenges of the Conventional V and I Sensing        |     |

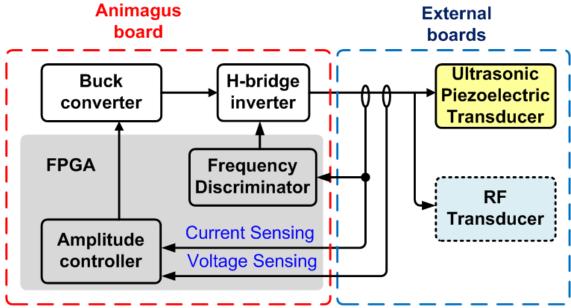

| 6.2 Sensing Scheme for VSD System with RF & US Transducers  |     |

| 6.2.1 Rogowski Coil Current Sensor                          |     |

| 6.2.2 Capacitive Voltage Divider                            |     |

| 6.3 I Sensing with 2 <sup>nd</sup> -order Active-RC Filter  |     |

| 6.4 V Sensing with 2 <sup>nd</sup> -order Tom-Thomas Filter |     |

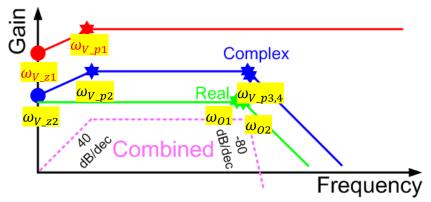

| 6.4.1 Real Zeros/Poles Matching                             |     |

| 6.4.1.1 Input Stage                                         | 183 |

| 6.4.1.2 Signal Processing Stage                             |     |

| 6.4.1.3 Output RC filter                                    | 184 |

| 6.4.1.4 Biquad BPF Matching                                 | 186 |

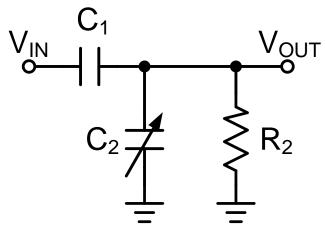

| 6.4.2 V Sensing with 2 <sup>nd</sup> -order MFB Filter      | 188 |

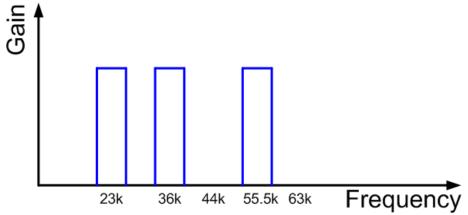

| 6.5 Digital Frequency Discriminator in FPGA                 | 189 |

| 6.5.1 Challenge in Frequency Discriminator                  | 189 |

| 6.5.2 IIR Band-pass Filter                                  | 192 |

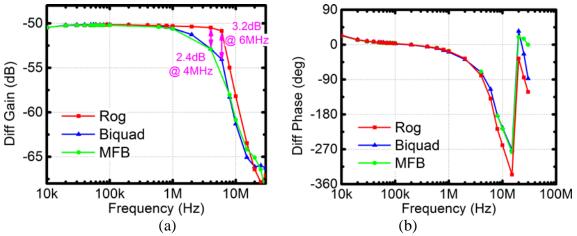

| 6.6 Measurement Results                                     | 193 |

| 6.6.1 Simulation & PCB Implementation                       | 193 |

| 6.6.2 Testing Setup & Approach                              | 197 |

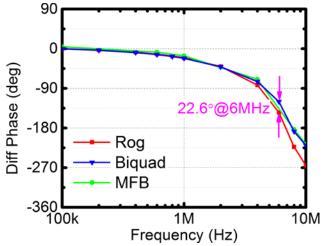

| 6.6.2.1 Matched Sensing Performance                         | 198 |

| 6.6.2.2 Matched Common-mode Performance                     | 199 |

| 6.7 Conclusion                                              | 200 |

| 7 CONCLUSIONS                                               | 201 |

| 7.1 Energy Harvesting for Internet of Things                | 201 |

| 7.2 Power Management for Biomedical Devices                 |     |

| REFERENCES                                                  | 203 |

| APPENDIX                                                    | 224 |

# LIST OF FIGURES

|                                                                                                                        | Page |

|------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1. Conceptual block diagram of the IoT smart nodes with energy harvesting technique.                            | 2    |

| Figure 2. The physical structure of PV cells and their operating mechanism                                             | 3    |

| Figure 3. (a) The electrical characteristics of PV cells, and (b) the equivalent model.                                | 4    |

| Figure 4. Physical structure of thermoelectric generators.                                                             | 6    |

| Figure 5. Architecture of commercial TEG products.                                                                     | 7    |

| Figure 6. (a) Electrical model and (b) transfer curves of generic TEGs.                                                | 7    |

| Figure 7. Structure of common piezoelectric transducers.                                                               | 10   |

| Figure 8. Block diagram of a RF energy harvester.                                                                      | 11   |

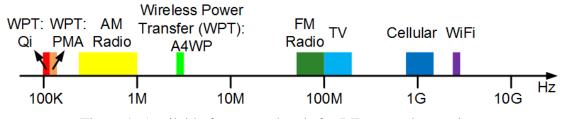

| Figure 9. Available frequency bands for RF energy harvesting.                                                          | 12   |

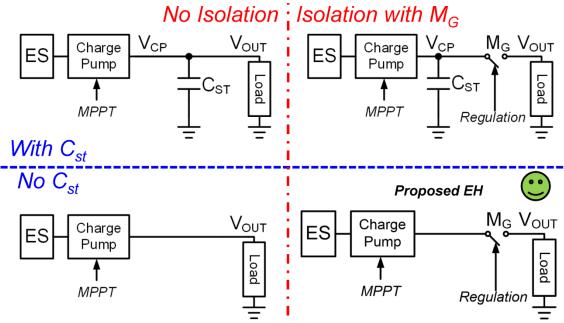

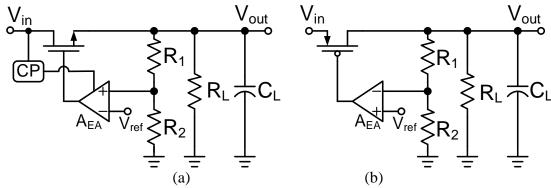

| Figure 10. Four different topologies of general energy harvesters.                                                     | 16   |

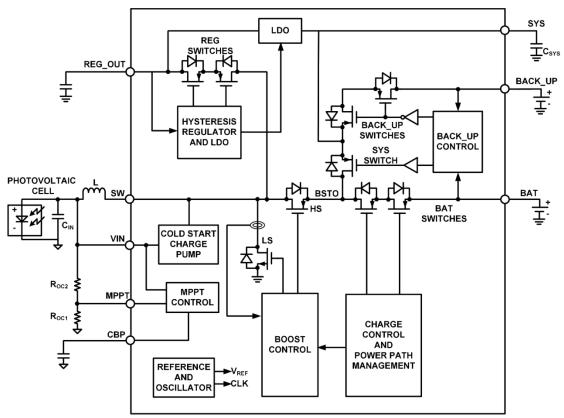

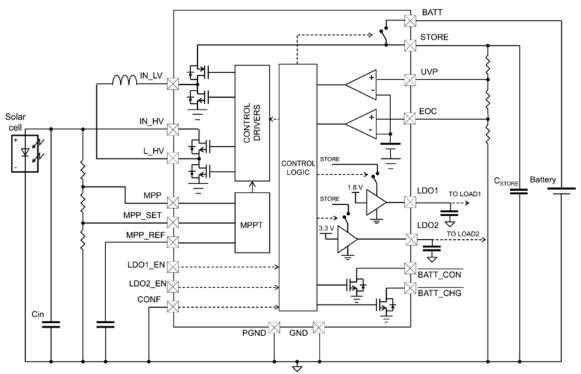

| Figure 11. Functional block diagram of boost-LDO energy harvester.                                                     | 19   |

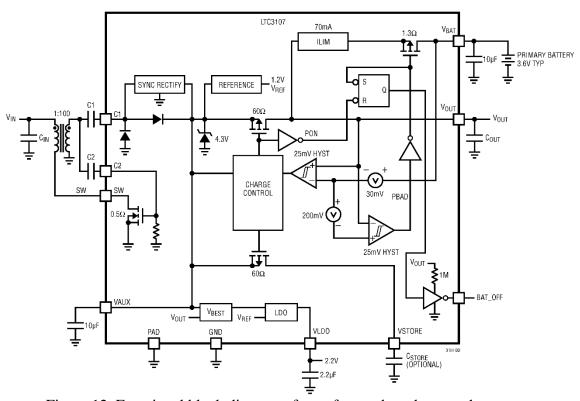

| Figure 12. Functional block diagram of transformer-based energy harvester                                              | 20   |

| Figure 13. Functional block diagram of buck-boost energy harvester                                                     | 21   |

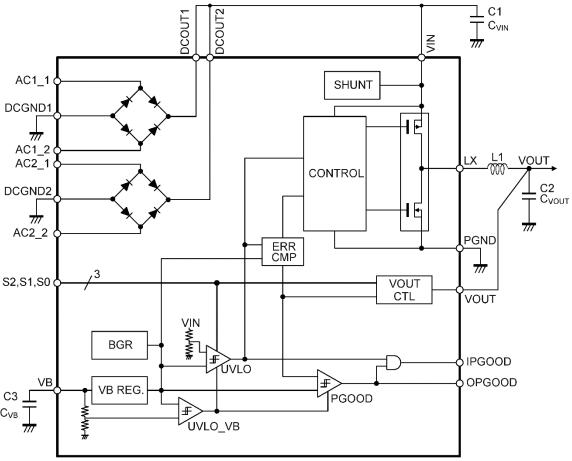

| Figure 14. Functional block diagram of AC-DC energy harvester.                                                         | 22   |

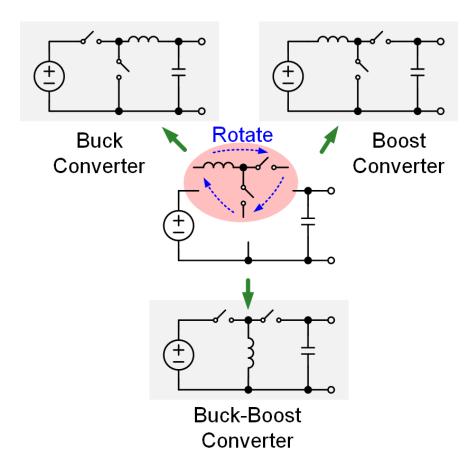

| Figure 15. General structures of inductive DC-DC power converters                                                      | 24   |

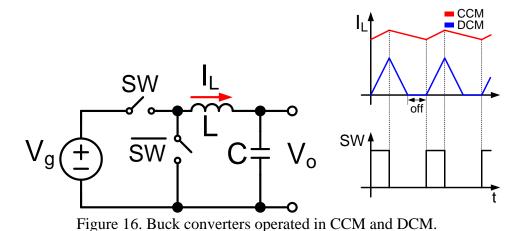

| Figure 16. Buck converters operated in CCM and DCM                                                                     | 25   |

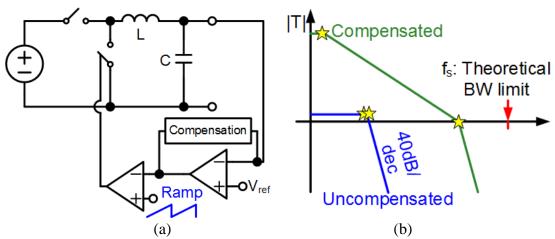

| Figure 17. (a) Conceptual voltage mode negative feedback loop with PWM, and (b) its small signal analysis in s-domain. | 26   |

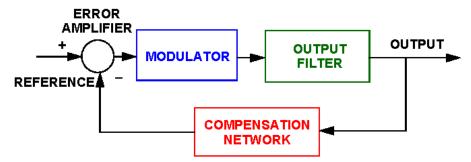

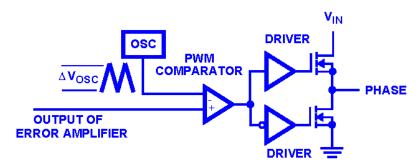

| Figure 18. Basic block diagram of the buck converter.                                                                  | 28   |

| Figure 19. Detailed architecture of the PWM modulator                                                                  | 28   |

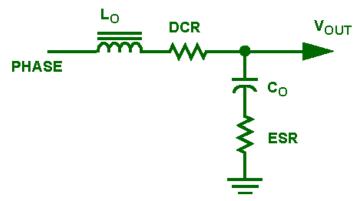

| Figure 20. Detailed architecture of the output filter                                                                  | 29   |

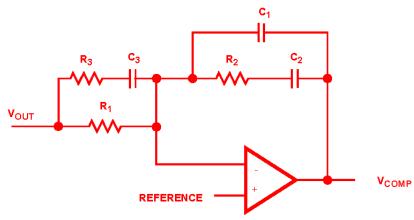

| Figure 21. | Detailed architecture of the error amplifier and the Type-III compensator                                                                                         | 29 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

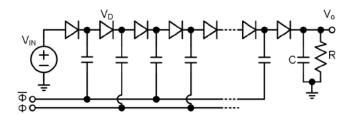

| Figure 22. | Switched capacitor SMPC composed of diodes and capacitors.                                                                                                        | 31 |

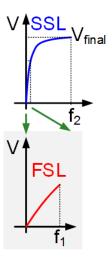

| Figure 23. | Slow-switching limit and fast-switching limit of charge pump                                                                                                      | 31 |

| Figure 24. | Architecture of the Dickson charge pump.                                                                                                                          | 34 |

| Figure 25. | Reuse of the higher gate control voltage from the following stages                                                                                                | 35 |

| Figure 26. | Architecture of the serial-parallel charge pump.                                                                                                                  | 36 |

| Figure 27. | Architecture of the Fibonacci charge pump.                                                                                                                        | 37 |

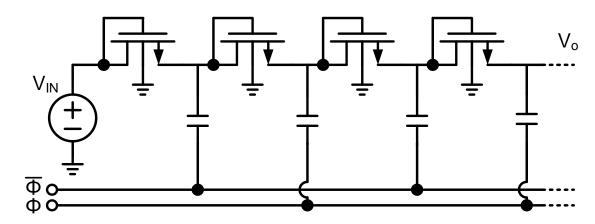

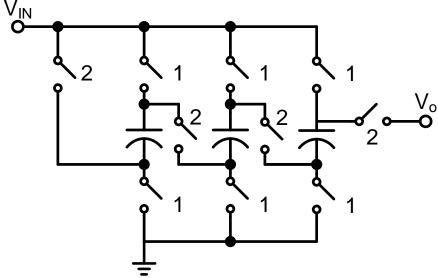

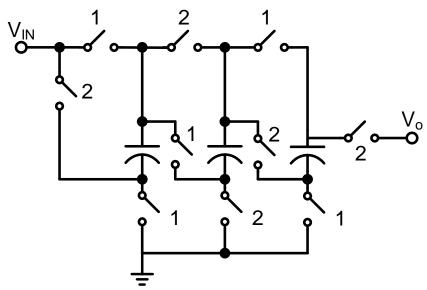

| Figure 28. | Architecture of the voltage doubler.                                                                                                                              | 37 |

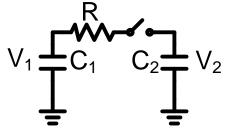

| Figure 29. | Generic model of the charge transfer in switched capacitor circuits                                                                                               | 39 |

| Figure 30. | Generic model of the single phase voltage doubler with a current source load.                                                                                     | 39 |

| Figure 31. | Low dropout regulators with (a) NMOS and (b) PMOS pass transistors                                                                                                | 42 |

| Figure 32. | Block diagram of the proposed energy harvester with the MPPT technique.                                                                                           | 45 |

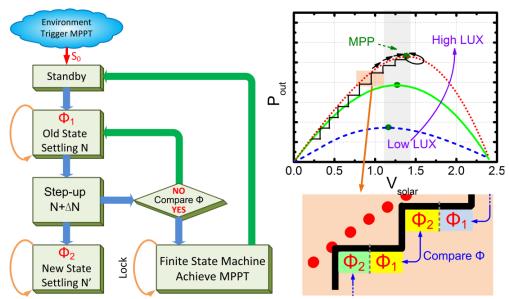

| Figure 33. | Flow chart of adaptive MPPT, and MPP moving curve during tracking procedure.                                                                                      | 48 |

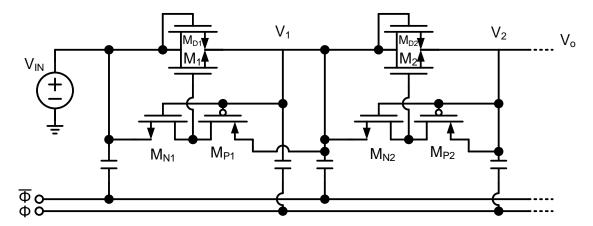

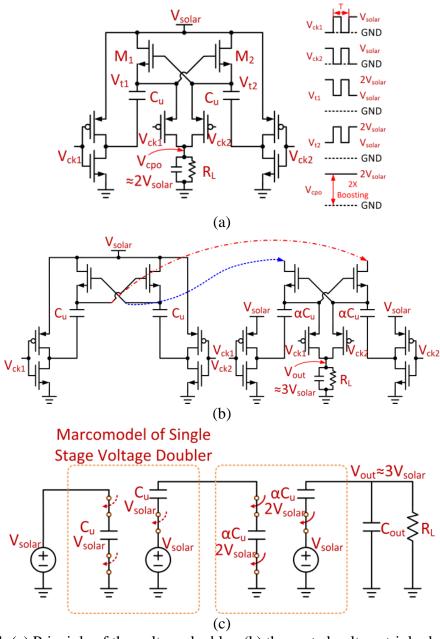

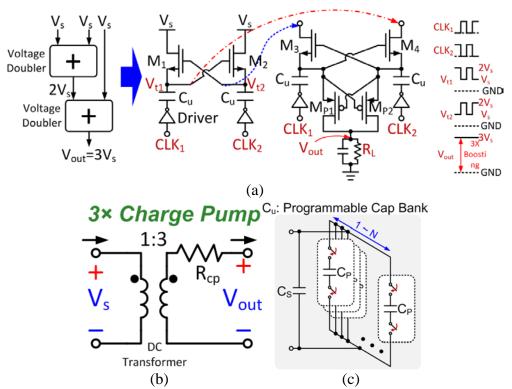

| Figure 34. | (a) Principle of the voltage doubler, (b) the nested voltage tripler built with 2 voltage doublers, (c) macromodel of the voltage tripler                         | 49 |

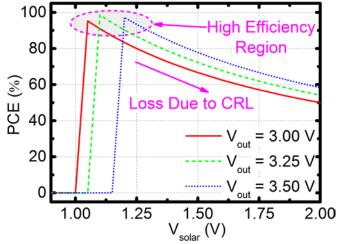

| Figure 35. | Power conversion efficiency (PCE) vs. V <sub>solar</sub> with 3-3.5 V V <sub>out</sub>                                                                            | 51 |

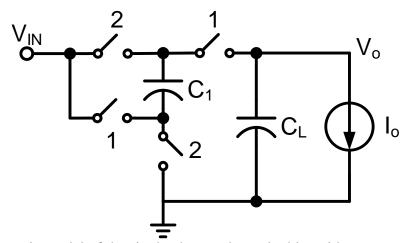

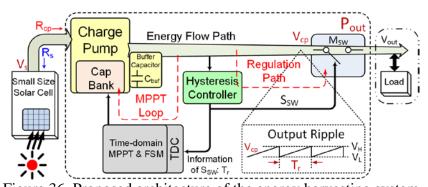

| Figure 36. | Proposed architecture of the energy harvesting system                                                                                                             | 52 |

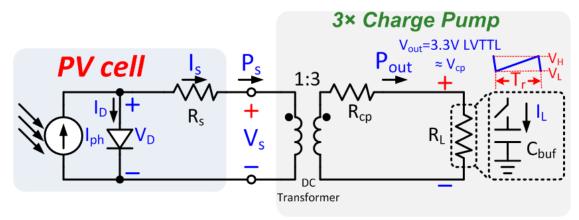

| Figure 37. | (a) Generic structure of the nested voltage tripler built with 2 voltage doublers, (b) macromodel of the 3× charge pump, and (c) the programmable capacitor bank. | 55 |

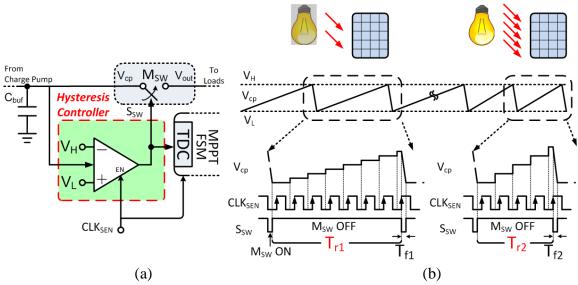

| Figure 38. | (a) Architecture of the hysteresis controller and (b) the operating waveforms.                                                                                    | 56 |

| Figure 39. | Self-triggered one-shot mechanism of the hysteresis controller                                                                                                    | 57 |

| Figure 40. | Pseudo-static model of a PV cell and charge pump power converter                                                                                                  | 58 |

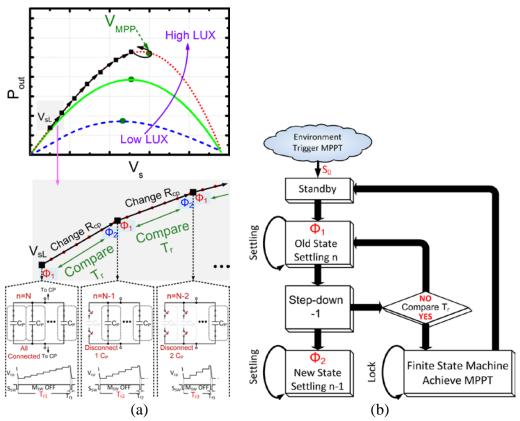

| Figure 41. | (a) Electrical characteristics of a PV cell under different illumination conditions and (b) flow chart of the adaptive MPPT for the PV harvesting system.                                                                                                                             | 61 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

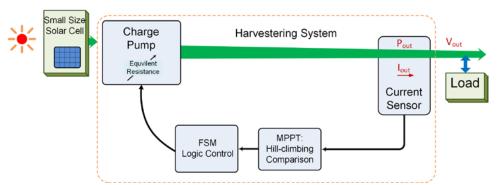

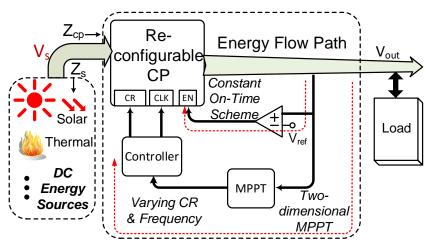

| Figure 42. | Proposed architecture of the reconfigurable energy harvester                                                                                                                                                                                                                          | 62 |

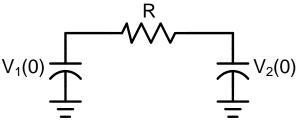

| Figure 43. | Macromodel for the charge redistribution loss.                                                                                                                                                                                                                                        | 63 |

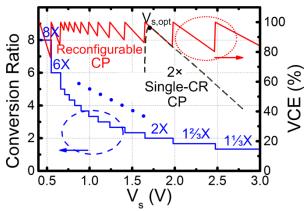

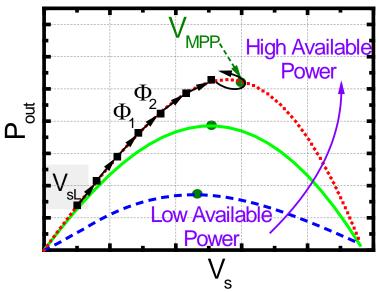

| Figure 44. | Influence of conversion ratios upon the harvesting efficiency                                                                                                                                                                                                                         | 64 |

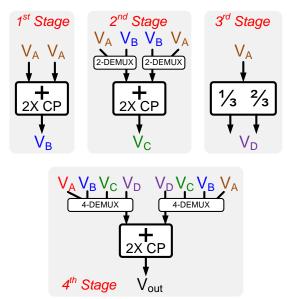

| Figure 45. | Conceptual diagram of the reconfigurable charge pump.                                                                                                                                                                                                                                 | 65 |

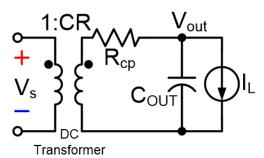

| Figure 46. | Pseudo-static macromodel of the charge pump.                                                                                                                                                                                                                                          | 66 |

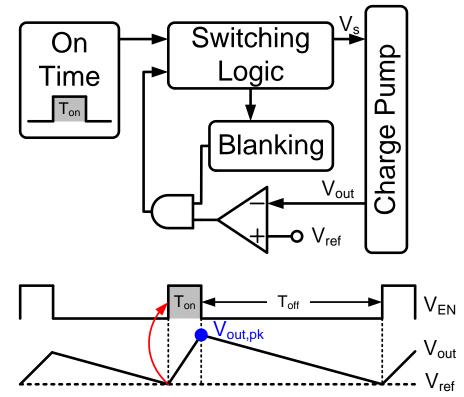

| Figure 47. | Conceptual diagram of the constant-on (COT) time regulation and waveforms.                                                                                                                                                                                                            | 67 |

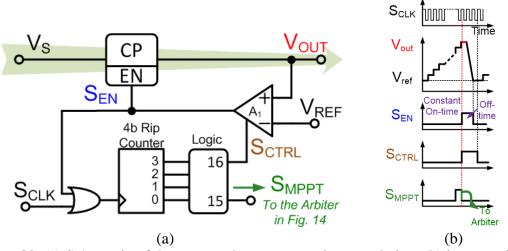

| Figure 48. | Generic nonlinear characteristics of energy sources and the hill-climbing MPPT algorithm.                                                                                                                                                                                             | 70 |

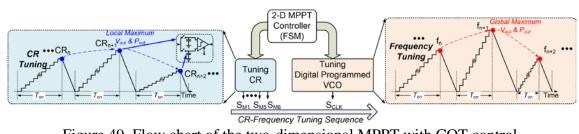

| Figure 49. | Flow chart of the two-dimensional MPPT with COT control.                                                                                                                                                                                                                              | 70 |

| Figure 50. | Conceptual block diagram of the proposed energy harvesting system                                                                                                                                                                                                                     | 73 |

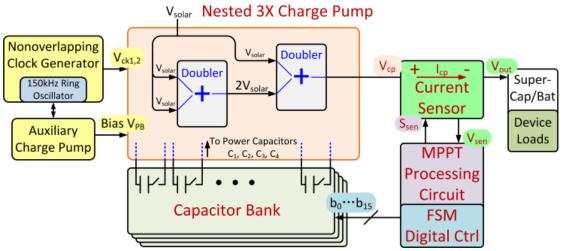

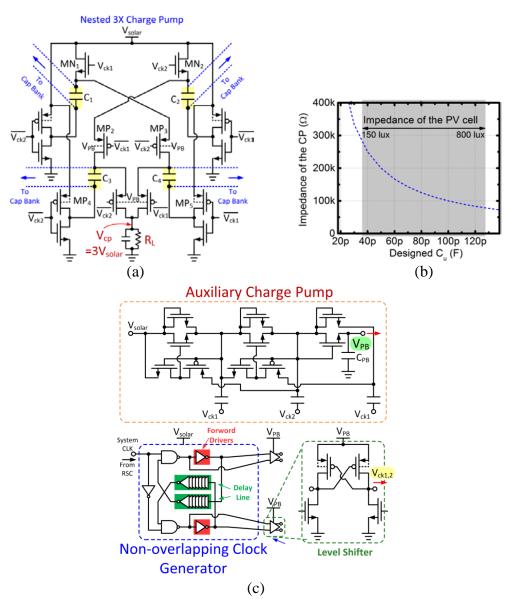

| Figure 51. | (a) Detailed structure of the nested voltage tripler, (b) impedance of the charge pump $Z_{cp}$ with designed $C_u$ values vs. impedance of PV cell $Z_{solar}$ under different light intensities, and (c) auxiliary charge pump, non-overlapping clock generator, and level shifter. | 74 |

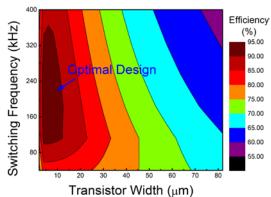

| Figure 52. | Efficiency trade-off between the power transistor gate width Wu and switching frequency fs.                                                                                                                                                                                           | 76 |

| Figure 53. | Designed time diagram of the MPPT controller                                                                                                                                                                                                                                          | 77 |

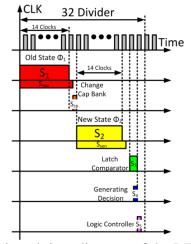

| Figure 54. | Simulated waveforms of the FSM for the MPPT procedure.                                                                                                                                                                                                                                | 78 |

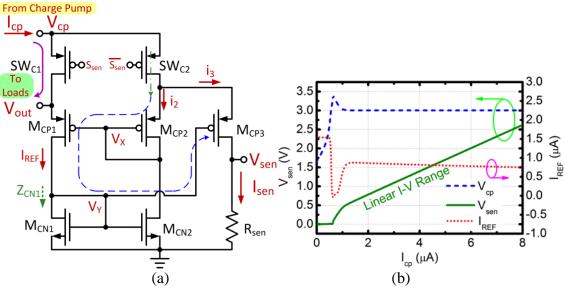

| Figure 55. | (a) Proposed structure of the current sensor, (b) characteristics of sensing voltage $V_{\text{sen}}$ , reference current $I_{\text{REF}}$ vs. throughput current $I_{\text{cp}}$                                                                                                     | 79 |

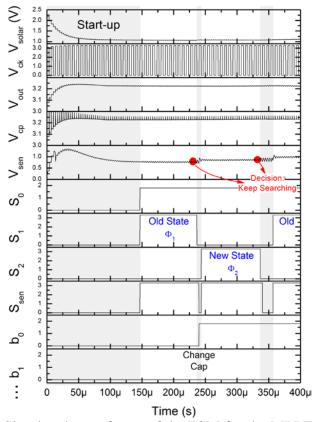

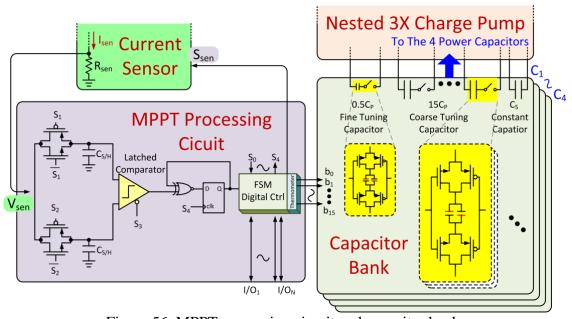

| Figure 56. | MPPT processing circuit and capacitor bank.                                                                                                                                                                                                                                           | 81 |

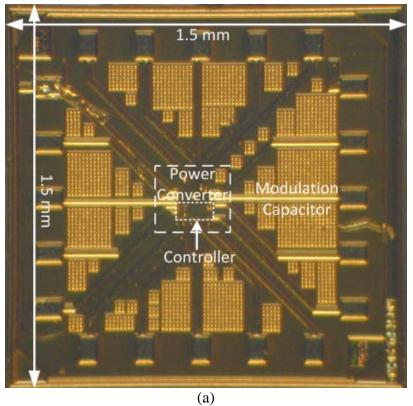

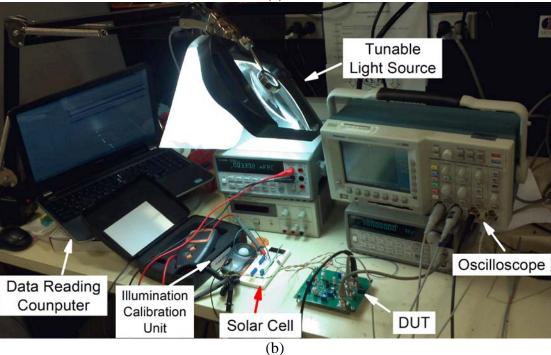

| Figure 57. | (a) Die photograph of the fabricated chip, (b) testing setup                                                                                                                                                                                                                          | 84 |

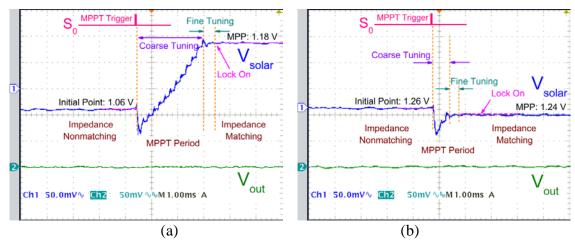

| Figure 58. | Experimental transient results of the MPPT procedure under (a) 400 lux, (b) 800 lux light intensity.                                                                                                                                                                                  | 85 |

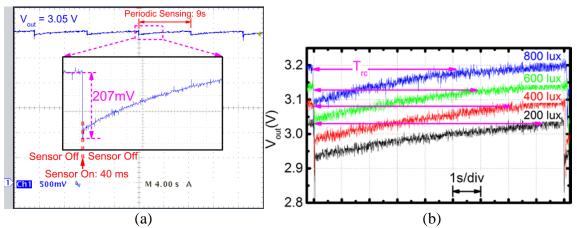

| Figure 59. | Experimental transient performance (a) with a wireless temperature sensor operating, (b) comparing one sensing period with different light intensities                                                                                                                                                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

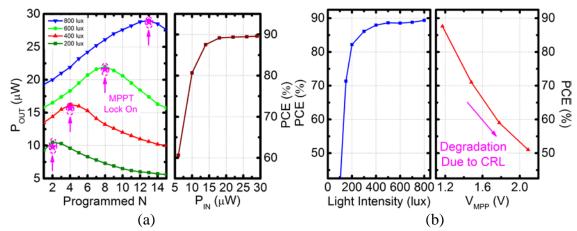

| Figure 60. | (a) Static output power with different programmed numbers of the capacitor bank under different light intensity, and end-to-end peak power conversion efficiency (PCE) with MPPT vs. different PV power or light intensities, (b) PCE vs. light intensity and PCE with different $V_{MPP}$ and charge redistribution losses. |

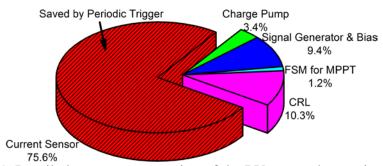

| Figure 61. | Detailed power consumption of the PV energy harvesting system89                                                                                                                                                                                                                                                              |

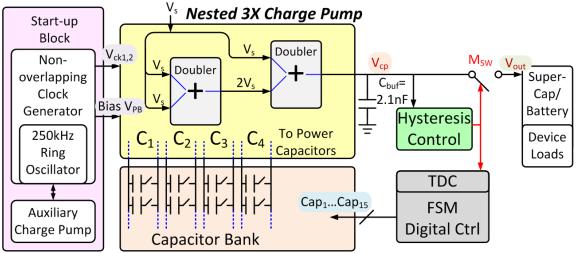

| Figure 62. | Detailed proposed architecture of the energy harvesting system92                                                                                                                                                                                                                                                             |

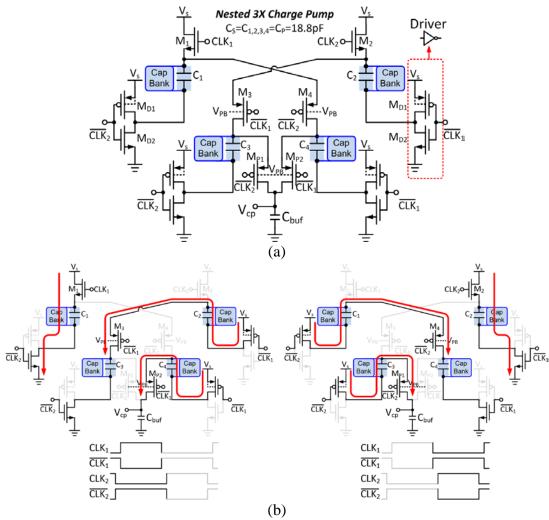

| Figure 63. | (a) Modified architecture of the nested 3× charge pump power converter and (b) its operation with the non-overlapping clocks in complementary phases.                                                                                                                                                                        |

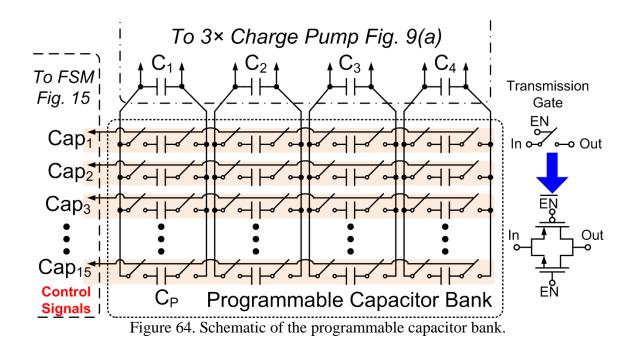

| Figure 64. | Schematic of the programmable capacitor bank                                                                                                                                                                                                                                                                                 |

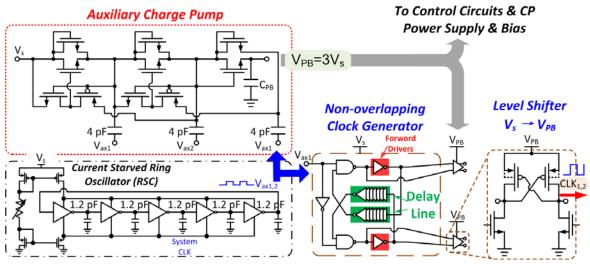

| Figure 65. | Startup circuits and auxiliary bias circuits for self-sustaining95                                                                                                                                                                                                                                                           |

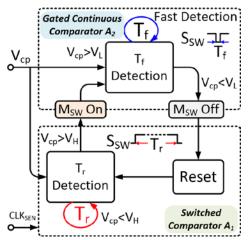

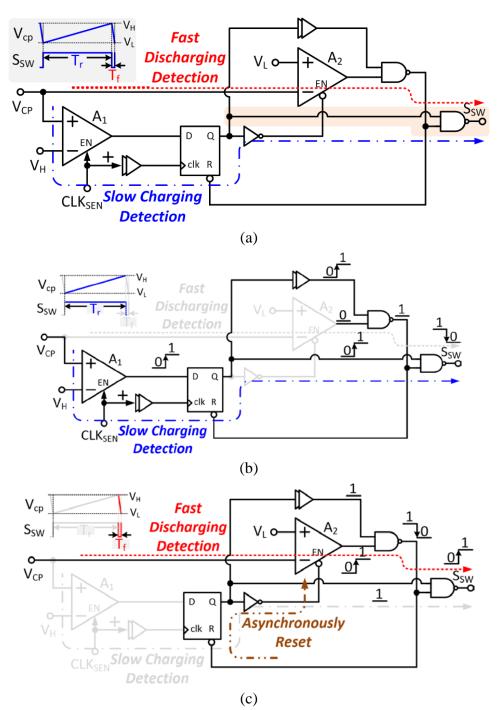

| Figure 66. | (a) Architecture of the self-triggered one-shot hysteresis controller, (b) when $S_{SW}=1$ and the controller detects $T_r$ , (c) when $S_{SW}=0$ and the controller detects $T_f$ .                                                                                                                                         |

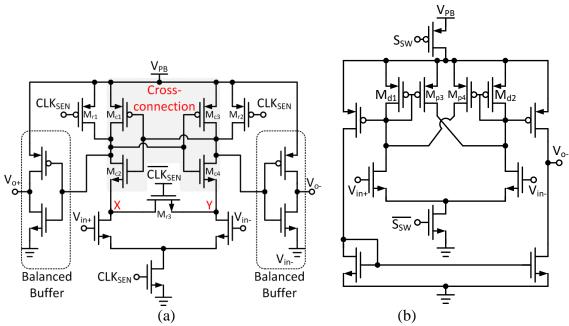

| Figure 67. | Structures of (a) the low power latched comparator A <sub>1</sub> and (b) the high speed amplifier A <sub>2</sub> 97                                                                                                                                                                                                         |

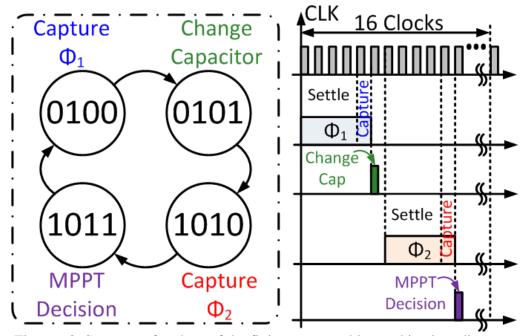

| Figure 68. | State transfer chart of the finite-state machine and its time diagram98                                                                                                                                                                                                                                                      |

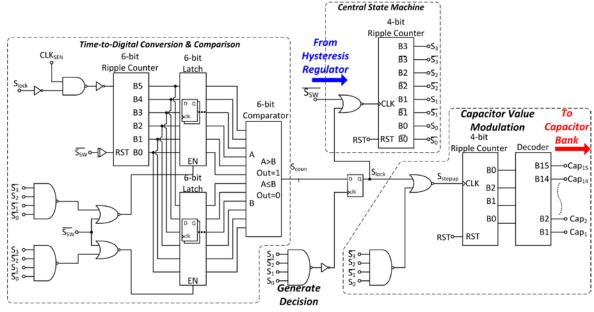

| Figure 69. | Simplified structure of the finite-state machine (FSM) with the TDC function                                                                                                                                                                                                                                                 |

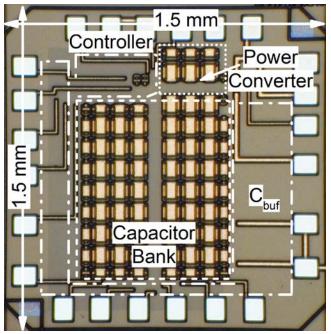

| Figure 70. | Die photograph of the fabricated chip                                                                                                                                                                                                                                                                                        |

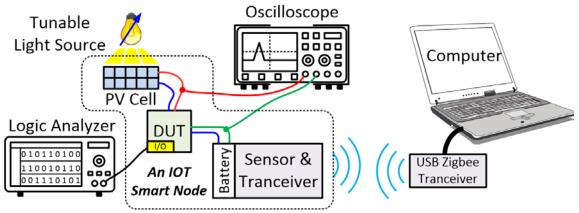

| Figure 71. | Testing setup for trickle charging an IoT smart node                                                                                                                                                                                                                                                                         |

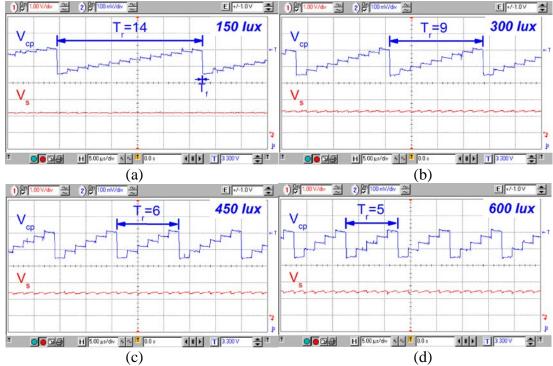

| Figure 72. | Different charging time $T_r$ under (a) 150, (b) 300, (c) 450 and (d) 600 lux conditions                                                                                                                                                                                                                                     |

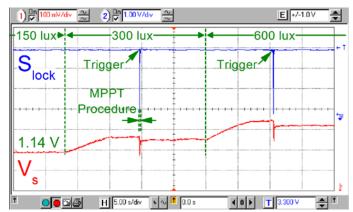

| Figure 73. | Transient MPPT with illumination changing from 150 lux to 600 lux 102                                                                                                                                                                                                                                                        |

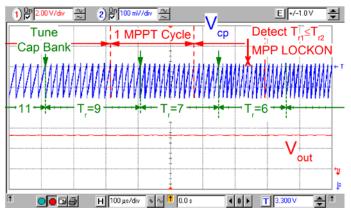

| Figure 74. | Transient V <sub>cp</sub> and V <sub>out</sub> waveforms during the MPPT procedure with 450 lux illumination 102                                                                                                                                                                                                             |

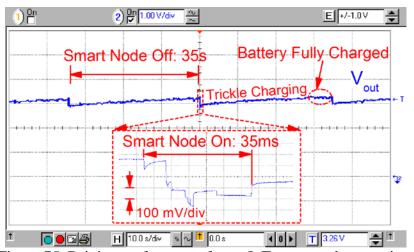

| Figure 75. | Driving performance for an IoT smart node operation                                                                                                                                                                                                           | 103 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

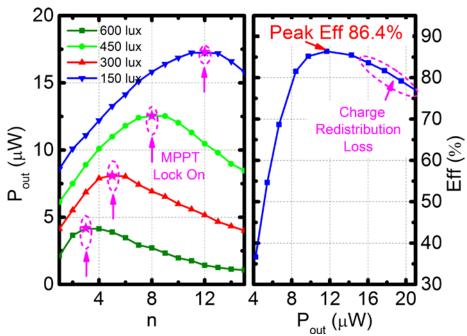

| Figure 76. | (Left) Output power with different capacitor values n under different light intensities and corresponding MPPs, and (Right) end-to-end peak efficiency with MPPT vs. different PV power.                                                                      | 104 |

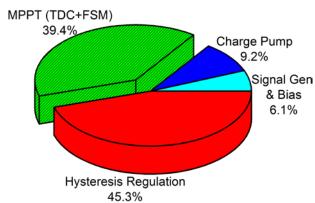

| Figure 77. | Detailed power consumption of the PV energy harvesting system                                                                                                                                                                                                 | 105 |

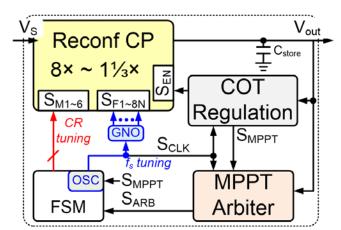

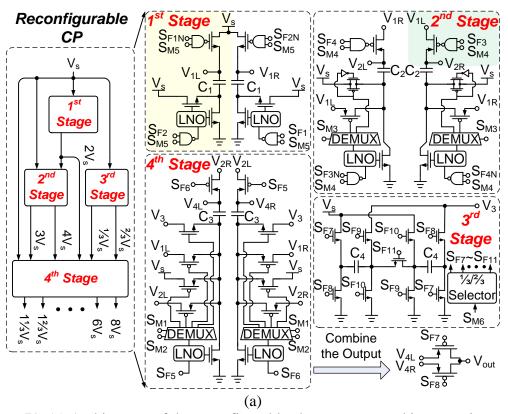

| Figure 78. | Implemented architecture of the reconfigurable energy harvester                                                                                                                                                                                               | 108 |

| Figure 79. | (a) Architecture of the reconfigurable charge pump, and its operation at (b) $CR = 8\times$ , (c) $CR = 3\frac{1}{3}\times$ , (d) $CR = 1\frac{1}{3}\times$                                                                                                   | 109 |

| Figure 80. | Principle of the shoot-through current during switching in the voltage doubler.                                                                                                                                                                               | 113 |

| Figure 81. | Generation of the global non-overlapping signals.                                                                                                                                                                                                             | 114 |

| Figure 82. | (a) Schematic of the proposed constant-on time regulation, (b) its operating waveforms.                                                                                                                                                                       | 115 |

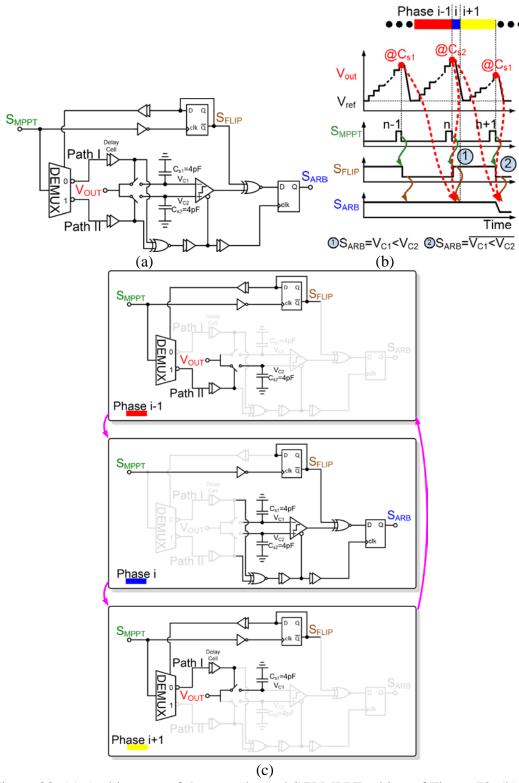

| Figure 83. | (a) Architecture of the two-channel S/H MPPT arbiter of Figure 78, (b) its operating waveforms, and (c) its operation in three periodic phases: i-1, i, and i+1                                                                                               | 117 |

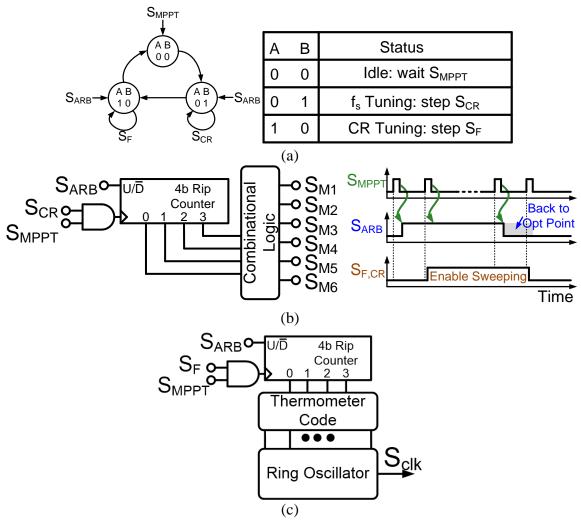

| Figure 84. | (a) State diagram of the finite state machine, (b) CR sweeping module, and (c) f <sub>s</sub> sweeping module.                                                                                                                                                | 119 |

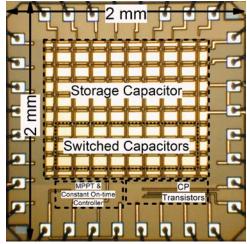

| Figure 85. | Die photograph of the fabricated chip.                                                                                                                                                                                                                        | 120 |

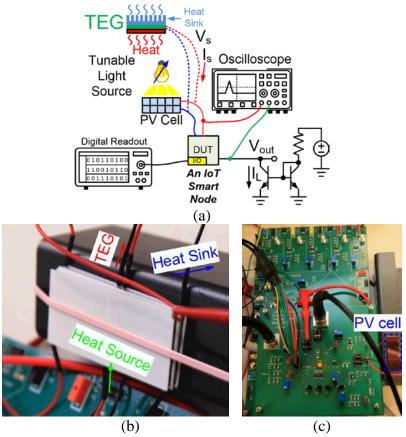

| Figure 86. | (a) Testing setup for the IoT smart node and detailed connection for (b) thermoelectric generator and (c) photovoltaic cell                                                                                                                                   | 121 |

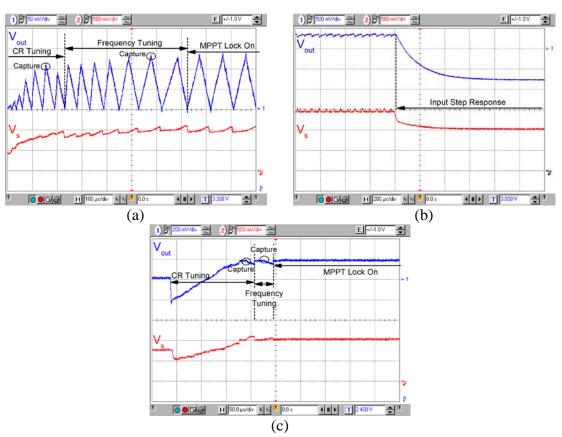

| Figure 87. | MPPT tracking performance with (a) light load condition with $P_s > P_{out}$ , (b) a step change in $V_s$ , and (c) heavy load condition with $P_s < P_{out}$                                                                                                 | 122 |

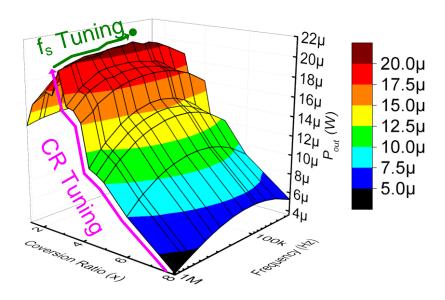

| Figure 88. | P <sub>out</sub> vs. CR and f <sub>s</sub> during the two-dimensional MPPT procedure                                                                                                                                                                          | 123 |

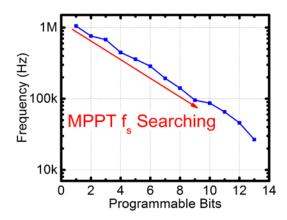

| Figure 89. | fs tuning capability of the digital programmed oscillator.                                                                                                                                                                                                    | 124 |

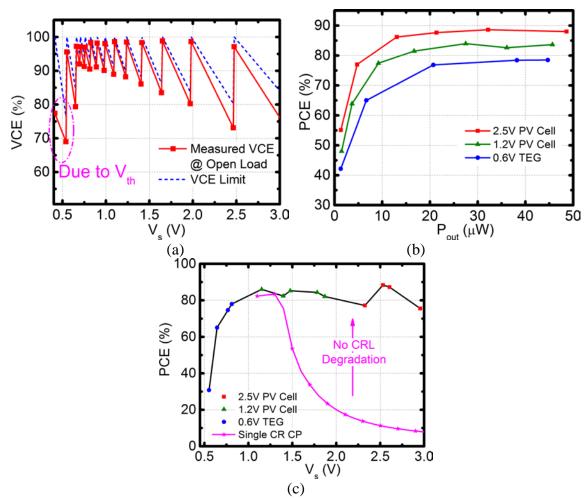

| Figure 90. | The measured (a) voltage conversion efficiency (VCE) between 0.45 V and 3 V; (b) power conversion efficiency (PCE) with three kinds of energy sources and various loading conditions; (c) PCE versus a wide input range and comparing with a 3× single CR CP. | 125 |

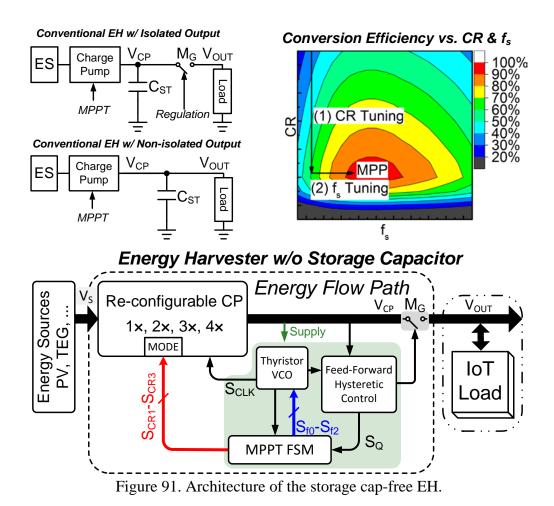

| Figure 91. | Architecture of the storage cap-free EH.                                                                                                                                                                                                                      | 131 |

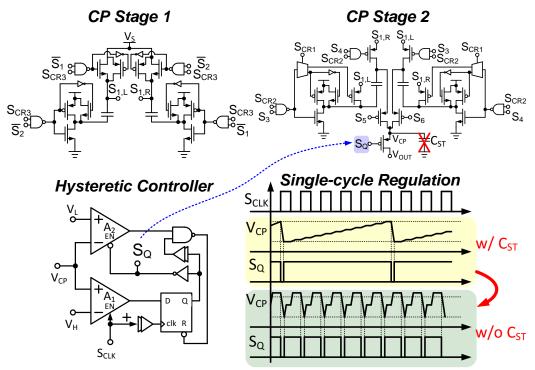

| Figure 92. C | CP and hysteretic regulation w/o C <sub>ST</sub>                                                                                                                                                                                            | 132 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

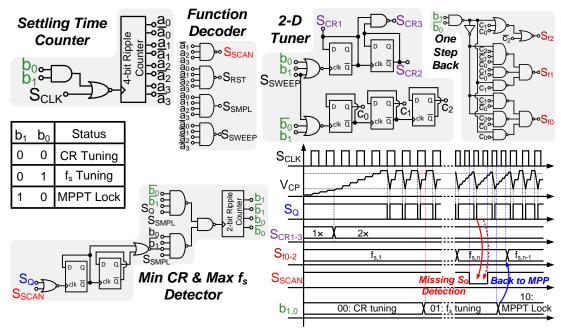

| Figure 93. F | FSM for a Single-cycle MPPT                                                                                                                                                                                                                 | 134 |

| Figure 94. 7 | Γhe thyristor-based VCO                                                                                                                                                                                                                     | 134 |

| Figure 95. S | Startup and MPPT tuning transients                                                                                                                                                                                                          | 135 |

| Figure 96. F | Performance of the thyristor-based VCO.                                                                                                                                                                                                     | 136 |

| Figure 97. I | Electromechanical model of the piezoelectric transducer at resonance                                                                                                                                                                        | 138 |

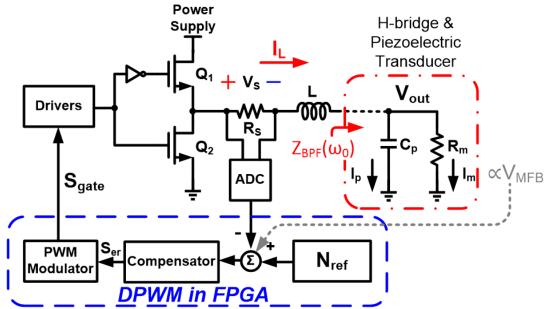

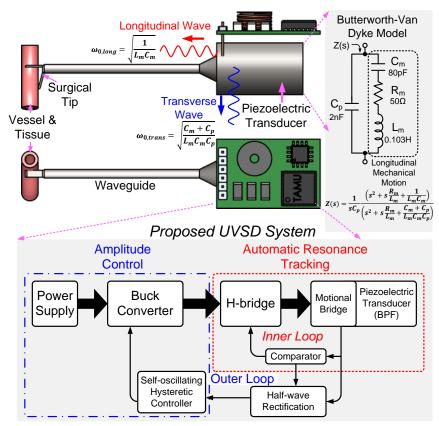

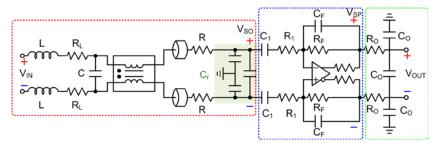

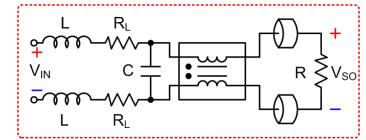

| _            | Architecture of the ultrasonic vessel sealing and dissecting (UVSD) system.                                                                                                                                                                 | 141 |

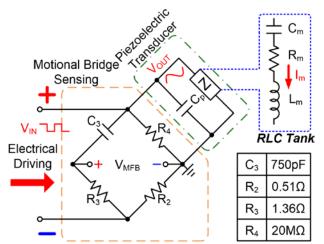

| Figure 99. N | Motional current sensing bridge circuit for the ultrasonic oscillation                                                                                                                                                                      | 142 |

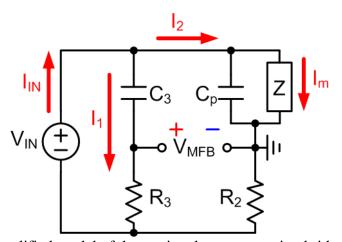

| Figure 100.  | Simplified model of the motional current sensing bridge at resonance                                                                                                                                                                        | 143 |

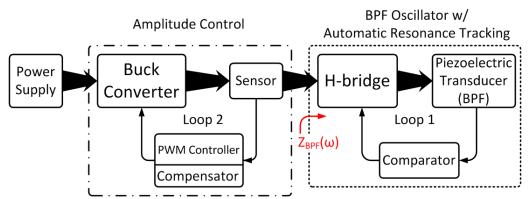

| -            | Dual loop automatic resonance tracking scheme with a BPF oscillator and power regulation.                                                                                                                                                   | 144 |

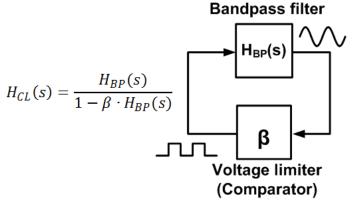

| Figure 102.  | Conceptual block diagram of the BPF oscillator.                                                                                                                                                                                             | 145 |

| Figure 103.  | Block diagram of the amplitude control loop in resonance.                                                                                                                                                                                   | 148 |

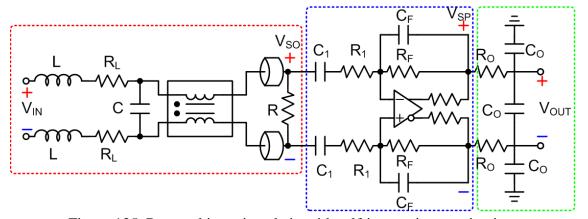

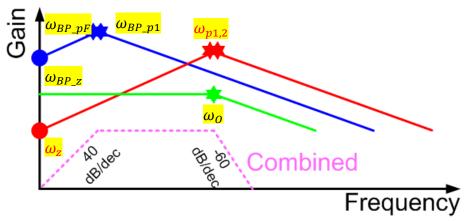

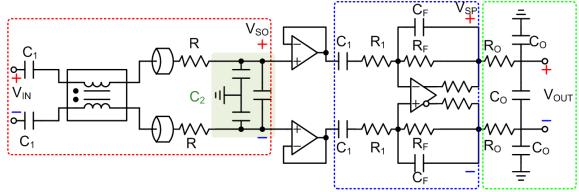

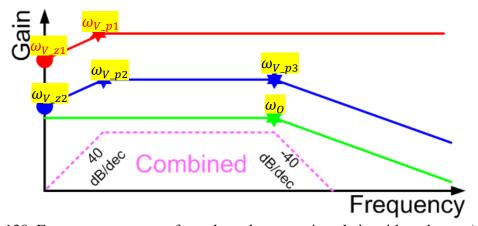

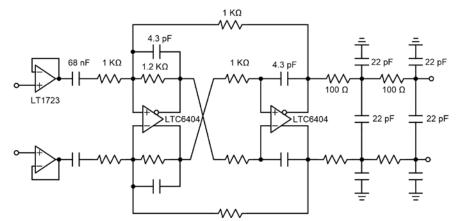

| Figure 104.  | Implementation of the BPF based oscillator                                                                                                                                                                                                  | 150 |

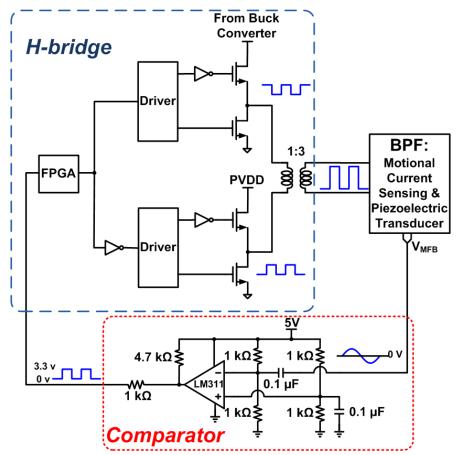

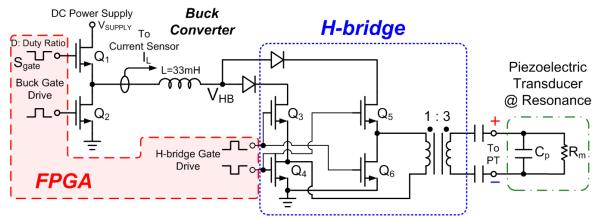

| Figure 105.  | Detailed structure of the buck converter and H-bridge                                                                                                                                                                                       | 151 |

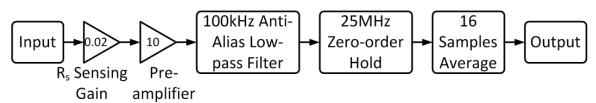

| Figure 106.  | Block diagram of the inductor current sensing scheme.                                                                                                                                                                                       | 153 |

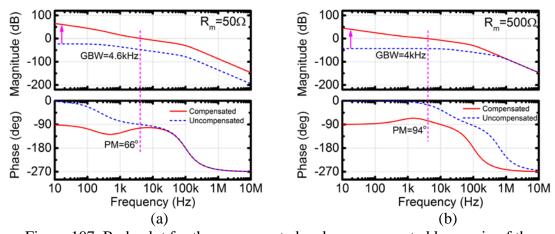

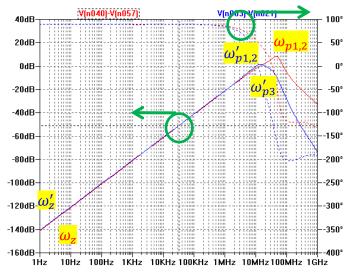

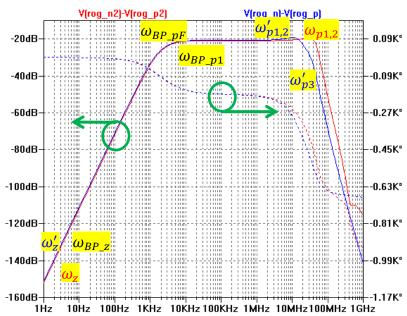

|              | Bode plot for the compensated and uncompensated loop gain of the proposed scheme with compensation for (a) minimum $R_m = 50~\Omega$ , and (b) maximum $R_m = 500~\Omega$ load.                                                             | 154 |

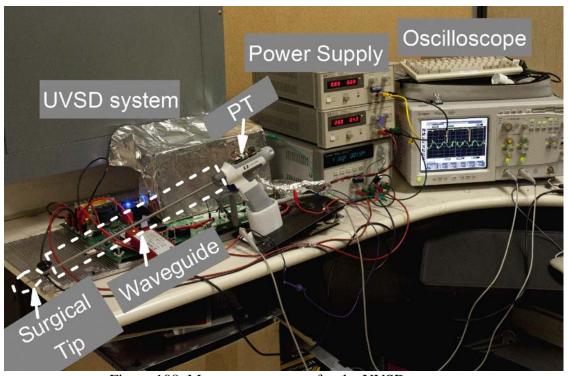

| Figure 108.  | Measurement setup for the UVSD system                                                                                                                                                                                                       | 155 |

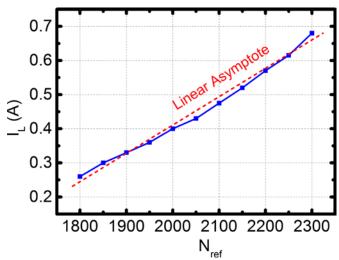

| Figure 109.  | Unloaded input current I <sub>in</sub> vs. reference values N <sub>ref</sub> of DPWM                                                                                                                                                        | 156 |

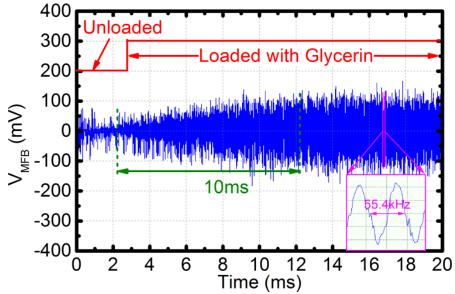

| Figure 110.  | Step settling time of the V <sub>MFB</sub> signal.                                                                                                                                                                                          | 157 |

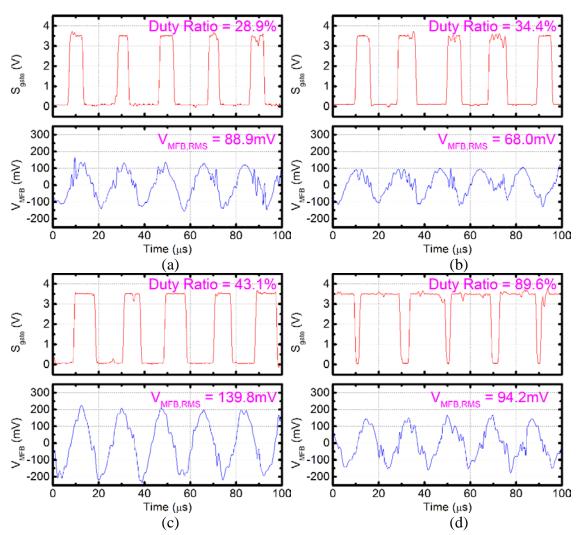

|              | Measured waveforms for four cases: (a) unloaded operation with $N_{ref}$ = 1800, (b) glycerin-loaded operation with $N_{ref}$ = 1800, (c) unloaded operation with $N_{ref}$ = 2100, and (d) glycerin-loaded operation with $N_{ref}$ = 2100 | 150 |

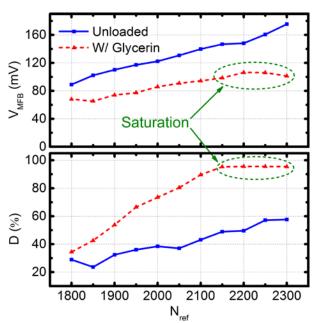

| •              | Sensed motional magnitude V <sub>MFB</sub> and duty ratio D vs. different control eferences N <sub>ref</sub> of the power regulator                     | 159 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

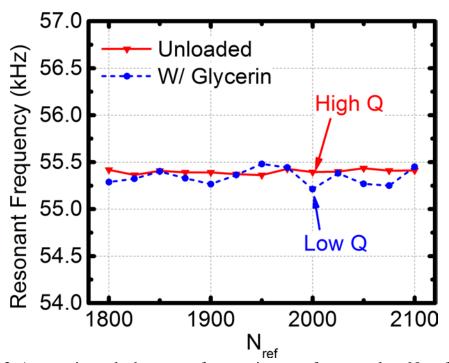

|                | Automatic tracked resonant frequencies vs. reference values N <sub>ref</sub> of DPWM.                                                                   | 160 |

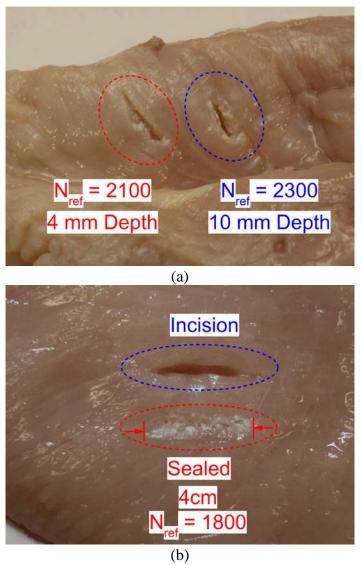

| •              | Tested samples: (a) different dissecting power and resulting depths with $N_{ref} = 2100$ and 2300, and (b) a sealing function setting $N_{ref} = 1800$ | 161 |

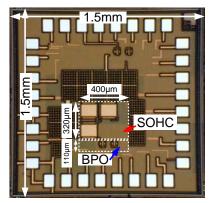

| Figure 115. D  | Die micrograph with 0.18-μm CMOS technology                                                                                                             | 163 |

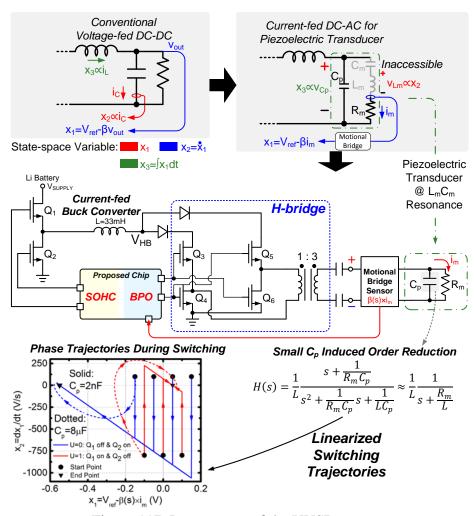

| Figure 116. C  | Conceptual architecture of the UVSD system.                                                                                                             | 164 |

| Figure 117. P  | Power stage of the UVSD system                                                                                                                          | 165 |

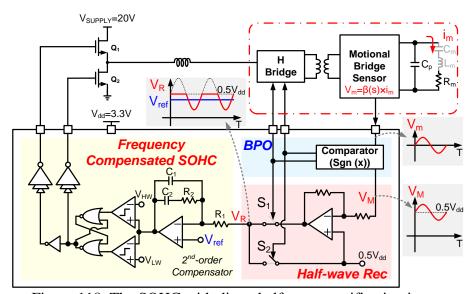

| Figure 118. T  | The SOHC with direct half-wave rectification input                                                                                                      | 166 |

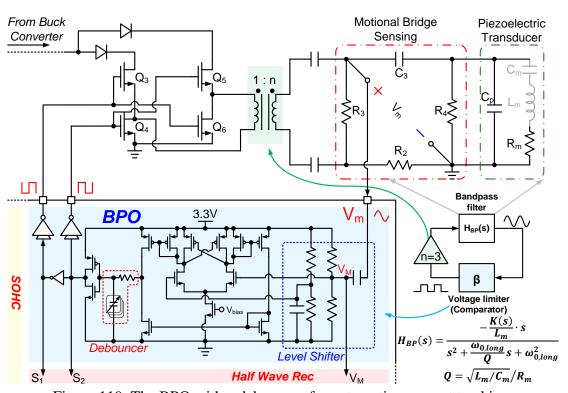

| Figure 119. T  | The BPO with a debouncer for automatic resonant tracking                                                                                                | 167 |

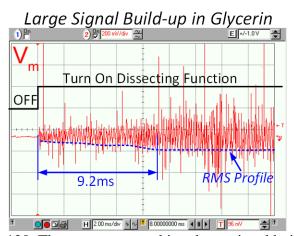

| Figure 120. T  | The resonance tracking, large signal build-up.                                                                                                          | 168 |

| Figure 121. P  | Performance of the debouncer                                                                                                                            | 169 |

| Figure 122. S  | Sealing and dissecting in vitro testing.                                                                                                                | 170 |

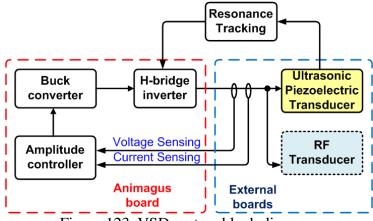

| Figure 123. V  | VSD system block diagram.                                                                                                                               | 173 |

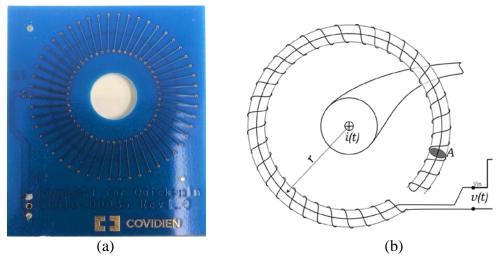

| Figure 124. (a | a) Rogowski coil for current sensing, and (b) its conceptual structure                                                                                  | 174 |

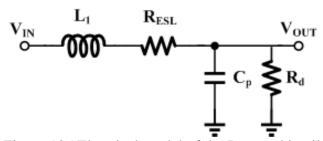

| Figure 125 El  | lectrical model of the Rogowski coil                                                                                                                    | 174 |

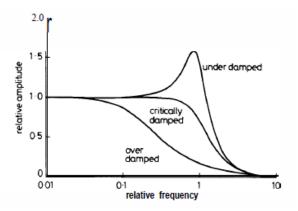

| Figure 126. F  | Frequency responses of Rogowski coil with different Q values                                                                                            | 175 |

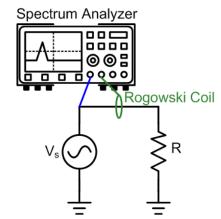

| Figure 127. T  | Testbench for the Rogowski coil.                                                                                                                        | 175 |

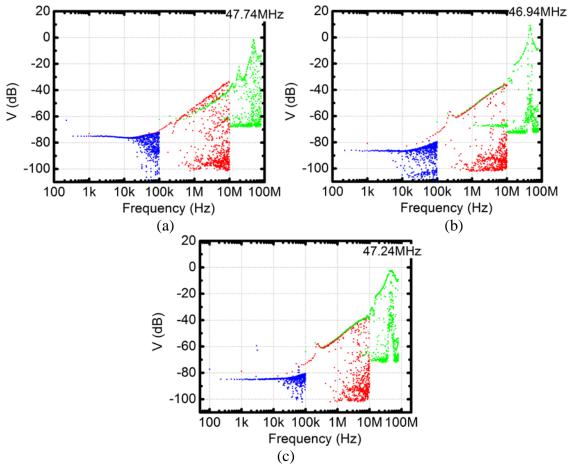

|                | Frequency responses of the Rogowski coil with three samples: (a), (b), nd (c).                                                                          | 176 |

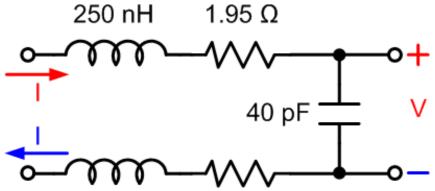

| Figure 129. E  | Extracted electrical model of the Rogowski coil                                                                                                         | 177 |

| Figure 130. E  | Electrical model of the capacitive voltage divider                                                                                                      | 177 |

| Figure 131. C  | Current sensing chain with three functional blocks                                                                                                      | 178 |

| Figure 132. S  | Self-integrating termination for the Rogowski coil                                                                                                      | 179 |

| Figure 133. | Simulated performance of (blue) passive integrating sensor, and (red) self-integrating sensor.                   | .179 |

|-------------|------------------------------------------------------------------------------------------------------------------|------|

| Figure 134. | Simulated performance of the entire current sensing with (blue) passive integrating, and (red) self-integrating. | .181 |

| Figure 135. | Rogowski sensing chain with self-integrating termination                                                         | .181 |

| Figure 136. | Frequency responses from the three functional blocks, and (bottom pink) the combined signal chain.               | .182 |

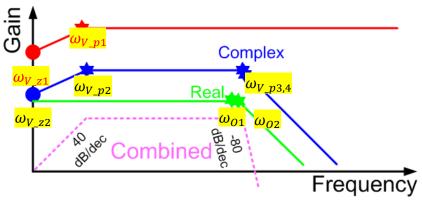

| Figure 137. | Frequency responses of the voltage sensing chain.                                                                | .183 |

| Figure 138. | Frequency responses from the voltage sensing chain with real zeros/poles                                         | .184 |

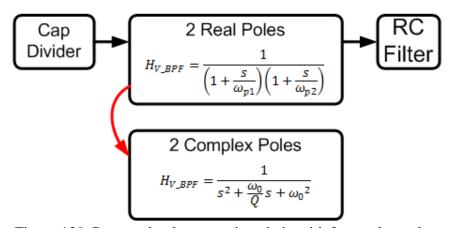

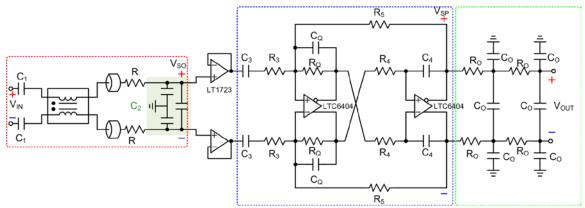

| Figure 139. | Proposed voltage sensing chain with 2 complex poles                                                              | .185 |

| Figure 140. | Proposed voltage sensing chain with biquad filter.                                                               | .186 |

| Figure 141. | Estimated frequency response of the voltage sensing chain with biquad BPF                                        | .187 |

| Figure 142. | Estimated frequency response of the current sensing chain with Op-Amp bandwidth limit.                           | .187 |

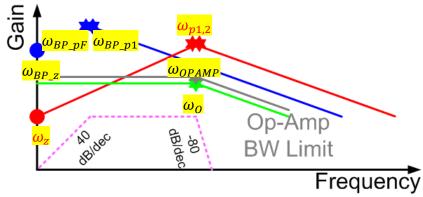

| Figure 143. | Proposed voltage sensing chain with MFB filter                                                                   | .188 |

| Figure 144. | Estimated frequency response of the voltage sensing chain with biquad BPF                                        | .188 |

| Figure 145. | Required pass and stop frequencies of the frequency discriminator                                                | .189 |

| Figure 146. | Proposed digital frequency discriminator in the FPGA module                                                      | .191 |

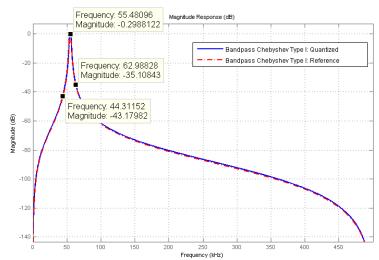

| Figure 147. | . Simulated frequency discriminator programmed at 55.5 kHz                                                       | .192 |

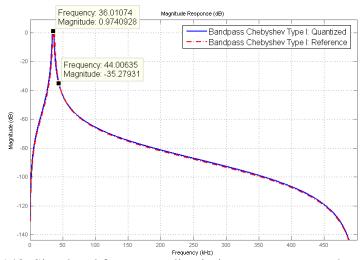

| Figure 148. | Simulated frequency discriminator programmed at 36 kHz                                                           | .192 |

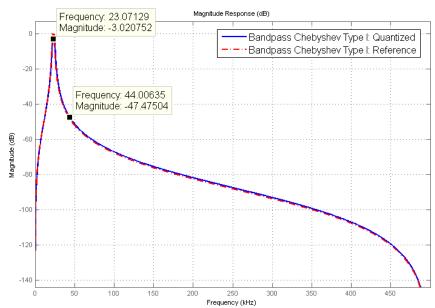

| Figure 149. | Simulated frequency discriminator programmed at 23 kHz.                                                          | .193 |

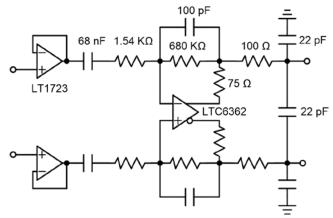

| Figure 150. | Proposed current sensing chain                                                                                   | .194 |

| Figure 151. | Proposed voltage sensing chain with biquad filter.                                                               | .194 |

| Figure 152. | Proposed voltage sensing chain with MFB filter                                                                   | .194 |

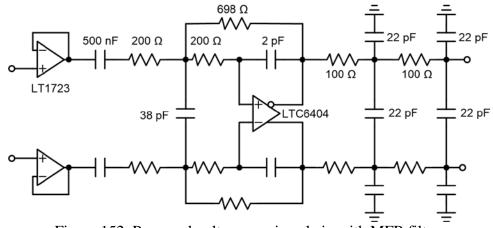

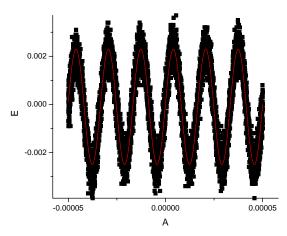

| Figure 153. Tested PCB with voltage and current sensing chains.                | 197 |

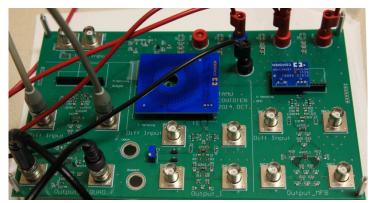

|--------------------------------------------------------------------------------|-----|

| Figure 154. Measured data fitting for a sinusoidal model                       | 197 |

| Figure 155. Measured data fitting for common-mode gain signal at 25 MHz        | 198 |

| Figure 156. Measured (a) differential gain and (b) phase of the sensing chains | 199 |

| Figure 157. Detailed phase mismatch.                                           | 199 |

| Figure 158. Common-mode gain of the voltage & current sensing chains           | 200 |

# LIST OF TABLES

| Page                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------|

| Table 1. Comparison table of crystalline and thin film PV cells                                                             |

| Table 2. Performance comparison of various TEGs                                                                             |

| Table 3. Performance comparison of various piezoelectric transducers tested at 60Hz frequency and 1G acceleration amplitude |

| Table 4. Performances of the 915MHz RF energy harvester                                                                     |

| Table 5. Comparison of various topologies of energy harvesters23                                                            |

| Table 6. Design tradeoffs of general DC-DC power converters30                                                               |

| Table 7. Design tradeoffs of general charge pumps40                                                                         |

| Table 8. Design tradeoffs of the LDO.                                                                                       |

| Table 9. Performance comparison of low energy harvesting systems with MPPT90                                                |

| Table 10. Performance comparison of PV energy harvesting systems with MPPT106                                               |

| Table 11. Reconfiguring signals for the CR tuning                                                                           |

| Table 12. Performance comparison of energy harvesting systems                                                               |

| Table 13. Performance comparison of this integrated version                                                                 |

| Table 14. Simulated gain and phase performances                                                                             |

| Table 15. Gain error at different frequencies                                                                               |

#### 1 INTRODUCTION

#### 1.1 Internet of Things and the Hardware Bottleneck

With recent developments in the Microelectromechanical Systems (MEMS) sensors and scaling-down of the silicon fabrication technology, the Internet of Things (IoT) has been proposed to uniquely identify objects and their virtual representations in an Internet-like structure [1]. Under such configuration, every object within the network can be tagged, analyzed, and managed to compose the event-driven mechanism of an IoT system [2]. As a leading topology and specific implementation of IoT, a Wireless Sensor Network (WSN) has been created to monitor, communicate, and process environmental information [3], [4]. In the WSN, the distributed sensors, also called smart nodes, should be integrated with SOC and wireless transceivers. The main practical challenge is how to power multiple electronic devices. Based on the selfsustaining operation scenario, the smart node is attached to objects without a power or signal wire connection. Since the occupied area of the harvesting system should also be minimized for monolithic integration, the available environmental energy is stringently limited, mandating the harvesting system to be highly energy-efficient. Another design challenge is the fact that the energy resource changes its power density depending on different environmental variables such as illumination intensity and temperature [5]. Thus, it requires the harvesting system to be adaptive to those environmental variations to achieve maximum power transfer.

Currently, radio-frequency (RF) electromagnetic waves are utilized to power radio-frequency identification devices (RFID) [6]-[8]. However, RFID acts as a passive transponder to the WSN only when RF power resides within a certain frequency range. Thus, the operation of a distributed smart node is not event-driven but scanned by an RF reader, resulting in passively monitoring. Trying to solve this issue, researchers have proposed a Battery Assisted Passive (BAP) RFID, which can actively transmit its sensed information using a small rechargeable on-board battery [9]. However, the reliability, size, and life-span of the on-board batteries are not satisfying and limit the development of the IoT [2].

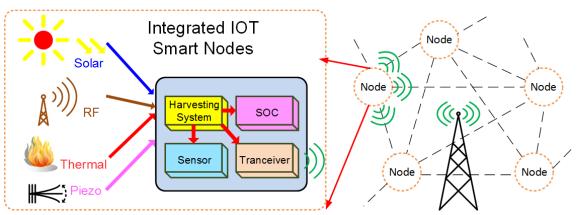

Figure 1. Conceptual block diagram of the IoT smart nodes with energy harvesting technique.

The IoT can be implemented by tagging objects as shown in Figure 1. The main difference from the conventional passive tag is that an IoT smart node includes a small size energy harvester, supercapacitor/battery, SOC, wireless transceiver, and sensor. The small energy sources embedded in the smart node, such as solar cells, RF, thermoelectric generators, and piezoelectric generators, can be a more flexible, robust, and efficient

power supply. Thus, the distributed nodes of Wireless Sensor Network can actively sense and exchange information with each other by low power communication technologies such as ZigBee or Bluetooth. The WSN can be widely applied in various applications, such as smart electrical grids, logistic flows, military or security wireless guards, and natural disaster sensor networks for forest fires, tsunamis, or earthquakes [3].

## 1.2 Characteristics of Energy Sources

#### 1.2.1 Photovoltaic Cell

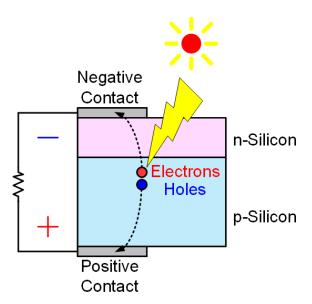

Figure 2. The physical structure of PV cells and their operating mechanism.

The photovoltaic effect is the generation of voltage or current in a material upon exposure to light. In principle, the photon excites the electrons in the valence band jumping to the conduction band as the free electrons with energy. Such a phenomenon

was firstly discovered by French physicist Alexandre-Edmond Becquerel in 1839. However, the applicable photovoltaic (PV) cell, also called solar cell, was initially proposed for powering the space satellites in later 1950s [10]. As shown in Figure 2, the fundamental mechanism is using the photon to excite a pair of electrons and protons in the vicinity of p-n-junction. The resulting electrons and protons will travel through the n-type and p-type materials to the electrodes respectively and this electricity is captured [11]. Therefore, the electrical behavior of PV cell could be modeled with current source, diode and passive components as illustrated in Figure 3 [12].

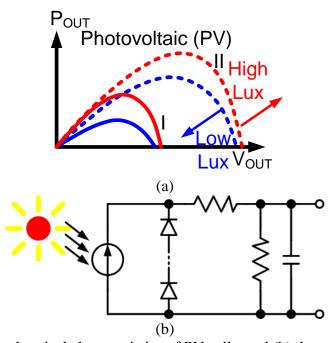

Figure 3. (a) The electrical characteristics of PV cells, and (b) the equivalent model.

With the advancement of semiconductor technology, nowadays PV cells have larger size and output power, and feasible for energy harvesting purposes. According to different fabrication technologies, the common PV cells in the nowadays market can be

categorized by crystalline silicon and thin film [13]. Their pros and cons are compared in Table 1. The crystalline silicon technology is similar with the conventional MOS technology and fabricates the PV cells as upon mono- or poly-silicon wafers. Its main advantage is premium quality and efficiency as high as 20% [14]. The energy conversion efficiency here is defined as the ratio between output electrical power and income light power. The disadvantage is the relatively expensive cost and limited physical size. Thus, less expensive substrate such as thin film technology was invented to conquer the cost and size problems. Basically, this technology fabricates the PV cells by depositing a thin semiconductor film upon glass or plastic substrates [15]. Due to the chemical vapor deposition (CVD) way of material deposition, the film is typically in the amorphous structure with worse quality compared with crystalline structure. Such an inferior characteristic cause a degenerated efficiency typically less than 15% [5], [16]. Also, the less expensive thin-film technology suffers a relatively short life-span and reliability issue [17], [18].

Table 1. Comparison table of crystalline and thin film PV cells.

|             | 1                                          |              |        |                         |              |

|-------------|--------------------------------------------|--------------|--------|-------------------------|--------------|

| PV type     | Fabrication                                | Efficiency   | Cost   | Longevity & Reliability | Cell<br>Size |

| Crystalline | Mono-Si                                    | Very<br>High | High   | High                    | Small        |

|             | Poly-Si                                    | High         | Medium | High                    | Small        |

| Thin-film   | a-Si, CdTe, CIGS,<br>DSC, flexible organic | Low          | Low    | Low                     | Large        |

#### 1.2.2 Thermoelectric Generator

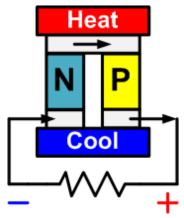

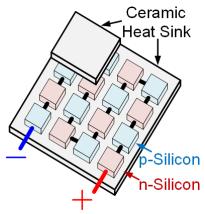

Figure 4. Physical structure of thermoelectric generators.

The thermoelectric generator (TEG) is another way of generating electricity. The physic principle is that the charge carriers, electrons and holes, will diffuse from the hot side to the cold side. Simultaneously, such massive moving generates current and electric power. To maximize the power generation capability, both electron and hole material are used as Figure 4 and called thermopile [19]. The relationship between heat and electricity was firstly identified by German Physicist Thomas Johann Seebeck [20]. It was later named Peltier-Seebeck effect and emphasized that such heat-electricity conversion is thermodynamically reversible. The energy accumulation,  $\dot{e}$ , could be fully defined by a thermoelectric equation as (1),

$$\dot{e} = \nabla \cdot (\kappa \nabla T) - \nabla \cdot (V + \Pi) \vec{J} + \dot{q}_{ext} \tag{1}$$

where  $\kappa$  is the thermal conductivity,  $\Pi$  is the Peltier coefficient, V is the local voltage,  $\vec{J}$  is the local current density, and  $q_{\text{ext}}$  is the added heat from any external source. The second term of this equation represents the energy carried by currents.

Figure 5. Architecture of commercial TEG products.

The typical structure of commercial TEG is demonstrated in Figure 5 [22]. Due to large temperature gradient is difficult to maintain, the thermovoltage of a single thermopile is typically lower than 1 mV in most applications. Therefore, tens or hundreds of thermopiles are cascaded as Figure 5 [23]. The top and bottom sides are fabricated by ceramic cases and function as the cold and hot faces.

Figure 6. (a) Electrical model and (b) transfer curves of generic TEGs.

The electrical model and transfer curves of generic TEGs are demonstrated in Figure 6. Table 2 lists typical performances of TEG for energy harvesting purposes [24]. There are two rules of thumb for choosing the proper TEG for energy harvesting

purposes. Firstly, different from PV cells in Figure 3, the TEG shows linear resistance which is proportional to the temperature gradient. It implies that the maximum output point is simply the half of the open circuit voltage (OCV), and the resulting MPPT scheme can be as simple as sensing the OCV. Secondly, to achieve harvestable voltage, the more cascaded thermopiles the easier for the following boost converter. However, the increasing series resistance will compromise the available output power quadratically. The commercial products typically are given specifications for the thermal management application instead of energy harvesting purposes. The  $V_{max}$  and  $I_{max}$  are the maximum operating conditions when using the TEG as a Peltier cooler. Therefore, a good rule of thumb for selecting the right TEG is to choose the largest product of  $V_{max} \times I_{max}$  for a specific size [23].

Table 2. Performance comparison of various TEGs.

| Manufacturer ID      | I <sub>max</sub> (A) | V <sub>max</sub> (V) | Q <sub>max</sub><br>(Watts) | No. of<br>Series<br>Piles | L×W<br>Size<br>(mm) |

|----------------------|----------------------|----------------------|-----------------------------|---------------------------|---------------------|

| HT9,3,F2,2525,TA,W6  | 9.6                  | 3.6                  | 20                          | N/A                       | 29×25               |

| HT6,12,F2,4040,TA,W6 | 6                    | 14.4                 | 51                          | 127                       | 44×40               |

| HT8,12,F2,4040,TA,W6 | 8.5                  | 14.4                 | 72                          | 127                       | 44×40               |

| HT4,6,F2,2143,TA,W6  | 3.7                  | 7.2                  | 16                          | 63                        | 43×21               |

| HT2,12,F2,3030,TA,W6 | 2.3                  | 14.4                 | 20                          | N/A                       | 34×30               |

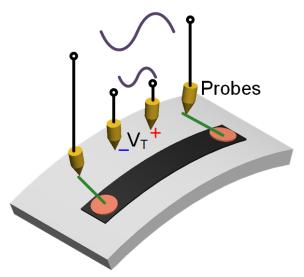

## 1.2.3 Piezoelectric Transducer

The mechanic energy is one of the most universal form of energy, and is conventionally converted into electricity by generators [25]. Their bulky sizes are not feasible for the compact energy harvesting purposes. Therefore, as a solid-state way of harvesting, the piezoelectric transducer (PT) is much smaller and ideal for this application. Its principle, called piezoelectricity, is intrinsic characteristics of crystal. This phenomena was firstly identified by French physicists Jacques and Pierre Curie in 1880 [26]. One simple explanation is that every crystal material can be modeled as a massive combination of electric dipole [27]. In steady state, the material shows neutral charge. Once applying external stress, the dipole moment will be changed and generates uneven electrical field as,

$$\vec{D} = \sigma \vec{T} + \varepsilon \vec{E} \tag{2}$$

where  $\overrightarrow{D}$  is electric charge density displacement,  $\sigma$  is coefficient of the piezoelectric effect,  $\overrightarrow{T}$  is stress,  $\varepsilon$  is permittivity, and  $\overrightarrow{E}$  is the electrical field strength. Typically, the applied stress  $\overrightarrow{T}$  is limited by the physic capability of crystal and is always in the form of vibration. Thus, the generated electrical field, harvested voltage and current are in AC form. This is the major difference between PT and other DC energy sources as PV and TEG. Note that the piezoelectricity is also a reversible procedure. As a mechanic actuator, it widely used in nowadays MEMS and mobile devices [28]-[30]. One biomedical application will be introduced in Section 5.

Figure 7. Structure of common piezoelectric transducers.

Table 3. Performance comparison of various piezoelectric transducers tested at 60Hz frequency and 1G acceleration amplitude.

| rrequericy and 10 acceleration amplitude. |                      |                       |                        |                          |                                      |                     |

|-------------------------------------------|----------------------|-----------------------|------------------------|--------------------------|--------------------------------------|---------------------|

| Manufacturer<br>ID                        | RMS<br>Power<br>(mW) | RMS<br>Voltage<br>(V) | Resistance $(k\Omega)$ | RMS OC<br>Voltage<br>(V) | Peak to Peak<br>Displacement<br>(mm) | L×W<br>Size<br>(mm) |

| PPA-1001                                  | 1.8                  | 7.1                   | 28.6                   | 12.2                     | 3.9                                  | 54.4×22.4           |

| PPA-1011                                  | 3.2                  | 7.9                   | 19.5                   | 13.8                     | 7.0                                  | 71×25.4             |

| PPA-1021                                  | 1.6                  | 14.0                  | 125.1                  | 20.5                     | 5.4                                  | 71×10.3             |

| PPA-2011                                  | 4.3                  | 7.9                   | 14.7                   | 14.8                     | 4.3                                  | 71×25.4             |

| PPA-4011                                  | 19.5                 | 10.2                  | 5.4                    | 20.2                     | 2.4                                  | 71×25.4             |

Although monocrystalline PT has stronger piezoelectric effect, its fabrication is difficult due to the high processing temperature. Therefore, low cost polycrystalline PT are more favorable for IoT energy harvesting [31]. A generic structure of commercial

PTs are illustrated in Figure 7. Various kinds of PTs and their characteristics are listed in Table 3. Due to the relative low frequency of mechanic vibration, the harvested power is below  $10 \,\mu W$ .

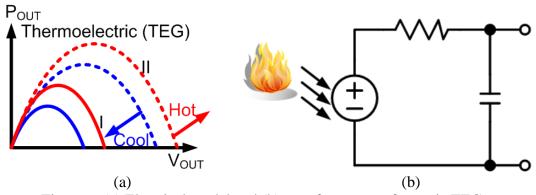

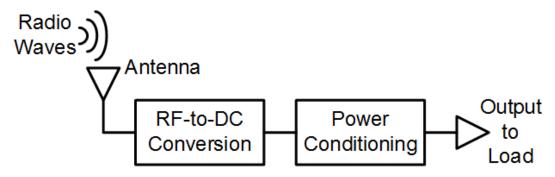

## 1.2.4 Radio Frequency Electromagnetic Wave

Radio frequency wireless communication is used in billions of transmitters worldwide, such as cell phones, radio, television, and emerging IoT mobile devices. Similar to transmit signals, the RF electromagnetic wave can be harvested by a system as Figure 8. The collecting components are antenna. It needs to be carefully designed to optimize the receiving magnitude of RF signal. The second part is the RF-to-DC power converter, which is a combination of high speed full-wave rectifier and boost converter [32]. Two critical issues are the impedance matching between antenna and rectifier, and the conversion efficiency of the boost converter. The power conditioning module handles the harvested energy and regulates it for specific load requirements.

Figure 8. Block diagram of a RF energy harvester.

The main advantage of RF energy is its pervasive nature. The aforementioned energy sources highly depend on spacing and intermediary material. For example, the

PV energy is very sensitive to shading conditions [33]. The TEG depends on not only heat generation, but also the path of heat sinking [34]. The PT requires continuous mechanic motion, which is difficult to be guaranteed in practical application [35]. As a comparison, the RF wave is less sensitive to the environment changing such like cloud and rainy days. Another advantage is the RF energy harvesting does not require dynamic MPPT as PV or TEG [36], which is done by designing a fixed shape antenna with a good receiving efficiency. The disadvantage of RF energy harvesting is its relative smaller magnitude, which drastically decay with respect to the square of distance. For example, a local 5kW AM radio station can only deliver hundreds of microwatts RF energy at 2.4 kM distance [37].

Figure 9. Available frequency bands for RF energy harvesting.

The RF candidate bands are broad from tens kHz AM radio up to GHz cell phone signals as shown in Figure 9. Generally, the higher frequency, the smaller antenna size and wave energy. The ideal antenna is an ultra-wide band (UWB) antenna for as many bands as possible; however, such design inevitably sacrifices performance in specific frequency to achieve a global optimization, and induces complex impedance matching in the following boost converter [38]. Therefore, for maximum harvested energy, nowadays

commercial products focus on a narrow band such as 850-950MHz of the P1100. Its specifications are listed in Table 4. Its minimum input power is -11.5dBm.

Table 4. Performances of the 915MHz RF energy harvester.

| Manufacturer ID | Minimum<br>Input Power<br>(dBm) | Maximum<br>Input Power<br>(dBm) | Maximum Output Current (mA) | Output<br>Voltage<br>(V) |

|-----------------|---------------------------------|---------------------------------|-----------------------------|--------------------------|

| P1110           | -5                              | 23                              | 100                         | 4.3                      |

| P2100B          | -12                             | 23                              | 100                         | 6                        |

## 1.3 Design Challenges of the Energy Harvesting

#### 1.3.1 Maximum Power Point Tracking Technique