# A STUDY OF OZONE AS AN OXYGEN SOURCE FOR THE GROWTH OF HIGH-K DIELECTRIC FILMS FOR GATE DIELECTRIC ON GAN/ALGAN/GAN

#### A Thesis

by

#### SHUVODIP BHATTACHARYA

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Chair of Committee, Committee Members, H. Rusty Harris Jun Kameoka

Aydin Karsilayan

Rupak Mahapatra

Head of Department, Miroslav M. Begovic

December 2016

Major Subject: Electrical Engineering

Copyright 2016 Shuvodip Bhattacharya

#### **ABSTRACT**

GaN is a promising alternative to silicon technology for the next-generation high-power and high-frequency electronics. The choice stems from the intrinsic properties of GaN of a wide bandgap and consequently high breakdown voltage, high saturation electron velocity and good thermal conductivity. Spontaneous and piezoelectric polarization effects cause accumulation of a high density of carriers at III-Nitride heterointerfaces enabling engineering of high mobility channels.

The primary factor inhibiting the further growth of GaN HEMTs is the high leakage current leading to device unreliability. The MIS-structure used in Si-CMOS processing has been adapted and shown to reduce leakage current in GaN technology. However, the introduction of an insulator adds another interface which suffers from poor quality due to innumerable traps with varying time constants. This leads to device threshold voltage instability and drain current collapse, while decreasing the device transconductance due to the increased gate-to-channel spatial separation. High-κ dielectrics have been shown to reduce leakage current with smaller decrease in transconductance in Si-CMOS technology and therefore, applied to GaN technology. ALD is recognized as a novel method for high-κ gate dielectric deposition, where H<sub>2</sub>O is primarily used as the oxygen source for growth; excellent properties have been reported. However, ozone-grown films show further suppressed leakage current and offer better interfacial quality on silicon.

In this study, MOSCaps have been developed on GaN/AlGaN/GaN heterostructures with PECVD Si<sub>3</sub>N<sub>4</sub> and ALD HfO<sub>2</sub> as the passivation layer and gate dielectric, respectively. HfO<sub>2</sub> was grown using *either* H<sub>2</sub>O *or* ozone as the oxygen source. XPS analysis, capacitance-

voltage, conductance-voltage and leakage current-voltage characteristics have been used as probes to study the quality of the film and its interface with the III-N semiconductor.

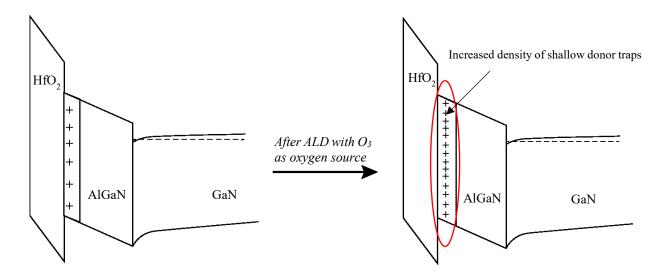

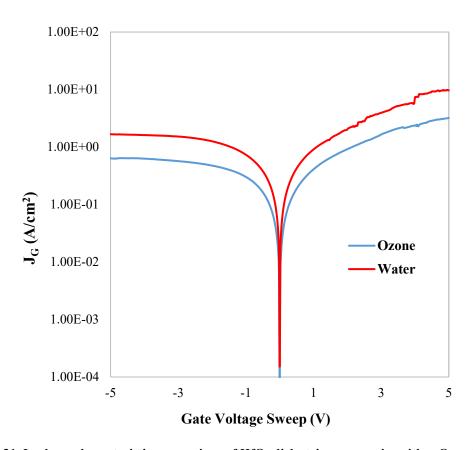

It is observed that due to the sufficient supply of oxygen, ozone helps in the formation of a better bulk dielectric by more complete oxidation. However, the interface is degraded by uncontrolled surface oxidation of the barrier layer or/and penetration of oxygen impurities, creating shallow donor traps aiding in leakage. The overall leakage current with the ozone-grown dielectric is reduced by almost half-an-order of magnitude due to the better bulk dielectric achieved.

To my parents...

#### **ACKNOWLEDGEMENTS**

I, hereby, would like to express my immeasurable appreciation and deepest gratitude for the help and support extended by the people mentioned hereafter toward the accomplishment of my two-year journey at Texas A&M University.

My deepest and sincerest gratitude goes out to my research adviser and mentor, Professor H. Rusty Harris, who has constantly appreciated my potential and imbibed in me the spirit to adventure into this arduous journey, with his excellent motivation and advice. Thank you for the spellbinding introduction in ECEN 688, to the enchanting area of fabrication and microelectronics, which happened be to my first course-work for my Master's program. This course provided me with a direction and paved the way for a new journey under your responsible supervision.

Sincere regards are also due to two of my course-mentors: Professor Haiyan Wang and Professor Jun Kameoka (who also happens to be one of my committee members), for their immensely helpful course content. In addition, I would like to thank them for their useful and insightful discussions about concurrent topics related to research and for providing me with constant enthusiasm to do better.

I would also like to thank my esteemed committee members: Professor Aydin Karsilayan and Professor Rupak Mahapatra, for taking valuable time out of their schedules to go through my thesis and come up with ideas of betterment.

A big thank you is due to everyone at AggieFab. Special mention should be made of Larry Rehn and Jim Gardner, for their constant full-fledged lab-support; they assisted me in

developing the proper care and skill to work with new equipment. Without you people, this work would not have been this smooth.

My sincerest gratitude goes out to all the staff associated with the Department of Electrical and Computer Engineering for all their support. Special thanks are due to Tammy Carda and Melissa Sheldon for passionately guiding me through the procedural complications and allowing me to concentrate only on my work by taking the responsibility for all paperwork.

The assistance, cooperation and company of my fellow group members deserve special mention. The companionship and cooperation of Alex, Feyza, Jae Woo, Michael, Pranav, Sravani and William will always be remembered. Thank you for all your support, time and the respect you have shown me. Thank you Alex, for being so supportive through the moments of anxiety and the moments of joy. Useful discussions with you were always a source of knowledge and relief for me. Thanks to William for constantly hammering me to take care of my health, besides your help on numerous other occasions.

My dear friend, Mohammadreza Soleymaniha, deserves special mention here. Your support, company and friendship helped me through the thick and thin. It is hard to describe the help you extended in words.

I would like to take this opportunity to thank some of my very special friends who have laughed and cried with me and have been available whenever I needed them.

Finally, all of this would have only been a dream without the support, immense love, endless encouragement, wise counsel and support of my parents. It would be the best feeling for me if this work makes them proud of their efforts in bringing me up the way they have.

## **NOMENCLATURE**

ε<sub>0</sub> Permittivity of vacuum

$\varepsilon_{\rm r}$  Relative electric permittivity

$\mu_n$  Mobility of electrons

2DEG 2-dimensional electron gas

ALD Atomic layer deposition

CV Capacitance-voltage measurements

CVD Chemical vapor deposition

DI Deionized

DRAM Dynamic random access memory

FET Field effect transistor

FG Forming gas

GaN Gallium nitride

GV Conductance-voltage measurement

HEMTs High electron mobility transistors

HFETs Heterostructure field effect transistors

JFoM Johnson figure-of-merit

MBE Molecular beam epitaxy

MIS Metal insulator semiconductor

MOCVD Metal-oxide chemical vapor deposition

MOS Metal oxide semiconductor

MOSCaps MOS capacitors

PDA Post-deposition anneal

PMA Post-metallization anneal

RF Radio frequency

RIE Reactive ion etching

TEMAH Tetrakis ethyl methyl amino-hafnium

TLM Transfer length method

TMA Trimethyl aluminum

$v_{\rm sat}$  Saturation velocity of electrons

$V_{TH}$  Threshold voltage

# **TABLE OF CONTENTS**

|                                                                   | Page |

|-------------------------------------------------------------------|------|

| ABSTRACT                                                          | ii   |

| ACKNOWLEDGEMENTS                                                  | v    |

| NOMENCLATURE                                                      | vii  |

| LIST OF FIGURES                                                   | xi   |

| LIST OF TABLES                                                    | xiv  |

| 1. INTRODUCTION                                                   | 1    |

| 1.1 GaN for RF applications                                       | 1    |

| 1.2 Potential for market                                          | 2    |

| 1.3 Schottky-contact HEMTs vs gated HEMTs                         | 3    |

| 1.4 Purpose of this study                                         | 6    |

| 1.5 Outline of thesis                                             | 6    |

| 2. THEORETICAL BACKGROUND                                         | 7    |

| 2.1 GaN properties                                                | 7    |

| 2.2 High-κ dielectrics                                            | 10   |

| 2.2.1 ALD of high-κ dielectrics                                   | 14   |

| 2.2.2 X-ray photoelectron spectroscopy (XPS)                      | 18   |

| 2.3 Electrical characterization techniques and conductance method | 20   |

| 3. FABRICATION OF BASELINE MOSCAPS ON                             |      |

| SILICON                                                           | 32   |

| 3.1 Device structure                                              | 32   |

| 3.2 Field dielectric module                                       | 33   |

| 3.3 Gate stack module                                             | 34   |

| 3.4 Back contact module                                           | 37   |

| 3.5 Electrical characterization                                   | 38   |

| 4. FABRICATION OF MOSCAPS ON GAN/ALGAN/GAN                        |      |

| HETEROSTRUCTURE                                                   | 43   |

| 4.1 Davica structura                                              | 13   |

|                                   | Page |

|-----------------------------------|------|

| 4.2 Contact module                | 44   |

| 4.2.1 Ohmic contacts              | 48   |

| 4.3 Gate stack module             | 51   |

| 4.4 Characterization              | 54   |

| 4.4.1 Chemical analysis           | 54   |

| 4.4.2 Electrical characterization | 58   |

| 5. SUMMARY                        | 66   |

| REFERENCES                        | 69   |

|                                   |      |

# LIST OF FIGURES

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

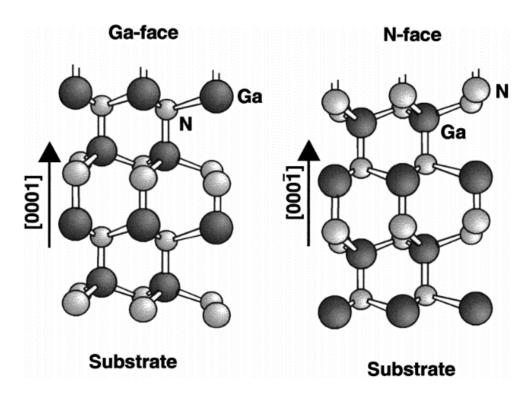

| Figure 1. | (a) Ga-faced and (b) N-faced GaN crystal structures. Reprinted from "Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures," by O. Ambacher <i>et. al</i> , 2000, <i>Journal of applied physics</i> , vol. 87, pp. 334-344, 2000. Copyright 2000 by American Institute of Physics. [5]                                                                                                                                        | 7    |

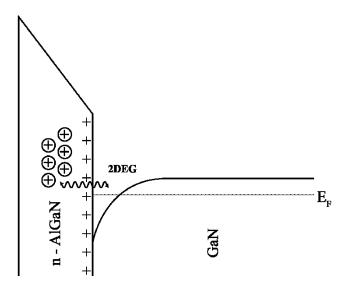

| Figure 2. | Band structure of n-AlGaN-GaN system showing the bending of the band and the presence of the 2DEG at the interface in equilibrium (Image shown here is not any simulated band diagram structure; it is used strictly for purpose of illustration)                                                                                                                                                                                                                                                            | 8    |

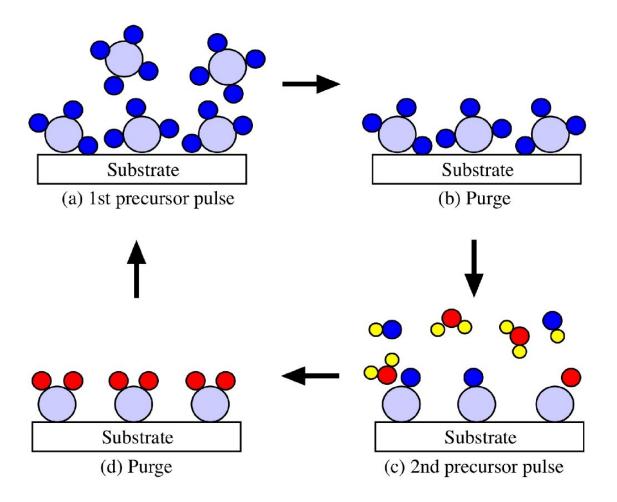

| Figure 3. | A schematic showing the presence of surface donors on an undoped-AlGaN layer surface providing electrons for the compensation of the polarization induced fixed positive charge at the AlGaN/GaN interface. These electrons are then trapped at the interface due to the high conduction band offset between GaN and AlGaN in what is known as a quantum well, forming the 2DEG at the interface (Image shown here is not any simulated band structure; it is used strictly for the purpose of illustration) | 9    |

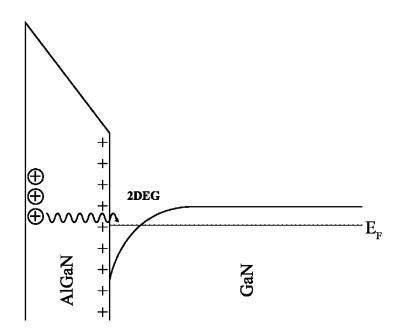

| Figure 4. | Schematic of ALD growth, reprinted from <i>Atomic Layer Deposition</i> , by Andrew R. Barron, July 2009, retrieved from http://cnx.org/contents/rimBK1xx@2/Atomic-Layer-Deposition.  Copyright 2009 by Andrew R. Barron. [4]                                                                                                                                                                                                                                                                                 | 14   |

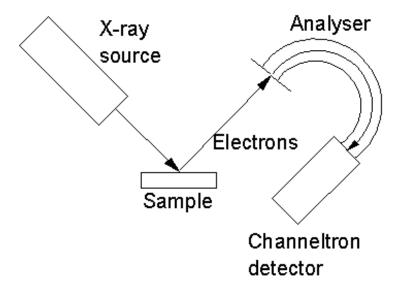

| Figure 5. | Schematic of an XPS system. Reprinted from 2. Film Analysis, by James R Petherbridge, July 2002, retrieved from http://www.chm.bris.ac.uk/pt/diamond/jamespthesis/chapter2.htm. Copyright 2002 by James R Petherbridge. [2]                                                                                                                                                                                                                                                                                  | 18   |

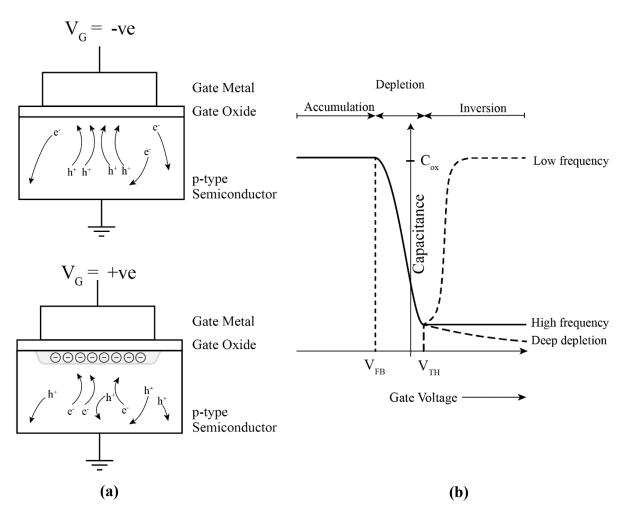

| Figure 6. | (a) Schematic of nMOSCap under accumulation (top) and inversion (bottom; grayed region shows the depletion region with immobile negative ions) (b) C-V characteristics of an ideal nMOS capacitor                                                                                                                                                                                                                                                                                                            | 21   |

|            |                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

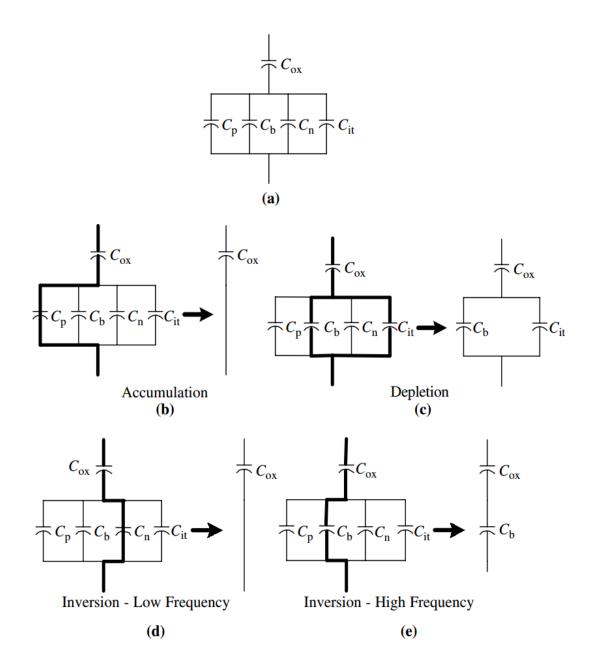

| Figure 7.  | Contributions to capacitance of the n-MOS system during various stages of traversing the C-V curves. Reprinted from <i>Semiconductor material and device characterization</i> (p. 323), by D. Schroder, 2006, Hoboken, NJ: John Wiley & Sons, Inc. Copyright 2006 by John Wiley & Sons, Inc. [1]                                                                                                     | 23   |

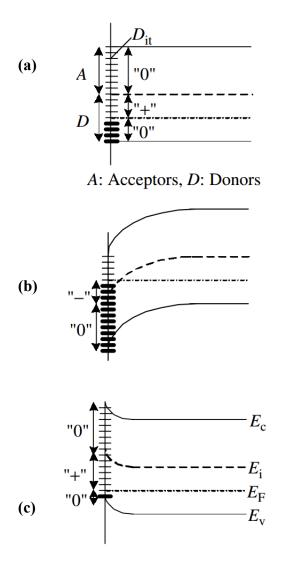

| Figure 8.  | Band diagram showing effect of interface states. Reprinted from <i>Semiconductor material and device characterization</i> (p. 343), by D. Schroder, 2006, Hoboken, NJ: John Wiley & Sons, Inc. Copyright 2006 by John Wiley & Sons, Inc. [1]                                                                                                                                                         | 26   |

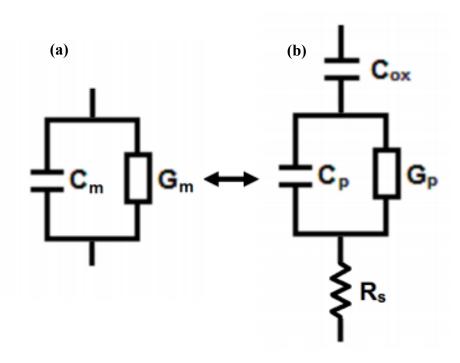

| Figure 9.  | (a) Circuit configuration as measured by the LCR meter. (b) Equivalent circuit configuration as suggested by Nicollian and Brews for the measurement of interface traps. Reprinted from <i>MOS (Metal Oxide Semiconductor) Physics and Technology</i> (p. 212), by E.H. Nicollian and J.R. Brews, 1982, Murray Hill, NJ: John Wiley and Sons. Copyright 1982 by Bell Laboratories, Incorporated. [3] | 28   |

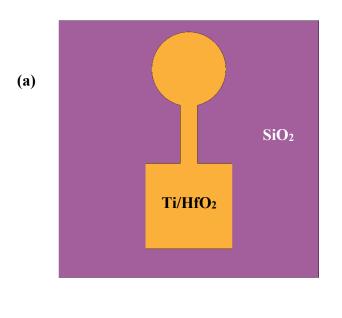

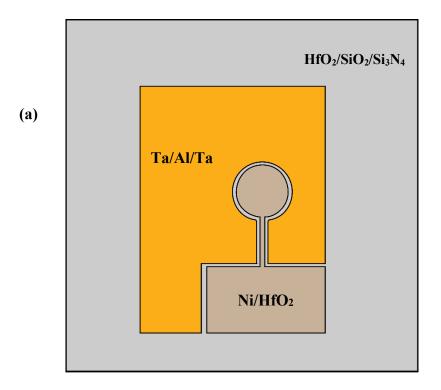

| Figure 10. | (a) Top-view and (b) cross-section of baseline MOSCaps developed on Si                                                                                                                                                                                                                                                                                                                               | 32   |

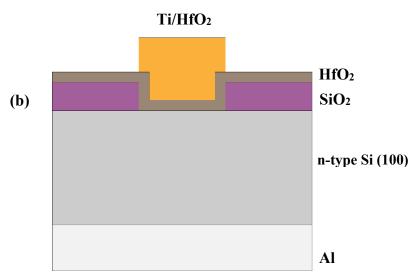

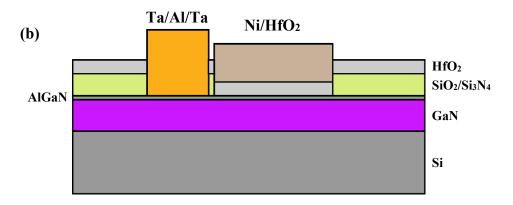

| Figure 11. | Micrograph of the final structure of MOSCaps with gate diameter of 100 μm (left) and 80 μm (right)                                                                                                                                                                                                                                                                                                   | 36   |

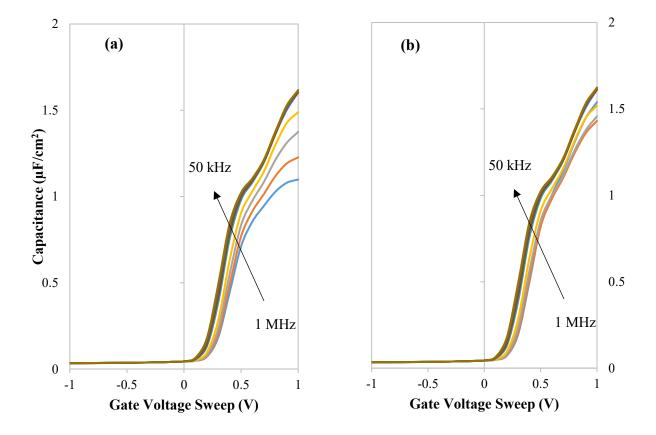

| Figure 12. | Measured capacitance-voltage characteristics (a) without and (b) with R <sub>s</sub> correction                                                                                                                                                                                                                                                                                                      | 38   |

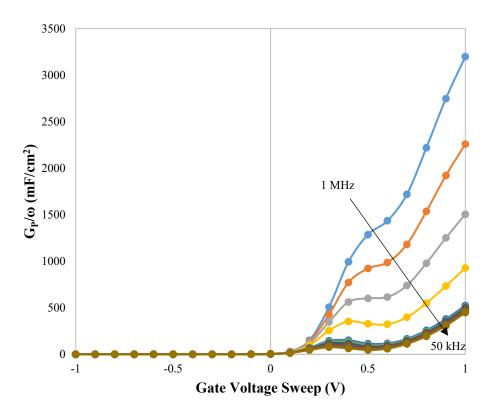

| Figure 13. | $R_S$ -corrected normalized conductance $G_P/\omega$ plot for the developed MOSCaps                                                                                                                                                                                                                                                                                                                  | 40   |

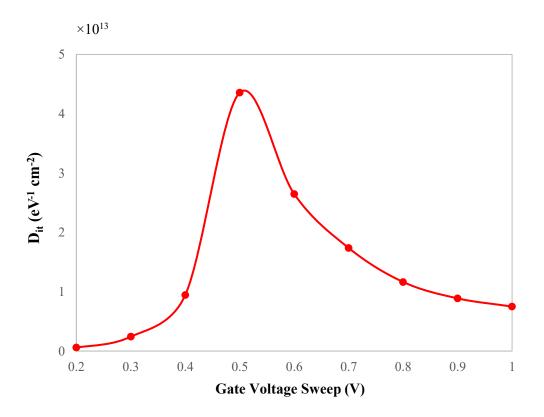

| Figure 14. | Extracted Dit vs. gate voltage                                                                                                                                                                                                                                                                                                                                                                       | 41   |

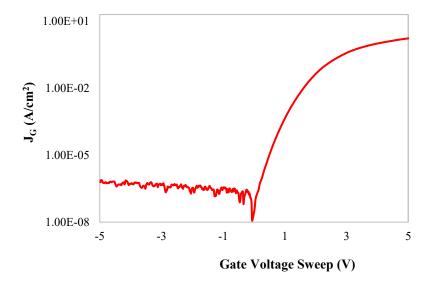

| Figure 15. | Leakage characteristics of Ti/HfO <sub>2</sub> /Si circular MOSCap structures with a diameter of 100μm                                                                                                                                                                                                                                                                                               | 42   |

| Figure 16. | (a) Top and (b) cross-section view of MOSCaps                                                                                                                                                                                                                                                                                                                                                        | 43   |

| Figure 17. | Zoomed-in area of the over-etch issue when using only wet etch                                                                                                                                                                                                                                                                                                                                       | 45   |

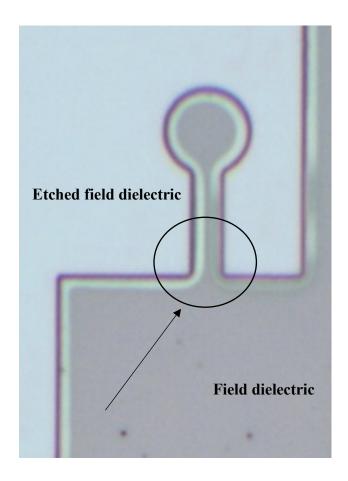

| Figure 18. | Capacitors in series can be combined into an equivalent capacitor                                                                                                                                                                                                                                                                                                                                    | 46   |

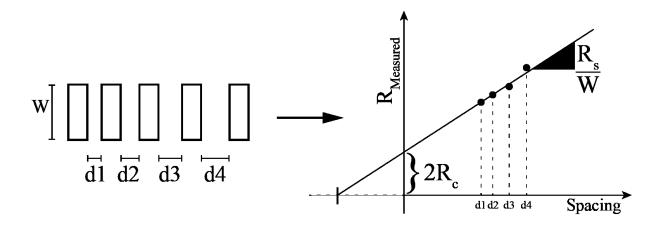

| Figure 19. | TLMs for contact resistance measurement (R <sub>C</sub> )                                                                                                                                                                                                                                                                                                                                            | 49   |

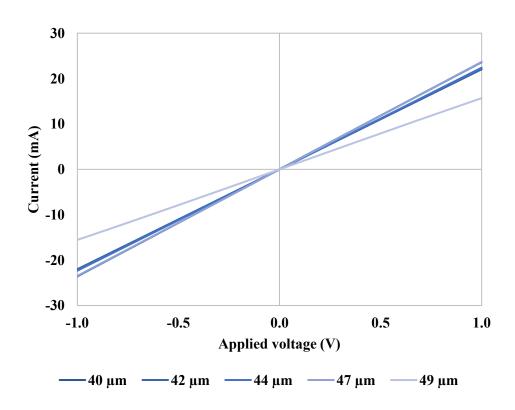

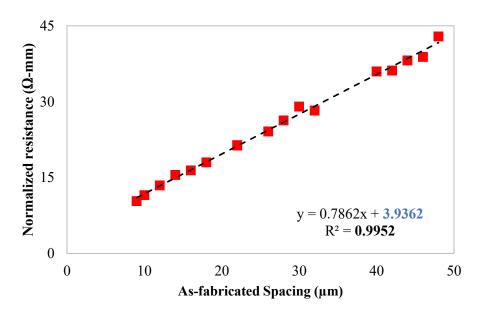

| Figure 20. | I-V measurements for TLM structures with increasing spacing                                                                                                                                                                                                                                                                                                                                          | 50   |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 21. | Plot of normalized resistance vs TLM spacing distance. As-fabricated spacing was used for retrieving true contact resistance data                                                                                                                                                                                                                                                                                                                     | 51   |

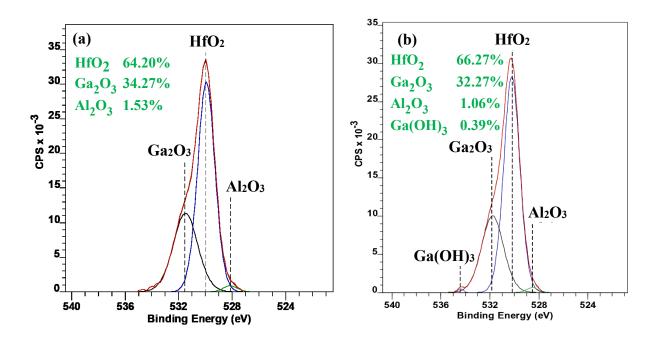

| Figure 22. | O 1s spectrum for (a) O <sub>3</sub> -based and (b) H <sub>2</sub> O-based HfO <sub>2</sub> film                                                                                                                                                                                                                                                                                                                                                      | 54   |

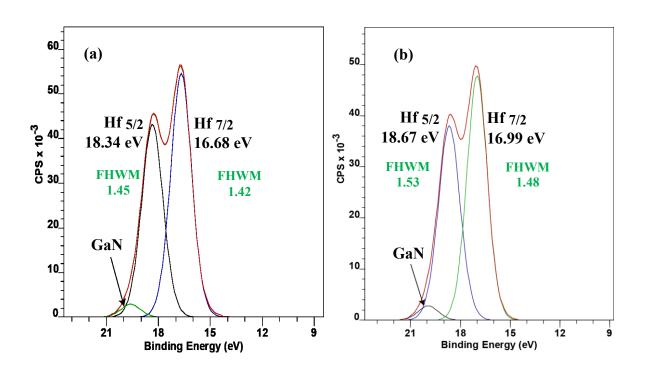

| Figure 23. | Hf 4f spectrum for (a) O <sub>3</sub> -based and (b) H <sub>2</sub> O-based HfO <sub>2</sub> film                                                                                                                                                                                                                                                                                                                                                     | 55   |

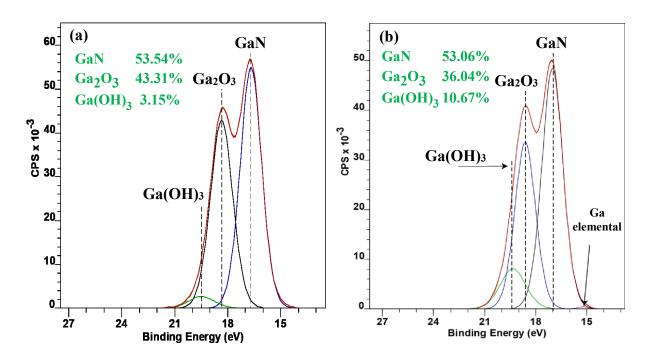

| Figure 24. | Ga 3d spectrum for (a) O <sub>3</sub> -based and (b) H <sub>2</sub> O-based HfO <sub>2</sub> film                                                                                                                                                                                                                                                                                                                                                     | 57   |

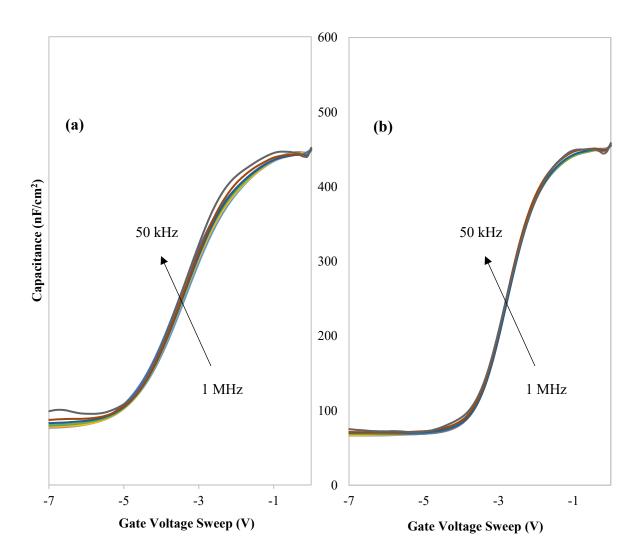

| Figure 25. | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                  | 59   |

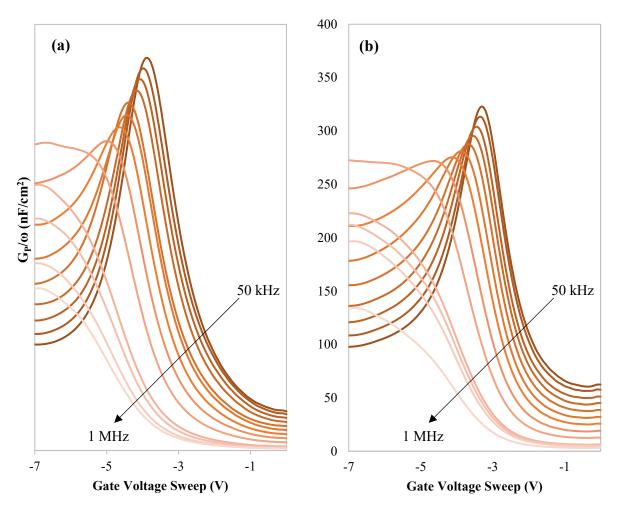

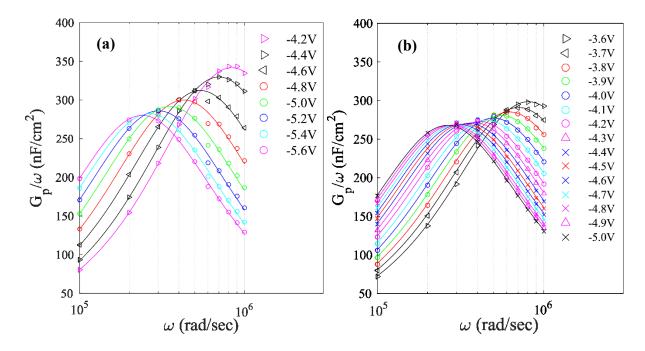

| Figure 26. | $R_s$ corrected $G_P/\omega$ curves for (a) $O_3\text{-}grown$ and (b) $H_2O\text{-}grown-HfO_2/GaN/AlGaN/GaN\ MOSCaps$                                                                                                                                                                                                                                                                                                                               | 60   |

| Figure 27. | $G_P/\omega$ vs. $\omega$ plots showing the extraction of the trap parameters by fitting the single state trap equation for (a) $O_3$ -based and (b) $H_2O$ -based sample                                                                                                                                                                                                                                                                             | 61   |

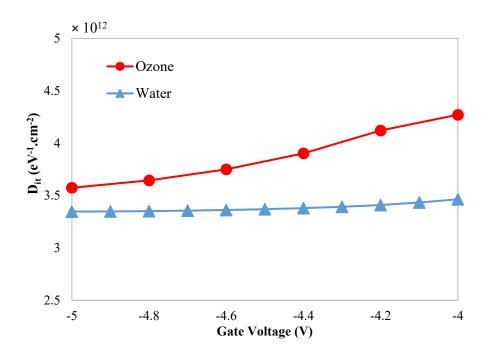

| Figure 28. | Extracted $D_{it}$ from the normalized $G_P/\omega$ vs. frequency plots using Eqn. 24                                                                                                                                                                                                                                                                                                                                                                 | 62   |

| Figure 29. | Extracted $\tau_{it}$ from the normalized $G_P/\omega$ vs. frequency plots using Eqn. 24                                                                                                                                                                                                                                                                                                                                                              | 62   |

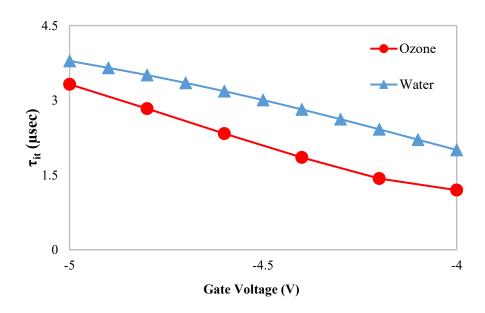

| Figure 30. | Possible mechanism for the increase in electrical trap activity for the O <sub>3</sub> -based sample under strong negative bias. With the formation of Ga <sub>2</sub> O <sub>3</sub> at the HfO <sub>2</sub> /AlGaN interface, there is an increase in the number of positive surface donors, leading to transfer of electrons to these empty surface donors from the channel showing up as an increased electrical activity in the conductance plot | 63   |

| Figure 31. | Leakage characteristic comparison of HfO <sub>2</sub> dielectric grown using either O <sub>3</sub> or H <sub>2</sub> O                                                                                                                                                                                                                                                                                                                                | 64   |

# LIST OF TABLES

|                                              | Page |

|----------------------------------------------|------|

| Table 1. Electronic properties of Si and GaN | 1    |

#### 1. INTRODUCTION

# 1.1 GaN for RF applications

GaN has many attractive properties for being the choice for next-generation high-power and high-speed electronic applications. It is a wide bandgap material (E  $_{\!g}\sim\!\!3.4eV)$  and has a high breakdown electric field, a high electron saturation velocity (higher than Si devices) and high density of states due to spontaneous polarization, all of which make it suitable for high output power density applications in communication technologies. Additionally, GaN is a direct bandgap material and finds immense usage in blue laser applications. When heterostructures are formed, for example with AlGaN, the induced strain in the film due to the differences in lattice parameters between GaN and AlGaN, added with the large potential barrier of the AlGaN on GaN causes a piezoelectric effect to add to the spontaneous polarization of AlGaN itself to accumulate a high density of carriers forming a well-confined channel called the 2-DEG at the interface, allowing vertical scaling engineering [5]. The high breakdown field and high mobility achieved allows for horizontal scaling which reduces the parasitic capacitance, increasing the potential for high cutoff frequencies  $(f_T)$ . A compilation of different electronic properties of competing semiconductors, Si, Ge and GaN is enlisted in Table 1.

Table 1. Electronic properties of Si and GaN

|                                        | Si              | GaAs | GaN           |

|----------------------------------------|-----------------|------|---------------|

| E <sub>g</sub> (eV)                    | 1.12 (indirect) | 1.42 | ~3.4 (direct) |

| $\mu_n \left( cm^2/V-s \right)$        | 1350            | 8500 | ~1800         |

| Ebreakdown (MV/cm)                     | 0.3             | 0.5  | 3.3           |

| $V_{\rm sat}$ (10 <sup>7</sup> cm/sec) | ~1.0            | ~1.1 | 2.5           |

| Er                                     | 11.9            | 12.9 | 8.9           |

| Heat dissipation, $\Theta$ (W/cm-K)    | 1.3             | ~0.4 | ~1.3          |

From previous works, the Johnson figure of merit (JFoM) ( $f_T \times E_{breakdown}$ ) of GaN-HEMTs can be seen to surpass the JFoM for the competing semiconductors namely GaAs and SiC, with an ultra-high  $f_T$  of 450GHz and simultaneous  $f_{MAX}$  of 440GHz [6]. The reduction of parasitic capacitances and delays allows for extreme parameters to be achieved using GaN-HEMTs. The channel in transistors made on Si work well till 140°C, beyond which external dopants cease to play any role, due to the small band-gap of Si. On the contrary, due to the larger band-gap of GaN, transistors made on GaN have been shown to withstand and work *well* up to temperatures of 300°C. These properties of GaN excited the research community to further study the potential of GaN to replace Si for high-speed and high output power devices.

#### 1.2 Potential for market

Power semiconductors have long been in the game for the development of high-power and high-voltage semiconductors for various applications including space electronics and radio-frequency communication applications. However, as Si-based power devices are reaching their technical limits, newer materials are in the process of replacing them. Among these, GaN has immense potential to be used in high-power and high-speed circuits which make them suitable for use in aerospace electronics, renewable energy systems, advanced next-generation communication systems, RADAR and RF frequency applications. GaN Power Semiconductors market has been estimated to be worth \$2.60 billion by the year 2022 [7].

However, according to a particular market research firm, Yole Développement, GaN still needs technical enhancements in the manufacturing process [8]. This mainly stems from the lack of high quality growth mechanisms for GaN, unlike its competing counterpart, Si. Transistors and RF-devices fabricated on GaN have proven to be excellent alternatives to their Si counterparts. The most important factor that can contribute to the exploding market of GaN

would be the ability to process GaN devices in a similar flow as the Si-CMOS processing. This would shorten the time needed for the maturity of the GaN processing, while reducing further research costs, development time and yield thereby reducing the cost per die. Additionally, the need for replacement of tools and equipment for the development of GaN technology would be minimal.

#### 1.3 Schottky-contact HEMTs vs gated HEMTs

Over the previous decade, GaN HEMTs have been investigated rigorously for their excellent performance [6, 9-11]. In HEMTs, a Schottky contact is essentially used to modulate the already formed channel, i.e. the 2DEG. However, HEMTs have been shown to have high leakage current due to activation and field-assisted tunneling, leading to low gate voltage swing capabilities [12]. These issues can be addressed by the introduction of the MIS-structure famous in Si-CMOS processing. It has indeed been found by various research groups that the MIS-HEMT counterparts allow large gate voltage swings (described as 10% decrease from the maximum transconductance,  $g_{max}$ ) without considerable increase in gate leakage current [13-15]. However, the introduction of a dielectric/insulator causes a negative shift in the threshold voltage, V<sub>TH</sub>, due to increase in the spatial distance between the channel and the gate which translates to lesser transconductance than the HEMT counterparts. These effects might be taken care of by the use of high-κ dielectrics – a larger dielectric constant translates to larger electrical energy storage by the dielectric film – this could mean effective modulation by the gate due to relatively less decrease in transconductance than that achieved with low-κ dielectrics. High-κ dielectrics are generally referenced to the dielectric constant of the industry standard dielectric for all this while, SiO<sub>2</sub>, which itself has a dielectric constant (κ) of 3.9. Various works have been reported on different insulators for the MIS-HEMT structures, namely HfO<sub>2</sub> [16, 17],

Al<sub>2</sub>O<sub>3</sub> [14], Si<sub>x</sub>N<sub>y</sub> [18], Sc<sub>2</sub>O<sub>3</sub> [19] and others. Amidst all the vast array of dielectrics, HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> have been studied extensively as alternatives for high-κ. It was shown by F Medjdoub *et. al.* that compared to unpassivated HEMTs, MISHEMTs with ALD Al<sub>2</sub>O<sub>3</sub> showed an order of reduction in leakage current and a considerable increase in drain current density [20]. Similar results were achieved by YUE YuanZheng *et. al.* [14].

HfO<sub>2</sub> has a high dielectric constant of 20-25 and a relatively wide band gap (5.6-5.8 eV) that attracted its extensive study as a gate dielectric on Si-MOSFETs. The performance of HfO<sub>2</sub> has likewise been studied on GaN HEMTs as an alternative high-κ dielectric. The advantage of HfO<sub>2</sub> lies in its high dielectric constant which allows it to store more electric energy. Thus, for the same film thickness, HfO<sub>2</sub> can be a better choice for modulating the channel than its lower-κ counterparts. Various deposition methods for HfO<sub>2</sub> have been studied which includes the likes of ALD, reactive ion sputtering and pulsed-laser deposition (PLD), among which HfO<sub>2</sub> grown using ALD results in a much better uniformity of the film due to the self-limiting growth properties of ALD [16, 21, 22]. C Liu et al. studied the properties of reactive sputtered HfO<sub>2</sub> and showed the promising capability of suppressing the leakage current by an order of five compared to its HEMT counterpart while maintaining a very high drain current and a relatively high transconductance, presumably due to the high dielectric constant of HfO<sub>2</sub> with added current collapse immunity [23]. Lee et al. studied the impact of ALD HfO<sub>2</sub> on device reliability and performance concluding with the excellent suppression of leakage current [21]. Yue et. al. studied the properties of a laminated gate dielectric stack with HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> (3nm/2nm) which resulted in an appreciable drain current and only single-digit percent decrease in transconductance, which was attributed mainly to the higher dielectric

constant of HfO<sub>2</sub> which allows it to store more charge for the same thickness of other dielectrics with lower dielectric constant [24].

ALD growth occurs over two cycles (binary reaction) - one cycle involves the introduction of the oxygen source, which prepares the surface by termination at -OH bonds when using  $H_2O$  as an oxygen source; in the subsequent cycle, metal precursors are introduced into the chamber, which break down the above mentioned bonds and form the desired oxide. More details about the principle of ALD growth and its benefits will be discussed in a later section. The most rigorously studied oxygen source for growth of high-κ dielectrics is H<sub>2</sub>O. Good performance parameters of MIS-HEMTs with high-κ dielectrics grown using H<sub>2</sub>O as oxygen source have been reported [25]. However, oxide films deposited by ALD with H<sub>2</sub>O as oxygen source have been known to have impurities, namely residual carbon and hydroxyl (-OH) groups, which may facilitate the formation of an interfacial oxide layer degrading the EOT and leakage characteristics of the dielectric film. J. B. Kim et. al. compared the characteristics of ALD Al<sub>2</sub>O<sub>3</sub> grown on Si substrates using either H<sub>2</sub>O or O<sub>3</sub>, in which case, growth done with O<sub>3</sub> showed lesser Al-Al clusters and –OH groups on the surface, groups which generally aid in leakage by degrading the interface and bulk properties of the film [26]. The reduction of -OH groups on the surface on O<sub>3</sub>-grown Al<sub>2</sub>O<sub>3</sub> enhanced the interfacial properties and resulted in a suppression of leakage current by one or two order(s) of magnitude compared to its H<sub>2</sub>O-based counterpart. C-V characteristics showed similar EOT and much less pronounced shift in flatband voltage in the O<sub>3</sub>-based Al<sub>2</sub>O<sub>3</sub>, which were again attributed to reduction of Al-Al clusters and removal of -OH groups from the surface. T Kobu et. al. extensively studied ALD Al<sub>2</sub>O<sub>3</sub> on GaN using H<sub>2</sub>O, O<sub>3</sub> and H<sub>2</sub>O and O<sub>3</sub> combined as oxygen source, which revealed that H and C contamination could be reduced to an appreciable extent by using both H<sub>2</sub>O and O<sub>3</sub> precursors as oxygen source as compared to the films grown using individual precursors [27]. Moreover, similar reduction in Al-Al bonds was observed by inclusion of O<sub>3</sub>, coupled with reduction of fixed charge that caused a positive shift in V<sub>TH</sub>. Such reduction in –OH, C and H impurities is required for device reliability and good interfacial quality.

# 1.4 Purpose of this study

In this work, a gate-last process flow of fabricating metal oxide semiconductor capacitors has been developed for both Si and GaN/AlGaN/GaN-on-Si heterostructures. The gate dielectric, HfO<sub>2</sub>, has been grown by ALD using either O<sub>3</sub> or H<sub>2</sub>O as the oxygen source. Chemical analyses of the dielectric film grown on GaN/AlGaN/GaN using the two different oxygen sources have been performed using XPS. Electrical characterization in the form of capacitance-voltage, conductance-voltage and leakage current density have been used as probes to study the interfacial and bulk properties of the dielectric.

#### 1.5 Outline of thesis

Section 1 has already dealt with a brief background and the need for MIS-HEMT structures with incorporation of high- $\kappa$  dielectrics. Section 2 introduces important theoretical background required for reviewing the content of this work along with essential information about interface traps, their behavior and their measurement from electrical characterization of metal insulator semiconductor capacitor structures. Section 3 and 4 deal with the fabrication of the MOS-capacitors on Si and GaN/AlGaN/GaN-on-Si respectively, along with electrical characterization, measurement of trap densities and device performance parameters. Finally, the important inferences of this work have been summarized and any future study possible has been discussed in Section 5.

#### 2. THEORETICAL BACKGROUND

## 2.1 GaN properties

Transistors fabricated on III-V semiconductors are called HEMTs. The high electron mobility and charge density comes from a combined effect of spontaneous and piezoelectric polarizations occurring in these materials. Due to the noncentrosymmetric structure of III-V compound crystals, they have two different crystallographic directions, which lie parallel to the basal plane (0001) and exhibit polarity along these axes [5]. In the hexagonal wurtzite GaN crystal, there can be termination at the surface with either Ga or N, forming Ga-face and N-face crystal respectively. By convention, a vector is denoted in the direction from a Ga atom to the nearest neighboring N atom. Hence, as shown in Fig. 1 [5], (0001) and (0001) is the Ga-

Figure 1. (a) Ga-faced and (b) N-faced GaN crystal structures. Reprinted from "Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures," by O. Ambacher *et. al*, 2000, *Journal of applied physics*, vol. 87, pp. 334-344, 2000. Copyright 2000 by American Institute of Physics. [5]

Figure 2. Band structure of n-AlGaN-GaN system showing the bending of the band and the presence of the 2DEG at the interface in equilibrium (Image shown here is not any simulated band diagram structure; it is used strictly for purpose of illustration)

face and N-face crystal respectively. The terminating atom decides the chemical and physical properties of these two different configurations.

When heterostructures are formed on Ga-faced GaN crystals, for example, AlGaN on GaN, the lattice mismatch between the two films causes a piezoelectric polarization which gives rise to a strong electrical field to the tune of 2MV/cm to be established and this strong field consequently induces a positive polarization charge at the AlGaN/GaN interface and the opposite negative polarization charge at the top of the AlGaN layer. Intuitively, the band tilts toward the interface, along with the Fermi level (see Fig. 2). For an n-doped AlGaN, which would then have donors in the bulk readily contributing conducting electrons, these electrons would then move toward the interface in order to compensate for the positive charge build-up at the interface and to restore local charge neutrality. The donors, now depleted, would have positive charges which reduces the overall intensity of the electric field in the AlGaN layer making the Fermi level flatter. These electrons would gather at the AlGaN/GaN interface,

forming the 2DEG, due to the Fermi level of GaN being lower than that of n-doped AlGaN. However, the whole concept of shifting intense research work toward heterostructure engineering was to avoid the various scattering effects associated with impurity doping in the channel material. Fortunately, for even an undoped AlGaN barrier layer, a 2DEG is formed at the interface of the AlGaN/GaN (see Fig. 3), which brings to question the origin of such electrons. In an undoped AlGaN layer, very few conducting electrons would be present and their concentration would not be enough to compensate for the large sheet of piezoelectric and spontaneous positive charge induced at the barrier interface with GaN. The possibility of electrons being supplied by the GaN bulk layer is almost absent because there exists a reverse electric field due to spontaneous polarization in the GaN bulk layer itself which would inhibit

Figure 3. A schematic showing the presence of surface donors on an undoped-AlGaN layer surface providing electrons for the compensation of the polarization induced fixed positive charge at the AlGaN/GaN interface. These electrons are then trapped at the interface due to the high conduction band offset between GaN and AlGaN in what is known as a quantum well, forming the 2DEG at the interface (Image shown here is not any simulated band structure; it is used strictly for the purpose of illustration)

the flow of electrons. It is assumed that surface donors at the top surface of AlGaN provide with sufficient electrons to compensate for the induced positive charges at the interface [28]. All of the above discussion reverses when a N-faced GaN is used as the substrate material.

In contrast to a Si-based FET, where a potential is required to form the channel of carriers, the channel is always present due to the presence of the 2DEG in III-N semiconductor technology. In order to cut off the channel, a negative voltage is required to be applied. From the point of view of reliable, less leaky devices, normally-off transistors are preferred. Several methods have been studied to fabricate normally off transistors on AlGaN/GaN, which include the use of N-faced GaN as the substrate as explored by S. Sugiura *et.al.*[22] or the use of fluorine-based plasma treatment of the GaN or AlGaN as reported by Chen *et.al.* where the embedded fluorine ions essentially act like fixed negative charges thereby repelling the 2DEG and consequently enabling enhancement-mode operation [29]. However, plasma treatments have been known to facilitate defect generation at the barrier/III-N interface causing an increase in the scattering effects, failing the purpose of the 2DEG.

## 2.2 High-κ dielectrics

Introducing high-κ dielectrics in fabrication of MOS structures traces its way back to the infamous Si-MOSFETs. Gordon Moore, the co-founder of Intel and Fairchild Semiconductor, in his 1965 paper, now famously known as Moore's law, made an observation which essentially described the doubling of the number of components (transistors) per integrated circuit every year [30]. In 1975, this observation was revisited by Moore himself to adjust the pace to "doubling every two years". Indeed, for a long time till the 2000's, the observation Moore made was holding, and steadfast growth was made in semiconductor industry to meet the challenging prophecy.

To keep up with the pace, the physical size of the transistors had to be reduced significantly to allow the doubling of components. Si was the most common semiconductor those days essentially because of the high quality native oxide, SiO2, and nitride, Si3N4, that could be formed by thermal treatments in an oxygen and a nitrogen environment respectively, followed by the quality of SiO<sub>2</sub> grown in a steam environment. These were excellent dielectrics for use in the capacitors required for DRAMs, because the quality of the interface between the semiconductor and its oxide was the best possible known to the semiconductor industry. The interface states density at the SiO<sub>2</sub>/SI interface was found to be a record low at  $\sim 10^9$  cm<sup>-2</sup>eV<sup>-1</sup>. The low interface states density allowed for further scaling of the dielectric down to a few nanometers helping to keep up with the pace of the Moore's law and exhibiting excellent leakage current performance parameters and admirable control of drain-to-source current via the gate. Classical mechanics ruled the mechanism of current control up to this point. The horizontal scaling led to dramatically decreasing the gate length (L<sub>g</sub>) and the vertical scaling required drastic decrease in the oxide thickness  $(t_{ox})$ , leading to the thinning of the dielectric to a few nanometers (~1 nm), the thickness of a few monolayers. As a reference, the oxide thicknesses for the 90 nm and 70 nm gate technology nodes are 1.2 nm and 0.7 nm respectively, compared to the 3nm thickness for tunneling limit for SiO<sub>2</sub>. This introduced a whole new world of issues with further scaling which called for an exponential increase in the amount of research and development for newer alternatives to SiO<sub>2</sub>.

Quantum physical effects started dominating the mechanisms of these scaled devices, especially tunneling. Tunneling is a quantum mechanical effect where electrons, if provided enough thermal or field energy in the form of an electrical field, can tunnel through a thin oxide layer. Various tunneling models have been developed over the past two decades, a few being

Fowler-Nordheim (FN), Direct Tunneling (DT) and Poole-Frenkel (PF) tunneling. Tunneling increases leakage currents which results in heat generation in the integrated circuit, thereby introducing unreliability in the device operation. Another issue often encountered in ultra-thin oxide films is soft-breakdown or temporary breakdown. Voltage stress on the gate contact induces a current which in turn increases leakage current, also resulting in device unreliability. When all these effects are combined with temperature and bias stressing, the devices with ultra-thin oxide films exhibit detrimental levels of leakage currents, to the order of 100 A/cm<sup>2</sup> at gate voltage of 1V, which can cause true breakdown of the devices. With the billions of transistors on a single chip, this leakage would mean power drain as well as heat dissipation problems.

The technological industry had to make an important consideration and rethink the whole process to keep up with the pace set by Moore's law. This paved the way for the introduction of the high- $\kappa$  dielectrics, where ' $\kappa$ ' refers to the dielectric constant. From a simple consideration of the parallel plate capacitance relation,

$$C_{equivalent} = \kappa \frac{\varepsilon_0 A}{t_{oxide}} \tag{1}$$

where  $\epsilon_0$  is the absolute permittivity of vacuum, A is the effective area of the capacitor,  $t_{oxide}$  is the effective thickness of the oxide and  $\kappa$  is the relative permittivity of the oxide, it can be seen that the capacitance is a multiple by a factor of ' $\kappa$ '. Hence it is possible to maintain a thick dielectric, where the factor ' $\kappa$ ' compensates for the thickness by maintaining the capacitance as would be achieved using a thin  $SiO_2$  layer. This introduces a concept namely 'effective oxide thickness (EOT)', which relates the thickness of the  $SiO_2$ , the semiconductor industry-standard dielectric thus far, that would be required to emulate the same capacitance as that of the corresponding thickness of high- $\kappa$  dielectric and can be expressed as follows:

$$EOT = t_{high-\kappa} \cdot \left(\frac{\kappa_{SiO_2}}{\kappa_{high-\kappa}}\right) \tag{2}$$

Since SiO<sub>2</sub> has many of the desirable properties required for the operation of gated devices, it is imperative that similar properties are to be desired from the high-κ dielectrics that would replace SiO<sub>2</sub>. Some of these property criteria are met by a few dielectrics, namely HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub> and others. However, there are several issues related with these high-κ dielectrics. They have poorer interfacial properties and thermal properties when compared to SiO<sub>2</sub>. The dielectric/semiconductor interface is characterized by at least two-to-three orders of magnitude more interfacial traps and oxide traps than SiO<sub>2</sub>, which act as centers for trapping electrons. During the gate voltage excursion, these traps dynamically charge and discharge and hence cause instability in the threshold voltage (V<sub>TH</sub>) of devices.

One of the most extensively studied oxides on Si is HfO<sub>2</sub>, owing to its low interfacial states density at the oxide/semiconductor interface, a very high dielectric constant (20-25) and a moderately wide band-gap (5.6-5.8 eV). Prior work on HfO<sub>2</sub> on Si and GaN-based devices can be found in Section 1.3 Schottky-contact HEMTs vs gated HEMTs.

A similar approach is applied to III-V semiconductor-based transistors. Several works have already been published on different experimental dielectrics, as enlisted in Section 1.3 Schottky-contact HEMTs vs gated HEMTs, in the search for a high-κ dielectric with desirable properties such as low oxygen vacancies and fixed charge, a relatively high thermal stability to withstand the high temperatures required for the Ohmic contact anneals, a good dielectric/semiconductor interface, and most importantly, a high breakdown field to withstand high blocking voltages of 1kV meant for developing next-generation high-power and high-voltage switching circuits.

# 2.2.1 ALD of high-κ dielectrics

Several deposition techniques have been studied in the recent past like MOCVD, MBE, RF Sputtering, PECVD, HDPCVD, ALD and others, all of which aim at faithful deposition of the dielectrics such that they have the least interfacial states density and fixed oxide charge. The most famous, however, out of all of these deposition methods is ALD. Extensive studies on the mechanisms of ALD have already been performed and it is a well-developed process.

Figure 4. Schematic of ALD growth, reprinted from *Atomic Layer Deposition*, by Andrew R. Barron, July 2009, retrieved from <a href="http://cnx.org/contents/rimBK1xx@2/Atomic-Layer-Deposition">http://cnx.org/contents/rimBK1xx@2/Atomic-Layer-Deposition</a>. Copyright 2009 by Andrew R. Barron. [4]

Realizing the potential for this deposition process, researchers and scientists are developing and synthesizing different organo-metallic compounds that can aid in the growth of alternative dielectrics using this process. It has been announced as the most preferred deposition process for growing high-κ dielectrics by the International Roadmap for Semiconductors (ITRS) [31].

ALD is a modified chemical vapor deposition system, which uses usually H<sub>2</sub>O as the oxygen source in one cycle and organo-metallic compounds as the precursor for the metal component of the dielectric in the subsequent cycle to form the desired dielectric film on the substrate [31]. The surface of the substrate is activated by a chemical reaction in every cycle. The oxygen source,  $H_2O$ , causes termination of the surface with -OH groups which act as the reaction centers for the subsequent step. The most intriguing aspect of ALD is that it forms a saturated surface with -OH terminated bonds and no further reaction of the same species occurs. In other words, there is only one layer of –OH terminated surface formed. This is called the self-limiting growth property of the ALD. A purge step using either Argon or Nitrogen is usually performed after the first pulse. Moving on, in the next step, when the organo-metallic compound is introduced into the chamber, the -OH bonds break and react with the organometallic compounds to form the desired dielectric and some gaseous by-products which can be removed from the chamber by another purge step immediately after the introduction of the metal precursor. A schematic of the ALD process is shown in Fig 4 [4]. Note that the schematic only shows the concept behind the growth; the cartoon doesn't use any specific precursor structure. The above properties of the ALD growth process allows for extremely low temperatures of deposition to be attained. The thermal budget is important to be maintained. This attributes itself to the following reason. Usually, high-κ dielectrics are oxides of transition metals. These transition metals have a high affinity for oxygen and form oxides very easily.

However, the transition metal oxides are easily crystallized at relatively low temperatures, which results in the formation of grain boundaries serving as percolation paths for leakage when a high transverse electric field is applied across the dielectric, ultimately leading to breakdown. Both of these properties are addressed by the ALD. Low temperature deposition is made possible by activating the surface chemically. Also, the low deposition temperature ensures the amorphous deposition of these transition metal oxides.

ALD growth of two of the most popular high-κ dielectrics, HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, have been studied extensively by the research fraternity. The organo-metallic precursors used for HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> are TEMAH and TMA respectively. A schematic of the possible chemical reaction for the growth of HfO<sub>2</sub> using H<sub>2</sub>O can be summarized as follows:

Step 1: After introduction of TEMAH into the ALD chamber.

$$-2 \text{ OH +Hf(NR}_1 R_2)_4 \longrightarrow -O \\ -O \\ \text{Hf(NR}_1 R_2)_2 + 2 \text{ HNR}_1 R_2$$

Step 2: After introduction of H<sub>2</sub>O into the ALD chamber.

On the contrary, when using O<sub>3</sub> as an oxygen source, the following possible reactions can be summarized as follows:

Step 1: After introduction of O<sub>3</sub> into the ALD chamber.

Step 2: After introduction of TEMAH into the ALD chamber.

It was shown by T Kobu *et. al.* that compared to the Al<sub>2</sub>O<sub>3</sub> film grown using H<sub>2</sub>O as oxygen source, the film grown using O<sub>3</sub> features a decrease in H concentration and an increase in C concentration [27]. The above observation can be attributed to the highly reactive nature of O<sub>3</sub>, which decomposes and forms more carbonates as compared to H<sub>2</sub>O. On the other hand, the decrease in H concentration can be explained by the 'dehydration' or removal of the –OH groups from the surface which have long been thought to facilitate the formation of an interfacial layer at the oxide/semiconductor interface, which can act as the source of short-to-long duration traps and cause instability in the threshold voltage of the devices. It was also shown by Kim *et. al.* that the advantage of using O<sub>3</sub> as the oxygen source is it reduces the possibility of formation of Al-Al clusters which can serve as leakage paths degrading the quality of the film [26]. The reduction was attributed to the deficiency of oxygen when using H<sub>2</sub>O as the source. Similar concepts can be applied to the deposition of HfO<sub>2</sub> using O<sub>3</sub>. In this work, ALD has been used as the deposition process for HfO<sub>2</sub> using TEMAH as the metal

precursor and either H<sub>2</sub>O or O<sub>3</sub> as the oxygen source on GaN/AlGaN/GaN and the interface properties thereof probed using chemical and electrical analysis techniques.

#### 2.2.2 X-ray photoelectron spectroscopy (XPS)

As has already been discussed, the surface and the semiconductor/dielectric interface are essential for the study of reliability and performance of transistors. Over the years, many important surface analysis techniques have been developed which include the likes of time-of-flight secondary ion mass spectroscopy (TOF-SIMS), Auger electron spectroscopy (AES) and X-ray electron spectroscopy (XPS). Each tool has its own advantages and disadvantages. Out of these, XPS is the most sensitive chemical analysis tool that has been in use for quite some time. A brief background into the principle and working is discussed below.

XPS, also referred to as Electron Spectroscopy for Chemical Analysis (ECSA), is based on the photoelectric effect that was first explained successfully by Einstein, for which he was

Figure 5. Schematic of an XPS system. Reprinted from 2. Film Analysis, by James R Petherbridge, July 2002, retrieved from <a href="http://www.chm.bris.ac.uk/pt/diamond/jamespthesis/chapter2.htm">http://www.chm.bris.ac.uk/pt/diamond/jamespthesis/chapter2.htm</a>. Copyright 2002 by James R Petherbridge. [2]

awarded the Nobel Prize in 1912. The sample under observation is subjected to a beam of photons of specific well-defined energies to energize the electrons bound in the atoms immediately below the surface of the sample (see Fig. 5) [2]. The monochromatic X-ray is formed by aiming a 10 keV electron gun at an Al or Mg target to produce Al  $K_{\alpha}$  and Mg  $K_{\alpha}$  X-rays, the spot size of the beam ranging from 20-200  $\mu$ m. When the energy of the photons in the beam is almost equal to or larger than the binding energy of the electrons, the electrons are knocked off from the surface and collected by a detector. The kinetic energy (KE), binding energy (BE), the photon bean energy (E<sub>photon</sub>) and the work function ( $\phi$ ) can be related as:

$$BE = E_{photon} - (\phi + KE) \tag{3}$$

Since the  $E_{photon}$  is known and the KE of the electron measured, the BE of the electrons can be measured by adjusting the  $\phi$ , which is dependent on both the system and the material being analyzed. In a condensed matter, according to the band theory and Pauli's exclusion principle, all energy levels are quantized. Thus extracting the BE value from the XPS peaks can help study the presence of chemical species and their binding states. Even though it seems to be a qualitative technique, XPS can be used for quantitative analysis. The number of electrons knocked off from the surface in response to the photon beam is directly proportional to the number of atoms of the specific energy at the surface. Chemical stoichiometry can be estimated from the atomic concentration acquired from the data. However, it is sometimes challenging to produce results to the atomic concentrations. An essential parameter used to understand the chemical composition of the surface is full-width at half-maximum (FWHM). As a rule of thumb, broadening of the peak may indicate a change in the chemical bonding state. Sometimes broadening of the peak may also indicate a localized charging of the surface, which might be due to the continuous beam of photons hitting the surface.

A few disadvantages however make XPS a time-consuming and cumbersome analysis technique. There is no doubt about the potential of XPS producing almost precise data, but it comes at a price. Surface preparation is an important step for performing XPS. The background noise generated by electrons, with energy lesser than the measurement energy, can degrade faithful analysis of chemical species. Also, it is important that the XPS chamber be under ultrahigh vacuum ( $<10^{-9}$ – $10^{-10}$  Torr) such that the mean free path ( $\lambda$ ) is essentially greater than the distance between the sample surface and the collector, to avoid collisions between residual chamber chemical species. The mean free path,  $\lambda$ , can be approximated by the following relation:

$$\lambda \approx \frac{5}{P(Torr)} cm \tag{4}$$

The XPS can be an excellent tool for chemical surface analysis for approximately 5–10 nm depth from the surface. The precision of the XPS has long served as a faithful tool for the study of surfaces.

#### 2.3 Electrical characterization techniques and conductance method

Performance of gated transistors depends heavily on the quality of the interface between the dielectric and the semiconductor substrate. Interfacial quality depends on a lot of factors, including the density of interfacial states and the presence of any undesired interface, which can be a primary contributor of slow and/or fast traps, the dynamic charging and discharging of which can contribute further to the performance degradation of the transistors. The density and distribution of these interfacial and bulk dielectric traps can heavily alter the performance parameters and reliability of these transistors. For example, a high interfacial trap density, D<sub>it</sub>, would result in a shift in the threshold voltage (V<sub>TH</sub>) and hysteresis, exhibiting a memory effect. Therefore, it is imperative that test structures be developed and studied

thoroughly before these materials can be applied to the fabrication of transistors in the industry. MOS capacitors have been used for long as excellent test structures for the study of any semiconductor system owing to the simplicity of their fabrication, the absence of drain and source effects and the capability to study just the interface between the oxide and the semiconductor. As a matter of fact, it was rightly pointed out by Nicollian and Brews that a lot (about 20) of the properties about the MOS-system can be studied using MOSCaps [3]. Though most of the development of MOSCaps and the methods of studying the

Figure 6. (a) Schematic of nMOSCap under accumulation (top) and inversion (bottom; grayed region shows the depletion region with immobile negative ions) (b) C-V characteristics of an ideal nMOS capacitor

insulator/semiconductor system was developed keeping SiO<sub>2</sub>/Si in mind, most of the methods of analysis and modeling usually work for the newer insulator/semiconductor system with proper modifications and assumptions.

The capacitance-voltage and conductance-voltage measurement techniques have been the most famous electrical characterization techniques of all time. The oxides generally have a lot of defects such as interface traps owing to unsatisfied dangling bonds or due to the incompatibility between the oxide and the semiconductor substrate, fixed oxide charges, trapped charges in the oxide and oxide vacancies. All of these can be measured, with proper methodology, using the C-V and G-V technique. An MOS capacitor is essentially a structure comprising (from top-to-bottom) a gate metal, a gate oxide layer and a semiconductor substrate. Three regions of the C-V data extracted from an MOS capacitor are of immense aid for the systematic study of the MOS system – accumulation, depletion and inversion. Figure 6 shows an ideal C-V curve as expected from an n-type MOS (where the majority carriers are holes, i.e. p-doped substrate) capacitor with the different regions outlined. Figure 7 shows the contributions from different factors in an MOS system to capacitance, including interface traps (C<sub>it</sub>), hole charge density (C<sub>p</sub>), electron charge density (C<sub>n</sub>), depletion region charge density (C<sub>b</sub>) and oxide capacitance at strong accumulation (C<sub>ox</sub>) due to majority carriers [1].

In accumulation at a negative voltage applied to the gate, a huge quantity of holes would gather at the dielectric/semiconductor interface. The admittance for  $C_p$  approaches a large number, which practically shorts it. Hence the only capacitance contribution in accumulation is due to  $C_{ox}$ , as shown in Fig. 7 (b) by the bold line.

Therefore, in accumulation,

$$C_{accumulation} = C_{oxide} \tag{5}$$

Figure 7. Contributions to capacitance of the n-MOS system during various stages of traversing the C-V curves. Reprinted from *Semiconductor material and device characterization* (p. 323), by D. Schroder, 2006, Hoboken, NJ: John Wiley & Sons, Inc. Copyright 2006 by John Wiley & Sons, Inc. [1]

As the gate voltage is increased slowly toward the positive bias, the holes are repelled by a transverse electric field that is set up in a direction from the gate to the substrate. The minority carriers, the electrons in this case, start getting attracted and the surface starts being depleted of holes. A space-charge region, also called the depletion region, is developed near the surface by negatively charged immobile ions that have been ripped off of holes. The total charge contained in this region,

$$Q_h = -qN_AW_d \tag{6}$$

where, N<sub>A</sub> is the number of immobile ions and W<sub>d</sub> is the width of the depletion region.

Since this is a charged region, there would be contribution of capacitance,  $C_b$ , from this region. Not only that, any interface states or traps that might be present, will contribute to the capacitance,  $C_{it}$ , in parallel to  $C_b$ , and together in series with  $C_{ox}$ , as shown in Fig. 7 (c). Therefore, in depletion,

$$\frac{1}{C_{depletion}} = \frac{1}{C_{oxide}} + \frac{1}{C_{it} + C_b} \tag{7}$$

Further increase in the gate voltage causes an inversion in the type of carriers due to strong depletion of the holes and gathering of large quantity of electrons. Theoretically, this happens when the band bending causes the Fermi energy level ( $E_F$ ) to go below the intrinsic Fermi level ( $E_F$ ) and creates a 'well' for minority carriers to dwell and interact with the gate voltage at the surface. This process is known as 'inversion' and the MOS system works on the principle of formation of this inversion layer, which essentially acts like a channel. The depletion region reaches a maximum width,  $W_{d \, (max)}$ , which can be related as:

$$W_{d_{max}} = \sqrt{\frac{4\varepsilon\phi_b}{qN_A}} \tag{8}$$

where,  $\epsilon$  is relative permittivity of the substrate,  $\phi_b$  is the total band bending at inversion and  $N_A$  is the number of immobile acceptor ions.

The voltage at which inversion occurs is known as threshold voltage,  $V_{TH}$ , and is related to the total charge carried by the minority carriers as:

$$Q_{inversion} = -C_{ox}(V_G - V_{TH}) \tag{9}$$

Beyond this point, if  $V_G$  is further increased, there is not much appreciable change in the  $Q_{inversion}$  or  $W_{d(max)}$ . In this region of operation, there are two possible outcomes. If the measurement of frequency of the AC signal has a time constant larger than or almost equal to that of the time constant of the  $Q_{inversion}$  modulating (slightly expanding and contracting)  $W_{depletion}$ , then the surface charge is able to follow the AC signal and thereby contribute to equivalent capacitance. Otherwise, there is almost no additional capacitance contribution and it is this value of capacitance that is the final capacitance in this region of operation. The above two cases have been shown in Fig. 6 as low-frequency and high-frequency curves respectively. Similar considerations can be made for capacitors developed on the III-V semiconductor system. Since III-V semiconductor systems are always on due to the presence of the 2DEG,  $V_{TH}$  essentially refers to the voltage where the channel made by the 2DEG is cut off.

The ideal C-V curves are often a dream and seldom are these achieved even with the state-of-the-art technological tools and equipment. In nature, every other material is filled with impurities and defects, which alter the true characteristics of the material. In the semiconductor industry and research family, it has always been the ultimate goal and challenge to reduce the defect levels to the minimum achievable, for better device performance and reliability. A few of the defects that alter and degrade semiconductor device performance and pose a threat to reliability include fixed oxide charge  $(Q_f)$ , oxide trapped charges  $(Q_{OT})$  and interface trapped charges  $(Q_{it})$ . A brief description of the just mentioned defects have been touched upon before moving on to the effect these have on transistor performance and the methods to measure them.

Fixed oxide charges  $(Q_f)$  lend their origin to the process of deposition of the dielectric. It has been shown that a higher temperature of growth or an anneal at an elevated temperature can cause annihilation of these fixed charges. These are positive charged centers and do not exhibit any electrical characteristics. On the contrary, in ultra-thin oxides, trapped oxide

Figure 8. Band diagram showing effect of interface states. Reprinted from Semiconductor material and device characterization (p. 343), by D. Schroder, 2006, Hoboken, NJ: John Wiley & Sons, Inc. Copyright 2006 by John Wiley & Sons, Inc. [1]

charges can be present. They appear in the dielectric mainly after initiation of leakage, especially by Fowler-Nordheim tunneling, because the electrons or holes might lose energy after entering the dielectric and thereby rest inside the dielectric.

Interfacial defects state density (Dit) are defects located at the semiconductor/dielectric interface. These can either be positive or negative, which mainly arise due to incompatibility between the substrate and the dielectric, defects due to structural differences between them, impurities that might be deposited or adsorbed during the dielectric deposition process or due to dangling bonds at the termination of the underlying surface that might not be satisfied during the deposition process. They are active centers for charge trapping when an electrical field is applied across them. They can either charge or discharge, i.e. trap and emit carriers during a sweep of the gate voltage. These are termed 'fast charges' due to their ability to charge and discharge fast compared to the other types of dielectric defects, namely fixed charges and oxide trapped charges. The charge possessed by these defects (Qit) can be equated from the slope of the C-V curves. The interface charges can have deleterious effect on the threshold voltage of transistors and thereby affect the reliability of transistors. A model predicts the nature of these interface states or traps as shown in Fig. 8 [1, 32]. Fig. 8 (a) shows the condition in which case  $V_G = 0$  V. All states below  $E_F$  would be occupied by electrons and hence, neutral. However, states above E<sub>F</sub> till E<sub>i</sub> would be unoccupied donors and hence exhibit a positive charge; beyond E<sub>i</sub> no states are occupied and hence they are neutral acceptors. Fig. 8 (b) shows the condition where  $V_G > 0V$ , in which case, the  $E_F$  is above  $E_i$  near the interface, which causes the states in the energy region  $(E_F - E_i)$  to be occupied acceptors and hence they exhibit a negative charge at flat-band condition. Finally, in Fig. 8 (c), for V<sub>G</sub> < 0V, unoccupied donors up to E<sub>i</sub> exhibit a positive charge, while unoccupied acceptors above E<sub>i</sub> exhibit no residual charge.

These traps can be quantified by high and low-frequency C-V measurements. They can respond to the AC signal if the frequency of measurement is low and comparable to their time constants and they can capture carriers as well as emit carriers, thereby working as trapping centers. This phenomenon of trapping introduces reliability issues in semiconductors by causing shifts in  $V_{TH}$ . At relatively higher frequencies of measurement, these traps are unable to follow the AC signal due to the swing time constant of the measurement voltage being quicker than that of the traps time constants,  $\tau_{it}$ . However, these traps can follow the slowly varying DC voltage and causes a stretching of the C-V curve in the transition region from

Figure 9. (a) Circuit configuration as measured by the LCR meter. (b) Equivalent circuit configuration as suggested by Nicollian and Brews for the measurement of interface traps. Reprinted from *MOS (Metal Oxide Semiconductor) Physics and Technology* (p. 212), by E.H. Nicollian and J.R. Brews, 1982, Murray Hill, NJ: John Wiley and Sons. Copyright 1982 by Bell Laboratories, Incorporated. [3]

accumulation to inversion, called "C-V stretch-out". The residual charge on these traps contribute a capacitance to the accumulation capacitance ( $C_{acc}$ ) (see Eqn. 10).

These traps can be quantified by making capacitance and conductance measurements using the LCR meter, which assumes the circuit configuration as shown in Fig. 9 (a) and an equivalent circuit configuration for the measurement of traps was proposed by Nicollian and Brews [3], because some correction needs to be applied to the measurement due to the loss of signal by the frequency-dependent trapping. Also, the parasitic series resistance,  $R_S$ , plays a part in signal loss before being picked up by the LCR meter. This causes an anomaly in the measurement of the actual oxide capacitance,  $C_{ox}$  and underestimation of the interface states density. The following equations were proposed by Nicollian and Brews for the correction of  $R_S$  and  $C_{ox}$ :

$$R_S = \frac{Gma}{\left( (Gma^2) + ((\omega)^2 * Cma^2) \right)}$$

(10)

and

$$Cox = Cma * \left(1 + \left(\frac{Gma}{\omega * Cma}\right)^2\right)$$

(11)

where  $C_{m,a}$  and  $G_{m,a}$  respectively are the capacitance and conductance measured in strong accumulation and  $\omega$  is the angular frequency of measurement. The equivalent and corrected parallel conductance,  $G_p$ , can then be related in terms of  $C_{ox}$ ,  $R_S$ ,  $C_m$ ,  $G_m$  and  $\omega$  as shown in the following equation:

$$\frac{G_p}{\omega} = \frac{-\omega^2 C_{ox}^2 (R_s C_m^2 \omega^2 + R_s G_m^2 - G_m)}{\omega^4 C_{ox}^2 C_m^2 R_s^2 + \omega^2 (C_{ox}^2 R_s^2 G_m^2 + C_m^2 + C_{ox}^2 - 2C_{ox}^2 R_s G_m - 2C_m C_{ox}) + G_m^2}$$

(12)

To quantify the frequency-dependent traps, the maximum value of  $\frac{G_p}{\omega}$  is related to the trap density as follows:

$$D_{it} \approx \frac{2.5}{qA} * \left(\frac{G_p}{\omega}\right)_{max} \tag{13}$$

where 'A' is the effective capacitor area and 'q' is the electronic charge. The most famous technique developed by Nicollian and Goetzberger in their paper in 1967 is the "conductance method" [33]. For the conductance method to be able to measure the traps accurately, the measurements need to be taken over a wide frequency range, especially toward the lower frequency range, because the interface traps lose activity on the high frequency range and the conductance method is a direct method of measuring the conductance of the traps. It is one of the most sensitive methods of quantifying traps and can be used to determine trap quantity in the depletion and weak inversion regions along with their time constants and their distribution.

The conductance method is one of the most direct and sensitive methods of detecting trap density at the interface. Using the electrical equivalent circuit shown in Fig. 9 as proposed by Nicollian and Brews for the measurement of interface trap density, the parallel conductance component G<sub>P</sub> can be calculated by the following relation:

$$\frac{\langle G_P \rangle}{\omega} = \frac{\omega C_{ox}^2 G_c}{G_c^2 + \omega^2 (C_{ox} - C_c)^2}$$

(14)

after correcting C<sub>m</sub> and G<sub>m</sub>, taking into account R<sub>S</sub> and C<sub>ox</sub> correction, where,

$$C_c = \frac{(Gm^2 + \omega^2 * Cm^2)Cm}{a^2 + \omega^2 * Cm^2}$$

(15)

and

$$G_c = \frac{(Gm^2 + \omega^2 * Cm^2)a}{a^2 + \omega^2 * Cm^2}$$

(16)

and

$$a = Gm - (Gm^2 + w^2 * Cm^2) * Rs$$

(17)

Then, the normalized  $\frac{\langle G_P \rangle}{\omega}$  is plotted versus  $\omega$  and  $D_{it}$  and  $\tau_{it}$  are extracted by fitting the experimental data to the following models.

For single trap density model:

$$\frac{\langle G_P \rangle}{\omega} = \frac{q D_{it} \omega \tau_{it}}{1 + (\omega \tau_{it})^2} \tag{18}$$

For a continuum of states density model:

$$\frac{\langle G_P \rangle}{\omega} = \frac{q D_{it}}{2\omega \tau_{it}} * \ln(1 + (\omega \tau_{it})^2)$$

(19)

# 3. FABRICATION OF BASELINE MOSCAPS ON SILICON

# 3.1 Device structure

The top-view and cross-section of the baseline MOSCaps developed on n-type Si is shown in Fig. 10. The fabrication comprises the following modules – field dielectric module,

Figure 10. (a) Top-view and (b) cross-section of baseline MOSCaps developed on Si

gate stack module and finally the back contact module. The following sub-sections deal with the fabrication challenges and procedures.

#### 3.2 Field dielectric module