# DOPED METAL OXIDE HIGH-K GATE DIELECTRIC FOR NONVOLATILE MEMORY AND LIGHT EMITTING APPLICATIONS

#### A Dissertation

by

#### SHUMAO ZHANG

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Yue Kuo

Committee Members, Jorge Seminario

Ohannes Eknoyan

Zhengdong Cheng

Head of Department, M. Nazmul Karim

December 2017

Major Subject: Chemical Engineering

Copyright 2017 Shumao Zhang

#### **ABSTRACT**

The zirconium-doped hafnium oxide (ZrHfO) high-*k* thin film has excellent gate dielectric properties, such as a higher crystallization temperature, a lower defect density, and a larger effective *k* value. As a promising high-*k* material, ZrHfO has been utilized for both nonvolatile memory (NVM) and light emitting applications. Replacing the polycrystalline Si floating gate, the discrete nanocrystals embedded ZrHfO gate dielectric can achieve promising NVM performance. On the other hand, warm white light can be emitted from the thermal excitation of nano-resistors form from the dielectric breakdown of the ZrHfO Metal-Oxide-Semiconductor (MOS) capacitor. This novel solid state incandescent light emitting device (SSI-LED) unveils a new concept for the lighting device evolution.

Nanocrystalline cadmium sulfide (nc-CdS) embedded ZrHfO high-k NVMs have been fabricated to reduce the frequency dispersion problem caused by defects at the nanocrystal/dielectric interface. The nc-CdS embedded device can retain about 53% of originally trapped holes for 10 years and exhibit outstanding memory function at low operation voltage. The study on the nc-CdSe embedded ZrHfO NVMs shows that the high temperature enhances the hole trapping but decreases the electron trapping. Based on the different temperature dependences, the stored electrons release faster than stored holes. The raised temperature accelerates the dielectric breakdown process by increasing defect densities and defect effective conduction radii.

The post deposition annealing (PDA) atmosphere is critical to the electrical and light emission characteristics of ZrHfO SSI-LEDs. It affects the dielectric breakdown, light emission intensity and efficiency by changing compositions of the high-k stack and the nano-resistor. The electrical properties, i.e., effective resistances and Schottky barrier heights of nano-resistors have been estimated. The nano-resistor behaves neither like a conductor nor like a semiconductor. Moreover, the barrier height inhomogeneity is observed due to the random and complicated nano-resistor formation. The embedding method and the heavily doped p-Si substrate have been employed to enhance the light emission from ZrHfO SSI-LEDs.

Lastly, extensive applications of this novel nano-resistor device for on-chip optical interconnects and as diode-like anti-fuses have been discussed.

# DEDICATION

Dedicated to my dearest father Shirong Zhang, mother Huibi Ji, brother Yumao Zhang, and my beloved wife, Yan Yang.

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to my Ph.D. advisor, Dr. Yue Kuo, for his tremendous support and guidance throughout my research at the Texas A&M University. His continuous intense training, guidance, and inspiration educated me into a professional and researcher on semiconductor processes and devices. His enthusiasm and devotion on academic work always invigorated me to engage in the chase of science. It is my pleasure and fortunate having his knowledgeable advice and carefully aimed direction in my research life.

I would like to express my sincere appreciation to Dr. Jorge Seminario, Dr. Ohannes Eknoyan, and Dr. Zhengdong Cheng for serving as my committee members and offering many profound comments and suggestions on my research. Their precious time is invaluable to me.

My heartfelt appreciation also goes to my previous colleagues in Thin Film Nano & Microelectronics Research Laboratory, Dr. Chi-Chou Lin, Dr. Kibum Kim, Mr. I-Syuan Lee, Mr. Kai Henry, Dr. Geng-Wei Chang, Dr. Chur-Shyang Fuh, Dr. Dong Li, Dr. Te-Chih Chen, Mr. Youzhi Lin, and Yusaku Magari, and current colleagues, Dr. Jingxin Jiang and Baizhen Gao, for the support on my research work and the friendship beyond the academic life. Your suggestion and assistance inspired enormously on my Ph.D. study. All of you helped make this dissertation possible. Special thanks to Chi-Chou for instructing many experiments, helping me fix machine problems, and much more.

I also want to thank Dr. Xiaoning Zhang of Xi'an Jiaotong University for providing valuable instruments on the pulse voltage generator and the SSI-LED matrix driving circuit. Thank Mr. Randy Marek, retired manager of the Technical Laboratory in the department of Chemical Engineering. He was all the time professional and supportive in solving our mechanical problems on everything.

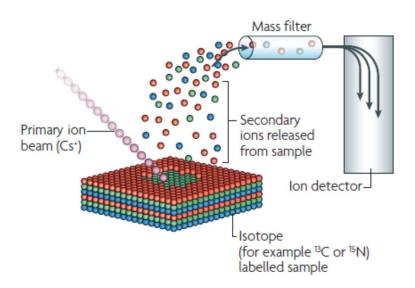

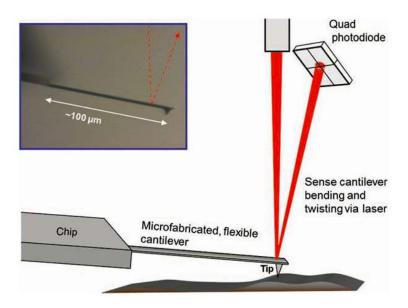

I am also very grateful to Dr. Andreas Holzenburg, Dr. Hansoo Kim, Dr. Wenrui Zhang, Dr. Stanislav Verkhoturov, and Dr. Wilson Serem, for their helpful instruction, assistance, and consultation on the TEM, SEM, SIMS, and AFM analyses, which are very critical to my research.

#### CONTRIBUTORS AND FUNDING SOURCES

#### **Contributors**

This work was supervised by a dissertation committee consisting of Professor Yue Kuo (advisor), Professor Jorge Seminario, and Professor Zhengdong Cheng of the Artie McFerrin Department of Chemical Engineering, and Professor Ohannes Eknoyan of the Department of Electrical and Computer Engineering.

All work for the dissertation was completed independently by the student.

# **Funding Sources**

This work was made possible in part by National Science Foundation under Award Number 0968862. Its contents are solely the responsibility of the authors and do not necessarily represent the official views of the Division of Civil, Mechanical, and Manufacturing Innovation (CMMI).

# TABLE OF CONTENTS

|                                                                                                                                                                                 | Page           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ABSTRACT                                                                                                                                                                        | ii             |

| DEDICATION                                                                                                                                                                      | iv             |

| ACKNOWLEDGEMENTS                                                                                                                                                                | v              |

| CONTRIBUTORS AND FUNDING SOURCES                                                                                                                                                | vii            |

| TABLE OF CONTENTS                                                                                                                                                               | viii           |

| LIST OF FIGURES                                                                                                                                                                 | xi             |

| LIST OF TABLES                                                                                                                                                                  | xviii          |

| CHAPTER I INTRODUCTION                                                                                                                                                          | 1              |

| 1.1 High-K Gate Dielectric                                                                                                                                                      | 10<br>20       |

| CHAPTER II EXPERIMENTAL                                                                                                                                                         | 31             |

| 2.1 Introduction 2.2 Fabrication Process Flow 2.3 Thin Film Deposition and Annealing 2.4 Material Characterization 2.5 Electrical Characterization 2.6 Optical Characterization | 31<br>35<br>41 |

| CHAPTER III CADMIUM SULFIDE EMBEDDED ZIRCONIUM-DOPED HAFNIUM OXIDE HIGH-K NONVOLATILE MEMORIES                                                                                  | 57             |

| 3.1 Introduction and Motivation                                                                                                                                                 | 57<br>OS       |

| CHAPTER IV TEMPERATURE EFFECTS ON NANOCRYSTALLINE                                 |     |

|-----------------------------------------------------------------------------------|-----|

| CADMIUM SELENIDE EMBEDDED ZIRCONIUM-DOPED HAFNIUM OXIDE                           | ,   |

| HIGH-K NONVOLATILE MEMORIES                                                       | 77  |

|                                                                                   |     |

| 4.1 Introduction and Motivation                                                   |     |

| 4.2 Experimental                                                                  |     |

| 4.3 Temperature Effects on Charge Trapping and Transfer Mechanisms                | /9  |

| 4.4 Temperature Effects on Dielectric Breakdown and Charge Retention Capabilities | 02  |

| 4.5 Summary                                                                       |     |

| 4.5 Summary                                                                       | 107 |

| CHAPTER V POST DEPOSITION ANNEALING ATMOSPHERE EFFECTS ON                         | [   |

| PERFORMANCE OF SOLID STATE INCANDESCENT LIGHT EMITTING                            |     |

| DEVICES                                                                           | 110 |

|                                                                                   |     |

| 5.1 Introduction and Motivation                                                   |     |

| 5.2 Experimental                                                                  |     |

| 5.3 PDA Atmosphere Effects on Electrical Properties                               |     |

| 5.4 PDA Atmosphere Effects on Light Emission Characteristics                      |     |

| 5.5 Summary                                                                       | 127 |

| CHAPTER VI ELECTRICAL PROPERTIES OF MANO RESISTORS IN                             |     |

| CHAPTER VI ELECTRICAL PROPERTIES OF NANO-RESISTORS IN                             | 120 |

| ZIRCONIUM-DOPED HAFNIUM OXIDE HIGH-K THIN FILMS                                   | 129 |

| 6.1 Introduction and Motivation                                                   | 129 |

| 6.2 Experimental                                                                  |     |

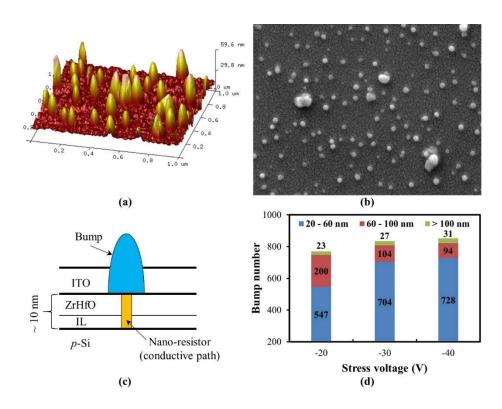

| 6.3 Bump Formation above the Nano-Resistor During Stress                          |     |

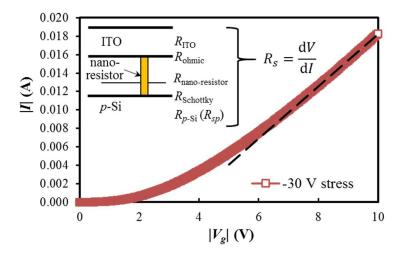

| 6.4 Estimation of Effective Resistance and Schottky Barrier Height                |     |

| 6.5 Stress Effects on Electrical Properties of Nano-Resistors                     |     |

| 6.6 Summary                                                                       |     |

| •                                                                                 |     |

| CHAPTER VII LIGHT EMISSION ENHANCEMENT ON SOLID STATE                             |     |

| INCANDESCENT LIGHT EMITTING DEVICES                                               | 141 |

|                                                                                   |     |

| 7.1 Introduction and Motivation                                                   |     |

| 7.2 WO <sub>x</sub> Embedded Zr-Doped HfO <sub>2</sub> High-K SSI-LEDs            |     |

| 7.3 SSI-LEDs Fabricated on Heavily-Doped <i>p</i> -Si Substrates                  |     |

| 7.4 Summary                                                                       | 133 |

| CHAPTER VIII EXTENSIVE APPLICATIONS OF NANO-RESISTOR                              |     |

| DEVICESDEVICENTIONS OF NANO-RESISTOR                                              | 157 |

|                                                                                   | 1 / |

| 8.1 Introduction and Motivation                                                   | 157 |

| 8.2 Light Filtration on SSI-LEDs                                                  |     |

| 8.3 Diode-Like Anti-Fuse Application                                              |     |

| 8.4 Summary                        | 174 |

|------------------------------------|-----|

| CHAPTER IX SUMMARY AND CONCLUSIONS | 176 |

| REFERENCES                         | 182 |

| APPENDIX A                         | 198 |

|                                    |     |

# LIST OF FIGURES

| Page                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1. Schematic structure of a <i>n</i> -channel MOSFET                                                                                                                                                           |

| Figure 2. Power consumption and gate leakage current density for a chip which has a 15 Å thick SiO <sub>2</sub> gate dielectric or an alternate dielectric exhibiting the same capacitance.                           |

| Figure 3. Static dielectric constant versus band gap for candidate high- <i>k</i> gate oxides5                                                                                                                        |

| Figure 4. $D_{it}$ of La <sub>2</sub> O <sub>3</sub> and HfO <sub>2</sub> thin films annealed at 500 °C                                                                                                               |

| Figure 5. Conduction band and valence band offsets of various high-k oxides on Si8                                                                                                                                    |

| Figure 6. Temperature-composition phase of HfO <sub>2</sub> -ZrO <sub>2</sub>                                                                                                                                         |

| Figure 7. EOT and gate leakage current of ZrHfO films after the PDA under different O <sub>2</sub> /N <sub>2</sub> ratios                                                                                             |

| Figure 8. Schematic cross-sectional structure of a flash memory core cell                                                                                                                                             |

| Figure 9. Current/voltage characteristics as a function of the threshold voltage of a flash cell                                                                                                                      |

| Figure 10. Energy band diagram for a typical FG structure                                                                                                                                                             |

| Figure 11. Schematic diagram illustrates how a defect chain affects the charge loss in conventional FG structure and nanocrystal embedded FG structure14                                                              |

| Figure 12. TEM image and schematic drawing of nanocrystal formation by self-assembly with increased duration of thermal treatment from (a) to (c); (d) Major driving forces in nanocrystal formation by self-assembly |

| Figure 13. Schematic drawing of nanocrystal formation by precipitation17                                                                                                                                              |

| Figure 14. Illustrations of Coulomb blockade effect                                                                                                                                                                   |

| Figure 15. Illustrations of quantum confinement effect                                                                                                                                                                |

| Figure 16. Energy band diagrams of a $p$ - $n$ <sup>+</sup> junction (a) without bias and (b) with applied bias $V$                                                                                                   |

| Figure 17. Schematic band structures of (a) GaAs and (b) GaP23                                                                                                                                                        |

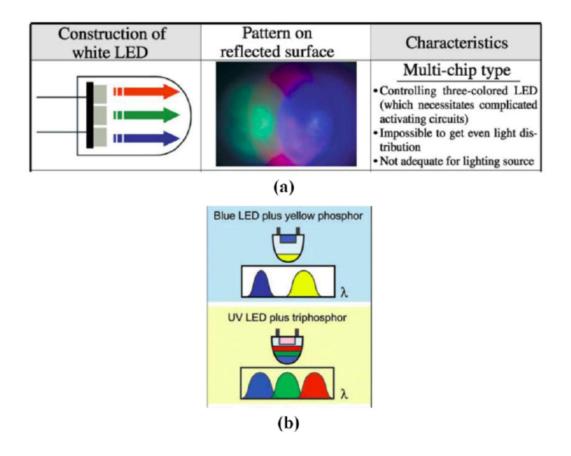

| Figure 18. Construction and characteristics of white LED: (a) through colored RGB LEDs and (b) through blue/UV LED in combination with phosphors                                                   | 25 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 19. Fabrication process flow of a nanocrystal embedded high- <i>k</i> gate dielectric MOS capacitor, its corresponding control MOS capacitor, or a SSI-LED                                  |    |

| Figure 20. Illustration of the pattern transferring process.                                                                                                                                       | 35 |

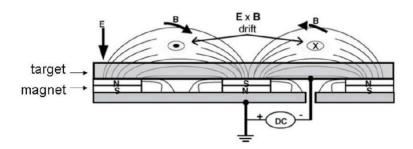

| Figure 21. The illustration of the RF magnetron sputtering system                                                                                                                                  | 36 |

| Figure 22. Schematic configuration of magnetron enhancement.                                                                                                                                       | 38 |

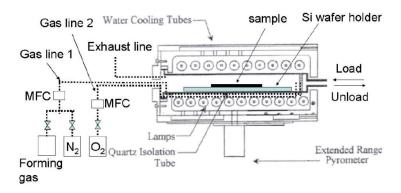

| Figure 23. Schematic diagram of RTA system.                                                                                                                                                        | 40 |

| Figure 24. Schematic illustration of a SIMS.                                                                                                                                                       | 43 |

| Figure 25. Schematic illustration of an AFM.                                                                                                                                                       | 44 |

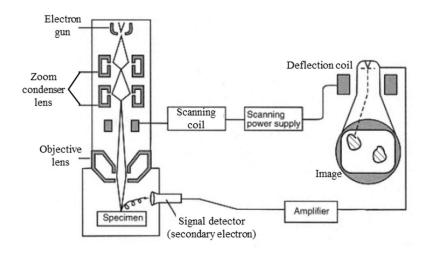

| Figure 26. Schematic diagram of SEM.                                                                                                                                                               | 46 |

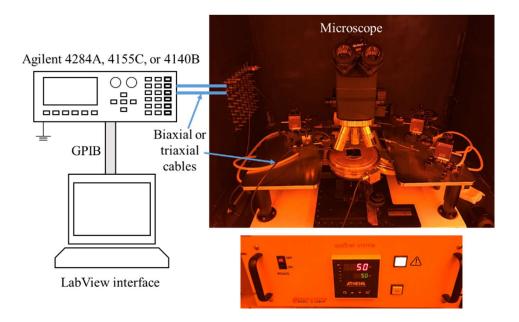

| Figure 27. Schematic diagram of electrical characterization system setup                                                                                                                           | 48 |

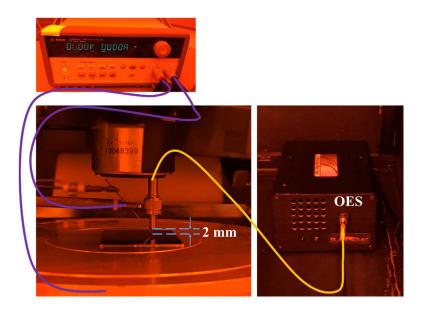

| Figure 28. Schematic diagram of optical characterization system setup.                                                                                                                             | 52 |

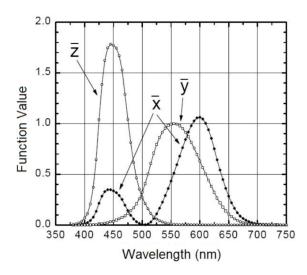

| Figure 29. The 1931 CIE color-matching functions.                                                                                                                                                  | 54 |

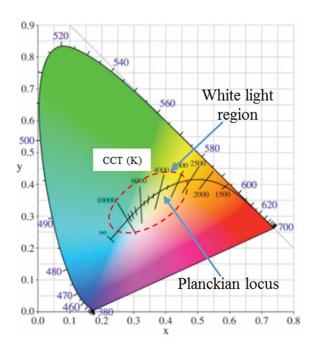

| Figure 30. The 1931 CIE chart with the Planckian locus.                                                                                                                                            | 54 |

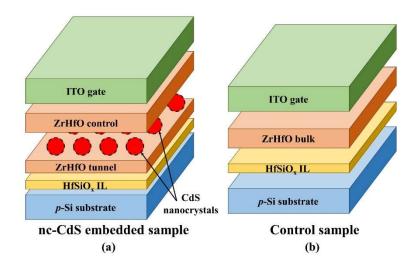

| Figure 31. Drawing of the device structures of the (a) nc-CdS embedded and (b) control samples.                                                                                                    | 59 |

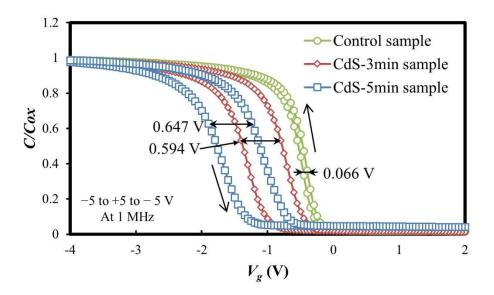

| Figure 32. $C$ - $V$ hysteresis curves of the control and nc-CdS embedded samples. $V_g$ swept from $-5$ to $+5$ to $-5$ V at 1 MHz.                                                               | 61 |

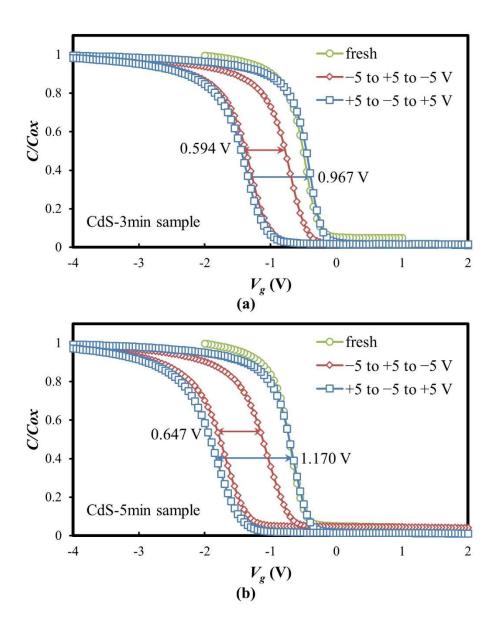

| Figure 33. $C$ - $V$ hysteresis curves of the nc-CdS embedded samples. $V_g$ swept from $-5$ to $+5$ to $-5$ V or $+5$ to $-5$ V at 1 MHz. Fresh: $-2$ to $+1$ V at 1 MHz                          |    |

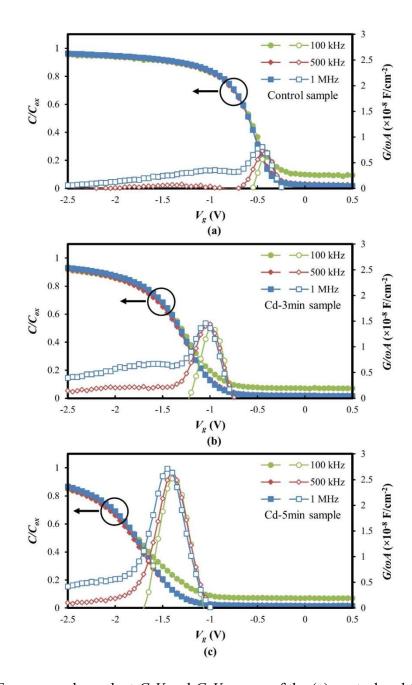

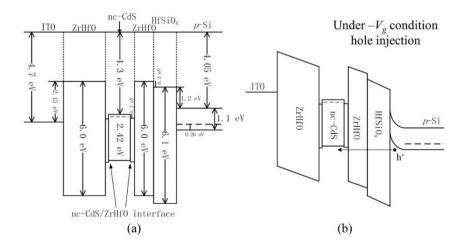

| Figure 34. Frequency-dependent $C$ - $V$ and $G$ - $V$ curves of the (a) control and (b)(c) nc-CdS embedded samples. $V_g$ swept from $-5$ to $+5$ to $-5$ V at $100$ kHz, $500$ kHz, and $1$ MHz. |    |

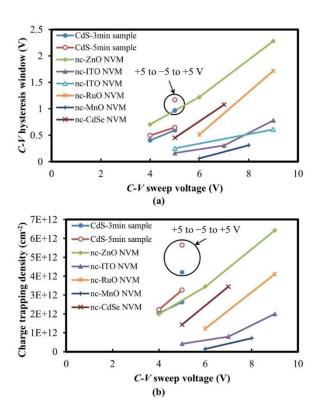

| Figure 35. Energy band diagrams of the nc-CdS embedded sample under the (a) unbiased and (b) negative $V_g$ stress conditions                                                                      | 67 |

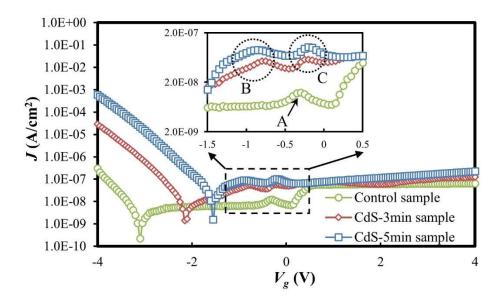

| Figure 36. Comparisons of (a) memory windows and (b) charge trapping density of the nc-CdS embedded samples and various nanocrystal embedded NVMs, i.e., ZnO, <sup>106</sup> nc-ITO, <sup>107,108</sup> nc-RuO, <sup>109,110</sup> nc-MnO, <sup>111</sup> and nc-CdSe, <sup>112</sup> embedded NVMs       | 7 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 37. $J$ - $V$ curves of the control and nc-CdS embedded samples. $V_g$ swept from $-4$ to $+4$ V. The inset is the magnified $J$ - $V$ curves in the range of $V_g = -1.5$ to $+0.5$ V.                                                                                                            | 9 |

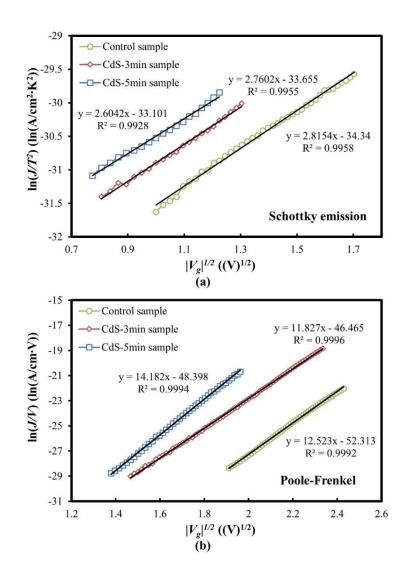

| Figure 38. (a) Schottky emission and (b) Poole-Frenkel fitting of <i>J-V</i> curves of the nc-CdS embedded samples                                                                                                                                                                                        | 1 |

| Figure 39. (a) $J_{ramp}$ and (b) $J_{relax}$ vs. $V_{ramp}$ curves of the control and nc-CdS embedded samples.                                                                                                                                                                                           | 3 |

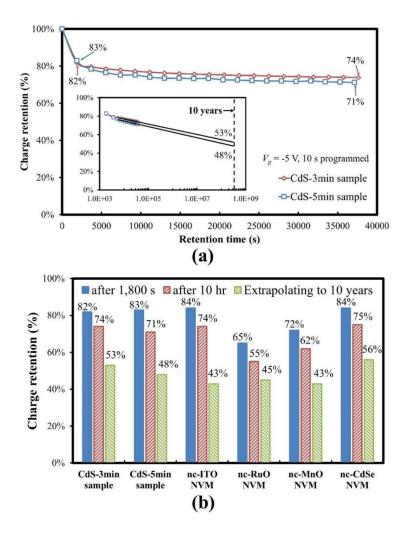

| Figure 40. (a) Hole retention characteristics of the nc-CdS embedded samples. Inset: 10-year extrapolation. (b) Comparisons of hole retention capabilities of the nc-CdS embedded samples and various nanocrystal embedded NVMs, i.e., nc-ITO, 107 nc-RuO, 109 nc-MnO, 111 and nc-CdSe, 112 embedded NVMs | 5 |

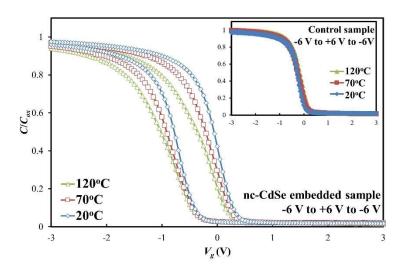

| Figure 41. $C$ - $V$ hysteresis curves of nc-CdSe embedded sample at 1 MHz at 20 °C, 70 °C, and 120 °C, respectively. $V_g$ swept from $-6$ V to $+6$ V to $-6$ V. Inset: control sample                                                                                                                  | 0 |

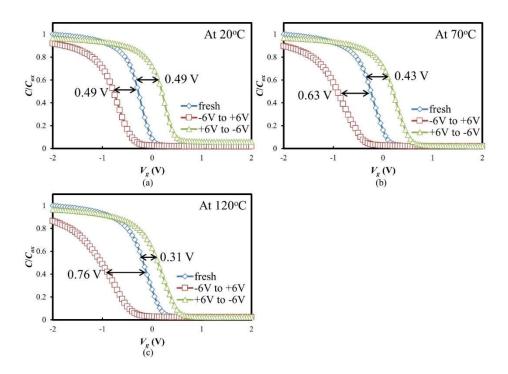

| Figure 42. $C$ - $V$ curves of the nc-CdSe embedded sample measured from $V_g$ = $-6$ V to $+6$ V and from $+6$ V to $-6$ V at 1MHz at (a) 20 °C, (b) 70 °C, and (c) 120 °C, respectively. Fresh: fresh sample measured from $V_g$ = $-2$ V to $+1$ V8                                                    | 2 |

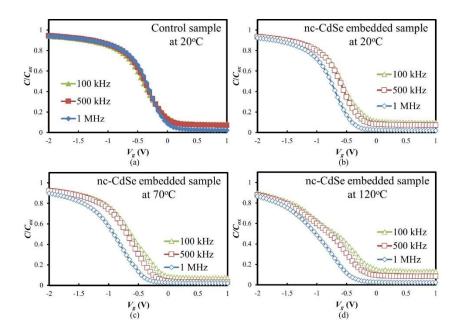

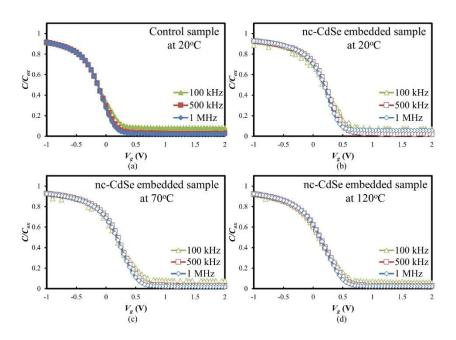

| Figure 43. $C$ - $V$ curves of (a) control and (b)(c)(d) nc-CdSe embedded samples at 20 °C, 70 °C, and 120 °C, measured from $V_g$ = $-6$ V to $+6$ V at 100 kHz, 500 kHz, and 1 MHz                                                                                                                      | 4 |

| Figure 44. $C$ - $V$ curves of (a) control and (b)(c)(d) nc-CdSe embedded samples at 20 °C, 70 °C, and 120 °C, measured from $V_g$ = +6 V to -6 V at 100 kHz, 500 kHz, and 1 MHz                                                                                                                          | 5 |

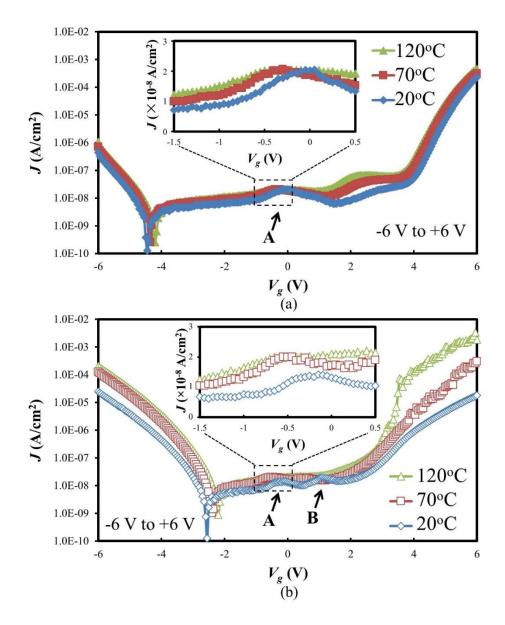

| Figure 45. <i>J-V</i> curves of (a) control and (b) nc-CdSe embedded samples. $V_g$ swept from $-6$ V to $+6$ V at 20 °C, 70 °C, and 120 °C, respectively. Inset: magnified curves in $V_g = -1.5$ V to $+0.5$ V.                                                                                         | 7 |

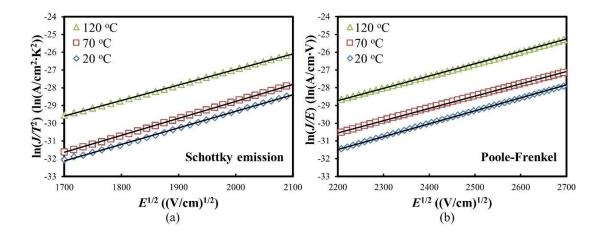

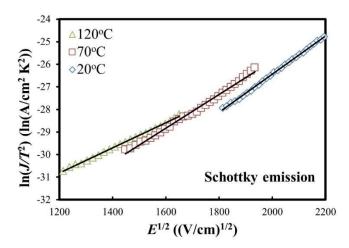

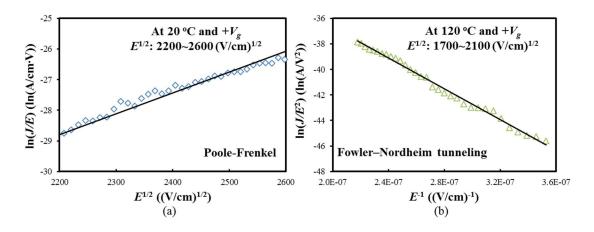

| Figure 46. Fitting of (a) Schottky emission and (b) Poole-Frenkel mechanisms in negative $V_g$ region at 20 °C, 70 °C, and 120 °C, respectively                                                                                                                                                           | 9 |

| Figure 47. Fitting of Schottky emission in positive $V_g$ region at 20 °C, 70 °C, and 120 °C, respectively.                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 48. Fitting of (a) Poole-Frenkel mechanism at 20 °C and (b) Fowler-Nordheim tunneling at 120 °C in negative $V_g$ region91                                                                                                                                                                                                 |

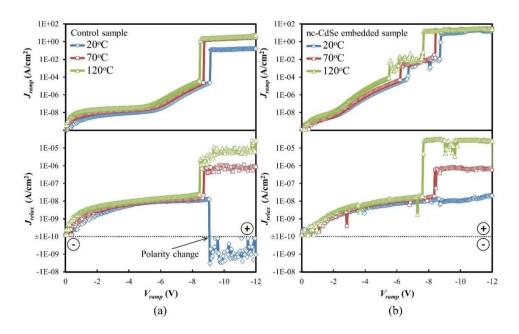

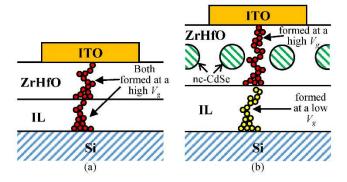

| Figure 49. $J_{ramp}$ - $V_{ramp}$ and $J_{relax}$ - $V_{ramp}$ curves of the (a) control and (b) nc-CdSe embedded samples at 20 °C, 70 °C, and 120 °C, respectively. $V_g$ swept from 0 to $-12$ V. Polarity of $J_{relax}$ is positive above the dash line and negative below the dash line.                                    |

| Figure 50. Cross-sectional views of structures of the (a) control and (b) nc-CdSe embedded samples with breakdown paths. IL: the HfSiO <sub>x</sub> interface layer95                                                                                                                                                             |

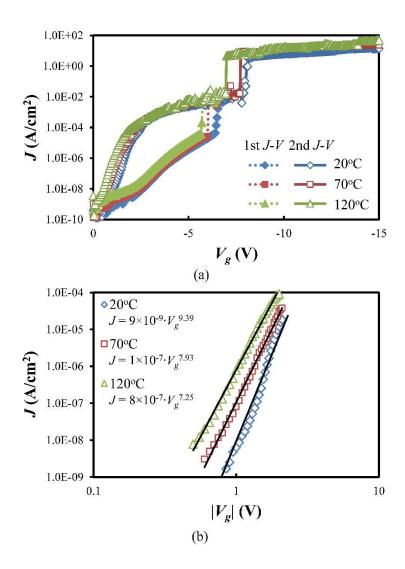

| Figure 51. (a) $J$ - $V$ curves of the nc-CdSe embedded sample at 20 °C, 70 °C, and 120 °C, respectively. $1^{\rm st}$ curves were measured from $V_g = 0$ V to immediately after the first-step breakdown. $2^{\rm nd}$ curves were measured from $V_g = 0$ V to $-15$ V. (b) Power law fitting of $2^{\rm nd}$ $J$ - $V$ curves |

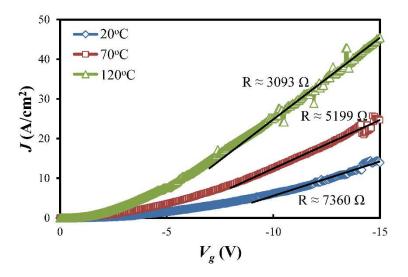

| Figure 52. <i>J-V</i> curves of the nc-CdSe embedded sample at 20 °C, 70 °C, and 120 °C, respectively. All samples were completely broken down previously. Ohm's law fitting of linear region of the curve.                                                                                                                       |

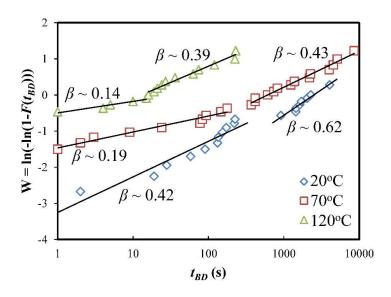

| Figure 53. TDDB Weibull distribution of the nc-CdSe embedded sample stressed at $V_g = -7$ V 20 °C, 70 °C, and 120 °C, respectively. $\beta$ values are shown next to individual curves                                                                                                                                           |

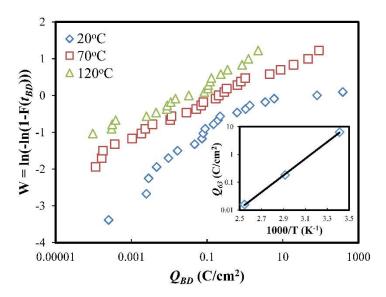

| Figure 54. Weibull distribution of $Q_{BD}$ 's of the nc-CdSe embedded sample stressed at $V_g = -7$ V and 20 °C, 70 °C, and 120 °C, respectively. Inset: Arrhenius plot of $Q_{BD}$ at 63.2% failure fraction ( $Q_{63}$ )                                                                                                       |

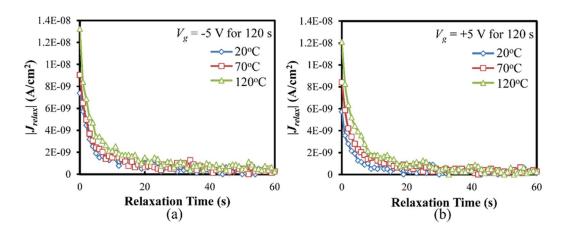

| Figure 55. $J_{relax}$ - $t$ curves of nc-CdSe embedded sample after removal of stress voltage of $V_g$ = (a) -5V and (b) +5 V for 120s at 20 °C, 70 °C, and 120 °C, respectively                                                                                                                                                 |

| Figure 56. Log-log plot of $J_{relax}$ - $t$ curves of the nc-CdSe embedded sample after removal of stress voltage with Curie-von Schweidler fitting. Stress at $V_g$ = (a) -5 V and (b) +5 V for 120 s at 20 °C, 70 °C, and 120 °C, respectively104                                                                              |

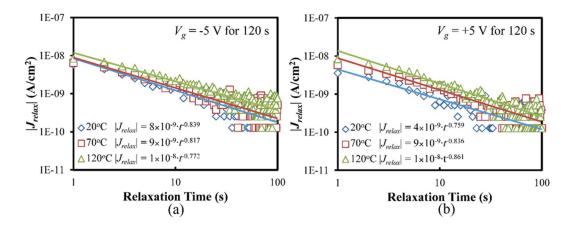

| Figure 57. Charge retention characteristics of the nc-CdSe embedded sample after stress at $V_g = (a) - 6$ V and $(b) + 6$ V. Stress time: 20 s. Temperature: 20 °C, 70 °C and 120 °C respectively. Inset: 10-year extrapolation curve.                                                                                           |

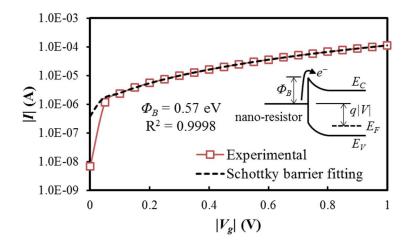

| Figure 71. (a) Effective resistances of nano-resistors connected in parallel of samples stressed at $V_g = -20 \text{ V}$ , $-30 \text{ V}$ , or $-40 \text{ V}$ , separately, for 20 min at room temperature. (b) Temperature dependence of effective resistances of nano-resistors. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

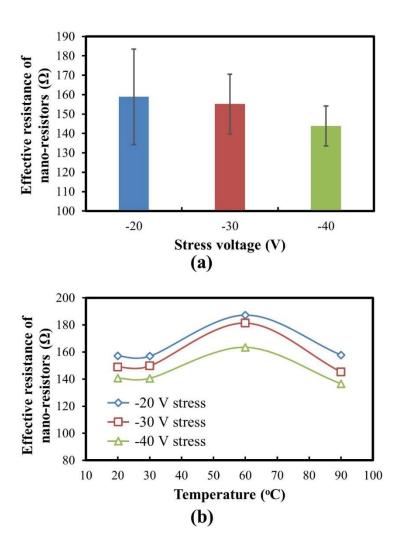

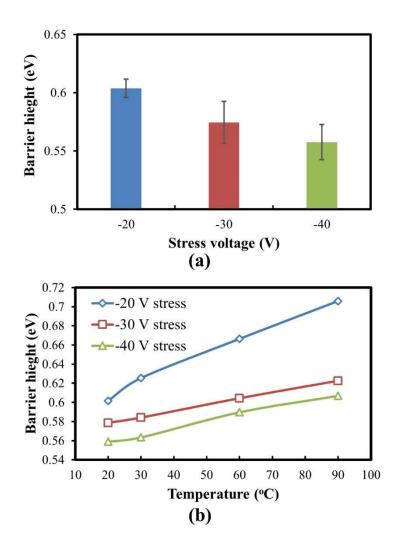

| Figure 72. (a) Schottky barrier heights of nano-resistors of samples stressed at $V_g = -20 \text{ V}$ , $-30 \text{ V}$ , or $-40 \text{ V}$ , separately, for 20 min at room temperature. (b) Temperature dependence of Schottky barrier heights of nano-resistors138               |

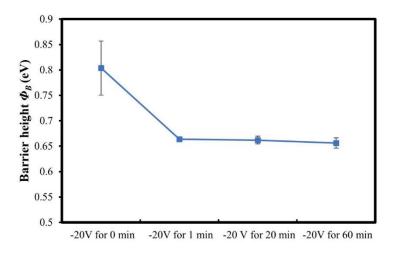

| Figure 73. Barrier heights of nano-resistors after being stressed at $V_g = -20 \text{ V}$ for different periods of time.                                                                                                                                                             |

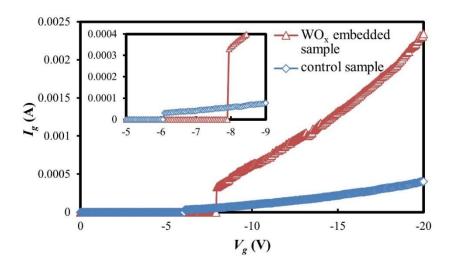

| Figure 74. $I$ - $V$ curves of the control and WO <sub>x</sub> embedded samples with $V_g$ from 0 to $-20 \text{ V}$ .                                                                                                                                                                |

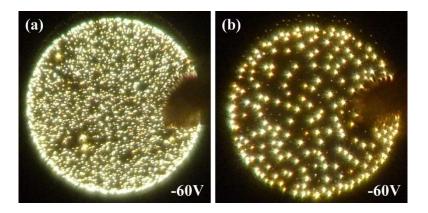

| Figure 75. High-magnification photos of the (a) control and (b) WO <sub>x</sub> embedded samples stressed at $V_g = -60 \text{ V}$                                                                                                                                                    |

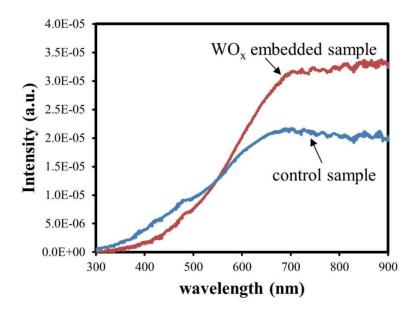

| Figure 76. Emission spectra of the control and $WO_x$ embedded samples at $V_g = -60$ V                                                                                                                                                                                               |

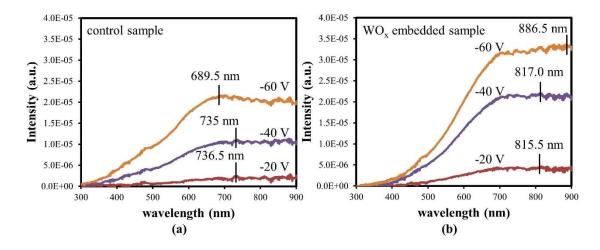

| Figure 77. Emission spectra of the (a) control and (b) WO <sub>x</sub> embedded samples stressed at $V_g = -20$ , $-40$ , and $-60$ V                                                                                                                                                 |

| Figure 78. $C$ - $V$ hysteresis of the $p$ and $p^+$ substrate samples with $V_g$ swept from $-2$ to $+1$ to $-2$ V at 1 MHz                                                                                                                                                          |

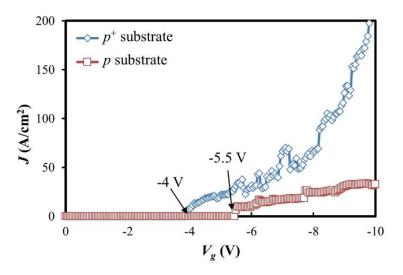

| Figure 79. $I$ - $V$ curves of the $p$ and $p^+$ substrate samples with $V_g$ swept from 0 V to $-10$ V                                                                                                                                                                               |

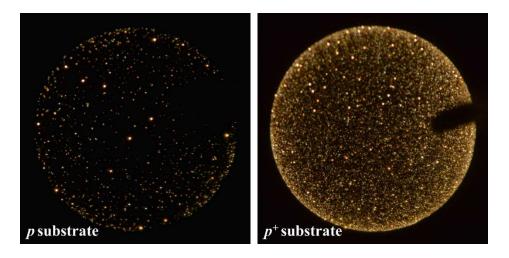

| Figure 80. High-magnification photos of the $p$ and $p^+$ substrate SSI-LEDs at $V_g = -25$ V                                                                                                                                                                                         |

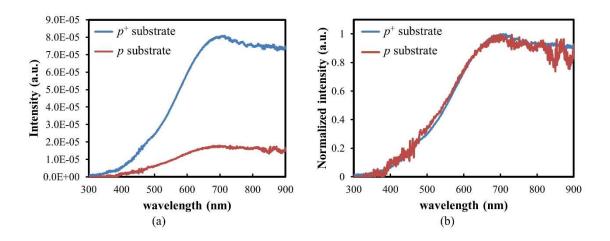

| Figure 81. (a) Light emission spectra and (b) normalized spectra of the $p$ and $p^+$ substrate SSI-LEDs at $V_g = -25$ V. (b) Normalized by the maximum intensity at the peak.                                                                                                       |

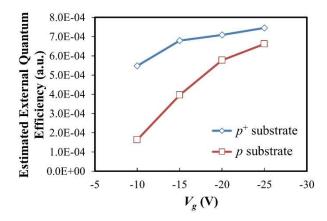

| Figure 82. Estimated $EQE$ 's of the $p$ and $p^+$ substrate SSI-LEDs at $V_g = -10$ to $-25$ V                                                                                                                                                                                       |

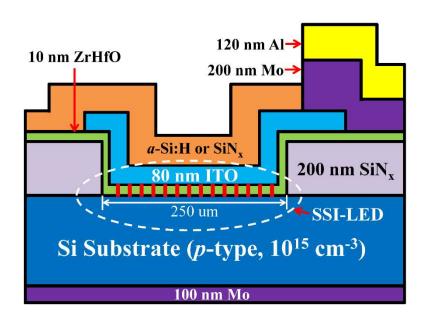

| Figure 83. Cross-sectional view of a ZrHfO SSI-LED with a coated thin film of <i>a</i> -Si:H or SiN <sub>x</sub>                                                                                                                                                                      |

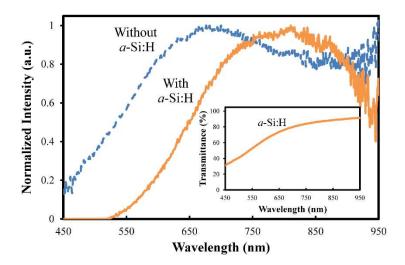

| Figure 84. Normalized light emission spectra of SSI-LEDs with and without a coated $a$ -Si:H thin film. Stressed at $V_g = -30$ V. Inset: Light spectral transmittances of the coated $a$ -Si:H film.                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

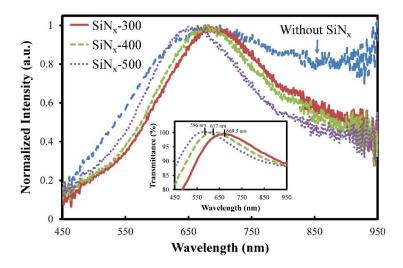

| Figure 85. Normalized light emission spectra of SSI-LEDs with and without being coated with three types of $SiN_x$ thin films. Stressed at $V_g = -30$ V. Inset: Light spectral transmittances of the coated $SiN_x$ films                                                                                                                  |

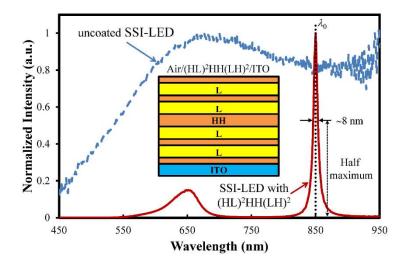

| Figure 86. Calculated light emission spectra of SSI-LEDs with and without being coated with a $(HL)^2HH(LH)^2$ Fabry-Perot filter. Normalized by the maximum intensities. $\lambda_0 = 850$ nm. H: 52.0 nm thick <i>a</i> -Si:H. L: 105.9 nm thick SiN <sub>x</sub> . Inset: cross-sectional view of the $(HL)^2HH(LH)^2$ filter on SSI-LED |

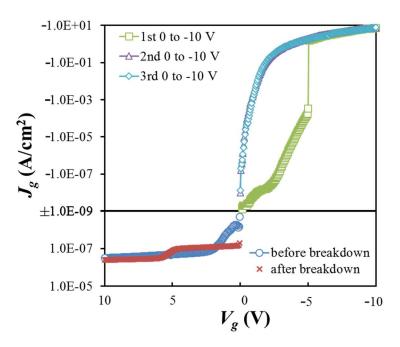

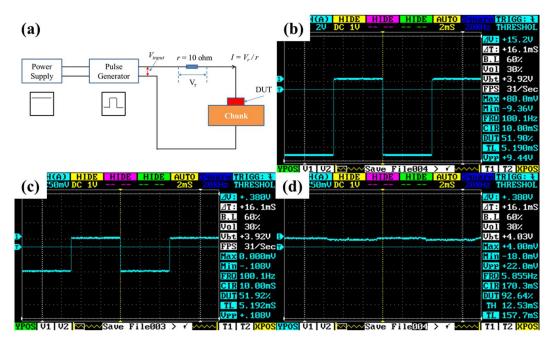

| Figure 87. Diode-like <i>I-V</i> curve of the 12-min-deposited ZrHfO MOS capacitor with the anti-fuse function                                                                                                                                                                                                                              |

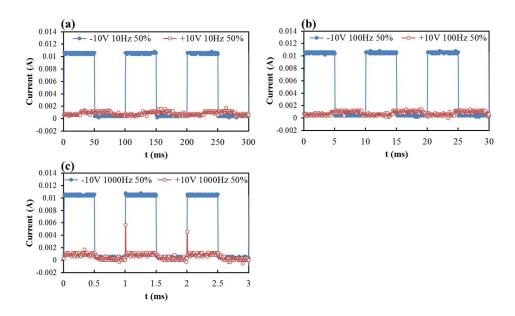

| Figure 88. (a) The circuit used to read the current through the DUT driven by a pulsed voltage. (b) The pulsed voltage input with $-10$ or $+10$ V of $100$ Hz and $50$ % duty cycle. The $V_r$ reading under the (c) $-10$ V and (d) $+10$ V pulsed voltage input.                                                                         |

| Figure 89. The current through the DUT driven by the pulsed voltage input with -10 or +10 V of 10-1000 Hz and 50 % duty cycle                                                                                                                                                                                                               |

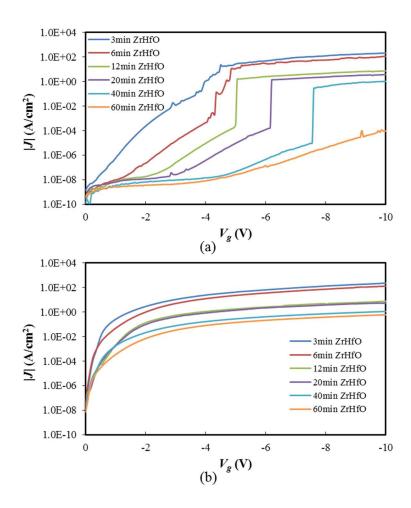

| Figure 90. <i>I-V</i> curves of the ZrHfO MOS capacitors with different dielectric thickness (a) before and (b) breakdown from 0 to -10 V                                                                                                                                                                                                   |

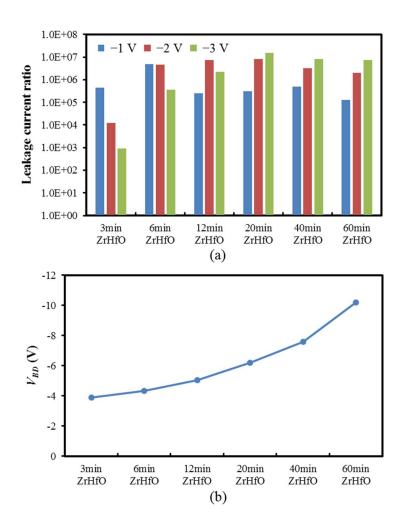

| Figure 91. Dielectric thickness effects on the (a) ratio of pre- to post-breakdown leakage current and (b) the breakdown voltage of ZrHfO anti-fuse devices172                                                                                                                                                                              |

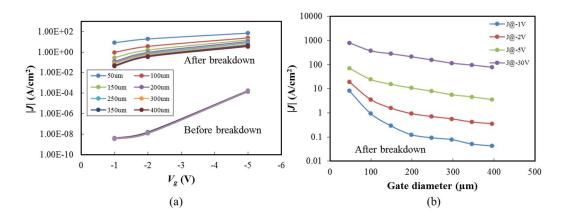

| Figure 92. Leakage currents of the 12-min-deposited ZrHfO anti-fuse devices with different sizes before and after breakdown                                                                                                                                                                                                                 |

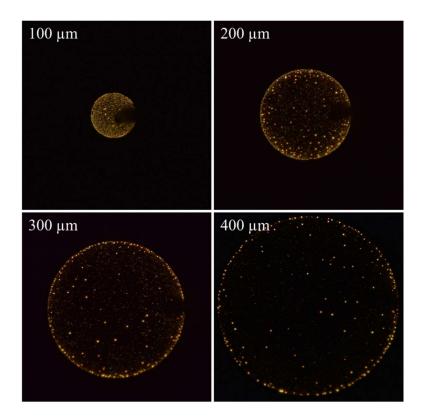

| Figure 93. Light emission photos of the 12-min-deposited ZrHfO SSI-LEDs with different sizes. Stress at $V_g = -30 \text{ V}$ .                                                                                                                                                                                                             |

# LIST OF TABLES

| Pa                                                                                                                                                      | age |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1. Parameters calculated from <i>C-V</i> hysteresis curves.                                                                                       | .61 |

| Table 2. Parameters calculated from <i>C-V</i> hysteresis curves of the N <sub>2</sub> and O <sub>2</sub> PDA samples                                   | .13 |

| Table 3. CIE characteristics of the N <sub>2</sub> and O <sub>2</sub> PDA SSI-LEDs1                                                                     | 25  |

| Table 4. CIE color coordinates, CCT, and CRI values for the control and WO <sub>x</sub> embedded samples at $V_g = -20$ , $-40$ , and $-60$ V           | 48  |

| Table 5. CIE color coordinates, CCT, and CRI values of the $p$ and $p^+$ substrate SSI-LEDs at $V_g = -25$ V.                                           | .54 |

| Table 6. Parameters calculated from <i>C-V</i> curves of the ZrHfO MOS capacitors with different ZrHfO deposition times from -2 to +1 to -2 V at 1 MHz1 | 70  |

#### CHAPTER I

#### INTRODUCTION

# 1.1 High-K Gate Dielectric

# 1.1.1 General Background

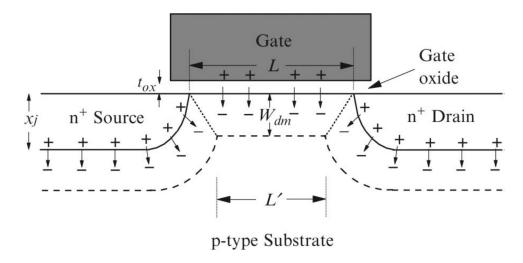

The rapid growth of the complementary metal oxide semiconductor (CMOS) integrated circuit (IC) technology keeps pushing the shrinking of silicon-based MOSFETs. To achieve great performance with such a high transistor density on a chip, the channel length (L), i.e., the distance between the source and drain as shown in Figure 1, has been reduced from micrometer scale to nanometer scale. The drive current  $(I_D)$  of a n-channel MOSFET can be expressed as the following equation:

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_G - V_T - \frac{V_D}{2} \right) V_D, \tag{1}$$

where W is the width of the channel,  $\mu_n$  is the effective mobility of electrons in the channel,  $C_{ox}$  is the gate capacitance associated with the gate dielectric when the underlying channel is in the accumulated state,  $V_D$  and  $V_G$  are the applied channel and gate voltage when the source is grounded, respectively, and  $V_T$  is the threshold voltage. According to the above equation, we can clearly figure out that the decrease of L can enhance the drive current and switch speed.

Figure 1. Schematic structure of a *n*-channel MOSFET. (Reprinted with permission from Ref. 2. Copyright 2012 IEEE.)

Nonetheless, when L decreases, the gate capacitance  $C_{ox}$  decreases following the parallel capacitance equation:<sup>1</sup>

$$C_{ox} = \frac{k\varepsilon_0 A}{t_{ox}}$$

[2]

where  $\varepsilon_0$  is the vacuum permittivity (8.854×10<sup>-12</sup> F/m), k is the dielectric constant or the relative permittivity of the gate dielectric (a ratio of a material dielectric permittivity to  $\varepsilon_0$ ),  $t_{ox}$  is the thickness of the gate dielectric oxide, and the gate area (A) is proportional to the channel length L. Since A decreases with the decrease of L,  $C_{ox}$  will also decrease, and according to Equation 1, it compensates for the improvement of the drive current. Based on Equation 2, there are two effective methods to maintain a larger  $C_{ox}$  with a smaller L to enhance the drive current: using a smaller  $t_{ox}$  or a larger k.

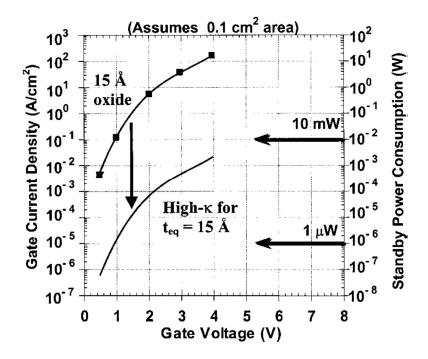

In current CMOS devices, the thermally-grown silicon dioxide (SiO<sub>2</sub>) film has been commonly used as the gate dielectric for decades due to its excellent bulk and interfacial properties, such as a large energy band gap ( $E_g \sim 9$  eV), a high dielectric breakdown strength ( $\sim 15$  MV/cm), a high crystallization temperature (> 1100 °C), and a low interface state density ( $D_{ii} < 10^{11}$  eV<sup>-1</sup>·cm<sup>-2</sup>).<sup>1,4,5</sup> For the device's scaling down, the SiO<sub>2</sub> thickness in a MOSFET keeps decreasing, but it will reach the limitation very soon. When the gate SiO<sub>2</sub> thickness is below 3 nm, the gate leakage current will become unacceptably large and several critical problems, e.g., power consumption and device reliability, will comes out.<sup>6,7</sup> In addition, the direct tunneling current through the SiO<sub>2</sub> gate dielectric will increase by 2 orders when the SiO<sub>2</sub> film thickness is reduced each 0.5 nm.<sup>8</sup> However, if we use a high-k material, e.g., to maintain the same  $C_{ox}$  as 15 Å thick SiO<sub>2</sub> does, we can reduce the gate leakage current and power consumption by 4 orders as shown in Figure 2. Therefore, the high-k material is needed for sub-3 nm thick gate dielectric devices.

Figure 2. Power consumption and gate leakage current density for a chip which has a 15 Å thick SiO<sub>2</sub> gate dielectric or an alternate dielectric exhibiting the same capacitance. (Reprinted with permission from Ref. 1. Copyright 2001 AIP.)

## 1.1.2 HfO<sub>2</sub> High-K Gate Dielectric

Several high-k materials, such as Ta<sub>2</sub>O<sub>5</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, and so on, have been proposed to replace the conventional SiO<sub>2</sub> gate dielectric in MOSFETs.<sup>9</sup> The most favorable advantage of these high-k films is that they can use a larger physical thickness than that of the SiO<sub>2</sub> film to achieve the same  $C_{ox}$  and equivalent oxide thickness (EOT).<sup>10</sup> The EOT can be estimated by the following equation:<sup>1</sup>

$$EOT = \frac{k_{SiO_2}}{k_{high-k}} t_{high-k}.$$

[3]

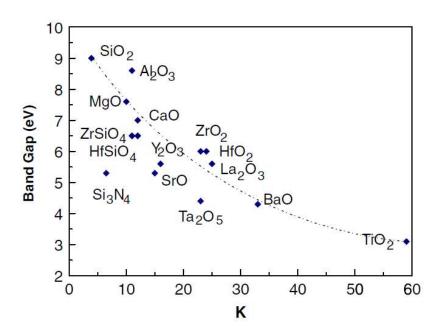

Thus, a large k value is always desirable and preferable to reach a small EOT with a large physical thickness. Nevertheless,  $E_g$  values have a roughly inverse dependence on k values following the equation:<sup>11</sup>

$$E_g \sim k^{-0.65}$$

[4]

To prevent a large leakage current,  $E_g$  values should be larger than 5 eV and the k value has to be in the reasonable range of 20-30 accordingly. Figure 3 shows that HfO<sub>2</sub>, ZrO<sub>2</sub>, and La<sub>2</sub>O<sub>3</sub> are the most promising candidate high-k materials. 12

Figure 3. Static dielectric constant versus band gap for candidate high-k gate oxides. (Data from Ref. 1 and 12.)

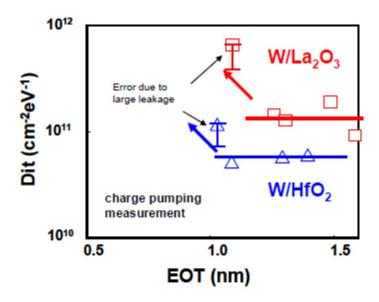

Since a high temperature treatment is required in the MOSFET fabrication for the post deposition annealing and dopant activation, the thermal stability is critical for the high-k material. 13 In the thermally instable high-k film, the amorphous-to-polycrystalline phase transition may occur and a large number of grain boundaries generates and form diffusion paths. 14 In this case, the gate leakage current increases dramactically. 15-16 On the other hand, the interfacial quality at the high-k/Si interface affects the interface density states and the carrier mobility in the channel. For most high-k films, the interface layer can be generated by the metal silicate or slicide formation from the reaction of the diffused metal atoms with Si and O or the metal oxide with Si during the high temperature process. <sup>17</sup> The formed layer always has a relatively low k and causes a large  $D_{it}$ . Therefore, it has been a key step for the high-k application in the IC fabrication to suppress the interface layer formation and minimize the  $D_{it}$ . Figure 4 shows the  $D_{it}$  of the HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> films deposited on the Si substrate after the 500 °C post deposition annealing (PDA) step.<sup>20</sup> Under the same PDA condition, the HfO<sub>2</sub> film has a lower D<sub>it</sub> than the La<sub>2</sub>O<sub>3</sub> film does, which excludes the latter to be the gate dielectric in this dissertation.

Figure 4.  $D_{it}$  of La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> thin films annealed at 500 °C. (Reprinted with permission from Ref. 20. Copyright 2008 IEEE.)

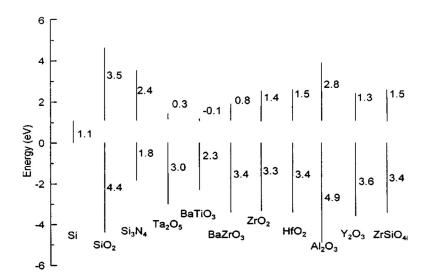

On the other hand, although the chemistries of  $HfO_2$  and  $ZrO_2$  are nearly identical,<sup>21</sup> the latter tends to form silicide with Si, which can degrade effective k values and increase gate leakage current.<sup>22,23</sup> Moreover, the conduction and valance band offsets of  $HfO_2$  are 1.5 eV and 3.4 eV with respect to Si,<sup>24</sup> respectively, which are relatively larger than those of  $ZrO_2$  and other high-k candidates with comparable k values as shown in Figure 5. Therefore,  $HfO_2$  is more favorable to serve as the gate dielectric in a MOSFET.

Figure 5. Conduction band and valence band offsets of various high-*k* oxides on Si. (Reprinted with permission from Ref. 24. Copyright 2000 AVS.)

# 1.1.3 Zr-doped HfO<sub>2</sub> High-K Gate Dielectric

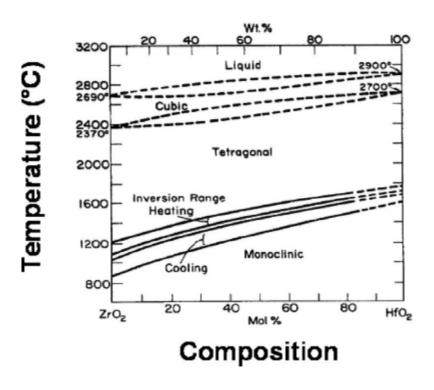

As discussed before, the HfO<sub>2</sub> high-k gate dielectric has been extensively used in the advanced MOSFET devices for its high effect k value, large conduction and valence band offsets with respect to Si, and thermally stable contact with Si.<sup>25</sup> However, there exists a great drawback of HfO<sub>2</sub> films for the MOSFET application, i.e., low crystallization temperature (< 500 °C).<sup>26</sup> In common IC processes, it will be very easy to form crystalline in HfO<sub>2</sub> films and transfer charges through the oxide layer via grain boundaries, forming a large gate leakage current. Previously, it is reported that adding a small amount of Zr into the Ta<sub>2</sub>O<sub>5</sub> high-k film can improve its amorphous-to-crystalline temperature, e.g., from 600 °C to 900 °C.<sup>27,28</sup> Since HfO<sub>2</sub> and ZrO<sub>2</sub> and have similar gate dielectric properties (i.e., k value,  $E_g$ , and band offsets) and are miscible as shown in Figure 6,<sup>29</sup> The Zr-doped HfO<sub>2</sub> (ZrHfO) high-k dielectric has been proposed to solve the low

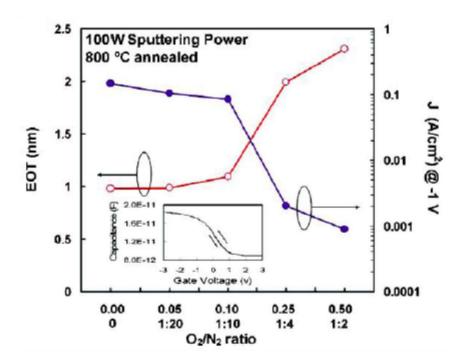

crystallization temperature problem. By adding a small amount of Zr (12 wt%), into a Hf target, the ZrHfO gate dielectric can be deposited by sputtering the composite targe in Ar/O<sub>2</sub> atmosphere.<sup>30</sup> Compared to the undoped HfO<sub>2</sub> film, the ZrHfO film showed a much higher amorphous-to-polycrystalline transition temperature (> 900 °C), a lower  $D_{it}$ , and a smaller EOT.<sup>30,31</sup> Furthermore, a sub-nanometer EOT (e.g., 0.97 nm) with low gate leakage current was achieved in the sputter-deposited ZrHfO high-k gate dielectric MOS capacitor as shown in Figure 7.<sup>30</sup> Therefore, ZrHfO is a good high-k gate dielectric material and will be applied in this dissertation for both nonvolatile memory and light emitting applications.

Figure 6. Temperature-composition phase of HfO<sub>2</sub>-ZrO<sub>2</sub>. (Reprinted with permission from Ref. 29. Copyright 2007 AIP.)

Figure 7. EOT and gate leakage current of ZrHfO films after the PDA under different  $O_2/N_2$  ratios. (Reprinted with permission from Ref. 30. Copyright 2007 ECS.)

## 1.2 Nanocrystal Nonvolatile Memory

#### 1.2.1 Conventional Flash Nonvolatile Memory

In 1980, the flash nonvolatile memory (NVM) was firstly proposed by Masuoka in Toshiba. Since then, the flash memory has been extensively investigated and widely exploited for the modern portable electronics. Currently, the NAND flash NVM dominates the market and production for its large capacities, fast write/erase speed, small erase units, and IC process compatibility. The NVM is defined as a device that can maintain in two distinguished charged states, i.e., the written and erased states, for more than 10 years with power.

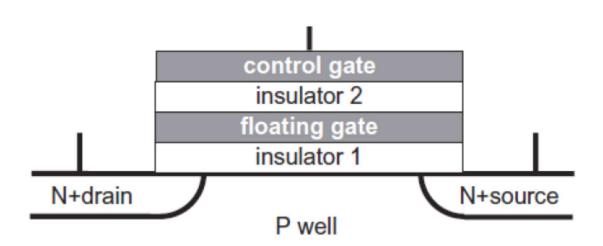

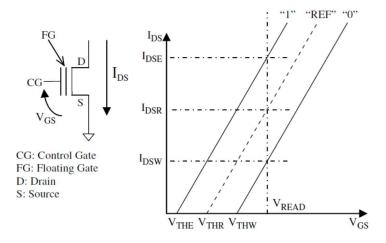

Figure 8 shows a typical structure of a flash memory core cell. This resembles a standard MOSFET with two gates, i.e., the control (CG) and floating (FG) gates.<sup>33</sup> The conventional FG layer is made from continuous poly-Si layer that functions as a potential well to trap charges. The device is written and erased by charges tunneling through the insulator 1, which therefore is named as "tunnel oxide"; the current leakage between FG and CG is blocked by the thicker insulator 2, which therefore is named as "control oxide". Normally, the cell represents the logic "0" by the written state and the logic "1" by the erased state, as shown in Figure 9.<sup>34</sup>

Figure 8. Schematic cross-sectional structure of a flash memory core cell. (Reprinted with permission from Ref. 33. Copyright 2007 Wiley.)

Figure 9. Current/voltage characteristics as a function of the threshold voltage of a flash cell. (Reprinted with permission from Ref. 34. Copyright 2008 Springer.)

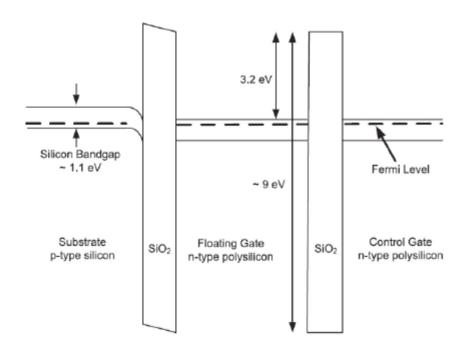

Figure 10 shows a typical band energy diagram for a conventional FG flash NVM made of poly-Si CG/control SiO<sub>2</sub>/poly-Si FG/tunnel SiO<sub>2</sub>/Si.<sup>33</sup> In the conduction band, the poly-Si FG layer is isolated the high energy barriers of the control and tunnel SiO<sub>2</sub> layers to provide the nonvolatile retention of stored charges. In order to write/erase the device, i.e., storing or releasing charges, the potential difference between the FG and either SiO<sub>2</sub> layer needs to be altered until charges can overcome the barrier. During these processes, charges mainly follow two conduction mechanisms, i.e., Fowler-Nordheim (F-N) tunneling and channel hot electron (CHE) injection. F-N tunneling is induced by a high electrical field where electrons can easily tunnel through the triangular barrier.<sup>35</sup> CHE injection happens when an electron gains energy from an electric field and then collides with the lattice to redirect itself into the FG layer.<sup>35</sup> Typically, the NOR device is written

by CHE and erased by F-N tunneling; the NAND device uses F-N tunneling for both operation.

Figure 10. Energy band diagram for a typical FG structure. (Reprinted with permission from Ref. 33. Copyright 2007 Wiley.)

## 1.2.2 Nanocrystals Embedded FG Structure

Following the Moor's law that the transistor number in a dense IC chip doubles every two years,<sup>36</sup> the flash NVM has to scale down the tunnel oxide thickness to achieve the goals of ultra-high density, fast speed, and energy-saving. However, when the thickness of the SiO<sub>2</sub> layer is scaled down to 1.2 nm, the leakage current becomes unacceptably large and stored charges will easily tunnel back to the Si substrate.<sup>1,6,35</sup>

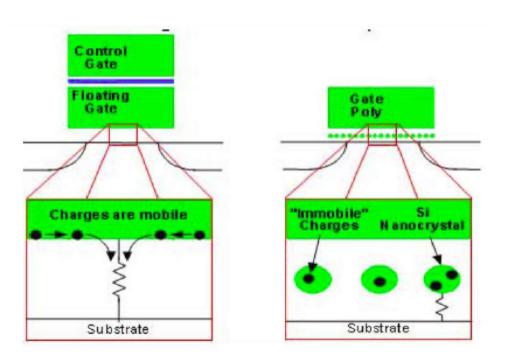

Moreover, all trapped charges can easily release from the conducive continuous poly-Si FG layer through a weak spot in the tunnel oxide layer, as shown in Figure 11.<sup>37</sup> This would cause a serious reliability issue for the memory application. Therefore, it was proposed by Tiwari in 1996 to use the discrete nanocrystalline Si (nc-Si) dots instead of the continuous FG layer.<sup>38</sup> In this structure, only part of the stored charges will be released when a leakage path forms through the tunnel oxide layer. Thus, this structure has drawn extensive attention as a promising candidate to replace the conventional FG NVM for the further scaling.

Figure 11. Schematic diagram illustrates how a defect chain affects the charge loss in conventional FG structure and nanocrystal embedded FG structure. (Reprinted with permission from Ref. 37. Copyright 2006 IEEE.)

#### 1.2.3 Fabrication of Embedded Nanocrystals

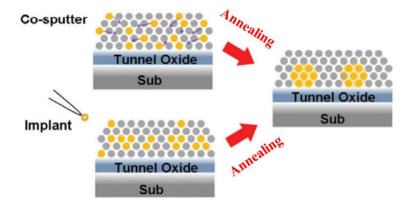

The nanocrystals embedded in the FG structure can be prepared by numerous methods, such as self-assembly and precipitation.<sup>35</sup> The basic procedure of self-assembly for nanocrystal formation is shown in Figures 12(a) to 12(c). A 1-5 nm thick film, i.e., charge trapping layer (CTL), is deposited and then annealed at a temperature close to its eutectic temperature in an inert ambient gas, usually N<sub>2</sub>, to convert the CTL into a discrete nanocrystalline form. The nanocrystal diameter is significantly influenced by the thickness of the embedded CTL as well as the annealing temperature and duration. <sup>39-42</sup> Fig. 12(d) shows the major driving forces driving this process, which is accomplished through the relaxation of film stress and limited by the surface energy. During the annealing, atoms can gain enough surface mobility and the film self-assembles into a more thermodynamically stable state with the minimum surface energy.<sup>42</sup> In the process, dispersion force and electrical double layer affect the nanocrystal size and location distributions. 42-44 This method is very popular for its easy operation and many kinds of materials, such as Si, cobalt (Co), gold (Au), tungsten (W), silver (Ag) and platinum (Pt), have been embedded into the FG by it. 40-42,45 On the other hand, Figure 13 shows the precipitation method that uses high injection energy (30-150 keV) ion implantation or codeposit system to form nanocrystals.<sup>35,46,47</sup> This process is usually followed by the thermal treatment, e.g., at 950-1050 °C for 30-60 min in N2 atmosphere. During the thermal process, reactants can gain enough energy to diffuse through the film and collide with other reactants to form nucleus. 48 At the high temperature, more reactants can bond to the nucleus and form discrete nanocrystalline dots in the CTL. However, the high-energy ion

implantation may damage the tunneling oxide and degrade the device performance. Additionally, this method cannot control the size and spatial distribution of nanocrystals in the gate dielectric. In this dissertation, the nc-CdS and nc-CdSe embedded ZrHfO gate dielectric stacks are fabricated based on the concept of the thin film self-assembly process. The thin embedded layer will be deposited by the sputtering technique and subjected to a rapid thermal process.

Figure 12. TEM image and schematic drawing of nanocrystal formation by self-assembly with increased duration of thermal treatment from (a) to (c); (d) Major driving forces in nanocrystal formation by self-assembly. (Reprinted with permission from Ref. 35. Copyright 2011 Elsevier.)

Figure 13. Schematic drawing of nanocrystal formation by precipitation. (Reprinted with permission from Ref. 35. Copyright 2011 Elsevier.)

## 1.2.4 Nanocrystals Engineering

The nc-Si is firstly used in the nanocrystal FG NVM by Tiwari in 1996 for its compatibility with the standard MOSFET technology. <sup>38</sup> However, the nc-Si embedded FG NVM suffers the degraded electron trapping capability and retention performance from two mechanisms, i.e., the Coulomb blockade and quantum confinement effects. <sup>49,50</sup>

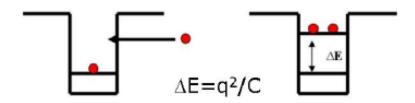

Coulomb blockade effect describes the energy level increase due to the trap of multiple electrons in the nanocrystal. This effect becomes more pronounced when the nanocrystal size is below 3 nm.<sup>51</sup> The raise of electrostatic potential from the trap of an electron can be approximately calculated from the below equation:

$$\Delta E = \frac{q^2}{C}$$

[5]

where q is the electron charge, C is the self-capacitance of the nanocrystal ( $C = 2\pi\epsilon_0 d$  where  $\epsilon_0$  is the dielectric constant of the tunnel oxide and d is the nanocrystal diameter). The increase of the electrostatic potential is illustrated in Figure 14. For an electron trapped

in a nc-Si of 5 nm diameter, the self-capacitance is approximately 0.7 atto farads and the increase of electrostatic potential energy is about 0.074 eV.<sup>38</sup> Therefore, the increase of energy level lower down the barrier between the nc-Si and the tunnel oxide, which degrades the device's retention performance. Moreover, as electrons are trapped in the nanocrystal, the built electrostatic potential decreases the electric field across the tunnel oxide and prevent the subsequent electrons from injecting into the nanocrystal. Consequently, the number of trapped electrons in the nc-Si is limited.

Figure 14. Illustrations of Coulomb blockade effect.

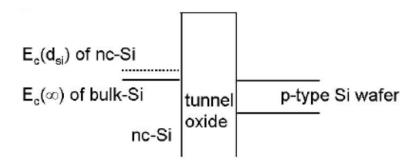

The quantum confinement effect is the enlargement of band gap as Si is prepared in the nanometer size. As a result, the energy band offset of nc-Si/tunnel oxide is reduced. The shift of the conduction band edge due to the quantum confinement effect can be estimated using the following equation,<sup>51</sup>

$$E_C(d_{Si}) - E_C(\infty) = \frac{1.39}{d_{Si}^2 + 1.788d_{Si} + 0.668}(eV)$$

[6]

where  $E_C(d_{Si})$  is the conduction band edge of the nc-Si,  $E_C(\infty)$  is the conduction band edge of the bulk Si, and  $d_{Si}$  is the nc-Si size in diameter. As shown in Figure 15, the increase of the conduction band edge for a 5 nm nc-Si is 0.04 eV.

Figure 15. Illustrations of quantum confinement effect.

Due to the Coulomb blockade and quantum confinement effects, the stored charges in the nc-Si will be easily tunneled back to Si substrate because of the lower band offset between nc-Si and tunnel oxide. One way to solve this problem is to replace the nc-Si by another nanocrystal material with a large electron affinity or work function and a small band gap. This can create a deep potential well in the conduction or valence band for better retention performance. <sup>52,53</sup> Thus, in this dissertation, nanocrystalline cadmium sulfide (nc-CdS) and nanocrystalline cadmium selenide (nc-CdSe) have been embedded into the gate dielectric as the charge trapping media. CdS is an *n*-type semiconductor with a large electron affinity of 4.3 eV and a small band gap of 2.42 eV. <sup>54</sup> CdSe is another *n*-type II-VI group semiconductor with a large work function of 4.8-5.0 eV and a small band gap of

2.3 eV.<sup>55</sup> They both create deep potential wells in the conduction and valence bands. As mentioned in last section, the ZrHfO high-*k* dielectric is exploited as the tunnel and control oxide layers for its excellent material and electrical properties. Therefore, the nc-CdS and nc-CdSe embedded ZrHfO high-k gate dielectric capacitors have been fabricated and characterized for the NVM functions.

### 1.3 Light Emitting Device

### 1.3.1 Conventional Light Emitting Device

In 1879, the incandescent light bulb was invented to emit warm white light with a W filament heated to a high temperature by Joule heating. <sup>56</sup> The light has a color temperature close to that of sunlight and extremely high color rendering index (CRI) of nearly 100. <sup>57</sup> However, the device can only convert the less than 5% of electrical energy into the visible light. Approximately at the same time, the fluorescent lamp was invented to provide a more efficient lighting alternative of 50-60 lm/W than the incandescent light bulb (< 20 lm/W). The fluorescent lamp relies on inelastic collisions of electrons with mercury atoms to emit ultra violet (UV) photons, which are subsequently absorbed by the lamp's fluorescent coating and converted into visible light. Commercial fluorescent lamps can be as efficient as 100 lm/W but they is limited by their poor CRI and color temperature. Moreover, it contains mercury vapor that is an environmental pollutant once leak out. <sup>58,59</sup>

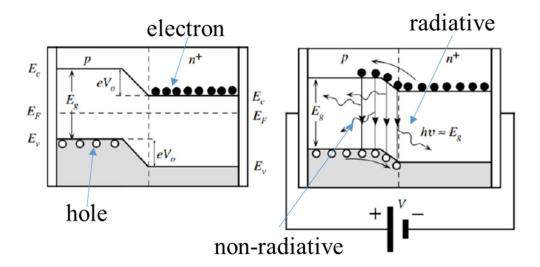

The light emitting device (LED) has a high conversion efficiency of  $\sim 80\%$  and a long lifetime of  $\sim 50,000$  hours. It is a promising lighting method to replace the incandescent light bulb and fluorescent lamp, which can reduce  $\sim 38\%$  of the total lighting

energy usage in the United States.<sup>60</sup> The first visible-spectrum red LED was developed in 1962 by Nick Holonyak, Jr. while working at General Electric.<sup>61</sup> It emitted light from a III-V compound semiconductor material, i.e.,  $Ga(As_{1-x}P_x)$ . The light emission principle of the LED is: under forward-biased condition, when carriers, i.e., electrons and holes are injected across the p-n junction, it emits incoherent light as shown in Figure 16.<sup>62</sup> The emitted photon energy is approximately equal to the bandgap energy as the following equation,<sup>62</sup>

$$hv = \frac{hc}{\lambda} \cong E_g$$

[7]

where h is the Planck's constant of  $6.626 \times 10^{-34}$  J/s, v is the frequency of light, c is the speed of light of  $3x10^8$  m/s,  $\lambda$  is the wavelength of light, and  $E_g$  is the band gap energy. Currently, commercialized LEDs are still made from III–V compound semiconductor materials. Different bandgap energies are used to produce different wavelengths of the emission lights, such as GaAlAs (red), AlInGaP (yellow-orange), InGaN (blue, green), AlInGaN (ultra violet).

Figure 16. Energy band diagrams of a p-n<sup>+</sup> junction (a) without bias and (b) with applied bias V. (Adapted from Ref. 62.)

The electron-hole recombination process can be classified into two kinds: radiative and non-radiative recombination.

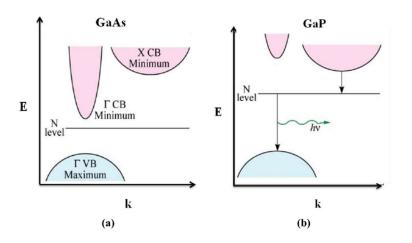

Radiative recombination is the band-to-band recombination that mainly happens in direct bandgap semiconductors. Figure 17(a) shows an example of a direct bandgap semiconductor, GaAs,<sup>63</sup> where the minimum energy of conduction band lies directly above the maximum energy of valence band in the momentum space energy. In this material, free electrons at the bottom of conduction band can recombine directly with free holes at the top of the valence band, as the momentum of the two carriers is the same. This transition from conduction band to valence band involves photon emission. Direct recombination occurs spontaneously.

Generally, the non-radiative recombination includes Auger recombination, surface recombination, or recombination at defects.<sup>64</sup> As shown in Fig. 17(b), the momentum

location of the minimum energy of conduction band is shifted by a k-vector compared to that of the maximum energy of valence band in an indirect bandgap semiconductor, e.g., GaP. Because of this momentum difference, the probability of direct recombination, i.e., radiative recombination is low. Additional dopants (impurities) are added in this kind of material to form shallow donor states. These donor states serve as the recombination centers that capture the free electrons locally and shift to the momentum location of the maximum energy of valence band for electron-hole recombination. Besides a photon emission, phonon emission or absorption has to take place, which should satisfy both energy and momentum conservations. This indirect recombination is called non-radiative recombination.

Figure 17. Schematic band structures of (a) GaAs and (b) GaP.

## 1.3.2 White Light Emitting Device

As discussed previously, the wavelength of light emitted from a *p-n* junction LED is decided by the bandgap energy of the semiconductor material, which has a very narrow band. For white light emission, there are two major methods as shown in Figure 18.<sup>65</sup> The first method is to combine red, green, and blue lights from three different LEDs.<sup>66</sup> However, a special driving circuit is required to balance the light colors.<sup>67</sup> The second method is to combine a blue or UV LED with a yellow phosphor or a tri-phosphor blend as shown in Fig. 18(b).<sup>68</sup> However, the light conversion of short wavelength to long wavelength always accompanies with the Stokes energy loss, which costs 10-30% of the overall power.<sup>56</sup> Therefore, a cheap single-chip white light LED is eagerly anticipated.

Figure 18. Construction and characteristics of white LED: (a) through colored RGB LEDs and (b) through blue/UV LED in combination with phosphors. (Reprinted with permission from Ref. 65. Copyright 2007 Wiley.)

On the other hand, the fabrication of these compound semiconductor epitaxy layers requires using the expensive molecular beam epitaxy (MBE) or the highly toxic metal organic chemical vapor deposition (MOCVD) processes. Moreover, the performance of these single crystal LEDs is critically affected by defect densities in p-n junction or WQ. They always suffer the poor lifetime problem from crystal defects during the mismatched growth. Separately, the LED can be made with the structure of the quantum dot (QD) embedded dielectric thin films, like nc-Si embedded silicon oxide (SiO<sub>x</sub>) or silicon nitride

$(SiN_x)$ .<sup>71,72</sup> The QDLED emits light from the electron-hole radiative recombination in the QD due to quantum confinement effects and exciton radiative recombination at defective bonds in the dielectric film.<sup>71</sup> Though, the QDLED is subject to the low power efficiency and the short lifetime, e.g., nc-Si embedded  $SiO_x$  or  $SiN_x$  matrix has a bad efficiency of <0.01% and a poor lifetime of <1,800 hr.<sup>72</sup>

# 1.3.3 Solid State Incandescent Light Emitting Device

It is desirable to have a LED that emits the broad band white light from a single device and can be fabricated with the low-cost, environmentally friendly, and ICcompatible processes with a long lifetime. Since 2011, Kuo's group proposed a new type of solid-state incandescent LED (SSI-LED) that emitted the warm white light similar to that of the incandescent bulb. 73-81 The light emitting principle of the SSI-LED is the thermal excitation of the nano-sized conductive path, i.e., nano-resistor, from the passage of a current.<sup>73-81</sup> Under the resistive heating, atoms in the nano-resistor are thermally excited and part of the thermal kinetic energy is transferred to electrons. 82 These excited electrons can relieve by photonic emission and it produces a continuous non-discrete spectrum due to the near-continuum of electron energy levels.82 The light emission spectrum is close to that of the incandescent light bulb, i.e., blackbody radiation. This kind of device is made from a MOS capacitor composed of an amorphous high-k dielectric thin film, such as Zr-doped HfO<sub>2</sub> (ZrHfO), HfO<sub>x</sub>, or WO<sub>x</sub>, on a p-type Si wafer. 73-81 The nanoresistor is formed from the breakdown of the high-k dielectric thin film, which generates a bump above it.<sup>79</sup>

These high-*k* dielectrics are often used in the MOS field-effect transistors (MOSFETs) or capacitors. Upon the deposition of the high-*k* dielectric film, a PDA step is carried out to densify and to reduce defects in the film. The PDA condition is critical to the material and electrical properties of the final device. For the SSI-LED, the PDA process influences the conductive path formation and therefore, characteristics of the emitted light. In this dissertation, the effect of the PDA atmosphere on the electrical and optical properties of the ZrHfO high-*k* SSI-LED have been investigated.

On the other hand, there is lack of detailed information of electrical properties of nano-resistors in this new type of device. It was reported that when conductive paths were formed from the hard breakdown of the metal oxide MOS capacitor, contacts at the gate/conductive path and conductive path/Si could be taken as the ohmic and Schottky contacts, separately.<sup>83</sup> Therefore, the effective resistance and Schottky barrier height of nano-resistors in the ZrHfO high-*k* SSI-LED have been studied under different stress voltages and temperatures.

### 1.4 Outline of this Dissertation

Chapter II focuses on the experimental methods utilized in this dissertation. Their corresponding background knowledge and the related equipment operations will be described. At first, the process flow of fabricating the ZrHfO high-k MOS capacitor with or without the embedded layer will be described in detail. Then, the fundamental background of the thin film deposition and annealing methods will be reviewed, including the radio frequency (RF) magnetron sputtering technique, the rapid thermal annealing

(RTA) equipment, and the plasma enhanced chemically vapor deposition (PECVD). The instruments and the background knowledge of the material characterizations, e.g., profilometer, secondary ion mass spectrometry (SIMS), atomic force microscopy (AFM), and scanning electron microscope (SEM) will be introduced. The electrical and optical characterizations of the ZrHfO high-k based NVMs and SSI-LEDs, such as system setups, capacitance-voltage (C-V), conductance-voltage (G-V), current density-voltage (J-V), and light spectrum measurements, will be also discussed in this chapter.

Chapter III focuses on the NVM application of the nc-CdS embedded ZrHfO high-k gate dielectric stack. The detailed electrical investigations of this device will be presented. The discrete nc-CdS prefers to trap holes other than electrons due to its n-type nature. The device shows negligible frequency dispersion phenomena which indicates holes are mainly trapped in the CdS nanocrystals. Due to the good contact between the nanocrystals and the high-k film, this NVM device shows excellent low voltage operation performance, i.e., comparable or even better memory windows and hole retention capabilities. More than half of the originally trapped holes can remain in the high-k stack for 10 years. The nc-CdS embedded ZrHfO high-k stack is a viable dielectric structure for the low power operating NVM application.

Chapter IV describes the temperature effects on the charge trapping/detrapping and transfer mechanisms as well as the dielectric breakdown behavior and retention capabilities of the nc-CdSe embedded ZrHfO gate dielectric NVM. The hole-trapping capacity increases but the electron-trapping capacity decreases with the increase of temperature. The frequency dispersion result shows more holes are loosely trapped at the

nanocrystal/high-k interface and electrons are mainly trapped in the bulk nanocrystal at high temperatures. The temperature dependence and mechanisms of charge transfer have been discussed. At the same time, the high temperature accelerates the failure process of the device and the statistical breakdown distribution has been analyzed. The temperature dependent relaxation current study shows that releases of the trapped holes and electrons are dominated by two different mechanisms. This causes the faster degradation of the electron retention capability.

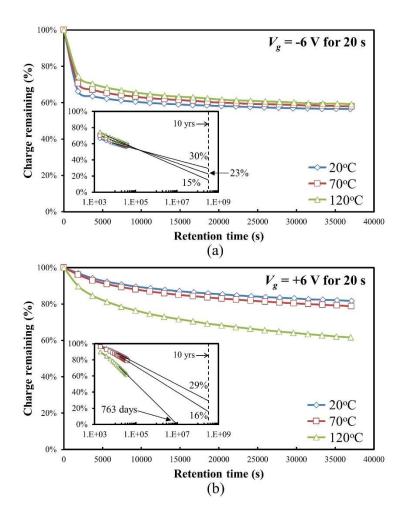

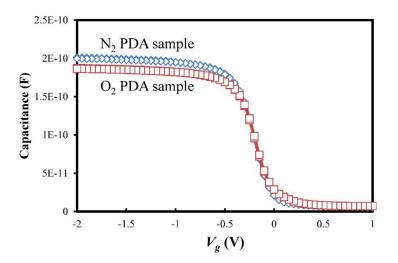

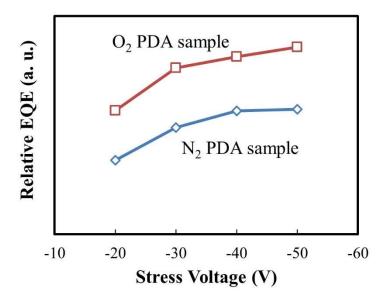

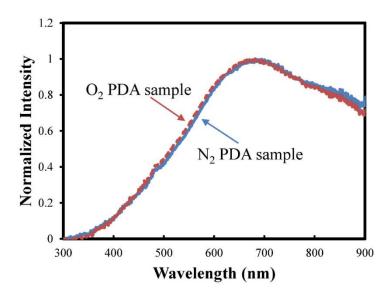

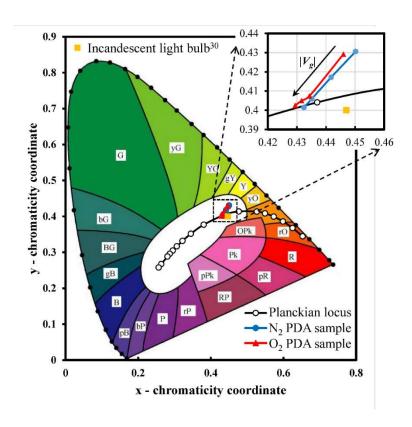

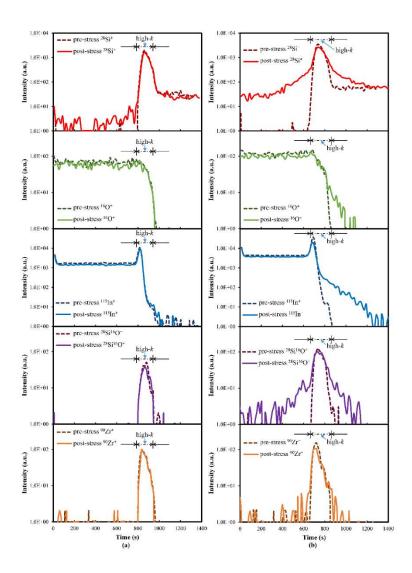

Chapter V discusses the PDA atmosphere effects on the electrical and optical properties of the ZrHfO based SSI-LED. The O<sub>2</sub> PDA step changes compositions of the original high-k stack and the nano-resistor formed from the dielectric breakdown. Therefore, it affects the device's interface state density, dielectric breakdown, leakage current, light emission intensity, light emission efficiency, and light chromaticity, which is an important factor for the performance of the SSI-LED.

Chapter VI describes the methods to estimate the electrical properties, i.e., the effective resistance and Schottky barrier height, of nano-resistors from the SSI-LED's current-voltage (*I-V*) curve. The temperature dependence of the nano-resistor effective resistance indicates the difference of nano-resistors from a conductor or a semiconductor. The effective barrier height increases with the increase of temperature, which is caused by the random and complicated formation of nano-resistors. The nano-resistor is fully developed after the 1 min stress.

Chapter VII focuses on two approaches to enhance the light emission characteristics of the SSI-LED, i.e., embedding the  $WO_x$  layer into the ZrHfO gate dielectric and using the heavily doped p-Si substrate for fabrication.

Chapter discusses the extensive applications of this novel nano-resistor device for the on-chip optical interconnect and the diode-like anti-fuse one-time programed NVM.

Chapter IX summarizes all studies in this dissertation and draws conclusions.

### CHAPTER II

#### EXPERIMENTAL

#### 2.1 Introduction

This chapter focuses on the experimental methods used in this dissertation. First, the process flow of fabricating the nanocrystal embedded high-*k* based NVM or the high-*k* based SSI-LED will be described in detail. Second, the background of RF magnetron sputtering, RTA, and PECVD will be introduced. Third, the material characterization instruments, such as profilometer, SIMS, AFM, and SEM will be discussed. Finally, the electrical and optical characterizations, such as, system setups as well as *C-V*, *G-V*, *J-V*, and light spectrum measurements, will be addressed.

### 2.2 Fabrication Process Flow

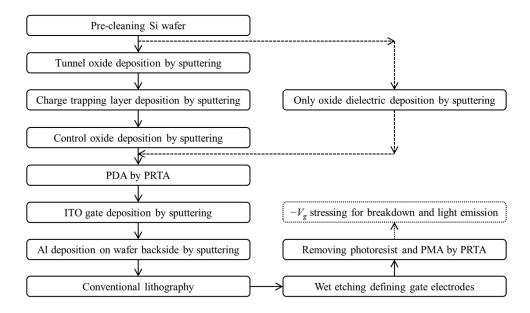

Figure 19 shows the process flow chart of fabricating a nanocrystal embedded high-k gate dielectric MOS capacitor, its corresponding control MOS capacitor, or a SSI-LED. In this dissertation, all the device will be fabricated on the <100> p-type Si substrate (resistivity 11-20  $\Omega$ ·cm, doping concentration ~10<sup>15</sup> cm<sup>-3</sup>, supplied from MEMC). The sample size is about 1.5 inch×1.5 inch.

The bare Si wafer was pre-cleaned by a dilute hydrofluoric acid (DHF, 2 %) solution for 5 min to remove the native oxide on the Si surface. The Si surface changed from hydrophilic to hydrophobic after removal of native oxide. Then, the substrate was flushed with the deionized water (DI, resistivity > 18 M $\Omega$ ·cm) for 5 min. After drying by

the N<sub>2</sub> blowing, the sample was immediately loaded into the load-lock chamber and transferred into the main chamber of the sputtering system.

Figure 19. Fabrication process flow of a nanocrystal embedded high-k gate dielectric MOS capacitor, its corresponding control MOS capacitor, or a SSI-LED.

In this dissertation, the high-*k* stack was deposited by the RF (13.56 MHz) magnetron sputtering. The ZrHfO film was deposited by sputtering a Zr/Hf (12/88 wt %) composite target in Ar/O<sub>2</sub> (1:1) at 60 W and 5 mTorr. For the ZrHfO (tunnel) / CTL / ZrHfO (control) tri-layer structure, the sputtering deposition sequence was 2 min ZrHfO deposition for tunnel oxide layer, the CTL deposition, and finally 10 min for control oxide layer. The CTL deposition condition depended on the embedded material. For comparison, the control sample that contained only 12 min sputter-deposited ZrHfO high-*k* gate

dielectric film with the embedded CTL layer was prepared under the same condition. Or a simple high-k gate dielectric MOS capacitor was fabricated with only one step ZrHfO sputtering deposition for the SSI-LED investigation.

After the high-*k* stack deposition, the PDA step was carried out with a RTA equipment to densify the as-deposited film, passivate the defects, and transform the continuous CTL film into the discrete nanocrystal form. Two kinds of gases were in the PDA step, i.e., N<sub>2</sub> and O<sub>2</sub>. The PDA condition varied from 800 °C to 900 °C for 1-3 min. After the PDA annealing, an 80 nm thick indium tin oxide (ITO) film was sputter-deposited from an ITO (99.99%) target in pure Ar at 80 W and 5 mTorr on top of the high-*k* stack. The ITO film was employed as the gate electrode due to its good conductivity and good interface contact with the metal oxide dielectric as well as the excellent transparency for the SSI-LED device. A 120 nm thick aluminum (Al) film was deposited, i.e., by sputtering an Al (99.999%) target in pure Ar at 80 W and 5 mTorr, on the backside of the Si substrate to form the ohmic contact.

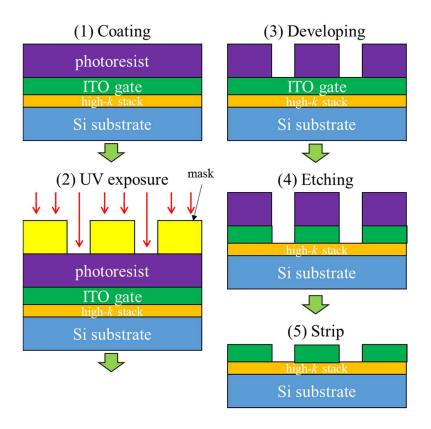

The conventional lithography process was carried out to pattern the gate electrode. First, the positive photoresist (AZ Electronics, AZ 5214-E) was spin coated on the top of the ITO gate and the backside of the Al contact. The spin speed of the spin coater (Chemat Technology, KW-4A) was set as 3.5-4.0 krpm and a 1.5-1.8 µm thick photoresist was coated on the surface. Then, the sample was soft baked at 90 °C for 1 min on a hot plate to evaporate the solvent and increase the adhesion. After that, the sample was loaded to the Quintel Q4000 aligner, directly covered with a patterned quartz mask in the contact mode, and exposed to the UV light at 10 mW/cm² for 30 s. After the exposure, the

patterned photoresist film was developed in the MIF 300 developer (AZ Electronics) solution, which was composed of tetramethylammonium hydroxide that dissolved the UV-exposed photoresist. This process took 1-5 min. Next, the sample was hard baked at 125  $^{\circ}$ C for 5 min in the oven to solidify the photoresist. After the hard baking, the ITO gate electrode was subsequently patterned by wet-etching non-photoresist-covered areas. The etching solution was aqua regia, i.e., HNO<sub>3</sub>:HCl (1:3), and the average etching rate was about 1000 nm/min. The remaining photoresist was removed by the acetone ultrasonic bath for 1 min and the finished sample was washed by isopropyl alcohol (99.9999%) and DI. Finally, the complete device was annealed at 300-400  $^{\circ}$ C in forming gas (H<sub>2</sub>/N<sub>2</sub> = 1:9) for 5 min, i.e., the post metal annealing (PMA) treatment, to passivate the oxygen deficiencies and dangling bonds as well as facilitate the Al diffusion into Si for the ohmic contact formation.

Figure 20. Illustration of the pattern transferring process.

# 2.3 Thin Film Deposition and Annealing

# 2.3.1 RF Magnetron Sputtering System

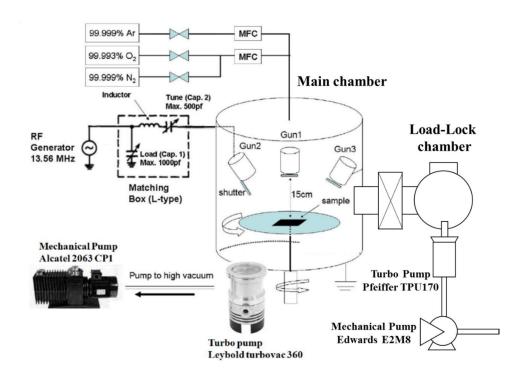

Figure 21 shows its schematic diagram of the sputtering system used in this dissertation, which is consisted of two chambers, i.e., load-lock and main chambers. Both chambers are made of the stainless steel, and vacuum sealed with the fluoroelastomers (Viton) O-rings and Cu gaskets.

Figure 21. The illustration of the RF magnetron sputtering system.

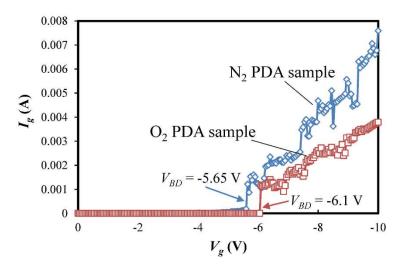

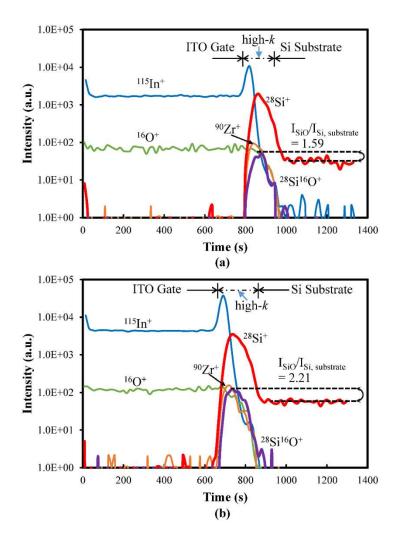

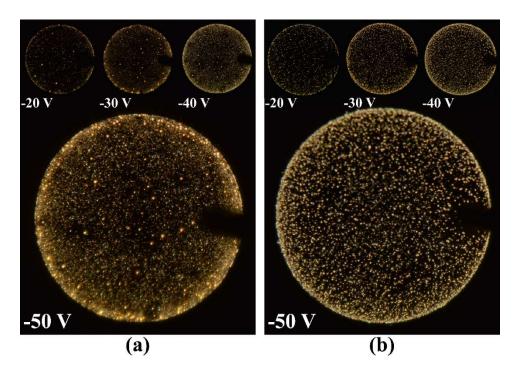

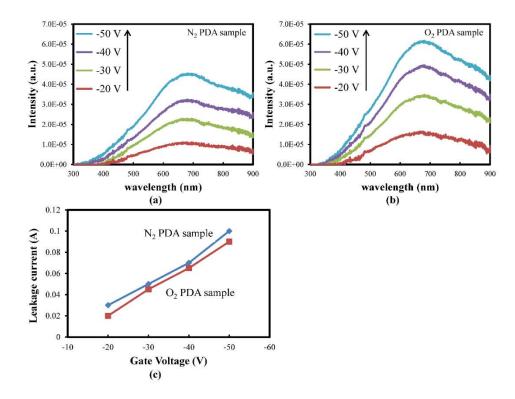

After the sample loading into the load-lock chamber, it was subsequently pumped down to about 10<sup>-5</sup> Torr by the combination of the mechanical pump (Edwards, E2M8) and turbo pump (Pfeiffer, TPU 170). This process takes about 20 min because of the chamber's small volume (15 L). Then, the sample was transferred into the main chamber of the sputtering system that was already in the high vacuum environment, i.e., < 10<sup>-5</sup> Torr. After the thin film deposition process, the sample was transferred back to the load-lock chamber without breaking the high vacuum environment in the main chamber. The main function of the load-lock system is to efficiently increase the sputtering deposition yield by avoiding the long pump down time of the main chamber and to minimize the exposure of the main chamber to the air contamination.