US009946475B2

# (12) United States Patent Jiang et al.

### (54) JOINT REWRITING AND ERROR CORRECTION IN WRITE-ONCE MEMORIES

(71) Applicants: California Institute of Technology,

Pasadena, CA (US); Texas A&M University System, College Station, TX

(US)

(72) Inventors: Anxiao Jiang, College Station, TX

(US); Yue Li, College Station, TX (US); Eyal En Gad, Pasadena, CA (US); Michael Langberg, Buffalo, NY (US); Jehoshua Bruck, Pasadena, CA

(US)

(73) Assignee: CALIFORNIA INSTITUTE OF

TECHNOLOGY, Pasadena, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 139 days.

(21) Appl. No.: 14/443,349

(22) PCT Filed: Jul. 5, 2013

(86) PCT No.: PCT/US2013/049480

§ 371 (c)(1),

(2) Date: May 15, 2015

(87) PCT Pub. No.: WO2014/116301

PCT Pub. Date: Jul. 31, 2014

(65) Prior Publication Data

US 2015/0293716 A1 Oct. 15, 2015

#### Related U.S. Application Data

(60) Provisional application No. 61/756,324, filed on Jan. 24, 2013.

(Continued)

(51) Int. Cl. *G06F 12/00* (2006.01) *G06F 13/00* (2006.01) (52) **U.S. Cl.**

(Continued)

(58) Field of Classification Search

(10) Patent No.:

(45) Date of Patent:

•

US 9,946,475 B2

Apr. 17, 2018

(Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

(Continued)

#### FOREIGN PATENT DOCUMENTS

WO 2011156745 A2 12/2011

#### OTHER PUBLICATIONS

Arikan, E., "Channel polarization: A method for constructing capacity-achieving codes for symmetric binary-input memoryless channels," IEEE Transactions on Information Theory, vol. 55, No. 7, pp. 3051-3073 (Jul. 20, 2009)

(Continued)

Primary Examiner — Charles Rones

Assistant Examiner — Sidney Li

(74) Attorney, Agent, or Firm — Turk IP Law, LLC

#### (57) ABSTRACT

Both rewriting and error correction are technologies usable for non-volatile memories, such as flash memories. A coding scheme is disclosed herein that combines rewriting and error correction for the write-once memory model. In some embodiments, code construction is based on polar codes, and supports any number of rewrites and corrects a substantial number of errors. The code may be analyzed for a binary (Continued)

symmetric channel. The results can be extended to multilevel cells and more general noise models.

#### 25 Claims, 15 Drawing Sheets

| (51) | Int. Cl.                                             |                                                 |  |  |

|------|------------------------------------------------------|-------------------------------------------------|--|--|

| ` /  | G06F 13/28                                           | (2006.01)                                       |  |  |

|      | G06F 3/06                                            | (2006.01)                                       |  |  |

|      | H03M 13/13                                           | (2006.01)                                       |  |  |

|      | G11C 11/56                                           | (2006.01)                                       |  |  |

|      | G06F 11/10                                           | (2006.01)                                       |  |  |

|      | G06F 12/02                                           | (2006.01)                                       |  |  |

|      | G11C 17/14                                           | (2006.01)                                       |  |  |

|      | G11C 29/04                                           | (2006.01)                                       |  |  |

| (52) | U.S. Cl.                                             |                                                 |  |  |

|      | CPC <i>G06F 11/1012</i> (2013.01); <i>H03M 13/13</i> |                                                 |  |  |

|      | (2013.01); G06F 11/1068 (2013.01); G0                |                                                 |  |  |

|      | 12/0246 (2013.01); G11C 11/5628 (2013.01)            |                                                 |  |  |

|      | G1.                                                  | <i>IC 11/5642</i> (2013.01); <i>G11C 17/146</i> |  |  |

####

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

(2013.01); G11C 2029/0411 (2013.01)

| 2002/0136068  |     |         | Widdershoven<br>Odenwalder H04L 1/0046 |

|---------------|-----|---------|----------------------------------------|

| 2002/0139 110 |     | 10/2002 | 370/329                                |

| 2004/0001408  | A1  | 1/2004  | Propps et al.                          |

| 2006/0279437  | A1* | 12/2006 | Luby H03M 13/1515                      |

|               |     |         | 341/50                                 |

| 2008/0168215  | A1* | 7/2008  | Jiang G06F 11/1072                     |

|               |     |         | 711/103                                |

| 2008/0198652  | A1* | 8/2008  | Shalvi G11C 11/56                      |

|               |     |         | 365/185.03                             |

#### OTHER PUBLICATIONS

Bohossian, V., et al., "Buffer Coding for Asymmetric Multi-Level Memory," IEEE International Symposium on Information Theory, pp. 1186-1190 (Jun. 24-29, 2007).

Burshtein, D., and Strugaiski, A., "Polar write once memory codes," IEEE International Symposium on Information Theory Proceedings (ISIT), pp. 1972-1976 (Jul. 1-6 2012).

Cohen, G., et al., "Linear binary code for write-once memories," IEEE Transactions on Information Theory, vol. 32. No. 5, pp. 697-700 (Sep. 1986).

Gad, E.E., et al., "Rank-Modulation Rewriting Codes for Flash Memories," IEEE International Symposium on Information Theory Proceedings (ISIT), pp. 704-708 (Jul. 7-12, 2013).

Heegard, C., "On the capacity of permanent memory," IEEE Transactions on Information Theory, vol. 31, No. 1, pp. 34-42 (Jan. 1985). International Search Report for International Application No. PCT/US2013/049480 dated Sep. 10, 2013.

Jiang, A., et al., "Floating Codes for Joint Information Storage in Write Asymmetric Memories," IEEE International Symposium on Information Theory, pp. 1166-1170 (Jun. 2007).

Korada, S.B., and Urbanke, R., "Polar Codes are Optimal for Lossy Source Coding," IEEE Transactions on Information Theory, vol. 56, No. 4, pp. 1751-1768 (Apr. 2010)

Kurkoski, B.M., "Lattices for Error Correction and Rewriting in Flash Memories," accessed at http://www.jaist.ac.jp/~kurkoski/pa-pers/conf/Kurkoski-nvmwl1.pdf, accessed on Mar. 19, 2015, pp. 1-4

Merkx, F., "Womcodes constructed with projective geometries," Traitement du Signal, vol. 1, No. 2-2, pp. 227-231 (Jan. 1984). Mohammed, S.A., "Coding Techniques for Error Correction and Rewriting in Flash Memories," Master's thesis, Texas A&M University, pp. 1-42 (Aug. 2010).

Rivest, R.L., and Shamir, A., "How to reuse a write-once memory," Information and Control, vol. 55, No. 1-3, pp. 1-19 (Oct.-Dec. 1982).

Shpilka, A., "Capacity Achieving Multiwrite WOM codes," IEEE Transactions on Information Theory, vol. 60, No. 3, pp. 1481-1487 (Mar. 3, 2014).

Shpilka, A., "Capacity Achieving Two-Write WOM Codes," Latin 2012: Theoretical Informatics Lecture Notes in Computer Science, vol. 7256, pp. 631-642 (Apr. 2012).

Tal, I., and Vardy, A., "How to Construct Polar Codes," IEEE Transactions on Information Theory, vol. 59, No. 10, pp. 6562-6582 (Jul. 10, 2013).

Wu, Y., "Low complexity codes for writing a write-once memory twice," IEEE International Symposium on Information Theory Proceedings (ISIT), pp. 1928-1932 (Jun. 2010).

Wu, Y., and Jiang, A., "Position Modulation Code for Rewriting Write-Once Memories," IEEE Transactions on Information Theory, vol. 57, No. 6, pp. 3692-3697 (Jun. 2011).

Yaakobi, E., and Shpilka, A., "High Sum-Rate Three-Write and Non-Binary WOM Codes," 2012 IEEE International Symposium on Information Theory Proceedings, pp. 1386-1390 (Jul. 1-6, 2012). Yaakobi, E., et al., "Codes for Write-Once Memories," IEEE Transactions on Information Theory, vol. 58 No. 9, pp. 5985-5999 (Sep. 2012).

Yaakobi, E., et al., "Efficient Two-Write WOM-Codes," 2010 IEEE Information Theory Workshop, pp. 1-5 (Aug. 30, 2010-Sep. 3, 2010).

Yaakobi, E., et al., "Error Characterization and Coding Schemes for Flash Memories," IEEE GLOBECOM Workshops (GC Wkshps), pp. 1856-1860 (Dec. 6-10, 2010)

Yaakobi, E., et al., "Muitiple Error-Correcting WOM-Codes," IEEE Transactions on Information Theory, vol. 58, No. 4, pp. 2220-2230 (Apr. 2012).

Zémor, G., and Cohen, G.D., "Error-correcting WOM-codes," IEEE Transactions on Information Theory, vol. 37, No. 3, pp. 730-734 (May 1991).

\* cited by examiner

Apr. 17, 2018

. (2)

FIG. 2

FIG. 3

FIG. 5

FIG. 6

FIG. 7A

FIG. 7B

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 16

# JOINT REWRITING AND ERROR CORRECTION IN WRITE-ONCE MEMORIES

## CROSS-REFERENCE TO RELATED APPLICATIONS

This Application is the U.S. National Stage filing under 35 U.S.C. § 371 of International Application No. PCT/US/13/49480, filed on Jul. 5, 2013, which claims the benefit under 35 U.S.C. § 119(e) of U.S. Provisional Application No. 61/756,324, filed on Jan. 24, 2013. The International Application and the U.S. Provisional Application are herein incorporated by reference in their entireties.

#### STATEMENT REGARDING GOVERNMENT SPONSORED RESEARCH AND DEVELOPMENT

The invention was made with government support under Grant No. CIF1218005 awarded by the National Science <sup>20</sup> Foundation. The government has certain rights in the invention.

#### TECHNICAL FIELD

The field generally relates to unidirectional or write only memories (WOM), which have cells which may be individually changed in a single direction, but are erased as a group, and more specifically but not exclusively to rewriting write only memories with error correction.

#### BACKGROUND

Unless otherwise indicated herein, the materials described in this section are not prior art to the claims in this application and are not admitted to be prior art by inclusion in this section.

Coding for rewriting is a technology used for flash memories. Coding has the potential to substantially increase the longevity, speed, and power efficiency of flash memo- 40 ries. Coding for rewriting has been proposed recently. See, e.g. V. Bohossian, A. Jiang, and J. Bruck, "Buffer coding for asymmetric multi-level memory," in Proc. IEEE Internatio. Nal Symposium on Information Theory, June 2007, pp. 1186-1190, and A. Jiang, V. Bohossian, and J. Bruck, 45 "Floating codes for joint information storage in write asymmetric memories," in Proc. IEEE International Symposium on Information Theory, June 2007, pp. 1166-1170, which are incorporated herein by reference. Since the time coding was initially proposed, many works have appeared in this area. 50 See, e.g. Y. Wu, "Low complexity codes for writing a write-once memory twice," in Proc. IEEE International Symposium on Information Theory, June 2010, pp. 1928-1932, Y. Wu and A. Jiang, "Position modulation code for rewriting write-once memories," IEEE Trans. Inf. Theor., 55 vol. 57, no. 6, pp. 3692-3697, June 2011, E. Yaakobi, S. Kayser, P. H. Siegel, A. Vardy, and J. K. Wolf, "Codes for write-once memories," IEEE Trans. Inf. Theor., vol. 58, no. 9, pp. 5985-5999, September 2012, and E. Yaakobi, S. Kayser, P. Siegel, A. Vardy, and J. Wolf, "Efficient two-write 60 wom-codes," in Proc. IEEE Information Theory Workshop, September 2010, pp. 1-5, which are incorporated herein by reference.

A model for rewriting is a write-once memory (WOM) model. See. e.g. R. L. Rivest and A. Shamir, "How to reuse 65 a write-once memory," *Information and Control*, vol. 55, no. 1-3, pp. 1-19, 1982, which is incorporated herein by refer-

2

ence. In the WOM model, a set of binary cells are used to store data, and the cell charge levels are increased when the data are rewritten. For flash memories, this constraint implies that the rewriting operation may delay the expensive block erasure, which leads to better preservation of cell quality and higher writing performance.

There have been many techniques for the design of WOM codes. They include linear code, tabular code, codes based on projective geometry, coset coding, etc. See, e.g. G. Cohen, P. Godlewski, and F. Merkx, "Linear binary code for write-once memories," IEEE Trans. Inf. Theor., vol. 32, no. 5, pp. 697-700, September 1986, Merkx, "Womcodes constructed with projective geometries" Traitement du Signal, vol. 1, no. 2-2, pp. 227-231, 1984, and R. L. Rivest and A. 15 Shamir, "How to reuse a write-once memory," Information and Control, vol. 55, no. 1-3, pp. 1-19, 1982, which are incorporated herein by reference. Codes with substantially higher rates were discovered in recent years. See, e.g. V. Bohossian, A. Jiang, and J. Bruck, "Buffer coding for asymmetric multi-level memory," in Proc. IEEE International Symposium on Information Theory, June 2007, pp. 1186-1190, and A. Jiang, V. Bohossian, and J. Bruck, "Floating codes for joint information storage in write asymmetric memories," in Proc. IEEE International Symposium on Information Theory, June 2007, pp. 1166-1170, which are incorporated herein by references. Since the time such coding was initially proposed, many works have appeared in this area. See, e.g. Y. Wu, "Low complexity codes for writing a write-once memory twice," in Proc. IEEE International Symposium on Information Theory, June 2010, pp. 1928-1 2, E. Yaakobi, S. Kayser, P. H. Siegel, A. Vardy, and J. K. Wolf, "Codes for write-once memories," *IEEE Trans*. Inf. Theor., vol. 58, no. 9, pp. 5985-5999, September 2012, which are incorporated herein by reference. In 2012, WOM codes that achieved capacity were discovered by Shpilka et al. and Burshtein et al. See, e.g. A. Shpilka, "Capacity achieving multiwrite wom codes," CoRR, vol. abs/ 1207.1128, 2012, "Capacity achieving two-write wom codes," in LATIN 2012: Theoretical Informatics, ser. Lecture Notes in Computer Science, vol. 7256. Springer Berlin Heidelberg, 2012, pp. 631-642, E. Yaakobi and A. Shpilka, "High sum-rate three-write and non-binary wom codes," in Proc. IEEE International Symposium on Information Theory, July 2012, pp. 1386-1390, and D. Burshtein and A. Strugatski, "Polar write once memory codes," in Proc. IEEE International Symposium on Information Theory, July 2012, pp. 1972-1976, which are incorporated herein by reference. The latter code used a construction based on polar coding.

Compared to the large amount of work on WOM codes, the work on WOM codes that also correct errors has been much more limited. Existing works are mainly on correcting a few errors (for example, 1, 2, or 3 errors). See, e.g. E. Yaakobi, P. Siegel, A. Vardy, and J. Wolf, "Multiple error-correcting wom-codes," *IEEE Trans. Inf. Theor.*, vol. 58, no. 4, pp. 2220-2230, April 2012, and G. Zemor and G. D. Cohen, "Error-correcting wom-codes," *IEEE Trans. Inf. Theor.*, vol. 37, no. 3, pp. 730-734, May 1991, which are incorporated herein by reference.

#### SUMMARY

Coding schemes that combine rewriting with error correction are discussed. In some embodiments, the schemes may support any number of rewrites and can correct a substantial number of errors. The code construction may use polar coding. In some embodiments, an analytical technique may be used which is based on frozen sets corresponding to

the WOM channel and the error channel, respectively, including their common degrading and common upgrading channels. In some embodiments, lower bounds to the sumrate may be achieved. The actual sum-rates may be further computed for various parameters. The analytical technique may focus on the binary symmetric channel (BSC). In practice, for relatively small error probabilities, the frozen set for BSC may be often contained in the frozen set for the WOM channel, which enables some embodiments to have a nested structure. The coding scheme can be further extended to multi-level cells (MLC) and more general noise models.

One aspect is a method of rewriting a memory. The method includes determining a current cell charge level of each of a plurality of cells of the memory, and generating a plurality of next cell charge levels according to a linear transformation, where each next cell charge level is generated based on a corresponding one of the current cell charge levels and based on input data. Each next cell charge level is greater than or equal to the corresponding current cell charge level, the plurality of next cell charge levels represent the input data, and the plurality of next cell charge levels include redundancy for error correction. The method also includes storing the next cell charge levels in the memory.

Another aspect is a method of reading a memory. The method includes determining current cell charge levels of a plurality of cells of the memory, where the current cell charge levels represent data and error correction information. The method also includes generating a plurality of data values, where the data values are generated based on a linear transformation of the current cell charge levels, and transmitting the data values to a data destination.

Another aspect is a memory system. The system includes a memory that includes a plurality of cells, a processor coupled to the memory and configured to determine current cell charge levels of the plurality of cells of the memory, and an encoder coupled to the memory and to the processor, and configured to generate a plurality of next cell charge levels according to a linear transformation, where each next cell charge level is generated based on a corresponding one of the current cell charge levels and based on input data. Each next cell charge level is greater than or equal to the corresponding previous cell charge level, the plurality of next cell charge levels represent the input data, and the plurality of next cell charge levels include redundancy for error correction. The system also includes a write device, configured to store the next cell charge levels in the memory.

Another aspect is a memory system. The system includes 45 a memory that includes a plurality of cells, a processor coupled to the memory and configured to determine current cell charge levels of the plurality of cells of the memory, where the current cell charge levels represent data and error correction information. The system also includes a decoder coupled to the processor and to the memory, and configured to generate a plurality of data values, where the data values are generated based on a linear transformation of the current cell charge levels. The system also includes a transmitter coupled the decoder and configured to transmit the data 55 values to a data destination.

The foregoing summary is illustrative and is not intended to be in any way limiting. In addition to the illustrative aspects, embodiments, and features described above, further aspects, embodiments, and features will become apparent by reference to the drawings and the following detailed description.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing and other features of this disclosure will become more fully apparent from the following description

4

and appended claims, taken in conjunction with the accompanying drawings. Understanding that these drawings depict only several embodiments in accordance with the disclosure and are, therefore, not to be considered limiting of its scope, the disclosure will be described with additional specificity and detail through use of the accompanying drawings, in which:

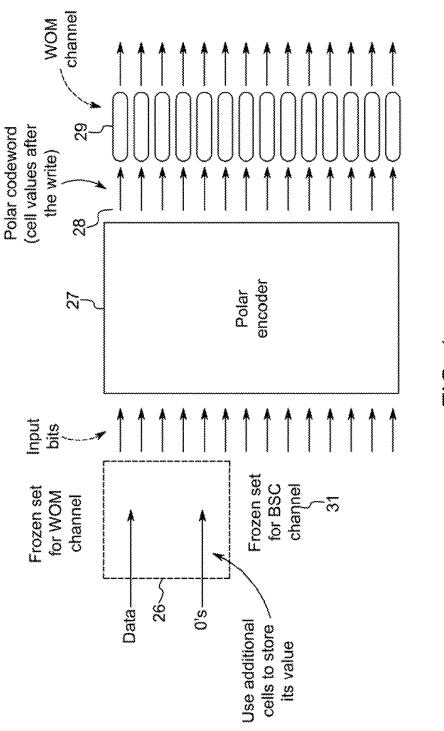

FIG. 1 is a block diagram illustrating an example write process.

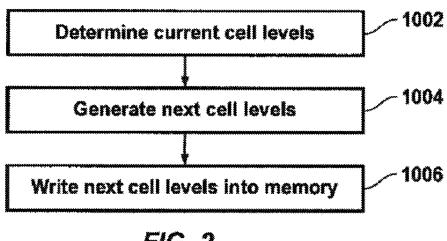

FIG. 2 is a flow diagram that shows example operations performed by a device for encoding a data value in a WOM rewrite process.

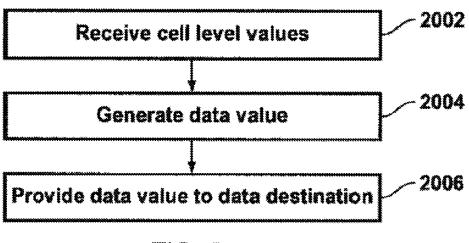

FIG. 3 is a flow diagram that shows example operations performed by a device for decoding a cell charge level value in a WOM read process.

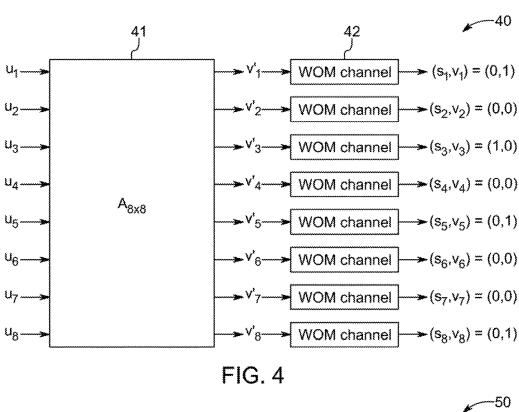

FIG. 4 is a block diagram that shows an example device for encoding a cell charge level value in a WOM rewrite process.

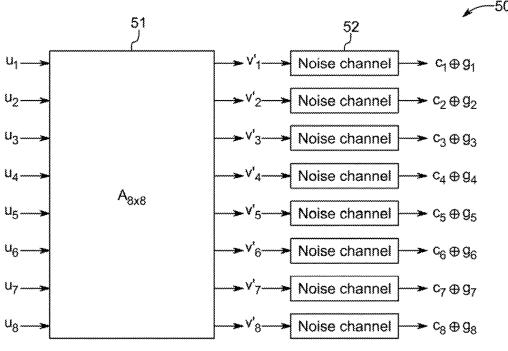

FIG. 5 is a block diagram that shows an example device for decoding a cell charge level value in a WOM read process.

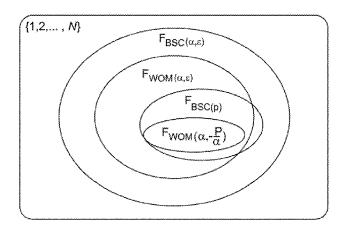

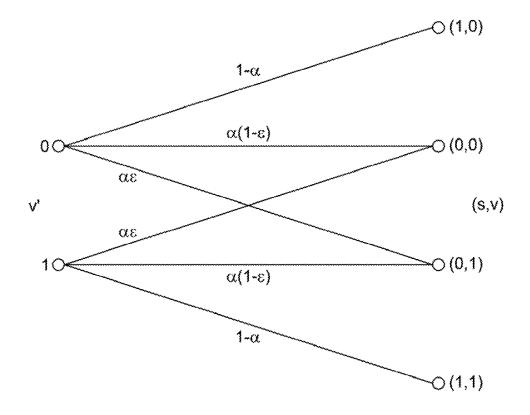

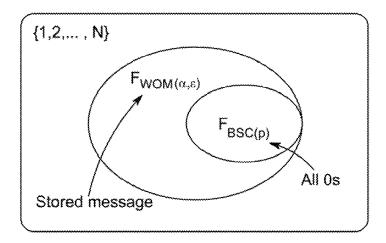

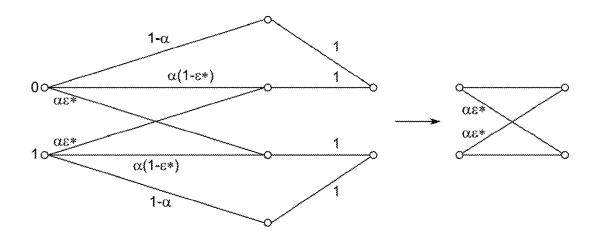

FIG. **6** illustrates an example WOM channel WOM  $(\alpha, \epsilon)$ . FIG. **7** illustrates examples of: (a) Nested code for  $F_{BSC(p)} \subseteq F_{WOM(\alpha, \epsilon)}$ , (b) General code.

FIG. 8 illustrates an example of: Degrading the channel WOM( $\alpha$ , $\epsilon$ \*) to BSC( $\alpha\epsilon$ \*). The two channels on the left and on the right may be equivalent.

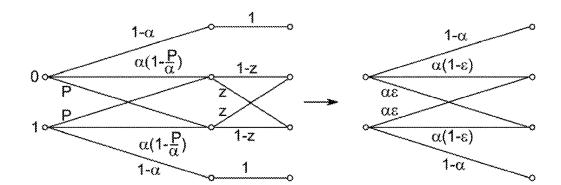

FIG. illustrates an example of: Degrading channel

$$WOM(\alpha, \frac{p}{\alpha})$$

to WOM( $\alpha,\epsilon$ ). Here

$$z = \frac{\alpha \varepsilon - p}{\alpha - 2p}$$

The two channels on the left and on the right may be equivalent.

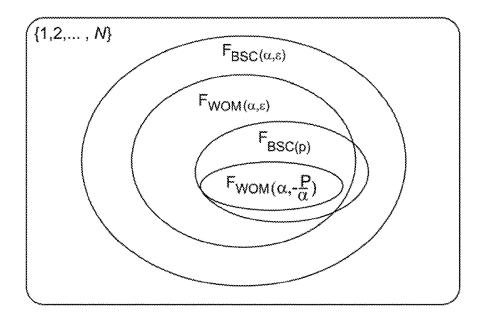

FIG. 10 illustrates an example of: The frozen sets for channels BSC(p),  $WOM(\alpha, \epsilon)$ ,

$$WOM\left(\alpha, \frac{p}{\alpha}\right)$$

and BSC( $\alpha \epsilon$ ). Here  $p \le \alpha \epsilon$ .

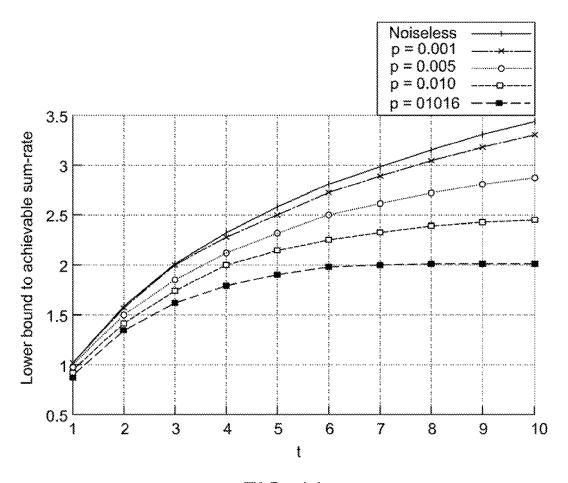

FIG. 11 is a graph illustrating an example of: Lower bound to achievable sum-rates for different error probability p.

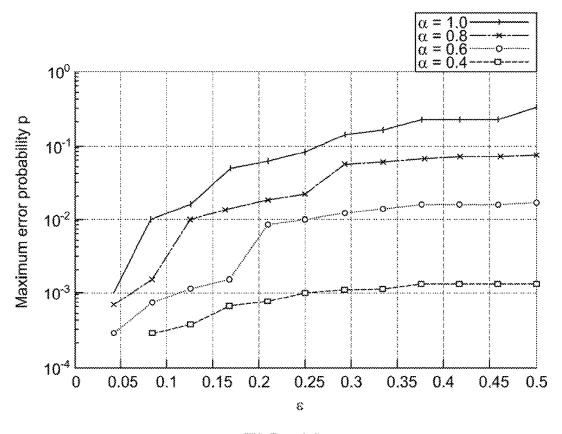

FIG. 12 is a graph illustrating an example of: The maximum value of p found for which  $F_{BSC(p)} \subseteq F_{WOM(\alpha,\epsilon)}$ .

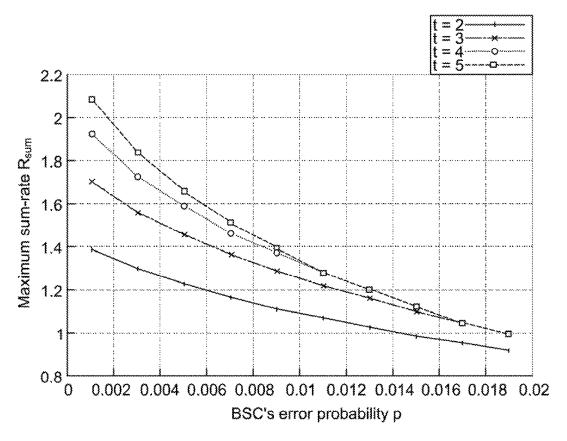

FIG. 13 is a graph illustrating an example of: Sum-rates for different t obtained in experimental search using code length N=8192, when  $F_{BSC(p)} \subseteq F_{WOM(\alpha, \epsilon)}$ .

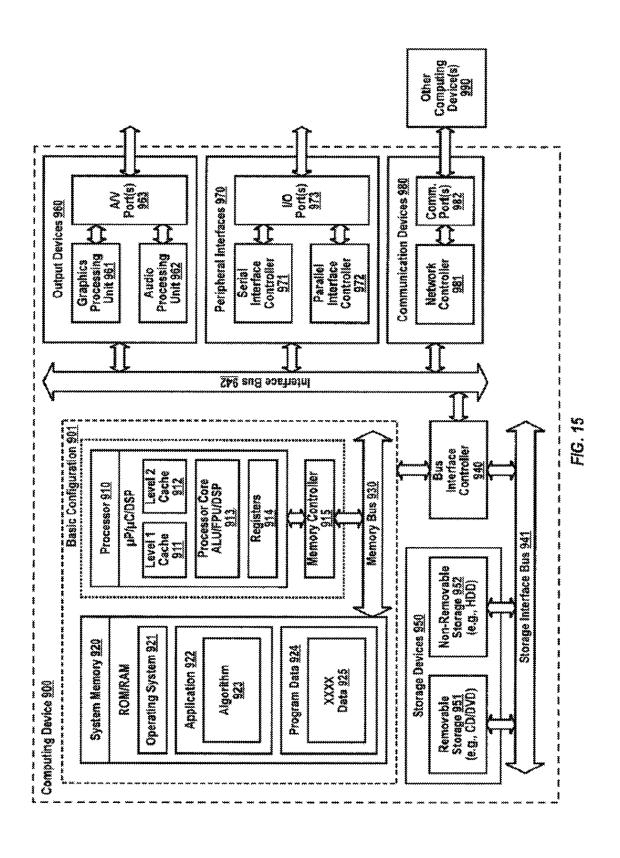

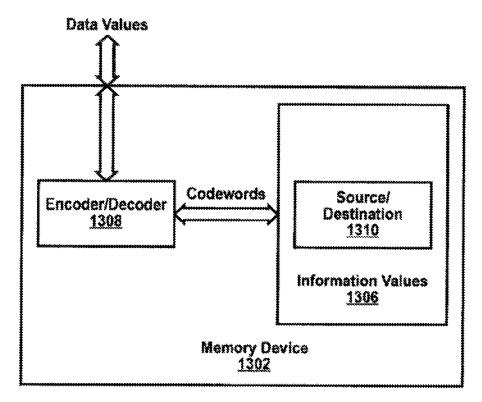

FIG. 14 is an illustration of an example memory device. FIG. 15 is a block diagram of an example computing device for communicating or otherwise operating with a memory device such as depicted in FIG. 14.

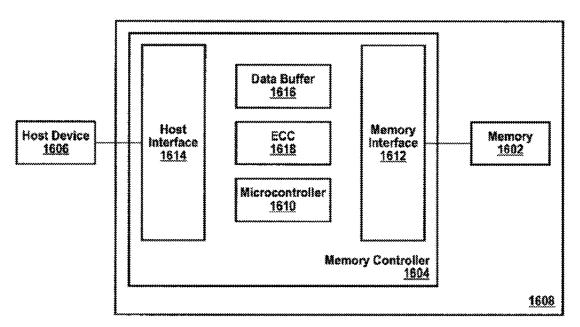

FIG. 16 is a block diagram that illustrates an example data flow in a system that operates according to aspects discussed herein.

All of the aspects and other features shown in the drawings are arranged according to at least some embodiments presented herein.

#### DETAILED DESCRIPTION

In the following detailed description, reference is made to the accompanying drawings, which form a part hereof. In the drawings, similar symbols typically identify similar components, unless context dictates otherwise. The illustrative embodiments described in the detailed description, drawings, and claims are not meant to be limiting. Other embodiments may be utilized, and other changes may be made, without departing from the spirit or scope of the subject matter presented herein. The aspects of the present disclosure, as generally described herein, and illustrated in the Figures, can be arranged, substituted, combined, separated, and designed in a wide variety of different configurations, all of which are explicitly contemplated herein.

This disclosure is generally drawn, inter alia, to methods, apparatus, systems, devices, and computer program products related to joint rewriting and error correction in write-once memories.

Briefly stated, both rewriting and error correction are 25 technologies that may be used for non-volatile memories, such as flash memories. This disclosure presents a coding scheme that combines rewriting and error correction for the write-once memory model. In some embodiments, code construction is based on polar codes, and supports any 30 number of rewrites and corrects a substantial number of errors. The code may be analyzed for a binary symmetric channel. The results can be extended to multi-level cells and more general noise models.

#### I. Introduction

This disclosure presents a code construction for error-correcting WOM codes. The code construction scheme may support any number of rewrites and can correct a substantial 40 number of errors.

For example, a memory may have N binary cells, where every cell has two charge levels: 0 and 1. The cell-programming method can only change a cell from 0 to 1, but not from 1 to 0. However, noise can change a cell in both 45 directions: from 0 to 1, and from 1 to 0.

The coding for the cell programming has two functions: (1) Rewrite data, which means to store new data that replace old data, and (2) Correct errors. In some embodiments, a coding method may support t writes, where each write is 50 also called a rewrite, and where t is an integer parameter greater than or equal to two.

After a write of data, noise may appear in the cell levels, and certain embodiments of cell programming can correct errors and recover the data stored by the latest write. In some 55 embodiments, each of the writes may use substantially the same process.

As an example, let  $(s1, s2, \ldots, sN)$  be a binary vector that represent the levels of the N binary cells before a write. Let  $(s'1, s'2, \ldots, s'N)$  be a binary vector that represent cell levels 60 of the N binary cells after this write. In addition, let  $(b1, b2, \ldots, bM)$  be a binary vector that represents the data to be written, where the data has M bits. Note the following constraints or conditions:

For i=1, 2, ..., N, s'i is greater than or equal to si. This 65 is because the cell-programming method increases a cell's level, but may not decrease it.

6

- 2) M is an integer parameter known to the system. Its value can be the same or different for the writes.

- 3) The cell levels (s1, s2, ..., sN) can be different from the cell levels right after the previous rewrite, because noise may have changed the cell levels since the previous rewrite.

To write the data (b1, b2,  $\dots$ , bM), the method may have the following inputs:

- (1) The current cell levels (s1, s2, ..., sN), and

- (2) The new data to store  $(b1, b2, \ldots, bM)$ .

Based on the inputs from (1) and (2), the method computes the output  $(s'1, s'2, \ldots, s'N)$ , and programs the cells to the new levels with the following constraints:

- 1) For i=1, 2, ..., N, s'i is greater than or equal to si.

- 2) The new cell levels (s'1, s'2, ..., siN) represents the new data (b1, b2, ..., bM), according to the mapping specified by the method.

FIG. 1 is a block diagram illustrating an example write process in accordance with some embodiments. The write process of FIG. 1 includes error correction, for example, as described above. Data to be stored in the memory is included with the frozen set for WOM channel 26, and is provided to the polar encoder 27. The polar encoder 27 generates a polar codeword 28, which is provided to a set of WOM channel device 29. The WOM channel devices 29 determine cell levels to be written into the WOM.

Data to be stored in the memory is included with the frozen set for WOM channel 26, and data of the frozen set for WOM channel 26 is provided to the polar encoder 27. In addition, additional data 31 is provided to the polar encoder 27. In the embodiment of FIG. 1, the additional data 31 is a frozen set for a binary symmetric channel (BSC) channel. The polar encoder 27 generates the polar codeword 28 based on the data of the frozen set for WOM channel 26 and the 35 additional data 31 of the frozen set for the BSC channel. The additional data 31 allows for the polar encoder 27 to generate a polar codeword 28 which includes data for error correction. The poplar encoder 27 generates the polar codeword 28 according to embodiments and example features of encoding schemes discussed in further detail below. As discussed below, the encoding schemes allow for the WOM to be written with error correction.

The polar codeword **28** is provided to a set of WOM channel devices **29**, which determine cell levels to be written into the WOM. The WOM channel devices **29** determine the cell levels such that the new state of the WOM includes the data of the frozen set and such that the only cell level changes in the WOM are from the 0 state to the 1 state. Embodiments of WOM channel devices are described below in further detail.

FIG. 2 is a flow diagram that shows example operations of a method that may be performed by a device for encoding a data value to be encoded into a codeword for rewriting the WOM in accordance with some embodiments. The device may comprise an external data storage device such as a flash memory device that receives data from a host device, such as a computer, and stores the data in accordance with error correction encoding schemes discussed below. For example, the device may comprise an encoder for the purpose of processing data values and producing corresponding codewords.

The method of FIG. 2 may include one or more operations, functions, or actions as illustrated by one or more of blocks 1002, 1004, and/or 1006. Although the blocks are illustrated in a sequential order, these blocks may also be performed in parallel, and/or in a different order than those described herein. Also, the various blocks may be combined

into fewer blocks, divided into additional blocks, and/or eliminated based upon the particular implementation. Additional blocks may be provided that represent other operations, functions, or actions.

The method shown in FIG. 2 may begin in block 1002 5 "determine current cell levels." Block 1002 may be followed by block 1004 "generate next cell levels," and block 1004 may be followed by block 1006 "write next cell levels into memory."

In the first operation, represented by the flow diagram 10 block 1002, current cell charge levels are determined. As discussed above, writing data into memory causes cell levels to change unidirectionally, for example, 0 to 1, but not 1 to 0. Accordingly, to determine which memory cells to change from 0 to 1, the current cell levels are determined.

In the next encoding operation, indicated by block 1004, next cell charge levels are generated based on the data to be written and on the current cell levels. Examples of techniques for determining next cell levels are discussed in further detail below. At block 1006, the next cell charge 20 levels are written into the memory. For example, the next cell levels may be stored into memory cells of a data device, or maybe provided to a memory of a host device, or may be transmitted to an external destination.

As a result, the rewriting method enable new data to be 25 stored in cells (to replace old data) two or more times without decreasing cell levels. In addition, an error correction method enables the most recently written data to be recovered even though noise may have changed the levels of some of the cells.

In particular, the rewriting operation takes the current cell levels  $(s1,\ldots,sN)$  and the new data  $(b1,\ldots,bM)$  as input, and computes new cell levels  $(s'1,\ldots,s'N)$ , where For  $i=1,\ldots,N$ , s'i is greater than or equal to si. In addition, the new cell-level vector  $(s'1,\ldots,s'N)$  represents the new data 35  $(b1,b2,\ldots,bM)$ , according to the mapping specified by the method. Accordingly, given the new cell levels  $(s'1,\ldots,s'N)$ , the decoding algorithm can uniquely determine the value of the new data  $(b1,\ldots,bM)$ .)

In some embodiments, to generate the next cell levels 40 such as in block **1004**, the method may use a binary matrix  $A_{N\times N}=(a_{i,j})_{N\times N}$  of N rows and N columns, whose value is fixed and known to the system. For example, for  $i=1,\ldots,N$  and  $j=1,\ldots,N$ ,  $a_{i,j}\in\{0,1\}$  is the bit in the i-th row and j-th column of the matrix  $A_{N\times N}$ . Furthermore, the method 45 may use a subset of  $\{1,2,\ldots,N\}$  denoted by FWOM, and another subset of  $\{1,2,\ldots,N\}$  denoted by FC to generate the next cell levels, such that:

FC contains at least one element. That is, |FC| is greater than or equal to 1,

There are M elements in FWOM but not in FC, that is, |FWOM-FC|=M,

At least one element of  $\{1,2,\ldots,N\}$  is neither in FWOM nor in FC. That is,  $|\{1,2,\ldots,N\}$ -FWOM-FC| is greater than or equal to 1.

FC is a subset of FWOM. That is, FC∈FWOM.

Furthermore, in some embodiments, to generate the next cell levels, the method may use a binary vector (g1, g2, :::, gN) called a dither, whose value is known to the system. The value of the dither can be the same or different for each of the rewrites. Two other binary vectors (v1, v2, ..., vN) and (v'1, v'2, ..., v'N) may be determined as follows:

For  $i=1,\ldots,N$ ,  $vi=si \oplus gi$  is called the value of the i-th cell before the write. Here  $\oplus$  is the exclusive-OR operation. 65 For  $i=1,\ldots,N$ ,  $v'i=s'i \oplus gi$  is called the value of the i-th cell after the write.

Furthermore, let  $A^{-1}_{N \times N}$  be the inverse of the matrix  $A_{N \times N}$ , and let  $(u1, u2, \ldots, uN)$  be the binary vector  $(u1, u2, \ldots, uN) = (v'1, v'2, \ldots, v'N) \ A^{-1}_{N \times N}$ . In addition, the vector  $(u1, u2, \ldots, uN)$  may have the following properties:

The value of the bits  $\{u_i | 1 \le i \le N, i \in F_{WOM} - F_C\}$ —namely those bits in  $(u1, \ldots, uN)$  whose indices are in FWOM FC—equals the value of the data (b1, .bM).

The value of the bits  $\{u_i | i \in F_C\}$  is a constant (such as all 0s or any other fixed value) known to the system.

The value of the bits {u,|1≤i≤N, i≠FWOM-FC} is computed by the method for rewriting.

In some embodiments, the number of cells whose levels are change from 0 to 1 by the rewriting method is minimized or otherwise reduced. Accordingly, the method may minimize or otherwise reduce the value of  $\Sigma_{i=1}^{N} s'_{i}$ - $s_{i}$ .

In some embodiments, the method may use the following  $1^{st}$  probabilistic model to describe the relationship between cell levels  $(s1, \ldots, sN)$  and  $(s'1, \ldots s'N)$ . Let

$$\alpha = 1 - \sum_{i=1}^{N} \frac{S_i}{N},$$

and let  $\epsilon \in [0, 1]$  be a real-number parameter whose value is known to the system. For  $i=1, \ldots, N$ ,

$$\begin{split} & Pr\{S_i = 0 \mid s_i' = 0\} = 1, \text{ and} \\ & Pr\{S_i = 1 \mid \hat{S}_i = 0\} = 0. \\ & Pr\{s_i = 0 \mid s_i' = 1\} = \frac{\alpha \varepsilon}{\alpha \varepsilon + 1 - \alpha} \text{ , and} \\ & Pr\{s = 1 \mid s_i' = 1\} = \frac{1 - \alpha}{\alpha \varepsilon + 1 - \alpha}. \end{split}$$

In some embodiments, the method may use the new cell levels (s'1, . . . , s'N) as the vector that maximizes or otherwise increases the value  $\Pr\{(s'1, \ldots, s'N) | (s1, \ldots, sN)\}$ .

In some embodiments, the method may choose the new cell levels  $(s'1, \ldots, s'N)$  as the vector that maximizes or otherwise increases the value  $\Pr\{(s1, \ldots, sN) | (s'1, \ldots, s'N)\}$ .

In some embodiments, to generate the next cell levels, the method may compute the value of bits u1, u2, . . . , uN sequentially, and subsequently computes the value of 50 cell levels (s'1, . . . , s'N) as (s'1, . . . , s'N)=(v'1, . . . , v'N)  $\oplus$ (g1, . . . , gN)=(u2, . . . , uN)·A $^{-1}_{N \times N} \oplus$ (g1, . . . , gN). For i=1, . . . , N, the method computes the following:

1: If  $\mathbf{i} \in F_{WOM}$ - $F_C$  and  $\mathbf{i}$  is the j-th element in  $F_{WOM}$ - $F_C$  (for  $\mathbf{j} \in \{1, 2, \ldots, M\}$ ), let  $\mathbf{u}_i = \mathbf{b}_j$  (the j-th bit in the new data). Otherwise, go to step 2.

2. If  $i \in F_C$ , let  $\mu_i$  be the constant value specified previously (such as the value 0). Otherwise, go to step 3.

3. If  $i \in \{1, 2, \ldots, N\}$ – $F_{WOM}$ , let  $\mu_i$  take the value that maximizes the value of  $\Pr\{v_2 | (v_1, v_1), \ldots, (s_N, v_N), \mu_1, \ldots, \mu_{i-1}\}$  assuming that each of  $\mu_{i+1}, \ldots, \mu_N$  is equally likely to be 0 and 1.

In some embodiments, the method may use the following  $2^{nd}$  probabilistic model to describe the relationship between vectors  $(v^i\mathbf{1},\ldots,v^iN)$  and  $((s\mathbf{1},v\mathbf{1}),\ldots,(sn,vn))$ . For  $I=1,\ldots,N$ .

$$\begin{array}{l} \Pr((s_i, v_i) = (1,0) | v'_i = 0) = 1 - \alpha, \ \Pr((s_i, v_i) = (0,0) | v'_i = 0) = \alpha(1 - \epsilon), \\ \Pr((s_i, v_i) = (0,1) | v'_i = 0) = \alpha \epsilon, \ \Pr((s_i, v_i) = (1,1) | v'_i = 0) = 0, \end{array}$$

$\Pr((s_i, \ v_i) = (1,0) | v_i' = 1) = 0, \ \Pr((s_i, \ v_i) = (0,0) | v_i' = 1) = \alpha \epsilon, \ \Pr(s_i, \ v_i') = (0,0) | v_i' = 1) = \alpha \epsilon, \ \Pr(s_i, \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = (0,0) | v_i' = 1 = \alpha \epsilon, \ \Pr(s_i', \ v_i') = \alpha \epsilon, \ \Pr(s_i', \ v_i$  $v_i$ )=(0,1)| $v_i$ =1= $\alpha$ (1- $\epsilon$ ),  $Pr((s_i, v_i)$ =(1,1)| $v_i$ =1)=1- $\alpha$ .

In some embodiments, the method may choose the new cell levels (s'1, ..., s'N) as the vector that maximizes or otherwise increases the value  $Pr\{(s'1, \ldots, s'N) | (s1, \ldots, s'N) | (s'1, \ldots, s'N) \}$ sN).

In some embodiments, the method may choose the new cell levels (s'1, . . . , s'N) as the vector that maximizes or otherwise increases the value  $Pr\{(s1, \ldots, sN) | (s'1, \ldots, s'N) \}$ s'N).

In some embodiments, the method may compute the value of bits u1, u2, . . . , uN sequentially, and subsequently computes the value of levels  $(s'1, \ldots, s'N)$  as  $(s'1, \ldots, s'N)$  $s'N = (v'1, \ldots, v'N) \oplus (g1, \ldots, gN) = (u2, \ldots, uN)$  $A^{-1}_{N \times N} \oplus \oplus (g1, \dots, gN)$ . For  $i=1, \dots, N$  the method may compute the following:

1: If  $i \in F_{WOM} - F_C$  and i is the j-th element in  $F_{WOM} - F_C$  (for  $j \in \{1, 2, ..., M\}$ ), let  $u_i = b_j$  (the j-th bit in the new data). Otherwise, go to step 2.

2: If  $i \in F_C$ , let  $u_t$  be the constant value specified previously (such as the value 0. Otherwise, go to step 3.

3: If  $i \in \{1, 2, ..., N\} - F_{WOM}$ , let  $\mu_i$  take the value that maximizes the value of  $\Pr\{\overline{\mu_i}|(s_1, \nu_1), \ldots, (s_N, \nu_N),$  $\mu_1, \ldots, \mu_{i-1}$  assuming that each of  $\mu_{i+1}, \ldots, \mu_N$  is equally likely to be 0 and 1.

In some embodiments, the matrix  $A_{N \times N}$ , may be specified  $_{25}$ as follows. Let m be a positive integer, and let  $N=2^m$ , Let

$$G2 = \begin{pmatrix} 1 & 0 \\ 1 & 1 \end{pmatrix}$$

and let  $A_{N \times N} = G_2^{\oplus m}$  be the m-th Krobecker product of  $G_2$ . In some embodiments, the dither may be a pseudorandom number, which can be generated by a pseudorandom-number generator using a seed number as input. The 35 seed number may be stored in the system.

In some embodiments, the method may compute the value of bits u1, u2, . . . , uN sequentially, and subsequently computes the value of cell levels (s'1, . . . , s'N) as  $(s'1, \dots, s'N) \ 1, \dots, \ v'N) \!\! \oplus \!\! (g1, \dots, \ gN) \!\! = \!\! (u2, \dots, \ 40)$ uN)  $A^{-1}_{N\times N}$   $\bigoplus$   $(g1, \ldots, gN)$ . For  $i=1, \ldots, N$ , the method may compute the following:

Step 1: Let  $y=(y_1, y_2, \dots, y_N)=((s_1, v_1), (s_2, v_2, \dots, (s_N, v_N)))$  $v_N$ )) be a vector of N elements, where every element  $y_i = (s_i, v_i)$  is a pair of bits.

Step 2: Let  $J=(j_1, j_2), \ldots, j_M)=F_{WOM}-F_C$  where  $j_1 < j_2 < j_3 < j_4 < j_4 < j_5 < j_6 < j_6 < j_6 < j_7 < j_8 < j_8 < j_9 < j_9$  $j_2 < \ldots < j_m$ . Let  $u_{F_{WOM-FC}} = (u_{j1}, u_{j2}, \ldots, u_{jM})$ . For  $I=1, \ldots, M$ , let  $u_{ji} = b_i$ .

Step 3: For every  $i \in F_C$ , let  $u_i = 0$ . Step 4: Compute the values of  $W_N^i(y, (u_1, u_2, \dots, 50))$

$|u_{i-1}||u_{i-1}||u_{i}=0$ ) and  $W_N^{i}(y, (u_{j1}, u_{j2}, \dots, u_{i-1}||u_{i}=1))$  for  $i=1, 2, \ldots, N$  as follows:

Depending on the parity of i, the value of  $W_N^{\ i}$  is recursively evaluated through one of the formulae below (beginning with n=N/2):

$$W_{2n}^{2i-1} \left( (y_1, y_2, \dots, y_{2n}), \right.$$

$$(u_1, u_2, \dots, u_{2i-2}) | u_{2i-1}) \sum_{u_{2i} \in (0,1)} \frac{1}{2} W_n^i ((y_1, y_2, \dots, y_n), \right.$$

$$(u_1, u_3, u_5, \dots, u_{2i-3}) \ominus (u_2, u_4, u_6, \dots, u_{2i-2}) | u_{2i-1} \ominus u_{2i} \right)$$

$$\begin{aligned} W_n^i((y_{n+1}, y_{n+2}, \dots, y_{2n}), & (u_2, u_4, u_6, \dots, u_{2i-2})|u_{2i}), \\ W_{2n}^{2i}((y_1, y_2, \dots, y_{2n}), & (u_1, u_2, \dots, u_{2i-1})|u_{2i}) = \\ & \frac{1}{2} W_n^i((y_1, y_2, \dots, y_n), \\ & (u_1, u_3, u_5, \dots, u_{2i-3}) \oplus (u_2, u_4, u_6, \dots, u_{2i-2})|u_{2i-1} \oplus u_{2i}) \end{aligned}$$

$W_n^i((y_{n+1}, y_{n+2}, \dots, y_{2n}), (u_2, u_4, u_6, \dots, u_{2i-2})|u_{2i})$

10 with the base cases

$$W_1^{-1}((1,0),(*)|0)=1-\alpha$$

$$W_1^{-1}((0,0),(*)|0)=\alpha(1-\epsilon)$$

$$W_1^{-1}((0,1),(*)|0)=\alpha\epsilon$$

$$W_1^{-1}((1,1),(*)|0)=0$$

$$W_1^{-1}((1,0),(*)|1)=0$$

$$W_1^{-1}((0,0),(*)|1)=\alpha\epsilon$$

$$W_1^{-1}((0,1),(*)|1) = \alpha(1-\epsilon)$$

$$W_1^{-1}((1,1),(*)|1)=1-\alpha.$$

(3)

where (\*) denotes an empty vector. The operator (1) between two binary vectors denotes the element-wise exclusive-OR computation. The operator ⊖ between two bits denotes the binary exclusive-OR computation.

Step 5: For i=1, 2, . . . , N, if  $i \notin F_{WOM}$ , then do the

Step 5.1: Let  $L_N^i$  (y,  $(u_1, u_2, \ldots, u_{i-1})$ ) take the value  $W_N^i(y, (u_1, u_2, \dots, u_{i-1})|u_i=0)/W_N^i(y, (u_1, u_2, \dots, u_{i-1})|u_i=0)$  $u_{i-1}$ ) $|u_i=1$ ).

Step 5.2: Let u, take the value 0 with probability

$$\frac{L_N^i(y, (u_1, u_2, \dots, u_{i-1}))}{1 + L_N^i(y, (u_1, u_2, \dots, u_{i-1}))}$$

and take the value 1 probability

$$\frac{1}{1 + L_N^i(y, (u_1, u_1, \dots, u_{i-1}))}.$$

55

Step 6: Let  $(v'_1, v'_2, \dots, v'_N) = (u_1, u_2, \dots, u_N) A_{N \times N};$ Step 7: Let  $(s'_1, s'_2, \dots, s'_N) = (v'_1 \oplus g_1, v'_2 \oplus g_2, \dots,$

Step 8: Check if  $s'_1 \ge s_i$  for  $i=1, \ldots, N$ . If yes, store the seed number used to generate the dither  $(g_1, \ldots, g_N)$  in the system, and let  $(s'_1, \ldots, s'_N)$  be the new cell levels; otherwise, use a new seed number to generate a new value for the dither  $(g_1, \ldots, g_N)$ , and return to Step 1 to repeat the computation.

In some embodiments, the matrix  $A_{N\times N}$  may be the generating matrix of a polar code, and FWOM may be 60 contained in the frozen set of the polar code corresponding to the channel described by the transition  $2^{nd}$  probabilistic model, where the channel has v'i as the channel input and (si, vi) as the channel output.

In some embodiments, FWOM may be determined as 65 follows:

For i=1, 2, , N, let z denote ((y1, y2, , yN), (u1, u2, , ui-1)), and compute a value

$$FER(W_N^i) = \sum_{z: W_N^i(z|0) < W_N^i(z|1)} W_N^i(z\mid 0) + \sum_{z: W_N^i(z|0) = W_N^i(z|1)} \frac{1}{2} W_N^i(z\mid 0).$$

Where  $W_N^i(z|0)$  and  $W_N^i(z|1)$  computed as discussed below. In addition, let  $\Delta R$  be a real number parameter greater than zero. Furthermore, let  $F_{WOM} = \{j_1, j_2, \ldots, j_{N(\alpha H(\epsilon) - \Delta R)}\}$  be a subset of  $\{1, 2, \ldots, N\}$  with cardinality  $N((\alpha H(\epsilon) - \Delta R),$  such that all values in  $\{FER(W_N^i)|i\in F_{WOM}\}$  are greater than or equal to each value in  $\{FER(W_N^i)|i\in \{1,\ldots,N\} - F_{WOM}\}$ .

In some embodiments, the matrix  $A_{N\times N}$  may be the generating matrix of a polar code.

After the rewrite described above, which changes cell levels to  $(s'1, s'2, \ldots, s'N)$  to store the data  $(b1, b2, \ldots, bM)$ , noise may appear in the cells and change the cell levels to  $(c1, c2, \ldots, CM)$ , where ci is a bit that is not necessarily equal to s'i. The error-correction method takes the noisy cell levels  $(c1, c2, \ldots, CM)$  as input, and outputs the stored data  $(b1, b2, \ldots, bM)$ .

FIG. 3 is a flow diagram that shows example operations of a method performed by a device for decoding cell level values received from the WOM to generate a data value as part of a read operation, in accordance with some embodiments. The device may comprise an external data storage device such as a flash memory device that receives data from a host device, such as a computer, and stores the data in accordance with an error correction encoding and decoding scheme schemes discussed below. For example, the device may comprise a decoder for the purpose of processing cell level values and producing corresponding data values.

The method of FIG. 3 may include one or more operations, functions, or actions as illustrated by one or more of blocks 2002, 2004, and/or 2006. Although the blocks are illustrated in a sequential order, these blocks may also be performed in parallel, and/or in a different order than those described herein. Also, the various blocks may be combined into fewer blocks, divided into additional blocks, and/or eliminated based upon the particular implementation. Additional blocks may be provided that represent other operations, functions, or actions.

The method shown in FIG. 3 may begin in block 2002 "receive cell level values." Block 2002 may be followed by 45 block 2004 "generate data value," and block 2004 may be followed by block 2006 "provide data value to data destination."

In the first operation, represented by the flow diagram block **2002**, a set of cell level values to be decoded is 50 retrieved from the WOM.

In the next decoding operation, indicated by block 2004, the set of values is decoded to generate the corresponding data value. Examples of techniques for decoding are discussed in further detail below. At block 2006, the data value 55 is provided to a data destination, such as a host computer. For example, the data value may be transmitted by a transmitter to the data destination.

In particular, to generate the data value, the decoding or error correction function may use a binary vector 60 (u'1, ..., 1'N) and has the following properties: Property 1: For any  $i \in F_C$ ,  $u'_i$  is given the fixed bit value that

has been assigned to  $u_i$  (which is know in the system). Property 2: Among all the values that satisfy Property 1, the value assigned to  $(u'_1, \ldots, u'_N)$  maximizes the probability that "the noise changed the codeword from  $(s'_1, \ldots, s'_N)=(u'_1, \ldots, u'_N)A_{N\times N} \oplus (g_1, \ldots, g_N)$  to  $(c_1, \ldots, c_N)$ ."

The probability may be determined by the errors' probabilistic characteristic. Accordingly, for every i∈FWOM−FC a data bit bj is recovered as u'i, where bj was assigned to ui for the most recent rewrite.

In some embodiments, to generate the data value, the method may use a binary matrix  $A_{N \times N} = (a_{i,j})_{N \times N}$  of N rows and N columns, whose value is fixed and known to the system. For example, for  $i=1,\ldots,N$  and  $j=1,\ldots,N$  a<sub>i,j</sub> $\in \{0,1\}$  is the bit in the i-th row and j-th column of the matrix  $A_{N \times N}$ . Furthermore, the method may use a subset of  $\{1,2,\ldots,N\}$  denoted by FWOM, and another subset of  $\{1,2,\ldots,N\}$  denoted by FC, such that:

FC contains at least one element. That is, |FC| is greater than or equal to 1,

There are M elements in FWOM but not in FC, that is, |FWOM-FC|=M,

At least one element of  $\{1, 2, ..., N\}$  is neither in FWOM nor in FC. That is,  $|\{1, 2, ..., N\}$ -FWOM-FC| is greater than or equal to 1.

FC is a subset of FWOM. That is, FC∈FWOM.

Furthermore, in some embodiments, the errors in the cells may have the following distribution:

Let  $p_0$  and  $p_1$  be two real-number parameters between 0 and 1. For  $i=1, \ldots, N$ , we have  $Pr\{c_i=0|s'_i=0\} \triangle Pr\{0|0\}=1-p_0$ ,  $Pr\{c_i=1|s'_i=0\} \triangle Pr\{1|0\}=p_0$ ,  $Pr\{c_i=0|s'_i=1\} \triangle Pr\{0|1\}=p_1$  and  $Pr\{c_i=1|s'_i=1\} \triangle Pr\{1|1\}=1-p_1$ .

In such embodiments, binary vector (( $u'1, \ldots, 1'N$ ) may have the following properties:

Property 1: For any  $i \in F_C$ ,  $u'_i$  is given the fixed bit value that has been assigned to  $u_i$  (which is know to the system). Property 2: Among all the values that satisfy Property 1, the value assigned to  $(u'_1, \ldots u'_N)$  maximizes the value of  $\Pi_{i=1}^N$   $\Pr\{c_i | \alpha_i\}$ , where  $\alpha_t$  denotes the ith bit in the vector  $(u'_1, \ldots u'_N)$   $A_{N \times N} \oplus (g_1, \ldots g_N)$ .

In some embodiments, the matrix  $A_{N \times N}$  may be the generating matrix of a polar code, and p is a real number parameter between zero and one. The method may correct errors and may recover the data values (b1, b2, ..., bM) as follows:

1: Recovering the value of  $(v_1, \ldots, v_N)$  using a decoding algorithm of an error-correcting polar code based on the following setting:

The polar code's generating matrix is  $A_{N\times N}$ .

The polar code encodes the user data  $(u_1,\ldots,u_N)$  into the codeword  $(v'_1,\ldots,v'_N)$  via the formula  $(v'_1,\ldots,v'_N)=(u_1,\ldots,u_N)A_{N\times N}$ .

For  $i=1, \ldots, N$ , the codeword bit  $v'_1$  is transmitted through a binary-symmetric channel with transition probability p; and the output of that binary-symmetric channel is the noisy codeword bit  $c_i$ .

The frozen set of the polar code corresponding to the binary-symmetric channel is contained in  $F_C$ ; and when encoding user data into the codeword, the user-data bits in  $F_C$  are fixed at known values (such as all 0's).

The decoding algorithm considers  $(c_1, \ldots, c_N)$  as the noisy codeword, and recovers the correct value of the original codeword  $(v'_1, \ldots, v'_N)$ .

2: Let  $(u_1, \ldots, u_N') = (v_1', \ldots, v_N') A_{N \times N}^{-1}$ . For every  $i \in F_{WOM} - F_C$ —say  $b_j$  was assigned to  $u_i$  for the most recent rewrite—we recover the data bit  $b_i$  as  $u_i'$ .

In some embodiments, to generate the data value, the decoding algorithm also may include computing the value of ui for  $i=1,\ldots,N$  as follows:

If  $i \in F_C$ , let  $u_i$  be the constant value that was assigned to it by the previous rewrite.

If  $i \not\in F_C$ , let  $u_i$  take the value that maximizes the value of  $\Pr\{u_i | c_1, \ldots, c_N, u_1, \ldots, u_{i-1}\}$  assuming that each of  $u_{i+1}, \ldots, u_N$  is equally likely to be 0 and 1.

In some embodiments, the decoding algorithm may be a list-decoding algorithm that is further specified as follows: Let L be a positive integer parameter that indicates the size of a list, where each element in the list is an assignment of value to  $(u1, u2, \ldots, ui-1)$  before the value of ui is computed. For  $i=1,\ldots,N$ , the decoding algorithm computes the value of ui with the following:

If  $i \in F_C$ , let  $u_i$  be constant value that was assigned to it by the previous rewrite.

If  $i \not\in F_C$ , for each element in the list (which is an assignment of value to  $(u_1, u_2, \ldots, u_{i-1})$ ), append to it the value assignment  $u_i = 0$ , and also append to it the value assignment  $u_i = 0$ , and also append to it the value assignment  $u_i = 1$ , thus converting that element into two new elements in the list. If the list now contains more than L elements, keep only the L elements that are most likely in the list. The likelihood of an element in the list may be computed as  $\Pr\{c_1, \ldots, c_N | u_1, \ldots, u_i\}$  assuming that each of  $u_{i+1}, \ldots, u_N$  is equally likely to be 0 and 1.

The most likely element in the list may then be chosen as the recovered value for  $(u1, \ldots, uN)$ .

In some embodiments, the stored data (b1,  $\dots$ , bM) may <sup>25</sup> itself be an error-correcting code C and therefore may contain redundancy. The decoding algorithm, in 1 may be further specified as follows:

Let L be a positive integer parameter that indicates the size of a list, where each element in the list is an assignment of value to (u1, u2, ..., ui-1) before the value of ui is computed. For i=1, ..., N, the decoding algorithm computes the value of ui with the following:

If  $i \in \hat{F}_C$ , let  $u_i$  be the constant value that was assigned to it by the previous write.

If  $i \not\in F_C$ , for each element in the list (which is an assignment of value to  $(u_1, u_2, \ldots, u_{i-1})$ ), append to it the value assignment  $u_i = 0$ , and also append to it the value assignment  $u_i = 1$ , thus converting that element into two new elements in the list. If the list now contains more than L elements, keep only the L elements that are most likely in the list. The likelihood of an element in the list may be computed as  $\Pr\{c_1, \ldots, c_N | u_1, \ldots, u_i\}$  assuming that each of  $u_{i+1}, \ldots, u_N$  is equally likely to be 0 and 1.

Then, for each element in the list, the method checks if its value assignment to  $(u_t|i\in F_{WOM}-F_C)$ , which should equal (b1, . . . , bM), is a valid codeword in the error-correcting code C; and if not, remove it from the list. Then, the method may choose the most likely element in the remaining list as the recovered value for  $(u1, \ldots, uN)$ .

In some embodiments, the decoding algorithm may be based on a belief-propagation decoding algorithm for polar error-correcting codes.

In some embodiments, the matrix  $A_{N \times N}$  may be specified as follows. Let m be a positive integer, and let  $N=2^m$ . Let

$$G2 = \begin{pmatrix} 1 & 0 \\ 1 & 1 \end{pmatrix},$$

and let  $A_{N \times N} = G_2^{\oplus m}$  be the m-th Kronecker product of  $G_2$ . In some embodiments, recovering the value action discussed above may further include the following:

1: Let  $y=(y_1, y_2, \ldots, y_N)=((c_1 \oplus g_1), (c_2 \oplus g_2) \ldots, 65$   $(c_N \oplus g_N))$  be a vector of N elements, where every element  $y_i=c_i \oplus g_i$  is a bit.

14

2: For every  $i \in F_C$ , let  $u_i = 0$ .

3: Compute the values of  $W_N^i(y, (u_1, u_2, \dots, u_{i-1})|u_i=0)$  and  $W_N^i(y, (u_1, u_2, \dots, u_{i-1})|u_i=1)$  for  $i=1, 2, \dots, N$  as follows:

Depending on the parity of i, the value of  $W_N^i$  is recursively evaluated through one of the formulae below (beginning with n=N/2):

$$0 \sum_{u_{2i\in(0,1)}} \frac{1}{2} W_n^i = \tag{5}$$

$$((y_1,\,y_2,\,\ldots\,\,,\,y_n),\,(u_1,\,u_3,\,u_5,\,\ldots\,\,,\,u_{2i-3})\ominus(u_2,\,u_4,\,u_6,\,\ldots\,\,,\,u_{2i-2})|\\ u_{2i-1}\ominus u_{2i}$$

$$W_n^i\Big((y_{n+1}, y_{n+2}, \dots, y_{2n}), (u_2, u_4, u_6, \dots, u_{2i-2})|u_{2i}),$$

$$W\frac{2i}{2n}((y_1, y_2, \dots, y_{2n}), (u_1, u_2, \dots, u_{2i-1})|u_{2i}) = \frac{1}{2}W_n^i((y_1, y_2, \dots, y_{2n}),$$

(6)

$$(u_1, u_3, u_5, \dots, u_{2i-3}) \oplus (u_2, u_4, u_6, \dots, u_{2i-2}) | u_{2i-1} \oplus u_{2i})$$

$$W_{\hat{p}}^i((y_{n+1}, y_{n+2}, \dots, y_{2n}), (u_2, u_4, u_6, \dots, u_{2i-2}) | u_{2i})$$

with the base cases

$$W_1^{-1}((0),(.)|0)=1-p$$

$$W_1^{-1}((1),(.)|0)=p$$

$$W_1^{-1}((0),(.)|1)=p$$

$$W_1^{-1}((1),(.)|1)=1-p$$

(7)

where (.) denotes an empty vector. The operator  $\oplus$  between two binary vectors denotes the element-wise exclusive-OR computation. The operator  $\oplus$  between two bits denotes the binary exclusive-OR computation.

4: For each ieF  $_{WOM}$ -F  $_C$ , if  $W_N{}^i(y_1, y_2, \ldots, y_N)$ ,  $(u_1, u_2, \ldots, u_{i-1})|u_i=0\rangle \ge W_N{}^i(y_1, y_2, \ldots, y_N)$ ,  $(u_1, u_2, \ldots, u_{i-1})|u_i=1\rangle$ , let  $u_i=0$ ; otherwise, let  $u_i=1$

5: Let  $\{u_i | i \in F_{WOM} - F_C\}$  be the recovered value for the data  $(b_1, \ldots, b_M)$ , where the mapping from the bits in  $\{u_i | i \in F_{WOM} - F_C\}$  to the bits in  $(b_1, \ldots, b_M)$  is as specified in the previous rewrite operation.

In some embodiments, the method may be a list-decoding algorithm further specified as follows:

Let L be a positive integer parameter that indicates the size of a list, where each element in the list is an assignment of value to (u1, u2, . . . ,ui-1) before the value of ui is computed. In addition, the method may include the following:

1: Let  $y=(y_1, y_2, \ldots, y_n)=((c_1 \oplus g_1), (c_2 \oplus g_2), \ldots, (c_N \oplus g_N))$  be a vector on N elements, where every element  $y_i=c_i \oplus g_i$  is a bit.

2: For every  $i \in F_C$ , let  $u_i = 0$ .

60

3: Compute the values of  $W_N^i(y, (u_1, u_2, \dots, u_{i-1})|u_i=0)$  55 and  $W_N^i(y, (u_1, u_2, \dots, u_{i-1})|u_i=1)$  for  $i=1, 2, \dots, N$  as follows:

Depending on the parity of i, the value of  $W_N^i$  is recursively evaluated through one of the formulae below (beginning with n=N/2):

$$\sum_{u_{2i\in(0,1)}} \frac{1}{2} W_n^i = \tag{8}$$

$$((y_1, y_2, \dots, y_n), (u_1, u_3, u_5, \dots, u_{2i-3}) \ominus (u_2, u_4, u_6, \dots, u_{2i-2})|$$

$$u_{2i-1} \ominus u_{2i}$$

20

15

-continued

$W_{n}^{i}((y_{n+1}, y_{n+2}, \dots, y_{2n}), (u_{2}, u_{4}, u_{6}, \dots, u_{2i-2})|u_{2i}),$   $W_{2n}^{2i}((y_{1}, y_{2}, \dots, y_{2n}), (u_{1}, u_{2}, \dots, u_{2i-n})|u_{2i}) = \frac{1}{2}W_{n}^{i}((y_{1}, y_{2}, \dots, y_{2n}),$   $(u_{1}, u_{3}, u_{5}, \dots, u_{2i-3}) \oplus (u_{2}, u_{4}, u_{6}, \dots, u_{2i-2})|u_{2i-1} \oplus u_{2i})W_{n}^{i} = ((y_{n+1}, y_{n+2}, \dots, y_{2n}), (u_{2}, u_{4}, u_{6}, \dots, u_{2i-2})|u_{2i})$  (9)

with the base cases

$$W_1^{-1}((0),(.)|0)=1-p$$

$W_1^{-1}((1),(.)|0)=p$

$W_1^{-1}((0),(.)|1)=p$

$W_1^{-1}((1),(.)|1)=1-p$  (1)

where (.) denotes an empty vector. The operator  $\oplus$  between two binary vectors denotes the element-wise exclusive-OR computation. The operator  $\oplus$  between two bits denotes the binary exclusive-OR computation.

4: For i=1, 2, ..., N, do:

If  $i \in F_C$ , for each element in the list (which is an assignment of value to  $(u_1, u_2, \ldots, u_{i-1})$ , append it to the value assignment  $u_i = 0$ , and also append it to the value assignment  $u_i = 1$ , thus converting that element into two new elements in the list. If the list now contains more than L elements, keep only the L elements that are most likely in the list. The likelihood of an element in the list may be computed as  $W_N^i((y_1, \ldots, y_N), (u_1, \ldots, u_{i-1})|u_i)$ .

5: Choose the most likely element in the list as the recovered value for  $(u_1, \ldots, u_N)$ . The likelihood of an element in the list here may be computed as  $W_N^N((y_r, \ldots, y_N), (u_1, \ldots, u_{N-1})|u_N)$ . Then let  $\{u_1|i\in F_{WOM}-F_C\}$  be the recovered value for the data  $(b_1, \ldots, b_M)$  where the mapping from the bits in  $\{u_1|i\in F_{WOM}-F_C\}$  to the bits in  $\{b_1, \ldots, b_M\}$  is as specified in the previous rewrite operation.

In some embodiments, the stored data (b1,  $\dots$ , bM) may itself be an error-correcting code C and therefore may contain redundancy and the method may include:

Let L be a positive integer parameter that indicates the size 40 of a list, where each, element in the list is an assignment of value to (u1, u2, . . . , ui-1) before the value of ui is computed. The method further includes the following:

1: Let  $y=(y_1, y_2, \ldots, y_n)=((c_1 \oplus g_1), (c_2 \oplus g_2), \ldots, (c_N \oplus g_N))$  be a vector of N elements, where every element  $y_i=c_i \oplus g_i$  is a bit.

2: For every  $i \in F_C$ , let  $u_i = 0$ .

3: Compute the values of  $W_N^i(y, (u_1, u_2, \ldots, u_{i-1})|u_i=0)$  and  $W_N^i(y, (u_1, u_2, \ldots, u_{i-1})|u_i=1)$  for  $i=1, 2, \ldots, N$  as follows:

Depending on the parity of i, the value of  $W_N^i$  is recursively evaluated through one of the formulae below (beginning with n=N/2):

$$\sum_{u_{2i=(0,1)}} \frac{1}{2} W_n^i = ((y_1, y_2, \dots, y_n),$$

(11)

$(u_1, u_3, u_5, \dots, u_{2i-3}) \ominus (u_2, u_4, u_6, \dots, u_{2i-2}) | u_{2i-1} \ominus u_{2i})$

$$W_{n}^{i}((y_{n+1}, y_{n+2}, \dots, y_{2n}), (u_{2}, u_{4}, u_{6}, \dots, u_{2i-2})|u_{2i}),$$

$$W_{2n}^{2i}((y_{1}, y_{2}, \dots, y_{2n}), (u_{1}, u_{2}, \dots, u_{2i-n})|u_{2i}) = \frac{1}{2}W_{n}^{i}((y_{1}, y_{2}, \dots, y_{2n}),$$

$$(12)$$

$$(u_1,\,u_3,\,u_5,\,\ldots\,,\,u_{2i-3}) \oplus (u_2,\,u_4,\,u_6,\,\ldots\,,\,u_{2i-2})|u_{2i-1} \oplus u_{2i}) \\ W^i_n((y_{n+1},\,y_{n+2},\,\ldots\,,\,y_{2n}),\,(u_2,\,u_4,\,u_6,\,\ldots\,,\,u_{2i-2})|u_{2i})$$

16

with the base cases

$$W_1^{-1}((0),(.)|0)=1-p$$

$$W_1^{-1}((1),(.)|0)=p$$

$$W_1^{-1}((0),(.)|1)=p$$

$$W_1^1((1),(.)|1)=1-p$$

(13)

where (.) denotes an empty vector. The operator  $\oplus$  between two binary vectors denotes the element-wise exclusive-OR computation. The operator  $\oplus$  between two bits denotes the binary exclusive-OR computation.

4: For i=1, 2, ..., N, do:

If  $i \in F_C$ , let  $u_i = 0$ .

If  $i \not\in F_C$ , for each element in the list (which is an assignment of value to  $(u_1, u_2, \ldots, u_{i-1})$ , append it to the value assignment  $u_i = 0$ , and also append it to the value assignment  $u_i = 1$ , thus converting that element into two new elements in the list. If the list now contains more than L elements, keep only the L elements that are most likely in the list. The likelihood of an element in the list may be computed as  $W_N^i((y_1, \ldots, y_N), (u_1, \ldots, u_{i-1})|u_i)$ .

5: Then, for each element in the list, check if its value assignment to  $(u_r|i\in F_{WOM}-F_C)$ , which should equal  $(b_1,\ldots,b_M)$ , is a valid codeword in the error-correcting code C; and if not, remove it from the list. Then, choose the most likely element in the remaining list as the recovered value for  $(u_1,\ldots u_N)$ . The likelihood of an element in the list here may be computed as  $W_N^N((y_1,\ldots,u_N),(u_1,\ldots,u_{N-1}))$ . Then let  $\{u_r|i\in F_{WOM}-F_C\}$  be the recovered value for the data  $(b_i,\ldots,b_M)$ , where the mapping from the bit in  $\{u_r|i\in F_{WOM}-F_C\}$  to the bits in  $(b_1,\ldots,b_M)$  is as specified in the previously rewrite operation.

In some embodiments, FC may be determined as follows: Let the target block error rate be B, a non-negative real-number parameter between 0 and 1. Let  $(j1,j2,\ldots,jN)$  be a permutation of  $\{1,2,\ldots,N\}$  such that the decoding error probability of the bit uj1 is the greatest, the decoding error probability of the bit uj2 is the second greatest, and so on, and the decoding error probability of the bit ujN is the smallest. Let the size of FC, |FC|, be chosen as the smallest integer such that the summation of the decoding error probabilities of the bits  $u_{j|F_C|+1}, u_{j|F_C|+2}, \ldots, u_{j_N}$  is no greater than B. Let FC= $\{j1,j2,\ldots,j|FC|\}$ .

In some embodiments, FC⊆FWOM. In alternative embodiments, FC is not a subset of FWOM. That is, 50 FC–FWOM is not empty.

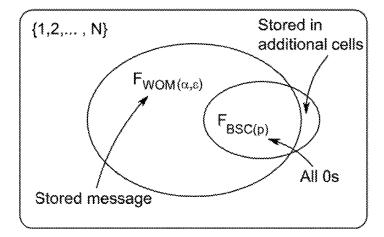

In some embodiments, the rewriting or encoding methods described above are modified to include storing the value of the bits  $\{u_i | i \in F_C - F_{WOM}\}$  in  $N_{additional}$  additional cells, using an error-correcting code of length  $N_{additional}$  that encodes | |FC-FWOM| bits. (Those additional cells are disjoint for the rewrites.)

In some embodiments, the error correction of decoding methods described above are modified to include recovering the value of the bits in  $\{u_i|i\in F_C-F_{WOM}\}$  by decoding the error-correcting code stored in the  $N_{additional}$  additional cells. In addition, the error correction or decoding method described above may be such that the value of the bits in  $\{u_i|i\in F_C-F_{WOM}\}$  is fixed as the above recovered value.

In some embodiments, for j=1, 2, ..., t, FCj denotes the set FC for the j-th rewrite. FWOMj denotes the set FWOM for the j-th rewrite, and N<sub>additional</sub> additional cells are used for a code that supports t rewrites and error-correction

processes. In such, embodiments, for j=1, . . . , t, M=IFCj-FWOMj bits are stored in the j-th rewrite. The code can be any code described herein.

In some embodiments, methods of encoding discussed above may be modified such that for  $j=1, 2, \ldots, t$ , and for the j-th rewrite, the value of the bits  $\{u_i | i \in F_{C,j} - F_{WOM,j}\}$  in the N<sub>additional</sub> additional cells, are stored using the code specified above for the N<sub>additional</sub> additional cells.

In some embodiments, for j=1, ..., t, M=|FC,j-FWOMj|bits are stored in the j-th rewrite, and methods of decoding discussed above may be modified such that the value of the bits in  $\{u_i | i \in F_{C,j} - F_{WOM,j}\}$  are recovered by decoding the rewrite- and error-correction code stored in the N<sub>additional</sub> additional cells. In addition, methods of decoding discussed above may be modified such that the value of the bits in 15  $\left\{\mathbf{u}_{i} \middle| \mathbf{i} \in \mathbf{F}_{C,j} - \mathbf{F}_{WOM,\; j}\right\}$  is fixed as the above value.

In some embodiments, the WOM cells are binary. In alternative or additional embodiments, every cell has q-levels: level 0, level  $1, \ldots,$  and level q-1,

and the exclusive-OR operation is generalized to the modular-q summation.

In such embodiments, methods for rewriting and errorcorrection or encoding may use the cells in the following level-by-level approach:

The methods may first use level 0 and level 1 and apply the 25 previously described features for binary cells;

The methods may then use level 1 and level 2 (as if they were level 0 and level 1) and apply the previously described features for binary cells;

The methods may then use level 2 and level 3 (as if they were level 0 and level 1) and apply the previously described features for binary cells;

The above process(es) may continue, until finally, the methods may use level q-2 and level q-1 (as if they were level 0 and level 1) and apply the previously described features for 35 binary cells.

In some embodiments, methods for rewriting and error correction or encoding may be modified such that each ui, si, gi, vi, s'i or v'i takes its value from the set  $\{0,1,\ldots,q-1\}$ , and the exclusive-OR operation may be generalized to the 40 modular-q summation.

An example, as discussed with reference to FIGS. 4 and

FIG. 4 illustrates an embodiment of an encoder. Let the code have N=8 cells. Let the  $A_{N\times N}=A_{8\times 8}$  matrix 41 be:

$$\begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \\ \end{pmatrix}$$

Consider a rewrite (encode) operation and the subsequent error-correction (decode) operation. For the rewrite, let the a=0:87. Let e=0:29. Let FWOM={1, 2, 4, 5, 6}. Let FC=  $\{2, 6\}$ . Let M=|FWOM-FC|=| $\{1, 4, 5\}$ |=3. And let the data to be stored be (b1, b2, ..., bM)=(b1, b2, b3)=(1,0, 1). Assume the cell levels before this rewrite are  $(s1,\dots,sN)\!\!=\!\!(s1,\dots,sN)\!\!=\!\!(0,0,1,0,0,0,0,0).\,As\;a\;result\;\;65$  $(v1, \ldots, vn) = (v1, \ldots, v8) = (s1 \oplus g1, \ldots, s8 \oplus g8) = (1, 0, 0)$ 0, 0, 1, 0, 0, 1).

18

Consider the rewrite where  $(v1, \ldots, v8)=(u1, \ldots, u8)$ A<sub>8×8</sub> and the transition probabilities of the WOM channels 42 are shown in FIG. 4. The method of rewriting calculates that (u1, ..., u8)=(1, 0, 0, 0, 1, 0, 0, 0) (note that u1=b1=1, u4=b2=0, u5=b3=1, and u2=u6=0); therefore (v'1, . . . , v'8)=(u1, . . . , u8)  $A_{8\times8}$ =(0, 0, 0, 0, 1, 0, 0, 0) and  $(s'1..., s'8)=(v'1 \oplus g1, ..., v'8 \oplus g8)=(1,0, 1, 0, 0, 0, 0, 1).$ As a result the cells are programmed to level  $(s'1, \ldots s'8)=(1, \ldots, s'8)$ 0, 1, 0, 0, 0, 0, 1).

To write the data  $(b_1, b_2, \ldots, b_M)$ , our method has the following inputs: (1) The current cell levels  $(s_1, s_2, \dots, s_N)$ , and (2) the new data to store  $(1, b_2, \dots b_M)$ . It then computes the output  $(s'_1, s'_2, \ldots, s'_N)$ , and programs the cells to those new levels. Here are our constraints:

- 1) As mentioned before, for i=1, 2, ..., N, we have the constraint that is  $s'_{i} \ge s_{i}$ .

- 2) The new cell levels  $(s'_1, s'_2, \dots, s'_N)$  represents the new data  $(b_1, b_2, \ldots, b_M)$ , via the mapping specified by our

Next, consider the error correction (decode). FIG. 5 illustrates an embodiment of a decoder. The noise channels 52 are each a binary-symmetric channel with error probability p. Assume that after the above rewrite, noise changes the cell levels from  $(s'1, \ldots, s'8)=(1, 0, 1, 0, 0, 0, 0, 1)$  to  $(c1, \ldots, c8)=(0, 1, 1, 0, 0, 0, 0, 1)$ . The method of error correction recovers the value of (u1, ... u8) as (1, 0, 0, 0, 1, 0, 0, 0) using the matrix 51. Therefore the stored data is correctly received as (b1, b2, b3)=(u1, u4, u5)=(1, 0, 1). 65540656V.1

The remainder of the description is organized as follows. Section II includes a basic model and notations. Section III includes an embodiment of code construction. Section IV includes embodiments of code. Section V includes embodiments of code extensions. Section VI includes an analysis of actual sum-rates achieved by a code embodiment. Section VII includes further example embodiments. Section VIII includes concluding remarks.

#### II. Basic Model

A memory may have  $N(=2^m)$  WOM cells that are used to store data, where each cell has two levels; 0 and 1. The cells can change only from level 0 to level 1, but not vice versa.

A sequence of t messages  $M_1, M_2, \dots, M_t$  may be written into the WOM cells, and when  $M_i$  is written, the value of the previous messages need not be remembered. (Let M, denote the number of bits in the message  $M_i$ , and let  $M_i \in \{0,1\}^{M_i}$ .) For simplicity, let the cells be all at level 0 before the first 50 write happens.

After cells are programmed, noise may appear in the cell levels. Noise may be considered to be a BSC with error probability p, denoted by BSC(p). These errors may be hard errors, namely, they physically change the cell levels from 0 55 to 1 or from 1 to 0. For flash memories, such errors can be caused by read/write disturbs, interference and charge leakage, for example, and may be quite common.

A. The Model for Rewriting

A code for rewriting and error correction may comprise of dither be  $(\mathbf{g1}, \ldots, \mathbf{gN}) = (\mathbf{g1}, \ldots, \mathbf{g8}) = (1,0,1,0,1,0,0,1)$ . Let 60 t encoding functions  $E_1, E_2, \ldots, E_t$  and t decoding functions  $D_1, D_2, \ldots, D_t$ . For i=1, 2, ..., N and j=1, 2, ..., t, let  $s_{i,j} \in \{0,1\}$  and  $s'_{i,j} \in \{0,1\}$  denote the level of the i-th cell right before and after the j-th write, respectively. As discussed above,  $s'_{i,j} \ge s_{i,j}$ . Let  $c_{i,j} \in \{0,1\}$  denote the level of the i-th cell at any time after the j-th write and before the (j+1)-th write, when reading of the message M, can happen. The error  $c_{i,i} \oplus s'_{i,i} \in \{0,1\}$  is the error in the i-th cell caused by the noise

$$E_i: \{0,1\}^N \times \{0,1\}^{M_j} \rightarrow \{0,1\}^8$$

changes the cell levels from  $s_j = (s_{1,j}, s_{2,j}, \ldots, s_{N,j})$  to  $s'_j = (s'_{1,j}, s'_{2,j}, \ldots, s'_{N,j})$  given the initial cell state  $s_j$  and the message to store  $M_j$ . (Namely,  $E_j(s_j, M_j) = s'_j$ .) When the reading of  $M_j$  happens, the decoding function

$$D_i: \{0,1\}^N \rightarrow \{0,1\}^{M_j}$$

recovers the message  $M_j$  given the noisy cell state  $c_j=(c_{1,j}, c_{2,j}, \ldots c_{N,j})$ . Namely,  $D_j(c_1)=M_j$ .) For  $j=1,\ldots,t$ ,

$$R_j = \frac{M_j}{N}$$

is called the rate of the j-th write.  $R_{sum} = \sum_{j=1}^{r} R_{j}$  is called the <sup>20</sup> sum-rate of the code. When there is no noise, the maximum sum-rate of WOM code is known to be  $\log_2(t+1)$ , however, for noisy WOM, the maximum sum-rate is still largely unknown.

#### B. Polar Codes

A short introduction to polar codes follows due to its relevance to the code construction embodiments discussed herein. A polar code is a linear block error correcting code proposed by Arkan, See, e.g. E. Arkan, "Channel polarization: A method for constructing capacity-achieving codes for symmetric binary-input memoryless channels," *IEEE Trans. Inf. Theor.*, vol. 55, no. 7, pp. 3051-3073, July 2009. It is the first known code with an explicit construction that provably achieves the channel capacity of symmetric binary-input discrete memoryless channels (B-DMC). The encoder of a polar code transforms N input bits  $\mathbf{u}=(\mathbf{u}_1,\,\mathbf{u}_2,\,\ldots\,,\,\mathbf{u}_N)$  to N codeword bits  $\mathbf{x}=(\mathbf{x}_1,\,\mathbf{x}_2,\,\ldots\,,\,\mathbf{x}_N)$  through a linear transformation. (e.g.  $\mathbf{x}=\mathbf{u}G_2^{\oplus m}$  where

$$G_2 = \begin{pmatrix} 1 & 0 \\ 1 & 1 \end{pmatrix},$$

and  $G_2^{\oplus m}$  is the m-th Kronecker product of  $G_2$ .) The N 45 codeword bits  $(x_1, x_2, \ldots, x_N)$  are transmitted through N independent copies of a B-DMC. For decoding, N transformed binary input channels  $\{W_N^{(1)}, W_N^{(2)}, \ldots, W_N^{(N)}\}$  can be synthesized for  $u_1, u_2, \ldots, u_N$  respectively. The channels are polarized such that for large N, the fraction of 50 indices i for which  $I(W_N^{(i)})$  is nearly 1 approaches the capacity of the B-DMC, while the values of  $I(W_N^{(i)})$  for the remaining indices i are nearly 0. The latter set of indices are called the frozen set. For error correction, the  $u_i$ 's with i in the frozen set take fixed values, and the other  $u_i$ 's are used 55 as information bits. A successive cancellation (SC) decoding algorithm achieves diminishing block error probability as N increases.

Polar code can also be used for optimal lossy source coding, which has various applications. See, e.g. S. Korada 60 and R. Urbanke, "Polar codes are optimal for lossy source coding," *IEEE Trans. Inf. Theor.*, vol. 56, no. 4, pp. 1751-1768, April 2010. In particular the idea may be used to build capacity achieving WOM codes. See, e.g., D. Burshtein and A. Strugatski, "Polar write once memory codes," in Proc. 65 IEEE international Symposium on Information Theory, July 2012, pp., 1972-1976.

20

The presented code analysis uses the concept of upgrading and degrading channels, defined based on frozen sets. As taught by Tal and Vardy, a channel W:  $X \rightarrow Z$  is called "degraded with respect to a channel W:  $X \rightarrow Y$ " if an equivalent channel of W' can be constructed by concatenating W with an additional channel Q:  $Y \rightarrow Z$ , where the inputs of Q are linked with the outputs of W. See, e.g. I. Tal and A. Vardy, "How to construct polar codes," CoRR, vol. abs/1105.6164, 2011. That is,

$$W(z|x)=\sum_{y\in y}W(y|x)Q(z|y)$$

It may be denoted as W'≤W. Equivalently, the channel W is called "an upgrade with respect to W", denoted by W≥W'.

#### III. Code Construction

In this section, embodiments of code construction are described that combine rewriting with error correction.

A. Basic Code Construction with a Nested Structure

1) General: First, consider a single rewrite (namely, one of the t writes). Let  $s=(s_1,\ s_2,\ \dots,\ s_N)\in\{0,1\}^N$  and  $s'=(s'_1,\ s'_2,\ \dots,\ s'_N)\in\{0,1\}^N$  denote the cell levels right before and after this rewrite, respectively. Let  $g=(g_1,\ g_2,\ \dots,\ g_n)$  be a pseudo-random, bit sequence with independent and identically distributed bits that are uniformly distributed. The value of g is known to both the encoder and the decoder, and g is called a dither.

For i=1, 2, ..., N, let  $v_i = s_i \oplus g_i \in \{0,1\}$  and  $v'_i = s'_i \oplus g_i \in \{0,1\}$  be the value of the i-th cell before and after the rewrite, respectively. The WOM channel is built, such as shown in FIG. 6, for this rewrite, denoted by WOM  $(\alpha, \varepsilon)$ .

Here  $\alpha \in [0,1]$  and

$$\varepsilon \in \left[0, \frac{1}{2}\right]$$

40 are given parameters, with

$$\alpha = 1 - \sum_{i=1}^{N} \frac{s_i}{N}$$

representing the fraction of cells, at level 0 before the rewrite, and

$$\varepsilon = \frac{\sum_{i=1}^{N} s_i' s_i}{N - \sum_{i=1}^{N} s_i}$$

representing the fraction of cells that are changed from level 0 to level 1 by the rewrite. Let  $F_{WOM(\alpha,\epsilon)} \subseteq \{1, 2, \dots, N\}$  be the frozen set of the polar code corresponding to this channel  $WOM(\alpha,\epsilon)$ . It is known that

$$\lim_{N\to\infty}\frac{|F_{WOM(\alpha,\varepsilon)}|}{N}=\alpha H(\varepsilon).$$

See, e.g. I. Tal and A. Vardy, "How to construct polar codes," CoRR, vol. abs/1105.61.64,2011.

For the noise channel BSC(p), let  $F_{BSC(p)} \subseteq \{1, 2, ..., N\}$  be the frozen set of the polar code corresponding to the channel BSC(p). It is known that

$$\lim_{N\to\infty}\frac{|F_{BSC(p)}|}{|N|}=H(p).$$

In this subsection,  $F_{BSC(p)} \subseteq F_{WOM(\alpha, \epsilon)}$ . This case is as illustrated in FIG. 7(*a*). In this case, the code has a nice nested structure: for any message  $M \in \{0,1\}^M$ , the set of cell values  $V_M \subseteq \{0,1\}^N$  that represent the message M is a linear subspace of a linear error correcting code (ECC) for the noise channel BSC(p), and  $\{V_M | M \in \{0,1\}^M\}$  form a partition of the ECC. Later the code may be extended to more general cases

2) The encoder: Let E:  $\{0,1\}^N \times \{0,1\}^M \rightarrow \{0,1\}^N$  be the encoder for this rewrite. Namely, given the current cell state s and the message to write  $M \in \{0,1\}^M$ , the encoder is configured to find a new cell state s'=E(s, M) that represents M and is above s (that is, cell levels only increase).

The encoding function in Algorithm 1 follows. Here y and  $\ ^{20}$  u are two vectors of length

$$N,\, u_{F_{WOM(\alpha,\varepsilon)}-F_{BSC(p)}} \stackrel{\Delta}{=} \{u_i \mid i \in F_{WOM(\alpha,\varepsilon)} - F_{BSC(p)}\}$$

are all the bits  $\mathbf{u}_i$  in the frozen set  $\mathbf{F}_{WOM(\alpha,\epsilon)}$  but not

$$F_{BSC(p)}, u_{F_{BSC(p)}} \stackrel{\Delta}{=} \{u_i \mid i \in F_{BSC(p)}\}$$

are all the bits  $\mathbf{u}_i$  in  $\mathbf{F}_{BSC(p)},$  and  $\mathbf{G_2}^{\oplus m}$  is the m-th Kronecker product of

$$G_2 = \begin{pmatrix} 1 & 0 \\ 1 & 1 \end{pmatrix}.$$

Algorithm 1 The encoding function s' = E(s, M)