# ENERGY-EFFICIENT PHOTONIC ARCHITECTURES FOR LARGE-SCALE DATA ANALYTICS

### A Dissertation

by

### DHARANIDHAR DANG

### Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

| Chair of Committee, | Rabi N. Mahapatra |

|---------------------|-------------------|

| Committee Members,  | Duncan M. Walker  |

|                     | Eun Jung Kim      |

|                     | Samuel Palermo    |

| Head of Department, | Dilma Da Silva    |

December 2018

Major Subject: Computer Engineering

Copyright 2018 Dharanidhar Dang

#### ABSTRACT

With silicon technology reaching its physical limit, conventional computing systems are incapable of offering ever-increasing performance requirement with limited power budget. This has propelled semiconductor community to seek for new computing paradigms that can offer high energy-efficiency. Silicon photonics with its ultra-low power characteristics, inherent parallelism, and large multiplexing capability, is one such promising paradigm. The goal of this research is to utilize silicon photonics to design energy-efficient exascale computing architectures.

This study is established through research in a number of directions. First, we propose a nonblocking,  $5 \times 5$ , low-cost on-chip photonic router. It incorporates mode-division-multiplexing in addition to wavelength-division-multiplexing and time-division-multiplexing for high-throughput. It is a first of its kind to the best of our knowledge. We use this router to design high-performance 2D and 3D mesh photonic network-on-chip (PNoC). Further, we introduce a novel laser-multiplexing scheme to further enhance the energy-efficiency of our PNoC designs. Components in a photonic system are highly susceptible to thermal variations. We propose IHDTM, a cross-layer dynamic thermal management technique which is a combination of device-level optimization and systemlevel thread migration. After demonstrating a highly reliable energy-efficienct photonic system, we intend to devise a high-performance photonic architecture for exascale data analytic applications. Multicast data dissemination is a major performance bottleneck for data analytic applications in cluster computing, as terabytes of data need to be distributed frequently from a single data source to hundreds of computing nodes. To overcome this bottleneck, we propose BiGNoC, a manycore chip platform with a novel application-specific photonic on-chip network architecture. Finally, we intend to utilize the exascale parallelism and ultrafast characteristics of silicon photonics to extend the state of the art in deep learning accelerator architectures. Training a deep learning network involves expensive computation overheads. As a result, most of the accelerators use pretrained weights and focus only on improving the design of inference phase. We propose a novel photonic-based backpropagation accelerator for high performance deep learning training. In addition, we present a design for convolutional neural network, BPLight-CNN, which incorporates the novel photonic backpropagation accelerator. BPLight-CNN is a first-of-its-kind photonic and memristor-based CNN architecture for end-to-end training and prediction.

## DEDICATION

To my parents.

#### ACKNOWLEDGMENTS

First, I want to thank my advisor, Dr. Rabi N Mahapatra for his generosity wisdom, and guidance throughout my graduate studies. He has continuosuly inspired and challenged me to evolve as a resarcher. This dissertation would not have reached to its fruition without his advice. I would also like to thank my thesis committee members, Dr. Duncan Walker, Dr. Eun Jung Kim, and Dr. Samuel Palermo for agreeing to be on the committee and for providing valuable suggestions and criticisms. I am grateful to Dr. Dilma Da Silva for her kindly advice. I am also thankful to Dr. Vikram Kinra of Aerospace Department for offering me a teaching fellowship which was beneficial to strengthen my teaching skill. The staff at Texas A&M's Department of Computer Science & Engineering have been very nice and helpful during the course of graduate school. Special thanks to Mr. Bruce Veals for providing logistics in a timely fashion.

I am thankful to my collaborators Dr. S.V. R. Chittamuru of Micron, Dr. Martin Fiers of Luceda Photonics, Dr. Karthik Swaminathan of IBM TJ Watson, Dr. Christopher Nitta of University of California, Davis, for giving time and valuable ideas during my PhD. Special thanks to Dr. Sudeep Pasricha of Colorado State University for his critical remarks. I would also like to thank my amazing labmates Jyotikrishna Dass, Syed Ali Hasnain, Karl Ott, Jerry Yiu, Deam Ieong, Biplab Patra for numerous priceless brainstorming sessions.

My work would not have been possible without the support of my family. My parents have always been a continuous source of inspiration. I would also like to thank my younger brother, Subrat Kumar Dang, for taking care of my family in my absense. Special thanks to my sisters Pramodini, Tilottama, Meera, and Bidyutlata for their unconditional love and affection. I am grateful to my mentor Dr. Debashis Sahoo of University of California, San Diego for inspiring and supporting me throughut my stay in the U.S.

I am highly thankful to Texas A&M Cricket Club and Austin Cricket Club to provide me with the opportunity to play cricket regularly. This was highly beneficial to maintain a good balance of professional and personal endeavors. Finally, I would like to thank my friends Rajarshi, Pulakesh, Abhijit, Hollie, Rushil, Atish, Sanjeev, Roneet, Akash, and Matthew for making my stay in the U.S. an unforgettable journey. Special thanks to Susovita, Artta, and Aurosmita for their affection and encouragement. During time away from home, they have been a constant source of support, motivation, and happiness.

#### CONTRIBUTORS AND FUNDING SOURCES

### Contributors

This work was supported by a thesis (or) dissertation committee consisting of Professor Rabi N Mahapatra [advisor], Professor Duncan H. Walker, and Professor Eun Jung Kim of the Department of Computer Science & Engineering and Professor Samuel Palermo of the Department of the Electrical & Computer Engineering.

The experimental analysis in chapter 4 was conducted in part by Dr.Sudeep Pasricha of Colorado State University.

All other work conducted for the thesis (or) dissertation was completed by the student independently.

#### **Funding Sources**

Graduate study was supported by a teaching fellowship from College of Engineering, Texas A&M University and graduate assistantships from the Department of Computer Science & Engineering.

### NOMENCLATURE

| MRR  | Microring Resonator                    |

|------|----------------------------------------|

| PNoC | Photonic Network-on-Chip               |

| СМР  | Chip Multiprocessor                    |

| SOC  | System-on-Chip                         |

| CNN  | Convolutional Neural Network           |

| DWDM | Dense Wavelength-division-multiplexing |

| TDM  | Time-division-multiplexing             |

| ADC  | Analog to Digital Converter            |

| DAC  | Digital to Analog Converter            |

| SOA  | Semiconductor Optical Amplifier        |

## TABLE OF CONTENTS

| AB  | STRA                                   | АСТ                                                                     | ii                                                                                                                                                                                           |

|-----|----------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DE  | DICA                                   | TION                                                                    | iv                                                                                                                                                                                           |

| AC  | KNO                                    | WLEDGN                                                                  | MENTS v                                                                                                                                                                                      |

| CO  | NTR                                    | BUTORS                                                                  | S AND FUNDING SOURCES vii                                                                                                                                                                    |

| NO  | MEN                                    | CLATUR                                                                  | Eviii                                                                                                                                                                                        |

| TAI | BLE                                    | OF CONT                                                                 | TENTS ix                                                                                                                                                                                     |

| LIS | T OF                                   | FIGURE                                                                  | xii                                                                                                                                                                                          |

| LIS | T OF                                   | TABLES                                                                  | sxvii                                                                                                                                                                                        |

| 1.  | INTF                                   | RODUCT                                                                  | ION 1                                                                                                                                                                                        |

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Advent o<br>Silicon P<br>Research<br>Contribu                           | formance Computing hits the wall!1of Silicon Photonics2hotonic Basics2Focus5tions5tion7                                                                                                      |

| 2.  | ADA                                    | PTIVE M                                                                 | IULTIPLEXING IN PHOTONIC NETWORK-ON-CHIP         8                                                                                                                                           |

|     | 2.1<br>2.2<br>2.3<br>2.4               | Related V<br>Contribut<br>Basics O<br>2.4.1 S<br>2.4.2 M<br>2<br>2<br>2 | bn8Works9tions11f Silicon Photonics11Silicon Photonic Components12Multiplexing142.4.2.1Wavelength-Division-Multiplexing142.4.2.2Mode-Division-Multiplexing15Proposed Adaptive Multiplexing16 |

|     | 2.5                                    |                                                                         | ication Flow                                                                                                                                                                                 |

|     | 2.6                                    |                                                                         | Router                                                                                                                                                                                       |

|     |                                        | 2.6.1 F                                                                 | Router Micro-architecture172.6.1.1Switching Fabric19                                                                                                                                         |

|    |          | 2.6.1.2 Network Interface                                       | 22 |

|----|----------|-----------------------------------------------------------------|----|

|    | 2.7      | Routing Algorithm                                               | 24 |

|    | 2.8      | Laser Multiplexing in 2D & 3D Photonic Network-on-Chip          | 27 |

|    |          | 2.8.1 Mechanism and Control                                     | 28 |

|    | 2.9      | Experiments & Results                                           | 29 |

|    |          | 2.9.1 Experimental Methodology                                  | 29 |

|    |          | 2.9.1.1 Microarchitecture Simulation on IPKISS                  | 29 |

|    |          | 2.9.2 Microarchitecture validation under traffic                | 30 |

|    |          | 2.9.3 Comparitive Analysis and Results                          | 31 |

|    |          | 2.9.3.1 Number of MRRs                                          | 32 |

|    |          | 2.9.3.2 Photonic area Overhead                                  | 33 |

|    |          | 2.9.3.3 Average Throughput                                      | 34 |

|    |          | 2.9.3.4 Energy Consumption                                      | 39 |

|    |          | 2.9.3.5 Optical Insertion loss                                  | 45 |

|    | 2.10     | Chapter Summary                                                 | 47 |

|    |          |                                                                 |    |

| 3. | CRO      | SS-LAYER DYNAMIC THERMAL MANAGEMENT IN PNOC                     | 49 |

|    | 0.1      |                                                                 | 40 |

|    | 3.1      | Why Thermal Management?                                         |    |

|    | 3.2      | Related Work                                                    |    |

|    | 3.3      |                                                                 |    |

|    |          | 3.3.1 Thermal Islands                                           |    |

|    | <b>.</b> | 3.3.2 Temperature-Aware Thread Migration Scheme ( <i>TATM</i> ) |    |

|    | 3.4      | Experiments, Results, and Analysis                              |    |

|    |          | 3.4.1 Experimental Setup                                        |    |

|    |          | 3.4.2 Experimental Results                                      |    |

|    | 3.5      | Chapter Summary                                                 | 69 |

| 4. |          | LICATION SPECIFIC PNOC FOR BIG DATA COMPUTING                   | 71 |

| 4. | AFF      | EICATION SPECIFIC FNOC FOR BIO DATA COMPUTING                   | /1 |

|    | 4.1      | Introduction                                                    | 71 |

|    | 4.2      | Related Work                                                    |    |

|    | 4.3      | Master-Servant Cluster Architecture                             | 78 |

|    |          | 4.3.1 MN-to-SN communication in MSNoC cluster                   | 78 |

|    |          |                                                                 |    |

|    |          | 4.3.3 SN-to-SN communication in MSNoC cluster                   | 85 |

|    | 4.4      | Sensitivity analysis                                            | 86 |

|    | 4.5      | BiGNoC Architecture                                             | 87 |

|    |          | 4.5.1 Homogeneous BiGNoC Architecture                           | 87 |

|    |          | 4.5.2 Heterogeneous BiGNoC architecture                         | 90 |

|    |          | 4.5.3 Application scheduling in BiGNoC                          | 91 |

|    | 4.6      | Experiments                                                     | 92 |

|    |          | 4.6.1 Experimental Setup                                        | 92 |

|    |          | 4.6.2       BigNoC: Sensitivity Analysis                        | 95 |

|    |          | 4.6.3     Experimental Results                                  |    |

|    |          | Lapermental Results                                             | 10 |

|    | 4.7   | Chapte  | er Summar  | ry                                   |  |

|----|-------|---------|------------|--------------------------------------|--|

| 5. | NEU   | ROMO    | RPHIC C    | OMPUTING USING SILICON PHOTONICS     |  |

|    | 5.1   | Introdu | ction      |                                      |  |

|    | 5.2   | Convol  | lutional N | eural Network: Overview              |  |

|    |       | 5.2.1   |            | f Convolutional Neural Network       |  |

|    |       | 5.2.2   |            | pagation Algorithm                   |  |

|    | 5.3   | Overvi  |            | hip Photonic Components              |  |

|    | 5.4   |         |            | rchitecture                          |  |

|    |       |         |            | vard CNN Architecture                |  |

|    |       |         | 5.4.1.1    | CONV Microarchitecture               |  |

|    |       |         | 5.4.1.2    | ReLU Microarchitecture               |  |

|    |       |         | 5.4.1.3    | POOL Microarchitecture               |  |

|    |       |         | 5.4.1.4    | FC Microarchitecture                 |  |

|    |       | 5.4.2   | Backpro    | pagation Architecture                |  |

|    |       | 5.4.3   | Weight U   | Jpdate and Peripheral Circuitry      |  |

|    |       |         | 5.4.3.1    | Weight-update circuitry              |  |

|    |       |         | 5.4.3.2    | Peripheral Circuitry                 |  |

|    | 5.5   | BPLig   | ht-CNN C   | ase Study                            |  |

|    | 5.6   | Experi  | mental Ar  | nalysis                              |  |

|    |       | 5.6.1   | CAD for    | BPLight-CNN                          |  |

|    |       |         | 5.6.1.1    | Power and Area Models                |  |

|    |       |         | 5.6.1.2    | Performance Models                   |  |

|    |       |         | 5.6.1.3    | Benchmarks and Datasets              |  |

|    |       | 5.6.2   | Sensitivi  | ty Analysis with Prediction Accuracy |  |

|    |       | 5.6.3   | Performa   | ance Analysis                        |  |

|    |       | 5.6.4   | Energy S   | Savings                              |  |

|    | 5.7   | Chapte  | er Summar  | ry                                   |  |

| 6. | CON   | ICLUSI  | ONS & F    | UTURE DIRECTIONS                     |  |

|    | 6.1   | Conclu  | isions     |                                      |  |

|    | 6.2   | Future  | Direction  | s                                    |  |

| RE | EFERE | ENCES   |            |                                      |  |

## LIST OF FIGURES

| FIGURE | E                                                                                                                                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Comparison of (a) delay of metallic interconnects & gate, and (b) energy-consumption of metallic interconnects & compute core, w.r.t. technology scaling                                                     |      |

| 1.2    | Communication flow in Silicon Photonics                                                                                                                                                                      | 5    |

| 2.1    | Selective coupling of the single-mode microrings to a specific spatial mode in mul-<br>timodal waveguide. <i>Reprinted with permission from</i> [1]                                                          | 16   |

| 2.2    | Communication flow in Silicon Photonics                                                                                                                                                                      | 17   |

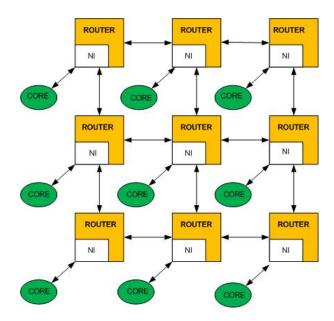

| 2.3    | 2D PNoC architecture                                                                                                                                                                                         | 18   |

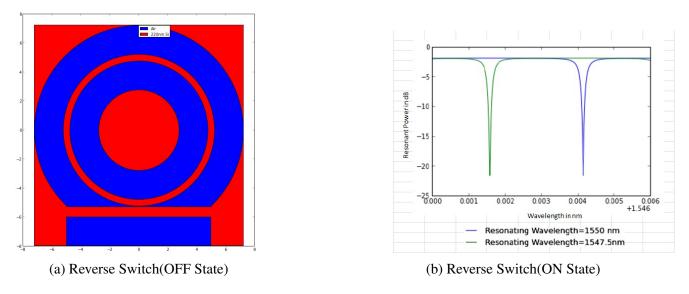

| 2.4    | MRR Switching. Reprinted with permission from [2]                                                                                                                                                            | 19   |

| 2.5    | Logical layout of $5 \times 5$ photonic router. <i>Reprinted with permission from</i> [2]                                                                                                                    | 21   |

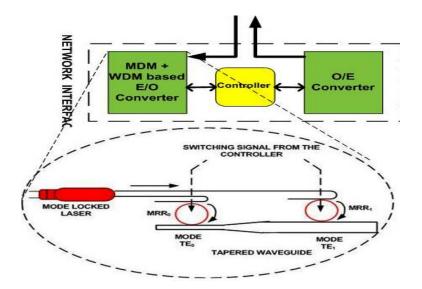

| 2.6    | MDM integrated Network-Interface                                                                                                                                                                             | 22   |

| 2.7    | Modelocked laser employing MDM                                                                                                                                                                               | 23   |

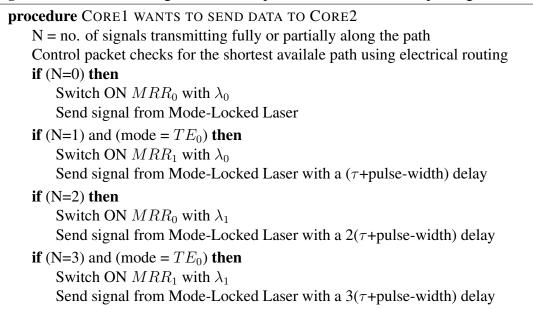

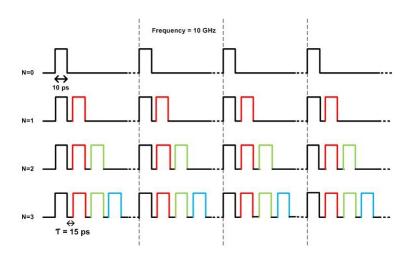

| 2.8    | Black pulse= $TE_0$ of $\lambda_0$ , red pulse= $TE_1$ of $\lambda_0$ , green pulse= $TE_0$ of $\lambda_1$ , blue pulse= $TE$ of $\lambda_1$ Timing diagram of TDM integrated Mode-Division-Multiplexing     |      |

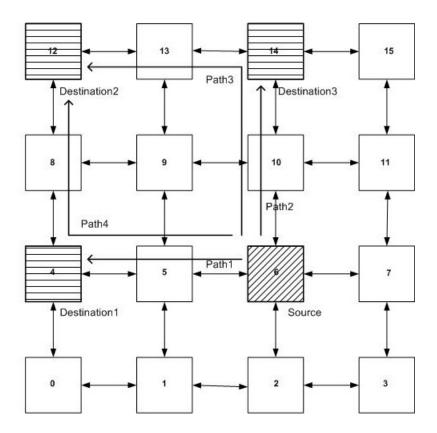

| 2.9    | Illustrating adaptive X-Y routing between 'Source', 'Destination 1', 'Destination 2' and 'Destination 3'                                                                                                     | 26   |

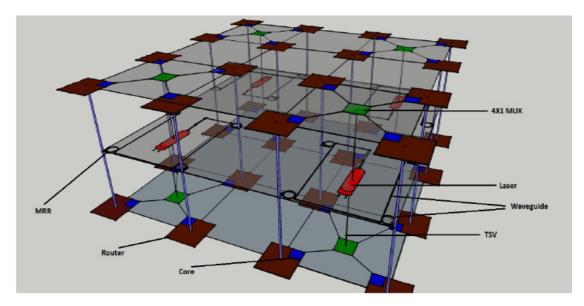

| 2.10   | Multilayer PNoC with Laser Multiplexing. Reprinted with permission from [3]                                                                                                                                  | 28   |

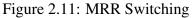

| 2.11   | MRR Switching                                                                                                                                                                                                | 31   |

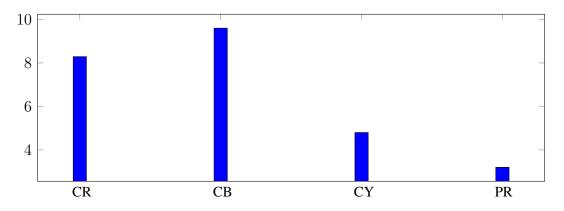

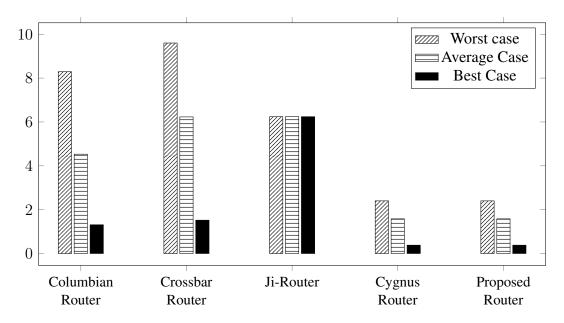

| 2.12   | Comparing number of MRRs/Router for different PNoC architectures; $LR=\lambda$ -Router CR=Columbian Router, CB=Crossbar Router, JR= Ji-router, PR=Proposed Router. <i>Reprinted with permission from</i> [2] | 32   |

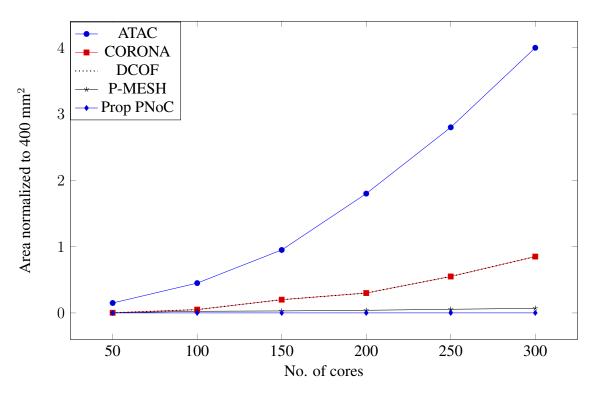

| 2.13   | Area overhead of different PNoC architectures with varying sizes                                                                                                                                             | 34   |

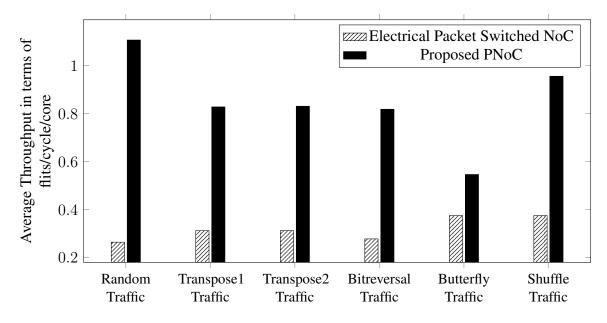

| 2.14   | Comparison of Average Throughput between Electrical noC and Proposed PNoC with various synthetic traffics                                                                                                    | 35   |

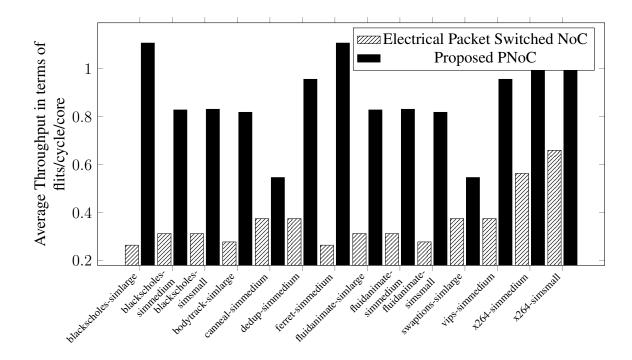

| 2.15   | Comparison of Average Throughput between Electrical noC and Proposed PNoC with PARSEC benchmark                                                                                                              | 36   |

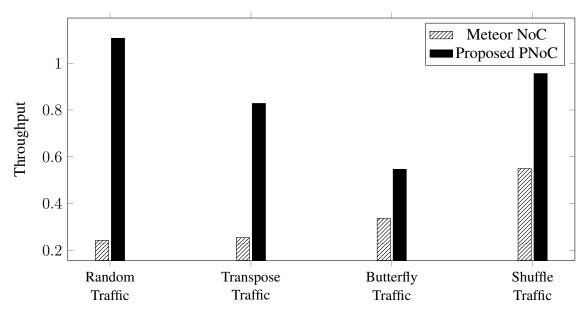

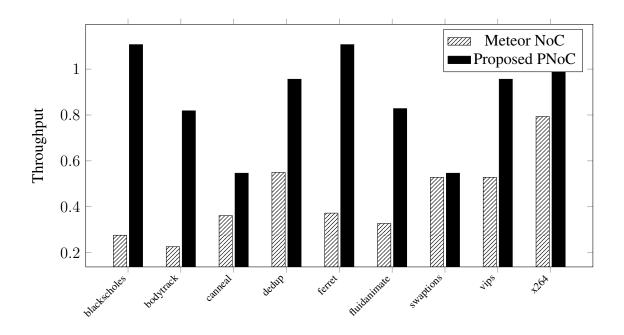

| 2.16 | Throughput(Synthetic Traffic): METEOR NoC vs Proposed PNoC                                                                                                                                                                   | 38 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.17 | Throughput(PARSEC Benchmark): METEOR NoC vs Proposed PNoC                                                                                                                                                                    | 38 |

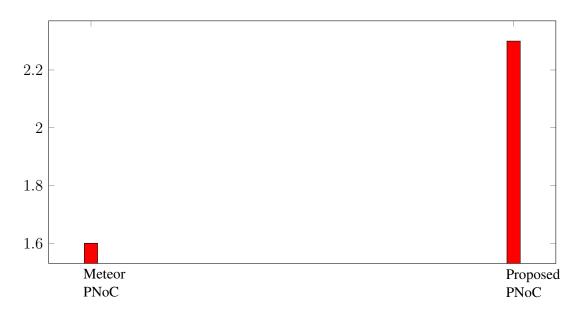

| 2.18 | Bandwidth/Photonic area(Meteor PNoC vs Proposed PNoC)                                                                                                                                                                        | 39 |

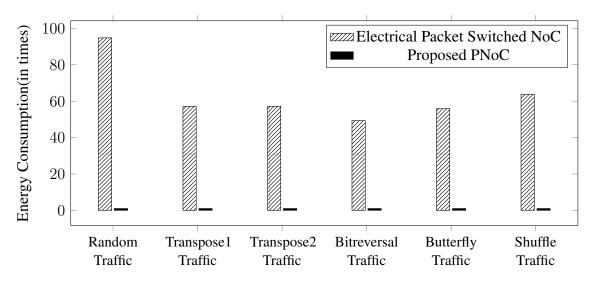

| 2.19 | Energy Consumption(Synthetic Traffic): Electrical noC vs Proposed PNoC                                                                                                                                                       | 42 |

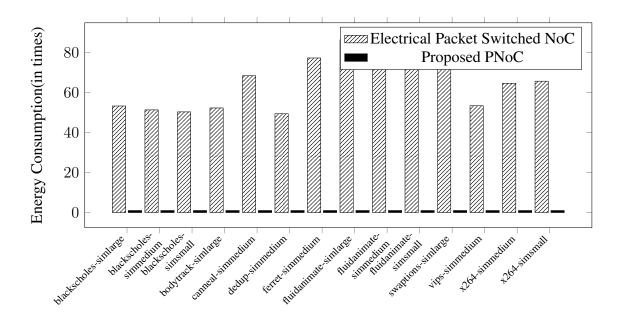

| 2.20 | Normalized Energy Consumption(PARSEC Benchmark): Electrical noC vs Proposed PNoC                                                                                                                                             | 43 |

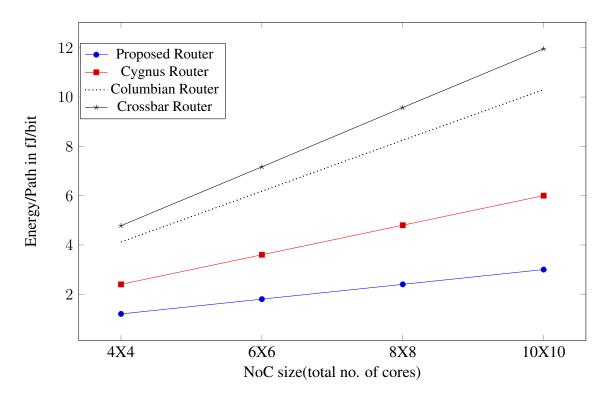

| 2.21 | Comparison of average energy consumption per optical path, in fJ/bit. <i>Reprinted</i> with permission from [2]                                                                                                              | 44 |

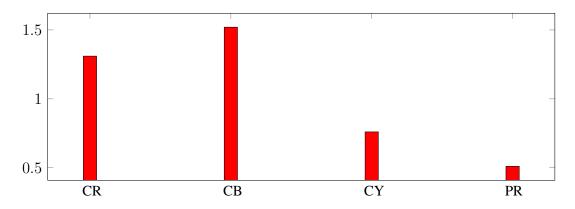

| 2.22 | Comparison of energy consumption per router in fJ/bit. <i>Reprinted with permission from</i> [2]                                                                                                                             | 45 |

| 2.23 | Average energy per Path for different PNoC sizes. <i>Reprinted with permission from</i> [2]                                                                                                                                  | 46 |

| 2.24 | Insertion loss per router in dB. Reprinted with permission from [2]                                                                                                                                                          | 47 |

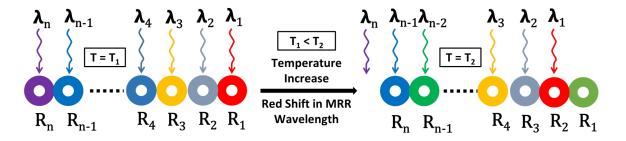

| 3.1  | Impact of thermal variations on MRRs. Reprinted with permission from [4]                                                                                                                                                     | 49 |

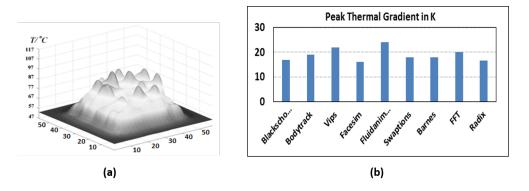

| 3.2  | Thermal Distribution: (a) a 64-core CMP, (b) Peak thermal gradient across a 64-core chip running 48-threaded PARSEC [5] and SPLASH-2 [6] benchmarks. <i>Reprinted with permission from</i> [4]                               | 51 |

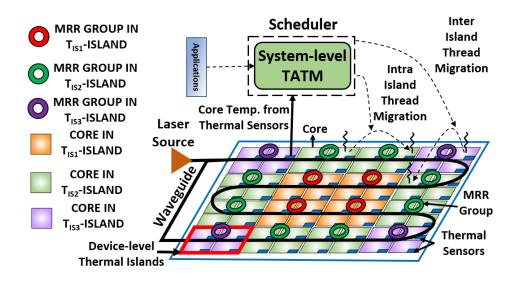

| 3.3  | IHDTM framework with device-level thermal islands and system-level temperature-<br>aware thread migration mechanism (TATM). <i>Reprinted with permission from</i> [4]                                                        | 52 |

| 3.4  | (a) MRR with adaptive heater (b) Thermal tuning of MRR. <i>Reprinted with permission from</i> [7]                                                                                                                            | 53 |

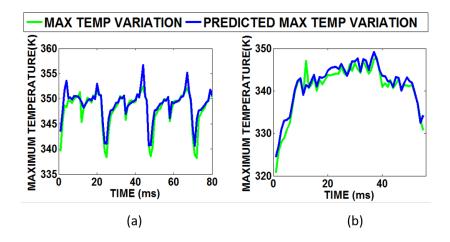

| 3.5  | Actual and predicted maximum temperature variation with execution time for (a) fluidanimate (FA) and (b) radiosity (RD) benchmarks run on a 64-core platform executing 32-threads. <i>Reprinted with permission from</i> [4] | 59 |

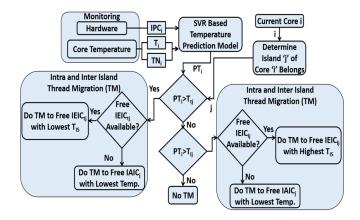

| 3.6  | Overview of TATM technique with support vector regression (SVR) based temper-<br>ature prediction model. <i>Reprinted with permission from</i> [4]                                                                           | 61 |

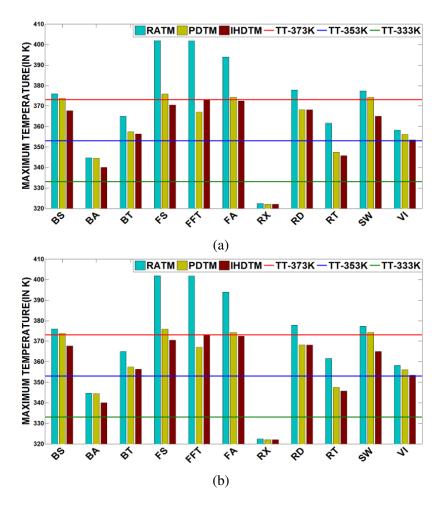

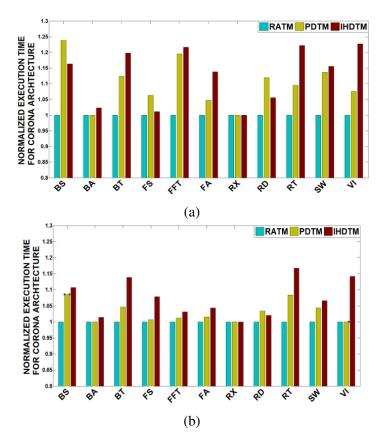

| 3.7  | Maximum temperature comparison of IHDTM with RATM and PDTM for (a) 48 (b) 32 threaded PARSEC and SPLASH-2 benchmarks executed on 64-core multi-core system with Corona PNoC. <i>Reprinted with permission from</i> [4]       | 65 |

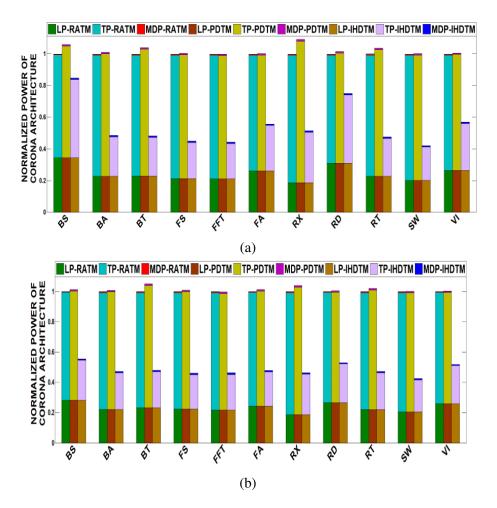

| 3.8  | Normalized power (Laser Power (LP), Trimming and tuning power (TP) and mod-<br>ulating and detecting Power (MDP)) comparison of IHDTM with RATM and PDTM<br>for (a) 48 and (b) 32 threaded applications of PARSEC and SPLASH-2 suites ex-<br>ecuted on Corona PNoC architectures for a 64-core multicore system. Results<br>shown are normalized w.r.t RATM. <i>Reprinted with permission from</i> [4]                                                                                                                                                    | 66 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

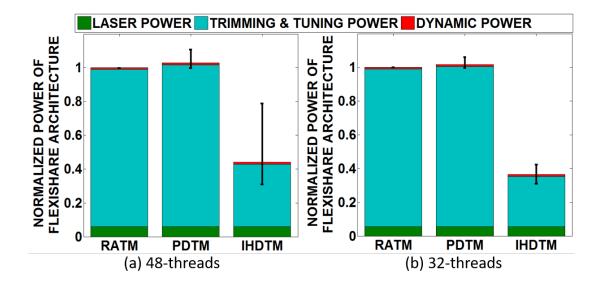

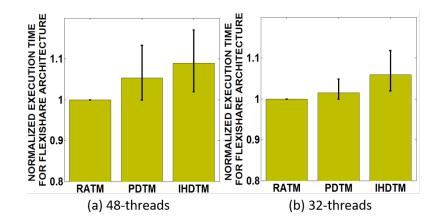

| 3.9  | Normalized average power (Laser Power (LP), Trimming and tuning power (TP) and modulating and detecting Power (MDP)) comparison of IHDTM with RATM and PDTM for (a) 48 and (b) 32 threaded applications of PARSEC and SPLASH-2 suites executed on Flexishare PNoC architectures for a 64-core multicore system. Power results are normalized wrt RATM results. Bars represent mean values of power dissipation; confidence intervals show variation in power dissipation across PARSEC and SPLASH-2 benchmarks. <i>Reprinted with permission from</i> [4] | 67 |

| 3.10 | Normalized execution time comparison of IHDTM with RATM and PDTM for<br>Corona PNoC running (a) 48; and (b) 32 threaded applications from PARSEC and<br>SPLASH-2 suites executed on 64-core system. Results shown are normalized wrt<br>RATM. <i>Reprinted with permission from</i> [4]                                                                                                                                                                                                                                                                   | 68 |

| 3.11 | Normalized average execution time comparison of IHDTM with RATM and PDTM for Flexishare PNoC running (a) 48; and (b) 32 threaded applications from PAR-SEC and SPLASH-2 suites executed on 64-core system. Power results are normalized wrt RATM results. Bars represent mean values of power dissipation; confidence intervals show variation in power dissipation across PARSEC and SPLASH-2 benchmarks. <i>Reprinted with permission from</i> [4]                                                                                                      | 69 |

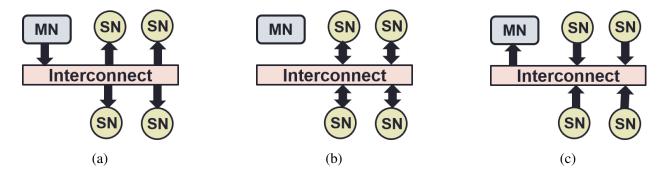

| 4.1  | MapReduce (a) multicast phase, (b) shuffle phase, and (c) aggregation phase of communication while executing iterative machine learning algorithms for large-scale data analytics applications. MN: Master Node; SN: Servant Node                                                                                                                                                                                                                                                                                                                         | 72 |

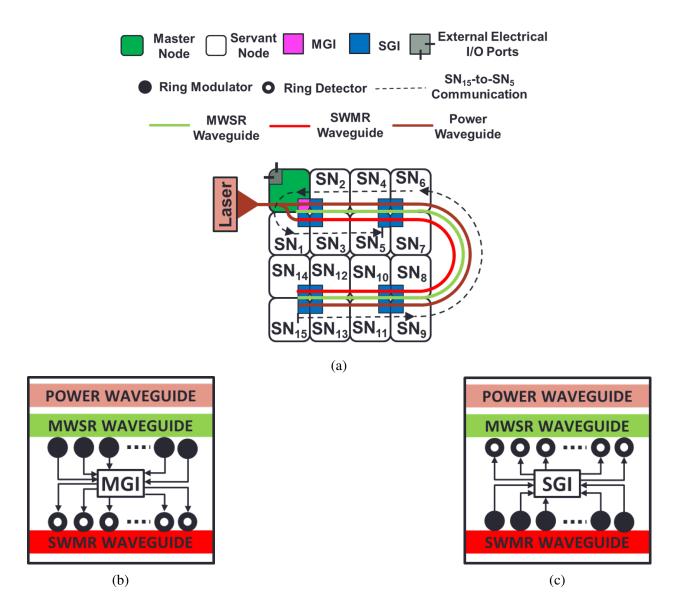

| 4.2  | (a) MSNoC layout with SWMR, MWSR, and power waveguides (b) master gate-<br>way interface (MGI) (c) servant gateway interface (SGI). <i>Reprinted with permis-</i><br><i>sion from</i> [8]                                                                                                                                                                                                                                                                                                                                                                 | 76 |

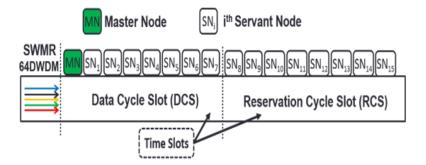

| 4.3  | Distribution of reservation cycle and data cycle slots within SWMR waveguide to enable MN-to-SN communication. <i>Reprinted with permission from</i> [8]                                                                                                                                                                                                                                                                                                                                                                                                  | 80 |

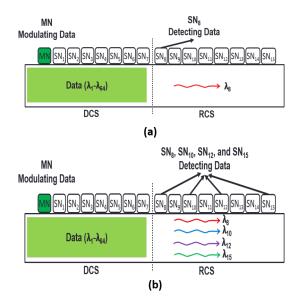

| 4.4  | (a) Transmission of unicast data from an MN to SN8 in MSNoC, which shows receiver selection wavelength $\lambda_8$ in RCS of the SWMR waveguide; (b) Multicast of data from an MN to multiple SNs SN8, SN10, SN12, and SN15 in MSNoC, which shows respective receiver selection wavelengths $\lambda_8$ , $\lambda_{10}$ , $\lambda_{12}$ , and $\lambda_{15}$ in RCS of the SWMR waveguide. <i>Reprinted with permission from</i> [8]                                                                                                                    | 82 |

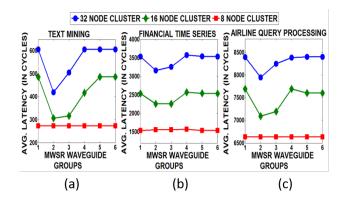

| 4.5  | Variation of average packet latency in MSNoC cluster with (a) 32 nodes (b) 16 nodes, and (c) 8 nodes having different MWSR waveguide groups (each group has 4 waveguides) across three big data applications. <i>Reprinted with permission from</i> [8]                                                                                                                                                                                                                                                                                                   | 85 |

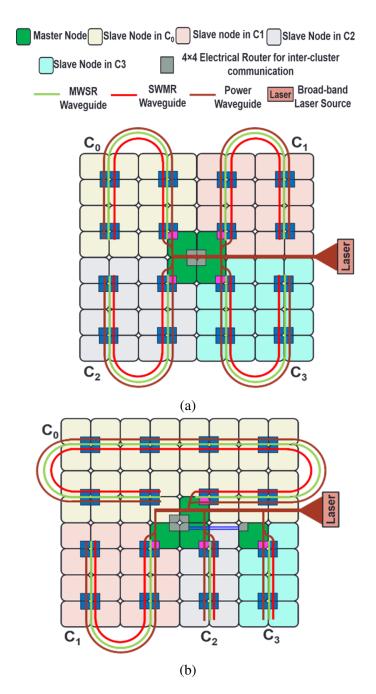

| 4.6  | <ul> <li>(a) Homogeneous BiGNoC with four uniform clusters C0, C1, C2, C3, with each cluster having 16 nodes, (b) Heterogeneous BiGNoC with four clusters C0, C1, C2, and C3 having 32, 16, 8, and 8 nodes, respectively. <i>Reprinted with permission from</i> [8]</li></ul> |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

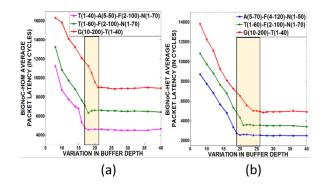

| 4.7  | Average packet latency comparison for (a) BiGNoC-HOM and (b) BiG-NoC-HET<br>in a 256-core CMP with different buffer depths (8-40). <i>Reprinted with permission</i><br><i>from</i> [8]                                                                                        |

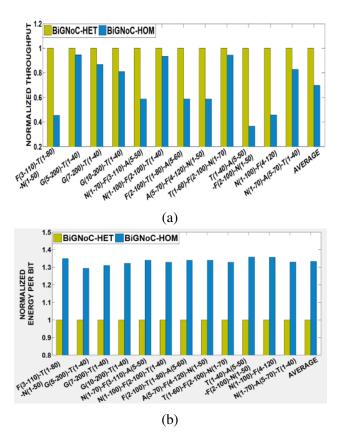

| 4.8  | (a) Normalized throughput, (b) normalized EPB comparison of BiG-NoC-HOM with BiGNoC-HET for 256-core CMP. Results are shown for multi-application workloads and normalized w.r.t. BiGNoC-HET. <i>Reprinted with permission from</i> [8] 99                                    |

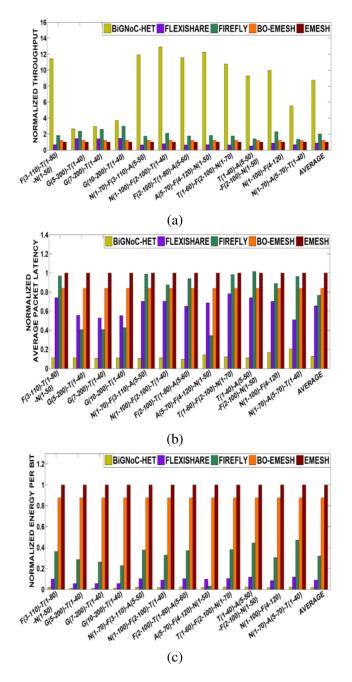

| 4.9  | Normalized (a) throughput (b) latency (c) EPB comparison of BiG-NoC-HET with other architectures for a 256-core CMP. Results are for multi-application work-loads and normalized w.r.t. EMesh. <i>Reprinted with permission from</i> [8]100                                   |

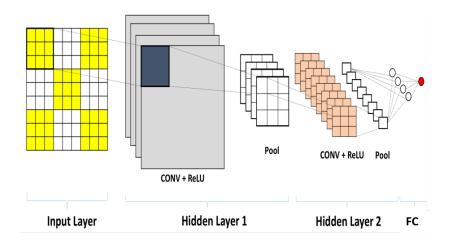

| 5.1  | Overview of CNN with two hidden layers and an FC layer. Each hidden layer comprises of [CONV-POOL]                                                                                                                                                                            |

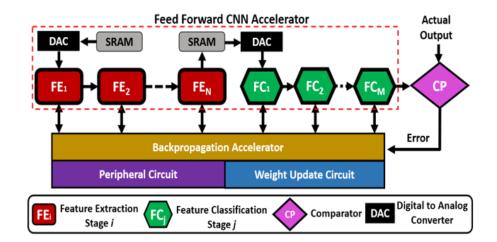

| 5.2  | Overview of <i>BPLight-CNN</i> Architecture                                                                                                                                                                                                                                   |

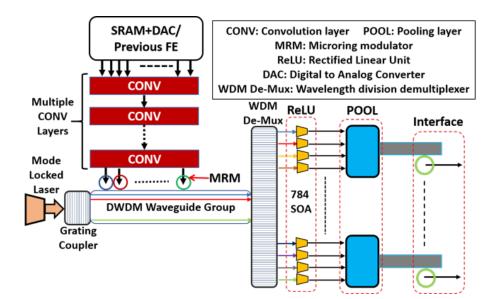

| 5.3  | Microarchitecture of Feature Extractor (FE) in <i>BPLight-CNN</i>                                                                                                                                                                                                             |

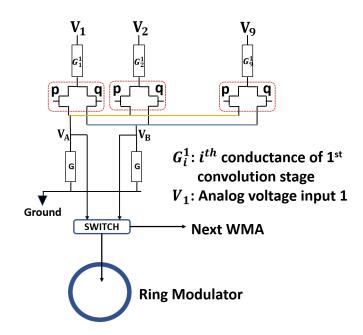

| 5.4  | Memristive convolution in a CONV layer. <i>Reprinted with permission from</i> [9]113                                                                                                                                                                                          |

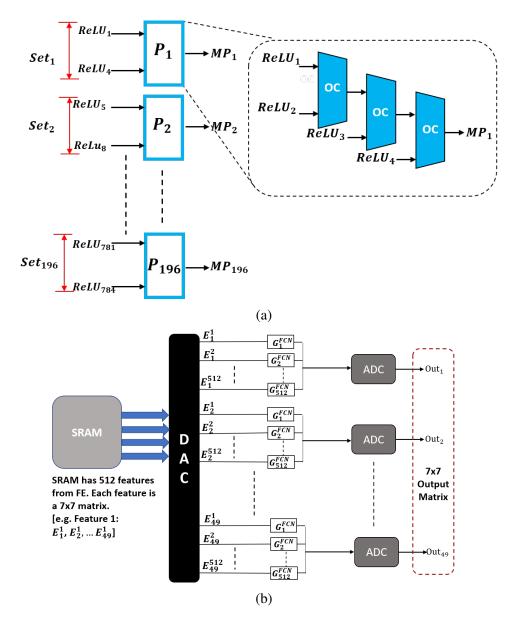

| 5.5  | (a) Cascaded optical comparator in POOL, (b) Fully Connected Layer (FC). <i>Reprinted with permission from</i> [9]116                                                                                                                                                         |

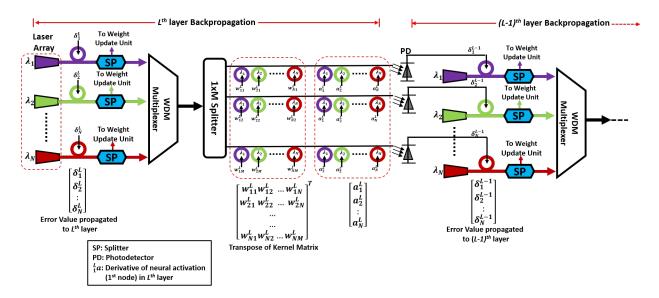

| 5.6  | Backpropagation architecture in <i>BPLight-CNN</i> which presents the backpropagation between the final layer $l = L$ and penultimate layer $l = L - 1$                                                                                                                       |

| 5.7  | Weight Update Circuitry for any layer <i>l</i> 121                                                                                                                                                                                                                            |

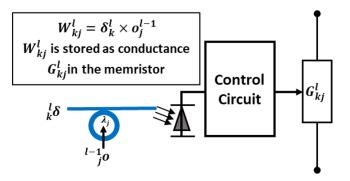

| 5.8  | (a) VGG-A implemented on <i>BPLight-CNN</i> (b) Pipelined dataflow in feedforward operation in <i>BPLight-CNN</i>                                                                                                                                                             |

| 5.9  | CNN Benchmark Configuration for VGG & LeNeT127                                                                                                                                                                                                                                |

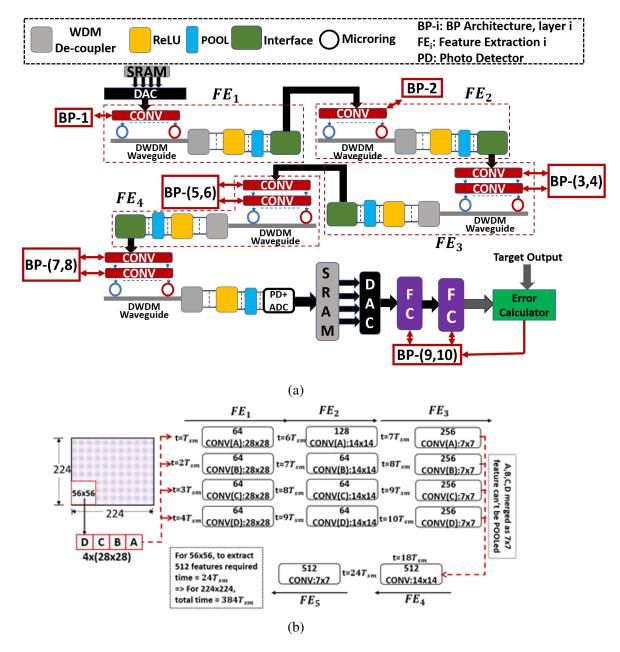

| 5.10 | (a) MRM Q-factor (b) MRM Finesse (c) average prediction accuracy w.r.t propa-<br>gation loss in photonic components diameter (assuming a 32-bit weight resolution). 128                                                                                                       |

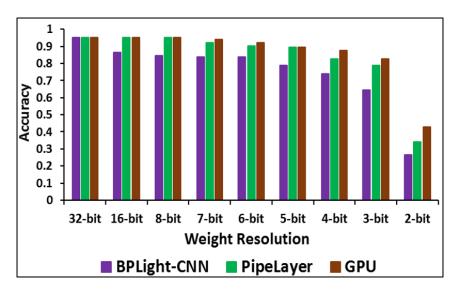

| 5.11 | <i>BPLight-CNN</i> average prediction accuracy comparison with PipeLayer [10] and GPU-based execution across different weight resolutions varying from 2-bit to 32-bit.                                                                                                       |

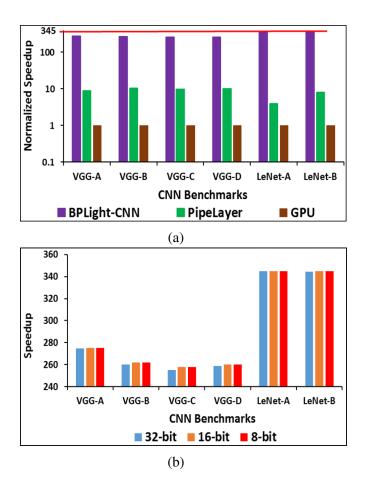

| 5.12 | (a) Normalized speedup (throughput) comparison across accelerators, (b) Speedup of <i>BPLight-CNN</i> w.r.t. weight resolution                                                                                                                                                |

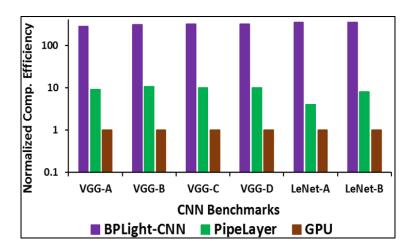

| 5.13 | Normalized computational | efficiency of | of BPLight- | CNN compared | to state-of-the-art. | 132 |

|------|--------------------------|---------------|-------------|--------------|----------------------|-----|

|------|--------------------------|---------------|-------------|--------------|----------------------|-----|

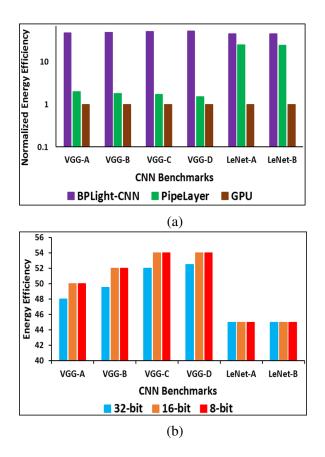

| 5.14 | (a) Normalized energy efficiency across accelerators, (b) Energy efficiency of <i>BPLight</i> - |

|------|-------------------------------------------------------------------------------------------------|

|      | CNN w.r.t. weight resolution                                                                    |

## LIST OF TABLES

| TABLE |                                                                                                                                                                    | Page  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2.1   | Design parameters for experimental setup. <i>Reprinted with permission from</i> [2]                                                                                | . 30  |

| 2.2   | Microring resonator requirement for a 8X8 CMP                                                                                                                      | . 37  |

| 2.3   | Optical losses. Reprinted with permission from [2]                                                                                                                 | . 41  |

| 3.1   | List of TATM parameters and their definitions. Reprinted with permission from [4].                                                                                 | . 56  |

| 3.2   | Properties of materials used by 3D-ICE tool. Reprinted with permission from [4]                                                                                    | . 62  |

| 4.1   | Micro-architectural parameters for MSNoC cluster. <i>Reprinted with permission from</i> [8]                                                                        | . 79  |

| 4.2   | Big data application benchmarks, with three variations each, based on their Master-Servant requirements [11], [12]-[13]. <i>Reprinted with permission from</i> [8] | . 94  |

| 4.3   | Energy and losses for photonic devices [14], [15], [16]. <i>Reprinted with permission from</i> [8]                                                                 | . 96  |

| 4.4   | Phototnic hardware comparison. Reprinted with permission from [8]                                                                                                  | . 101 |

| 5.1   | BPLight-CNN parameter details                                                                                                                                      | . 126 |

#### 1. INTRODUCTION

#### **1.1 High Performance Computing hits the wall!**

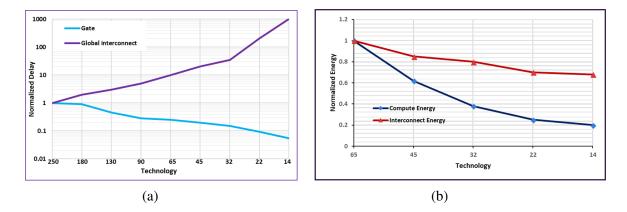

The trend of integrating several computing cores into a single die has seen exemplary rise in the last decade. If the same trend continues we may find more than 200 cores in a single chip by 2025. With the rise in core-density in chip-multiprocessors, the on-chip communication fabric, commonly known as Network-on-Chip (NoC), has become a power and performance bottleneck. This is solely due to the technological limitations of metallic interconnects to scale energy and delay at the same rate as that of a core. As illustrated in Fig.1.1(a), the gap between metallic interconnect delay and gate delay rises rapidly as transistor size shrinks [17]. In addition to that, the scaling in energy consumption of metallic interconnects is very low compared to the scaling in computing core as shown in Fig.1.1(b). The metallic interconnect latency could be reduced by using repeaters; however, that incurs high energy consumption.

Figure 1.1: Comparison of (a) delay of metallic interconnects & gate, and (b) energy-consumption of metallic interconnects & compute core, w.r.t. technology scaling

The speed of metallic interconnects is thus limited by power budget as a result of which further scaling of chip multiprocessors is detrimental. Therefore, it is a general consensus that metallic

interconnects alone will not be able to satisfy the power and performance demands of future manycore processors. This has propelled the research community to explore more efficient interconnect technologies. Silicon photonics with its low-power characteristics and inherent parallism is one such technology.

#### 1.2 Advent of Silicon Photonics

On-chip photonic links, enabled by breakthrough in silicon photonics, provide several advantages over traditional metallic counterparts, such as near light speed data transfer, higher bandwidth density, and low power dissipation. Moreover, photonic links have several times lower datadependent energy consumption compared to electrical wires, enabling the design of high-radix networks that are easier to program. Silicon photonics is thus becoming an exciting new option for on-chip communication, and has catalyzed much research in the area of photonic NoCs (PNoCs) for manycore systems. Silicon photonics could be fabricated monolithically on the same die or on a separate layer through 3D integration, thus forming the foundation of combining electronic and photonic devices in next-generation chip designs.

Establishing silicon photonics as an ideal alternative to electrical interconnect technologies would require strong cases in support of photonics's superiority in terms of both power consumption and performance. This calls for novel photonic on-chip network designs that efficiently utilize photonic links, advances in photonic devices, and automatic CAD tools to assist engineers in the designing process.

#### **1.3** Silicon Photonic Basics

Photonic interconnects and routers are the building blocks of photonic NoCs. A photonic router consists of high-speed microring resonator(MRR) based switches and extremely low-latency photonic waveguides to provide photonic NoC as an alternative to electrical NoCs. Before diving into the details it is better to be familiar with some of the photonic components which are used and to have a understanding of how a simple communication takes place between two cores in a PNoC.

Silicon Photonic Waveguide:- Silicon photonic waveguide is the building block of several photonic components and lays the foundation for integrating photonics with a Silicon substrate. They are the basis of many optical devices such as MRRs, Directional Couplers, Multiplexers and Demultiplexers, communication channel etc. It basically consists of a Si core having an extremely small cross-section sorrounded by  $SiO_2$  cladding material. Due to the difference in refractive index of the core and the cladding the light travels being confined within the waveguide due to total internal reflection.

*MRR*:- Micro-ring resonator is one of the priniciple components of a photonic network-on-chip. As quoted in the Laser and Photoics Reviews, A generic Ring Resonator consists of an optical waveguide which is looped back on itself, such that a resonance occurs when the optical path length of the resonator is exactly a whole number of wavelengths. So in this way a MRR is capable of supporting multiple resonances which have a gap equal to the free spectral range(FSR) which in turn depends on the resonator length. The practical application of the MRR is always along with a coupler which is necessary for it to interact with the outside world. It is basically an accessing mechanism. When in the loop the round trip phase shift equals the integer times  $2\pi$ , resonance occurs and the wave is coupled successfully to or from the MRR.

*Silicon photonic Laser*:- Laser sources can be of different types depending upon the need of transmission. In the proposed design we have used Mode-Locked Lasers which will be described in the upcoming sections. The important fact is that they are the major source of power in a PNoC.

*Photo-detector*:- At the reciever end, the light passing through the silicon waveguide must be detected in order to reconvert the modulated data into electronic form. Photodetectors contain PIN photodiodes to convert optical powerinto electric current. Recently graphene is said to be a promising material for ultra-broadband photodetectors[18].

*Silicon Optical Modulator*:- It is used to modulate a light beam propagating in the optical waveguide with electrical data signals. The most common method of achieving modulation in silicon devices so far has been to exploit the plasma dispersion effect, in which the concentration of free charges in silicon changes the real and imaginary parts of the refractive index[19]. Micro-Ring modulators has been widely explored due to its compact footprint and low drive voltage. The nature resonant frequency of a micro-ring can be shifted by an index change and thus a large modulation depth occurs near the resonance.

*Optical coupler*:- Its a challenge in silicon photonics to obtain efficient coupling between highly confined mode in a waveguide and the large diamter mode in optical fibre to couple light in and out of the chip. Recently several solutions like surface gratings and tapers in which the thickness and width of silicon layer are increased are proposed.

*Silicon photonic transmitter*:- The silicon photonic transmitter comprises of the laser source, optical modulator that modulates the light signal with electric signal data and the multiplexer that multiplexes the signal light of multiple wavelengths or modes in this case to be transmitted on a single transmission line.

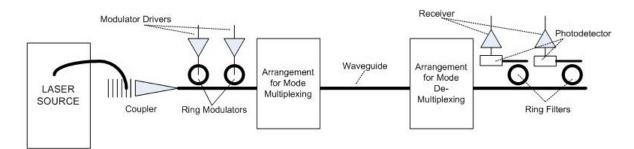

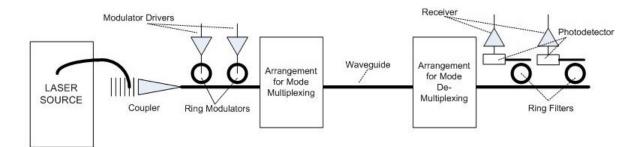

The process of optical communication starts with the laser source producing the light which is coupled into the waveguide on chip with the help of a silicon optical coupler. The Ring modulator along with the multiplexer then modulates the electronic signal from the core on to the appropriate channel. It is transmitted along the waveguide till the destination. The propogation path can be changed or switched by appropriate photonic switches along the path made by the combination of MRRs and waveguides. At the destination the light signal is detected by the photo-detector and is demodulated to feed the information to the destination processor core. The whole process is depicted in the following figure.

Figure 1.2: Communication flow in Silicon Photonics

#### **1.4 Research Focus**

This dissertation focuses on the efficient use of silicon photonics interconnects and devices to design high-performance computing architectures. It begins with the design of a novel ultrafast on-chip photonic router. Such a router is used to design efficient 2D and 3D photonic on-chip network architecture. Further, the dissertation studies the impact of thermal variations in photonic architectures to take necessary measures. In addition to high-throguhput photonic on-chip network architectures, the dissertation also investigates in designing deep learning architectures using photonic-based neuromorphic computing.

#### **1.5** Contributions

The contributions of this dissertation are as follows:

Adaptive Multiplexing in Photonic Network-on-Chip:-In this work, we propose a non-blocking, low power, low-cost, and high performance 5Œ5 photonic router design using silicon microring resonators(MRR). In this router, we introduce wavelength-division-multiplexing (WDM) compatible mode-division-multiplexing (MDM) scheme for maximizing the aggregate bandwidth. The proposed photonic router is utilized to design low-cost and energy-efficient 2D and 3D photonic network-on-chip (PNoC). Laser is found to be the most power hungry element in a photonic system. The proposed PNoCs adopt a novel laser-multiplexing scheme to enhance their energy-efficiency. Our PNoC demonstrates 50% lower energy consumption and 25% lower area overhead compared to the state-of-the-art PNoC designs.

- IHDTM: Islands of Heaters based Dynamic Thermal Management in Photonic Network-on-Chip:-the operation of photonic NoCs (PNoCs) is very sensitive to temperature variations that frequently occur on a chip. These variations can create significant reliability issues for PNoCs. For example, microring resonators (MRRs) which are the building blocks of PNoCs, may resonate at another wavelength instead of their designated wavelength due to thermal variations, which can lead to bandwidth wastage and data corruption in PNoCs. This paper proposes a novel run-time framework to overcome temperature-induced issues in PNoCs. The framework consists of (i) a PID controlled heater mechanism to nullify the thermal gradient across PNoCs, (ii) a device-level thermal island framework to distribute MRRs across regions of temperatures; and (iii) a system-level proactive thread migration technique to avoid on-chip thermal threshold violations and to reduce MRR tuningtrimming power by migrating threads between cores.Our experimental results with 64-core Corona and Flexishare PNoCs indicate that the proposed approach reliably satisfies on-chip thermal thresholds and maintains high network bandwidth while reducing total power consumption by up to 64.1%.

- BigNoC: Application Specific Photonic Network-on-Chip Architecture Big Data Computing:-In the era of big data, high performance data analytics applications are frequently executed on large-scale cluster architectures to accomplish massive data-parallel computations. Often, these applications involve iterative machine learning algorithms to extract information and make predictions from large data sets. Multicast data dissemination is one of the major performance bottlenecks for such data analytics applications in cluster computing, as terabytes of data need to be distributed frequently from a single data source to hundreds of computing nodes. To overcome this bottleneck for big data applications, we propose BiG-NoC, a manycore chip platform with a novel application-specific photonic network-on-chip (PNoC) fabric. BiGNoC is designed for big data computing and exploits multicasting in photonic waveguides. For high performance data analytics applications, BiGNoC improves throughput by up to 9.9Œ while reducing latency by up to 88% and energy-per-bit by up to

98% over two state-of-the-art PNoC architectures as well as a broadcast-optimized electrical mesh NoC architecture, and a traditional electrical mesh NoC architecture.

Neuromorphic Photonic Architecture for Deep Learning:Training deep learning networks involves continuous weight updates across the various layers of the deep network while using backpropagation algorithm (BP). This results in expensive computation overheads while training. As a result, most of the accelerators use pre-trained weights and focus only on improving the design of inference phase. However, the recent trend is to build a complete deep learning accelerator by incorporating the training module. Such efforts require an ultrafast architecture for executing the BP algorithm. In this paper, we propose a novel photonicbased backpropagation accelerator for high performance deep learning training. In addition, we present a design for convolutional neural network, BPLight-CNN, which incorporates the novel photonic backpropagation accelerator. BPLight-CNN is a first-of-its-kind photonic and memristor-based CNN architecture for end-to-end training and prediction. We simulate BPLight-CNN using a standard photonic-based CAD framework such as IPKISS for benchmark models, namely, LeNet and VGG-Net. The proposed design achieves at least 35x acceleration in training in addition to 31x improvement in computational efficiency and 45x energy saving compared to the state-of-the-art designs, without any loss of accuracy.

#### 1.6 Organization

The rest of the dissertation is organized as follows. Chapter 2 illustrates the detailed design of an energy-efficient PNoC architecture with a novel multiplexign scheme. This is followed by demonstration of a dynamic thermal management framework for PNoCs in Chapter 3. Chapter 4 presents an application specific PNoC architecture design for large-scale data analytics applications. Then, Chapter 5 illustrates the design of a complete deep learning accelerator using silicon photonics. Finally, Chapter 6 concludes the dissertation with directions for future research.

#### 2. ADAPTIVE MULTIPLEXING IN PHOTONIC NETWORK-ON-CHIP\*

#### 2.1 Motivation

<sup>1</sup>In the contemporary era, information is generated in abundance. In order to process those information, various efforts have been made to increase the processor performance. According to Moore's law the processor performance doubles up every two years. But until 2000 according to the law the processor speed kept on increasing. After that it was tough to increase the overall performance by increasing the efficiency of a single processor. This limitation or in other words constraint was overcome with the dawn of the era of chip multiprocessors(CMP). As was stated in [20][21] performance gain was to be derived by increase in the number of processor cores on chip. This approach has enhanced the throughput performance in CMPs by exploiting parallellism with less power requirements. Semiconductor roadmap[17] predicts that in the next decade feature size will shrink to sub-10-nm regime. This leap in the process technology will scale the number of cores and threads per devices rather than increase speed or complexity of an indivdual core. This will result in faster processing with the help of thousands of threads running highly parallel codes. But this paradigm shift in the computing world poses newer challenges and issues which needs to be addressed.

Increasing density trend of CMPs involves considerable amount of interaction among the cores on chip. The cores will need to access data from local and distant caches as well as off-chip memory. As a result it requires higher bandwidth and a lower latency to support extensive communication among a large number of cores. Semiconductor NoCs would not provide such a large bandwidth while maintaining an acceptable level of power consumption[17]. The limitation of metallic interconnects in terms of loss, dispersion, cross-talk and speed are becoming increasingly obvious as interconnect density rises. In order to address the growing communication requirements, alternative on-chip interconnect paradigms are required.

Recently, integrated photonic links are being adopted as reliable and attractive alternative to tra-

<sup>&</sup>lt;sup>1</sup>Adapted with permission from [2] & [3]

ditional metallic interconnects [22]. They hold promise to higher rate data transfer with minimal power dissipation [23]. Photonic links avoid capacitive, resistive and signal integrity constraints and allow efficient realization of physical connectivity. Also, *low loss in optical waveguides* [22] and *bit rate transparency* [24] are added advantages of photonic on-chip communication. The key power savings rises from the fact that once a photonic path is established, the data are transmitted end to end without the need for repeating, regenerating and buffering[25]. On the contrary in electrical NoCs messages are buffered, regenerated and transmitted over several router links en route to the destination. In addition to that over the past several years remarkable advances and breakthroughs have been made in the field of silicon photonics. All these support for a high performance, low power, and low cost photonic NoC (PNoC). PNoC is by far the most promising archetype to meet the needs of the next generation on-chip communication.

#### 2.2 Related Works

In recent years several Photonic NoC (PNoC) architectures have been proposed using topologies like mesh [23], torus [22], crossbar[26], and clos[27].

We can classify photonic NoC architectures into two major categories based on the communication techniques used: (1) deterministic passive networks, and (2) dynamic switching networks. Wavelength selective passive networks utilize deterministic switching in which a fixed routing pattern is defined during the network design and the optical path between the source and destination is established by dynamically selecting a specific wavelength at the source or the destination [27]. Passive networks offer limited scalability and complicated design[28]. Whereas optical networks using dynamic switching are circuit switching networks, where the routing pattern is dynamically set beforehand by an electronic controller [23][22]. It is imperative to combine microelectronic control technology and photnic transmission as it is difficult to realize signal processing in photon-ics.

Various crosbar topology based PNoC architecture has been examined by the researchers as in [22][27] and [26]. They have proposed several channel sharing crossbar architectures called Single-Write-Multiple-Read(SWMR) or Multiple-Write-Single-Read(MWSR) architectures. Bat-

ten et al[26] implemented an opto-electrical global crossbar between small groups of cores and DRAM models[26]. Vantrease et al proposed Corona, a 3D MWSR channel sharing crossbar architecture where there is a dedicated channel for listening for each node, but several nodes compete to send messages on the same channel[29]. Pan et al also proposed a SWMR based crossbar design[30]. Though these designs correctly addredssed the latency issues faced by several other contenporary architectures they suffer from scalability as fully connected crossbars do not scale well[31].

Shacham et al proposed a hybrid electrical-photonic NoC architecture[25]. They used a electrical control circuit for arbitration and a photonic message transmission circuit. Though the use of a hybrid architecture was a brilliant idea which we have also followed in our design, the placement of MRRs as photnic switching elements involved turning on more number of MRRs. Though their design provides a higher bandwidth than the electrical NoCs the average latency per throughput is not significantly improved.

Hendry et all proposed a TDM based photonic arbitration circuit due to the absence of photonic buffers which addressed the issue of average latency[32]. But the TDM based arbitration makes the whole communication more deterministic rather than adaptive. Also it results in unnecessary turning on of MRRs in setting up paths between a source and destination.

It is reported in [26] that the wavelength selective passive network exhibits low latency as the wavelength selecting time is much shorter than the network configuration time. On the contrary, switching networks offer higher aggregate bandwidth by adopting WDM technology. Also, circuit switching in optical domain is more compact and it offers good scalability [33]. So among the various architectures discussed above almost all of them prefer a hybrid opto-electronic network.

Router is a critical component of NoC. Several MRR based optical routers have been proposed in the literature [33][23][25][34]. In [33], a low power, low cost, and non-blocking 5X5 optical router has been proposed using 16 MRRs. The design appears to be non-scalable due to significant power consumption when network size increases. In [25], the authors have proposed a  $4 \times 4$  hybrid, blocking router using 8 MRRs. This design is complex and the aggregate bandwidth is limited due to its blocking nature. M. Briere et al proposed the  $\lambda$  router[35]. It uses a passive switching fabric and WDM technology. An  $N \times N \lambda$ -router requires N wavelengths and multiple basic  $2 \times 2$  switching elements to realize non-blocking switching function. In order to fully utilize all the components it prefers N to be even which may not be feasible in every case. The authors in [34] proposed a  $4 \times 4 \lambda$ -router using passive switching fabric with 30 MRRs incorporating Wave Division Multiplexing(WDM). Due to use of increasing number of waveguide crossings and MRRs, such a design results in higher insertion loss rendering it non-scalable. A. W. Poon et al proposed a  $5 \times 5$  optical router based on an optimized crossbar[36]. In this architecture each port of the router is aligned to its corresponding direction to reduce the waveguide crossings around the switching fabric. Therefore a high performance, low power, and low cost photonic router is highly desirable for scalable NoC.

#### 2.3 Contributions

In this chapter, we illustrate the following:-

(1) A novel  $5 \times 5$  non-blocking photonic router design which incorporates *mode-division-multiplexing* in conjunction with *wavelength-division-multiplexing* for high performance. The proposed approach is the first of its kind to the best of our knowledge. (2) A logical layout of the photonic router. (3) Simulation of the proposed design with standard CAD tools which demonstrates  $4 \times$  higher throughput and up to 33% improvement in energy-saving compared to the best reported result. (4) A novel laser-multiplexing scheme for energy-efficient 3D PNoC architectures based on the proposed router.

#### 2.4 Basics Of Silicon Photonics

Optical interconnects and routers are the building blocks of photonic NoCs. A photonic router consists of high speed Microring Resonator(MRR) based switches and extremely low-latency optical waveguides to provide photonic NoC as an alternative to electrical NoCs. Before diving into

the details it is better to be familiar with some of the photonic components which are the building blocks of the proposed PNoC and the associated terminologies. It is also necessary to have an understanding of how a simple communication takes place between two cores in a PNoC.

#### 2.4.1 Silicon Photonic Components

Silicon Photonic Waveguide:- Silicon photonic waveguide is the building block of several photonic components and lays the foundation for integrating photonics with a Silicon substrate. They are the basis of many optical devices such as MRRs, Directional Couplers, Multiplexers and Demultiplexers, communication channel etc. It basically consists of a Si core having an extremely small cross-section sorrounded by  $SiO_2$  cladding material. Due to the difference in refractive index of the core and the cladding the light travels being confined within the waveguide due to total internal reflection.

*MRR*:- Micro-ring resonator is one of the principal components of a photonic network-on-chip. As quoted in the Laser and Photoics Reviews[37], a generic ring resonator consists of an optical waveguide which is looped back onto itself such that a resonance occurs when the optical path length of the resonator is exactly a whole number of wavelengths. So in this way an MRR is capable of supporting multiple resonances with a gap equal to the free spectral range(FSR) which in turn depends on the resonator length. The practical application of MRR is always along with a coupler which is necessary for it to interact with the outside world. It is basically an accessing mechanism. When in the loop the round trip phase shift equals the integer times  $2\pi$ , resonance occurs and the wave is coupled successfully to or from the MRR.

*Silicon photonic Laser*:- Laser sources can be of different types depending upon the need of transmission. In the proposed design we have used Mode-Locked Lasers. The important fact is that they are the major source of power consumption in a PNoC.

*Photo-detector*:- At the reciever end, the light passing through the silicon waveguide must be detected in order to reconvert the modulated data into electronic form. Photodetectors contain PIN photodiodes to convert optical power into electric current. Recently, graphene is said to be a promising material for ultra-broadband photodetectors[18].

*Silicon Optical Modulator*:- It is used to modulate a light beam propagating in the optical waveguide with electrical data signals. The most common method of achieving modulation in silicon devices so far has been to exploit the plasma dispersion effect, in which the concentration of free charges in silicon changes the real and imaginary parts of the refractive index[19]. Micro-Ring modulators has been widely explored due to its compact footprint and low drive voltage. The nature resonant frequency of a micro-ring can be shifted by an index change and thus a large modulation depth occurs near the resonance.

*Optical coupler*:- It is a challenge in silicon photonics to obtain efficient coupling between highly confined mode in a waveguide and the large diamter mode in optical fibre to couple light in and out of the chip. Recently several solutions like surface gratings and tapers are proposed in which the thickness and width of silicon layer are increased.

*Silicon photonic transmitter*:- The silicon photonic transmitter comprises of a laser source, an optical modulator that modulates the light signal with electric signal data and a multiplexer that multiplexes the signal light of multiple wavelengths or modes to be transmitted on a single transmission line.

*Mode-Locked Laser*:- Mode-locked-laser consists of an active laser resonator, and an optical mirror. Laser resonator produces ultra fast optical pulse circulating around it. Each time the pulse hits the optical mirror, a pulse is emitted out of the laser. As a result, an optical pulse train of specific wavelength and time period is generated. This phenomenon is called mode-locking as all the modes are trapped inside the laser resonator as a single pulse and hence the term mode-lockedlaser.

#### 2.4.2 Multiplexing

As mentioned in the introduction, the advent of silicon photonics as an alternative to conventional CMOS chips was imperative owing to its superior bandwidth capability and lower power dissipation. In order to facilitate such a higher aggregate bandwidth several multiplexing techniques have been proposed. The goal of multiplexing is to boost the aggregrate throughput by utilising the existing communication infrastructure on a chip. Over the recent years, with the increase in technical finesse of fabrication technology, researchers have been able to exploit unique features of light to come up with several multiplexing techniques.

#### 2.4.2.1 Wavelength-Division-Multiplexing

Wavelength-Division-Multiplexing(WDM) is the most commonly used technology to increase the bandwidth of the optical communication system. In this scheme multiple wavelengths are employed to carry optical signals from the source to destination. The data rate in optical communication is limited to the modulation speed but the overall bandwidth can be scaled with the no of wavelengths used in a system acting as parallel communication channels.

Dense WDM(DWDM) technology has been used to enable tens of channels with varying carrier wavelengths over single mode optical fibres in long optical networks. But due to its sensitivity to temperature, the emission wavelengths of the laser need to be aligned and stabilized properly. It makes the switching and routing in DWDM systems complicated, power hungry and expensive rendering it unsuitable for on-chip communication[38]. The alternative is coarse WDM(CWDM) which has less requirements in terms of alignment/control. A 4 -channel CWDM link with 400

GHz channel spacing has been used to realize 50 Gbps communication link between two chips[39].

#### 2.4.2.2 Mode-Division-Multiplexing

A mode can be defined as an electromagnetic field distribution that satisfies the theoritical requirements for propagation in a waveguide or oscillation in a cavity or in other words an elect-tromagnetic wave travelling in a fiber. Exploiting spatial mode as an independent channel in conjuction with WDM would increase the bandwidth density of an-chip interconnect by manifolds, reduce the number of waveguide crossings and add an additional design degree of freedom in next generation photonic networks. Earlier there have been efforts of implementing mode multiplexing based on Mach-Zehnder interferometers[40][41], Multi-mode interference(MMI) couplers[42][43] etc. But they had larger footprints and supported a limited number of optical modes.

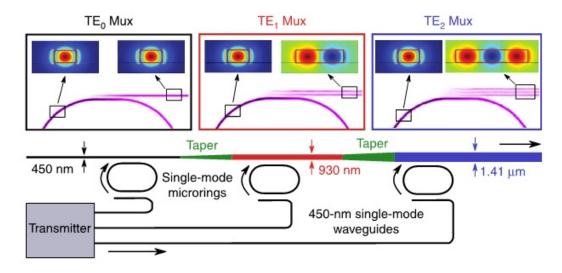

In 2014 Luo et al came up with a micro-ring resonator based on-chip WDM-compatible modedivision multiplexing (and demultiplexing scheme)[1]. They demonstrated the capability of the design to be multiple co-propagating 10Gb/s high-speed communication signals reaching upto 60 Gb/s of aggregate bandwidth.

On the basis of propagation constant matching, an optical mode in a single mode waveguide can be evanescently coupled to a specific spatial mode in an adjacent multimode waveguide, in which the coupling strength to the node depends on the width of the multimode waveguide[1]. The propagation constants of different spatial modes can vary significantly due to the high core-cladding index contrast. In Fig.2.1 taken from [1], the arrangement of the ring resonators and waveguides for facilitating mode multiplexing is shown.

The Ring resonators are formed from a 450-nm wide waveguide. They are designed to support only the fundamental TE mode with effective refractive index( $R_{eff}$ ) of 2.46. The multimodal transfer waveguide is tapered at several places. When the waveguide width corresponds to 450 nm, 930 nm, or  $1.41\mu$ , the effective indices of  $TE_0$ ,  $TE_1$  or  $TE_2$  modes respectively, match the effective index of  $TE_0$  mode of the microring to the  $TE_0$ ,  $TE_1$  or  $TE_2$  modes in the multimode waveguide. By adjusting the coupling gap and coupler length between microrings and waveguides, the insertion loss for the desired mode and the power coupled to other modes can be minimized. All these

Figure 2.1: Selective coupling of the single-mode microrings to a specific spatial mode in multimodal waveguide. *Reprinted with permission from* [1]

features along with an integrated heater on top of each microring to tune the Microring resonances to align to the WDM channels optimizes the performance of the whole device.

Looking at the bigger picture, each microring resonator can support 87 WDM channels over the entire C-band(1530-1565nm) keeping the channel spacing as 50GHz. Luo et al demonstrated that tapering the multimode-waveguide upto  $2.37\mu$ , 5 spatial modes can be supported. With the above setup, potentially an amazing 4.35Tbps aggregate data rate can be supported.

#### 2.4.3 Proposed Adaptive Multiplexing

In our proposed design we adopt the aforementioned WDM-compatible MDM arrangement to design a high throughput and low power consuming photonic router. For our experiments we used two modes each of the two wavelengths we used for communication. The respective MRRs are turned on with the help of an electrical controller whose functional algorithm will be properly described in chapter 3.

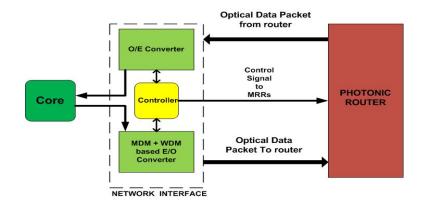

#### 2.5 Communication Flow

The process of optical communication starts with the laser source producing the light which is coupled with the waveguide on chip with the help of a silicon optical coupler. The Ring modulator modulates the electronic signal from the core on to the appropriate channel. The multiplexer's job is to couple the modulated signal onto the desired wavelength and mode in the multimodal transmission fibre. Data is then transmitted along the waveguide till the destination. The propogation path can be changed or switched by appropriate photonic switches along the path made by the combination of MRRs and waveguides. At the destination the light signal is detected by the photo-detector and is demodulated to feed the information to the destination processor core. The whole process is depicted as a symbolic diagram in the following figure.

Figure 2.2: Communication flow in Silicon Photonics

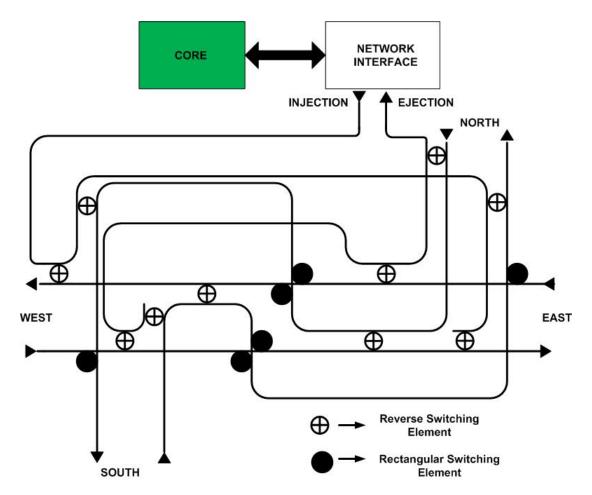

#### 2.6 Photonic Router

The proposed photonic router is a fully non-blocking  $5 \times 5$  photonic router for NoC design. A photonic router in a PNoC consists of a number of I/O ports, a switching fabric connecting the input ports to the output ports, and injection/ejection ports connected to the local IP core via the network interface(NI). Fig.2.3 shows a 2D-mesh PNoC architecture consisting of five-port photonic routers. We zeroed on using a 2D mesh topolgy due to the same reasons that made them popular in electronic NoCs. Their appropriateness to handle a large variety of work-loads and their good layout compatibility with a tiled CMP chip[44] apply in photonic NoCs too.

#### 2.6.1 Router Micro-architecture

The hybrid photonic router consists of mainly two circuits :-

1- Photonic circuit switching circuit 2- Electronic packet switching circuit The PNoC microarchi-

Figure 2.3: 2D PNoC architecture

tecture adopts a hybrid design. It combines a photonic switching fabric for circuit-switched bulk data transmission and an electronic packet-switched network for distributed control through *control packet* transmission. Hence the term 'hybrid' refers to the concept of combining electronic and photonic components as well as to the idea of combining a packet-switched network and a circuit-switched network.

This takes advantage of both the technologies i.e. photonic and electronic. Photonic technology provides superior advantages in terms of low power, large bandwidth and high speed communication. On the other hand, electronic control technology offers flexibility to adopt packet-switching. Packet switching requires buffering which is difficult to implement with photonic components. The main objective of employing a hybrid scheme is to address the higher power consumption in electronic NoCs, that scales up with the bandwidth[21].

The photonic interconnection network consists of MRR and waveguide based routers and links to communicate large data packets. The electronic control network, comprising of an eletrconic controller integrated with each photonic router controls the operation of the photonic network. In this research we mainly focus on the photonic router micro-architecture rather than the electronic controller. In the following subsections we discuss the detailed switching elements and router layout. We will go through the infrastructure responsible for boosting the performance of the photonic router.

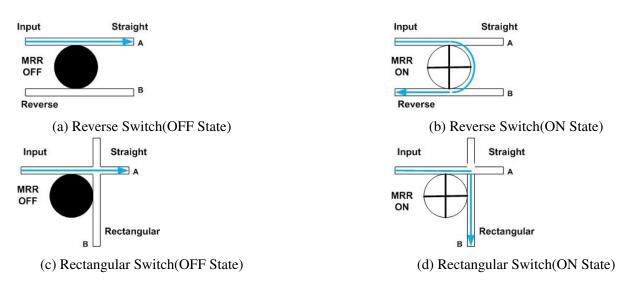

#### 2.6.1.1 Switching Fabric

A switching element in a fabric is composed of MRRs and waveguides as shown in Fig.2.4. The switching fabric consists of a set of parallel and rectangular  $1 \times 2$  switching elements unlike  $2 \times 2$  conventional electrical switches where each  $1 \times 2$  switching element serves the purpose of parallel or orthogonal routing using fewer MRRs. We introduce in brief the working principles of  $1 \times 2$  switching elements used in router micro-architecture.

Basic 1×2 Switching Element using MRR :-

Figure 2.4: MRR Switching. Reprinted with permission from [2]

The basic switching element of a photonic router is a micro-ring resonator. A MRR is a circularly coiled waveguide which has the property of rotating the optical signal in the clock-wise direction. During 'OFF' state of MRR, optical signal with wavelength  $\lambda_{on}$  propagates from the input port to the straight port(refer: Fig.3.8a and Fig.2.4c). When turned 'ON' it couples the resonating optical signal (indicated by arrow) in waveguide A and transmits it by coupling it to waveguide

B as shown in Fig.3.8b and Fig.2.4d. One can see that, in Fig.2.4d as the waveguide B is placed orthogonal to the waveguide A, the MRR helps in turning the optical signal in the rectangular direction. However it involves crossing of the two waveguides which may lead to loss due to cross-talk while passing multiple optical signals. It also results in higher insertion loss. To reverse the direction of propagation of the optical signal, one has to use combination of two rectangular switching circuits resulting in two waveguide crossing points. So, in order to decrease the number of crossing points of waveguides and usage of MRRs, a reverse parallel switching arrangement is made as shown in Fig.3.8b. In this arrangement when the MRR is 'ON', it helps in coupling the optical signal from waveguide A to waveguide B in reverse direction. This mechanism makes MRR an  $1 \times 2$  switching element. With the help of these two types of switching arrangements, we were able to reduce the number of MRRs being used while reducing the no. of waveguide crossing points.