# ADAPTIVE INTEGRATED CIRCUIT DESIGN FOR VARIATION RESILIENCE AND SECURITY

### A Dissertation

by

### JIAFAN WANG

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

| Chair of Committee,    | Jiang Hu                |

|------------------------|-------------------------|

| Co-Chair of Committee, | Edgar Sánchez-Sinencio  |

| Committee Members,     | Peng Li                 |

|                        | Duncan M. (Hank) Walker |

| Head of Department,    | Miroslav M. Begovic     |

August 2017

Major Subject: Computer Engineering

Copyright 2017 Jiafan Wang

#### ABSTRACT

The past few decades witness the burgeoning development of integrated circuit in terms of process technology scaling. Along with the tremendous benefits coming from the scaling, challenges are also presented in various stages. During the design time, the complexity of developing a circuit with millions to billions of smaller size transistors is extended after the variations are taken into account. The difficulty of analyzing these non-deterministic properties makes the allocation scheme of redundant resource hardly work in a cost-efficient way. Besides fabrication variations, analog circuits are suffered from severe performance degradations owing to their physical attributes which are vulnerable to aging effects. As such, the post-silicon calibration approach gains increasing attentions to compensate the performance mismatch. For the user-end applications, additional system failures result from the pirated and counterfeited devices provided by the untrusted semiconductor supply chain. Again analog circuits show their weakness to this threat due to the shortage of piracy avoidance techniques.

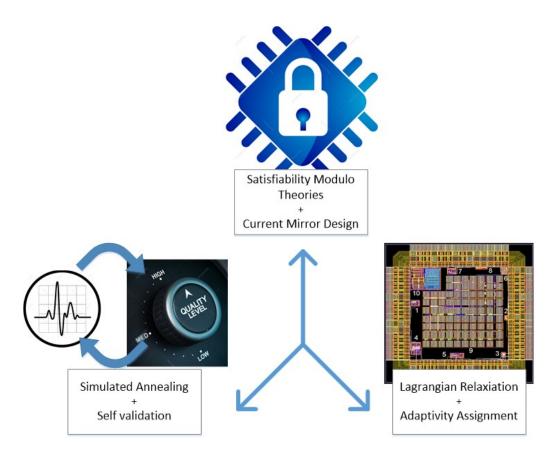

In this dissertation, we propose three adaptive integrated circuit designs to overcome these challenges respectively. The first one investigates the variability-aware gate implementation with the consideration of the overhead control of adaptivity assignment. This design improves the variation resilience typically for digital circuits while optimizing the power consumption and timing yield. The second design is implemented as a selfvalidation system for the calibration of diverse analog circuits. The system is completely integrated on chip to enhance the convenience without external assistance. In the last design, a classic analog component is further studied to establish the configurable locking mechanism for analog circuits. The use of Satisfiability Modulo Theories addresses the difficulty of searching the unique unlocking pattern of non-Boolean variables.

#### ACKNOWLEDGMENTS

Looking back on my five years' pursuit of the doctoral degree, I experienced the confusion at the first year in Texas A&M University, the frustration due to the bottle neck of researches, and the doubt of personal ability after the failure. It is hardly for me to struggle to the end without the help from different people.

First and foremost, I would like to thank my advisor, Professor Jiang Hu, who helps me tremendously both in research and in life. Knowledge is not the only thing he conveys to me but also the rigorous ethic of the work, strict demands on oneself, and tolerant attitude to others. It's my honor to be his student.

Moreover, I wish to express the sincere gratitude to my co-advisor, Professor Edgar Sánchez-Sinencio. He provides me the golden opportunity to prove my idea by chip fabrication and forgives my mistake during the first access to the interdisciplinary project. His trust guarantees our final success.

I also need to give grateful thanks to my lab mates, Hao He, Congyin Shi, Sanghoon Lee, and Adriana Sanabria-Borbon. Working with them in different challenging projects are the best memories of my academic life. They make me believe that team work could move around any obstacles.

I appreciate my parents. They have had no idea of my research since I left them fifteen years ago. However, they always stood by my side whenever I needed their suggestions, financial aid, or just a telephone greeting. I know I shall feel for ever in their debt.

Last but not the least, I want to thank my wife Xuefen Cheng, who gave up her own promising career just to support my academic dream. Her companion and encouragement are the impetuses to make me through the most difficult time during the international study period.

#### CONTRIBUTORS AND FUNDING SOURCES

### Contributors

This work was supervised by a dissertation committee consisting of Professor Jiang Hu [advisor], Edgar Sánchez-Sinencio [co-advisor], and Peng Li of the Department of Electrical & Computer Engineering and Professor Duncan M. (Hank) Walker of the Department of Computer Science and Engineering.

All work for the dissertation was completed by the student, in collaboration with Hao He, Congyin Shi and Adriana Sanabria-Borbon of the Department of Electrical & Computer Engineering.

### **Funding Sources**

The dissertation research is partially supported by National Science Foundation (CCF-1255193, CNS-1618824) and Semiconductor Research Corporation (2013-TJ-2421, 2016-TS-2688).

## NOMENCLATURE

| VLSI   | Very Large Scale Integration                      |

|--------|---------------------------------------------------|

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| LR     | Lagrangian Relaxation                             |

| ABB    | Adaptive Body Bias                                |

| FBB    | Forward Body Bias                                 |

| SSTA   | Statistical Static Timing Analysis                |

| CUT    | Circuit Under Test                                |

| ADC    | Analog-to-Digital Converter                       |

| BPF    | Band Pass Filter                                  |

| SA     | Simulated Annealing                               |

| SS     | Sensitivity Search                                |

| CORDIC | COordinate Rotation DIgital Computer              |

| OTA    | Operational Transconductance Amplifier            |

| ССМ    | Configurable Current Mirror                       |

| SAT    | Boolean Satisfiability Problem                    |

| SMT    | Satisfiability Modulo Theories                    |

| PUF    | Physically Unclonable Function                    |

## TABLE OF CONTENTS

| AB  | STR                                           | ACT                                                          |                                                                         | ii                                                          |

|-----|-----------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------|

| AC  | CKNO                                          | WLED                                                         | GMENTS                                                                  | iii                                                         |

| СС  | ONTR                                          | IBUTO                                                        | RS AND FUNDING SOURCES                                                  | iv                                                          |

| NC  | OMEN                                          | ICLATI                                                       | URE                                                                     | v                                                           |

| TA  | BLE                                           | OF CO                                                        | NTENTS                                                                  | vi                                                          |

| LIS | ST OF                                         | F FIGUI                                                      | RES                                                                     | ix                                                          |

| LIS | ST OF                                         | F TABL                                                       | ES                                                                      | xiii                                                        |

| 1   |                                               |                                                              |                                                                         |                                                             |

| 1.  |                                               |                                                              | CTION OF CIRCUIT ADAPTIVITY IN VERY LARGE SCALE         ION         ION | 1                                                           |

|     | 1.1<br>1.2                                    |                                                              | cance of Circuit Adaptivity                                             | 1<br>2                                                      |

| 2.  | OPT                                           | IMIZA                                                        | TION WITH ADAPTIVE CIRCUIT DESIGN                                       | 4                                                           |

|     | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Backgr<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6 | action                                                                  | 4<br>6<br>8<br>10<br>11<br>12<br>14<br>15<br>15<br>17<br>19 |

|     | 2.4                                           |                                                              | blem Solution                                                           | 20<br>20                                                    |

|    |      | 2.4.3 Iterative Refinement                         | 23 |

|----|------|----------------------------------------------------|----|

|    |      | 2.4.4 Solution for Redundant Counting              | 24 |

|    | 2.5  | Dual Problem Solution                              | 26 |

|    | 2.6  | Experiment Results                                 | 28 |

|    |      |                                                    |    |

| 3. |      | LT-IN SELF OPTIMIZATION FOR VARIATION RESILIENCE   |    |

|    | OF A | ANALOG FILTERS                                     | 34 |

|    | 3.1  | Introduction                                       | 34 |

|    | 3.2  | Background                                         | 36 |

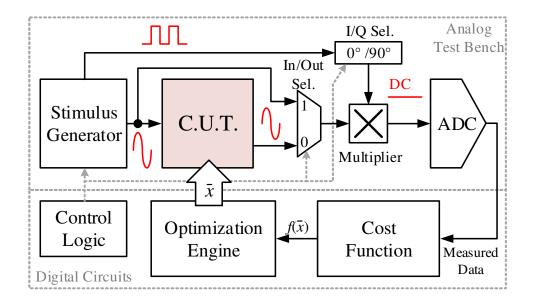

|    |      | 3.2.1 System Architecture                          | 36 |

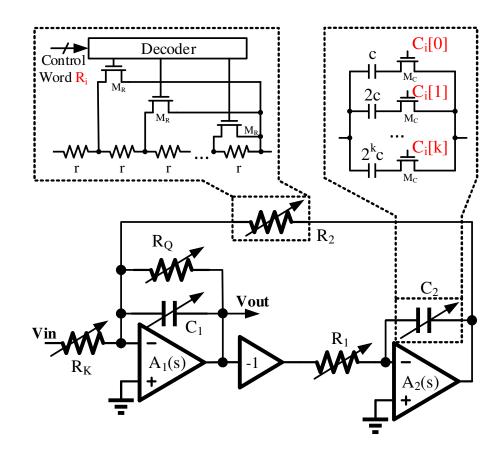

|    |      | 3.2.2 Programmable Bandpass Filter                 | 37 |

|    |      | 3.2.3 Non-ideal Effects                            | 39 |

|    | 3.3  | Cost Function Design and Implementation            | 40 |

|    |      | 3.3.1 Optimization Cost Function                   | 40 |

|    |      | 3.3.2 Circuit Implementation                       | 42 |

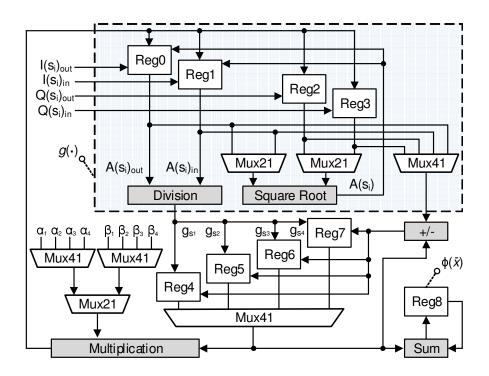

|    |      | 3.3.3 CORDIC Algorithm Based Calculation           | 45 |

|    | 3.4  | Optimization Engine and Implementation             | 46 |

|    |      | 3.4.1 Hybrid Optimization Algorithm                | 46 |

|    |      | 3.4.2 State Machine Diagram                        | 49 |

|    | 3.5  | Reconfigurable Circuit Design and Implementation   | 51 |

|    |      | 3.5.1 Post-silicon Configuration                   | 51 |

|    |      | 3.5.2 General Microprocessor                       | 52 |

|    | 3.6  | Experiment Results for Non-Reconfigurable Circuit  | 54 |

|    |      | 3.6.1 Test Chip Measurement Results                | 54 |

|    |      | 3.6.2 Evaluation of Variation Resilience           | 55 |

|    |      | 3.6.3 Verification of Reconfigurable Circuit       | 57 |

|    |      | 3.6.4 Comparison of Algorithm Performance          | 60 |

|    |      | 3.6.5 Die Photographs for Tapeout Chips            | 63 |

| 4  | TIN  |                                                    | ~  |

| 4. | IHV  | VARTING ANALOG IC PIRACY VIA COMBINATIONAL LOCKING | 66 |

|    | 4.1  | Introduction                                       | 66 |

|    |      | 4.1.1 Previous Works                               | 68 |

|    | 4.2  | Overview and Scope of This Work                    | 69 |

|    | 4.3  | Attack Analysis                                    | 71 |

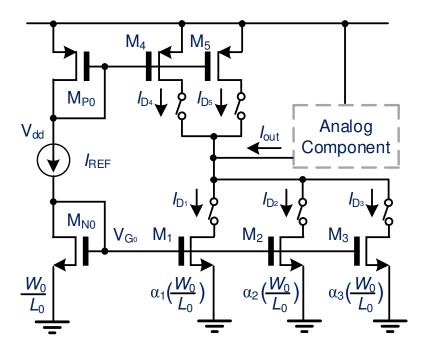

|    | 4.4  | Current Mirror and Its Role in Analog ICs          | 73 |

|    |      | 4.4.1 Basic MOSFET Current Mirror                  | 73 |

|    |      | 4.4.2 Importance of Bias Current                   | 75 |

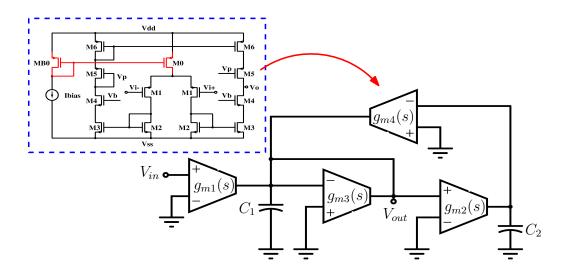

|    |      | 4.4.3 Application in Gm-C Band Pass Filter         | 76 |

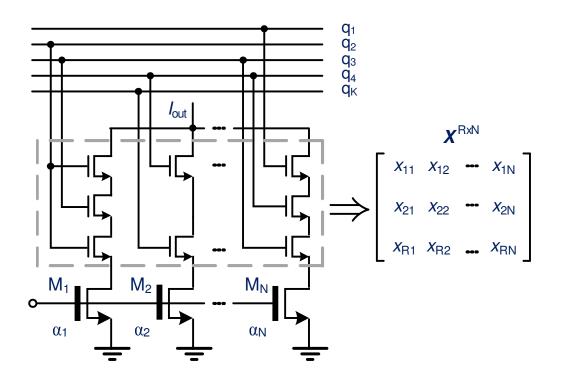

|    | 4.5  | Configurable Current Mirror for Locking            | 78 |

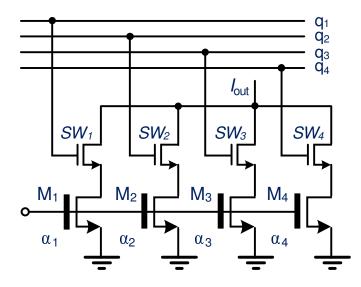

|    |      | 4.5.1 Difficulties of Naïve Configurable Design    | 78 |

|    |      | 4.5.2 A General Locking Architecture               | 80 |

|    | 4.5.3    | Locking Design by Satisfiability Modulo Theories | 82 |

|----|----------|--------------------------------------------------|----|

|    | 4.5.4    | Formulation of SMT Constraints                   | 83 |

|    | 4.6 Expe | riment Results and Discussion                    | 85 |

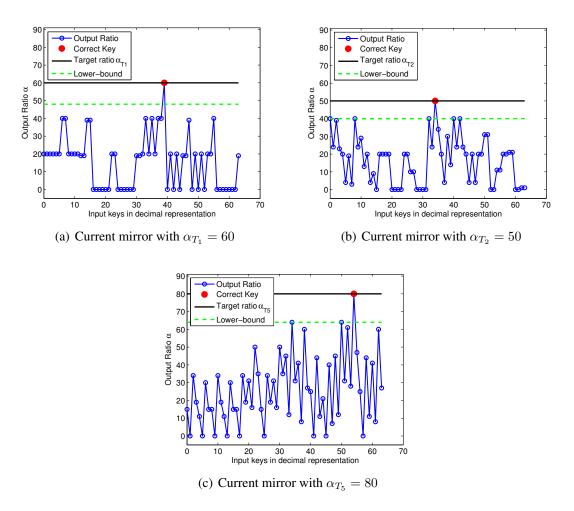

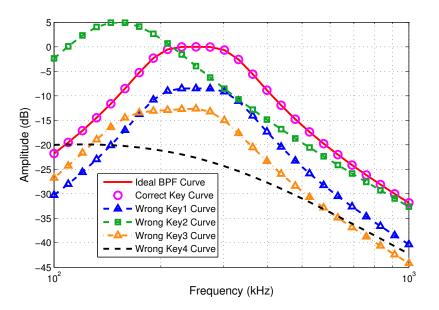

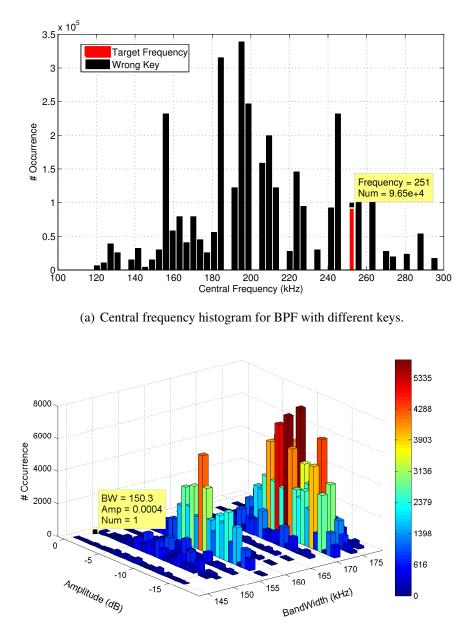

|    | 4.6.1    | Experiment Result of BPF (Band-Pass Filter)      | 85 |

|    | 4.6.2    | Experiment Result of Quadrature Oscillator       | 89 |

|    | 4.6.3    | Experiment Result of LC Oscillator               | 90 |

|    | 4.6.4    | Experiment of Class-D Amplifier                  | 92 |

|    | 4.6.5    | Security Protection Level and Attack Analysis    | 93 |

|    | 4.6.6    | Area and Design Overhead                         | 96 |

| 5. | SUMMAR   | Y AND CONCLUSIONS                                | 98 |

| RE | FERENCE  | S                                                | 99 |

## LIST OF FIGURES

| FIGURE                                         | FIGURE                                                                                                                                                                                                                                                                                                                          |    |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 Circuit adaptivity in different scenarios. |                                                                                                                                                                                                                                                                                                                                 | 3  |

| 2.1                                            | Static timing analysis. (a) Arrival time analysis by forward traversal from primary inputs; (b) Required time analysis by backward traversal from primary outputs.                                                                                                                                                              | 7  |

| 2.2                                            | Adaptive circuit with the control of body biasing                                                                                                                                                                                                                                                                               | 9  |

| 2.3                                            | Different adaptivity assignment schemes. (a) Over-design in gate implementation selection (gate sizing and $V_{th}$ assignment); (b) Under-design and coarse-grained adaptivity; (c) Under design and fine-grained adaptivity; (d) Collaborative gate implementation selection and fine-grained adaptivity. Reprinted from [1]. | 10 |

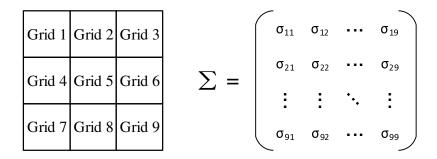

| 2.4                                            | Chip die with 9 grids and its corresponding $9\times9$ covariance matrix                                                                                                                                                                                                                                                        | 15 |

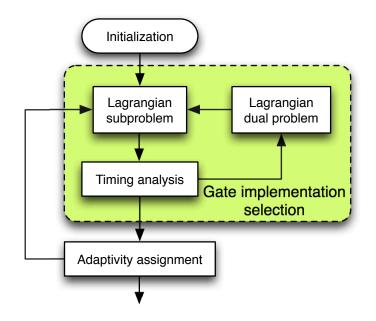

| 2.5                                            | Overview of the adaptivity-aware gate implementation selection algorithm flow. Reprinted from [1].                                                                                                                                                                                                                              | 16 |

| 2.6                                            | Backward topological traverse with inferior pruning.                                                                                                                                                                                                                                                                            | 20 |

| 2.7                                            | Forward topological traverse with solution back trace                                                                                                                                                                                                                                                                           | 21 |

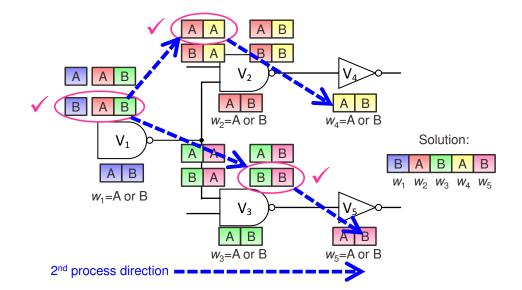

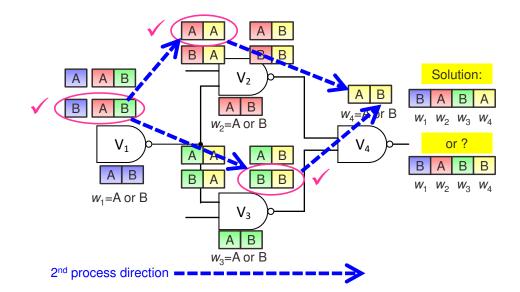

| 2.8                                            | Forward topological traverse with solution inconsistence                                                                                                                                                                                                                                                                        | 22 |

| 2.9                                            | Forward topological traverse with solution restoration                                                                                                                                                                                                                                                                          | 23 |

| 2.10                                           | Backward topological traverse followed by iterative refinement                                                                                                                                                                                                                                                                  | 24 |

| 2.11                                           | Backward topological order solution propagation on DAG. (a) Cost <i>Ld</i> is double-counted at node <i>a</i> . (b) Conventional approach to avoid double counting. (c) Propagation only on spanning tree (in solid edges). Reprinted from [1].                                                                                 | 25 |

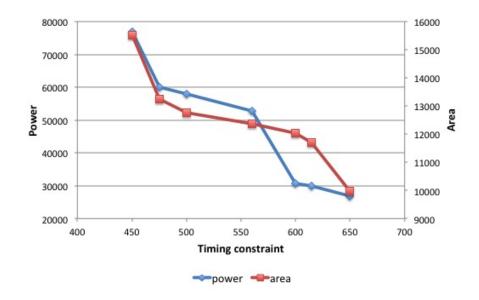

| 2.12                                           | Power/area-timing tradeoff for circuit c7552. Reprinted from [1]                                                                                                                                                                                                                                                                | 33 |

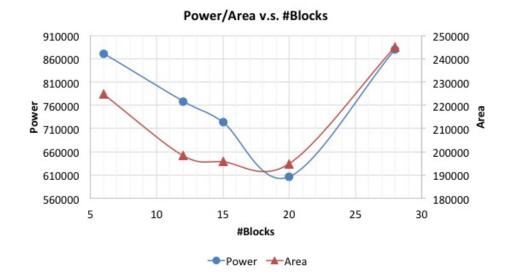

| 2.13                                           | Power/area vs. granularity for circuit fft. Reprinted from [1]                                                                                                                                                                                                                                                                  | 33 |

| 3. | 1  | Overview of the proposed built-in self optimization system architecture.<br>Reprinted from [2]                                                                                                                                                                                                                                                                 | 37 |

|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3. | 2  | Second-order band-pass filter and the configurable resistance/capacitor array structure. Reprinted from [2]                                                                                                                                                                                                                                                    | 38 |

| 3. | 3  | Cost function circuit diagram. Each gray rectangle is an arithmetic block, and each white rectangle is a register. "Reg" implies the resistor, while "Mux21" and "Mux41" represent the 2-to-1 and 4-to-1 multiplexers, respectively.                                                                                                                           | 43 |

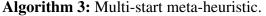

| 3. | 4  | Specific processes during the multi-start meta-heuristic. (a) random update to SA neighbor $(x'_1, x'_2)$ based on the old solution and temperature $T$ in SA. (b) curve of SA acceptance probability based on $\Delta \phi$ and the temperature $T$ . (c) all four neighbors around the $\vec{x}_{best}$ during the SS. (d) LFSR based pseudo random process. | 49 |

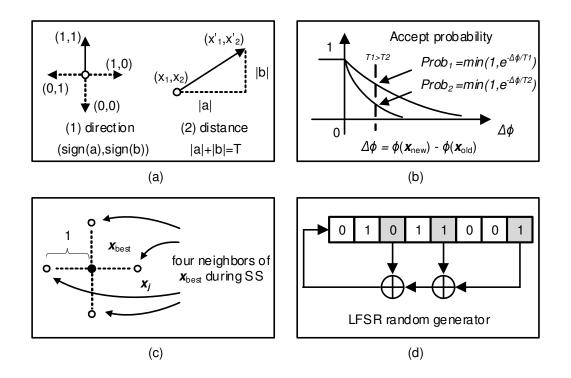

| 3. | 5  | The high-level state machine of multi-start meta-heuristic, in which the upper multi-start SA and the lower sensitivity-based searches are divided by the horizontal dashed line. Reprinted from [2]                                                                                                                                                           | 50 |

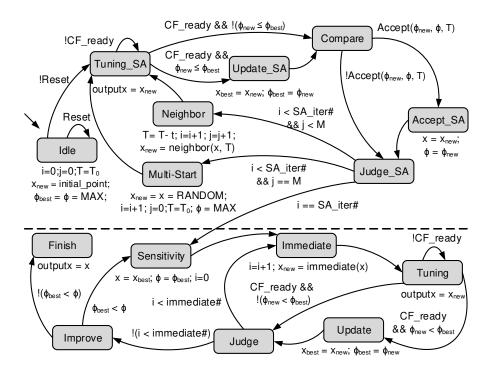

| 3. | 6  | Components of the designed microprocessor and its working flow                                                                                                                                                                                                                                                                                                 | 52 |

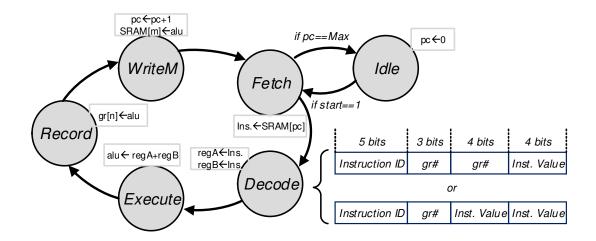

| 3. | 7  | High-level state machine of the microprocessor and 16-bit instructions                                                                                                                                                                                                                                                                                         | 53 |

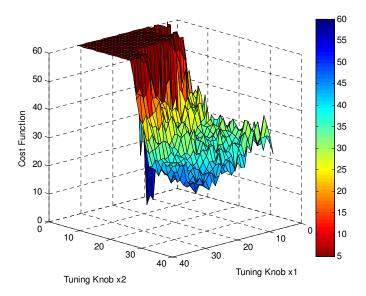

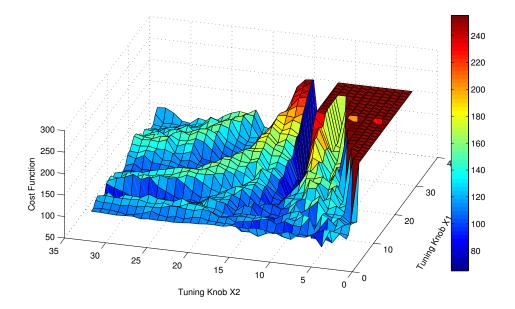

| 3. | 8  | Cost function $\Phi(\vec{x})$ for decision variables $\vec{x} = (x_1, x_2)$ corresponding to $R_{x_1}$ and $R_{x_2}$ in the BPF with $f_c = 31MHz$ and $BW = 8MHz$ . The measurements are based on the test chip. Reprinted from [2]                                                                                                                           | 55 |

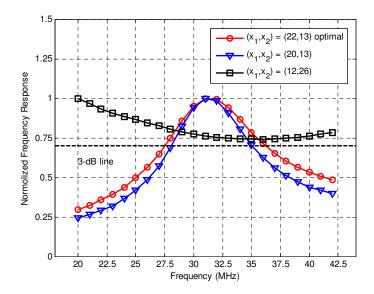

| 3. | 9  | Frequency responses under different decision variables. The design target is the BPF with $f_c = 31MHz$ and $BW = 8MHz$ . Reprinted from [2]                                                                                                                                                                                                                   | 56 |

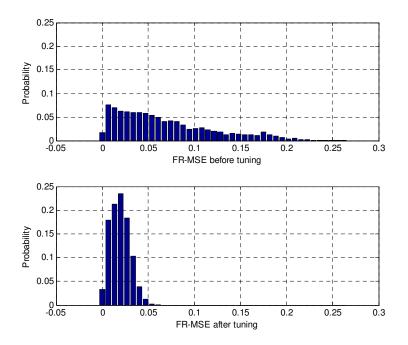

| 3. | 10 | Probability density functions of frequency response mean squared error (MSE) before and after the self optimization from the 5,000-run Monte Carlo simulation on BPF with $f_c = 25MHz$ and $BW = 15MHz$ . Reprinted from [2].                                                                                                                                 | 56 |

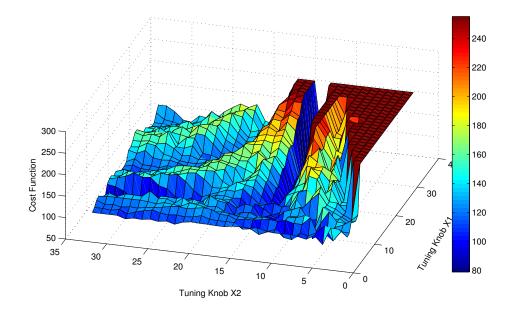

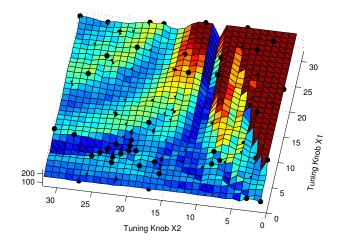

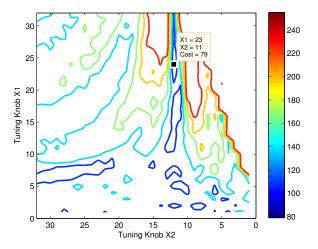

| 3. | 11 | Cost function $\Phi(\vec{x})$ for decision variables $\vec{x} = (x_1, x_2)$ corresponding to $R_{x_1}$ and $R_{x_2}$ in the BPF with $f_c = 74MHz$ and $BW = 13MHz$ . The measurements are based on the test chip                                                                                                                                              | 57 |

| 3. | 12 | Cost function curve calculated by the microprocessor with the same con-<br>figuration in Figure 3.11.                                                                                                                                                                                                                                                          | 58 |

| 3. | 13 | Search trace and optimal point found by the microprocessor                                                                                                                                                                                                                                                                                                     | 59 |

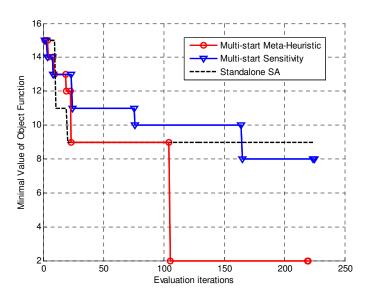

| 3.14 | Cost function changes over iterations for our multi-start meta-heuristic,<br>multi-start sensitivity and standalone SA on BPF with $f_c = 23MHz$ and<br>BW = 6MHz. Reprinted from [2] | 60   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.15 | Cumulative distribution functions of solution errors vs. the optimal solution from the simulation performed on 4,000 BPFs. Reprinted from [2].                                        | 61   |

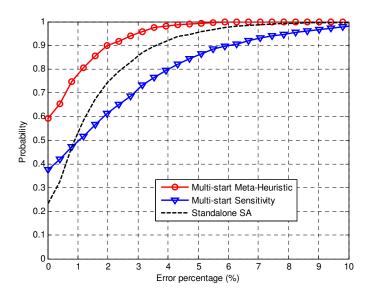

| 3.16 | Chip die photograph of the proposed built-in self-optimization system.<br>CUT includes the active-RC BPF, and the digital circuits are fully inte-<br>grated in one block.            | 63   |

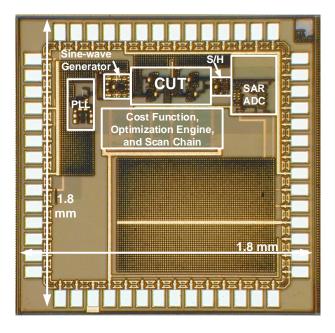

| 3.17 | Chip die photograph of the reconfigurable optimization system including the microprocessor and on-chip SRAM 1024x8 bit.                                                               | 64   |

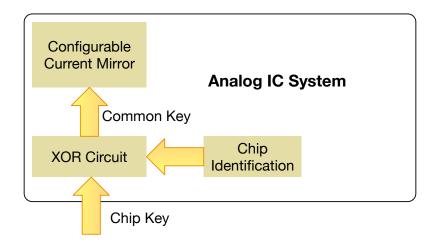

| 4.1  | Locking system overview. Reprinted from [3]                                                                                                                                           | 70   |

| 4.2  | Basic MOSFET current mirror with five finger branches. Reprinted from [3].                                                                                                            | 74   |

| 4.3  | Gm-C implementation of BPF with differential amplifiers. Reprinted from [3].                                                                                                          | . 76 |

| 4.4  | A naïve design of configurable current mirror. Reprinted from [3]                                                                                                                     | 78   |

| 4.5  | An example of the proposed locking architecture. Reprinted from [3]                                                                                                                   | 80   |

| 4.6  | Bias currents from different keys for three current mirrors in the 4th order BPF. Reprinted from [3].                                                                                 | 86   |

| 4.7  | Normalized frequency responses of the 4th-order BPF with $f_c = 250kHz$<br>and $BW = 150kHz$ , for different keys. Reprinted from [3]                                                 | 87   |

| 4.8  | Only one key makes the BPF satisfying $f_c = 250kHz$ , $BW = 150kHz$<br>and $Amplitude = 0dB$ . Reprinted from [3].                                                                   | 88   |

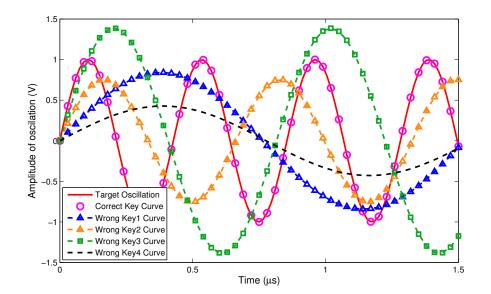

| 4.9  | Normalized oscillation frequencies of the quadrature oscillator with $f_{osc} = 2.34MHz$ , affected by different keys. Reprinted from [3]                                             | 89   |

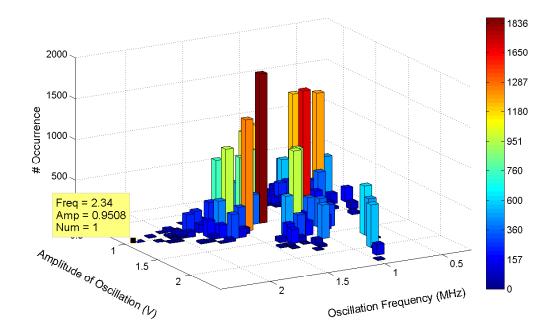

| 4.10 | Oscillation frequency and amplitude histogram of the quadrature oscillator with $f_{osc} = 2.34MHz$ , for different keys. Reprinted from [3].                                         | 90   |

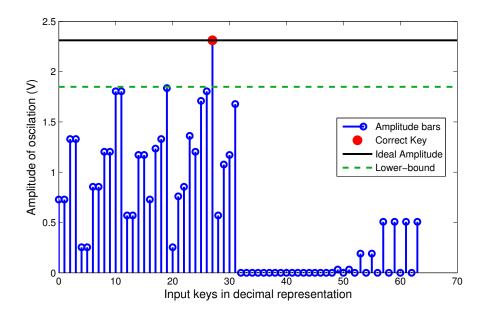

| 4.11 | Oscillation amplitudes of the LC oscillator with $f_{osc} = 2GHz$ for all combinations of 6-bit key for CCM7. Reprinted from [3].                                                     | 91   |

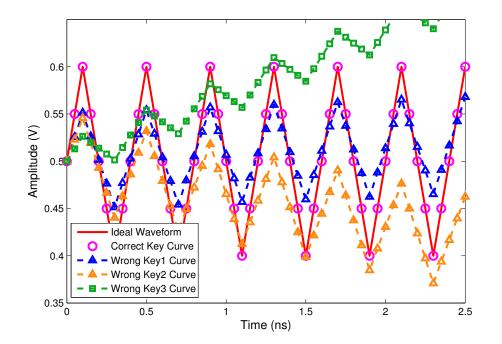

| 4.12 | Triangular waveforms of the generator for different keys for two current mirrors, CCM9 and CCM10. Reprinted from [3]                                                                  | 92   |

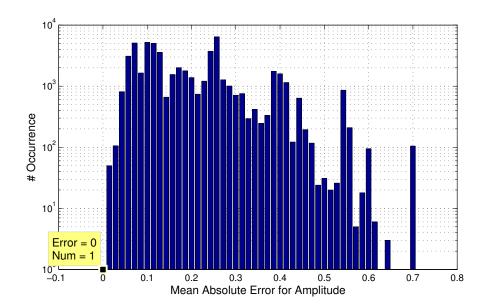

| 4.13 | Amplitude error histogram of the triangle generator with $\Delta = 30\%$ and $\Theta = \infty$ , for different keys. Reprinted from [3]. | 93 |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

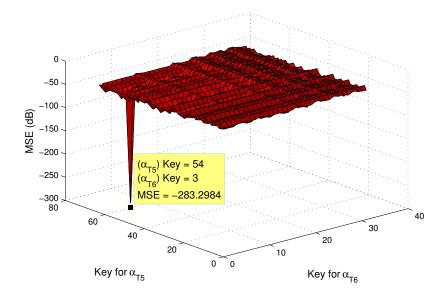

| 4.14 | MSE curve in the second stage of the 4th order BPF satisfying $f_c = 250kHz$ , $BW = 150kHz$ and $Amplitude = 0dB$ . Reprinted from [3]  | 95 |

## LIST OF TABLES

| TABLE |                                                                                                                                                                                                                            | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Experimental results of Naïve method with only forward body bias (FBB). Total area overhead and power overhead are denoted by $\Delta A$ and $\Delta W$ , respectively. Reprinted from [1].                                | 29   |

| 2.2   | Experimental results of our method with only forward body bias (FBB). Gate area, total area and power overhead are denoted by $\Delta A_g$ , $\Delta A$ , and $\Delta W$ , respectively. Reprinted from [1]                | 30   |

| 2.3   | Experimental results of Naïve method with forward body bias and reverse body bias (ABB). Total area and power overhead are denoted by $\Delta A$ and $\Delta W$ , respectively. Reprinted from [1]                         | 31   |

| 2.4   | Experimental results of our method with forward body bias and reverse body bias (ABB). Gate area, total area and power overhead are denoted by $\Delta A_g$ , $\Delta A$ and $\Delta W$ , respectively. Reprinted from [1] | 32   |

| 3.1   | Usage of registers within the summation circuit.                                                                                                                                                                           | 44   |

| 3.2   | Gate count, power and processing time comparison. Reprinted from [2].                                                                                                                                                      | 62   |

| 3.3   | SRAM memory space consumption for microprocessor                                                                                                                                                                           | 62   |

| 4.1   | Area overhead and key bitwidth. Reprinted from [3]                                                                                                                                                                         | 96   |

| 4.2   | Runtime for solving the SMT for different bitwidths. Reprinted from [3]                                                                                                                                                    | 97   |

# 1. INTRODUCTION OF CIRCUIT ADAPTIVITY IN VERY LARGE SCALE INTEGRATION

#### 1.1 Significance of Circuit Adaptivity

In adaptive integrated circuits (ICs), the word "adaptive" implies the feature of circuit modifications after the hardware fabrication. As the increasingly scaling of IC process technology, the necessity of this feature is enhanced by the exacerbation of parametric variations in transistors' attributes, such as geometry size, oxide thickness, doping density, etc. These interior mismatches further cause the measurable loss to the output performance.

For example, when process technology scales down from 350 nm to 90 nm, chip yields reported by the foundries have reduced from nearly 90% to 50% [4]. This situation is even worse at Taiwan Semiconductor Manufacturing Company's (TSMC's) 10 nm process, such that a unexpected low yield rate for Apple's A10X chips is likely to disrupt the production schedule of iPad in March 2017 [5]. Besides process variations, aging effects manifest themselves as another major source of characteristic changes of devices, particularly analog circuits. For a Class A amplifier designed in a 65 nm process, the simulation based on the Channel Hot Carrier degradation (CHC) model indicates a significant gain loss of 15% over ten years' lifetime [6]. Moreover, the early in-use system failures caused by the pirated and counterfeited components could be regarded as a severe form of performance degradation, which has now turned into an emerging threat to the global IC security. Again, a study by IHS technology [7] presents that analog ICs rank the first out of five most counterfeited semiconductors due to their relative large size compared to digital circuits and the shortage of piracy avoidance techniques.

To overcome the above challenges, circuit adaptivity shows its significance in differ-

ent stages of the very large scale integrated (VLSI) circuit design. For example, during the design time, the adaptivity circuits, with the ability of body bias control or voltage adaptation, are technically introduced to the original system. They will be invoked later by the timing violation detectors at runtime and compensate the performance degradation by modifying the body bias or supply voltage. Another scenario to apply the adaptivity is the post-fabrication tuning. Essentially relying on the in-situ configurable structure, circuit performance could be calibrated towards the designed specifications whenever it's needed before the advent of final wear-out stage. Furthermore, the circuit adaptivity may contribute to the field of hardware security. Similar to the digital lock, the adaptive circuit won't enable the whole design until the correct keys are provided. Otherwise it locks the system by malfunction or even entire breakdown.

#### **1.2 Difficulties and Algorithms**

Despite the significance of circuit adaptivity, to figure out the appropriate ways of considering the adaptivity is not an easy task under different situations. For instance, to compensate the variations during the design time, the conventional optimization has to be re-formulated with the introduction of the variation property. The run-time calibration method will be limited to the area consumption of the tuning strategy if it is implemented on chip. And the protection level of the key-lock scheme will be weakened in case the configurable circuits are not well designed.

In this dissertation, we proposed systematic ways to assign the circuit adaptivity. In Chapter 2, a Lagrangian Relaxation based algorithm is further improved to optimize the gate implementation under the process variations. Body bias is applied as an additional dimension to minimize the system power assumption, while the adaptivity overhead is also handled in the optimization function. The stochastic evaluation is executed to analyzed the circuit timing to maintain the performance with a high probability. In Chapter 3, a

Figure 1.1: Circuit adaptivity in different scenarios.

self calibration design is implemented on-chip to adjust the performance of analog circuits towards the designed specifications. The calibration circuit is based on meta-heuristic with the balance between computation complexity and searching quality. The effectiveness of the circuit is demonstrated by both the chip measurement and simulation. In Chapter 4, inspired from the variation-sensitive analog circuits, we upgrade the common used current mirror as a locking structure to supplement the lack of protection to the analog system. Depending on the satisfiability module theories, the locking structure is so well designed that it could only be opened by a unique key out of numerous candidates, while all other keys will lead to the system malfunction or totally breakdown.

#### 2. OPTIMIZATION WITH ADAPTIVE CIRCUIT DESIGN\*

#### 2.1 Introduction

As a power-efficient approach to variation resilience, adaptive circuit design has been demonstrated the effectiveness by results from test chips using body biasing [8], voltage interpolation [9], circuit reconfiguration [10] or a combination of them. The purpose of these changes is to compensate the performance variability due to manufacturing process variations [8], device aging effect [11], and thermal fluctuations [12] while to bring power savings to the whole circuit.

Although numerous adaptive design techniques have been reported, the adaptivity overhead is only mentioned in several previous works [10, 13, 14], and has rarely been a main emphasis. Actually, the overhead of adaptive design highly depends on its granularity. Coarse-grained adaptivity, such as uniform adaptivity for an entire processor core, has relatively small amortized overhead. For example, if a processor core has only one critical path replica based sensor, the area overhead is only 0.2% [15]. When intra-die variations are more pronounced [16], fine-grained adaptivity [9, 14] (in blocks of hundreds or thousands of gates) allows the compensation to be applied in a pinpoint manner. Evidently, fine-grained adaptivity tends to entail large overhead of sensors, voltage regulators and control circuits. This can cause as much as 50% area overhead for voltage interpolation [13] and 20% in [10, 14].

In addition to the area overhead, the effectiveness of power saving also largely depends on the granularity. For example, many variation effects are intrinsically fine-grained. Therefore, two adjacent transistors may have different doping densities due to process fluctuations. If adaptivity is coarse-grained, e.g., an entire processor core adapts uniformly, the

<sup>\*</sup>Reprinted from "Collaborative Gate Implementation Selection and Adaptivity Assignment for Robust Combinational Circuits", by Hao He, Jiafan Wang, Jiang Hu, ©2015 IEEE.

adaptation must aim at transistors with the most critical timing requirement on the core. Evidently, this is hardly an efficient use of power. By contrast, fine-grained adaptivity, in blocks of hundreds or thousands of gates, speeds up the critical components with the cost of increasing additional power within a small region while keeps other non-critical components working in a large and low power state, thus enables power saving to the whole circuit in spite of the large area overhead.

Obviously, one prefers the power savings from fine-grained adaptivity but not its large overhead. Nevertheless, there are very few works on the optimization of adaptive circuit, especially the control of its overhead. One attempt is to perform gate clustering. In [17], an algorithm is introduced for joint design-time and post-silicon tuning optimization, but with little attention on the overhead issue. Moreover, it assumes that gate size can be continuously changed while most of modern designs are based on highly discrete cell libraries. The objective of [18, 19] is to minimize the overhead of adaptive body biasing (ABB). These works attempt to cluster gates with similar timing criticality and variability and are very useful in deciding adaptivity granularity, but they assume ABB is applied to all clusters. Another work [20] restricts variation sensors only at timing critical paths so that the overhead is not excessively large. However, it does not consider control or voltage generation overhead. Variability-aware discrete gate sizing is discussed in [21, 22]. These works are focused on how to propagate statistical timing information during sizing without much emphasis on the optimization aspect.

In this chapter, we develop a general algorithm framework for the optimization of adaptive circuit design with the consideration of overhead control [1]. Since adaptivity optimization is closely related with gate implementation selection (gate sizing and threshold voltage assignment), we perform them jointly such that their efforts are concerted with each other. Evidently, variations must be accounted and make the optimization problem rather difficult. We make use of Lagrangian relaxation that solves a multi-objective problem in two layers – subproblem and dual problem. The subproblem is focused on solution search while the dual problem can employ variability-aware models to guide the tradeoff among multiple objectives. As such, accurate models are used in a lightweight manner without causing too long runtime. The main advantages of our approach includes the following:

- 1. Compared to [17], which is restricted to linear and continuous models, our work is a discrete approach and compatible with realistic models in industry.

- 2. Our work provides a relatively complete adaptivity assignment solution for general adaptive circuit designs while the works of [18, 19] focus on clustering and ABB.

- 3. A new technique to solve the over-counting problem with less cost estimate error is proposed in our work, without increasing the overall algorithm complexity.

- 4. Area overhead is explicitly handled in our work but neglected in [17]. Experimental results on benchmark circuits confirm the effectiveness of our method.

#### 2.2 Background

### 2.2.1 Timing Constraint and Gate Implementation

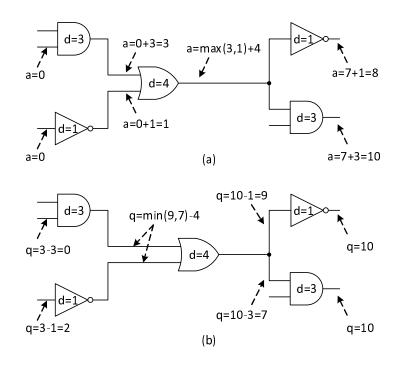

One target of the physical design of digital circuits is to derive the timing satisfied circuit, which defines that all signals arriving at the primary inputs at time a should reach the primary outputs no later than q, given the gate delay d of each cell. Since the timing information is only given at the primary inputs and primary outputs, the satisfaction of the whole circuit is guaranteed by the sufficient and necessary condition that all the arrival times derived from a in Figure 2.1 (a) shouldn't be later than the required arrival times derived from q in Figure 2.1 (b) at every net within the circuit. Since the delay is fixed when the circuit design is done, this analysis method is also named as the Static Timing Analysis (STA).

Need to mention that, for the multi-fanin gate, signals might arrive at the input pins of

Figure 2.1: Static timing analysis. (a) Arrival time analysis by forward traversal from primary inputs; (b) Required time analysis by backward traversal from primary outputs.

$v_m$  at different times in Figure 2.1 (a). Here the latest arrival time at the output of this gate is considered by  $a_m = max_{i \in fanin(m)}(a_i + d_m)$ , which could make sure the timing analysis work under the worst case signal propagation. Similar situation happens in Figure 2.1 (b) for the gate  $v_m$  due to its multiple fanouts. Still followed by the worst case guarantee of signal propagation, the required arrival time at the input of this gate is obtained by  $q_m = min_{j \in fanout(m)}(q_j - d_m)$ . Therefore, the time slack defined by (q - a) at each point in the circuit could be used as a variable to evaluate the gate implementation.

Gate implementation is a classic technique during the physical design of digital circuits. It determines the gate size and threshold voltage of each gate so as to minimize the total power consumption of the circuit subject to the timing constraints. Under different implementations of each gate size and threshold voltage, the delay information d of an individual gate in Figure 2.1 will vary, and then affect the global timing status of the circuit.

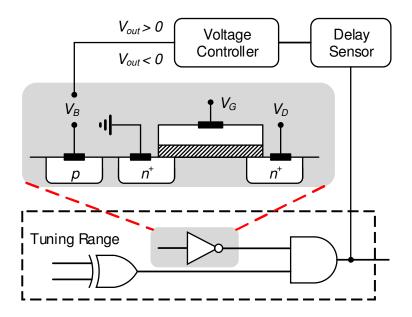

#### 2.2.2 Adaptive Body Biasing

ABB technique is based on the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) body effect, which refers to the change in the transistor threshold voltage  $V_{th}$ . An analytical equation (2.1) shows the dependence of  $V_{th}$  on the source-to-body bias  $V_{SB}$  as follow.

$$V_{th} = V_{th0} + \gamma (\sqrt{|V_{SB} - 2\phi_F|} - \sqrt{|2\phi_F|}), \quad V_{SB} = V_S - V_B$$

(2.1)

where  $V_{th0}$  is the threshold voltage with zero body bias ( $V_{SB} = 0$ ) and is achieved by tying the substrate on the die to the source, e.g. power supply  $V_{DD}$  (in case of PMOS) or ground (in case of NMOS).  $\phi_F$  and  $\gamma$  are the Fermi potential and the body effect parameter, respectively.

The effect of  $V_{th}$  to the subthreshold leakage current  $I_{subn}$  and the gate delay d is further revealed in [18]

$$I_{subn} = K_1 e^{\frac{V_{GS} - V_{th}}{n\nu_T}}$$

$$d = \frac{K_2}{(V_{DD} - V_{th})^{\alpha}}$$

(2.2)

where  $\alpha$  is the velocity saturation index,  $\nu_T$  is the thermal voltage and n is the subthreshold swing coefficient.  $K_1$  and  $K_2$  are the factors related to the original subthreshold leakage current and gate delay, respectively.

As for the total power model, we apply  $P = P_{dyn} + P_{leakage}$ , where  $P_{dyn}$  is the dynamic power, and  $P_{leakage}$  includes the leakage mechanisms affected by  $V_{th}$ , especially the subthreshold leakage  $P_{subn} = V_{DD}I_{subn}$ . For other leakage components, such as bodysource/drain junction diode leakage, and band-to-band tunneling, we didn't consider them in our design, yet the optimization method introduced in Section 2.3 could be extended by adding them to the target function.

Thus, by manipulating the body voltage  $V_B$ , the adaptive circuit which consists the delay sensor and voltage controller is able to adjust all the  $V_{th}$  of NMOS gates in the dashed line rectangle of Figure 2.2, and then affects the leakage power and circuit delay in that area. For example, a positive body voltage ( $V_B > 0$ ) will decrease the adjusted threshold voltage  $V_{th}$  and result in a larger current  $I_{subn}$  and smaller transistor delay d according to (2.2). This is called the Forward Body Biasing (FBB), while the similar analysis can be applied to Reverse Body Biasing (RBB) if  $V_B < 0$ . Need to mention that, all the gates within the tuning range of the certain adaptive circuit will follow the same body bias configuration. Therefore, in a FBB-only adaptive circuit, the tuning range is usually applied to cover to the critical path.

Figure 2.2: Adaptive circuit with the control of body biasing.

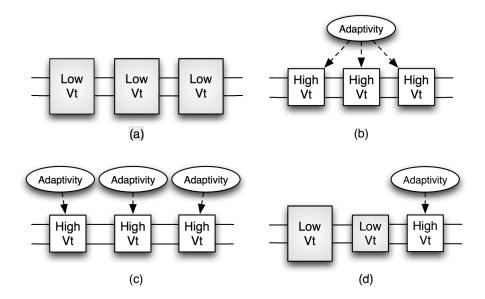

#### 2.2.3 Adaptivity Assignment Scheme

Regarded as the redundancy to the original circuit design, the adaptive circuit makes the effectiveness as well as overhead highly dependent on its granularity. Besides, the existing of adaptive circuit also affects the gate sizing and threshold voltage assignment within its control range. Therefore, the adaptivity assignment scheme is highly related with the conventional gate implementation selection.

Figure 2.3: Different adaptivity assignment schemes. (a) Over-design in gate implementation selection (gate sizing and  $V_{th}$  assignment); (b) Under-design and coarse-grained adaptivity; (c) Under design and fine-grained adaptivity; (d) Collaborative gate implementation selection and fine-grained adaptivity. Reprinted from [1].

Without considering prospective adaptivity, gate implementation selection tends to result in over-design like in Figure 2.3 (a), which entails large power dissipation. An arbitrary anticipation of adaptivity may lead to under design in gate implementation selection. If the under design is fixed by coarse-grained adaptivity like in Figure 2.3 (b), the power efficiency is still poor as the adaptivity power is applied according to the worst place in a circuit. A fine-grained adaptivity like in Figure 2.3 (c) has a large area overhead for compensating the under-design. In our proposed collaborative optimization, gate implementation and adaptivity help each other and thus may provide solution with both high power-efficiency and low adaptivity overhead like in Figure 2.3 (d).

#### 2.2.4 Lagrangian Relaxation

Lagrangian Relaxation is an efficient mathematical optimization framework used to solve the optimization problems with tough constraints. For example, the optimization problem could be formulated as follow

Minimize

$$f(\vec{x})$$

(2.3)

s.t.  $g_1(\vec{x}) \leq 0, g_2(\vec{x}) \leq 0$

$\vec{x} \in X$

where  $f(\cdot)$  is the objective function related to decision variables x, which belong to the finite solution space X.  $g_1(\cdot)$  and  $g_2(\cdot)$  are the "hard to solve" and "easy to solve" inequality constraints, respectively. By "hard to solve", we actually mean the constraints similar to (2.7) or (2.8) which are hardly to be solved in a linear time or denoted by a straightforward analytical form.

The Lagrangian relaxation is achieved by multiplying the constraint violation with weighting factors (Lagrangian multipliers), and then moving the weighted terms into the objective function as penalties. For example, after the relaxation of  $g_1(\vec{x})$ , the optimization

problem in (2.3) is converted as follow

Minimize

$$\mathcal{L}(\vec{\lambda}, \vec{x}) := f(\vec{x}) + \vec{\lambda} \cdot g_1(\vec{x})$$

(2.4)

s.t.  $g_2(\vec{x}) \leq 0, \ \vec{x} \in X$

where  $\mathcal{L}(\vec{\lambda}, \vec{x})$  is named the Lagrangian function, and the vector of Lagrangian multipliers  $\vec{\lambda}$  should be non-negative and have the same dimension as  $g_1(\vec{x})$ . The relaxed problem in (2.4), or namely Lagrangian subproblem, derives the fancy property of concavity since it is the lower envelope of a finite linear functions of  $\vec{\lambda}$ . Thus, it could be handled by the well-studied convex optimization algorithms.

Moreover, if  $\lambda \ge 0$  and  $g_1(\vec{x}) \le 0$ , then it's apparent that the objective function  $\mathcal{L}(\vec{\lambda}, \vec{x}) = f(\vec{x}) + \vec{\lambda} \cdot g_1(\vec{x})$  in the relaxed problem (2.4) is less or equal to  $f(\vec{x})$  in the original problem (2.3). To minimize the gap, the dual problem is defined in (2.5). It could be further proved that if  $\vec{\lambda}^*$  is the optimal solution of the dual problem, then the optimal solution of  $\mathcal{L}(\vec{\lambda^*}, \vec{x})$  will also optimize the original problem.

Maximize

$$\mathcal{L}(\vec{\lambda}) := min\mathcal{L}(\vec{\lambda}, \vec{x})$$

(2.5)

s.t.  $\vec{\lambda} \ge 0$

#### 2.2.5 Application in Gate Implementation Selection

To formulate the problem of gate sizing and threshold voltage assignment by applying Lagrangian relaxation, the circuit is first described as a directed acyclic graph (DAG) G(V, E), where the vertexes set V includes all the gates, and each edge  $(v_i, v_j)$  of set E represents the wire connection between gate  $v_i$  and  $v_j$  [23]. Besides, arrival times a at the primary input gates I(G) and required arrival times q at the primary output gates of G are also given. Then, the gate size  $w_i$  and threshold voltage  $h_i$  of each gate  $v_i \in V$  is determined as

Minimize

$$\sum_{v_i \in V} p(v_i)$$

(2.6)

s.t.

$$q(v_i) \ge a(v_i), \qquad \forall v_i \in I(G)$$

(2.7)

$$q(v_i) \ge q(v_j) + D(v_j, v_i), \quad \forall (v_j, v_i) \in E$$

(2.8)

$$w_i \in W_i, h_i \in H_i \qquad \forall v_i \in V \tag{2.9}$$

where  $p(v_i)$  is the summation of dynamic and leakage power on gate  $v_i$ , and  $D(v_j, v_i)$ shows the delay from  $v_j$  to  $v_i$ . W and H are the discrete sets of gate size and threshold voltage provided by the process technology library, respectively.

To solve this problem, the timing constraints are relaxed by multiplying the penalty of Lagrangian multiplier  $\vec{\lambda}$  and then integrated into the cost function [24]. The Lagrangian function is given as

$$\mathcal{L}(\vec{\lambda}, \vec{w}, \vec{h}, \vec{a}, \vec{q}) = \sum_{v_i \in V} p(v_i) + \sum_{v_i \in I(G)} \lambda_{i0}(a_i - q_i) + \sum_{(v_j, v_i) \in E} \lambda_{ji}(q_j + D(v_j, v_i) - q_i)$$

(2.10)

The Lagrangian function in (2.10) is further simplified by the algebraic transformation in [23], and thus becomes the LR subproblem in (2.11) given the multiplier  $\vec{\lambda}$ . The Lagrangian dual problem in which the  $\vec{\lambda}$  is determined to maximize the Function (2.5) could be solved by the subgradient method and is elaborated in Section (2.5).

Minimize

$$\mathcal{L}(\vec{\lambda}, \vec{w}, \vec{h}) = \sum_{v_i \in V} p(v_i) + \sum_{(v_j, v_i) \in E} \lambda_{ji} D(v_j, v_i)$$

(2.11)

s.t.  $w_i \in W_i, h_i \in H_i \ \forall v_i \in V$

#### 2.2.6 Process Variation Modeling

In order to deal with the performance variability during the circuit design, the sources of the variations are analyzed and could be mainly classified into two types. The first one is the inter-die variation which differs from die to die and keeps the identical variation effect to all the gates' parameters on a single die. e.g., the timing analysis on the data path of the design manufactured through the same mask. The second type is intra-die variation which affects the gates' parameters on the same die differently, e.g., the metal width of two inverters locating in different grids.

As for inter-die variation, it is relatively easy to handle with in a variation-aware circuit design algorithm, due to its uniform feature across the entire chip. By contrast, the spatial correlations need to be considered in the intra-die variation. For example, the the delay of a single gate is modeled as [25]

$$d = d_0 + \sum_i \frac{\partial d}{\partial p_i} (p_i - \mu_{p_i}) + N(0, \Sigma)$$

(2.12)

where  $d_0$  is the nominal delay, and *i* is the index of the grid in the circuit. The  $p_i$  denotes a location-dependent random component whose mean value and gradient are equal to  $\mu_{p_i}$ and  $\frac{\partial d}{\partial p_i}$ , respectively.

Especially, the reason to use grid index i to represent the location-dependent random component is that we assume all gates locate within the same grid will have identical variation distributions. Therefore, it can conclude that there is only one random component in one grid for each random component, or say the grid index i is one-to-one mapping to the random component. As for  $N(0, \Sigma)$ , it represents the normal distribution of the random components, and  $\Sigma$  is the covariance matrix. For example in Figure 2.4, a chip die with  $3row \times 3col = 9$  grids, will have a  $9 \times 9$  covariance matrix  $\Sigma$ .

Figure 2.4: Chip die with 9 grids and its corresponding  $9 \times 9$  covariance matrix.

#### 2.3 **Problem Formulation**

The input to our algorithm is a combinational logic circuit C, which has been clustered into a set of blocks  $\mathcal{B} = \{B_1, B_2, ...\}$  [18], timing constraints and adaptivity policy. An adaptivity policy is to control circuit tuning according to results from variation sensors. All gates in the same block follow the same adaptivity configuration. We assume that adaptivities of blocks are independent of each other. If a block is assigned with adaptivity, its tuning is based on its own sensors. This is often true in practice as people tend to avoid high complexity unless it is very necessary. Our algorithm decides whether or not to assign adaptivity to each block. Its objective and constraints include power, timing, robustness to variations and adaptivity area overhead.

#### 2.3.1 Overview of Algorithm Flow

In Figure 2.5, the overall algorithm iterates between gate implementation selection and adaptivity assignment. The gate implementation selection part is handled by Lagrangian relaxation. Its formulation is to minimize power dissipation subject to timing constraints with consideration of variations. Area is not explicitly in the formulation as power and area are correlated in gate sizing. A main reason to use LR here is the runtime cost of timing analysis. For adaptive circuit optimization, variations must be considered and statistical

static timing analysis (SSTA) is computationally expensive. By solving the problem in two layers of Lagrangian subproblem and dual problem, the calls to SSTA can be restricted to the dual problem part. Then, the subproblem can be solved using simple models while the overall solution quality is not compromised due to the SSTA guidance in solving the dual problem. The problem size of adaptivity assignment is significantly smaller and allows SSTA to be called more frequently. Therefore, the adaptivity assignment is solved by a sensitivity-based heuristic. In the adaptivity assignment, adaptivity area overhead is explicitly treated as a constraint. The overall flow of our algorithm is shown in Figure 2.5. The outer iteration between gate implementation selection and adaptivity assignment is conducted for only a few times. More iterations are performed within the gate implementation selection part.

Figure 2.5: Overview of the adaptivity-aware gate implementation selection algorithm flow. Reprinted from [1].

#### 2.3.2 Variation-aware Gate Implementation

Gate implementation selection is to select size and threshold voltage for each gate in a given circuit according to a cell library. Compared to previous works, our method must be adaptivity-aware. That is, if a block is assigned with adaptivity, our implementation selection must be performed with anticipation of performance-power changes due to the adaptivity. Of course, our selection algorithm must take variations into account as well. We make such sophisticated enhancement over a previous work of deterministic gate implementation selection [24]. Moreover, we propose a new technique to avoid redundant counting when candidate solutions are propagated in circuit traversals.

The input includes a combinational logic circuit represented by a directed acyclic graph (DAG) G(V, E), where V is the set of gates and E is a set of edge connections. For each gate  $v_i \in V$ , we need to select an implementation  $\xi(v_i)$ , including size and threshold voltage, from a given cell library. The circuit is partitioned into a set of blocks  $\mathcal{B} = \{B_1, B_2, ...\}$ . There is a binary parameter  $\Phi_i \in \{0, 1\}$  to tell if block  $B_i$  is assigned adaptivity. If a block is assigned adaptivity, all gates in the block are tuned uniformly according to a given adaptivity policy. We use  $\varphi(B_i) \in \{\phi_0, \phi_1, ..., \phi_{max}\}$  to denote adaptive tuning effort level. For example,  $\phi_0$  means zero body bias and  $\phi_{max}$  indicates the maximum forward body bias. Then, the delay of a gate  $v_i$  depends on both its implementation and adaptivity, and is represented by  $d_{v_i}(\xi_i, \varphi_i)$ . Of course, a gate delay is also affected by its input slew and load capacitance. For the sake of brevity, we omit them in the notation. Similarly, the power dissipation, including dynamic and static power, of a gate  $v_i$  is denoted by  $w_{v_i}(\xi_i, \varphi_i)$ .

When variations are considered, delay  $d_{v_i}(\xi_i, \varphi_i)$  becomes a random variable. We employ statistical static timing analysis (SSTA) [25] to capture the variability-aware timing behavior with consideration of spatial correlations. If a block is assigned adaptivity, ac-

cording to SSTA and the adaptivity policy, we can estimate the probability that a block is at certain tuning level, i.e.,  $P(\varphi(B_i) = \phi_j)$ . Then, we can obtain the expected power of a gate as  $\bar{w}_{v_i}(\xi_i) = \sum_{j=0}^{max} P_{v_i}(\phi_j) \cdot w_{v_i}(\xi_i, \phi_j)$ . For timing, we only evaluate the case where the maximal tuning effort level is applied if a block has adaptivity. There are two reasons. First, we focus on design-time optimization and only search for a solution that can conform to timing constraints at runtime. If an adaptivity is assigned, an adaptivity policy can always apply the maximal level to satisfy timing constraints based on our solutions. Second, considering probability of tuning configurations on top of probability of variations causes very high estimation complexity and risk of inaccuracy. Our algorithm accommodates general delay, power and variation models, although the Elmore delay model is used here and random variables are assumed to follow Gaussian distributions.

Here is the problem formulation for the gate implementation selection:

Min

$$\sum_{v_i \in V} \bar{w}_{v_i}(\xi_i)$$

(2.13)

s.t.

$$a_u + d_{u,v}(\vec{\xi}, \varphi_u(\Phi_u)) \le a_v, \forall (u, v) \in E$$

(2.14)

$$P(a_v \le Q_v) \ge \Upsilon, \forall v \in PO(V)$$

(2.15)

$$\varphi_u(\Phi_u) = \begin{cases} \phi_{max} & if \quad \Phi_u = 1\\ \phi_0 & if \quad \Phi_u = 0 \end{cases}$$

(2.16)

where P(.) indicates probability,  $a_u$  is the arrival time at gate u,  $\vec{\xi}$  represents the gate implementation selections for all gates,  $Q_v$  is the required arrival time,  $\Upsilon$  is the constraint for timing yield and PO(V) means primary output gates. If the probability distribution is Gaussian, the probability percentile constraint can be easily represented in terms of mean and standard deviation  $\sigma$ . For example,  $\Upsilon = 99.7\%$  requires the mean plus  $3\sigma$  delay satisfies the required arrival time constraint.

#### 2.3.3 Variation-aware Lagrangian Relaxation

This problem is transformed by Lagrangian relaxation [23] to minimize the following Lagrangian function.

$$\mathcal{L}_{\vec{\lambda}}(\vec{\xi}) = \sum_{v_i \in V} \bar{w}_{v_i}(\xi_i) + \sum_{(u,v) \in E} \lambda_{u,v}(a_u + \tilde{d}_{u,v}(\vec{\xi}, \varphi_u(\Phi_u)) - a_v)$$

(2.17)

where  $\vec{\lambda}$  is the vector of Lagrangian multipliers and  $\tilde{d}$  indicates the mean plus certain  $\sigma$  delay. This is the so-called Lagrangian subproblem. The problem of finding the  $\vec{\lambda}$  to maximize the optimal solution to the subproblem is the Lagrangian dual problem. Like in [23, 24], we solve the Lagrangian dual problem using subgradient method guided by SSTA. By doing so, the Lagrangian subproblem is allowed to use simple and less accurate timing and variability models.

By applying the Kuhn-Tucker conditions [23], the subproblem can be further reduced to minimize:

$$\mathcal{L}_{\vec{\mu}}(\vec{\xi}) = \sum_{v_i \in V} \bar{w}_{v_i}(\xi_i) + \sum_{(u,v) \in E} \mu_{u,v} \tilde{d}_{u,v}(\vec{\xi}, \varphi_u(\Phi_u))$$

(2.18)

where  $\vec{\mu}$  is a simple function of  $\vec{\lambda}$  [23]. We solve the reduced subproblem  $\mathcal{L}_{\vec{\mu}}(\vec{\xi})$  by Joint Relaxation and Restriction (JRR) [24]. JRR is a dynamic programming-like solution search. It iteratively propagates candidate solutions in reverse topological order and topological order traversals of *G*. Such propagation of multiple solutions on a DAG is very challenging as history conflict may happen for solution merging at reconvergence nodes. The work of [24] relaxes the constraint of history consistency in the first reverse topological order search and restores the consistency in subsequent topological order search. In later iterations, additional restrictions are applied so that history conflict no longer occurs.

#### 2.4 Subproblem Solution

For the sake of clarity, only the gate size w is the solution for each gate in the circuit and the threshold voltage h is omitted. To find out the best solutions for all gates, the algorithm first performs a backward search from the primary output to the primary input, and then traces back from the primary input to the primary output.

#### 2.4.1 Backward Search with Inferior Pruning

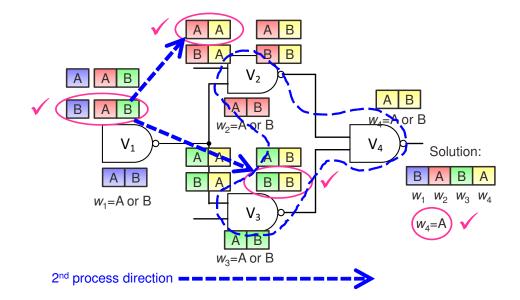

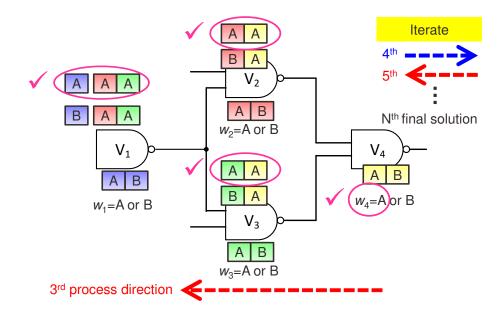

Figure 2.6: Backward topological traverse with inferior pruning.

In Figure 2.6, to find out the w selection for each cell, which has only two options A and B, we starts from the primary output, e.g.  $v_4$ . Then, all the solution combinations are evaluated among the fanin cells of  $v_4$  as well as their fanout cones. e.g.,  $v_2$  and  $v_4$  are evaluated together, and totally four combinations are generated. After the inferior pruning, one of the four solutions is preserved as ( $w_2 = A$ ,  $w_4 = A$ ). Similar process is used to  $v_3$

and  $v_5$ . Thus another four combinations are generated, and still only one solution ( $w_3 = B$ ,  $w_5 = B$ ) is assumed to be kept. Next, when either  $v_2$  or  $v_3$  is under the calculation,  $v_1$ ,  $v_2$  and  $v_3$  are evaluated together, since  $v_1$  is the common fanin cell for  $v_2$  and  $v_3$ . Therefore, the combinations at  $v_1$  are derived, and the one with the minimal cost function and no timing violation is selected as the best solution.

Obviously, without the inferior pruning method, the reverse topological traverse in Figure 2.6 suffers from the exponential solutions at the fanin gate with the increase of circuit hierarchy. Therefore, inferior pruning at the fanin gate is necessary to reduce the process time and storing space. Proved in [24], for a specific size  $w_i$  of any gate  $v_i$ , at most one non-inferior solution at  $v_i$  can be preserved after pruning. This property is justified by the fact that, each solution of a cell v could be represented by the pair of capacitance c and required arrival time q, and then only the solution with the maximum q is not pruned out.

Figure 2.7: Forward topological traverse with solution back trace.

After that, since each solution at  $v_1$  keeps all the historical information, a forward tracking is available in Figure 2.7, and all the solutions for the gates from  $v_1$  till the primary outputs could be determined.

#### 2.4.2 Solution Inconsistence and Forward Restoration

The backward search with inferior pruning works well until it comes to a problem when reconvergence path exists, i.e., the multi-fanin gate. For example in Figure 2.8, suppose after the backward search, the best solution  $w_1$  is get at the primary input  $v_1$ , and the forward tracking determines the solutions of  $v_2$  and  $v_3$  as  $w_2 = A$  and  $w_3 = B$ , respectively. However, it fails to tell the w of  $v_4$ , since the best solutions for  $v_2$  and  $v_3$  are based on different w of  $v_4$  in the reverse topological traverse.

Figure 2.8: Forward topological traverse with solution inconsistence.

A restoration method is applied to solved the solution inconsistence during the forward tracking in Figure 2.9. For the multi-fanin gate  $v_4$ , instead of simply applied the solutions

inherited from its different fanin cells  $v_2$  and  $v_3$ , we derive  $v_4$ 's solution  $w_4$  by a further calculation based on the best solutions  $w_2 = A$  and  $w_3 = B$  for fanin gates  $v_2$  and  $v_3$ , respectively. By this way, the w solution for  $v_4$  is determined as the one that leads to the minimal cost, and the solution inconsistence is solved.

Figure 2.9: Forward topological traverse with solution restoration.

#### 2.4.3 Iterative Refinement

Need to mention that, once the best solution of  $v_4$  is achieved after the forward restoration, the best solutions for the gates  $v_2$  and  $v_3$  in Figure 2.9 may mismatch with those in the backward search, since they are based on different solution of  $v_4$ . In Figure 2.10, this disadvantage could be alleviated by performing the 3rd round of backward search during which the solutions are fixed for all the multi-fanin gates. Similarly, the 4th round forward restoration is also needed since the best solutions of  $v_2$  and  $v_3$  are likely changed, and  $v_4$  is affected so on so forth. This iterative refinement [24] is performed until the solutions are converged or the iteration limit is reached.

Figure 2.10: Backward topological traverse followed by iterative refinement.

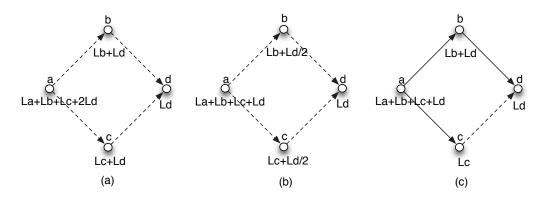

## 2.4.4 Solution for Redundant Counting

The candidate solution propagations on a DAG faces another problem. That is, a cost may be over-counted repeatedly. For example, let us consider the propagation of cost Lon a simple DAG in Figure 2.11 (a) in reverse topological order. The L here corresponds to the  $\mathcal{L}_{\vec{\mu}}$  to be minimized in the reduced Lagrangian subproblem. Cost Ld at node d is propagated to both node b and c. When solutions from b and c are merged at node a, Ldis counted twice. In some cases, the count may happen more than twice. This problem is noticed more than two decades ago in works on technology mapping [26]. It was solved by splitting the cost at multi-fanin nodes like Figure 2.11 (b). This cost splitting can avoid the redundant counting. However, some cost estimate, like those at node b and c in Figure 2.11 (b), may see significant error and result in solution quality loss.

Figure 2.11: Backward topological order solution propagation on DAG. (a) Cost Ld is double-counted at node a. (b) Conventional approach to avoid double counting. (c) Propagation only on spanning tree (in solid edges). Reprinted from [1].

We propose a new technique to solve the over-counting problem with less cost estimate error. This technique is also simple to implement and does not increase the overall algorithm complexity. It consists of the following key steps.

- 1. Construction of spanning tree. Before the solution search, we perform a depth first search (DFS) on G. During the DFS, when the target node of an edge has already been visited, this edge is added into set E. After the DFS, by removing E from G, we obtain a normal spanning tree T, whose edges are solid in Figure 2.11 (c).

- 2. Cost propagated on T. Cost  $L_T$  is propagated only along edges in T so that no double counting can happen. This is illustrated in Figure 2.11 (c).

- 3. Cost for pruning. Another cost  $L_p$  is maintained for solution pruning at each node. For a single-fanout node, like b and c in Figure 2.11, its  $L_p$  is the sum of its local cost and fanout node  $L_p$  cost. For example,  $L_p$  at node c is Lc + Ld. At a multi-

fanout node, its  $L_p$  is the sum of its local cost and its fanout  $L_T$  cost. For example, the  $L_p$  at node a is La + Lb + Lc + Ld.

The purpose of  $L_T$  is to avoid the double counting while  $L_p$  is to reduce under-estimate due to the removal of <u>E</u>. For example, Ld needs to be counted for the pruning at node ceven though edge (c, d) is not in T.

## 2.5 Dual Problem Solution

As formulated in Equation (2.11),  $\mathcal{L}(\vec{\lambda}) := \min \mathcal{L}(\vec{\lambda}, \vec{w}, \vec{h})$  features the concavity over  $\vec{\lambda} \ge 0$ . Therefore, in order to maximize  $\mathcal{L}(\vec{\lambda})$ , the steepest descent algorithm is reasonable to come up with. However, considering that the  $\mathcal{L}(\vec{\lambda})$  is not differentiable in the general case, we apply the subgradient based algorithm, which updates the  $\vec{\lambda}$  iteratively following the direction of subgradient.

The pseudo code is given by Algorithm 1, which could be divided into two parts, the update of Lagrangian multipliers and the satisfaction to KKT condition. In Steps 1-16, all the edges are evaluated, and each edge e(u, v) denoted by the source gate u and the target gate v is corresponding to one Lagrangian multiplier  $\lambda_e(u, v)$ . The update function of  $\lambda_e(u, v)$  is given by

$$\lambda_{e(u,v)} := \begin{cases} \lambda_{e(u,v)} + \rho(a_u - Q_u), & \text{if } v \in PO(V) \\ \lambda_{e(u,v)} + \rho(a_u + D_v - a_v), & \text{if } v \notin PO(V) \&\& \ u \notin PI(V) \\ \lambda_{e(u,v)} + \rho(D_v - a_v), & \text{if } u \in PI(V) \end{cases}$$

(2.19)

according to [23], where PO(V) and PI(V) represent the primary output gates and primary input gates, respectively.  $\rho$  is the step size. The nonnegativity of Lagrangian multipliers  $\lambda_e(u, v)$  is guaranteed by Steps 13-15. Steps 17-28 are used to adjust the  $\lambda_e(u, v)$  in order to satisfy the KKT condition [23] that  $\sum_{e_o \in output(u)} \lambda_{e_o} = \sum_{e_i \in input(u)} \lambda_{e_i}, \forall u \in V$ . **Input** : Combinational circuit G(V, E), cell library L, gate size w and threshold voltage h solution for each  $u, v \in V$ , and the timing info  $\vec{a}$  at each net as well as the  $\vec{Q}$  at the primary output of G

**Output**:  $\lambda$  for each timing constraint

```

1 for each e(u, v) \in E do

if u.type = Primary_Input then

2

a_u \leftarrow 0;

3

else

4

5

a_u \leftarrow u.a;

6

end

if v.type = Primary_Output then

7

a_v \leftarrow Q_v; \ d_v \leftarrow 0;

8

else

9

a_v \leftarrow v.a; \ d_v \leftarrow v.R(w_v, h_v) \times \sum_{m \in fanout(v)} (m.C(w_m, h_m));

10

end

11

\lambda_{e(u,v)} \leftarrow \lambda_{e(u,v)} + step\_size \times (a_u + d_v - a_v);

12

if \lambda_{e(u,v)} < 0 then

13

\lambda_{e(u,v)} \leftarrow 0;

14

end

15

16 end

17 for each \ u \in V do

18

\lambda_{out} \leftarrow 0; \ \lambda_{in} \leftarrow 0;

for each e_o \in out\_edge(u) do

19

\lambda_{out} \leftarrow \lambda_{out} + \lambda_{e_o};

20

end

21

for each e_i \in in\_edge(u) do

22

\lambda_{in} \leftarrow \lambda_{in} + \lambda_{e_i};

23

end

24

for each e_i \in in\_edge(u) do

25

\lambda_{e_i} \leftarrow \lambda_{e_i} \times (\lambda_{out}/\lambda_{in});

26

end

27

28 end

29 return \vec{\lambda}:

```

Algorithm 1: Subgradient-based approach for updating Lagrangian multipliers.

#### 2.6 Experiment Results

In order to evaluate the effectiveness of our algorithm, we attempt to compare it with other approaches in experiments. To the best of our knowledge, there is no previous work on joint gate implementation selection and adaptivity assignment with consideration of overhead control. Therefore, we compare with the following approaches.

- 1. Baseline. Variability-aware gate implementation selection without adaptivity. This is to emulate conventional non-adaptive designs.

- 2. Naïve adaptivity assignment. If only forward body bias (FBB) is considered, adaptivity is assigned to any block that has negative slack in terms of mean plus certain  $\sigma$  value. This is to emulate what designers may do for adaptive circuit design without adaptivity optimization tools. In ABB where both FBB and reverse body bias are allowed, the naïve method simply assigns adaptivity for all blocks. Actually, this is the approach of [18].

In the experiments, gates are modeled by RC switches and the Elmore delay model is employed. We extend a previous SSTA work [25] to perform timing analysis and estimate timing yield as well as variability-aware delay  $\tilde{d}_{u,v}(\vec{\xi}, \varphi_u(\Phi_u))$ . We consider gate length variations with standard deviation  $\sigma$  being 5% of nominal value, and gate width variations with  $\sigma$  of 2.7% of nominal width. We use adaptive body bias (ABB) [8, 18] as adaptivity. The power model, including dynamic and leakage power, and impact of ABB on delay and power are based on [18]. The adaptivity area overhead includes two parts. Per-gate overhead due to manufacturing process requirement is derived from [18]. Per-block overhead due to sensor and tuning circuits is estimated according to [8]. The experiments are performed on ISCAS85 and ISPD13 [27] benchmark circuits. The largest circuit in the ISPD13 suite has about 150K gates. All methods are implemented with C/C++ and the experiments are performed on AMD Opteron processor with 2.2GHz frequency and

Table 2.1: Experimental results of Naïve method with only forward body bias (FBB). Total area overhead and power overhead are denoted by  $\Delta A$  and  $\Delta W$ , respectively. Reprinted from [1].

|             |        |                 | Baseline | Naïve |            |            |         |

|-------------|--------|-----------------|----------|-------|------------|------------|---------|

| Circuit     | #gates | $ \mathcal{B} $ | Yield    | Yield | $\Delta A$ | $\Delta W$ | CPU (s) |

| c432        | 171    | 4               | 94.9%    | 99.3% | 707        | 6564       | 1       |

| c499        | 218    | 5               | 91.6%    | 97.7% | 1433       | 10975      | 1       |

| c880        | 383    | 5               | 96.3%    | 98.9% | 809        | 5123       | 1       |

| c1355       | 562    | 4               | 88.8%    | 99.9% | 1587       | 26442      | 2       |

| c1908       | 972    | 6               | 75.9%    | 99.9% | 1380       | 19049      | 4       |

| c2670       | 1287   | 5               | 94.6%    | 98.2% | 947        | 6156       | 5       |

| c3540       | 1705   | 5               | 73.6%    | 99.9% | 1759       | 21952      | 8       |

| c5315       | 2351   | 6               | 90.9%    | 99.8% | 2602       | 29364      | 10      |

| c6288       | 2416   | 6               | 93.9%    | 99.9% | 1931       | 50323      | 11      |

| c7552       | 3625   | 5               | 41.8%    | 99.9% | 3291       | 42878      | 18      |

| fft         | 32281  | 20              | 81.2%    | 99.1% | 15742      | 194576     | 310     |

| cordic      | 41601  | 20              | 73.9%    | 99.5% | 22618      | 443511     | 493     |

| des_perf    | 112644 | 22              | 83.5%    | 99.2% | 43608      | 204159     | 750     |

| matrix_mult | 155325 | 20              | 44.0%    | 99.1% | 78028      | 1382050    | 1378    |

| Average     |        |                 | 80.4%    | 99.3% | 12603      | 174509     | 214     |

Linux operating system. The gate implementation selection for each method is performed with 14 iterations, i.e., Lagrangian multipliers are updated 14 times. The best solution in terms of problem formulation is selected. In our collaborative optimization approach, the iteration between gate implementation selection and adaptivity assignment is conducted twice.