## FORMAL VERIFICATION OF A MESI-BASED CACHE IMPLEMENTATION

A Thesis

by

## VENKATESHWAR KOTTAPALLI

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Chair of Committee, Aakash Tyagi Committee Members, Duncan M. Walker Jiang Hu Head of Department, Dilma Da Silva

August 2017

Major Subject: Computer Engineering

Copyright 2017 Venkateshwar Kottapalli

#### ABSTRACT

Cache coherency is crucial to multi-core systems with a shared memory programming model. Coherency protocols have been formally verified at the architectural level with relative ease. However, several subtle issues creep into the hardware realization of cache in a multi-processor environment. The assumption, made in the abstract model, that state transitions are atomic, is invalid for the HDL implementation. Each transition is composed of many concurrent multi-core operations. As a result, even with a blocking bus, several transient states come into existence. Most modern processors optimize communication with a split-transaction bus, this results in further transient states and race conditions. Therefore, the design and verification of cache coherency is increasingly complex and challenging.

Simulation techniques are insufficient to ensure memory consistency and the absence of deadlock, livelock, and starvation. At best, it is tediously complex and time consuming to reach confidence in functionality with simulation. Formal methods are ideally suited to identify the numerous race conditions and subtle failures. In this study, we perform formal property verification on the RTL of a multi-core level-1 cache design based on snooping MESI protocol. We demonstrate full-proof verification of the coherence module in Jasper-Gold using complexity reduction techniques through parameterization. We verify that the assumptions needed to constrain inputs of the stand-alone cache coherence module are satisfied as valid assertions in the instantiation environment. We compare results obtained from formal property verification against a state-of-the-art UVM environment. We highlight the benefits of a synergistic collaboration between simulation and formal techniques. We present formal analysis as a generic toolkit with numerous usage models in the digital design process.

# DEDICATION

To my parents, my sister, my extended family, and my friends.

#### ACKNOWLEDGMENTS

I would like to express my deepest gratitude to Prof. Aakash Tyagi for his constant support throughout the duration of my graduate study. His persistent optimism and encouragement, prodded me on, especially during periods of disbelief and doubt. This thesis would be improbable without his guidance and help.

I am forever indebted to Prof. Flemming Andersen for providing direction and technical expertise. I am grateful for his friendly, jovial, and immensely supportive mentorship. Prof. Andersen, through weekly interactions, has constantly inspired patience, dedication, and clarity of thought in me. I am grateful to Prof. Michael Quinn for his support, supervision, and encouragement with the UVM simulation effort. I wish to thank Prof. Walker and Prof. Hu for serving as members of my thesis committee, and providing valuable feedback. Additionally, I am thankful to Prof. Sunil Khatri for rousing my creativity and interest in research, while helping me identify my goals.

I am grateful to Surakshith M. Narasegowda, Abhinav Sethi and Sheena Goel, for providing critical assistance at different stages of this project. Surakshith and Sheena helped with the execution of dynamic verification, while Abhinav assisted with design changes. I would also like to thank Yuhao Yang and previous designers of the legacy cache implementation.

I wish to thank the ECE and CSE departments at TAMU for giving me an opportunity to extend my skills and evolve. I am thankful to the CSE graduate advising office, Ms. Karrie Bourquin in particular, for assistance with the logistic requirements. Lastly, I am immensely grateful to my family and friends for their encouragement and belief in my abilities.

#### CONTRIBUTORS AND FUNDING SOURCES

### Contributors

This work was supported by a thesis committee consisting of Professor Aakash Tyagi, Professor Flemming Andersen, and Professor Duncan M. Walker of the Department of Computer Science and Engineering (CSE), and Professor Jiang Hu of the Department of Electrical and Computer Engineering (ECE).

The legacy RTL code and specification, used as a starting point for the thesis, was provided by Prof. Aakash Tyagi, and Prof. Michael Quinn. Surakshith M. Narasegowda assisted in implementation of the dynamic verification scenarios listed in Section 3.2. Abhinav Sethi helped with the bug fix described in Section 5.2.2.3. Sheena Goel supported the analysis of coverage, described in Section 5.1.2.

All other work conducted for the thesis was completed by the student independently.

### **Funding Sources**

Graduate study was partly supported by a scholarship from the ECE department at Texas A&M University.

## NOMENCLATURE

| HDL  | Hardware Description Language                    |

|------|--------------------------------------------------|

| RTL  | Register Transfer Level                          |

| UVM  | Universal Verification Methodology               |

| UVC  | UVM Verification Component                       |

| FV   | Formal Verification                              |

| FPV  | Formal Property Verification                     |

| FEV  | Formal Equivalence Verification                  |

| MSI  | Modified, Shared, and Invalid Protocol           |

| MESI | Modified, Exclusive, Shared and Invalid Protocol |

| SV   | SystemVerilog                                    |

| SVA  | SystemVerilog Assertions                         |

| FSM  | Finite State Machine                             |

| LLC  | Last-Level Cache                                 |

| PLRU | Pseudo-Least Recently Used                       |

| ABV  | Assertion-based Verification                     |

| DV   | Data Value invariant                             |

| SWMR | Single-Write, Multiple-Read invariant            |

# TABLE OF CONTENTS

|     | F                                                                                               | Page                     |

|-----|-------------------------------------------------------------------------------------------------|--------------------------|

| AB  | STRACT                                                                                          | ii                       |

| DE  | DICATION                                                                                        | iii                      |

| AC  | KNOWLEDGMENTS                                                                                   | iv                       |

| CO  | NTRIBUTORS AND FUNDING SOURCES                                                                  | v                        |

| NO  | MENCLATURE                                                                                      | vi                       |

| TA  | BLE OF CONTENTS                                                                                 | vii                      |

| LIS | T OF FIGURES                                                                                    | xi                       |

| LIS | T OF TABLES                                                                                     | xiii                     |

| 1.  | INTRODUCTION                                                                                    | 1                        |

|     | 1.1       Cache Coherence                                                                       | 1<br>3                   |

| 2.  | VERIFICATION OF CACHE COHERENCE                                                                 | 5                        |

|     | 2.1Need for Robust Verification2.2Previous Work2.3Approach2.4Objectives2.5Design Implementation | 5<br>8<br>10<br>12<br>13 |

| 3.  | SIMULATION-BASED VERIFICATION                                                                   | 15                       |

|     | <ul> <li>3.1 UVM Verification Environment</li></ul>                                             | 17<br>22<br>27<br>28     |

| 4.  | FORMAL VERIFICATION                                                                             | 31                       |

|    | 4.1 | Forma | l Property | Verification                                                                                                      |

|----|-----|-------|------------|-------------------------------------------------------------------------------------------------------------------|

|    |     | 4.1.1 |            | ion Plan                                                                                                          |

|    |     | 4.1.2 | Cover St   | atements                                                                                                          |

|    |     | 4.1.3 | Complex    | tity Staging                                                                                                      |

|    |     | 4.1.4 | Assertion  | ns                                                                                                                |

|    |     | 4.1.5 |            | tity Reduction Techniques                                                                                         |

|    |     |       | 4.1.5.1    | Formal friendly properties                                                                                        |

|    |     |       | 4.1.5.2    | Auxiliary code                                                                                                    |

|    |     |       | 4.1.5.3    | Reference models                                                                                                  |

|    |     |       | 4.1.5.4    | Parameterization                                                                                                  |

|    |     |       | 4.1.5.5    | Free variables                                                                                                    |

|    |     |       | 4.1.5.6    | Memory abstraction                                                                                                |

|    | 4.2 | Forma | l Equivale | nce Verification                                                                                                  |

|    |     |       |            |                                                                                                                   |

| 5. | RES | ULTS  |            |                                                                                                                   |

|    | 5.1 | ылл   | Environm   | ent                                                                                                               |

|    | 5.1 | 5.1.1 |            | scovered $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $57$                             |

|    |     | J.1.1 | 5.1.1.1    |                                                                                                                   |

|    |     |       | 5.1.1.2    | Signal cp_in_cache de-asserted during bus_rd_snoop 58<br>Signal cp_in_cache de-asserted during bus_rdx_snoop . 58 |

|    |     |       | 5.1.1.2    | Signal shared_local not generated for modified snoop                                                              |

|    |     |       | 3.1.1.3    | block hit                                                                                                         |

|    |     |       | 5.1.1.4    |                                                                                                                   |

|    |     |       | 5.1.1.4    | Incorrect LRU replacement       58         Incorrect instruction address bound       59                           |

|    |     |       | 5.1.1.5    |                                                                                                                   |

|    |     |       | 5.1.1.7    | MESI state update during invalidate_snoop                                                                         |

|    |     |       | 5.1.1.7    |                                                                                                                   |

|    |     |       | 5.1.1.8    | 1 11                                                                                                              |

|    |     |       | 5.1.1.9    | Response to snoop-side invalidate request60Discrepancy with reference model due to silent eviction60              |

|    |     |       | 5.1.1.10   | Incorrect update of LRU state variable                                                                            |

|    |     |       | 5.1.1.12   | LRU state variable for shared to modified transition                                                              |

|    |     |       |            | Contention between CPU and snoop-side requests 63                                                                 |

|    |     | 5.1.2 |            | 1 1                                                                                                               |

|    | 5.2 |       | -          | e                                                                                                                 |

|    | 5.2 | 5.2.1 |            | ion for Reduced Design Parameters                                                                                 |

|    |     | 5.2.1 |            | scovered $\ldots$ $\ldots$ $72$                                                                                   |

|    |     | 5.2.2 | 5.2.2.1    | Absence of reset signal   72                                                                                      |

|    |     |       | 5.2.2.1    | Presence of in-out ports                                                                                          |

|    |     |       | 5.2.2.2    | Contention between CPU and snoop-side requests                                                                    |

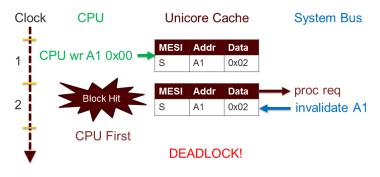

|    |     |       | 5.2.2.3    | Deadlock situation                                                                                                |

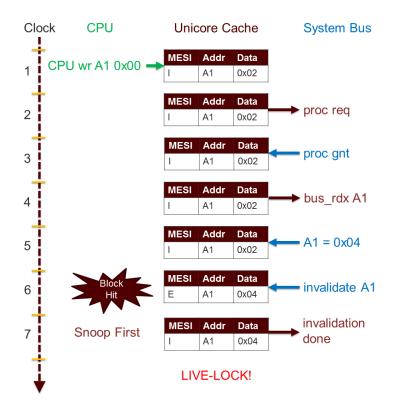

|    |     |       | 5.2.2.4    | Livelock situation                                                                                                |

|    |     |       | 5.2.2.5    | Bus request without CPU operation                                                                                 |

|    |     |       | 5.2.2.0    |                                                                                                                   |

|    |     |       | J.L.L.I    | Signal cp_in_cache for incoming invalidate request 80                                                             |

|     |      |            | 5.2.2.8 Invalidation acknowledgment during CPU first priority . 8 | 60        |

|-----|------|------------|-------------------------------------------------------------------|-----------|

|     |      |            | 5.2.2.9 De-assertion of CPU first priority                        | 60        |

|     |      |            | 5.2.2.10 Incorrect next-state logic in MESI FSM                   | 81        |

|     |      |            | 5.2.2.11 LRU state implemented as latches                         | 81        |

|     |      |            | 5.2.2.12 De-assertion of signal data_in_bus_cpu_lv1 8             | 81        |

|     |      |            | 5.2.2.13 De-assertion of signal cpu_wr_done                       | 32        |

|     |      |            | 5.2.2.14 Multiple drivers for lv2_wr_done                         | 32        |

|     |      | 5.2.3      |                                                                   | 32        |

|     |      | 5.2.4      | Formal as Design Aid                                              | 33        |

|     | 5.3  | Compa      | arison between Formal and Simulation                              | 35        |

|     | 5.4  | Collab     | oration between Formal and Simulation                             | <u>89</u> |

|     |      | 5.4.1      | Validating FPV Assumptions in Simulation                          | <u>9</u>  |

|     |      | 5.4.2      | Bug-hunting FPV                                                   | <u>9</u>  |

|     |      | 5.4.3      | Improving Simulation Code Coverage                                | 0         |

|     |      | 5.4.4      |                                                                   | 0         |

|     |      |            |                                                                   |           |

| 6.  | CON  | CLUSI      | IONS                                                              | )1        |

|     | 6.1  | Future     | Work                                                              | 94        |

|     | -    |            |                                                                   | ·         |

| REI | FERE | ENCES      |                                                                   | 6         |

| API | PENI | DIX A.     | SPECIFICATION                                                     | 12        |

|     | A.1  | Algori     | thm Description                                                   | )5        |

|     |      |            | Replacement Policy                                                | 15        |

|     |      | A.1.2      | MESI Protocol                                                     | )5        |

|     | A.2  | Design     | 1 Hierarchy                                                       | )6        |

|     | A.3  | -          | erface                                                            | 18        |

|     |      | A.3.1      |                                                                   |           |

|     |      | A.3.2      | Multi-core Cache Interface                                        | 19        |

|     | A.4  |            | ted Behavior                                                      | 19        |

|     |      |            | CPU Read                                                          | 0         |

|     |      |            | A.4.1.1 Case 1: Read hit                                          | 0         |

|     |      |            | A.4.1.2 Case 2: Read miss                                         | 0         |

|     |      | A.4.2      | CPU Write                                                         | 3         |

|     |      |            | A.4.2.1 Case 1: Write hit                                         | 3         |

|     |      |            | A.4.2.2 Case 2: Write miss                                        |           |

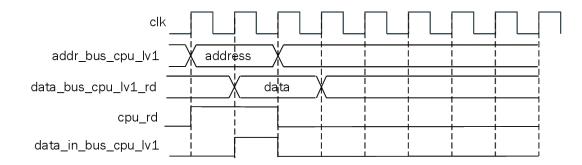

|     | A.5  | Timing     | g Specification                                                   |           |

|     | A.6  | -          | blexer Specification                                              |           |

|     | A.7  | -          | 2 Cache                                                           |           |

|     | A.8  |            | r Specification                                                   |           |

|     | 1.0  | 1 11 01101 |                                                                   | ∕⊥        |

| APPEN       | DIX B. | PROPERTIES                               | 2 |

|-------------|--------|------------------------------------------|---|

| <b>B</b> .1 | Cover  | Points                                   | 2 |

|             | B.1.1  | Uni-core Module                          | 2 |

|             | B.1.2  | Multi-core Module                        | 6 |

| B.2         | Assum  | nptions                                  | 6 |

|             | B.2.1  | Uni-core Module                          | 7 |

|             |        | B.2.1.1 Complexity stage 1               | 0 |

|             |        | B.2.1.2 Complexity stage 2               | 0 |

|             |        | B.2.1.3 Complexity stage 3               | 1 |

|             | B.2.2  | Multi-core Module                        | 1 |

| B.3         | Assert | ions                                     | 3 |

|             | B.3.1  | Uni-core Module                          | 3 |

|             |        | B.3.1.1 CPU-lv1 interface                | 4 |

|             |        | B.3.1.2 System bus interface             | 4 |

|             |        | B.3.1.3 Liveness properties              | 5 |

|             |        | B.3.1.4 MESI protocol                    | 6 |

|             |        | B.3.1.5 Coherence and memory consistency | 7 |

|             |        | B.3.1.6 Bug fixes                        | 8 |

|             | B.3.2  | Multi-core Module                        | 9 |

|             |        |                                          |   |

# LIST OF FIGURES

| FIGURI | E                                                              | Page |

|--------|----------------------------------------------------------------|------|

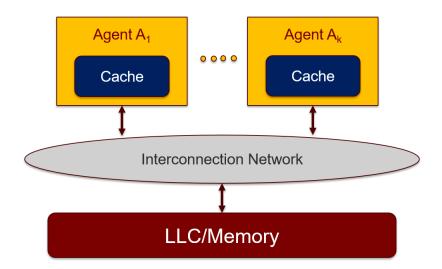

| 1.1    | A typical shared memory system                                 | 2    |

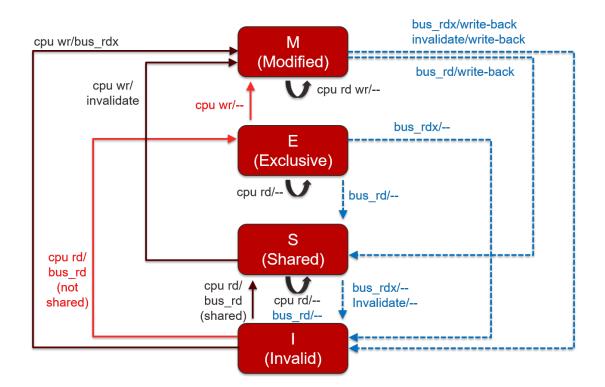

| 1.2    | The architectural MESI state diagram                           | 4    |

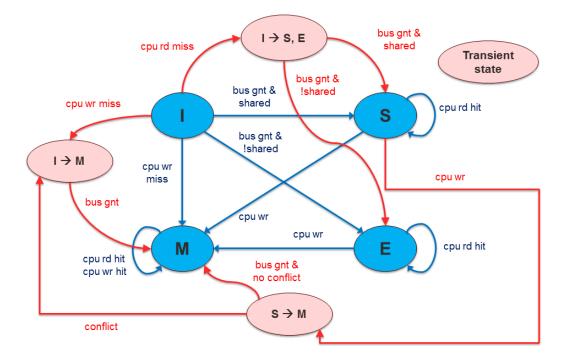

| 2.1    | Simplified MESI state diagram with transition states           | 6    |

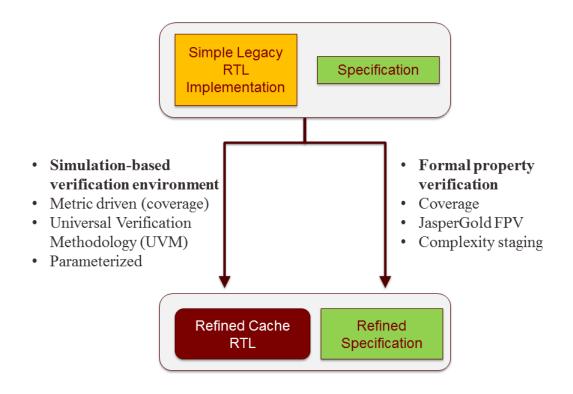

| 2.2    | Verification approach                                          | 11   |

| 2.3    | System block diagram                                           | 13   |

| 3.1    | UVM verification environment                                   | 16   |

| 3.2    | Verification flow for a single CPU transaction                 | 21   |

| 3.3    | Coverage as an indication of verification completeness         | 29   |

| 4.1    | Motivation for formal verification                             | 32   |

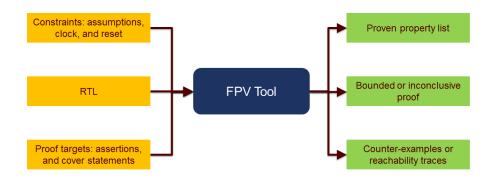

| 4.2    | FPV tool execution                                             | 35   |

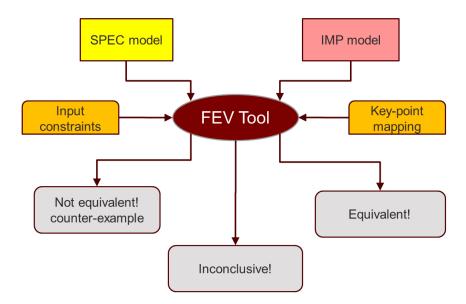

| 4.3    | Typical FEV execution                                          | 52   |

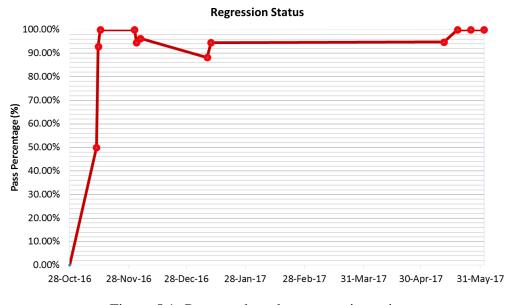

| 5.1    | Pass rate based on regression suite                            | 57   |

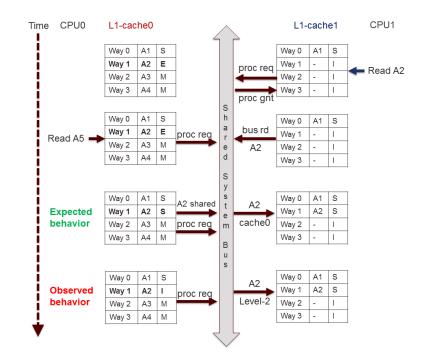

| 5.2    | Silent eviction issue                                          | 61   |

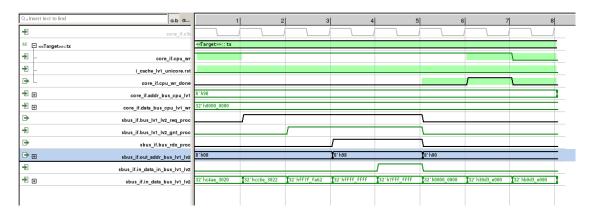

| 5.3    | CPU write miss operation as a JG cover statement               | 65   |

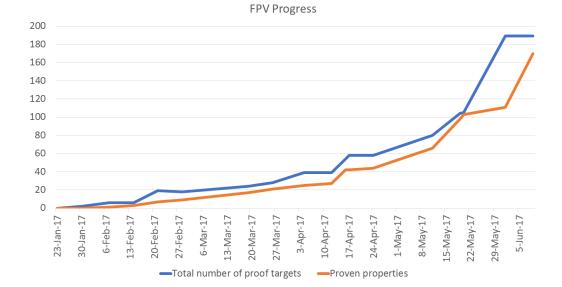

| 5.4    | FPV progress over time                                         | 70   |

| 5.5    | Example of contention issue                                    | 73   |

| 5.6    | JasperGold counter-example for contention issue                | 74   |

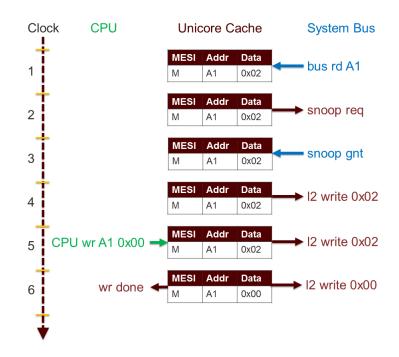

| 5.7    | Example of deadlock                                            | 77   |

| 5.8    | Example of livelock                                            | 79   |

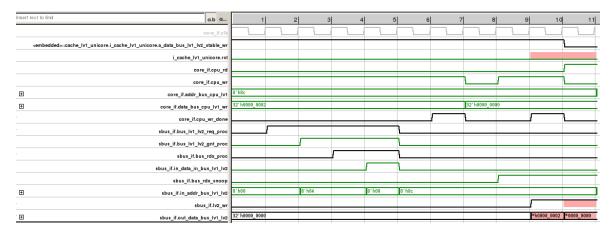

| 5.9    | Counter-example highlighting bus request without CPU operation | 80   |

| A.1  | Block diagram of the complete system                    | 103 |

|------|---------------------------------------------------------|-----|

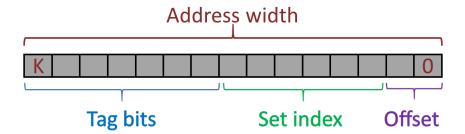

| A.2  | Relation between address, tag, index and offset         | 104 |

| A.3  | MESI coherence protocol                                 | 106 |

| A.4  | Multi-core L1 cache design hierarchy                    | 107 |

| A.5  | Read hit scenario                                       | 117 |

| A.6  | Write hit scenario with shared block                    | 117 |

| A.7  | Snoop scenario for bus rd with copy in shared/exclusive | 118 |

| A.8  | Snoop scenario for bus rd with copy in modified         | 118 |

| A.9  | Read serviced by level-2 cache                          | 120 |

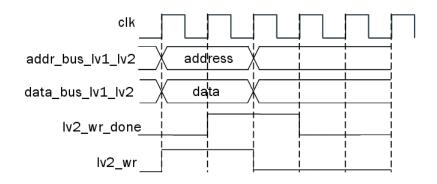

| A.10 | Write back to level-2 cache                             | 120 |

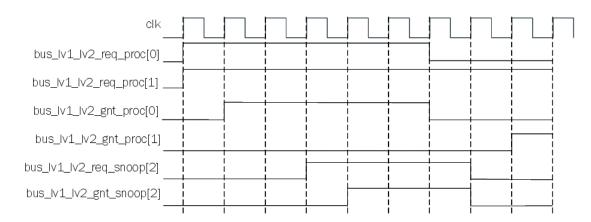

| A.11 | Arbiter timing diagram                                  | 121 |

# LIST OF TABLES

Page

TABLE

| 3.1  | Elements of CPU driver transaction                                                                                                                                                                                                                       | 19                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 3.2  | Elements of CPU monitor packet                                                                                                                                                                                                                           | 20                                                    |

| 3.3  | Elements of SBUS packet                                                                                                                                                                                                                                  | 20                                                    |

| 3.4  | Functions to be verified                                                                                                                                                                                                                                 | 22                                                    |

| 3.5  | Test scenarios with description                                                                                                                                                                                                                          | 23                                                    |

| 4.1  | Formal verification plan                                                                                                                                                                                                                                 | 37                                                    |

| 5.1  | Infrastructure for verification                                                                                                                                                                                                                          | 54                                                    |

| 5.2  | Time-line of verification progress                                                                                                                                                                                                                       | 55                                                    |

| 5.3  | Status of regression suite for original design parameters                                                                                                                                                                                                | 56                                                    |

| 5.4  | Status of regression suite for reduced design parameters (RC)                                                                                                                                                                                            | 56                                                    |

| 5.5  | Code coverage metrics without any exclusions                                                                                                                                                                                                             | 64                                                    |

| 5.6  | Assertion coverage metrics                                                                                                                                                                                                                               | 64                                                    |

| 5.7  | Functional coverage after analysis                                                                                                                                                                                                                       | 64                                                    |

| 5.8  | Property summary for uni-core FPV                                                                                                                                                                                                                        | 66                                                    |

| 5.9  | Assertion status for uni-core FPV                                                                                                                                                                                                                        | 67                                                    |

| 5.10 | Bounded proofs in uni-core FPV                                                                                                                                                                                                                           | 67                                                    |

| 5.11 | Property summary for multi-core FPV                                                                                                                                                                                                                      | 69                                                    |

| 5.12 | Assertion status for multi-core FPV                                                                                                                                                                                                                      | 69                                                    |

| 5.13 | Bounded proofs in multi-core FPV                                                                                                                                                                                                                         | 70                                                    |

| 5.14 | Solution to concurrency issue: Priority when CPU request observed first .                                                                                                                                                                                | 75                                                    |

|      | <ul> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>4.1</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>5.10</li> <li>5.11</li> <li>5.12</li> <li>5.13</li> </ul> | <ul> <li>3.2 Elements of CPU monitor packet</li></ul> |

| 5.15 | Solution to concurrency issue: Priority when snoop request observed first | 75  |

|------|---------------------------------------------------------------------------|-----|

| 5.16 | Coverage metrics for FPV                                                  | 82  |

| 5.17 | Design size for our FPV                                                   | 83  |

| 5.18 | Generic analysis of formal vs simulation                                  | 86  |

| 5.19 | Comparison of results from formal vs simulation                           | 88  |

| A.1  | Pseudo-LRU replacement policy                                             | 105 |

| A.2  | Pseudo-LRU state update                                                   | 105 |

| A.3  | IO interface for uni-core cache                                           | 108 |

| A.4  | IO interface for multi-core cache                                         | 110 |

#### 1. INTRODUCTION

Caches are vital components of modern processors. They dramatically improve system performance by reducing the number of accesses to main memory. Most microprocessors have several layers of cache to hide the increasing divide between processor and memory performance. In the current era of multi-core systems, we are presented with two architectural choices: a shared memory model or a distributed model. The distributed model dictates that each core has its own private memory. Different cores exchange information using a message passing interface. The shared memory model, which assumes that all cores access a common, single memory, is more popular of the two options. At any instance of time, multiple cached copies could exist in a shared memory system. Therefore, coherence and consistency are crucial in order to ensure correct functionality of such a system. This chapter establishes formal definitions of coherence, consistency and the MESI protocol.

#### **1.1 Cache Coherence**

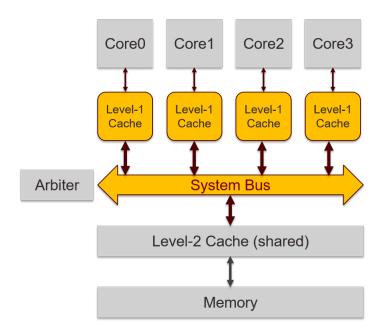

A typical shared memory system is illustrated in Figure 1.1. Multiple agents are connected through an interconnection network. An agent could be a processor, a direct memory access (DMA) block, or an external device that can write and read from memory. All the agents can perform loads and stores to all physical addresses. Each agent has its own private cache, and the last-level cache (LLC) is shared by all the cores.

Multiple copies of a data block can exist in the system. Intuitively, coherence implies that all the agents see the same, correct value of the datum at a given time. This is essential to ensure compliance with the shared memory model, and ease of debug. Additionally, caches are architecturally invisible, dictating that programmers should not functionally identify the presence or absence of caches.

Figure 1.1: A typical shared memory system

Numerous definitions of cache coherence can be found in published literature. But, a coherent system would satisfy all the definitions, as they are equivalent. In this study, our preferred definition of coherence is that offered by Hill et al. [2]. The following invariants compose the formal definition<sup>1</sup> of coherence [2].

- Single-Writer, Multiple-Read (SWMR) Invariant: At a given logical time, a single core can have read-write access or multiple cores can have read only access to a given memory location.

- 2. **Data-Value (DV) Invariant:** The value of a given data block is the same as the last write access.

Memory consistency, a related concept, is often confused with coherence. Consistency specifies that "a system should appear to execute all threads' loads and stores to all memory locations in a total order that respects the program order of each thread" [2]. A distinguishing feature between coherency and consistency is that coherency is defined on

<sup>&</sup>lt;sup>1</sup>Invariants SWMR and DV are captured and proven as interface level assertions in our FPV effort

a per-memory location basis, while consistency is specified with respect to all memory locations. Although, it is theoretically possible to have a consistent model with incoherence [3], this topic remains an academic curiosity. Consistency is achieved through coherence protocols. Therefore, cache protocols are vital to the correct design and functionality of a modern processor.

#### **1.2** Coherence Protocols

Coherence protocols enforce the two invariants necessary in a coherent system. Protocols are implemented as a finite state machine(FSM) in each of the storage structures (cache and LLC). A distributed system of cache controllers communicate with each other using transactions and messages to ensure coherence. The type and number of messages and states depends on the particular cache coherence protocol.

In general, there are two classes of protocols, namely snooping-based and directorybased [4]. Snooping-based mechanisms rely on broadcasting messages to all the agents. Most commonly, cores observe the transactions over a shared bus interface and respond accordingly. Collectively, all the controllers ensure coherence. Within directory-based techniques, a central directory holds the state of each data block. State contains information about the current owner (read-write) or sharers (read-only). Requests are point-to-point in directory based controllers. In this study, we consider a snooping-based protocol that relies on a shared bus interconnect, as it is predominant in modern multi-core processors.

Additionally, cache controllers can be classified into invalidate and update protocols, based on action performed in case of a CPU write. An invalidate protocol would request other agents to invalidate their copy of the data block. An update protocol would rather update all existing copies of the block within the system. We restrict our scope to the MESI protocol, which is a popular invalidate technique.

MESI represents the four possible states of a cache block, namely modified, exclusive,

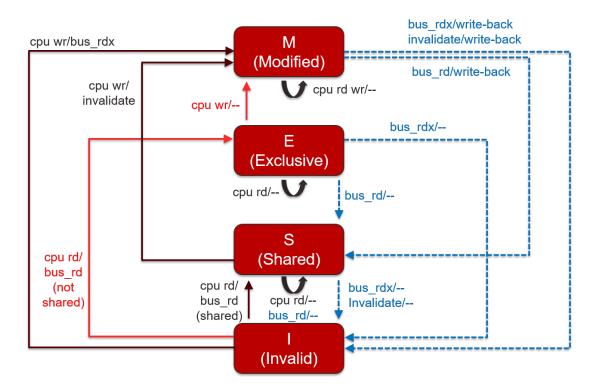

Figure 1.2: The architectural MESI state diagram

shared, and invalid. The architectural state diagram of the MESI protocol is illustrated in Figure 1.2. A processor has read-write access to a block that is in modified or exclusive state in its private cache. At a given time, any one of the agents alone can have a block in modified or exclusive state. A block in shared state provides read-only access to the core.

Transitions to the left of states in Figure 1.2 represent processor side requests and the subsequent controller action on the shared bus. More precisely, read and write are requests from the core; bus rdx (read to modify), bus rd (read-only) and invalidate are requests broadcast on the shared system bus. State transitions to the right on Figure 1.2, signify incoming bus requests and corresponding responses. Collectively, all the cache controllers work together, by adhering to the MESI state diagram, to realize a coherent system.

#### 2. VERIFICATION OF CACHE COHERENCE

In this chapter, we motivate the need for full-proof verification of cache controllers. We present previous work and distinguish it from this thesis in Section 2.2. Thereafter, we describe our approach, objectives, and design implementation in Sections 2.3, 2.4, and 2.5 respectively.

#### 2.1 Need for Robust Verification

The design and verification of cache controllers is notoriously complex [5]. Aside from design and performance considerations, a cache implementation must consider the coherence protocol as well as the communication fabric for functional robustness. The coherence protocol is subject to several race conditions in a truly parallel system with concurrent requests. The MESI protocol defined in Section 1.2 is an abstract model, it simplifies numerous details which are of critical significance in the hardware realization.

Firstly, state transitions are assumed to be atomic in the architectural model. This is impossible to achieve in implementation. The controller would arbitrate for shared resources like the system bus, before performing a state transition. This non-atomicity leads to the existence of transient states. A typical modern processor's cache has about 4 stable states and around 10 transient states [6]. Transient states increase the complexity and lead to additional race conditions. The presence of an atomic bus does not obviate the need for transient states. Although a blocking bus would ensure that not more than one transaction is outstanding on the system bus, state transitions could still be non-atomic. Transient states necessary for a MESI-based controller with an atomic bus is depicted in Figure 2.1 [7]. Transitions due to incoming system bus requests are hidden in Figure 2.1 for simplicity. Race conditions arise when conflicting requests are observed on the processor side and the system bus side. The large number of states and race conditions

Figure 2.1: Simplified MESI state diagram with transition states

make verification and design extremely challenging.

Second, several performance optimizations are introduced in modern designs. The most prominent example is a split transaction bus. A blocking bus is inefficient from a performance viewpoint. Therefore, modern processors allow multiple outstanding requests on the shared system bus. This would require buffers within the cache controller in order to track outstanding requests. Responses to the system bus requests could arrive out of order. As a result, the design complexity increases tremendously. Recent improvements like write-back buffers, complex interconnection networks, hardware transactional memory, and hierarchical caches further contribute to the design complexity.

Additionally, the communication fabric of the controller is prone to deadlock, livelock and starvation. Therefore, we must also verify the communication infrastructure for correctness, liveness, and fairness.

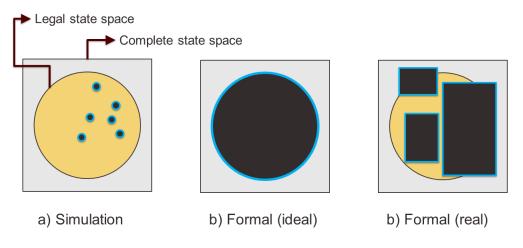

Simulation-based techniques alone are insufficient in the verification of caches. They often fail to identify race conditions and critical failures in corner case scenarios. It is challenging to reach confidence in coherence using simulation due to concurrency, and the large number of states and transitions in a cache controller. Vantrease et al. assert that a total of 60 state transitions exist in the simple MSI protocol, when we consider race conditions [6]. Simulation suffers from the lack of controllability, and tedious debug. Simulation does not provide sufficient fine-grained control to exercise interesting corner cases, mainly due to the rigid nature of test-bench components. Certain legal behavior could be prevented by inherent assumptions made within testbench components. We depend on pseudo-random stimulus to fortuitously exercise and identify failing scenarios. The large number of states and transitions makes it improbable to identify all failing corner cases in simulation, leading to critical bug escapes. Even in cases when failures are exercised, debug is tedious and time-consuming due to large traces in which the failure is identified several thousand cycles after the source of error. Coherence design flaws have escaped into shipping products in the past. A popular example is the Intel core2duo coherence bug, "A139: Cache data access request from one core hitting a modified line in the L1 data cache of the other core may cause unpredictable system behavior." [8]. In order to prevent future bug escapes, design teams must ensure robust verification of the complex cache controller.

Formal verification with clever abstraction techniques is often cited as the ideal method for cache verification. There are few documented examples of a verified cache coherence protocol in SystemVerilog or other hardware description languages [5]. Abstract models of protocols have been formally verified in the past with relative ease. However, there is a significant semantic gap between the architectural model and hardware realization. Therefore, we apply formal property verification to guarantee coherence of our MESI-cache RTL implementation. This was primarily enabled by parameterizing the implementation to solve the complexity problem that would otherwise prevent full-proof verification of the RTL model.

### 2.2 Previous Work

The design and verification of cache has remained an active research focus for over three decades [9]. Numerous advancements have been proposed with emphasis on either performance or security. Specifically within the purview of cache coherence, several techniques have been explored to make the verification problem more tractable. In this section, we summarize efforts aimed at solving the verification challenge of coherence protocols.

Clarke et al. pioneered the use of formal verification for coherence with the Futurebus+ protocol in 1993 [10]. Thereafter, coherence protocols are typically verified using formal techniques only at the architecture level [11, 12, 13, 14, 15] with tools like Murphi and TLA+. Complexity and the lack of formal tool support for SystemVerilog prohibited effective application of formal methods to the register-transfer-level (RTL) description. At the abstract level, subtle implementation details like timing are excluded to reduce complexity, which in turn facilitates formal techniques. However, there is significant semantic gap between the abstract model and HDL implementation. It is often more challenging to verify coherence of the HDL implementation of a formally verified abstract protocol rather than verifying the architectural model [5]. Once the higher level abstract model is formally verified, equivalence verification is attempted between the RTL implementation and the abstract model. Pong et al. used formal techniques to verify the protocol, but depended on random simulations to verify the implementation [11]. Standard practice is to use simulation for RTL verification of cache controllers. Refinement checkers are developed from the high-level model for use in simulation-based verification of RTL [15]. There are few published examples of formally verified cache hardware descriptions [5]. Dave et al. suggest the use of high-level synthesis to tackle the verification problem [5]. They demonstrate that automatic synthesis of high-performance, realistic coherence protocols is feasible using Bluespec SystemVerilog (BSV), a guarded atomic hardware description language. Formal verification is performed on a modular, parameterized description in BSV. However, this technique has not been adopted in the industry due to limitations of high-level synthesis.

Recent developments in formal tools, increasing computation power, and main memory size permit a thorough reinvestigation of the applicability of formal techniques. Therefore, we focus on applying clever complexity reduction techniques and standard formal property verification to a parameterized MESI cache RTL design using JasperGold, a model checking tool from Cadence.

In our approach, parameterization enables formal property verification on a reduced configuration of the cache design. Parameterization has previously been used in several studies to simplify the complexity problem and to verify coherence protocols at the abstract level [14, 16, 17]. Safety and liveness properties of several complex cache protocols including split transaction versions have been proven in languages like Murphi. Our approach is unique in the manner that we perform parameterized verification at the RTL level in SystemVerilog, unlike earlier studies which focus on the guarded atomic model. To the best of our knowledge, this is the first study to formally verify MESI-based cache coherence at the RTL level using parameterization.

Alternatively, several efforts have aimed to reduce the complexity and simplify cache coherence. A notable example is atomic coherence by Vantrease et al. [6], which proposes the use of optical mutual exclusion to avoid race conditions completely. Verification is simplified by serializing conflicting coherence requests to the same address. Another example is fractal coherence, which provides a design for verification technique of massively multi-core systems, amenable to formal tools. The DeNovo cache coherence protocol pro-

posed by Komuravelli and Adve [18, 19], places limitations on the allowed parallelism to simplify transient states and non-determinism. Our project is independent of the above techniques. Therefore, our findings can be used to augment and assist validation of the above methods.

Runtime or dynamic verification in actual hardware is also proposed as a means to tackle the complex cache verification problem. Cantin et al. demonstrated the use of additional hardware to detect design errors in addition to manufacturing defects [20]. DeOrio et al. proposed CoSma, a novel technology to provide post-silicon validation of cache coherence protocols in multi-core systems [21]. The drawbacks of post-silicon validation is not limited to hardware and performance overhead alone. Diagnosis of functional errors is challenging due to the limited internal node observability in prototype hardware [22]. Although testing in hardware is orders of magnitude faster than simulation and formal verification, postponing detection of functional errors to post-silicon is restricted by the cost of fabrication.

In 2011, a collaborative initiative between JasperGold and ARM resulted in the formal verification of the ARM AMBA ACE cache coherence [23]. They initially performed abstract protocol verification, and subsequently completed full-proof verification of the HDL implementation. Our study has several similarities to the published version of this effort in many aspects. However, intricate details about the properties and techniques employed by the industry collaboration remain confidential. Therefore, this work contributes by highlighting the properties and methods necessary to prove coherence at the RTL level.

### 2.3 Approach

The primary objective is to develop a cache controller that adheres to the specification, coherence and a valid communication infrastructure. The interconnect is required to be free of deadlock, livelock and starvation. Additionally, it should obey the dictated input-

Figure 2.2: Verification approach

output protocol. In this study, we begin with a simple legacy implementation which has been minimally verified with basic test scenarios, similar to how designers in the industry perform a sanity check before release to the verification team. Therefore, the legacy RTL is free from trivial design failures. As illustrated in Figure 2.2, we simultaneously apply simulation and formal techniques to enhance the design as and when we identify bugs. Bugs are essentially deviations from the defined specification. If necessary, we update the specification in case of an architectural flaw. The goal is to complete full-proof verification while eliminating complex corner case bugs and failures.

We offer an effective comparison between simulation and formal methods for the pur-

pose of cache verification at the HDL level. We develop a state-of-the-art, simulationbased environment for this purpose, based on the principles of random, coverage driven verification. Details of the Universal Verification Methodology (UVM) test-bench, a simulation standard predominantly used in the industry, are provided in Chapter 3. The formal verification effort is described in Chapter 4. We apply property verification, with clever abstraction techniques and a sound complexity staging plan, to our design. Parameterization of the design is performed to make formal analysis feasible. Equivalence checking, as reported in Section 4.2 is used to ensure correctness and functionality post-parameterization.

We comment about the return-on-investment of engineering effort in simulation, and formal analysis. Evaluation criteria for the comparison includes, but is not limited to, critical failures identified, ease of debug, length of failing traces, time to develop the environment, and proof of forward progress. Through the effort, we hope to identify methods suited for a symbiotic relationship between the two techniques. We also wish to summarize the design principles required to enable formal analysis of large, complex designs.

#### 2.4 Objectives

The main objectives of this study are outlined below:

- Define properties necessary to guarantee coherence, and correctness of the communication infrastructure

- Identify techniques to achieve a synergistic collaboration between simulation and formal

- Provide a foundation for formal verification of complex, performance-aggressive cache designs

- Highlight design principles necessary to enable large scale formal verification

• Develop an effective comparison between simulation and formal methods for coherence verification at the RTL level

### 2.5 Design Implementation

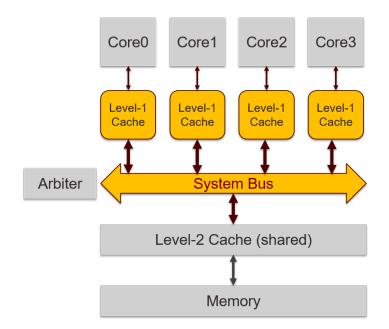

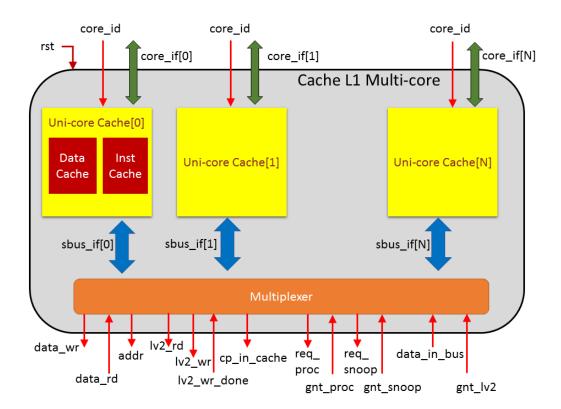

The cache implementation under consideration is snooping-based with a shared system bus and uses the MESI coherence protocol. We perform robust verification to transform a readily available, toy design into a synthesizable, bug-free, product-ready design. A block diagram of the envisioned system is presented as Figure 2.3. We strive to develop a robust Register Transfer Level (RTL) description of the level-1 cache and system bus module. For simulation purposes, we use behavioral models of the cores, arbiter, level-2 cache, and memory block. The design is heavily parameterized with numerous options available including number of cores, address width, data width, cache line size, and cache size.

Figure 2.3: System block diagram

Each CPU core is assigned a private level-1 (L1) cache, while all cores share the level-

2 (L2) unified cache. Address space is partitioned into separate instruction and data space. L1 cache is separated into data and instruction cache, but level-2 cache is unified and serves the entire address range. Coherence is maintained through messages on the shared system bus, in adherence to the MESI cache protocol. An arbiter provides exclusive grant of the system bus in a round-robin fashion to ensure fairness. The system bus is atomic; therefore, at any point in time, a maximum of one outstanding request can be pending on the bus. Caches are inclusive, and conform to write-back and write-allocate mechanisms. Additionally, the design policy operates in accordance with a pseudo-LRU (least recently used) cache replacement algorithm. The detailed design specification is included in Appendix A.

#### 3. SIMULATION-BASED VERIFICATION

Simulation is the primary verification technique for integrated circuit design, widely used in the industry for over three decades now [24, 25]. Input stimulus is fed to the design-under-verification (DUV) continuously throughout the duration of the test. Observed outputs are compared with the expected outputs, usually generated by an independent reference model. Considerable amount of infrastructure is required to be developed before any verification can be performed. Common components include stimulus generators, output monitors, checkers, coverage models, and scoreboards. Stimulus generators determine inputs to the DUV at every instance (clock cycle). Output monitors capture the observed outputs into high-level transactions, which are eventually forwarded to the scoreboard. Checkers are embedded within the monitors and scoreboards to detect forbidden behavior or specific failures. Coverage monitors are required to ensure that the entire range of functionality has been verified. Scoreboards generally house high-level checkers and reference models. Most verification components are interdependent. Therefore, substantial time and effort is required even before basic, typical behavior can be verified.

Over the years, substantial improvements in methodology have resulted in increased efficiency and shorter verification cycles. The key technologies responsible are pseudorandom stimulus, intellectual property (IP) based design [26], metric-driven approach, assertion-based verification [27], and standardized methodologies. Improvements are primarily focused on enhancing re-use, predictability, ease of use, and automation. Though often incomplete, pseudo-random stimulus is effective in detecting corner cases and covering a wide range of behavior in a single test scenario. Assertions are critical to detect flaws early in the design cycle. They pin-point to the actual source of the failure, unlike high-level checkers, which usually detect failures late and fail to indicate the source. Layered stimulus is essential for easy debug and understanding. Standard, open methodologies like OVM, VMM and UVM provide crucial interoperability between tools, companies and vendors. We use present-day industry standard techniques throughout the project to get an accurate comparison between formal and simulation, with respect to cache verification.

In this chapter, we describe the simulation-based verification effort in detail. We develop a state-of-the-art Universal Verification Methodology (UVM) test-bench (TB) built on SystemVerilog (SV). Proven standard industry practices like coverage (metric) driven closure, pseudo-random stimulus, and embedded assertions are rigorously enforced and followed [24, 28, 29].

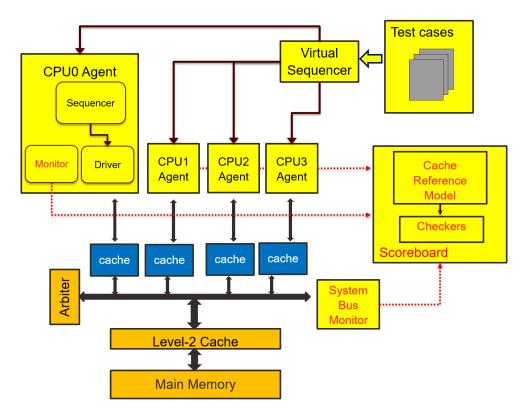

Figure 3.1: UVM verification environment

#### **3.1 UVM Verification Environment**

UVM is the industry standard technique used for functional hardware verification [24, 29, 30]. We develop a complete UVM verification environment with pseudo-random stimulus and a metric-driven approach to verify our cache design. A key component of this environment is the transaction-accurate reference model which is used as the golden version. Figure 3.1 represents the overall structure of the test-bench. UVM components developed include CPU agent, virtual sequencer, test cases, scoreboard and the system bus monitor. Behavioral models are used to describe the level-2 cache, memory, and arbiter. The RTL blocks and behavioral models are borrowed from a previous project, while UVM components are devised from scratch. It is important to note that the design (RTL) was partially verified using a testbench-based verification environment in an earlier project with directed testing. This was similar to a minimalistic test-bench typically used by designers to verify basic functionality. Therefore, trivial bugs have been weeded out of the design well in advance. Behavioral models are assumed to be error-free. Hence, the main focus of verification is the multi-core level-1 cache.

The UVM verification components (UVCs) used in the environment are described below.

#### • CPU Agent:

The CPU agent extends from the 'uvm\_agent' base class. It consists of a monitor, a driver, and a sequencer. It mimics the role of a CPU core connected to the level-1 cache in the final SoC design. Sub-components and their functions are listed below:

**Driver:** extends from 'uvm\_driver' base class. It has access to the CPU-Lv1 interface, through which it interacts with the DUV. It drives signals on the interface based on transactions received from the sequencer. It connects to the sequencer through a handshake mechanism inbuilt in UVM.

- **Sequencer:** extends from 'uvm\_sequencer' base class. It receives transactions from the virtual sequencer and forwards it to the driver. It behaves in a sequential manner. Therefore, a maximum of one transaction is driven at any given point of time.

- **Monitor:** extends from 'uvm\_monitor' base class. It also has access to the CPU-Lv1 interface, but it can only passively observe the signals. It does not have the capability to affect any of the interface signals. It packages observed behavior into meaningful CPU monitor packets, which are passed onto the scoreboard for high-level checks. Simple interface level checks are implemented as assertions in the monitor. Coverage collectors are also realized in this component.

### • System Bus Monitor:

The system bus monitor (SBUS) is a passive component extending from base class 'uvm\_monitor'. It observes signals on the system bus interface to create an SBUS packet. This packet is sent to the scoreboard for comparison with the expected SBUS packet. SBUS contains checkers for the DUV outputs on the system bus interface. Collectors are present to monitor coverage on bus activity.

### • Scoreboard:

The scoreboard, which extends from 'uvm\_scoreboard', houses the cache reference model and high level checkers. It is mainly responsible for ensuring transaction accuracy of the DUV outputs. Two broad classes of DUV outputs are the data returned to the CPU agent, and system bus activity necessary for coherence. The cache reference model mimics the complete functionality of the DUV. Behavioral modeling combined with associative arrays facilitate an efficient implementation in SystemVerilog. The reference model is similar to a guarded atomic model. It assumes that transactions are atomic, which is not always true in the RTL implementation. It provides the expected data and system bus activity for comparison with observed output packets.

#### • Virtual Sequencer:

This component is crucial to have fine-grained control of the transactions on each of the CPU agents. It is also referred to as multi-channel sequencer. We define temporal relations between operations on agents through the virtual sequencer. For instance, we can define parallel transactions on each of the CPU agents. It receives a sequence from the test class and forwards transactions to the agents as specified in the virtual sequence.

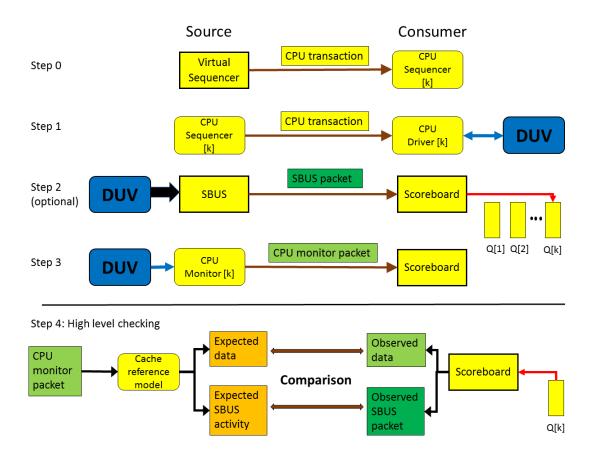

UVM data items enable communication between the various verification infrastructure components. Three types of transactions are used, namely CPU driver transaction, CPU monitor packet, and SBUS packet. CPU driver transaction is created in the test class and is consumed by the CPU driver. CPU monitor packet, as is obvious from the name, is born in the CPU monitor and consumed by the scoreboard. Similarly, SBUS packet is transferred from SBUS to the scoreboard. Member elements and their corresponding descriptions are presented in Tables 3.1, 3.2, and 3.3.

| Member       | Description                                                   |

|--------------|---------------------------------------------------------------|

| Request type | Read or write request                                         |

| Data         | Write data for a write request                                |

| Address      | Address to be accessed                                        |

| Cache type   | Instruction or data cache access                              |

| Wait cycles  | Number of clock cycles to wait before driving the transaction |

Table 3.1: Elements of CPU driver transaction

| Table 3.2: Elements of CPU monitor packe | et |

|------------------------------------------|----|

|------------------------------------------|----|

| Member       | Description                                                      |

|--------------|------------------------------------------------------------------|

| Request type | Read or write request                                            |

| Data         | Data from cache for read or CPU for write                        |

| Address      | Address to be accessed                                           |

| Cache type   | Instruction or data cache access                                 |

| Service time | Number of clock cycles for the entire transaction                |

| Illegal      | Flag to indicate if transaction is invalid i.e. write to I-cache |

Table 3.3: Elements of SBUS packet

| Member              | Description                                               |

|---------------------|-----------------------------------------------------------|

| Bus request type    | BusRD or BusRDX or Invalidate or IcacheRD                 |

| Cache number        | ID of the primary cache which obtained bus access         |

| Address             | Primary address of the bus request                        |

| Read data           | Data returned to the primary bus request                  |

| Request serviced by | ID of the cache which serviced the primary bus request    |

| Copy in cache       | Flag to indicate if 'cp_in_cache' was asserted            |

| Shared              | Flag to indicate if 'shared' signal was high              |

| Snoop requests      | ID of all the caches which requested snoop access         |

| Snoop write back    | Flag to indicate if snoop cache performed write-back      |

| Write data snoop    | Data of the snoop write-back                              |

| Dirty evict flag    | Indication if the primary cache evicted a dirty block     |

| Dirty evict address | Address of the evicted cache line                         |

| Dirty evict data    | Data of the eviction                                      |

| Service time        | Total number of clock cycles taken by the bus transaction |

The verification flow for a single CPU operation in this test-bench is depicted in Figure 3.2. The CPU transaction is first received by the driver, which stimulates the DUV input interface accordingly. If the operation requires a system bus message, DUV would request for bus access and initiate the creation of a SBUS packet. Once the bus request is complete, the system bus monitor forwards the packet to the scoreboard. Depending on the primary cache ID, scoreboard pushes the packet into an appropriate queue. Next, DUV can respond to the CPU agent with the required data(read request) or 'acknowledge' signal (write request), completing the CPU operation. As soon as the transaction is completed, the CPU monitor transmits the monitor packet to the scoreboard. Scoreboard feeds the CPU packet to the reference model, which in turn provides the ideal data and system bus activity. Finally, expected SBUS packet is compared with the observed bus activity by popping an SBUS packet from the appropriate queue.

Figure 3.2: Verification flow for a single CPU transaction

A key feature of the verification environment, like the RTL design, is that it is highly parameterized. We can easily configure features like address width, data width, cache size, length of a cache block, and number of cores. Parameters can be adjusted with no changes to the test-bench infrastructure. Principles of modularity, re-use, and interoperability are followed rigorously by adhering to UVM guidelines.

#### 3.2 Verification Scenarios

A prudent verification plan is crucial for success in the first attempt. In the previous section, we discussed the test-bench infrastructure and verification flow. In this section, we describe critical features, verification methods and specific test cases identified during the planning stage.

| Function              | Description                                                    |

|-----------------------|----------------------------------------------------------------|

| Basic connectivity    | Ensure that the input-output interface is functional.          |

| IO protocol adherence | Design should adhere to the input-output protocol as specified |

| Read to I-cache       | Read operation to the instruction cache                        |

| Write to I-cache      | Write operation to instruction cache should be ignored         |

| Read to D-cache       | Data cache must supply appropriate data to the CPU             |

| Write to D-cache      | Data should be written to the correct address                  |

| PLRU I-cache          | Pseudo LRU replacement policy must be followed by the in-      |

|                       | struction cache                                                |

| PLRU D-cache          | Pseudo LRU replacement policy must be accurate in the data     |

|                       | cache operation                                                |

| MESI protocol         | Cache should respond/send messages on the system bus as ne-    |

|                       | cessitated by the MESI protocol (data cache only)              |

Table 3.4: Functions to be verified

Detailed design specification, provided in Appendix A, is treated as the golden reference. The level-1 multi-core cache design is the main focus of our verification effort. We assume that the level-2 cache (LLC), the arbiter and memory are bug-free behavioral descriptions. As mentioned earlier, both the design and verification environment are parameterized for a flexible number of cores. We concentrate on a 4-core RTL block comprising of four uni-core cache instantiations. We do not sub-divide the process into different levels of verification. We verify the complete RTL block as one single entity. However, particular test cases would focus only on the functionality of a uni-core cache. We adopt a Grey-box approach in this endeavor, by tapping into few signals internal to the multi-core block. Stimulus is pseudo-random, as scenarios are predominantly pseudo-random with a few directed test cases.

Features identified as crucial for verification are listed in Table 3.4. One or more features are verified in each of the test scenarios described in Table 3.5. Amongst the features, MESI operation is most challenging to verify and debug, due to the sheer number of possibilities. A total of 22 test scenarios were planned and executed. The primary cache and the snooping caches involved were randomized for every test.

| No. | Scenario           | Description                                                  |  |  |

|-----|--------------------|--------------------------------------------------------------|--|--|

| 1   | Read miss I-cache  | - Initiate a read request to a block not present in the      |  |  |

|     |                    | instruction cache                                            |  |  |

| 2   | Read hit I-cache   | - Initiate a read request to an instruction block            |  |  |

|     |                    | - Wait for the data to arrive in cache                       |  |  |

|     |                    | - Initiate a read request to the same block                  |  |  |

| 3   | Write miss I-cache | - Initiate a write request to a block not present in the     |  |  |

|     |                    | instruction cache                                            |  |  |

| 4   | Write hit I-cache  | - Initiate a read request to an instruction block            |  |  |

|     |                    | - Wait for the data to arrive in cache                       |  |  |

|     |                    | - Initiate a write request to the same block                 |  |  |

| 5   | Read miss D-cache  | - Initiate a read request to a block not present in the data |  |  |

|     | serviced by L2     | cache of any processor                                       |  |  |

Table 3.5: Test scenarios with description

| No.                                 | Scenario            | Description                                                |

|-------------------------------------|---------------------|------------------------------------------------------------|

| 6                                   | Read miss D-cache   | - Read request to a block on the secondary CPU-1           |

|                                     | serviced by another | Case 1: Snoop cache is in M                                |

|                                     | core's cache        | * Write request to block on secondary CPU-1                |

|                                     |                     | Case 2: Snoop cache is in E                                |

|                                     |                     | * Do nothing                                               |

|                                     |                     | Case 3: Snoop cache is in S                                |

|                                     |                     | * Read request to block on secondary CPU-2                 |

|                                     |                     | - Read request on primary CPU to the same block            |

| 7                                   | Read hit D-cache    | -Read request to a data block on primary CPU               |

|                                     |                     | Case 1: Primary cache is in M                              |

|                                     |                     | * Write request to this block on primary CPU               |

|                                     |                     | Case 2: Primary cache is in E                              |

|                                     |                     | * Do nothing; block already in E state                     |

|                                     |                     | Case 3: Primary cache is in S                              |

|                                     |                     | * Read request to this block on secondary CPU              |

|                                     |                     | - Read request on primary Proc to the same block           |

| 8                                   | Write miss D-cache  | - Select a case randomly                                   |

|                                     |                     | Case 1: Secondary CPU cache is in I                        |

|                                     |                     | * Do nothing                                               |

|                                     |                     | Case 2: Secondary CPU cache is in M                        |

|                                     |                     | * Write request to the block on secondary CPU              |

|                                     |                     | Case 3: Secondary CPU cache is in E                        |

|                                     |                     | * Read request to the block on secondary CPU               |

|                                     |                     | Case 4: Secondary CPU cache is in S                        |

|                                     |                     | * Read request on primary and secondary CPUs               |

|                                     |                     | * Evict the block from primary cache                       |

|                                     |                     | - Write request to block on the primary CPU                |

| 9                                   | Write hit D-cache   | - Select a case randomly                                   |

|                                     |                     | Case 1: primary CPU cache is in M                          |

|                                     |                     | * Write request to the data block                          |

|                                     |                     | Case 2: primary CPU cache is in S                          |

|                                     |                     | * Read request on both primary and secondary CPU           |

|                                     |                     | Case 3: primary CPU cache is in E                          |

|                                     |                     | * Read request to the data block                           |

| - Write request on primary CPU to t |                     | - Write request on primary CPU to the same block.          |

| 10                                  | LRU read I-cache    | - Initiate read requests R1-R8 to 8 instruction blocks of  |

|                                     |                     | the same set index, ensure that at least 5 of these blocks |

|                                     |                     | are unique                                                 |

Table 3.5: Continued

| No. | Scenario            | Description                                                |  |  |

|-----|---------------------|------------------------------------------------------------|--|--|

| 11  | LRU read D-cache    | - Initiate read requests R1-R8 to 8 data blocks of the     |  |  |

|     |                     | same set index, ensure that at least 5 of these blocks are |  |  |

|     |                     | unique                                                     |  |  |

| 12  | LRU write D-cache   | - Initiate read/write operations A1-A8 to 8 data blocks    |  |  |

|     |                     | of the same set index, ensure that at least 5 of these     |  |  |

|     |                     | blocks are unique and that the last 4 accesses are write   |  |  |

|     |                     | operations                                                 |  |  |

| 13  | Snoop BusRd request | - Randomly select a case                                   |  |  |

|     |                     | Case 1: Primary CPU cache is in I                          |  |  |

|     |                     | * Do nothing                                               |  |  |

|     |                     | Case 2: Primary CPU cache is in E                          |  |  |

|     |                     | * Read request to the block of interest on primary         |  |  |

|     |                     | Case 3: Primary CPU cache is in M                          |  |  |

|     |                     | * Write request to the block of interest on primary        |  |  |

|     |                     | Case 4: Primary CPU cache is in S                          |  |  |

|     |                     | * Read request to the block on secondary CPU               |  |  |

|     |                     | * Read request to the block on primary CPU                 |  |  |

|     |                     | * Evict the block of interest on secondary CPU             |  |  |

|     |                     | - Read request on the secondary CPU for the block          |  |  |

|     |                     | - Confirm the state transition in primary cache            |  |  |

| 14  | Snoop BusRdx re-    | - Randomly select a case                                   |  |  |

|     | quest               | Case 1: Primary CPU cache is in I                          |  |  |

|     |                     | * Do nothing                                               |  |  |

|     |                     | Case 2: Primary CPU cache is in E                          |  |  |

|     |                     | * Read request to the block of interest on primary         |  |  |

|     |                     | Case 3: Primary CPU cache is in M                          |  |  |

|     |                     | * Write request to the block of interest on primary        |  |  |

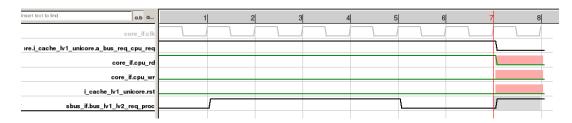

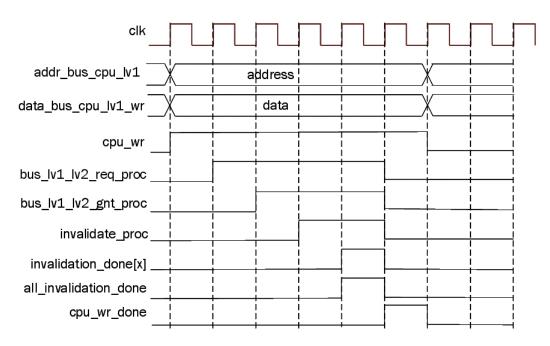

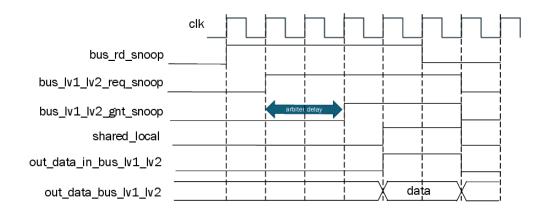

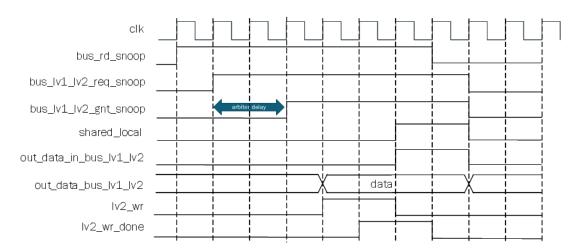

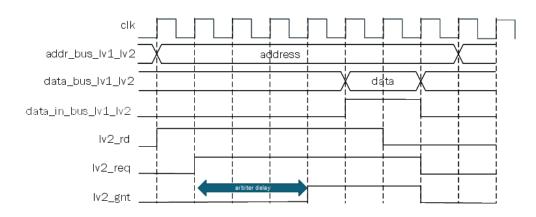

|     |                     | Case 4: Primary CPU cache is in S                          |  |  |