## MILLIMETER-WAVE CONCURRENT DUAL-BAND BICMOS RFIC

## FRONT-END MODULE FOR COMMUNICATION AND SENSING SYSTEMS

A Dissertation

by

## YOUNGMAN UM

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Cam Nguyen          |

|---------------------|---------------------|

| Committee Members,  | Robert D. Nevels    |

|                     | Chin B. Su          |

|                     | Binayak Mohanty     |

| Head of Department, | Miroslav M. Begovic |

May 2017

Major Subject: Electrical Engineering

Copyright 2017 Youngman Um

### ABSTRACT

This dissertation presents new circuit architectures and techniques for improving several key performances of BiCMOS RFIC building blocks that are used in wireless communication and sensing systems operating at millimeter-wave frequencies. The developed circuits and front-end module can be employed in concurrent dual-band transceivers for communication and sensing systems such as phased array and RFID systems.

New 0.18- $\mu$ m CMOS dual-bandpass filtering single-pole double-throw (SPDT) and transmit/receive (T/R) switches have been developed, and they operate in two different frequency bands centered at around 40 and 60 GHz (Design 1) and 24 and 60 GHz (Designs 2, 3 and 4). Design 1 is a concurrent dual-bandpass filtering T/R switch consisting of three SPDT switches based on a 3<sup>rd</sup> order band-pass filter with shunt nMOS transistors as the switching function. Design 2 is a 24/60-GHz concurrent dual-bandpass T/R switch consisting of dual-band  $\lambda/4$  LC networks and resonators with shunt nMOS transistors as the switching function. Design 3 is a dual-band SPDT and T/R switches, which are capable of band-pass filtering as well as separate and concurrent switching operations in single/dual-band and transmission/reception. These components can act as diplexers with switching functions. Design 4 is a wideband concurrent dual-band SPDT switch with integrated dual-bandpass filtering, which is configured to make it approximately equivalent to a dual-band resonator in the on-state operation.

A fully integrated 24/60-GHz concurrent dual-band LNA utilizing a dual-band LC circuit has been proposed. The LNA is based on a two-stage cascode topology with inductive degeneration. The dual-band LC circuit has the quarter-wavelength characteristic at two different frequencies, and it shows the dual pass-band and single stop-band characteristics when it is connected to the ground in shunt. Due to the cancellation of the stop-band signal and low-pass response by the LC circuit connected to the cascode nodes of the 1<sup>st</sup> and 2<sup>nd</sup> stages in the LNA, the LNA presents high stop-band rejection and good gain balance at 24 and 60 GHz.

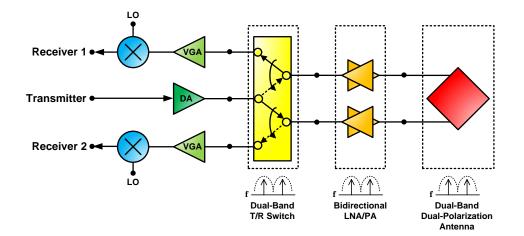

A concurrent dual-band front-end module (FEM) consisting of a 24/60-GHz dual-band antenna, a five-port T/R switch, two LNAs and one PA has been proposed. The FEM can be employed in systems with dual-polarization, for instance, phased array and RFID reader systems.

## DEDICATION

To my beloved my wife Yeomyeong Jeon, son Jisung Joseph Um, daughter Jooah

Sophia Um, and my heavenly father

for all their love and the unbelievable support

### ACKNOWLEDGEMENTS

This dissertation would have not been completed without many people's help. First of all, I would like to thank my committee chair and advisor, Prof. Cam Nguyen for his guidance, support, and encouragement throughout my doctoral degree period at Texas A&M University.

I sincerely thank my committee members, Prof. Robert Nevels, Prof. Chin Su, and Prof. Binayak Mohanty for their comments and support. I am also grateful to Prof. Kai Chang for his kind encouragement.

I would like to send my thanks to Prof. Jaehoon Choi at Hanyang University, Seoul, Republic of Korea for his encouragement and help.

I would like to express my thanks to Mr. Cody Hale, design engineering manager at Qorvo Inc. He offered me an internship opportunity and I had an excellent experience and he gave me many technical advices during the internship period.

I would like to thank my former and current laboratory colleagues, Dr. Cuong Huynh, Dr. Jaeyoung Lee, Dr. Kyoungwoon Kim, Dr. Donghyun Lee, Dr. Sunhwan Jang, Dr. Chadi Geha, Juseok Bae and Meng-Jie Hsiao for their technical discussions, help, and friendship. I wish them all the best and great success in their careers and life.

I would like to send my thanks to Prof. Byul Hur in the Department of Engineering Technology and Industrial Distribution at Texas A&M University. In spite of the short time, he has given me encouragement and support. I would like to express my special and deepest appreciation to my family members. I thank my parents, Chonggook Um and Hongsuk Lee for their love, prayers, and support not only during my doctoral degree period but also during my entire life. And, I would like to thank my sister, Jayoung Um for her encouragement. Also, I would like to show my appreciation to my father-in-law and mother-in-law, Insuk Jeon and Boknam Yoon for their constant prayers and support.

I would like to show my thanks to my beloved wife, Yeomyeong Jeon, and two children, Jisung Um and Jooah Um for their love, support and encouragement. I should express my sincere appreciation for their sacrifice. I will give back what they have given me.

Finally, I would like to express all gratitude and appreciation to my heavenly father. He has given me the strength to finish my doctoral degree. I am so grateful for his love, guidance, and support.

## **CONTRIBUTORS AND FUNDING SOURCES**

## Contributors

Part 1, faculty committee recognition

This work was supervised by the dissertation committee consisting of Professor Cam Nguyen, Robert D. Nevels and Chin B. Su of the Department of Electrical and Computer Engineering and Professor Binayak Mohanty of the Department of Biological and Agricultural Engineering.

#### Part 2, student/collaborator contributions

The 24- and 60-GHz power amplifiers (PAs) and 24/60-GHz diplexer depicted in Chapter IV was developed by Dr. Kyoungwoon Kim of the Department of Electrical and Computer Engineering and the 24-GHz PA was published in 2014.

All other work conducted for the dissertation was completed by Youngman Um independently.

### **Funding Sources**

This work was made possible in part by the National Priorities Research Program (NPRP) under Grant Number 6-241-2-102.

Its contents are solely the responsibility of the authors and do not necessarily represent the official views of the Qatar National Research Fund (a member of Qatar Foundation).

## TABLE OF CONTENTS

|                                                            | Page  |

|------------------------------------------------------------|-------|

| ABSTRACT                                                   | ii    |

| DEDICATION                                                 | iv    |

| ACKNOWLEDGEMENTS                                           | v     |

| CONTRIBUTORS AND FUNDING SOURCES                           | vii   |

| TABLE OF CONTENTS                                          | viii  |

| LIST OF FIGURES                                            | xi    |

| LIST OF TABLES                                             | xviii |

| CHAPTER I INTRODUCTION                                     | 1     |

| 1.1 Introduction and Background                            | 1     |

| 1.2 System Description                                     | 7     |

| 1.2.1 A 24/60-GHz Dual-Band Dual-Mode RFID Reader System   | 7     |

| 1.2.2 A 24/60-GHz Concurrent Dual-Band Phased Array System | 12    |

| 1.2.3 Possible Applications                                | 14    |

| 1.3 Dissertation Organization                              | 16    |

| CHAPTER II CMOS DUAL-BAND BAND-PASS FILTERING SWITCH       | 17    |

| 2.1 Background and Motivation                              | 17    |

| 2.1.1 MOSFET with Deep N-Well                              | 18    |

| 2.1.2 Trade-Off for Typical Switch Topology                | 21    |

| Insertion Loss                                             | 22    |

| Isolation                                                  | 23    |

| Figure of Merit (FOM)                                      | 23    |

| Power Handling Capability and Nonlinearity                 | 24    |

| 2.1.3 Basic Switch Topology                                | 26    |

| 2.1.4 Motivation for Multi-Band Band-Pass Filtering Switch | 29    |

| 2.1.5 Band-Pass Filter Theory                              | 32    |

| Admittance Inverter (J-inverter) Implementation            | 35    |

| Dual-Band Parallel Resonator                               | 36    |

| 2.2 High-Isolation Multi-Port Millimetre-Wave CMOS Dual-Band T/R Switch  |    |

|--------------------------------------------------------------------------|----|

| Integrated Band-Pass Filtering Function (Design 1)                       | 38 |

| 2.2.1 40/60-GHz Dual-Band Band-Pass Filter                               | 38 |

| 2.2.2 40/60-GHz Dual-Band Band-Pass Filtering SPDT Switch                | 42 |

| 2.2.3 40/60-GHz Dual-Band Band-Pass Filtering T/R Switch                 | 44 |

| 2.2.4 Simulation and Measurement Results                                 | 48 |

| 2.3 A Millimeter-Wave CMOS Dual-Bandpass T/R Switch with Dual-Band       |    |

| LC Network (Design 2)                                                    | 52 |

| 2.3.1 Dual-Band Quarter-Wavelength LC Circuit                            | 52 |

| 2.3.2 24/60-GHz-Bandpass Filtering T/R Switch                            | 58 |

| 2.3.3 Simulation and Measurement Results                                 | 62 |

| 2.4 High-Isolation Multi-Mode Multi-Function 24/60-GHz CMOS Dual-Band    |    |

| Band-Pass Filtering SPDT and T/R Switches (Design 3)                     | 66 |

| 2.4.1 Single-Band 24- and 60-GHz Band-Pass Filtering SPST Switches       | 67 |

| 2.4.2 24/60-GHz Dual-Band Band-Pass Filtering SPDT Switch                | 70 |

| 24-GHz Single-Band Operation Mode                                        | 71 |

| 60-GHz Single-Band Operation Mode                                        | 73 |

| 24/60-GHz Concurrent Dual-Band Operation Mode                            | 73 |

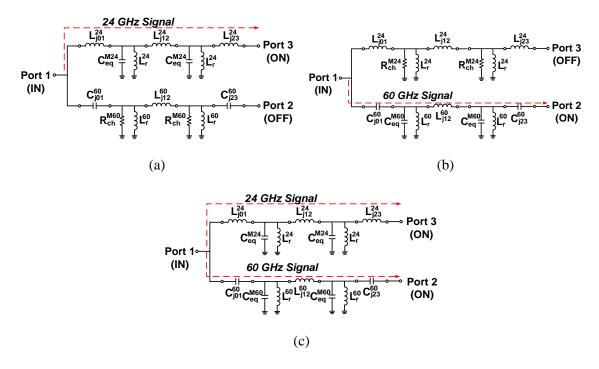

| 2.4.3 24/60-GHz Dual-Band Band-Pass Filtering T/R Switch                 | 74 |

| 24-GHz TX/RX Concurrent Operation                                        | 77 |

| 60-GHz TX/RX Concurrent Operation                                        | 78 |

| 24-GHz RX/60-GHz TX Concurrent Dual-Band Operation                       | 79 |

| 2.4.4 Simulation and Measurement Results                                 | 80 |

| 2.5 A Wideband Dual-Bandpass 0.18-µm CMOS SPDT Switch utilizing Dual-    |    |

| Band Resonator Concept (Design 4)                                        | 87 |

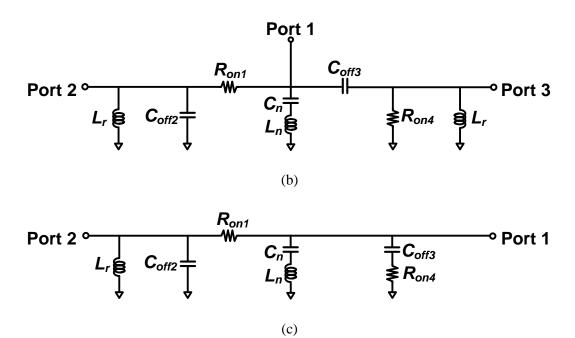

| 2.5.1 Switch Architecture, Design and Analysis                           | 87 |

| 2.5.2 Simulation and Measurement Results                                 | 92 |

| 2.6 Summary of the Developed Switches                                    | 95 |

|                                                                          |    |

| CHAPTER III MILLIMETER-WAVE CONCURRENT DUAL-BAND LOW-                    |    |

|                                                                          | 01 |

|                                                                          | -  |

| 3.1 Fundamentals of Low-Noise Amplifier (LNA) 1                          | 02 |

|                                                                          | 02 |

|                                                                          | 04 |

|                                                                          | 05 |

| 3.1.4 Power Handling Capability and Nonlinearity of the Concurrent Dual- |    |

|                                                                          | 06 |

|                                                                          | 07 |

|                                                                          | 08 |

| •                                                                        | 12 |

|                                                                          | 15 |

|                                                                          | 22 |

|                                                                          | 25 |

|                                                                          |    |

| CHAPTER IV DESIGN OF A SIGE BICMOS CONCURRENT DUAL-BAND<br>FRONT-END MODULE            | 127                                    |

|----------------------------------------------------------------------------------------|----------------------------------------|

| <ul> <li>4.1 Introduction</li></ul>                                                    | 127<br>127<br>132<br>132<br>134<br>136 |

| CHAPTER V SUMMARY AND CONCLUSION                                                       | 138                                    |

| <ul><li>5.1 Dissertation Summary</li><li>5.2 Recommendations for Future Work</li></ul> | 138<br>141                             |

| REFERENCES                                                                             | 142                                    |

# LIST OF FIGURES

| FIGUI | RE                                                                                                                                                                                                                                                                                  | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

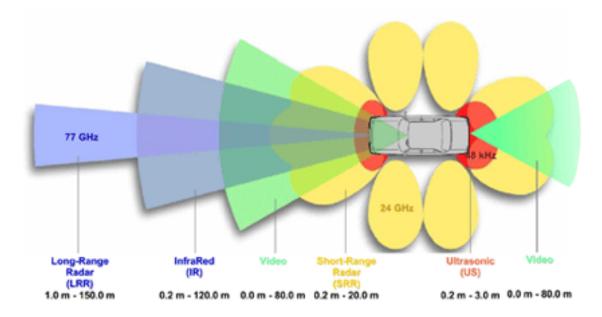

| 1.1   | Vehicle radar system                                                                                                                                                                                                                                                                | 3    |

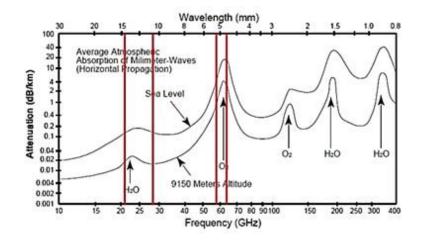

| 1.2   | Air attenuation at microwave and millimeter-wave frequencies                                                                                                                                                                                                                        | 3    |

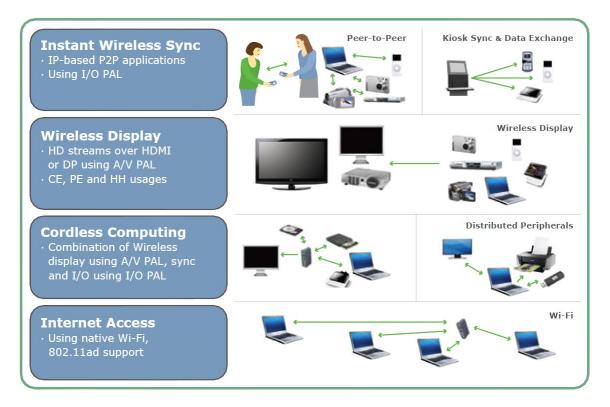

| 1.3   | Applications for 60-GHz communication systems                                                                                                                                                                                                                                       | 4    |

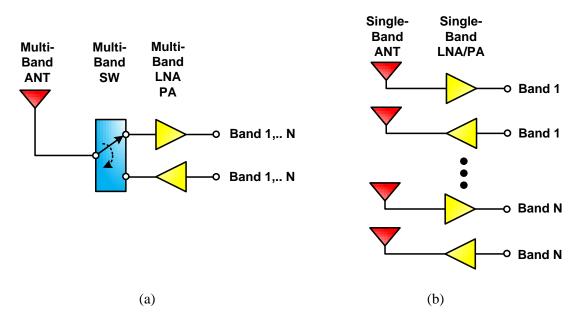

| 1.4   | Block diagram of a multi-band system: (a) One multi-band system and (b) multiple and parallel system operating at different operating frequency bands                                                                                                                               | 5    |

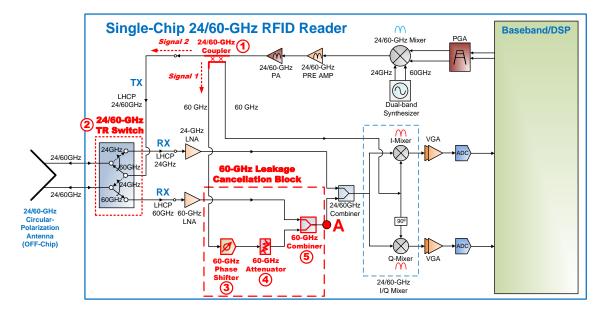

| 1.5   | Block diagram of the proposed 24/60-GHz dual-band RFID reader system                                                                                                                                                                                                                | 7    |

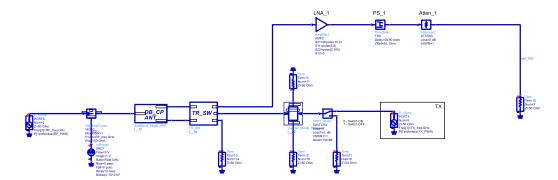

| 1.6   | ADS simulation setup to verify the TX leakage cancellation technique                                                                                                                                                                                                                | 9    |

| 1.7   | Simulated results of the signals' cancellation at Combiner's output                                                                                                                                                                                                                 | 10   |

| 1.8   | Simulation result comparison for modulation index at the combiner's output: (a) ASK modulation RX input signal, (b) output signal at the combiner's output with TX leakage cancellation block, and (c) output signal at the combiner's output without TX leakage cancellation block | 11   |

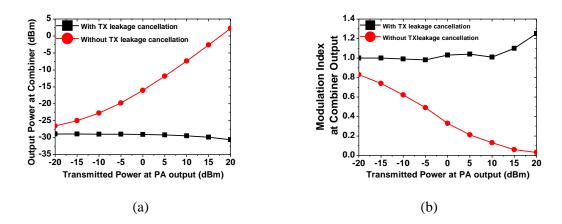

| 1.9   | Simulation results comparison for signal power and modulation index at combiner's output: (a) output powers at combiner's output and (b) modulation index at combiner's output                                                                                                      | 11   |

| 1.10  | Block diagram of the proposed 24/60-GHz concurrent dual-band transceiver for phased array system                                                                                                                                                                                    | 14   |

| 1.11  | Possible applications: (a) 24/60-GHz RFID baggage tracking system and (b) 24/60-GHz satellite communication system                                                                                                                                                                  | 15   |

| 2.1   | Cross sectional view of a deep n-well transistor: (a) schematic (b) equivalent model when $V_c = 1.8$ (c) and 0 V (d), and (e) simulation setup to obtain $R_{on}$ and $C_{off}$                                                                                                    | 19   |

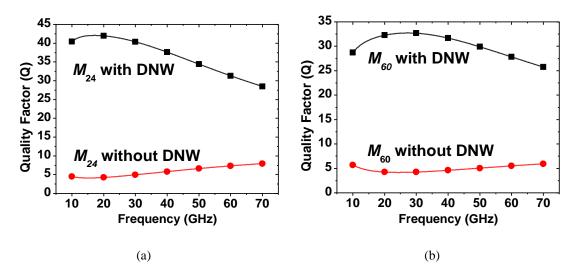

| 2.2   | Simulated Q for off-state nMOS transistors: (a) $M_{24}$ and (b) $M_{60}$ with/without DNW                                                                                                                                                                                          | 21   |

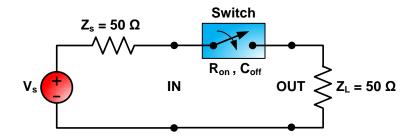

| 2.3  | RF switch model in a 50- $\Omega$ network                                                                                                                                                                                                                                                                              | 22 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.4  | Typical RF receiver chain for total noise figure (NF) calculation                                                                                                                                                                                                                                                      | 22 |

| 2.5  | Descriptions of (a) $P_{1dB}$ , (b) $IP_3$ (c) cascaded nonlinear stages, and (d) measurement set-up for dual-tone signal                                                                                                                                                                                              | 24 |

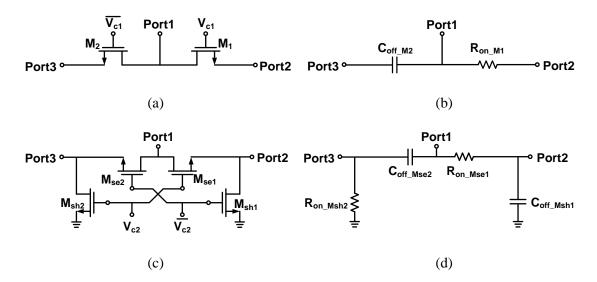

| 2.6  | Fundamental SPDT switch topologies: (a) series switch, (b) equivalent circuit of (a) when $V_{c1} = 1.8 \text{ V}$ , (c) series-shunt switch, and (d) equivalent circuit of (c) when $V_{c2} = 1.8 \text{ V}$ .                                                                                                        | 27 |

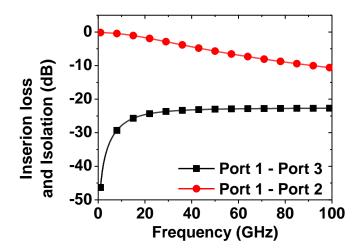

| 2.7  | Simulated IL and ISO for Port 1 – Port 2 and Port 1 – Port 3 of the series-<br>shunt SPDT switch in Fig. 2.6(c)                                                                                                                                                                                                        | 29 |

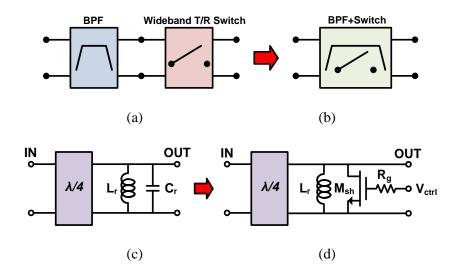

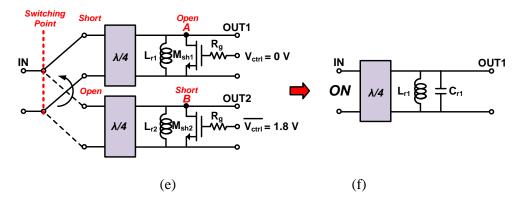

| 2.8  | Band-pass filtering switch design concept: (a) conventional BPF and switch structure, (b) the proposed BPF + switch structure, (c) quarter-wavelength circuit and parallel resonator, (d) quarter-wavelength circuit and parallel resonator replaced with nMOS transistor                                              | 3( |

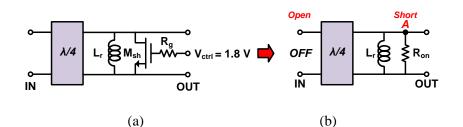

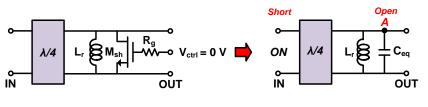

| 2.9  | Operations of the proposed band-pass filtering switch design concept: (a) band-pass filtering switch when $V_{ctrl} = 1.8 \text{ V}$ , (b) equivalent circuit of (a), (c) band-pass filtering switch when $V_{ctrl} = 0 \text{ V}$ , (d) equivalent circuit of (c), (e) SPDT switch, and (f) equivalent circuit of (e) | 31 |

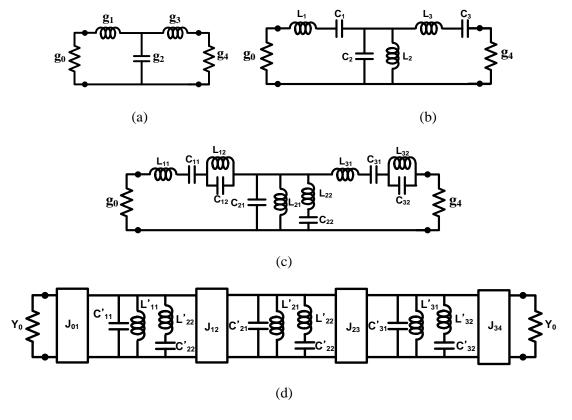

| 2.10 | (a) LPF prototype, (b) BPF prototype, (c) dual-band BPF prototype, and (d) dual-band BPF with J-inverter and parallel resonator                                                                                                                                                                                        | 33 |

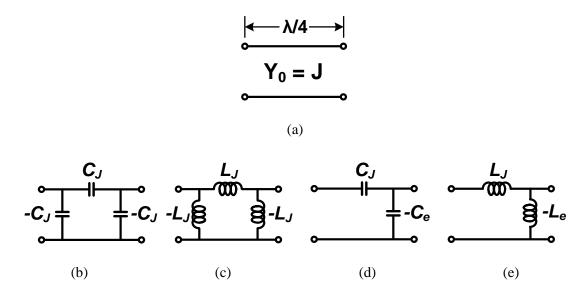

| 2.11 | <ul><li>(a) J-inverter implementation as quarter-wavelength transformer, (b), (c),</li><li>(d) and (e) equivalent lumped-element circuits of J-inverter</li></ul>                                                                                                                                                      | 35 |

| 2.12 | Conventional dual-band parallel resonator                                                                                                                                                                                                                                                                              | 37 |

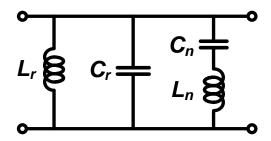

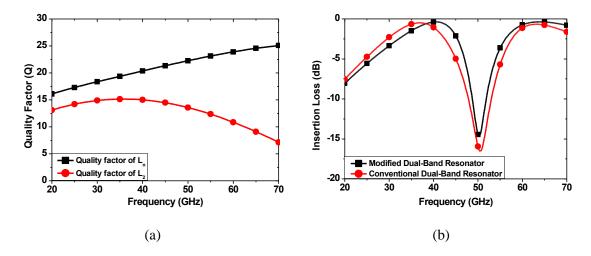

| 2.13 | Evolution of dual-band resonator: (a) conventional dual-band resonator, (b) modified dual-band resonator implementing J-inverter and (c) modified dual-band resonator                                                                                                                                                  | 39 |

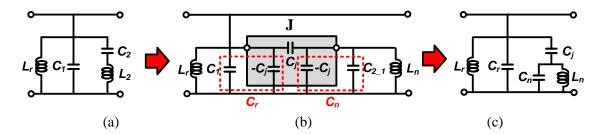

| 2.14 | Comparison of simulated quality factor (Q) of inductors $L_n$ and $L_2$ , and insertion losses of modified and conventional dual-band resonators: (a) quality factors (Q) of inductors $L_n$ and $L_2$ and (b) insertion losses of modified and conventional dual-band resonators                                      | 4( |

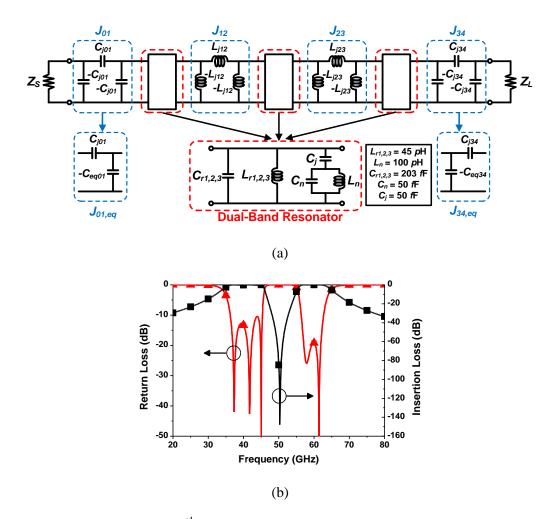

| 2.15 | (a) Schematic of the 3 <sup>rd</sup> order dual-band band-pass filter using dual-band resonator and J-inverter and (b) its return loss and insertion loss                                                                                                                                                              | 41 |

| 2.16 | Schematic of the 40/60-GHz dual-band band-pass filtering SPDT switch                                                                                                                                                                                                            | 42 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.17 | Schematic of the 40/60-GHz dual-band band-pass filtering T/R switch                                                                                                                                                                                                             | 46 |

| 2.18 | A microphotograph of the 40/60-GHz dual-band band-pass filtering T/R switch                                                                                                                                                                                                     | 47 |

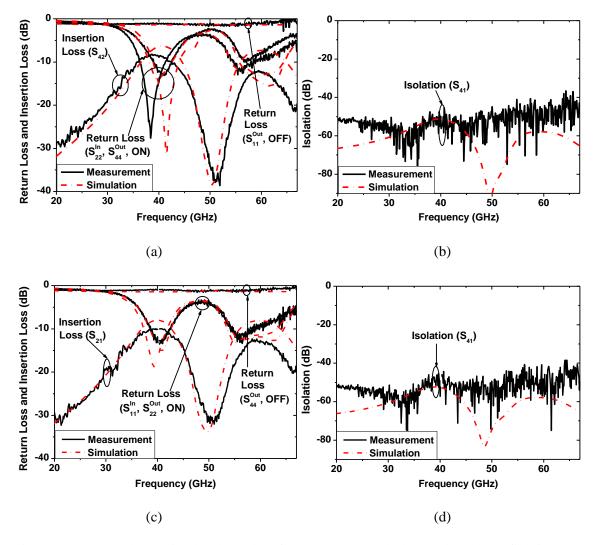

| 2.19 | Measured and simulated results of the 40/60-GHz dual-band band-pass filtering T/R switch: (a) return loss and insertion loss, and (b) isolation for receiving operation mode, (c) return loss and insertion loss, and (d) isolation for transmitting operation mode             | 49 |

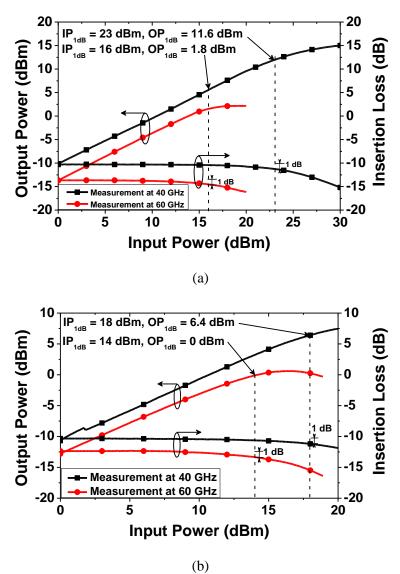

| 2.20 | Measured $P_{1dB}$ of the 40/60-GHz dual-band band-pass filtering T/R switch:<br>(a) individual 40- or 60-GHz input signal (b) concurrent 40 and 60 GHz input signals                                                                                                           | 51 |

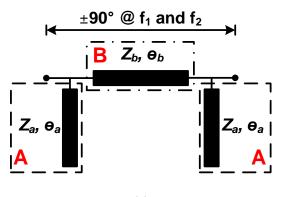

| 2.21 | Quarter-wavelength transmission line at two different frequencies (Model 1), (b) and (c) proposed equivalent dual-band LC networks (Models 2 and 3)                                                                                                                             | 53 |

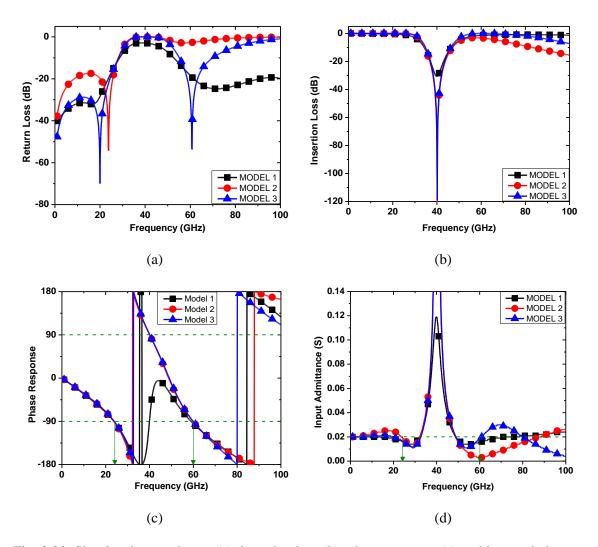

| 2.22 | Simulated return losses (a), insertion loss (b), phase response (c) and input admittance (d) of the 24/60-GHz dual-band transmission line and LC networks (Model 1, 2 and 3) shown in Fig. 2.21                                                                                 | 57 |

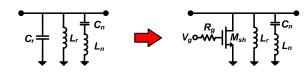

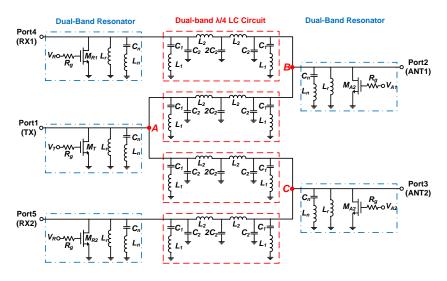

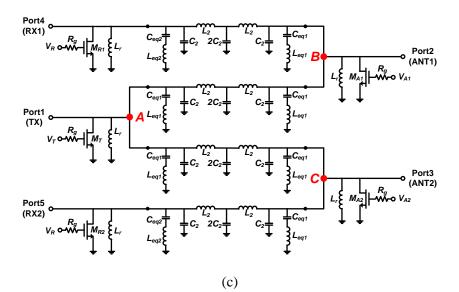

| 2.23 | Schematics of the 24/60-GHz dual-band resonator (a) and dual-bandpass T/R switch (b) and (c)                                                                                                                                                                                    | 59 |

| 2.24 | Microphotograph of the fabricated 24/60-GHz dual-bandpass T/R switch. The port numbers correspond to those in Fig. 2.23(c)                                                                                                                                                      | 61 |

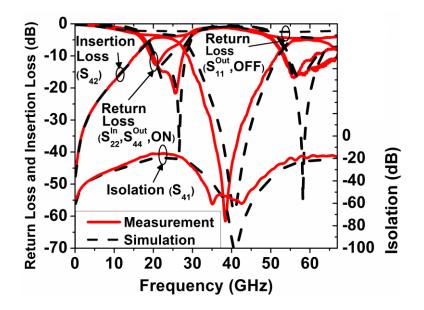

| 2.25 | Measured and simulated results of the 24/60-GHz dual-bandpass T/R switch: (a) receiving and (b) transmitting operations                                                                                                                                                         | 63 |

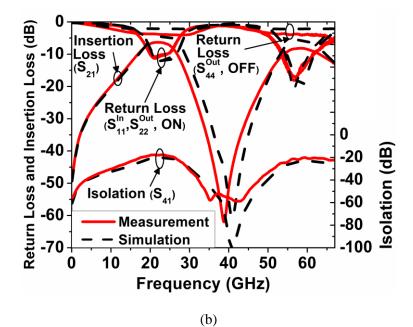

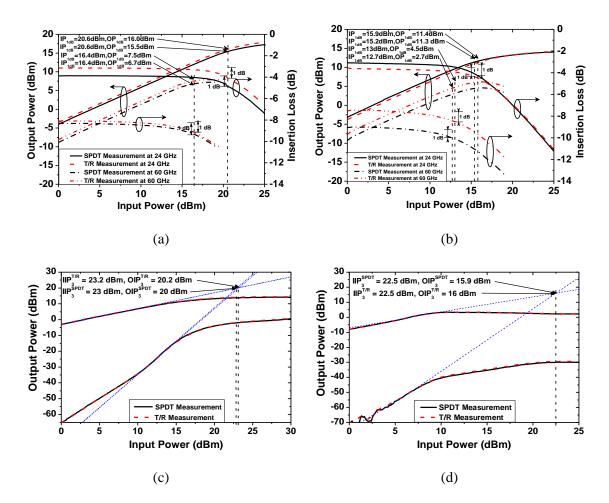

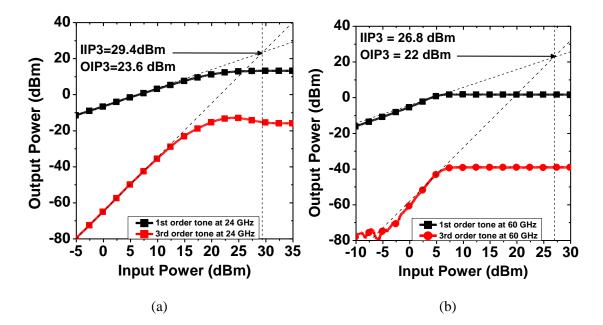

| 2.26 | Measured $P_{1dB}$ of the designed T/R switch with 24-GHz and 60-GHz single-tone input (a) and 24-/60-GHz concurrent dual-tone input (b), and measured $IP_3$ for single-band mode at 24 GHz (c) and 60 GHz (d)                                                                 | 65 |

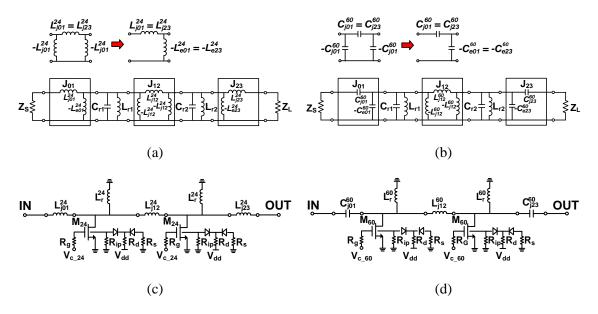

| 2.27 | Schematics of the band-pass filtering SPST switches: (a) 24-GHz band-<br>pass filter and J-inverter implementation, (b) 60-GHz band-pass filter and<br>J-inverter implementation, (c) 24-GHz band-pass filtering SPST switch,<br>and (d) 24-GHz band-pass filtering SPST switch | 67 |

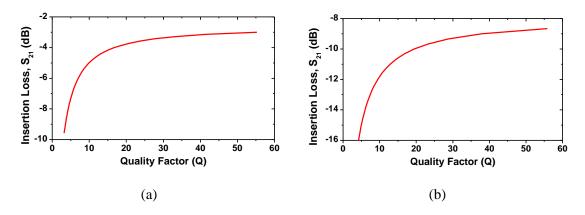

| 2.28 | Simulated insertion losses of the 24- and 60-GHz SPST switches versus Q of the off-state transistors: Transistor $M_{24}$ at 24 GHz (a) and Transistor $M_{60}$ at 60 GHz (b)                                                                                                                                             | 70 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

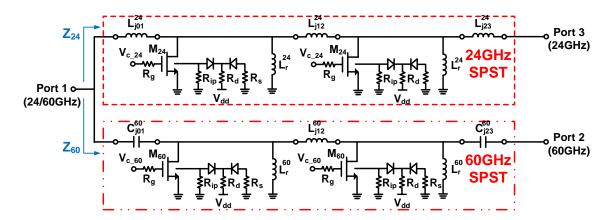

| 2.29 | Schematic of the 24/60-GHz dual-band band-pass filtering SPDT switch                                                                                                                                                                                                                                                      | 71 |

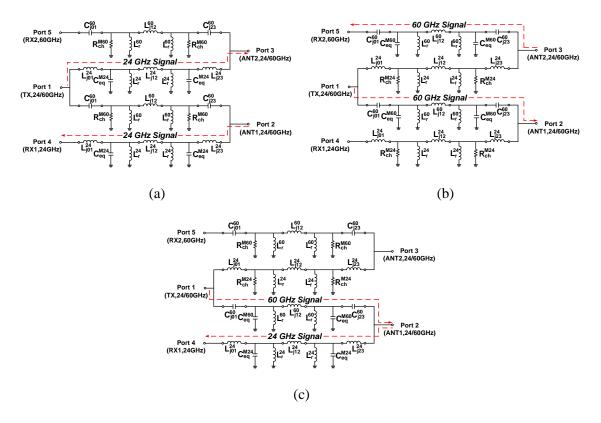

| 2.30 | Operations of the 24/60-GHz dual-band band-pass filtering SPDT switch:<br>(a) 24-GHz single-band operation, (b) 60-GHz single-band operation, and<br>(c) 24/60-GHz concurrent dual-band operation                                                                                                                         | 72 |

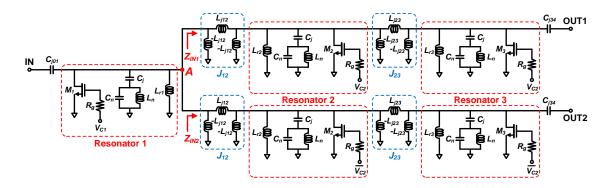

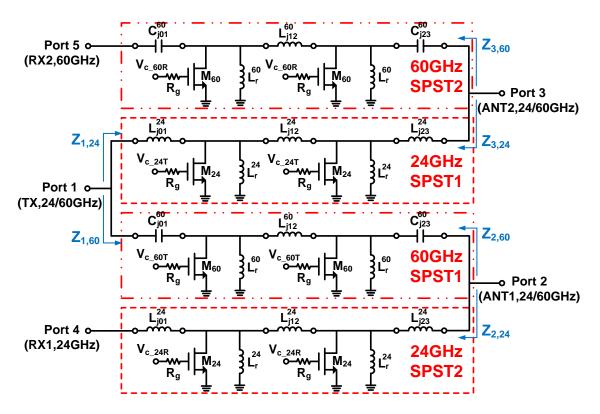

| 2.31 | Schematic of the 24/60-GHz dual-band band-pass filtering T/R switch                                                                                                                                                                                                                                                       | 75 |

| 2.32 | Operations of the 24/60-GHz dual-band band-pass filtering SPDT switch:<br>(a) 24-GHz single-band operation, (b) 60-GHz single-band operation, and<br>(c) 24/60-GHz concurrent dual-band operation                                                                                                                         | 77 |

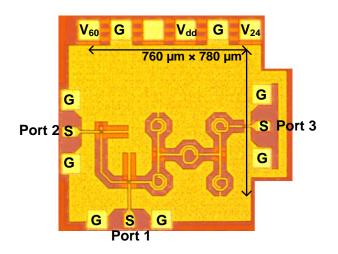

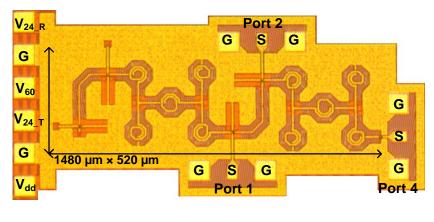

| 2.33 | Microphotographs of the $24/60$ -GHz dual-band band-pass filtering SPDT switch (a) and T/R switch's part (b). The port numbers in (a) and (b) correspond to those in Fig. 2.31, respectively                                                                                                                              | 81 |

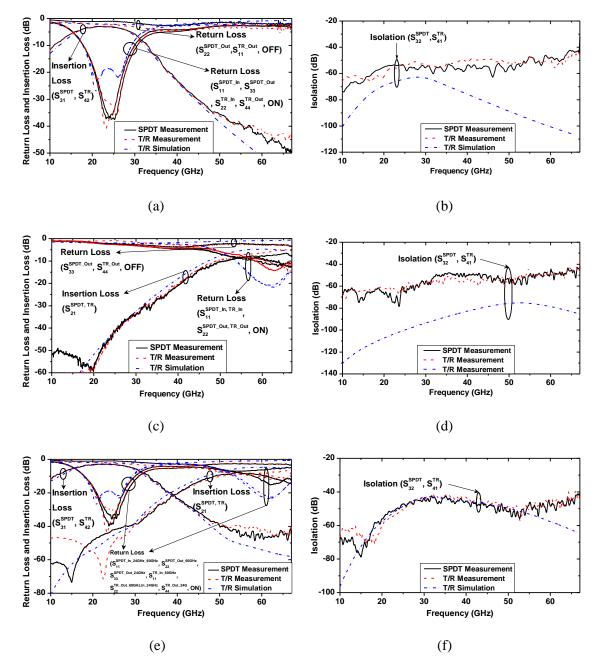

| 2.34 | Measured and simulated results of the 24/60-GHz dual-band band-pass filtering SPDT and T/R switches: (a) and (b) 24-GHz operation, (c) and (d) 60-GHz operation, and (e) and (f) 24/60-GHz concurrent operation                                                                                                           | 82 |

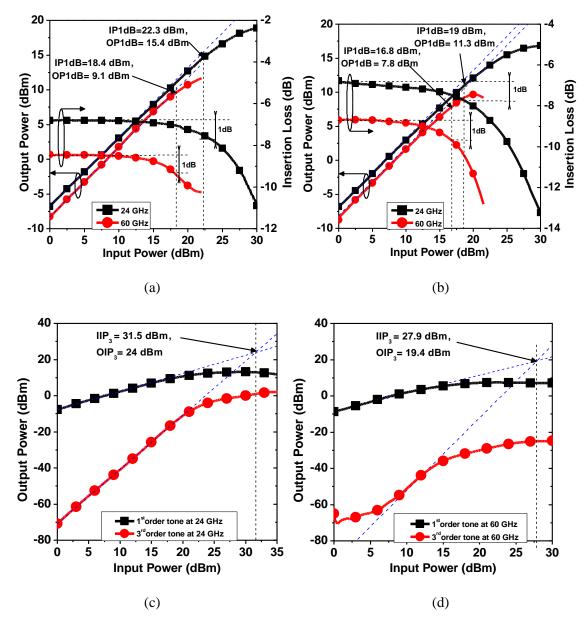

| 2.35 | Measured linearity ( $P_{1dB}$ and $IP_3$ ) of the 24/60-GHz dual-band band-pass filtering SPDT and T/R switches: (a) Measured $P_{1dB}$ at 24 GHz and 60 GHz for single-band operation (b) Measured $P_{1dB}$ at 24 and 60 GHz for concurrent operation (c) Measured $IP_3$ at 24 GHz, and (d) Measured $IP_3$ at 60 GHz | 86 |

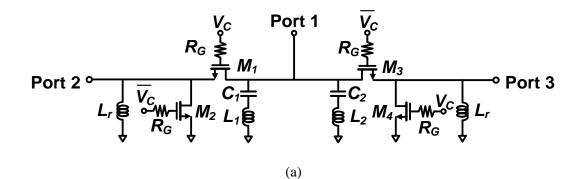

| 2.36 | Concurrent dual-wideband SPDT switch: (a) schematic, (b) equivalent circuit when $V_c = 1.8$ V and $\overline{V_c} = 0$ V, and (c) simplified network between Ports 1 and 2                                                                                                                                               | 88 |

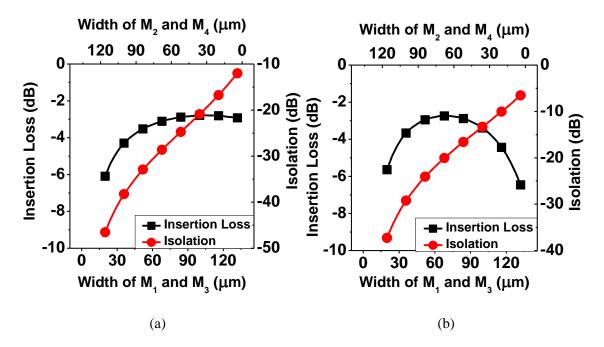

| 2.37 | Simulated insertion loss and isolation with respect to the width of $M_1$ and $M_3$ (or $M_2$ and $M_4$ ) at 24 GHz (a) and 60 GHz (b)                                                                                                                                                                                    | 90 |

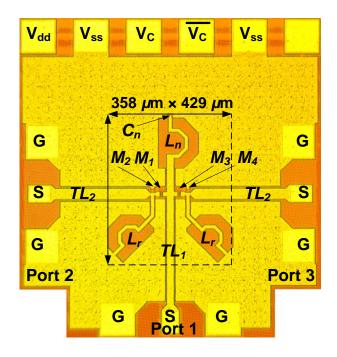

| 2.38 | Microphotograph of the fabricated concurrent dual-wideband SPDT switch. Port numbers correspond the numbers in Fig. 2.36(a)                                                                                                                                                                                               | 91 |

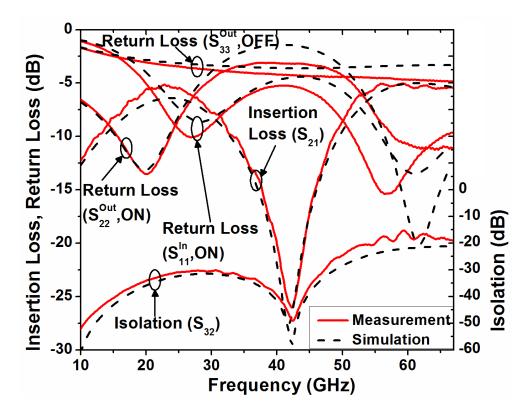

| 2.39 | Measured and post-layout simulated results of the concurrent dual-<br>wideband SPDT switch                                                                                                                                                                                                                                | 92 |

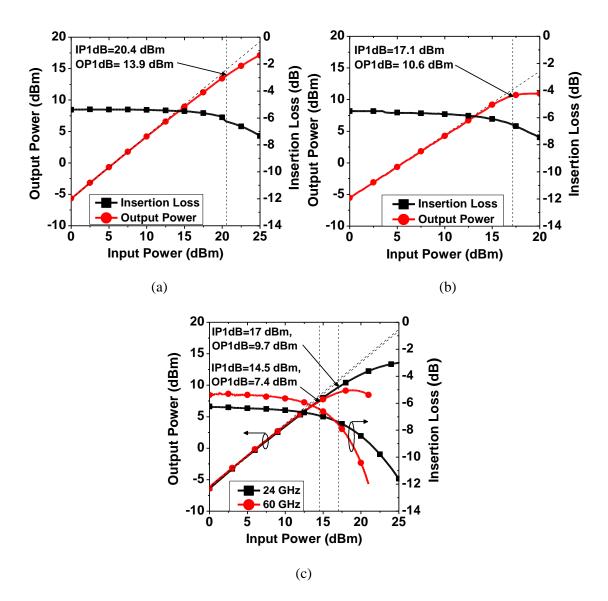

| 2.40 | Measured $P_{1dB}$ of the concurrent dual-wideband SPDT switch with 24-GHz single-tone input (a), 60-GHz single-tone input (b), and 24-/60-GHz                                            |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | concurrent dual-tone input (c)                                                                                                                                                            | 93  |

| 2.41 | Measured $IP_3$ for single-band modes at 24 GHz (a) and 60 GHz (b)                                                                                                                        | 94  |

| 2.42 | Block diagram of the possible dual-band front-end module                                                                                                                                  | 97  |

| 3.1  | Block diagram of the LNA for simple NF calculation                                                                                                                                        | 102 |

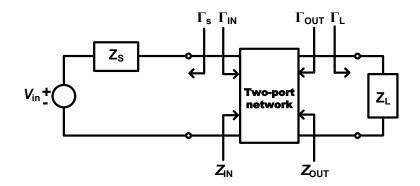

| 3.2  | Two-port network [40]                                                                                                                                                                     | 104 |

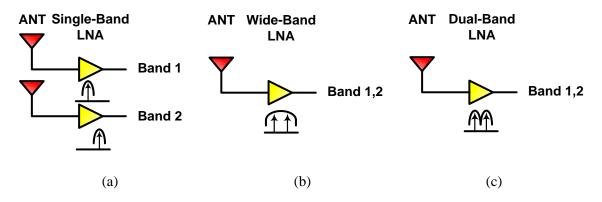

| 3.3  | Dual-band system consisting of: (a) LNAs operating in each band of interest, (b) wideband LNA operating in bands of interest and (c) LNA operating in dual bands of interest concurrently | 105 |

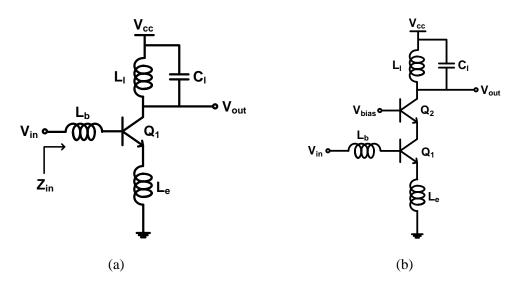

| 3.4  | Commonly used single-band BJT LNAs: (a) common-emitter LNA with<br>an inductive degeneration and (b) cascode LNA with inductive<br>degeneration                                           | 107 |

| 3.5  | Small-signal model of the common-emitter LNA with inductive degeneration                                                                                                                  | 108 |

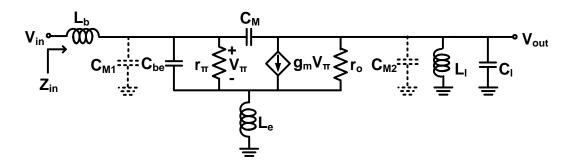

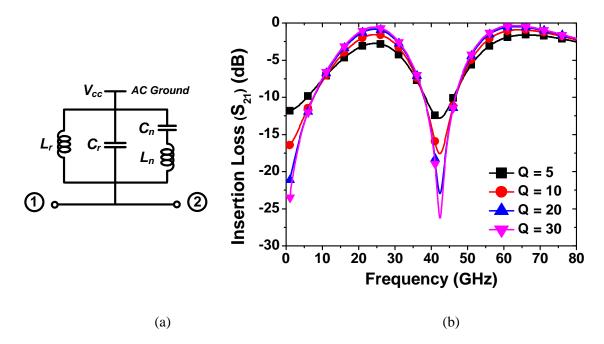

| 3.6  | (a) Conventional dual-band load and (b) simulated insertion loss of the conventional dual-band load as the Q factor of the integrated inductors is varied from 5 to 30                    | 110 |

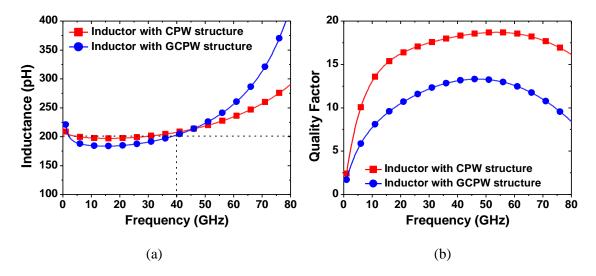

| 3.7  | (a) Simulated inductance of and (b) quality factor comparison of inductors with CPW and GCPW structures                                                                                   | 112 |

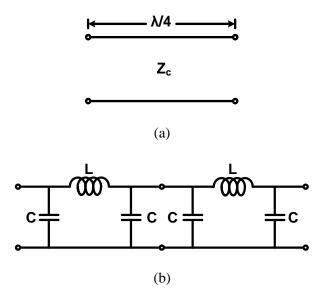

| 3.8  | (a) Quarter-wave length transmission line and (b) 2 <sup>nd</sup> order equivalent LC circuit                                                                                             | 113 |

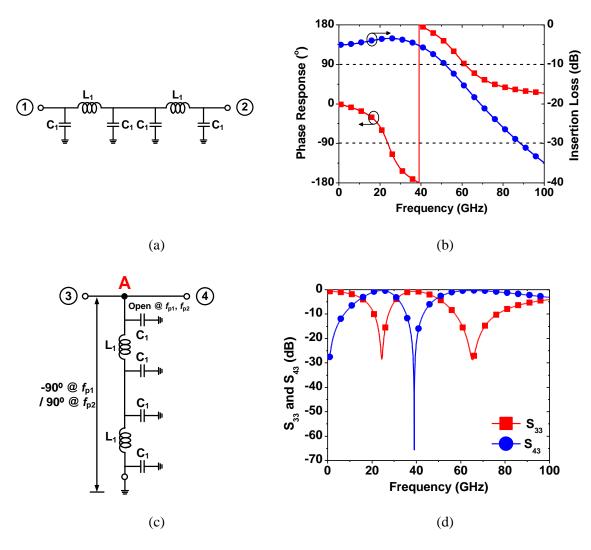

| 3.9  | Quarter-wavelength dual-band LC circuit: (a) series LC circuit, (b) simulated phase response of (a), (c) parallel LC circuit, and (d) simulated return loss and insertion loss of (c)     | 114 |

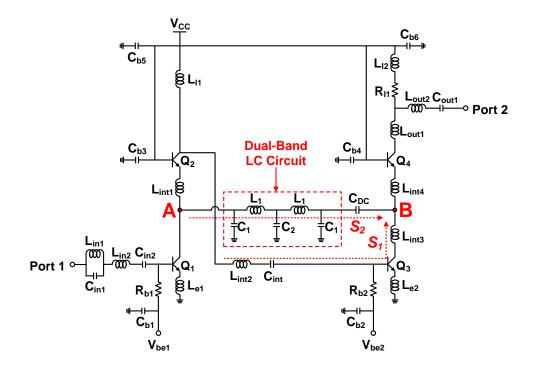

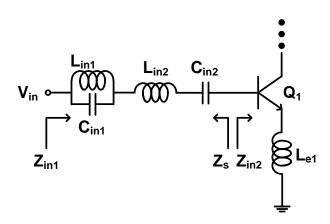

| 3.10 | Schematic of the 24/60-GHz concurrent dual-band LNA                                                                                                                                       | 116 |

| 3.11 | Input matching of the proposed 24/60-GHz concurrent dual-band LNA                                                                                                                         | 117 |

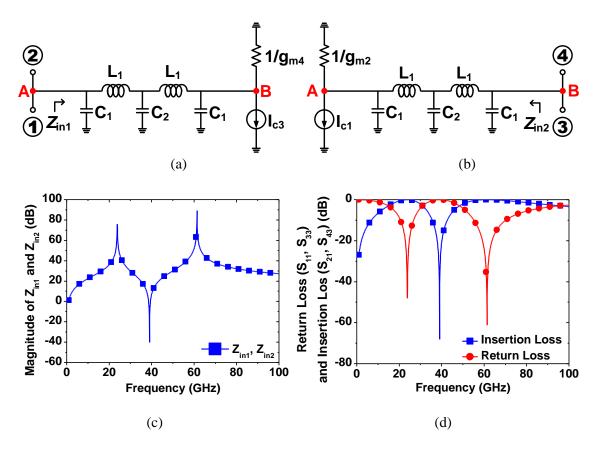

| 3.12 | Equivalent circuit models of the dual-band LC circuit in the LNA (a) looking into node 'B' at node 'A', (b) looking into node 'A' at node 'B', (c) simulated impedance magnitude of $Z_{in1}$ and $Z_{in2}$ in Figs. 3.12(a) and (b), and (d) simulated return losses ( $S_{11}$ and $S_{33}$ ) and insertion losses ( $S_{21}$ and $S_{43}$ ) of Figs. 3.12(a) and (b) | 118 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

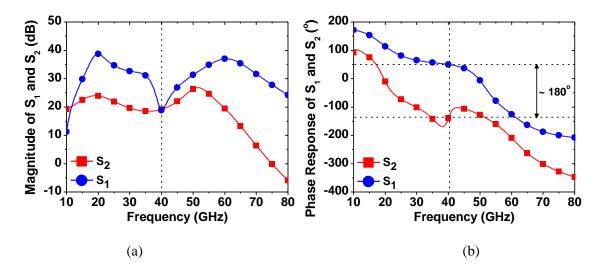

| 3.13 | (a) Simulated magnitude and (b) phase response of the 'S <sub>1</sub> ' and 'S <sub>2</sub> ' in Fig. $3.10$                                                                                                                                                                                                                                                            | 119 |

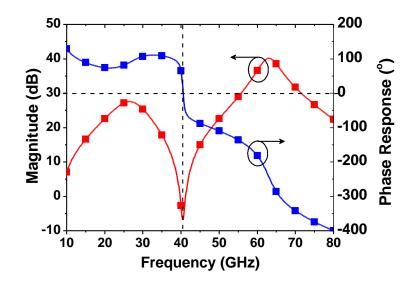

| 3.14 | Simulated magnitude and phase response of the combined signal $(S_1'+S_2')$ at both ends (nodes 'A' and 'B') of the dual-band LC circuit in Fig. 3.10 when the $S_1$ and $S_2$ meet                                                                                                                                                                                     | 120 |

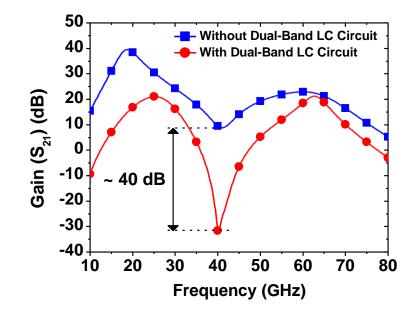

| 3.15 | Simulated gain $(S_{21})$ of the proposed LNA with and without the dual-band LC circuit.                                                                                                                                                                                                                                                                                | 121 |

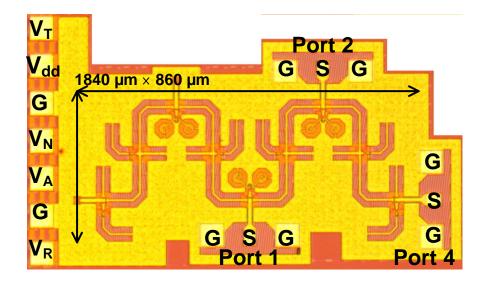

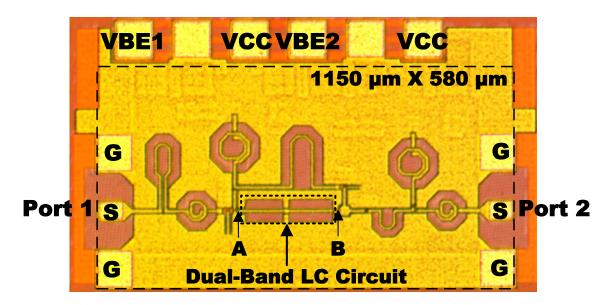

| 3.16 | Microphotograph of the 24/60-GHz dual-band LNA. Locations for node 'A' and 'B' correspond to the those in Fig. 3.10                                                                                                                                                                                                                                                     | 122 |

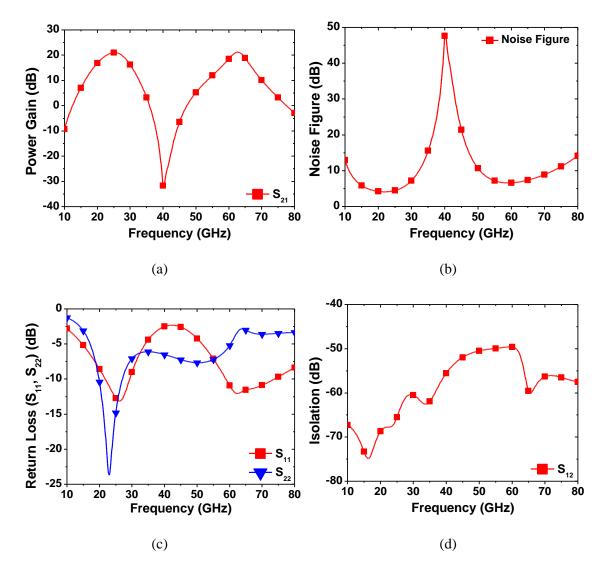

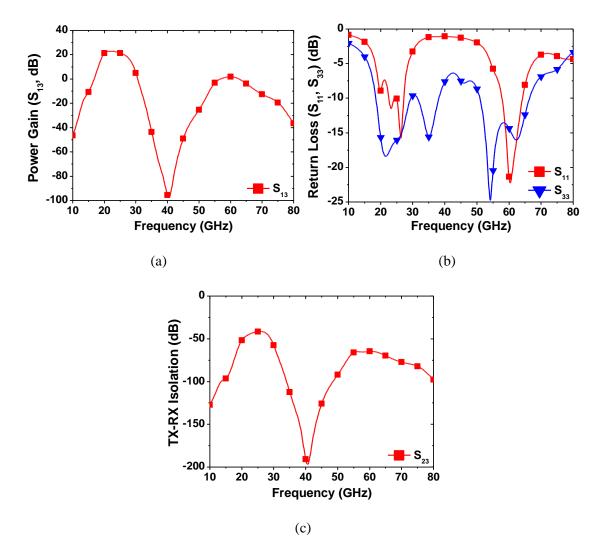

| 3.17 | Simulated results for: (a) gain, (b) NF, (c) $S_{11}$ and $S_{22}$ and (d) isolation ( $S_{12}$ )                                                                                                                                                                                                                                                                       | 123 |

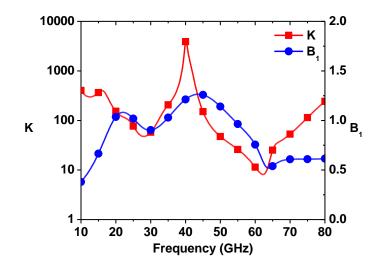

| 3.18 | Simulated stability factors K and B <sub>1</sub>                                                                                                                                                                                                                                                                                                                        | 124 |

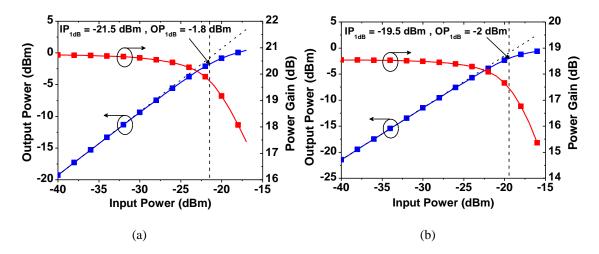

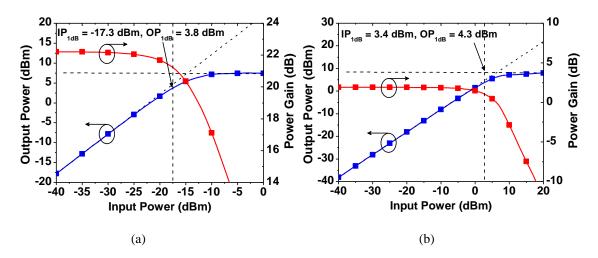

| 3.19 | Simulated P <sub>1dB</sub> s at: (a) 24 GHz and (b) 60 GHz                                                                                                                                                                                                                                                                                                              | 125 |

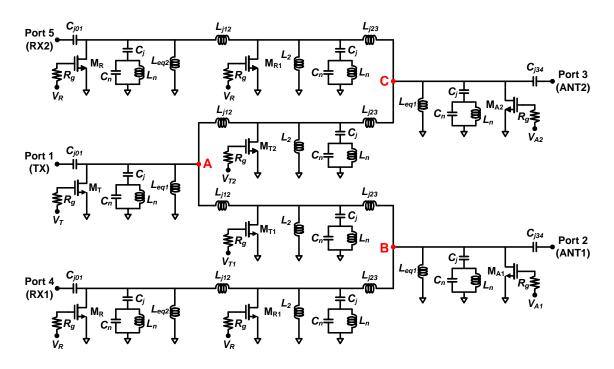

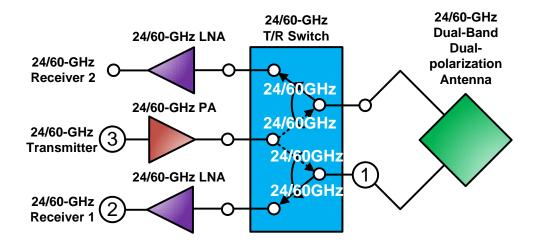

| 4.1  | Block diagram of the 24/60-GHz dual-band front-end module (FEM)                                                                                                                                                                                                                                                                                                         | 128 |

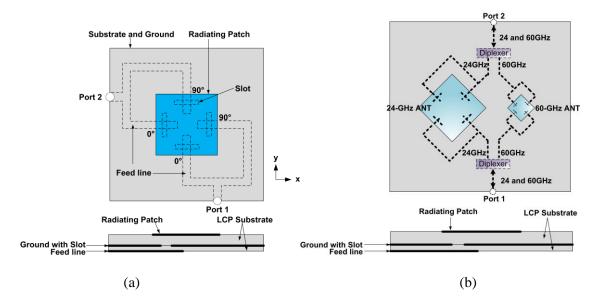

| 4.2  | Conceptual antenna structures of dual-polarized circular antenna for: (a) single-frequency band and (b) dual-frequency bands                                                                                                                                                                                                                                            | 129 |

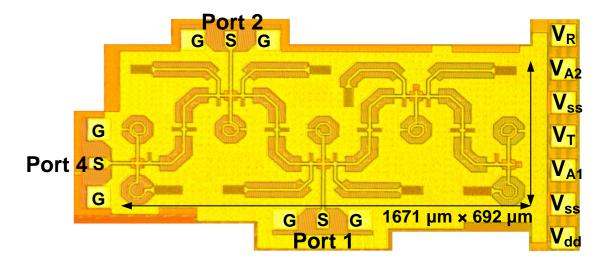

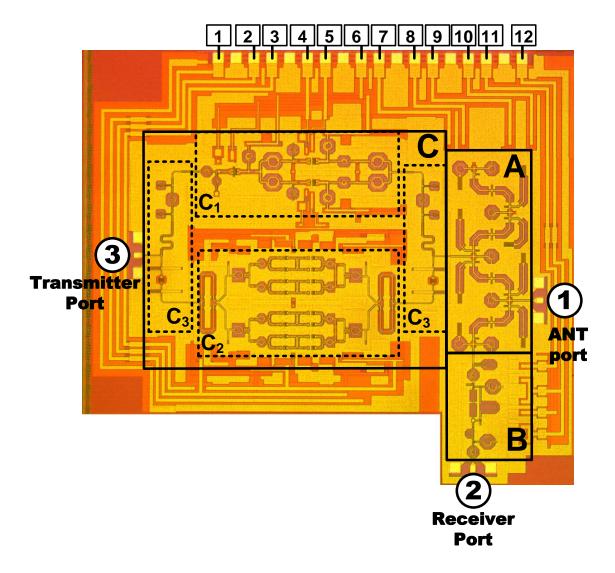

| 4.3  | Microphotograph of the proposed 24/60-GHz concurrent dual-band FEM.<br>Port number correspond to those in Fig. 4.1                                                                                                                                                                                                                                                      | 130 |

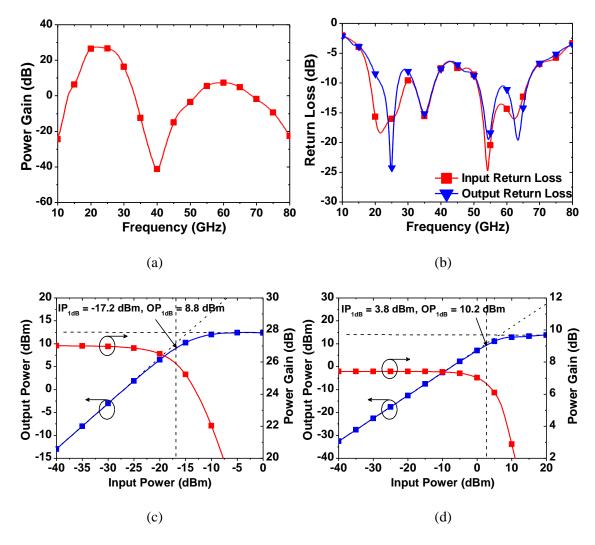

| 4.4  | Simulated results of the 24/60-GHz concurrent dual-band PA [57] for: (a) power gain, (b) input and output return losses, (c) $P_{1dB}$ and $P_{out}$ at 24 GHz, and (d) $P_{1dB}$ and $P_{out}$ at 60 GHz                                                                                                                                                               | 131 |

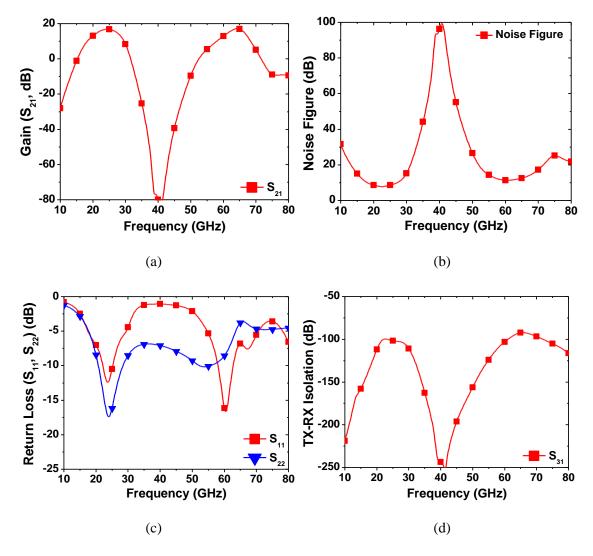

| 4.5  | Simulated results of the FEM in receiving operation for: (a) gain $(S_{32})$ , (b) NF, (c) $S_{11}$ and $S_{22}$ and (d) TX–RX isolation $(S_{13})$ . Port numbers correspond to those in Fig. 4.3                                                                                                                                                                      | 133 |

| 4.6  | Simulated input and output P <sub>1dB</sub> s at: (a) 24 GHz and (b) 60 GHz                                                                                                                                                                                                                                                                                             | 134 |

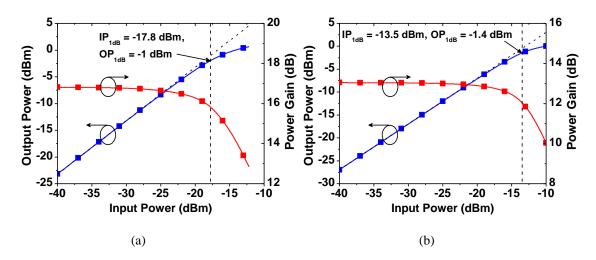

| 4.7 | Simulated results of the FEM in transmitting operation for: (a) power gain $(S_{13})$ , (b) input and output return losses, and (c) TX–RX isolation $(S_{23})$ | 135 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.8 | Simulated input and output $P_{1dB}s$ and $P_{out}$ of the FEM in the transmitting operation at: (a) 24 GHz and (b) 60 GHz                                     | 136 |

# LIST OF TABLES

| TABLE |                                                                                                         | Page |

|-------|---------------------------------------------------------------------------------------------------------|------|

| 1.1   | 24, 60 and 77 GHz Frequency Characteristics                                                             | 2    |

| 1.2   | Characteristic Summary of Dual-Frequency Combinations                                                   | 5    |

| 1.3   | Simulation Setup Parameters                                                                             | 9    |

| 2.1   | Dual-Band Band-Pass Filtering T/R Switch's Parameters                                                   | 46   |

| 2.2   | Dual-Band Band-Pass Filtering T/R Switch's Parameters                                                   | 60   |

| 2.3   | Dual-Band Band-Pass Filtering T/R Switch's Parameters                                                   | 75   |

| 2.4   | Dual-Band Band-Pass Filtering SPDT Switch's Parameters                                                  | 91   |

| 2.5   | Performance Summary of the Developed Dual-Band SPDT and T/R<br>Switches                                 | 95   |

| 2.6   | Performance Summary of the Existing Single-Band 24-, 40- and 60-GHz, and Dual-Band 24.5/35 GHz Switches | 96   |

| 3.1   | 24/60-GHz Concurrent Dual-Band LNA's Parameters Values                                                  | 116  |

| 3.2   | Performance Summary of the Developed Concurrent Dual-Band LNA and Existing Concurrent Dual-Band LNAs    | 126  |

| 4.1   | DC Bias Setup for Receiving and Transmitting Operations                                                 | 132  |

| 4.2   | Simulated Performance Summary of the 24/60-GHz Concurrent Dual-<br>Band Front-End Module (FEM)          | 137  |

### **CHAPTER I**

### INTRODUCTION

### **1.1 Introduction and Background**

The rapid emergence of numerous applications of radar, sensing, and wireless communications in many areas such as public communications, item management, transportation safety, health care, military and etc. has resulted in a substantial movement toward novel circuit topologies and techniques with improved performances, low cost and high level of integrations using CMOS and BiCMOS technologies. Meanwhile, increasing interests in larger bandwidths lead integrated circuits to move toward higher frequencies [1]. Also, there are huge amounts of applications in low frequencies, and most of the frequencies have been already allocated and used. Furthermore, the needs of 5-G wireless frequency bands have been looming large. Therefore, applications at higher frequencies such as millimeter-wave (mmW) frequencies have more interests in researches. Industrial, Scientific and Medical (ISM) bands such as those around 24-GHz band (22-29 GHz), 60-GHz band (57-64 GHz) and 77-GHz bans (77-81 GHz) at mmW frequencies have been allocated as unlicensed frequency bands. Table 1.1 shows advantages, disadvantages, and possible applications at the frequencies. Increased bandwidth leads to high data rate communication, which is calculated as [2]

$$C = B * \log_2\left(1 + \frac{S}{N}\right) \text{ [bps]}$$

(1.1)

| Operating<br>Frequency | Advantages                  | Disadvantages              | Possible Applications       |

|------------------------|-----------------------------|----------------------------|-----------------------------|

| 24 GHz<br>(22–29 GHz)  | -Low attenuation in air     | -Less possible antenna on- | -Vehicle anti-collision     |

|                        | -High isolation between     | chip                       | -Vehicle identification     |

|                        | floors                      |                            | -Parking management         |

|                        | -Higher data rate           |                            | -Electronic toll collection |

|                        | -Long range possible        |                            |                             |

| 60 GHz                 | -High data rate             | -High attenuation in air   | -Indoor application         |

| (57–64 GHz)            | -Possible antenna on-chip   | -Only indoor application   | -Short range                |

|                        | -Spatial isolation          | -Interference with home    | communication               |

|                        | -Higher implicit security   | networking system          |                             |

|                        |                             | -High power consumption    |                             |

| 77 GHz<br>(77–81 GHz)  | -High directivity possible  | -High power consumption    | -Vehicle anti-collision     |

|                        | -Possible antenna on-chip   |                            | -Vehicle identification     |

|                        | -Long detection range       |                            |                             |

|                        | -can be used with car radar |                            |                             |

|                        | -Less interference          |                            |                             |

Table 1.124, 60 and 77 GHz Frequency Characteristics

, where C is maximum capacity of the channel, B is bandwidth of the channel, S/N is signal-to-noise ratio (SNR).

Also, the shorten wavelength at mmW frequencies can lead to the miniaturization of the entire communication system. Especially, for antenna design, not only an on-chip antenna but also an array antenna can be implemented, and this feature can be an important advantage to implement communication systems at mmW frequencies beyond the systems implemented at low frequencies. As shown in Table 1.1, these inherent characteristics of the mmW frequencies can be employed in a variety of applications, e. g. short- and long-distance communication systems, vehicle radar system

Fig. 1.1. Vehicle radar system.

Fig. 1.2. Air attenuation at microwave and millimeter-wave frequencies.

(also called Vehicle anti-collision system), and 60-GHz indoor network system. Fig. 1.1 shows the vehicle radar system and the functions of operating frequencies. In the system, 24 and 77-GHz frequencies are utilized as short- and long-distance radar

Fig. 1.3. Applications for 60-GHz communication systems.

communications, respectively, and for anti-collision systems. The 60 GHz band is a very interesting frequency band that has high air attenuations as shown in Fig. 1.2. Due to this fact, it is mainly used as short-distance or indoor communications and security solutions as shown in Fig. 1.3. Since the bandwidth (BW) of the 60-GHz communication band is 7 GHz (57–64 GHz), the data rate reaches up to several Gbps. It means that high definition uncompressed streaming video, interactive gaming, digital photography, digital home movies and data and file transfer are possible, which can lead to a connector free platform and a muti-gigbit cloud connectivity.

Fig. 1.4. Block diagram of a multi-band system: (a) One multi-band system and (b) multiple and parallel system operating at different operating frequency bands.

| Frequency<br>Combination | Advantages                                                                                                               | Disadvantages                                                                                                                                                                                           |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24 / 60 GHz              | <ul> <li>Long and short range communication</li> <li>Direct conversion system</li> <li>(Simpler architecture)</li> </ul> | - Difficult on-chip 24-GHz Antenna                                                                                                                                                                      |

| 24 / 77 GHz              | - Long range communication                                                                                               | <ul> <li>Already used for vehicle anti-collision<br/>(co-channel interference)</li> <li>Heterodyne structure (complex<br/>structure)</li> <li>Difficult on-chip 24-GHz Antenna</li> </ul>               |

| 60 / 77 GHz              | - Long and short range communication                                                                                     | <ul> <li>Already used for vehicle anti-collision<br/>(co-channel interference)</li> <li>Heterodyne structure (complex<br/>structure)</li> <li>Very high-Q BPF(Switch) required at<br/>77 GHz</li> </ul> |

Table 1.2

Characteristic Summary of Dual-Frequency Combinations

Also, the huge 7-GHz BW is used as a high-data rate wireless connectivity such

as IEEE 801.11ad for the next-generation WiFi (also call WiGig) and IEEE 802.15.3c standards for Wireless Personal Area Network (WPAN) [3].

Multi-band RF systems in Fig. 1.4(a) have provided numerous advantages and have more capabilities as compared to single-band counterparts in Fig. 1.4(b). The ability of operating multiple bands increases the diversity of RF systems for sensing and communication functions at multiple frequencies. Moreover, achieving concurrent functions over multiband enables a single RF system to be used at multiband simultaneously – avoiding the need of physically combining separate RF systems, each working in an individual band, together, which is difficult (and expensive) to realize in practice – particularly when many bands are involved. This leads to improvement in size, cost and power consumption. Table 1.2 shows advantages, disadvantages and possible applications for possible dual-frequency combinations for dual-band systems. Among the frequency combinations, 24- and 60-GHz frequency combination has been selected due to their simplicity and versatility for this research.

In this dissertation, a 24/60-GHz concurrent dual-band BiCMOS front-end module applicable to RFID, phased array and communication systems has been proposed. Especially, the designs of a switch, a LNA and a front-end module, which consists of switch, LNA and PA, will be described in the following sections.

Fig. 1.5. Block diagram of the proposed 24/60-GHz dual-band RFID reader system.

### **1.2 System Description**

### 1.2.1 A 24/60-GHz Dual-Band Dual-Mode RFID Reader System

A RFID system fundamentally consists of a RFID reader and a tag. A RFID reader transmits signals to a tag, then, the tag back-scatters its information to the reader. According to with or without battery in the tag, active and passive RFIDs are classified, respectively [4]. In this chapter, the RFID system using dual circular polarization, e. g. left- and right-handed circular polarizations, and dual modes, e. g. active and passive modes, has been proposed. Operating frequencies are 24 and 60 GHz that are employed for active and passive RFID systems, respectively.

Fig. 1.5 shows the block diagram of the proposed 24/60-GHz dual-band RFID reader system with a shared two-port antenna for receiving and transmitting operations. While the 24-GHz active RFID system works in separate transmitting (TX) and

receiving (RX) operations, the 60-GHz passive RFID system operates in simultaneous TX and RX operations. In passive RFID system, circulator, in which a signal entering any port is transmitted to the next port in rotation, is used as a front-end component and the circulator should have a low insertion loss and noise figure, and high linearity and isolation. Even though on-chip circulators show good isolation, they show poor linearity and noise figure [5], [6] and are not desirable for fully integration. Furthermore, signal leaked from TX port to RX port can be problematic in passive RFID systems.

To solve this problem, a TX leakage cancellation (TLC) technique has been proposed in the system. The TLC system consists of 24/60-GHz coupler (①), 24/60-GHz T/R switch (2), 60-GHz phase shifter (3), 60-GHz attenuator (4) and 60-GHz combiner (③) as shown in Fig. 1.5. The T/R Switch consists of two 24-GHz and two 60-GHz SPST switches, which are placed alternately, and has five ports. The T/R switch will be described in Sec. 2.4. In the 60-GHz passive RFID operation, transmitted signals from PA output are classified as two signals: one is a coupled signal (signal 1 in Fig. 1.5) by a coupler (①) and another is a thru signal (*signal 2* in Fig. 1.5) via the coupler (①), respectively. Although the *signal 2* can be leaked from TX port to 60-GHz RX port in the T/R switch (2), the signal is attenuated due to high isolation by off-state 24-GHz SPST switch between TX port and 60-GHz RX port. Since, however, some of the signal 2 can also be leaked into the receiver through antenna's another port without radiating at antenna and the signals are amplified by LNA, which can be harmful to the receiver, and

Fig. 1.6. ADS Simulation setup to verify the TX leakage cancellation technique.

Table 1.3 Simulation Setup Parameters

| TX output power (PA output)       | 10 dBm                   |  |

|-----------------------------------|--------------------------|--|

| RX input power (T/R switch input) | -30 dBm                  |  |

| TX, RX carrier frequency          | 60 GHz                   |  |

| Modulation                        | ASK, modulation index: 1 |  |

the hence leaked signals should be canceled out. To cancel out the leaked signals, the *signal 1* is directed to go through the 60-GHz phase shifter (③) and attenuator (④), and meet the *signal 2*, which is leaked from antenna and amplified by LNA, at node 'A' in Fig. 1.5. Eventually, the two signals will be canceled out due to their same magnitude and 180-deg out of phase.

To evaluate the performance of the TLC technique, Fig. 1.6 shows the ADS [7] simulation setup consisting of antenna, T/R switch, coupler, LNA, phase shifter and attenuator with simulation setup parameters listed in Table 1.3. Fig. 1.7 shows the simulated result of the signals at input (*Combiner\_IN1* and *Combiner\_IN2*) and output (*Combiner\_OUT* at node 'A') of 60-GHz combiner (⑤).

Fig. 1.7. Simulated results of the signals' cancellation at 60-GHz Combiner's output.

Two input signals have the same magnitude and 180-deg out of phase, and then the signals are canceled out at the output. The cancellation ratio is calculated as

$$Cancellation\_ratio = -20\log_{10}\left(\frac{Combiner\_OUT}{Combiner\_IN2}\right)$$

(1.2)

The simulated cancellation ratio is around 40 dB.

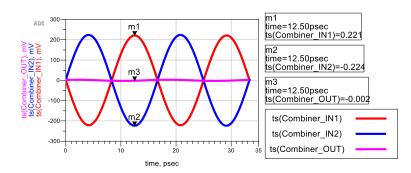

Fig. 1.8 shows the simulated results of an ASK modulation index in Fig. 1.8(a) defined as

$$Modulation\_index = \frac{S_2}{S_1}$$

(1.3)

Figs. 1.8(a), (b) and (c) show the modulated incoming RF signal at the antenna and the signals at the combiner output (node 'A' in Fig. 1.5) with and without TLC technique, respectively.

With TLC technique, while the modulation index is kept as around 1, the modulation index deteriorates due to leaked TX signal without TLC technique.

Fig. 1.8. Simulated result comparison for modulation index at the combiner's output: (a) ASK modulation RX input signal, (b) output signal at the combiner's output with TX leakage cancellation block, and (c) output signal at the combiner's output without TX leakage cancellation block.

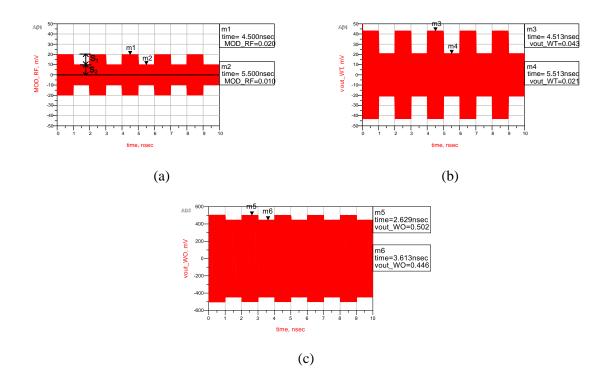

Fig. 1.9. Simulation results comparison for signal power and modulation index at combiner's output: (a) output powers at combiner's output and (b) modulation index at combiner's output.

Fig. 1.9 shows the signal power level at combiner output (node 'A' in Fig. 1.5)

with respect to the transmitted power at PA output, which will be potentially expected as the signal power leaked from the antenna, with and without TLC technique. With TLC technique, the modulation index and the signal power are kept stable regardless of transmitted power at the PA output. However, without TLC technique, the signal power leaked from the antenna increases, and the modulation index significantly decreases as the transmitted power increases. Therefore, the TLC technique prevents TX leakage signals from coming to the receiver effectively.

#### 1.2.2 A 24/60-GHz Concurrent Dual-Band Phased Array System

Phased array system has some advantages beyond single antenna systems. Representative features are to improve the signal to interference plus noise ratio (SINR), to increase output power by increased antenna gain, and to implement beamforming [8], thus the phased array system is often employed in a radar system. The total transmitted output power is calculated as equivalent isotopically radiated power (EIRP) as

$$EIRP[dB] = P_t - L + G, \ G_{array}[dB] \cong G_s + 10\log n \tag{1.4}$$

, where  $P_t$  is the transmitted power at PA output, L is the loss by antenna mismatch, and G is the antenna's gain,  $G_{array}$  is the array antenna's gain consisting of n-single antenna, n is the number of single antennas and  $G_s$  is the single antenna's gain.

In the array system, equation (1.4) says that the gain of total array antenna increases compared to that of single antenna, and total transmitted output power is higher than that of single-antenna system [9].

In the phased array system, beam scanning angle (or main lobe angle) can be determined according to the phase difference by a phase shifter and an array antenna structure. For instance, the scanning angle of a sixteen-element linear array in the same distance can be calculated as [9]

$$\theta = \sin^{-1} \left( \frac{\psi}{2\pi \left( \frac{d}{\lambda} \right)} \right) \tag{1.5}$$

, where  $\theta$  is the scanning angle,  $\psi$  is the phase shift across the array, d is the distance between each antenna. Since the main lobe of the radiation pattern is generated at the angle ( $\theta$ ), directive communication at  $\theta$  is possible.

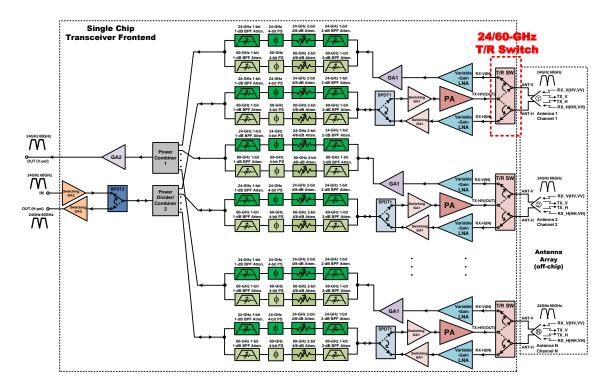

Fig. 1.10 shows a block diagram of the proposed 24/60-GHz concurrent dualband transceiver for a phased array system. The system consists of sixteen-identical front-end modules, which constitute an antenna, a T/R switch, a LNA, a PA, an attenuator and a phase shifter. Also, the system employs a dual polarization such as a vertical and horizontal polarization, and it can lead to improve object detection accuracy. In this dissertation, the 24/60-GHz concurrent dual-band T/R switch, which is shown inside the dashed box in Fig. 1.10, has been designed, fabricated and measured. It will be described in Sec. 2. 3.

Fig. 1.10. Block diagram of the proposed 24/60-GHz concurrent dual-band transceiver for phased array system.

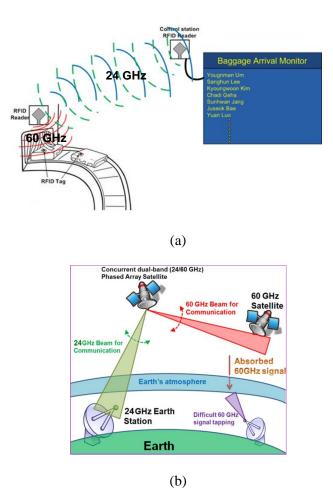

## **1.2.3** Possible Applications

Using the dual frequencies, some applications can be implemented as shown in Fig. 1.11. Fig. 1.11(a) shows a RFID baggage tracking system employing 24-GHz longand 60-GHz short-distance communication characteristics. Since there are a lot of similar-sized, -colored and -shaped bags on the baggage claim conveyor belt in airports, it is difficult to find one's own bag easily. Therefore, the dual-band RFID system can be applicable to this situation. Baggage tags (having RFID tags) communicate with a RFID reader installed on the baggage conveyor via 60 GHz, and the RFID reader communicates with another RFID reader connected to a baggage arrival monitor via 24

Fig. 1.11. Possible applications: (a) 24/60-GHz RFID baggage tracking system and (b) 24/60-GHz satellite communication system.

GHz to show the passengers whose baggage arrives. Fig. 1.11(b) shows the radar application for a satellite communication system, and it utilizes air attenuation rate's difference at 24 and 60 GHz. Because the 60-GHz signal is easily absorbed by the earth's air, 60 GHz is only used for satellites' inter-communication. On the other hand, satellites communicate with the radar station on the earth via 24 GHz.

## **1.3 Dissertation Organization**

This dissertation presents several new circuits and techniques to improve performances of some essential CMOS and BiCMOS RFIC components operating at millimeter-wave frequencies (K, Ka and V bands), and the integration of concurrent dual-band front-end module operating at K and V bands applicable to phase array and RFID communication systems.

Chapter II begins with the fundamentals of RF switches, and then introduces four different dual-band switches with band-pass filtering function. Their design, analysis and measurement results are presented. In Chapter III, a concurrent dual-band LNA is described. To obtain dual-band characteristic, dual-band quarter-wavelength LC network has been employed. Chapter IV presents the concurrent dual-band front-end module consisting of dual-band T/R switch described in Chapter II, dual-band LNA proposed in Chapter III and dual-band PA contributed by a lab colleague. Finally, in Chapter V, the conclusion and summary of this dissertation is provided.

#### **CHAPTER II**

### **CMOS DUAL-BAND BAND-PASS FILTERING SWITCH\***

### 2.1 Background and Motivation

A RF switch is an important component in RF/millimeter-wave communication and radar systems. Moreover, it is important due to the switch functions as a circuit that selects one among several branches, e. g. transmitting and receiving branches. The RF switch can be generally employed in Time Division Duplexing (TDD) systems consisting of transmitter, receiver, switch, and one shared antenna [10]. In Frequency Division Duplexing (FDD), the switch can be implemented with branches operating at different frequency bands.

For the switch design, traditionally, Gallium arsenide (GaAs) switches have been used because of their low on-resistance and off-capacitance, and high linearity at high frequencies [11]. Since Silicon-On-Insulator (SOI) technology reduces capacitive coupling with substrate due to a buried oxide layer and is implemented on high resistivity substrate, the switches on SOI have shown low-insertion loss and highisolation characteristics [12]–[15]. However, due to the improvement of CMOS process, the performance of CMOS switches has been improved. As a result, CMOS switches became an alternative solution that can replace expensive GaAs and SOI switches in low cost, low power applications [11].

<sup>\*</sup> Copyright 2017 Reproduced by permission of the Institution of Engineering & Technology, from Um Y, Nguyen C. High-Isolation Multi-Port Millimetre-Wave CMOS Dual-Band T/R Switch with Integrated Band-Pass Filtering Function. IET Microwaves, Antennas & Propagation. 2017 Jan 29; 11(2):253-9, and Y. Um and C. Nguyen, "A Millimeter-Wave CMOS Dual-Bandpass T/R Switch with Dual-Band LC Network," *IEEE Microw. Wireless Compon. Lett.*, in progress

Transmit/receive (T/R) and single-pole double-throw (SPDT) switches are often being used in RF transceivers. For receiving operation, RF signals pass through (on-chip or off-chip) band-pass filter (BPF), switch and LNA to receiver. For transmitting operation, the RF signals amplified by PA pass through the switch and BPF. In RF transceivers, external band-pass filters are normally used together with T/R switches to reduce undesired out-of-band signals. While these separate band-pass filters can be implemented as off- or on-chip components, they tend to increase the size and cost of the overall system. A more effective approach is to integrate the band-pass filter function with switches to make a dual-function (switching and filtering) simultaneously.

In this chapter, new 0.18- $\mu$ m CMOS dual-band band-pass filter SPDT and T/R switches are proposed. They can operate in two different frequency bands centered at around 40 and 60 GHz, as well as 24 and 60 GHz.

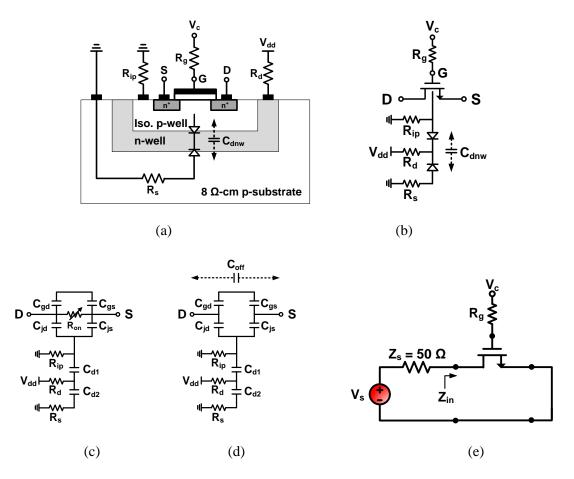

### 2.1.1 MOSFET with Deep N-Well

Body-floating technique and deep *n*-well transistors are used to prevent RF signals from the *p*-substrate leaking into the bulks of the transistors. Hence, they can isolate the bulks of the transistors from the *p*-substrate and, in turn, increasing the isolation of the transistors [16], [17]. Fig. 2.1 shows a cross sectional view and equivalent circuits of nMOS transistors with deep *n*-well (DNW). In order to maximize the isolation, the isolated *p*-well and DNW are biased at 0 V and 1.8 V (V<sub>dd</sub>) through large resistors,  $R_{ip}$  (10  $k\Omega$ ) and  $R_d$  (20  $k\Omega$ ), respectively. If the high voltage (higher than threshold voltage, Vth) is applied to the gate, the transistor connects (ON-state) the

Fig. 2.1. Cross sectional view of a deep n-well transistor: (a) schematic (b) equivalent model when  $V_c = 1.8$  (c) and 0 V (d), and (e) simulation set-up to obtain  $R_{on}$  and  $C_{off}$ .

source and the drain together. On the other hand, the transistors disconnect (OFF-state) the source and the drain if low voltage is applied to the gate [18]. Fig. 2.1(c) and (d) show the on- and off-state nMOS transistors with DNW that are approximately equivalent to the on-resistor ( $R_{on}$ ) and equivalent capacitor ( $C_{eq}$ ), respectively. The  $R_{on}$  and  $C_{eq}$  can be calculated as

$$R_{on} = \frac{1}{\mu_n C_{ox} \frac{W}{L} \left( V_{GS} - V_{th} \right)}$$

(2.1)

, where  $\mu_n$  is the majority-carrier mobility of the nMOS transistor with DNW,  $C_{ox}$  is the gate oxide capacitance, W is the width of the transistor, L is the length of the transistor,  $V_{GS}$  is a voltage between the gate and source,  $V_{th}$  is threshold voltage [18].

The equivalent capacitance  $C_{eq}$  of the on- and off-state nMOS transistor with DNW consists of the gate-source ( $C_{gs}$ ), gate-drain ( $C_{gd}$ ), junction ( $C_{js}$  and  $C_{jd}$ ), and deep n-well ( $C_{dnw}$  consisting of  $C_{d1}$  and  $C_{d2}$ ) capacitances [19].

Fig. 2.1(e) also shows the schemetic to simulate  $R_{on}$  and  $C_{off}$  of on- and off-state nMOS transistors with DNW, where they can be determined as

$$R_{on} = real(Z_{in_on}) \text{ and } C_{off} = \frac{1}{2\pi f * imag(Z_{in_off})}$$

(2.2)

, where  $Z_{in_on}$  and  $Z_{in_off}$  are the input impedances when the nMOS transistor with DNW is on and off state, respectively.

The nMOS transistor with DNW is biased in off-state and the quality (Q) factor of their equivalent off-capacitor  $C_{off}$  affects the switch performance. Fig. 2.2 shows the simulated Q-factor of the off-state transistors (M<sub>24</sub> and M<sub>60</sub>) with and without DNW using the simulation setup in Fig. 2.1(e) and obtained as

$$Q = \frac{1}{2\pi f * real(Z_{in_off}) * C_{off}}$$

(2.3)

, where  $Z_{in_off}$  and  $C_{off}$  are again the input impedance and off-capacitance when nMOS transistor with/without DNW is off state, respectively.

Widths/lengths of the  $M_{24}$  and  $M_{60}$  are 420  $\mu$ m/0.18  $\mu$ m and 240  $\mu$ m/0.18  $\mu$ m, respectively. The simulated Q-factors are 41.5/4.5 and 27.8/5.5 at 24 and 60 GHz

Fig. 2.2. Simulated Q for off-state nMOS transistors: (a)  $M_{24}$  and (b)  $M_{60}$  with/without DNW.

with/without DNW, respectively. As shown in Fig. 2.2, it is verified that the Q-factor of the off-state transistors with DNW is much higher than that of off-state transistor without DNW, and nMOS transistor with DNW structure can be used to achieve the low insertion loss for the switch design.

# 2.1.2 Trade-Off for Typical Switch Topology

Performances of the switch can be evaluated as its insertion loss (IL), isolation (ISO), figure of merit (FOM) such as  $R_{on}*C_{off}$ ,  $P_{1dB}$  and  $IP_3$ . They will be described in the following sub-sections.

Fig. 2.3. RF switch model in a 50- $\Omega$  network.

Fig. 2.4. Typical RF receiver chain for total noise figure (NF) calculation.

# **Insertion Loss**

Insertion loss (IL) is the attenuation between input and output ports of the on-state switch. Since the  $R_{on}$  of the switch is a loss factor of the switch, the IL of the switch in Fig. 2.3 can be calculated as

$$IL = -20\log_{10} \left| \frac{Z_L + Z_s}{Z_L + Z_s + R_{on}} \right| \text{ [dB]}$$

(2.4)

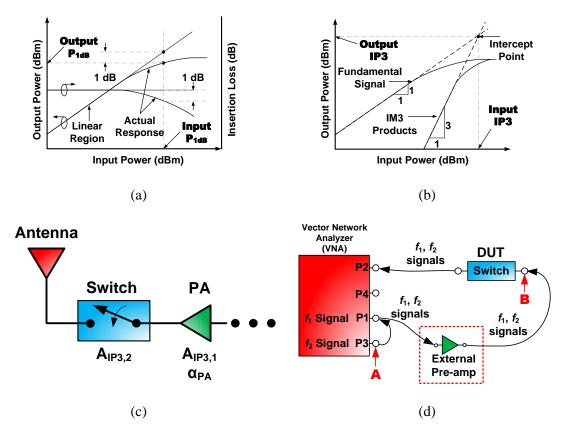

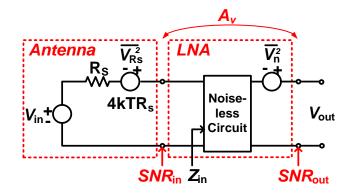

From (2.4), in order to get lower IL,  $R_{on}$  should be as low as possible. Fig. 2.4 shows a typical RF receiver chain, and equation (2.5) is the total noise figure (NF) calculation of the receiver chain. The IL and NF of the switch and LNA directly effects on the total NF of the receiver according to

$$NF_{total} = L_{sw} + \frac{N_{LNA} - 1}{L_{sw}^{-1}} + \dots = L_{sw} \cdot N_{LNA} + \dots$$

(2.5)

Therefore, to reduce the total NF of the receiver, the IL of the switch should be as low as possible or the switch should be located after a LNA amplifier with a high gain.

# Isolation

Isolation (ISO) is defined as the attenuation not only between the input and output in the off-state SPST switch, but also between the on- and off-state outputs in a SPDT or a multi-port switch. The ISO of the switch can be calculated as

$$ISO = -20\log_{10} \left| \frac{Z_L + Z_s}{Z_L + Z_s + 1/j\omega C_{off}} \right| [dB]$$

(2.6)

From (2.6), in order to get higher ISO, Coff should be as low as possible.

# **Figure of Merit (FOM)**

Figure of Merit (FOM) is a performance factor to evaluate the switch. In general, FOM of the switch is defined as

$$FOM = R_{on} * C_{off} [s]$$

(2.7)

, where  $R_{on}$  and  $C_{off}$  are the on-resistance and off-capacitance of the nMOS transistor, respectively. Equation (2.7) says that lower FOM can be obtained by lower  $R_{on}$ , which means lower insertion loss, and lower  $C_{off}$ , which means higher isolation.

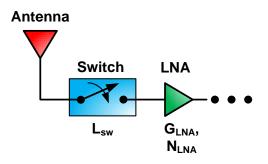

Fig. 2.5. Descriptions of (a)  $P_{1dB}$ , (b)  $IP_3$ , (c) cascaded nonlinear stages, and (d) measurement set-up for dual-tone signal.

## **Power Handling Capability and Nonlinearity**

Power handling capability and nonlinearity of the switch can be evaluated as  $P_{1dB}$  and  $IP_3$  of the switch. Figs. 2.5(a) and (b) show the descriptions of the input and output  $P_{1dB}$ , and the input and output IP3 with respect to input power levels, respectively.  $P_{1dB}$  is the gain (or loss) 1-dB compression point. As the power level of the fundamental tones injected to the device under test (DUT) increases, the DUT maintains constant gain or loss. However, the gain or loss starts to drop or increase at certain power level. The  $P_{1dB}$  is the 1-dB gain drop point or 1-dB loss increment

point and means how much power the DUT can handle. IP<sub>3</sub> is the third order intercept point. When two closely spaced fundamental tones ( $f_1$  and  $f_2$ ) are injected into the DUT, the DUT generates inter-modulation products due to its nonlinearity characteristic. Among the products, the 3<sup>rd</sup> order inter-modulation products (also called as IM3 products in Fig. 2.5(b)) such as  $2*f_1-f_2$  and  $2*f_2-f_1$  can be serious because they can be located close to the fundamental tones and distort them. As the fundamental tones' power level increases, the IM3 products' power level also increases by three times of the fundamental signal's increment. The two signals' power levels are same at certain power level. This power level is the IP<sub>3</sub> point that measures how linear the DUT is. Since the switch is typically located after PA in transmitter as shown in Fig. 2.5(c), the nonlinearity of the latter components becomes more critical [20], [21], hence the power handling capability of the switch should be as high as possible and equation (2.8) explains the reason.

$$\frac{1}{A_{IP3}^2} \approx \frac{1}{A_{IP3,1}^2} + \frac{\alpha_1^2}{A_{IP3,2}^2}$$

(2.8)

, where A<sub>IP3</sub> is the total IP<sub>3</sub> magnitude of the cascaded nonlinear stage in Fig. 2.5(c), A<sub>IP3,1</sub>, A<sub>IP3,2</sub> are the IP<sub>3</sub> magnitudes of the PA and the switch, respectively, and  $\alpha_{PA}^2$  is the gain of PA.

Fig. 2.5(d) shows the simplest two-tone ( $f_1$  and  $f_2$ ) measurement setup for P<sub>1dB</sub> and IP<sub>3</sub>. To generate the two-tone signals,  $f_2$  signal from Port 3 is combined with  $f_1$  signal at Port 1 through an internal combiner in the VNA as shown in Fig. 2.5(d) and then the combined signal ( $f_1$  and  $f_2$ ) is injected to the DUT (switch). While the input

power level at 'B' in Fig. 2.5(d) injected to the switch could reach higher level than the anticipated power handling capability of the switch, the output power level at 'A' in Fig. 2.5(d) can be limited at millimeter-wave frequencies. In order to increase the input power level for the DUT, additional external pre-amp is normally used as shown in Fig. 2.5(d).

## 2.1.3 Basic Switch Topology

A switch can be classified as Single Pole Single Throw (SPST), Single Pole Double Throw (SPDT), Single Pole Multi Throw (SPxT), Multi Pole Multi Throw (xPxT), Transmit and Receive (T/R) switches and etc. Most fundamental structure is SPST switch and other switches are generally implemented by combining several identical SPST switches together with one common input port.

Fig. 2.6 shows two fundamental topologies for SPDT switches. Figs. 2.6(a) and (b) show series switch and its equivalent circuit. When  $V_{c1}$  is biased at 1.8 V in Fig. 2.6(a), the IL and ISO of on- and off-state branches are derived as

$$IL = -20\log_{10} \left| \frac{2 \cdot Z_0}{2 \cdot Z_0 + R_{on_M1}} \right| \text{ and } ISO = -20 \cdot \log_{10} \left| \frac{2 \cdot Z_0}{2 \cdot Z_0 + \frac{1}{j\omega C_{off_M2}}} \right| (2.9)$$

Т

T

, where  $Z_0$  is the terminating impedance of ports 1, 2 and 3.

According to (2.9), in this switch, increasing the width of the series nMOS ( $M_1$  and  $M_2$ ) improves the insertion loss of the switch as  $R_{on}$  decreases according to (2.1). However, it can deteriorate the isolation of the switch because of the increased parasitic capacitance

Fig. 2.6. Fundamental SPDT switch topologies: (a) series switch, (b) equivalent circuit of (a) when  $V_{c1} = 1.8$  V, (c) series-shunt switch, and (d) equivalent circuit of (c) when  $V_{c2} = 1.8$  V.

that results from the widened widths, which results in more signal leakage from the input to output.

On the other hand, Fig. 2.6(c) shows series-shunt SPDT switch topology. This switch is implemented to achieve not only lower IL but also higher ISO compared to series SPDT switch topology as shown in Fig. 2.6(a). When  $V_{c2}$  is biased at 1.8 V in Fig. 2.6(c), the SPDT switch, which is on-state in Port 2, can be equivalent to the circuit in Fig. 2.6(d). On-state Port 1–Port 2 and off-state Port 1–Port 3 can be seen as simple RC circuits with their cut-off frequency (3-dB frequency) obtained as

$$f_{c_{on-state}} = \frac{1}{2\pi R_{on_{Msel}}C_{off_{Msh1}}} \text{ and } f_{c_{off_{-state}}} = \frac{1}{2\pi R_{on_{Msh2}}C_{off_{Mse2}}} \text{ [Hz]}$$

(2.10)

In on state, from (2.10), higher 3-dB cut-off frequency ( $f_c$ ) and wider operating frequency (DC to  $f_c$ ) can be obtained by lower the FOM described in Sec. 2.1.2.3.

And, the IL and ISO of the switch are derived as

$$IL = -20 \log_{10} \left| \frac{2 * Z_0}{2 * Z_0 + \frac{1}{\frac{1}{R_{on\_Mse1}} + j\omega C_{off\_Msh1}}} \right| \text{ and}$$

$$ISO = -20 \log_{10} \left| \frac{2 * Z_0}{2 * Z_0 + \frac{1}{R_{on\_Msh2} + j\omega C_{off\_Mse2}}} \right|$$

$$(2.11)$$

, where  $Z_0$  is terminating impedance of ports 1, 2 and 3.

Equation (2.11) verifies that series-shunt SPDT switch can achieve lower IL and higher ISO compared to series SPDT switch assuming of the same size of the transistors  $(M_1=M_2=M_{se1}=M_{se2})$ . That is, series nMOS ( $M_{se1}$  and  $M_{se2}$ ) and shunt nMOS ( $M_{sh1}$  and  $M_{sh2}$ ) are employed to enhance the insertion loss and isolation of the switch, respectively.

In the series-shunt switch, similarly to series switch, increasing the width of series nMOS ( $M_{se1}$  and  $M_{se2}$ ) enhances IL of the switch, but reduces isolation due to the increased parasitic capacitance. On the other hand, increasing the width of the shunt nMOS ( $M_{sh1}$  and  $M_{sh2}$ ) can improve the ISO, but it can also result in signal leakage from input to ground. Therefore, a trade-off between series and shunt nMOS transistors needs to be considered, and each optimum width needs to be found for the best performance of the switch.

Fig. 2.7. Simulated IL and ISO for Port 1 - Port 2 and Port 1 - Port 3 of the series-shunt SPDT switch in Fig. 2.6(c).

Fig. 2.7 shows the low-pass and high-pass responses of IL and ISO in the seriesshunt switch and it can be seen that the IL increases and ISO decreases, respectively, as frequency increases. Therefore, the switch is more suitable to DC–several-GHz switch.

## 2.1.4 Motivation for Multi-Band Band-Pass Filtering Switch

As mentioned in Sec. 2.1.3, since the IL and ISO of the typical series-shunt switch show the low-pass and high-pass responses by its structural characteristic, it is difficult to design a switch having single or multi-band band-pass filtering function.

The reasons that multi-band filtering function is needed for the switch will be followed. T/R switches and band-pass filters (BPFs) are widely employed in communication and radar systems as transmitting and receiving, and frequency selective circuits, respectively. To achieve both switching and band-pass filtering in systems, external BPF and wideband switch are commonly utilized together as depicted in Fig.

Fig. 2.8. Band-pass filtering switch design concept: (a) conventional BPF and switch structure, (b) the proposed BPF + switch structure, (c) quarter-wavelength circuit and parallel resonator, (d) quarter-wavelength circuit and parallel resonator replaced with nMOS transistor.