# LOW-VOLTAGE, LOW-POWER CIRCUITS FOR DATA COMMUNICATION SYSTEMS

A Dissertation

by

#### MINGDENG CHEN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2003

Major Subject: Electrical Engineering

# LOW-VOLTAGE, LOW-POWER CIRCUITS FOR DATA COMMUNICATION SYSTEMS

A Dissertation

by

#### MINGDENG CHEN

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

| proved as to style and content by:          |                                 |

|---------------------------------------------|---------------------------------|

| Jose Silva-Martinez<br>(Chair of Committee) | Edgar Sánchez-Sinencio (Member) |

| Zixiang Xiong<br>(Member)                   | Glenn Agnolet<br>(Member)       |

| Chanan Singh (Head of Department)           |                                 |

December 2003

Major Subject: Electrical Engineering

#### **ABSTRACT**

Low-Voltage, Low-Power Circuits for Data Communication Systems.

(December 2003)

Mingdeng Chen,

B.S., National University of Defense Technology, P. R. China;

M.S., National University of Defense Technology, P. R. China

Chair of Advisory Committee: Dr. Jose Silva-Martinez

There are growing industrial demands for low-voltage supply and low-power consumption circuits and systems. This is especially true for very high integration level and very large scale integrated (VLSI) mixed-signal chips and system-on-a-chip. It is mainly due to the limited power dissipation within a small area and the costs related to the packaging and thermal management.

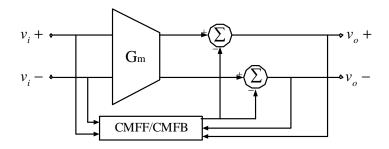

In this research work, two low-voltage, low-power integrated circuits used for data communication systems are introduced. The first one is a high performance continuous-time linear phase filter with automatic frequency tuning. The filter can be used in hard disk driver systems and wired communication systems such as 1000Base-T transceivers. A pseudo-differential operational transconductance amplifier (OTA) based on transistors operating in triode region is used to achieve a large linear signal swing with low-voltage supplies. A common-mode (CM) control circuit that combines common-mode feedback (CMFB), common-mode feedforward (CMFF), and adaptive-bias has been proposed.

With a 2.3V single supply, the filter's total harmonic distortion is less than -44dB for a  $2V_{PP}$  differential input, which is due to the well controlled CM behavior. The ratio of the root mean square value of the ac signal to the power supply voltage is around 31%, which is much better than previous realizations.

The second integrated circuit includes two LVDS drivers used for high-speed point-to-point links. By removing the stacked switches used in the conventional structures, both LVDS drivers can operate with ultra low-voltage supplies. Although the Double Current Sources (DCS) LVDS driver draws twice minimum static current as required by the signal swing, it is quite simple and achieves very high speed operation. The Switchable Current Sources (SCS) LVDS driver, by dynamically switching the current sources, draws minimum static current and reduces the power consumption by 60% compared to the previously reported LVDS drivers. Both LVDS drivers are compliant to the standards and operate at data rates up to gigabits-per-second.

## **DEDICATION**

To my Parents,

To my brothers and my sisters,

To my dearest wife Ju,

And to my lovely daughter Annie

For their love and support

#### **ACKNOWLEDGMENTS**

I would like to express my sincere appreciation to my advisor, professor Jose Silva-Martinez, for his guidance, support, and encouragement during my studies at Texas A&M University. His creativity and insight into circuit design helped me a lot in my research. His energy and love of what he is doing inspires me a lot. I feel very grateful for his supervision both on the technical and the personal levels during my stay at College Station.

I would like to thank and acknowledge Dr. Edgar Sánchez-Sinencio. It was he who welcomed me into the group. His kind help, support, and encouragement made my study fruitful and joyful.

I would like to thank and acknowledge Moises Robinson, Shahriar Rokhsaz, and Michael Nix. They helped me a lot on my internships with RocketChips, which is now the Communication Technology Division (CTD), Xilinx Inc.. They are not only my mentors and advisors, they are also my close friends.

I would like to thank all my colleagues in the Analog & Mixed Signal Center for their friendship and all of their help over the years. Ahmed Mohieldin helped me a lot on the filter design. Lab manager Sung Tae Moon is very helpful and helped me a lot on my chip testing. Ari, Chunyu, Bo, and Wenjun, all helped me a lot.

I would like to thank my committee members: Dr. Zixiang Xiong, and Dr. Glenn Agnolet for their precious time and valuable comments on my research.

I also want to thank the secretary of our group, Ella Gallagher, who is the person you want to ask about any questions and help.

Special thanks to my parents, my brothers, and my sisters. Special thanks to my mother-in-law. Without her help, I could not focus on my research. Special thanks to my wife Ju, who is always there for me, no matter whether I am rich or poor, happy or sad. She is my ever. I could not achieve this without her extraordinary love and support in every sense. Finally, special thanks to my lovely daughter Annie, who is my sunshine. Her every movement, every word, even "noise" makes me so happy and proud.

# TABLE OF CONTENTS

|                                                                  | Page |

|------------------------------------------------------------------|------|

| ABSTRACT                                                         | iii  |

| DEDICATION                                                       | v    |

| ACKNOWLEDGMENTS                                                  | vi   |

| TABLE OF CONTENTS                                                | viii |

| LIST OF FIGURES                                                  | xi   |

| LIST OF TABLES                                                   | XV   |

| CHAPTER                                                          |      |

| I INTRODUCTION                                                   | 1    |

| 1.1. Low-Voltage, Low-Power Mixed-Signal Circuits and Systems    |      |

| 1.3. Operational Transconductance Amplifiers (OTAs)              | 4    |

| 1.4. High Order Filters                                          |      |

| 1.5. Linear Phase Filter Approximations                          |      |

| 1.5.2 Gain Boosting and Group Delay Shaping                      |      |

| 1.6. Group Delay Sensitivity                                     |      |

| 1.7. Low-Voltage Differential Signaling (LVDS) Drivers           |      |

| 1.8. Main Contributions                                          |      |

| 1.9. Organization                                                |      |

| II A $2V_{PP}$ , 80-200MHZ FOURTH-ORDER CONTINUOUS-TIME LINEAR   |      |

| PHASE FILTER WITH AUTOMATIC FREQUENCY TUNING                     | 17   |

| 2.1. Background and Motivation                                   | 17   |

| 2.2. Pseudo-Differential OTAs and Their Characteristics          |      |

| 2.3. Common-Mode Control Techniques for Pseudo-Differential OTAs | 22   |

| 2.3.1 Pseudo-Differential OTAs with Common-Mode Feedforward      | 22   |

| 2.3.2 Fully-Balanced Transconductor Based on Single-Ended OTAs   | 25   |

| CHAPTER                                                          | Page |

|------------------------------------------------------------------|------|

| 2.3.3 Common-Mode Control Circuit Using Both CMFF and CMFB       | 27   |

| 2.3.4 Adaptive Biasing for Tunable Transconductors               | 29   |

| 2.4. Pseudo-Differential Transconductor                          | 31   |

| 2.4.1 Optimizing the Linear Range                                | 32   |

| 2.4.2 Regulated Gain Control (RGC) Loop                          | 34   |

| 2.4.3 Short-Channel Effects                                      | 38   |

| 2.5. Common-Mode Control Circuits                                | 42   |

| 2.5.1 Common-Mode Control Principle                              | 43   |

| 2.5.2 Common-Mode Control Frequency Response                     | 45   |

| 2.5.3 A Fast Common-Mode Control Circuit                         | 47   |

| 2.6. Filter Architecture                                         | 51   |

| 2.7. Automatic Tuning System                                     | 53   |

| 2.8. Experimental Results                                        | 58   |

| 2.9. Conclusions                                                 | 67   |

| III LOW-VOLTAGE, LOW-POWER LVDS DRIVERS                          | 68   |

| 3.1. Background and Motivation                                   | 60   |

| 3.2. LVDS Interfaces                                             |      |

| 3.3. LVDS Driver Structures                                      |      |

| 3.3.1 Typical Bridged-Switches LVDS Driver                       |      |

| 3.3.2 All NMOS Switches LVDS Driver with CMFB                    |      |

| 3.3.3 Two Switches LVDS Drivers                                  |      |

| 3.4. Roadmap to the Low-Voltage, Low-Power LVDS Drivers          |      |

| 3.4.1 LVDS Driver Specifications                                 |      |

| 3.4.2 Headroom Issues Associated with the Previous LVDS Drivers  |      |

| 3.4.3 Double Current Sources (DCS) LVDS Driver                   |      |

| 3.4.4 Switchable Current Sources (SCS) LVDS Driver               |      |

| 3.4.5 Pull Up/Down Circuits                                      |      |

| 3.4.6 Proposed SCS LVDS Driver with Passive Pull Up/Down Circuit |      |

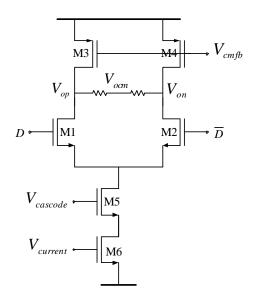

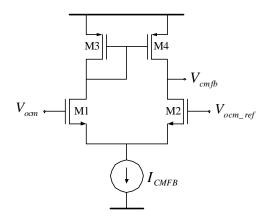

| 3.5. DCS LVDS Driver Circuit Design                              |      |

| 3.5.1 DCS LVDS Driver Core and CMFB                              |      |

| 3.5.2 Adaptive Current Generator                                 |      |

| 3.6. SCS LVDS Driver Circuit Design                              |      |

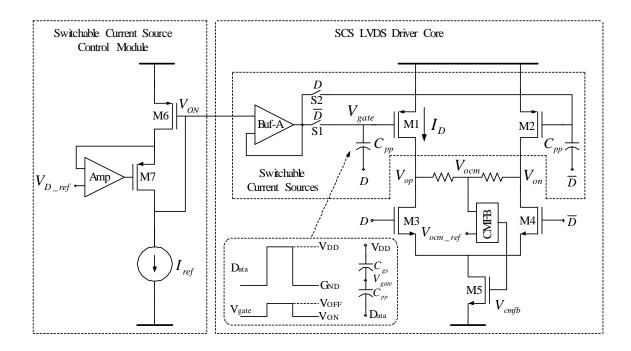

| 3.6.1 SCS LVDS Driver Core                                       |      |

| 3.6.2 SCS LVDS Driver Switchable Current Source Control Module   |      |

| 3.7. Simulation Results                                          |      |

| 3.7.1 DCS LVDS Simulation Results                                |      |

| 3.7.2 SCS LVDS Driver Simulation Results                         |      |

| 3.8. Experimental Results                                        |      |

| 3.8.1 DCS LVDS Driver Experimental Results                       |      |

| 3.8.2 SCS LVDS Driver Experimental Results                       | 112  |

| CHAPTER                         | Page |

|---------------------------------|------|

| 3.9. Comparison and Conclusions | 116  |

| IV CONCLUSIONS                  | 119  |

| REFERENCES                      | 121  |

| VITA                            | 127  |

## LIST OF FIGURES

|               |                                                                                  | Page |

|---------------|----------------------------------------------------------------------------------|------|

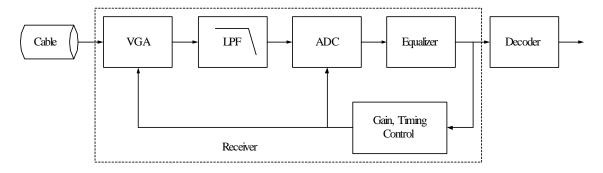

| Figure I.1    | Simplified 1000Base-T receiver block diagram                                     | 3    |

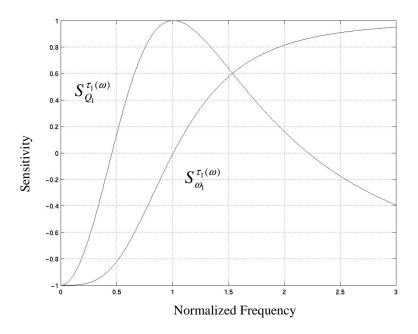

| Figure I.2    | Group delay sensitivities for the first biquad                                   | 12   |

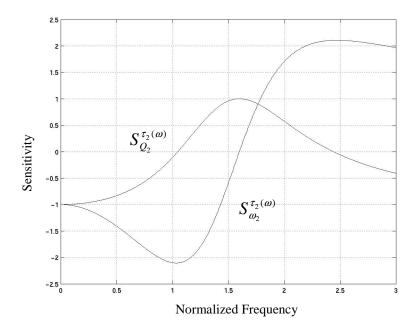

| Figure I.3    | Group delay sensitivities for the second biquad                                  | 13   |

| Figure II.1a  | Fully-differential structure                                                     | 20   |

| Figure II.1b  | Pseudo-differential structure                                                    | 20   |

| Figure II.2   | Common-mode feedforward scheme                                                   | 23   |

| Figure II.3   | Balanced transconductor based on single-ended OTAs                               | 25   |

| Figure II.4   | Fully-balanced configuration using two multi-inputs single-ended transconductors | 26   |

| Figure II.5   | Pseudo-differential transconductor with CMFF and CMFB                            | 28   |

| Figure II.6   | Tunable transconductor with CMFB                                                 | 30   |

| Figure II.7   | Pseudo-differential OTA                                                          | 32   |

| Figure II.8   | Configuration for evaluating OTA transconductance                                | 35   |

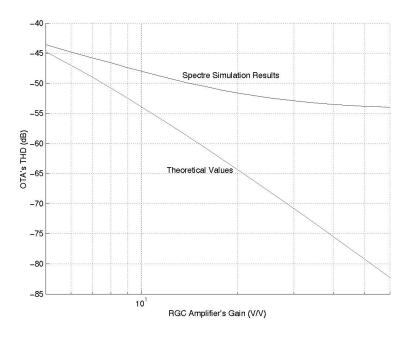

| Figure II.9   | OTA's THD vs. RGC amplifier's gain (L <sub>M1</sub> =0.6µm)                      | 37   |

| Figure II.10  | RGC amplifier                                                                    | 38   |

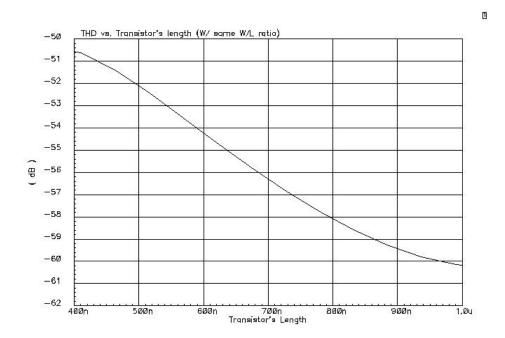

| Figure II.11  | OTA's THD vs. input transistor M1's length L                                     | 41   |

| Figure II.12a | Conventional CM control using separate CMFB and CMFF                             | 42   |

| Figure II.12b | Proposed CM control that combines CMFB and CMFF                                  | 43   |

| Figure II.13  | Common-mode control circuit                                                      | 43   |

| Figure II.14  | Simplified CMFB loop equivalent circuit                                          | 45   |

|               | Pa                                                                                                                                  | .ge |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure II.15  | CMFB closed loop CM step response with a CM current step of 50µA                                                                    | 47  |

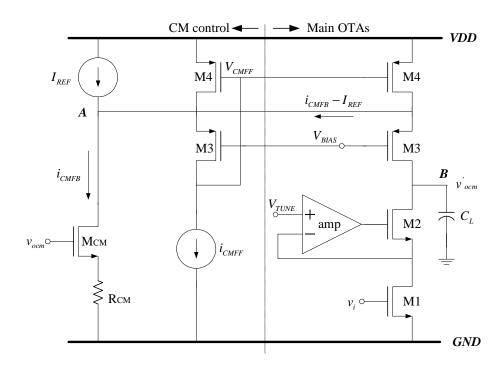

| Figure II.16  | Conceptual schematic of a faster common-mode control circuit                                                                        | 49  |

| Figure II.17  | A fast common-mode control circuit                                                                                                  | 50  |

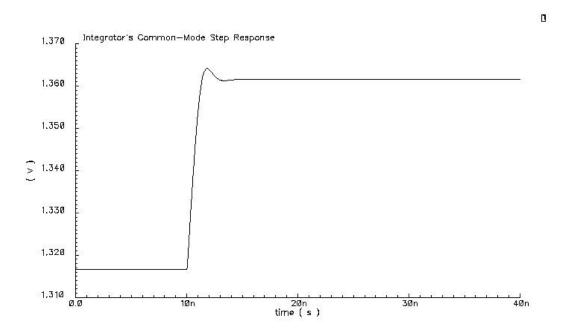

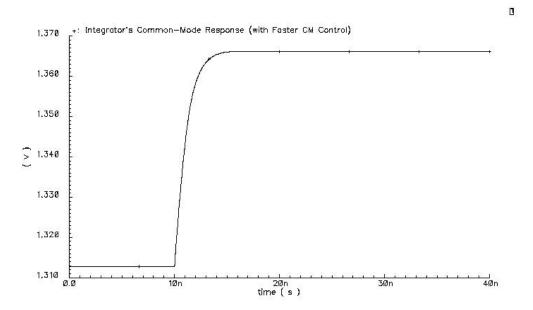

| Figure II.18  | CMFB closed loop CM step response with a CM current step of 50µA                                                                    | 51  |

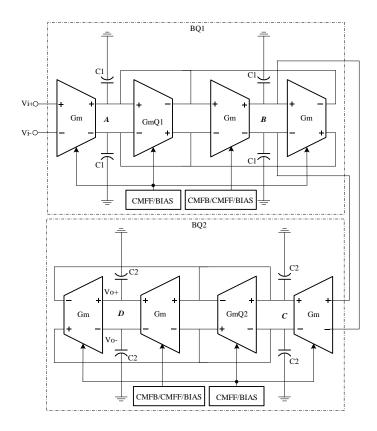

| Figure II.19  | 4 <sup>th</sup> -order equiripple linear phase filter                                                                               | 52  |

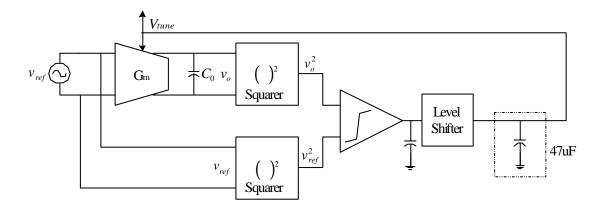

| Figure II.20  | Block diagram of the automatic tuning system                                                                                        | 54  |

| Figure II.21  | Squarer                                                                                                                             | 56  |

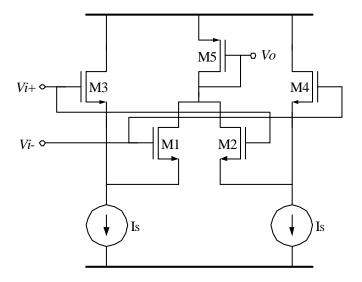

| Figure II.22a | Comparator                                                                                                                          | 57  |

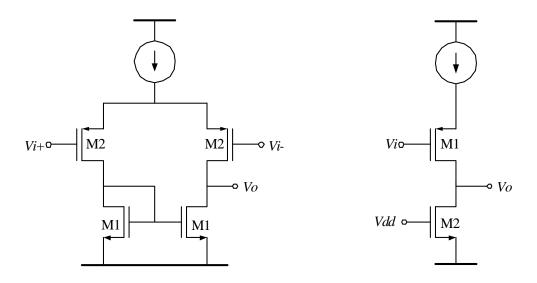

| Figure II.22b | Level-shifter                                                                                                                       | 57  |

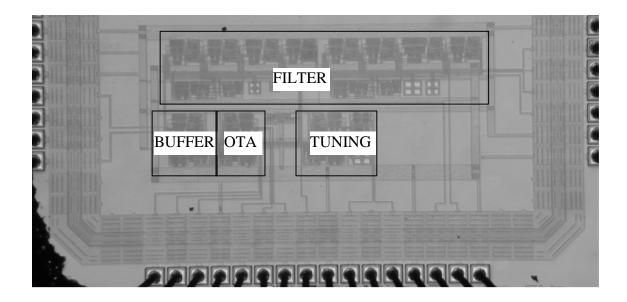

| Figure II.23  | Chip micrograph                                                                                                                     | 58  |

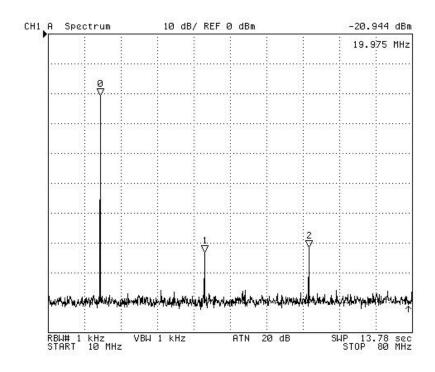

| Figure II.24  | OTA's output spectrum (V <sub>in</sub> =2V <sub>pp</sub> )                                                                          | 59  |

| Figure II.25  | Filter's output spectrum (V <sub>in</sub> =2V <sub>pp</sub> )                                                                       | 60  |

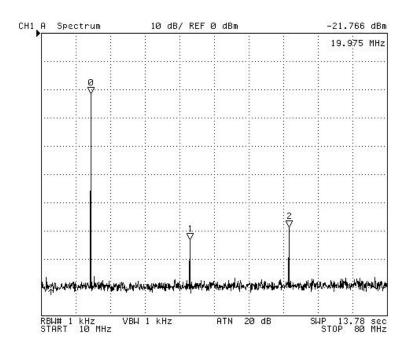

| Figure II.26  | Filter's IM3 for a two-tone input (@60MHz and 70MHz) of $1V_{pp}$ each                                                              | 60  |

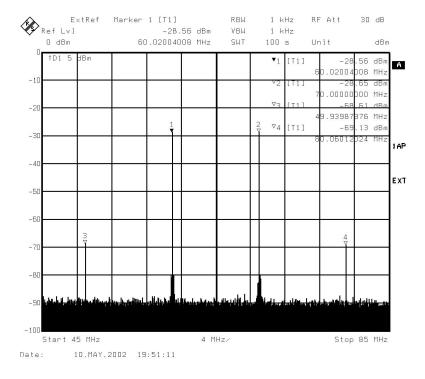

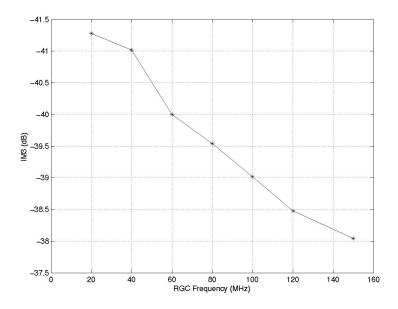

| Figure II.27  | Filter's IM3 vs. frequency (V <sub>1</sub> =1V <sub>pp</sub> , V <sub>2</sub> =1V <sub>pp</sub> )                                   | 61  |

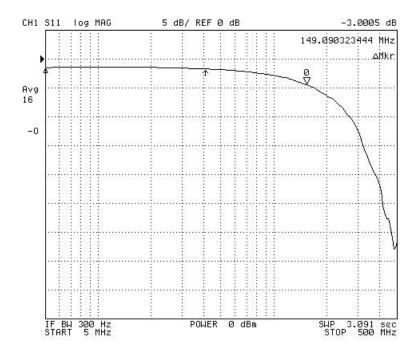

| Figure II.28  | Filter magnitude response with a bandwidth of 150MHz                                                                                | 62  |

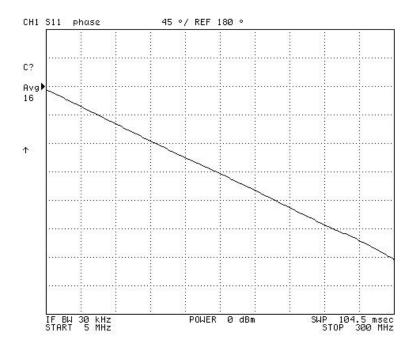

| Figure II.29  | Filter's phase response with a bandwidth of 150MHz                                                                                  | 62  |

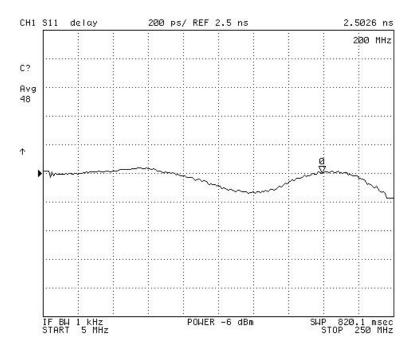

| Figure II.30  | Filter's group delay response with a bandwidth of 150MHz                                                                            | 63  |

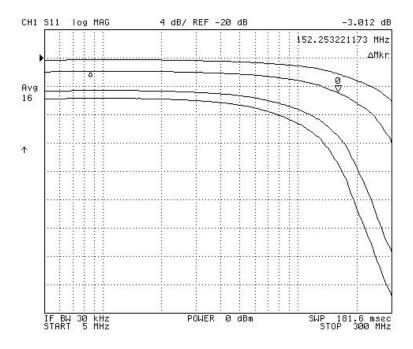

| Figure II.31  | Zoomed filter's magnitude response with automatic frequency tuning system (reference frequency = 80MHz, 100MHz, 150MHz, and 200MHz) | 64  |

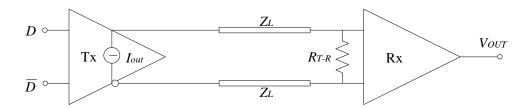

| Figure III.1a | LVDS interface with line termination at the receiver end                                                                            | 71  |

|                |                                                                                                   | Page |

|----------------|---------------------------------------------------------------------------------------------------|------|

| Figure III.1b  | LVDS interface with termination at the receiver and source ends for gigabits-per-second operation | 72   |

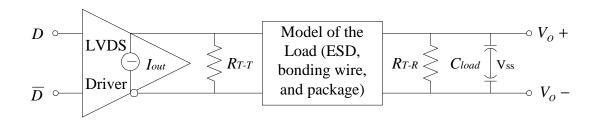

| Figure III.2a  | Typical LVDS driver model                                                                         | 74   |

| Figure III.2b  | A possible implementation                                                                         | 74   |

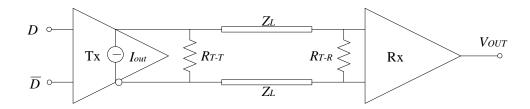

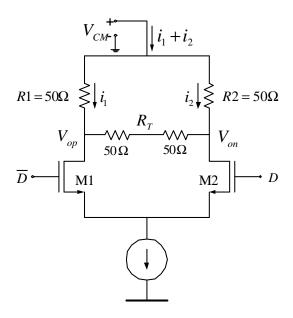

| Figure III.3a  | LVDS driver core                                                                                  | 75   |

| Figure III.3b  | LVDS driver CMFB                                                                                  | 75   |

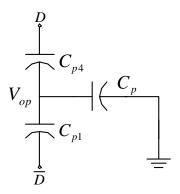

| Figure III.3c  | Parasitic capacitors associated with the charge injection                                         | 76   |

| Figure III.4   | Two switches LVDS driver                                                                          | 78   |

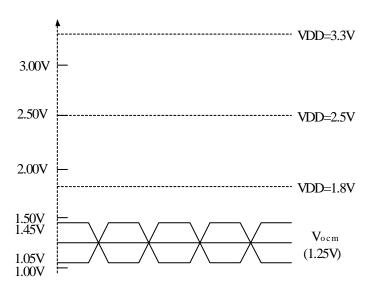

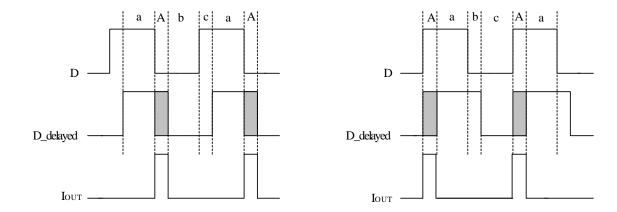

| Figure III.5   | LVDS signal formatting                                                                            | 79   |

| Figure III.6a  | DCS LVDS driver model                                                                             | 83   |

| Figure III.6b  | Possible implementation.                                                                          | 83   |

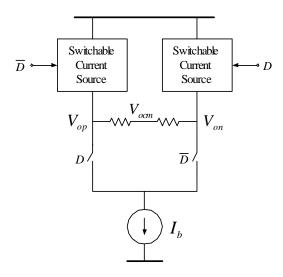

| Figure III.7   | SCS LVDS driver model                                                                             | 84   |

| Figure III.8   | Main principle of the SCS LVDS driver                                                             | 85   |

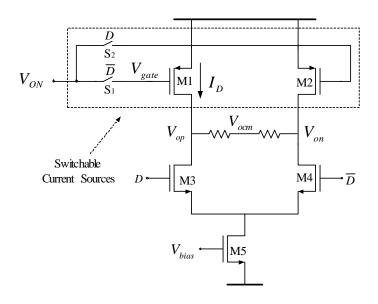

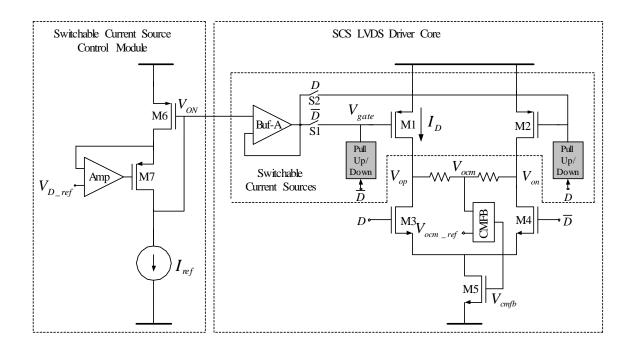

| Figure III.9   | Schematic of the SCS LVDS driver with active pull up/down                                         | 86   |

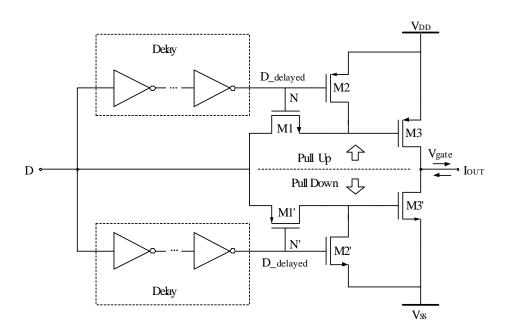

| Figure III.10  | Active pull up/down circuit                                                                       | 88   |

| Figure III.11a | Pull-up circuit waveforms                                                                         | 89   |

| Figure III.11b | Pull-down circuit waveforms.                                                                      | 89   |

| Figure III.12  | Schematic of the proposed LVDS driver                                                             | 92   |

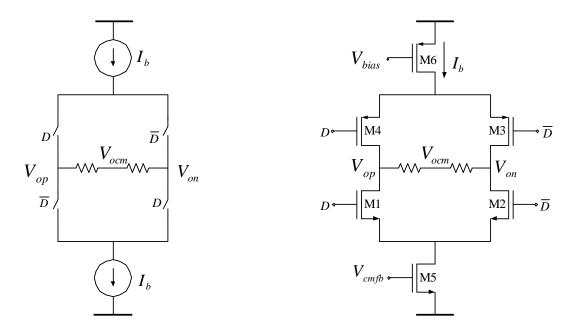

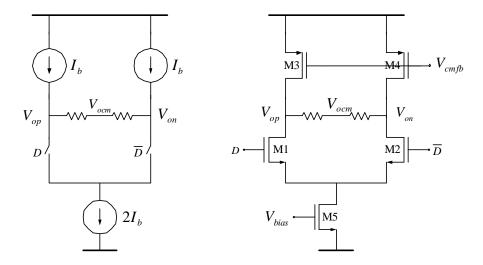

| Figure III.13  | DCS LVDS driver core                                                                              | 94   |

| Figure III.14  | DCS LVDS driver CMFB                                                                              | 95   |

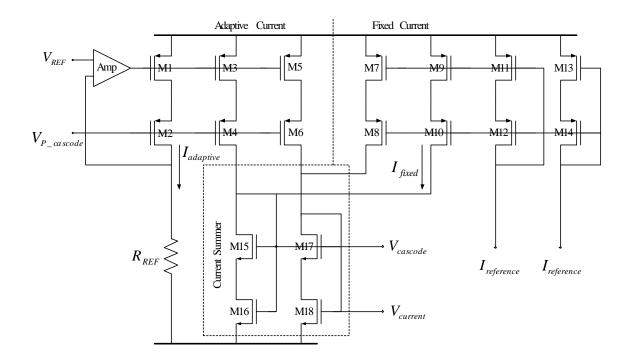

| Figure III.15  | Adaptive biasing current source                                                                   | 97   |

| Figure III.16  | Telescope amplifier                                                                               | 99   |

| Figure III.17  | RGC amplifier                                                                                     | 100  |

|               | Page                                                                                       |

|---------------|--------------------------------------------------------------------------------------------|

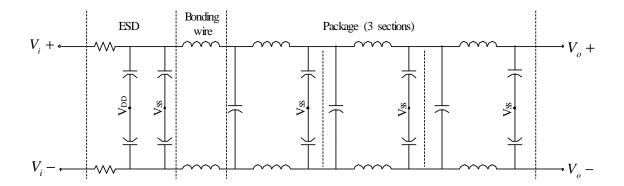

| Figure III.18 | Simulation configuration for the LVDS drivers101                                           |

| Figure III.19 | Model of the load used for simulations                                                     |

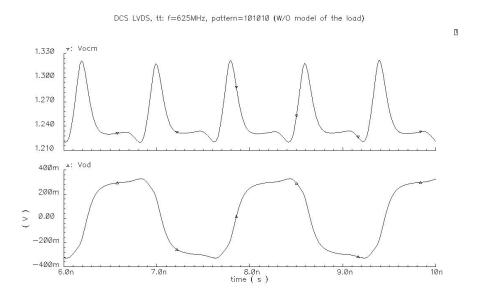

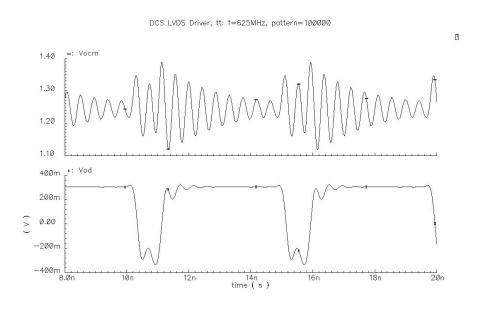

| Figure III.20 | DCS LVDS driver output waveforms without the load model (101010)                           |

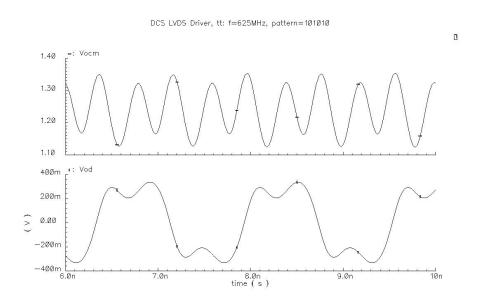

| Figure III.21 | DCS LVDS driver output waveforms with the load model (101010)103                           |

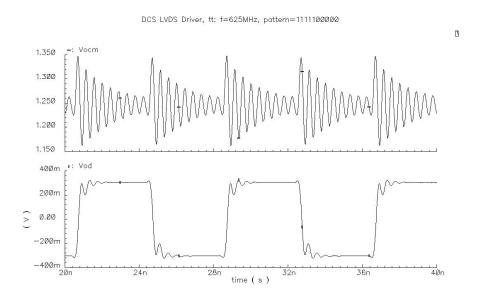

| Figure III.22 | DCS LVDS driver output waveforms with the load model (1111100000)                          |

| Figure III.23 | DCS LVDS driver output waveforms with the load model (100000)104                           |

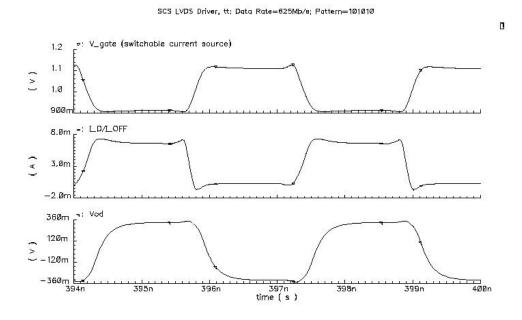

| Figure III.24 | Switchable current source gate voltage, drain current, and the output differential voltage |

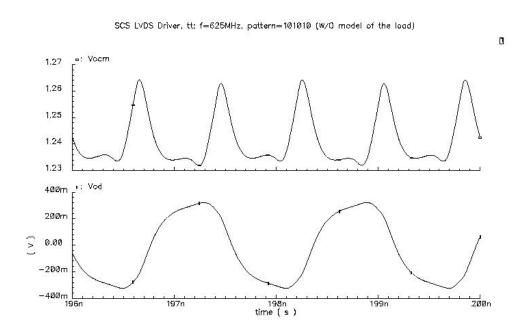

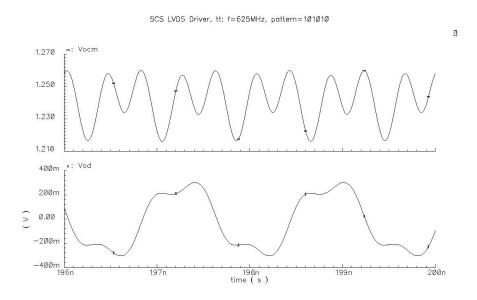

| Figure III.25 | SCS LVDS driver output waveforms without the load model (101010)                           |

| Figure III.26 | SCS LVDS driver output waveforms with the load model (101010) 108                          |

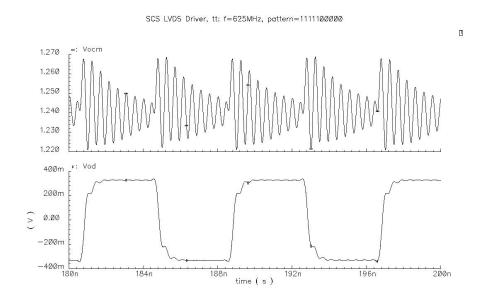

| Figure III.27 | SCS LVDS driver output waveforms with the load model (1111100000)                          |

| Figure III.28 | SCS LVDS driver output waveforms with the load model (100000) 109                          |

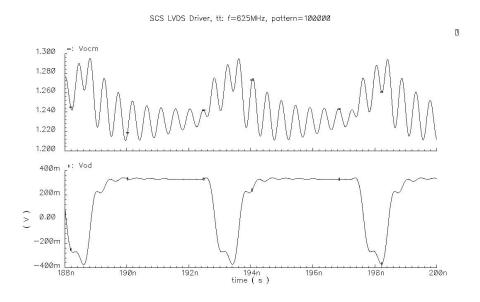

| Figure III.29 | DCS and SCS LVDS drivers chip micrograph110                                                |

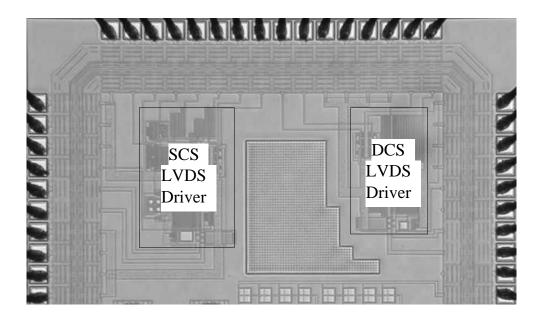

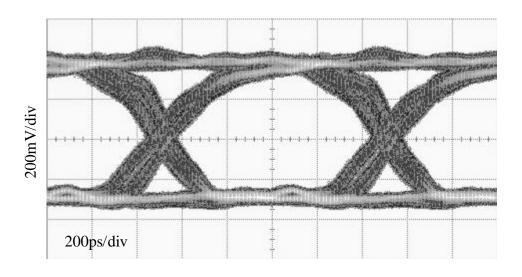

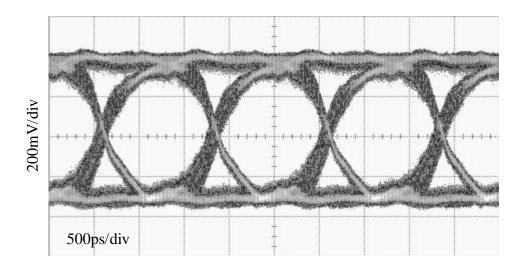

| Figure III.30 | DCS LVDS driver eye diagram (data rate = 680Mb/s)111                                       |

| Figure III.31 | DCS LVDS driver eye diagram (data rate = 1.0Gb/s)111                                       |

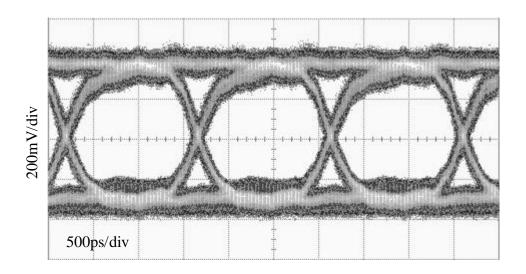

| Figure III.32 | SCS LVDS driver eye diagram (data rate = 680Mb/s)112                                       |

| Figure III.33 | SCS LVDS driver eye diagram (data rate = 1.0Gb/s)113                                       |

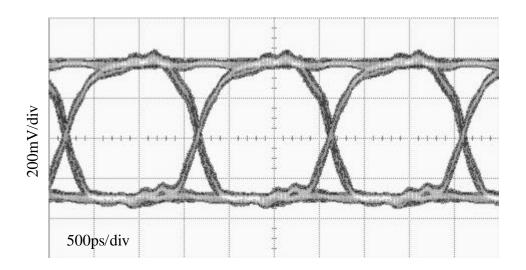

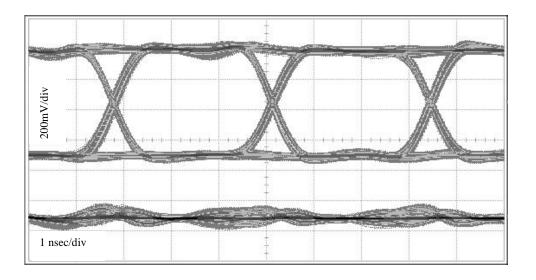

| Figure III.34 | SCS LVDS driver output signals (data rate = 300Mb/s)114                                    |

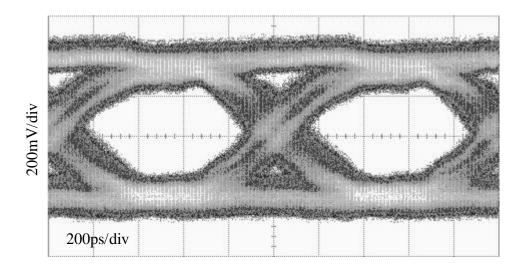

| Figure III.35 | SCS LVDS driver eye diagram ( $V_{DD}=1.6V$ ; data rate = 800Mb/s)115                      |

## LIST OF TABLES

|             | F                                                                                      | Page |

|-------------|----------------------------------------------------------------------------------------|------|

| Table I.1   | 4 <sup>th</sup> -order Bessel-Thomason linear phase filter parameters                  | 8    |

| Table I.2   | 4 <sup>th</sup> -order 0.05° equiripple linear phase filter parameters                 | 8    |

| Table II.1  | OTA's THD vs. input transistor length L ( $V_{in} = 2V_{ppd}$ )                        | 41   |

| Table II.2  | OTA transistor dimensions and bias conditions                                          | 42   |

| Table II.3  | Capacitances at the filter's nodes                                                     | 53   |

| Table II.4  | Performance summary of the standalone filter prototype fabricated in 0.35 CMOS process | 65   |

| Table II.5  | Comparison of several linear phase filters                                             | 66   |

| Table III.1 | Specification for LVDS driver                                                          | 80   |

| Table III.2 | Transistor dimensions and parasitic capacitances of the DCS LVDS core                  | 94   |

| Table III.3 | Transistor dimensions and parasitic capacitances of the SCS LVDS core                  | 98   |

| Table III.4 | Current consumption for DCS and SCS LVDS drivers                                       | 117  |

| Table III.5 | Comparison with the previous realizations                                              | 118  |

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1. Low-Voltage, Low-Power Mixed-Signal Circuits and Systems

There are growing industrial demands for low-voltage supply and low-power consumption circuits and systems [1]. From modern portable computers and communication devices to more traditional applications such as medical devices, the need for circuits and systems that operate with smaller supply voltages and consume minimum power is immense and endless. This is specially true for very high integration level and very large scale integrated (VLSI) mixed-signal chips and system-on-a-chip. It is mainly due to the limited power dissipation within a small area and so the costs related to the packaging and thermal management. Also portable applications require to extend the battery life as well.

This trend has forced designers to develop new approaches more amenable to low-voltage and low-power integrated circuits and it poses lots of challenges for all involved: processes, devices, circuits, and system architectures [1]. Low-voltage and low-power electronic systems have been pursued continuously; recently we have been seeing continuous advances in process technologies, in device modeling for computer simulation, in circuit design techniques, and in approaches to system design--all aim at

This dissertation follows the style and format of IEEE Journal of Solid-State Circuits.

\_

the production of electronic systems that operate from very low supply voltages and that dissipate very low power.

In mixed-signal systems, the analog circuits are combined with digital circuits in order to get the best performance with low-voltage supply and low-power consumption. This combination should be in an optimal way and the optimization process is application dependent.

#### 1.2. Types of Filters

Filters are systems that can be used to manipulate the frequency spectrum of signals and they are essential in many different applications. Filters are usually used to get ride of the unwanted noise and reject the surrounding interference. For example, they can be used to band-limit signals and noise in data conversion systems and communication systems; provide magnitude and phase equalization in hard disk driver systems, transmission lines, and cables; select band, reject image, and detect signals in RF communication systems. Figure I.1 shows a simplified 1000Base-T receiver which includes a continuous-time filter. The signal coming from the cable is amplified to a certain level through the variable gain amplifier (VGA). The low-pass continuous-time filter is used to limit signal and noise bandwidth and provide anti-aliasing prior sampling. The analog-to-digital converter (ADC) digitizes the filtered output to take the advantages of the Digital Signal Processing (DSP) unit. The equalizer provides the equalization and the equalized signal goes to the decoder. The gain/timing control module is used to adjust the gain of the VGA. Although we are living in a digital age,

many digital systems interfacing with the real analog world might use continuous-time filters.

Figure I.1 Simplified 1000Base-T receiver block diagram

There are mainly two types of filters: digital filters and analog filters. While the data samples are discrete for digital filters, analog filters process continuous signals. Analog filters can be further divided into passive filters and active filters. While passive filters comprise passive components only such as resistors, capacitors, and inductors, active filters use active devices such as operational amplifiers (OPAMP) and/or operational transconductance amplifiers (OTA). Active filters can also be classified into Active-RC, Switched-Capacitor (sampled-data filters), OTA-C/Gm-C, and LC filters. Passive filters do not employ amplifiers and usually they are off-chip filters and are not suitable for integrated circuits. Active-RC and Switched-Capacitor filters are suitable for low to medium frequency applications, but they are not suitable for high frequency applications. This is mainly due to the very wide bandwidth and very large unity-gain frequency requirements for the used operational amplifiers. OTA-C/Gm-C filters use the

whole frequency range up to the unity-gain frequency of the operational transconductance amplifiers and they can be used in medium to high frequency systems. But due to the sensitivity to the parasitics and that operational transconductance amplifiers are power hungry for frequencies in the GHz frequency range, OTA-C filters are not suitable for very high frequency systems. For GHz frequency systems, LC filters become feasible because the required values for Ls and Cs are small so that they can be used for IC solutions. Because of the low quality factor of the on-chip inductors, Q-enhancement is usually needed for LC filters.

Another important issue associated with high performance filters is the automatic tuning. Because of the process, supply, and temperature (PVT) variations, the frequency response and the quality factor of the filter deviates from the desired ones; hence efficient and cost effective automatic tuning systems are needed for high performance systems.

#### **1.3. Operational Transconductance Amplifiers (OTAs)**

Operational transconductance amplifiers (OTAs) are the key active building blocks of continuous-time filters. They can be generally classified into three types: single-ended, fully-differential (FD), and pseudo-differential (PD) OTAs. Most modern high performance analog integrated circuits make use of fully differential signal paths [2]. With OTAs, this technique results in differential outputs as well as differential inputs; hence they are referred to as fully differential OTAs. Fully differential OTAs are preferred because they provide better dynamic range over their single-ended counter

parts, this is mainly due to their larger signal swing, better distortion performance, and better common-mode noise and supply noise rejection. For symmetrical circuits, the common-mode noise appears in both outputs and can be easily rejected. For example, fully differential structures reject noise from the substrate as well as from pass-transistor switches turning off in switched-capacitor applications. If the circuit is built in a symmetric manner, then ideally the noise will affect both signal paths identically, and will be rejected, since only the difference between signals is of importance. In other words, the noise will not affect the differential signal, which is the signal of interest, since both sides of the differential signals see the same noise. In reality, the rejection only partially occurs since the mechanism introducing the noise are usually nonlinear with respect to voltage levels. One example is the substrate noise, which feeds in through junction capacitors and they are nonlinear. However, the noise rejection of a fully differential design will be much better than that for a single-ended output design.

The main drawback of using fully differential OTAs is that a common-mode feedback (CMFB) circuit must be added. This extra circuit is needed to establish the common-mode output voltage. This CMFB circuit is also used to suppress the common-mode signal components over the whole band of differential operation that tends to saturate the different stages [3]. The design of a good CMFB circuit is nontrivial. The speed of the common-mode path should be comparable to that of the differential path, otherwise the common-mode noise (e.g., power supply noise) may be significantly amplified such that the output signal becomes distorted. Also, the CMFB circuit is often a source of noise injection and increases the load capacitance that needs to be driven.

Regardless of the limitations described above, fully differential OTAs work very well and can substantially improve the system's quality, especially in very unfriendly environments such as mixed-mode applications. However, at lower supply voltages, pseudo-differential operation transconductances could be used to avoid the voltage drop across the tail current source used in the fully differential structures. Removing the tail current source achieves a larger signal swing, but it also results in larger common-mode gain. So it requires to carefully control the common-mode response for pseudo-differential OTAs. In some cases, the CMFB requirements may be relaxed [3]. For example, if the common-mode gain is small, the CMFB speed might be reduced (e.g., for a pseudo-differential OTA with common-mode feedforward, the requirements of the CMFB can be relaxed).

#### 1.4. High Order Filters

Usually a second-order filter can not provide the required selectivity required in many practical systems. So high order filters are necessary to provide enough selectivity. There are three main approaches to achieve high order filters: cascade of biquadratic sections without feedback [4], cascade of biquadratic sections with feedback [5], and LC ladder filter emulation [6].

In the cascade of biquadratic sections approach, high order functions are achieved by the direct connection of second-order biquadratic sections. This method provides the simplicity of the filter design and tuning scheme design. But its disadvantage is that the overall filter transfer function is sensitive to the biquad's parameter variations, which are caused by the inevitable process, supply voltage, and temperature (PVT) variations. So its sensitivity performance is not good enough.

Cascaded biquadratics with feedback loops are also based on biquadratic sections, but with some negative feedback [7]. This approach provides better overall filter transfer function sensitivity performance compared to the corresponding cascade of biquadratic sections without feedback [8].

There are mainly two methods to emulate LC ladder filters: emulating the LC ladder filter functionally by realizing the currents and node voltages of the ladder [9] or implementing the inductors using active elements. These approaches provide the best sensitivity performance over the cascaded approaches without/with feedback.

#### 1.5. Linear Phase Filter Approximations

Integrated continuous-time filters used for hard disk driver systems and some digital communication systems such as 1000Base-T are good examples for linear phase filters. The primary purpose of this kind of filters is to limit the signal and noise bandwidth. In general, there is no stringent magnitude response requirements in the passband or stopband, but it must have a linear phase or a constant group delay for all signal frequencies to maintain the data integrity. Non-uniform group delay causes phase distortion and leads to detection problems. In practice, a small group delay deviation or a ripple of about 5% is permitted and a filter with an order of 4-7 maybe used.

#### 1.5.1 Bessel-Thomson and Equiripple Linear Phase Filter Approximations

Bessel-Thomson approximation (maximally flat delay) and equiripple delay approximation are the two main filter approximations used for the design of filters with approximately constant group delay [10-11]. For a fourth-order linear phase filter, the normalized frequencies  $\omega_i$ s and  $Q_i$ s for both Bessel-Thomson and  $0.05^\circ$  Equiripple linear phase filters are shown in Table I.1 and Table I.2.

Table I.1 4<sup>th</sup>-order Bessel-Thomason linear phase filter parameters

| Filter Section | ω <sub>i</sub> , rad/sec | Qi                    |

|----------------|--------------------------|-----------------------|

| Biquad 1       | $\omega_1 = 1.419$       | Q <sub>1</sub> =0.522 |

| Biquad 2       | $\omega_2 = 1.591$       | Q <sub>2</sub> =0.806 |

Table I.2 4<sup>th</sup>-order 0.05° equiripple linear phase filter parameters

| Filter Section | ω <sub>i</sub> , rad/sec | $Q_{i}$               |

|----------------|--------------------------|-----------------------|

| Biquad 1       | $\omega_1 = 1.007$       | Q <sub>1</sub> =0.573 |

| Biquad 2       | $\omega_2 = 1.599$       | Q <sub>2</sub> =1.148 |

From Tables I.1 and I.2, we can see that for the Bessel-Thomson filter, the biquad section's  $Q_i$ s are smaller, and the  $\omega_i$ s are more closely clustered. However, the group delay for the  $0.05^\circ$  equiripple filter is flat up to  $1.5F_c$  vs.  $1.0F_c$  for the Bessel-Thomson

filter. Also, equiripple filter has a better selectivity than the Bessel-Thomson filter with the same order.

#### 1.5.2 Gain Boosting and Group Delay Shaping

In addition to the basic functions, some times additional magnitude and group delay shaping functions are added to facilitate the detection process (e.g., read channel filters). Magnitude boost is provided within the appropriate frequency band in order to remove the undesired effect of bit shift due to the influence of the neighboring pulse [12]. This pulse slimming must not distort the group delay. Also in order to compensate for the non-uniform group delay of the components, or simply to provide flexibility in detection, the group delay may be modified in some frequency bands.

These additional requirements of magnitude and group delay shaping are provided by modifying the basic linear phase filters, and the overall transfer function H(s) takes the form

$$H(s) = \frac{N(s)}{D(s)} \tag{1}$$

where D(s) corresponds to the basic, classical linear phase filter transfer function, and N(s) is the added polynomial that incorporates the modifications stated above.

The numerator N(s) provides the magnitude and group delay shaping via two transmission zeroes:

$$N(s) = \left(1 + K_1 \frac{s}{\omega_1} - K_2 \frac{s^2}{\omega_1^2}\right) \tag{2}$$

—If  $K_1$ =0, and  $K_2$ >0, then  $N(j\omega)=1+K_2\omega^2/\omega_1^2$ , and it provides magnitude shaping without affecting the group delay response.

—If  $K_1\neq 0$ , and  $K_2=0$ , then  $N(s)=1+K_1s/\omega_1$ , and it provides group delay shaping without affecting the magnitude response significantly.

—If  $K_1$  and  $K_2$  are properly selected, then N(s) might provide two asymmetrical zeroes and it provides both magnitude and group delay shaping. The interaction between the magnitude and group delay is very small—magnitude boost is pronounced at high frequencies around  $\omega_0$  and group delay shaping is more effective at low frequencies. For all practical purposes,  $K_1$  and  $K_2$  are used to independently program group delay and magnitude shaping.

#### 1.6. Group Delay Sensitivity

A second-order low-pass biquadratic transfer function can be written as

$$H(s) = \frac{\omega_0^2}{s^2 + s \cdot \frac{\omega_0}{O} + \omega_0^2}$$

(3)

For real frequencies,  $s=j\omega$ , H(s) can be partitioned into a gain component  $G(\omega)$  and a phase component  $\Theta(\omega)$  as given by

$$H(j\omega) = G(\omega) \cdot e^{j\Theta(\omega)} \tag{4}$$

The gain sensitivities of the biquad to  $\omega_0$  and Q are [13]:

$$S_Q^{G(\omega)} = \left[1 + Q^2 \left(\frac{\omega}{\omega_0} - \frac{\omega_0}{\omega}\right)^2\right]^{-1} \tag{5}$$

$$S_{\omega_0}^{G(\omega)} = S_Q^{G(\omega)} \cdot \left[ 1 + 2Q^2 \left( \frac{\omega^2}{\omega_0^2} - 1 \right) \right]$$

(6)

As shown in [14], the group delay sensitivities to  $\omega_0$  and Q can be expressed as

$$S_O^{\tau(\omega)} = -1 + 2 \cdot S_O^{G(\omega)} \tag{7}$$

$$S_{\omega_0}^{\tau(\omega)} = -3 + \frac{2}{1 + \frac{\omega^2}{\omega_0^2}} + 2 \cdot S_{\omega_0}^{G(\omega)}$$

(8)

For a transfer function composed of N second-order low-pass biquads, the group delay variation can be written as

$$\frac{\Delta \tau}{\tau} = \sum_{i=1}^{N} \left( S_{Q_i}^{\tau_i} \frac{\Delta Q_i}{Q_i} + S_{\omega_i}^{\tau_i} \frac{\Delta \omega_i}{\omega_i} \right) \frac{\tau_i}{\tau}$$

(9)

Expressions (7)-(9) can be used to find the integrator's specifications such as the DC gain and excess.

For the fourth-order equiripple linear phase filter designed in this dissertation, its transfer function is

$$H(s) = \frac{\omega_1^2}{s^2 + s \cdot \frac{\omega_1}{Q_1} + \omega_1^2} \cdot \frac{\omega_2^2}{s^2 + s \cdot \frac{\omega_2}{Q_2} + \omega_2^2}$$

(10)

where  $\omega_1$ =1.0075,  $Q_1$ =0.5734,  $\omega_2$ =1.5987, and  $Q_2$ =1.1481. Figure I.2 and Figure I.3 show the group delay sensitivity functions for the two biquadratic sections. While the group delay sensitivities to both the quality and resonant frequency are less than 1 for the

first biquad, the sensitivity to the resonant frequency for the second biquad is larger than 1. So it is important to minimize the resonant frequency variations to reduce the group delay ripple. In this dissertation, the quality factor  $Q_i$  is implemented as the ratio of two scaled operational transconductance and the resonant frequency  $\omega_i$  is implemented as the ratio of transconductance to capacitance. While the quality factor  $Q_i$  is well controlled by the scaling, the resonant  $\omega_i$  can vary significantly. So an automatic frequency tuning scheme is used to reduce the group delay variations.

Figure I.2 Group delay sensitivities for the first biquad

Figure I.3 Group delay sensitivities for the second biquad

#### 1.7. Low-Voltage Differential Signaling (LVDS) Drivers

The ever-increasing processing speed of microprocessor motherboards, optical transmission links, chip-to-chip communications, etc., is pushing the off-chip data rate into the gigabits-per-second range. While scaled CMOS technologies continue to enhance the on-chip operating speeds, off-chip data rates have gained little benefit from the increased silicon integration. This is primarily due to the excessive power consumption necessary for driving impedance-controlled electrical interconnects, which leads to an increase in the costs related to packaging and thermal management [15].

In the past, off-chip high data rates were achieved by massive parallelism, with the disadvantages of increased complexity, excessive pins needed, and increased cost for the

IC package and the printed circuit board (PCB). So it is beneficial to move the off-chip data rate to the range of Gb/s-per-pin or above. Also reducing the power consumption is critical for battery-powered portable systems as well as some other systems in order to extend the battery life and reduce the cost related to packaging and additional cooling systems.

Scalable Coherent Interface (SCI) is a high-speed packet transmission protocol that efficiently provides the functionality of bus-like transactions (read, write, lock, etc.), but it uses a collection of fast point-to-point links instead of physical buses to reach higher speeds. The initial physical implementations are based on emitter coupled logic (ECL) signal levels [16], which consume more power than is practical in the low-cost workstation environment and are inconvenient for some applications.

Low voltage differential signaling (LVDS) is a standardized data transmission format that is widely used for serial data transmissions [17]. It is a technology developed to provide a low-power and low-voltage alternative to ECL and other high-speed I/O interfaces for point-to-point transmissions. LVDS achieves higher speed and significant power savings by means of a differential scheme for transmission and termination, in conjunction with low voltage swing.

#### 1.8. Main Contributions

A low-voltage, low-power, high performance continuous-time linear phase filter with automatic frequency tuning is designed. The optimal design of a pseudo-differential transconductor using transistors operating in triode region is discussed. A common-mode control circuit that combines CMFB, common-mode feedforward (CMFF), and adaptive-bias has been presented. A large linear signal swing  $(2V_{ppd})$  has been achieved due to the well controlled common-mode (CM) behavior. The ratio of the root mean square value of the ac signal to the power supply voltage is around 31%, which is much better than previous realizations.

Two low-voltage, low-power, and high speed LVDS drivers are designed. The Double Current Sources (DCS) LVDS driver is simple and fast, but the drawback is that its static current consumption is as twice as the minimum required by the voltage swing. The Switchable Current Sources (SCS) LVDS driver, by dynamically switching the current sources, draws minimum static current and reduces the power consumption by 60% compared to the previously reported LVDS drivers. While the previous realizations can not operate properly with low-voltage supplies, both the DCS and SCS LVDS drivers are suitable for low-voltage supply applications. The two LVDS drivers are compliant to the standards and can operate at data rates up to gigabits-per-second.

#### 1.9. Organization

Two low-voltage, low-power integrated circuits used for data communication systems are presented in Chapter II and Chapter III, respectively. In each chapter, the background and motivations for each design are introduced first. Following the discussion of the current status of the research on those topics, the new ideas and the circuit designs are presented. The difference among these designs and the previously reported works are pointed out and emphasized. The detailed design issues associated with these designs are also discussed. Some of the simulation results and the silicon experimental results are included to verify the new ideas and designs. Specifically, Chapter II discusses a low-voltage, low-power, high performance continuous-time linear phase filter with automatic frequency tuning. The filter can be used for wired communication systems such as 1000Base-T and hard disk driver systems. Chapter III presents a low-voltage, low-power differential signaling (LVDS) driver, which is used for point-to-point links such as chip-to-chip communications. Finally, Chapter IV draws some conclusions and summarizes the main contributions of this research work.

#### **CHAPTER II**

# A $2V_{pp}$ , 80-200MHZ FOURTH-ORDER CONTINUOUS-TIME LINEAR PHASE FILTER WITH AUTOMATIC FREQUENCY TUNING

#### 2.1. Background and Motivation

The growing demand of portable electronic equipment and system-on-a-chip has been pushing the industry to design efficient circuits for low power supply voltages and low power consumption. In analog/mixed signal processing, fully differential structures are often used due to their better dynamic range (larger signal swing, better distortion performance, and better common-mode noise and supply noise rejection) over single-ended structures. For applications of low power supply voltages and large signal swings, pseudo-differential structures become attractive since they avoid the voltage drop across the tail current source. But inherently pseudo-differential structures have the same low frequency transconductance for both differential and common-mode signals. Therefore, the use of pseudo-differential structures requires a careful and efficient control over the common-mode behavior of the circuits.

Continuous efforts have been made to control the common-mode (CM) behavior of pseudo-differential architectures [18-22]. The common-mode control circuit should not only stabilize the OTA output common-mode voltage, but also reject the input common-mode signals and supply noises. So usually it is not enough to control the CM behavior

of pseudo-differential architectures by using a common-mode feedback (CMFB) only. We also need a common-mode feedforward (CMFF) to suppress CM signals. For tunable filters and other differential systems, an adaptive mechanism is also needed to control the CM behavior over the tuning range. In the standalone CMFF scheme [19], the CM current is partially cancelled at the output stage of the transconductor, but the CM voltage at the output nodes is not always properly controlled. In [20], the authors use a fully-balanced (FB) architecture based on single-ended blocks to suppress the CM components. The efficiency of this approach depends on good matching between two single-ended transconductors which is usually difficult to satisfy, especially for high frequency applications. Both CMFB and CMFF were used in [21]. The cancellation of the CM components relies on good matching among the triode transistors in the Gm cell, CMFB, and CMFF. It also relies on good matching among several transistors (the current sources and the current mirrors). In [22], an adaptive-bias mechanism to improve the stability of the CM voltage over the tuning range is proposed; its efficiency depends on the performance of the CMFB only.

In a 1000Base-T receiver, a continuous-time low-pass filter is needed to limit the signal and noise bandwidth and provide anti-aliasing prior to sampling. The main specifications of this filter for the original project are:

- The THD must be less than –40dB for a 2V<sub>ppd</sub> input signal;

- The bandwidth of the filter is tunable from 45MHz to 105MHz;

- Single 1.8V supply;

- The process is 0.18µm CMOS.

The most challenging specification is the large linear signal swing. Since we do not have access to the 0.18µm CMOS process, we used 0.35µm CMOS process and a single 2.3V supply. Later on, we also modified the bandwidth requirements to that the tunable range of the filter is from 80MHz to 200MHz, with a nominal bandwidth of 150MHz in order that this filter can also be used for other higher speed applications. This filter can also be used for hard-disk read channel systems.

#### 2.2. Pseudo-differential OTAs and Their Characteristics

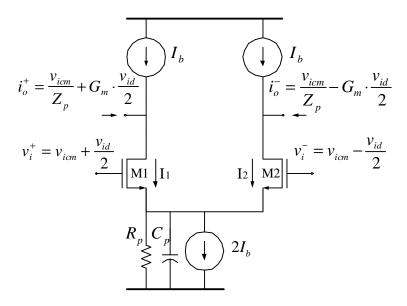

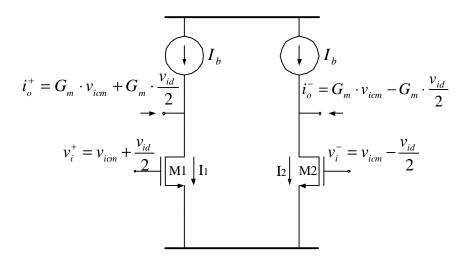

The topology of a generic fully-differential transconductor is shown in Figure II.1a [19]. While M1 and M2 are shown as simple NMOS transistors here, they can represent arbitrary unilateral active devices with transconductance of G<sub>m</sub>. The input signal can be expressed as

$$v_i^+ = v_{icm} + \frac{v_{id}}{2} {1a}$$

$$v_{i}^{-} = v_{icm} - \frac{v_{id}}{2} \tag{1b}$$

where  $\nu_{icm}$  is the input common-mode signal, and  $\nu_{id}$  is the input differential signal. In the fully-differential configuration, the rejection of the common-mode signal is achieved by the large output impedance  $Z_p$  ( $Z_p = R_p || C_p$ ) of the tail current source, especially at relatively low frequencies.

Figure II.1a Fully-differential structure

Figure II.1b Pseudo-differential structure

At lower supply voltages, a pseudo-differential architecture, Figure II.1b, could be used to avoid the voltage drop across the tail current source. This solution usually

achieves a larger signal swing, but it requires to carefully control its response to common-mode signals. Actually, for this circuit, the transconductance for the input common-mode signal is exactly equal to that for the differential input signal.

Besides the large common-mode gain, we also need to consider another important characteristics for transconductors: linearity.

The pseudo-differential transconductor shown in Figure II.1b can be seen as a combination of two parallel single-ended branches. If we consider the non-linear voltage-to-current conversion, the drain currents of transistors M1 and M2 (I<sub>1</sub> and I<sub>2</sub>) can be generally expressed as

$$I_{1} = I_{b} + \alpha_{1}(v_{i}^{+}) + \alpha_{2}(v_{i}^{+})^{2} + \alpha_{3}(v_{i}^{+})^{3}$$

(2a)

$$I_1 = I_b + \alpha_1(v_i^-) + \alpha_2(v_i^-)^2 + \alpha_3(v_i^-)^3$$

(2b)

where  $I_b$  is the bias current, and  $v_i^+$  and  $v_i^-$  are the input signals as expressed in equations (1a) and (1b).  $\alpha_1$ ,  $\alpha_2$ , and  $\alpha_3$  are the coefficients of the polynomial, where  $\alpha_2$  and  $\alpha_3$  are used to represent the OTA non-linearitiesy. Notice that higher order harmonics (greater than third-order) are neglected here.

The output differential current  $(i_{o,PD})$  for the pseudo-differential structures can then be calculated as

$$i_{o,PD} = \alpha_1 v_{id} + 2\alpha_2 v_{id} v_{icm} + \alpha_3 (3v_{id} v_{icm}^2 + v_{id}^2 / 4)$$

(3a)

If the same expression is derived for the fully-differential structure ( $I_1+I_2=$  constant), the output differential current ( $i_{o,FD}$ ) is

$$i_{o,FD} = \alpha_1 v_{id} - \left(\frac{\alpha_2^2}{\alpha_1} - \frac{\alpha_3}{4}\right) v_{id}^3$$

(3b)

Comparing the expressions for the two output differential currents, we have the following observations:

• The pseudo-differential structure presents additional distortion terms which arises from the common-mode signal. In particular, even-order terms can appear in a perfectly symmetrical structure due to the product of the differential and common-mode signals (which is not the case for fully-differential structures).

To minimize the importance of this effect, when using a pseudo-differential structure, the transconductance must be designed to be as linear as possible. Also the common-mode signal must be minimized, i.e., a strong and efficient common-mode control circuit is needed for pseudo-differential structures. As a consequence, the combination of common-mode feedforward (CMFF) and common-mode feedback (CMFB) is essential for high performance systems based on pseudo-differential structures.

# 2.3. Common-Mode Control Techniques for Pseudo-Differential OTAs

#### 2.3.1 Pseudo-Differential OTAs with Common-Mode Feedforward

As discussed in section 2.2., strong and efficient common-mode control circuits are needed for high performance systems based on pseudo-differential structures. A common-mode feedforward scheme was first proposed in [19]. Its basic idea is to use

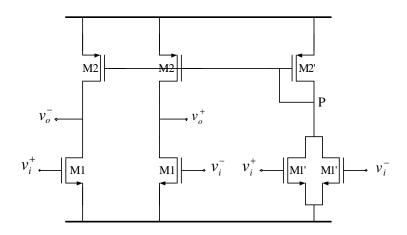

some transconductor to detect the input common-mode signal, convert it into current, mirror the current to the main transconductor, and partially cancel the input common-mode signal. The configuration of the idea with simple CMOS implementation is shown in Figure II.2.

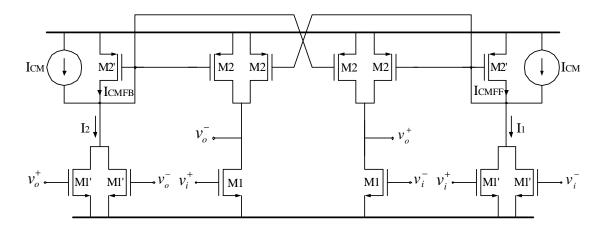

Figure II.2 Common-mode feedforward scheme

Transistors M1 and M2 are the core of the transconductor. Transistors M1' have the half dimensions as M1 and they are used to detect the input common-mode signal and convert it into common-mode current. This current flows through transistor M2' and it is mirrored into the main transconductor. This current cancels the common-mode current generated by transistors M1 and reduces the common-mode gain. In particular, the current flowing into the output nodes of the transconductor can be expressed as

$$i_{ocm} = g_{m1}v_{icm} - g_{m1}v_{icm} \cdot \frac{g_{m2}}{g_{m2} + g_{o1} + g_{o2} + sC_p}$$

$$= v_{icm} \cdot \frac{g_{m1}(g_{o1} + g_{o2} + sC_p)}{g_{m2} + g_{o1} + g_{o2} + sC_p}$$

(4)

where  $C_p$  is the parasitic capacitance associated with the mirroring node P. The common-mode gain is

$$A_{CM} \equiv \frac{v_{ocm}}{v_{icm}} = \frac{g_{m1}(g_{o1} + g_{o2} + sC_p)}{g_{m2} + g_{o1} + g_{o2} + sC_p} \cdot \frac{1}{g_{o1} + g_{o2}}$$

(5)

At DC, it can be seen from (4) that the output common-mode current  $i_{\text{ocm}}$  is non-zero, which is caused by the finite output transconductance of the transistors. The DC common-mode gain is approximated by

$$A_{CM}(0) = \frac{g_{m1}}{g_{m2} + g_{o1} + g_{o2}} \approx 1 \tag{6}$$

Equation (6) says that the common-mode feedforward reduces the low frequency common-mode gain to approximately 1. At very high frequencies, the common-mode gain is approximated by

$$A_{CM}(\infty) = \frac{g_{m1}}{g_{o1} + g_{o2}} >> 1 \tag{7}$$

which means that the CMFF does not work well at very high frequencies. At high frequencies, the mirroring node P is AC grounded and the common-mode feedforward path is disabled.

While the CMFF scheme reduces the common-mode gain, it does not set the output common-mode voltage. Lossy-integrators can be used to control the output commonmode voltages. In fact, a pseudo-differential transconductor closed in negative feedback creates a low impedance node for both the differential and common-mode signals. Also CMFF schemes add loads to the driving stages.

# 2.3.2 Fully-Balanced Transconductor Based on Single-Ended OTAs

Figure II.3 shows a balanced transconductor [23] based on two singled-ended (SE) OTAs. For each of the SE OTA, its common-mode gain is also given by equation (5). The SE OTA subtracts the common-mode components from M1 and cancels them out at the output, while it sums the differential-mode component at the output. Therefore, SE transconductor inherently has a small common-mode gain and a large differential gain.

Figure II.3 Balanced transconductor based on single-ended OTAs

In the balanced transconductor based on SE OTAs, the output common-mode voltage is not defined and it depends on the input common-mode signal (common-mode gain is 1 at low frequencies). So a common-mode feedback is necessary to fix the proper operating point. Since the common-mode gain is small (approximately 1), the CMFB

circuit does not require a wide bandwidth; therefore, the CMFB circuit does not consume much power.

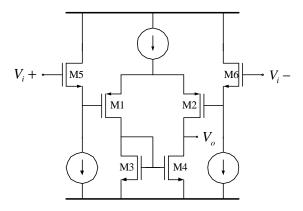

A fully balanced CMOS transconductor was proposed in [20]. The conceptual implementation is shown in Figure II.4. This fully-balanced transconductor uses two single-ended transconductors with same transconductance. Besides taking advantage of the small common-mode gain of SE transconductors, this fully-balanced configuration also includes the function of common-mode feedback. Specifically, the current corresponding to the common-mode output voltage (CM current) is produced by adding each current corresponding to each output voltage. Then, the CM current is compared with the current corresponding to the output common-mode reference voltage V<sub>cm</sub>, and the difference is fed to both the plus and minus outputs. The current-mode addition and subtraction are realized by current mirrors. The multi-inputs can be realized by connecting transistors in parallel to input transistors.

Figure II.4 Fully-balanced configuration using two multi-inputs single-ended transconductors

Although fully-balanced architectures include the functions of both CMFF and CMFB, they need good matching between the two single-ended transconductors, which is not easy to achieve, especially for high frequency systems.

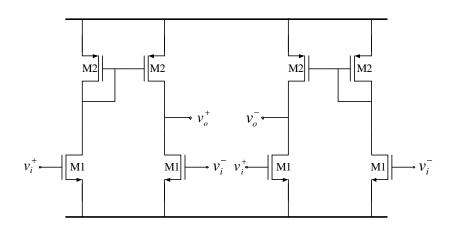

## 2.3.3 Common-Mode Control Circuit Using Both CMFF and CMFB

As reported in [21], a common-mode control circuit based on CMFF scheme combines CMFF and CMFB. A simplified CMOS version is used here for explanation. The transconductor with the CM control is shown in Figure II.5. Transistors M1 and M2 compose the main transconductor. The right most part of the transconductor is the CMFF circuit, while the left most part of the main transconductor is the CMFB circuit. An assumption is made here that transistors M1 and M1' are working in triode region. Transistors M1' have the half dimensions as M1. The CMFF used here is very similar to the one shown in Figure II.2, except that a common-mode reference current I<sub>CM</sub> is added. The left side CMFB is the same as the CMFF, with the exception that the gates of transistors M1' are connected to the outputs of the main transconductor.

Figure II.5 Pseudo-differential transconductor with CMFF and CMFB

The common-mode reference current I<sub>CM</sub> shown in Figure II.5 is defined as follows

$$I_{CM} = \frac{\beta}{2} \left[ V_{CM} - V_T - \frac{1}{2} V_{DS} \right] V_{DS}$$

(8)

where  $V_{CM}$  is the reference common-mode voltage and it is generated by a bias circuit. The currents  $I_1$  and  $I_2$  generated by the CMFF and CMFB circuits can be expressed as

$$I_{1} = I_{CMFF} + I_{CM} = \beta \left[ V_{icm} - V_{T} - \frac{1}{2} V_{DS} \right] V_{DS}$$

(9)

$$I_{2} = I_{CMFB} + I_{CM} = \beta \left[ V_{ocm} - V_{T} - \frac{1}{2} V_{DS} \right] V_{DS}$$

(10)

Currents  $I_{\text{CMFF}}$  and  $I_{\text{CMFB}}$  generated respectively by the CMFF and CMFB are fed back into the main transconductor via two PMOS devices, resulting the following bias current

$$I_{B} = I_{CMFF} + I_{CMFB}$$

$$= \beta \left[ V_{icm} - V_{T} - \frac{1}{2} V_{DS} \right] V_{DS} + \beta V_{DS} \left( V_{ocm} - V_{CM} \right)$$

(11)

where the first term corresponds to the current required to reject the input CM signal and the second term corresponds to the current used to set the transconductor output CM voltage  $V_{\text{ocm}}$  to CM reference voltage  $V_{\text{CM}}$ .

The advantage of this CM control scheme is that it combines the CMFF and CMFB together. The disadvantages are that the CMFF and CMFB are correlated (both use  $I_{CM}$ , both use the same transistors as the input transistors, etc.); It needs good match among many components (M1 and M1', M2 and M2', two  $I_{CM}$ ), which is difficult to satisfy, especially for high frequency systems. The CMFB gain is fixed by the input transistors M1' and their transconductance is relatively small since they are working in triode region. Also, the CM reference current  $I_{CM}$  needs to be generated.

### 2.3.4 Adaptive Biasing for Tunable Transconductors

For tunable transconductors, it is desirable to control the output common-mode voltage to a fixed value over the whole tuning range in order not to degrade the transconductor's dynamic range. This issue becomes more critical for low-voltage applications, since the voltage swings are inherently constrained to small headroom voltages.

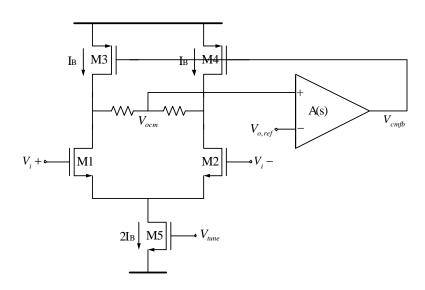

Figure II.6 shows a typical tunable transconductor with CMFB. Assume that under nominal conditions, the tail current source M5 sinks  $2I_B$ , the PMOS active load M3(M4) sources  $I_B$ . Also assume that the output common-mode voltage  $V_{ocm}$  equals the output CM reference voltage  $V_{o,ref}$ , and the common-mode control voltage is  $V_{cmfb}$ . Suppose during tuning, the tail current source M5 needs to sink  $2(I_B+\Delta I_B)$ . Then the top active load M3(M4) needs to source  $I_B+\Delta I_B$ , and the CMFB control voltage can be denoted as

$V_{cmfb}$ + $\Delta V_{cmfb}$ . Since the amplifier's gain is finite, the output CM voltage  $V_{ocm}$  is no longer equal to  $V_{o,ref}$ , i.e., the tuning forces the output CM voltage  $V_{ocm}$  to deviate from the CM reference voltage  $V_{o,ref}$ .

Figure II.6 Tunable transconductor with CMFB

An adaptive CMFB is proposed in [22]. This adaptive CMFB eliminates meaningful deviations of the CM voltage over transconductance tuning by delivering to the transconductor load an adaptive current. The adaptive current is produced by a tuning voltage dependent bias generator and it is mirrored to the tail current of the CMFB. The CMFB adjusts the transconductor active load current so that the output common-mode voltage remains the same over the tuning range. The pseudo-differential transconductor adopted in that paper uses only CMFB to control its CM behavior. So the CM control efficiency dependent on the CMFB only.

#### 2.4. Pseudo-Differential Transconductor

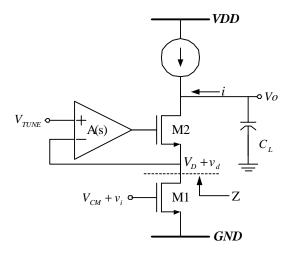

From section 2.1, it can be seen that the most challenging specification of the filter is the very large linear signal swing. It is well known that a transistor working in triode region has a linear transconductance if its drain-source voltage is constant. Using the simple MOS transistor model, the drain current of a NMOS transistor working in triode region can be expressed as

$$i_D = \beta [(v_{GS} - V_{TN})v_{DS} - \frac{1}{2}v_{DS}^2]$$

(12)

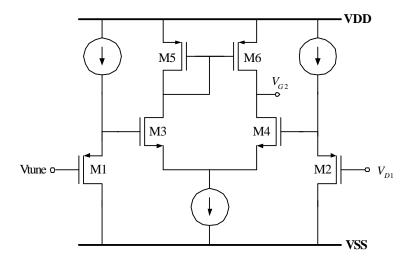

where  $\beta = \mu_n C_{ox}(W/L)$  and  $V_{TN}$  are the transconductance parameter and the threshold voltage, respectively. Assuming the drain-source voltage  $v_{DS}$  is constant, then the transistor has a linear transconductance and it is given by  $\beta v_{DS}$ . Also as discussed in section 1.3, a pseudo-differential OTA achieves larger signal swings than a fully-differential OTA by removing the tail current source. So a pseudo-differential OTA based on transistors operating in triode region is used for the filter design and it is shown in Figure II.7 [24]. Transistors M1 operate in triode region and they convert the voltage into current in a linear fashion. Transistors M2 and amplifier amp form a regulated-gain-control (RGC) loop and they are used to fix the drain voltage of M1. M3 and M4 are the cascoded active load of the OTA. M2, M3, and M4 are working in saturation region. The tuning voltage  $V_{TUNE}$  is used to adjust the OTA's transconductance. Assuming the amplifier amp is ideal and its gain is infinite, then we have both a constant drain-source voltage  $v_{DS1}$ = $V_{TUNE}$  independent of the input voltage level, and a linear transconductance given by  $\beta V_{TUNE}$ .

Figure II.7 Pseudo-differential OTA

In order to get the best OTA linearity performance, there are several design issues need to be addressed properly. First, we need to determine the common-mode voltage properly to maximize the linear range. Second, we need to optimize the design of the RGC amplifier amp so that M1's drain voltage is fixed well and its transconductance is linear, even at high frequencies. Also we need investigate the short channel effects of the input transistors M1 to have a good trade off between linearity performance and frequency response.

# 2.4.1 Optimizing the Linear Range

Let's consider a single branch and determine the CM voltage  $V_{CM}$  that maximizes the OTA linear input range. Assume that the power supply is  $V_{DD}$ . Let us denote the gate

voltage of M2 by  $V_{G2}$ , the gate voltage of M1 by  $V_{CM}$ - $\nu_i$ , and the output voltage by  $V_{CM}$ + $\nu_o$ , where  $V_{CM}$  is the CM reference voltage, where  $\nu_i$  and  $\nu_o$  are the input and output AC signals, respectively.

Since transistor M1 must operate in triode region for better linearity, then

$$V_{CM} - V_{i,\text{max}} - V_{TN} > V_{TUNE} \tag{13}$$

where  $v_{i,max}$  is the maximum amplitude of the input signal.

Also, transistor M3 must operate in saturation region, then

$$V_{CM} + v_{o,\text{max}} < V_{BIAS} + \left| V_{TP} \right| \tag{14}$$

where  $v_{o,max}$  is the maximum amplitude of the output signal.

In order to maximize the signal swing, we need to select the bias voltage  $V_{BIAS}$  such that the source-drain voltage of M4 is a bit larger than  $|V_{DSAT4}|$ . Assume we also have to support  $V_{DSAT3}(=V_{DSAT4})$  for the source-drain voltage of M3, then equation (14) yields:

$$V_{CM} + v_{o,\text{max}} < V_{DD} - 2|V_{DSAT4}| \tag{15}$$

From the filter transfer function (which will be discussed in section 2.6.), it can be seen that the signal swing at all of the filter's nodes are always equal or less than the input signal swing. So we can assume that the OTA's maximum input signal equals the maximum output signal; i.e.  $v_{i,max}=v_{o,max}$ . According to (13) and (15), the maximum input signal can be obtained as:

$$v_{i,\text{max}} = \frac{1}{2} (V_{DD} - V_{TN} - V_{TUNE}) - |V_{DSAT4}|$$

(16)

where  $V_{\text{TUNE}}$  is obtained from the required filter bandwidth and the transconductance of the OTA.

As a result of this, the common-mode voltage that maximizes the linear signal range is given by:

$$V_{CM} = V_{DD} - v_{i,\text{max}} - 2|V_{DSAT4}| \tag{17}$$

For a supply voltage of 2.3V, a threshold voltage  $V_{TN}$  of 0.6V, an overdriving voltage  $V_{DSAT}$  of 0.2V, and a tuning voltage  $V_{TUNE}$  of 0.2V, the maximum input voltage  $v_{i,max}$  is 0.55V and the common-mode voltage  $v_{CM}$  which maximizes the linear signal swing is 1.35V.

## 2.4.2 Regulated Gain Control (RGC) Loop

The design of the RGC loop is critical for the OTA's linearity performance. One of the main sources of OTA's non-linearity is the low gain of the RGC loop at high frequencies, since smaller RGC loop gain leads to larger  $\nu_{DS1}$  variations, leading to larger harmonic distortion components. Figure II.8 is a simplified configuration used to evaluate the OTA performance. Capacitor  $C_L$  has a large capacitance, and it grounds the output for AC signals.

Figure II.8 Configuration for evaluating OTA transconductance

According to equation (12), and neglecting the second-order term  $v_d^2/2$ , it can be shown that the AC current across the capacitor  $C_L$  can be expressed as:

$$i \cong \beta [V_D v_i + v_d v_i + (V_{CM} - V_{TN}) v_d - V_D v_d]$$

(18)

Using typical small signal analysis, the impedance looking into the RGC from the drain of M1 is approximated by an impedance  $Z\cong 1/((A(s)+1)g_{m2})$ , where A(s) is the gain of the RGC amplifier. Using  $v_d\cong -iZ$ , equation (18) leads to:

$$i = \frac{V_D v_i}{1/\beta + Z[(V_{CM} - V_{TN}) - V_D] + Zv_i}$$

(19)

And using Taylor series expansion with respect to  $\nu_{i}$ , then we have:

$$i = \alpha_1 v_i + \alpha_2 v_i^2 + \alpha_3 v_i^3 + \cdots$$

(20)

where  $\alpha_1 = \frac{\beta V_D}{1 + \beta Z (V_{CM} - V_{TN} - V_D)}$ ,

$$\alpha_{2} = \frac{\beta^{2} Z V_{D}}{\left[1 + \beta Z (V_{CM} - V_{TN} - V_{D})\right]^{2}},$$

$$\alpha_{3} = \frac{\beta^{3} Z^{2} V_{D}}{\left[1 + \beta Z (V_{CM} - V_{TN} - V_{D})\right]^{3}}, \dots$$

Neglecting the higher order terms, the third-order harmonic distortion can be expressed as:

$$HD3 \cong \frac{V_i^2}{4} \cdot \frac{\beta^2 Z^2}{[1 + \beta Z(V_{CM} - V_{TN} - V_D)]^2}$$

$$= \frac{V_i^2}{4} \cdot \frac{\beta^2}{[(A(s) + 1)g_{m2} + \beta(V_{CM} - V_{TN} - V_D)]^2}$$

(21)

where  $V_i$  is the magnitude of the input signal, and A(s) is the RGC amplifier gain. The above expression shows the relationship between  $(A(s)+1)g_{m2}$  and the third-order harmonic distortion. Figure II.9 shows the OTA's THD simulation results and the theoretical HD3 predicted by (21). When the amplifier's gain is small (e.g., A(s)<6), the OTA's THD is dominated by  $(A(s)+1)g_{m2}$  and the theoretical values are close to the simulated ones; but with large amplifier's gain, the OTA's THD is limited by the short-channel effects (which will be discussed in the next section). It can be seen that in order to achieve THD figures around -50dB, the RGC amplifier's gain should be greater than 10V/V over the whole passband of the filter. Note that the non-zero impedance Z causes OTA transconductance reduction, which is clear from the expression of  $\alpha_1$ .

Figure II.9 OTA's THD vs. RGC amplifier's gain (L<sub>M1</sub>=0.6µm)

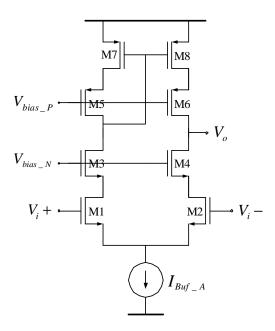

Another important issue is the RGC loop stability, which has been already discussed in [25]. The implementation of the RGC amplifier is shown in Figure II.10. It is composed of a single-ended amplifier and two source followers. The source follower M2 shifts up M1's drain voltage  $\nu_{DS1}$ , giving more room to the OTA's input stage and increasing the transconductance tuning range. The reason that we use two source followers is that we can have a clear idea about M1's drain voltage during the testing. The designed amplifier amp has a low-frequency gain of 31dB, a unity-gain frequency of 1.25GHz with a phase margin of  $68^{\circ}$ , and a current consumption is  $540\mu A$ .

Figure II.10 RGC amplifier

#### **2.4.3 Short-Channel Effects**

Short-channel effects affect the OTA's linearity as well. For short channel devices, the effective carrier mobility ( $\mu_{eff}$ ) is a function of both lateral and vertical electric fields [26], and it can be expressed as:

$$\mu_{eff} = \mu_0 \cdot \frac{1}{1 + \theta (V_{GS} + v_{gs} - V_T)} \cdot \frac{1}{1 + \frac{1}{LE_c} (V_{DS} + v_{ds})}$$

(22)

where  $\mu_0$  is the low electric field mobility,  $E_c$  is the critical electric field, and  $\theta$  is a fitting parameter which is inversely proportional to the oxide thickness.

From equations (12) and (22), if the lateral electric field effect is fixed by the RGC loop, which fixes the drain-source voltage  $v_{DS}$ , the effective carrier mobility  $\mu_{eff}$  should be independent of transistor length L, and so the OTA's linearity should be independent of the transistor length L.

In fact, according to higher order models [27], the above expression is only a simplified approximation for the drain-source current equation used by the Spice model. It can not predict the OTA's linearity versus the transistor length.

In [27], a more complex drain-source current model is used, and it is expressed as

$$I_{DS} = \frac{I_{DS,0}}{1 + \frac{R_{DS}I_{DS,0}}{V_{DS,eff}}} \left(1 + \frac{V_{DS} - V_{DS,eff}}{V_{A}}\right) \cdot \left(1 + \frac{V_{DS} - V_{DS,eff}}{V_{A,SCBE}}\right)$$

(23)

where

$$I_{DS,0} = \frac{W_{eff} u_{eff} C_{ox} V_{GST,eff}}{L_{eff} \left[ 1 + V_{DS,eff} / \left( \varepsilon_{sat} L_{eff} \right) \right]} \left[ 1 - \frac{A_{bulk} V_{DS,eff}}{2 \left( V_{GST,eff} + 2kT / q \right)} \right] V_{DS,eff}$$

(24)

$$V_{GST,eff} = \frac{2nkT/q \ln \left[ 1 + \exp\left(\frac{V_{GS,eff} - V_{T}}{2nkT/q}\right) \right]}{1 + 2n\frac{C_{ox}}{C_{dep,0}'} \exp\left(-\frac{V_{GS,eff} - V_{T} - 2 \cdot VOFF}{2nkT/q}\right)}$$

(25)

$$V_{GS,eff} = V_{GS} - V_{poly,eff} \tag{26}$$

$$V_{poly,eff} = 1.12 - \frac{1}{2} \left( 1.12 - V_{poly} - \delta + \sqrt{(1.12 - V_{poly} - \delta)^2 + 4 \cdot \delta \cdot 1.12} \right)$$

(27)

$$V_{poly} = \frac{q \in {}_{s} NGATEC_{ox}^{'2} \cdot 10^{6}}{2} \left[ \sqrt{1 + \frac{2(V_{GS} - V_{FB} - 2\phi_{f})}{q \in {}_{s} NGATEC_{ox}^{'2} \cdot 10^{6}}} - 1 \right]^{2}$$

(28)

$$V_{T} = V_{TH0} + \delta_{NP} (\Delta V_{T,body\_effect} - \Delta V_{T,ch\arg e\_sharing} - \Delta V_{T,DIBL} + \Delta V_{T,reverse\_short\_channel} + \Delta V_{T,narrow\_width} + \Delta V_{T,small\_size})$$

(29)

$$\Delta V_{T,ch\,\mathrm{arg}\,e}$$

sharing =  $DVTO$ .

$$\left[\exp\left(-DVT1\frac{L_{eff}}{2L_{t}}\right) + 2\exp\left(-DVT1\frac{L_{eff}}{L_{t}}\right)\right]\left(V_{bi} - 2\phi_{f}\right)$$

(30)

$\Delta V_{\scriptscriptstyle T, small\_size} = DVT0W \cdot \\$

$$\left[\exp\left(-DVT1W\frac{W_{eff}L_{eff}}{2L_{tw}}\right) + 2\exp\left(-DVT1W\frac{W_{eff}L_{eff}}{L_{tw}}\right)\right]\left(V_{bi} - 2\phi_f\right)$$

(31)

It can be seen that  $V_{GST,eff}$  is a function of  $V_{GS,eff}$  and  $V_T$ ; where  $V_T$  is a nonlinear function of  $L_{eff}$ . Also,  $V_{DS,eff}$ ,  $R_{DS}$ ,  $A_{bulk}$ ,  $V_A$ , etc., all depend on  $V_{GST,eff}$ .

So it is too complicated to get a simple expression for the OTA linearity as function of the transistor length. So it is realistic here to refer to the simulation results.

In order to see the transistor length's effect on the OTA's linearity, we assume that the RGC amplifier has an infinite gain and we keep W/L constant for the input transistors M1. The simulation results for the OTA's THD versus the input transistor's length L are shown in Figure II.11 and they are summarized in Table II.1.

Figure II.11 OTA's THD vs. input transistor M1's length L

Table II.1 OTA's THD vs. input transistor length L ( $V_{in} = 2V_{ppd}$ )

| Transistor Length L (μm) | 0.4   | 0.6   | 0.8   | 1.0   |

|--------------------------|-------|-------|-------|-------|

| OTA's THD (dB)           | -50.6 | -54.3 | -58.2 | -60.2 |

So we choose a transistor length of 0.6µm so that the OTA's THD is about -50dB with the actual RGC amplifier, in order to meet the filter's linearity specifications.

All of the issues discussed above have been considered in the OTA's design. The OTA has a low frequency gain of 31dB and an excess phase of –4.6° at a unity-gain frequency of 150MHz. The OTA transistor dimensions and bias currents are summarized in Table II.2.

| Transistor            | M1     | M2     | M3      | M4      | M5     | M6     | M7     |

|-----------------------|--------|--------|---------|---------|--------|--------|--------|

| W/L(μm/μm)            | 40/0.6 | 48/0.4 | 240/0.4 | 320/0.4 | 36/0.4 | 36/0.6 | 24/0.6 |

| $I_{\text{bias}}(mA)$ | 1.08   | 1.08   | 1.08    | 1.08    | 0.18   | 0.18   | 0.18   |

Table II.2 OTA transistor dimensions and bias conditions

#### 2.5. Common-Mode Control Circuits

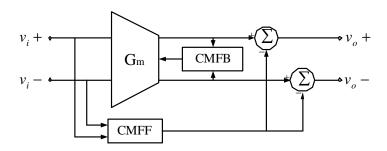

The OTA shown in Figure II.7 requires a proper common-mode control system. It should not only stabilize the OTA output CM voltage, but also reject the input CM signals and supply noise. So the combination of a CMFB and a CMFF for the CM control is essential for high performance systems with pseudo-differential architectures. Due to the benefits of the CMFF, the loop gain and bandwidth requirements of the CMFB can be relaxed. Conventional CM control circuits for pseudo-differential structures with CMFB and/or CMFF are shown in Figure II.12a. In order to simplify the design of pseudo-differential architectures, it is more efficient to have a CM control circuit that combines CMFB and CMFF together as shown in Figure II.12b. A CM control system with this feature is used here.

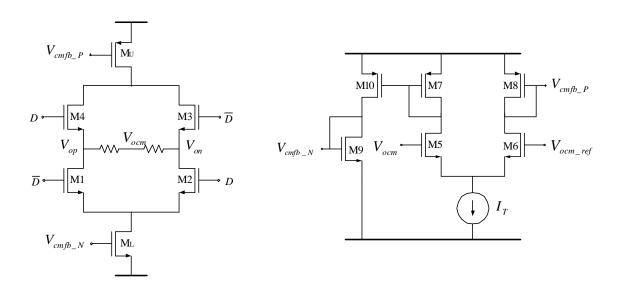

Figure II.12a Conventional CM control using separate CMFB and CMFF

Figure II.12b Proposed CM control that combines CMFB and CMFF

# 2.5.1 Common-Mode Control Principle

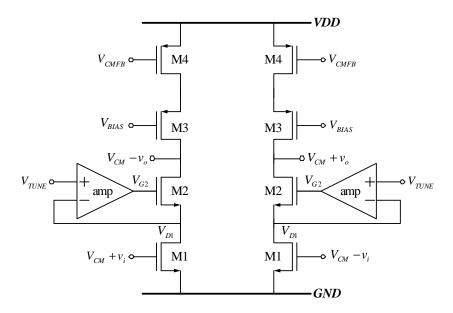

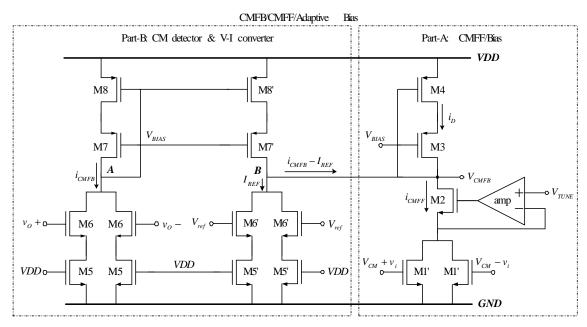

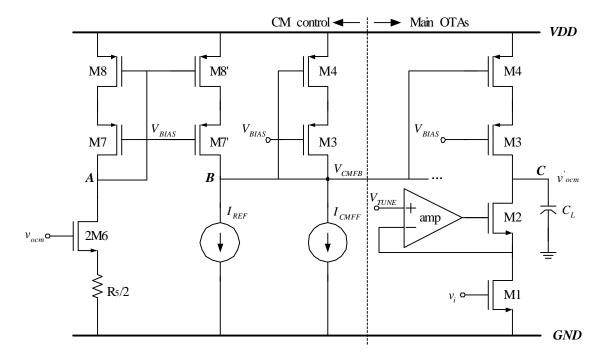

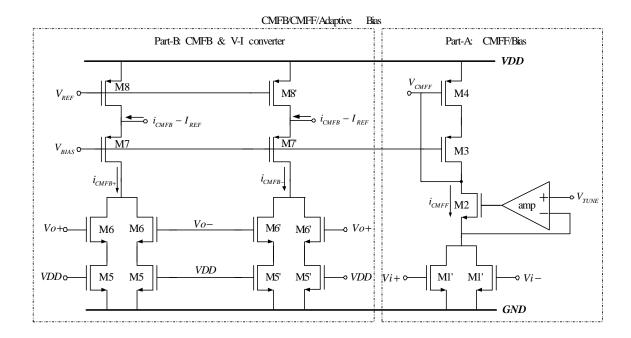

The basic idea of the proposed CM control circuit is that the circuit senses the input CM information as well as the output CM information, then it combines both signals together to control the OTA's CM behavior. The implementation of the CM control is shown in Figure II.13.

Figure II.13 Common-mode control circuit

The CM control circuit contains two parts. *Part-A* is a CMFF and an adaptive bias circuit. *Part-B* is a CM detector and V-I converter. The combination of the two parts functions as a CMFB, a CMFF, and an adaptive-bias scheme. In *Part-A*, the CMFF/Bias is a replica of a single branch of the OTA except that the dimensions of M1' are one half of the main OTA's input transistor (M1 in Figure II.7). Transistors M1' are connected to the inputs of the OTA and they are used to cancel the CM input signal. The CMFF current is:

$$i_{CMFF} = I_{CMFF} + 2g_{m1}^{'} v_{icm} = I_{CMFF} + g_{m1} v_{icm}$$

(32)