# EQUALIZATION ARCHITECTURES FOR HIGH SPEED ADC-BASED SERIAL I/O RECEIVERS

#### A Dissertation

by

#### AYMAN OSAMA AMIN MOHAMED SHAFIK

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Chair of Committee, Samuel Palermo Committee Members, Jose Silva-Martinez

Jean-Francois Chamberland-Tremblay

Mahmoud El-Halwagi

Head of Department, Miroslav M. Begovic

May 2016

Major Subject: Electrical Engineering

Copyright 2016 Ayman Osama Amin Mohamed Shafik

#### ABSTRACT

The growth in worldwide network traffic due to the rise of cloud computing and wireless video consumption has required servers and routers to support increased serial I/O data rates over legacy channels with significant frequency-dependent attenuation. For these high-loss channel applications, ADC-based high-speed links are being considered due to their ability to enable powerful digital signal processing (DSP) algorithms for equalization and symbol detection. Relative to mixed-signal equalizers, digital implementations offer robustness to process, voltage and temperature (PVT) variations, are easier to re-configure, and can leverage CMOS technology scaling in a straight-forward manner. Despite these advantages, ADC-based receivers are generally more complex and have higher power consumption relative to mixed-signal receivers. The ensuing digital equalization can also consume a significant amount of power which is comparable to the ADC contribution. Novel techniques to reduce complexity and improve power efficiency, both for the ADC and the subsequent digital equalization, are necessary.

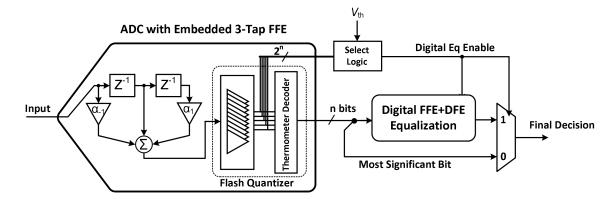

This dissertation presents efficient modeling and implementation approaches for ADC-based serial I/O receivers. A statistical modeling framework is developed, which is able to capture ADC related errors, including quantization noise, INL/DNL errors and time interleaving mismatch errors. A novel 10GS/s hybrid ADC-based receiver, which combines both embedded and digital equalization, is then presented. Leveraging a time-interleaved asynchronous successive approximation ADC architecture, a new structure for 3-tap embedded FFE inside the ADC with low power/area overhead is used. In addition, a dynamically-enabled digital 4-tap FFE + 3-tap DFE equalizer architecture is introduced, which uses reliable symbol detection to

achieve remarkable savings in the digital equalization power. Measurement results over several FR4 channels verify the accuracy of the modeling approach and the effectiveness of the proposed receiver. The comparison of the fabricated prototype against state-of-the-art ADC-based receivers shows the ability of the proposed architecture to compensate for the highest loss channel, while achieving the best power efficiency among other works.

To My Mom and Dad,

who taught me most of what I know,

and showed me the way to learn the rest.

To My wife Basma,

the joy of my life,

and my two little angels, Omar and Malik.

#### ACKNOWLEDGEMENTS

All praise is due to ALLAH, lord of the heavens and the earth, who taught by the pen, taught man that which he knew not.

It was a long and hard journey. From the time I left my home town more than six years ago, reaching towards the unknown. During this journey, I was blessed to meet so many wonderful people, from whom I've learned a lot. To them I must say great thanks, as without you, this journey would have never been a success. I'm forever in debt to your help and support.

First and foremost, I'd like to thank my advisor, Prof. Samuel Palermo. Thank you for showing me how a world-class research should be, and thank you for helping me become a better engineer. I'd like to thank my colleagues in Dr. Palermo's group: Ehsan, Osama, Keytaek, Cheng, Younghoon, Noah, Shengchang and Shiva. Thank you dear Ehsan. This would have never been achieved without your help.

I should thank Prof. Edgar Sanchez-Sinencio, Prof. Jose Silva-Martinez, Prof. Sebastian Hoyos, and Prof. Kamran Entesari in Analog and Mixed-Signal Center for their wonderful classes that helped shape my knowledge. Special thanks to Dr. Hoyos for his valuable contributions to my work. I would also like to thank my committee members, Prof. Jean-Francois Chamberland-Tremblay and Prof. Mahmoud El-Halwagi. I appreciate the support of Semiconductor Research Corporation (SRC), National Science Foundation (NSF) Texas Instruments and HP labs for funding my research.

Many thanks go to my fellow researches in the analog mixed signal group. To The four Mohammads: El-Nozahi, Mobarak, Mostafa, and Mohsen, to Ahmed Amer, Ehab, Ahmed Alaa, Kholy, Hatem, Sherief, Abuzaid and Omar. To my dear room mate for two years Ramy Saad, who was truly patient and helpful to me as a new-comer.

As part of my PhD experience, I had the chance to work for two great companies as a design intern, which added a lot to my experience. I wish to thank Jun Cao, Hamid Hatamkhany and Afshin Momtaz from Broadcom, and E-Hung Chen, Jihong Ren, Masum Hussain and Jared Zerbe from Rambus for the mentoring and the valuable discussions I had during my internships.

During my stay, I was privileged to meet many great Egyptian friends that helped me in all ways, both in College Station and elsewhere. I would like to thank Ahmed Ragab, Ahmed Rabea, Ahmed Salah, Bahaa Hafez, Farag Elnaggar, Mostafa Mosa and Tarek Elgohary for their support and help.

Last but never least, I would like to thank my Mom and Dad for their unlimited support and love. Thank you for always having you by my side even when we are thousands of miles apart. Thank you for always believing in me. To my lovely wife, who tolerated me through the painful PhD journey, and shared my moments of joy and despair, and my two angels Omar and Malik: Thank you.

# TABLE OF CONTENTS

|     |                                           |                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                         |

|-----|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| AB  | STRA                                      | ACT                                                                                                                                                                                                                                                                                                                                                                                                   | . ii                                                         |

| DE  | DICA                                      | TION                                                                                                                                                                                                                                                                                                                                                                                                  | . iv                                                         |

| AC  | KNO                                       | WLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                           | . v                                                          |

| TA  | BLE (                                     | OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                           | . vii                                                        |

| LIS | T OF                                      | FIGURES                                                                                                                                                                                                                                                                                                                                                                                               | . ix                                                         |

| LIS | T OF                                      | TABLES                                                                                                                                                                                                                                                                                                                                                                                                | . xiv                                                        |

| 1.  | INTR                                      | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                             | . 1                                                          |

|     | 1.1                                       | Dissertation Organization                                                                                                                                                                                                                                                                                                                                                                             | . 3                                                          |

| 2.  | BACI                                      | KGROUND ON HIGH-SPEED ADC-BASED RECEIVERS                                                                                                                                                                                                                                                                                                                                                             | . 5                                                          |

|     | 2.2 1 2 2 2 3 2 3 2 3 3 3 3 3 3 3 3 3 3 3 | Basic ADC Concepts, Sampling and Quantization Time-Interleaving of ADCs  2.2.1 Offset Mismatch Error 2.2.2 Gain Mismatch Error 2.2.3 Bandwidth Mismatch Error 2.2.4 Timing Mismatch Error Multi-Phase Generation and Timing Skew Calibration 2.3.1 Multi-Phase Clock Generation 2.3.2 Clock Skew Detection and Correction Equalization in High Speed Links Applications 2.4.1 Equalization Techniques | . 10<br>. 12<br>. 14<br>. 16<br>. 19<br>. 21<br>. 22<br>. 24 |

|     | 3.1 3<br>3.2 3                            | Statistical BER Modeling                                                                                                                                                                                                                                                                                                                                                                              | . 35<br>. 38<br>. 39<br>. 41                                 |

|    | 3.3  | Explo  | ration of Design Specifications for ADC-Based Receiver Archi- |     |

|----|------|--------|---------------------------------------------------------------|-----|

|    |      | tectur | res                                                           | 51  |

|    |      | 3.3.1  | Embedded Partial Analog Equalization                          | 51  |

|    |      | 3.3.2  | Requirements on Digital Feed-Forward Equalizer (FFE)          | 63  |

|    |      | 3.3.3  | Requirements on Digital Decision Feed-Back Equalizer (DFE)    | 63  |

| 4. | A 10 | OGS/S  | HYBRID ADC-BASED RECEIVER*                                    | 68  |

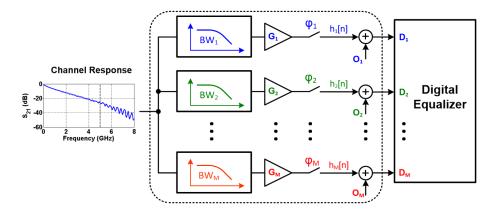

|    | 4.1  | Hybri  | d ADC-Based Receiver Architecture                             | 70  |

|    | 4.2  | Async  | chronous SAR ADC Implementation                               | 77  |

|    |      | 4.2.1  | SAR ADC with Embedded 3-Tap FFE                               | 78  |

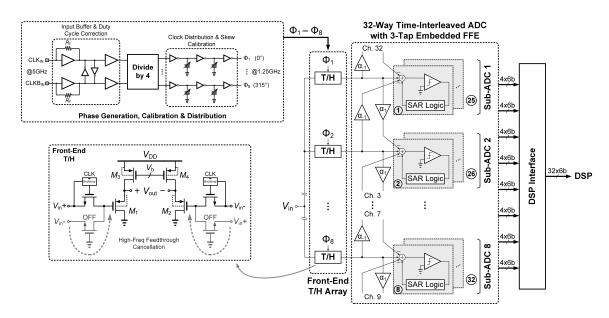

|    |      | 4.2.2  | 10GS/s Time-Interleaved ADC Architecture                      | 80  |

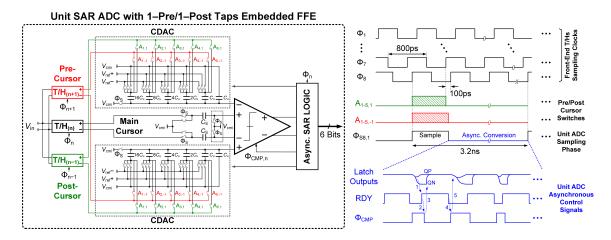

|    |      | 4.2.3  | Unit Asynchronous SAR ADC                                     | 81  |

|    | 4.3  | Dynar  | mically-Enabled Digital Equalizer                             | 84  |

|    | 4.4  | Exper  | rimental Results                                              | 88  |

|    |      | 4.4.1  | ADC Characterization                                          | 89  |

|    |      | 4.4.2  | ADC-Based Receiver Characterization                           | 90  |

| 5. | COI  | NCLUS  | ION AND FUTURE WORK                                           | 97  |

|    | 5.1  | Concl  | usion                                                         | 97  |

|    | 5.2  | Recon  | nmendations for Future Work                                   | 98  |

|    |      | 5.2.1  | Hybrid ADC-based Receiver with Flash ADC Implementation       | 99  |

| DΙ | מממי | FNCE   | Q                                                             | 100 |

# LIST OF FIGURES

| FΙ | GURI | E                                                                                                                          | Page |

|----|------|----------------------------------------------------------------------------------------------------------------------------|------|

|    | 1.1  | Expected growth in global internet traffic                                                                                 | 2    |

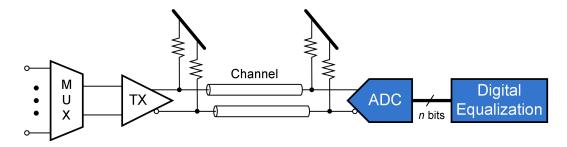

|    | 1.2  | Block diagram of ADC-based serial link receiver                                                                            | 3    |

|    | 2.1  | Effect of sampling jitter on SNR of signal                                                                                 | 7    |

|    | 2.2  | Area sampling of input PDF and equivalent quantization noise model.                                                        | 8    |

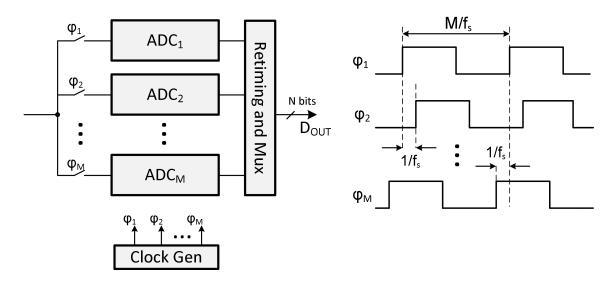

|    | 2.3  | Block diagram of an N-way time-interleaved ADC                                                                             | 10   |

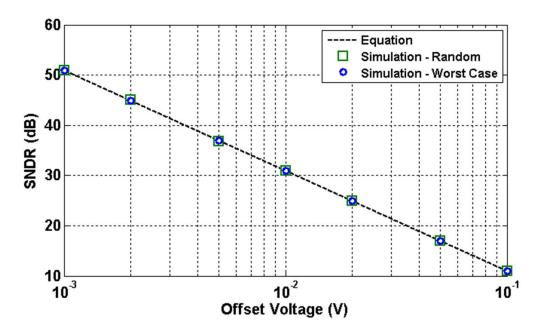

|    | 2.4  | Effect of offset mismatch on SNDR of signal                                                                                | 13   |

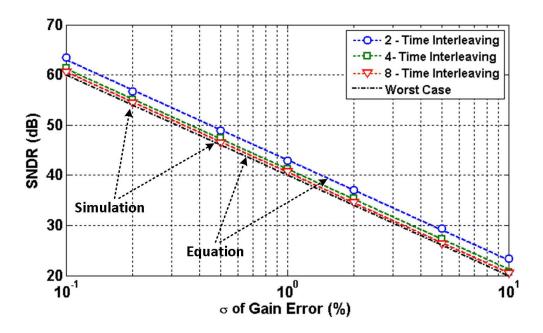

|    | 2.5  | Effect of gain mismatch on SNDR of signal                                                                                  | 15   |

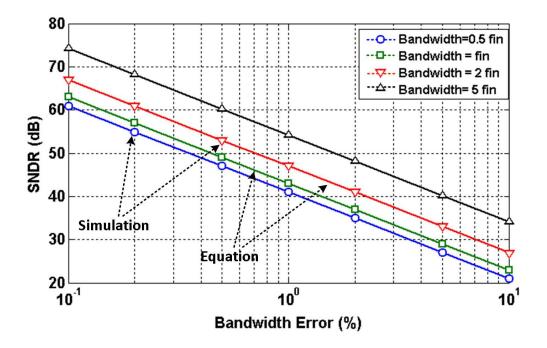

|    | 2.6  | Effect of bandwidth mismatch on SNDR of signal                                                                             | 17   |

|    | 2.7  | Effect of statistical bandwidth mismatch on SNDR of signal                                                                 | 19   |

|    | 2.8  | Effect of timing skew mismatch on SNDR of signal                                                                           | 21   |

|    | 2.9  | Block diagrams of divider-based and DLL-based clock generators                                                             | 22   |

|    | 2.10 | An example of divider-based 8-phase clock generator, showing two different realizations of clocked SR latch                | 23   |

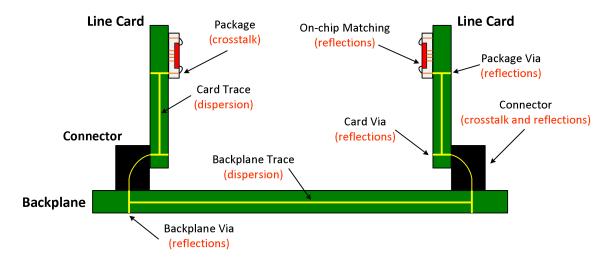

|    | 2.11 | Cross-section of backplane system.                                                                                         | 26   |

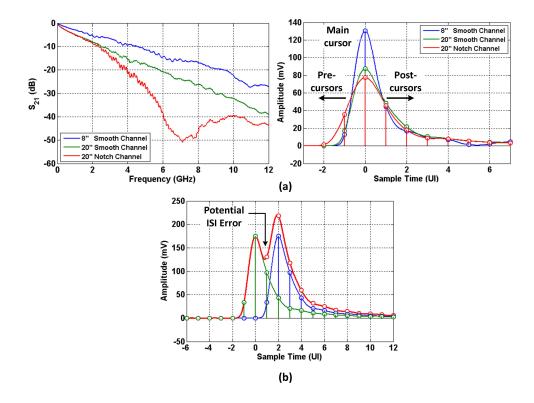

|    | 2.12 | (a) Channel and pulse responses for three backplance channels, and (b) Error due to inter-symbol interference (ISI) effect | 28   |

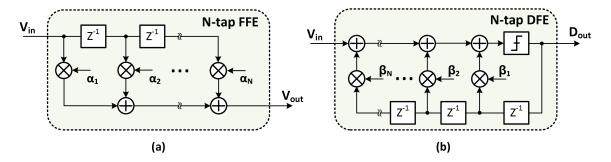

|    | 2.13 | Block diagram of (a) N-tap FFE and (b) N-tap DFE equalization                                                              | 29   |

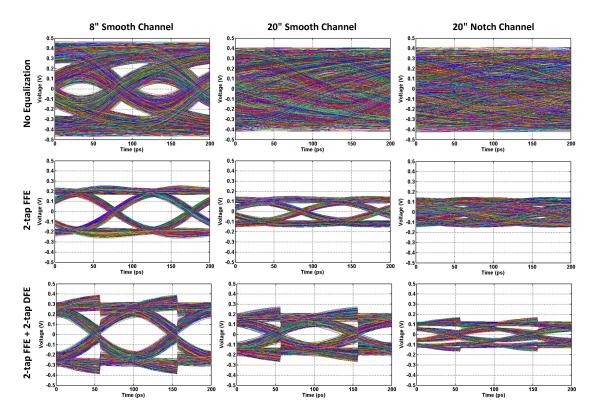

|    | 2.14 | Eye diagram for the three backplance channels of fig 2.12 (a) under different equalization condition                       | 31   |

|    | 3.1  | Block diagram of a high speed link with ADC-based receiver                                                                 | 33   |

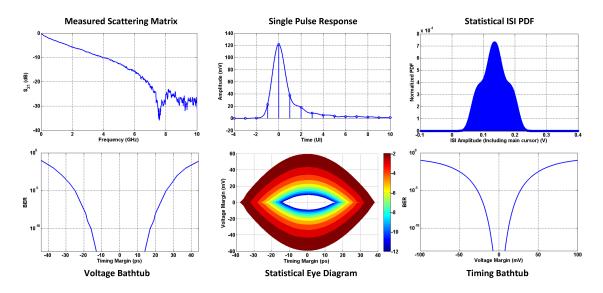

|    | 3.2  | Statistical simulation framework                                                                                           | 34   |

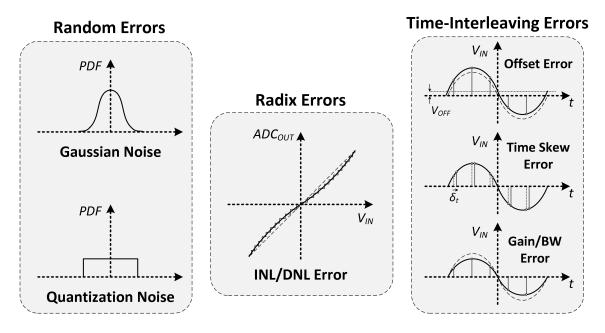

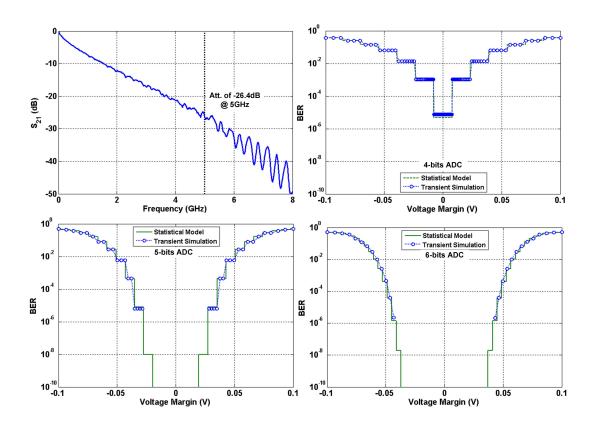

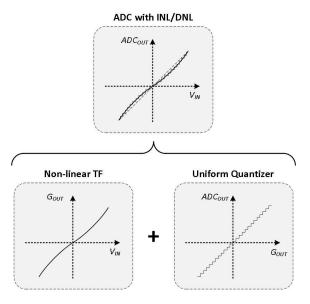

| 3.3  | Types of ADC-related errors                                                                                                                                                                                                                                                                                         | 38 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

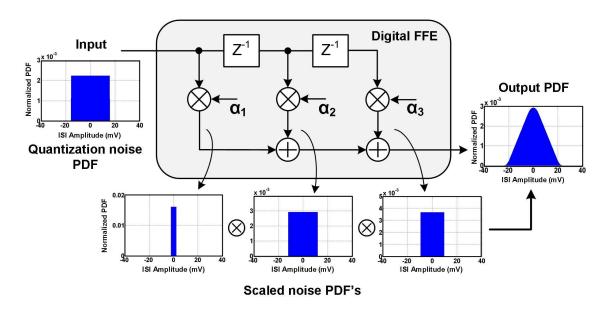

| 3.4  | Modeling of quantization noise amplification through digital FFE                                                                                                                                                                                                                                                    | 39 |

| 3.5  | Comparison between the quantization noise model and transient simulations                                                                                                                                                                                                                                           | 40 |

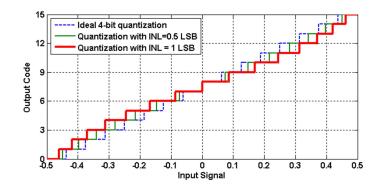

| 3.6  | ADC quantizer characteristics with sinusoidal INL (note the missing code when INL=1LSB)                                                                                                                                                                                                                             | 41 |

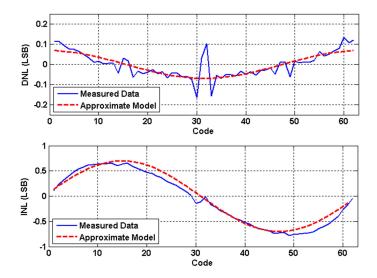

| 3.7  | Comparison between sinusoidal INL model and measured data                                                                                                                                                                                                                                                           | 42 |

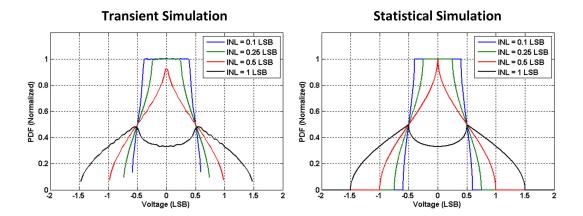

| 3.8  | Comparison between quantization noise PDF extracted from transient simulations with uniform input and the statistical convolution model.                                                                                                                                                                            | 43 |

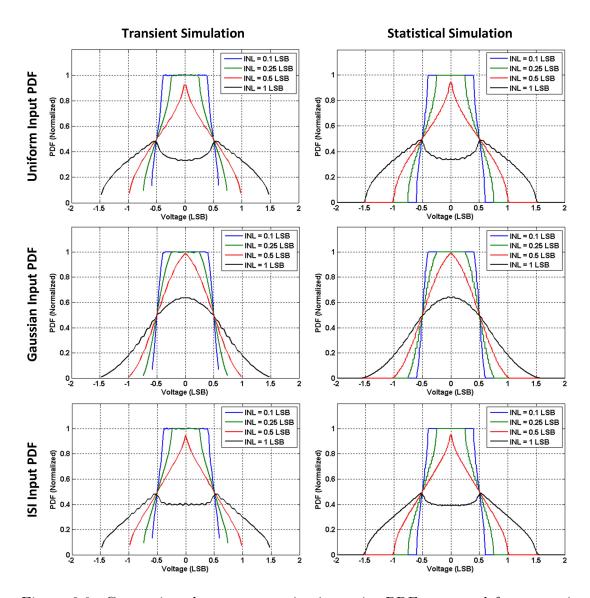

| 3.9  | Comparison between quantization noise PDF extracted from transient simulations and the statistical models based on equation 3.11 for three different cases of input PDFs                                                                                                                                            | 45 |

| 3.10 | Comparison between quantization noise PDF after the digital FFE extracted from transient simulations and the one calculated using the statistical model, for two different cases of input PDF                                                                                                                       | 46 |

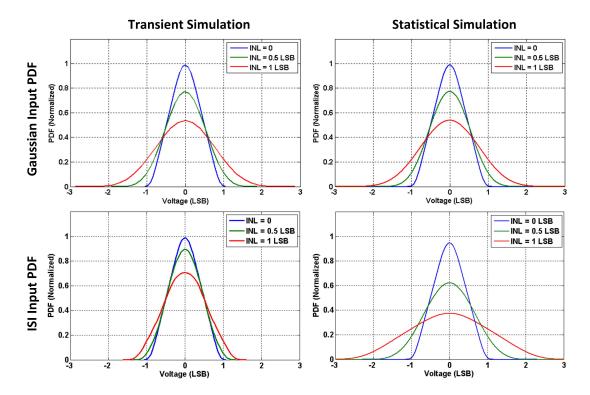

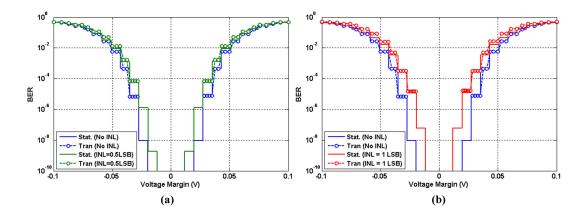

| 3.11 | Comparison between the quantization noise model using histogram data and transient simulations for (a) INL=0.5 LSB and (b) INL=1 LSB                                                                                                                                                                                | 47 |

| 3.12 | Block diagram of time-interleaved system showing the mismatch errors                                                                                                                                                                                                                                                | 48 |

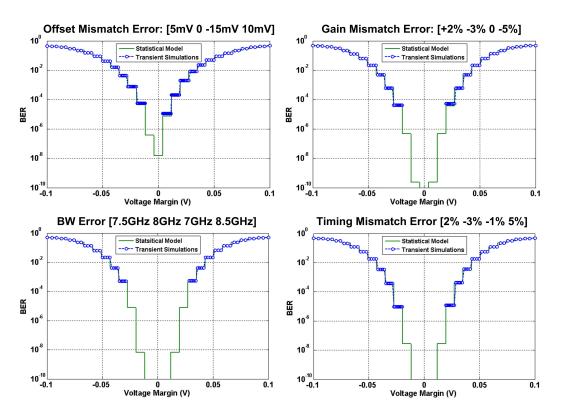

| 3.13 | Comparison between time interleaving statistical model and transient simulations                                                                                                                                                                                                                                    | 50 |

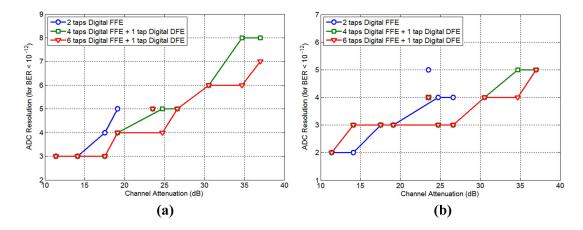

| 3.14 | ADC resolution requirements for ADC-based 10Gbps receiver with (a) all-digital equalization and (b) 2 taps embedded FFE                                                                                                                                                                                             | 53 |

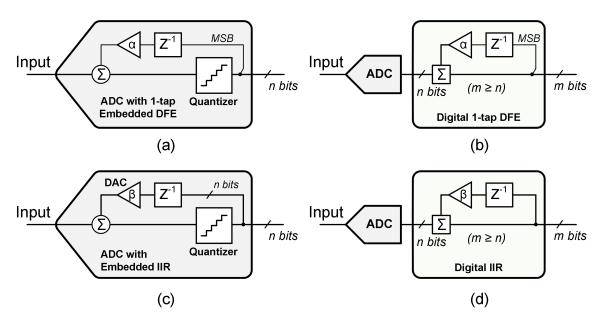

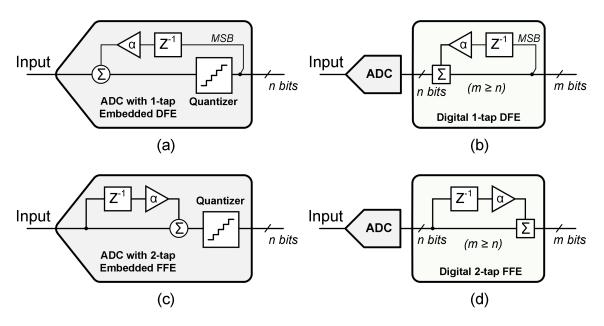

| 3.15 | Block diagrams of (a),(b) embedded vs. digital DFE, and (c) and (d) embedded vs. digital IIR.                                                                                                                                                                                                                       | 54 |

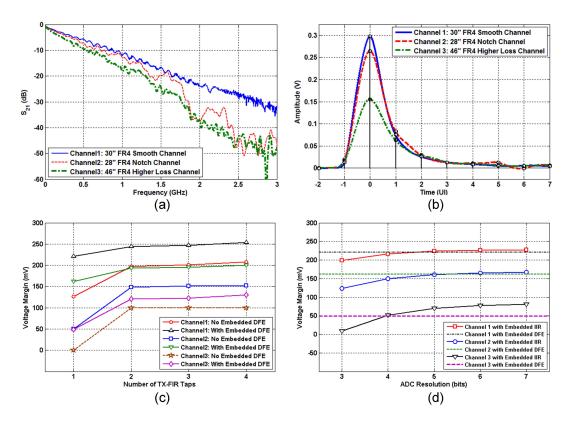

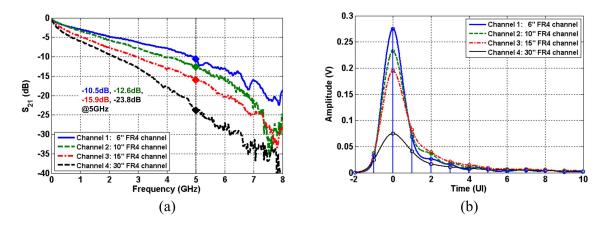

| 3.16 | (a) Magnitude and (b) 1.6Gb/s pulse responses of three FR4 channels. (c) Impact of including one tap of embedded DFE equalization for different levels of TX-FIR equalization, and (d) impact of ADC resolution with embedded DFE and embedded IIR equalization with no TX FIR equalization over three FR4 channels | 56 |

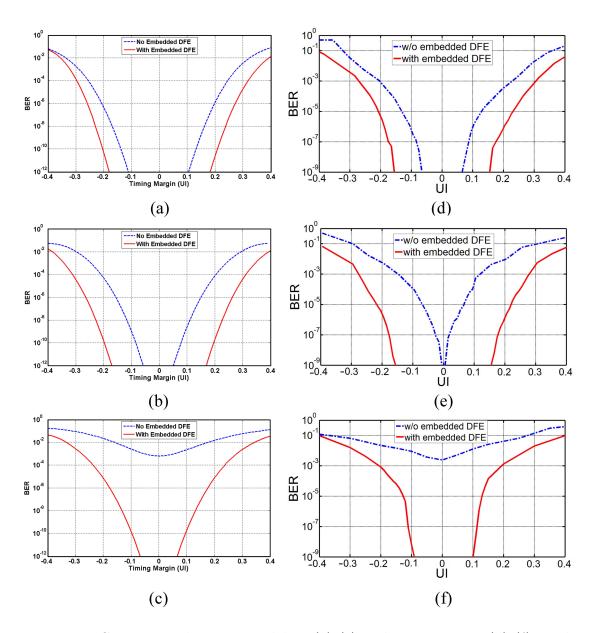

| 3.17 | Comparison between modeling (a)-(c) and measurement (d)-(f) results for $1.6 GS/s$ prototype with embedded DFE                                                                                                                                                                                                                                           | 58 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.18 | Block diagrams of (a) embedded vs. digital DFE, and (b) embedded vs. digital FFE                                                                                                                                                                                                                                                                         | 59 |

| 3.19 | (a) Magnitude and (b) 10Gb/s pulse responses of four FR4 channels.                                                                                                                                                                                                                                                                                       | 60 |

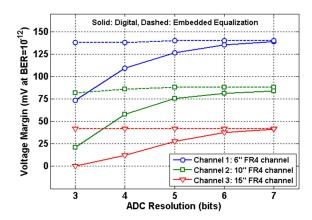

| 3.20 | Simulated voltage margin versus ADC resolution with both digital and embedded implementations of a 2-tap FFE + 1-tap DFE equalization structure for channels 1-3 in Fig. 3.19                                                                                                                                                                            | 61 |

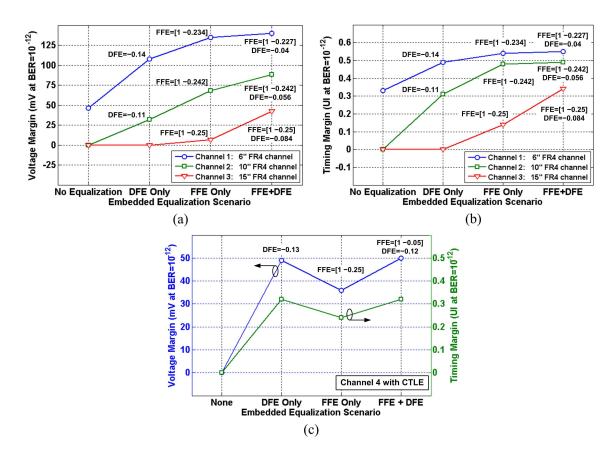

| 3.21 | Impact of including embedded DFE and FFE equalization on (a) voltage margin and (b) timing margin for channels 1-3 in Fig. 3.19, with tap coefficients shown for the embedded equalization. (c) Impact of including embedded DFE and FFE equalization on voltage margin and timing margin in the presence of a front-end CTLE for channel 4 in Fig. 3.19 | 62 |

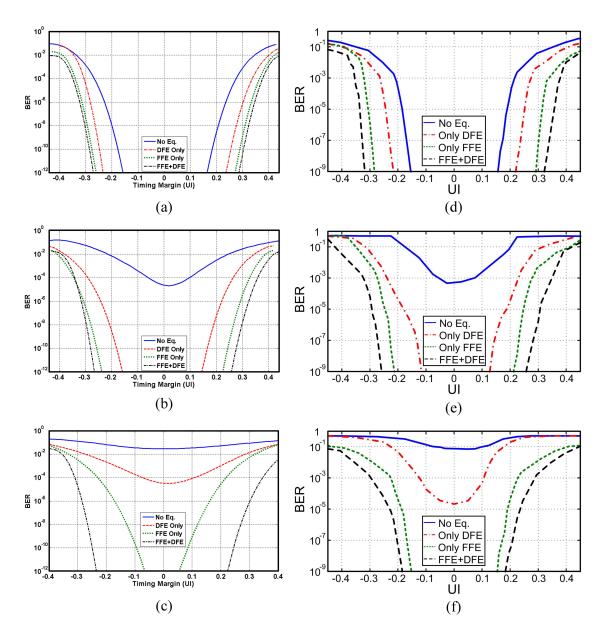

| 3.22 | Comparison between modeling (a)-(c) and measurement (d)-(f) results for $10 \text{GS/s}$ prototype with embedded FFE+DFE                                                                                                                                                                                                                                 | 64 |

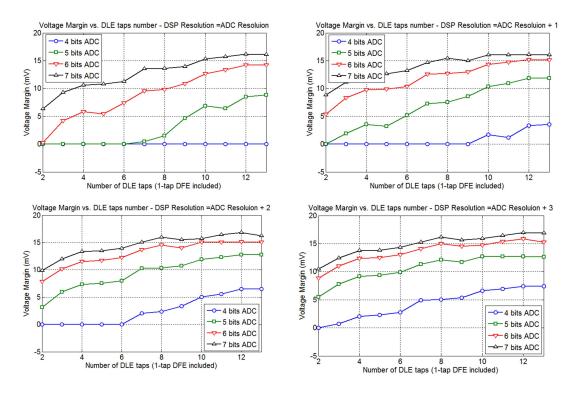

| 3.23 | Voltage margins for 10Gbps operation under different conditions of ADC resolution and digital equalization                                                                                                                                                                                                                                               | 65 |

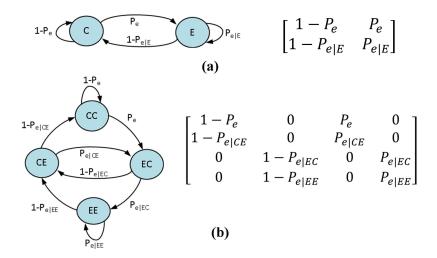

| 3.24 | Markov chain model showing the transition probability graph and matrix for (a) 1 tap of DFE and (b) 2 taps of DFE                                                                                                                                                                                                                                        | 66 |

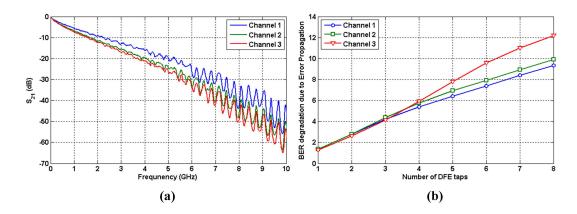

| 3.25 | BER degradation due to error propagation vs. number of DFE taps for 3 backplane channels                                                                                                                                                                                                                                                                 | 67 |

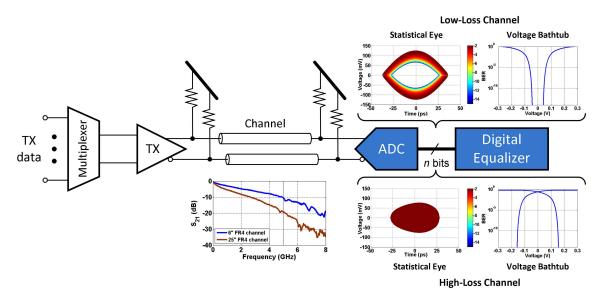

| 4.1  | A 10Gb/s high-speed electrical link system with a front-end ADC and digital equalizer                                                                                                                                                                                                                                                                    | 70 |

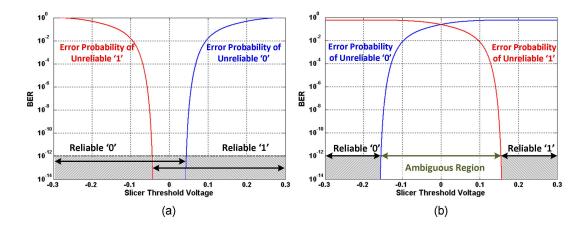

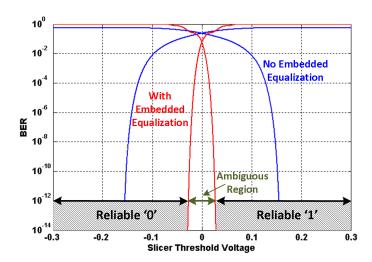

| 4.2  | 10Gb/s BER voltage bathtub curves for the 4.1 lower-loss channel and (b) higher-loss channel                                                                                                                                                                                                                                                             | 72 |

| 4.3  | $10{ m Gb/s}$ BER voltage bathtub curves for the Fig. 1 higher-loss channel when an embedded 3-tap FFE is included in the front-end ADC                                                                                                                                                                                                                  | 73 |

| 4.4  | Proposed hybrid ADC-based receiver architecture                                                                                                                                                                                                                                                                                                          | 74 |

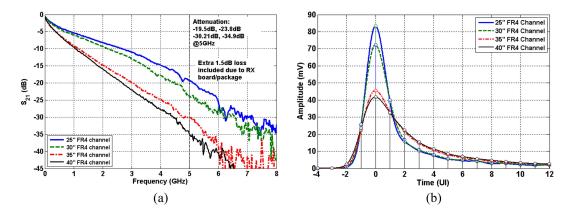

| 4.5  | (a) Magnitude and (b) 10Gb/s pulse responses of four FR4 channels.                                                                                                                                                                                                                                                                                       | 75 |

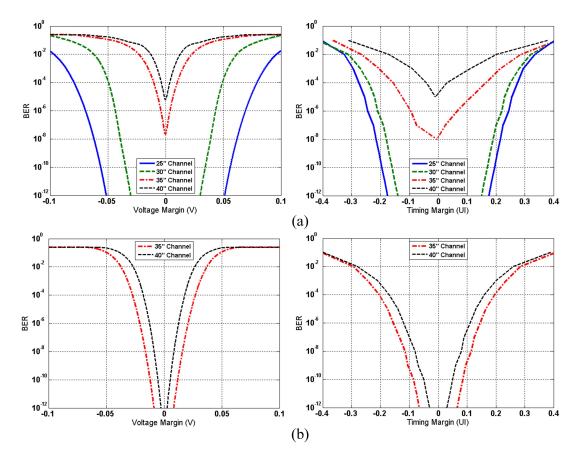

| 4.6  | Simulated voltage and timing margins for (a) the four Fig. 4.5 channels with 3-tap embedded FFE only and (b) the two higher attenuation channels with both 3-tap embedded FFE and digital equalization                                                                                   | 76 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

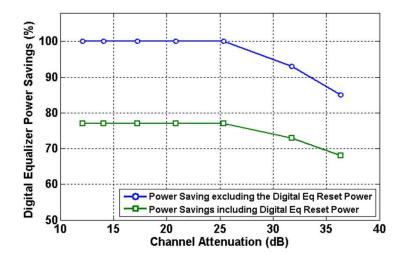

| 4.7  | Simulated digital equalizer power savings versus channel attenuation with the proposed hybrid ADC-based receiver architecture                                                                                                                                                            | 77 |

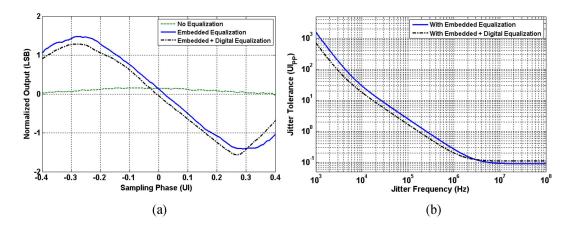

| 4.8  | Simulated hybrid-ADC receiver baud-rate CDR performance for operation over the 35 channel: (a) Mueller-Muller phase detector characteristics, (b) jitter tolerance for BER=10-12                                                                                                         | 78 |

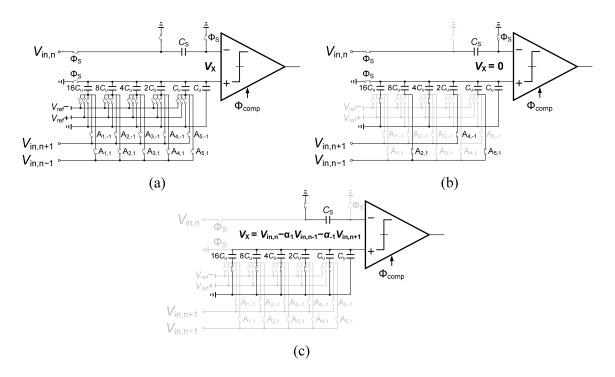

| 4.9  | Simplified unit SAR ADC with embedded 3-tap FFE: (a) single-ended schematic, and operation during the (b) sampling phase, and (c) first MSB evaluation assuming $A_{1,-1}A_{2,-1}A_{3,-1}A_{4,-1}A_{5,-1}=00010$ and $A_{1,1}A_{2,1}A_{3,1}A_{4,1}A_{5,1}=01001$ for the post-cursor tap | 80 |

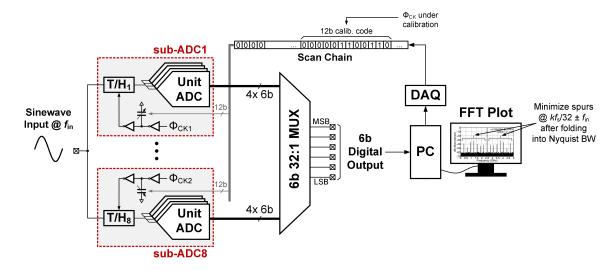

| 4.10 | Block diagram of the 32-way time-interleaved asynchronous SAR ADC with 3-tap embedded FFE                                                                                                                                                                                                | 81 |

| 4.11 | Fully-differential schematic of the unit asynchronous SAR ADC with sampled 3-tap embedded FFE                                                                                                                                                                                            | 82 |

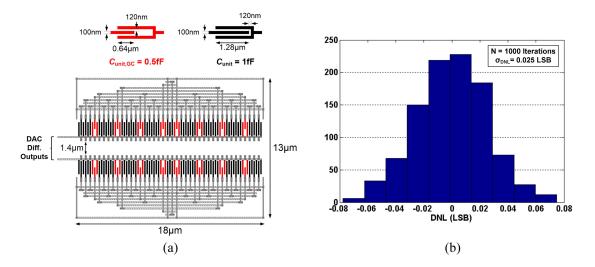

| 4.12 | Custom layout of the differential capacitive DAC with 1fF MOM unit capacitors and embedded gain calibration, and (b) CDAC worst-case 01111 to 10000 transition DNL simulation results using 1000 Monte Carlo iterations                                                                  | 83 |

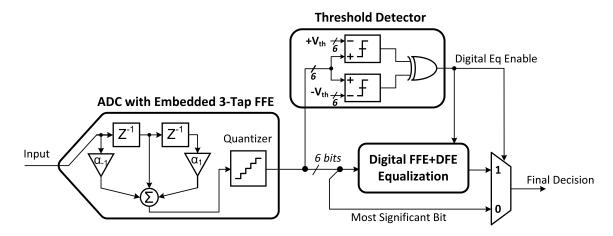

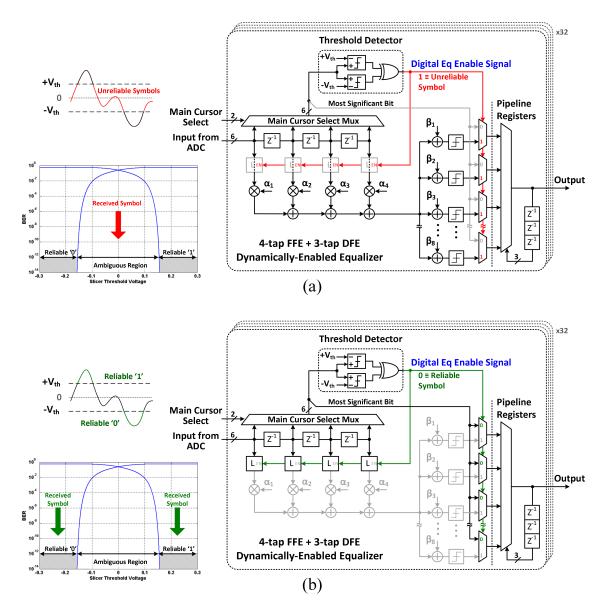

| 4.13 | Block diagram of the per-symbol dynamically-enabled digital equalizer with 4-tap reconfigurable FFE and 3-tap loop-unrolled DFE: (a) operation under reception of an unreliable symbol and (b) operation under reception of a reliable symbol                                            | 85 |

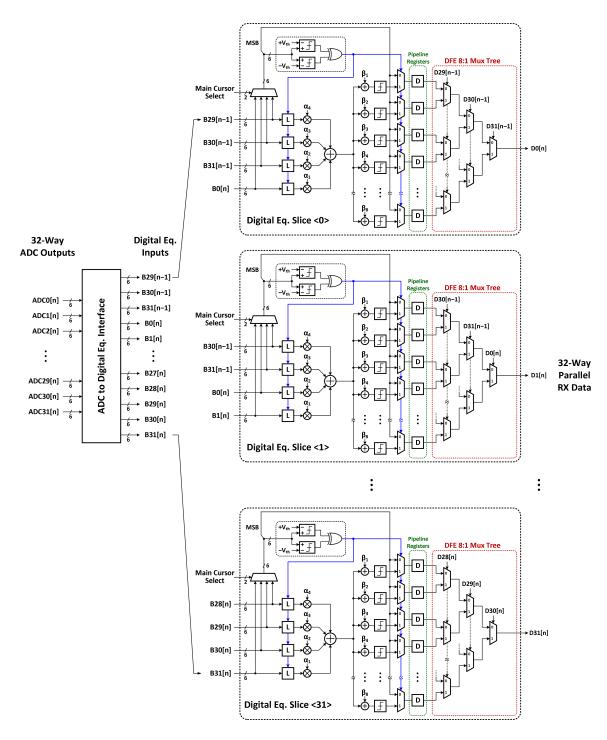

| 4.14 | Detailed implementation of the dynamically-enabled 32-way parallel 4-tap FFE and 3-tap loop-unrolled DFE digital equalizer                                                                                                                                                               | 87 |

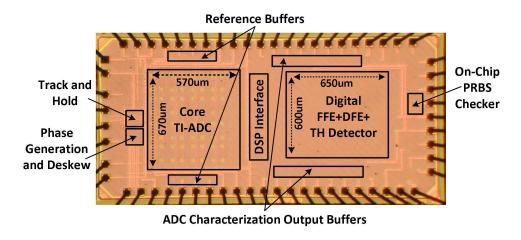

| 4.15 | Prototype ADC-based receiver chip microphotograph                                                                                                                                                                                                                                        | 88 |

| 4.16 | Simplified diagram of foreground clock skew calibration setup                                                                                                                                                                                                                            | 89 |

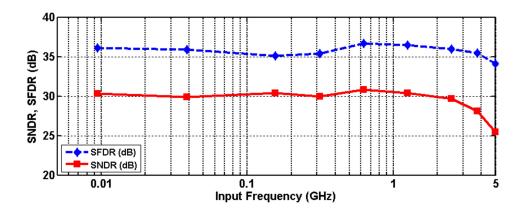

| 4.17 | ADC SNDR and SFDR vs. input frequency at fs = 10 GHz                                                                                                                                                                                                                                     | 90 |

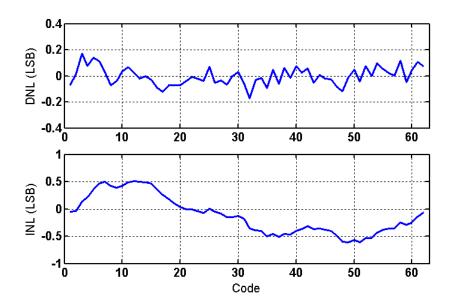

| 4.18 | DNL/INL plots with fin = 9.46 MHz at fs = 10 GHz                                                                                                                                                                                                                                         | 91 |

| 4.19 | Measured tap coefficient range and resolution using DC input voltages for embedded FFE pre- and post- taps                                                                                                                                                                               | 91 |

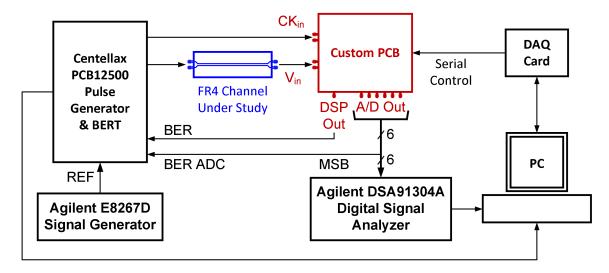

| 4.20 | ADC-based receiver characterization test setup                                                                                                                                                                            | 92 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

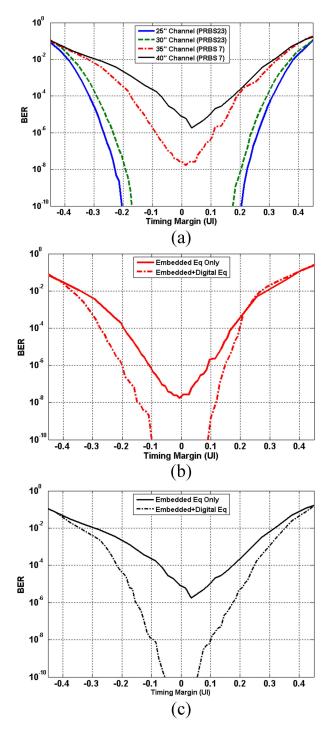

| 4.21 | Measured bathtub curves for operation over the four Fig. 4.5 FR4 channels with (a) embedded equalization only, and collaborative use of the embedded and digital equalizers for (b) the 35 channel and (c) the 40 channel | 93 |

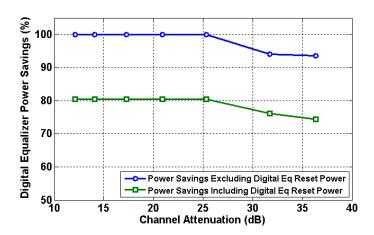

| 4.22 | ${\it Measured \ digital \ equalization \ power \ savings \ versus \ channel \ attenuation.}$                                                                                                                             | 94 |

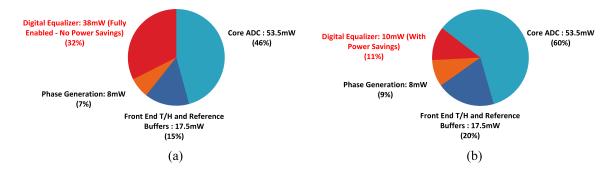

| 4.23 | ADC-based receiver power breakdown for operation over the 36.4dB channel: (a) without per-symbol dynamic enabling and (b) with per-symbol dynamic enabling of the digital equalizer                                       | 95 |

| 5.1  | Decomposition of INL error into linearity $+$ quantization errors $\cdot \cdot \cdot \cdot$                                                                                                                               | 98 |

| 5.2  | Block diagram of hybrid-ADC based receiver with inherent threshold detection using Flash ADC                                                                                                                              | 99 |

# LIST OF TABLES

| TABLE                                                         | Page |

|---------------------------------------------------------------|------|

|                                                               |      |

| 4.1 Proposed 10Gb/s ADC-Based Receiver Performance Comparison | . 96 |

#### 1. INTRODUCTION

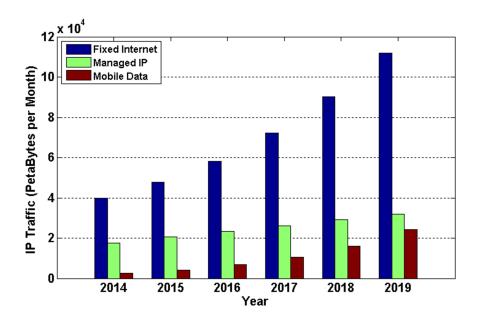

The rapid increase in the number of internet users, as well as the advances in network-enabled devices and connections, led to a continued growth in the global IP traffic over the past few years. Faster broadband speeds are allowing more users to access emerging services such as cloud computing and video on demand (VON) streaming services. Fig. 1.1 shows the projected growth of global internet traffic, in PetaBytes (10<sup>15</sup> Bytes) per month, where the total IP traffic is expected to nearly triple from 2014 to 2019 [1]. This increase in internet traffic requires an equivalent improvement in data centers, in terms of the number of servers and their data rates, which translates to more power dissipation. This is one of the main drivers of the high speed serial link communications market.

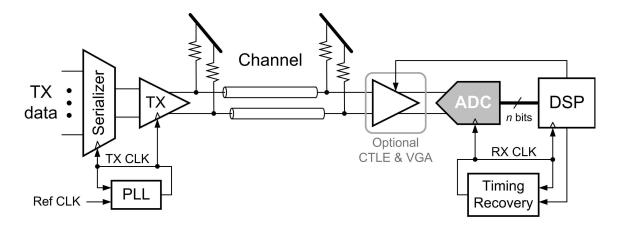

As the data rates of wire-line communication links increases, channel impairments such as skin effect, dielectric loss, fiber dispersion, reflections and cross-talk become more pronounced. This warrants more interest in analog-to-digital converter (ADC)-based serial link receivers (Fig. 1.2), as they allow for more complex and flexible back-end digital signal processing (DSP) relative to binary or mixed-signal receivers [2–5]. Utilizing this back-end DSP allows for complex digital equalization and more bandwidth-efficient modulation schemes, while also displaying reduced process/voltage/temperature (PVT) sensitivity. Furthermore, these architectures offer straightforward design translation and can directly leverage the area and power scaling offered by new CMOS technology nodes.

Despite these advantages, ADC-based receivers are generally more complex and have higher power consumption relative to mixed-signal receivers [6]. While significant improvements in multi-GS/s ADC figure-of-merit (FOM) have been recently

Figure 1.1: Expected growth in global internet traffic.

achieved [7–9], the ensuing digital equalization can also consume a significant amount of power which is comparable to the ADC contribution [2]. Thus, in order to reduce the power of these ADC-based receiver systems, techniques to improve equalization efficiency and relax ADC resolution requirements have been developed. Non-uniform ADC quantization has been proposed to enable efficient implementations of digital decision feedback equalizers (DFEs) with either a minimal number of comparators [10], a BER-optimal threshold settings [11] or a thermometer-code selection-based architecture [5]. However, these designs do not allow for any digital feedforward equalization (FFE), which is useful for canceling pre-cursor and long-tail ISI. Other promising approaches included embedding partial analog equalization inside the ADC [12–14] which allows for both reduced ADC resolution and also relaxes the requirements of the following digital equalization [15]. On the digital equalization front, techniques such as parallelized distributed arithmetic [16] and multiple supply and frequency domains [17] have been utilized to improve the digital equalizer power

Figure 1.2: Block diagram of ADC-based serial link receiver.

efficiency.

This research targets the design of efficient ADC-based receiver implementation with 10Gb/s data rate in 65nm CMOS. The ideas proposed in this work, however, can be extended to higher data rates, and can efficiently leverage CMOS scaling to more advanced technology nodes.

### 1.1 Dissertation Organization

Section 2 presents a background overview on the topic of ADC-based receiver design. An introduction on sampling and quantization in ADCs is first presented. Challenges in the design of multi-Gbps time interleaved ADCs are then discussed. Details on the design of one of the critical blocks, the clock generation and timing calibration circuitry, is reviewed. Brief discussion of high-speed link architectures and different receiver equalization techniques, namely feed-forward equalization (FFE), infinite impulse response equalizer (IIR) and decision feedback equalization (DFE), are given.

The remainder of this work focuses on the modeling, design and implementation of power efficient ADC-based receiver architectures. In section 3, a statistical modeling framework is presented, which can predict the system performance both efficiently and accurately, down to the target bit error rate (BER) of  $10^{-12}$  or lower. The framework builds on state of the art statistical binary links receiver simulation tools [18,19], by extending it to the ADC-based receiver case. ADC-related non-idealities such as quantization noise, linearity errors and time interleaving errors are included in the statistical model. The model is then used to evaluate different techniques to efficiently embed partial analog equalization inside the front-end high-speed ADC, potentially improving the efficiency of the full ADC-based receiver [15]. Two case studies of high speed ADCs with embedded equalization are considered [13,14], where good matching between the model and measurement results verifies the the accuracy of the model.

Next, a novel hybrid ADC-based receiver architecture that combines embedded and digital equalization is discussed in section 4. By dynamically enabling the digital equalizer on a per-symbol basis, considerable amount of power of the digital equalization may be saved, where the concept of reliable symbol detection is used to ensure the digital equalizer is only enabled when the received symbol is unreliable, and disabled otherwise. A receiver prototype is fabricated in 65nm CMOS, with an asynchronous SAR ADC architecture used for the front-end ADC. Three taps of partial analog FFE are efficiently embedded inside the capacitive DAC of the ADC, and 4 taps of digital FFE plus 3 taps of digital DFE are fully synthesized as the back-end equalizer. Measurement results over different FR4 channels prove the effectiveness of the proposed architecture, where comparison with state of the art ADC-based receivers shows that the architecture can equalize for the highest loss channel, while achieving the best power efficiency [20].

Finally, section 5 concludes the research presented, and suggests some interesting ideas to extend the work in the future.

#### 2. BACKGROUND ON HIGH-SPEED ADC-BASED RECEIVERS

This section explains briefly some concepts that are closely related to the design of ADC-based serial link receivers. First, basic concepts of ADC operation, the sampling and the quantization, are revised. Next, the idea of time interleaving, which enables multi-Gbps operation of ADCs, is discussed. Implications that arise due to mismatches in time interleaving architecture are analyzed, showing how those non-idealities can affect the performance of the ADC. Following this, the design of the clock generation and timing calibration circuitry, which is curial to the operation of the time interleaved structure, is reviewed. Different equalization and signaling architectures used in high speed link systems are then presented.

#### 2.1 Basic ADC Concepts, Sampling and Quantization

The basic operation of any ADC includes two main quantization functions, sampling of the input, which may be viewed as quantization in the time domain, followed by amplitude quantization into discrete digital levels. In order to ensure proper reconstruction of the signal, the Nyquist criteria must be fulfilled during the sampling, where the input bandwidth must be kept below one half of the sampling frequency to prevent aliasing [21]. In ADC-based high speed link applications, the channel loss limits the bandwidth of the input signal, eliminating the need for explicit ant-aliasing filter.

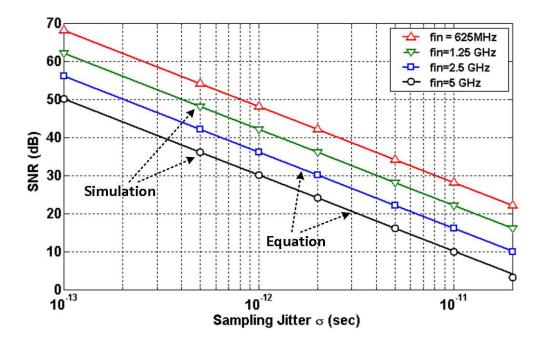

While it is theoretically possible to fully recover the signal after sampling, the jitter on the sampling clock is going to add an error to the output signal, since the ideal sampling instants are modulated by the sampling clock jitter. The error due to jitter may be written as [22]:

$$\Delta X[nT] = \epsilon[nT] \left. \frac{dX(t)}{dt} \right|_{(t=nT)}$$

(2.1)

Where  $\epsilon[nT]$  is the jitter at sampling instant. Assuming an input sine wave:

$$X(t) = Asin(\omega_{in}t) \tag{2.2}$$

The error may be given as:

$$\Delta X[nT] = \epsilon[nT] A\omega_{in} cos(\omega_{in} nT)$$

(2.3)

This introduces a limit on the maximum SNR an ADC could achieve under certain jitter conditions. With the sine wave input assumption, this maximum SNR may be given as [22]:

$$SNR = \frac{P_{signal}}{P_{error}} = \frac{A^2/2}{A^2 \omega_{in}^2 \epsilon_J^2/2} = \frac{1}{\epsilon_J^2 \omega_{in}^2}$$

$$SNR_{dB} = -20 \cdot log(\epsilon_J \omega_{in})$$

(2.4)

Where  $\epsilon_J$  is the rms value of the jitter.

To show the effect of jitter on the SNR degradation, a MATLAB model is used, where a sine wave is sampled with the presence of random jitter, and the resulting SNR is extracted from the output spectrum. The results are shown in Fig. 2.1 for different input frequencies, and equation 2.4 is also plotted for comparison. As expected, the simulation results and the calculated values match each other closely.

In reality, however, the input signal may not always be sinusoidal. It can be proven [23] that for the case of a random input signal which has a rectangular spectrum with maximum frequency of  $\omega_{in}$ , the SNR is given as:

Figure 2.1: Effect of sampling jitter on SNR of signal.

$$SNR = \frac{3}{\epsilon_J^2 \omega_{in}^2}$$

$$SNR_{dB} = -20 \cdot log(\epsilon_J \omega_{in}) + 4.77$$

(2.5)

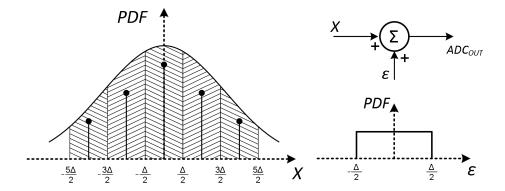

Next, the error due to quantization of the input signal is considered. While sampling may be viewed as quantization of the input signal in the time domain, amplitude quantization, on the other hand, may be viewed as "area sampling" of the input probability density function (PDF) [24]. The quantization process works to concentrate the PDF of the input signal over each quantization interval into a single quantized output level, converting the continuous input PDF into a discrete output probability mass function (PMF), as shown in Fig. 2.2. Assuming uniform quantization, this is mathematically equivalent to performing a convolution operation between the in-

Figure 2.2: Area sampling of input PDF and equivalent quantization noise model.

put PDF and a uniform PDF, with width equal to the quantization interval, and then multiplying the resulting PDF with an impulse train to obtain the final PMF. This model has been presented by Widrow as the pesudo-quantization noise (PQN) model [25], where under certain conditions, the quantization noise may be assumed to be uniform over the quantization interval, and the effect of quantization may be approximated as an additive noise term.

Now, assuming an ADC with N-bit resolution, and full scale equal to  $V_{FS}$ , the width of the quantization interval is given by:

$$\Delta = \frac{V_{FS}}{2^N} \tag{2.6}$$

The quantization noise power, assuming a uniform error PDF over one quantization interval, may then be calculated as:

$$E(\epsilon_q^2) = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} \epsilon^2 d\epsilon$$

$$= \frac{\Delta^2}{12}$$

(2.7)

Assuming a sinusoidal input with full scale amplitude leads to the well-known SNR formula:

$$SNR = 1.5 \times 2^{2N}$$

$SNR_{dB} = 6.02N + 1.76$  (2.8)

The formula suggests that the SNR of the ADC improves by 4X for every additional bit of resolution. Now, if the input signal is assumed to be uniform rather than sinusoidal, the SNR changes slightly to:

$$SNR = 2^{2N}$$

$$SNR_{dB} = 6.02N$$

(2.9)

Alternatively, assuming the input signal has a Gaussian random PDF, with the full scale set to  $\pm 3\sigma$  of the random distribution, and assuming no quantizer overload [26], the SNR becomes:

$$SNR = \frac{1}{3} \times 2^{2N}$$

$$SNR_{dB} = 6.02N - 4.77$$

(2.10)

Comparing equations 2.8 and 2.10, a difference in SNR equivalent to more than one bit of resolution can be observed. Noting that equation 2.8 is usually used to extract the effective number of bits (ENOB) specification of an ADC, it's important to keep in mind that this number is calculated assuming a sinusoidal input signal, which may not be always be accurate when a different input, e.g. with Gaussian PDF,

Figure 2.3: Block diagram of an N-way time-interleaved ADC.

is used. In general, when it comes to random input signals, the highest possible SNR that may be obtained from a uniform quantizer is obtained when the input PDF is uniform [26].

#### 2.2 Time-Interleaving of ADCs

In order to enable multi-Gbps operation, time interleaving is usually incorporated in ADC design, as shown in Fig. 2.3. A time interleaved ADC consists of M sub-ADCs operating in parallel. Each sub-ADC operates at 1/M of the sampling frequency of the full ADC [27], enabling sampling rates higher than the technology limit. In reality, mismatches between the interleaved channels degrades the ADC performance, and must to be calibrated. These mismatches are usually due to three main types of errors: offset errors, gain errors and time skew errors [28, 29].

The output signal of an M-channel time interleaved ADC may be given as:

$$y(t) = x(t) \sum_{k=-\infty}^{\infty} \delta(t - MkT) + x(t) \sum_{k=-\infty}^{\infty} \delta(t - (Mk+1)T)$$

$$+x(t) \sum_{k=-\infty}^{\infty} \delta(t - (Mk+2)T) + \dots$$

$$+x(t) \sum_{k=-\infty}^{\infty} \delta(t - (Mk+M-1)T)$$

$$(2.11)$$

Where  $\delta(.)$  denotes the delta Dirac function. The spectrum of this signal may be written as:

$$Y(f) = X(f) \otimes \sum_{k=-\infty}^{\infty} \delta(f - \frac{kf_s}{M}) + X(f) \otimes \sum_{k=-\infty}^{\infty} \delta(f - \frac{kf_s}{M}) e^{-j2\pi \frac{f}{f_s}}$$

$$+X(f) \otimes \sum_{k=-\infty}^{\infty} \delta(f - \frac{kf_s}{M}) e^{-j2\pi \frac{2f}{f_s}} + \dots$$

$$+X(f) \otimes \sum_{k=-\infty}^{\infty} \delta(f - \frac{kf_s}{M}) e^{-j2\pi \frac{(M-1)f}{f_s}}$$

$$(2.12)$$

Since each channel is sampled at  $f_s/M$ , this means that the spectrum at each channel output will contain images every  $kf_s/M$ , k=0,1,2,...M-1. Under ideal conditions, the phase difference between the interleaved channels results in canceling of all the images except for those at  $kf_s$ . In reality, however, mismatches between the interleaved channels will cause incomplete cancellation of the signal images, resulting in aliasing of the uncancelled images which produces errors at the output signal. In the following subsection, the three mismatch error sources are discussed, and there impact on the sampled signal is analyzed.

## 2.2.1 Offset Mismatch Error

The offset error arises in the ADC due to process variations in the comparator, leading to the threshold being slightly shifted from its nominal value. Mismatches in the offset voltage between the time interleaved channels result in degradation in the ADC performance. To quantify this degradation, a worst case scenario is assumed, where the offset voltage between interleaved channels toggles between  $\pm V_{OF}$ . This creates a tone at half the sampling frequency, which is added to the input signal, resulting in a spur in the output spectrum at  $f_s/2$ . The SNDR due to this error may be written as, assuming an input sine wave with full scale swing:

$$SNDR = \frac{(V_{FS}/2)^2/2}{V_{OF}^2} = \frac{V_{FS}^2}{8 \cdot V_{OF}^2}$$

$$SNDR_{dB} = 20 \cdot log\left(\frac{V_{FS}}{V_{OF}}\right) - 9.03$$

(2.13)

Where due to sampling at  $f_s/2$ , the offset signal power is  $V_{OF}^2$  rather than  $V_{OF}^2/2$ . Alternatively, if a random normal distribution of the offset voltage with standard deviation  $\sigma_{OF}$  is assumed, the resulting SNDR is:

$$SNDR = \frac{(V_{FS}/2)^2/2}{\sigma_{OF}^2} = \frac{V_{FS}^2}{8 \cdot \sigma_{OF}^2}$$

$$SNDR_{dB} = 20 \cdot log\left(\frac{V_{FS}}{\sigma_{OF}}\right) - 9.03$$

(2.14)

Comparing equations 2.13 and 2.14, it is obvious that from an SNDR perspective, the effect of a worst case offset mismatch with offset voltage  $\pm V_{OF}$ , is equivalent to the effect of a random Gaussian distributed offset mismatch, when the standard deviation is equal to  $V_{OF}$ .

Figure 2.4: Effect of offset mismatch on SNDR of signal.

To demonstrate the effect of offset mismatch on ADC performance, a MATLAB model is used to calculate the SNDR of an ideally sampled signal, when both a worst case offset error and randomly distributed offset errors are added. The results are shown in Fig. 2.4, where an 8-channel time interleaved system is assumed with full scale voltage of 1V. For the Gaussian offset errors case, 10<sup>3</sup> transient simulations are performed, with a set of randomly generated offset voltages per simulation used as the offsets of the interleaving channel. The SNDR is then calculated based on the expected value (average) of the distortion across all simulations, excluding the dc offset error [30]. The results show perfect matching between the two simulation cases, and with the result obtained using equation 2.13 or 2.14, also plotted for comparison.

It's worth noting that since the offset error is added to the input, the error is independent of the input signal frequency. In addition, the SNDR degradation due

to offset error is independent on the time interleaving factor. In general, the offset error results in tones at  $kf_s/M$ , where k = 0, 1, 2, ...M/2 [28].

The gain mismatch error may be decomposed into two types, dc gain error and ac gain error, where the latter represents the bandwidth mismatch between the time interleaved channels. Each of the two errors will be considered separately, starting with the dc gain error, simply referred to as the gain error. To prevent confusion, the ac gain error will be referred to as the bandwidth error.

# 2.2.2 Gain Mismatch Error

Following a similar approach to the offset error, the effect of the gain mismatch may be quantified assuming worst case gain error variations, for which the dc gain will change between  $(1+\epsilon_g)$  and  $(1-\epsilon_g)$ , meaning that the input signal will be multiplied by a sine wave at  $f_s/2$  with amplitude equal to  $\epsilon_g$ . Due to the multiplication, the resulting tones will appear at  $f_s/2 \pm f_{in}$ , resulting in an SNDR given by:

$$SNDR = \frac{(V_{FS}/2).^2/2}{(V_{FS}.\epsilon_g/2)^2/2} = \frac{1}{\epsilon_g^2}$$

$$SNDR_{dB} = -20 \cdot log(\epsilon_g)$$

(2.15)

The effect of the gain error may also be considered statistically. It may be proven that, assuming the gain error has a random distribution with Gaussian PDF, the SNDR is given by [31,32]:

$$SNDR \approx \frac{M}{M-1} \cdot \frac{1}{\sigma_g^2}$$

(2.16)

$$SNDR_{dB} \approx -10 \cdot \log\left(\frac{M-1}{M} \cdot \sigma_g^2\right)$$

Figure 2.5: Effect of gain mismatch on SNDR of signal.

Where  $\sigma_g$  is the standard deviation of the gain error.

The effect of gain mismatch is simulated similar to the offset error case, and the results are shown in Fig. 2.5. As equation 2.16 suggests, the SNDR will have some dependence on the time interleaving factor. However, as the interleaving factor increases, the gain error effect becomes less dependent on the interleaving factor, and the SNDR approaches that of the worst case, showing a behavior similar to the offset error. The time interleaving dependence results in an SNDR difference of 3dB between M=2 and  $M=\infty$ . Compared to the theoretical SNDR calculated by equations 2.15 and 2.16, the transient results match perfectly. The gain error is neither dependent on the input full-scale voltage nor the input frequency. In general, the gain error results in tones at  $(i/M)f_s \pm fin$ , where i=0,1,2,...M/2 [28].

### 2.2.3 Bandwidth Mismatch Error

Unlike dc gain error, bandwidth error will affect both the magnitude and the phase of the input signal. In order to find the effect of bandwidth error on SNDR, a single-pole system is assumed, where the nominal gain and phase are given by [33]

$$A(\omega) = \frac{1}{\sqrt{1 + (\omega/\omega_B)^2}}$$

$$\Phi(\omega) = -tan^{-1}(\frac{\omega}{\omega_B})$$

(2.17)

Where  $\omega_B$  is the bandwidth. Now, in order to find error due to bandwidth mismatch, the gain and phase errors are calculated as follows:

$$\frac{\Delta A}{\Delta \omega_B} = \frac{A}{\omega_B} \cdot \frac{(\omega/\omega_B)^2}{1 + (\omega/\omega_B)^2}$$

(2.18)

$$\frac{\Delta t}{\Delta \omega_B} = \frac{1}{\omega_B} \frac{\Delta \Phi}{\Delta \omega_B} = \frac{1}{\omega_B^2} \cdot \frac{1}{1 + (\omega/\omega_B)^2}$$

(2.19)

The error due to bandwidth mismatch may be expressed as [33]:

$$e(t) = (A + \Delta A) \cdot V_{in}(t + \Delta t) - A \cdot V_{in}(t) \approx \Delta A V_{in}(t) + A \frac{\partial V_{in}}{\partial t} \Delta t$$

(2.20)

For a sinusoidal input this reduces to:

$$e(t) \approx V_{in}(t) \cdot (\Delta A + j\omega A \Delta t)$$

(2.21)

The SNDR may be written as:

Figure 2.6: Effect of bandwidth mismatch on SNDR of signal.

$$SNDR = \frac{A^2}{\Delta A^2 + (\omega A \Delta t)^2}$$

(2.22)

Substituting from 2.18 and 2.19 and simplification finally gives:

$$SNDR = \left(\frac{\omega_B}{\Delta\omega_B}\right)^2 \cdot \frac{1 + (\omega/\omega_B)^2}{(\omega/\omega_B)^2}$$

$$SNDR_{dB} = -20 \cdot log\left(\frac{\omega \cdot \Delta\omega_B/\omega_B^2}{\sqrt{1 + (\omega/\omega_B)^2}}\right)$$

(2.23)

As with the previous two errors, the effect of bandwidth mismatch on SNDR is simulated in MATLAB using transient simulations to verify the theoretical equation. Assuming the error condition where the bandwidth toggles between  $\omega_B \cdot (1 \pm \Delta \omega_B)$ ,

the SNDR is plotted against the bandwidth error, and the results are shown in Fig. 2.6 for different bandwidth to input frequency  $(\omega_B/\omega)$  ratios. As this ratio increases, suggesting higher system bandwidth, the effect of bandwidth mismatch errors is reduced, resulting in better SNDR. Results from equation 2.23 are also plotted, showing perfect matching with the simulation results. As the equation suggests, no dependence on the time interleaving factor is observed. Note that this error scenario does not cause worst case condition here, where for the bandwidth error, worst case is expected when the bandwidth mismatch results in the minimum bandwidth for all the channels.

Now, if a Gaussian random distribution of the mismatch error is assumed, the SNDR is expected to depend on the time interleaving factor similar to the gain error case. By modifying equation 2.23 to include the time interleaving factor similar to equation 2.16, the SNDR becomes:

$$SNDR = \frac{M}{M-1} \cdot \left(\frac{\omega_B}{\sigma_{\omega_B}}\right)^2 \cdot \frac{1 + (\omega/\omega_B)^2}{(\omega/\omega_B)^2}$$

$$SNDR_{dB} = -20 \cdot \log\left(\sqrt{\frac{M-1}{M}} \cdot \frac{\omega \cdot \sigma_{\omega_B}/\omega_B^2}{\sqrt{1 + (\omega/\omega_B)^2}}\right)$$

(2.24)

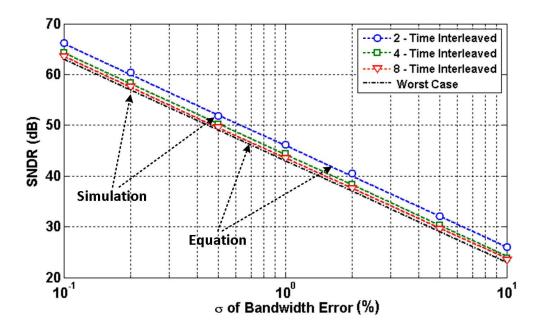

Where  $\sigma_{\omega_B}$  is the standard deviation of the random mismatch error. Transient simulation are performed with the random mismatch, and the results are plotted in Fig. 2.7, assuming  $\omega = \omega_B$ . The results show very good matching between the simulations and equation 2.24. Similar to the gain error case, as the number of interleaving channels increases, the SNDR becomes less dependent on the interleaving factor, and approaches that of equation 2.23. In general, the bandwidth mismatch depends on the input frequency, but is independent on the input amplitude. Similar to the gain mismatch case, bandwidth mismatch results in tones at  $(i/M) f_s \pm fin$ ,

Figure 2.7: Effect of statistical bandwidth mismatch on SNDR of signal.

where i = 0, 1, 2, ...M/2.

## 2.2.4 Timing Mismatch Error

The effect of timing mismatch is very similar to that of sampling jitter, where the sampling instants are modulated by the skew errors. Unlike the error due to jitter, the timing mismatch error is deterministic. Assuming a worst case scenario, where the timing skew of each channel toggles between  $\pm \Delta \tau$ , this is equivalent to full rate sampling with a clock that has a period toggling between  $T - \Delta \tau$  and  $T + \Delta \tau$ . Following a similar approach to the one used for equation 2.3, the SNDR can be written as:

$$SNDR = \frac{A^2/2}{A^2 \omega_{in}^2 \Delta \tau^2/2} = \frac{1}{\Delta \tau^2 \omega_{in}^2}$$

$$SNDR_{dB} = -20 \cdot log(\Delta \tau \omega_{in})$$

(2.25)

Comparing this result to that of equation 2.4 for the case of random jitter, the two equations are very similar to each other.

The effect of timing mismatch may also be treated statistically. It can be proven [34] that the SNDR with random timing mismatch effect may be written as:

$$SNDR \approx \frac{M}{M-1} \cdot \frac{1}{R_x''(0) \cdot \sigma_\tau^2}$$

(2.26)

Where  $R_x(.)$  is the autocorrelation function of the input and  $\sigma_{\tau}$  is the standard deviation of the timing error. For a sinusoidal input,  $R''_x(0) = \omega_{in}^2$ , and the SNDR may be written as:

$$SNDR \approx \frac{M}{M-1} \cdot \frac{1}{\omega_{in}^2 \sigma_{\tau}^2}$$

$$SNDR_{dB} \approx -10 \cdot log \left(\frac{M-1}{M} \cdot \omega_{in}^2 \sigma_{\tau}^2\right)$$

(2.27)

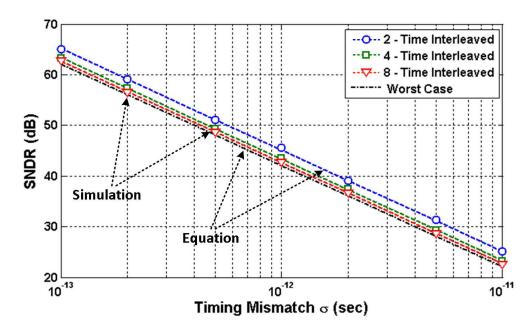

From equation 2.26, it may be concluded that the timing mismatch error follows similar dependence on interleaving factor to that of gain or bandwidth errors, and as the interleaving factor increases, the expression in equation 2.27 approaches that of equations 2.25.

The MATLAB model is used to validate the results obtained in equation 2.27, and the waveforms are shown in Fig 2.8, showing perfect matching between simulations and theoretical equations. In general, similar to gain and bandwidth errors, the

Figure 2.8: Effect of timing skew mismatch on SNDR of signal.

timing mismatch errors depend on the input frequency and is independent on its amplitude. The error results in tones at  $(i/M)f_s \pm fin$ , where i = 0, 1, 2, ...M/2 [28].

## 2.3 Multi-Phase Generation and Timing Skew Calibration

One of the critical blocks in the design of time interleaving ADCs is the clock generation circuit. An M-channel time interleaved architecture requires M evenly spaced phases each running at  $f_s/M$ . Due to process variations and other systematic errors, the clock phases are skewed and require calibration. As discussed in the previous section, unlike offset and gain mismatches which are static errors, meaning that they are independent on the input frequency, the timing skew error is dynamic, making it harder to calibrate. In this section, different architecture for multi-phase clock generation and clock skew detection and correction methods are discussed.

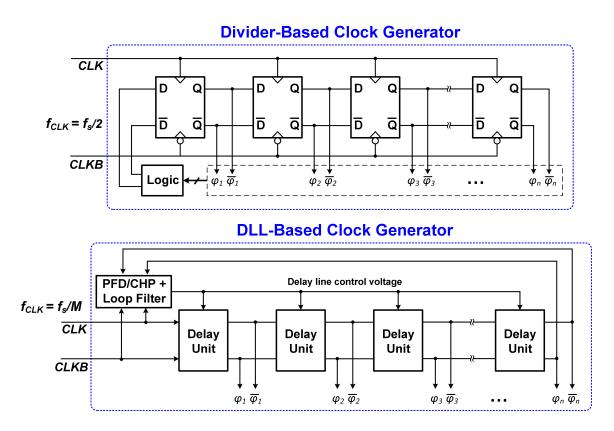

Figure 2.9: Block diagrams of divider-based and DLL-based clock generators

#### 2.3.1 Multi-Phase Clock Generation

Different methods exist for multi-phase generation [35]. Two of the famous methods are DLL-based and divider-based phase generators. Simplified block diagrams of the two architectures are shown in Fig. 2.9. For the divider-based generator, an input clock at full sampling rate  $f_s$  is synchronously divided by M to generate the time interleaving phases. For the case of fully differential implementation, like the one shown in the figure, two phase of clock at half the sampling rate  $f_s/2$  can be used instead, as long as 50% duty cycle is guaranteed. The DLL-based phase generator, on the other hand, does not require a full rate clock, where the delay of a voltage controlled delay line is locked to generate the required phases. It was proven, however,

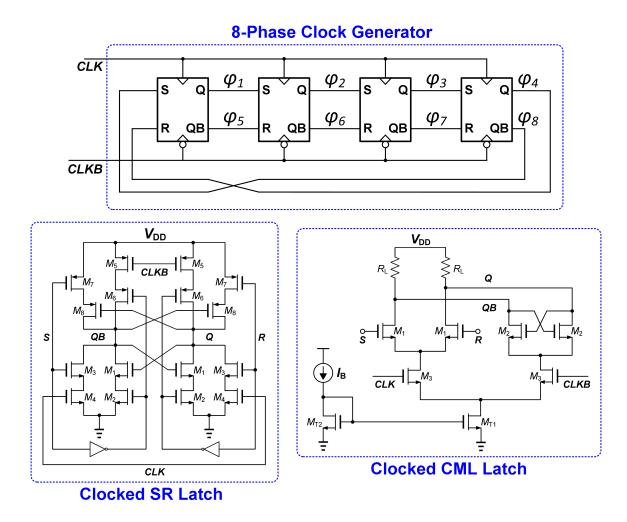

Figure 2.10: An example of divider-based 8-phase clock generator, showing two different realizations of clocked SR latch

that the divider-based architecture out-performs the DLL-based in many cases [36]. One reason is that the DLL architecture suffers from jitter accumulation through the delay line, which is not a problem in the divider-based architecture, since the phase is reset every clock edge. Another advantage of the divider-based generator is that it usually has a wider operating range, since no delay-tuned elements are required which usually have limited delay range.

An example of an 8-phase clock phase generator using the divider-based architec-

ture is shown in Fig. 2.10, using SR latches. Depending on the operating frequency, two different implementations of the SR latch is shown. In the first realization, the SR latch is a modified version of the balanced SR latch presented in [37] is used, where clocking controls are added to the latch. By utilizing the balanced latch architecture, a fully differential implementation of the divider is possible. This clock phase generator is used for two 6 bit 10GS/s time interleaved SAR ADCs [14,20]. In the second realization, a CML architecture is used to enable higher speed operation, where the phase generator is used for a 6 bit 25GS/s binary-search ADC [9].

#### 2.3.2 Clock Skew Detection and Correction

Many techniques exist in the literature for detection and correction of the timing skew error. Those techniques may be divided into three categories [38]: all analog methods [39], in which both the detection and correction are realized in the analog domain, all-digital methods [40] in which the process is fully realized in the digital domain and mixed mode techniques that usually combine digital detection and analog correction. The third method is the most common one, since analog detection of timing skew is susceptible to PVT variations, making it very hard to detect skew errors in the order of sub-picoseconds. All-digital detection performs the skew detection in the digital domain, allowing it to detect skew errors at much higher accuracies. The correction, however, is also implemented in the digital domain, requiring complex fractional filters to interpolate between already sampled data points. The mixed-mode method performs the digital detection, and corrects the phases by adjusting the delay of digitally-controlled variable delay elements, which corrects the clock phases before the input is sampled.

Different methods have been proposed to perform the digital skew detection. Since the skew error results in tones in the output spectrum, one method is to use the output spectrum with a known sinusoidal input to extract the timing information [41, 42]. A main drawback of this method is that it can only be performed as a foreground calibration, since a well-defined sinusoidal input signal is required. Another drawback is that the implementation of the FFT to extract the spectrum of the output is not straight forward. A simpler detection method is to use code density test (CDT) to measure the phase spacing between every two adjacent phases [43]. Here, an asynchronous input signal is applied, and a histogram counter is used to count the input signal edge transitions between every two adjacent sampling clocks [44]. Since the input is asynchronous with respect to the sampling clocks, the number of counted transitions is proportional to the spacing between the two phases. Although this implementation is simpler, it still needs an asynchronous input, making it suitable for foreground calibration only.

To enable background calibration, a correlation-based detection method was proposed in [45], where an extra reference sub-ADC channel is used, and the cross-correlation between the output of every interleaved channel and the reference channel is maximized through a calibration loop, which is equivalent to the two sampling phases being aligned. Another method, also based on correlation, was later proposed, which requires no extra reference channel [46]. Instead of calculating the cross-correlation with a reference signal, the auto-correlation functions of the input at two consequent sampling instants are calculated. The difference between those two auto-correlation functions is finally used to extract the skew information [46].

### 2.4 Equalization in High Speed Links Applications

The bandwidth of electrical interconnects is generally limited by high frequency loss of electrical traces, reflections due to impedance mismatches and cross-talk of adjacent signal traces [47], as shown in Fig. 2.11, for an example of a backplane

Figure 2.11: Cross-section of backplane system.

channel system. Skin effect and dielectric losses of the PCB traces cause frequency dependent attenuation or dispersion, resulting in signal attenuation at high frequencies. The skin effect describes the current crowding near the conductor surface, which results in a resistive loss proportional to the square root of the frequency [48]. The loss factor due to the skin effect may be written as [49]:

$$\alpha_R = \frac{\sqrt{\pi\mu\rho}}{4Z_0 w} \sqrt{f} \tag{2.28}$$

Where  $\mu$  is the magnetic permeability,  $\rho$  is the conductor resistivity and w is the width of the wire, assuming rectangular strip wire.

Dielectric loss describes the loss due to dissipation of energy in the dielectric material, mathematically expresses as an imaginary part to the dielectric permittivity. This results in a loss term proportional to the frequency of the signal [49]. The loss factor may be given as:

$$\alpha_D = \frac{\pi \sqrt{\epsilon_r} tan\delta_D}{c} f \tag{2.29}$$

Where  $\epsilon_r$  is the relative dielectric permittivity, c is the speed of light and  $tan\delta_D$  is the loss tangent of the dielectric material.

Impedance discontinuities due to PCB trace vias or other non-ideal matching conditions result in signal reflections. If the source termination is not perfectly matched, the reflection may bounce back and fourth between the source and the discontinuity giving rise to multiple reflections, which appear at the receiver end as attenuated replicas of the transmitted signal, causing interference errors. Capacitive and inductive coupling of adjacent traces generate cross-talk errors, which may be caused by near-end (NEXT) aggressors or far-end (FEXT) aggressors [50], also giving rise to interference errors. In practice, cross-talk can be a major limit to high speed link scaling [47], where the cross-talk energy may exceed the through channel signal energy, requiring the use of cross-talk cancellation techniques [51].

Fig. 2.12(a) shows the frequency dependence of channel loss for three different backplane channels, two with smooth responses and one with a frequency notch. The 10GS/s pulse responses of the channels are also shown. It may be concluded from the figure that the channel with the longer trace has higher attenuation, which translates into a wider or "more dispersed" shape of the pulse response. In addition, the channel with the frequency null, which usually appears due to signal reflections, has worse pulse response. Instead of a single pulse, the dispersed pulse response has pre-cursor and post-cursor components in addition to its main cursor. Those components interfere with the previous and following data symbols, causing the so called inter-symbol interference (ISI). This is demonstrated in Fig 2.12(b), where the pattern "101" is transmitted through the 20-inch smooth channel, and the output is shown in the figure. The ISI error may cause the middle 0 symbol to be misinterpreted as a 1 symbol, resulting in a potential bit error.

Figure 2.12: (a) Channel and pulse responses for three backplance channels, and (b) Error due to inter-symbol interference (ISI) effect

### 2.4.1 Equalization Techniques

In order to extend the bandwidth of electrical channels to enable high speed operation, signal equalization is usually employed to cancel the effect of ISI. Equalizers can be implemented as linear or non-linear filters, can have continuous time or discrete time implementations and may be placed at the transmitter side or at the receiver side. In the following discussion, Two main types of equalizers, the feed-forward equalizer (FFE) and decision feedback equalizer (DFE) are considered. Another type of linear equalizer, the continuous-time linear equalizer (CTLE), is also common at the receiver side, where an active or passive filter implements a high-pass function to equalize the signal. The equalization achieved by CTLE is usually limited

Figure 2.13: Block diagram of (a) N-tap FFE and (b) N-tap DFE equalization.

to first order compensation. In addition, the operating speed is limited by the gain-bandwidth product of the amplifier, which may result in increased power dissipation to achieve high speed operation. As a continuous time system, the CTLE may also be very sensitive to process, voltage and temperature (PVT) variations, requiring some form of tuning for proper operation [52].

### 2.4.1.1 Feed-Forward Equalization (FFE)

In the feed-forward type of equalization, time delayed and scaled versions of the signal are used to implement a finite impulse response (FIR) filter to equalize the channel, as shown in Fig. 2.13(a). The FFE may be implemented at the transmitter side, usually called TX-FIR, which provides pre-emphasis to the signal before the channel. One limitation of the TX-FIR is the peak power constraint of the transmitter swing [53], which means that in order to achieve high frequency boosting, the low frequency components of the signal are attenuated. Another disadvantage is that the equalization occurs before the channel, which means that adaptive equalization can not be used to optimize for the TX-FIR taps, unless a back-channel is provided which is not generally available.

At the receiver side, the FFE equalization can either use an analog or a digital implementation. With an analog FFE implementation, the received analog signal is

delayed using delay cells and scaled by the equalizer coefficient. This architecture is usually used to implement fractionally spaced filters [54,55]. With enough dynamic range, this filter may boost the high frequency content of the signal rather than attenuate the low frequency components. The filter taps may also be adaptively tuned without the need of a back-channel, since the signal equalization is implemented after the channel. The realization of the analog delay cells and tap coefficients may be an issue, since they would be susceptible to PVT variations. A digital FFE implementation, on the other hand, provides robustness to PVT variations, but requires an analog-to-digital converter (ADC) at the receiver front-end.

In general, due to its linear implementation, the FFE equalizer suffers from the issue of noise amplification, where the noise and cross-talk is amplified along with the signal. Even in the case of digital FFE implementation, the FFE equalizer will amplify the quantization noise added to the signal due to the ADC quantization.

## 2.4.1.2 Decision Feedback Equalization (DFE)

Unlike FFE, the DFE is a nonlinear equalizer which works to directly subtract the post-cursor ISI components of the signal, as shown in Fig. 2.13 (b). The DFE therefore does not suffer from the noise amplification problem, since symbol decisions are made before subtraction of the ISI. The DFE, however, suffers from critical feedback timing limitations, where the feedback loop elements need to be fast enough to close the loop timing before the next symbol arrives. Speculation may be used to relax the timing constraints, where the DFE taps are loop-unrolled to implement all possible coefficient cases, and the proper case is selected based on the previous symbols through a multiplexer [56]. The complexity of the system grows exponentially with the number of unrolled taps, limiting the number of DFE taps that may be speculated.

Figure 2.14: Eye diagram for the three backplance channels of fig 2.12 (a) under different equalization condition.

To demonstrate the effect of equalization on the received signal, the three channels of Fig. 2.12 are simulated with random data input, and the output eye-diagrams are shown in Fig. 2.14 for different equalization scenarios. First, with no equalization, only the lowest-loss 8-inch channel shows an open eye, while the eye is closed for the other two 20-inch channels. Adding 2 taps of FFE equalization, the voltage margin for the first channel improves significantly, and an open eye may be obtained for the smooth 20-inch channel. However, for the 20-inch notch channel, the eye is still closed. Combining 2 taps of FFE with 2 taps of DFE finally results in an eye opening for the highest loss channel, while further improving the eye opening for the other two channels.

#### 3. STATISTICAL MODELING OF ADC-BASED RECEIVERS\*

As data rates for serial I/O links increase, operation over standard legacy channels becomes more challenging due to excessive frequency-dependent channel attenuation, which causes large amounts of inter-symbol interference (ISI). In order to operate reliably over such channels at high data rates, equalizer circuits in the form of continuous time linear (CTLE), feed-forward (FFE) or decision-feedback (DFE) equalizers are usually employed [6]. While analog equalization can allow for increased system data rate, there has been on-going interest in ADC-based high-speed links (Fig. 3.1), where CMOS technology scaling allows for the efficient implementation of powerful on-chip digital signal processing (DSP) algorithms for equalization and symbol detection [2,57]. This digital equalization offers robustness to PVT variations and is easier to re-configure than mixed-signal equalization circuitry. Moreover, ADC-based receivers also enable more spectrally-efficient modulation schemes such as duo-binary and PAM4, and more complicated equalization strategies such as sequence estimation.

Despite these advantages, ADC-based receivers are generally more complex and consume higher power than binary receivers [58]. Even with state of the art multi-GS/s ADC implementations, power is often prohibitive for many systems where link power efficiency is the key metric. The digital equalization that follows the ADC can also consume significant power, comparable to the power of the ADC [2]. To enable

<sup>\*© 2013</sup> IEEE. Part of section 3.3 is reprinted, with permission, from E. Zhian Tabasy, A. Shafik, S. Huang, N.-W. Yang, S. Hoyos, and S. Palermo, "A 6-b 1.6-GS/s ADC with redundant cycle one-tap embedded DFE in 90-nm CMOS," IEEE J. Solid-State Circuits, vol. 48, no. 8, pp. 1885–1897, Aug. 2013.

<sup>\*© 2014</sup> IEEE. Part of section 3.3 is reprinted, with permission, from E. Zhian Tabasy, A. Shafik, K. Lee, S. Hoyos, and S. Palermo, "A 6 bit 10 GS/s TI-SAR ADC with low-overhead embedded FFE/DFE equalization for wireline receiver applications," IEEE J. Solid-State Circuits, vol. 49, no. 11, pp. 2560–2574, Nov. 2014.

Figure 3.1: Block diagram of a high speed link with ADC-based receiver.

ADC-based receivers for these systems, a fast and reliable analysis tool is required to rapidly investigate trade-offs in system complexity and performance, in order to arrive at optimal ADC resolution and digital equalizer complexity requirements. The tool may also be useful in studying the effectiveness of system and circuit techniques used to save power in ADC-based receivers such as partial analog pre-equalization [14].

The growing complexity of high speed links systems made it impractical to use time domain Monte Carlo (transient) simulations alone to predict the system performance, where the number of bits required to validate typical bit error rate (BER) requirements ( $< 10^{-12}$ ) becomes prohibitive. On the other hand, worst case analysis methodologies such as peak distortion analysis are often pessimistic and result in over design. For these reasons, most of today's high speed link simulation tools use statistical models to predict performance metrics such as BER without the need for lengthy bit-by-bit simulations [18, 19].

While these statistical tools are growing mature for binary links, conventional modeling approaches for ADC-based receivers and digital equalization use ADC performance metrics based on mean-square error (MSE), such as signal-to-noise and distortion ratio (SNDR) or effective number of bits (ENOB) [59, 60]. Currently, high-speed link analysis tools are unable to model ADC-related non-idealities such

Figure 3.2: Statistical simulation framework.