# CLASS-G HEADPHONE AMPLIFIER ARCHITECTURES

# A Thesis

by

# BHARADVAJ BHAMIDIPATI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2010

Major Subject: Electrical Engineering

# CLASS-G HEADPHONE AMPLIFIER ARCHITECTURES

#### A Thesis

by

# BHARADVAJ BHAMIDIPATI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

Approved by:

Chair of Committee, Edgar Sánchez-Sinencio Committee Members, Hamid A. Toliyat

Samuel Palermo

Duncan Henry M. Walker

Head of Department, Costas N. Georghiades

December 2010

Major Subject: Electrical Engineering

#### ABSTRACT

Class-G Headphone Amplifier Architectures. (December 2010)

Bharadvaj Bhamidipati, B.E. (Hons.), Birla Institute of Technology & Science,

Pilani, India.

Chair of Advisory Committee: Dr. Edgar Sánchez-Sinencio

To maximize the battery life of portable audio devices like iPods, MP3 players and mobile phones, there is a need for audio power amplifiers with low quiescent power, high efficiency along with uncompromising quality (Distortion performance/THD) and low cost. Despite their high efficiency, Class-D amplifiers are undesirable as headphone drivers in mobile devices, owing to their high EMI radiation, additional costs due to filtering required at the output and also their poor linearity at small signal levels. Almost all of todays headphone drivers are Class-AB linear amplifiers, with poor efficiencies.

Here we propose a Class-G linear amplifier, which uses rail switching to improve efficiency. It can be viewed as a Class-AB amplifier operating from the lower supply and a Class-C amplifier from the higher supply. Though the classical definition of efficiency using full-scale sine wave does not show much improvement for Class-G (85.9%) over Class-AB (78%), we demonstrate that the Class-G audio amplifiers can have significant improvement of efficiencies (battery life) in the practical sense. By considering the amplitude distribution of audio signals a new realistic definition of efficiency has been proposed. This definition helps in demonstrating the advantage of using Class-G over Class-AB and also helps in optimizing the choice of supply voltages which is critical to maximizing the efficiency of Class-G amplifiers.

Two new circuit topologies have been proposed and thoroughly investigated.

The first circuit is more like a developmental stage and is designed/fabricated in AMI 0.5um. The second proposed Class-G amplifier with modified Class-AB bias, implemented in IBM 90nm, achieves -82.5dB THD+N by seamless supply switching and uses the least reported quiescent power (350 $\mu$ W) and area (0.08mm<sup>2</sup>).

То

my parents Sujatha and Rama Sastry my sister Srivani

and

my girlfriend Veena

#### ACKNOWLEDGMENTS

First of all, I want to thank my advisor, Dr. Sánchez-Sinencio, for all the motivation and support he has provided. I feel extremely fortunate to be the student of a great visionary. I express my deepest gratitude to him for being very demanding and also understanding the hectic class/work schedules, extracting the best out of me.

I also want to thank Prof. Hamid A. Toliyat, Dr. Samuel Palermo and Prof. Duncan Henry M. Walker for serving on my degree committee and reviewing my work.

Thanks to Ella and Tammy for their prompt help with all the paper work.

I am grateful to MOSIS and IBM for providing fabrication support. I also want to thank John Tucker of Cirrus Logic for his very useful suggestions on the practical aspects of audio amplifier design.

Someone who needs a special mention is my teacher, Mr. Anurup Mitra at BITS, Pilani, for being an inspiration to me and many others to pursue a career in analog design. The insights he has given me have been invaluable in understanding and working with circuits.

Special thanks to Adrian Colli and Joselyn Torres for working with this project in 90nm technology while I was away. The discussions on amplifier compensation with Seenu proved very useful. It would have been impossible to finish the project in time without Reza's layout help. Without Felix's help in setting up the technologies, making the submission, testing and using the equipment, it would have been impossible to finish the work on time.

Analog design is not just about having great ideas and intuitive understanding. It also needs a lot of experience along with expertise. The elderly advice of Felix, Didem,

El-Nozahi, Mostafa, Mohsen, Raghavendra and Mandar had a significant contribution towards my learning at A&M. Not to forget the various technical discussions with peers/colleagues Jorge, Jin, Chao, Salvador, Viva, Mohan and Srikanth has been of vital importance for my success at A&M.

The company of my room mates and friends Shiva, Vivek, Raj, Vinay and Gupta has made my two year stay at A&M memorable. The motivation and moral support from my friends Vikram, Vikas and Deepthi during the tough times have helped me to remain focussed on my work.

Finally, the unconditional love that I receive from my family has been, and will be, the driving force that keeps me moving ahead in all walks of life.

# TABLE OF CONTENTS

| CHAPTER |                                                     | Page |

|---------|-----------------------------------------------------|------|

| I       | INTRODUCTION                                        | . 1  |

|         | A. Audio power amplifiers                           | . 1  |

|         | B. Brief history of audio amplifiers                |      |

|         | C. Classification of audio power amplifiers         |      |

|         | 1. Class-A                                          | . 4  |

|         | 2. Class-B/AB                                       | . 5  |

|         | 3. Class-C                                          | . 6  |

|         | 4. Note on Class-A/AB/B/C                           | . 7  |

|         | 5. Class-D                                          |      |

|         | 6. Class-G                                          |      |

|         | D. Portable electronics: The place for Class-G      |      |

|         | E. Scope of this work                               | . 13 |

| II      | TRUE EFFICIENCY OF AN AUDIO POWER AMPLIFIER         | . 14 |

|         | A. Classical efficiency                             | . 14 |

|         | 1. Class-A                                          |      |

|         | 2. Class-B/AB                                       | . 17 |

|         | 3. Class-G                                          | . 19 |

|         | 4. Multi-level Class-G                              | . 20 |

|         | 5. Class-D                                          | . 21 |

|         | 6. Class-H                                          | . 22 |

|         | B. Crest factor of audio signals and its importance | . 23 |

|         | C. True efficiency                                  | . 24 |

|         | 1. Instantaneous efficiencies of Class-AB/G/D       | . 24 |

|         | 2. Amplitude distribution function of some typical  |      |

|         | audio signals                                       |      |

|         | 3. Power efficiency formula                         |      |

|         | 4. Comparison of practical efficiencies             |      |

|         | 5. Note on audio volume and efficiency              | . 34 |

| III     | CLASS-G AMPLIFIERS                                  | . 36 |

|         | A. Previous work on Class-G                         | . 36 |

|         | B. Series Vs Parallel Class-G structures            | . 40 |

| CHAPTER  |                                                                 | Page |

|----------|-----------------------------------------------------------------|------|

|          | C. Class-AB: The corner stone for Class-G                       | 41   |

|          | 1. Brief look at various Class-AB output stages                 | 43   |

|          | D. Important design choices                                     | 46   |

|          | 1. $V_{DSAT}$ of smaller drivers                                | 46   |

|          | 2. Smaller supply and instantaneous efficiency                  | 48   |

|          | 3. Number of supply levels (Multi-level Class-G)                | 50   |

|          | E. Linearity                                                    | 50   |

|          | F. SR of amplifier and comparators                              | 53   |

| IV       | CLASS-G IMPLEMENTATION                                          | 54   |

|          | A. Circuit topology 1                                           | 54   |

|          | 1. Design and working                                           | 54   |

|          | 2. SNR and noise requirements                                   | 58   |

|          | 3. Step by step sample design procedure                         | 59   |

|          | 4. Results of implementation in ami 0.5um technology            | 60   |

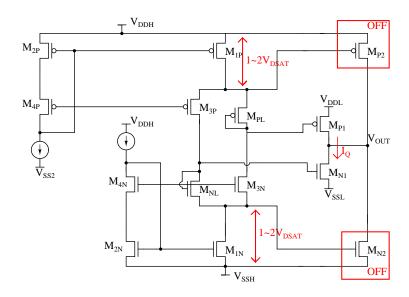

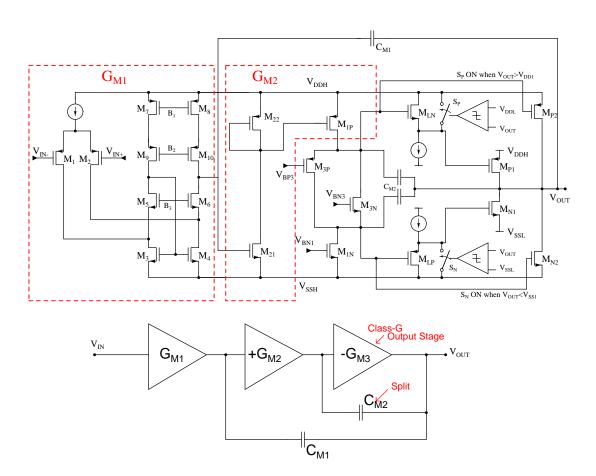

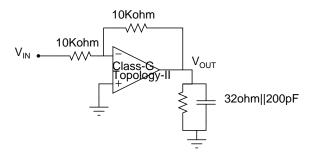

|          | B. Circuit topology 2                                           | 65   |

|          | 1. Modified Class-AB bias                                       | 65   |

|          | 2. Design and working                                           | 68   |

|          | 3. Results of implementation in ami $0.5\mathrm{um}$ technology | 70   |

|          | 4. Results of implementation in IBM 90nm technology .           | 74   |

|          | C. Comparison of results with state-of-the-art                  | 76   |

|          | D. Conclusion                                                   | 79   |

|          | E. Future work                                                  | 81   |

| REFERENC | CES                                                             | 82   |

| VITA     |                                                                 | 96   |

# LIST OF TABLES

| TABLE |                                                                                      | Page |

|-------|--------------------------------------------------------------------------------------|------|

| I     | Summary of Class-A, AB, B, C output stage operation                                  | 8    |

| II    | Example demonstrating the power efficiency formula                                   | 34   |

| III   | Comparison of efficiencies of Class-AB/G/D with application of typical audio signals | 35   |

| IV    | $V_{DSAT}$ and $I_Q$ trade-off                                                       | 48   |

| V     | Two level supply vs three level supply comparison                                    | 50   |

| VI    | Simulation and experimental results of circuit topology-1                            | 64   |

| VII   | Experimental results of circuit topology-2 in ami $0.5\mathrm{um}$ technology .      | 75   |

| VIII  | Experimental results of circuit topology-2 in IBM 90nm technology .                  | 78   |

# LIST OF FIGURES

| FIGUR | E                                                                        | Page |

|-------|--------------------------------------------------------------------------|------|

| 1     | Typical Class-A amplifiers                                               | 4    |

| 2     | Typical Class-B amplifier                                                | 6    |

| 3     | Transfer characteristics of linear/pseudo-linear classes of amplifiers . | 7    |

| 4     | Typical Class-D amplifier                                                | 8    |

| 5     | Class-D amplifier using sliding mode control                             | 10   |

| 6     | Supply and output voltages in a Class-A amplifier                        | 16   |

| 7     | Supply and load currents in a Class-A amplifier                          | 16   |

| 8     | Supply and output voltages in a Class-AB amplifier                       | 18   |

| 9     | Supply and load currents in a Class-AB amplifier                         | 18   |

| 10    | Supply and output voltages in a Class-G amplifier                        | 20   |

| 11    | Supply and output voltages in a multi-level Class-G amplifier            | 21   |

| 12    | Class-G operation                                                        | 22   |

| 13    | Class-H operation                                                        | 23   |

| 14    | Class-AB amplifier block diagram                                         | 25   |

| 15    | Class-G amplifier block diagram                                          | 25   |

| 16    | Instantaneous efficiencies of ideal Class-AB/G amplifiers                | 26   |

| 17    | Instantaneous efficiencies of real Class-AB/G/D amplifiers               | 26   |

| 18    | Amplitude distribution function of sine wave                             | 28   |

| 19    | Amplitude distribution function of Signal 1                              | 29   |

| FIGURE | E                                                                     | Page |

|--------|-----------------------------------------------------------------------|------|

| 20     | Amplitude distribution function of Signal 2                           | 29   |

| 21     | Amplitude distribution function of Signal 3                           | 30   |

| 22     | Amplitude distribution function of Signal 4                           | 30   |

| 23     | Amplitude distribution function of Signal 5                           | 31   |

| 24     | Amplitude distribution function of Signal 6                           | 31   |

| 25     | Amplitude distribution function of Signal 7                           | 32   |

| 26     | Previous Class-G implementation-I                                     | 37   |

| 27     | Previous Class-G implementation-II                                    | 39   |

| 28     | Series and parallel type Class-G output stages                        | 40   |

| 29     | Shift-in type Class-G output stage                                    | 42   |

| 30     | Shift-out type Class-G output stage                                   | 43   |

| 31     | Source follower Class-AB output stage                                 | 44   |

| 32     | Class-AB output stage with error amplifiers and common source devices | s 45 |

| 33     | Effect of $V_{DSAT}$ of smaller drivers                               | 47   |

| 34     | Effect of smaller supply                                              | 49   |

| 35     | Audio amplifier block diagram                                         | 51   |

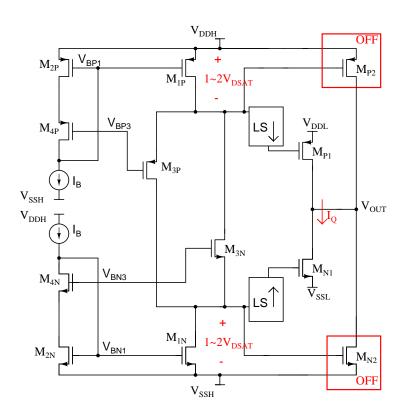

| 36     | Class-G circuit topology-1                                            | 55   |

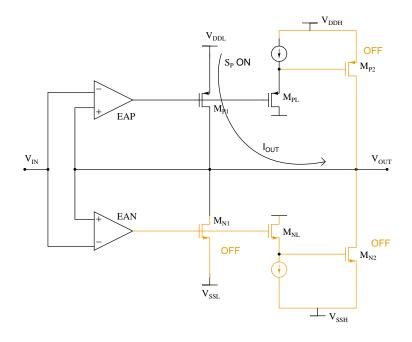

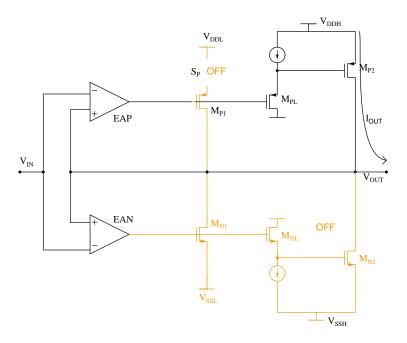

| 37     | Working of Class-G circuit topology-1 for $0 < V_{OUT} < V_{DDL}$     | 56   |

| 38     | Working of Class-G circuit topology-1 for $V_{OUT} > V_{DDL}$         | 56   |

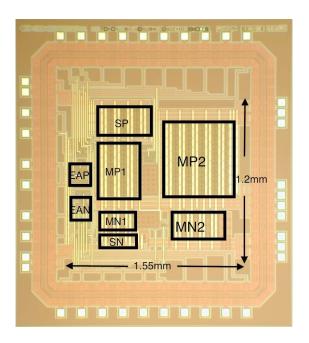

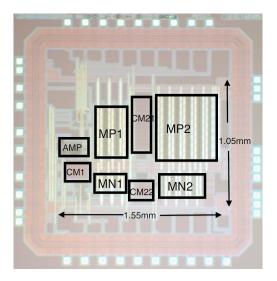

| 39     | Die micrograph of topology-1                                          | 61   |

| 40     | Test setup for topology-1                                             | 61   |

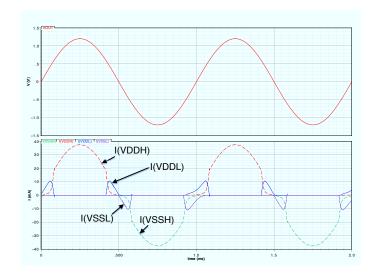

| 41     | Load currents from different supplies in topology-1                   | 62   |

| FIGUR | E                                                                           | Page |

|-------|-----------------------------------------------------------------------------|------|

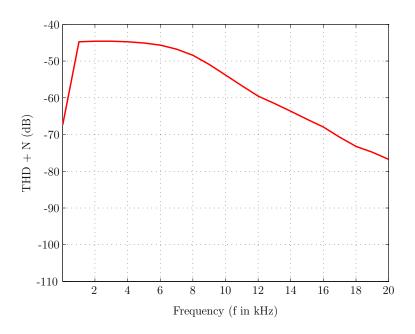

| 42    | THD+N vs. frequency of topology-1                                           | 63   |

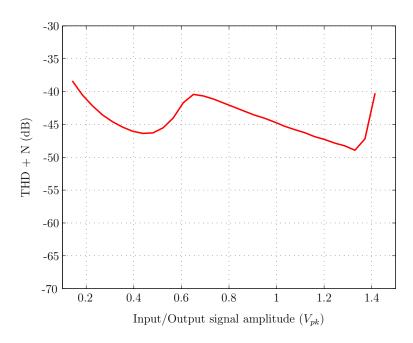

| 43    | THD+N vs. amplitude of topology-1                                           | 63   |

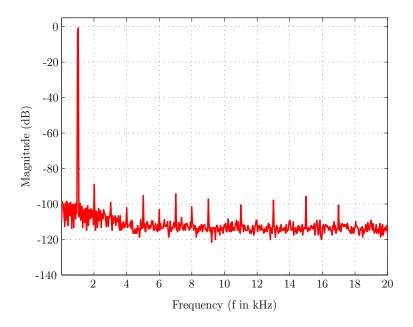

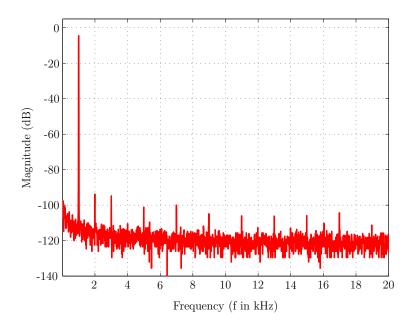

| 44    | FFT of topology-1 for $1.3V_{pk}$ input                                     | 64   |

| 45    | Class-AB Montecelli bias                                                    | 65   |

| 46    | Modified Class-AB bias 1 for Class-G                                        | 67   |

| 47    | Modified Class-AB bias 2 for Class-G                                        | 68   |

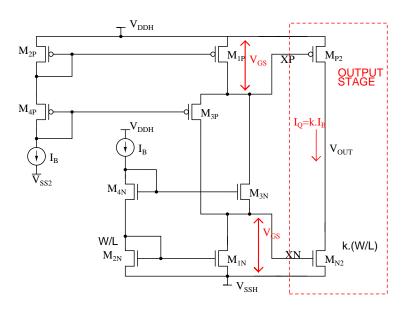

| 48    | Class-G circuit topology-2                                                  | 69   |

| 49    | Die micrograph of topology-2 in ami 0.5um technology                        | 70   |

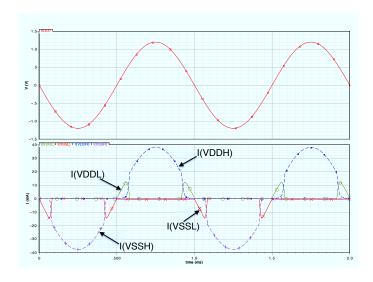

| 50    | Test setup for topology-2                                                   | 71   |

| 51    | Load currents from different supplies in topology-2 in ami 0.5um technology | 71   |

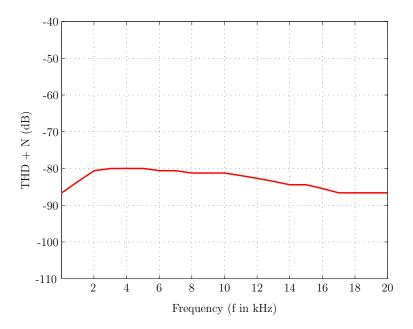

| 52    | THD+N vs. frequency of topology-2 in ami 0.5um technology                   | 72   |

| 53    | THD+N vs. amplitude of topology-2 in ami 0.5um technology                   | 73   |

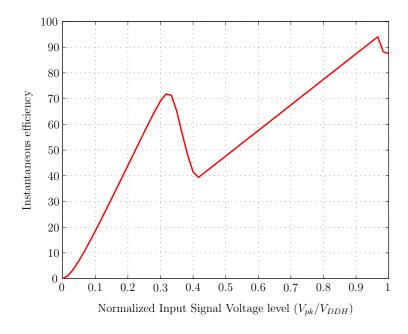

| 54    | Instantaneous efficiency of topology-2 in ami 0.5um technology              | 73   |

| 55    | FFT of topology-2 for $1.3V_{pk}$ input in ami 0.5um technology             | 74   |

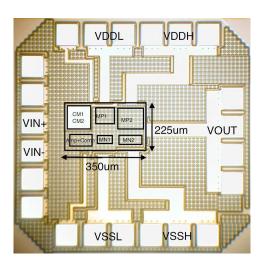

| 56    | Die micrograph of topology-2 in IBM 90nm technology                         | 75   |

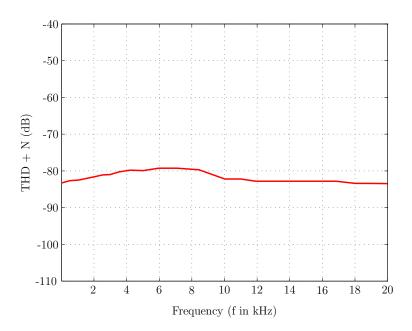

| 57    | THD+N vs. frequency of topology-2 in IBM 90nm technology                    | 76   |

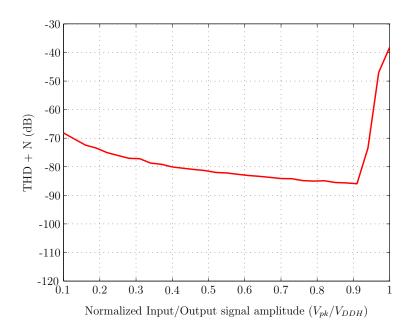

| 58    | THD+N vs. amplitude of topology-2 in IBM 90nm technology                    | 77   |

| 59    | Instantaneous efficiency of topology-2 in IBM 90nm technology $$            | 77   |

| 60    | FFT of topology-2 for $0.85V_{pk}$ input in IBM 90nm technology             | 78   |

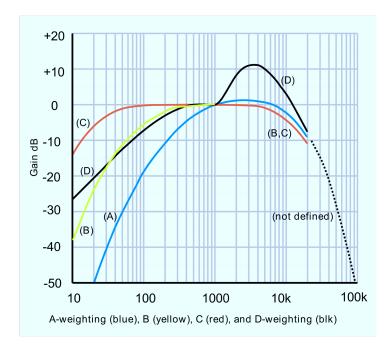

| 61    | A-weight filter                                                             | 79   |

| 62    | Comparison of results with state-of-the-art headphone drivers               | 80   |

### CHAPTER I

#### INTRODUCTION

#### A. Audio power amplifiers

An audio power amplifier is an electronic amplifier that amplifies low-power audio signals (signals composed primarily of frequencies between 20-20 KHz, the human range of hearing) to a level suitable for driving loudspeakers or other transducers like headphones and is the final stage in a typical audio playback chain. The preceding stages in such a chain are low power audio amplifiers, which perform tasks like pre-amplification, equalization, tone control, mixing/effects, or audio sources. Power amplifiers may have power ratings ranging from less than 100 mW to several hundreds of watts. Stereo amplifiers consist of two identical, but electrically independent, amplifier circuits housed in a single chassis, often sharing a common power supply.

The ideal amplifier delivers an output signal that, aside from its higher power level, is identical in relative spectral content to the input signal. In reality, the amplifier generates various forms of distortion: harmonic distortion (tones at multiples of the desired signal frequency), intermodulation distortion (spurious sum or difference frequencies created when multiple tones are applied to the amplifier simultaneously, as in the case of music or speech amplification), and transient intermodulation distortion (caused by rapid fluctuations of the input signal level). All forms of distortion are measured as percentages of the desired signal amplitude. Other parameters that are used to define an amplifier's characteristics include frequency response and signal-to-noise ratio in the audio band (SNR). While the above metrics define the quality of audio power amplifier, efficiency of the amplifier determines how efficiently the

The journal model is IEEE Transactions on Automatic Control.

amplifier can utilize the available power from the power supply, it is defined as the ratio of total power delivered to the load to total power consumed from all the power supplies.

#### B. Brief history of audio amplifiers

The first audio amplifier [1] was made in 1906 by a man named Lee De Forest and came in the form of the triode vacuum tube. This particular mechanism evolved from the audion, which was developed by De Forest. Unlike the triode, which has three elements, the audion only had two and did not amplify sound. Later on during the same year, the triode, a device with capability of adjusting the movement of electrons from a filament to a plate and thus modulating sound, was invented. It was vital in the invention of the first AM radio.

After World War II, there was a surging of technology because of the advancements developed during the war. The earliest kinds of audio amplifiers were made of vacuum tubes or valves. An example of these is the Williamson amplifier [1], which was introduced in 1946. At the time, this particular device was considered cutting edge and produced higher quality sound compared to other amplifiers available at the time. The market for sound amplifiers was robust and the valve-type devices can be owned at affordable rates. By the 1960s, gramophones and televisions made valve amplifiers quite popular.

By the 1970s, valve technology was replaced by the silicon transistor [1]. Although valves were not completely wiped out as evidenced by the popularity of the cathode ray tubes, which was used for amplifier applications, silicon transistors became more and more present. Transistors amplify sound by changing the voltage of the audio input through the use of semiconductors. The reasons for the preference of

transistors over valves were that they were smaller and thus more energy-efficient. In addition to these, they're also better at reducing distortion levels and were cheaper to make.

There is a lot of controversy [2], [3] over the superiority of vacuum tube audio amplifiers over the transistor ones. The complications and controversy stem from the fact that music is played for human beings to hear, whose nonlinear ear-brain hearing systems are far from fully understood. Since no one knows exactly how to model the human auditory system, no one knows exactly what engineering measurements are appropriate to evaluating the performance of audio equipment. A smidgen of some kinds of distortion may sound worse to the ear than larger amounts of other kinds. So ultimately, the only way to judge audio equipment is by listening to it. Hence the controversy: subjective human perception—especially when flanked by questions of artistic merit—is made to order for arguments and disputation.

Briefly stated, a commercially viable number of people find that they prefer the sound produced by tubed equipment [2], [3] in three areas: musical-instrument (MI) amplifiers (mainly guitar amps), some processing devices used in recording studios, and a small but growing percentage of high-fidelity equipment at the high end of the audiophile market. These areas employ vacuum tubes of the type once known as receiving tubes, but now called simply tubes. Not only has the use of vacuum tubes in these fields defied the semiconductor tide elsewhere, but such use and demand has even surged in the course of the 1990s. Even today in the era of portable music players many audiophiles relish the warmth of vacuum tube audio amplifiers.

### C. Classification of audio power amplifiers

For a long time the only amplifier classes relevant to high-quality audio were Class-A and Class-AB. This is because valves were the only active devices, and Class-B valve amplifiers generated so much distortion that they were barely acceptable even for public address purposes. All amplifiers with pretensions to high fidelity operated in pushpull Class-A. Solid-state gives much more freedom of design. We will see the meaning of Classes A, B/AB, D and G; and this certainly covers a vast majority of the solid-state amplifiers exploited commercially [4].

#### 1. Class-A

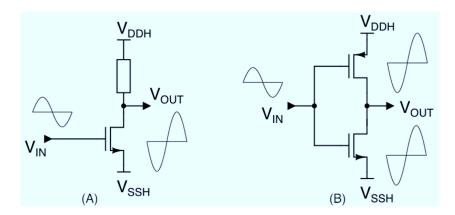

Fig. 1. Typical Class-A amplifiers

In a Class-A amplifier Fig. 1 current flows continuously in all the output devices, which enables the nonlinearities of turning them on and off to be avoided. Each of

the device conducts for the whole 360 degree phase of a sine wave. They come in two rather different kinds, although this is rarely explicitly stated, which work in very different ways.

One kind of Class-A stage Fig. 1B is simply a Class-B stage with sufficient current flowing for neither device to turn off under normal loading. The great advantage of this approach is that it cannot abruptly run out of output current; if the load impedance becomes lower than specified then the amplifier simply takes brief excursions into Class-AB, hopefully with a modest increase in distortion and no seriously audible distress.

The other kind Fig. 1A could be called the voltage controlled current source (VCCS) type, which is in essence a single common source with an active load sourcing/sinking the current. If this latter element runs out of current capability it makes the output stage clip much as if it had run out of output voltage. This kind of output stage demands a very clear idea of how low an impedance it will be asked to drive before the design begins.

#### 2. Class-B/AB

In a Class-B amplifier shown in Fig. 2 current flows exactly for half the time in each of the output devices (for 180 degree phase of sine wave about zero). The device connected to the positive supply  $M_{P2}$  conducts during the positive half cycle of signal and the one connected to negative supply  $M_{N2}$  conducts during the negative half cycle of signal. There is a crossover at zero where both the devices are off. As the input gets closer to zero, the devices get closer to turn off and exhibit more non-linear behavior introducing lot of distortion. This makes the text book Class-B useless for real applications. Instead, letting each of the drivers  $M_{P2}$  &  $M_{N2}$  conduct for slightly more than 180 degrees of signal phase by modifying the biasing makes it a Class-AB

Fig. 2. Typical Class-B amplifier

stage. In real applications the terms Class-B and Class-AB are used synonymously and they usually mean Class-AB.

Class-AB is a Class-B amplifier with no or significantly reduced crossover. Each of the device conducts for just more than 180 degrees phase of the sine wave across zero. At zero, both the devices are on taking some quiescent power but significantly less than the Class-A amplifier.

#### 3. Class-C

Class-C implies device conduction for significantly less than 50% of the time ( $\ll$ 180 degrees phase of a sine wave about zero), and is normally only usable in radio work, where an LC circuit can smooth out the current pulses and filter harmonics. In the context of audio we can say a Class-B stage which has no conduction about zero as

working in Class-C. Though there is no meaning in using Class-C for audio, as the definition itself implies large distortion. It will be a helpful tool in understanding the Class-G.

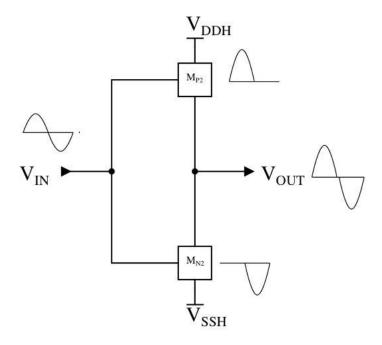

# 4. Note on Class-A/AB/B/C

Essentially all these four classes are the same linear/pseudo-linear circuit. The only thing that differentiates them is how the output driver devices are biased. The transfer characteristics of these classes of amplifiers is summarized in the Fig. 3. As we keep increasing the quiescent current in the devices; we move from Class-C towards Class-A as explained in Table I.

Fig. 3. Transfer characteristics of linear/pseudo-linear classes of amplifiers

Table I. Summary of Class-A, AB, B, C output stage operation

| Type     | Bias Current  | Conduction angle |

|----------|---------------|------------------|

| Class-A  | $I_{out,max}$ | $360^{o}$        |

| Class-AB | just > 0      | $just > 180^o$   |

| Class-B  | 0             | 180°             |

| Class-C  | 0             | < 180°           |

Fig. 4. Typical Class-D amplifier

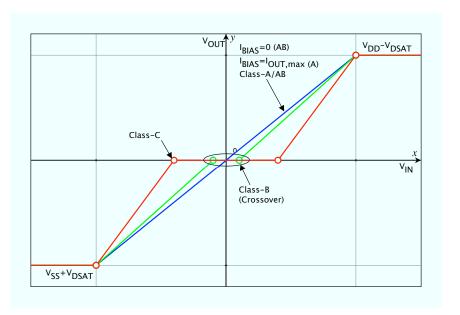

#### 5. Class-D

These amplifiers continuously switch the output from one rail to the other at a very high frequency, controlling the mark/space ratio to give an average representing the instantaneous level of the audio signal; this is alternatively called pulse width modulation (PWM). Great effort and ingenuity has been devoted to this approach, for the efficiency is in theory very high, but the practical difficulties are severe, especially so in a world of tightening EMC legislation, where it is not at all clear that a 200 kHz high-power square wave is a good place to start.

Class D audio amplifiers are typically based on pulse width-modulation (PWM) to generate the output waveform. An analog audio signal (20Hz - 20kHz) is compared with a high frequency carrier (> 200 kHz) to generate a switching wave (PWM). This wave is further increased by a power stage in order to drive the output load. Once the signal is modulated, it is passed through a low-pass filter to recover the analog wave and eliminate the high frequency components [5].

The traditional class D audio amplifier architecture is depicted in Fig. 4. It is an open-loop based system whose main block is represented by the comparator (PWM generator). This topology requires having a well controlled triangular wave shape (carrier signal) which adds cost and potential degradation for non-ideal triangular waveform. The power stage block allows the system to minimize the output resistance of the amplifier in such way that most of the output power is delivered to the load, typically a speaker, through the low-pass filter whose frequency response is designed to be as flat as possible within the audible frequency band.

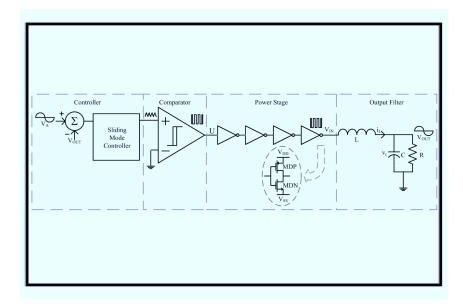

Another ingenious approach to Class-D amplifiers [6][7] applies sliding mode (SM) control technique and is shown in Fig. 5. Linearity of the system is enhanced by using negative feedback. Furthermore, this approach avoids the triangular wave signal

Fig. 5. Class-D amplifier using sliding mode control

used in conventional class D audio amplifiers. The stability of the proposed amplifier is not affected by process and temperature variations (PTV) or by any initial conditions. One of the best features of SM control is its robustness to external perturbations [8][9]. It consists of four basic subsystems: the controller, a hysteresis comparator, the output power stage and the output filter. Ideal SM control reproduces exactly the same waveform at the output stage of the class D amplifier using PWM; however, due to hardware implementation, SM control faces two main obstacles, the quasi-differentiation operation and the non-infinite switching frequency.

Distortion is not inherently low in either of these approaches, and the amount of global negative feedback that can be applied is severely limited by the pole due to the effective sampling frequency in the forward path. A sharp cut-off low-pass filter is needed between amplifier and speaker, to remove most of the RF; this will require at least two or four inductors (for stereo) and will cost money, but its worst feature is that it will only give a flat frequency response into one specific load impedance.

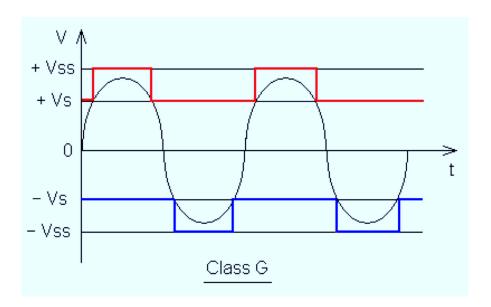

#### 6. Class-G

This concept was introduced by Hitachi in 1976 [10] with the aim of reducing amplifier power dissipation. Musical signals have a high peak-to-average ratio (crest factor), spending most of the time at low levels, so internal dissipation is significantly reduced by working from low-voltage rails for small outputs and switching to higher rails for larger excursions.

Class-G amplifier can be viewed as a Class-AB amplifier operating from the smaller supply and then a Class-C amplifier from the original (higher) supply rail. This is very advantageous especially in case of audio where the crest factor of the signal is typically 12-20dB. By using a smaller supply, when the input/output signal level is low we get higher efficiency, without affecting the maximum signal output (Dynamic range). The challenge is to make sure switching between the supplies introduces only a little/no non-linearity.

The above concept described can be extended to multiple supply levels, but it must be remembered that the additional supplies can not be generated for free. A more detailed discussion on the number of supply levels has been presented in a latter chapter when we discuss the efficiency in more detail.

# D. Portable electronics: The place for Class-G

With the rapid growth of mobile electronics market for entertainment, there has been increased demand for devices and designs with very low standby power consumption and very high efficiencies to achieve increased battery life; all at uncompromising

performance and no increase in cost. Headphone drivers are no exception to this trend. Also there has been a trend, which is pushing all of the system functionality on to a single system on chip, to make the gadgets more and more compact and cost effective. This means, the more friendlily your design is to rest of the system, the better it is.

The Class-D switching amplifiers have very good efficiencies, but the switching causes a lot of unacceptable Electro Magnetic Interference [4] both on-chip and off-chip, making it unacceptable for integration on to any devices with RF components. Also the switching EMI prohibits the use of audio cable as an antenna for FM radio, which is present in most of the present day mobile audio devices. Apart from the EMI problems with Class-D switching amplifiers, the cost of external filter required is also a concern. Moreover, the high distortion and low efficiencies of Class-D switching amplifiers at low signal levels make them undesirable and even unacceptable as headphone drivers in mobile applications. Almost all of todays headphone drivers use Class-AB linear output stages, despite their very poor efficiencies. Class-G will be an ideal way to improve the efficiencies in portable audio devices.

Why only portable audio and why not all audio amplifiers can be of Class-G type? The Class-G amplifier will deliver much better power efficiency compared to Class-AB in any kind of application but Class-D amplifiers will be of greater benefit in big standalone audio systems, where special technologies with devices having low on resistance can be used, where the EMI interference is not a big problem and also where the use of external LC filters is acceptable. Class-D will deliver better efficiencies at competitive linearity numbers compared to the linear classes of power amplifiers (even more than Class-G). Its only when we are integrating things together they become a concern. Thats why we do not see Class-D amplifiers in portable devices and it is the right place for Class-G.

# E. Scope of this work

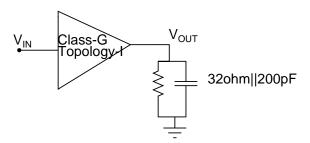

Firstly, the concept of audio amplifier efficiency has been looked at in practical sense using the amplitude distribution characteristics of the audio signals. This enables us to choose the supply voltages optimally to maximize the efficiency of Class-G audio amplifiers. After taking a closer look at the existing Class-G works we demonstrate the concepts of class-G and various design trade-offs in detail. Finally, two circuit level Class-G implementations using the developed concepts have been proposed, implemented, fabricated in silicon and tested.

### CHAPTER II

#### TRUE EFFICIENCY OF AN AUDIO POWER AMPLIFIER

Power Efficiency by itself is not a difficult term to understand. It defines how much of the total electrical power consumed is delivered to the load (speaker) as shown in equation (2.1). No electrical circuit is 100% efficient, always some power is dissipated in the circuit and is lost as heat. With the need for longer battery life and tighter integration in the portable devices, it is becoming increasingly important to care about the efficiency of circuits.

$$\eta = \frac{P_L}{P_{SUP}} \tag{2.1}$$

Though the term power efficiency is very old, and is constantly dwelled upon, it is very poorly understood. It is treated merely as a number to judge the quality rather than in its true sense. In this chapter we look at power efficiency in its true and useful sense rather than in the typical casual approach. From now on we refer to "power efficiency" only as "efficiency" and it is a reasonable to so because the frequency of audio operation is very low.

#### A. Classical efficiency

The efficiency numbers we see most of the time are derived from the classical definition. It is the ratio of average power delivered to the load to the average power taken from the supply during one cycle of a sine/cosine wave input. Why were people using that? Thanks to Fourier, sine/cosine is the classical signal used to test any system and often rail-to-rail signal is used because it gives the best number. Moreover, the calculation of efficiency is very straight forward when we use these sine/cosine input.

The efficiency of an amplifier is highly dependent on the input signal that we are using. But people have given little importance to it and they have been using efficiency in very casual sense. Before we go into a more realistic treatment of efficiency we will briefly go through the mathematics involved in reaching the classical efficiency numbers we see everywhere. This will help us as an aid to understanding the efficiency in true sense later on.

#### 1. Class-A

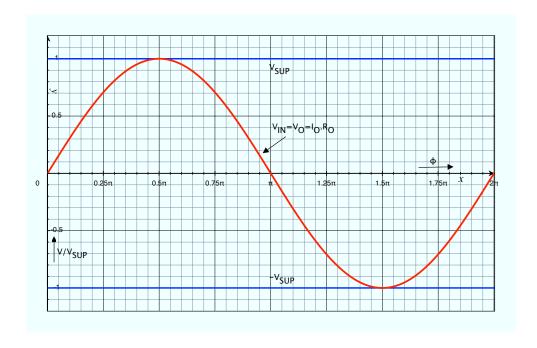

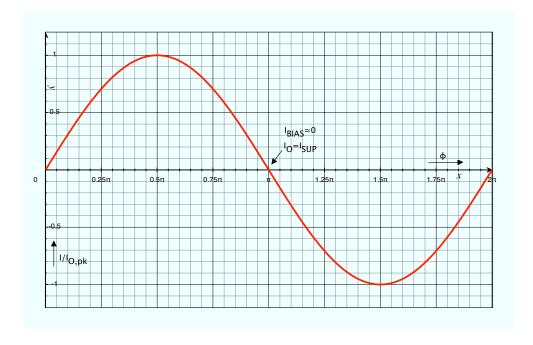

The Class-A power stage is just a standard, textbook small-signal amplifier on steroids. The basic assumption in Class-A design is that bias levels are chosen so that the driving transistor operates in saturation region throughout. The primary distinction between Class-A power stage and small-signal amplifier is that, the signal currents in a power stage are substantial fraction of bias level. Class-A power stages have got very good linearity but at the expense of efficiency. There is always power dissipation due to bias current even when there is no signal. The Class-A operation is explained in Figs. 6, 7 where  $\pm V_{SUP}$  are the supply voltages,  $V_o$  is the output voltage and  $V_{o,pk}$  is the output voltage amplitude; and  $I_{SUP}$  is the total current drawn from the supply,  $I_o$  is the load current and  $I_{o,pk}$  is the amplitude of supply current.

Assuming a close to ideal Class-A amplifier

$$V_{o,pk} = V_{SUP}$$

$$I_{BIAS} = I_{o,pk}$$

(2.2)

Total power delivered to the load:

$$P_{L} = \frac{1}{T} \int V_{o}(t) \cdot I_{o}(t) dt = \frac{2V_{o,pk}^{2}}{\pi \cdot R} \int_{0}^{\frac{\pi}{2}} \sin^{2}(\phi) d\phi = \frac{V_{o,pk}^{2}}{2 \cdot R}$$

(2.3)

Fig. 6. Supply and output voltages in a Class-A amplifier

Fig. 7. Supply and load currents in a Class-A amplifier

Total current drawn from the supply:

$$I_{SUP} = I_B + I_o = I_{o,pk} + I_{o,pk}.sin(\phi)$$

(2.4)

Total power drawn from the supply:

$$P_{SUP} = \frac{1}{T} \int V_{SUP}(t) \cdot I_{SUP}(t) dt = \frac{V_{o,pk}^2}{\pi \cdot R} \int_0^{2\pi} (1 + \sin(\phi)) d\phi = \frac{2V_{o,pk}^2}{R}$$

(2.5)

Classical Efficiency of Class-A amplifier:

$$\eta_A = \frac{P_L}{P_{SUP}} = \frac{1}{4} = 25\% \tag{2.6}$$

This calculation assumes fairly ideal behavior, considering the  $V_{DSAT}$  of the transistors and some more bias current for both the drivers to have some current in all operating conditions pushes this 25% number down to 10-15%.

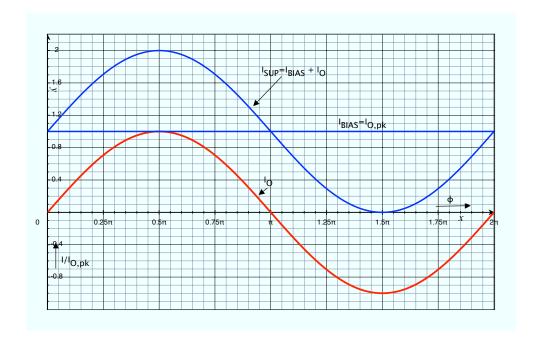

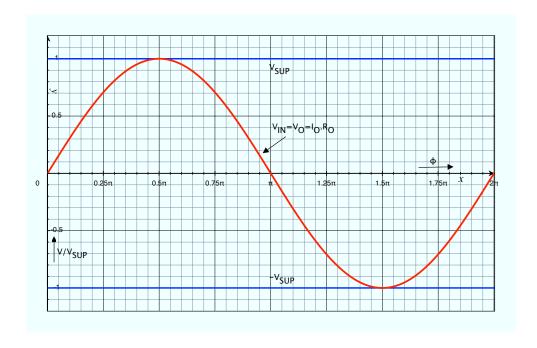

The first step to improving the efficiency of a power stage is taken by trying to reduce the bias current and making it ideally zero in class-B case. This comes with some undesirable effects of crossover distortion, so the bias current is chosen to be as much minimum as possible to get rid of crossover distortion in case of a Class-AB amplifier. The typical Class-B amplifier operation is described in the Figs. 8 and 9 with all the variables having the same meaning as explained in Class-A.

It can be understood from the Fig. 9, that the current drawn from the supply is exactly the amount required to drive the load, so there is no reduction of efficiency due to current. Now the instantaneous efficiency of amplifier can be defined as  $\frac{V_o}{V_{SUP}}$ . If the amplifier is assumed close to ideal then  $V_{o,pk} \simeq V_{SUP}$ .

The total power delivered to the load is same as in equation (2.3) and the total

Fig. 8. Supply and output voltages in a Class-AB amplifier

Fig. 9. Supply and load currents in a Class-AB amplifier

power drawn from the supply is:

$$P_{SUP} = \frac{1}{T} \int V_{SUP}(t) \cdot I_{SUP}(t) dt = \frac{2V_{o,pk}^2}{\pi \cdot R} \int_0^{\frac{\pi}{2}} sin(\phi) d\phi = \frac{2V_{o,pk}^2}{\pi \cdot R}$$

(2.7)

And the classical efficiency of the nearly ideal Class-AB amplifier is:

$$\eta_{AB} = \frac{P_L}{P_{SUP}} = \frac{\pi}{4} = 78.54\% \tag{2.8}$$

In practical conditions is typically about 35-50%.

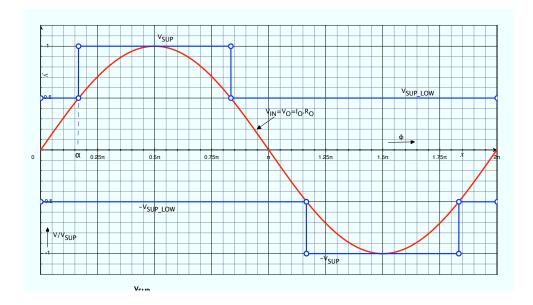

#### 3. Class-G

The obvious next step to improving efficiency is to lower the supply rail (as the instantaneous efficiency is only limited by supply voltage not by current anymore as discussed in the Class-B operation) when the input signal is small to improve the efficiency. The Class-G operation is explained with two different voltage levels in Fig. 10. The  $\alpha$  in Fig. 10 refers to the phase of the sinusoid at which the voltage level switching takes place and thus the lower supply level  $V_{SUP\_LOW} = V_{SUP}.Sin\alpha$ .

The total power delivered to the load is same as in equation (2.3) and the total power drawn from the supply is:

$$P_{SUP} = \frac{1}{T} \int V_{SUP}(t) \cdot I_{SUP}(t) dt = \frac{2V_{o,pk}^2}{\pi \cdot R} \left[ \int_0^\alpha \sin(\alpha) \sin(\phi) d\phi + \int_\alpha^{\frac{\pi}{2}} \sin(\phi) d\phi \right]$$

$$= \frac{2V_{o,pk}^2}{\pi \cdot R} \left[ \sin\alpha + (1 - \sin\alpha) \cos\alpha \right]$$

(2.9)

And the classical efficiency of the nearly ideal Class-G amplifier with two supply levels can be shown to be maximized at  $\alpha = \frac{\pi}{4}$ :

$$\eta_G = \frac{\pi}{4} \left[ \frac{1}{\sin\alpha + (1 - \sin\alpha)\cos\alpha} \right] = 85.9\% \tag{2.10}$$

Fig. 10. Supply and output voltages in a Class-G amplifier

This gives a maximum theoretical efficiency of 85.9%. At the first look this may not seem a great improvement compared to the amount of pains that have to be taken for generating and switching between the supply levels. This is quite deceiving and is one of the reasons there is not much work on Class-G. With a clear understanding of amplitude characteristics, the benefits of Class-G can be seen easily. In the following in sections we will see more of it.

#### 4. Multi-level Class-G

For the sake of completeness an n-level Class-G operation is presented in the Fig. 11 and its efficiency can be shown to be

$$\eta_G = \frac{\pi}{4} \left[ \frac{1}{\sin \alpha_1 + \ldots + (\sin \alpha_{i+1} - \sin \alpha_i) \cos \alpha_i + \ldots + (1 - \sin \alpha_{n-1}) \cos \alpha_{n-1}} \right]$$

(2.11)

where  $sin(\alpha_i) = \frac{V_{DDi}}{V_{DDN}}$  and each of the  $V_{DDi}$ 's i=1,2,...n. are the n-supply levels. and  $\alpha_i$ 's are the corresponding phases of sine wave as defined.

Fig. 11. Supply and output voltages in a multi-level Class-G amplifier

#### 5. Class-D

With the nearly ideal kind of analysis of amplifiers we have been doing to achieve the classical efficiency numbers, Class-D amplifiers should have 100% efficiency as the output of the power amplifier either sits on the positive rail or the negative rail giving no scope for any power loss. The output is passively filtered to get the output voltage. But nothing is ideal, there will be losses due to dynamic consumption, leakage and finite on-resistance of power switches.

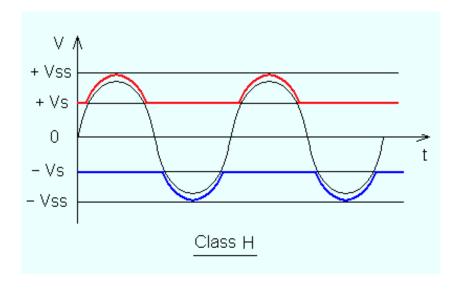

### 6. Class-H

As the number of supply levels(n) in the multi-level Class-G amplifier tends to infinity, it becomes a Class-H amplifier. Ideally Supply should look same as the output. But in reality supply will take some kind of modulated form depending on the input. The fundamental difference between Class-G and H is illustrated in the figures Fig. 12 and Fig. 13. Both Class-G and Class-H are similar in concept of improving efficiency in a different implementation. Class-H amplifiers are still far from practicality, to interest researchers because generating a supply modulated by input will in itself have very bad efficiency.

Fig. 12. Class-G operation

Fig. 13. Class-H operation

#### B. Crest factor of audio signals and its importance

The crest factor or peak-to-average ratio (PAR) or peak-to-average power ratio (PAPR) is a measurement of a waveform, calculated from the peak amplitude of the waveform divided by the RMS value of the waveform. It tells us something about the power distribution across amplitudes in a signal. The audio signals are known to have crest factors in the range of 12-20dB. Music has a widely-varying crest factor. Typical values for a processed mix are around 4-8 (which corresponds to 12-18 dB of headroom, usually involving audio level compression), and 8-10 for an unprocessed recording (18-20 dB). Which means the average amplitude of an audio signal is 4-10 times smaller than its peak value. The crest factor of our standard test signal sine/cosine wave is  $20log(\frac{V_{o,pk}}{V_{o,rms}}) = 20log(\sqrt{2}) = 3dB$ .

Why do we care about it? Because the efficiency of an amplifier depends sub-

stantially on the input signal. When the value of output voltage is  $0.9 * V_{SUP}$  and assuming the total current taken from supply is completely delivered to the load the instantaneous efficiency is 90% and it is only 10% when the output voltage is  $0.1 * V_{SUP}$ . The Class-AB efficiency derived in equation (2.8) is 78.54% for a rail-to-rail sine wave, it drops by 50% to 39.27% for a sine wave with half its amplitude. The conclusion is the power distribution across different signal levels in an audio signal is very different from that of a sine wave just from the knowledge of their crest factor. In the next section we dig further into the actual amplitude distribution of audio by examining some test signals to understand how the efficiency of an amplifier can be maximized in the true sense. Soon we will realize how far the classical definition of efficiency is from reality.

## C. True efficiency

True efficiency of an amplifier can be defined only with respect to a signal or set of signals with similar amplitude distribution function(adf) which will be defined later in this chapter. We use the instantaneous efficiency curves of various amplifiers along with amplitude distribution functions of some typical audio signals to demonstrate the range of true efficiencies for various classes of audio amplifiers.

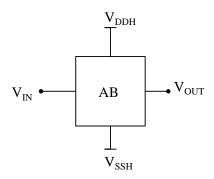

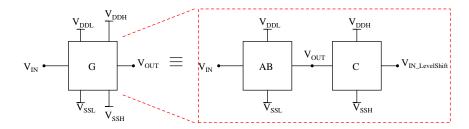

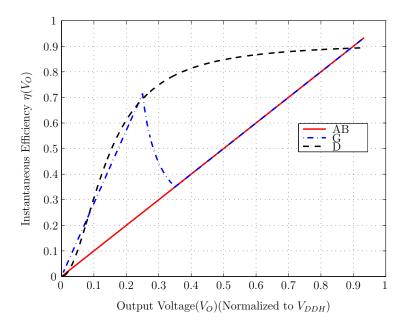

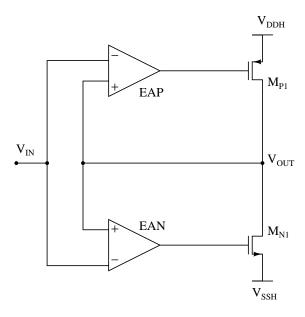

### 1. Instantaneous efficiencies of Class-AB/G/D

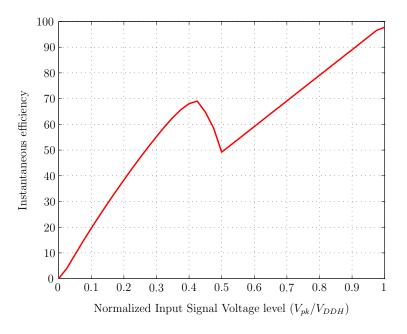

Instantaneous efficiency is efficiency of the amplifier at a given instant. Instantaneous efficiencies of ideal Class-AB (Fig. 14) and Class-G (Fig. 15) amplifiers are shown in Fig. 16. They are pretty simple and straight forward to understand. Assuming all the supply current is being delivered to the load, the instantaneous efficiency of the class-AB amplifier is just  $V_{OUT}/V_{SUP}$  and is a straight line which goes from 0 to 1 as

the normalized input signal goes from 0 to 1.

Fig. 14. Class-AB amplifier block diagram

Fig. 15. Class-G amplifier block diagram

The instantaneous efficiency curve of Class-G can also understood very similarly. Now that output is driven from the smaller supply till it exceeds the smaller supply. The efficiency reaches 100% when the output equal to smaller supply then it drops to  $\frac{V_{SUP\_LOW}}{V_{SUP\_HIGH}}X100$  and follows the Class-AB curve as there is no more difference between Class-AB and Class-G. In the example curve shown the lower supply is 40% of the larger supply, hence use see the peak in Class-G efficiency at 0.4 normalized signal value.

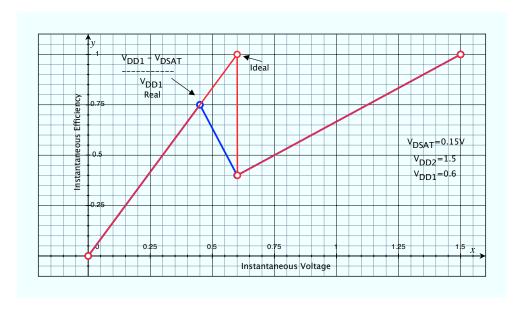

Figure 17 gives a more realistic instantaneous plots of Class-AB/G/D amplifiers. The Class-AB and Class-G plots include a small quiescent current and the  $V_{DSAT}$

Fig. 16. Instantaneous efficiencies of ideal Class-AB/G amplifiers

Fig. 17. Instantaneous efficiencies of real Class-AB/G/D amplifiers

influence of the drivers making the peak acceptable amplitude to about 90% of  $V_{SUP}$ . The effect of  $V_{DSAT}$  of smaller driver in Class-G also limits the intermediate efficiency peak from reaching 100% as in the ideal case. The instantaneous efficiency plot for Class-D is just an estimate from the typical efficiency vs. amplitude plots (might not be 100% accurate). These are the instantaneous efficiencies used in calculating the true efficiencies of these amplifiers in the last section of this chapter.

Figure 17 shows that Class-D amplifiers have better efficiencies at almost all signal levels. Yes, that is right and that is the reason why as discussed in chapter 1, Class-D amplifiers are a better choice when it comes to large loads and in places where there are no EMI concerns.

## 2. Amplitude distribution function of some typical audio signals

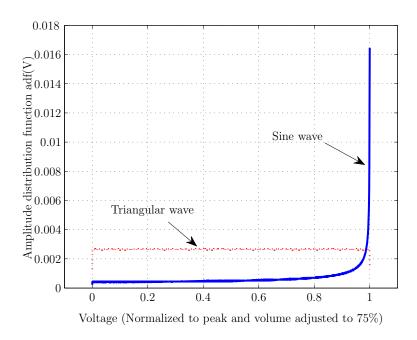

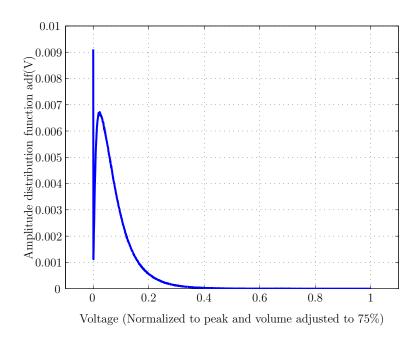

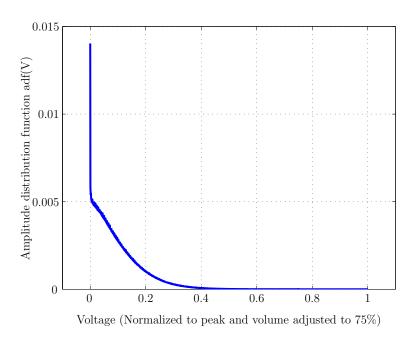

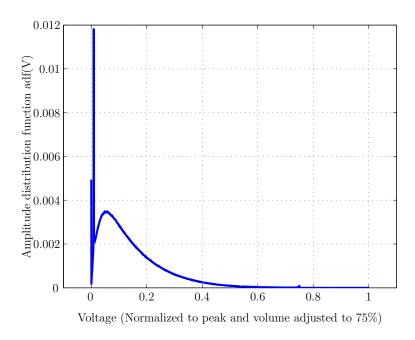

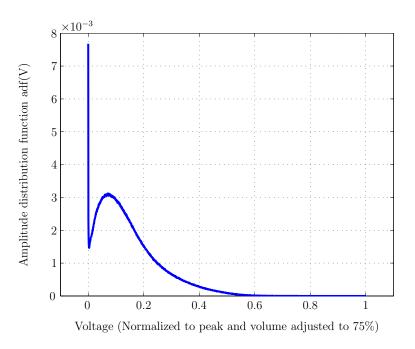

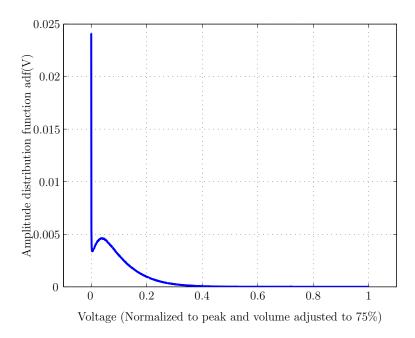

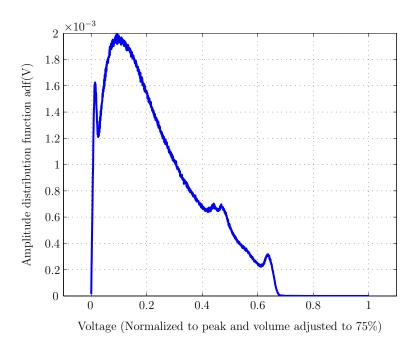

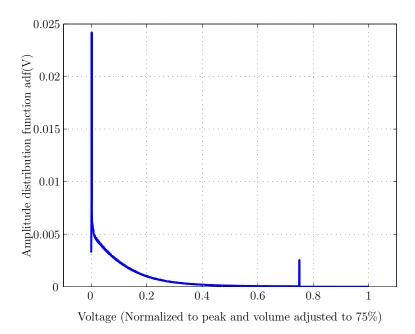

Amplitude distribution function  $adf(V_o)$  has been defined as the probability of occurrence of signal with value  $V_o$  and has the units  $V^{-1}$ . This value will tell us the fraction of time the input/output of the amplifier will spend at that particular voltage level. If we plot the adf of a square wave with two levels one at 0 and the other at +ve rail and 50% duty cycle, we will have two impulses each with magnitude 0.5 at 0 and 1(since the signal is normalized to peak). A rail-to-rail triangular wave being a linear increase or decrease the adf is like uniform distribution. It spends equal fraction of time at all signal levels as shown in Fig. 18. The adf of a rail-to-rail sine wave has been shown in the Fig. 18. It can be seen, a sine wave spends greater amount of time closer to its peak (signal is normalized to this value) ( $\phi = \frac{\pi}{2}$ ). This is intuitive as the rate of change of sine wave (derivative) is maximum at ( $\phi = 0$ ) where the value of sine is zero and the rate of change is minimum at its peak. On the contrary audio signals spend most of the time and hence contain most of the energy in their lower signal levels. A set of typical audio signals have been analyzed and their adf's

are presented in Figs. 19(melody), 20(heavy beat), 21 (soft rock), 22 (club mix), 23 (rock), 24(classical), 25(more vocal). The genres mentioned are only for reference, depending on the actual signal the distribution may vary for any genre.

Fig. 18. Amplitude distribution function of sine wave

### 3. Power efficiency formula

It is not possible to calculate the efficiency of an amplifier in true sense for a very long and complex signal like audio using the classical approach presented in the first section of this chapter because the integrals become hopeless to compute. Here we derive a formula which uses the instantaneous efficiency of the amplifier and the amplitude distribution function of the signal to calculate a more meaningful number which denotes the true efficiency of that amplifier with that input signal. It gives us a realistic efficiency value for all the signals with similar amplitude distribution characteristics.

Fig. 19. Amplitude distribution function of Signal 1

Fig. 20. Amplitude distribution function of Signal 2

Fig. 21. Amplitude distribution function of Signal 3

Fig. 22. Amplitude distribution function of Signal 4

Fig. 23. Amplitude distribution function of Signal 5

Fig. 24. Amplitude distribution function of Signal 6

Fig. 25. Amplitude distribution function of Signal 7

If the instantaneous output voltage is  $V_o$  then the instantaneous power delivered to the load  $R_L$  is:

$$P_L(V_o) = \frac{V_o^2}{R_L} {2.12}$$

and further if the instantaneous efficiency of the amplifier is  $\eta(V_o)$  then the instantaneous power taken from the supply is:

$$P_{SUP}(V_o) = \frac{P_L}{\eta(V_o)}$$

$$for V_o \neq 0$$

(2.13)

Now within the total duration of the signal if the signal spends  $adf(V_o)$  fraction of time at level  $V_o$  then the total average power delivered to the load( $R_L$ ) is:

$$P_{L,avg} = \frac{1}{R_L} \int_0^{V_{o,pk}} adf(V_o).V_o^2.dV_o$$

(2.14)

Extending the calculation to the total average power consumed from the supply is:

$$P_{SUP,avg} = \left[ adf(0).P_Q + \frac{1}{R_L} \int_{0}^{V_{o,pk}} \frac{adf(V_o).V_o^2}{\eta(V_o)} . dV_o \right]$$

(2.15)

where adf(0) is the fraction of time spent at zero signal level and  $P_Q$  is the quiescent power consumption. This term has been taken out of the integral because when there is zero signal, the instantaneous efficiency is zero and the integral will be undefined.

Now using the above two equations (2.14)(2.15) we have the true average efficiency of the amplifier for the given signal as

$$\eta_{true} = \frac{P_{L,avg}}{P_{SUP,avg}} = \frac{\int_{0}^{V_{o,pk}} adf(V_o) \cdot \frac{V_o^2}{R_L} \cdot dV_o}{adf(0) \cdot P_Q + \int_{0}^{V_{o,pk}} \frac{adf(V_o) \cdot V_o^2}{\eta(V_o) \cdot R_L} \cdot dV_o}$$

(2.16)

To illustrate the above efficiency formula we can use a simple example from Table II. Consider a signal with two phases of operation. The signal spends 40% of time in phase I and the system has an efficiency of 20% and consumes 100W during this phase. The signal spends 60% of time in phase II and the system has an efficiency of 80% and consumes 50W during this phase. The average power delivered to the load and taken from supply can be calculated as in equation 2.17. This gives us the effective efficiency to be 45.71%. The advantage with the above method is the complexity doesn't increase with length of the signal. Once the amplitude distribution characteristics are known we can calculate the true efficiency.

$$P_{L,avg} = 0.4 * 0.2 * 100 + 0.6 * 0.8 * 50 = 32W$$

$$P_{SUP,avg} = 0.4 * 100 + 0.6 * 50 = 70W$$

$$\eta = 32/70 = 45.71\%$$

(2.17)

Table II. Example demonstrating the power efficiency formula

| Example  | Fraction of | Instantaneous | $P_{SUP}(\text{phase})$ |

|----------|-------------|---------------|-------------------------|

|          | time        | efficiency    |                         |

| Phase I  | 40%         | 20%           | 100W                    |

| Phase II | 60%         | 80%           | 50W                     |

# 4. Comparison of practical efficiencies

The typical audio signals presented in the section C.2 of this chapter and the instantaneous efficiency plots of class-AB/G/D amplifiers presented in section C.1 are used with the efficiency formula and the following summary of comparison is obtained as shown in Table III. The user is assumed to be using the amplifier at 75% of maximum signal level. We can clearly see that Class-AB is far behind Class-G and Class-D for all kinds of signals. For the signals (1,2,5) in which the majority of power is concentrated in very small signal levels Class-G & D are very close in efficiencies. For the signals in which the power is reasonably spread out Class-D does only a little better than Class-G because of its better instantaneous efficiency for moderate to high signal levels as in Fig. 17. If the user uses the amplifier at a much lower (<50%) volume setting (input power level) then Class-G and Class-D will perform very close in terms efficiency as with signals (1,2,5) because the whole adf's of the signals shrink down with reduction in volume.

## 5. Note on audio volume and efficiency

As we increase/decrease the playback volume, the amplitude distribution functions shown previously also expand/shrink along the signal axis. This means, it becomes

Table III. Comparison of efficiencies of Class-AB/G/D with application of typical audio signals

| $\frac{Class}{Input}$ | Class-AB | Class-G | Class-D |

|-----------------------|----------|---------|---------|

| Sine                  | 78.5%    | 81%     | 88%     |

| Signal 1              | 13.4%    | 34.2%   | 31.2%   |

| Signal 2              | 17%      | 40%     | 42%     |

| Signal 3              | 23%      | 44%     | 57%     |

| Signal 4              | 22%      | 43.3%   | 57%     |

| Signal 5              | 16%      | 39%     | 40%     |

| Signal 6              | 34%      | 48%     | 73%     |

| Signal 7              | 25%      | 46%     | 55%     |

more and more important to improve the instantaneous efficiency at smaller signal levels when the devices are used at less volume. To maximally optimize the amplifier efficiency, the smaller voltage supply levels has to be dynamically scaled based on the user volume setting. This requires complex power management and is outside the scope of this work and is left for future research.

### CHAPTER III

#### CLASS-G AMPLIFIERS

In this section, we take a look at the previous works on Class-G and then discuss the logical development of a high-performance circuit implementation of Class-G output stage from the basic Class-AB concepts and existing Class-G structures. Then we discuss various design choices and trade-offs involved in an optimum Class-G output stage design.

### A. Previous work on Class-G

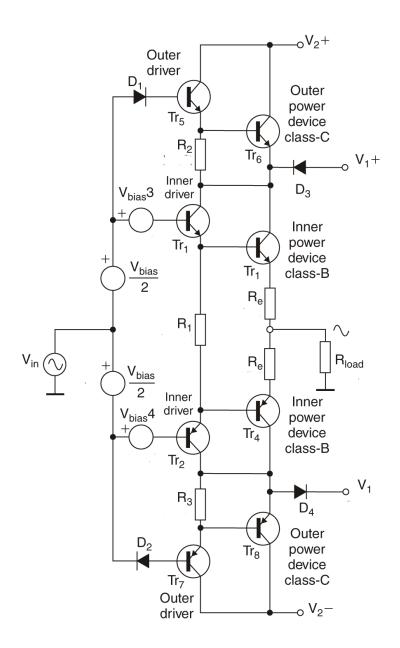

Though the idea of Class-G was first reported in Aug 1976, radio electronics journal. Questionable quality due to glitching commutation diodes [4] and the large amount of heat dissipation in them, kept the efficiencies very low. This kept it far from the interest of the researchers. A sample circuit from [4] is shown in Fig. 26. This figure shows a predriver and power stage in Class-G configuration. As in this example, majority of the existing solutions [11][12][10] are based on the basic class-AB source/emitter follower configuration shown in the figure on page 44 (more detail of this buffer configuration in next section) which has the fundamental drawbacks of low voltage swing due to  $V_{GS(BE)}$  drop and large non-linearities. The  $V_{GS(BE)}$  drop is also costly in terms of efficiency considering the small supply voltages used in present day technologies.

The following are Class-G implementations for other applications and are not very linear. Hence we only touch upon the useful ideas. The design presented in [13][14] is for a digital transmit line drivers but it proposes the concept of predictive switching which can be useful in the evolution of class-G. Using this idea by processing the digital audio data before it reaches the amplifier, we will have time to do efficient

Fig. 26. Previous Class-G implementation-I

power management. The design in [15] shown in emphasizes on the idea of gradual switching, but the design as such overlooks the fundamental by using a class-A kind of structure which can't really improve the efficiency. There are other Class-G driver implementations in the literature intended for central office applications [16][17][18]. The main drawback of all these is that they are not intended to be very linear as audio amplifiers.

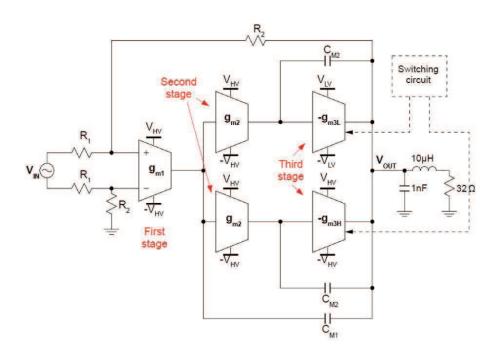

The latest Class-G implementation [19] fails to choose the smaller supply voltages optimally, which as we see in the chapter 2 is the most important to maximize efficiency. The block diagram of this circuit is shown in Fig. 27. It does brute-force switching between supplies, by forcefully turning on/off the parallel output stages with an external circuit. The parallel paths require separate compensation and hence double the required compensation capacitance.

There are a couple of Class-G commercial products, though not many details are known, here is a brief account of what has been done. [20] and [21] follow very similar approach to Class-G implementation. They have a single driver and the supply switching is done by the power management block. The major drawback with this approach is there is delay between the signal crossing the supply threshold and the power management circuit reacting with rail switching. This causes signal clipping and there will be distortion. The output stage linearity is marketed with not much mention about the clipping that happens when there is supply switching. [22] follows a parallel driver strategy and uses three rails (direct +ve supply and two -ve supplies generated using charge pump) for its 2.4W speaker amplifier. The main drawback is it is not ground referenced and requires DC blocking capacitors. The architecture of its output stage is not known as well.

Fig. 27. Previous Class-G implementation-II

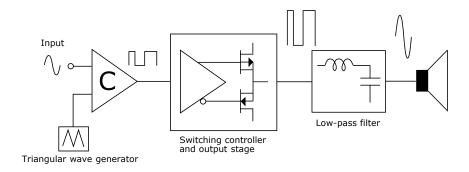

## B. Series Vs Parallel Class-G structures

By the definition of Class-G, It is just an extension of Class-AB stage, where we improve on the efficiency by using a smaller supply voltage when the input/output signal level is low. There are two basic ways in which this can be realized: The 'series' implementation and the 'parallel' implementation are as shown in Figs. 28(A) and 28(B) respectively.

Fig. 28. Series and parallel type Class-G output stages

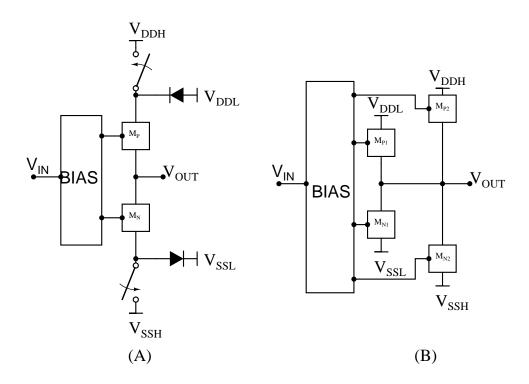

The most commonly used topology [11][12] is the series topology in Fig. 28A, when the output voltage is smaller than the lower supply the diode is forward biased and the switch connected to the higher supply is open, thus the output is driven by the lower supply through the forward biased diode and when the output voltage is higher than the lower supply the diode is reverse biased and the switch is closed, hence the

output is driven from the higher supply. The main drawback with this implementation is the forward biased diode drop in the smaller supply path can not be afforded in the present day low voltage portable electronics. Even if we have a specialized diode with small turn-on voltage  $V_{on}$ , the  $V_{on}$  of the diode directly affects the lower part of the instantaneous efficiency curve which we have seen is very important in the design of a Class-G stage.

The 'parallel' implementation [10] doesn't have the above drawback but takes considerably larger area compared to the series type because we now have four drivers instead of two. In today's market the efficiency of a design is more important than a fraction of silicon area. From here on in this work Class-G output stage always means 'parallel' type unless specifically stated.

In a Class-G output stage as long as the signal is smaller than the lower supply the smaller driver stage is active and when the signal is larger than the lower supply level, the bigger driver is active. To prevent powering up of the lower supply from the higher supply, the smaller driver should be turned-off and we will discuss more on ways to do it in the last section of this chapter. The switching between the supplies has to happen seamlessly, by adding no or only very little distortion, which is the most critical factor in audio amplifier design. Further in this chapter we will show how this has be achieved.

#### C. Class-AB: The corner stone for Class-G

With a closer look at the Class-G behavior, its not difficult to understand it is a normal Class-AB amplifier operating from the lower supply as long as the signal is smaller than the lower supply and when the signal becomes larger than the lower supply, the bigger driver stage of 'parallel' type implementation should become active. If we look keenly, this is nothing but a Class-C behavior. In short, in a Class-G output stage, the signal is applied to both smaller driver stage(from lower supply) which is pure Class-AB type and bigger driver(from higher supply) which is of Class-C type.

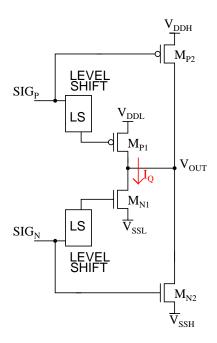

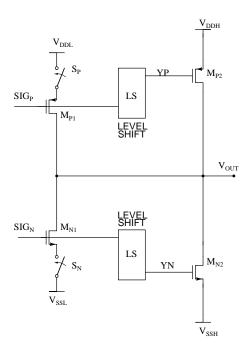

As discussed in chapter 1, Class-A/AB/B/C are all the same output stage biased differently. Class-AB is biased with a little bias current and Class-C is biased such that the both the driver transistors of that stage will remain off for a significant portion of the signal about zero. Understanding this fundamental concept leads us to the obvious Class-G output stage implementation as shown in the Figs. 29 and 30. So now we can see Class-G as a Class-AB + Class-C(Level shift + driver).

Fig. 29. Shift-in type Class-G output stage

The first of the two figures shown is 'shift-in' type as the signal is applied to the bigger driver stage and is shifted in using the level shifter to bias the smaller driver stage and similarly the second one is 'shift-out' type.

Fig. 30. Shift-out type Class-G output stage

An even closer look, reveals how much similar the design of a Class-AB output stage is to the design of Class-G. Class-G is just an extension of Class-AB: In a Class-AB output stage we have two driver transistors and one cross-over point about zero. Similarly in Class-G we have four driver transistors and three cross-over points at zero,  $V_{DDL}$  and  $V_{SSL}$ . Understanding this helps us in applying the existing linearizing techniques for Class-AB on Class-G.

## 1. Brief look at various Class-AB output stages

The most basic of Class-AB output stage is made up of PMOS and NMOS source followers with their sources joined at their output as shown in Fig. 31 biasing details are left out. The major drawback of this the output node can not go closer than one  $V_T$  to the rails as shown in equation 3.1, this poses a large drop in efficiency as shown

in equation 3.4 considering the small supply voltages in use. This was the most widely used topology in the past and almost all of the existing Class-G literature also uses this topology with BJTs.

$$V_{SIGP} \le V_{DDH}$$

$$V_{OUT} = V_{SIGP} - V_{GS_{MN}}$$

$$= > V_{OUT} < V_{DDH} - V_{GS_{MN}}$$

(3.1)

$$\eta_{inst_{max}} = \frac{V_{OUT,max}.I_L}{V_{DDH}.I_L}$$

$$\eta_{inst_{max}} = \frac{V_{DDH} - V_{GS_{MN}}}{V_{DDH}}$$

(3.2)

Fig. 31. Source follower Class-AB output stage

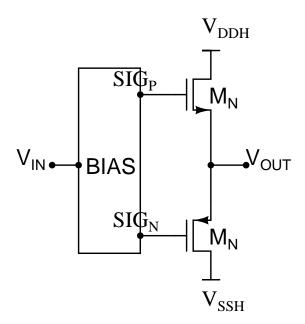

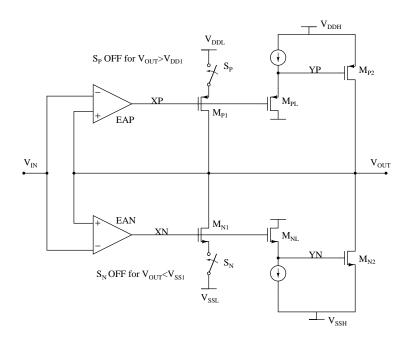

A much better Class-AB topology [23][24] formed by PMOS and NMOS common

Fig. 32. Class-AB output stage with error amplifiers and common source devices

sources joined by their drains at the output as in the case of an inverter, but the biasing is such that only a little bias current flows through it. An example of such circuit can be seen in Fig. 32. The paradox is we are using the high output impedance and gain to close the loop and build an excellent buffer. In quiescent state the error amplifier outputs bias the driver transistors such that they conduct little current. When the input becomes positive the output voltage of the error amplifiers EAP and EAN drop and the PMOS  $M_{P1}$ will start driving the output such that it is equal to the input and the NMOS  $M_{N1}$  remains turned-off. When the input goes below zero, the vice-versa happens NMOS is active and PMOS is off. Unlike the buffer in Fig. 31 this one can swing as close as one  $V_{DSAT}$  to the rail as shown in equation 3.3 and this improves the maximum achievable instantaneous efficiency significantly.

For the transistor  $M_{N1}$  to be in saturation

$$V_{DS,MN1} > V_{GS,MN1} - V_{T,MN1}$$

$$=> V_{OUT} > V_{G,MN1} - V_{T,MN1}$$

$$=> V_{OUT} > V_{DSAT,MN1}$$

(3.3)

$$\eta_{inst_{max}} = \frac{V_{OUT,max}.I_L}{V_{DDH}.I_L}$$

$$\eta_{inst_{max}} = \frac{V_{DDH} - V_{DSAT_{MP1}}}{V_{DDH}}$$

(3.4)

The problem with the circuit in Fig. 32 is poor control over quiescent current. To over come this there are advanced biasing schemes used in [25][26][27][28][29][30]. With any of these Class-AB design as base we can develop a class-G amplifier using parallel output stages and shift-in/shift-out level shifters to bias the bigger driver in Class-C mode making the whole setup to work in Class-G configuration as explained in previous section.

### D. Important design choices

From the preceding sections, it should be clear why we choose Class-G parallel type output stage with common source type drivers. In this section, we will look at some of the quantitative design considerations of this kind of Class-G output stage.

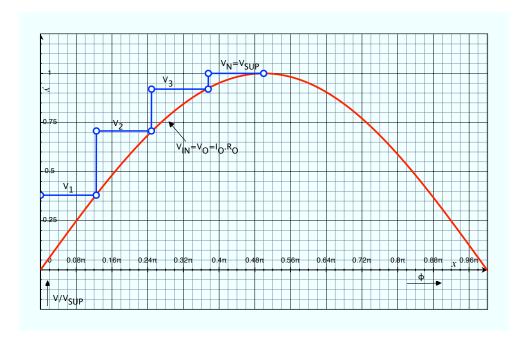

# 1. $V_{DSAT}$ of smaller drivers

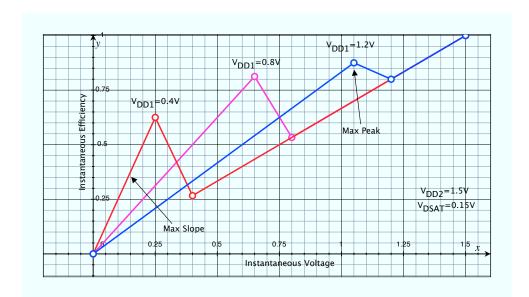

The fact that instantaneous efficiency curve of Class-G as in Fig. 33 at the lower signal levels is very important in maximizing the overall efficiency because the audio signal spends a major faction of time at small signal levels. Understanding the impact of  $V_{DSAT}$  of smaller drivers is needed for optimum design.

Fig. 33. Effect of  $V_{DSAT}$  of smaller drivers

Figure 33 shows the Class-G instantaneous efficiency curves ideal and  $V_{DSAT} = 150mV$ . In case of ideal Class-G the instantaneous efficiency reaches 100% at  $V_{IN} = V_{DDL} = 0.6$  whereas in case of real Class-G the peak instantaneous efficiency is about  $\frac{V_{DDL} - V_{DSAT}}{V_{DDL}}$  which is equal to 75% in this case. When the signal is greater than  $V_{DDL} - V_{DSAT}$  the smaller driver goes into triode and to keep the distortion low the bigger should start driving the output, hence the efficiency drops from here on. When the output signal crosses  $V_{DDL}$  the efficiency curve starts following the original one. When the output signal level is between  $V_{DDL} - V_{DSAT}$  and  $V_{DDL}$  we assumed linear handover from smaller driver to larger driver (first order approximation).

$$\frac{I_{pk}}{I_Q} = \left(\frac{V_{DSAT,max,pk}}{V_{DSAT,min,Q}}\right)^2 \tag{3.5}$$

Minimizing  $V_{DSAT,max,pk}$  of driver when peak load current  $(I_{pk})$  is flowing through smaller driver may seem to be an obvious choice but it is limited by the quiescent

current budget. The peak current taken from the smaller driver is defined by the smaller supply voltage and the minimum  $V_{DSAT}$  of driver transistors in quiescent state  $(V_{DSAT,min,Q})$  is limited by the process variation of  $V_T$ . If we choose to bias the drivers in deep sub-threshold (to minimize  $V_{DSAT,min,Q}$ ) in quiescent condition, then any smaller  $V_T$  variation will be amplified into huge variation in  $I_Q$  by the large  $g_m$  of driver (due to its size). The equation (3.5) now shows that the quiescent current  $I_Q$  and  $V_{DSAT,max,pk}$  (which affects the efficiency peak we discussed) are inversely proportional. A careful choice of  $V_{DSAT,max,pk}$  has to be made for an optimal design.

For example if we have  $V_{DDL}=0.6V$  and the  $V_T$  variation with process and temperature is about 50mV. It is safer to choose 75mV or more as the  $V_{DSAT,min,Q}$ . Now  $I_{pk}$  is roughly defined by the smaller supply voltage value and load impedance (32 $\Omega$ ) and is equal to  $0.6V/32\Omega=18mA$ . Now using these the possible values for  $I_Q \& V_{DSAT,max,pk}$  are shown in the Table IV.

Table IV.  $V_{DSAT}$  and  $I_Q$  trade-off.

| $I_Q$      | $V_{DSAT,max,pk}$ |  |

|------------|-------------------|--|

| $200\mu$ A | 0.7V              |  |

| 800μ A     | 0.35V             |  |

| 2mA        | 0.23V             |  |

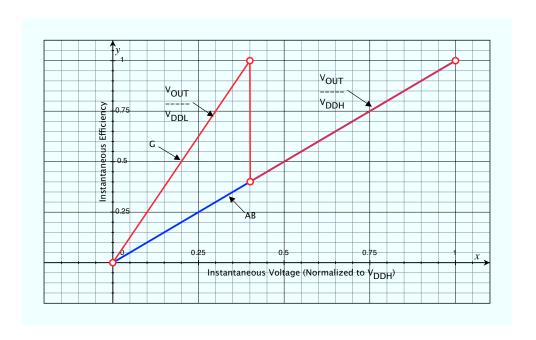

## 2. Smaller supply and instantaneous efficiency

One of the most important design choices to make is the choice of smaller supply. The main reason to use a smaller supply is to improve the efficiency. So it is essential to understand the impact of smaller supply on the over all efficiency which in turn

can be understood by understanding its impact on instantaneous efficiency.

Fig. 34. Effect of smaller supply

Figure 34 shows instantaneous efficiency curve for three different smaller supply values. It can be seen that, for a given smaller driver  $V_{DSAT}$  the intermediate peak in the instantaneous efficiency curve increases with the smaller supply value, where as the slope of the lower part of the instantaneous efficiency curve decreases. It must be remembered that we have to maximize the overall efficiency and not the intermediate peak.

From our analysis of audio signals in chapter 2, we can observe that most of the audio power is concentrated in the signal levels less than 30-40% of the maximum. So the region from 0 to 30-40% of higher supply level should have the maximum possible efficiency. Hence, it is optimum to choose the smaller supply level to be about 40-45% of higher supply level. This ensures that we are driving most of the signal power with the best possible efficiency. This is way far from the classical calculation which yields

$71\% \ (sin(\pi/4)).$

# 3. Number of supply levels (Multi-level Class-G)

Is it beneficial to use a multi-level class-G? What if we have three supplies instead of two. We will need to generate six supplies instead of four. They do not come for free, each will have efficiency loss from a regulator or charge pump. Further there will need for an additional driver stage, the effect of its  $V_{DSAT}$  and not to forget two additional cross-over points adding distortion. A brief comparison of two level vs. three level class-G is presented in the Table V. It is not a great idea to use any more than two levels of supply. An optimum choice of lower supply level does much more good than going for a multi-level class-G.

Table V. Two level supply vs three level supply comparison

|                     | Two level                         | Three level            |

|---------------------|-----------------------------------|------------------------|

| Supplies            | $4({\rm less}\ \eta\ {\rm loss})$ | $6$ (more $\eta$ loss) |

| Drivers             | 4(less area)                      | 6(more area)           |

| $V_{DSAT}\eta$ loss | at 1 smaller driver               | at 2 smaller drivers   |

| Complexity          | average                           | high                   |

| Overall $\eta$      | Comparable or two level is better |                        |

## E. Linearity

We know that in Class-AB amplifier the major sources of non-linearity are the crossover distortion and the triode non-linearity when the output is driven close to the rail. To minimize the cross-over distortion some quiescent current is burnt and the triode non-linearity is left as a trade-off for smaller die area as it shows up only occasionally when the signal is too large.

Extending this to Class-G we have cross-over distortion arising from three points and the triode non-linearity is also present. The cross-over at zero crossing is minimized by burning some quiescent current as in Class-AB. The bigger drivers should be biased such that they start delivering a portion of current to the load when the smaller drivers reach triode region. This minimizes cross-over distortion near the smaller supply levels.

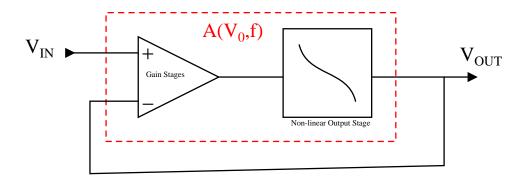

It is not practical to mathematically analyze the distortion since the output MOS transistors operate in all three possible regions of operation during one cycle of a sine wave input. But some insight is required in order to design optimally, even when we are taking the help of simulator. So, let us take a look at the Closed loop amplifier.

Fig. 35. Audio amplifier block diagram

The most important of all in linearizing the circuits, is the use of negative feed-back. It is known to suppress the second harmonic approximately by the square of loop gain (improve HD2 by loop gain) and suppress the third harmonic by approximately cube of loop gain (improve HD3 by square of loop gain). Let us get an intuition of why this happens using first order approximation with out going into

cumbersome mathematics. Here in Fig. 35 we show the model of an audio amplifier, with a gain stage and a non-linear output stage (Can be Class-AB or G). The total gain of audio amplifier is  $A(V_o, f)$ , it is obviously a function of frequency (f) as is any other amplifier and in this case also a function of output voltage  $(V_o)$  as the output stage is non-linear (the  $g_m$  of output stage can vary by about 10-50X with output voltage). As long as the system is stable we know

$$(V_{in} - V_o).A = V_o$$

$$Err = V_o - V_{in} = \frac{-V_{in}}{1+A}$$

(3.6)

Let us say we have a constant frequency sine wave input to the system and the  $min[A(V_o)]$  is 60dB, then following the above equation the ratio of input to the error between input and output at that frequency will be greater than 60dB, no matter how non-linear the output stage is. So then what happens to all the non-linearity generated? It is spread in to the higher frequency harmonics just as in delta-sigma modulator noise shaping. The conclusion is the open loop gain of the audio amplifier in the band 20-10kHz is of prime importance in achieving high linearity. Why 10kHz and not 20kHz? Because all the harmonics of any frequency greater than 10kHz falls outside the audible spectrum.

The open-loop gain can be used to explain the above two mentioned sources of non-linearity. The crossover distortion occurs because, when there is no quiescent current the  $g_m$  of the output stage becomes too low reducing the open loop gain. The same thing happens when one of the driver enters the triode-region; the loop gain drops and the distortion error increases. It should be understood that increasing the gain in the preceding stages lets us reduce the crossover distortion (or the quiescent current) and also triode distortion. This is a very important trade-off between

linearity, quiescent current and power in the amplifier.

# F. SR of amplifier and comparators

The maximum rate at which an audio signal changes determines the slew rate specifications. Consider the sine wave with amplitude  $A_m$  and frequency  $f_{in}$ . The maximum rate at which it can change is given by:

$$V = A_m.sin(2.\pi.f_{in}.t)$$

$$\frac{\Delta V}{\Delta t} = A_m.2.\pi.f_{in}.cos(2.\pi.f_{in}.t)$$

$$SR = \frac{\Delta V}{\Delta t}_{max} = A_m.2.\pi.f_{in} = A_m.\omega_{in}$$

(3.7)

$$SR \ge V_{DDH}.2.\pi.(20kHz) \tag{3.8}$$

For an audio signal this can be obtained by using  $A_m = V_{DDH}$  and  $f_{in} = 20kHz$ . The slew rate at all internal nodes of the multi-stage amplifier should be better than the above obtained value in the equation (3.8).

The comparators we use to turn-off the smaller driver stage when input crosses the lower supply level should act faster than the rate at which the signal changes in order to prevent any glitches which fall in the signal band. Hence the slew rate of the comparator should be 3 to 4 times the signal SR derived in the equation (3.8).

## CHAPTER IV

#### CLASS-G IMPLEMENTATION