## PARALLEL SIMULATION FOR VLSI POWER GRID

A Dissertation

by

## LE ZHANG

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Vivek Sarin    |

|---------------------|----------------|

| Committee Members,  | Duncan Walker  |

|                     | Rabi Mahapatra |

|                     | Peng Li        |

| Head of Department, | Dilma Da Silva |

August 2015

Major Subject: Computer Engineering

Copyright 2015 Le Zhang

### ABSTRACT

Due to the increasing complexity of VLSI circuits, power grid simulation has become more and more time-consuming. Hence, there is a need for fast and accurate power grid simulator. In order to perform power grid simulation in a timely manner, parallel algorithms have been developed to accelerate the simulation. In this dissertation, we present parallel algorithms and software for power grid simulation on CPU-GPU platforms. The power grid is divided into disjoint partitions. The partitions are enlarged using Breath First Search (BFS) method. In the partition enlarging process, a portion of edges are ignored to make the matrix factorization light-weight. Solving the enlarged partitions using a direct solver serves as a preconditioner for the Preconditioned Conjugate Gradient (PCG) method that is used to solve the power grid. This work combines the advantages of direct solvers and iterative solvers to obtain an efficient hybrid parallel solver. Two-tier parallelism is harnessed using MPI for partitions and CUDA within each partition. The experiments conducted on supercomputing clusters demonstrate significant speed improvements over a state-of-the-art direct solver in both static and transient analysis.

# DEDICATION

I dedicate this dissertation to my parents, my wife and my son.

### ACKNOWLEDGEMENTS

First, I would like to thank my Ph.D advisor and committee chair Dr. Vivek Sarin. The work I have done during my Ph.D career would not be accomplished without his support and guidance. His insight in my research topic helped me solve a lot of problems. Every time when I encountered a tough problem, he always gave me useful suggestions at the first moment.

I am also grateful to my committee members, Dr. Duncan Walker, Dr. Rabi Mahapatra, and Dr. Peng Li, for their guidance in their courses and valuable suggestions for the dissertation. I appreciate their time to serve on my committee.

My gratitude also goes to the Department of Computer Science and Engineering at Texas A&M University for supporting me with teaching assistantship. I also want to extend my gratitude to Dr. Joseph Hurley, Dr. Andreas Klappenecker, Dr. Hyunyoung Lee and Dr. Teresa Leyk for their help when I worked as teaching assistant in their courses.

I thank my friends Yue Liu and Yuqing Zhang for their encouragement and friendship during my life at Texas A&M University.

Finally, I would like to thank my wife and my parents for their support and love.

## TABLE OF CONTENTS

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iii                                                                        |

| ACKKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iv                                                                         |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                          |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | vii                                                                        |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | viii                                                                       |

| CHAPTER I INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                          |

| I.1 Background<br>I.2 Survey of power grid simulation<br>I.3 Proposed work<br>CHAPTER II ENLARGED-PARTITION BASED PARALLEL SOLVER FOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| POWER GRID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| <ul> <li>II.1 Modeling and mathematical background</li> <li>II.1.1 Modeling the power grid</li> <li>II.2 Preconditioned conjugate gradient (PCG) method</li> <li>II.2 Parallel iterative solver based on enlarged partitions</li> <li>II.2.1Power grid partitioning</li> <li>II.2.2 Naive partition-enlarging approach</li> <li>II.2.3 Improved partition-enlarging approach using breadth-first search</li> <li>II.2.4 Error reduction using preconditioned conjugate gradient method</li> <li>II.3 Computational complexity and performance modeling</li> <li>II.3.1 Complexity analysis</li> <li>II.4 Parallelism</li></ul> | 18<br>22<br>24<br>24<br>24<br>26<br>27<br>34<br>38<br>38<br>40<br>40<br>42 |

| CHAPTER III STATIC ANALYSIS OF POWER GRIDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                                                                         |

| <ul> <li>III.1 Static analysis of power grid problem</li> <li>III.2 Experimental results</li> <li>III.2.1 Comparison with state-of-the-art direct solver</li> <li>III.2.2 Comparison with other iterative solvers</li> <li>III.2.3 MPI-based parallel performance</li> </ul>                                                                                                                                                                                                                                                                                                                                                   | 47<br>48<br>52<br>53                                                       |

| III.2.4 GPU-accelerated parallel performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                                                         |

| III.2.5 Impact of partitioning                                          | 56 |

|-------------------------------------------------------------------------|----|

| III.2.6 Impact of parameters                                            |    |

| III.2.7 Performance on different machines                               |    |

| III.2.8 Different parallel implementation                               | 61 |

| III.2.9 Scalability                                                     | 63 |

| CHAPTER IV PARALLEL TRANSIENT ANALYSIS OF POWER GRID                    | 64 |

| IV.1 Transient analysis problem                                         | 64 |

| IV.2 Applying EPPCG in transient analysis                               |    |

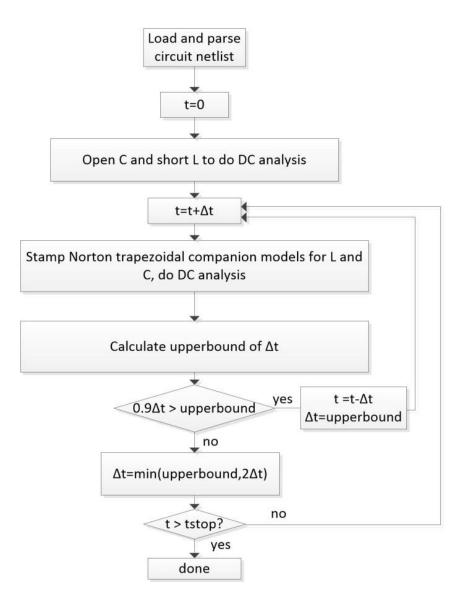

| IV.2.1 Fixed time step vs. variable time step                           |    |

| IV.2.2 Step size control for EPPCG                                      | 72 |

| IV.3 Experimental results                                               |    |

| IV.3.1 Comparison with CHOLMOD with fixed time step                     | 75 |

| IV.3.2 Comparison of EPPCG with variable time step and CHOLMOD with     |    |

| fixed time step                                                         |    |

| IV.3.3 Comparison of EPPCG with fixed time step and EPPCG with variable |    |

| time step                                                               | 79 |

| IV.3.4 MPI-based parallel performance                                   |    |

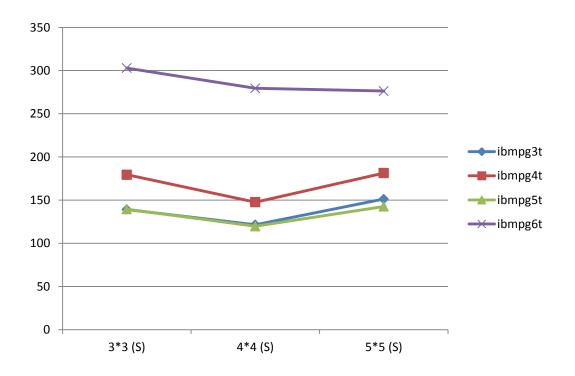

| IV.3.5 Impact of partitioning                                           |    |

| CHAPTER V CONCLUSION                                                    | 83 |

| REFERENCES                                                              | 85 |

## LIST OF FIGURES

| Figure 1. Modeling of a power grid19                                                        |

|---------------------------------------------------------------------------------------------|

| Figure 2. A simple example of power grid20                                                  |

| Figure 3. Partitioning of a power grid into $4 \times 4$ subgrids23                         |

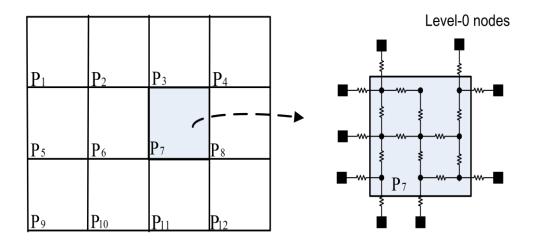

| Figure 4. Constructing the enlarged partition25                                             |

| Figure 5. Including inner nodes and edges                                                   |

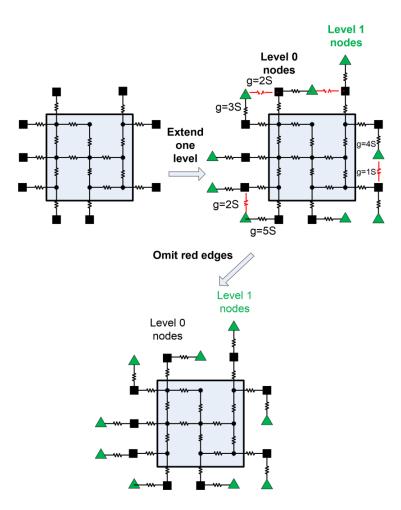

| Figure 6. Extending a partition                                                             |

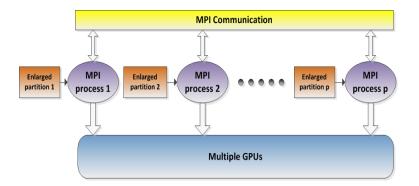

| Figure 7. Parallelization scheme                                                            |

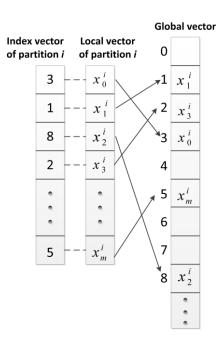

| Figure 8. Local and global vector projection                                                |

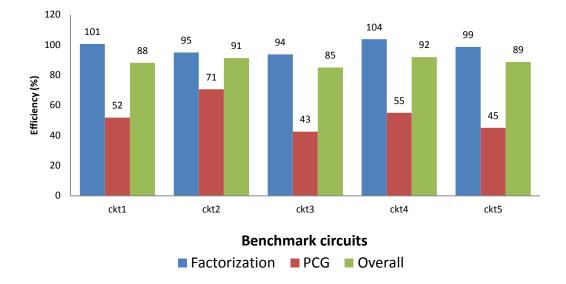

| Figure 9. MPI parallel efficiency for different benchmarks                                  |

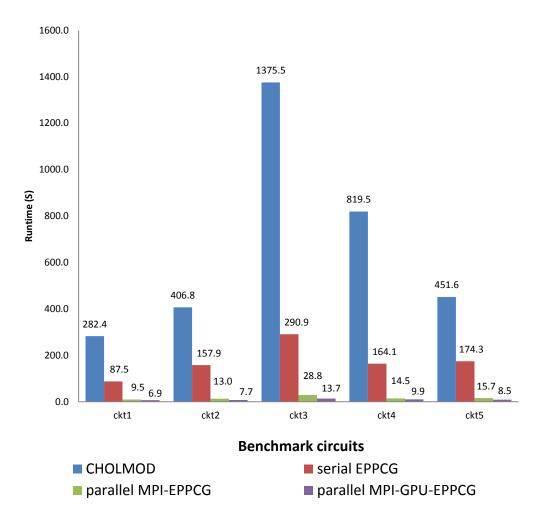

| Figure 10. Overall parallel performance (time in seconds)                                   |

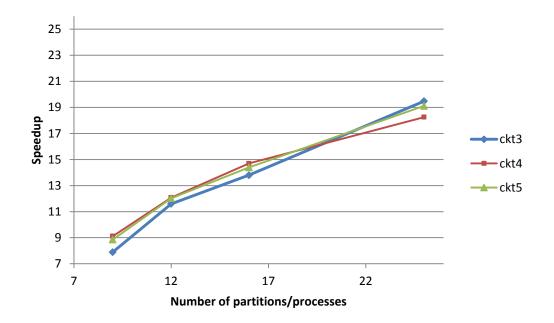

| Figure 11. Parallel performance with different number of partitions                         |

| Figure 12. Modeling power grid in transient analysis                                        |

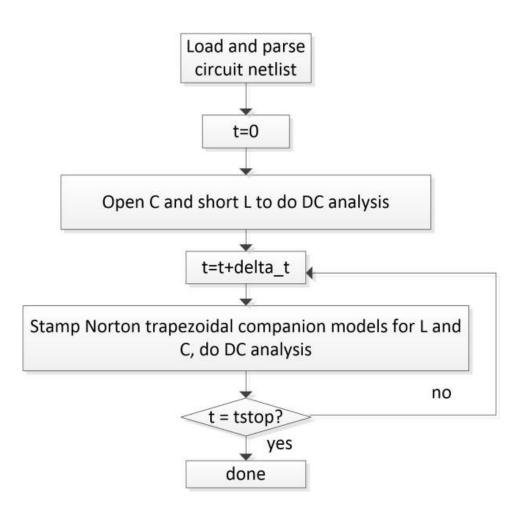

| Figure 13. Flow of transient analysis with a fixed time step                                |

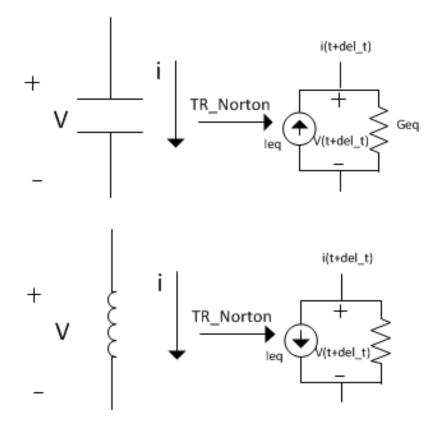

| Figure 14. Companion model for <i>C</i> and <i>L</i>                                        |

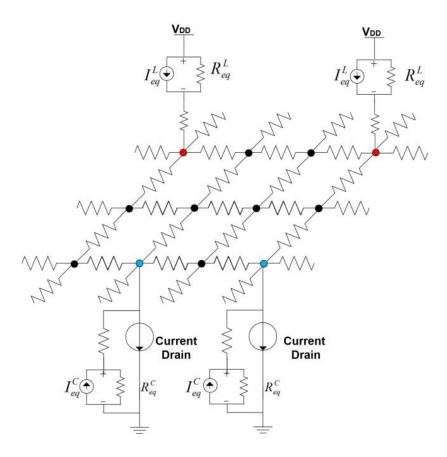

| Figure 15. Companion model of power grid                                                    |

| Figure 16. Flow of variable time step analysis73                                            |

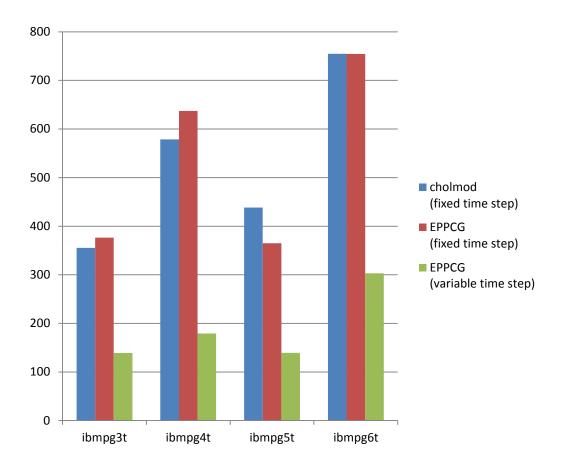

| Figure 17. Performance comparison among CHOLMOD, EPPCG(fixed step) and EPPCG(variable step) |

| Figure 18. Transient performance with different partitioning scheme                         |

## LIST OF TABLES

| Table I. Solution errors of enlarged partitions with different EP-size        | 33 |

|-------------------------------------------------------------------------------|----|

| Table II. Specification of experimental power grids                           | 49 |

| Table III. Speed improvement over direct solver                               | 50 |

| Table IV. Speed comparison between iterative solvers and serial EP-PCG solver | 51 |

| Table V. MPI parallel performance                                             | 52 |

| Table VI. Enhancing parallel performance with GPUs                            | 54 |

| Table VII. MPI-GPU-EPPCG performance with different number of partitions      | 57 |

| Table VIII. Parallel performance with varying parameters                      | 59 |

| Table IX. Comparison of EPPCG performance between machines                    | 60 |

| Table X. Comparison between MPI and OpenMP performance                        | 61 |

| Table XI. EPPCG performance on different benchmarks                           | 62 |

| Table XII. Specification of power grids for transient analysis                | 74 |

| Table XIII. Parallel EPPCG vs CHOLMOD with constant time step                 | 76 |

| Table XIV. EPPCG with variable time step vs CHOLMOD with fixed time step      | 77 |

| Table XV. EPPCG performance with different time step strategies               | 78 |

| Table XVI. MPI parallelization performance                                    | 80 |

| Table XVII. EPPCG performance with different number of partitions             | 81 |

#### CHAPTER I

#### INTRODUCTION

#### I.1 Background

In modern industry, VLSI circuits have become more and more complicated in structure. The VLSI chip design flow consists of several steps, such as architectural and logic design, circuit and layout design, and fabrication [1]. Each step needs verification and testing to guarantee the functionality of the chips. In order to ensure chips run functionally, simulation techniques are widely adopted. Circuit simulation was introduced to industry in 1950s [2]. Circuit simulation and verification, including power grid (a.k.a. power delivery network) simulation, play a critical role in VLSI design. The functionality of a circuit design can be verified by using computer simulation without fabricating real chips. Therefore, simulation provides an inexpensive and efficient way in the VLSI circuit design process.

Power grid simulation is part of circuit simulation in VLSI design. The power grid consists of metal layers that provide power to active devices in the VLSI circuit. In each metal layer, power networks are modeled as vertical and horizontal wires. Different layers are connected through vias. In the widely used flip-chip package [3], Controlled Collapse Chip Connections (C4) bumps provide connections between the external power supply and the power grid. In the power grid simulation, the voltage drop, a.k.a. IR drop, is estimated through simulation to check the functionality of a power grid. Even though the wires in the power grid are made of metal, a small resistance can lead to nonignorable IR drop. If the IR drop exceeds a threshold (typically 10% of  $V_{DD}$ ), the chip could become defective. Therefore, detecting over-threshold IR drop is a key process in power grid design. Another factor that needs to be estimated is electromigration [4]. Electromigration is generated by the movement of electrons in metal interconnects. It can result in connection disruptions derived from heating and diffusive displacement. One way to simulate electromigration is to calculate branch currents and guarantee that the branch currents do not exceed a specific threshold. The branch currents can be obtained using the value of node voltages and the value of the resistance between two nodes.

At the present time, the size of the power grid is increasing quickly due to a rapid increase in the size and complexity of VLSI circuits. The number of nodes in a VLSI power grid can easily reach hundreds of millions. As a consequence, solving a VLSI power grid is extremely time-consuming. Furthermore, the industry is focused on low power design, which introduces additional challenges for power grid design [5]. Voltage can easily drop below safe thresholds in low power chips, resulting in a the chip that fails to operate functionally [6].

Power grid simulation can be categorized as static analysis and transient analysis. Static analysis is conducted by ignoring all the capacitors and inductors. The static power grid simulation is the basis of transient analysis. Transient analysis can be conducted by implementing static analysis at different time steps by using the companion model for capacitors and inductors. In static analysis, power grid can be modeled as a sparse linear system. Consider a linear system

$$Ax = b \tag{1}$$

where  $A \in \mathbb{R}^{N \times N}$ , x and  $b \in \mathbb{R}^N$ , N is an integer representing the size of the system.

The matrix *A* is a sparse matrix, where there are a lot of zero entries in the matrix and a small portion of the entries are non-zeros. Sparse linear matrices are often stored in different formats [7]. Compressed Row Storage (CRS) and Compressed Column Storage (CCS) are widely used in linear system solvers since they are friendly to matrix and vector operations. Coordinate format (COO) is another sparse matrix storage format. It is easy for maintenance (e.g., delete, add, modify, etc). However, COO is not suitable for linear system solver operations. List of lists (LIL) is another sparse matrix storage format. The entries are often sorted by column index. This feature makes LIL faster for look up and good for incremental matrix construction.

Equation (1) can be solved using either a direct solver or an iterative solver. The most famous direct solver is Gaussian Elimination, which is also considered as LU solver. The matrix is factored as a lower triangle matrix L and an upper triangle matrix U. Then a backward or forward substitution is applied to solve the linear system. The complexity of LU factorization is  $O(n^3)$ , and the backward and forward substitutions cost O(n) each, where n is the size of the system. With regard to sparse linear systems, the complexity of LU factorization can be reduced to  $O(n^{1.5})$ . From the complexity, the factorization dominates the solution process. Thus if the factorization can be parallelized, the direct solver would achieve much higher performance.

The advantage of direct solvers is that the solution is accurate and the cost is low. In current academia and industry, the state-of-the –art direct solver named CHOLMOD [8] is widely used. CHOLMOD is an excellent direct solver designed by Dr. Tim Davis. It utilizes graph theory to optimize the computation in Cholesky decomposition in direct solver. The disadvantage of direct solvers is huge memory usage and difficulty of parallelization. Direct solvers need to store the factors in memory which could cost  $O(n^2)$  space for a sparse matrix unless special techniques are used. Techniques such as nested dissection ordering [9] can lower the storage requirement to O(nlogn). Parallelization of direct solvers is limited since the factorization and substitution solve need to wait for results from previous row or column [10].

The sparse linear system can be solved using iterative solvers. The most wellknown iterative solvers include Jacobi method, Gauss-Seidel method, Conjugate Gradient method (CG) and Generalized Minimum-Residual method (GMRES). Typically, an iterative solver needs O(n) memory storage. The advantage of iterative solvers includes potential for parallelism and a low memory footprint. Iterative solvers are friendly to parallelization since the whole process only includes matrix vector operations. The vectors are reused so that the memory usage is low.

However, the solution accuracy is an issue for iterative solvers. Thus a reasonable tolerance of solution error is needed to guarantee the solution accuracy. Furthermore, iterative solvers are prone to suffer from slow convergence. Krylov subspace method is a technique to accelerate convergence of iterations. The Krylov method is based on Krylov space projection and different choice of Krylov subspace leads to different iterative methods [11, 12]. Further acceleration can be achieved by using preconditioners. Preconditioners are often used to accelerate convergence of iterative solvers. A good preconditioner can make the iterative solver even fast than a direct solver. However, finding a good preconditioner is challenging. Also, different linear systems perform differently using different preconditioners. Thus, a particular preconditioner needs to be constructed for each linear system. Given a linear system (1), if the condition number  $\kappa(A)$  is large, the system is ill-conditioned [13]. Ill-conditioned linear system could bring uncertainty to the solution. Preconditioning can reduce the condition number of a linear system, such that more reliable solution can be obtained.

Power grid simulation can be categorized as static analysis and transient analysis. Static analysis is to simulate the behavior of DC status. In static analysis, all the capacitors and inductors are ignored by opening the capacitors and shorting the inductors. The resulting power grid is a resistance network and can be modeled as a linear system as (1). Solving the power grid is to obtain the voltage value of each node. Then the branch current can be calculated using the voltages of the two end nodes. Therefore, the behavior of the power grid can be estimated from the voltage at each node. Transient analysis is to simulate the time-varying behavior of power grid. In transient analysis, the power grid is a RCL consisting of resistance, conductance and inductance. The noise in the power grid consists of IR-drop and  $L \cdot di/dt$ ,. In order to simulate the transient behavior, static analysis is conducted at multiple time instances. The solution process at a specific moment is a process of DC analysis. One must note that, in transient analysis with constant time-step, the conductance matrix remains the

same during the transient analysis and only the right-hand-side vector changes by applying the solution of previous time step. Thus, direct solver always performs better than iterative solver in transient analysis since the matrix factor can be reused during the transient simulation.

Solving a real power grid is challenging due to the size and complexity of the power grid. The following issues need to be considered for a power grid solver:

• Memory usage:

A real power grid can easily have hundreds of millions of nodes. The memory usage for storing the linear system and solving the linear system is quite huge. As we know, iterative solvers use less memory than direct solvers. However, the memory storage for an iterative solver can reach hundreds of Giga Bytes. This huge memory requirement makes the computation difficult to conduct since the modern computers are not equipped with large sized memory. Therefore, solving a real power grid often needs special computers with hundreds of Giga-byte memory installed. In order to solve the memory problem, distributed computing techniques can be used to distribute the burden onto multiple machines. Each machine does not need to have huge memory but the overall memory size is large enough for solving the power grid. Although distributed computing gives power grid solver a solution to meet the huge memory requirement, the management of distributed memory and optimization of data transfer between memories are very challenging.

6

• Time cost:

As VLSI circuit size increases, the time to solve a power grid increases drastically. The low efficiency of power grid solver makes the power grid design process quite time-consuming. Every time a problem is found in the power grid design after simulation, the power grid needs to be modified to fix the design problem. Then another power grid simulation is conducted on the new design. If multiple such design problems are encountered in the design loop, the costly power grid simulation needs to be done several times until the design has no flaw. This design process suffers due to inefficient power grid solver. Therefore, acceleration of power grid simulation is desired in current IC industry.

• Solution Accuracy:

Solution accuracy is required in power grid simulation. If the couputed solution is not accurate enough, the fabricated chip could malfunction. This solution inaccuracy could result in huge time and financial loss in reality. As we know, direct solvers always have high solution accuracy, whereas iterative solvers may suffer from low solution accuracy. Iterative solvers are widely used since they require less memory storage and they can beat direct solvers in speed with an effective preconditioner. The solution accuracy becomes an issue for iterative solvers, since iterative solvers often suffer from slow convergence derived from small error tolerance. If an effective and efficient preconditioner can be constructed to accelerate the convergence of iterative solvers, the power grid simulation would benefit from the acceleration. • Scalability:

Scalability is an important factor in power grid simulation since the size of power grids varies. A good power grid solver should be scalable and have consistent performance over different sized power grids. Parallel algorithms developed on distributed systems are ideal to meet scalability demands since the time cost and memory usage can be assigned to multiple machines to obtain good performance on runtime and memory storage.

## I.2 Survey of power grid simulation

General circuit can be simulated using SPICE [14]. SPICE is not a perfect power grid solver since the characteristic of power grids is not fully addressed. Therefore, simulators developed for power grids are desired. Power grid simulation has been investigated using different techniques. The power grid problem for the static case can be modeled as an s.p.d (symmetric positive definite) linear system. In [15], a Preconditioned Conjugate Gradient (PCG) method with sub-circuit based preconditioner is presented. Good performance is reported when using a mutable preconditioner at each iteration. Multigrid methods are widely-used in power grid analysis. A multigrid based grid reduction mechanism results in less work-load [16]. More recently, an algebraic multigrid approach was presented in [17] that achieves good performance in both runtime and memory usage. A preconditioned Krylov-subspace iterative method for solving large-scale power grid problems was proposed in [18], where the authors implemented a PCG method to accelerate the rate of convergence. The random walk approach introduced in [19, 20] helps in incremental analysis where the conductance matrix is changed to simulate the change of resistance network (length and width change of the wires). [21] presents a support graph based iterative solver. The effective preconditioner reduces the number of iterations to within an acceptable range. In [22], a relaxation iterative method is discussed. This work was presented as node-by-node traversals and row-by-row traversals and achieves good performance.

Transient analysis is an important topic in IC circuit simulation. Different time step strategies affect the performance of transient solvers. [23] presents a power grid solver for transient analysis. This work adopts a grid reduction strategy to obtain much better results compared to SPICE. In [24], a telescopic projective numerical integration method is presented. An adaptively controlled integration method is discussed in [25]. The time step is adjusted during the transient analysis and the implementation achieves automatic load balancing. The parallel implementation on multi-core machines shows encouraging results. Various transient analysis methods for power grids are presented in [26-28]. [28] presents a transient power grid solver that applies symmetric formulation and uses fast Cholesky factorizations. Model order reduction (MOR) technique is utilized in [27] to reduce the data dimensionality. In this work, a direct solver and multimode moment matching techniques are used to achieve good performance. [26] presents a transient solver based on waveform relaxation techniques. A combination of partitioning and convergence acceleration is used to achieve good performance. The method is highly parallelizable and scalable on power grids with different sizes. In [29], a transmission-line-modeling-alternating-direction method is proposed. This work first models the power grid as a structure of transmission line meshes. Then alternatingdirection-implicit method is adopted to conduct transient analysis with high stability. [30] introduces an efficient transient power grid solver. The authors developed an efficient algorithm to reduce the complexity of the power grid using regularities. An efficient solver for transient analysis of the power grid is discussed in [31]. A smart mapping approach is developed in this work to obtain accurate solutions. The performance is improved by utilizing a memorized supernode technique. [32] introduces a transient analysis method that uses a hierarchical relaxed approach. The relaxation technique help obtain significant speedups over PCG and SPICE3.

In order to solve realistic problems in a reasonable amount of time, it is necessary to develop parallel algorithms for power grid analysis. Parallel algorithms for power grid simulation need to be implemented on parallel computers to obtain the solution faster. The current widely used parallel computing technoogies include Message Passing Interface (MPI), OpenMP and GPU. MPI is a message passing library for parallel computing. The MPI standard was first introduced in 1994. MPI provides an interface for users to create multiple jobs as separate processes and run the jobs concurrently. Different processes communicate with each other using messages [33]. OpenMP is a shared memory based parallel computing interface. OpenMP utilizes threads to run multiple jobs concurrently [34]. As the modern computing clusters and multi-core techniques develop, MPI and OpenMP help gain better performance while retaining portability. In contrast, the GPU is a hardware platform developed for processing 3D graphics and visual effect [35]. Currently, researchers found GPUs have the ability of accelerating more general computation, especially matrix computations [36], based on its many-core characteristic. Consequently, General-Purpose Computing on Graphics Processing units (GPGPU) was introduced in 2003 SIGGRAPH conference. CPU-GPU hybrid parallelization is a way to gain better performance. [37] presents a CPU-GPU hybrid approach applied in multifrontal method. Power grid simulation can benefit from those parallel computing techniques. GPGPU technology has been used in Electronic Design Automation (EDA) for years. In [38], the authors successfully accelerated two costly computations, Sparse-Matrix Vector Product (SMVP) and graph traversal in EDA using GPU. [39] introduced GPU a programming scheme for EDA using OpenCL.

In parallel power grid analysis, the biggest challenge is partitioning the grid into sub-grids such that the solution can be obtained quickly by solving sub-problems concurrently. A parallel direct solver was presented in [40], where a parallel matrix inversion algorithm was shown to achieve good time and memory performance. Partitioning based parallel solvers are presented in [41-43] and [44]. Domain decomposition method is adopted in [41] to solve power grid. However, this method suffers from costly processing of the overlapping area. [43] presents a non-overlapping domain decomposition approach. In this work, too much time is spent on forming the Schur complements. Locality driven parallel analysis was introduced in [42], where the authors divide the grid into coupled sections and use locality property to compensate the boundary effect and decouple the sections. This method could exhibit low performance if the C4 bumps are distributed sparsely throughout the power grid. The reason is that sparse distribution of C4 bumps can lead to huge window size, in which solving the windows is expensive. [45] presents a parallel forward and back substitution method. This method computes independent variables in parallel and develops a node ordering to eliminate the data dependency. Random walk has been reported to be applied in solving power grids [46-48]. Through statistical estimation, the node voltages can be obtained in a certain number of walks. However, if the  $V_{DD}$  destination is too far from the 'home', this method can suffer from large number of walks. In [26], the authors propose a waveformrelaxation based transient power grid simulator. The performance of the method may degrade when the initial guess is not reasonable. Macro-modeling method is presented in [49, 50]. In this work, a divide and conquer strategy is adopted over geometry partitioned power grids. The power grid is divided into small sub-partitions, and ports and interfaces are constructed by applying matrix substitution on different sub-partitions. The drawback of this method is that it suffers from dense matrix operations derived from ports. Another pattern based iterative solver is presented in [51]. In this work, pattern structure help to achieve performance improvement on both time and memory. GPU is adopted in Poisson optimized solver in [52]. The GPU implementation of Poisson solver benefits from multi-threaded GPU acceleration. Although the approach performs well, lack of parallelization make these method not ideal to large scale power grids. A transform-based iterative solver using GPUs is proposed in [53, 54]. The solver performs well for 3-D multiple-layer power grids. A GPU-based multigrid PCG solver is presented in [55]. The authors adopted a multigrid preconditioned CG method and successfully accelerate the solver on GPU platform.

Power grid simulation is a step in power grid design [56]. The behavior of a power grid needs to be simulated multiple times to obtain a design for fabrication. The power grid design is a discussed in the following literatures. A parallel design method of power grid is presented in [57]. In this work, a macro-modeling strategy is adopted to implement partition based optimization. [58] discusses the use of linear programming to improve power grid wire size optimization.

#### **I.3 Proposed work**

In this work, we adopt a divide-and-conquer strategy and propose an enlarged partition based parallel iterative solver for large-scale flip-chip power grid simulation. This approach divides the power grid into multiple partitions. In order to obtain an approximate solution for each partition, an enlarged partition is generated to enclose the original partition. Two partition enlarging methods are discussed in this dissertation. One is a na we approach, in which a large area is specified to include all the nodes and edges as extension. The idea of this approach is simple. However, this na we approach could have the following drawbacks. First, isolated nodes may be generated since the boundary of the new enlarged partition does not rely on the connection between two nodes. Isolated node may result in singular linear system that cannot be solved. Second, the na we approach includes all the nodes and edges into the enlarged partition which may not be useful to obtain more accurate solutions. This makes the solving process of enlarged partition over-burdened and downgrades the parallel performance. Third, in a real chip, the whole power grid could consist of disconnected sub-grids. The na we

approach could bring nodes and edges that do not belong to the partition. In this case, the solution accuracy is lowered and computation on unnecessary nodes affects the parallel performance. In order to overcome these drawbacks, a Breadth First Search (BFS) based partition enlarging algorithm is proposed. The enlarged partition first includes all the edges and nodes in the original partition. Then starting from the boundary nodes, a BFS method is applied to include more nodes and edges. When a new node is encountered, the edge with the largest conductance value is retained. All the other edges from this new node are ignored. This strategy trims most of the edges that have low influence on the solution and only retains the edges that are more useful to the solution. In order to control the solution accuracy, all the edges are retained up to a certain level. This step is necessary in our approach since the solution error is large if no such edges are retained outside the original partition. By solving the enlarged partitions one by one, an approximate solution for each partition is obtained. An approximation to the global solution is constructed from partition solutions. Since the global error is large, one can use PCG to reduce the error below the specified threshold. The enlarged-partition solver acts as a preconditioner for PCG.

The solver can be parallelized using MPI on a multi-processor supercomputer. Each enlarged partition is factored and solved by an MPI process. Besides, other computations within the PCG algorithm are assigned to different MPI processes to obtain good runtime performance. Between MPI processes on different cores/machines, data transfer rate play an important role in the time performance. MPI\_Allgather and MPI\_Reduction are two routine used in data transmission. The parallelization of EPPCG can be separated into two parts: factorization and matrix-vector operations. Factorization is parallelized by assigning each partition matrix to a computing node/core. Data transmission between nodes/cores is not necessary since the factorization is conducted on each enlarged partition itself. Other computations include matrix-vector multiplication, vector-vector inner produce, vector summation, etc. Matrix vector multiplication is computed on the enlarged partition since at least one more layer outside the original partitions is needed to obtain the correct results. Other vector related computations are implemented on partitions since no additional data is needed outside the original partition. The GPU is adopted to accelerate the factorization within the direct solver CHOLMOD. A two-tier parallelization is used to obtain the best performance.

The experiments are conducted on IBM P/G benchmarks and artificial largescale benchmarks. Both static and transient analysis is implemented. In static analysis, all the capacitors and inductors are ignored and the power grid is simplified as a resistant network. Only a sparse linear system is solved in static analysis. Our experimental results show that the enlarged partition based preconditioner is effective. The fully parallelizable preconditioner is computed and stored on different machines, such that the time and space cost are distributed onto different machines. The parallelization of our implementation is efficient. The best results obtained on the largest benchmark demonstrate a speedup improvement of 130X over the state-of-the-art direct solver CHOLMOD when using 16 cores. The effective preconditioner and efficient parallelization makes our approach much faster than CHOLMOD. In transient analysis, the same enlarged partition based preconditioner is used. Static analysis is conducted multiple times at different time instances. In general, a direct solver is ideal for transient analysis, since the most time-consuming process of factorization only needs to be conducted once in fixed time-step scenario. In constant time-step transient analysis, our approach is slower than direct solver due to the costly PCG solving process. In variable time-step scenario, our approach performs better than direct solver since the factorization needs to be computed at each time step.

The main contributions of this work can be summarized as follows:

- The proposed enlarged-partition based preconditioner is effective. It reduces the number of iterations significantly compared to classical preconditoners. As a consequence, the proposed EPPCG method converges in fewer iterations.

- Our proposed enlarged-partition based preconditioner is fully parallelized on enlarged partitions. The experimental results show the parallelization of preconditioner achieves super-linear speedups in some cases.

- In order to reduce the size of the linear system derived from the enlarged partitions, Breadth-First Search method is adopted when enlarging the partition. This strategy makes the enlarged partitions lightweight and eliminates the potential for isolated nodes.

- A two-tier parallelism is adopted on CPU-GPU hybrid platforms. MPI implementation on CPU is much faster than CHOLMOD. Using GPU acceleration, matrix factorization is further accelerated over dense matrix operations in CHOLMOD. Although GPU results in several times speedup, the

combination with efficient MPI implementation makes the speedup significantly improved. The efficient implementation of MPI-GPU help the proposed approach run 130X faster over the state-of-the-art direct solver on large benchmarks.

- Previous partition based power grid solvers suffer from costly processing of boundary areas. In [42] and [43], the conductance matrix associated with the boundary area can be either a dense matrix of the graph network or of huge size. Our proposed partition enlarging method extends the partition through edges and ignores edges that have relatively less information. The method makes the generated conductance lightweight for computations.

- Transient analysis is conducted using EPPCG method. Direct solvers are hard to beat in runtime due to the reuse of factorization. Our approach combines the advantages of direct solver and iterative solver. The factorization in EPPCG can also be reused in transient analysis. In fixed time-step scenario, we observed comparable time with CHOLMOD. In variable time-step scenario, our approach performs better than CHOLMOD.

#### CHAPTER II

## ENLARGED-PARTITION BASED PARALLEL SOLVER FOR POWER GRID<sup>\*</sup>

#### **II.1 Modeling and mathematical background**

### *II.1.1 Modeling the power grid*

Power grid plays an important role by providing power to active devices in electronic chips. IR drop would be significant if only single or multiple wires are used for power delivery. Power grids are designed to minimize the IR drop and guarantee the functionality of chips.

Power grid simulation is part of VLSI circuit simulation, and consists of simulating the behavior of the power network. Power grid simulation is a necessary step before fabricating actual chips to examine faults in the design. The low-cost and easy-to-change properties make the power grid simulation a necessary step in power grid design.

A power grid can be modeled as an RCL network consisting of metal wires. In our work, we conduct both static analysis and transient analysis. Transient analysis can be implemented as static analysis on multiple time points. Therefore, the proposed algorithm for solving power grids is described over static analysis. The strategy for transient analysis will be discussed based on static analysis approach. The power grid is modeled as a resistance network by ignoring the capacitors and inductors. The structure

<sup>&</sup>lt;sup>\*</sup> Part of this chapter is reprinted with permission from "An enlarged-partition based preconditioned iterative solver for parallel power grid simulation" by L. Zhang and V. Sarin, in *Quality Electronic Design, 15th International Symposium on*, pp. 715-722, 2014, Copyright[2014] IEEE. [44]

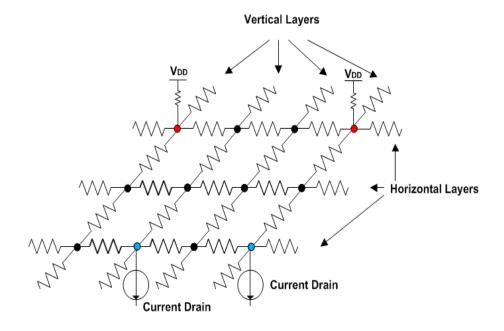

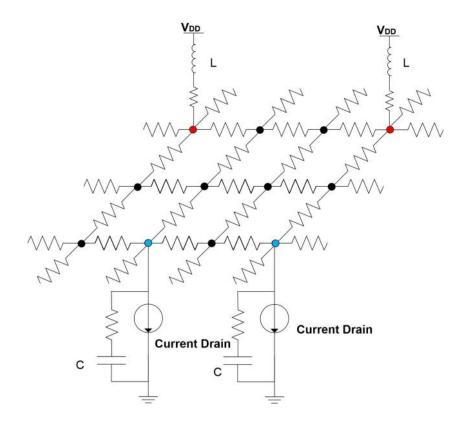

of the power grid can be irregular, in which the nodes in the power grid are not wellconnected. The static power grid is a resistance network, which can be described as a weighted graph where nodes are connected to each other through edges with weight (resistance value). In the following discussion, we call the resistance between two nodes 'edge'. Typically, a power grid contains multiple layers including vertical and horizontal layers, and consists of  $V_{DD}$  and GND networks. Figure 1 shows a  $V_{DD}$  power network. The red circles represent C4 bump connections, where the external power supply ( $V_{DD}$ ) is connected to the power grid. Active devices that pull current from the power grid are modeled as current drains. Different layers are connected through vias. The power grid can be considered as a 3D structure that is more difficult to solve than a 2D structure

Figure 1. Modeling of a power grid

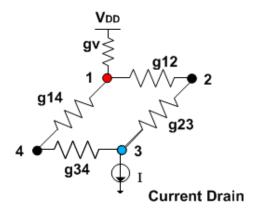

Figure 2. A simple example of power grid

[59]. GND network is similar to  $V_{DD}$  network except the C4 bumps are connected to GND and the direction of current drains is opposite.

In power grid simulation, the voltage of each node is unknown. Solving a power grid is a process to obtain the values of those node voltages. Moreover, branch currents can be calculated using the obtained node voltages. Nowadays, power grid simulation is very costly in both time and space due to the huge size of VLSI circuits. Therefore, fast power grid solver is in great need.

Based on Kirchhoff's current law, the current flowing out of a node equals that flowing into a node. Figure 2 shows a simple example of power grid. Taking node 3 as example, we have

$$g_{34}(V_4 - V_3) + g_{23}(V_2 - V_3) = I$$

<sup>(2)</sup>

A more general equation for an arbitrary node x is

$$\sum_{i} g_{ix} (V_i - V_x) = \sum_{m} I_{xm}$$

(3)

where node i denotes a neighbor of node x,  $g_{ix}$  denotes the conductance between node i and node x, and  $I_{xm}$  denotes one of the current drains on node x.

In matrix form, based on Modified Nodal Analysis (MNA) [60], the overall power grid system can be modeled as a linear system.

$$GV = I \tag{4}$$

Assume there are N nodes and M C4 bumps in the power grid, G is an  $(N + M) \times (N + M)$  matrix which represents a conductance matrix with information about  $V_{DD}$ , V is an  $(N + M) \times 1$  vector which represents the unknown node voltages, and I is an  $(N + M) \times 1$  vector which represents the current load of active devices and  $V_{DD}$  values. Now that  $V_{DD}$  is connected between GND and the power grid, the linear system can be reduced by eliminating M rows/columns as illustrated below.

Since  $V_{DD}$  is a known constant, the size of the matrix can be reduced by eliminating columns and rows that correspond to  $V_{DD}$  nodes. The revised linear system can be described as

$$\begin{pmatrix} g_{12} + g_{14} + g_{v} & -g_{12} & 0 & -g_{14} \\ -g_{12} & g_{12} + g_{23} & -g_{23} & 0 \\ 0 & -g_{23} & g_{23} + g_{34} & -g_{34} \\ -g_{14} & 0 & -g_{34} & g_{14} + g_{34} \end{pmatrix} \begin{pmatrix} v_{1} \\ v_{2} \\ v_{3} \\ v_{4} \end{pmatrix} = \begin{pmatrix} V_{DD}g_{v} \\ 0 \\ -I \\ 0 \end{pmatrix}$$

(5)

Based on the discussion above, the power grid system is modeled as an improved linear system

$$G'V' = I' \tag{6}$$

Assume there are N nodes in the power grid, Here, G' is an N  $\times$  N matrix which represents the conductance matrix, V' is an N  $\times$  1 vector which represented the unknown node voltages, l' is an N  $\times$  1 vector which stands for the current load of active devices and  $V_{DD}/g_v$  for C4 bumps. G' is a symmetric positive-definite system.

The sparse linear system (6) can be solved using many methods consisting of direct solvers and iterative solvers. The direct solver usually first factorizes the matrix of the linear system, then backward/forward substitution is adopted to obtain the solutions. When solving a sparse linear system, the factorization costs the most of the runtime compared to backward/forward substitution. The benefit of direct solver is that direct solver can solve the linear system more accurately than iterative solver. The most widely used direct solver is LU factorization and backward substitution. Usually, factorization such as LU factorization and Cholesky factorization are used to store the factors for reuse. Iterative methods, including GMRES and Conjugate Gradient methods, solve the linear system in an iterative way to reduce the error step by step. Generally, direct solver is faster but requires more space storage. Iterative solvers use less memory but depend on a good preconditioner to achieve fast convergence. Our algorithm described in next section is a combination of direct solver and iterative solver that combines the advantage of both solvers.

### II.1.2 Preconditioned conjugate gradient (PCG) method

Conjugate Gradient (CG) method is a widely used iterative method for solving s.p.d. linear system Ax = b [61]. An advantage of the CG method is that it requires much less memory compared to direct methods. Although convergence of CG is guaranteed for s.p.d systems, it may still need large number of iterations to converge. Most of the time, in order to reduce the number of iterations, preconditioning method is used.

Preconditioning is an approach to reduce the computational time when solving a linear system Ax = b. A preconditioner, say M, is a matrix such that the condition number of  $M^{-1}A$  is small. Typically, the preconditioner M is applied to the linear system equation as  $M^{-1}Ax = M^{-1}b$ . If the preconditioner M is close enough to A (i. e.,  $M^{-1}A \approx I$ ), the linear system will become much easier to solve. Each iteration of PCG requires a preconditioning step. The preconditioning step involves computing Mz = r.

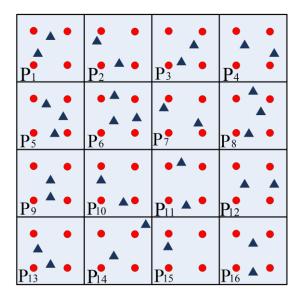

Figure 3. Partitioning of a power grid into  $4 \times 4$  subgrids. Red circles represent C4 bumps; blue triangles represent current drains

A good preconditioner is key to accelerating the rate of convergence of the PCG method. If the preconditioner is easy to set up, but the condition number of  $M^{-1}A$  is large, the number of iteration will not drop and the time required to solve the system can be high. On the other hand, if the condition number of  $M^{-1}A$  is small, but the cost of computing and applying the preconditioner is large, solving the system will still be costly. Setting up a preconditioner often requires a lot of computation time. If the process of setting up a preconditioner can be parallelized, the total run time will be significantly reduced.

### **II.2** Parallel iterative solver based on enlarged partitions

Parallelization of power grid simulation is challenging, because it is hard to separate the power grid into decoupled sub-grids. In this section, an enlarged-partition based preconditioned power grid solver is proposed.

### *II.2.1Power grid partitioning*

In order to solve the power grid in parallel, the basic idea is to separate the power grid into multiple disjoint partitions. Figure 3 shows a power grid divided into  $3 \times 4$  partitions. Our partitioning strategy is to divide the power grid into equal-sized partitions in geometry. The edges that are across the partition boundaries are neglected and all the nodes are retained. Approximate solutions within each partition can be obtained by solving those sub-grids/partitions. However, the error of the approximate solution is far beyond our tolerance due to the inaccurate solution on the boundaries. Inspired by the

'spatial locality' property of power grid [62], the partitions are enlarged to achieve more accurate solutions.

Spatial locality demonstrates that C4 bumps modeled in a power grid have a limited spatial range of influence on the node voltages. In other words, if a node is close to a C4 bump, the IR drop from the C4 bump at that node is subtle; if a node is far from a C4 bump, the IR drop from the C4 bump at that node is significant. If we solve a larger area which enclose the original partition and retain the solutions within the partition, we can obtain more accurate solutions within the partition including the boundary. Based on the discussion above, we enlarge the partitions to include more nodes and edges such that the solution errors can be reduced.

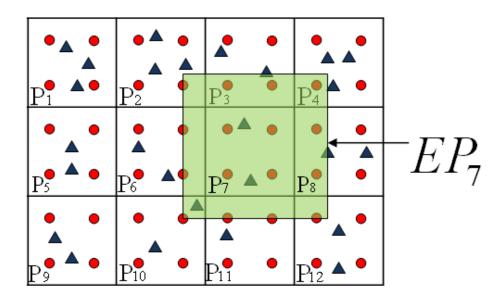

Figure 4. Constructing the enlarged partition

#### *II.2.2 Naive partition-enlarging approach*

Since the power grid is separated into partitions geometrically, a straightforward way to enlarge the partition is to move the border of the partition outwards to a certain distance (Figure 4). After enlarging the partition, the nodes and edges in the original partition are retained and more nodes and edges are included. Note that the edges across the new boundary are omitted.

Suppose the power grid is divided into P partitions. For each partition, we have a linear system

$$G_{ep}^i v_{ep}^i = I_{ep}^i , (7)$$

where  $G_{ep}^{i}$  is the conductance matrix for enlarged partition i;  $v_{ep}^{i}$  is the node voltage vector; and  $I_{ep}^{i}$  is the vector representing current drains. After solving (7), we obtain  $v_{ep}^{i}$  which denotes the solution of an enlarged partitions. In  $v_{ep}^{i}$ , only the voltage solutions at the nodes that belongs to the original partition are retained and other voltage solutions are ignored. Therefore, solving all the enlarged partitions provides voltage solutions on each original partition. The voltage solution derived from the enlarged partition is more accurate compared to the linear system from the original partition because the influence of external C4 bumps near the boundary of the partition is captured.

The straightforward enlarging method is effective and easy to implement. However, it may introduce difficulties for the solution process. It has the following drawbacks. First, the irregular power grid can consist of disjoint sub-grids. The straightforward partitioning method could include disconnected nodes and edges from other sub-grids. Second, in a real power grid, a node is not always connected to all its

Figure 5. Including inner nodes and edges

neighbors. If such a node happens to lie next to the boundary and all its edges are across the boundary, this node will be an isolated node that is not connected to any other nodes. Isolated nodes cause the power grid matrix to become singular. In order to overcome these drawbacks and make the solving process more efficient, we propose an improved partitioning method based on Breadth-First Search (BFS) algorithm.

## *II.2.3 Improved partition-enlarging approach using breadth-first search*

The approach described in II.2.2 is too expensive, since unrelated nodes and edges are also included in the enlarged partition. If we consider the area outside the partition as layers, we can extend the partition up to a certain layer and we can select edges to be included in the enlarged partitions. In this way, the number of nodes and number of edges are fewer than those of the naive approach. As a consequence, the size of the generated linear system matrix and the number of non-zeros will be reduced. This size reduction helps improve the efficiency of the solver.

Since the partition is enlarged layer by layer, we adopt a BFS method to extend the original partition. The resulting enlarged partition is a tree-like structure outside the original partition. Note that we do not include all the edges in the BFS tree, but select the edge with the largest conductance that connects to a node.

To enlarge a partition using BFS our approach consists of the following steps:

1. Retain all the nodes and edges in partitions. All the boundary edges across the partition borders as well as the nodes connected by the edges are retained. The nodes that lie outside the partitions and are connected by boundary edges are called level-0 nodes (Figure 5).

2. Starting with those level-0 nodes, apply breadth first search algorithm to extend the partitions. The level of an extended node is the shortest distance from level 0. The level of an unvisited node is set to -1. If a node is encountered during BFS, the largest edge (defined as the largest conductance) from its parent in the preceding level is retained in the BFS tree (Figure 6). The enlarged partition size (EP-Size) is defined as the number of levels extended out of the original partitions.

3. In order to have better control of the solution accuracy, additional edges are added to the BFS tree. The number of levels for which all edges will be included is defined as retained-level size (RL-Size). For example, if RL-Size is k, then all edges incident on nodes at levels 0 through k are retained. RL-Size is an adjustable parameter to make the partition solution more accurate. Experiments suggest that RL-Size is a necessary parameter to control the solution accuracy and ensure convergence to the solution.

4. Return resulting enlarged partition.

The overall algorithm for enlarging a partition is described in Algorithm 1.

Figure 6. Extending a partition

# ALGORITHM 1. Enlarging a Partition

Input: An partition with node and edge information; boundary information of the

partition; EP-size; RL-size

Output: An enlarged partition with node and edge information.

- 1: Mark all the internal nodes and edges as 'retained', set the level of those nodes = 0.

- 2: Mark all the boundary edges and the nodes connected by boundary edges as 'retained'.

- 3: Mark all the nodes in Step 1 and 2 as 'visited'.

- 4: Create a queue-BFSQueue and push the nodes connected by boundary edges into

BFSQueue, and set the level of those nodes = 1;

- 5: while(BFSQueue not empty)

- 6: CurrentNode=BFSQueue.pop();

- 7: *if*(node.level>EP\_size) then

- 8: *return;*

- 9: end if

- 10: for(each neighbor node-NeiNode of CurrentNode)

- 11: *if*(NeiNode not visited)

- *12: BFSQueue.push(NeiNode)*

- 13: mark NeiNode as 'visited' and set NeiNode's level to

### *CurrentNode.level+1*

- *14: if*(*NeiNode.level*<=*RL\_size*) *then*

- 15: retain all the edges connecting NeiNode and 'visited'

nodes

## *16: end if*

17: check NeiNode's edges connecting to nodes one level lower, retain the edges that holds the largest conductance value and ignore the other edges.

18: end if

*19: end for*

20: end while

One must note that each enlarged partition must have at least one C4 bump. Otherwise, based on the discussion in II.1, the matrix of the generated linear system will be singular. A singular matrix makes the linear system unsolvable. Thus, in our approach, if there are no C4 bumps in the resulting enlarged partition, the enlarged partition is further extended to enclose at least one C4 bump.

Compared to the naive enlarging strategy, the BFS-based partition enlarging approach overcomes a number of drawbacks and reduces the size of the enlarged partition.

1. In a real chip, the power grid can consist of several disjoint sub-grids. During the enlarging process, the naive approach does not consider this situation but extends the border outwards. In this case, it is possible that the enlarged partition includes nodes and edges from other unrelated sub-grids that do not improve the accuracy of the solution on the primary partition. The BFS-based approach does not include these nodes and edges in the enlarged partition, making the partition lightweight and efficient for computations. 2. The naive approach retains all the edges in the enlarged partition. In contrast, the BFS-based partition enlarging method only includes the edges that have the most useful information (largest conductance) and neglect other edges. This strategy reduces the time to solve the enlarged partition system since the conductance matrices have fewer non-zeros due to the inclusion of fewer edges.

3. In a power grid, there exist nodes that are not connected to every neighbor. The naive approach to extending the partitions ends up including some nodes that may not be connected to any other nodes inside the enlarged partition. These resulting isolated nodes make the conductance matrix singular since they have no incident edges. In the BFS-based approach, since each included node is visited from its neighbor and at least one edge from this node is retained, there does not exist any isolated nodes. The BFS-based approach make the enlarged partition friendly to linear system solvers.

After constructing the enlarged partitions using BFS, we have linear systems for enlarged partitions as

$$\overline{G_{ep}^{i}} \, \overline{V_{ep}^{i}} = \overline{I_{ep}^{i}} \tag{8}$$

where  $\overline{G_{ep}^{i}}$  is the conductance matrix for enlarged partition i;  $\overline{V_{ep}^{i}}$  denotes the associated node voltage vector; and  $\overline{I_{ep}^{i}}$  represents the current source vector. After (8) is solved, the solutions belonging to the original partitions are extracted. The solutions are more accurate than the ones obtained from the original partition.

| EP-size | Max error | Average error |

|---------|-----------|---------------|

| 0       | 153.2%    | 7.9%          |

| 5       | 42.8%     | 4.3%          |

| 15      | 10.9%     | 1.2%          |

| 200     | 0.0%      | 0.0%          |

Table I. Solution errors of enlarged partitions with different EP-size

To verify that the enlarged partitions lead to more accurate solutions, we compare the average error and maximum error in Table I. The results are obtained on the benchmark ckt3 (introduced in III.2) with  $3 \times 4$  partitions. As described before, after solving the enlarged partition, only the solutions on the nodes that belong to the original partition are retained. Max error denotes the maximum relative error in node voltage by solving the enlarged partitions; Average error denotes the relative average error. The solution was obtained using a direct solver to guarantee computational accuracy. RL-size is set to be 0 to better demonstrate the comparison. The trend of error changes illustrates that the larger the enlarged partition is, the more accurate the solution we obtain. Two

extreme cases are that EP-size equals 0 and EP-size is large enough to make the enlarged partition cover the whole power grid. As for the first case, the error is huge as seen in the first row of Table I. In the second case, the whole power grid is solved and only the solutions within the original partition are retained. The error is 0 because the exact solutions are obtained.

## II.2.4 Error reduction using preconditioned conjugate gradient method

As presented in II.2.3, larger enlarged partitions lead to more accurate solutions. However, larger enlarged partitions are more costly to solve. Using modest size of enlarged partitions, we obtain solution errors that are still larger than our tolerance. In order to reduce the solution error in an efficient way, we adopt PCG method to conduct the error reduction.

Next, we first briefly review the CG method and preconditioning technique. Then, the proposed Enlarged-Partition based Preconditioned Conjugate Gradient (EPPCG) method is presented.

CG is an iterative Krylov subspace method for solving s.p.d linear systems [12]. Compared to direct solvers, CG requires less memory storage and is friendly to extremely large sparse linear systems. CG method is often enhanced by applying a preconditioner to achieve fast convergence.

Preconditioning is a method to accelerate the solution of linear systems. Suppose we have a linear system Ax = b. Preconditioning is to apply a matrix M to the linear system as  $M^{-1}Ax = M^{-1}b$ , such that the condition number of  $M^{-1}A$  is less than that of A. By applying an effective preconditioner to a linear system, the linear system becomes easier to solve. One extreme case is where M = A, then the left-hand side of the linear system becomes x. As a result, the linear system has been solved by applying such a preconditioner. Usually, a preconditioner is used in iterative solver to accelerate the convergence. In PCG, a preconditioner M is used in each iteration involving computing a matrix-vector product  $z = M^{-1}r$ . Note that z can be computed by solving an equivalent linear system Mz = r. The preconditioner M can be explicit or implicit. In PCG, an explicit preconditioner is applied by computing the matrix-vector product as  $z = M^{-1}r$ . An implicit preconditioner does not have an explicit expression. It outputs a vector z using a given input vector r after a process of computations. This process refers to a preconditioning process.

A good preconditioner is key to the performance of the PCG method. Ideally, a preconditioner is inexpensive to construct and effective for reducing the number of iterations. In our proposed EPPCG method, we apply the implicit preconditioner by solving the enlarged partitions and extracting the solutions belonging to the original partitions as described in Algorithm 2. In other words, given an input vector r, we approximate the solution of the linear system Mz = r by solving the enlarged partitions.

The proposed preconditioner has the following advantages.

The preconditioner is parallelizable. The preconditioner is conducted by solving the enlarged partitions. Solving the enlarged partitions can be done in parallel. In EPPCG, preconditioning costs most of the runtime. A parallelizable preconditioner can help reduce the runtime drastically. Our experimental results discussed in Chapter III indicate that the enlaregedpartition based preconditioner is effective for achieving fast convergence in EPPCG. The proposed preconditioner reduces the number of iterations significantly.

# ALGORITHM 2. Enlarged Partition Based Preconditioner

**Input:** N  $\times$  1vector r, enlarged partition information containing retained node IDs and edges.

**Output:** Preconditioned N  $\times$  1 vector z

- 1: Separate r into  $r_{ep}^{i}$  based on enlarged partition information

- 2: for(each enlarged partition)

- 3: solve  $G_{ep}^i z_{ep}^i = r_{ep}^i$  using a direct solver;

- 4: end for

- 5: for(each original partition)

- 6: extract  $z^i$  of original partitions from  $z_{ep}^i$ ;

- 7: end for

- 8: combine  $z^i$  into the global vector z

- 9: return z

# ALGORITHM 3. EPPCG

**Define:** tol is the error tolerance; K<sub>max</sub>is the maximum number of iterations;

**Input:** The global conductance matrix G; the global current drain vector I; the error tolerance tol; the maximum number of iterations  $K_{max}$

Output: The node voltage vector v.

1: Factorize the conductance matrix  $G_{ep}^{i}$  for each enlarged partition

2: Obtain an initial solution  $v_0$  by applying EP preconditioner on vector I.

3:  $r_0 = I - Gv_0$  //matrix-vector multiplication is conducted on enlarged partitions

- 4: Obtain the preconditioned vector z by applying EP preconditioner on  $r_0$ .

- 5:  $t_0 = r_0$

- 6: while  $(k \leq K_{max})$

- 7: do  $\alpha_k = \frac{\langle r_k, z_k \rangle}{\langle t_k, Gt_k \rangle}$

$$8: \qquad v_{k+1} = v_k + \alpha_k t_k$$

9:  $r_{k+1} = r_k - \alpha_k G t_k$  //matrix-vector multiplication is conducted on enlarged partitions

10: If

$$(||r|| < tol_{k+1})$$

return  $v_{k+1}$

11: Obtain  $z_{k+1}$  by applying EP perconditioner on  $r_{k+1}$

12:

$$\beta_k = \frac{\langle r_{k+1}, z_{k+1} \rangle}{\langle r_k, z_k \rangle}$$

13:

$$t_{k+1} = z_{k+1} + \beta_k t_{k+1}$$

*14:* k = k + 1

## 15: end while

The overall EPPCG algorithm is described as Algorithm 3. The enlarged partitions are solved using a state-of-the-art direct solver, CHOLMOD [8, 63]. CHOLMOD consists of matrix factorization and triangular solve. The runtime of matrix factorization dominates the whole process. The conductance matrices of enlarged partitions do not change in EPPCG. Thus, we factor the matrix before entering the PCG loop, so that the factors are re-used in each iteration. This strategy helps improve performance by eliminating unnecessary repeated factorization.

## **II.3** Computational complexity and performance modeling

## II.3.1 Complexity analysis

As described in Algorithm 3, the EPPCG method consists of two main computational parts. One is the factorization and triangular solve of the conductance matrices for enlarged partitions. The other one consists of remaining computations in PCG method such as matrix-vector multiplications, vector inner-products and other vector operations.

Suppose the power grid is divided into P partitions, enlarging the P partitions results in P enlarged partitions. The number of nodes in the partitions are  $n_1, n_2, ..., n_P$ . For enlarged partition i, suppose the factorization of conductance matrix for enlarged partition costs  $T_f(n_i)$  and applying the preconditioner costs  $T_p(n_i)$ . The runtime of matrix-vector multiplication is defined as  $T_{mv}(n_i)$  and the runtime of vector inner-

product is defined as  $T_{vi}(n_i)$ . Each of the vector operations, such as vector additions, scalar-vector multiplications, is defined as  $T_v(n_i)$ , since they have the same complexity. The overall sequential runtime of EPPCG can be described as

$$T = \sum_{i=1}^{P} T_{f}(n_{i}) + 2\sum_{i=1}^{P} T_{p}(n_{i}) + \sum_{i=1}^{P} T_{mv}(n_{i}) + \sum_{i=1}^{P} T_{v}(n_{i}) + m\left(\sum_{i=1}^{P} T_{p}(n_{i}) + \sum_{i=1}^{P} T_{mv}(n_{i}) + 9\sum_{i=1}^{P} T_{v}(n_{i})\right)$$

(9)

where T denotes the overall runtime and m denotes the number of iterations. Based on our experiments, m is in the range of [2-6]. Note that  $T_p(n_i)$  includes triangular solve and vector extraction operations as illustrated in Algorithm 2. For each enlarged partitions with  $n_i$  nodes,  $T_f(n_i) = O(n_i^{1.5})$ ,  $T_p(n_i) = O(n_i \log n_i)$ , and  $T_v(n_i) = O(n_i)$ [9]. To estimate  $T_{mv}(n_i)$ , we consider the structure of the power grid. In a power grid, a node is connected to up to four neighbor nodes. As a result, there are at most 4 non-zeros at each row/column in the conductance matrix. For a power grid with n nodes, a matrixvector multiplication runs at most 7n operations. Thus,  $T_{mv}(n_i) = O(n_i)$ .

More interesting analysis is the parallel complexity estimation. Assume the number of processors is identical to the number of partitions. Each item in (9) is determined by the slowest process. The overall parallel runtime can be approximated as an equation

$$\overline{T} = \max_{1 \le i \le P} T_f(n_i) + 2 \max_{1 \le i \le P} T_p(n_i) + \max_{1 \le i \le P} T_{mv}(n_i) + \max_{1 \le i \le P} T_v(n_i) + m \left( \max_{1 \le i \le P} T_p(n_i) + \max_{1 \le i \le P} T_{mv}(n_i) + 9 \max_{1 \le i \le P} T_v(n_i) \right)$$

(10)

where  $\overline{T}$  denotes the overall runtime of parallel EPPCG. Since power grid is divided into partitions with equal size and the partitions are enlarged to the same level, the resulting enlarged partitions are of similar size. This work load balance helps the parallel implementation achieve significant speedup. Let  $\tilde{n}$  denote the number of nodes of the largest enlarged partition. Based on the estimate of each item discussed above,  $\overline{T} = O(\tilde{n}^{1.5} + m\tilde{n}log\tilde{n})$ . In the complexity estimation, the factorization of conductance matrices dominates the whole algorithm for extremely large power grids. The parallelization of factorization step helps reduce the runtime drastically.

## II.3.2 Performance modeling

EP-size and RL-size are two parameters to control the speed of convergence of EPPCG. On one hand, if EP-size and RL-size are too large, the factorization time increase due to the expansion of conductance matrices. On the other hand, if EP-size and RL-size are too small, the convergence becomes slow due to the inaccuracy of the solutions to the enlarged partitions. Therefore, finding optimal EP-size and RL-size helps maximize the efficiency of EPPCG. RL-size is found to be 0.75×EP-size approximately in our experiments. Thus, in the following discussion, we are focused on finding the optimal EP-size.

The parallel runtime is approximated in (10). We divide the power grid into equal-sized partitions and the enlarged partitions are formed by extending the partition to the same level. Therefore, the work load of each enlarged partition is similar. We can obtain the following equation derived from (10).

$$\overline{T} \approx T_f(\bar{n}) + 2T_p(\bar{n}) + T_{mv}(\bar{n}) + T_v(\bar{n}) + m\left(T_p(\bar{n}) + T_{mv}(\bar{n}) + T_v(\bar{n})\right)$$

(11)

where  $\overline{n}$  denotes the average number of nodes in an enlarged partition.

Based on our discussion on time complexity in II.3.1,  $T_f(\bar{n})$ ,  $T_p(\bar{n})$ , and  $T_{mv}(\bar{n})$  can be approximated as follows.

$$T_f(\bar{n}) \approx C_1 \bar{n}^{1.5} + K_1$$

(12)

$$T_{mv}(\bar{n}) \approx C_2 \bar{n} + K_2 \tag{13}$$

$$T_p(\bar{n}) \approx C_3 \bar{n} \log \bar{n} + K_3 \tag{14}$$

where  $C_1$ ,  $C_2$ ,  $C_3$ ,  $K_1$ ,  $K_2$ , and  $K_3$  are constants.

Suppose there are n nodes and p partitions, the average number of nodes in a partition is n/p. If we consider the partition as a square, each side of the square contains  $\sqrt{n/p}$  nodes. Since the original partition is large and the number of levels of extension is not significant, we can ignore the difference of number of nodes between levels. Note that the partition is extended on all the four sides of the square. Therefore, the number of nodes added by extending the partition can be approximated as  $4Ep\sqrt{n/p}$ , where Ep denotes EP-size. The total number of nodes  $\overline{n}$  in an enlarged partition can be approximated as follows.

$$\bar{n} \approx 4Ep\sqrt{\frac{n}{p} + \frac{n}{p}}$$

(15)

Based on our experimental observation,  $T_f(\bar{n})$  and  $T_{mv}(\bar{n})$  dominates the overall runtime, and the typical value of m is 3. Therefore,  $\overline{T}$  can be approximated using the following equation.

$$\overline{T} \approx C_1 \left( 4Ep \sqrt{\frac{n}{p}} + \frac{n}{p} \right)^{1.5} + K_1 + C_2 \left( 4Ep \sqrt{\frac{n}{p}} + \frac{n}{p} \right) + K_2$$

(16)