# DYNAMIC MODELING FOR DESIGN AND ANALYSIS OF MEMRISTIVE

# AND STATIC RANDOM ACCESS MEMORIES

# A Dissertation

by

# YENPO HO

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Garng M. Huang      |

|---------------------|---------------------|

| Committee Members,  | Peng Li             |

|                     | Jose Silva-Martinez |

|                     | Guergana Petrova    |

| Head of Department, | Chanan Singh        |

August 2014

Major Subject: Electrical Engineering

Copyright 2014 Yenpo Ho

### ABSTRACT

Nowadays, the trend of modern memory technology is going towards the following directions: (1) look for new nonvolatile devices; (2) keep scaling down the existing volatile devices. Although nonvolatile devices enable to switch off its power supply to further suppress standby power, the down sides are the low switching speed and the complicated dynamic cell characteristics. On the other hand, researchers are looking to scale down SRAM since it is the most reliable and fast. However, the SRAM suffers read and write failure due to lack of good stability optimizing metric. To tackle the above mentioned problems, this work first introduces a promising nonvolatile device called Memristor, which is said to be possible to replace our memory devices now. By starting from basic memristor device equations, this work aims to develop a comprehensive set of properties and design equations for memristor based memory. The introduced schemes are specifically targeting key device properties relevant to memory operations. Using the discovered properties, a simple design of read/write circuits is investigated. In the second part of this work, SRAM stability analysis is focused. SRAM verification and stability analysis has become an essential task to investigate soft-errors. This work aims to extend the SNM to a new era. Based on the introduced Region-Analysis in this work, SRAM stability can be explained using bifurcation theory, and closed form expression can be derived. The derived expression provides physical characterization of SRAM noise tolerance property; thus has potential to provide needed design insights. Overall, dynamics of memristor and SRAM are strongly emphasized.

The derived memristor properties reveals that the memristor state change requires some time; it indicates that the memristor-based memory needs some "critical time" to flip the logic. Similarly to the SRAM, the SRAM write operation not only needs the injected current over a "critical current" but also need to maintain for some "critical time". In short, both memristor-based memory and SRAM show the timely manner for read/write operation. Furthermore, the developed analytical formulae are able to reveal the dynamic aspect on memory read/write operations which address the key concern for modern memory technology.

# DEDICATION

To my lovely father (Jii-Chung Ho) and mother (Li-Li Hu)

and in memory of my grandparents.

#### ACKNOWLEDGEMENTS

First of all, my appreciation goes to my advisor, Dr. Garng M. Huang, for his long-time support and guidance throughout my graduate study. Doctor Huang is always being a role model as a brilliant scientist with rigorous scientific attitude and wisdom, inspiring and encouraging to his students. He not only has taught me technical knowledge for my research work but also the vision to explore new areas for my future professional development. I am truly grateful to him for letting me involve in this interesting project.

I am greatly indebted to Dr. Peng Li. The work presented in this dissertation would not have been done without his support. His advice and guidance are vital to my PhD research. I am heartily thankful to him for sharing his thoughts and giving me helpful suggestions.

In addition, I would like to thank Dr. José Silva-Martínez and Dr. Guergana Petrova for serving on my committee. Thanks also go to my friends: Wenzong Wang, Hangtian Lei, Tian Lan, Li-Wei Tseng, Saeed Samadi, Ting-Xuan Chen and Hung-Yi Liao (Coze). Their friendship makes my time at Texas A&M University a joyful experience. Furthermore, I also want to thank Kai Jiang, Chenyan Guo, Kaigui Xie, Rui Ma and Jun An (Visiting professor) for being as my mentor provide advice toward the success of research path. They made my years at College Station a memorial one.

# TABLE OF CONTENTS

|                                                                                                                                     | Page                 |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ABSTRACT                                                                                                                            | ii                   |

| DEDICATION                                                                                                                          | iv                   |

| ACKNOWLEDGEMENTS                                                                                                                    | v                    |

| TABLE OF CONTENTS                                                                                                                   | vi                   |

| LIST OF FIGURES                                                                                                                     | viii                 |

| LIST OF TABLES                                                                                                                      | xii                  |

| CHAPTER I INTRODUCTION                                                                                                              | 1                    |

| <ol> <li>1.1. Literature Review</li> <li>1.2. Research Contribution in This Work</li> <li>1.3. Dissertation Organization</li> </ol> | 1<br>3<br>4          |

| CHAPTER II REALIZATION OF MEMRISTOR DEVICES                                                                                         | 7                    |

| <ul><li>2.1. The Memristor Theory Background</li><li>2.2. The Memristor Device Models</li></ul>                                     | 7<br>8               |

| CHAPTER III DYNAMIC BEHAVIOR OF MEMRISTOR DEVICE AND<br>ITS PROPERTIES FOR MEMORY USE                                               | 13                   |

| <ul> <li>3.1. Characterize the Fundamental Memristor Device</li></ul>                                                               | 14<br>29<br>30<br>37 |

| CHAPTER IV BACKGROUND ON THE STATIC RANDOM ACCESS MEMORY                                                                            | 41                   |

| <ul><li>4.1. How Does SRAM Work?</li><li>4.2. Traditional Static Noise Margin</li></ul>                                             | 41<br>45             |

# Page

| CHAPTER V THE DYNAMIC MODEL FOR SRAM CELL                                                                                                                | 48        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 5.1. The MOSFET Transistor Model                                                                                                                         | 48        |

| 5.2. The Dynamic Model for SRAM                                                                                                                          | 52        |

| CHAPTER VI SRAM STABILITY AND ITS MATHEMATICAL EQUIVALENCE                                                                                               | 56        |

| 6.1. Voltage Transfer Curves (VTCs)                                                                                                                      | 57        |

| 6.2. The SRAM Equilibrium Points                                                                                                                         | 58        |

| 6.3. Stability Boundary of an SRAM                                                                                                                       | 58        |

| 6.4. Noise Induced Bifurcation and SRAM Instability Study                                                                                                | 66        |

| CHAPTER VII THE ANALYTICAL SOLUTION FOR STATIC NOISE<br>MARGIN VIA THE CONCEPT OF CRITICAL CURRENT                                                       | 76        |

| 7.1. The Point of Instability for an SRAM                                                                                                                | 77        |

| 7.2. The Region Analysis                                                                                                                                 | 78        |

| 7.3. The Analytical Solution for Critical Current                                                                                                        | 84        |

| 7.4. Static Noise Margin Metric in Current Representation                                                                                                | 92        |

| 7.5. The Analytical Solution for Read/Write Margins in                                                                                                   |           |

| Current Representation                                                                                                                                   | 95        |

| CHAPTER VIII THE ANALYTICAL SOLUTION FOR DYNAMIC<br>NOISE MARGIN VIA THE CONCEPT OF CRITICAL TIME                                                        | 97        |

| <ul><li>8.1. The Definition of Dynamic Noise Margin (DNM)</li><li>8.2. The SRAM Cell Dynamics and Analytical Solution for Dynamic Noise Margin</li></ul> | 98<br>100 |

| CHAPTER IX SUMMARY                                                                                                                                       | 110       |

| 9.1. Summary and Contributions                                                                                                                           | 110       |

|                                                                                                                                                          | 114       |

| 9.3. Acknowledgement                                                                                                                                     | 116       |

| REFERENCES                                                                                                                                               | 117       |

| APPENDIX A THE RELATION OF CRITICAL CURRENT AND CRITIAL VOLTAGE                                                                                          | 128       |

# LIST OF FIGURES

| FIGUR | FIGURE                                                                                                                                                                                                                          |    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

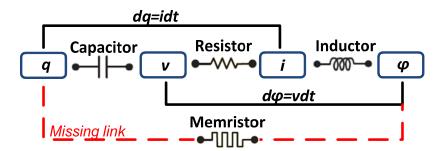

| 2.1   | Four fundamental circuit elements: Resistance $(dv=R \cdot di)$ ,<br>capacitance $(dq=C \cdot dv)$ , inductance $(d\varphi=L \cdot di)$ , and memristance<br>$(d\varphi=M \cdot dq)$ which is the missing link that Chua argued | 7  |

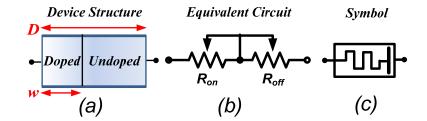

| 2.2   | <ul><li>(a) Memristor device structure; (b) equivalent circuit model and</li><li>(c) symbol for memristor.</li></ul>                                                                                                            | 9  |

| 3.1   | A memristor biased using current source <i>I</i> <sub>in</sub>                                                                                                                                                                  | 15 |

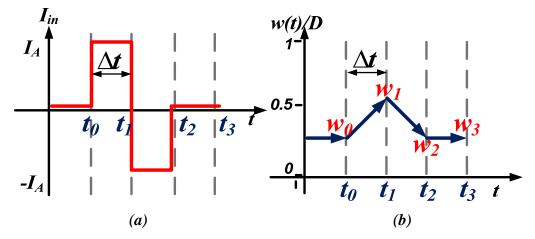

| 3.2   | A square-waveform current source $I_{in}$ has amplitude $I_A$ and $-I_A$ with equal width $\Delta t$ (a) causes the memristor state (b) transition from $w_0$ to $w_3$ .                                                        | 19 |

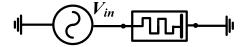

| 3.3   | A memristor biased using voltage source Vin.                                                                                                                                                                                    | 19 |

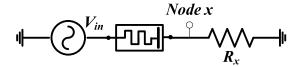

| 3.4   | A voltage divider consisting of a constant resistor $R_x$ in series with a flux-controlled memristor $M(\varphi)$ .                                                                                                             | 25 |

| 3.5   | The window function vs. <i>w/D</i> plot                                                                                                                                                                                         | 29 |

| 3.6   | Memristor output levels. (a) The output low margin is at 0.4 and output high margin is at 0.6 in linear drift model; (b) output levels in nonlinear drift model.                                                                | 30 |

| 3.7   | Write signals (bottom) and corresponding memristor states (top)                                                                                                                                                                 | 31 |

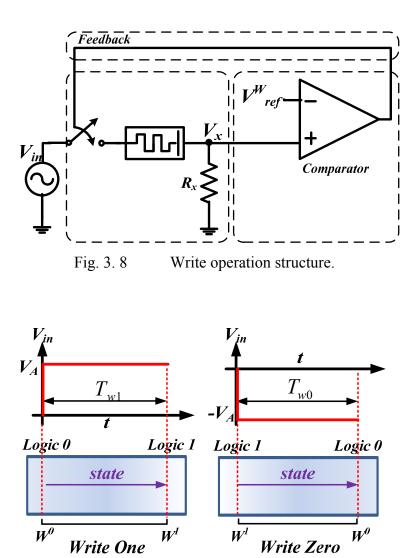

| 3.8   | Write operation structure                                                                                                                                                                                                       | 33 |

| 3.9   | Write pulses (top) and corresponding memristor states (bottom)                                                                                                                                                                  | 33 |

| 3.10  | (a) Operation stages; (b) read pattern.                                                                                                                                                                                         | 36 |

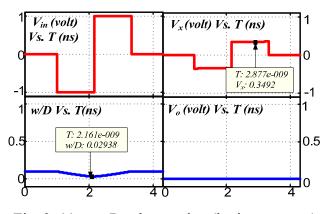

| 3.11  | Read operation (logic zero case).                                                                                                                                                                                               | 39 |

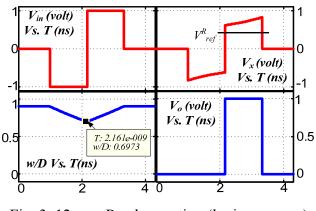

| 3.12  | 2 Read operation (logic one case).                                                                                                                                                                                              | 39 |

| 3.13  | Proposed memristor-based memory array structure                                                                                                                                                                                 | 40 |

# FIGURE

| URI | URE                                                                                                           |    |

|-----|---------------------------------------------------------------------------------------------------------------|----|

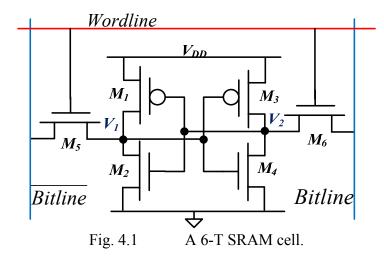

| 4.1 | A 6-T SRAM cell.                                                                                              | 41 |

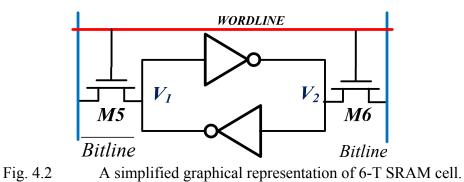

| 4.2 | A simplified graphical representation of 6-T SRAM cell.                                                       | 42 |

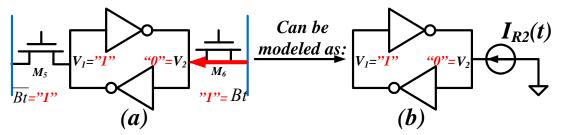

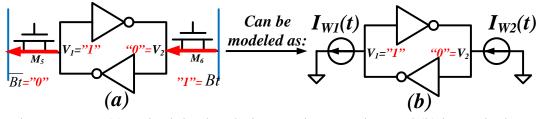

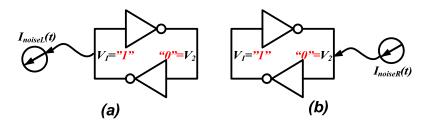

| 4.3 | (a) Noise injection during a read operation, and (b) its equivalent model.                                    | 42 |

| 4.4 | (a) Noise injection during a write operation, and (b) its equivalent model.                                   | 43 |

| 4.5 | An SRAM state flip caused by (a) a current going away; (b) a current injection in standby mode.               | 45 |

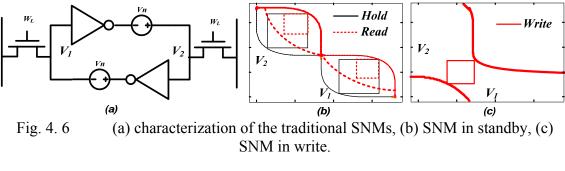

| 4.6 | <ul><li>(a) characterization of the traditional SNMs, (b) SNM in standby,</li><li>(c) SNM in write.</li></ul> | 47 |

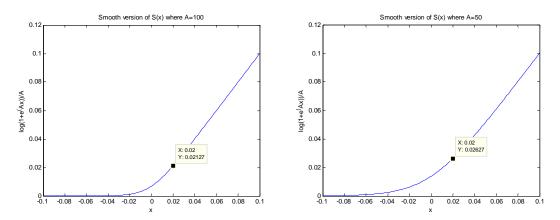

| 5.1 | The plot of smooth version of S(x) with A=100 (Left) and A=50 (Right)                                         | 52 |

| 5.2 | The SRAM cell with internal lumped capacitors drawn                                                           | 53 |

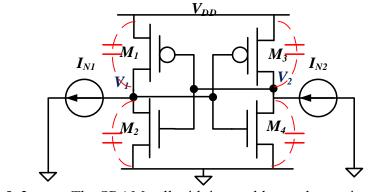

| 5.3 | The SRAM cell with cross-coupled voltage sources inserted                                                     | 54 |

| 6.1 | An example of voltage transfer curves on a 65nm technology SRAM                                               | 57 |

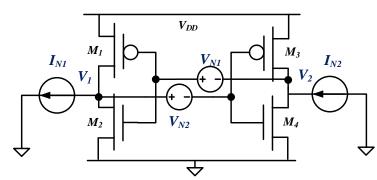

| 6.2 | Example of phase portrait for an SRAM                                                                         | 61 |

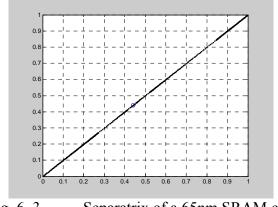

| 6.3 | Separatrix of a 65nm SRAM cell                                                                                | 64 |

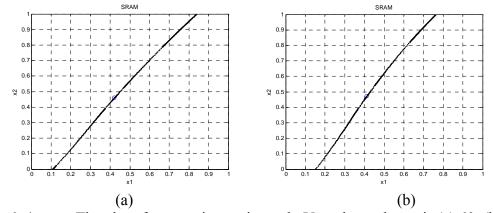

| 6.4 | The plot of separatrix varying only V <sub>th</sub> values when n is (a) 60;<br>(b) 80                        | 65 |

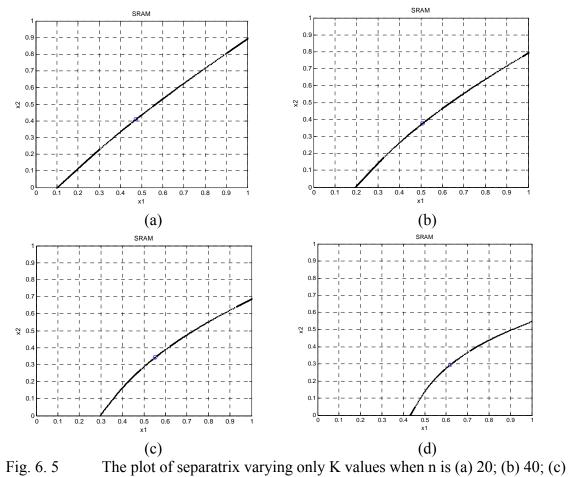

| 6.5 | The plot of separatrix varying only K values when n is (a) 20;<br>(b) 40; (c) 60; (d) 80                      | 66 |

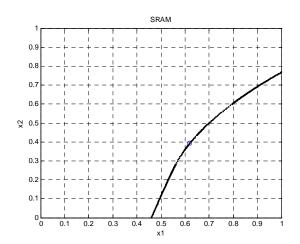

| 6.6 | The plot of separatrix varying $V_{th}$ and $K$ values at n=70                                                | 67 |

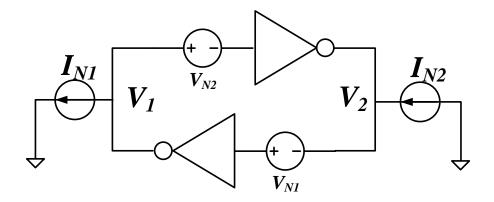

| 6.7 | The SRAM topology with voltage and current noise sources incorporated (simplified view).                      | 69 |

# FIGURE

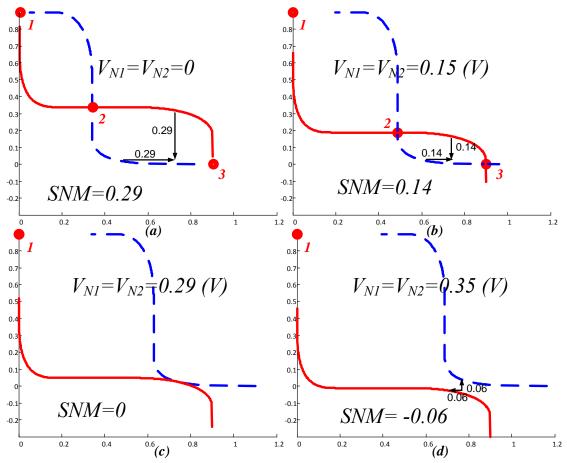

| 6.8 | Illustration of saddle node bifurcation. The voltage transfer curves when (a) $V_N$ is zero; (b) $V_N$ is 0.15 volt; (c) $V_N=0.29$ volt; (c) $V_N=0.35$ volt.                                                                                                                                                                                                                                                                               | 70  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

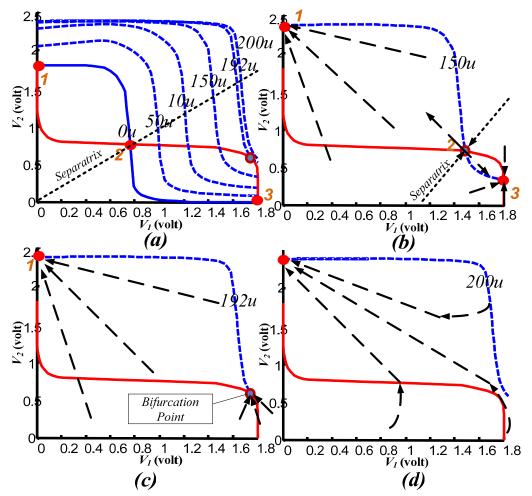

| 6.9 | (a) Illustration of saddle node bifurcation as $I_{n2}$ increases from zero to 200uA, (b) SRAM Butterfly curve when $I_{n2}$ =150uA, (c) SRAM Butterfly curve when $I_{n2}$ =192uA, (d) SRAM Butterfly curve when $I_{n2}$ =200uA.                                                                                                                                                                                                           | 75  |

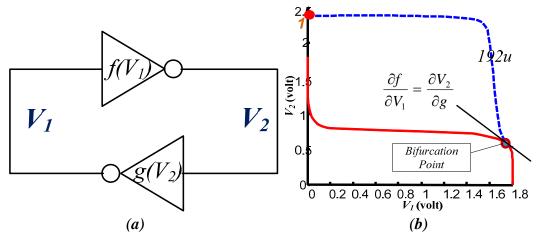

| 7.1 | (a) Symbol for two cross-coupled inverters where functions $f$ and $g$ are for the top and bottom inverter; (b) Phase portrait plot showing two transfer curves tangent at bifurcation have the slope indicated                                                                                                                                                                                                                              | 78  |

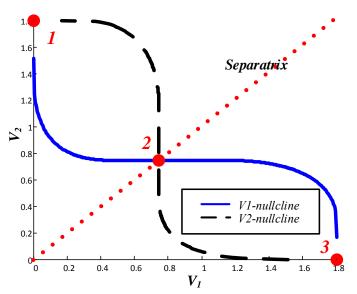

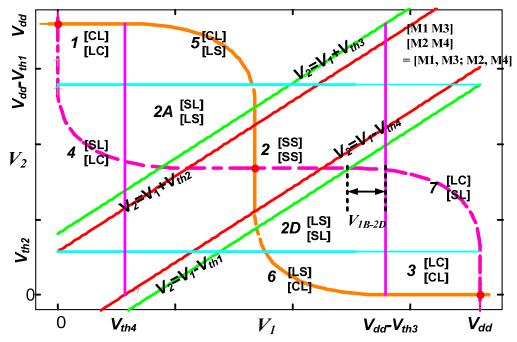

| 7.2 | The nullclines and region formation of an SRAM. The $V_{1B-2D}$ is all<br>the possible range for $V_1$ to have bifurcation in Region 2D.<br>[C= Cutoff; L= Linear; S= Saturation.]                                                                                                                                                                                                                                                           | 80  |

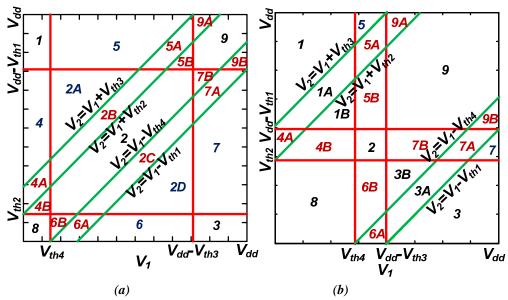

| 7.3 | (a) An example of assigned regions for an SRAM; (b) the assigned regions when $V_{dd}$ is reduced.                                                                                                                                                                                                                                                                                                                                           | 81  |

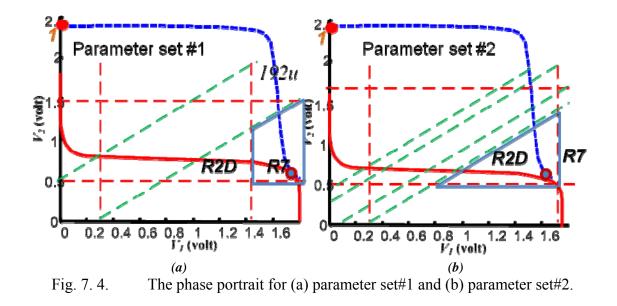

| 7.4 | The phase portrait for (a) parameter set#1 and (b) parameter set#2                                                                                                                                                                                                                                                                                                                                                                           | 82  |

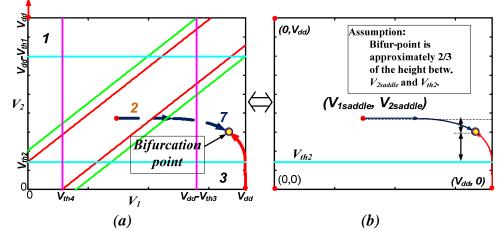

| 7.5 | (a) The plot of SRAM equilibrium points as $I_{n2}$ changes. Increasing<br>the magnitude of $I_{n2}$ will make the saddle (in region 2 when $I_{n2}=0$ )<br>collapsed with the stable node (in region 3 when $I_{n2}=0$ ) and resulting<br>saddle node bifurcation in region 7; (b) Illustration showing that the<br>bifurcation point is approximately 2/3 of the height between $V_{2saddle}$<br>and $V_{th2}$ on the same phase portrait. | 87  |

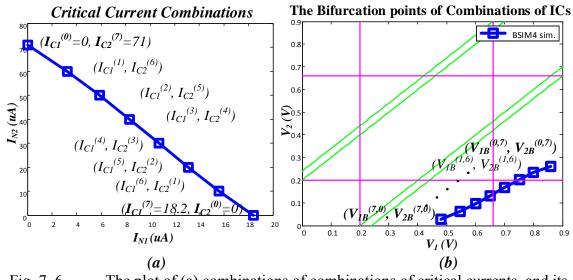

| 7.6 | The plot of (a) combinations of combinations of critical currents, and its (b) corresponding bifurcation point locations.                                                                                                                                                                                                                                                                                                                    | 91  |

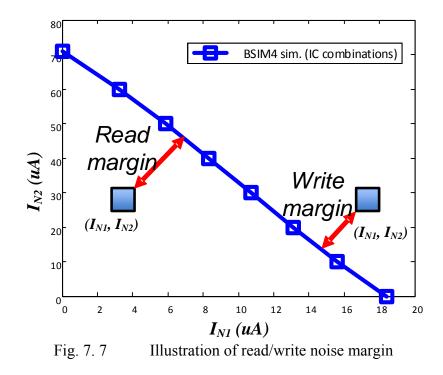

| 7.7 | Illustration of read/write noise margin                                                                                                                                                                                                                                                                                                                                                                                                      | 93  |

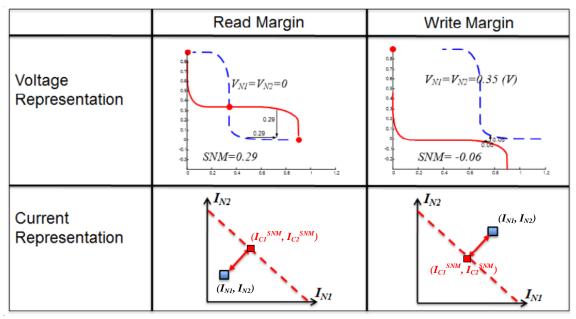

| 7.8 | The summary of static noise margin in voltage representation and in current representation.                                                                                                                                                                                                                                                                                                                                                  | 95  |

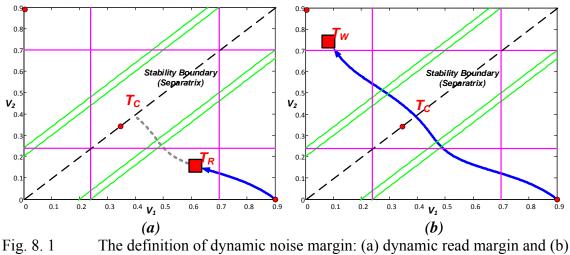

| 8.1 | The definition of dynamic noise margin: (a) dynamic read margin<br>and (b) dynamic write margin.                                                                                                                                                                                                                                                                                                                                             | 98  |

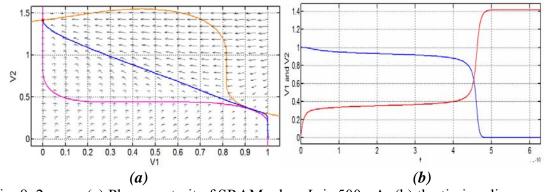

| 8.2 | (a) Phase portrait of SRAM when $I_N$ is 500 $\mu$ A; (b) the timing diagram of this cell.                                                                                                                                                                                                                                                                                                                                                   | 102 |

Page

# FIGURE

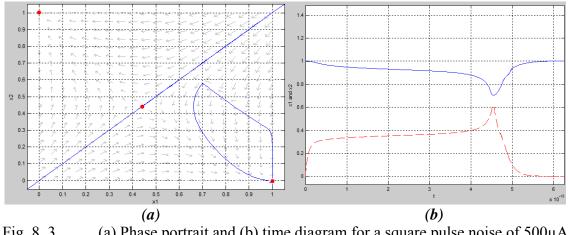

| 8.3 | (a) Phase portrait and (b) time diagram for a square pulse noise of 500µA amplitude and 0.43ns duration                                                                                                                                        | 102 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

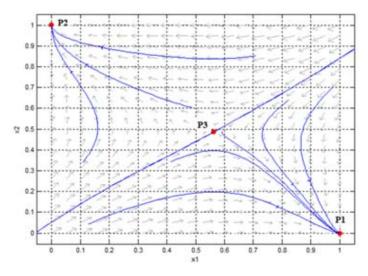

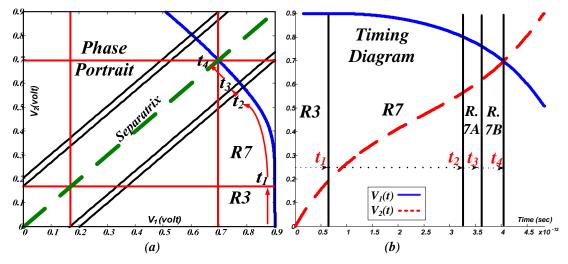

| 8.4 | <ul> <li>(a) The simulated phase portrait of a 65nm SRAM based on the S-H model. It shows a cell state crosses separatrix</li> <li>(45° line through origin) and flips to the other side; (b) the timing diagram of the cell state.</li> </ul> | 103 |

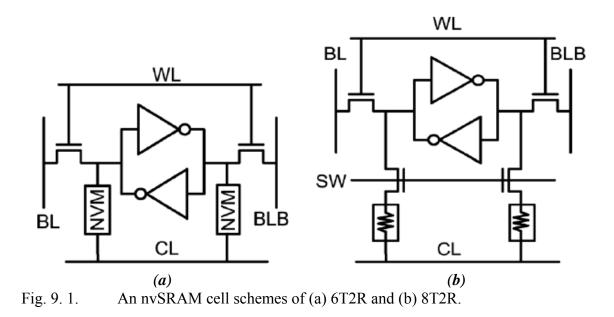

| 9.1 | An nvSRAM cell schemes of (a) 6T2R and (b) 8T2R                                                                                                                                                                                                | 116 |

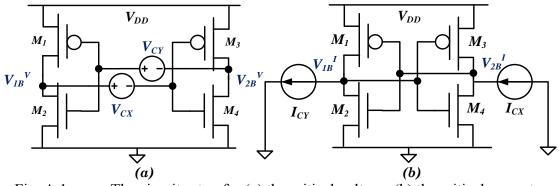

| A.1 | The circuit setup for (a) the critical voltage; (b) the critical current.                                                                                                                                                                      | 128 |

Page

# LIST OF TABLES

| TABLE |                                                                                                             | Page |

|-------|-------------------------------------------------------------------------------------------------------------|------|

| 5.1   | Basic Transistor Drain Current Equations                                                                    | 48   |

| 5.2   | Shichman-Hodges Representation                                                                              | 49   |

| 7.1   | Summary of Region of Bifurcation                                                                            | 83   |

| 7.2   | The BSIM4 Data on a 65nm Technology SRAM (unit is $\mu A$ )                                                 | 91   |

| 9.1   | Summary on the Sensitivity of the System Parameters                                                         | 113  |

| A.1   | The Critical Voltage and Critical Time on Five Random Design<br>Choices Using Numerical Method on L-1 Model | 132  |

| A.2   | The Comparison on the Exact Values vs. $2^{st}$ Order Expansion $(V_{CX}=V_{CY})$                           | 132  |

| A.3   | The Comparison on the Exact Values vs. $1^{st}$ Order Expansion $(V_{CX}=V_{CY})$                           | 132  |

## CHAPTER I

#### INTRODUCTION

#### 1.1. Literature Review

# 1.1.1. The Existing Works on Memristor Cell

Very recently, a new device with pinched hysteresis was demonstrated [1-3], which was recognized as the first real-life realization of the so-called missing fourth circuit element, *memristor*. As a new nanometer device, memristor has drawn a significant interest from the research community [4-11]. Memristor was first theoretically predicted by L. Chua in 1971 [12]. The concept of memristor gained a broader scope in a series of works such as those of L. Chua and S. M. Kang [13-17]. In late 2008, S. Williams, *et al.* unveiled a two-terminal titanium dioxide nanoscale device that exhibited memristive characteristics, thus igniting renewed interest in memristors [18].

Recent research has showcased a number of promising applications of memristor devices. It has been shown by S. Williams and coworkers that solid-state memristors can be used to realize crossbar latches, which could replace transistors in future computers, while taking up a much smaller area [19-22]. There exists a great interest in searching for the next generation of universal memories, which are able to ubiquitously replace traditional DRAM, SRAM. The nonvolatile nature of memristors makes them an attractive candidate for the next-generation memory technology. Memristor memories may have greater data density than hard drives with access times potentially similar to SRAMs. It has been shown that memristor devices can be scaled down to 10nm or below and memristor memories can achieve an integration density of 100Gbits/cm<sup>2</sup>, a few times higher than today's advanced flash memory technologies [23-24]. More broadly, research has been done aiming at employing memristors in programmable logics [25-31], and analog circuit applications [32-38]. In the mean time, researchers have found that LC electronic networks with memristors can model adaptive behavior of unicellular organisms. Results have indicated that electronic circuits with memristors subjected to a train of periodic pulses behave like brain functions, which are able to learn and anticipate. Such a learning circuit may find its valuable applications in a variety of areas, e.g., neural networks and artificial intelligences [39-46].

# 1.1.2. Existing Works on Static Random Access Memory (SRAM)

SRAM provides indispensable on-chip data storage for an extremely wide variety of electronic applications including microprocessor, ASICs, FPGAs, and DSPs. In today's chip designs, the silicon area occupied by SRAM-based caches dominates over other logic devices, which may constitute more than 70% of chip area. In the past decades, aggressive scaling of transistor feature size has been a primary force driving higher SRAM integration density [47] [48]. On the other hand, the supply voltage is scaled down to meet device reliability constraints and to reduce power consumption. However, the stability margin of SRAM has been significantly degraded by such aggressive scaling. As a result, nanometer SRAM designs are getting increasingly susceptible to various noise problems and there is a growing concern on read-ability and

write-ability. Increasing process variation also has a dramatic impact on the stability of highly scaled SRAM designs.

The traditional static noise margin (SNM) analysis is widely used to characterize the robustness of an SRAM cell. It measure the largest differential voltage noise that can be tolerated at the two storage nodes [49] [50]. More specifically, the SNM is determined as the side of largest square that can be inscribed between the mirrored DC voltage transfer curves (VTCs) of the cross-coupled inverters. However, such a measure is intrinsically unable to characterize the dynamic process that leads to state flips, which is critical for understanding the complete stability picture.

In 2006, the work done by Zhang [51] investigates the SRAM dynamics stability noise margin in linear gate model. Compare to this work, the SRAM dynamic noise margin is derived in Shichman Hodges model (Level-1), which is more complicated model and thus provide more design insights.

#### 1.2. Research Contribution in This Work

# 1.2.1. Contribution on the Memristor-Based Memory

In this work, by extending the preliminary work in [52], we systematically develop a rather complete set of properties and design equations for guiding the development of memristor based memories. We show important dynamical behaviors of memristor devices and how these characteristics will influence all aspects of analysis and design of memristor memories. Our analyses are much more general than what is presented in [52] and no longer assume a zero on-resistance value to simplify the derived

closed-form equations. We refine the derived equations in more details including, but not limited to, the above relaxed condition, and conclude them by useful properties. Utilizing these memristor properties as design guidance, we then investigate the design of memory read/write schemes and peripheral circuits. Important data integrity and parameter mismatch issues are discussed in depth. Finally, we use extensive simulations to verify the derived properties and demonstrate their usage in memory circuit design.

#### 1.2.2. Contribution on the Static Random Access Memory

In this work, we extend the traditional static noise margin concept to a broader view. Stability will be defined by examining both the magnitude and duration of the injected current noise required to flip the SRAM state. As such, our new stability margin concepts fundamentally capture the temporal aspects of the state flip and provide immediate design insights for enhancing dynamic stability. The concepts of critical current and critical time, based on theoretically rigorous stability analysis of the dynamic behaviors of SRAM cells, provide physical characterizations of SRAM stability. Lastly, we explore an analytical approach to the evaluation of dynamic stability analysis for SRAMs.

## 1.3. Dissertation Organization

In this dissertation, beginning from Chapter II, the fundamental theory of memristor and the basic concept will be introduced. Most of the research works in the memristor area use the models proposed by HP research group. The proposed HP memristor models can be categorized in linear and nonlinear drift model. Some of the commonly seen memristor models will be covered.

Chapter III introduces the dynamic behavior of memristor device will influence all aspect of design of memristor memories. The design flow has three basic steps: (1) Systematically develop a rather complete set of properties and design equations for guiding the development of memristor based memories, and show important dynamical behaviors of memristor devices and how these characteristics will influence all aspects of analysis and design of memristor memories. (2) Define logic one/zero region on a memristor cell. (3) Investigate the design of memory read/write schemes.

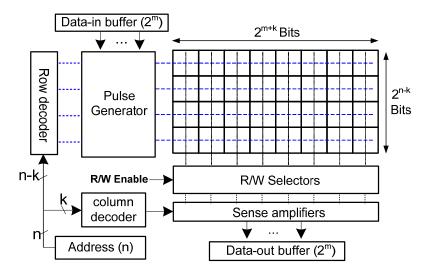

Beginning with Chapter IV, we first start with the background on SRAM operations and stability issues. Next in Chapter V, modified nodal analysis will be discussed, and we introduce the SRAM circuit and the corresponding nonlinear differential equations based on Shichman-Hodges model.

In Chapter VI, we discuss the bifurcation study to demonstrate the SRAM stability issues. We show that three equilibria are located in three different regions. Then we show the equilibria are two stable equilibria and a saddle (or meta-stable point). From there, we show that the saddle-node bifurcation will happen at a certain injected current magnitude called critical current or  $I_C$ . From the phase portrait analysis, when injected current amplitude reaches  $I_C$ , we observed that two equilibria collide and result in a saddle-node bifurcation. The collision location is called the bifurcation point. When this happens, the two colliding equilibria disappear, and only the other remaining stable

equilibrium point will survive. The cell state will traverse to that equilibrium point and causes state flip.

Next, in Chapter VII, we introduce region analysis to derive the stability margin analytically for an SRAM. We partition the state space into regions. The equilibrium point locations in terms of a noise injection and system parameters are derived. Furthermore, focus on the region of bifurcation; we derive the bifurcation point and  $I_C$ analytically. However, the outcome of analytical solution on bifurcation point and  $I_C$  is very complicate. For that, we observe on the numerical property and propose a new method to derive analytical solution for  $I_C$  and that can greatly simplifies the equation but keep the accuracy.

In Chapter VIII, we further derive the analytical formula for critical time ( $T_c$ ). We show that a perturbed transient state trajectory will pass the stability boundary (called separatrix) resulting the state flip when the injected current has higher magnitude than  $I_c$ . For a perfectly symmetric SRAM, the stability boundary is a 45 degree line that passes through the origin. However, the injected current greater than  $I_c$  does not necessarily implies that the cell will flip its state [51] [53]. The current must be greater than  $I_c$  for a certain period of time (defined as critical time or  $T_c$ ) to cross the separatrix. Once the state of the cell crosses the separatrix, the state will flip even the noise disappears. However, it is still not clear how the SRAM parameters physically influenced the phenomena observed from phase portrait analysis. Accordingly, we resort to analytical form solutions to find the relations. Lastly, in Chapter IX, we conclude the  $I_c$  and  $T_c$  dependency on technology parameters for design insights.

#### CHAPTER II

### REALIZATION OF MEMRISTOR DEVICE

## 2.1 The Memristor Theory Background

The fundamental basic circuit elements are resistor, capacitor, and inductor. Resistor relates voltage and current (dv=R.di), capacitor relates charge and voltage (dq=C.dv), and inductor relates flux and current ( $d\varphi=L.di$ ), respectively. The relation between flux and charge is evidently missing. As shown in Fig. 2.1, Chua argued that there is a missing link between flux and charge, which he called memristance *M*. [12]

Fig. 2. 1 Four fundamental circuit elements: Resistance  $(dv=R\cdot di)$ , capacitance  $(dq=C\cdot dv)$ , inductance  $(d\varphi=L\cdot di)$ , and memristance  $(d\varphi=M\cdot dq)$  which is the missing link that Chua argued.

By definition, a linear (constant) memristor acts like resistance. However, if  $\varphi$ -q relation is non-linear, the device behavior is more complex. The memristor characteristics, also referred to as memristance, can be described as:

$$M = d\varphi/dq \,. \tag{2.1}$$

Similarly, the inverse of the q- $\varphi$  relation is called memductance:

$$W = dq/d\varphi \,. \tag{2.2}$$

From (2.1) and (2.2), it can be also seen:

$$v = M \cdot i \,, \tag{2.3}$$

$$i = W \cdot v \,. \tag{2.4}$$

The memristance M in (2.3) is equal to voltage over current which is also known as the resistance in the linear case. Therefore, memristance has the same unit (*Ohm*) as resistance. Similarly in (2.4), the memductance has the unit of conductance. The inverse of memductance would be memristance, so

$$M = 1/W. \tag{2.5}$$

## 2.2 The Memristor Device Models

Hewlett Packard demonstrated the first fabricated physical structure of a memristor device in 2008 also known as *Titanium dioxide memristor*. The HP researcher, R.S. Williams, claims that the device is an electrically switchable semiconductor thin film sandwiched between two metal contacts [18]. The semiconductor thin film has a certain length *D*, and consists of a doped and un-doped region as shown in Fig. 2.2(a). The internal state variable *w* represents the length of the doped region. The doped region has low resistance while that of the un-doped region is much higher. As an external voltage bias v(t) is applied across the device, the length *w* will change due to charged dopant drifting. Hence, the device's total resistivity changes. Fig. 2.2(b) shows its equivalent circuit model, and Fig. 2.2(c) shows the memristor symbol used in a circuit schematic. If the doped region extends to the full length *D*, that is w/D=1.0, the total resistivity of the device would be dominated by the low resistivity

region, with a value measured to be  $R_{on}$ . Likewise, when the un-doped region extends to the full length D, i.e. w/D=0, the total resistance is denoted as  $R_{off}$ . Thus, the mathematical model for memristive device resistance can be described as [18]:

$$R(w) = (R_{on} \cdot w/D + R_{off} \cdot (1 - w/D)), \qquad (2.6)$$

or it can be written as:

$$R(w) = R_{off} - \left(R_{off} - R_{on}\right) \cdot w/D.$$

(2.7)

Because of physical constraint  $0 \le w \le D$ , *Property 1* is concluded.

**Property 1**:  $R_{on}$  corresponds to memristor state w=D.  $R_{off}$  corresponds to memristor state w=0. The device resistance is bounded between:  $R_{on} \leq R(w) \leq R_{off}$

Fig. 2. 2 (a) Memristor device structure; (b) equivalent circuit model and (c) symbol for memristor.

Fig. 2.2(c) shows the memristor symbol used in a circuit schematic. The orientation of the symbol follows the equivalent circuit in Fig. 2.2(b), where  $R_{on}$  is at the left and  $R_{off}$  is at the right. The polarity matters in memristor circuits. If a bias condition excites the memristance to increase, the reverse connection of memristor would decrease the memristance, which is also equivalent to reverse the polarity of the biasing source. Using this resistive viewpoint, we have

$$v = R(w) \cdot i \,. \tag{2.8}$$

Referring to Fig. 2.1, equation (2.8) presents the relation of voltage and current. According to the recent research results, there are two types of memristor models: linear drift model, and nonlinear drift model.

### 2.2.1 Linear Drift Model

The linear dopant drift model assumes a uniform electric field across the device. The net electric field induced a current flow through the memristor device is found to be linearly proportional to the drift-diffusion velocity. Since the drift-diffusion velocity corresponds to the speed of doped region (dw/dt), the following equation established [18]:

$$\frac{dw}{dt} = \mu_v \cdot \frac{R_{on}}{D} \cdot i \tag{2.9}$$

where  $\mu_v$  is the average ion mobility.

### 2.2.2 Nonlinear Drift Model

According to the actual memristor device manufactured in HP's lab, the small voltage can yield enormous electric field in nano-scale devices, which produce significant highly nonlinear ionic transport. These nonlinearities appear to slow down the drift velocity at the thin film edges, where the speed of the state transition around the boundary gradually decreases to zero. This nonlinear dopant-drifting phenomenon is so called the *boundary effect* [6] [54-56]. The nonlinear effect and its modeling are still not

fully understood and an ongoing research which has been pointed out by Kavehei [56]. Nevertheless, one approach to model the boundary effect is by applying *window function* f(w) to the drift velocity equation. That is

$$dw/dt = \mu_v \cdot R_{on}/D \cdot i \cdot f(w/D). \qquad (2.10)$$

A widely proposed window function introduced by [6] and [54] is the following:

$$f(x) = 1 - (2 \cdot x - 1)^{2 \cdot P}$$

(2.11)

where P is the *control parameter* that needs to be matched to the manufactured memristor data. The control parameter can only be positive integers.

However, the theoretical models can go much deeper than just window functions. In late 2008, the research group at Hewlett-Packard further announces the memristive switch mechanism of a flux-controlled memristor can be described as follows [57]:

$$I = w^{n}\beta \cdot \sinh(\alpha \cdot V) + \chi \cdot (\exp(\gamma \cdot V)) - 1)$$

(2.12)

where *w* is memristor state, *V* is the applied voltage to memristor, *I* is the current through memristor, and all others are fitting parameters. When the memristor is around  $R_{on}$ , Yang et al. (2008) referred to as ON state, the following approximation valid [57]:

$$I \approx \beta \cdot \sinh(\alpha \cdot V) \,. \tag{2.13}$$

A more detail descriptions on the dynamics of internal ionic transport involved quantum mechanics. Due to that reason, the suggested expression for the drift velocity becomes very non-linear at strong applied fields: [57]

$$\frac{dw}{dt} = f_{on} \sinh(\frac{i}{i_{on}}) \cdot \exp\left[-\exp\left(\left(\frac{w-a_{on}}{w_c}\right) - \frac{|i|}{b}\right) - \frac{w}{w_c}\right]$$

(2.14)

and

$$\frac{dw}{dt} = f_{off} \sinh(\frac{i}{i_{off}}) \cdot \exp\left[-\exp\left(\left(\frac{w - a_{off}}{w_c}\right) - \frac{|i|}{b}\right) - \frac{w}{w_c}\right]$$

(2.15)

where  $i_{on}$ ,  $i_{off}$  are the minimum on and off magnitude,  $w_c$ , b and  $a_{off}$  are constants acquired by parameter fitting, and *i* is the applied current through memristor. Equation (2.14) is applicable when *i*<0, and (2.15) is applicable otherwise.

Based on the provided memristor model from HP, the minimum current for memristor state switching is not clear by the given simple linear drift formula. As we can see from the more completed memristor model, if the injected current i is less than the on or off magnitude (*i*on or *i*off), the value out of hyperbolic sine would be very small, thus the positive or negative drifting velocity would also be small. Therefore, the on and off currents work as a critical current for the memristor state to move, where the linear drift model does not indicate such on or off current phenomenon. However, the more completed model is more complicated than window function and difficult to work with. Nowadays scientists are still looking for other reasonable models.

#### CHAPTER III

# DYNAMIC BEHAVIOR OF MEMRISTOR DEVICE AND ITS PROPERTIES FOR MEMORY USE \*

In this Chapter, the characterization on the fundamental memristor device are heavily emphasized. From the basic memristor device model, systematically develop a rather complete set of properties and design equations for guiding the development of memristor based memories. Next, it's assigning memristor area into logic regions. A single memristor cell is to partition to disjointed regions: Logic one and logic zero regions. A safety margin is in between the regions to account for possible noise injection. Finally, a brief demonstration on memristor-based memory is provided. The derived memristor properties will be utilized to illustrate the memristor-based memory read/write operations. The derived designed formulae shown in (3.34) and (3.35) indicate the amount of minimum required time to switch the logic state. The write signal must be sustained longer than the minimum time for a successful write. Similar to devices like SRAM, the SRAM state to flip, the write signal must sustain long than the critical time". For the SRAM state to flip, the write signal must sustain long than the critical time for a successful write.

<sup>\*©[2012]</sup> IEEE. Reprinted, with permission, from "Dynamical Properties and Design Analysis for Nonvolatile Memristor Memories," by Y. Ho, G. M. Huang, P. Li., *IEEE Trans. Circuits and Systems-I: Regular Paper*, vol. 58, no. 4, April 2011.

Moreover, the proposed read/write scheme used the derived properties as guidance. The design analysis is specifically targeting key electrical memristor device characteristics relevant to, but not limited to, memory operations.

# 3.1. Characterize The Fundamental Memristor Device

The purpose of characterize the memristor device is to transform the basic memristor device models and derive a set of closed-form design equations. The results succinctly capture the memristor behaviors in a way relevant to memory operations and provide clear design insights by re-derive the model equations.

# 3.1.1. Characteristics in Linear Drift Model

Memristors can be *charge-controlled* or *flux-controlled* depending on the biasing condition [12]. More specifically, when a memristor is connected to a current source, the current source will inject charges through the memristor cell. It is convenient to treat such a memristor as charge controlled because the state of the memristor changes according to the amount of charge injection, and the state causes memristance to change. On the other hand, when a voltage source is added across a memristor, it is natural to consider the memristor as flux controlled. In this case, the state of the memristor changes according to the amount of flux injection, and the state causes memristance to change.

## 3.1.1.1. Charge-Controlled Memristance

For a charge-controlled memristance, the memristor state controlled by the charge through the cell, and the state of memristor determines memristance. Figure 3.1 shows a memristor biased using a current source  $I_{in}$ , and  $I_{in}$  can be any waveform. Integrating (2.9) yields the instantaneous w(t):

$$w(t) = w_0 + \mu_v \cdot \frac{R_{on}}{D} \cdot q \tag{3.1}$$

where  $w_0$  is the initial state for state variable w. The state of memristor moves from  $w_0$  according to the charge going to the memristor cell. If there is a positive charge injection, the state will move to a higher position,  $w > w_0$ . If negative charge is injected, memristor state will move to lower position,  $w < w_0$ . However, memristor state has a physical constraint: the state is bounded in between zero and total length D, namely  $0 \le w \le D$ . Due to the physical constraint, we show that the internal memristor state corresponds to the following effective q range:

$$-w_0 D/(\mu_v R_{on}) \le q \le (D - w_0) D/(\mu_v R_{on}).$$

(3.2)

Property 2 describes the actual behavior of memristor state.

Fig. 3.1 A memristor biased using current source *I*<sub>in</sub>.

**Property 2**: The state (length of the doped region) is charge-controlled and can be described as follows:

$$\frac{w}{D} = \begin{cases} 1 & q > Q_{UP} \\ w_0 / D + \mu_v \cdot \frac{R_{on}}{D^2} \cdot q, & Q_{LOW} < q < Q_{UP} \\ 0 & q < Q_{LOW} \end{cases}$$

(3.3)

$Q_{UP} = (D - w_0)D/(\mu_v R_{on})$  and  $Q_{LOW} = -w_0D/(\mu_v R_{on})$ where  $w_0$  is the initial state, D is the memristor length,  $\mu_v$  is the average ion mobility and q is injected charges.  $Q_{UP}$  is the upper limit of effective charge injection, and  $Q_{LOW}$  is the lower limit of effective charge injection.

Mathematically, when actual charge injection is more than the upper limit of effective charge injection, the state will not go further after it reaches w=D. Likewise, the lowest state is at zero even if charge injection is lower than the bottom limit of effective charge injection.

As (3.3) indicates, the memristance works as a charge driven resistance. Equation (3.3) together with (2.7), implies:

$$R(w) = M(q). \tag{3.4}$$

The resistance becomes charge dependent; hence, the charge-controlled memristace is concluded in *Property 3*.

**Property 3:** Charge-controlled memristance can be described as follows:  $M(q) = R_{off} - (R_{off} - R_{on}) \cdot \left(\frac{w_0}{D} + \frac{\mu_v R_{on}}{D^2} \cdot q\right).$ (3.5)

*The equation is valid in the range:*  $Q_{LOW} \leq q \leq Q_{UP}$ .

As a special case where  $w_0=0$  and  $R_{on}$  is small enough such that  $(R_{off}-R_{on})\approx R_{off}$ , charge-controlled memristance can be simplified to:

$$M(q) = R_{off} \cdot \left(1 - \frac{\mu_v R_{on}}{D^2} \cdot q(t)\right).$$

(3.6)

Suppose a memristor  $M_a$  is biased using current sources  $I_a$  and a memristor  $M_b$  is biased using  $I_b$ , in which  $I_a$  and  $I_b$  have different waveform patterns. Source  $I_a$  is a sinusoidal waveform and  $I_b$  has a square-wave pattern. Based on (3.3) from *Property 2*, change of the state is controlled by the charges through the memristor. Since the charge is integral of the current with respect to time, the state change caused by  $I_a$  would be the same to that by  $I_b$  if both have the same integrated charges. This result is summarized in *Property* 4.

**Property 4**: The state change of a memristor biased using a current source is only a function of the integrated bias charge regardless of the waveform shape of the bias current.

One unique property of the memristor has been observed is that the internal state w always comes back to the initial place if the integral of current is zero over a time period. Figure 3.2 is a brief demonstration. The current source  $I_{in}$  has positive and negative pulse with equal amplitude and width. Starting from initial state  $w_0$  at  $t_0$ , the state rises due to the positive pulse from  $t_0$  to  $t_1$ , letting the state rest at  $w_1$ . Based on (3.3), the value for  $w_1$  is:

$$w_1/D = w_0/D + \mu_v \cdot \frac{R_{on}}{D^2} \cdot (I_A \cdot \Delta t)$$

(3.7)

where  $(I_A \Delta t)$  is the charge injection by the positive pulse. From  $t_1$  to  $t_2$ , the negative pulse follows, which moves the state from  $w_1$  to  $w_2$ , and  $w_2$  can be expressed in terms of  $w_1$  as:

$$w_2/D = w_1/D + \mu_v \cdot \frac{R_{on}}{D^2} \cdot (-I_A \cdot \Delta t)$$

(3.8)

where  $(-I_A \Delta t)$  is the charge injected by the negative pulse. The state  $w_2$  can be rewritten in terms of  $w_0$  by substituting (3.7) to (3.8), which gives  $w_2=w_0$ . This indicates that the final state  $w_2$  will be the same as initial state  $w_0$ . This type of input waveforms in Fig. 3.2(a) are referred to as *zero net-charge injection* inputs because the integral of the current over the corresponding time period is zero. Zero net-charge injection waveforms do not have to be square waveform; it can be sinusoidal or any other waveforms as long as the integral over a period is zero. Zero net-charge inputs can bring the state back to original level regardless the initial state. However, the state comes back only when the charge exerts onto memristor is within the effective q range described in (3.2). Otherwise, the state will not come back to the original level. This concludes *Property 5*. As will be demonstrated in the following sections, this property plays an essential role in design of memristor memories.

**Property 5**: If charge injection exerted onto a memristor is a zero net-charge injection, memristor state will move back to its original position if the exerted charge is within the effective q range:  $Q_{LOW} \leq q \leq Q_{UP}$ .

Fig. 3. 2 A square-waveform current source  $I_{in}$  has amplitude  $I_A$  and  $-I_A$  with equal width  $\Delta t$  (a) causes the memristor state (b) transition from  $w_0$  to  $w_3$ .

## 3.1.1.2. Voltage-Controlled Memristance

Fig. 3. 3 A memristor biased using voltage source V<sub>in</sub>.

For a flux-controlled memristance, the memristor state is controlled by the flux across the cell, and the state of the memristor drives memristance. When a voltage source biases a memristor, the memristor can be considered as flux-controlled. Fig. 3.3 shows a memristor biased using a voltage source  $V_{in}$ , and  $V_{in}$  can be any waveform. Denote  $\beta$  the off/on ratio ( $R_{off}=R_{on}\beta$ ). Equation (2.9) can be rewritten as:

$$\frac{dw}{dt} = \frac{\mu_v}{D\beta - w \cdot (\beta - 1)} \cdot v.$$

(3.9)

After certain manipulations using differential calculus, we get

$$w^{2} - \frac{2 \cdot D\beta}{(\beta - 1)} w + \frac{2}{(\beta - 1)} \cdot (\mu_{v} \cdot \varphi + C) = 0$$

(3.10)

where

$$C = D\beta \cdot w_0 - (\beta - 1)/2 \cdot w_0^2.$$

(3.11)

Since the integration of the voltage is the flux, denoted by  $\varphi$ , directly relates *w* with flux  $\varphi$  in a nonlinear fashion. Solving the quadratic equation of (3.10) and picking up the physically meaningful root leads to:

$$w(t) = \frac{D\beta}{(\beta - 1)} \cdot \left[ 1 - \sqrt{\left(1 - \frac{\beta - 1}{D\beta} w_0\right)^2 - \frac{2\mu_v(\beta - 1)}{(D\beta)^2} \cdot \varphi(t)} \right]$$

(3. 12)

where  $w(t=0)=w_0$  is the initial condition. Equation (3.12) shows an explicit dependency of the internal variable w(t) on the applied flux. Note that this formula clearly indicates that w(t) is a function of the *flux* applied; it is indirectly dependent on the voltage across the memristor. The input voltage waveform with the same flux leads to the same memristor state.

Due to the finite length *D* of the thin film, the internal memristor state is constrained as:  $0 \le w(t)/D \le I$ , which corresponds to the following effective flux range:

$$-\frac{\Phi_{D}}{R_{off}^{2}}\left(R_{off}^{2}-R(w_{0})^{2}\right) \le \varphi(t) \le \frac{\Phi_{D}}{R_{off}^{2}}\left(R(w_{0})^{2}-R_{on}^{2}\right).$$

(3.13)

As a result, the more complete set of the state equations are shown in *Property 6*.

**Property 6:** The state (length of the doped region) is flux-controlled and can be described as follows:

$$\frac{w}{D} = \begin{cases} 1 & \varphi \ge \Phi_{UP} \\ \frac{\beta}{\beta - 1} \left[ 1 - \sqrt{\left(\frac{R(w_0)}{R_{off}}\right)^2 - \frac{\varphi}{\Phi_D}} \right], \Phi_{LOW} < \varphi < \Phi_{UP} \\ 0 & \varphi \le \Phi_{LOW} \end{cases}$$

(3.14)

$$\Phi_{D} \left( p_{(-1)}^2 - p_{(-1)}^2 \right) = \operatorname{and}_{D} \left( p_{(-1)}^2 - p_{(-1)}^2 \right)$$

$$\Phi_{UP} = \frac{\Phi_D}{R_{off}^2} \left( R(w_0)^2 - R_{on}^2 \right) \quad \text{and} \quad \Phi_{LOW} = -\frac{\Phi_D}{R_{off}^2} \left( R_{off}^2 - R(w_0)^2 \right)$$

where  $\beta$  denoted the off/on ratio ( $R_{off}=R_{on} \beta$ ),  $w_0$  is the initial state, D is the memristor length,  $\mu_v$  is the average ion mobility and  $\varphi$  is injected flux.  $\Phi_{UP}$  is the upper limit of effective flux injection;  $\Phi_{LOW}$  is the lower limit of effective flux injection, and

$$\Phi_D = \frac{(\beta D)^2}{2\mu_v(\beta - 1)}$$

Because of the memristor physical constraint,  $0 \le w(t)/D \le 1$ , memristor state w would not be more than D when the applied flux across memristor is over the upper bound, and it would not be lower than zero when the applied flux is smaller than the lower bound. Thus, the derived equation (3.14) works only when the applied flux is within the effective range. In other words, for a particular memristor, if the applied flux is larger than the upper limit of the effective range,  $\varphi$  would be the upper limit of effective injection. Likewise,  $\varphi$  would be the lower limit of effective injection if the applied flux is lower than the effective range.

As *Property 6* indicates, the memristance works as a flux driven resistance, thus it implies:

$$R(w) = M(\varphi) . \tag{3.15}$$

By substituting (3.14) into (2.7), the resistance becomes charge dependent, hence, the

charge-controlled memristace is concluded in *Property* 7. The corollary 7.1 also follows.

*Property 7: Flux-controlled memristance can be described as follows:*

$$M(\varphi) = R_{off} \sqrt{\left(\frac{R(w_0)}{R_{off}}\right)^2 - \frac{\varphi}{\Phi_D}}.$$

(3.16)

*The equation is valid in the flux range:*  $\Phi_{LOW} \leq \varphi \leq \Phi_{UP}$ *.*

*Corollary* 7.1:  $R_{on} \leq M(\varphi) \leq R_{off}$  as seen from (3.16) and Property 1.

When a single voltage source biases a memristor cell, it generates flux across the memristor and also pushes charges through the memristor. The state of the memristor supposes to move regards to the charge through memristor based on *Property 2*. The applied flux to the memristor cell would also change the state based on *Property 6*. Thus, the memristance change by charge or by flux should be identical, which implies:

$$M(q) = M(\varphi). \tag{3.17}$$

Therefore, the q- $\varphi$  relationship can be expressed as:

$$q(\varphi) = \frac{2\Phi_D}{R_{off}} \left[ \left( \frac{R(w_0)}{R_{off}} \right) - \sqrt{\left( \frac{R(w_0)}{R_{off}} \right)^2 - \frac{\varphi}{\Phi_D}} \right].$$

(3.18)

According to the definition of memductance, the memductance is derived to be:

$$W(\varphi) = \frac{1}{R_{off}} \cdot \sqrt{\left(\frac{R(w_0)}{R_{off}}\right)^2 - \frac{\varphi}{\Phi_D}}.$$

(3.19)

Based on (2.5), the inverse of memductance gives memristance. Since memductance has flux as the control variable, the inverse of that gives flux-controlled memristance, which is the same as (3.16).

Compared to the properties on charge-controlled case, similar properties can be developed. Suppose a memristor  $M_a$  is biased using voltage sources  $V_a$  and a memristor  $M_b$  is biased using  $V_b$ , in which  $V_a$  and  $V_b$  have different waveform patterns. The change to the memristor states would be the same regardless their waveform shapes as long as the flux injections (integration of their voltages) remain the same, as summarized in *Property 8*.

**Property 8**: The state change of a memristor biased using a voltage source is only a function of the integrated bias voltage regardless of the waveform shape of the bias voltage.

In addition, a *zero net-flux injection* input, one whose integrated voltage over the time is zero, pushes state of the memristor back to the initial level provided that the flux exerted onto the memristor is within the effective  $\varphi$  range described in *Property 7*. *Property 9* summarizes this phenomenon.

**Property 9**: If the flux injection exerted onto a memristor is a zero net-flux injection, memristor state will move back to its original position if the exerted charge is within the effective  $\varphi$  range:  $\Phi_{LOW} \le \varphi \le \Phi_{UP}$ .

**Property 10**: The memristor state is initially at  $w_0$ . Suppose the state of memristor is desired to move to a feasible state w by a square-wave voltage pulse that has amplitude  $V_A$  and width  $T_w$ , the required width  $T_w$  is:

$$T_{w} = \frac{\Phi_{D}}{V_{A}R_{off}^{2}} \Big[ (R(w_{0}))^{2} - (R(w))^{2} \Big].$$

(3.20)

Property 10 addresses how much time is needed to move memristor state from an initial  $w_0$  to any state w. Assume memristor state be initially at state  $w_0$ . Based on Property 6, suppose the state of memristor is desired to move to an arbitrary state w, the

applied flux needed across the memristor to do this job is:

$$\varphi(t) = \frac{\Phi_D}{R_{off}^2} \Big[ (R(w_0))^2 - (R(w(t)))^2 \Big].$$

(3.21)

Let the applied voltage be a square-wave pulse with amplitude  $V_A$  and width  $T_w$ , the flux across the memristor is described as follows:

$$\varphi(t) = \int_{0}^{t} v(\tau) \partial \tau = \begin{cases} V_A \cdot t & \text{if } t \leq T_w \\ V_A \cdot T_w & \text{if } t > T_w \end{cases}$$

(3.22)

When time is in between zero and  $T_w$ , the voltage magnitude is  $V_A$  and flux is accumulating in this time range. When time goes beyond  $T_w$ , the voltage magnitude is zero, so no more flux increment beyond time  $T_w$ . Hence, the total flux injection for a square-wave pulse is the amplitude times the width, which is  $V_A T_w$  in this case. The total flux injection determines the change of memristor state. The required width needed to move memristor state from  $w_0$  to w is concluded in *Property 10*. As a special case, the required time needed to move memristor state from w=0 to w=D is the same as to move from w=D to w=0. This leads to *Corollary 10.1*.

**Corollary 10.1**: Suppose a voltage square-wave pulse has amplitude  $V_A$  and width  $T_w$  is applied to a memristor. The duration needed for memristor state to move from w=0 to w=D is the same as what is required to move the state from w=D to w=0, and the required duration  $T_w$  is:

$$T_{w} = \left| \frac{\Phi_{D}}{V_{A} R_{off}^{2}} \cdot \left( R_{off}^{2} - R_{on}^{2} \right) \right|.$$

(3.23)

Fig. 3.4 A voltage divider consisting of a constant resistor  $R_x$  in series with a flux-controlled memristor  $M(\varphi)$ .

Furthermore, consider a series connection of a constant resistor  $R_x$  and a memristor, biased using a voltage source, as shown in Fig. 3.4. Using the notion of voltage division, which will prove shortly, we show the voltage response at node x in *Property 11*.

**Property 11**: In the voltage divider shown in Fig. 3.4, the node voltage response at node x is given by

$$V_{x} = V_{in} \frac{R_{x}}{R_{x} + M(\varphi_{in} - \varphi_{x})}$$

(3.24)

where  $V_x$  is the voltage at node x,  $\varphi_{in}$  is the input flux injection,  $\varphi_x$  is the flux accumulated at node x, and  $\varphi_{in}-\varphi_x$  is the flux across memristor M.

To prove *Property 11*, we derive the input-output relationship of the divider circuit by solving  $\varphi_x$  in terms of  $\varphi_{in}$  analytically. Note that  $\varphi_{in}$  is the input flux injection,  $\varphi_x$  is the flux accumulated at node x, and  $\varphi_{in}-\varphi_x$  is the flux across memristor M. Based on Kirchhoff's Current Law, the KCL equation at node x implies that all the net charges into node x would be zero. Hence, the charges (integral of current) went through the memristor,  $q_x$ , should be the same charges went through the resistor, so  $q_x=\varphi_x/R_x$ . Accordingly, the flux across memristor is  $\varphi_{in}-\varphi_x$ , and replacing  $\varphi$  by  $\varphi_{in}-\varphi_x$  and q by  $q_x$  in (3.18) yields the charges went through the memristor:

$$\frac{2\Phi_D}{R_{off}} \left[ \left( \frac{R(w_0)}{R_{off}} \right) - \sqrt{\left( \frac{R(w_0)}{R_{off}} \right)^2 - \frac{\varphi_{in} - \varphi_x}{\Phi_D}} \right] = \frac{\varphi_x}{R_x}$$

(3.25)

in which  $\varphi_x$  has an unique solution as shown below:

$$\varphi_{x}(t) = \frac{2\Phi_{D}R_{x}}{R_{off}} \cdot \left[\frac{R_{x} + R(w_{0})}{R_{off}} - \sqrt{\left(\frac{R_{x} + R(w_{0})}{R_{off}}\right)^{2} - \frac{\varphi_{in}(t)}{\Phi_{D}}}\right].$$

(3.26)

Since voltage  $V_x$  is the total derivative of  $\varphi_x$ ,  $V_x$  is derived to be:

$$V_{x} = V_{in} \cdot R_{x} / \left[ R_{off} \sqrt{\left(\frac{R_{x} + R(w_{0})}{R_{off}}\right)^{2} - \frac{\varphi_{in}}{\Phi_{D}}} \right]$$

(3. 27)

Therefore, the memristance  $M(\varphi_{in}-\varphi_x)$  has become:

$$M(\varphi_{in} - \varphi_x) = R_{off} \left(\overline{\Phi}_x - R_x / R_{off}\right)$$

(3.28)

where

$$\overline{\Phi}_{X} = \sqrt{\left(\frac{R_{x} + R(w_{0})}{R_{off}}\right)^{2} - \frac{\varphi_{in}}{\Phi_{D}}}.$$

(3.29)

Finally, substituting (3.28) back to (3.24) shows that is exactly equal to (3.27). Therefore, that memristor series-connect resistor circuit in Fig. 3.4 indeed behaves as a voltage divider.

**Property 12**: For the circuit in Fig. 3.4, assume the voltage source  $V_{in}$  is a squarewave pulse with an amplitude  $V_A$  and a width  $T_w$ . To move the state of the memristor from  $w_0$  to w, the required width  $T_w$  is:

$$T_{w} = \frac{\Phi_{D}}{V_{A}R_{off}^{2}} \cdot \left[ (R(w_{o}) + R_{x})^{2} - (R(w) + R_{x})^{2} \right] \cdot$$

(3.30)

*Property 12* specifies the time needed to move the memristor state from an initial *w*<sub>0</sub> to *w* for the divider circuit shown in Fig. 3.4. Note that the flux across memristor is

$\varphi_{in}-\varphi_x$ , and  $\varphi_x$  is already derived in (3.26). Substituting  $\varphi=\varphi_{in}-\varphi_x$  into (3.21) and yield the following analytical form:

$$\varphi_{in}(w) = \frac{\Phi_D}{R_{off}^2} \cdot \left[ (R(w_o) + R_x)^2 - (R(w) + R_x)^2 \right].$$

(3.31)

Equation (3.31) reveals the amount of flux injection needed to move the memristor state from  $w_0$  to w. For a supply voltage given in (3.22), as a special case, to move the state from  $w_0=0$  to w=D requires the same  $T_w$  as what is needed to move from state w=0 to w=D. This leads to *Corollary 12.1*.

**Corollary 12.1**: For the circuit in Fig. 3.4, assume the voltage source  $V_{in}$  is a squarewave pulse with an amplitude  $V_A$  and a width  $T_w$ . The duration needed for the memristor state to move from w=0 to w=D is the same as what is needed to move the state from w=D to w=0, and the required duration  $T_w$  is:

$$T_{w} = \left| \frac{\Phi_{D}}{V_{A} R_{off}^{2}} \cdot \left[ (R_{off} + R_{x})^{2} - (R_{on} + R_{x})^{2} \right].$$

(3.32)

A memristor has an effective flux restriction due to finite length *D. Property 6* demonstrates the effective  $\varphi$  range for a single memristor case. Thus, the total input fluxinjection  $\varphi_{in}$  across memristor and a resistor should have a range as well. The upper bound of such effective range is the amount of flux that pulls initial state  $w_0$  to *D*. Thus, substituting w=0 and w=D into (3.31) gives the lower and upper bound. This result is summarized in *Property 13*. **Property 13**: When a memristor is connected in series with a resistor as shown in Fig. 3.4, the effective range for  $\varphi_{in}$  across both memristor and resistor is:

$$\Phi_{LOW} \le \varphi_{in} \le \Phi_{UP} \tag{3.33}$$

where  $\varphi_{in}$  is integral of  $V_{in}$  and,

$$\overline{\Phi}_{LOW} = -\frac{\Phi_D}{R_{off}^2} \left( (R_{off} + R_x)^2 - (R(w_o) + R_x)^2 \right)$$

$$\overline{\Phi}_{UP} = \frac{\Phi_D}{R_{off}^2} \left( (R(w_o) + R_x)^2 - (R_{on} + R_x)^2 \right)$$

**Property 14**: Consider the circuit in Fig. 3.4 and assume the voltage source  $V_{in}$  has a zero-net-flux injection pattern. The memristor state will move back to the initial level provided that the applied input flux is within the effective range in (3.33).

Finally, *Property 14* shows that a zero net-flux input voltage pattern will insure that the state of the memristor comes back to the initial position for the circuit shown in Fig. 3.4. It provides important design guidance for ensuring read stability as discussed in detail in later sections. To prove *Property 14*, simply set  $\varphi_{in}$  equal to zero in (3.31) and solve for possible solutions for R(w); two possible numerical solutions exist: one is  $w=w_0$ , and the other solution is outside of the memristor physical range. Therefore, the state will be back to the initial level as  $w=w_0$ . However, *Property 14* is true only when the effective flux range condition as in *Property 13* is satisfied.

# 3.1.2. Characteristics in Nonlinear Drift Model

In nonlinear drift model, the window function reflects the following fact: as the memristor state moves toward the boundary (w=0 or w=D), the dopant drift velocity drastically decreases. However, the state equation behaves close to the linear drift assumption in the region between, in which the properties in the linear drift model are

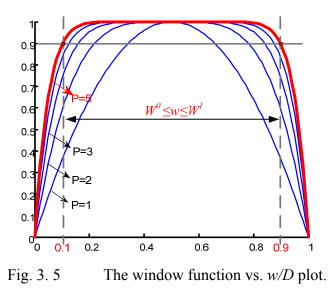

preserved. As shown in Fig. 3.5, the linear drift operation region is  $0.1 \le w \le 0.9$ . Accordingly, it is desirable to operate in a smaller linear range, say,  $W^0 \le w \le W^1$ , for faster switches and easier design. When approaching the boundaries, the constant average mobility used in the linear model,  $\mu_v$ , is the upper bound of the nonlinear average mobility used in the nonlinear models.

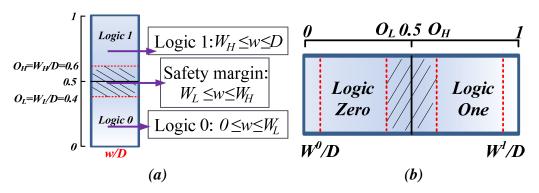

## 3.2. Define Logic Regions

For simplicity, a memristor is at *logic zero* when  $0 \le w/D \le 0.5$  and *logic one* when  $0.5 \le w/D \le 1.0$ . The corresponding ideal output low and high levels are w/D=0 and w/D=1.0, respectively. In reality, to account for possible noise injections, a safety margin is specified for each logic output:  $0 \le w/D \le O_L$ ,  $(O_L=W_L/D \le 0.5)$  for logic zero, and  $O_H \le w/D \le 1.0$  ( $O_H=W_H/D > 0.5$ ) for logic one. The region in between  $O_L \le w/D \le O_H$  is an unsafe region that should be avoided for read/write data integrity. Fig. 3.6(a) illustrates the situation where  $O_L=0.4$  and  $O_H=0.6$ .

On the other hand, the logic zero/one region needs to be defined before the memristor cell used as memory. With the consideration of the boundary effect, the memristor state is to keep off the boundary. For that, let  $W^0$  be the lower limit and  $W^1$  the upper limit, the ideal linear memristor state will only transition between  $W^0 \le w \le W^1$ . Moreover,  $W^0$  and  $W^1$  separate the nonlinear boundaries and the linear region, which are dependent on the fabrication. Fig. 3.6(b) shows an illustration of the defined output levels.

Fig. 3. 6 Memristor output levels. (a) The output low margin is at 0.4 and output high margin is at 0.6 in linear drift model; (b) output levels in nonlinear drift model.

## 3.3. Memory Cell Read/Write Operations

## 3.3.1. Write Operation Scheme

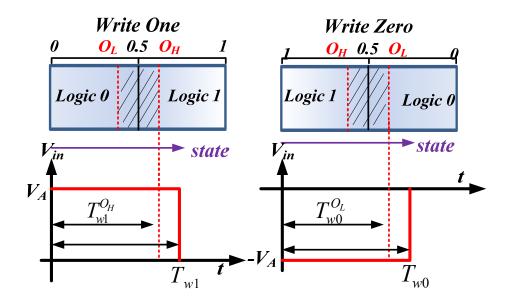

To write a logic value to a memristor cell, the proposed way is to have a structure in Fig. 3.7, where the memristor state will alter by the flux injection. Let the applied voltage be a square-wave pulse with amplitude  $V_A$  and width  $T_w$ .

Fig. 3. 7 Write signals (bottom) and corresponding memristor states (top).

Assume initially the state  $w_0$  is initial rest at ideal logic zero state, and it is desirable to write logic one to the cell. For the write process, input voltage  $V_{in}$  generates a square-wave pulse that has magnitude  $+V_A$  and width  $T_{wl}$  as shown in Fig. 3.7. Pulse width  $T_{wl}$  must be longer than the minimum required time  $T_{wl}^{Ow}$  to insure the state rest inside the logic one region after write. The minimum required time  $T_{wl}^{Ow}$  is derived to be:

$$T_{w1}^{O_W} = \frac{\Phi_D}{|V_A| R_{off}^2} \Big[ R_{w0}^2 - R(W_H)^2 \Big],$$

(3.34)

where  $R_{w0}$  is the resistance at logic zero state. If the initial state  $w_0$  but somewhere inside the logic 0 region, a successful write can be guaranteed as long as  $T_{wl} \ge T_{wl}^{Ow}$ . Similarly to write a logic zero, the input voltage  $V_{in}$  is a negative square-wave pulse ( $-V_A$ ) with duration  $T_{w0}$ . The minimum required time  $T_{w0}^{OL}$  would be:

$$T_{w0}^{O_L} = \frac{\Phi_D}{|V_A| R_{off}^2} \Big[ R(W_L)^2 - R_{w1}^2 \Big].$$

(3.35)

where Rw1 is the resistance at ideal logic one state. The write zero process would be successful if pulse width  $T_{w0}$  is at least greater than  $T_{w0}^{OL}$ . Thus, a write signal that has duration equal or larger than the derived minimum required time can insure a successful write. Similar to devices like SRAM, the SRAM write operation also requires a minimum write time called "critical time". For the SRAM state to flip, the write signal must sustain long than the critical time for a successful write.

Moreover, the memristor state w=0 and w=D are as ideal logic zero and one states in linear drift model. The equation from *Corollary 10.1* specifies the required pulse widths to move a state from  $w_0=0$  to w=D or move from  $w_0=D$  to w=0. Therefore, the write pulse is highly recommended to have the width in *Corollary 10.1* so the state reaches the ideal logic zero/one state.

Suppose the memristor behavior follows nonlinear drift model. The state  $W^0$  and  $W^1$  are the ideal logic zero and one state. The goal of write operation is to precisely move the state to  $W^0$  for logic zero and  $W^1$  for logic one. They are done by write zero and one process. The proposed write scheme is briefly shown in Fig. 3.8, and Fig. 3.9 illustrates the corresponding pulses for write one/zero process.

Suppose the cell is desirable to write to ideal logic one state, the write one process is performed. Because positive flux injection raises the state, as shown in Fig. 3.9, the state increases due to constant magnitude pulse  $V_A$ . The reference voltage  $V^{W}_{ref}$  is set to:

$$V^{W}_{ref} = V_{A} \cdot R_{x} / (R_{x} + R(W^{1})).$$

(3.36)

The reference voltage  $V^{W_{ref}}$  would come to the same as  $V_x$  after some time. When that happens, the memristor state reached the desire state, and the comparator sends a feedback signal to switch off the write pulse.

Fig. 3. 9 Write pulses (top) and corresponding memristor states (bottom).

The write zero operation is very similar. A constant magnitude  $-V_A$  is applied to the memristor if the memristor does not initially stores a logic zero. The reference voltage is set according to the equation below for write zero process:

$$V^{W}_{ref} = -V_{A} \cdot R_{x} / (R_{x} + R(W^{0})).$$

(3.37)

In other words, the write process sets  $V_{in}$  to a constant  $V_A$  or  $-V_A$  magnitude pulse depends on whether writing logic one or zero, and  $V^{W}_{ref}$  is set accordingly.

## 3.3.2 Read Operation Scheme

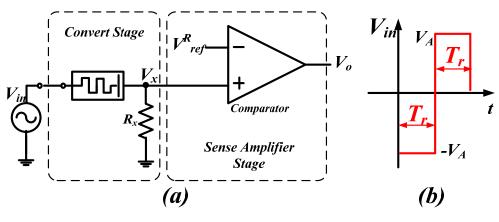

The proposed memristor based memory cell structure is in Fig. 3.10; such read scheme works for both linear and nonlinear models. A read is performed in two stages: convert stage and amplifier stage. In convert stage, the memristor state information converts into a voltage signal,  $V_x$ , which reflects the memristor state information. The sense amplifier stage determines the logic based on  $V_x$  and output full-swing digital scale.

The designed read signal pattern has a negative pulse followed by a positive pulse with equal magnitude and duration as shown in Fig. 3.10(b). This read pattern will enforce zero net flux injection over one period to avoid altering memristor state after a read access.

In order to extract the information of the internal state, a voltage excitation is applied, which will perturb the memristor state. Due to the memristor property mentioned above, zero net flux injection read pattern avoids altering the memristor state after read cycles. The negative pulse cycle decreases the state and the positive cycle brings the state back up. The read pulse  $T_r$  reflects the amount of perturbation to the memristor state. Large perturbation would lead to data integrity issues. If ideal one state (at  $W^1$ ) is stored, the read pulse would be constrained by the  $W_H$  margin so the state would not travel to unsafe region. If ideal zero state (at  $W^0$ ) is initially stored, the negative pulse drags the state to nonlinear region. The design on read process is motivated by the insights that nonlinear drift will slow down the drift process of the dopants, thus the designed read flux is a conservative bound based on the linear drift model that will not trap the dopants to the boundary. Accordingly, we constrain the read pulse based on our linear model, that is

$$T_{r} < \left| \frac{\Phi_{D}}{V_{A} R_{off}^{2}} \right| \cdot \min \left\{ \frac{\left| \left( R(W^{1}) + R_{x} \right)^{2} - \left( R(W_{H}) + R_{x} \right)^{2} \right|}{\left| \left( R(W^{L}) + R_{x} \right)^{2} - \left( R(W^{0}) + R_{x} \right)^{2} \right|} \right\}$$

(3.38)

which is taking the minimum flux injection to move the state from  $W^l$  to  $W^H$  or  $W^0$  to  $W^L$ .

The resistor in series with the memristor is to convert the memristor state into a voltage signal since the current through the memristor carries the memristor state information, thus the voltage at node x ( $V_x$ ) would reflect the memristor state information. Use the simplified resistance model,  $V_x$  can be expressed as:

$$V_{x} = V_{in} \cdot R_{x} / (R_{x} + R(w)).$$

(3.39)

Let the reference voltage set to:

$$V_{ref}^{R}(t) = V_{A}/2$$

(3.40)

which  $V_A$  is the pulse magnitude shown in Fig. 3.10(b). The negative pulse comes at the first cycle makes  $V_x$  negative, and  $V_o$  would be zero out of the comparator. At the second

cycle of read pattern,  $V_x$  is compared with  $V^{R}_{ref}$  to determine the logic. If the state is below half of D,  $V_x$  would be below  $V^{R}_{ref}$ , and logic zero is read. Similarly,  $V_x$  higher than  $V^{R}_{ref}$  indicates the memristor state is in upper half of its length D, and logic one is read. For that, the corresponding  $R_x$  is the following:

$$R_x = (R_{on} + R_{off})/2.$$

(3.41)

This way, we can distinguish logic zero and logic one.

Fig. 3. 10 (a) Operation stages; (b) read pattern.