# HIGH-PERFORMANCE ORGANIC THIN-FILM TRANSISTOR

## A Dissertation

by

## YUNBUM JUNG

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Chair of Committee, Xing Cheng Committee Members, Choongho Yu

Jun Zou

Kamran Entesari

Head of Department, Chanan Singh

May 2014

Major Subject: Electrical Engineering

Copyright 2014 Yunbum Jung

#### **ABSTRACT**

Organic compounds have been regarded as insulators for a long time. However, a semi-conductive organic material was discovered in the late 1940s. Since then, many organic semiconductors have been found and studied. However, the current carriers have quite lower mobility than those of inorganic counterparts so far. In spite of the low mobility, organic semiconductor devices have many interesting advantages such as lowcost fabrication, easy process, diverse substrate materials, and so on. Owing to the benefit of the low-cost fabrication, organic semiconductor can be applied to large-area electronic devices as well as ubiquitous devices. Although organic semiconductor has been widely utilized in electronics, its low performance has extremely restricted application in integrated circuits (ICs) that are essential for high-tech electronics. In order to be competitive in market, the performance improvement of organic thin film transistors (OTFTs) has become an indispensable prerequisite. Although the low performance of conventional OTFTs basically results from the inherent low carrier mobility, it is also attributed to low resolution fabrication processes and their inferior configuration with large parasitic capacitance.

With regard to solutions to improve the performance of OTFTs, three novel strategies are proposed in this work: submicron metal patterning, self-aligned structure, and metal semiconductor field-effect transistor (MESFET)-like structure. To realize the solutions, a new concept of lithography, dual-layer thermal nanoimprint, is devised and its potential for submicron organic semiconductor patterning is experimented. In

addition to the submicron resolution, two innovative patterning techniques, single-layer patterning and double-layer patterning, are successfully developed through the dual-layer thermal nanoimprint. Both patterning techniques can be utilized in fabricating self-aligned OTFTs and organic metal semiconductor field-effect transistors (OMESFETs). In the case of OMESFETs that require multiple-level metallization, the application of the dual-layer thermal nanoimprint lithography is extended from two-dimension to three-dimension to achieve self-aligned metallization that completely eliminates alignment errors. The 3D dual-layer thermal nanoimprint enables a sub-100 nm gap between metal patterns on an organic active layer. Because of the capability of nanoscale metal patterning on organic semiconductors with high overlay accuracy, this self-aligned metallization technique can be effectively utilized to fabricate high-performance top-contact OMESFETs.

# DEDICATION

This dissertation is dedicated to my beloved wife, Yoojea, and my adorable sons, Soomin and Woojin, for their endless encouragement, unconditional trust, and true love.

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest appreciation to my advisor, Dr. Xing Cheng, who has been a respectable and generous mentor to me. His continuous and convincing advice led me in the right direction. He also encouraged me to explore new challenges. With his invaluable guidance and encouragement, I was able to accomplish significant achievements in my work and finally complete this dissertation.

I am sincerely grateful to my committee members, Dr. Choongho Yu, Dr. Jun Zou, and Dr. Kamran Entesari, for their time and care. Their constructive criticism and best suggestions improved the quality of my research.

I am thankful for helpful comments and hints that I received from my colleagues, Yichen Lo and Youwei Jiang. And, my gratitude also goes out to ECE department staff members, Tammy Carda, Robert Akins, Jim Gardner, and Dennie Spears. Their great assistance made my research go smoothly. I also give thanks to National Science Foundation for their financial support throughout my doctoral course.

My parents, parents-in-law, brother, and sister-in-law truly deserve my warm appreciation. Their prayer and encouragement have sustained me thus far. Finally, I wholeheartedly thank my wife, Yoojea, and my sons, Soomin and Woojin, who always stand by me in joy and sorrow. Words cannot express how grateful I am for the love and trust they have shown me.

## **NOMENCLATURE**

Al Aluminum

Au Gold

BOE Buffered Oxide Etch

BST Barium Strontium Titanate

BZT Barium Zirconate Titanate

CHF<sub>3</sub> Trifluoromethane

Cr Chromium

E-beam Electron-beam

FDTS 1H,1H,2H,2H-perfluorodecyltrichlorosilane

FET Field-Effect Transistor

TES-ADT 5,11-bis(triethylsilylethynyl) anthradithiophene

FTS (tridecafluoro-1,1,2,2-tetrahydrooctyl) trichlorosilane

HMDS Hexamethyldisilazane

HOMO Highest Occupied Molecular Orbital

IC Integrated Circuit

IP Ionization Potential

LUMO Lowest Unoccupied Molecular Orbital

MESFET Metal Semiconductor Field-Effect Transistor

MTR Multiple Trapping and Release

NIL Nanoimprint Lithography

OMESFET Organic Metal Semiconductor Field-Effect Transistor

OTFT Organic Thin-Film Transistor

OTS Octodecyltrichlorosilane

P3HT Poly (3-hexylthiophene-2,5-diyl)

PECVD Plasma-Enhanced Chemical Vapor Deposition

PGMEA Propylene glycol methyl ether acetate

PMMA Poly (methyl methacrylate)

PVA Polyvinyl acetate

RFID Radio Frequency Identification

RIE Reactive Ion Etching

SAM Self-Aligned Monolayer

SEM Scanning Electron Microscope

Si<sub>3</sub>N<sub>4</sub> Silicon nitride

SiO<sub>2</sub> Silicon dioxide

Tg Glass Transition Temperature

TIPS-PEN 6,13-bis(triisopropylsilylethynyl) pentacene

UV Ultra Violet

.

# TABLE OF CONTENTS

|                                                                           | Page |

|---------------------------------------------------------------------------|------|

| ABSTRACT                                                                  | ii   |

| DEDICATION                                                                | iv   |

| ACKNOWLEDGEMENTS                                                          | v    |

| NOMENCLATURE                                                              | vi   |

| TABLE OF CONTENTS                                                         | viii |

| LIST OF FIGURES                                                           | X    |

| LIST OF TABLES                                                            | xiv  |

| CHAPTER I INTRODUCTION AND PRINCIPLE OF ORGANIC THIN-FILM TRANSISTOR      | 1    |

| 1.1 Overview of OTFTs                                                     |      |

| 1.2 Organic semiconductors                                                |      |

| 1.3 Gate dielectrics                                                      |      |

| 1.5 Solutions towards a high performance OTFT                             |      |

| CHAPTER II DUAL-LAYER THERMAL NANOIMPRINT LITHOGRAPHY WITHOUT DRY ETCHING | 22   |

| 2.1 Introduction                                                          | 22   |

| 2.2 Experimental methods                                                  |      |

| 2.2.1 Adhesion improvement and dual polymer layer on SiO <sub>2</sub>     | 25   |

| 2.2.2 Non-compatibility testing for PMMA and P3HT                         | 26   |

| 2.2.3 Single-layer patterning                                             |      |

| 2.2.4 Double-layer patterning                                             |      |

| 2.2.5 Temperature range for dual-layer thermal nanoimprint                |      |

| 2.3 Results and discussion.                                               |      |

| 2.3.1 Non-compatibility of PMMA and P3HT                                  |      |

| 2.3.2 Single-layer patterning without residual layer                      |      |

| 2.3.3 Double-layer patterning                                             |      |

| 2.3.4 Temperature range for dual-layer thermal nanoimprint                | 40   |

| 2.4 Summary                                                                            | 41     |

|----------------------------------------------------------------------------------------|--------|

| CHAPTER III SELF-ALIGNED METALLIZATION ON ORGANIC                                      |        |

| SEMICONDUCTOR THROUGH 3D DUAL-LAYER THERMAL NANOIMPRIN                                 | VT .43 |

| SEMICONDECTOR TIMOCOM SE DOME EMILER MERINA INTROMATRIA                                | 11.15  |

| 3.1 Introduction                                                                       | 43     |

| 3.2 Experimental methods                                                               | 45     |

| 3.2.1 Self-aligned metallization on P3HT based on isotropic side-wings                 | 45     |

| 3.2.1.1 3D imprint mold fabrication                                                    |        |

| 3.2.1.2 Dual-layer thermal nanoimprint for 3D PMMA patterns on P3HT                    |        |

| 3.2.1.3 Self-aligned metallization                                                     | 48     |

| 3.2.2 Self-aligned metallization based on anisotropic side-wings                       |        |

| 3.2.2.1 Anisotropic 3D mold fabrication                                                |        |

| 3.2.2.2 Single-layer PMMA patterning and self-aligned metallization                    |        |

| 3.3 Results and discussion.                                                            |        |

| 3.3.1 Self-aligned metallization based on isotropic side-wings                         |        |

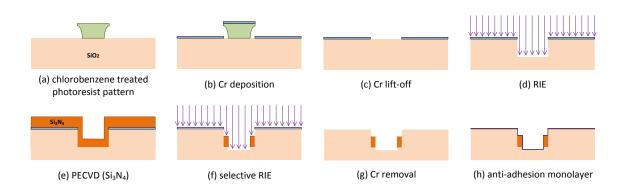

| 3.3.1.1 3D imprint mold with isotropic recesses                                        |        |

| 3.3.1.2 3D PMMA patterns on P3HT                                                       |        |

| 3.3.1.3 Self-aligned metallization                                                     |        |

| 3.3.2 Self-aligned metallization based on anisotropic side-wings                       |        |

| 3.3.2.1 3D nanoimprint mold with anisotropic recesses                                  |        |

| 3.3.2.2 Self-aligned metallization                                                     |        |

| 3.3.3 Applications of self-aligned metallization on organic semiconductors 3.4 Summary |        |

| 5.4 Summary                                                                            | 04     |

| CHAPTER IV ORGANIC METAL SEMICONDUCTOR FIELD-EFFECT                                    |        |

| FRANSISTOR FABRICATED THROUGH 3D THERMAL NANOIMPRINT                                   |        |

| BASED SELF-ALIGNED METALLIZATION                                                       | 66     |

|                                                                                        |        |

| 4.1 Introduction                                                                       | 66     |

| 4.2 Experimental methods                                                               |        |

| 4.2.1 Nanoimprint-aware layout                                                         |        |

| 4.2.2 Fabrication of OMESFET                                                           |        |

| 4.2.3 Electrical characteristics                                                       |        |

| 4.3 Results and discussion                                                             |        |

| 4.3.1 Configuration                                                                    |        |

| 4.3.2 Rectifying behavior                                                              |        |

| 4.3.3 Electrical characteristics                                                       |        |

| 4.4 Summary                                                                            | 79     |

| CHAPTER V CONCLUSION                                                                   | 81     |

|                                                                                        |        |

| REFERENCES                                                                             | 83     |

# LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Figure 1. Schematic views of conventional OTFTs                                                                                                                                                                                                                                                                                                                                                                                  | 3                        |

| Figure 2. Schematic energy level diagram of gold and P3HT before (a) and a contact. Hole-injection barrier ( $\phi_h$ ) is calculated from the ionization potential (IP) of P3HT, the work function ( $\phi$ ) of gold, and the interdipole barrier ( $\Delta_{dipole}$ ).                                                                                                                                                       | n<br>face                |

| Figure 3. Carrier mobility of organic and inorganic semiconductors                                                                                                                                                                                                                                                                                                                                                               | 8                        |

| Figure 4. Classification of organic semiconductors                                                                                                                                                                                                                                                                                                                                                                               | 9                        |

| Figure 5. Molecular structures of soluble small molecules                                                                                                                                                                                                                                                                                                                                                                        | 11                       |

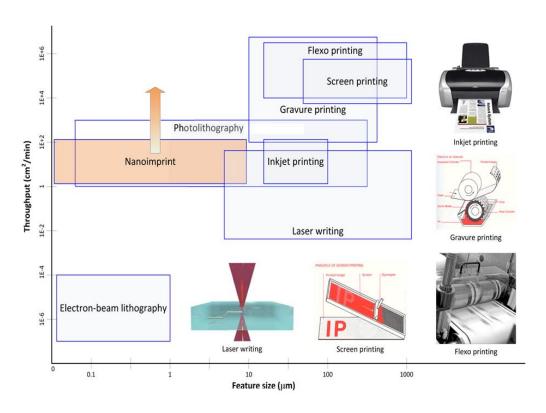

| Figure 6. Throughputs and resolutions of commercial lithography techniques                                                                                                                                                                                                                                                                                                                                                       | s16                      |

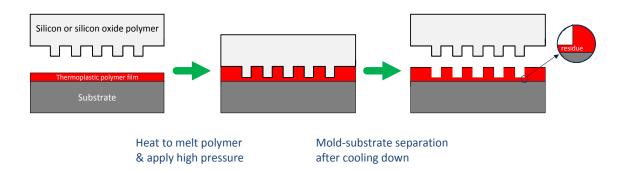

| Figure 7. A schematic for thermal nanoimprint lithography process                                                                                                                                                                                                                                                                                                                                                                | 18                       |

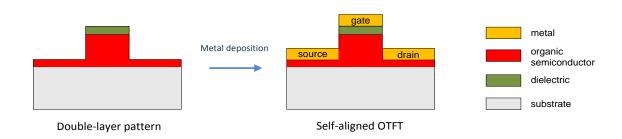

| Figure 8. A self-aligned OTFT using double-layer pattern                                                                                                                                                                                                                                                                                                                                                                         | 19                       |

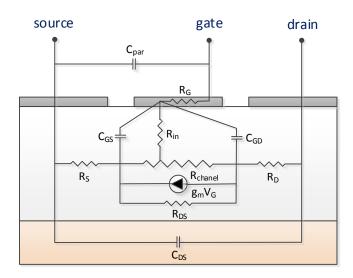

| Figure 9. A small-signal equivalent circuit of a MESFET                                                                                                                                                                                                                                                                                                                                                                          | 20                       |

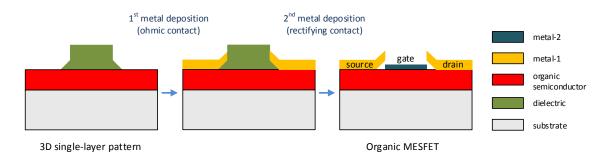

| Figure 10. An OMESFET fabricated based on 3D single-layer patterns                                                                                                                                                                                                                                                                                                                                                               | 21                       |

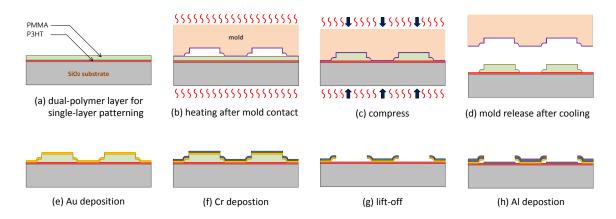

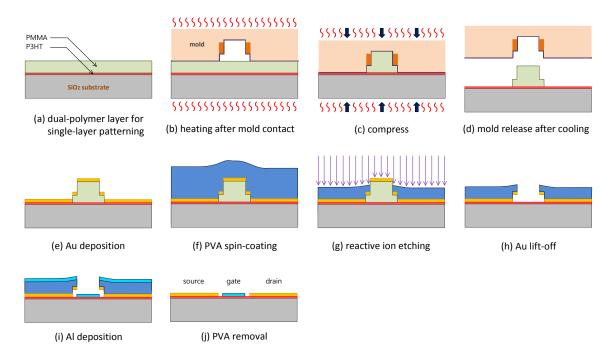

| Figure 11. A schematic for the dual-layer thermal nanoimprint lithography p shows single-layer patterning. Only the top PMMA layer is pattern while the bottom P3HT layer is intact.                                                                                                                                                                                                                                             | ied,                     |

| Figure 12. A schematic for the dual-layer thermal nanoimprint lithography p shows double-layer patterning. Both PMMA and P3HT layers are patterned.                                                                                                                                                                                                                                                                              |                          |

| Figure 13. Optical microscope images of PMMA dewetting on P3HT at 180 and (b), including defects) and 220 °C (c). The orange-colored region P3HT and the red-colored region is PMMA                                                                                                                                                                                                                                              | on is                    |

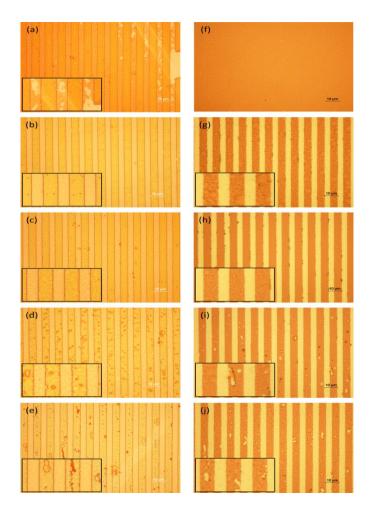

| Figure 14. Optical microscope images of single-layer patterns (a, b, c, d, and optical microscope images after their gold lift-off (f, g, h, i, and j) wt. % PMMA in toluene is spin-coated at 3000, 3300, 4000, 5000, 7000 rpm, respectively. (a) The PMMA residual layer exists after nanoimprint, thus no gold pattern in (f). Notice that P3HT surface is patterned by nanoimprint in (f); (b) and (c) have no PMMA residual | where 3<br>and<br>is not |

| after nanoimprint, and (g) and (h) show smooth 5 µm gold lines on top of P3HT after lift-off; in (d) and (e), PMMA is too thin to completely fill mold cavities, leading to defects in the form of voids in PMMA patterns. Gold lift-off in (i) and (j) shows gold patches in-between gold lines due to PMMA voids.                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

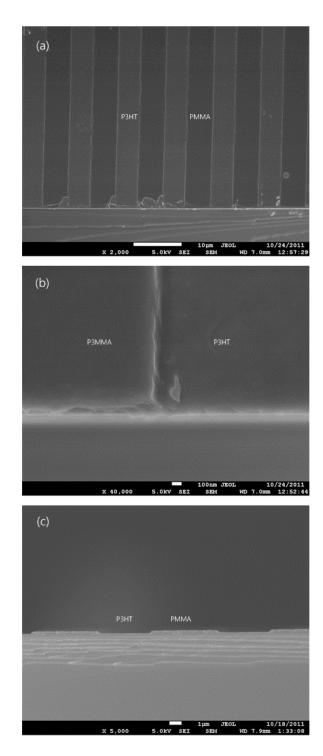

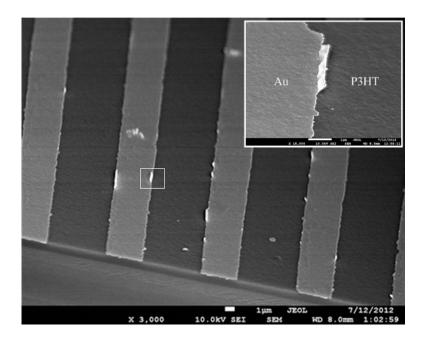

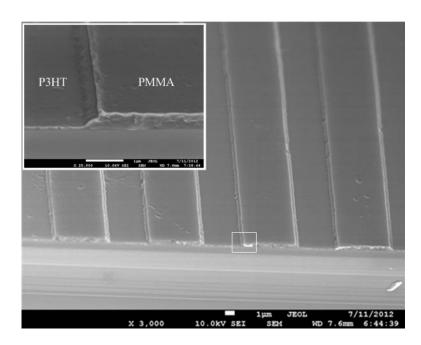

| Figure 15. SEM images of the single PMMA layer patterns where 3 wt. % PMMA is spin-coated at 3500 rpm: (a) and (b) are the perspective views and (c) is the cross-sectional view                                                                                                                                                                                                                                                                       |

| Figure 16. An SEM image of voids in PMMA patterns due to incomplete filling of mold cavity by PMMA melt where 3 wt. % PMMA is spin-coated at 7000 rpm                                                                                                                                                                                                                                                                                                  |

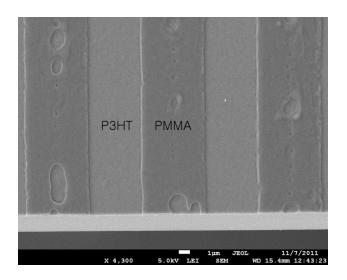

| Figure 17. Optical microscope images of P3HT surface from single spin-coating (a) and multiple spin-coating (b), and their SEM cross-sectional images ((c) single spin-coating and (d) multiple spin-coating). The thickness of the P3HT layer from single spin-coating varies between 1.13 and 1.33 µm while the thickness from multiple spin-coating is uniform at 730nm                                                                             |

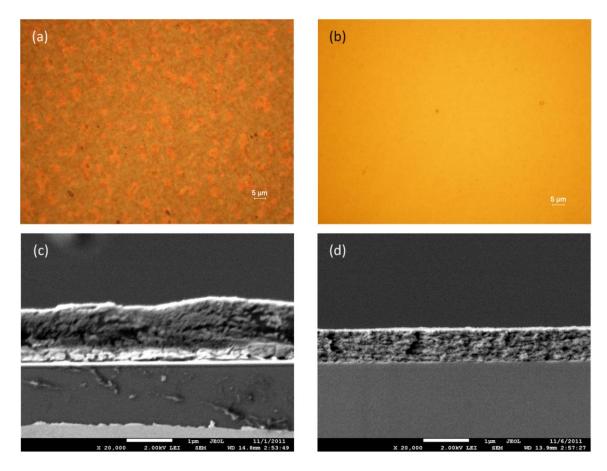

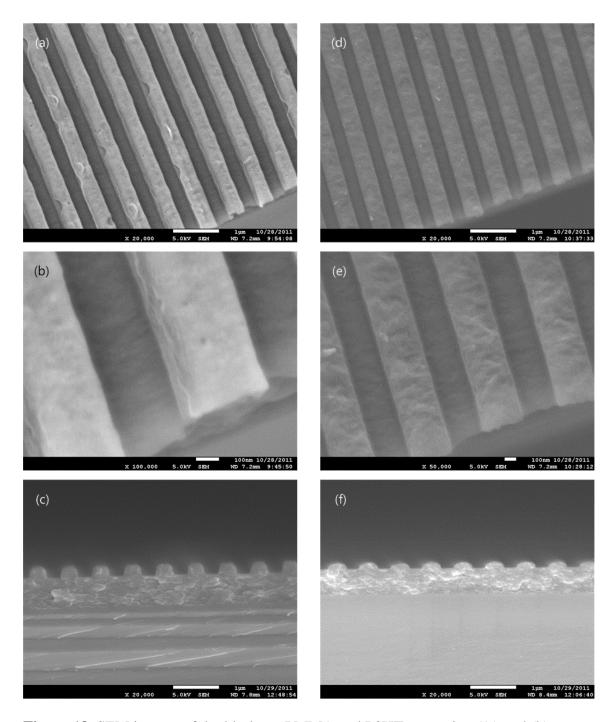

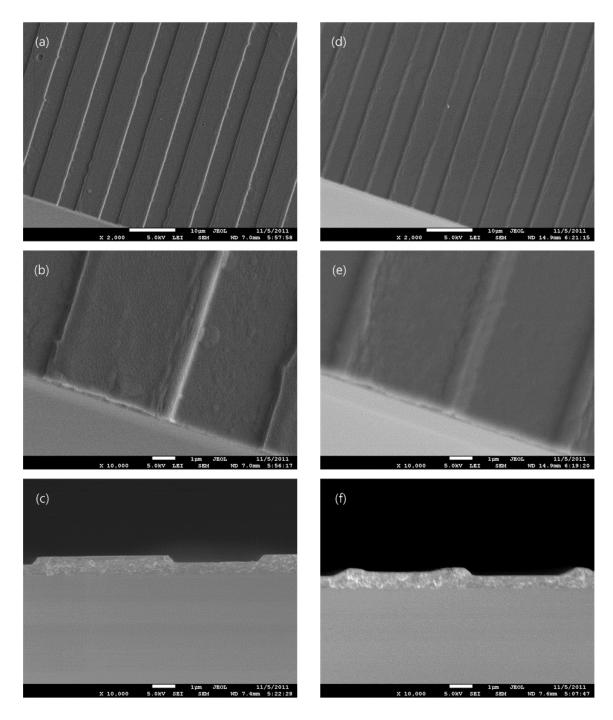

| Figure 18. SEM images of double-layer PMMA and P3HT patterning ((a) and (b) are the perspective views and (c) is the cross-sectional view) and their SEM images after removing PMMA ((d) and (e) are the perspective views and (f) is the cross-sectional view). P3HT patterns with single peak are formed under the PMMA patterns. The mold used in this case has a cavity width of 400 nm.                                                           |

| Figure 19. SEM images of double-layer PMMA and P3HT patterning ((a) and (b) are the perspective views and (c) is the cross-sectional view) and their SEM images after removing PMMA ((d) and (e) are the perspective views and (f) is the cross-sectional view). P3HT patterns with double peak are formed under the PMMA patterns. The mold used in this case has a cavity width of 5.5 µm.                                                           |

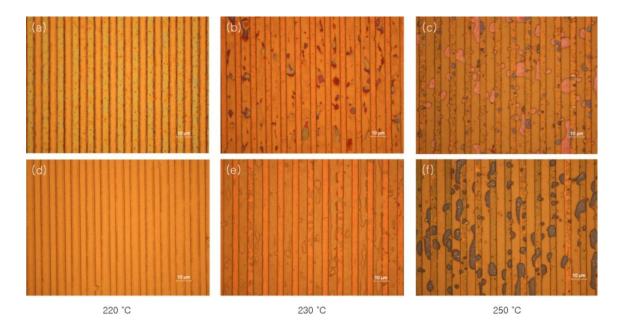

| Figure 20. Optical microscope images of amixture of PMMA and P3HT melts in dual-layer nanoimprint at (a) 220, (b) 230, and (c) 250 °C. Their optical microscope images after removing PMMA are shown in (d), (e), and (f), respectively                                                                                                                                                                                                                |

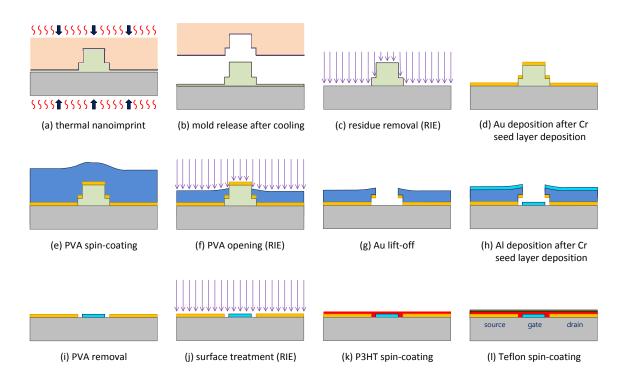

| Figure 21. A schematic for the self-aligned metallization process based on istropic side-wings (scheme 1). The 3D nanoimprint mold can be fabricated by a combination of wet and dry etching. The nanoimprint process parameters are controlled such that only single-layer patterning of PMMA is accomplished and there is no PMMA residue layer in step (d) (See [71]). After the step (h), we have two metal patterns in contact with P3HT: gold xi |

| as ohmic contact and aluminum as Schottky contact. Such structure can be used as OMESFET in which the gold serves as the source/drain contacts and the aluminum serves as the gate control. The separation between the gold and the aluminum, which is a critical parameter for high-performance OMESFETs, is controlled by the mold structure  | .45 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

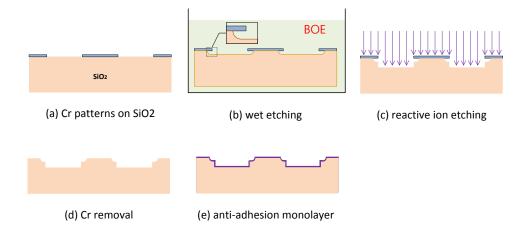

| Figure 22. A schematic for the fabrication process for the 3D mold used in scheme 1. The mold has isotropic recesses formed by wet oxide etching                                                                                                                                                                                                | .47 |

| Figure 23. A prospective SEM image of the first metal patterns consisting of only gold. Most side-wing structures of the gold patterns were destroyed by the ultrasonic agitation after the lift-off step.                                                                                                                                      | .49 |

| Figure 24. A schematic for the self-aligned metallization process based on anisotropic side-wings (scheme 2). The 3D mold is fabricated by a selective dry etching step.                                                                                                                                                                        | .50 |

| Figure 25. A schematic for the fabrication process for the 3D mold used in scheme 2. The mold has anisotropic (vertical) recesses.                                                                                                                                                                                                              | .51 |

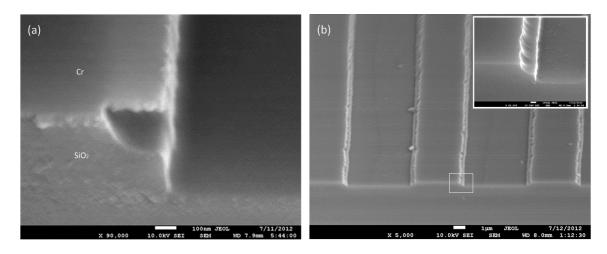

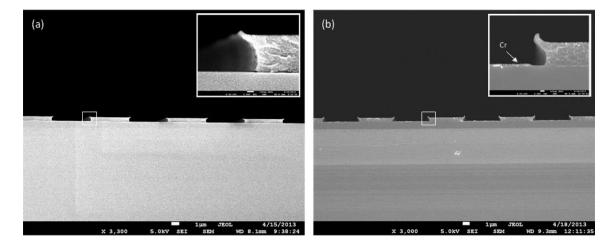

| Figure 26. Prospective SEM images of the 3D mold with isotropic undercut structures before (a) and after (b) Cr removal. The undercut radius varies in a tolerable range of 20 nm.                                                                                                                                                              | .54 |

| Figure 27. A prospective SEM image of the 3D PMMA patterns with rounded footings after dual-layer thermal nanoimprint.                                                                                                                                                                                                                          | .55 |

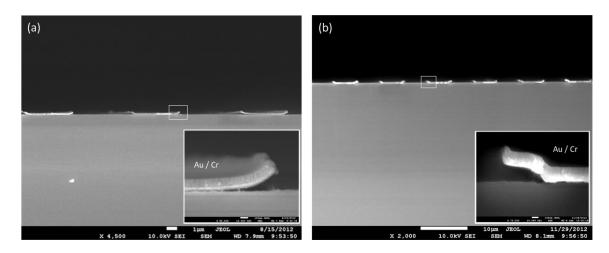

| Figure 28. Cross-sectional SEM images of the first metal pattern. The side-wing shapes are affected by the Au/Cr ratio. (a): 50 nm Au / 100 nm Cr and (b): 110 nm Au / 60 nm Cr. In (a), the high compressive stress resulted from thick Cr layer led to the peeling of Au/Cr film from P3HT surface                                            | .56 |

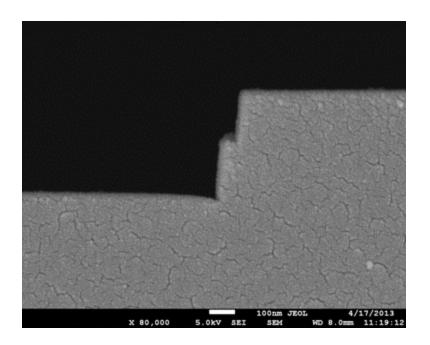

| Figure 29. SEM images of metal patterns: (a) a prospective image of the first Au/Cr pattern with curved side-wings; and (b) a cross-sectional image of the self-aligned metal patterns.                                                                                                                                                         | .57 |

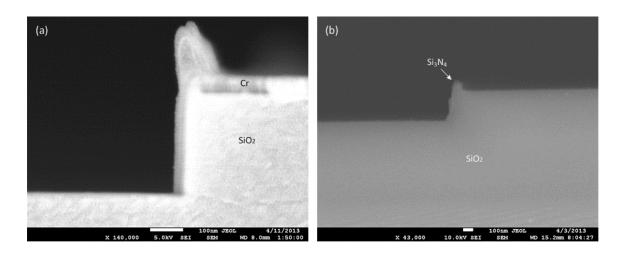

| Figure 30. Cross-sectional SEM images that show the chromium mask layer with an edge jut (a) and an undesired silicon nitride protrusion (b). The edge protrusion negatively affected the PECVD deposition of silicon nitride and subsequent selective dry etching. Eventually it led to the silicon nitride protrusion after chromium removal. | 58  |

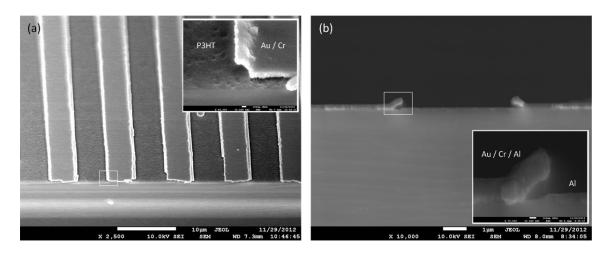

| Figure 31. Cross-sectional SEM images of (a) chlorobenzene-treated photoresist pattern and (b) chromium pattern without an edge jut.                                                                                                                                                                                                            | .59 |

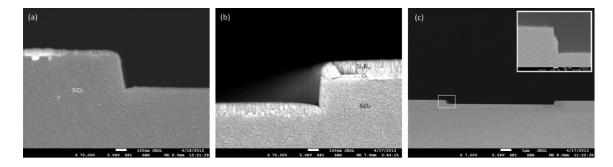

| Figure 32. Cross-sectional SEM images that show the sequence of 3D mold generation: (a) initial trench after the first dry etching, (b) silicon nitride deposited by PECVD, and (c) 3D imprint mold with anisotropic recesses on sidewalls after selective dry etching of silicon nitride and chromium removal.                                        | .60 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

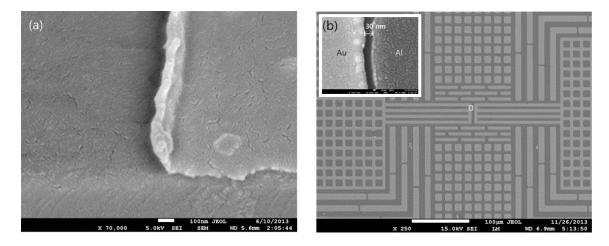

| Figure 33. SEM images for the key steps of self-aligned metallization from an anisotropic side-wing: (a) 3D PMMA pattern on P3HT, (b) PVA film spin-coated after gold deposition, (c) anisotropic side-wing supported by PVA after gold lift-off, and (d) gold and aluminum patterns on P3HT with 60 nm gap after aluminum deposition and PVA removal. |     |

| Figure 34. Cross-sectional views of OFETs. While traditional structures (a, b) includes large overlaps, the suggested MESFET-like structure (c) eliminates the overlap as well as gate insulator.                                                                                                                                                      | .68 |

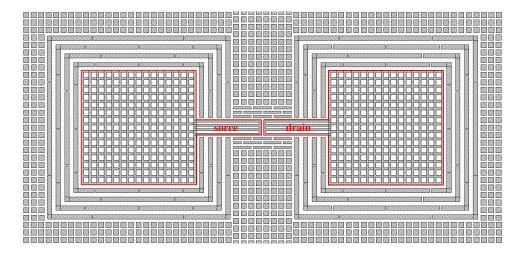

| Figure 35. A nanoimprint-aware layout defining source and drain. Dummy patterns are utilized in undefined area as well as defined area to keep a uniform pattern density.                                                                                                                                                                              | 69  |

| Figure 36. A cross-sectional SEM image of the 3D nanoimprint mold with an anisotropic shoulder on its sidewall                                                                                                                                                                                                                                         | 70  |

| Figure 37. A schematic for the fabrication process of a full bottom contact type OMESFET with self-aligned electrodes. The anisotropic side-wing defines the regular gap between gate and source/drain.                                                                                                                                                | .72 |

| Figure 38. SEM images of metal patterns. The anisotropic side-wing of the first metal pattern is utilized as a self-align mask (a: prospective view) and 30 nm gap between electrodes is achieved after completing the self-aligned metallization (b: top view)                                                                                        | .75 |

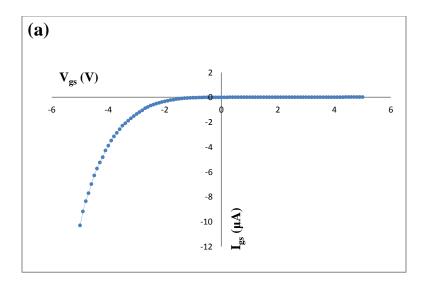

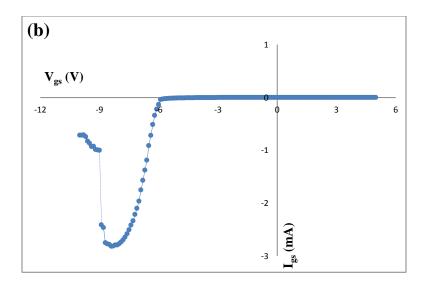

| Figure 39. Rectifying characteristic (a) and break-down phenomenon (b) in the OMESFET measured from a gate-source biasing                                                                                                                                                                                                                              | 76  |

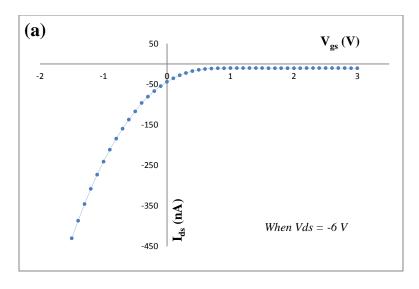

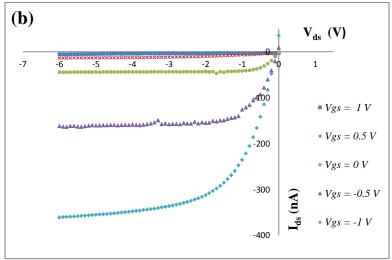

| Figure 40. Transfer (a) and output (b) characteristics of the OMESFET                                                                                                                                                                                                                                                                                  | 79  |

# LIST OF TABLES

|                                                               | Page |

|---------------------------------------------------------------|------|

| Table 1. PMMA film thickness at different spin-coating speeds | 34   |

|                                                               |      |

|                                                               |      |

#### CHAPTER I

#### INTRODUCTION AND PRINCIPLE OF ORGANIC THIN-FILM TRANSISTOR

Since the first OTFT was developed in 1986 [1], OTFTs have continuously been the keen interest of numerous researchers. The unceasing concerns are mostly attributed to their charming potentiality of very low-cost manufacturing that can be achieved from simple device structures and easy processing steps [2]. Owing to the high cost-effectiveness, OTFTs are preferred for large-area and low-cost applications such as active-matrix driving circuits for display, smart cards, low-cost radio frequency identification (RFID) tags, simple ICs, and memory devices. Furthermore, OTFTs can be fabricated at low-temperatures, even at room temperature, so that there are broad options for substrate materials; plastic or paper can be also used for the substrate. Consequently, flexible or transparent electronics are realized in such applications of display and electronic paper. The novel properties of flexibility and transparency enable the forming of a new paradigm of future electronics.

In spite of such unique advantages, OTFTs still have a long way to overtake their inorganic counterparts in a real commercial market. Although OTFTs have been gradually deployed for low-performance electronics on a commercial scale, their performance is extremely too low to satisfy market expectations that have become used to inorganic high-tech electronics. In order to extend the area of their commercial applications, it is indispensable to improve their poor performance. While there have been enormous efforts to improve the inferior electrical characteristics of materials,

studies on device structural and dimension-wise improvement have been in a stalemate for a long time because there has been no available lithography technique for the improvement. Therefore, it is difficult to expect a dramatic performance improvement of OTFTs without innovation of lithography techniques.

As the need of an innovative lithography technique comes to the forefront in realizing high-performance OTFTs, we have tried to assess the possibility of performance improvement from the nanoimprint lithography that is regarded as one of the next generation lithography techniques for sub-10 nm patterning. In order to make a breakthrough, however, the existing nanoimprint flow essentially needs to make up for its condition requiring a dry-etching that may seriously degrade the electrical characteristics of an organic semiconductor active layer. As a way to avoid the dry-etching, a new concept of nanoimprint, called dual-layer thermal nanoimprint, is devised. In addition, the concept is expanded from two-dimension to three-dimension to efficiently realize the structural improvement of OTFTs. For the first step towards high-performance OTFTs, appropriate solutions based on the dual-layer thermal nanoimprint are suggested after thoroughly explaining the principle of conventional OTFTs in this chapter. In the following chapters, the feasibility of the solutions is investigated through experimental results and then performance improvement is reported.

#### 1.1 Overview of OTFTs

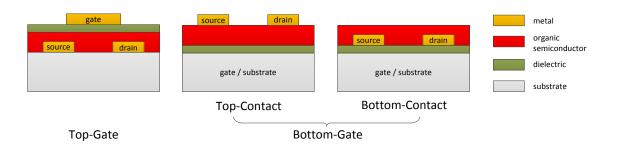

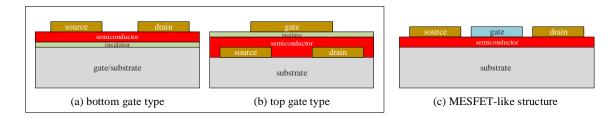

The three basic elements of OTFTs are a gate insulator, a thin organic active layer, and three electrodes – source, drain, and gate. According to their arrangement, conventional OTFTs are commonly classified into top-gate and bottom-gate types: the bottom-gate type of OTFTs is sorted into top-contact and bottom-contact types in more detail [3]. As shown in figure 1, the gate is separated from the organic active layer by the gate insulator whereas the other two electrodes, the drain and the source, are in contact with the organic semiconductor film. In the bottom-gate type, a heavily doped semiconductor substrate is often used for the gate so that a fabrication process is much simpler than that of the top-gate type because it does not need a metal patterning step for the gate.

**Figure 1.** Schematic views of conventional OTFTs

As one of field-effect transistors, the carrier (hole or electron) distribution and mobility of OTFTs are also controlled by electric field change in an organic active layer. Because the organic active layer is morphologically in the form of a thin-film, it is difficult to gather carriers in inversion mode so that accumulation and depletion modes

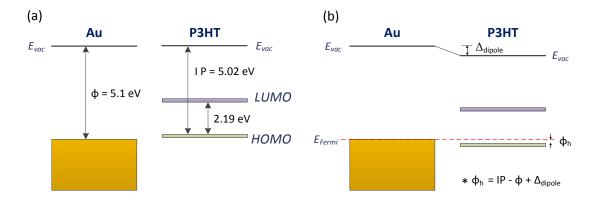

are utilized to create and remove a conducting channel between source and drain, respectively [4]. In order to transport carriers from source to drain, extra carriers should be injected from source and then flow through a conducting channel. The type of carrier can be determined from the relative location between the Fermi level of a metal used for source electrode and the molecular energy level of an organic semiconductor. When the Fermi level of the metal is near to the highest occupied molecular orbital (HOMO) level of the organic semiconductor, holes are easily injected to the organic semiconductor while electron injection seems unlikely. In a case that the Fermi level of the metal is near to the lowest unoccupied molecular orbital (LUMO) level of the organic semiconductor, electrons are carriers injected from source electrode. Figure 2 illustrates the energy level of a p-type OTFT in which gold (Au) is used for electrodes and poly (3-hexylthiophene-2,5-diyl) (P3HT) is used for organic semiconductor. As seen in the energy level, the Fermi level of gold is near to the HOMO level of P3HT. Therefore, holes are injected and then transported to drain electrode when the drain electrode is negatively biased compared to the grounded source electrode.

**Figure 2.** Schematic energy level diagram of gold and P3HT before (a) and after (b) contact. Hole-injection barrier  $(\varphi_h)$  is calculated from the ionization potential (IP) of P3HT, the work function  $(\varphi)$  of gold, and the interface dipole barrier  $(\Delta_{dipole})$ .

Unlike completely delocalized charge carriers in a crystalline material, charge carriers in an amorphous organic semiconductor are highly localized due to irregular lattice and defect sites. Charge transport in delocalized states is interrupted by thermally-induced lattice deformations that lead to carrier scattering. Therefore, the carrier mobility in crystalline materials tends to drop with increasing temperature. On the other hand, the charge carriers in most organic semiconductors move faster at a higher temperature. The different tendency can be rationalized through several models of charge transport in amorphous semiconductors. As the first model, hopping mechanism was introduced in 1960 [5]. In the model, the charge is assumed to hop from an occupied state to a nearest unoccupied state with the assist of phonons. The initial model was further expanded to variable-range hopping instead of the limited hopping to the nearest unoccupied state [6]. The charge transport is also explained in the multiple trapping and release (MTR) model [7]. In the MTR model, charge carriers transit through a narrow

delocalized band while their motion is interrupted by carrier trapping into the high concentration of localized states (traps). The trapped carriers are released through thermal activation. In the MTR model, the drift mobility( $\mu_D$ ) can be expressed by

$$\mu_D = \mu_0 \alpha \exp\left(-\frac{\Delta E_t}{kT}\right)$$

[Eq. 1]

where  $\mu_0$  is the mobility in the delocalized band,  $\alpha$  is the ratio of the density of states at the bottom of the delocalized band to the density of traps, and  $\Delta E_t$  is energy difference between the edge of the delocalized band and the trap level in a single trap level.

According to the type of injected carriers, OTFTs are classified into two types, p-type and n-type. However, n-type OTFTs have been rarely utilized due to their drastic atmospheric decay and electron mobility that is substantially lower than the hole mobility of p-type OTFTs. It was found that the low electron mobility was attributed to electrons trapped by hydroxyl groups at the interface of dielectric and organic semiconductor [8]. By adopting hydroxyl-free gate dielectrics, the electron mobility of 1.46 cm<sup>2</sup>/Vs was demonstrated from a n-type OTFT with a fullerene (C<sub>60</sub>) channel [9]. In spite of the improved mobility, the practical application of n-type OTFTs is still far-off because of their instability in ambient air. Although there were several reports of air-stable n-type OTFTs whose semiconductor channels had high electron affinities so that the channel hardly reacts with moisture and oxygen, their mobility was too low to operate as a functional device [10, 11]. In addition, electrodes of n-type OTFTs need to have low work function for efficient electron injection. But, the electrodes with low

work function are easily hydroxylated and oxidized. As a result, the electrodes change into insulating dielectrics and delaminate from the organic semiconductor so that their conductivity seriously drops. Due to the main issue of the air-stability, p-type OTFTs have been mostly used for commercial organic electronics whereas n-type OTFTs are still in the level of laboratory research items.

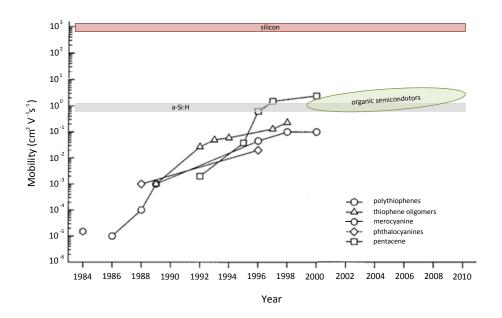

## 1.2 Organic semiconductors

Organic semiconductors are required to induce carrier mobility and current modulation (the ratio of I<sub>on</sub>/I<sub>off</sub>) high enough to function as a good active layer of OTFTs. Unlike strong covalent bonds in inorganic semiconductors, organic molecules are bonded by the weak Van der Waals force so that the weak inter-molecular coupling results in high effective mass [12]. In addition, their carrier movements are interrupted by scattering at crystalline grain boundaries and self-trapping. As a result, the best carrier mobility of an organic semiconductor is still three orders of magnitude lower than that of an inorganic semiconductor as shown in figure 3 [13, 14].

Figure 3. Carrier mobility of organic and inorganic semiconductors

Organic semiconductors are sorted into small molecules and conjugated polymers based on their sizes [15]. For example, pentacene belongs to the group of small molecules and P3HT is one of the conjugated polymers as shown in figure 4. According to the classified groups, they show different features that affect fabrication processes and electrical characteristics of OTFTs. As to thin-film preparation for an organic active layer, conjugated polymers can be deposited in a solution phase whereas small molecules are mostly processed in a gas phase. Unlike vapor deposition that requires high vacuum, solution-based processes such as printing and spin-coating techniques can be easily carried out at room temperature. In addition, the solution-based processes can be applied to large area at a very high speed. Consequently, polymer thin-films can be deposited at a low cost and with a high throughput compared to small molecule thin-films.

Figure 4. Classification of organic semiconductors

In spite of such advantages in a fabrication process, conjugated polymers in solution tend to form a thin-film with poorer electrical property. The reason can be found from the degree of crystallization of organic semiconductor. Conjugated polymers are mostly semi-crystalline with amorphous regions after deposition while small molecules can form organic crystals. Because ordered structure through crystallization facilitates

more rapid carrier movement in organic semiconductor, crystallized small molecules show much higher carrier mobility than conjugated polymer. For example, pentacene, one of commonly used small molecules, was already optimized to have the hole mobility of  $5.5 \text{ cm}^2/\text{Vs}$  that is higher than the carrier mobility of hydrogenated amorphous silicon ( $\mu$  of a-Si:H: ~ 1 cm<sup>2</sup>/Vs) [16]. On the other hand, the maximum carrier mobility of conjugated polymers still stays in the order of  $0.1 \text{ cm}^2/\text{Vs}$  [17].

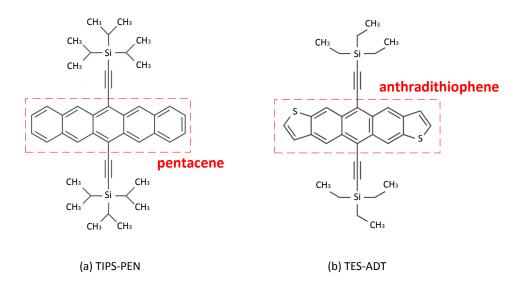

Despite of the high carrier mobility, small molecules are not preferred for a large-area application due to the expensive cost of vacuum deposition. Therefore, the solubility of organic semiconductors is indispensable for price competitiveness. One way to make small molecules soluble is to substitute some ends of the small molecules with soluble precursors [18]. This approach efficiently increases the solubility of small molecules at a cost of electronic property degradation that results from non-conductible precursors. Representative soluble small molecules are 6,13-bis(triisopropylsilylethynyl) pentacene (TIPS-PEN) and 5,11-bis(triethylsilylethynyl) anthradithiophene (TES-ADT) that are synthesized from pentacene and anthradithiophene by combining soluble precursors (figure 5). It was reported that the carrier mobilities of 1.0 cm<sup>2</sup>/Vs and 1.8 cm<sup>2</sup>/Vs were achieved in OTFTs using TES-ADT and TIPS-PEN, respectively [19, 20]. Although it is hard to avoid some extent of performance degradation, the soluble precursor technique deserves in-depth researches because soluble small molecules not only show relatively high mobility compared to conjugated polymers, but also enable a low-cost fabrication.

**Figure 5.** Molecular structures of soluble small molecules

In addition to developing efficient soluble small molecules, several notable efforts have been made for the purpose of maximizing the carrier mobility through single-crystals. Because single-crystals have highly ordered molecular structures and no crystal defect, it has been expected that the highest carrier mobility can be realized from single-crystalline OTFTs. However, many experiments in early stages did not achieve satisfactory results so that mobility in single-crystalline OTFTs were even lower than the highest mobility previously reported for the same materials [21-23]. Their poor performance mainly resulted from the bad interface of single-crystals rather than the single-crystal itself. Although it has been regarded as a hard task to make fragile and flat single-crystals consistently contact both insulator and source/drain electrodes, there has been continuous research to improve the interface condition. As a result, a carrier mobility of 19 cm<sup>2</sup>/Vs was realized from an OTFT with rubrene single-crystals [24].

#### 1.3 Gate dielectrics

Gate dielectric in OTFTs is another crucial component whose effects on device performance are much broader than in inorganic transistors [3, 25]. The effects of the gate dielectric can be comprehensively analyzed in terms of insulator material, surface roughness, polarity at interface with an organic semiconductor, and employed device configuration (bottom-gate type or top-gate type). As an inorganic dielectric material, silicon dioxide (SiO<sub>2</sub>) has been traditionally utilized. Given large numbers of defects and low carrier density in organic semiconductor active layers, however, the relative low dielectric constant of  $SiO_2$  (k = 3.9) cannot induce a sufficient amount of accumulated charges at a low-voltage bias. Consequently, the need of high-k insulators arose to realize the low-voltage operation of OTFTs. The first low-voltage operation was demonstrated from pentacene-based TFTs which used high-k insulators such as barium strontium titanate (BST, k = 16), barium zirconate titanate (BZT, k = 17.3), and silicon nitride (Si<sub>3</sub>N<sub>4</sub>, k = 6.2) [26]. The OTFTs exhibited mobility of higher than 0.3 cm<sup>2</sup>/Vs at the operation voltage of 5V. Although there were several controversial reports showing that carrier mobility decreased with increasing dielectric constant due to enhanced charge localization at higher polarity interface [27, 28], high-k insulators have been continuously researched as an effective way to reduce operating voltage [29, 30].

In addition to the dielectric constant, insulator surface state is another important parameter because it directly interacts with an organic semiconductor active layer. A rough surface leads to carrier traps at the insulator-semiconductor interface and it hinders the formation of a highly oriented organic semiconductor film. Consequently,

the interface roughness seriously degrades the available carrier mobility especially in bottom-gate type devices. The roughness can be effectively reduced by employing self-aligned monolayers (SAMs) such as hexamethyldisilazane (HMDS), octodecyltrichlorosilane (OTS), (tridecafluoro-1,1,2,2-tetrahydrooctyl) trichlorosilane (FTS) and phosphonic acid monolayers on the gate dielectric before depositing the organic semiconductor [31-33]. The SAMs can also chemically modify the dielectric surface so that it lowers surface-energy. As a result of the surface treatment, gate dielectric surface becomes smooth and passivated. The modified insulator surface enhances the molecular ordering of organic semiconductor and minimizes the carrier trap density at semiconductor-insulator interface. A polycrystalline pentacene TFT with a phosphonic acid-treated alumina dielectric even showed a mobility of ~ 3 cm²/Vs which is close to that of a single-crystalline device [33].

Unlike in bottom-gate type OTFTs, only limited deposition processes can be harnessed to form dielectric films in top-contact type OTFTs in which the dielectric deposition processes may seriously affect the electrical characteristics of susceptible organic semiconductor active layers. Hence, OTFTs have been mostly fabricated in the configuration of bottom-gate devices. Although there were attempts to deposit inorganic materials such as Ta<sub>2</sub>O<sub>5</sub> on organic semiconductor films through relatively safe electron-beam evaporation, it was also reported that high off-current occurred in the top-gate devices with the inorganic dielectrics [34]. The high off-current may be explained by oxygen doping during the evaporation process. In spite of the challenging gate dielectric deposition, top-gate configuration is still worth considering because mobility tends to be

several times higher in a top-gate structure than in a bottom-gate structure [34]. To easily and safely realize top-gate devices, solution-based processes such as printing or spin-coating have been considered. Therefore, most top-gate OTFTs have been fabricated with solution-processible organic materials as their gate dielectric instead of inorganics. In addition to the solution-processibility, organic materials are compatible with flexible devices. In spite of such advantages of organic insulators, OTFTs with organic gate dielectrics were less attractive to practical applications due to their high operating voltages that were required to compensate their quite low capacitors. However, their operating voltages have been recently improved through ultrathin organic insulator films that have been formed by self-aligned mono- or multiple-layers or 3D cross-linked multilayers [35-37]. While thin inorganic insulators typically suffers large leakage current, the ultrathin organic insulators show much better insulating property so that they are compatible with low-voltage operation devices.

#### 1.4 Fabrication and its limitations

Although there are several deep submicron lithography techniques such as optical lithography, electron beam (E-beam) lithography, and nanoimprint lithography in industry, those techniques have not been deployed on an organic semiconductor film due to strict conditions of OTFT fabrication. Because organic semiconductors are susceptible to ultra violet (UV) light and oxygen that critically degrade the performance of OTFT, the high-resolution lithography techniques - that normally use intensive UV light or oxygen plasma as their lithography resource - have not been applied to electrode

patterning on organic semiconductor. For instance, a device is exposed to intensive UV light during optical lithography. In case of E-beam lithography, it is a destructive lithography so that organic semiconductor film is destroyed during patterning. Organic semiconductor film is also damaged by an oxygen dry etching that is normally carried out after nanoimprint lithography.

In spite of the strict conditions of organic semiconductor fabrication, several research groups realized nanoscale OTFTs in the bottom-gate and bottom-contact structure. Because they deposited organic semiconductor active layer after forming all other elements of an OTFT that were patterned through high-resolution lithography techniques, organic semiconductor film was not damaged by UV or oxygen plasma. However, the nanoscale OTFTs did not show a significant performance improvement due to critical drawbacks of the bottom-contact structure such as high contact resistance and poor crystallization of organic semiconductor [38, 39]. Therefore, the bottom-contact type of OTFTs became less attractive to a commercial market. On the other hand, the top-contact type of OTFTs has been mostly fabricated through low-resolution lithography techniques that do not have a negative influence on the performance of OTFTs.

Direct evaporation through a shadow mask and various printings – inkjet printing, screen printing, stencil printing, gravure printing, micro-contact printing, and laser-transfer printing – have been commonly used to safely pattern electrodes on the organic active layer [40-42]. Because those techniques can be carried out at a low-temperature, even at room temperature, they can be freely applied to diverse substrates including

flexible or transparent materials. Besides, they show not only cost-effectiveness but also high throughputs owing to simple operations so that those techniques are suitable for large area applications. In spite of such attractive advantages, most of them have a resolution limitation that still stays at microscale as shown in figure 6. Although there is a possibility to form nanoscale metal patterns through a fine shadow masking [43], there are several insuperable obstacles in expending the possibility from a laboratory result to commercial mass products. For example, holes of the shadow mask are shrinking or disappear over multiple evaporations. Furthermore, the thin membrane of the shadow mask is easily bent so that it can cover only a restricted small area without the mask bending. Therefore, commercial OTFTs have been typically fabricated in microscale.

Figure 6. Throughputs and resolutions of commercial lithography techniques

## 1.5 Solutions towards a high performance OTFT

Low performance of OTFTs is mostly attributed to poor electrical characteristics of the organic semiconductor active layer, rough insulator, large overlap capacitance of conventional device structures, and low-resolution of available lithography techniques. There have been tremendous efforts to improve the electrical characteristic of organic semiconductor and insulator. As a result, the carrier mobility of amorphous silicon was already beaten by several organic semiconductors although average carrier mobility of crystalline inorganic semiconductors is still quite higher. On the other hand, there have been rare attempts to overcome the structural weakness and the resolution limitation although remarkable performance improvement was theoretically expected from the equation of cut-off frequency( $f_T$ ), which is one of the most important performance measures for OTFTs. The equation is written as:

$$f_T = \frac{g_m}{2\pi (C_G + C_{par})}$$

[Eq. 2]

where  $g_m \left( = \frac{W C_G}{L} \mu V_{DS} \right)$  is transconductance,  $C_G$  is gate capacitance, and  $C_{par}$  is overlap parasitic capacitance between source, drain, and gate. For example, the cut-off frequency of 800 MHz is expected when channel length is reduced to 0.1  $\mu$ m although the cut-off frequency of today's OTFTs is still slower than 1 MHz.

Among deep submicron lithography techniques, the nanoimprint lithography (NIL) technique has room to avoid negative factors on subtle organic active layer.

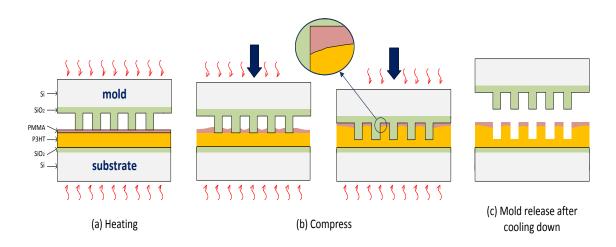

Nanoimprint is defined as a mechanical forming technique that physically molds a deformable material into a desired shape or pattern. There are two kinds of nanoimprint techniques. One is UV nanoimprint and the other is thermal nanoimprint. Like the optical lithography, UV nanoimprint involves intensive UV light. So it is not proper for OTFT patterning. However, thermal nanoimprint does not involve UV light. But, it is normally followed by oxygen dry etching to remove a residue layer. As shown in figure 7, the residue layer is formed as a by-product of nanoimprint process. Therefore, patterns can be complete only after removing the unwanted residue layer. If the residue layer is not formed during a thermal nanoimprint, the thermal nanoimprint is a possible solution to achieve deep submicron organic patterns. In addition to the high resolution, high throughput and low-cost process can be achieved by the thermal nanoimprint due to its quite simple operation mechanism.

**Figure 7.** A schematic for thermal nanoimprint lithography process

There is more room to improve the performance of OTFTs. It is impossible to get a self-aligned structure from the conventional configurations. In order to enable a self-

aligned OTFT, a concept of double-layer patterning is considered as shown in figure 8. Because thermal nanoimprint resist can be used as a dielectric and nanoimprint can deform organic semiconductor film as well as the resist, thermal nanoimprint is a good candidate for the double-layer patterning. If two polymers that are used as the resist and the organic semiconductor are not mixed during thermal nanoimprint, the thermal nanoimprint on the dual-polymer layer may form the double-layer patterns that will be used to achieve the self-aligned OTFT.

Figure 8. A self-aligned OTFT using double-layer pattern

In addition, the performance of OTFT can be improved through MESFET-like structure. The MESFET structure eliminates the overlap between source, drain, and gate as shown in figure 9. Furthermore, the structure tends to minimize the gap between source (or drain) and gate so that parasitic resistance existing between electrodes are reduced. Hence, the MESFET-like structure is an effective way to decrease parasitic resistance and capacitance. Based on the more complex equation of cut-off frequency [44],

$$f_T = \frac{g_m}{2\pi \left[ C_G \left( 1 + \frac{R_D + R_S}{R_{DS}} \right) + C_{GD} g_m (R_D + R_S) + C_{par} \right]}$$

[Eq. 3]

where source and drain resistances ( $R_S$ ,  $R_D$ ,  $R_{DS}$ ) and gate-drain capacitance ( $C_{GD}$ ) are additionally considered, higher cut-off frequency is expected from the reduced parasitic resistance and capacitance.

**Figure 9.** A small-signal equivalent circuit of a MESFET [44]

In addition, rectifying contact at gate efficiently replace a poor gate insulator that is considered as one of main performance degradation factors in OTFTs. In order to realize the MESFET-like structure without alignment errors, the application of the dual-layer thermal nanoimprint is expanded from two-dimension to three-dimension. As illustrated in figure 10, 3D resist pattern leads to 1<sup>st</sup> metal pattern with side-wing. The side-wing structure is utilized for self-aligned 2<sup>nd</sup> metal pattern.

Figure 10. An OMESFET fabricated based on 3D single-layer patterns

#### CHAPTER II

# DUAL-LAYER THERMAL NANOIMPRINT LITHOGRAPHY WITHOUT DRY ${\sf ETCHING}^*$

#### 2.1 Introduction

Nanoimprint lithography has been widely researched as one of the next generation lithography techniques since it was first demonstrated that it has nanoscale patterning capability [45, 46]. Nanoimprint is based on a direct mechanical molding of a deformable resist layer [47-49]. Therefore, it not only simplifies the lithography process, but also overcomes the resolution limitation that exists in photolithography due to light scattering. In addition, the nanoimprint resist can be a specific functional material that remains as an active component of a device instead of serving just as a mask layer for pattern transfer [50]. The mechanical deformation of a nanoimprint resist can provide sub-10 nm resolution at low cost [51, 52].

Despite its advantages, nanoimprint still needs development to satisfy strict industrial requirements for mass production such as high throughput, high yield, and process stability over multiple layers [50]. One of the challenges comes from the residual layer, which should be removed to complete pattern definition [53]. Therefore, an oxygen plasma dry etching after the thermal imprinting process is usually needed to remove the unwanted residual layer. However, dry etching renders nanoimprint

<sup>\*</sup>Reprinted with permission from "Dual-layer thermal nanoimprint lithography without dry etching" by Yunbum Jung and Xing Cheng, 2012. Journal of Micromechanics and Microengineering, 22(8), p 0805011-0805011-9, Copyright 2012 by IOP Publishing.

incompatible with soft functional materials such as organic semiconductors because the oxygen dry etching will degrade or even destroy those materials. There have been several studies to realize residue-free or negligible residual layer nanoimprinting and satisfactory results were achieved in both curable resists and polymer resists through incomplete mold cavity filling [54-56].

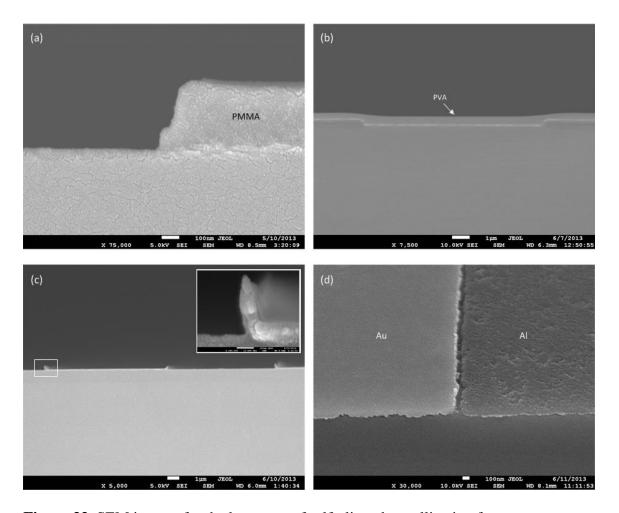

In order to accomplish residue-free nanoimprint on an organic semiconductor, we demonstrate in this paper an efficient thermal nanoimprint onto dual non-compatible polymer layers, poly (methyl methacrylate) (PMMA) on P3HT. These two polymers are non-compatible with each other and they do not mix even above their glass-transition temperatures (T<sub>g</sub> of PMMA: 105 °C [57] of and T<sub>g</sub> of P3HT: 45 °C [58]). Depending on thermal nanoimprint parameters such as polymer thickness, mold depth, and nanoimprint temperature, two distinct and useful patterns can be formed as schematically shown in figures 11 and 12. In figure 11, pattern is only formed in the PMMA layer and this case is referred to as single-layer patterning. In figure 12, pattern is formed in both PMMA and P3HT layers and this scenario is referred to as double-layer patterning. The key concern of the single-layer pattern imprinting is to remove the PMMA residual layer on the P3HT without damaging the P3HT layer. It is successfully achieved through a delicate resist volume control. In the case of double-layer patterning, the flatness of the interfacial boundary between the PMMA and the P3HT layers is crucial for applications such as self-aligned OTFT. A smooth interfacial boundary can be achieved by controlling mold geometry and polymer film thickness. The patterning technique described in this work eliminates the oxygen dry etching step in thermal nanoimprint.

This feature makes the patterning process highly compatible with organic functional materials such as conjugated semiconducting polymers. Both single- and double-layer patterns can find important applications in the fabrication of organic electronics.

**Figure 11.** A schematic for the dual-layer thermal nanoimprint lithography process shows single-layer patterning. Only the top PMMA layer is patterned, while the bottom P3HT layer is intact.

**Figure 12.** A schematic for the dual-layer thermal nanoimprint lithography process shows double-layer patterning. Both PMMA and P3HT layers are patterned.

#### 2.2 Experimental methods

#### 2.2.1 Adhesion improvement and dual polymer layer on SiO<sub>2</sub>

Because P3HT thin film has poor adhesion on an oxide substrate, adhesion improvement is required for fabrication processes. In order to improve the adhesion of the P3HT thin film, amino-functionalized alkylsilane monolayer (bis[3-(trimthoxysilyl) propyl]-ethylenediamine, Gelest Inc.) was coated on the oxide surface before spincoating the P3HT thin film [59]. The adhesion improvement was tested by visually observing the P3HT thin film in an ultrasound bath. While the P3HT thin film on a pure SiO<sub>2</sub> substrate started to peel off after 15 sec of sonication, the P3HT thin film on an aminosilane-coated substrate endured sonication for several minutes. The silane solution was prepared by adding 2 ml silane into methanol: distilled water (95ml: 5ml) that had been adjusted to pH = 5 with acetic acid. After 5 min for silanol formation, the wafer was dipped into the silane solution for 2 min and then it was rinsed in methanol. The wafer was cured at 110 °C for 10 min on a hotplate after drying methanol with nitrogen blowing. Afterwards, the adhesion-promoted oxidized silicon substrate was spin-coated with P3HT (highly regioregular, molecular weight: 20,000 ~ 40,000, Rieke Metals) and PMMA (molecular weight: 15,000, Sigma-Aldrich) consecutively. The P3HT solution and the PMMA solution were prepared by dissolving polymers in 1,2-dichlorobenzene and toluene, respectively. Various solution concentrations and spin-coating speeds were used for this study.

#### 2.2.2 Non-compatibility testing for PMMA and P3HT

Non-compatible characteristic between PMMA and P3HT is a prerequisite for dual-layer thermal nanoimprint because it prevents the intermixing of PMMA and P3HT during nanoimprint and enables PMMA to dewet on P3HT. In order to verify the non-compatibility, thermal tests were carried out on SiO<sub>2</sub> samples that had been spin-coated with a dual PMMA (110 nm) and P3HT (85 nm) film. The thermal tests were performed in such a way that each sample was simply heated up to an intended temperature and then it was immediately cooled down. In order to investigate how temperature affects the dewetting process, the thermal tests were done at two different temperatures (180 and 220 °C). After cooling down the samples, the dewetting behavior of the PMMA layer was observed through an optical microscope.

#### 2.2.3 Single-layer patterning

A silicon dioxide mold with 200 nm depth was prepared for imprinting. The mold was fabricated by photolithography and dry etching. The mold had 10 μm period grating with 45 % duty cycle (trench width: 5.5 μm and protrusion width: 4.5 μm).

1H,1H,2H,2H-perfluorodecyltrichlorosilane (FDTS, molecular weight: 581.56, Gelest Inc.) was coated over the mold for the purpose of anti-adhesion [60]. P3HT in 1,2-dichlorobenzene (10 mg/ml) was first spin-coated at 400 rpm for 5 min on the adhesion-promoted SiO<sub>2</sub> substrate to obtain 85 nm thick P3HT film. The P3HT-coated wafer was baked at 140 °C for 10 min in a vacuum oven. After the P3HT deposition, 3 wt. % PMMA in toluene was spin-coated on the P3HT layer at various spin-coating speeds

(3000, 3300, 3500, 4000, 5000 and 7000 rpm) for 1 min and then the wafer was baked at 90 °C for 5 min. Toluene can dissolve P3HT very slowly, so quick spin-coating of PMMA in toluene on P3HT surface had minimal observable effect on the P3HT layer. Moreover, PMMA and P3HT will become phase segregated during nanoimprint due to their non-compatibility and even some intermixing may occur at the layer interface during spin-coating. Nanoimprint was performed in a commercial hydraulic hot press (Specac) with heated aluminum (Al) plates. The mold was initially brought into contact with the dual-polymer film. Then the mold and substrate were heated to 180 °C and a pressure of 2500 psi was applied. While keeping the temperature and the pressure constant, the sample was annealed for 20 min. After the annealing time, the sample was cooled down to below their glass transition temperatures and then the mold was released from the patterned substrate. PMMA patterns and the P3HT layer were observed through both optical microscope and scanning electron microscope (SEM). In order to clearly verify whether a PMMA residual layer existed on the P3HT layer, gold was deposited on the patterned sample through a metal evaporator and then the sample was immersed in propylene glycol methyl ether acetate (PGMEA, molecular weight: 132.16, Sigma-Aldrich) to remove PMMA. PGMEA is a solvent that has no harmful impact on P3HT [61]. In order to promote the gold lift-off, ultrasound was applied to the sample in PGMEA for 30 sec. The lift-off result can be used to check if there exists a PMMA residual layer on top of P3HT after nanoimprint.

#### 2.2.4 Double-layer patterning

In order to imprint both P3HT and PMMA in double-layer patterning, a thick P3HT layer is preferred. Although a high P3HT concentration in 1,2-dichlorobenzene (50 mg/ml) increases the thickness of the P3HT layer, it results in a rough P3HT surface and a large film thickness non-uniformity. The rough P3HT surface is attributed to the semi-crystalline nature of P3HT [62]. As a way to get a smooth P3HT surface, a multiple spin-coating technique was adopted. Although the multiple spin-coating method reduced film thickness, it was effective in achieving a smooth surface. After P3HT in 1,2dichlorobenzene (50 mg/ml) was spin-coated on an adhesion-promoted SiO<sub>2</sub> substrate at 400 rpm for 5 min, P3HT in 1,2-dichlorobenzene (30 mg/ml) was spin-coated thrice and then P3HT in 1,2-dichlorobenzene (10 mg/ml) was spin-coated twice. Each additional P3HT spin-coating was done at 1000 rpm for 5 min. After each P3HT spin-coating, the sample was baked at 140 °C for 10 min in vacuum oven. After depositing the thick and smooth P3HT layer, 2.5 wt. % PMMA in toluene was spin-coated on the P3HT layer at 6000 rpm for 1 min and then the sample was baked at 90 °C for 5 min. Two SiO<sub>2</sub> molds were prepared to investigate the effect of mold geometry on the boundary interface between the PMMA and the P3HT layers. One had 10 µm period grating with 45 % duty cycle (trench width: 5.5 µm and protrusion width: 4.5 µm) and its depth was 400 nm. The other had 750 nm period grating with 47 % duty cycle (trench width: 400 nm and protrusion width: 350 nm) and the mold depth was 350 nm. Both molds were coated with FDTS. Each mold was used for a dual-layer thermal nanoimprint as described in figure 12. The imprint was also carried out at 180 °C and a pressure of 2500 psi with an

annealing time of 20 min. The dual-layer patterns and the boundary interface between P3HT and PMMA were investigated by SEM and optical microscope. To clearly visualize the P3HT structure under the PMMA patterns, each patterned sample was also observed after removing the top PMMA layer by dipping the samples in PGMEA.

#### 2.2.5 Temperature range for dual-layer thermal nanoimprint

PMMA is non-compatible with P3HT and a smooth interface between the two layers can be maintained during nanoimprint. However at very high temperatures, both polymers melt and their viscosities become much lower. Consequently inter-penetration of liquid domains occurs during nanoimprint and it leads to irregular interface between the two layers. In order to find the upper limit of temperature, dual-layer thermal nanoimprints were performed on 60 nm PMMA on 730 nm P3HT at various temperatures (220, 230, and 250 °C). For these nanoimprints, a mold with 400 nm depth and 10 µm period grating was used. After each nanoimprint, patterns were investigated by optical microscope. In order to identify the inter-penetration of liquid domains of PMMA and P3HT, each sample was observed again through the optical microscope after dipping in PGMEA, which only dissolved the top PMMA layer.

#### 2.3 Results and discussion

#### 2.3.1 Non-compatibility of PMMA and P3HT

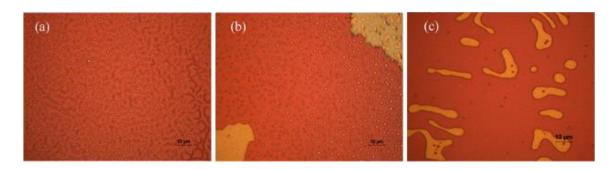

A thin PMMA film dewets on the P3HT layer at a high temperature because both polymers do not mix in a molten-state and the surface energy of the P3HT layer is low

[63]. As shown in figure 13, the dewetting starts with the ruptures of the PMMA film. As PMMA thin film dewets (figures 13(a) and (b)), bead- and worm-like PMMA ruptures (red color) occurs on P3HT surface (orange color). As the temperature increases, the dewetting quickly proceeds by expanding the ruptures and larger patches of PMMA are formed on P3HT surface (figure 13(c)). The fast dewetting progress is attributed to a lower viscosity of PMMA at a higher temperature. Since dewetting behavior is needed to achieve residual layer-free thermal nanoimprint [54], it is expected that PMMA melt can slip on P3HT surface and be squeezed into a mold cavity without leaving a residual layer on P3HT.

**Figure 13.** Optical microscope images of PMMA dewetting on P3HT at 180  $^{\circ}$ C ((a) and (b), including defects) and 220  $^{\circ}$ C (c). The orange-colored region is P3HT and the red-colored region is PMMA.

#### 2.3.2 Single-layer patterning without residual layer

Single-layer PMMA patterns without a residual layer on the P3HT layer are successfully achieved through nanoimprint only where 3 wt. % PMMA in toluene is spin-coated between 3300 rpm and 4000 rpm. Given the mold geometry, trench width: 5.5 µm, protrusion width: 4.5 µm and depth: 200 nm, 110 nm PMMA film thickness is

required to completely fill the mold cavity. Therefore, the result corresponds well with the measured PMMA film thickness (table 1). Although tiny dents that are resulted from incomplete filling exist on some PMMA patterns, they do not critically degrade the quality of the patterns as a lift-off mask. As shown in figure 14, no residual layer in the patterns is verified through a gold lift-off. Meanwhile, excessive or insufficient PMMA resist gives rise to a failure of gold patterning on top of P3HT. The residual layer due to excessive PMMA resist can be intuitively observed from the optical microscope image (figure 14(a)) that includes areas where some part of the residual layer peels off because of locally poor anti-adhesion of the mold. Furthermore, no gold pattern after the lift-off (figure 14(f)) proves the existence of the residual layer in PMMA patterns when PMMA is spin-coated at 3000 rpm. On the other hand, insufficient PMMA resist leads to incomplete filling of the mold cavity (figures 14(d) and (e)). In these cases, the lower P3HT layer is too thin to be deformed at the nanoimprint pressure, so the thin P3HT layer does not contribute to filling the mold cavity. Additionally, we found in our experiments that thin P3HT can only be imprinted at a temperature much higher than its glass transition temperature due to its high molecular weight and high viscosity. After gold lift-off, undesired gold patches between 5 µm gold lines are observed on the P3HT surface as seen in figures 14(i) and (j). In the cases when PMMA thickness is just enough to completely fill mold cavity, smooth PMMA patterns without residual layer are achieved in figures 14(b) and (c). Consequently, gold lift-off on those samples yields smooth and uniform gold lines on the P3HT surface (figures 14(g) and (h)). SEM micrographs verify these observations from optical microscope. In figure 15, wellformed PMMA patterns on top of the P3HT surface are shown under the optimal processing parameters. When PMMA is too thin to fill the mold cavity, voids in PMMA patterns are clearly seen in figure 16.

**Figure 14.** Optical microscope images of single-layer patterns (a, b, c, d, and e) and optical microscope images after their gold lift-off (f, g, h, i, and j) where 3 wt. % PMMA in toluene is spin-coated at 3000, 3300, 4000, 5000, and 7000 rpm, respectively. (a) The PMMA residual layer exists after nanoimprint, thus no gold pattern in (f). Notice that P3HT surface is not patterned by nanoimprint in (f); (b) and (c) have no PMMA residual layer after nanoimprint, and (g) and (h) show smooth 5 μm gold lines on top of P3HT after lift-off; in (d) and (e), PMMA is too thin to completely fill mold cavities, leading to defects in the form of voids in PMMA patterns. Gold lift-off in (i) and (j) shows gold patches in-between gold lines due to PMMA voids.

**Figure 15.** SEM images of the single PMMA layer patterns where 3 wt. % PMMA is spin-coated at 3500 rpm: (a) and (b) are the perspective views and (c) is the cross-sectional view.

**Figure 16.** An SEM image of voids in PMMA patterns due to incomplete filling of mold cavity by PMMA melt where 3 wt. % PMMA is spin-coated at 7000 rpm.

**Table 1.** PMMA film thickness at different spin-coating speeds

| spin-coating speed | PMMA film thickness (nm) |     |     |         |

|--------------------|--------------------------|-----|-----|---------|

| (rpm)              | measured data            |     |     | average |

| 1000               | 152                      | 153 | 154 | 153     |

| 2000               | 127                      | 129 | 134 | 130     |

| 3000               | 108                      | 111 | 113 | 110.7   |

| 4000               | 97                       | 101 | 102 | 100     |

| 5000               | 85                       | 86  | 88  | 86.3    |

| 7000               | 72                       | 73  | 75  | 73.3    |

The single-layer patterning can be utilized in organic semiconductor device fabrication. Due to material sensitivity, traditional photolithography and metal lift-off cannot be applied to conjugated polymers [64]. A direct metal deposition through a shadow mask has been commonly used to place metal pads on top of organic semiconductors. Recently, metal patterns in the nanoscale were realized through the approach [43]. However, the cost for such high-resolution shadow mask is high and this

approach cannot be applied to a large area because of the distortion of the vulnerable high-resolution shadow mask. Furthermore, the high-resolution apertures of the shadow mask may shrink or be blocked over multiple metal depositions. Nanoimprint is compatible to organic semiconductor because the patterning only requires heat and pressure. However, nanoimprint has not been used for patterning metal structures on top of organic semiconductors because it generally requires an oxygen dry-etching step to remove the residual layer before metal lift-off, which will seriously damage organic semiconductors. By eliminating the oxygen dry-etching step, the single-layer patterning makes it possible to pattern high-resolution metal pads on top of organic semiconductors for various types of organic electronic devices with improved performance.

## 2.3.3 Double-layer patterning