# DESIGN OF OPTICAL INTERCONNECT TRANSCEIVER CIRCUITS AND NETWORK-ON-CHIP ARCHITECTURES FOR INTER- AND INTRA-CHIP COMMUNICATION

A Dissertation

by

#### **CHENG LI**

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Samuel Palermo Committee Members, Paul V. Gratz

> Christi K. Madsen Duncan M. Walker

Head of Department, Head of Department

December 2013

Major Subject: Electrical Engineering

Copyright 2013 Cheng Li

#### **ABSTRACT**

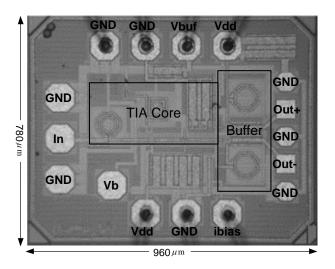

The rapid expansion in data communication due to the increased multimedia applications and cloud computing services necessitates improvements in optical transceiver circuitry power efficiency as these systems scale well past 10 Gb/s. In order to meet these requirements, a 26 GHz transimpedance amplifier (TIA) is presented in a 0.25- $\mu$ m SiGe BiCMOS technology. It employs a transformer-based regulated cascode (RGC) input stage which provides passive negative-feedback gain that enhances the effective transconductance of the TIA's input common-base transistor; reducing the input resistance and providing considerable bandwidth extension without significant noise degradation or power consumption. The TIA achieves a 53 dB $\Omega$  single-ended transimpedance gain with a 26 GHz bandwidth and 21.3 pA $\sqrt{Hz}$  average input-referred noise current spectral density. Total chip power including output buffering is 28.2 mW from a 2.5 V supply, with the core TIA consuming 8.2 mW, and the chip area including pads is 960  $\mu$ m × 780  $\mu$ m.

With the advance of photonic devices, optical interconnects becomes a promising technology to replace the conventional electrical channels for the high-bandwidth and power efficient inter/intra-chip interconnect. Second, a silicon photonic transceiver is presented for a silicon ring resonator-based optical interconnect architecture in a 1V standard 65nm CMOS technology. The transmitter circuits incorporate high-swing drivers with non-linear pre-emphasis and automatic bias-based tuning for resonance wavelength stabilization. An optical forwarded-clock adaptive inverter-based transimpedance amplifier (TIA) receiver trades-off power for varying link budgets by employing an on-die eye monitor and scaling the TIA supply for the required sensitivity. At 5Gb/s operation, the ring modulator under  $4V_{pp}$  driver achieves 12.7dB extinction ratio with 4.04mW power consumption, while

a 0.28nm tuning range is obtained at  $6.8\mu\text{W/GHz}$  efficiency with the bias-based tuning scheme implemented with the  $2V_{pp}$  transmitter. When tested with a wire-bonded 150f-F p-i-n photodetector, the receiver achieves -12.7dBm sensitivity at a BER= $10^{-15}$  and consumes 2.2mW at 8Gb/s.

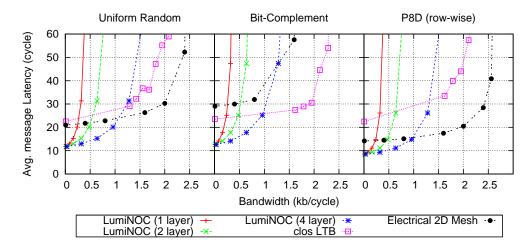

Third, a novel Nano-Photonic Network-on-Chip (NoC) architecture, called LumiNoC, is proposed for high performance and power-efficient interconnects for the chip-multiprocessors (CMPs). A 64-node LumiNoC under synthetic traffic enjoys 50% less latency at low loads versus other reported photonic NoCs, and ~25% less latency versus the electrical 2D mesh NoCs on realistic workloads. Under the same ideal throughput, LumiNoC achieves laser power reduction of 78%, and overall power reduction of 44% versus competing designs.

#### **ACKNOWLEDGEMENTS**

It has been my great fortunate to work with many wonderful people during my PhD study at Texas A&M University. First and foremost, my advisor, Prof. Samuel Palermo, has inspired me to this interesting and exciting field with his enthusiasm and guided me through my research work with his brightness thinking. I sincerely thank Prof. Paul V. Gratz, Prof. Christi K. Madsen and Prof. Duncan M. Walker for serving as my thesis committee. Your valuable suggestions and discussion are very important for my research. I would especially like to thank Prof. Paul V. Gratz for his guidance on my research on photonic network-on-chip project with his kindness, openness, brightness and patience.

My sincere gratitude also goes to my colleagues (Ehsan Zhian Tabasy, Geng Tang and Alex Titriku) for their collaboration. I will never forget those sleepless nights we spent together trying to catch the deadline of the chip tapeout. I am also thankful to my collaborators outside Texas A&M University. I performed the photonic transceiver test with Rui Bai from Oregon State University at HP Labs, and we exchanged the opinions and experience of circuit design. It is my great pleasure to work with Chin-Hui Chen and Marco Fiorentino from HP Laboratories. They provided tremendous support for the photonic device design and optical testbench set up.

Above all, my research would not be possible without the support from my family. This thesis is dedicated to my wife, who became a great mother of two kids during my PhD study, and my parents who have supported me unconditionally during their life. I feel sorry to my son Jonathan, since most of the time he needed me to be with him, I was staying in the lab for the research work. But Dad promises you we will enjoy more happy family time together, no matter how busy dad will be. My love is always with you.

# TABLE OF CONTENTS

|     |                                                | P                                                                                                        | Page                                                                 |

|-----|------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| ΑF  | BSTR.                                          | ACT                                                                                                      | ii                                                                   |

| AC  | CKNC                                           | WLEDGEMENTS                                                                                              | iv                                                                   |

| TA  | BLE                                            | OF CONTENTS                                                                                              | v                                                                    |

| LIS | ST OI                                          | FFIGURES                                                                                                 | vii                                                                  |

| LIS | ST OI                                          | FTABLES                                                                                                  | xii                                                                  |

| 1.  | INT                                            | RODUCTION                                                                                                | 1                                                                    |

| 2.  | BAC                                            | KGROUND                                                                                                  | 6                                                                    |

|     | 2.1                                            | Integrated Silicon Photonic Devices for Optical Interconnects                                            | 6<br>8<br>12<br>14                                                   |

| 3.  |                                                | IGN OF OPTICAL RECEIVER FRONT-END CIRCUITS FOR HIGH-<br>ED OPTICAL TRANSMISSION*                         | 15                                                                   |

| 4.  | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>SILI | High-Speed Transimpedance Amplifier Design Challenges and Potential Solutions                            | 17<br>18<br>18<br>20<br>21<br>22<br>22<br>26<br>33<br>36<br>44<br>45 |

| ᅻ.  | 4.1<br>4.2<br>4.3                              | Silicon Ring Resonator Based Photonic Interconnect Design Considerations Silicon Ring Resonator Modeling | 47<br>50<br>50                                                       |

|    | 4.4   | Non-Linear Pre-emphasis Modulator Driver Transmitter           |    |

|----|-------|----------------------------------------------------------------|----|

|    | 4.5   | Automatic Bias-based Wavelength Stabilization                  | 5  |

|    | 4.6   | Optical Forwarded-Clock Receiver                               |    |

|    | 4.7   | Experimental Results                                           | 6  |

|    | 4.8   | Summary                                                        | 4  |

| 5. | EXP   | LORATION OF PHOTONIC NETWORK-ON-CHIP ARCHITECTURES* 7          | 5  |

|    | 5.1   | Photonic Network-on-chip Technical Background                  | 7  |

|    | 5.2   | Related Work                                                   | 9  |

|    | 5.3   | Power Efficiency in Photonic Interconnect                      | 2  |

|    | 5.4   | LumiNOC Architecture                                           |    |

|    |       | 5.4.1 LumiNOC Subnet Design                                    | 8  |

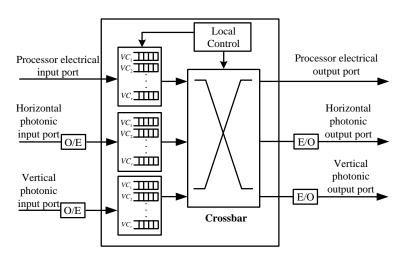

|    |       | 5.4.2 Router Microarchitecture                                 | 13 |

|    | 5.5   | Implementation                                                 | 14 |

|    |       | 5.5.1 Photonic Power Model                                     |    |

|    |       | 5.5.2 Power Comparison                                         | 19 |

|    | 5.6   | Evaluation                                                     | 1  |

|    |       | 5.6.1 Methodology                                              | 1  |

|    |       | 5.6.2 Synthetic Workload Results                               | )2 |

|    |       | 5.6.3 Realistic Workload Results                               | 13 |

|    |       | 5.6.4 Power Efficiency                                         | )4 |

|    |       | 5.6.5 Discussion                                               | )4 |

|    | 5.7   | Summary                                                        | 15 |

| 6. | PRO   | JECTION OF SILICON PHOTONICS INTEGRATION                       | 16 |

|    | 6.1   | Chip Area Estimation for 128-node PNoC                         | 16 |

|    | 6.2   | Silicon Ring Based Transceiver Energy Efficiency Projection 10 | 7  |

| 7. | CON   | ICLUSION                                                       | 2  |

| RF | EFERI | ENCES                                                          | 5  |

# LIST OF FIGURES

| FIGUR | E                                                                                                                                                                                            | Page  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.1   | A typical structure of optical transmission system                                                                                                                                           | 1     |

| 1.2   | Future chip multiprocessor (CMP) with 256 compute tiles utilizing a global interconnect network-on-chip (NoC)                                                                                | 3     |

| 2.1   | Compare of (a) quantum well laser; (b) quantum dot laser                                                                                                                                     | 6     |

| 2.2   | Normalized quantum dot comb laser spectrum with channel spacing of 43 GHz (left). A relative intensity noise plot from 100kHz to 10GHz for one channel (right). (Figure reproduced from [1]) | 7     |

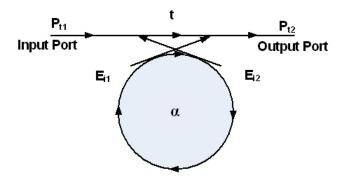

| 2.3   | Ring modualtor configuration                                                                                                                                                                 | 8     |

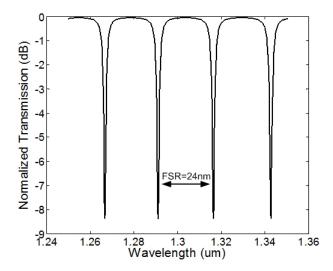

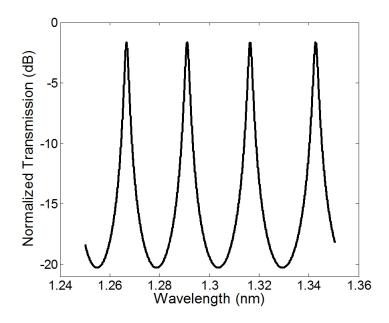

| 2.4   | Simulated transmission spectrum at ring resonator throughput port                                                                                                                            | 9     |

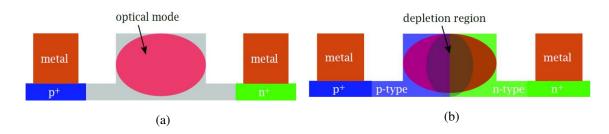

| 2.5   | Cross section view of silicon ring resonators: (a) carrier-injection mode; (b) depletion mode                                                                                                | 11    |

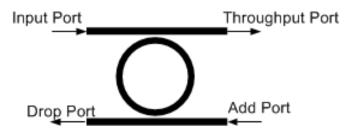

| 2.6   | Ring filter configuration                                                                                                                                                                    | 12    |

| 2.7   | Simulated optical spectrum at ring filter drop port                                                                                                                                          | 13    |

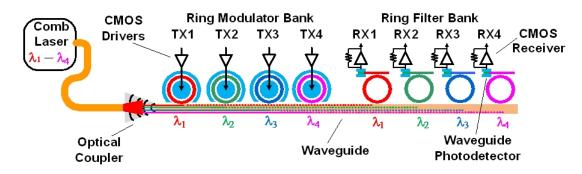

| 2.8   | Silicon ring resonator-based wavelength-division-multiplexing (WDM) link                                                                                                                     | s. 14 |

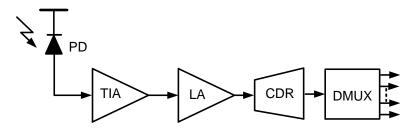

| 3.1   | Optical receiver system block diagram                                                                                                                                                        | 15    |

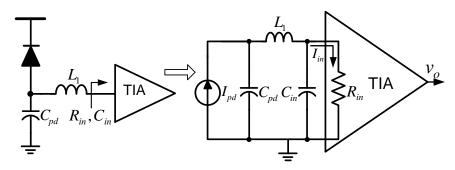

| 3.2   | Bandwidth enhancement by inserting a series inductor between the photo-diode and the TIA                                                                                                     | 18    |

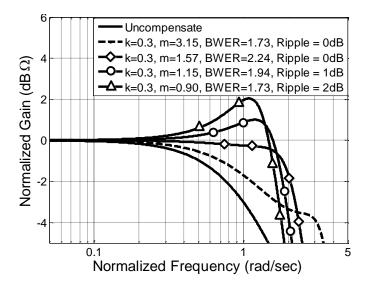

| 3.3   | Frequency response of inductive series peaking $\pi$ -network for various $m$ values ( $k$ =0.3)                                                                                             | 19    |

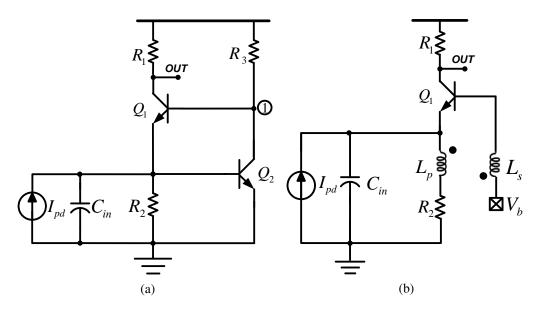

| 3.4   | Regulated cascode input stage: (a) conventional topology, (b) proposed transformer-based topology                                                                                            | 20    |

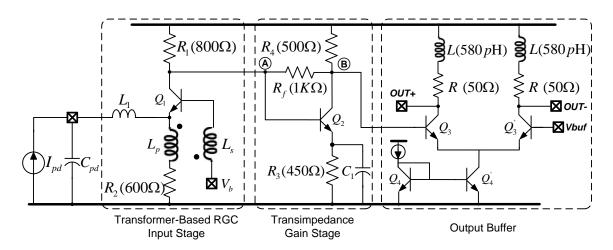

| 3.5   | Transformer-based RGC TIA schematic                                                                                                                                                          | 22    |

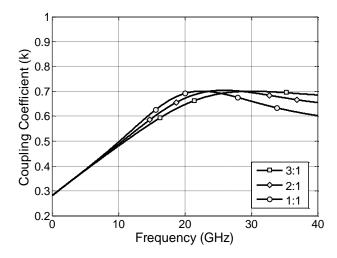

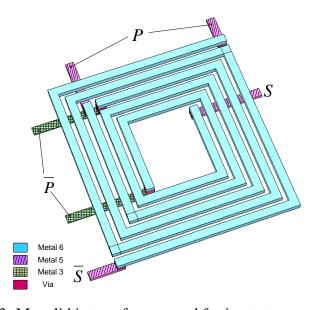

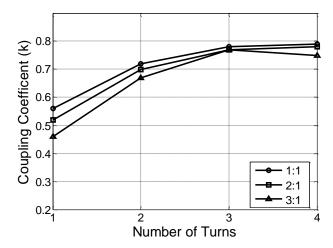

| 3.6   | Simulated 2.5-turn transformer coupling coefficient vs frequency with different turn ratios.                                                                                                 | 24    |

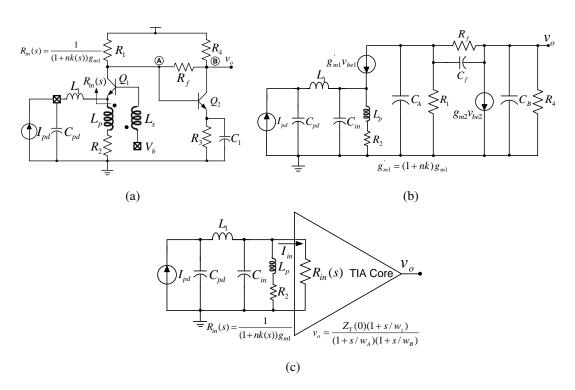

| 3.7  | (a) TIA schematic without the output buffer, (b) Equivalent small-signal model, (c) Equivalent analysis model                                                                                                                                               |    |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

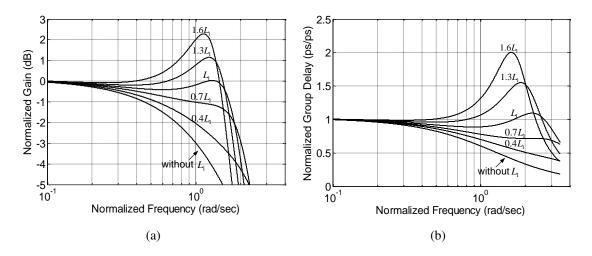

| 3.8  | Simulated TIA frequency response with various series inductance values: (a) normalized transimpedance gain, (b) group-delay of input $\pi$ -network. The frequency axis in both curves is normalized to the 3-dB bandwidth without series inductive peaking |    |  |  |

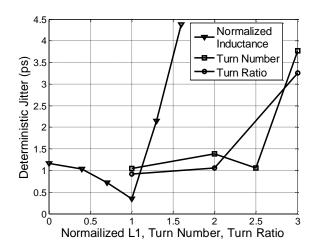

| 3.9  | Simulated 40 Gb/s deterministic jitter performance of the proposed TIA with a $2^{31}$ -1 pattern                                                                                                                                                           | 30 |  |  |

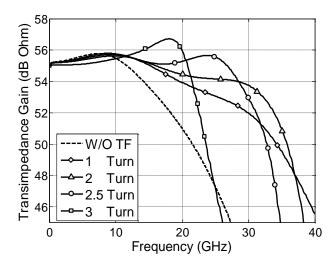

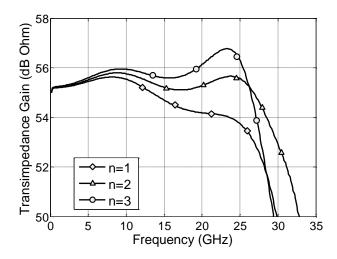

| 3.10 | Simulated transimpedance frequency response with different transformer turn number, transformer turn ratio is fixed at $n = 2, \dots, \dots$                                                                                                                | 31 |  |  |

| 3.11 | Simulated transimpedance frequency response with different transformer turn ratio, transformer turn number is fixed at 2.5                                                                                                                                  | 32 |  |  |

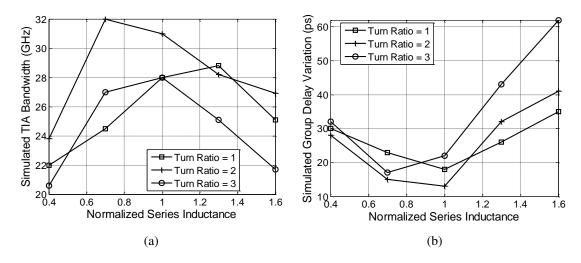

| 3.12 | Simulated TIA performance versus series inductance $L_1$ for different transformer turn ratios: (a) bandwidth, (b) group delay variation. Here the series inductance is normalized to the optimum value of 830 $pH$                                         | 32 |  |  |

| 3.13 | Monolithic transformer used for input stage $g_m$ -boosting                                                                                                                                                                                                 | 33 |  |  |

| 3.14 | Simulated transformer coupling coefficient at 20 GHz vs turn number with different turn ratios                                                                                                                                                              | 35 |  |  |

| 3.15 | Die photograph                                                                                                                                                                                                                                              | 36 |  |  |

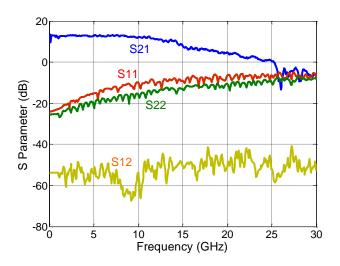

| 3.16 | Measured TIA single-ended S-parameters                                                                                                                                                                                                                      | 37 |  |  |

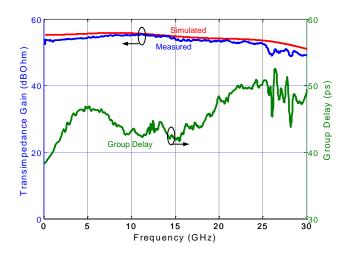

| 3.17 | Single-ended simulated/measured transimpedance gain and measured group delay.                                                                                                                                                                               | 38 |  |  |

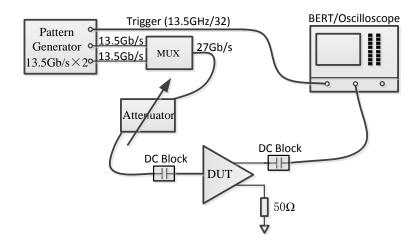

| 3.18 | Measurement setup for eye diagram and BER test                                                                                                                                                                                                              | 39 |  |  |

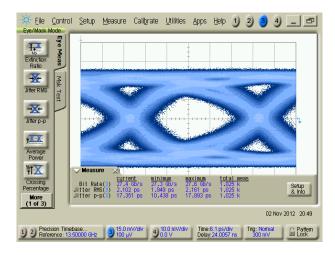

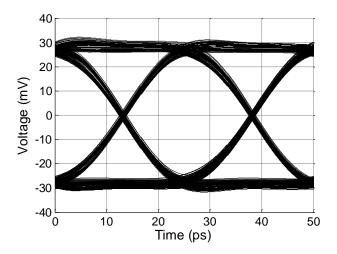

| 3.19 | Measured 27 Gb/s single-ended eye-diagram with a 125 $\mu A_{pp}$ $2^{15}$ -1 PRBS input signal                                                                                                                                                             | 40 |  |  |

| 3.20 | Post-layout simulated single-ended 40 Gb/s eye-diagram of the proposed TIA with 100 $\mu A_{pp}$ input current                                                                                                                                              | 40 |  |  |

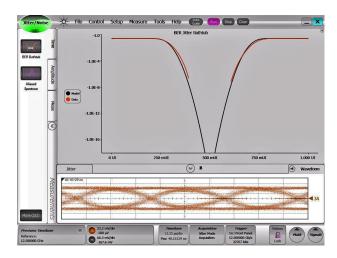

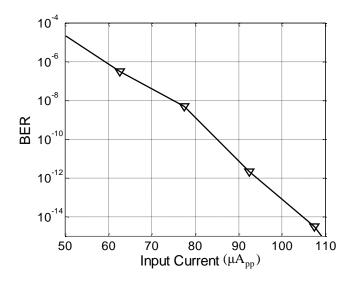

| 3.21 | BER jitter bathtub plot with 25 Gbps 150 $\mu A_{pp}$ PRBS $2^{15}$ -1 input                                                                                                                                                                                | 41 |  |  |

| 3.22 | Measured BER versus input current                                                                                                                                                                                                                           | 41 |  |  |

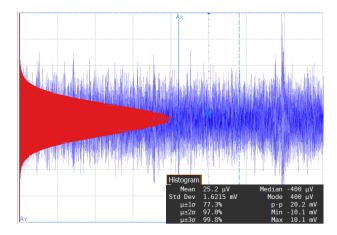

| 3.23 | Measured TIA single-ended integrated output noise                                                                                                                                                                                                           | 42 |  |  |

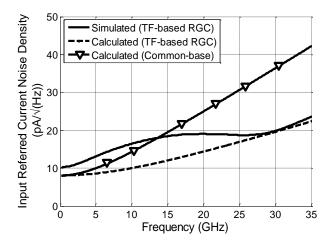

| 3.24 | Simulated and calculated input-referred current noise density for the proposed transformer-based RGC input-stage TIA and a simple common-base input-stage TIA                                                                       | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

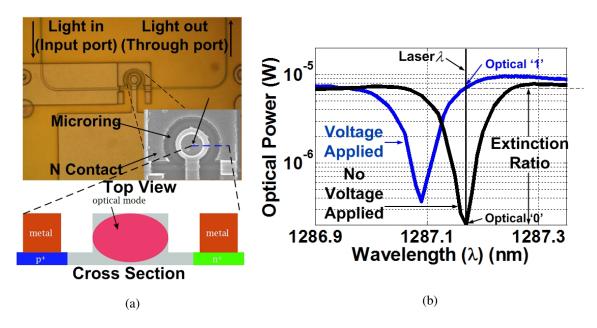

| 4.1  | (a) Top and cross section views of carrier-injection silicon ring resonator modulator, (b) optical spectrum at through port                                                                                                         | 47 |

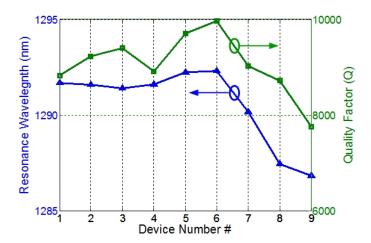

| 4.2  | Measured quality factor and resonance wavelength of nine $2.5\mu m$ radius silicon ring modulators fabricated on an 8" 130nm CMOS SOI wafer                                                                                         | 48 |

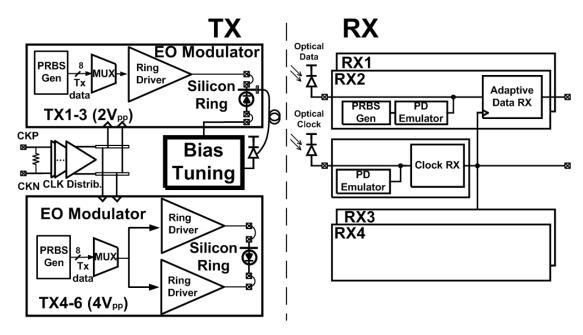

| 4.3  | Photonic transceiver circuits prototype block diagram                                                                                                                                                                               | 50 |

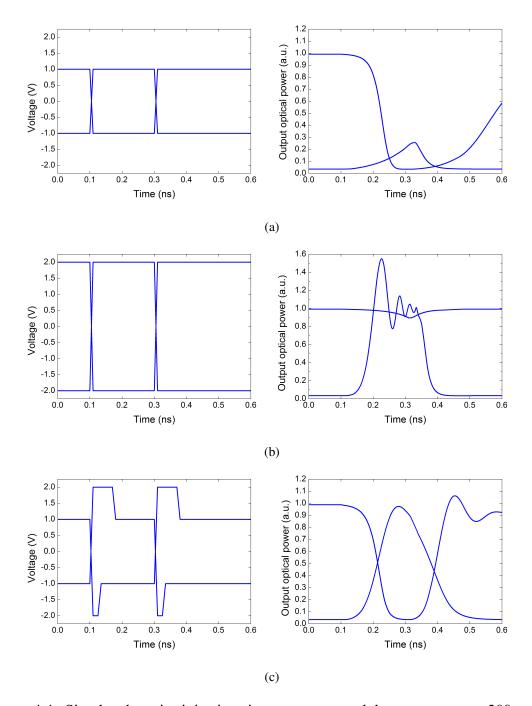

| 4.4  | Simulated carrier-injection ring resonator modulator response to 200ps data pulses with: (a) $2V_{pp}$ simple modulation, (b) $4V_{pp}$ simple modulation, , (c) $4V_{pp}$ modulation with pre-emphasis                             | 53 |

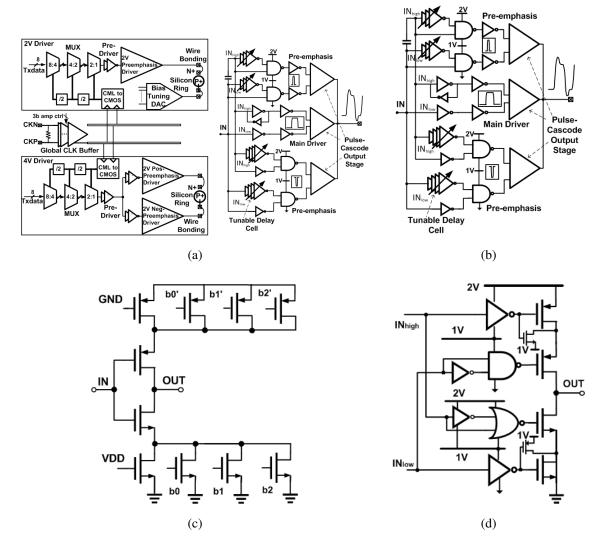

| 4.5  | Non-linear pre-emphasis modulator driver transmitters: (a) transmitter block diagrams, (b) per-terminal 2V pre-emphasis driver, (c) tunable delay cell, (d) pulsed-cascode output stage.                                            | 55 |

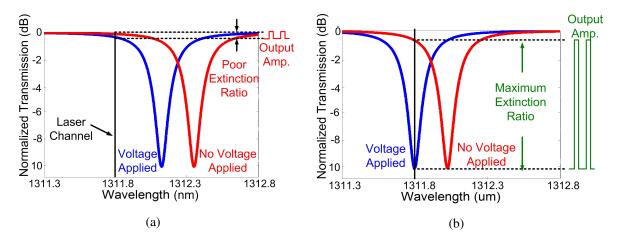

| 4.6  | Ring resonator modulator transmission curves with high and low modulation voltage levels when: (a) resonance wavelength is not aligned with input laser wavelength; (b) resonance wavelength is aligned with input laser wavelength | 56 |

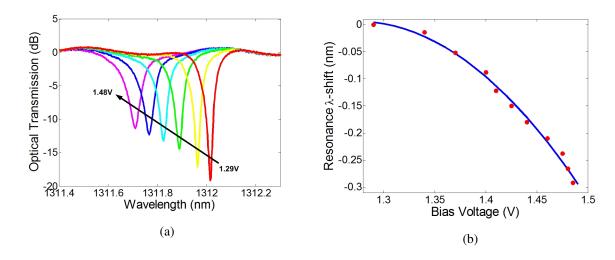

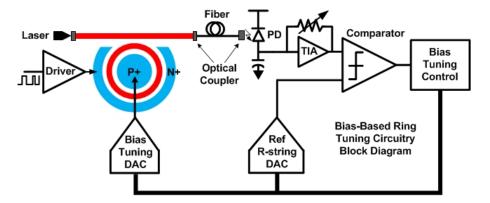

| 4.7  | Measured carrier-injection ring resonator modulator performance: (a) optical transmission spectrum at different bias levels; (b) resonance wavelength shift versus bias voltage                                                     | 57 |

| 4.8  | Bias-based ring resonator modulator semi-digital wavelength stabilization loop                                                                                                                                                      | 58 |

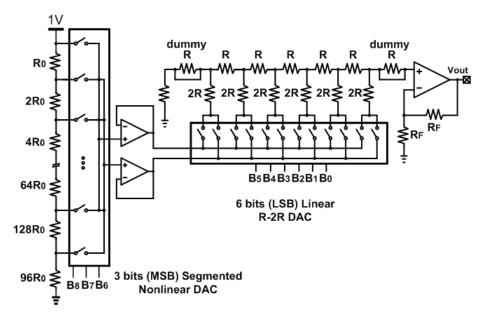

| 4.9  | 9-bit non-linear bias tuning DAC                                                                                                                                                                                                    | 59 |

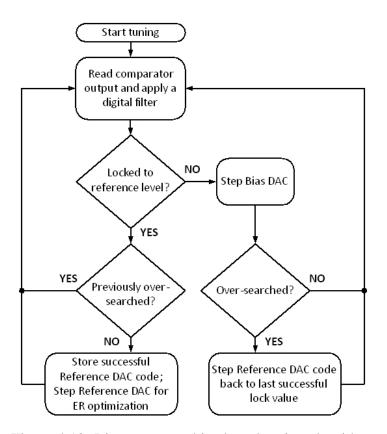

| 4.10 | Ring resonator bias-based tuning algorithm                                                                                                                                                                                          | 59 |

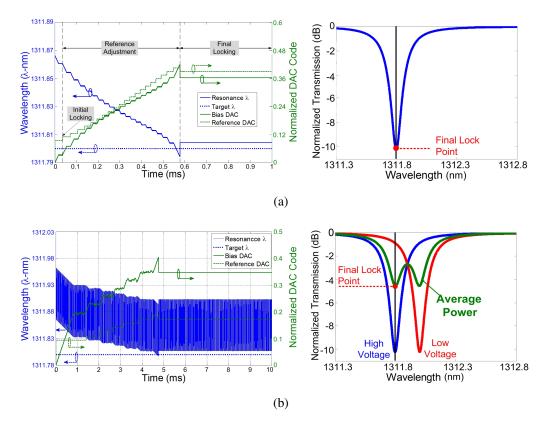

| 4.11 | Simulated tuning waveforms and final optical transmission curves for (a) static tuning mode, and (b) dynamic tuning mode                                                                                                            | 61 |

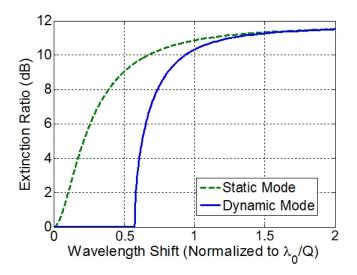

| 4.12 | Extinction ratio versus modulated wavelength shift for static and dynamic tuning modes                                                                                                                                              | 61 |

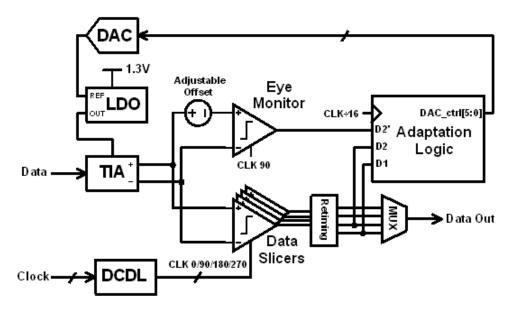

| 4.13 | Adaptive sensitivity-power data receiver                                                                                                                                                                                            | 62 |

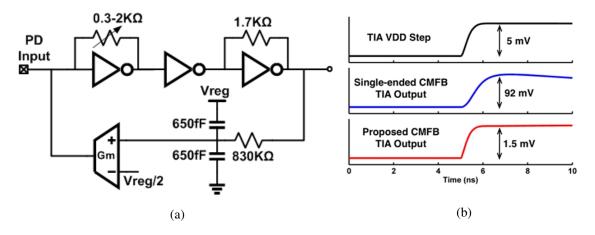

| 4.14 | Inverter-based TIA front-end: (a) schematic, (b) simulated TIA common-mode output response to a 5mV power supply step                                                                                                               | 64 |

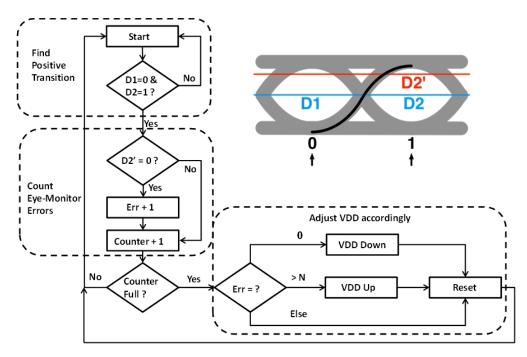

| 4.15 | Optical receiver sensitivity-power adaption algorithm                                                                                                                                                                                                        | 65 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

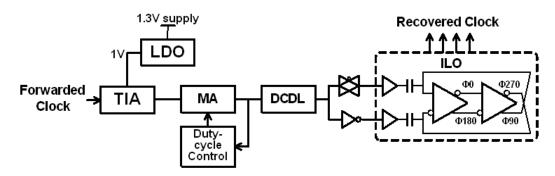

| 4.16 | Optical clock receiver.                                                                                                                                                                                                                                      | 65 |

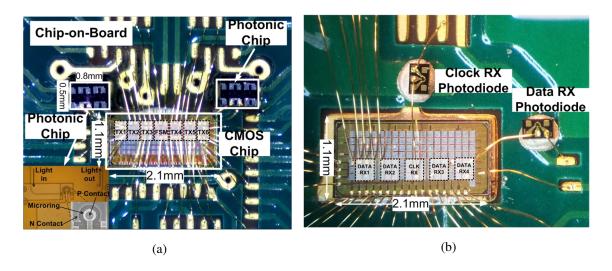

| 4.17 | Optical transceiver circuits prototype bonded for electrical characterization and optical testing. (a) Optical transmitter configuration with silicon ring resonator modulators. (b) Optical receiver configuration with commercial photodetectors.          | 66 |

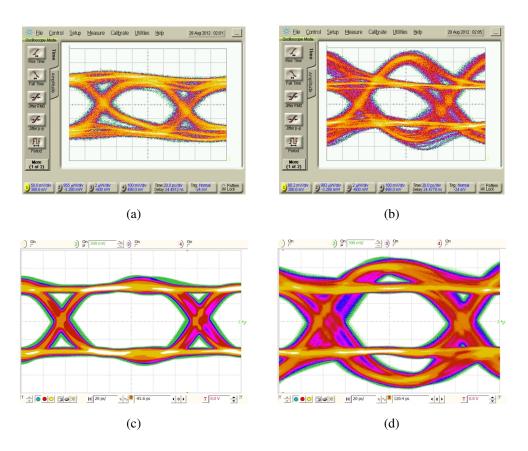

| 4.18 | Modulator drivers' electrical eye diagrams. 9Gb/s operation with $2V_{pp}$ driver with (a) minimum pre-emphasis, (b) maximum pre-emphasis. 8Gb/s operation with $4V_{pp}$ driver with (c) minimum pre-emphasis (d) maximum pre-emphasis                      | 67 |

| 4.19 | 5 Gb/s optical eye diagrams with silicon carrier-injection ring resonator modulators driven by the 4Vpp transmitter: (a) minimum pre-emphasis settings; (b) optimized pre-emphasis settings                                                                  | 68 |

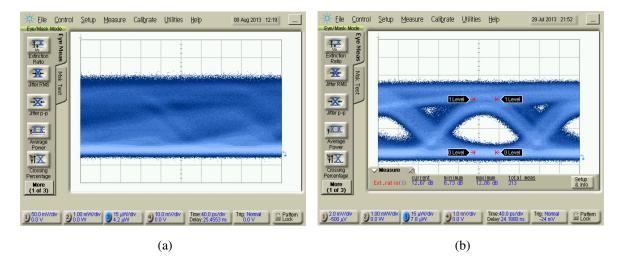

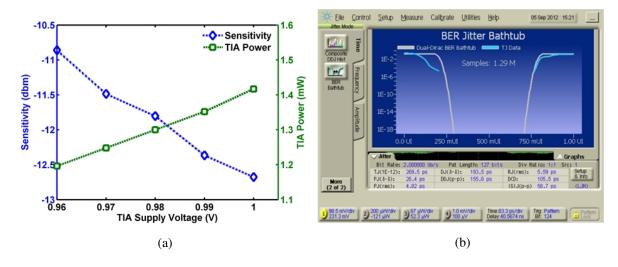

| 4.20 | Ring resonator bias-based wavelength stabilization measurements: (a) ring 1's 500Mb/s eye diagrams demonstrating the automatic bias tuning stabilizing to 1286.93nm, (b) ring 2's 800Mb/s eye diagrams with input laser wavelengths of 1311.86 and 1311.96nm | 69 |

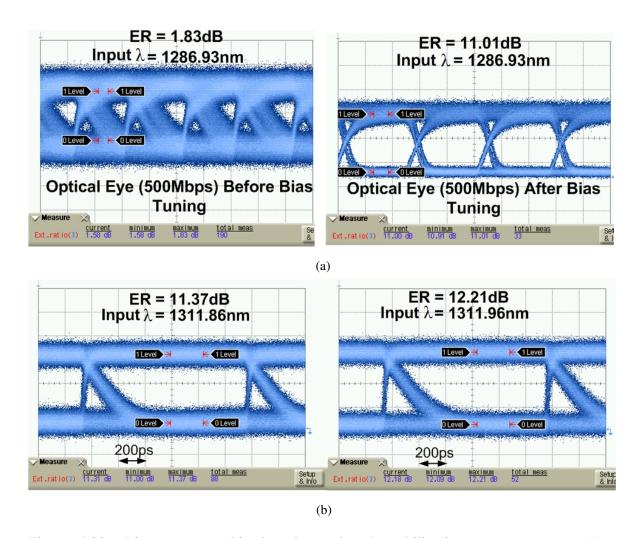

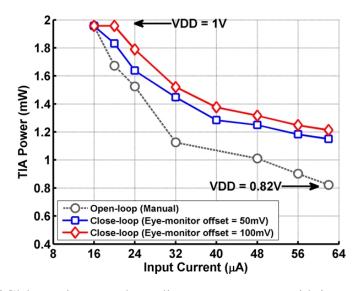

| 4.21 | 8Gb/s receiver supply scaling measurements: (a) sensitivity (BER=10 <sup>-</sup> 15) and power versus TIA supply voltage, (b) BER bathtub plot for a power supply of 0.96V                                                                                   | 70 |

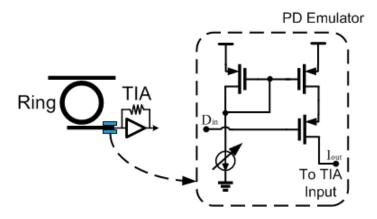

| 4.22 | Integrated photodetector emulator circuit                                                                                                                                                                                                                    | 71 |

| 4.23 | 10Gb/s receiver supply scaling measurements with integrated photodetector emulator                                                                                                                                                                           | 71 |

| 4.24 | Optically forwarded-clock receiver measurements: (a) 2GHz recovered clock waveform, (b) jitter versus input optical power                                                                                                                                    | 72 |

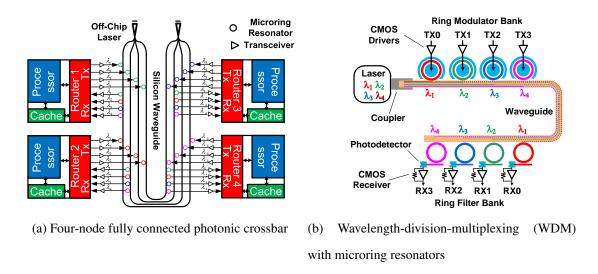

| 5.1  | Basics of photonic on-chip interconnect                                                                                                                                                                                                                      | 77 |

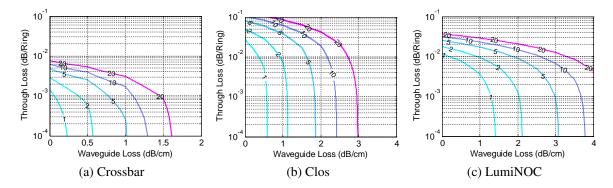

| 5.2  | Optical link budgets for the photonic data channels of various photonic NoCs                                                                                                                                                                                 | 84 |

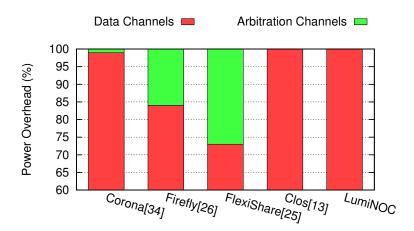

| 5.3  | Optical power overhead of arbitration channels in various photonic NoCs.                                                                                                                                                                                     | 85 |

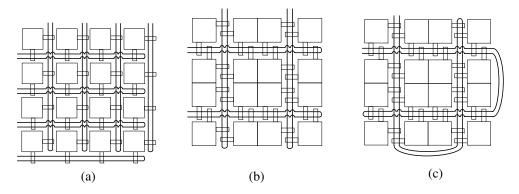

| 5.4  | LumiNOC interconnection of CMP with 16 tiles - (a) One-row interconnection, (b) Two-rows interconnection, (c) Four-rows interconnection                                                                                                                      | 86 |

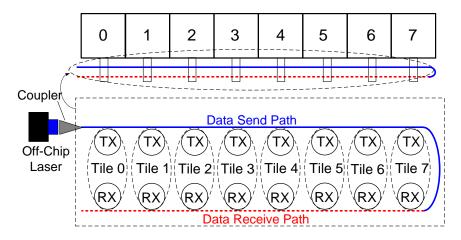

| 5.5  | Bold circles (TX and RX) represent groups of rings, and each pair in the oval are for a single node.                                                                                                                                                         | 89 |

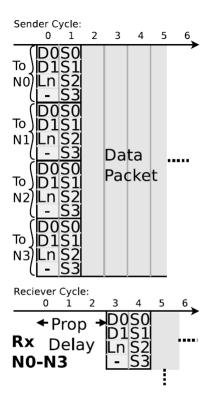

| 5.6  | Arbitration on 4 a node subnet                                                                                                                           | 92  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.7  | Router microarchitecture                                                                                                                                 | 93  |

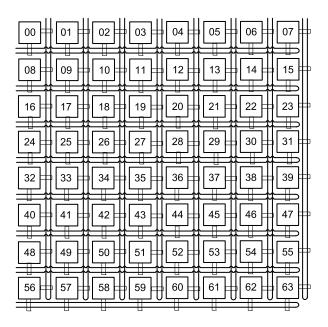

| 5.8  | One-row LumiNOC with 64 tiles                                                                                                                            | 94  |

| 5.9  | Electrical Laser Power (W) contour plots for networks with the same aggregate throughput (assuming 30% efficient electrical to optical power conversion) | 98  |

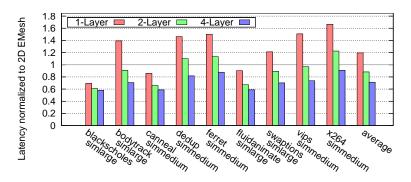

| 5.10 | Synthetic workloads showing LumiNOC vs. Clos LTBw and electrical network                                                                                 | 103 |

| 5.11 | Message Latency in PARSEC benchmarks for LumiNOC compared to electrical network                                                                          | 104 |

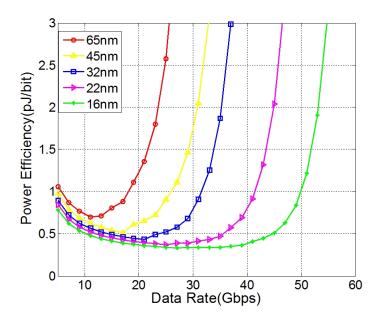

| 6.1  | Schematic of a single-stage inverter-based resistive shunt feedback CMOS TIA with a photodetector                                                        | 109 |

| 6.2  | Transceiver circuitry power efficiency vs. data rate under different CMOS technologies.                                                                  | 110 |

# LIST OF TABLES

| TABLE |                                                                                                                                                                                                                                                                                                                                  | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1   | Key parameters of the input-stage transformer                                                                                                                                                                                                                                                                                    | 23   |

| 3.2   | TIA performance comparisons                                                                                                                                                                                                                                                                                                      | 44   |

| 4.1   | Performance summary and comparisons                                                                                                                                                                                                                                                                                              | 73   |

| 5.1   | Components of optical loss                                                                                                                                                                                                                                                                                                       | 96   |

| 5.2   | Configuration comparison of various photonic NoC architectures - $N_{core}$ = number of cores in the CMP, $N_{node}$ = number of nodes in the NoC, $N_{rt}$ = total number of routers, $N_{wg}$ = total number of waveguides, $N_{wv}$ = total number of wavelengths, $N_{ring}$ = total number of rings, ITP = Ideal Throughput | 99   |

| 5.3   | Power efficiency comparison of different photonic NoC architectures - ELP = Electrical Laser Power, TTP = Thermal Tuning Power, ERP = Electrical Router Power, EO/OE = Electrical to optical/Optical to electrical conversion power, ITP = Ideal Throughput, TP = Total Power                                                    | 100  |

| 6.1   | Area of building blocks in silicon ring-based photonic transceiver                                                                                                                                                                                                                                                               | 107  |

| 6.2   | Technology roadmap for CMOS transistors                                                                                                                                                                                                                                                                                          | 108  |

| 6.3   | 128-node PNoC area estimation, via/pad area vs circuits area                                                                                                                                                                                                                                                                     | 108  |

#### INTRODUCTION

Bandwidth demands continue to scale up rapidly to meet the development of bandwidth-hungry multimedia applications and cloud computing services. There is an urgent need to maximize the capacity that can be transported by optical backbone networks in order to meet both business and residential customers' requirements, while as always at a cost-effective way (lower energy cost per bit). As a result, energy-efficient optical transceiver circuits are paramount for the high-speed long-haul and mid-range optical transmission system.

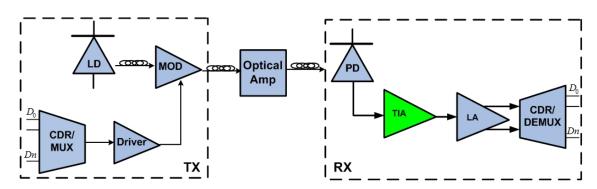

Figure 1.1: A typical structure of optical transmission system.

Fig. 1.1 illustrates a typical structure of optical transmission system. At the transmitter side, the laser source is modulated by the optical modulator driven by the electrical driver, and then the modulated optical signal is transmitted via single-mode fiber. Depending on the transmission distance, optical amplifiers might be inserted in certain span to compensate the optical signal loss in the transmission. At receiver side, a photodiode first converts the optical signal to electrical current. Then an optical receiver front-end circuits, transimpedance amplifier (TIA), converts and amplifiers the current to a voltage

signal, which is further amplified by the limiting amplifier to achieve a signal sufficient for the reliable operation of the subsequent clock and data recovery (CDR) circuits. In this dissertation, chapter 3 presents an optical receiver front-end TIA serving as a very import building block in the optical receiver system. As the optical pre-amplifier, TIA dominates the entire receiver's power, bandwidth, sensitivity and noise performance.

In addition, energy-efficient interconnects are paramount for next-generation high-performance networking and computing applications. However, conventional inter/intrachip electrical interconnects will not be able to increase their pin-bandwidths significantly due to channel-loss limitations. Signal attenuation, dispersion and cross-talk severely limit the reach of copper-based links beyond 10 Gb/s. While many have proposed techniques to overcome these limitations and extend the reach of copper, such techniques are usually complicated or have high power consumption requirements, and will not scale to higher data rates. Therefore, optical short reach interconnects are emerging as a replacement for the conventional electrical link as the inter-chip or even future intra-chip communication method. Chapter 4 describes a silicon photonic transceiver circuits for a ring resonator-based optical interconnect architecture, providing the potential for silicon photonic links that can deliver distance-independent connectivity whose pin-bandwidth scales with the degree of wavelength-division multiplexing.

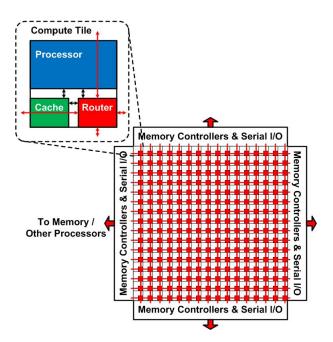

Figure 1.2: Future chip multiprocessor (CMP) with 256 compute tiles utilizing a global interconnect network-on-chip (NoC).

The amount of data communicated between cores and off-chip to memory or other processors also scales as the number of cores increases in future many-core systems shown in Fig. 1.2. Projections based on data from the International Technology Roadmap for Semi-conductors (ITRS) [2] shows that greater than tera-byte aggregate bandwidth is required for the future many-core chip-multiprocessors (CMPs). This explosion in both intra- and inter-chip bandwidth requires interconnect systems to achieve very high energy efficiency in order to comply with power budgets that have plateaued near 100W due to thermal constraints. However, the electrical channel limitations is even more obvious for the on-chip wires. Serious challenges exist in achieving projected communication bandwidth over electrical channels while still satisfying I/O power and density constraints due to high-frequency loss of electrical traces, reflections caused from impedance discontinuities, and crosstalk from adjacent signals. While advanced signaling and circuit techniques, such

as equalization [3], capacitive drivers [4], and RF-interconnects [5], can be leveraged to extend on-chip wire bandwidth, the significant power costs incurred with this additional complexity is prohibitive for future compute systems. The efficiency of current stateof-the-art Network-on-chip (NoCs) with simple CMOS inverter-based repeaters is near 2pJ/bit [6], allowing for only near 1TB/s throughput with a typical 20% allowance from the total 100W processor power budget. Monolithic silicon photonics, which offers highspeed photonic devices, THz-bandwidth waveguides and immense bandwidth-density via wavelength-division-multiplexing (WDM) [7–12], provides architectures suitable to efficiently scale to meet future many-core systems' bandwidth demands. Typical optical channels, including glass fibers and on-chip waveguides display signal loss characteristics which varies only fractions of dBs over wide wavelength ranges (tens of nanometers), allowing for data transmission of several Tb/s without the requirement of channel equalization. This simplifies design of optical links in a manner similar to non-channel limited electrical links. Another important feature of optical interconnects is the ability to combine multiple data channels on a single waveguide via wavelength-division-multiplexing (WDM) and greatly improve bandwidth density.

Due to the benefits of silicon photonics, recently photonic NoCs (PNoCs) have emerged as a potential replacement for electrical NoCs. Much of the current research in PNoCs focuses on leveraging the high bandwidth of photonic interconnect. Some designs propose using electrical interconnect to coordinate and arbitrate a shared photonic medium, effectively trading increased latency for higher bandwidth. While increased bandwidth without regard for latency is useful for some applications, it eschews the primary benefit of PNoCs over electrical NoCs for CMPs, low latency. Other recent photonic NoC proposals attempt to address the latency of arbitration. In particular, several groups have proposed crossbar or Clos topologies to improve the latency of multi-core photonic interconnect arbitration. While these designs do provide low latency and high bandwidth, it

comes at a high cost in terms of bandwidth per Watt of static power due to the need to significantly over-provision the network to achieve low latency. There is a clear need for a PNoC architecture that is energy-efficient and scalable while maintaining the goals of low latency and high bandwidth. In chapter 5, a novel photonic NoC architecture, called LumiNOC, is proposed to address the issues of power and resource overhead due to channel over-provisioning, while reducing latency and maintaining high bandwidth.

This dissertation is organized as below. Chapter 2 describes the background of integrated silicon photonics. A TIA design which employing a novel transconductance boosting and series inductive peaking to efficiently obtain significant bandwidth extension and low-noise performance is discussed in Chapter 3. Chapter 4 presents a silicon photonic transceiver circuits for a ring resonator-based optical interconnect architecture that address limited modulator bandwidth, variations in ring resonator resonance wavelength and link budget, and efficient receiver clocking. Moving to the architecture level, Chapter 5 discusses a novel photonic NoC (LumiNOC) architecture to address the issues of power and resource overhead due to channel over-provisioning, while reducing latency and maintaining high bandwidth. Chapter 6 projects the 128-node PNoC area cost and link power efficiency under different CMOS technologies. Finally, Chapter 7 concludes the thesis.

#### 2. BACKGROUND

This chapter gives an overview of the silicon photopic components for energy-efficient and compact-size intra/inter-chip interconnects. The theory of ring resonator is discussed and two types of silicon ring resonator, carrier-injection ring and depletion ring, are also compared. This section ends with an introduction of a silicon ring resonator based wavelength-division-multiplexing (WDM) link as a potential alternative of the electrical channel for future high-speed, power-efficient interconnects.

#### 2.1 Integrated Silicon Photonic Devices for Optical Interconnects

#### 2.1.1 Laser Sources

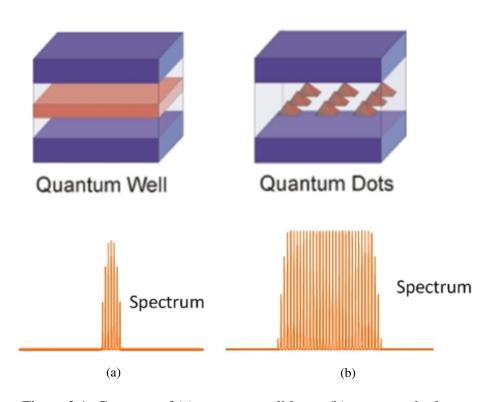

Figure 2.1: Compare of (a) quantum well laser; (b) quantum dot laser.

An impediment to adopt high density WDM for short reach optical interconnects is that each WDM wavelength currently requires its own expensive DFB laser [13]. The alternative is to use a power and area efficient broad-spectrum light emitter replacing the gang of DFB lasers. Comb laser [1] is developed to meet the short range optical interconnect requirement. The comb laser injects multiple wavelengths at 1310nm wavelength range to the silicon waveguide via the optical grating coupler. Unlike the conventional laser sources (Fig. 2.1a), which are composed of multiple quantum wells, the comb laser uses quantum dots (Fig. 2.1b) and generates multiple wavelengths simultaneously. Instead of using fewer wavelength with each modulated at very high speed (e.g. using multiple DFB laser sources), which dramatically increases the power at electrical side, comb laser uses more wavelengths with each modulated at lower data rate to achieve the same aggregate bandwidth, however, at much better overall power efficiency. Typically, a comb laser can generate 16-64 effective wavelengths with optical power of 0.2-1mW on each channel, as shown in Fig. 2.2. Channel spacing is in the range of 50GHz to 100GHz.

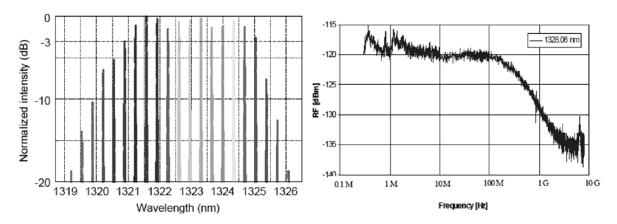

Figure 2.2: Normalized quantum dot comb laser spectrum with channel spacing of 43 GHz (left). A relative intensity noise plot from 100kHz to 10GHz for one channel (right). (Figure reproduced from [1]).

#### 2.1.2 Optical Modulators

Silicon Ring Resonator: Silicon ring resonator is a potential candidate to enable the platform for large-scale monolithic integration of optics and microelectronics. It can be configured either as an optical modulator or a WDM drop filter. Silicon ring resonator modulators/filters offer advantages of small size, relative to Mach-Zehnder modulators [14, 15], and increased filter functionality, relative to electro-absorption modulators [16]. Silicon photonic links based on ring resonator devices provide a unique opportunity to deliver distance-independent connectivity whose pin-bandwidth scales with the degree of wavelength-division multiplexing.

Figure 2.3: Ring modualtor configuration.

A basic silicon ring resonator consists of a straight waveguide unidirectional coupled with a circular waveguide, as shown in Fig. 2.3. When an optical input signal with power  $P_{t1}$  is launched into the input port (left side) of the waveguide, its intensity is split into an output signal at through port (right side) and a feedback signal which is either coupled to the through port of the waveguide or trapped inside the ring. With the input power normalized to unity, the transmission power  $P_{t2}$  at throughput port can be obtained by the following equation 2.1:

$$P_{t2} = \frac{a^2 + |t|^2 - 2a|t|\cos(\theta + \phi_t)}{1 + a^2|t|^2 - 2a|t|\cos(\theta + \phi_t)},$$

(2.1)

where |t| represents the coupling losses,  $\phi_t$  is the phase of the coupler and  $\alpha$  is the loss coefficient of the ring. In the equation,  $\theta = 4\pi^2 n_{eff} \frac{r}{\lambda}$ , where  $n_{eff}$  is the effective refractive index and  $\lambda$  is the optical wavelength. At the resonance, most energy will be trapped in the ring resonator due to the destructive interference within the ring. Fig. 2.4 shows the normalized output power at ring modulator throughput port as a function of the wavelength. The spectrum displays a notch-shaped characteristic at periodic resonance wavelengths, repeating over a free spectral range (FSR) defined as equation 2.2.

$$FSR = \frac{\lambda^2}{n_{eff}L},\tag{2.2}$$

where  $n_{eff}$  is the effective refractive index of the ring waveguide, and L is the circumference of the ring device. Because FSR is inversely proportional to the size of the ring resonator, the ring must be small in order to achieve a high FSR.

Figure 2.4: Simulated transmission spectrum at ring resonator throughput port.

The full width and half maximum (FWHM) of the ring device can be written as equation 2.3, with k represents the normalized coupling coefficient of the coupler between the straight waveguide and circular waveguide of the ring device.

$$FWHM = \frac{k^2 \lambda^2}{\pi * L * n_{eff}},\tag{2.3}$$

The quality factor (Q) is another key specification of the ring resonator, which is a measure of the sharpness of the resonance. It is defined as the ratio of the operation wavelength and the resonance width, shown in equation 2.4. A typical silicon ring resonator can achieve a relatively large Q of 8000 [17].

$$Q = \pi \frac{n_{eff}L}{\lambda} \frac{t}{1 - t^2},\tag{2.4}$$

Fig. 2.5 shows the cross section view of two types of silicon ring resonator modulators. The p-i-n junction-based carrier-injection devices [11, 17], shown in Fig. 2.5a, operate primarily in forward-bias. The waveguide region defining the optical mode is confined within the intrinsic region to avoid optical absorption losses in the heavily doped p-type and n-type regions. When the junction is forward-biased, carriers can be injected into the intrinsic region, where the refractive index is also changed. Modulation based on carrier-injection ring generally can achieve large extinction ratio. However, the modulation speed is generally limited due to the long minority carrier lifetime (~1ns) of the p-i-n junction. This limitation can be partially mitigated by using modulation equalization technic [11]. The carrier-depletion devices [18], shown in Fig. 2.5b, operate primarily in reverse-bias. The waveguide in depletion device is lightly doped, resulting a p-n diode can be operated in reverse-bias to deplete carriers from a central region [19]. Although a depletion ring generally achieves higher modulation speeds relative to a carrier-injection ring due

to the ability to rapidly change the depletion width, its modulation depth is limited due to the relatively low doping concentration in the waveguide to avoid excessive loss. In contrast, carrier-injection ring modulators can provide large refractive index changes and high modulation depths, but are limited by long minority carrier lifetimes.

Figure 2.5: Cross section view of silicon ring resonators: (a) carrier-injection mode; (b) depletion mode.

However, a major barriers to widespread adoption of ring-based silicon photonics is the non-uniformity in the fabrication at both the die and wafer scales [20]. For example, the resonance wavelengths of silicon ring resonators depend on the device dimensions, effective refractive index and etch depths across a wafer. Due to the fabrication variation, identical rings at different locations in the wafer can cause significant variation in their passband wavelengths. it is very difficult to fabricate ring resonated at the exactly required wavelength under current silicon-on-insulator (SOI) process. In addition, silicon ring resonator performance is also sensitive to the temperature variation, which causes the resonance wavelength drifts and degrades the modulation extinction ratio. Therefore tunability is essential for the piratical application of ring modulator. Two methods are commonly used for tuning the resonance wavelength when the ring modulator is in operation, which are the thermo-optic tuning and electro-optic tuning. Thermo-optic tuning is implemented by implanting a heater nearby the ring waveguide to heat the entire device.

The heat changes the refractive index of the material which in turn shifts the resonances towards the larger wavelength. It should be noted that the thermo-optic tuning process is fairly slow (~ms) and significant power is needed to maintain the tuned status. However it is suitable for the case where large refractive index change is required. Another tuning method is electro-optic tuning. An electric field is applied over the ring to change carrier density in the waveguide, leading to the refractive index change. The tuning range is relatively small compared to the thermal tuning method [8], but it has the advantage of fast tuning speed and better tuning efficiency.

#### 2.1.3 Optical Drop Filter and Waveguide Photodetector

Ring Drop Filter: Silicon ring resonator can also be configured as the optical filter by adding an additional straight waveguide functioning as add-drop port, as shown in Fig. 2.6. The four ports of the ring resonator are referred as input port, throughput port, drop port and add port. The simulated optical spectrum at ring filter drop port is shown in Fig. 2.7. The resonance peaks at periodic resonance wavelengths also repeat over a free spectral range (FSR). The modulated signal can be filtered out by aligning the resonance peak with the carrier wavelength.

Figure 2.6: Ring filter configuration.

Figure 2.7: Simulated optical spectrum at ring filter drop port.

Waveguide Photodetector: Photodetector absorbs incident light, and then creates accumulated charge carriers that can be measured by electronic circuits. Conventional lateral p-i-n photodetector is not suitable for the integrated photonics applications due to the large area required to improve the photo-response. Recently, significant research in silicon photonics has been focused on realizing individual components of photonic integrated circuits. However, silicon is transparent to the standard telecommunication wavelengths used for short-range photonic interconnects, and therefore cannot be used as an active element of a photodetector. In recent years the epitaxial integration of germanium with silicon waveguides has led to several device structures that are promising for high-bandwidth interconnects. For example, a germanium waveguide photodetector has been demonstrated using selective growth on a siliconon-insulator platform [21, 22], and a SiGe waveguide photodetector has been developed to reduce the lattice mismatch experienced by Ge photodetectors [23]. However, their dark current densities are typically higher than conventional

III-V photodetectors primarily due to dislocations from the growth on a silicon substrate. In addition, their absorption is typically lower at wavelengths beyond 1550nm, leading to lower responsivity at longer wavelengths.

#### 2.2 Silicon Ring Resonator Based Photonic Interconnects

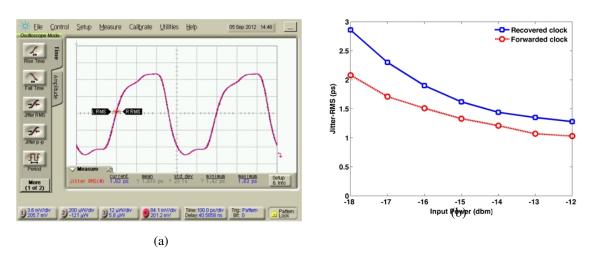

Figure 2.8: Silicon ring resonator-based wavelength-division-multiplexing (WDM) link.

Silicon photonic links based on ring resonator devices provide a unique opportunity to deliver distance-independent connectivity whose pin-bandwidth scales with the degree of wavelength-division multiplexing. As shown in Fig. 2.8, multiple wavelengths ( $\lambda_1$ - $\lambda_4$ ) generated by an off-chip comb laser are coupled into a silicon waveguide via an optical coupler. At the transmit side, ring modulators insert data onto a specific wavelength through electro-optical modulation. These modulated optical signals propagate through the waveguide and arrive at the receiver side where ring filters drop the modulated optical signals of a specific wavelength at a receiver channel with photodetectors (PD) that convert the signals back to the electrical domain.

# 3. DESIGN OF OPTICAL RECEIVER FRONT-END CIRCUITS FOR HIGH-SPEED OPTICAL TRANSMISSION\*

The continuous growth of data volume due to increased multimedia applications and cloud computing services requires that the data rates of optical communication systems scale to supply this demand. This rapid expansion in data communication also necessitates improvements in optical transceiver circuitry power efficiency as these systems scale well past 10Gb/s.

Figure 3.1: Optical receiver system block diagram.

A typical optical receiver architecture is shown in Fig. 3.1. The photodetector detects the optical signal and converts it to electrical current. A transimpedance amplifier (TIA) then converts this current signal into a voltage which is passed through a limiting amplifier (LA) to achieve a signal sufficient for reliable operation of the subsequent clock and data recovery (CDR) circuits. After the CDR, a demultiplexer is used to generate multiple low-speed data streams for further processing. Transimpedance amplifiers as the optical receiver front-end circuits typically determine the overall optical link performance, as their

<sup>\*</sup>Reprinted with permission from "A Low-Power 26-GHz Transformer-Based Regulated Cascode SiGe BiCMOS Transimpedance Amplifier" by Cheng Li, 2013, IEEE Journal of Solid-State Circuits, Volume: 48, Issue: 5, Page(s): 1264 - 1275, Copyright 2013 by IEEE

speed and sensitivity set the maximum data rate and tolerable channel loss.

This chapter describes a 26 GHz transimpedance amplifier (TIA) that employs a transformer-based regulated cascode (RGC) input stage which provides passive negative-feedback gain that enhances the effective transconductance of the TIA's input common-base transistor; reducing the input resistance and isolating the parasitic photodiode capacitance. This allows for considerable bandwidth extension without significant noise degradation or power consumption. Further bandwidth extension is achieved through series inductive peaking to isolate the photodetector capacitance from the TIA input. The optimum choice of series inductive peaking value and key transformer parameters for bandwidth extension and jitter minimization is analyzed. Fabricated in a 0.25- $\mu$ m SiGe BiCMOS technology and tested with an on-chip 150~fF capacitor to emulate a photodiode, the TIA achieves a  $53~\text{dB}\Omega$  single-ended transimpedance gain with a 26~GHz bandwidth and  $21.3~\text{pA}\sqrt{Hz}$  average input-referred noise current spectral density. Total chip power including output buffering is 28.2~mW from a 2.5~V supply, with the core TIA consuming 8.2~mW, and the chip area including pads is  $960~\mu$ m  $\times 780~\mu$ m.

This chapter is organized as following. Design challenges of high-speed TIA and potential solutions are discussed in Section 3.1. Common bandwidth extension techniques, including series inductive peaking and the active regulated cascode topology, are reviewed in Section 3.2. Section 3.3 discusses the transformer-based RGC input stage, where the mutual magnetic coupling of the on-chip transformer provides a negative feedback between the emitter and base terminals of the common-base input stage; improving the input transistor effective transconductance and allowing for extended bandwidth. The complete TIA topology is detailed in Section 3.4, along with analysis on the optimization of the series inductance and key transformer parameters to extend bandwidth, while limiting frequency peaking and group delay variation. Experimental results of the TIA, fabricated in a 0.25  $\mu$ m SiGe BiCMOS technology, are presented in Section 3.5. Finally, Section 3.6

concludes the chapter.

#### 3.1 High-Speed Transimpedance Amplifier Design Challenges and Potential Solutions

One TIA design challenge stems from the potentially large photodiode parasitic capacitance, which deteriorates both the bandwidth and noise performance of the system. Various input stages have been proposed [24–27] to relax this bandwidth limitation. A popular technique to obtain a very small input resistance involves modifying a conventional common-gate/common-base (CG/CB) input stage to a regulated cascode (RGC) architecture which employs active negative feedback gain to boost the input transconductance [24, 25]. This reduced input resistance pushes the input pole to a higher frequency, relaxing trade-offs between TIA gain and bandwidth. However, conventional RGC topologies require additional voltage headroom due to the cascode topology. Moreover, extra power is required in the feedback stage in order to avoid excessive TIA frequency peaking and obtain sufficient noise performance [24].

An efficient way to boost transistor transconductance involves passive transformer-based negative feedback. In this method, magnetic coupling between the transformer primary and secondary windings is utilized to realize negative feedback gain without introducing additional power and noise. While this approach has been employed in narrow-band LNA design [28], applying this in broad-band TIA design requires tight control on frequency peaking and group delay variation, particularly when combined with other bandwidth extension techniques [29].

Series inductive peaking is another technique to extending TIA bandwidth. Placing inductors in series between amplifier stages forms an equivalent  $\pi$ -network which isolates the capacitance of the stages [30,31]. In TIA design, this is often used to isolate the photodetector capacitance from the TIA input capacitance. While this approach is effective, the inductance should be optimized to limit frequency peaking and group delay variation.

#### 3.2 Overview of Bandwidth Extension Techniques

This section reviews the two key bandwidth extension techniques used in the presented TIA design, series inductive peaking and input transistor transconductance-boosting via the regulated cascode topology.

#### 3.2.1 Series Inductive Peaking

Figure 3.2: Bandwidth enhancement by inserting a series inductor between the photodiode and the TIA.

Series inductive peaking [30–34] is an effective method to extend bandwidth in multistage amplifiers by isolating a stage's output capacitance from the subsequent stage's input capacitance. This technique is often leveraged in TIA design by interposing an inductor between the photodiode and the circuit input, as shown in Fig. 3.2. From the equivalent small-signal model, the series inductor  $L_1$  isolates the two parasitic capacitors ( $C_{pd}$  and  $C_{in}$ ), forming a  $\pi$ -network which extends the bandwidth relative to a lumped RC system. Following a similar approach as in [33], the current-mode transfer function of this  $\pi$ network can be expressed as the following third-order expression.

Figure 3.3: Frequency response of inductive series peaking  $\pi$ -network for various m values (k=0.3).

$$\frac{I_{in}}{I_{pd}} = \frac{1}{s^3 R_{in} L_1 C_{pd} C_{in} + s^2 L_1 C_{pd} + s R_{in} (C_{pd} + C_{in}) + 1}$$

$$= \frac{1}{(\frac{s}{\omega_0})^3 \frac{k}{m} (1 - k) + (\frac{s}{\omega_0})^2 \frac{1 - k}{m} + \frac{s}{\omega_0} + 1}$$

(3.1)

where  $k=\frac{C_{in}}{C_{in}+C_{pd}}$  and  $m=\frac{R_{in}^2(C_{pd}+C_{in})}{L_1}$ . Significant bandwidth extension ratios (BWER) can be achieved by choosing different k and m values, as shown in Fig. 3.3, where the frequency is normalized to the 3-dB frequency ( $\omega_0=\frac{1}{(C_{pd}+C_{in})R_{in}}$ ) of the uncompensated case with  $L_1=0$ . However, it is important to avoid values which cause large gain ripple in the frequency response, as this introduces large group delay variation and results in significant signal distortion [31]. A more detailed analysis of the relationship between the bandwidth extension and group-delay variation in the proposed TIA can be found in Section 3.4.

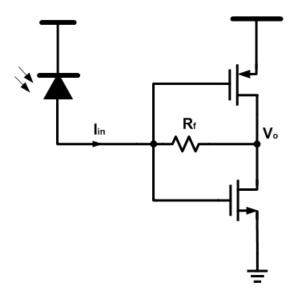

Figure 3.4: Regulated cascode input stage: (a) conventional topology, (b) proposed transformer-based topology.

#### 3.2.2 Conventional RGC Topology

TIA bandwidth extension can also be achieved by reducing the input resistance. The regulated cascode topology [24], shown in Fig. 3.4a, achieves this by using a common-base input stage  $(Q_1)$  with local active feedback  $(Q_2)$  to boost the transconductance of  $Q_1$  and provide a small signal input resistance of

$$R_{in} \simeq \frac{1}{g_{m1}(1 + g_{m2}R_3)}. (3.2)$$

An important feature of this gain-boosted common-base input stage is that it isolates the photodiode capacitance from subsequent amplifier stages. Used in combination with a subsequent feedback TIA, a high transimpedance can be achieved while maintaining stability over a wide input capacitance range.

However, a conventional RGC topology has a power overhead due to the headroom

necessary to support the two base-emitter voltages and maintain a suitable frequency response. In addition, the local feedback stage introduces a zero  $(z_1)$  in the transimpedance transfer function. This zero can be estimated by  $z_1 = (r_{\pi 1}||r_{o2}||R_3)C_{p1}$ , where,  $r_{\pi 1}$  is the base-emitter resistance of transistor  $Q_1$ ,  $r_{o2}$  is the collector resistance of transistor  $Q_2$ , and  $C_{p1}$  is the total parasitic capacitance at node 1 of Fig. 3.4a. In order to avoid the frequency peaking of transimpedance gain, a smaller resistor  $R_3$  is normally used to set this zero in the roll-off region of the gain curve [35]. For a given negative-feedback gain and  $g_m$ -boosting factor, this results in an increased  $Q_2$  bias current. In addition, the local feedback transistor can contribute substantial thermal noise at high frequency, thus degrading the system noise performance.

#### 3.3 Transformer-based RGC Input Stage

The TIA proposed in this work employs passive transformer-based negative feedback, shown in Fig. 3.4b, in order to provide input  $g_m$ -boosting. Relative to a conventional RGC input stage, this approach trades off increased area from the large transformer to avoid the power and noise of an added active amplifier stage. Here the transformer consists of primary  $(L_p)$  and secondary inductors  $(L_s)$ , with the bias voltage  $V_b$  provided externally. Feedback via mutual magnetic coupling in the transformer provides anti-phase operation between the emitter and base terminals, thus boosting the transconductance of the common-base transistor to

$$g'_{m} = (1 + nk)g_{m}. (3.3)$$

Here the turn ratio n is

$$n = \sqrt{L_s/L_p} \tag{3.4}$$

and the coupling coefficient k is

$$k = M/\sqrt{L_s L_p},\tag{3.5}$$

where M is the mutual inductance between the primary and secondary windings [36]. The coupling coefficient indicates the magnetic coupling strength in the transformer and is intrinsically less than unity due to magnetic flux leakage. In order to effectively boost the transconductance of the input transistor, thus reducing the effective resistance at input node and extending the TIA bandwidth, the monolithic transformer should be designed to achieve a relatively high magnetic coupling coefficient over a wide frequency range. This implies careful design of the wires that comprise the transformer windings, the turn number, and the turn ratio. The details of transformer design for achieving considerable bandwidth extension and low deterministic jitter are described in Section IV.

#### 3.4 TIA Design

### 3.4.1 TIA Topology

Figure 3.5: Transformer-based RGC TIA schematic.

The complete schematic of the transformer-based regulated cascode TIA is shown in Fig. 3.5. Both series inductive peaking  $(L_1)$  and input transistor  $g_m$ -boosting via transformer-based negative feedback are leveraged in order to extend TIA bandwidth. Table 3.1 gives the key parameters for the input-stage transformer. The  $g_m$ -boosted common-base input stage isolates the photodiode capacitance from the second-stage feedback TIA. This common-emitter gain stage, consisting of  $(Q_2$  and  $R_4)$  with local shunt feedback resistor  $(R_f)$  connected between the base and collector terminals, provides the majority of the transimpedance gain.  $R_3$  and  $C_1$  are inserted in the second stage to provide an appropriate level shift for the DC voltage at emitter terminal. The final stage is a differential output buffer which converts the TIA's single-ended output to differential outputs and drives the  $50\Omega$  load of the measurement equipment. Here shunt inductive peaking [37] is also used to achieve broadband operation. As this simple output buffer is not a major point of emphasis in this design, emitter degeneration is not included in the output buffer current mirror.

Table 3.1: Key parameters of the input-stage transformer

| $L_p$   | $L_s$   | Turn Number | Turn Ratio (n) | Coupling Coefficient (k) at 20 GHz |

|---------|---------|-------------|----------------|------------------------------------|

| 0.28 nH | 1.09 nH | 2.5         | 2              | 0.68                               |

Assuming sufficiently large boosted  $g_{m1}$  and  $g_{m2}R_f$  values, the low frequency transimpedance from the input to node B of Fig. 3.5 is approximately

$$Z_T(0) \simeq g_{m2} R_4(R_1 || \frac{R_f}{1 + g_{m2} R_4})$$

(3.6)

At the input, since the  $(Q_1)$  transconductance is boosted by the negative feedback from

the on-chip transformer, the resistance at the input node can be expressed as

$$R_{in}(s) \simeq \frac{1}{g_{m1}(1 + nk(s))}$$

(3.7)

where k(s) displays a high-pass response, as shown in Fig. 3.6. With turn ratio n=2 and coupling coefficient k near 0.7 at 20GHz, the input resistance can be reduced to a relatively low value. Note, this high-pass coupling coefficient can also be leveraged to compensate for bandwidth degradation caused by the circuits poles.

Figure 3.6: Simulated 2.5-turn transformer coupling coefficient vs frequency with different turn ratios.

The trade-offs between input resistance, noise, and voltage headroom pose challenges in the design of a high-speed TIA based on a single common-base topology. In order to obtain a low input resistance the bias current needs to be large, which, for a given voltage headroom, limits the load resistor  $R_1$  which sets the transimpedance gain and the TIA noise performance [38]. Moreover, a large load resistor reduces the TIA output bandwidth. The proposed TIA architecture alleviates these trade-offs by utilizing a transformer-based input

stage that enhances the transconductance without increasing the bias current, thus reducing the input resistance. At node A of Fig. 3.5, the local shunt feedback lowers the node resistance down by the factor of the open loop gain of the second amplifier stage. Although the relatively low impedance caused by the local resistive shunt feedback sacrifices the transimpedance gain of first stage, it overcomes the bandwidth limit due to the large output impedance of the simple common-base topology. Finally, the effective resistance at node B is  $\frac{1}{gm_2}||R_4$ , which is inherently small. Due to this TIA topology, all major signal path poles reside at relatively high frequencies, making this architecture suitable for wideband, high speed applications.

Since passive transformer-based negative feedback is utilized to boost the input transconductance, the noise penalty of the active feedback amplifier in the conventional RGC input stage is avoided. Considering transistor collector current shot noise and base resistance thermal noise [39], the input-referred noise current can be derived as

$$\frac{i_{n,in}^2}{i_{n,in}^2} \simeq \frac{4kT}{R_1} + \frac{4kT}{R_2} + \frac{4kT}{R_f}

+ 2kT(\frac{1}{g_{m2}} + 2r_{b2} + \frac{2}{g_{m2}^2 R_4})\omega^2 C_A^2

+ 4kT(\frac{g_{m1}}{2} + r_{b1}g_{m1}^2 + \frac{1}{R_f} + \frac{1}{R_1})\frac{\omega^2 C_{in}^2}{g_{m1}'^2}$$

(3.8)

where  $r_{b1}$  and  $r_{b2}$  are the base resistance of  $Q_1$  and  $Q_2$ , respectively. Here,  $g'_{m1}$  is the boosted transconductance and  $C_{in}$  and  $C_A$  are the total parasitic capacitance at the input node and  $Q_1$ 's collector, respectively. From (3.8), the boosted  $g'_{m1}$  value, which is a function of the feedback from the transformer comprised of  $L_p$  and  $L_s$ , should also provide a reduction in the last noise term at no power overhead.

### 3.4.2 Bandwidth Extension Analysis

While on-chip inductors and transformers can be used to enhance broadband amplifier bandwidth and overcome a given process's transimpedance limit, improperly designed inductor values can cause frequency peaking and lead to relatively large group delay variation and signal distortion. This has been well studied in the work of [31] and [40]. In this subsection, we model the frequency response of the proposed TIA, neglecting the output buffer (Fig. 4.4a), in order to select the series inductance value and transformer design parameters. We extend the approach of [40] for TIA modeling with series inductive peaking to include both the frequency-dependent response of the transformer-based  $g_m$ -boosting and a more accurate 2-pole and 1-zero feedback TIA model.

Figure 3.7: (a) TIA schematic without the output buffer, (b) Equivalent small-signal model, (c) Equivalent analysis model.

Fig. 3.7b shows the equivalent TIA small-signal model. The equivalent resistance seen into the emitter of transistor  $Q_1$  is taken from (3.3). As shown in Fig. 3.7c, the proposed TIA is then simplified to a passive  $\pi$ -network followed by the feedback TIA model. Including the transformer's primary inductor, the transfer function of this  $\pi$ -network can be written as a fourth-order expression. The feedback TIA is modeled with two poles located at nodes A and B in Fig. 3.7a and a zero from the parasitic capacitance in parallel with the local feedback resistor. Overall, the complete TIA transfer function is approximated as (3.9),

$$Z_T(s) \simeq \frac{R_1 R_4}{R_1 (1 + g_{m2} R_4) + R_f} \times \frac{(s R_f C_f + 1 - g_{m2} R_f)}{(s R_A C_A + 1)(s R_B C_B + 1)} \times \frac{L_p s + R_2}{a_4 s^4 + a_3 s^3 + a_2 s^2 + a_1 s + a_0}$$

(3.9)

where

$$\begin{split} a_0 &= R_2 + R_{in}(s), \\ a_1 &= R_2 R_{in}(s) (C_{pd} + C_{in}) + L_p, \\ a_2 &= L_1 C_{pd} (R_2 + R_{in}(s)) + R_{in}(s) L_p (C_{pd} + C_{in}), \\ a_3 &= L_1 R_2 R_{in}(s) C_{pd} C_{in} + L_1 L_p C_{pd}, \\ a_4 &= L_1 L_p C_{pd} C_{in} R_{in}(s), \\ R_A &= R_1 || \frac{R_f}{1 + g_{m2} R_4}, \\ R_B &= \frac{1}{gm_2} || R_4, \\ C_A &= C_{cs1} + C_{be2} + C_f (1 + g_{m2} R_4) + C_{bc1} \;, \\ \text{and} \; C_B &= C_f + C_{cs2}. \end{split}$$

Here  $C_{pd}$  denotes the parasitic photodiode capacitance and the bond pad capacitance,  $C_{cs1}$  and  $C_{bc1}$  are the  $Q_1$  collector-substrate and base-collector capacitances, respectively,  $C_{be2}$  and  $C_{cs2}$  are the  $Q_2$  base-emitter and collector-substrate capacitances, respectively, and  $C_f$  is the depletion capacitance of the collector-base junction of  $Q_2$ .

Using this model, the series peaking inductance and transformer design parameters are chosen for a flat frequency response, low group delay variation, and low deterministic jitter. The series inductance is selected to achieve a Butterworth response with maximally flat gain magnitude and the total TIA's response is optimized by varying the transformer turn number and turn ratio. As  $L_1$ ,  $L_p$ , and  $L_s$  need to be jointly optimized, this iterative process is outlined in the following steps.

Step 1: Using initial reasonable transformer parameters (e.g. 2 turns and turn ratio of 2:1), optimize the series inductance  $L_1$  for reasonable bandwidth extension, low jitter and group delay variation;

$Step\ 2$ : Using the  $L_1$  value found in Step 1 and the initial turn ratio, optimize the transformer turn number;

$Step\ 3$ : Using the  $L_1$  value found in Step 1 and turn number found in Step 2, optimize the transformer turn ratio;

Step 4: Using the transformer parameters found in Steps 2 and 3, re-optimize the series inductance;

$Step\ 5$ : If necessary, re-optimize the transformer parameters and finalize the design. The following sub-sections provide key design insights on how the series inductance and transformer parameters impact the TIA performance, with the assumption for each of the parameters that the other design parameters are already optimized.

### 3.4.2.1 Series Peaking Inductance

In order to achieve a flat frequency response, low group-delay variation, and low deterministic jitter, the inductance of  $L_1$  in Fig. 3.5 needs to be carefully selected. The simulated TIA transimpedance frequency response is shown in Fig. 3.8a for various  $L_1$  inductance values, with a finite-Q inductor model employed, and a 220fF capacitance to model the photodetector and input bondpad. Also, an initial transformer design with 2

turns and a 2:1 turn ratio is assumed. Here both the transimpedance gain is normalized to one and the frequency axis is normalized to the 3-dB bandwidth without series inductive peaking ( $L_1$ =0). A Butterworth response with maximally flat magnitude and 1.8× bandwidth extension is achieved when employing a proper series inductor value of  $L_1$ =820 pH. Note that higher inductance values also cause peaking in the frequency response, thus leading to relatively large group-delay variations, as shown in Fig. 3.8b. The chosen series inductor value of  $L_1$ =820 pH and Q of  $\sim$ 8 achieves a low group delay variation of  $\pm$ 10% and, as shown in Fig. 3.9, minimal deterministic jitter with a 40Gb/s  $2^{31}$ -1 PRBS pattern. Post-layout simulations indicate that this series inductance value is suitable for photodetector capacitance variations near  $\pm$ 20%, while still maintaining <1dB gain peaking and 5% bandwidth degradation. While an octagonal-shaped inductor is employed in the final design, this geometry choice is not essential, as post-layout simulations indicate that a Q of approximately three can be used without degrading the bandwidth more than 10%.

Figure 3.8: Simulated TIA frequency response with various series inductance values: (a) normalized transimpedance gain, (b) group-delay of input  $\pi$ -network. The frequency axis in both curves is normalized to the 3-dB bandwidth without series inductive peaking.

Figure 3.9: Simulated 40 Gb/s deterministic jitter performance of the proposed TIA with a  $2^{31}$ -1 pattern.

Realizing  $L_1$  fully with an on-chip series peaking inductor value is directly applicable for an optical receiver with monolithically integrated photodetectors [41]. For optical receivers which have off-chip photodetectors, a portion of the series peaking inductor  $L_1$  could be realized with the bondwire inductance between the photodetector and the TIA input pad. In this case, a smaller on-chip peaking inductor could still be included to isolate the bond pad capacitance from the TIA input capacitance for further bandwidth extension [31].

## 3.4.2.2 Transformer Turn Number

The total TIA response is optimized by setting the transformer turn number and ratio. Using the  $L_1=820~pH$  value to optimize the input  $\pi$ -network and assuming an initial 2:1 transformer turn ratio, the turn number is varied to observe how the change in coupling coefficient affects the TIA's frequency response. Here the transformer area is increased in order to increase the turn number, which results in increased parasitic resistance and capacitance. For example, the 3-turn transformer was designed by adding an extra turn to

the 2-turn design, incurring a 72% area increase. As shown in Fig. 3.10, increasing turn number allows for bandwidth extension up to a point. However, when the transformer becomes large, as in the 3-turn case, the incurred parasitics cause a steep roll-off in the frequency response. A 2.5 turn number allows for a maximally flat bandwidth response, and, as shown in Fig. 3.9, minimal deterministic jitter with a 40Gb/s  $2^{31}$ -1 PRBS pattern.

Figure 3.10: Simulated transimpedance frequency response with different transformer turn number, transformer turn ratio is fixed at n = 2.

### 3.4.2.3 Transformer Turn Ratio

Transformer turn ratio is another important parameter which sets the amount of input transistor  $g_m$ -boosting. Using a 2.5-turn transformer value, the turn ratio is optimized for maximum bandwidth enhancement and minimum magnitude variation. As shown in Fig. 3.11, increasing turn ratio allows for bandwidth extension due to increased input transistor transconductance. However, again due to transformer size issues, the incurred parasitics cause excessive frequency peaking and a steep roll-off with n=3. Also, as shown in Fig. 3.9, a large increase in deterministic jitter is observed for a turn ratio larger than two.

The final transformer design uses n = 2 and 2.5 turns, which allows for a simulated TIA -3dB-bandwidth of 32 GHz.

Figure 3.11: Simulated transimpedance frequency response with different transformer turn ratio, transformer turn number is fixed at 2.5.

Figure 3.12: Simulated TIA performance versus series inductance  $L_1$  for different transformer turn ratios: (a) bandwidth, (b) group delay variation. Here the series inductance is normalized to the optimum value of 830 pH.

As mentioned previously, the overall design procedure is an iterative process to optimize the series peaking inductance and key transformer parameters. Fig. 3.12 shows how the TIA bandwidth and group delay vary over a more complete design space of various series inductor values, normalized to the optimum 820 pH value, and transformer turn ratios. Overall, a turn ratio of two yields the maximum bandwidth and minimum group delay variation. Note that while a smaller value relative to the chosen 820 pH series inductor yields a potentially wider bandwidth, this would result in sub-optimum group delay variation.

## 3.4.3 Transformer Design