## DESIGN OF ANALOG & MIXED SIGNAL CIRCUITS IN CONTINUOUS-TIME SIGMA-DELTA MODULATORS FOR SYSTEM-ON-CHIP APPLICATIONS

#### A Dissertation

by

#### **CHANG JOON PARK**

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chairs of Committee, Jose Silva-Martinez

Committee Members, Aydin Ilker Karsilayan

Byung-Jun Yoon

Jay Porter

Head of Department, Chanan Singh

December 2013

Major Subject: Electrical Engineering

Copyright 2013 Chang Joon Park

#### **ABSTRACT**

Software-defined radio receivers (SDRs) have become popular to accommodate multi-standard wireless services using a single chip-set solution in mobile telecommunication systems. In SDRs, the signal is down-converted to an intermediate frequency and then digitalized. This approach relaxes the specifications for most of the analog front-end building blocks by performing most of the signal processing in the digital domain. However, since the analog-to-digital converter (ADC) is located as close as possible to the antenna in SDR architectures, the ADC specification requirements are very stringent because a large amount of interference signals are present at the ADC input due to the removal of filtering blocks, which particularly affects the dynamic range (DR) specification. Sigma-delta ( $\Sigma\Delta$ ) ADCs have several benefits such as low implementation cost, especially when the architecture contains mostly digital circuits. Furthermore, continuous-time (CT)  $\Sigma\Delta$  ADCs allow elimination of the anti-aliasing filter because input signals are sampled after the integrator. The bandwidth requirements for the amplifiers in CT  $\Sigma\Delta$  ADCs can be relaxed due to the continuous operation without stringing settling time requirements. Therefore, they are suitable for high-speed and low-power applications. In addition, CT  $\Sigma\Delta$  ADCs achieve high resolution due to the  $\Sigma\Delta$ modulator's noise shaping property. However, the in-band quantization noise is shaped by the analog loop filter and the distortions of the analog loop filter directly affect the system output. Hence, highly linear low-noise loop filters are required for highperformance  $\Sigma\Delta$  modulators.

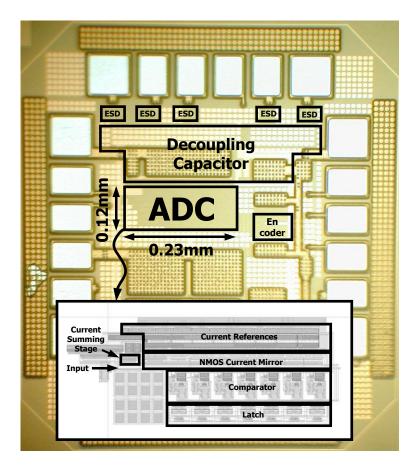

The first task in this research focused on using CMOS 90 nm technology to design and fabricate a 5<sup>TH</sup>-order active-RC loop filter with a cutoff frequency of 20 MHz for a low pass (LP) CT  $\Sigma\Delta$  modulator. The active-RC topology was selected because of the high DR requirement in SDR applications. The amplifiers in the first stage of the loop filter were implemented with linearization techniques employing anti-parallel cancellation and source degeneration in the second stage of the amplifiers. These techniques improve the third-order intermodulation (IM3) by approximately 10 dB; while noise, area, and power consumption do not increase by more than 10%. Second, a current-mode adder-flash ADC was also fabricated as part of a LP CT  $\Sigma\Delta$  modulator. The new current-mode operation developed through this research makes possible a 53% power reduction. The new technology also lessens existing problems associated with voltage-mode flash ADCs, which are mainly related to voltage headroom restrictions, speed of operation, offsets, and power efficiency of the latches. The core of the currentmode adder-flash ADC was fabricated in CMOS 90 nm technology with 1.2 V supply; it dissipates 3.34 mW while operating at 1.48 GHz and consumes a die area of 0.0276 mm<sup>2</sup>. System-on chip (SoC) solutions are becoming more popular in mobile telecommunication systems to improve the portability and competitiveness of products. Since the analog/RF and digital blocks often share the same external power supply in SoC solutions, the on-chip generation of clean power supplies is necessary to avoid system performance degradation due to supply noises. Finally, the critical design issues for external capacitor-less low drop-out (LDO) regulators for SoC applications are addressed in this dissertation, especially the challenges related to power supply rejection

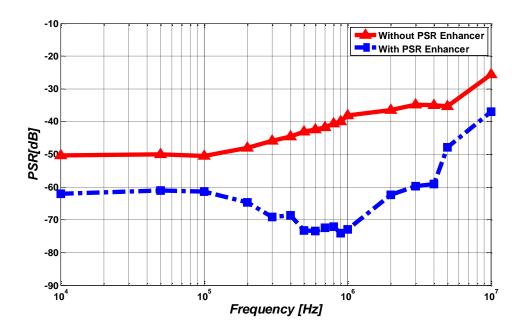

at high frequencies as well as loop stability and transient response. The paths of the power supply noise to the LDO output were analyzed, and a power supply noise cancellation circuit was developed. The power supply rejection (PSR) performance was improved by using a replica circuit that tracks the main supply noise under process-voltage-temperature variations and all operating conditions. Fabricated in a 0.18  $\mu$ m CMOS technology with 1.8 V supply, the entire proposed LDO consumes 55  $\mu$ A of quiescent current while in standby operation, and it has a drop-out voltage of 200 mV when providing 50 mA to the load. Its active core chip area is 0.14 mm<sup>2</sup>. Compared to a conventional uncompensated LDO, the proposed architecture presents a PSR improvement of 34 dB and 25 dB at 1 MHz and 4 MHz, respectively.

## **DEDICATION**

To my parents, brother and parents-in-law To my dearest wife, Joo Young Jung, and adorable son, Daniel Joonyoung Park

#### **ACKNOWLEDGMENTS**

First of all, I would like to express my sincere gratitude to my advisor Dr. Jose Silva-Martinez for his support and guidance throughout my graduate studies at Texas A&M University. I greatly benefited from his deep intuition and strong knowledge in analog circuit and system design. I also want to thank my PhD committee members, Dr. Aydin Ilker Karsilayan, Dr. Byung-Jun Yoon, and Dr. Jay Porter, for agreeing to serve on my committee and their time spent on my committee. Also, special thanks to Dr. Xing Cheng, the instructor of my first class in Texas A&M University (TAMU). His encouragement relaxed my anxiety and gave me the confidence I needed.

I would like to thank the graduate students who worked with me on my research projects at Texas A&M University; namely, Marvin Onabajo, Hyung-Joon Jeon, Alfredo Perez, Hemasundar Mohan Geddada, Aravind Kumar Padyana, and Saikrishna Ganta.

I also want to express my appreciation to all my colleagues in the TAMU Analog and Mixed Signal Center (AMSC) for helpful conversations regarding research and course projects; especially to Jusung Kim, Raghavendra Kulkarni, Ramy Saad, Joselyn Torres, Hongbo Chen, Andreas Larsson, Jason Wardlaw, John Mincey, Erik Pankratz, Charles Sekyiamah, Richard Turkson, Karthik Raviprakash, Akshay Godbole, Jiayi Jin, Haoyu Qian, Adrian Colli, Hsien-Pu Chen, Younghoon Song and Byung-ho Min. Furthermore, special thanks goes to the secretary of AMSC group, Ella Gallagher, for her kind help.

I would like to thank my academic advisor Dr. Il-Gu Yun from Yonsei University in Seoul, Korea and Dr. Sung-Mo "Steve" Kang from the University of California, Santa Cruz for their guidance and encouragement.

In closing, I am grateful for the encouragement and understanding, as well as support, from my parents, brother and parents-in law. Especially, I am grateful to my lovely wife, Joo Young Jung, for her love, encouragement, patience and sacrifice. I couldn't successively finish this long journey without her.

## **TABLE OF CONTENTS**

|                                                                                                                                                                                                                                                      | Page             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ABSTRACT                                                                                                                                                                                                                                             | ii               |

| DEDICATION                                                                                                                                                                                                                                           | v                |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                      | vi               |

| TABLE OF CONTENTS                                                                                                                                                                                                                                    | viii             |

| LIST OF FIGURES                                                                                                                                                                                                                                      | xi               |

| LIST OF TABLES                                                                                                                                                                                                                                       | XV               |

| I. INTRODUCTION                                                                                                                                                                                                                                      | 1                |

| I.1. Background and Motivation  I.2. Design Issues I.2.1. Non-linearities I.2.2. Excess loop delay I.2.3. Blocker I.2.4. Jitter I.3. Research Focus I.4. Dissertation Organization  II. 5 <sup>TH</sup> -ORDER ACTIVE-RC FILTER FOR BLOCKER TOLERANT | 2<br>3<br>4<br>5 |

| CONTINUOUS-TIME SIGMA-DELTA MODULATORS  II.1. Background and Motivation  II.2. System-level Overview of the Blocker Tolerant CT LP ΣΔ ADC Archit                                                                                                     | 9<br>ecture11    |

| II.2.1. Design challenge of the loop filter                                                                                                                                                                                                          | 16<br>17<br>20   |

| II.4. Amplifier                                                                                                                                                                                                                                      | 23<br>24<br>25   |

| II.5. Layout and Results II.5.1. Layout                                                                                                                                                                                                              | 31               |

| II.5.2. Simulation results                                            | 32    |

|-----------------------------------------------------------------------|-------|

| II.5.2.1. The first stage of the loop filter                          |       |

| II.5.2.2. The second and third stages of the loop filter              |       |

| II.5.3. ADC chip measurements with embedded loop filter               |       |

| II.6. Summarizing Remarks                                             |       |

|                                                                       |       |

| III. CURRENT-MODE ADDER-QUANTIZER FOR BROADBAND LOW-                  | POWER |

| CONTINUOUS-TIME SIGMA-DELTA MODULATORS                                | 41    |

| III.1. Background                                                     | 41    |

| III.2. Typical Summing and Flash ADC Architecture                     |       |

| III.2.1. Conventional ADC architecture                                |       |

| III.2.2. Voltage-mode summing and quantizer                           |       |

| III.3. Proposed Summing and Flash ADC Architecture                    |       |

| III.3.1. Current-mode summing and quantizer                           |       |

| III.3.2. Current summing and mirroring stage                          |       |

| III.3.3. Input impedance of the current-mode adder                    |       |

| III.3.4. Current comparison stage                                     |       |

| III.3.5. PVT variations                                               |       |

| III.4. Chip Measurement Results                                       | 62    |

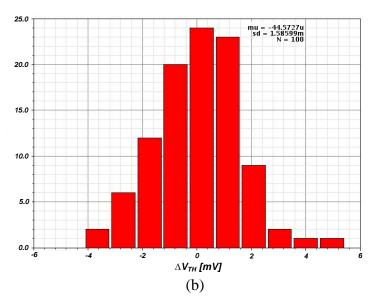

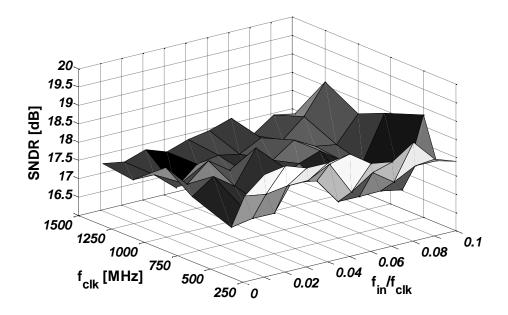

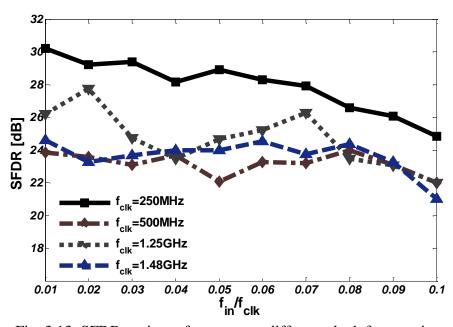

| III.4.1. SNDR and SFDR versus input frequency                         |       |

| III.4.2. ENOB versus clock frequency                                  |       |

| III.4.3. DNL and INL                                                  |       |

| III.4.4. Output spectrum                                              | 67    |

| III.5. Summarizing Remarks                                            | 71    |

|                                                                       |       |

| IV. HIGH POWER SUPPLY REJECTION (PSR) EXTERNAL CAPACITO               |       |

| LOW DROP-OUT (LDO) REGULATOR                                          | 12    |

| IV.1. Background                                                      | 72    |

| IV.2. Existing Solutions.                                             |       |

| IV.3. Fundamental PSR Limitations of Conventional LDOs                |       |

| IV.3.1. PSR limitation due to the gate-source capacitance of the pass |       |

| transistor                                                            |       |

| IV.3.2. PSR limitation due to the error amplifier                     |       |

| IV.3.3. Effect of the pass transistor's output impedance              |       |

| IV.4. Proposed PSR Enhancement Technique                              |       |

| IV.5. Circuit Implementation                                          |       |

| IV.5.1. PSR enhancer                                                  |       |

| IV.5.2. Key LDO components                                            |       |

| IV.5.2.1. Error amplifier                                             |       |

| IV.5.2.2. Frequency compensation and fast slew enhancement of         |       |

| IV.6. Prototype Measurement Results                  | 98  |

|------------------------------------------------------|-----|

| IV.6.1. Measurement set up                           |     |

| IV.6.2. Power supply rejection (PSR)                 | 101 |

| IV.6.3. Deflection voltage                           | 103 |

| IV.6.4. Transient response: load and line regulation | 104 |

| IV.6.5. Output noise                                 | 106 |

| IV.7. Summarizing Remarks                            | 108 |

| IV.8. Supplemental: DC Line Regulation Analysis      | 109 |

| V. SUMMARY AND CONCLUSIONS                           | 111 |

| REFERENCES                                           | 114 |

## LIST OF FIGURES

|            | Page                                                                                                                                                                                                                          |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.1.  | Power spectrum density of quantization noise9                                                                                                                                                                                 |

| Fig. 2.2.  | Typical block diagram of single-bit $\Sigma\Delta$ modulator                                                                                                                                                                  |

| _          | $5^{TH}$ -order CT LP $\Sigma\Delta$ ADC architecture with overload detector monitoring the critical filter nodes and controlling the attenuator13                                                                            |

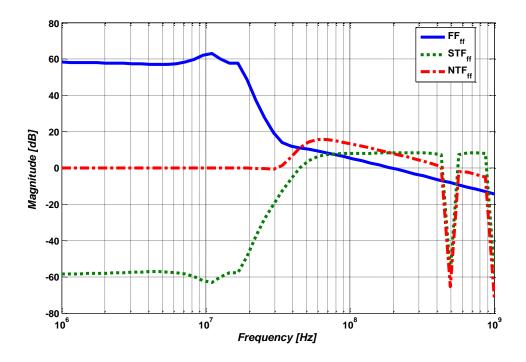

|            | Simulated the closed loop AC gain from input to the internal nodes of $5^{\text{TH}}$ -order CT LP $\Sigma\Delta$ ADC with FF compensation14                                                                                  |

| Fig. 2.5.  | Transfer functions in feed-forward (FF) architecture17                                                                                                                                                                        |

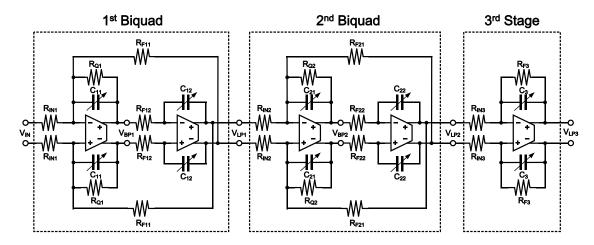

| Fig. 2.6.  | 5 <sup>TH</sup> -order active-RC loop filter                                                                                                                                                                                  |

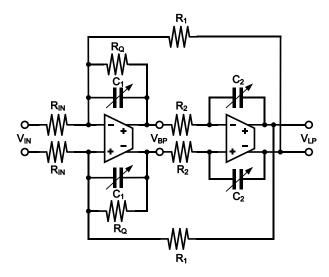

| Fig. 2.7.  | Two integrator loop biquad22                                                                                                                                                                                                  |

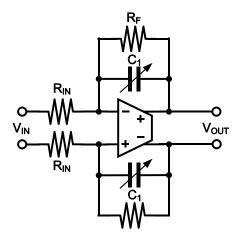

| Fig. 2.8.  | First-order integrator for the third stage of the loop filter23                                                                                                                                                               |

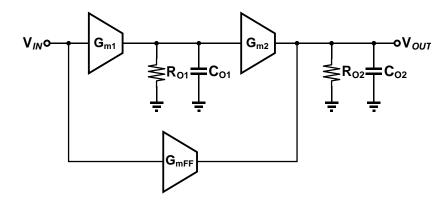

| Fig. 2.9.  | The block diagram of a two-stage amplifier with FF compensation24                                                                                                                                                             |

| Fig. 2.10. | The schematic of the Amplifier-I used in the first stage of the loop filter26                                                                                                                                                 |

| Fig. 2.11. | Amplifiers test-bench with loading (a) Amplifier-I, and (b) Amplifier-II28                                                                                                                                                    |

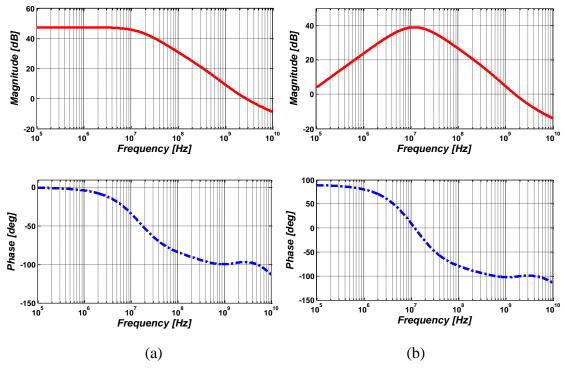

| Fig. 2.12. | (a) Open-loop gain, and (b) loop gain of the Amplifier-I30                                                                                                                                                                    |

| Fig. 2.13. | (a) Open-loop gain, and (b) loop gain of the Amplifier-II30                                                                                                                                                                   |

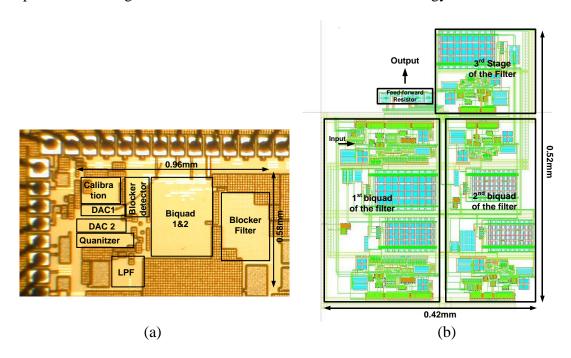

| Fig. 2.14. | (a) CT LP $\Sigma\Delta$ ADC chip microphotograph, and (b) layout of the $5^{TH}$ -order LP loop filter                                                                                                                       |

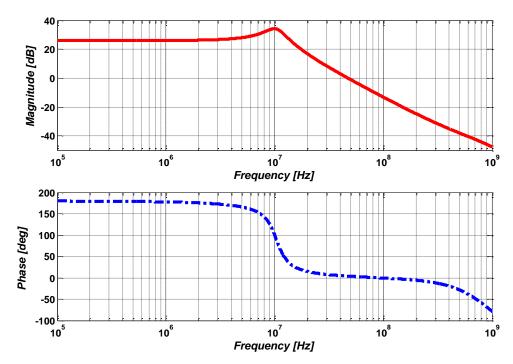

| -          | AC magnitude and phase response of the first stage of the loop filter                                                                                                                                                         |

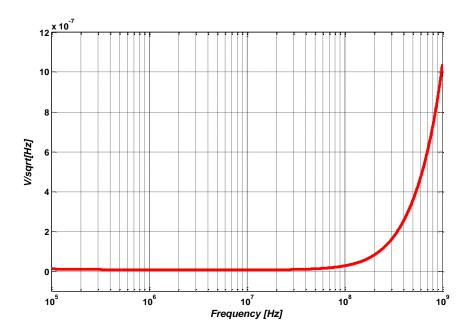

| Fig. 2.16. | Input referred noise density of the first stage of the loop filter33                                                                                                                                                          |

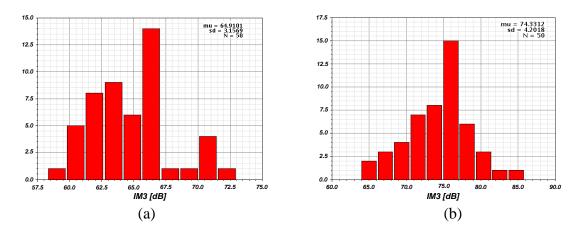

| -          | The IM3 in the first stage of the loop filter (a) without harmonic cancellation, and (b) with harmonic cancellation @ 400mV <sub>pk</sub> differential output swing (Monte Carlo simulation with 10 MHz and 11 MHz two tones) |

| Fig. 2.18. AC magnitude and phase response of the second stage of the loop filter |                                                                                                                                                                                                                                      |    |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.19.                                                                        | AC magnitude and phase response of the third stage of the loop filter                                                                                                                                                                | 35 |

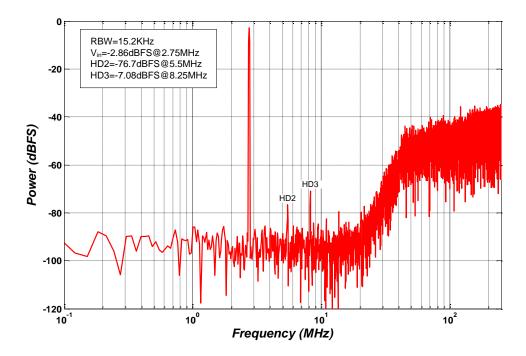

| Fig. 2.20.                                                                        | Measured output spectrum of the CT LP $\Sigma\Delta$ modulator with -2.86 dBFS input signal at 2.75 MHz                                                                                                                              | 37 |

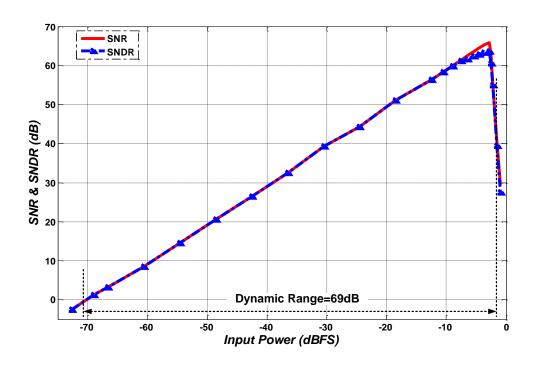

| Fig. 2.21.                                                                        | Measured SNR and SNDR versus input signal power.                                                                                                                                                                                     | 38 |

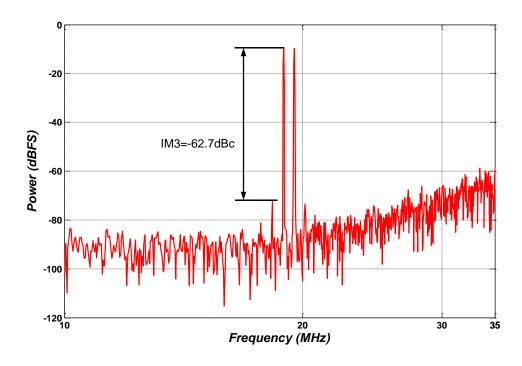

| Fig. 2.22.                                                                        | Two tone test for IM3 performance measurement                                                                                                                                                                                        | 38 |

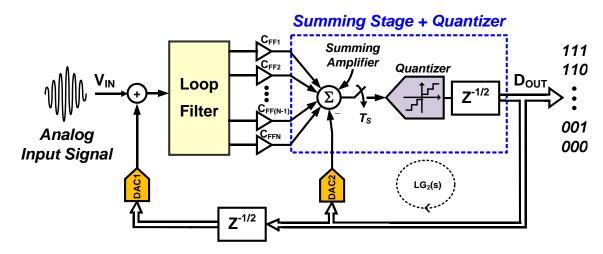

| Fig. 3.1.                                                                         | A CT $\Sigma\Delta$ modulator with feed-forward (FF) compensation                                                                                                                                                                    | 43 |

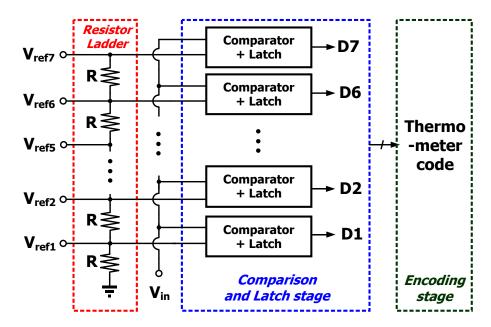

| Fig. 3.2.                                                                         | Voltage-mode summing amplifier and quantizer                                                                                                                                                                                         | 45 |

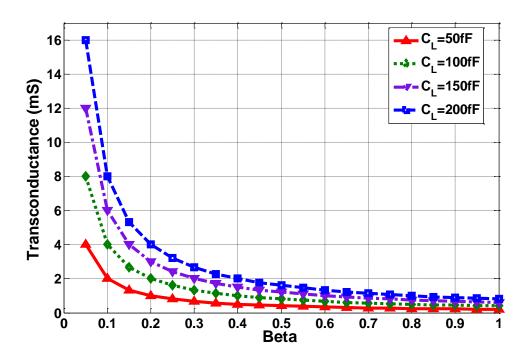

| Fig. 3.3.                                                                         | Required transconductances $(G_m)$ for the summing amplifier vs. $\beta$                                                                                                                                                             | 46 |

| Fig. 3.4.                                                                         | Simplified schematic of the conventional single-ended 3-bit voltage -mode flash ADC                                                                                                                                                  | 47 |

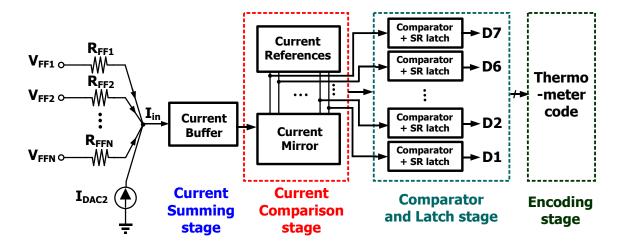

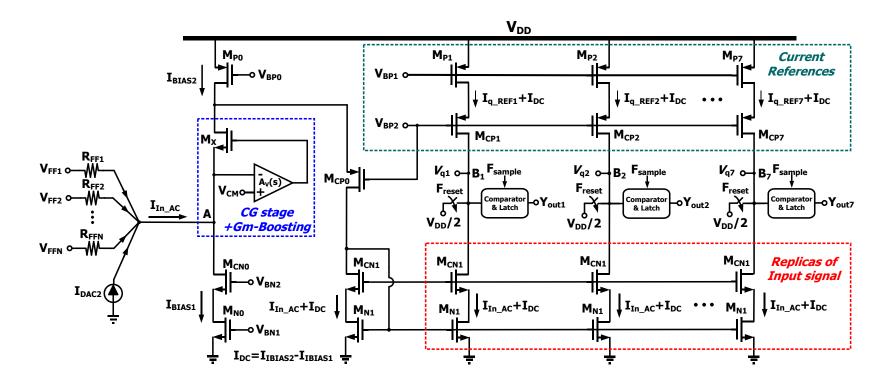

| Fig. 3.5.                                                                         | Architecture of the summing block and flash ADC with current -mode operation: single-ended version                                                                                                                                   | 49 |

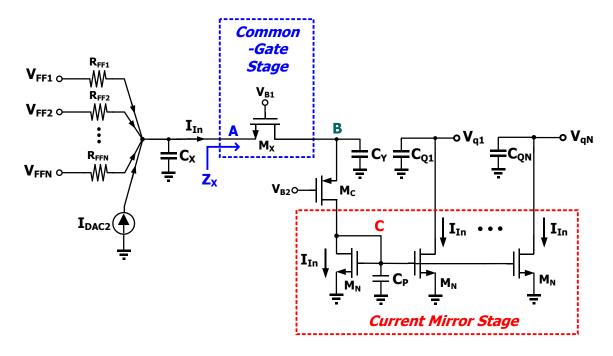

| Fig. 3.6.                                                                         | Simplified schematic of the current-mode summing and mirroring stage                                                                                                                                                                 | 50 |

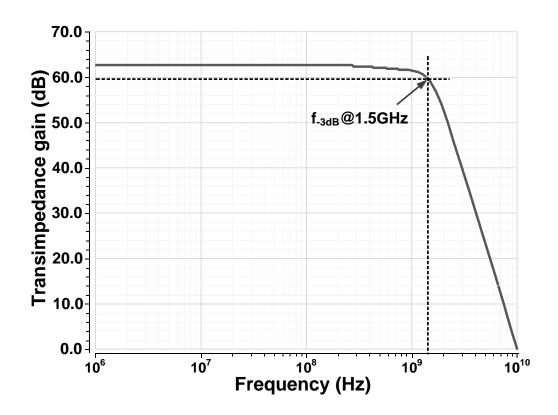

| Fig. 3.7.                                                                         | Frequency response of the current summing and mirroring stage $(V_{qN}/I_{DAC2} \text{ in Fig. 3.6})$                                                                                                                                | 51 |

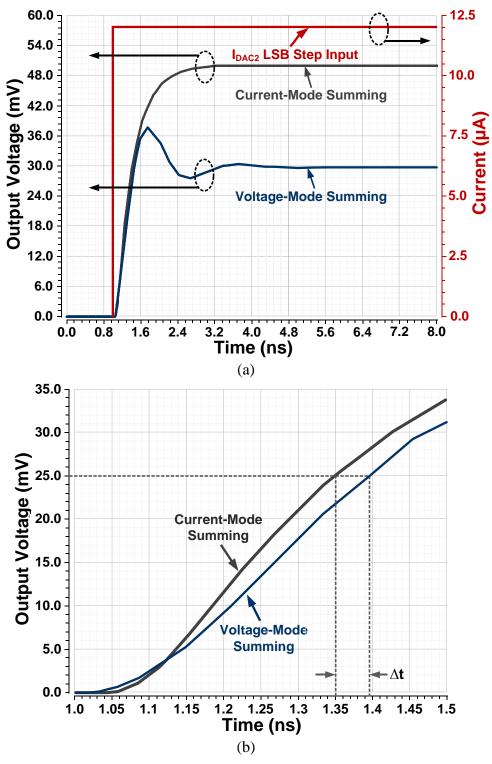

| Fig. 3.8.                                                                         | (a) Differential step response of the voltage-mode summing and current summing and mirroring stage, and (b) the zoomed-in differential step response view of both cases from 1 ns to 1.5 ns                                          | 54 |

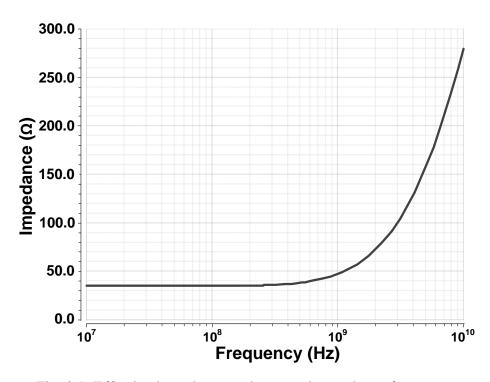

| Fig. 3.9.                                                                         | Effective impedance at the summing node vs. frequency                                                                                                                                                                                | 56 |

| Fig. 3.10.                                                                        | Schematic of the proposed current-mode flash ADC with summing stage (single-ended equivalent of the differential circuit)                                                                                                            | 58 |

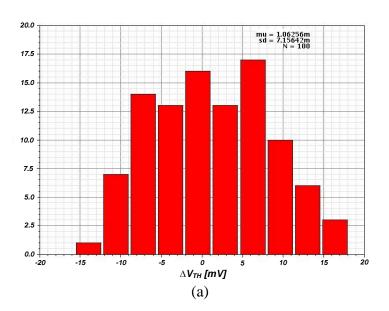

| Fig. 3.11.                                                                        | Histogram (100 runs) of the threshold voltage differences of the current mirror devices (MN1 in Fig. 10) from Monte Carlo simulations: (a) without matched transistors in the layout, and (b) with matched transistors in the layout | 60 |

| Fig. 3.12. | SNDR vs. input frequency at different clock frequencies                                                                                                                                                                                                                                           | 63  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 3.13. | SFDR vs. input frequency at different clock frequencies                                                                                                                                                                                                                                           | 63  |

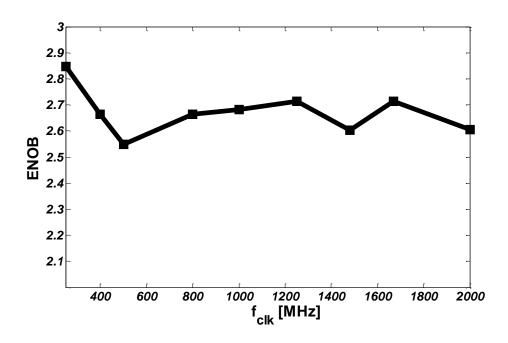

| Fig. 3.14. | ENOB vs. clock frequency with a full-scale 10 MHz input signal                                                                                                                                                                                                                                    | 65  |

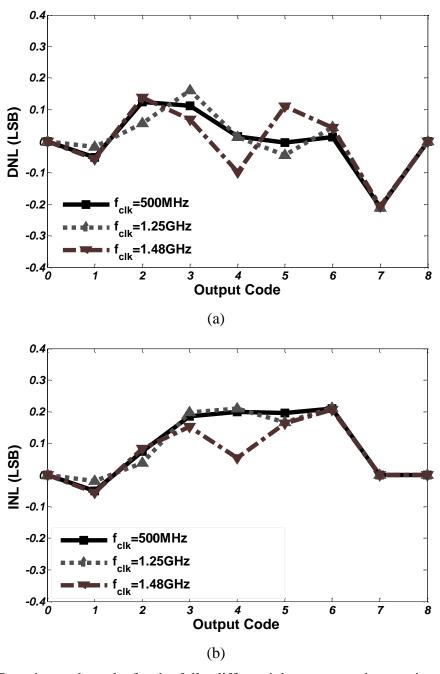

| Fig. 3.15. | Experimental results for the fully-differential current-mode quantizer; (a) DNL, and (b) INL of the ADC at different clock frequencies. (Offset and gain error are adjusted to zero.)                                                                                                             | 66  |

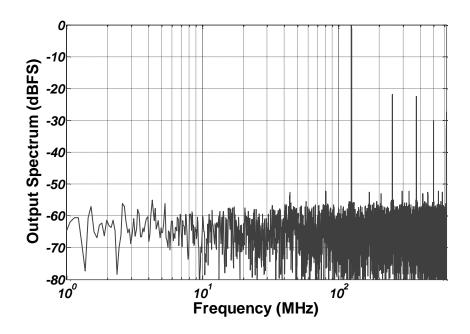

| Fig. 3.16. | Output spectrum for 125 MHz input at 1.25 GHz clock frequency                                                                                                                                                                                                                                     | 67  |

| Fig. 3.17. | Chip microphotograph of the prototype current-mode flash ADC                                                                                                                                                                                                                                      | 68  |

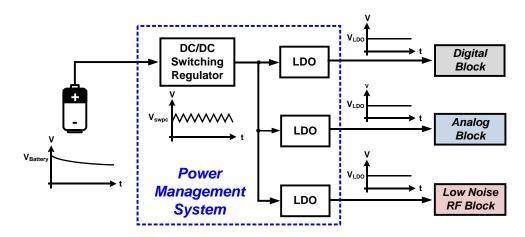

| Fig. 4.1.  | Typical power management system for SoC applications                                                                                                                                                                                                                                              | 72  |

| Fig. 4.2.  | Input to output power supply ripple paths in conventional LDOs                                                                                                                                                                                                                                    | 75  |

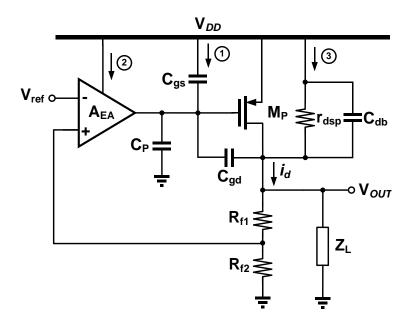

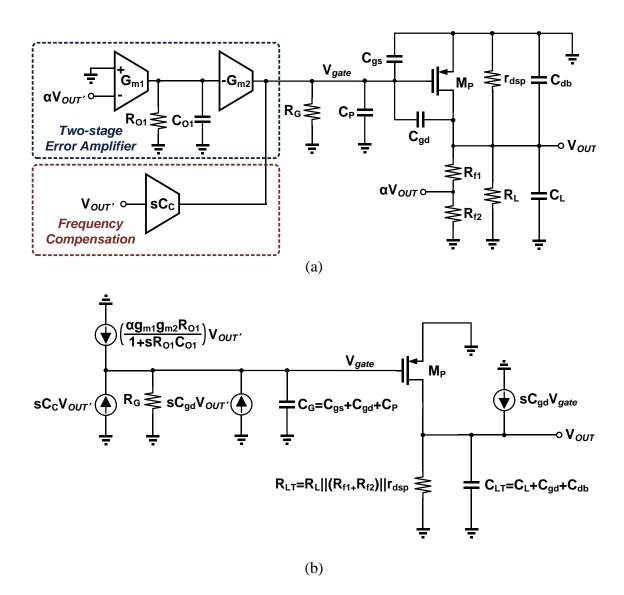

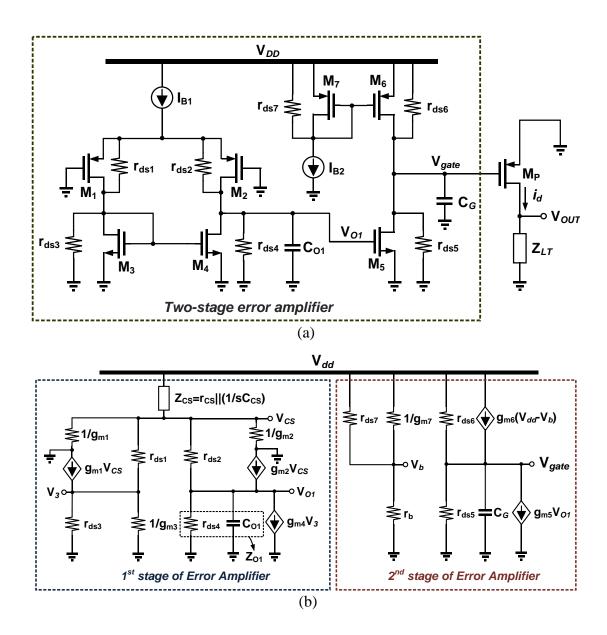

| Fig. 4.3.  | (a) Open-loop schematic of a conventional external capacitor-less LDO with frequency compensation for a two-stage error amplifier, and (b) its small-signal equivalent circuit.                                                                                                                   | 76  |

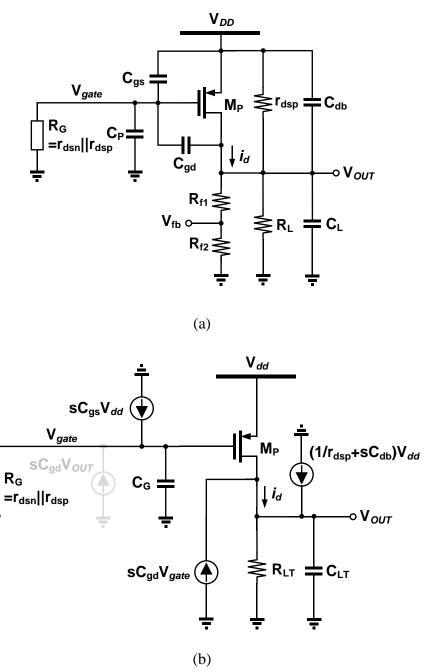

| Fig. 4.4.  | (a) High-frequency supply noise leakage due to the pass transistor of an LDO, and (b) small-signal equivalent with floating capacitors represented by grounded capacitors and voltage-controlled current sources.                                                                                 | 78  |

| Fig. 4.5.  | (a) Typical two-stage error amplifier, and (b) small signal model of error amplifier for PSRR                                                                                                                                                                                                     | 80  |

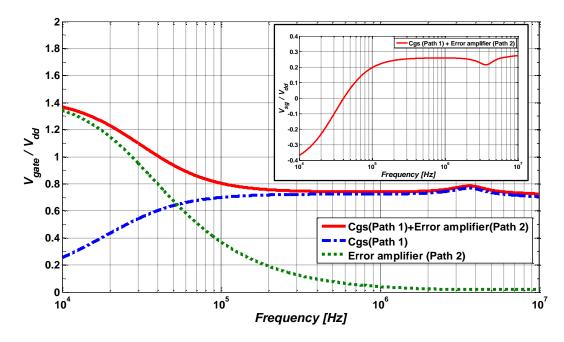

| Fig. 4.6.  | Simulated $V_{gate}/V_{dd}$ and $V_{sg}/V_{dd}$ of transistor $M_P$ due to $C_{gs}$ (Path 1), and the error amplifier (Path 2) in the direct paths                                                                                                                                                | 83  |

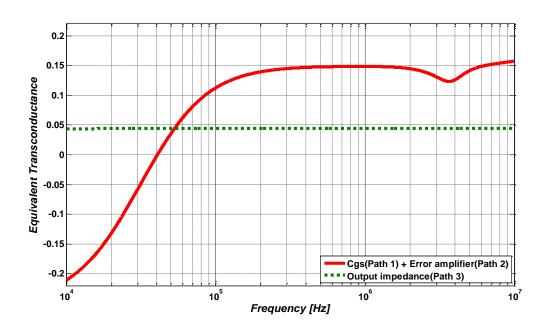

| Fig. 4.7.  | Simulated equivalent transconductances in the direct paths                                                                                                                                                                                                                                        | 84  |

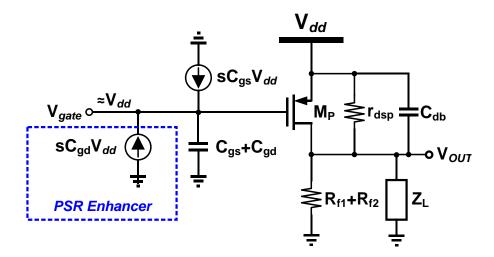

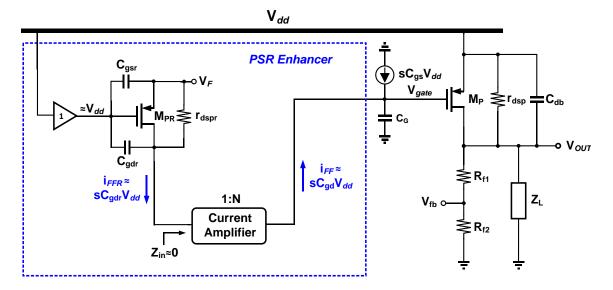

| Fig. 4.8.  | Small-signal model of the proposed PSR enhancement technique                                                                                                                                                                                                                                      | 86  |

| Fig. 4.9.  | Conceptual schematic of the proposed PSR enhancer                                                                                                                                                                                                                                                 | 87  |

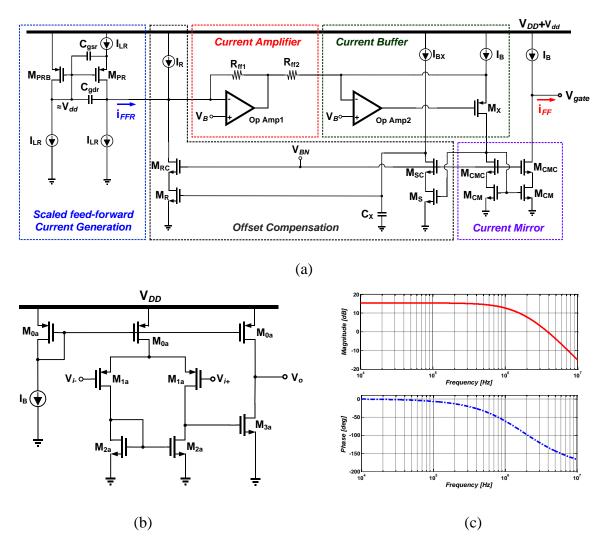

| Fig. 4.10. | (a) PSR enhancer circuitry, (b) schematic of the amplifier used in the current amplifier and current buffer, and (c) simulated Cadence open -loop AC response of Op Amp1 with $R_{ff1}$ =200 K $\Omega$ and $R_{ff2}$ =2 K $\Omega$ ; dominant pole is located at the gate of transistor $M_{3a}$ | 90  |

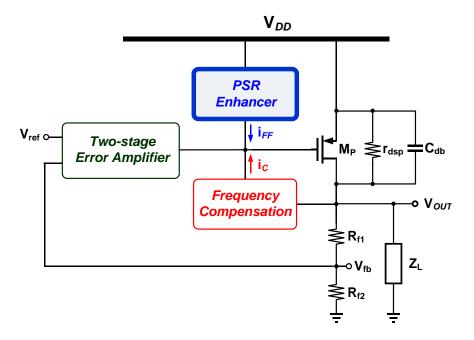

| Fig. 4.11. | Proposed PSR-compensated LDO architecture                                                                                                                                                                                                                                                         | .91 |

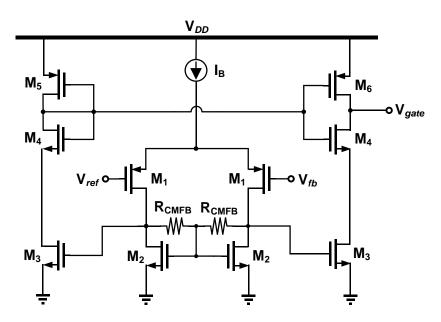

| Fig. 4.12. | Transistor-level implementation of the single-ended two-stage error amplifier with fully differential input stage                             | 92  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 4.13. | Frequency compensation and fast slew enhancement circuitry                                                                                    | 93  |

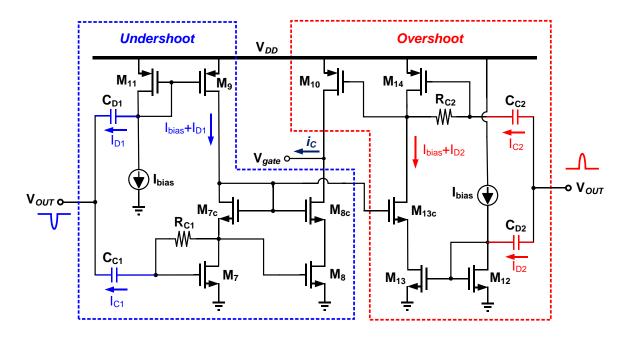

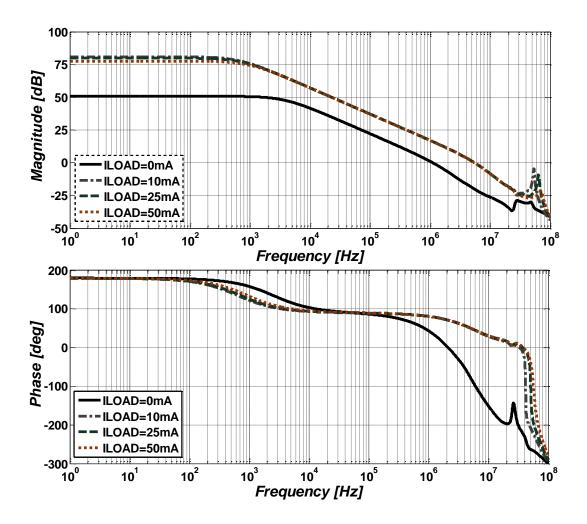

| Fig. 4.14. | Simulated full range open-loop AC response (0 – 50 mA)                                                                                        | 94  |

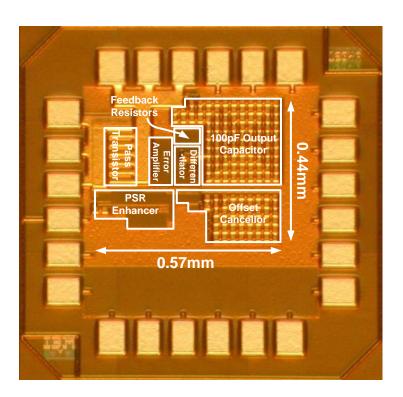

| Fig. 4.15. | Chip micrograph of the fabricated LDO with a total active area of 0.25 mm <sup>2</sup>                                                        | 98  |

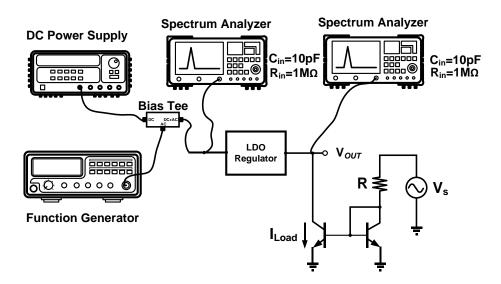

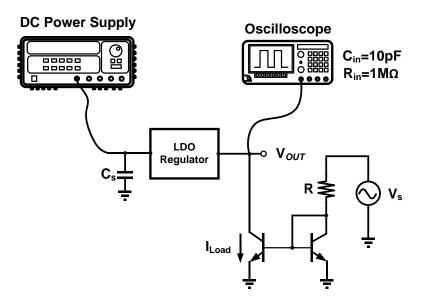

| Fig. 4.16. | Measurement set up for PSR                                                                                                                    | 99  |

| Fig. 4.17. | Measurement set up for load transient                                                                                                         | 100 |

| Fig. 4.18. | Measured PSR with and without the proposed PSR enhancer ( $I_{LOAD}$ =50 mA)                                                                  | 102 |

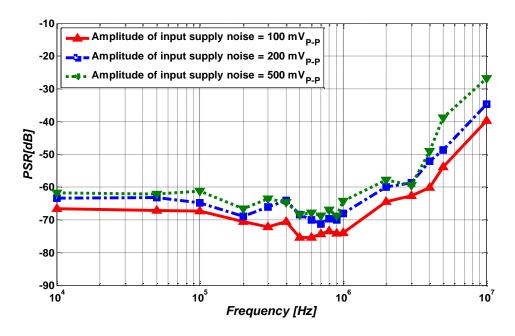

| Fig. 4.19. | Simulated PSR of the LDO with large power supply noises (I <sub>LOAD</sub> =50 mA)                                                            | 102 |

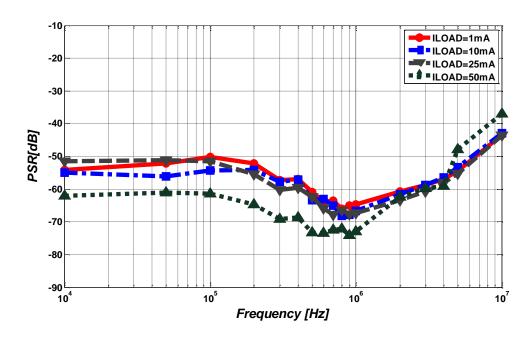

| Fig. 4.20. | Measured PSR with PSR enhancer for different load currents                                                                                    | 103 |

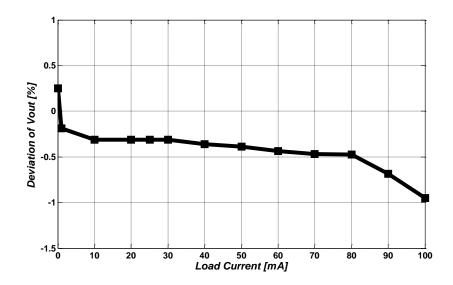

| Fig. 4.21. | Measured load regulation                                                                                                                      | 104 |

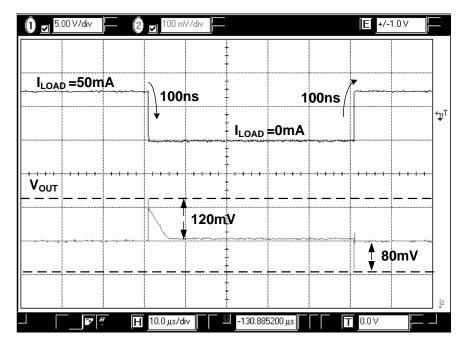

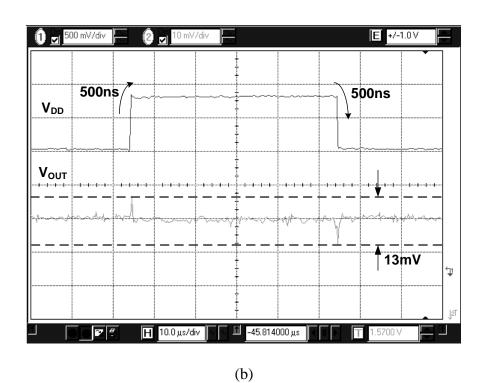

| Fig. 4.22. | (a) Measured load transient response for a load current step of 50 mA and (b) measured line transient response ( $I_{LOAD} = 50 \text{ mA}$ ) |     |

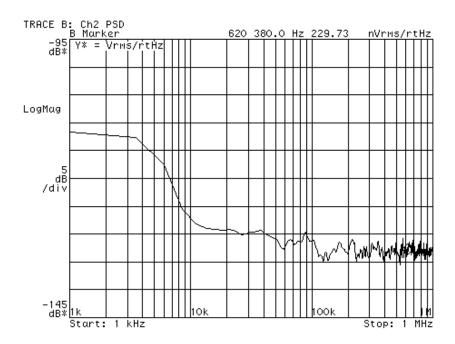

| Fig. 4.23. | Measured LDO output noise for I <sub>LOAD</sub> = 50 mA                                                                                       | 106 |

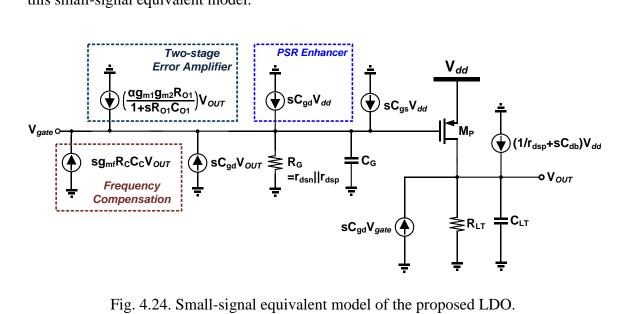

| Fig. 4.24. | Small-signal equivalent model of the proposed LDO                                                                                             | 109 |

## LIST OF TABLES

|               | Pag                                                                                                                                              | ţе |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table. II.1.  | System level design parameters                                                                                                                   | 4  |

| Table. II.2.  | Components values used in the implementation of the loop filter1                                                                                 | 8  |

| Table. II.3.  | Performance requirements of each stage of the loop filter                                                                                        | 0  |

| Table. II.4.  | Parameters of the Amplifier-I used in first stage of the loop filter2                                                                            | :7 |

| Table. II.5.  | Amplifier-I vs. Amplifier-II of the first stage of the loop filter2                                                                              | 9  |

| Table. II.6.  | The first stage of the loop filter w/o and with harmonic cancellation3                                                                           | 4  |

| Table. II.7.  | Performances of the second and third stages of the loop filter3                                                                                  | 6  |

| Table. II.8.  | Performance parameters of the 5 <sup>TH</sup> -order low-pass loop filter3                                                                       | 6  |

| Table. III.1. | Intra-die variability (with minimum dimensions) vs. CMOS technology node                                                                         | 8  |

| Table. III.2. | Voltage-mode summing vs. current-mode summing5                                                                                                   | 5  |

| Table. III.3. | Performance summary of the proposed current-mode adder-quantizer and comparison with prior adders and quantizers in CT $\Sigma\Delta$ modulators | 9  |

| Table. III.4. | Performance summary of the proposed current-mode flash ADC and comparison with prior works                                                       | С  |

| Table. IV.1.  | Dimensions and bias conditions of relevant transistors9                                                                                          | 7  |

| Table. IV.2.  | Performance summary for the proposed LDO and comparison10                                                                                        | 7  |

#### I. INTRODUCTION

#### I.1. Background and Motivation

Recently, trends in the microelectronics industry have resulted in a multitude of system-on chip (SoC) implementations in which analog and digital parts are integrated on the same die. Next generation wireless devices will have to support many different standards with a single chipset solution to reduce the cost of products and to increase the performance competitiveness of devices [1]. Generally, it is desirable to relax the specifications for most radio frequency (RF) front-end building blocks with new architectures and digitize the signal as close as possible to the antenna, which increases the demand for high-performance analog-to-digital converters (ADCs). Especially when weak fundamental signals are delivered along with strong interferers as in multi-standard applications, high performance ADCs are required for broadband connections of different wireless networks. However, the requirements of a large bandwidth, high operating frequency and high resolution make the design of ADCs very challenging. Since significant parts of the signal processing are performed in digital domain nowadays, sigma-delta ( $\Sigma\Delta$ ) ADCs have attracted a lot of attention as digital-friendly ADC implementations with high performance and good efficiency.

The transfer function of the analog loop filter in the  $\Sigma\Delta$  modulator defines the quantization noise-shaping behavior. Therefore, the performance of the analog loop filter is one of the main factors impacting the overall performance of the  $\Sigma\Delta$  modulator. The selection of the loop topology greatly affects the circuit implementation options for the analog loop filter. In general, two kinds of loop filter architectures are used for single-

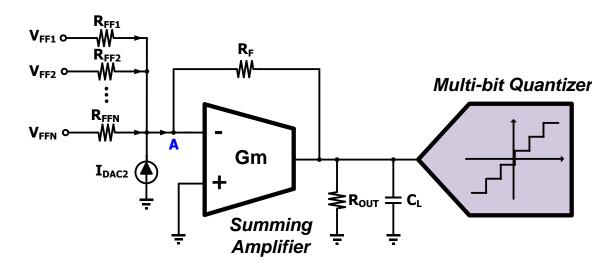

stage modulators. One is cascade of integrators with distributed feed-back (CIFB), and the other is a cascade of integrators with feed-forward summation (CIFF). Since the performance requirements of the subsequent stages can be relaxed compared to the first stages (at the input) in feed-forward architecture, the power consumption due to the non-critical blocks can be reduced. The CIFF requires only two accurate DACs, and the signal swing at the internal nodes of the modulator is relaxed with this architecture. However, the CIFF topology needs an additional summing stage to perform feed-forward summation for each integrator output. To guarantee loop stability, the additional summing stage should not add the extra delay. Hence, the implementation of a special summing scheme instead of the conventional voltage-mode summing stage can result in remarkable power savings.

Another SoC implementation challenge is that multi-standard SoC solutions are often designed with one or two shared power supplies for all analog/RF and digital blocks. Thus, SoC performances are frequently degraded due to the noises leaking through the supply of each building block. Therefore, high power supply rejection and low drop-out regulators are important building blocks in the single chip-set designed to establish a multi-standard solution to minimize the impacts of noises on system performance.

#### I.2. Design Issues

High-dynamic range  $\Sigma\Delta$  ADC can be achieved employing a high-order loop filter that shapes the in-band quantization noise. However, there are several noise sources including the quantization noise and non-idealities in the system. The non-idealities of continuous-time  $\Sigma\Delta$  ADCs include non-linearities from loop filter and multi-bit DAC,

excess loop delay and clock jitter. Since the  $\Sigma\Delta$  ADC's performance can be degraded by them, their effects should be considered with regards to circuit implementation.

#### *I.2.1.Non-linearities*

The harmonic distortion in-band due to introduced non-linearities of the circuits degrades the dynamic range of the ADC. In multi-bit  $\Sigma\Delta$  ADC, the major sources of non-linearities come from the loop filter and multi-bit DAC. First of all, any non-linearities of the loop filter directly get reflected at the output of the  $\Sigma\Delta$  ADC as a distortion. The non-linear Op-amps within the integrators contribute to the harmonic distortions, which degrade the resolution of the  $\Sigma\Delta$  ADC. Therefore, the non-linearities of the first loop filter stage dominate the linearity performance of the  $\Sigma\Delta$  ADC. Secondly, if multi-bit quantizers are employed in the  $\Sigma\Delta$  ADC, the current source mismatch in the multi-bit DAC generates the distortion. This distortion of the DAC also degrades the performance of the  $\Sigma\Delta$  ADC since the DAC is connected to the input stage, and harmonic distortion of the DAC will pass through the system as input signal without any noise shaping.

#### I.2.2. Excess loop delay

The building blocks in the  $\Sigma\Delta$  modulator including the comparator, the D flip-flops and the DACs all have propagation delay. The excess loop delay is referred to as a finite delay from the sampling clock edge to the change in the output at the feedback node. Since the modulator pulse response at the sampling instances is changed with the unwanted excess loop delay in the  $\Sigma\Delta$  modulator, the noise shaping transfer function is

changed. As shown in [2], the excess loop delay may eventually make the continuoustime  $\Sigma\Delta$  modulators unstable and degrade the performance of the  $\Sigma\Delta$  ADC. The excess loop delay is a major issue in high frequency operation due to decreasing use of the affordable excess loop delay. There are two different ways to compensate for decreasing performance of the excess loop delay. One is building a direct path around the quantizer. This direct feedback path with additional feedback DAC minimizes the impact of the excess loop delay [3]. Another is to add tunability by adopting a programmable delay compensation block in the main feedback path [4].

#### I.2.3. Blocker

Blockers are interferers that desensitize a circuit even if the gain does not fall to zero. Several blockers appear at the ADC input and even more will appear as the ADC moves closer to the antenna. High internal voltage swings in the presence of blockers tends to push the system into a nonlinear state. Intermodulation between strong out-of-band (OOB) blockers from ADC input and high-pass shaped noise from feedback causes noise folding over the desired channel. Hence, ADC performance is degraded.

There are several methods to improve blocker tolerances. In [5], the combination of a high-pass filter (HPF) in the feedback path and low-pass filter (LPF) in the feed-forward path is used in a continuous-time (CT)  $\Sigma\Delta$  ADC. For power savings, the reconfigurable  $\Sigma\Delta$  architectures employing the dynamic changing of the signal transfer function (STF) roll-off are suggested [6-8].

#### I.2.4. Jitter

There are random variations on the transition edge of a clock or in any oscillator waveform. These random variations are defined as clock jitter. Clock jitter causes a random variation in the pulse width of DACs, and it adds a random phase noise to the output. Wideband jitter modulates both signal and shaped quantization error and fills the signal band with white noise. Therefore, jitter noise is usually one of the important reasons for limited ADC resolution with high sampling frequency. Different DAC pulse shapes will result in different levels of jitter sensitivity. In other words, the jitter effect can directly relate to the number of clock transitions in DAC pulse shape. Since the transitions always happen in the settled condition of DAC feedback in the switchcapacitor type (SC) DAC used in the discrete-time (DT)  $\Sigma\Delta$  ADC, it has better performance on jitter than the switch-current DAC, e.g., return-to-zero (RZ), and the non-return-to-zero (NRZ) DACs in a CT  $\Sigma\Delta$  ADC. Therefore, the effects of clock jitter are a critical issue in a CT  $\Sigma\Delta$  ADC with a high-frequency sampling clock. The key to alleviating clock jitter effects is determining how to prevent the large level transition in feedback caused by DAC pulse shapes. Different signal shapes shown in [9] can prevent large level transitions such as those evidenced by square waves and compares between the several kinds of DAC pulse shapes.

#### I.3. Research Focus

The analog loop filter is a critical  $\Sigma\Delta$  modulator component because it defines the noise-transfer function (NTF) and thereby the quantization noise-shaping behavior. Furthermore, the stability of the  $\Sigma\Delta$  modulator mainly depends on the location of the

poles and zeros in the loop filter. Also, the noise and distortion introduced by the first stage of the loop filter directly appears at the output of  $\Sigma\Delta$  modulator without noise shaping and often limits the overall performance of the  $\Sigma\Delta$  modulator. Therefore, the loop filter is frequently the most critical block in a  $\Sigma\Delta$  modulator. To avoid limiting the overall performance due to the analog loop filter, the 5<sup>TH</sup>-order active-RC loop filter can perform at least to the order of 11-12 bits with less than 10 mW power consumption, which is implemented as part of a 20 MHz bandwidth (BW) low pass (LP) continuous-time (CT)  $\Sigma\Delta$  modulator in IBM 90 nm CMOS technology.

The summing amplifier in  $\Sigma\Delta$  ADCs requires wide bandwidth to guarantee stability of the system after compensating for the excess loop delay introduced by the parasitic poles of the filter's active components. In lieu of the power-hungry summing amplifier, a current-mode adder and quantizer are proposed to achieve low power  $\Sigma\Delta$  ADCs without degrading the entire ADC performances. The design issues of the summing amplifier are fully addressed and analyzed in this dissertation. In addition, the comparison between voltage-mode summing and current-mode summing is presented. The current-mode summing stage is followed by the current comparison stage and strongARM comparator with SR latches as a quantizer in the CT  $\Sigma\Delta$  modulator with feed-forward (FF) compensation. The current-mode flash ADC alleviates existing problems associated with voltage-mode flash ADCs, which are mainly related to voltage headroom restrictions, speed of operation, offsets, and power efficiency of the latches. The new design techniques are applied to the design of a 20 MHz BW  $5^{TH}$ -order LP CT  $\Sigma\Delta$  modulator

with FF compensation. The current-mode adder and quantizer are also implemented in IBM 90 nm CMOS technology.

Another focus in this research is to overcome the high frequency power supply rejection (PSR) limitation of external capacitor-less low drop-out (LDO) regulators. The fundamental PSR limitations due to the existing paths between the noisy supply and the output are analyzed, including the error amplifier and pass transistor, the gate-source parasitic capacitance, and finite output impedance. Although the feed-forward supply noise cancellation in high PSR LDOs is not a new approach, the LDO's performance can be maintained high under all loading conditions without requiring manual tuning by the technique presented in this dissertation. The parasitic capacitances of the pass transistor under the different loading conditions are precisely tracked by the PSR enhancement employing a replica pass transistor and a current amplifier. The robustness of the proposed scheme was demonstrated by measurement results. The proposed external capacitor-less LDO with PSR enhancement scheme was designed and fabricated in IBM 0.18 µm CMOS technology, and it achieved -40 dB PSR up to 8 MHz for all load conditions. Using the new PSR enhancement scheme, the PSR is improved more than 25 dB for 0.4 MHz - 4 MHz.

#### **I.4 Dissertation Organization**

This dissertation focuses on the design consideration of the analog and mixed-signal circuits for CT  $\Sigma\Delta$  ADCs in broadband applications. Furthermore, the design issues for external capacitor-less low drop-out regulators with high power supply rejection for SoC applications are analyzed prior to introducing the enhancement method.

An overview of the CT  $\Sigma\Delta$  modulator is given in Section II. The design considerations and implementation of a 5<sup>TH</sup>-order active-RC loop filter for a blockertolerant CT LP  $\Sigma\Delta$  ADC is also presented in Section II. The typical architecture of CT  $\Sigma\Delta$  modulators with FF compensation is explained in Section III along with the most important design issues related to weighted summing of the outputs of various loop filter nodes and the feedback signal from the direct path around the quantizer using the second DAC for minimizing the excess loop delay effects. In addition, a comparison between voltage-mode summing and current-mode summing is made. A current-mode adderquantizer for low-power CT  $\Sigma\Delta$  modulators is presented in Section III. Section IV introduces an external capacitor-less high PSR LDO regulator for SoC applications and analyzes its fundamental PSR limitations at high frequencies due to the paths through which supply noise can leak to the load. Section IV also provides a literature review of research by peers who were also determined to improve PSR of LDOs. Finally, the section offers an explanation, demonstration, and analysis of measured results showing how the innovative PSR compensation scheme can be used to overcome the lack of high PSR at high frequencies with a replica circuit that tracks the main supply noise under process-voltage-temperature (PVT) variations. Section V summarizes the contributions of this dissertation.

# II. $5^{TH}$ -ORDER ACTIVE-RC FILTER FOR BLOCKER TOLERANT CONTINUOUS-TIME SIGMA-DELTA MODULATORS

#### II.1. Background and Motivation

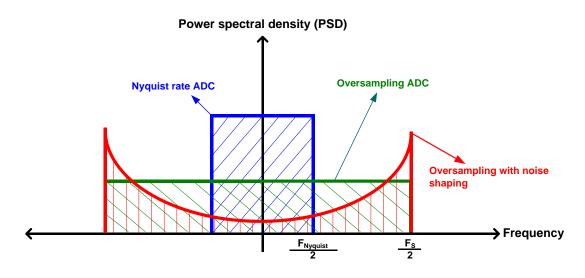

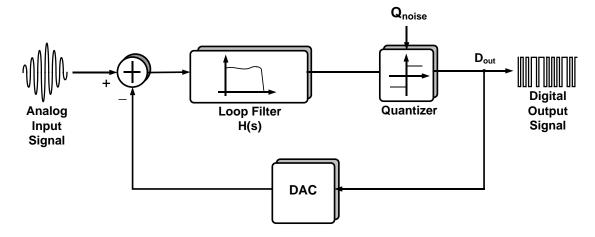

The basic principles of the sigma-delta ( $\Sigma\Delta$ ) analog-to-digital converter (ADC) are oversampling and noise-shaping [10]. Quantization noise is spread over the whole sampling frequency through oversampling. Since the quantization noise is shaped by the  $\Sigma\Delta$  operation, the in-band quantization noise is decreased while the out-of-band quantization noise is increased as shown in Fig. 2.1. Therefore,  $\Sigma\Delta$  ADCs can achieve high resolution by forming a closed-loop system with an embedded loop filter to reduce the number of bits required for the quantizer in the loop. Fig. 2.2 displays the typical block diagram of a single-bit  $\Sigma\Delta$  modulator. The loop transfer function and the proper loop topology are determined during system level design of the  $\Sigma\Delta$  modulator, which leads to the particular specifications for each building block.

Fig. 2.1. Power spectrum density of quantization noise

Fig. 2.2. Typical block diagram of single-bit  $\Sigma\Delta$  modulator

Recently, the trends of the wireless receiver architecture is to move the ADC as close as possible to the antenna by eliminating the pre-filtering and most of the signal processing is done in digital domain [7, 11-12]. This approach demands stringent DR requirements on the ADC. Since pre-filtering is removed in the receiver, strong OOB blockers occupy most of the ADC dynamic range. The blockers degrade the signal-to-noise ratio (SNR) of in-band signal and also destabilize the  $\Sigma\Delta$  loop by overloading it with huge signal swings [8]. A CT  $\Sigma\Delta$  modulator employing feedback (FB) loop architecture can increase the blocker tolerance since its signal transfer function (STF) has faster roll-off outside the signal bandwidth. However, FB topology mainly due to the several feedback DACs consumes more power and occupies more silicon area than their feed-forward (FF) counterparts. A CT  $\Sigma\Delta$  modulator employing feed-forward (FF) has unwanted OOB peaking and lower order STF roll-off outside the signal band. However, it consumes less power and has better area efficient than FB topology.

There are several approaches to improve blocker tolerances in previous researches [5]; i) the combination of a HPF in the feedback and a counter LPF in the feed-forward path in a CT  $\Sigma\Delta$  ADC [5]. However, this architecture demands stringent matching requirements between HPF and LPF in order to avoid the stability issue for high frequency operation. Furthermore, noise and linearity issues arise since these additional blocks are placed at the input of the modulator. ii) To save power consumptions, reconfigurable  $\Sigma\Delta$  architectures that dynamically change the STF roll-off depending on the blockers at the input were proposed in [7-8]. The solution reported in [7] monitors an internal node of the ADC to detect blockers and the loop order change is done by modifying the loop parameters. However, the reported approach is not very attractive for wireless applications due to its large time constants. The order of the ADC was reconfigured based on desired channel and interferer levels in [8]. A 5-bit flash ADC at the input of the ADC estimates the level of blocker power and digital signal processing (DSP). System instability may appear when strong agile blockers are present at the ADC input due to latency in DSP processing. Therefore, we proposed low power blocker tolerant CT LP  $\Sigma\Delta$  ADC which doesn't have stability issue due to complexity and latency.

## II.2. System-level Overview of the Blocker Tolerant CT LP $\Sigma\Delta$ ADC Architecture

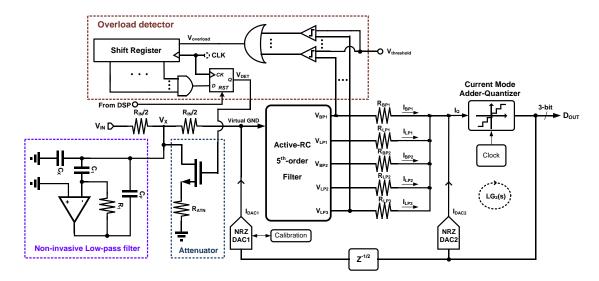

The system level block diagram of  $5^{TH}$ -order CT LP  $\Sigma\Delta$  modulator with overload detector and non-invasive low-pass filter is depicted in Fig. 2.3. The cascade of integrators in the feed-forward (CIFF) topology is employed in the loop filter and two feedback DACs are implemented in the feedback path [13]. An extra summing stage is

added to sum multiple feed-forward outputs of each integrator. Two current-steering 3bit unary weighted DACs are employed in the feedback path. Since the non-idealities of the main feedback DAC (DAC1) (due to unavoidable mismatches, parasitic capacitors and so on) appear at the ADC output without any noise shaping, a digitally-assisted current source calibration scheme is employed for DAC1 that has the most stringent requirements in terms of linearity and noise performance. In order to improve the blocker tolerance a non-invasive low-pass filter is employed at the input of the ADC. This filter can reduce the ADC input power by attenuating OOB blockers. The filter absorbs the OOB blocker power at the most critical frequencies, and it is built using a low-gain, high-bandwidth, class-AB amplifier that meets large signal performance requirements with good linearity and low power consumption [14]. Since OOB blockers cause peaking at internal nodes of the loop filter and overload the CT  $\Sigma\Delta$  ADC loop, an overload detection block is designed to detect peaking and avoid saturation of the ADC loop due to blockers. The employed wide-bandwidth overload detector and variable gain attenuator are very effective in detecting and attenuating the agile blockers. The overload detection system consists of a set of simple voltage level comparators, digital logic and a signal attenuator implemented with a T-network at the ADC input [14].

Fig. 2.3.  $5^{TH}$ -order CT LP  $\Sigma\Delta$  ADC architecture with overload detector monitoring the critical filter nodes and controlling the attenuator.

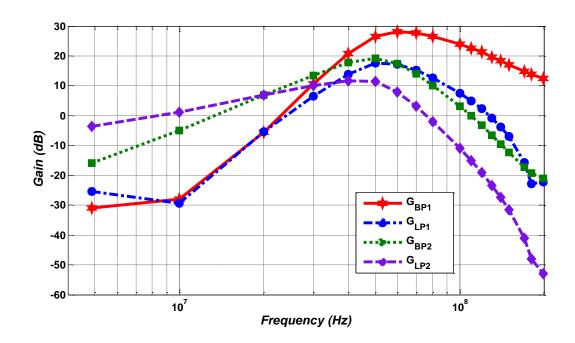

Since the CIFF topology has the highest sensitivity to peak effects due to blockers, it was selected to evaluate the proposed scheme for blocker tolerant CT LP  $\Sigma\Delta$  ADC. Fig. 2.4 displays the voltage gain at various filter nodes. In other words, the voltage gains are the direct trajectories from modulator input ( $V_{IN}$ ) to the integrator output nodes ( $V_{BP1}$ ,  $V_{LP1}$ ,  $V_{BP2}$ ,  $V_{LP2}$  or  $V_{LP3}$  in Fig. 2.3) of the loop filter that do not touch the loop, LG<sub>2</sub>. The closed-loop gain from  $V_{IN}$  to  $V_{XPi}$  is expressed as [14]:

$$G_{XPi}(j\omega) = FF_{XPi}(j\omega) \left(1 + K_{fb}H_D(j\omega)e^{-i\omega T_S}\right) NTF(j\omega), \qquad (2.1)$$

where  $FF_{XPi}$  (j $\omega$ ) is the open-loop voltage gain,  $K_{fb}$  is the coefficient of a secondary feedback DAC (DAC2), and  $H_D$  (j $\omega$ ) denotes the Laplace transform of the DAC output waveform. The important system level design parameters for CT LP  $\Sigma\Delta$  ADC are listed in Table II.1.

Fig. 2.4. Simulated the closed loop AC gain from input to the internal nodes of  $5^{TH}$ -order CT LP  $\Sigma\Delta$  ADC with FF compensation.

TABLE II.1 System level design parameters

| Parameter                             | Value      |

|---------------------------------------|------------|

| Technology                            | CMOS 90 nm |

| Supply Voltage                        | 1.2 V      |

| Resolution                            | 12 bits    |

| Signal Bandwidth                      | 20 MHz     |

| Sampling Frequency                    | 500 MHz    |

| Oversampling ratio (OSR)              | 12.5       |

| Order                                 | 5          |

| Resolution of Quantizer and DACs      | 3 bits     |

| · · · · · · · · · · · · · · · · · · · | ·          |

#### II.2.1. Design challenge of the loop filter

The design of the analog loop filter is a major challenge in the implementation of a high performance low-power CT LP ΣΔ ADCs In order to achieve high signal-toquantization-noise-ratio (SQNR), the analog loop filter should have high dynamic range [15] and a high-order to shape the in-band quantization noise. Conventionally, the loop filters of a CT  $\Sigma\Delta$  modulator are realized with active integrators, such as active-RC or G<sub>m</sub>-C integrators [16]. Active-RC integrators have the advantage of better linearity than G<sub>m</sub>-C integrators due to the closed-loop operation at high frequencies [17], but at the expense of more power consumption. Also, additional tuning circuitry is required due to the large deviation of RC time-constant with PVT variations in active-RC integrators. The finite gain and gain-bandwidth product (GBW) of the amplifiers cause the main non-idealities of active-RC integrators. Furthermore, circuit noise and distortion due to the amplifiers used in integrators degrade the performance of the  $\Sigma\Delta$  modulator. Especially, the first integrator limits the performances of the entire  $\Sigma\Delta$  modulator since its noise and distortion directly appear at the output of the  $\Sigma\Delta$  modulator. However, noise and distortion of the subsequent stages are shaped by the  $\Sigma\Delta$  loop. Hence, to achieve high performance, the first stage of a  $\Sigma\Delta$  modulator dissipates significant power consumption when compared to the overall power budget.

In the discussed example, the targeted ADC resolution is 12-bits over 20 MHz bandwidth (BW). To avoid limiting the overall performance, the loop filter should be able to perform at least to the order of 12 bits signal-to-noise and distortion rejection (SNDR). Since the analog loop filter introduces excess loop delay, the summing

amplifier has to have a wide bandwidth to guarantee stability of the system. Therefore, the design of a low-power summing stage in FF topology is another design challenge for the high-speed operation.

#### II.2.2. Filter transfer function

The most common method to design a CT  $\Sigma\Delta$  modulator is to first find the equivalent DT  $\Sigma\Delta$  modulator loop filter and then transform it to the continuous-time domain using an impulse invariant transformation (IIT) [18]. After impulse invariant transformation, the s-domain open-loop transfer function is expressed as

$$\begin{aligned} & \text{H(s)} \\ & = \frac{(1.224 \times 10^9)s^4 + (4.398 \times 10^{17})s^3 + (1.113 \times 10^{26})s^2 + (1.66 \times 10^{34})s + (1.221 \times 10^{42})}{s^5 + (6.681 \times 10^7)s^4 + (1.822 \times 10^{16})s^3 + (8.015 \times 10^{23})s^2 + (6.594 \times 10^{31})s + (1.454 \times 10^{39})} \end{aligned}$$

where the pole frequencies in the design discussed in this section are located at 10MHz, 18MHz, and 3.26MHz, respectively.

$$STF = \frac{H(s)}{1 + H(s)} \tag{2.3}$$

$$NTF = \frac{1}{1 + H(s)} \tag{2.4}$$

The corresponding transfer functions, STF, NTF and FF, are depicted in Fig. 2.5. The loop filter with feed-forward paths has 5 poles and 4 zeros. Since the poles in  $FF_{ff}(s)$  coincide with the zeros of the NTF and cancel out each other,  $FF_{ff}(s)$  exhibits first-order OOB blockers roll-off at higher frequencies around and beyond the unity gain frequency. Moreover, the  $STF_{ff}$  displays flat in-band response.

Fig. 2.5. Transfer functions in feed-forward (FF) architecture

## **II.3.** Loop Filter Architecture

The  $5^{TH}$ -order transfer function of the loop filter is realized using FF architecture. As shown in Fig. 2.6; it consists of a cascade of two second-order loop biquad stages and a first-order integrator stage. The outputs of each stage are combined through multiple FF paths with a summing stage. The first stage of the loop filter is the most demanding stage because noise and distortion requirements for the first stage of the loop filter and the main feedback DAC (DAC1) have a strong impact on the overall performance of the entire  $\Sigma\Delta$  modulator. As a result, a large transconductance ( $G_m$ ) of the input stage of amplifiers used in the first stage of the loop filter is needed for noise minimization. In addition, high loop gain and large bias currents in the first stage are necessary for high linearity and tolerance to the loading from the main feedback DAC (DAC1). The loop

filter consists of the three stages. The cut-off frequencies of the first and second stages of loop biquad are placed at 10 MHz and 18 MHz, respectively. The cut-off frequency of the third integrator stage is 3.26 MHz.

Fig. 2.6. 5<sup>TH</sup>-order active-RC loop filter

The components values used in the loop filter are listed in Table II.2.

TABLE II.2 COMPONENTS VALUES USED IN THE IMPLEMENTATION OF THE LOOP FILTER

|              | Parameter Value    |          |  |  |

|--------------|--------------------|----------|--|--|

|              | $R_{\rm IN1}$      | 800 Ω    |  |  |

| T'           | $R_{F11}, R_{F12}$ | 10.4 KΩ  |  |  |

| First stage  | R <sub>Q1</sub>    | 31.2 K Ω |  |  |

|              | $C_{11}, C_{12}$   | 1.405 pF |  |  |

| Second stage | R <sub>IN2</sub>   | 4 ΚΩ     |  |  |

|              | $R_{F21},R_{F22}$  | 22.4 ΚΩ  |  |  |

|              | $R_{Q2}$           | 134.4 ΚΩ |  |  |

|              | $C_{21}, C_{22}$   | 0.37 pF  |  |  |

|              | $R_{IN3}$          | 8 ΚΩ     |  |  |

| Third stage  | $R_{F3}$           | 48 ΚΩ    |  |  |

|              | C <sub>3</sub>     | 1.003 pF |  |  |

Since the desired in-band signal in a  $\Sigma\Delta$  modulator is processed by the loop filter, having a very linear loop filter is necessary. Any non-linearities in the loop filter will appear as spurs in the output spectrum of the modulator. All in-band noise corrupts the desired signal content. The most critical noise and distortion for the overall performance of the loop filter are introduced by the first stage of the loop filter. Since the nonidealities of second and third stages are noise shaped by the previous (first) stage, their performance requirements are relaxed. The thermal noise floor of the amplifier used in the first stage of the loop filter should be lower than the quantization noise for optimal performance of the  $\Sigma\Delta$  modulator. To tolerate the presence of strong blockers at the input of the ADC, the third-order inter-modulation (IM3) of the amplifier in the first stage of the loop filter is important. An amplifier with high pass-band gain and high bandwidth is required in the first stage of the loop filter. With 20 MHz signal bandwidth and 500 MHz sampling frequency, the bandwidth requirement of the amplifier used in the very first integrator was determined as over 1 GHz with system-level simulations. Also, a DC-gain of about 50 dB is necessary for low in-band distortion in the discussed system design. The loop filter must employ fully-differential circuitry to minimize sensitivity to supply and substrate noise coupling. The important performance requirements of the 5<sup>TH</sup>-order loop filter are listed in Table II.3.

TABLE II.3

PERFORMANCE REQUIREMENTS OF EACH STAGE OF THE LOOP FILTER

| Block           | Order | DC-gain | Cut-off<br>frequency | Quality<br>Factor | Noise, SNR |

|-----------------|-------|---------|----------------------|-------------------|------------|

| First stage     | 2     | 26 dB   | 10 MHz               | 3                 | > 74 dB    |

| Second stage    | 2     | 15 dB   | 18 MHz               | 6                 | > 62 dB    |

| Third stage     | 1     | 15 dB   | 3.26 MHz             | -                 | > 52 dB    |

| Complete Filter | 5     | 56 dB   | 20 MHz               | -                 | > 74 dB    |

### II.3.1. Second-order loop biquad

The first and second stages of the loop filter are implemented with the same two-integrator loop configuration, which is the summed-feedback type (depicted in Fig. 2.7). The summed-feedback structure provides band-pass (BP) and low-pass (LP) outputs that are independently controlled in the filter. Assuming that the amplifiers provide large gain, the transfer functions can be expressed as follows:

$$\frac{V_{BP}}{V_{IN}} = \frac{sC_2R_2\left(\frac{R_1}{R_{IN}}\right)}{1 + sC_2\left(\frac{R_1R_2}{R_0}\right) + s^2C_1C_2R_1R_2}$$

(2.5)

$$\frac{V_{LP}}{V_{IN}} = \frac{\left(\frac{R_1}{R_{IN}}\right)}{1 + sC_2\left(\frac{R_1R_2}{R_0}\right) + s^2C_1C_2R_1R_2}$$

(2.6)

The design parameters can be obtained by:

$$DC Gain(A_0) = \frac{R_1}{R_{IN}}$$

(2.7)

Quality Factor (Q) =

$$\frac{R_Q}{\sqrt{R_1 R_2}} \sqrt{\frac{C_1}{C_2}}$$

(2.8)

Cut\_off Frequency

$$(\omega_0) = \sqrt{\frac{1}{R_1 R_2 C_1 C_2}}$$

(2.9)

DC-gain ( $A_O$ ) and the quality factor (Q) of the biquad are determined by the ratio of resistors, and the cut-off frequency ( $\omega_O$ ) can be tuned using a variable resistor or capacitor. Therefore, the values of the resistors ( $R_{IN}$ ,  $R_1$ ,  $R_2$ , and  $R_Q$ ) and capacitors ( $C_1$  and  $C_2$ ) in the biquadratic section can be determined according to the DC-gain and quality factor requirements. However, since thermal noise of the first stage directly appears at the output of the modulator, it should be minimized. The input-referred noise of the biquad can approximately be expressed as:

$$V_{\text{in}_{n}}^{2} = 4kTR_{\text{IN}} \left[ 1 + \frac{R_{\text{IN}}}{R_{1}} + \frac{R_{\text{IN}}}{R_{Q}} \right] + 4kTR_{2}|sC_{2}R_{2}|^{2}$$

$$+ \left[ V_{n\_\text{amp\_I}}^{2} + V_{n\_\text{amp\_II}}^{2}|sC_{2}R_{2}|^{2} \right] \left| \frac{R_{\text{IN}}}{R_{Q}} + sC_{1}R_{\text{IN}} \right|^{2}$$

(2.10)

where  $V_{n,amp\_I}^2$  and  $V_{n,amp\_II}^2$  are the input-referred noise of the first and second amplifiers of the biquad, respectively. The first amplifier (Amplifier-I) and input resistor ( $R_{IN}$ ) of the biquad are the main noise contributors at low frequencies. The value of  $R_{IN}$  is selected based on the noise requirement, and the value of the other resistors and capacitors is determined from the loop filter specifications and using equation (2.7)-(2.9).

Fig. 2.7. Two integrator loop biquad.

### *II.3.2 First-order integrator*

As shown in Fig. 2.8, the lossy integrator is realized with a first-order integrator of the third stage in the loop filter. Assuming that the amplifier provides large gain, the transfer function can be expressed as follows:

$$\frac{V_{OUT}}{V_{IN}} = \left(\frac{R_F}{R_{IN}}\right) \left(\frac{1}{1 + sR_FC_1}\right)$$

(2.11)

The design parameters can be obtained as:

$$DC Gain(A_0) = \frac{R_F}{R_{IN}}$$

(2.12)

Cut\_off Frequency

$$(\omega_0) = \frac{1}{R_F C_1}$$

(2.13)

The values of resistor ( $R_{IN}$ ,  $R_F$ ) and capacitor ( $C_1$ ) are determined from the loop filter specifications, gain and bandwidth, and using equations (2.12)-(2.13). The integrator time constants can vary due to PVT variations of absolute values of resistors and capacitors. In order to compensate for PVT variations, the capacitor banks that can

provide  $\pm 30\%$  tuning range are implemented for each capacitor of the loop filter to adjust the location of the pole implemented by the integrator.

Fig. 2.8. First-order integrator for the third stage of the loop filter.

# II.4. Amplifier

The thermal noise floor of the amplifier used in the first stage of the loop filter should be lower than the quantization noise for optimal performance of the modulator. To tolerate the presence of strong blockers at the input of the ADC, IM3 of the amplifier in the first stage of the loop filter is important. An amplifier with high pass band gain and high bandwidth is required in the first stage of the loop filter. With 20 MHz signal bandwidth and 500 MHz sampling frequency, the bandwidth requirement of the amplifier used in the very first integrator was determined as 1 GHz with system-level simulations. Also, a DC-gain of about 50 dB is necessary for low in-band distortion. The filter must employ fully-differential circuitry throughout to minimize sensitivity to supply and substrate noise coupling.

### II.4.1. Amplifier architecture

The amplifier used in the first integrator stage needs to satisfy high gain and bandwidth requirements, which are contradicting design requirements. High-gain amplifiers typically use multi-stage architectures with long channel length devices at low bias current levels. High-bandwidth amplifiers typically use single-stage architectures with short-channel devices at high bias current levels.

Fig. 2.9. The block diagram of a two-stage amplifier with FF compensation.

To satisfy the high gain and bandwidth requirements simultaneously, a two-stage amplifier with FF compensation is adopted [19]. Fig. 2.9 displays the block diagram of a two-stage amplifier with FF compensation. The overall voltage transfer function of the amplifier can also be expressed as follows:

$$H(s) = \frac{(G_{m1}R_{01})(G_{m2}R_{02})}{(1 + sR_{01}C_{01})(1 + sR_{02}C_{02})} + \frac{G_{mFF}R_{02}}{(1 + sR_{02}C_{02})}$$

(2.14)

Assuming that  $G_{m2}=G_{mFF}$ , equation (2.14) can be simplified as:

$$H(s) = \{G_{m2}R_{O2}(1 + G_{m1}R_{O1})\} \left\{ \frac{1 + \frac{sR_{O1}C_{O1}}{(1 + G_{m1}R_{O1})}}{(1 + sR_{O1}C_{O1})(1 + sR_{O2}C_{O2})} \right\}$$

(2.15)

With this FF technique, the negative phase shift introduced by the poles in the forward path is compensated by the positive phase shift introduced by the LHP zero in the feed-forward path. Because a LHP zero is created without using any Miller capacitor, the dominant pole is not pushed to lower frequencies. Therefore, a higher gain-bandwidth product with fast step response can be achieved. Also, the settling time requirement of the first amplifier is the most demanding due to feedback DAC.

# II.4.2. Circuit implementation

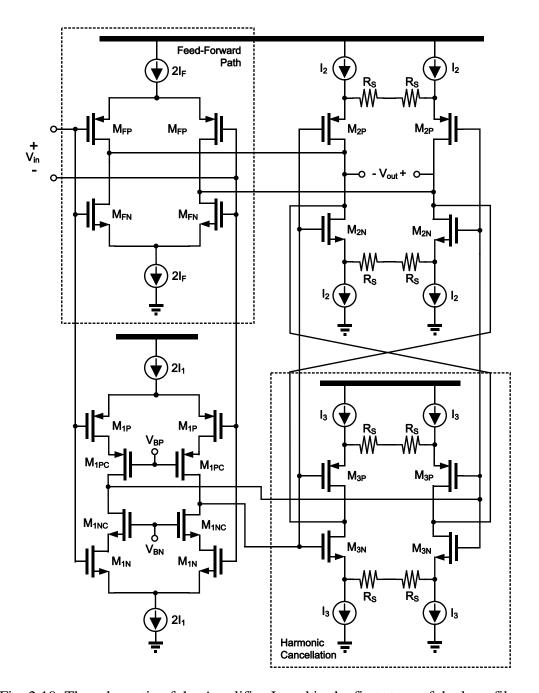

The fully-differential circuit implementation of the amplifier is shown in Fig. 2.10. The first and the feed-forward stages are the main contributors to the input-referred thermal noise of the amplifier. To reduce the input-referred noise aspect and increase the gain, the transconductance  $(G_m)$  and output resistance of the first stage should be increased. Since the output swing of the first stage of the amplifier does not have to be high because the signal is further amplified by the gain of the second stage, a cascode stage and a complementary input stage were selected. The second and feed-forward stages are optimized for high bandwidth and medium gain performance. The transconductance  $(G_m)$  of the second and feed-forward stages should be increased as much as possible to the push poles to higher frequencies. For better linearity, the second and feed-forward stages also has to be large. That is why we use the complementary stage in second and feed-forward stages. Also, we use an additional differential pair connected in antiparallel with second stage and source degeneration technique to improve the linearity [20].

Fig. 2.10. The schematic of the Amplifier-I used in the first stage of the loop filter.

The auxiliary circuit is designed such that its main transconductance  $(G_m)$  is smaller than the transconductance  $(G_m)$  of the second stage. However, its third harmonic distortion is designed to be similar to that of the second stage transistor such that the cross-coupling circuitry partially cancels the harmonic distortion of the second stage. The DC common-mode levels at the output of the first and second stage of the amplifier are set to 0.6 V, and they are controlled by a common-mode feedback circuit (CMFB) for each stage. The amplifier was optimized with respect to stability, noise, linearity, and power. The parameters of Amplifier-I used in the first stage of the loop filter are listed in Table II.4.

TABLE II.4

PARAMETERS OF THE AMPLIFIER-I USED IN THE FIRST STAGE OF THE LOOP FILTER.

|                   |                   | Dimension (W/L) | Bias current (µA) |

|-------------------|-------------------|-----------------|-------------------|

|                   | $M_{1P}$          | 60 μm / 200 nm  | 200 μΑ            |

| First             | M <sub>1PC</sub>  | 60 μm / 200 nm  | 200 μΑ            |

| stage             | M <sub>1NC</sub>  | 24 μm / 300 nm  | 200 μΑ            |

|                   | $M_{1N}$          | 24 μm / 300 nm  | 200 μΑ            |

| Second            | $M_{2P}$          | 144 μm / 200 nm | 400 μΑ            |

| stage             | $M_{2N}$          | 42 μm / 300 nm  | 400 μΑ            |

| Feed-forward      | $M_{FP}$          | 136 µm / 200 nm | 400 μΑ            |

| stage             | $M_{\mathrm{FN}}$ | 40 μm / 300 nm  | 400 μΑ            |

| Anti- parallel    | $M_{3P}$          | 36 μm / 200 nm  | 100 μΑ            |

| stage             | $M_{3N}$          | 10 μm / 300 nm  | 100 μΑ            |

| $R_{\rm s}$       |                   | 20 Ω            |                   |

| $V_{\mathrm{BP}}$ |                   | 0.4 V           |                   |

| $V_{ m BN}$       |                   | 0.8 V           |                   |

The second integrator of the first stage in the loop filter employs the same amplifier structure, but was designed to consume less power. From the third to the fifth integrator of the loop filter, the same amplifier structure is employed except that the linearization technique is removed and the power consumption is reduced.

## II.4.3. Simulation results of the amplifiers

The loop gain was simulated by considering the loading of the amplifier in the twointegrator loop biquadratic structure as shown in Fig. 2.11.

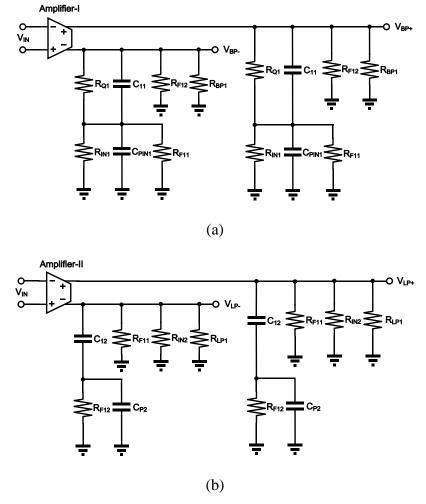

Fig. 2.11. Amplifiers test-bench with loading (a) Amplifier-I, and (b) Amplifier-II.

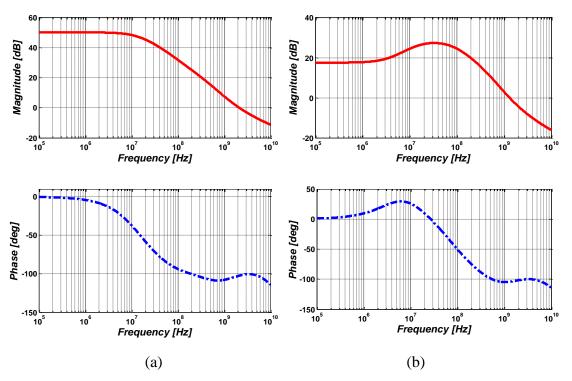

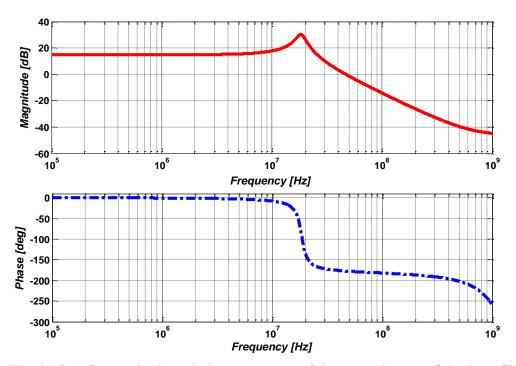

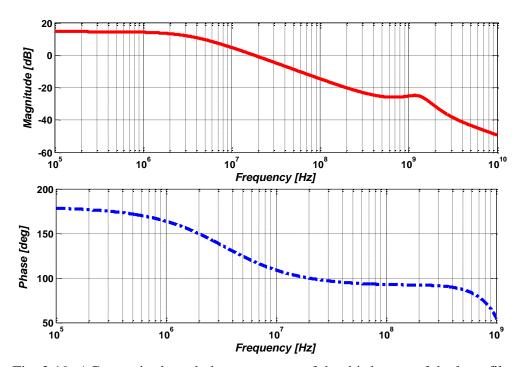

Fig. 2.12 and Fig. 2.13 display simulated AC magnitude and phase response plot of the Amplifier-I and Amplifier-II used in the first stage of the loop filter, yielding the following results: i) Amplifier-I (Fig. 2.12): the phase margin is 77° at the unity gain frequency of 2.1 GHz. It has an open-loop DC gain of 50 dB while the voltage gain is 45 dB at 20MHz. ii) Amplifier-II (Fig. 2.13): the phase margin is 84° at the unity gain frequency of 2.7 GHz. It has an open-loop DC gain of 47 dB, while the voltage gain is 43 dB at 20 MHz. The performances of the Amplifier-I and Amplifier-II of the first stage of the loop filter are summarized in Table II.5.

TABLE II.5

AMPLIFIER-I VS. AMPLIFIER-II OF THE FIRST STAGE OF THE LOOP FILTER

|                                                                                           | Amplifier-I      | Amplifier-II     |

|-------------------------------------------------------------------------------------------|------------------|------------------|

| Open-loop DC gain                                                                         | 50 dB            | 47.43 dB         |

| Gain bandwidth product                                                                    | 2.1 GHz          | 2.7 GHz          |

| Input referred integrated noise density (Up to 20 MHz and Temperature = $80  ^{\circ}$ C) | 13.33 uV         | 14.57 uV         |

| Phase Margin                                                                              | 77 degree        | 84 degree        |

| Spot noise (@ 20 MHz and Temperature = $80  ^{\circ}$ C)                                  | 2.52 nV/sqrt(Hz) | 2.87 nV/sqrt(Hz) |

| Power consumption                                                                         | 2.64 mW          | 2.11 mW          |

Fig. 2.12. (a) Open-loop gain, and (b) loop gain of Amplifier-I.

Fig. 2-13. (a) Open-loop gain, and (b) loop gain of Amplifier-II.

# II.5. Layout and Results

# II.5.1. Layout

The microphotograph of the entire CT  $\Sigma\Delta$  ADC including all the building blocks is shown in Fig. 2.14. The active area of the entire CT LP  $\Sigma\Delta$  ADC occupies 0.43 mm<sup>2</sup> silicon area (shown in Fig. 2.14(a)). The total area of the 5<sup>TH</sup>-order loop filter occupies approximately 0.22 mm<sup>2</sup> (shown in Fig. 2.14(b)). The CT LP  $\Sigma\Delta$  ADC including the loop filter was designed and fabricated in a 90 nm CMOS technology.

Fig. 2.14. (a) CT LP  $\Sigma\Delta$  ADC chip microphotograph, and (b) layout of the 5<sup>TH</sup>-order LP loop filter.

### II.5.2. Simulation results

# II.5.2.1. The first stage of the loop filter

The simulation results for the first stage of the loop filter are presented in this section. Fig. 2.15 displays the AC magnitude and phase responses of the first stage of the loop filter. The DC-gain of the first stage of the loop filter is 26 dB, and its quality factor is 3. The cut-off frequency of the first stage in the loop filter is 10 MHz.

Fig. 2.15. AC magnitude and phase response of the first stage of the loop filter.