### FREQUENCY SYNTHESIS IN WIRELESS AND WIRELINE SYSTEMS

A Dissertation

by

# DIDEM ZELIHA TÜRKER

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

December 2010

Major Subject: Electrical Engineering

### FREQUENCY SYNTHESIS IN WIRELESS AND WIRELINE SYSTEMS

### A Dissertation

by

### DIDEM ZELIHA TÜRKER

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Edgar Sánchez-Sinencio |

|---------------------|------------------------|

| Committee Members,  | Jose Silva-Martinez    |

|                     | Costas N. Georghiades  |

|                     | Sıla Çetinkaya         |

| Head of Department, | Costas N. Georghiades  |

December 2010

Major Subject: Electrical Engineering

#### ABSTRACT

# Frequency Synthesis in Wireless and Wireline Systems. (December 2010) Didem Zeliha Türker, B.S., Sabanci University Chair of Advisory Committee: Dr. Edgar Sánchez-Sinencio

First, a frequency synthesizer for IEEE 802.15.4 / ZigBee transceiver applications that employs dynamic True Single Phase Clocking (TSPC) circuits in its frequency dividers is presented and through the analysis and measurement results of this synthesizer, the need for low power circuit techniques in frequency dividers is discussed.

Next, Differential Cascode Voltage-Switch-Logic (DCVSL) based delay cells are explored for implementing radio-frequency (RF) frequency dividers of low power frequency synthesizers. DCVSL flip-flops offer small input and clock capacitance which makes the power consumption of these circuits and their driving stages, very low. We perform a delay analysis of DCVSL circuits and propose a closed-form delay model that predicts the speed of DCVSL circuits with 8% worst case accuracy. The proposed delay model also demonstrates that DCVSL circuits suffer from a large low-to-high propagation delay ( $\tau_{PLH}$ ) which limits their speed and results in asymmetrical output waveforms. Our proposed enhanced DCVSL, which we call DCVSL-R, solves this delay bottleneck, reducing  $\tau_{PLH}$  and achieving faster operation.

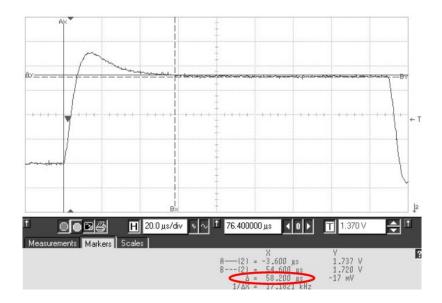

We implement two ring-oscillator-based voltage controlled oscillators (VCOs) in  $0.13\mu$ m technology with DCVSL and DCVSL-R delay cells. In measurements, for the same oscillation frequency (2.4GHz) and same phase noise (-113dBc/Hz at 10MHz), DCVSL-R VCO consumes 30% less power than the DCVSL VCO. We also use the proposed DCVSL-R circuit to implement the 2.4GHz dual-modulus prescaler of a low power frequency synthesizer in  $0.18\mu$ m technology. In measurements, the synthesizer exhibits -135dBc/Hz phase noise at 10MHz offset and 58 $\mu$ m settling time with 8.3mW

power consumption, only 1.07mW of which is consumed by the dual modulus prescaler and the buffer that drives it. When compared to other dual modulus prescalers with similar division ratios and operating frequencies in literature, DCVSL-R dual modulus prescaler demonstrates the lowest power consumption.

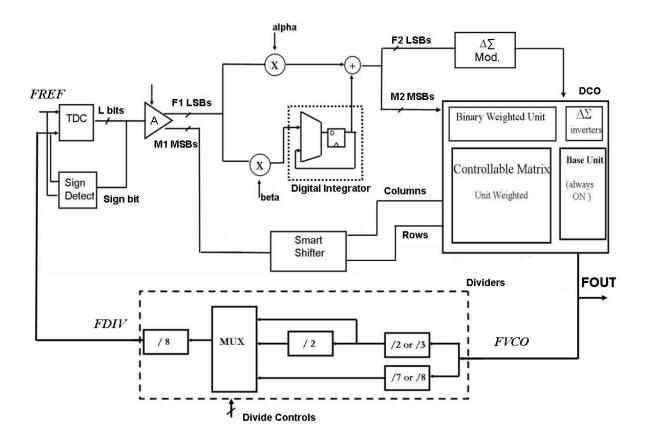

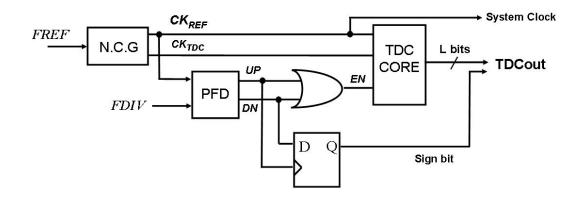

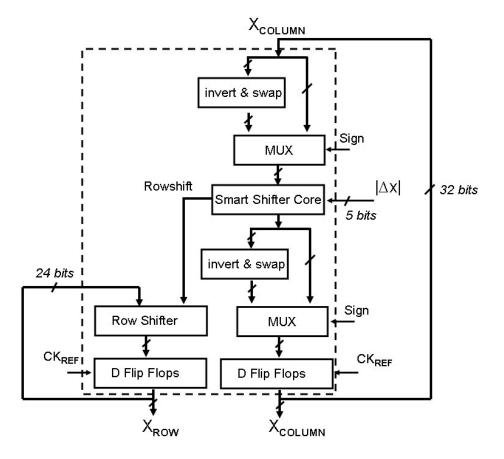

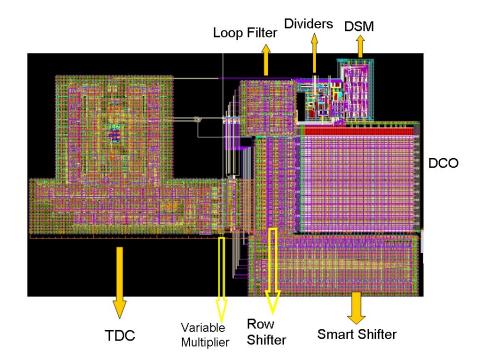

An all digital phase locked loop (ADPLL) that operates for a wide range of frequencies to serve as a multi-protocol compatible PLL for microprocessor and serial link applications, is presented. The proposed ADPLL is truly digital and is implemented in a standard complementary metal-oxide-semiconductor (CMOS) technology without any analog/RF or non-scalable components. It addresses the challenges that come along with continuous wide range of operation such as stability and phase frequency detection for a large frequency error range. A proposed multi-bit bidirectional smart shifter serves as the digitally controlled oscillator (DCO) control and tunes the DCO frequency by turning on/off inverter units in a large row/column matrix that constitute the ring oscillator. The smart shifter block is completely digital, consisting of standard cell logic gates, and is capable of tracking the row/column unit availability of the DCO and shifting multiple bits per single update cycle. This enables fast frequency acquisition times without necessitating dual loop filter or gear shifting mechanisms.

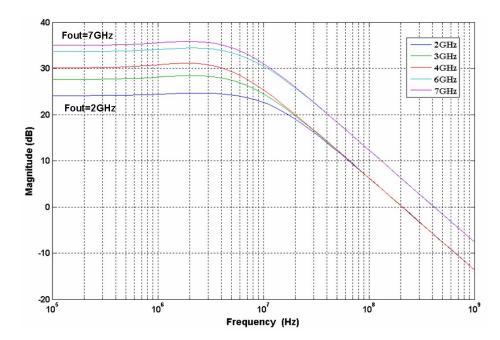

The proposed ADPLL loop architecture does not employ costly, cumbersome DACs or binary to thermometer converters and minimizes loop filter and DCO control complexity. The wide range ADPLL is implemented in 90nm digital CMOS technology and has a 9-bit TDC, the output of which is processed by a 10-bit digital loop filter and a 5-bit smart shifter. In measurements, the synthesizer achieves 2.5GHz-7.3GHz operation while consuming 10mW/GHz power, with an active area of 0.23  $mm^2$ .

To my mom Hülya, my dad Yalvaç, and my sister Dilsad

&

To Zeki and Maya

#### ACKNOWLEDGMENTS

I was very lucky to be surrounded by wonderful people who helped and supported me throughout my studies at Texas A&M University. I am grateful to my advisor Dr. Edgar Sánchez-Sinencio, for his invaluable guidance, encouragement and support throughout the years. His vision, experience, knowledge and enthusiasm in research and in life, has been and will be a constant source of inspiration for me.

I would like to thank my advisory committee Dr. Jose Silva-Martinez, Dr. Costas N. Georghiades and Dr. Sıla Çetinkaya for their valuable support, discussion and suggestions.

I am very grateful to Dr. Yusuf Leblebici, my academic advisor during my undergraduate studies, for introducing me to the exciting area of microelectronics and circuit design. His wonderful teaching and encouragement is the reason why I decided to continue my studies and dared to start working towards a Ph.D. in this field.

I would like to thank Dr. Alexander Rylyakov from IBM T.J. Watson Research Center, for his valuable guidance. His excitement for his work, openness and desire to share his wealth of knowledge with others, is such an inspiration for me and his feedback and discussions have been an invaluable source of support in my research.

I would also like to thank Dr. Sunil P. Khatri for his valuable discussions and suggestions. It was in his class, that we came up with an idea that motivated and enabled a valuable portion of my research. I am humbled by his kindness and support.

I thank Texas Instruments for their kind support throughout my Ph.D.

My years of studies at the AMSC would not have been the same without the wonderful Ms. Ella Gallagher. Her spirit has always been a constant source of joy in our office and her strict rules and planning creates an organized and successful office environment for the students and the professors in our group. As I leave AMSC, I will miss her dearly.

I would like to thank Tammy Carda, our department's senior academic advisor, for her valuable help and kindness throughout the years.

I had the opportunity to meet many wonderful colleagues at the AMSC throughout the years. I would like to thank Rangakrishnan Srinivasan, whom I worked with in several projects during my Ph.D. and who has been a wonderful friend to me for many years. I thank Sang Wook Park for the many discussions we had on our research and for his valuable support and feedback. I also thank Alberto Valdes-Garcia for the many valuable discussions we had but most importantly for being such a dear friend. I thank Sathya Venkatesh for being such a good friend whose strength, positivity and wit have always impressed me. I would also like to thank my friends and colleagues Felix O. Fernandez, Hesam Aslanzadeh, Raghavendra Kulkarni, Manisha Gambhir, Chinmaya Mishra, David Hernandez, Faisal Hussien, Erik Pankratz, Jorge Zarate, Mohammed Mohsen, Seenu Gopalraju and Adrian Colli-Menchi. They have not only impressed me with their brightness, but also have been good friends to me.

I also met wonderful friends in College Station throughout the years. I would like to thank Baris Gunersel, Paola Guerrero and Selcuk Dincal for their beautiful friendship and support. We shared unforgettable memories and College Station would not have been the same without them.

I would like to thank my friends from Turkey; Hanife, Buke, Kivilcim, Burcu, Cigdem, Mehmet, Tuba, Mukaddes, Baris and Emrah whose support throughout the years meant a lot to me. I would like to thank my family. I am grateful to my parents Hülya and Yalvaç Türker and my sister Dilsad Karacabey, whose unconditional love and support is behind every achievement I had in my life, big or small. They always made sure that I know, that wherever I am, however far I may be from them, they are always with me, in my heart. Anything that I accomplish in my life is because of them.

I thank my dear nephew Kaan and my little nephew that I can't wait to welcome into the world, and my brother in law Tolga Karacabey, for their love and support. I thank my dear Lucy; her memory will always be in my heart and I will never forget that she was what I dreamt for throughout my childhood. I miss her everyday. I would also like to thank my late grandfather Mustafa Özcan; his hardwork, kindness and his love for life and his family has always inspired me to push myself in my career and in life. My late grandfather Ramazan Türker for teaching me that true success comes from being hardworking, honorable and honest. Their memories are always with me. I also thank my grandmother and my namesake Zeliha Türker, for always believing in me and her endless love and support. My grandmother Nebahat Özcan for showing me that kindness and love are the key behind a happy life and family. I thank all of them with all my heart.

Finally, I would like to thank my dear Zeki and my lovely Maya. Maya's unconditional love, innocence, sweetness and her wonderful heart has been a constant reminder of what the most important things in life are. I thank Zeki, with all my heart, for being my constant source of support, for his endless love, kindness and patience. Words cannot express how grateful I am that they are in my life, and how much I love them. I know that when I am with them, I am home.

# TABLE OF CONTENTS

| ABSTRACT   | ۱<br>                                                                                                 | iii                                                                |

|------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| ACKNOWL    | EDGMENTS                                                                                              | vi                                                                 |

| TABLE OF   | CONTENTS                                                                                              | ix                                                                 |

| LIST OF FI | GURES                                                                                                 | xi                                                                 |

| LIST OF TA | BLES                                                                                                  | viii                                                               |

| CHAPTER    |                                                                                                       |                                                                    |

| Ι          | INTRODUCTION                                                                                          | 1                                                                  |

|            | A. Motivation and Contributions                                                                       | 1                                                                  |

|            | B. Overview                                                                                           | 4                                                                  |

| II         | A FULLY INTEGRATED FREQUENCY SYNTHESIZER<br>FOR ZIGBEE APPLICATIONS                                   | 6                                                                  |

|            | <ul> <li>A. IEEE 802.15.4 / ZigBee</li> <li>B. Frequency Synthesis for a ZigBee Transceiver</li></ul> | 6<br>7<br>10<br>18<br>18<br>20<br>22<br>24<br>27<br>32<br>34<br>37 |

| III        | FREQUENCY DIVIDER CIRCUITS AND A NEW DCVSL-<br>R DELAY CELL                                           | 40                                                                 |

|            | <ul> <li>A. Frequency Divider Circuit Techniques</li></ul>                                            | 40<br>42<br>45<br>45                                               |

|     | <ol> <li>Model Accuracy</li> <li>Process Variations</li> <li>Process Variations</li> <li>Discussion on DCVSL Delay Behavior</li> <li>Droposed DCVSL-R Circuit</li> </ol> | 52<br>55<br>55<br>57                                                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| IV  | A LOW POWER FREQUENCY SYNTHESIZER WITH DCVSL-<br>R DIVIDERS                                                                                                              | 63                                                                                        |

|     | A. Implementation                                                                                                                                                        | 63<br>67<br>71                                                                            |

| V   | RING OSCILLATORS USING DCVSL AND DCVSL-R DE-<br>LAY CELLS                                                                                                                | 75                                                                                        |

|     | A. Ring Oscillator DesignB. Measurement ResultsC. Performance Evaluation                                                                                                 | 76<br>77<br>86                                                                            |

| VI  | ALL DIGITAL PHASE LOCKED LOOPS                                                                                                                                           | 88                                                                                        |

|     | A. Background and Motivation                                                                                                                                             | 88<br>89<br>95<br>99                                                                      |

| VII | A WIDE RANGE ALL DIGITAL PLL                                                                                                                                             | 102                                                                                       |

|     | <ul> <li>A. Previous Work</li></ul>                                                                                                                                      | $102 \\ 104 \\ 108 \\ 109 \\ 112 \\ 118 \\ 121 \\ 127 \\ 128 \\ 131 \\ 133 \\ 141 \\ 146$ |

|     | 1. Standard Cell Design                                                                                                                                                  | 147                                                                                       |

|          | <ol> <li>Power Supply Distribution</li></ol>                                                                       |    |

|----------|--------------------------------------------------------------------------------------------------------------------|----|

| VIII     | CONCLUSIONS                                                                                                        | 57 |

|          | A. Summary                                                                                                         |    |

| REFERENC | $EES \dots $ | 62 |

| APPENDIX | A                                                                                                                  | 73 |

| APPENDIX | B                                                                                                                  | 90 |

| VITA     |                                                                                                                    | 00 |

## LIST OF FIGURES

| FIGURE |                                                                                                                                                              | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Block diagram of a standard transceiver system                                                                                                               | 9    |

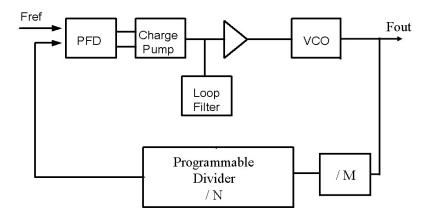

| 2      | Block diagram of the ZigBee frequency synthesizer                                                                                                            | 12   |

| 3      | Second order loop filter of the charge-pump based PLL                                                                                                        | 13   |

| 4      | Block diagram of a divide-by-2 frequency divider                                                                                                             | 19   |

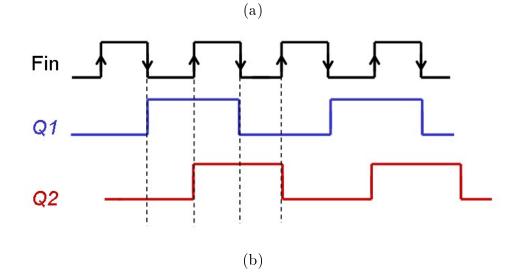

| 5      | Divide-by-2 operation (a) state diagram (b) input and output timing                                                                                          | 20   |

| 6      | Block diagram of a divide-by-3 frequency divider                                                                                                             | 21   |

| 7      | State table of a divide-by-3 frequency divider                                                                                                               | 22   |

| 8      | Block diagram of a dual modulus divide-by-3/4 frequency divider $$ .                                                                                         | 23   |

| 9      | Block diagram of the NOR based divide-by-3/4 circuit $\ .$                                                                                                   | 24   |

| 10     | Block diagram of a pulse-swallow programmable divider $\ldots$                                                                                               | 25   |

| 11     | Block diagram of the P counter and S block $\ldots \ldots \ldots \ldots \ldots$                                                                              | 27   |

| 12     | Dual modulus (15/16) prescaler block diagram                                                                                                                 | 28   |

| 13     | State table of the 15/16 prescaler                                                                                                                           | 29   |

| 14     | Circuit-level simulations of glitch in divide-by-3/4 circuit at 2.4GHz operation (a) using regular TSPC logic (b) using glitch-free TSPC logic               | 30   |

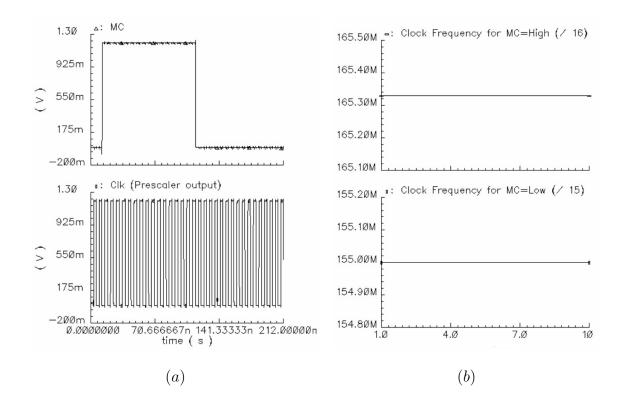

| 15     | Post-layout simulations of $15/16$ prescaler circuit at 2.48GHz operation                                                                                    | n 31 |

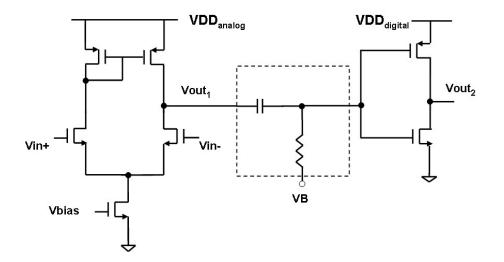

| 16     | Schematic of the differential to single ended buffer, the bias-T circuit to set proper common mode level and the first inverter of the inverter chain buffer | 32   |

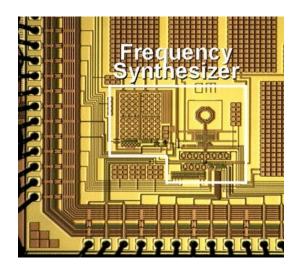

| 17     | Die micrograph of the frequency synthesizer                                                                                                                  | 34   |

| FIGU | JRE |

|------|-----|

|------|-----|

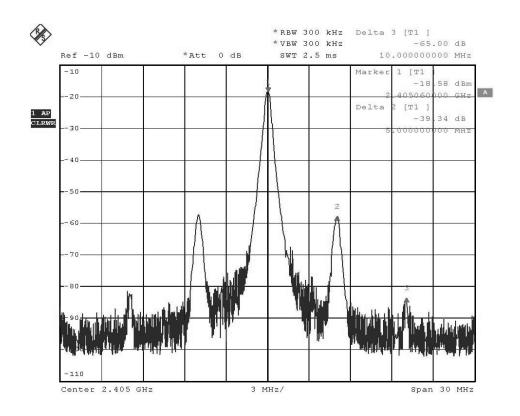

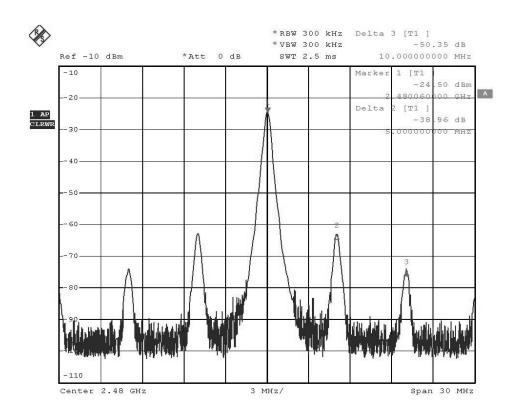

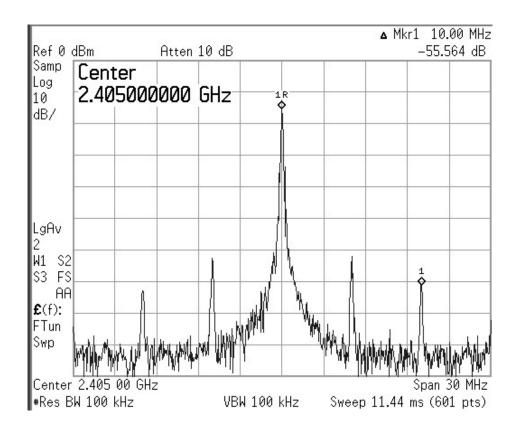

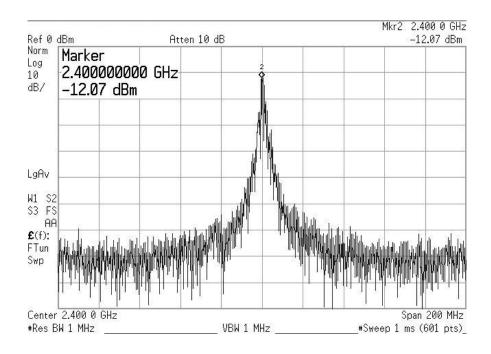

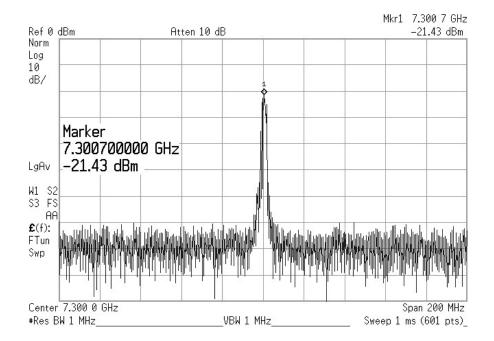

| 18 | Measured output spectrum of the synthesizer demonstrating first channel of ZigBee                                                                                                    | 35 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

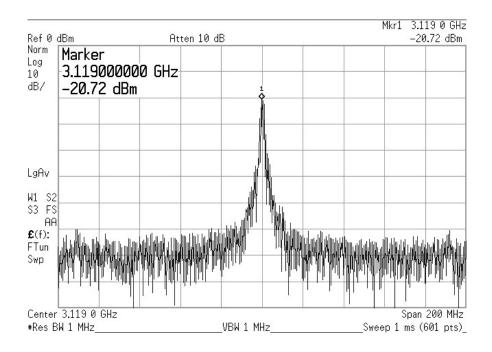

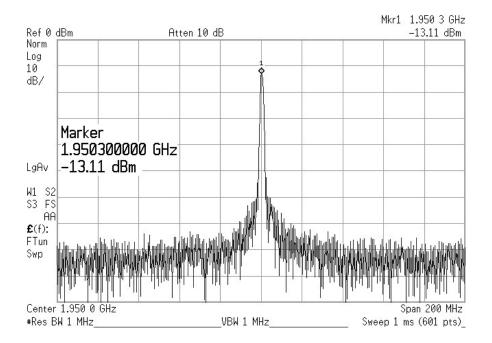

| 19 | Measured output spectrum of the synthesizer for channel 16 of ZigBee $$                                                                                                              | 36 |

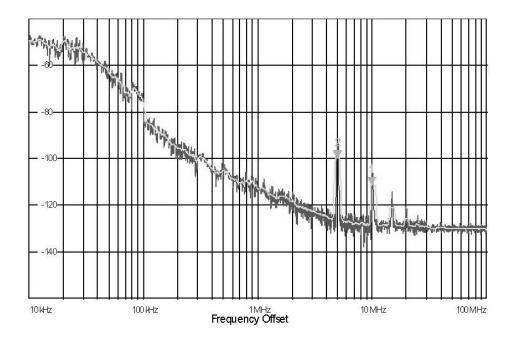

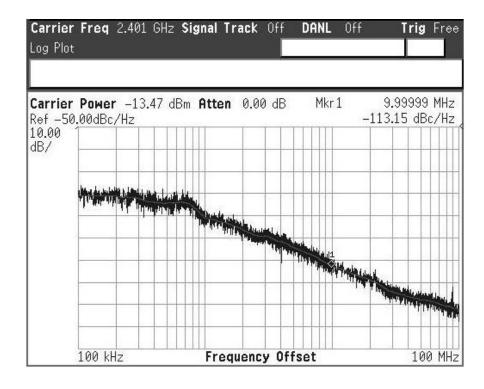

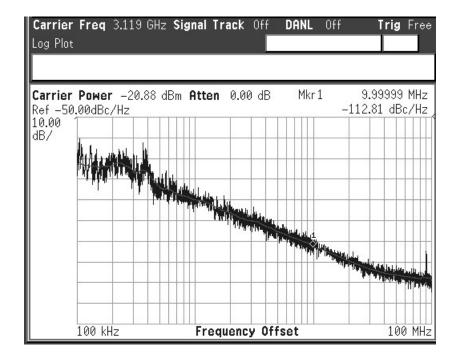

| 20 | Phase noise spectrum of the frequency synthesizer                                                                                                                                    | 36 |

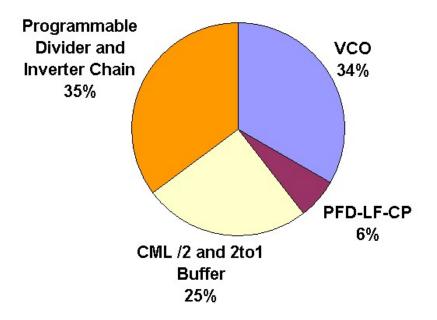

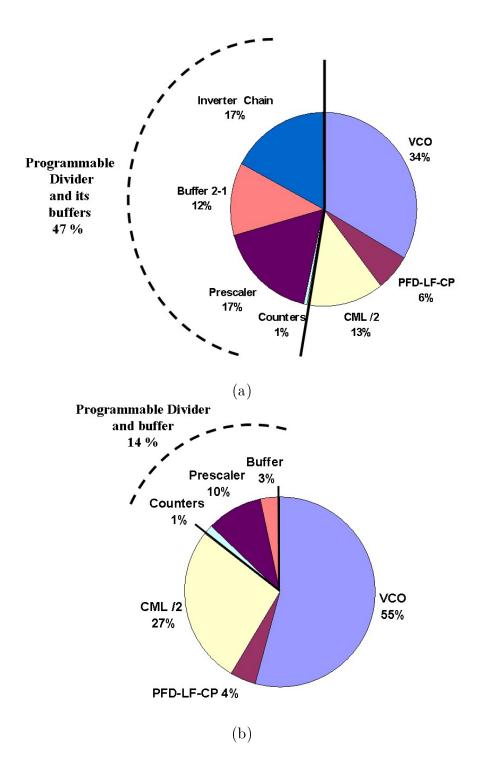

| 21 | Pie chart of the measured power consumption distribution in the ZigBee synthesizer                                                                                                   | 38 |

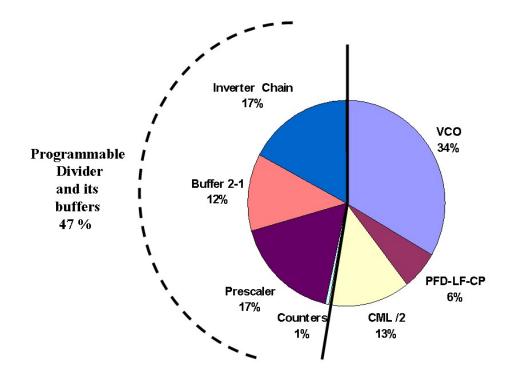

| 22 | Pie chart of the power consumption distribution in the ZigBee synthesizer with individual frequency divider blocks                                                                   | 39 |

| 23 | Schematic of a CML latch                                                                                                                                                             | 41 |

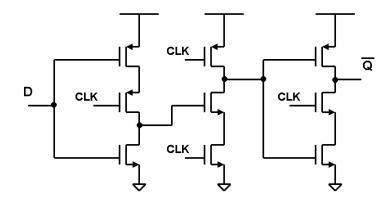

| 24 | Schematic of a TSPC D-flip-flop                                                                                                                                                      | 42 |

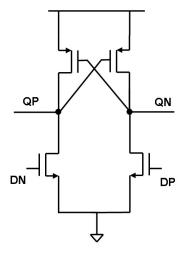

| 25 | Schematic of a DCVSL inverter                                                                                                                                                        | 43 |

| 26 | Two-clock-phase DCVSL flip-flop                                                                                                                                                      | 45 |

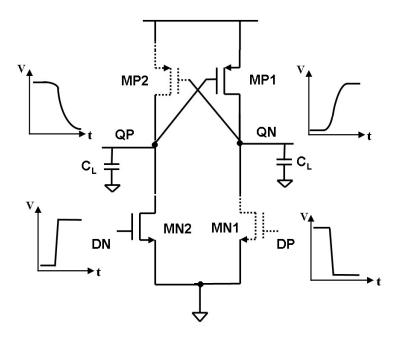

| 27 | DCVSL inverter setup for transient delay analysis                                                                                                                                    | 46 |

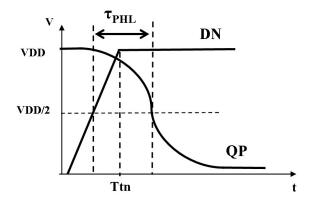

| 28 | Propagation delay derivation for $\tau_{PHL}$                                                                                                                                        | 47 |

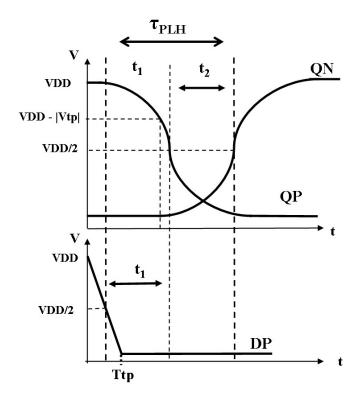

| 29 | Propagation delay derivation for $	au_{PLH} = t_1 + t_2 \dots \dots \dots \dots$                                                                                                     | 49 |

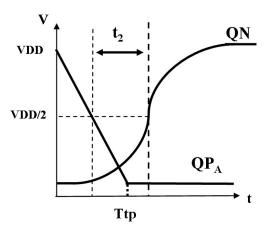

| 30 | Approximation of $t_2$                                                                                                                                                               | 50 |

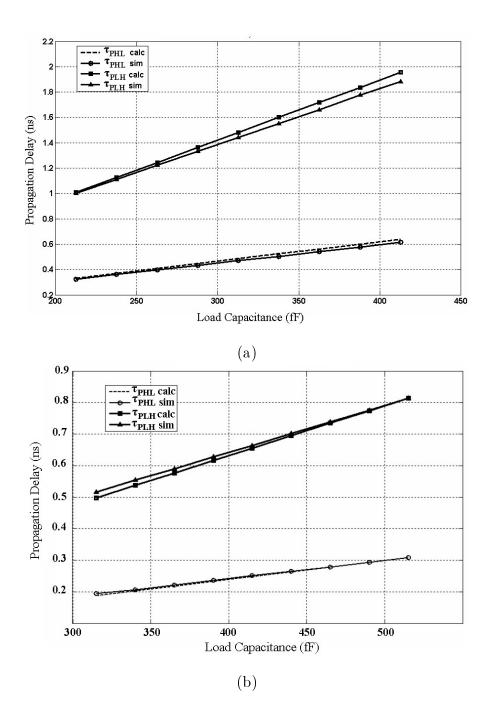

| 31 | Comparison of calculated vs. simulated values of $\tau_{PLH}$ and $\tau_{PHL}$<br>(a) for (WP/WN)=1.33 in 0.18 $\mu$ m technology (b) for (WP/WN)=1.57<br>in 0.13 $\mu$ m technology | 53 |

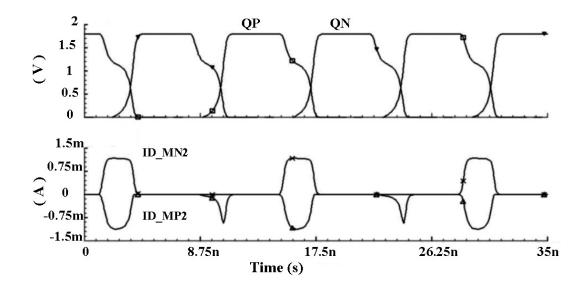

| 32 | Simulated voltage and current waveforms of a DCVSL inverter in 0.18 $\mu$ m for WP/WN=3, demonstrating mid-transition slow-down $~$ .                                                | 56 |

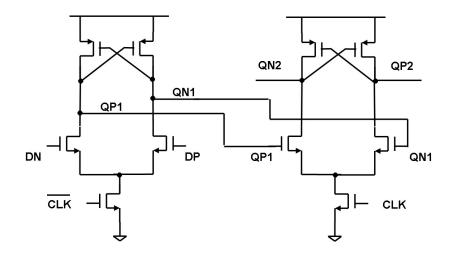

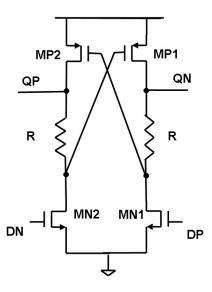

| 33 | Proposed DCVSL-R circuit                                                                                                                                                             | 57 |

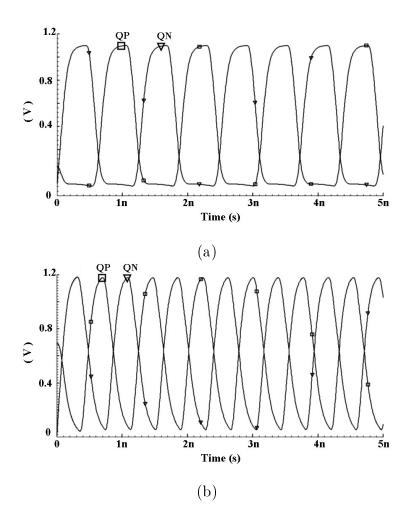

| 34 | Inverter output waveforms in a ring oscillator setting for WP/WN=1 (a) for conventional DCVSL (b) for proposed DCVSL-R with $R=380$ ohms                                             | 50 |

|    | $\Pi = 300 0 \Pi \Pi S \dots \dots$                                                        | 59 |

| FI | GU | RE |

|----|----|----|

|----|----|----|

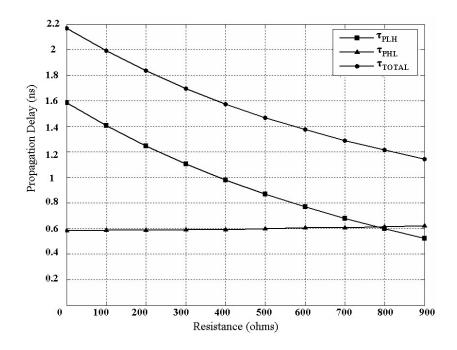

| 35 | Circuit-level simulation results for $\tau_{PLH}$ , $\tau_{PHL}$ and $\tau_{TOTAL}$ values vs. the resistance R for a DCVSL-R inverter with (WP/WN)=1.66 in 0.18 $\mu$ m technology                              | 60 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 36 | Circuit-level simulation of propagation delay vs. the resistance R for a DCVSL-R inverter with $(WP/WN)=1.66$ in $0.18\mu$ m technology for values of R past the point of symmetry $\ldots \ldots \ldots \ldots$ | 62 |

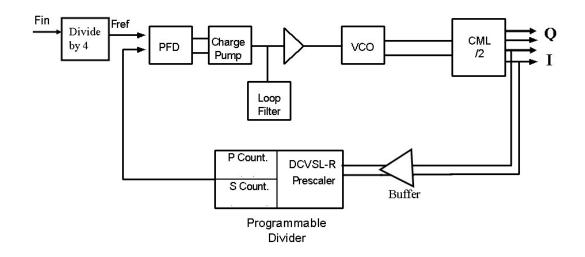

| 37 | Block diagram of the new PLL with DCVSL-R divider $\ldots$ .                                                                                                                                                     | 64 |

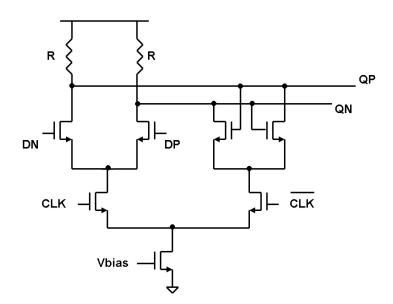

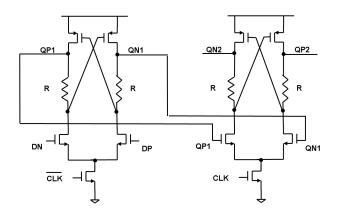

| 38 | Circuit level diagram of D flip-flops used in the DCVSL-R based prescaler                                                                                                                                        | 66 |

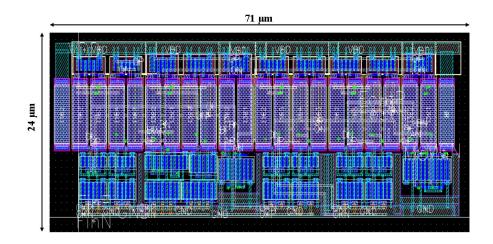

| 39 | Layout of the DCVSL-R based dual modulus (15/16) prescaler $~$                                                                                                                                                   | 66 |

| 40 | Output frequency spectrum of the new synthesizer with DCVSL-<br>R dividers at 2.405GHz                                                                                                                           | 68 |

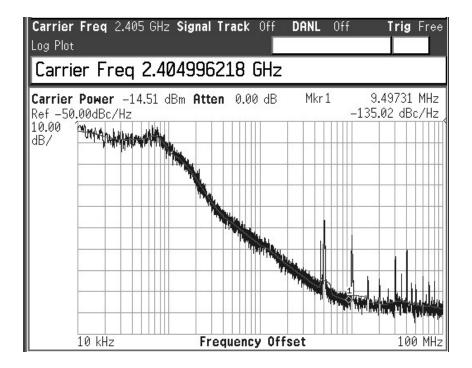

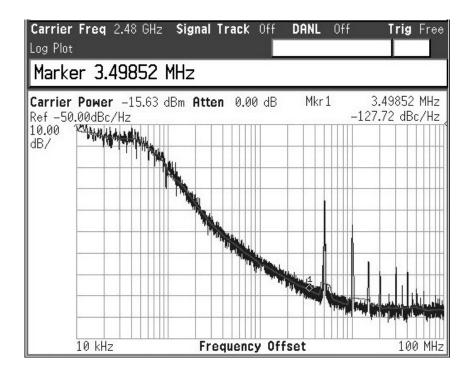

| 41 | Phase noise spectrum of the new synthesizer at $2.405 \text{GHz}$                                                                                                                                                | 69 |

| 42 | New frequency synthesizer measured phase noise spectrum at $2.48 \text{GHz}$                                                                                                                                     | 69 |

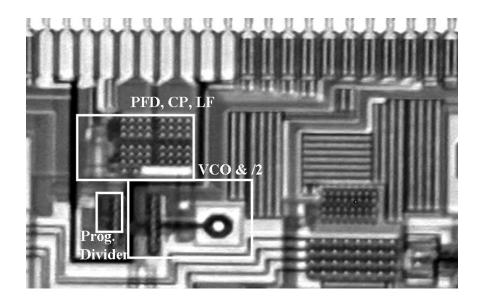

| 43 | Die micrograph of the new PLL                                                                                                                                                                                    | 70 |

| 44 | New frequency synthesizer measured settling time                                                                                                                                                                 | 70 |

| 45 | Power consumption distribution of the synthesizer with TSPC dividers and the new synthesizer with DCVSL-R dividers                                                                                               | 74 |

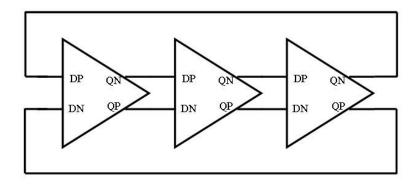

| 46 | Block diagram of the three stage ring oscillators                                                                                                                                                                | 75 |

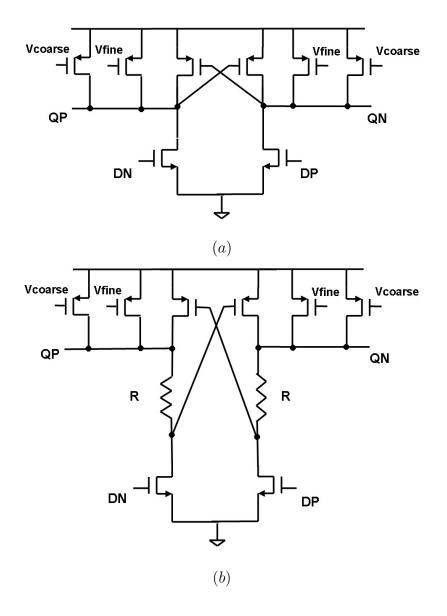

| 47 | VCO delay cells (a) conventional DCVSL for OSC1 (b) proposed<br>DCVSL-R for OSC1-R                                                                                                                               | 76 |

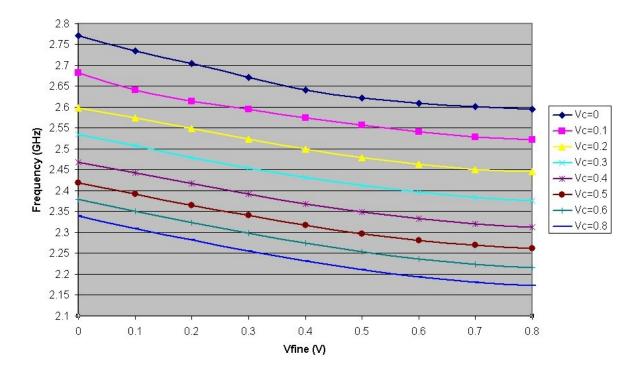

| 48 | Measured fine and coarse tuning range of OSC1 at 1.2V supply $\ldots$                                                                                                                                            | 78 |

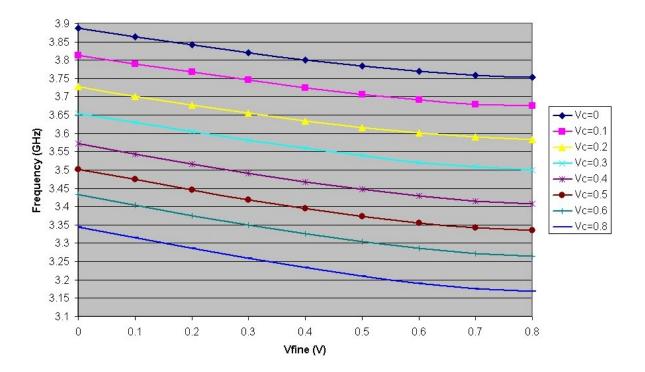

| 49 | Measured fine and coarse tuning range of OSC1-R at $1.2\mathrm{V}$ supply $% 1.2\mathrm{V}$ .                                                                                                                    | 78 |

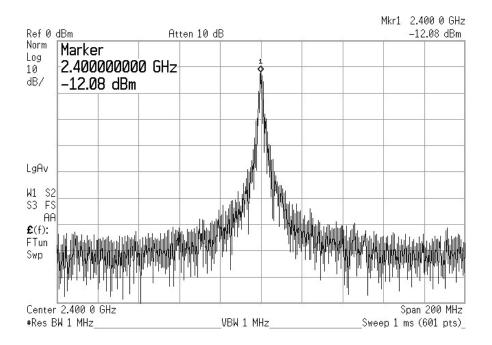

| 50 | Measured output frequency spectrum of OSC1 at $2.4 \mathrm{GHz}$ operation .                                                                                                                                     | 79 |

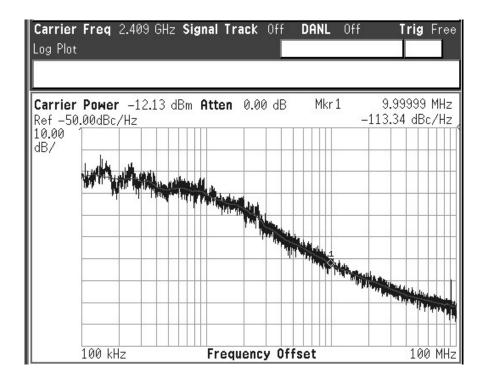

| 51 | Measured phase noise spectrum of OSC1 at 2.4GHz operation $\ldots$                                                                                                                                               | 79 |

| 52 | Measured output frequency spectrum of OSC1-R at 2.4GHz operation                        | 80  |

|----|-----------------------------------------------------------------------------------------|-----|

| 53 | Measured phase noise spectrum of OSC1-R at 2.4GHz operation                             | 80  |

| 54 | Output frequency spectrum of OSC1-R at 3.12GHz and 2.8mW power                          | 82  |

| 55 | Phase noise spectrum of OSC1-R at 3.12GHz and 2.8mW power                               | 82  |

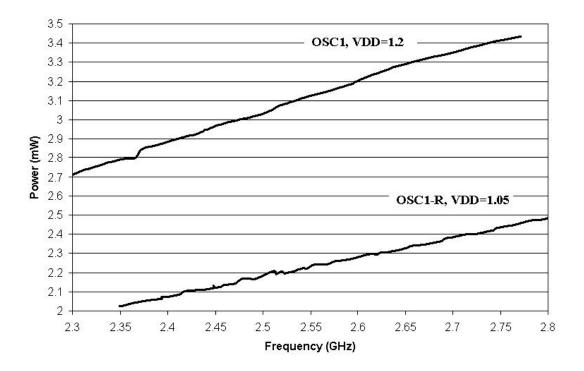

| 56 | Ring VCO measured power vs. frequency curves for OSC1 and OSC1-R                        | 83  |

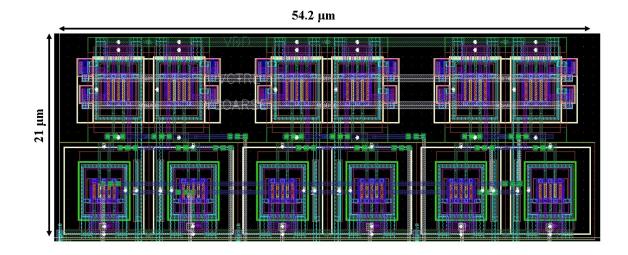

| 57 | Layout of OSC1 (based on DCVSL)                                                         | 85  |

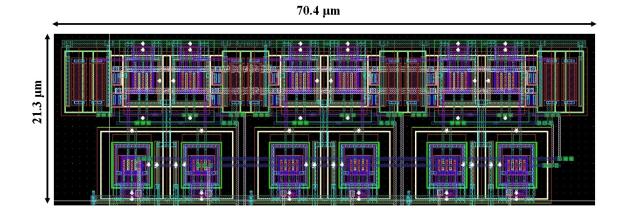

| 58 | Layout of OSC1-R (based on DCVSL-R)                                                     | 85  |

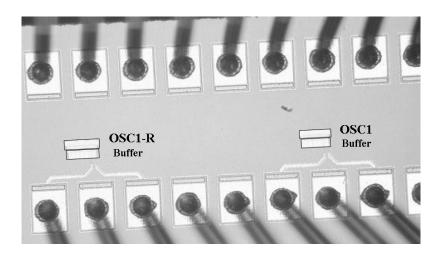

| 59 | Die micrograph of OSC1 and OSC1-R                                                       | 86  |

| 60 | Block diagram of a conventional DPLL                                                    | 89  |

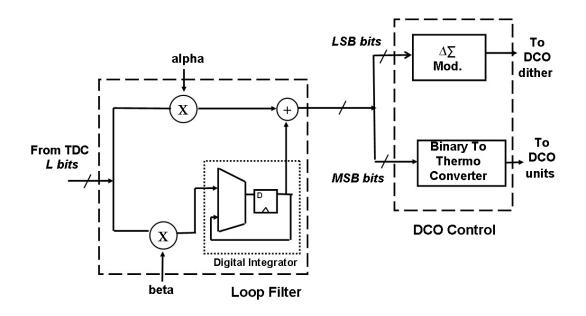

| 61 | A conventional proportional integral digital loop filter and DCO control interface      | 91  |

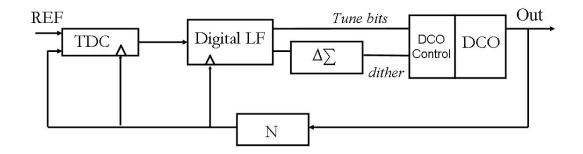

| 62 | Block diagram of the proposed all digital PLL                                           | 105 |

| 63 | System level diagram of the time to digital converter $\ldots$ .                        | 108 |

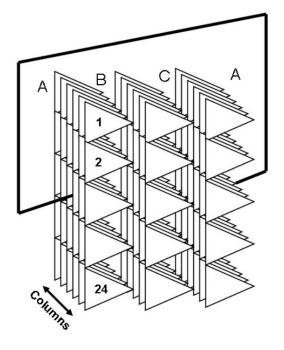

| 64 | Three stage ring oscillator based DCO 3-D representation $\ldots$ .                     | 110 |

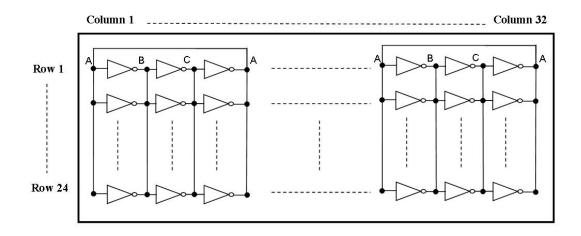

| 65 | Three stage ring oscillator based DCO put in a row-column matrix for ease in control    | 111 |

| 66 | Block diagram of a conventional 3-bit barrel shifter                                    | 112 |

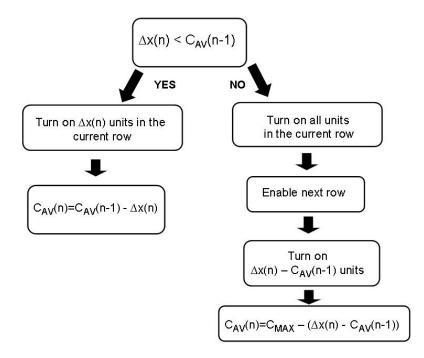

| 67 | Operational flow diagram of the smart shifter                                           | 113 |

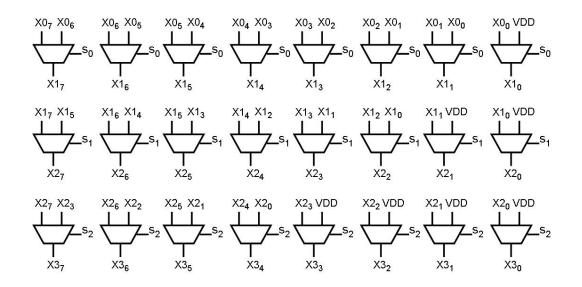

| 68 | Block diagram of a 3-bit implementation of the proposed smart shifter                   | 114 |

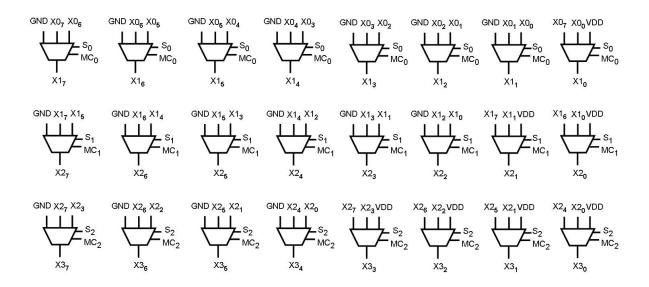

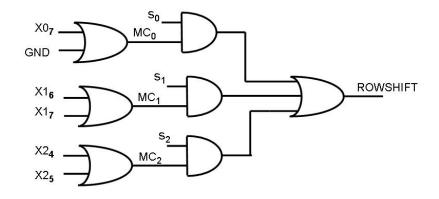

| 69 | Generation of MC controls and rowshift signals in 3-bit smart shifter                   | 115 |

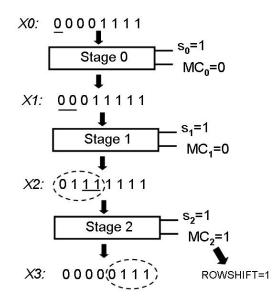

| 70 | Sample operation of the 3-bit smart shifter                                             | 117 |

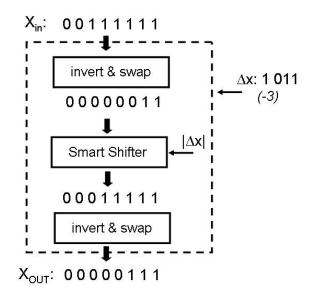

| 71 | Block diagram and sample operation of right-shifting using the left-shift smart shifter | 119 |

| 72 | Block diagram of the complete bidirectional row/column shifter<br>as the DCO interface                                         | 120 |

|----|--------------------------------------------------------------------------------------------------------------------------------|-----|

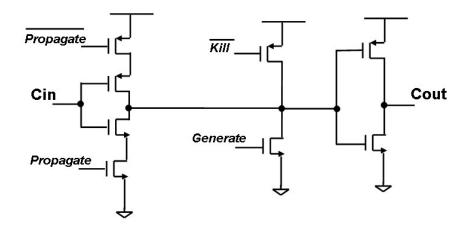

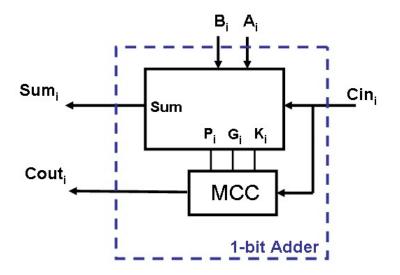

| 73 | Transistor level implementation of a Manchester Carry Chain 1                                                                  | 122 |

| 74 | A 1-bit full adder using Manchester Carry Chain                                                                                | 123 |

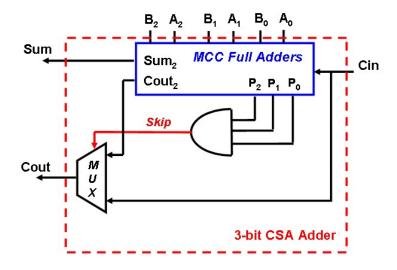

| 75 | Block diagram of the 3-bit Carry-Skip Adder used in the loop filter . 1                                                        | 124 |

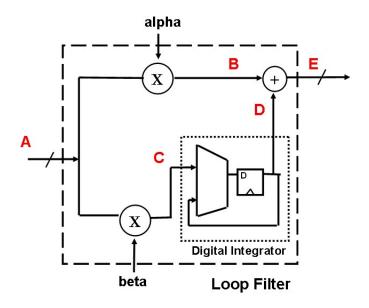

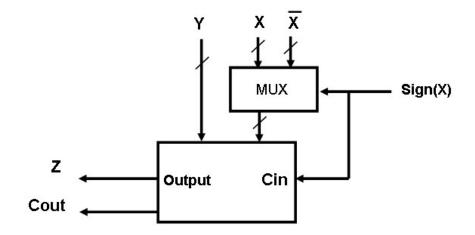

| 76 | Block diagram of the loop filter                                                                                               | 125 |

| 77 | Block diagram of an adder/subtractor                                                                                           | 126 |

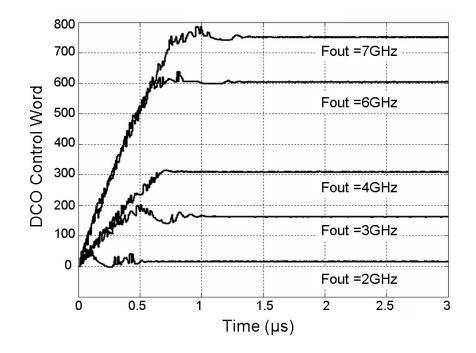

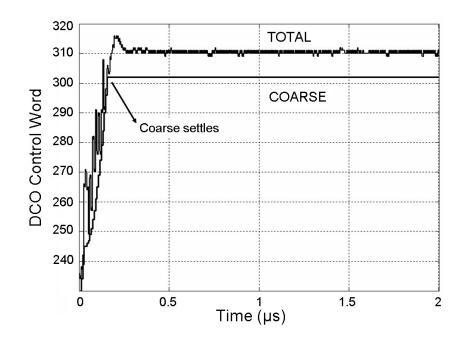

| 78 | Simulink time-domain simulations of the ADPLL, DCO total con-<br>trol word for ADPLL operation frequencies between 2GHz-7GHz 1 | 129 |

| 79 | Simulink time-domain simulations of the ADPLL, detail of total and coarse DCO control words for 4GHz operation 1               | 130 |

| 80 | Simulink time-domain simulations of the ADPLL, TDC output at 6GHz operation                                                    | 130 |

| 81 | Measurement instruments and setup for ADPLL 1                                                                                  | 131 |

| 82 | Printed circuit board of ADPLL with connecting cables                                                                          | 132 |

| 83 | Printed circuit board of ADPLL                                                                                                 | 133 |

| 84 | DCO Output frequency spectrum - minimum frequency for VDD=1V 1                                                                 | 135 |

| 85 | DCO Output frequency spectrum - maximum frequency for $VDD=1V$ 1                                                               | 135 |

| 86 | DCO Output frequency spectrum - minimum frequency for $VDD=0.9V1$                                                              | 136 |

| 87 | DCO Output frequency spectrum - maximum frequency for VDD=0.9V1                                                                | 136 |

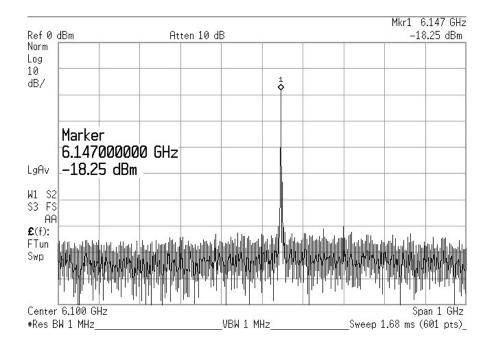

| 88 | DCO wide span output frequency spectrum at 7.3GHz operation $\therefore$ 1                                                     | 137 |

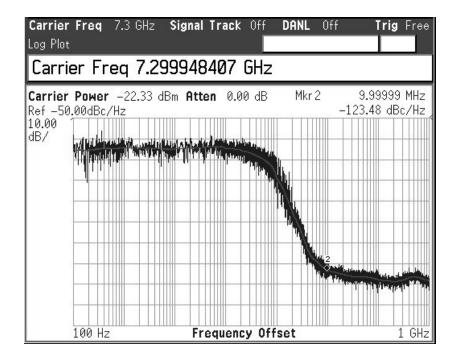

| 89 | DCO phase noise spectrum for 7.3GHz operation                                                                                  | 138 |

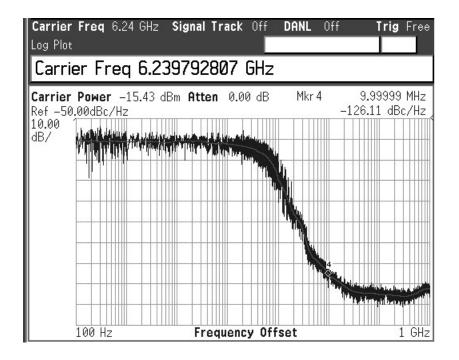

| 90 | DCO phase noise spectrum for 6.24GHz operation                                                                                 | 138 |

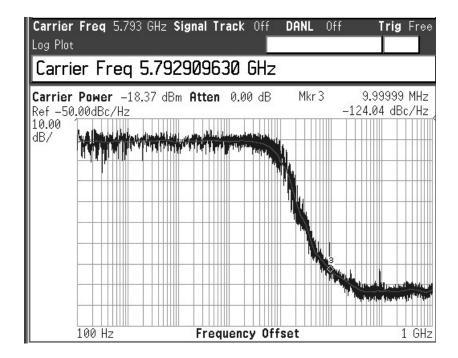

| 91 | DCO phase noise spectrum for 5.8GHz operation                                                                                  | 139 |

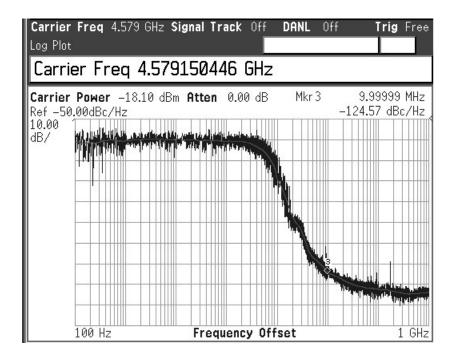

| 92  | DCO phase noise spectrum for 4.58GHz operation                                                                 | 139 |

|-----|----------------------------------------------------------------------------------------------------------------|-----|

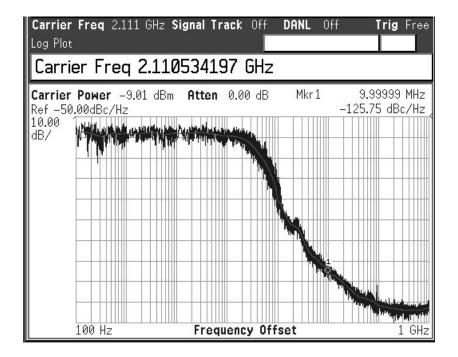

| 93  | DCO phase noise spectrum for 2.11GHz operation                                                                 | 140 |

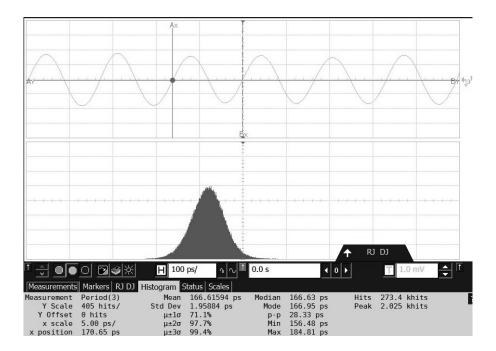

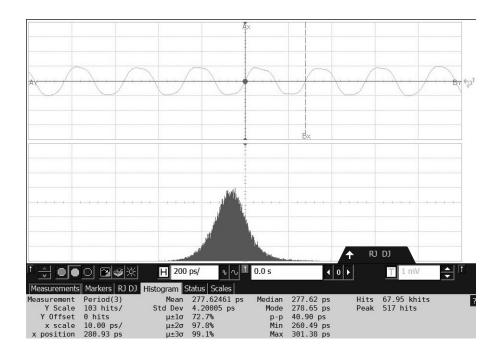

| 94  | ADPLL output and its period histogram at 6GHz operation with 1.9ps rms period jitter                           | 143 |

| 95  | ADPLL output and its period histogram at 3.6GHz operation with 4.2ps rms period jitter                         | 143 |

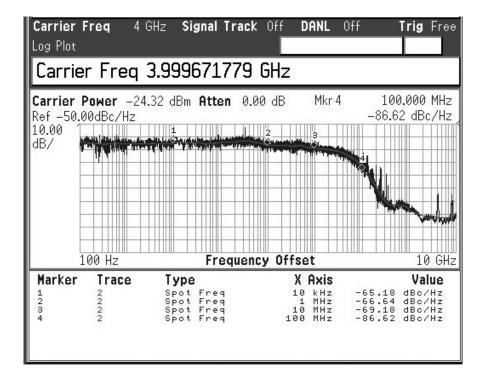

| 96  | ADPLL output phase noise spectrum for 4GHz operation $\ldots$ .                                                | 144 |

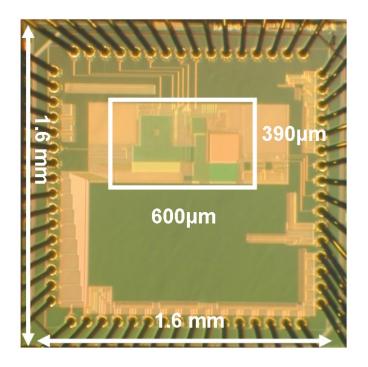

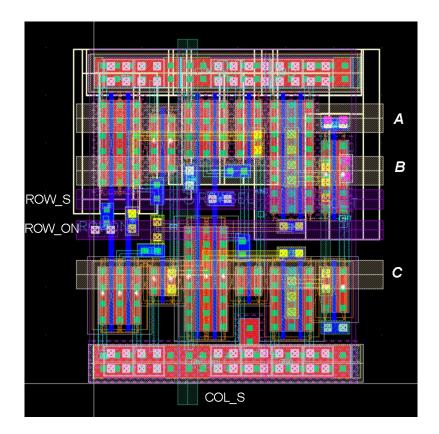

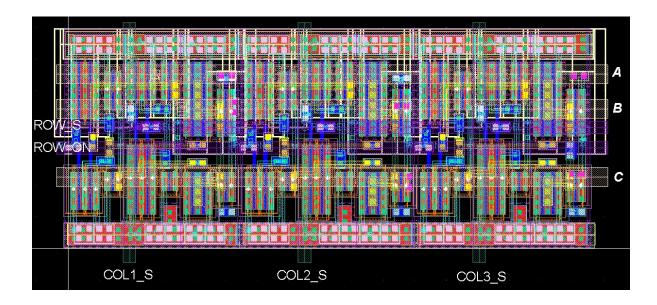

| 97  | ADPLL die micrograph                                                                                           | 145 |

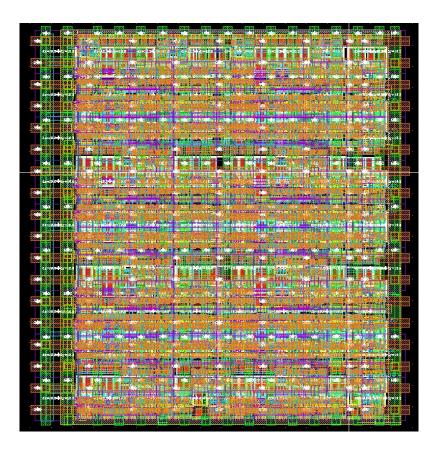

| 98  | Layout of the ADPLL active area implemented in 90nm digital CMOS $$                                            | 146 |

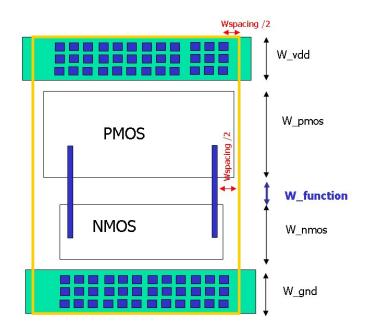

| 99  | Demonstration of standard library cell layout                                                                  | 148 |

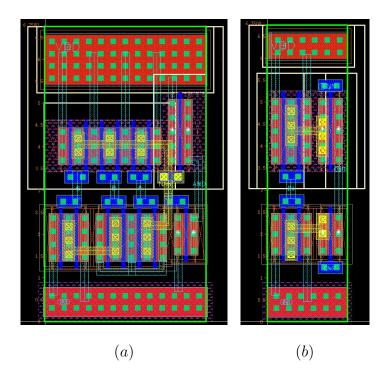

| 100 | Standard library cell layout examples Height=6.75 $\mu$ m (a)a 3-input AND gate (b) a current starved inverter | 149 |

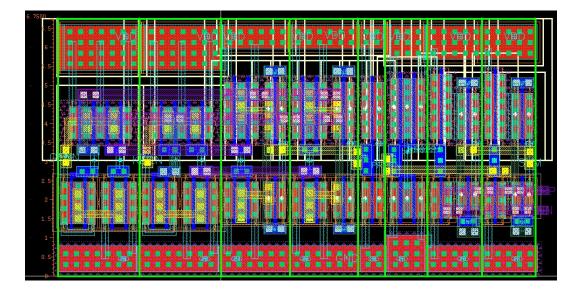

| 101 | Layout of a full adder consisting of standard cells                                                            | 150 |

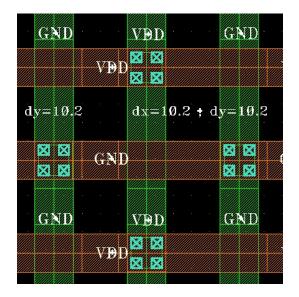

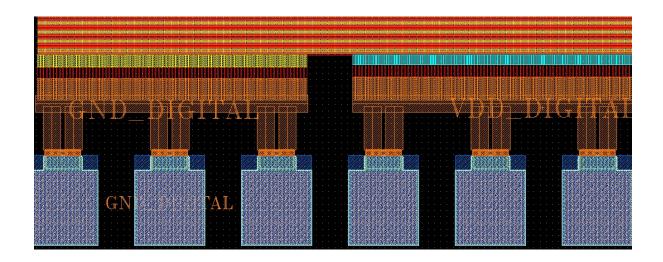

| 102 | Supply grid with horizontal metal 9 and vertical metal 8 layers $\ldots$                                       | 152 |

| 103 | Digital loop filter layout with power supply grid (89 $\mu{\rm m}\ge94~\mu{\rm m})$                            | 152 |

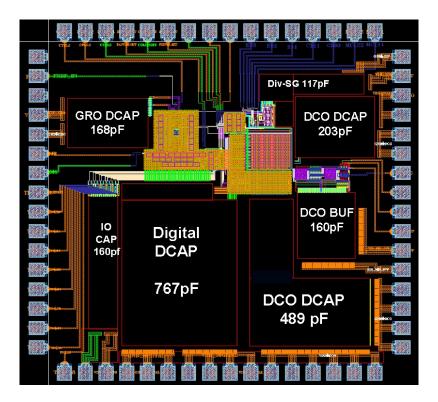

| 104 | Layout of the ADPLL chip with pads and decoupling capacitors                                                   | 153 |

| 105 | Detailed view of power supply routing from pads                                                                | 153 |

| 106 | Layout of a single DCO row/column matrix unit                                                                  | 155 |

| 107 | Layout of the three stage DCO ring unit                                                                        | 156 |

| 108 | Block diagram of a PLL with a prescaling divider before the pulse-<br>swallow divider                          | 175 |

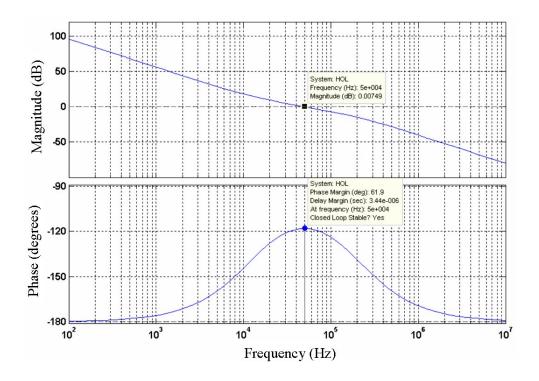

| 109 | Bode plot of the open loop gain of the third order PLL $\ldots$ $\ldots$                                       | 187 |

| 110 | Bode plot of the open loop gain of the second order approximation of the PLL                                   | 187 |

| FIGURE |                                                                             | Page |

|--------|-----------------------------------------------------------------------------|------|

| 111    | Closed loop frequency response of the third order PLL                       | 189  |

| 112    | Closed loop frequency response of the second order approximation of the PLL | 189  |

| 113    | Step response of the closed loop ADPLL                                      | 198  |

| 114    | Frequency response of the closed loop ADPLL                                 | 198  |

### LIST OF TABLES

TABLE

| Ι    | List of various wireless receivers and their FS power consumption $\ . \ .$                                                       | 8  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| II   | Performance specifications for a ZigBee frequency synthesizer $\ldots$                                                            | 10 |

| III  | Charge pump based PLL building block transfer functions for se-<br>cond order continuous approximation linear analysis            | 15 |

| IV   | Summary of the PLL second order loop parameters                                                                                   | 16 |

| V    | Useful relations between second order approximation loop parameters                                                               | 16 |

| VI   | Summary of loop parameters used in the fabricated ZigBee fre-<br>quency synthesizer prototype                                     | 17 |

| VII  | Summary of the pulse-swallow divider parameter values                                                                             | 26 |

| VIII | Measured performance of the ZigBee frequency synthesizer                                                                          | 37 |

| IX   | Values of DCVSL delay model empirical correction factors $\ldots$ .                                                               | 52 |

| Х    | A list of calculated and simulated values of $\tau_{PLH}$ , $\tau_{PHL}$ and model<br>error for various transistor configurations | 54 |

| XI   | Measured performance summary of the frequency synthesizer $\ldots$ .                                                              | 67 |

| XII  | Performance comparison of the DCVSL-R prescaler with previous-<br>ly reported solutions                                           | 72 |

| XIII | Measured performance summary of OSC1 (based on Fig.47(a)) and OSC1-R (based on Fig.47(b))                                         | 84 |

| XIV  | Performance comparison of OSC1-R with previously reported solutions                                                               | 87 |

| XV   | List of DPLL loop parameters                                                                                                      | 94 |

| XVI  | Summary of the DPLL important second order loop expressions                                                                       | 95 |

## TABLE

| XVII  | Summary of the loop parameters of the implemented ADPLL $\ldots$ .               | 106 |

|-------|----------------------------------------------------------------------------------|-----|

| XVIII | Truth table of 2-bit controlled MUX                                              | 115 |

| XIX   | Measured DCO power supply level and tuning range                                 | 134 |

| XX    | Measured DCO figure of merit for various frequencies                             | 141 |

| XXI   | ADPLL measured performance summary                                               | 145 |

| XXII  | Damping factor and pole locations in a second order system $\ldots$ .            | 179 |

| XXIII | Closed loop bandwidth of the designed ADPLL based on its fre-<br>quency response | 197 |

### CHAPTER I

#### INTRODUCTION

#### A. Motivation and Contributions

The present advancements in the information technology are driven by the developments and innovations in Integrated Circuit Design Techniques. Small laptops with high computational powers, wireless internet and information transfer facilities, cell phones and many other electronic devices that we use in daily life rely on the efficient implementations of communication circuits, receiver/transmitter radios on silicon. These receiver and transmitter circuits require the use of phase locked loops (PLL) for down/up conversion of the data carrying signal in wireless transceiver applications and for clock generation in serial link and microprocessor applications. This dissertation focuses on the design, analysis and implementation of these phase locked loop based frequency synthesizers and clock generators as well as their building blocks.

The frequency synthesizer is one of the key elements of a wireless transceiver. Several performance parameters of the synthesizer such as phase noise, frequency spurs, settling time, has considerable effect on the overall wireless system behavior. Power consumption performance of a wireless transceiver determines its battery life. Active during both transmit and receive modes, the frequency synthesizer has significant contribution to the overall power consumption of the transceiver. Particularly, the synthesizer employs several frequency dividers that operate at RF channel frequency, making the design of this block a challenge for low-power wireless transceiver applications.

This dissertation follows the style of IEEE Journal of Solid-State Circuits.

Along with frequency of operation and technology speed, the circuit topology is key in determining the power consumption of frequency dividers. Until recently, Current Mode Logic (CML) circuits were widely employed in the frequency dividers of synthesizers [1], [2], [3] due to their capability of high speed operation. With the migration towards sub-micron technologies, digital dynamic-circuit techniques such as True-Single-Phase Clocking (TSPC) are becoming popular [4], [5] to optimize the power consumption of high-speed frequency dividers.

In this dissertation, first, the design, implementation and measurements of a frequency synthesizer that employs TSPC based frequency dividers will be presented where the goal is to provide a low power solution for an IEEE 802.15.4 / ZigBee [6] transceiver application. It will be demonstrated that the implementation of the frequency dividers is crucial in minimizing the power consumption of the frequency synthesizer. A discussion on high speed circuit techniques to implement the RF frequency dividers of a frequency synthesizer will be presented.

Later, we focus on a logic family called Differential Cascode Voltage-Switch Logic (DCVSL) as a candidate to implement the RF dividers of a frequency synthesizer. The key benefits of DCVSL are its low input capacitance, differential nature, and low power consumption. However, DCVSL delay cells have a delay bottleneck; their low-to-high-transition propagation delay ( $\tau_{PLH}$ ) is inherently larger than their high-to-low-transition propagation delay ( $\tau_{PHL}$ ). The large  $\tau_{PLH}$  presents a speed bottleneck for the DCVSL cells and results in asymmetric differential output waveforms where the rising output lags the falling output. While the discrepancy between the two differential outputs is addressed in a few earlier works [7], [8], a detailed analysis of the inherent delay problem is not presented.

We analyze the delay behavior of DCVSL inverters and propose a closed-form delay model to characterize and predict the delay behavior of DCVSL circuits and demonstrate their inherent speed bottleneck. Then, we propose a circuit solution, which we term Differential Cascode Voltage Switch Logic with Resistive-enhancement (DCVSL-R), to overcome this speed bottleneck. We explore the use of the proposed circuit in the delay cells of ring oscillators to improve the power-consumption and speed trade off in these circuits and provide a comparison of DCVSL and DCVSL-R based ring oscillators through measurements. We also implement a fully integrated frequency synthesizer using the proposed DCVSL-R in its high speed frequency dividers, for low power 2.4GHz band wireless transceiver applications and present measurement results of this low power frequency synthesizer.

Analog PLLs have been widely used in communication systems. However, as the smaller, deep sub-micron technologies enable the shrinking of digital circuits, the design of analog intense circuits become more challenging. An all digital approach to implement the PLL, which is an integral part of communication systems, would enable the benefits of technology scaling in terms of low area and low voltage and will increase the integration capability of the PLL with the rest of the digital circuitry. If the PLL is implemented in an all-digital manner, the expensive need for special mixed signal processes can also be eliminated.

In this work, an all digital PLL (ADPLL) that addresses the speed and performance demands of today's wireline and microprocessor applications is designed and fabricated. The proposed ADPLL is truly digital, using a standard bulk CMOS technology (UMC 90nm CMOS) and does not require any analog/RF or non-scalable R/L/C components. The ADPLL achieves the synthesis of a wide range of output frequencies, (2.5GHz - 7.3GHz in measurements), to serve as a multi-standard compatible PLL. It addresses the challenges that come along with wide range of operation such as stability and phase frequency detection for a large frequency error range. The proposed loop accommodates a multi-bit linear time-to-digital converter (TDC) and avoids the use of digital-to-analog converters (DACs) or binary-to-thermometer (B-T) converter circuits. A proposed all digital digitally-controlled oscillator (DCO) control block, that we refer to as the Smart Shifter, facilitates faster frequency tuning per loop cycle for the wide-range PLL while minimizing implementation complexity.

#### B. Overview

Chapter II presents the design and analysis of a fully integrated frequency synthesizer with TSPC frequency dividers, that targets 2.4GHz IEEE 802.15.4 / ZigBee transceiver applications, with a focus on the design issues of the frequency dividers. In this chapter, we discuss frequency divider basics and present measurement results of the frequency synthesizer that was fabricated in 0.18  $\mu$ m CMOS technology.

Chapter III discusses various circuit topologies and offers DCVSL circuits as a candidate to implement the RF frequency dividers of frequency synthesizers. This chapter presents a delay analysis, that characterizes the operation of and pinpoints the key speed bottleneck of, DCVSL circuits. This chapter also proposes a circuit technique, DCVSL-R, which improves the speed and power consumption performance trade off of DCVSL circuits and fixes their output asymmetry.

Chapter IV presents a low-power frequency synthesizer, the programmable dividers of which are implemented with the proposed DCVSL-R circuit. This chapter provides measurement results of the frequency synthesizer that was fabricated in 0.18  $\mu$ m CMOS technology and a comparison of the presented frequency divider with similar frequency dividers that are reported in literature.

Chapter V discusses the implementation of two ring-oscillator-based voltage controlled oscillators (VCO) that utilize DCVSL and DCVSL-R delay cells that are fabricated in 0.13  $\mu$ m CMOS technology. This chapter demonstrates the performance improvement of the latter, through measurement results. A comparison of the proposed DCVSL-R based ring oscillator with other state-of-the art ring oscillators in literature, is also presented.

Chapter VI provides an analysis of all digital PLLs. A discussion on the motivation of moving the PLLs into digital domain is presented, along with the loop analysis of an ADPLL, a discussion on noise in ADPLLs and a summary of design challenges.

In Chapter VII, we present a wide range ADPLL and discuss the proposed loop architecture as well as building block designs. This chapter also demonstrates system level simulations of the proposed ADPLL along with the measurement results of an ADPLL prototype that was fabricated in 90 nm digital CMOS technology.

Finally, Chapter VIII concludes this dissertation.

### CHAPTER II

# A FULLY INTEGRATED FREQUENCY SYNTHESIZER FOR ZIGBEE APPLICATIONS

#### A. IEEE 802.15.4 / ZigBee

Wireless networking has become an integral part of everyday life. In the last decade, machine to machine sensor networks and remotely controlled wireless communication systems became popular. Machine to machine systems connect and network household appliances, air conditioners, heat sensors, gas sensors or simply RFID tags for tracking purposes. The basic idea behind these applications is to eliminate the user effort and try to form a network between the machine systems for environmental control, health monitoring or security issues. Remotely controlled communication systems are similar but involve the user end, where a user can create a household network to control everything from the garage door to alarm systems. Similarly, a remote network could control the automation systems in an office building or campus such as security systems, etc.

Although there is a growing number of wireless communication standards today, none of them address such low-cost applications since they require complex circuitry and protocols with higher data rates (UWB, Bluetooth, Wi-Fi) or higher communication ranges (GPRS, GSM). Such standards address wireless communication platforms that target high performance where the transfer of voice, data, video occurs between networking nodes or involves very large distances.

IEEE 802.15.4 / ZigBee [6] is a wireless personal area network (WPAN) standard that specifically targets remote control and sensor monitoring applications. Zig-Bee defines a flexible networking system to accommodate up to tens of thousands of nodes/sensors in a single network to perform a vast range of remote controlling applications that arise in every day life in home or industrial environments such as automated meter reading, remote lighting systems, etc. ZigBee has low data rate (up to 250 kb/s depending on the frequency band) and short range specifications (1-100m) that enable the extreme low cost and long battery life.

IEEE 802.15.4 / ZigBee is defined over three frequency bands [6]. It has one channel in the European 868MHz band, 10 channels in the 915MHz ISM band and 16 channels in the 2.4GHz ISM band. In this work, we will focus on the 2.4GHz ISM band. In this band, ZigBee has 250kbps data rate, offset quadrature phase shift keying (OQPSK) modulation and 5MHz channel spacing [6], [9].

### B. Frequency Synthesis for a ZigBee Transceiver

Since a ZigBee network could have thousands of nodes, such a large network can be feasible only through an extremely low cost wireless solution for each node, and would require an ease of implementation and maintenance of the system, requiring long battery lives measured in years. The battery life of a device is determined by its power consumption while the cost and size of it is determined by the area. With this motivation in mind, the emphasis of the design of a ZigBee transceiver (or any stand-alone building block developed for a ZigBee transceiver) is on minimizing the power consumption and minimizing complexity and area while meeting the ZigBee performance specifications.

The contribution of the frequency synthesizer to the overall power consumption of the transceiver is very significant due to the fact that the frequency synthesizer has multiple building blocks that operate at the highest RF frequency of the transceiver. Moreover, the frequency synthesizer is active during both receive and transmit modes, contributing to the overall power consumption of the device at all times.

To understand the effect of the frequency synthesizer power consumption in a wireless transceiver, Table I summarizes the total power consumption of the receiver, the power of the frequency synthesizer and its percentage in the receiver for several designs that target various different wireless standards. It is seen that the power consumption of the frequency synthesizer is a significant factor in determining the overall power of the receiver. Hence, any improvement and technique that would reduce the power consumption of the synthesizer will have a direct effect on the whole system power and the battery life of the device.

| Receiver   | Wireless                   | Receiver              | FS Power   | FS Power   |

|------------|----------------------------|-----------------------|------------|------------|

| iteetivei  | Standard                   | Power                 | I S I Owei | Percentage |

| [10], [11] | $\operatorname{Bluetooth}$ | $69.75 \mathrm{\ mW}$ | 31.25  mW  | 44.8%      |

|            | IEEE 802.11b               | (w/o ADC)             | 51.25 mvv  | 44.070     |

| [12]       | Ultrawideband              | $285 \mathrm{~mW}$    | 200  mW    | 70%        |

| [12]       | Wireless LAN               | $55.7 \mathrm{mW}$    | 20.5 mW    | 36.8~%     |

| [10]       | [13] (IEEE 802.11a)        | (w/o ADC)             | 20.0 1110  | 00.0 /0    |

Table I. List of various wireless receivers and their FS power consumption

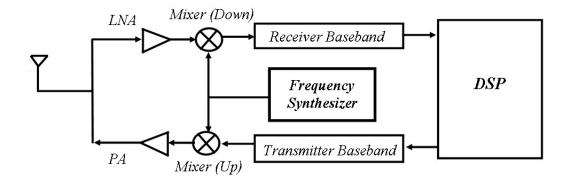

A frequency synthesizer is designed to be used in a fully integrated ZigBee transceiver as shown in Fig. 1. A direct conversion (zero-IF) receiver architecture provides many receiver system level benefits such as eliminating the need for image rejection [14]. From the synthesizer's point of view, a transceiver with direct-conversion receiver utilizes the same frequency synthesizer in both the transmit and receive paths which results in significant area savings. Therefore, the target transceiver architecture will be assumed a direct-conversion architecture.

Fig. 1. Block diagram of a standard transceiver system

In the target 2.4GHz ISM band, ZigBee employs OQPSK with half-sine wave shaping. Due to the quadrature nature of the modulation, the transmit path will include in-phase (I) and quadrature (Q) up-conversion paths while the receiver will consist of I and Q down-conversion paths. Therefore, the ZigBee synthesizer should generate quadrature local oscillation (LO) signals to be compatible in a transceiver environment.

The design specifications of the frequency synthesizer should be derived from the standard specifications. For instance, the standard determines symbol rate (62.5 kilo-symbols / sec) as well as the receive to transmit turnaround time (duration of 12 symbols). This leads to the derivation of the synthesizer settling time of 192  $\mu$ s. Similarly the standard defines the adjacent and alternate channel (5MHz and 10MHz away from the channel, respectively) interference test and this, along with the modulation scheme and the tolerable bit error rate, determine phase noise and spur suppression specifications. Table II summarizes the ZigBee frequency synthesizer specifications. ZigBee standard requires 0dB adjacent channel interferer rejection while this specification for the alternate channel is 30dB [6]. This results in a tighter alternate channel spur suppression specification than the adjacent channel suppression, as seen in Table II. A detailed derivation of these specifications from the ZigBee standard is provided in [15], [16]. A detailed look at the derivation of frequency synthesizer specifications from a wireless standard, is given in [17], [11].

| Performance Metric  | Value                              |

|---------------------|------------------------------------|

| Frequency Synthesis | 2.405GHz - 2.48 GHz                |

| Channel Spacing     | 5MHz                               |

| Number of Channels  | 16                                 |

| Settling Time       | $< 192 \ \mu s$                    |

| Settling Accuracy   | $\pm$ 40ppm (96 kHz)               |

| Spur Suppression    | < -13dBc at 5MHz                   |

| Spur Suppression    | < -43dBc at 10MHz                  |

| Phase Noise         | $<-112 \rm dBc/Hz$ at 10MHz offset |

| I Hase Noise        | < -102dBc/Hz at 3.5MHz offset      |

Table II. Performance specifications for a ZigBee frequency synthesizer

#### C. Synthesizer Implementation

As discussed in Section A, the focus of the design of this ZigBee synthesizer is in keeping the implementation simple (low-cost) and having low-power consumption (long battery life). An integer-N based architecture is chosen due to its simplicity in implementation when compared to their fractional-N based counterparts. In an integer-N architecture the maximum reference frequency is determined by the greatest common divisor (GCD) of the channel frequencies and the channel spacing of the targeted wireless standard, as given in (2.1) [17].

$$F_{REF MAX} = GCD(F_O, F_{SP})$$

(2.1)

where  $F_O$  is the channel center frequency and  $F_{SP}$  is the channel spacing. It is seen that channel spacing can also serve as the PLL's reference frequency. Therefore, a reference frequency of 5MHz is used in this design. The relationship between the output frequency and the reference frequency is given by:

$$FOUT = FREF \times N \tag{2.2}$$

where N is the frequency division ratio. Note that in a fully-integrated PLL solution, the reference frequency is often generated by a stable crystal oscillator [18] and is therefore constant. Then, (2.2) shows that the frequency synthesizer output tone can be controlled through changing the divider ratio.

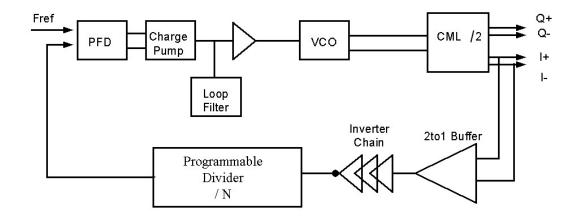

The block diagram of the synthesizer is shown in Fig. 2. To meet the requirements of Table II, the synthesizer generates quadrature LO outputs for 16 channels, spaced with 5MHz, through the programmable frequency divider ratio N. The values of Nare:

$$N = 481, 482, \dots, 495, 496 \tag{2.3}$$

There are alternative solutions to generate quadrature components of the received / transmitted signal in a wireless radio such as using passive RC networks or active frequency dividers. While the use of active frequency dividers consumes additional power, it is usually preferred over passive solutions due to its minimal amplitude and

Fig. 2. Block diagram of the ZigBee frequency synthesizer

phase mismatch. Moreover, with the use of an active divide-by-2 circuit to generate IQ components of the carrier, the VCO operates at double the channel frequency and the LO output is generated by dividing the VCO output frequency by 2. This prevents injection pulling and PA load pulling problems that commonly occur in monolithic implementations of transceivers [14], [19].

The stability and frequency dependent behavior of the loop is analyzed in phase domain where the input of the system is defined as the phase difference between the reference and the divider output signals and the output of the system is defined as the phase of the PLL output signal. Note that frequency lock is a very nonlinear behavior. Therefore, for a linear analysis to apply, it is assumed that the input phase error of the PLL is small.

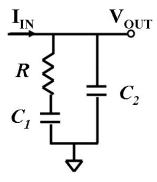

The frequency synthesizer is implemented as a type II, third order charge-pump based integer-N PLL in TSMC 0.18  $\mu$ m CMOS technology [4]. The loop filter is shown in Fig. 3. The loop type is determined by the number of integrations [20]. In the PLL of Fig. 2, the two integrations come from the loop filter and from the VCO where frequency is converted into phase through integration.

Fig. 3. Second order loop filter of the charge-pump based PLL

The transfer function of the loop filter shown in Fig. 3 is:

$$H_{LF}(s) = \frac{1}{(C_1 + C_2)} \frac{s/w_z + 1}{s(s/w_p + 1)}$$

(2.4)

where the zero and the pole created by the loop filter are given by (2.5) and (2.6).

$$w_z = \frac{1}{RC_1} \tag{2.5}$$

$$w_p = \frac{C_1 + C_2}{RC_1 C_2} \tag{2.6}$$

The loop pole  $w_p$  occurs due to  $C_2$  of the loop filter. This capacitor is added to the loop filter to minimize ripples on the VCO control line that arise due to the voltage drops on R. However, to maintain the stability of the system, this pole is often placed further than the loop zero and loop bandwidth. Then, the capacitor  $C_2$  is often much smaller then  $C_1$  such that:

$$w_p \approx \frac{1}{RC_2} \quad (C_1 >> C_2) \tag{2.7}$$

With a second order loop filter, and the integration that comes from the VCO, the PLL is a type II, third-order system. However, since  $w_p$  is placed much further than the loop bandwidth and for frequencies that are of interest, the loop behaves similar to a second order system. Then, the loop filter transfer function be approximated as follows:

$$H_{LF}(s) \approx \frac{1}{C_1} \frac{s/w_z + 1}{s}$$

(2.8)

which can be rewritten as:

$$H_{LF}(s) \approx R \frac{s + w_z}{s} \tag{2.9}$$

While analyzing the loop as a second order system is a valid approximation, for phase margin analysis, the placement of  $w_p$  should be considered to ensure stability. A detailed analysis on the third-order analysis of a PLL can be found in [21].

Table III summarizes the individual building block transfer functions in the phase-domain continuous approximation linear analysis of the PLL where  $\Delta \phi_{in}$  is the phase difference at the PFD input,  $K_{VCO}$  is the VCO frequency gain in radians/(second×V), N is the feedback division ratio in the loop,  $I_{CP}$  is the charge pump current and  $w_z$  is the loop filter zero given in (2.5). Further information on the continuous approximation linear analysis of charge-pump based PLLs, the derivation of the below equations and the third-order loop analysis can be found in Appendix A and in [21–24].

Based on Table III, the second order approximation of the closed-loop transfer

| Building Block     | Transfer Function                                       |

|--------------------|---------------------------------------------------------|

| PFD and            | $\frac{I_{out}}{\Delta\phi_{in}} = \frac{I_{CP}}{2\pi}$ |

| Charge Pump        | $\frac{1}{\Delta\phi_{in}} = \frac{1}{2\pi}$            |

| Loop               | $\frac{V_{out}}{I_{in}} = R \times \frac{s + w_z}{s}$   |

| Filter             | $I_{in} = n \land - s$                                  |

| Voltage Controlled | $\frac{\phi_{out}}{V_{in}} = \frac{K_{VCO}}{s}$         |

| Oscillator         | $V_{in}$ s                                              |

| Frequency          | $\frac{\phi_{out}}{\phi_{in}} = \frac{1}{N}$            |

| Dividers           | $\phi_{in} = \overline{N}$                              |

Table III. Charge pump based PLL building block transfer functions for second order continuous approximation linear analysis

function of the PLL is given by:

$$H_{CL\_PLL}(s) = \frac{\phi_{out}}{\phi_{in}} = \frac{(K_{LOOP} \times N)(s + w_z)}{s^2 + (K_{LOOP})s + K_{LOOP}w_z}$$

(2.10)

where

$$K_{LOOP} = \frac{K_{VCO}I_{CP}R}{2\pi N} \tag{2.11}$$

Note that N is the frequency division ratio in the feedback dividers. Any frequency division in the forward path should be separately incorporated in the loop transfer function to the forward path gain. Note that the units of  $K_{VCO}$  in this text is defined in radians/(second × V). A common mistake is to assume  $K_{VCO}$  in Hz/V and not take the  $2\pi$  factor into account in the loop gain. If  $K_{VCO}$  is defined in Hz/V, then the VCO gain in the loop transfer function should be  $2\pi K_{VCO}$  since it is a phase domain analysis. To avoid confusion, one should be careful to maintain consistency in the definition and units of the loop parameters.

Based on (2.10), important loop parameters such as the natural frequency  $(w_n)$ , the damping factor  $(\xi)$  of the system and the closed loop 3-dB bandwidth  $(w_c)$  are determined as summarized in Table IV.

| Control Parameter | Expression                                      | Charge-pump PLL Expressions                                |

|-------------------|-------------------------------------------------|------------------------------------------------------------|

| Natural           | $w_n = \sqrt{K_{LOOP}w_z}$                      | $w_n = \sqrt{\frac{K_{VCO}I_{CP}}{2\pi NC_1}}$             |

| Frequency         |                                                 | $w_n = \sqrt{-2\pi N C_1}$                                 |

| Damping           | $\xi = \frac{1}{2} \sqrt{\frac{K_{LOOP}}{w_z}}$ | $\xi = \frac{R}{2} \sqrt{\frac{K_{VCO}I_{CP}C_1}{2\pi N}}$ |

| Factor            |                                                 | $\zeta = 2 \sqrt{2\pi N}$                                  |

| Loop              | $w_c \approx GBW = K_{LOOP}$                    | $w_c = \frac{K_{VCO}I_{CP}R}{2\pi N}$                      |

| Bandwidth         |                                                 | $\omega_c = 2\pi N$                                        |

Table IV. Summary of the PLL second order loop parameters

Table V. Useful relations between second order approximation loop parameters

| Parameters        | Relations              |

|-------------------|------------------------|

| Loop Bandwidth    | $w_c \approx 2\xi w_n$ |

| Natural Frequency | $w_n = 2\xi w_z$       |

| Loop Zero         | $w_z = w_c w_n^2$      |

Some useful relations between the loop parameters are given in Table V. Note that the approximation of  $w_c$  comes from the fact that the closed loop 3-dB bandwidth of a feedback system is approximately equal to the gain bandwidth product(GBW) of its open loop gain [18].

Based on the ZigBee specifications given in Table II, the loop equations in Table IV and technology-dependent factors (current gain, control voltage dynamic range, varactor gain, etc.) the building block design parameters are determined and are listed in Table VI. The details of the derivation of the parameters in Table VI can be found in [15].

Appendix A provides a detailed design procedure and loop design analysis for charge-pump based PLLs and provides an alternative loop design for a ZigBee synthesizer as a design example.

| Loop Parameter    | Value                                       |  |  |

|-------------------|---------------------------------------------|--|--|

| $w_c$             | $2\pi \times 30 \mathrm{kHz}$               |  |  |

| $w_z$             | $2\pi \times 7.5 \mathrm{kHz}$              |  |  |

| ξ                 | $\approx 1$                                 |  |  |

| $w_p$             | $2\pi \times 120 \mathrm{kHz}$              |  |  |

| $K_{VCO}, I_{CP}$ | $2\pi$ $\times$ 135MHz/V , 20 $\mu {\rm A}$ |  |  |

| $R, C_1, C_2$     | 61  kohms, 346  pF, 21.62 pF                |  |  |

Table VI. Summary of loop parameters used in the fabricated ZigBee frequency synthesizer prototype

The synthesizer consists of three separate voltage supply domains. The phasefrequency detector (PFD) and charge pump (CP) both use thick-oxide transistors and have a 3V supply instead of the nominal 1.8V of the 0.18  $\mu$ m technology, to allow for cascode transistors in the charge pump and to improve matching. This configuration also increases the dynamic range of the control voltage and allows for a low VCO gain  $(2\pi \times 135MHz/V)$  to achieve the desired frequency range. The loop filter (LF) is a fully integrated solution that features an active capacitance multiplier [25].

It is common practice to separate the digital circuit supply from the analog power supply to minimize noise coupling from the notoriously noisy digital to the sensitive analog. Therefore, the digital frequency dividers (programmable divider and the inverter chain buffer that drives it) operate under a separate supply voltage. Since the digital circuit power consumption is directly related to its supply level, we operate these digital circuitry at a lower supply of 1.3V. The LC-tank VCO, the divide-by-2 circuit that follows it and the differential-to-single-ended (2to1) buffer that drives the digital divider circuitry all operate at the nominal 1.8V supply.

The VCO operates at twice the channel frequency range (4.81GHz - 4.96GHz) and features frequency tuning through the use of PMOS inversion varactors and junction varactors for discrete coarse and continuous fine tuning, respectively. The PFD, CP, LF and VCO are designed by Mr. Rangakrishnan Srinivasan and the details of their design are provided in [15]. In this dissertation, we focus on the implementation details of the frequency dividers.

### D. Frequency Dividers

# 1. Divider Basics

# a. Divide-by-2 Operation

As seen in Fig. 2, a divide-by-2 prescaler circuit generates quadrature LO signals to be used by up/down conversion mixers of a transceiver. Note that since the VCO operates at double the channel frequencies, this divider circuit should operate at 5GHz range and is therefore critical in terms of power consumption and performance.

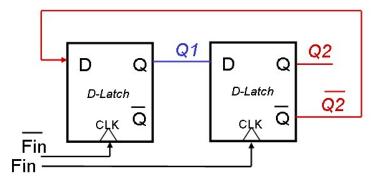

Fig. 4 shows the block diagram of a simple divide-by-2 circuit. Note that it con-

Fig. 4. Block diagram of a divide-by-2 frequency divider

sists of a D-flip-flop (two D-latches in master-slave configuration), placed in a negative unity feedback. To understand how this circuit divides its clock input's frequency, we should examine its state table and timing diagram, given in Fig. 5 (a) and (b), respectively.

In the state table, each row represents the next state of the output that occurs after the previous state. Note that the outputs  $Q_2$  and  $Q_1$  have a period, twice that of the clock signal and these outputs have 90 degrees of phase difference. This shows that a divide-by-2 circuit that consists of two master-slave latches, inherently generates quadrature phases at its two latch outputs.

The circuit implementation of the divider depends on several design metrics such as operating frequency and clock input signal swing. Several circuit techniques will be discussed in detail, in Chapter III Section A. In the proposed ZigBee synthesizer, the divide-by-2 circuit is implemented with Current Mode Logic [2,3,26,27] due to its ability to operate at very high frequencies and for quality quadrature signal generation with very small IQ mismatch and with smaller controlled swing at the LO to improve mixer linearity.

| State Table |    |    |  |

|-------------|----|----|--|

| Fin         | Q1 | Q2 |  |

| 1           | 0  | 0  |  |

| 0           | 1  | 0  |  |

| 1           | 1  | 1  |  |

| 0           | 0  | 1  |  |

| 1           | 0  | 0  |  |

| 0           | 1  | 0  |  |

Fig. 5. Divide-by-2 operation (a) state diagram (b) input and output timing

# b. Division By an Odd Ratio

The most basic frequency division, divide-by-2 operation, was discussed and demonstrated in Fig. 4 and Fig. 5. Similarly, frequency division where the division ratio is a power of 2, can be implemented by cascading asynchronous divide-by-2 stages. However, division by an odd number is not as straightforward.

One of the most commonly used odd number dividers is a divide-by-3 circuit [14].

The block diagram of a divide-by-3 circuit is shown in Fig. 6. The operation of a divide-by-3, and most odd-ratio divisions, are based on power-of-2 ratio divisions and additional logic controls that prevent certain output states and therefore limit the total number of states, and therefore the period, of the output signals.

Fig. 6. Block diagram of a divide-by-3 frequency divider

The divide-by-3 circuit example of Fig. 6 consists of two D-flip-flops. Note that in Fig. 4, we demonstrated the most simple division through a single flip-flop which consists of two latches. However, often, the latches are not shown for simplicity and only the D-flop-flops are shown in block diagrams. Therefore, in the following divider block diagrams, we will only show the flip-flops, since the internal master-slave latches are implied by the definition of a flip-flop.

The additional AND gate in the divide-by-3 circuit results in the below relationship between the two outputs Q1 and  $\overline{Q2}$  and prevents the output state 00.

$$Q1(n) = \overline{Q2}(n-1) \tag{2.12}$$

$$\overline{Q2}(n) = \overline{Q2}(n-1) \text{ AND } Q1(n-1)$$

$$\overline{Q2}(n) = Q2(n-1) \text{ OR } \overline{Q1}(n-1)$$

(2.13)

The resulting state table for the outputs is shown in Fig. 7. Note that the states of

| State               | Table            |

|---------------------|------------------|

| Q <sub>1</sub><br>0 | $\overline{Q_2}$ |

| 1                   | 1                |

| 1<br>0              | 0<br>1           |

| 1                   | 1<br>0           |

| 0                   | 1                |

Fig. 7. State table of a divide-by-3 frequency divider

Fin are not shown for simplicity, but each state of Q1 and  $\overline{Q2}$  are triggered by a transition of Fin. Therefore, each row (each state of Q1 and  $\overline{Q2}$ ) implies one clock period of Fin. It is seen that the outputs have three possible states, therefore three times the period of the input clock Fin.

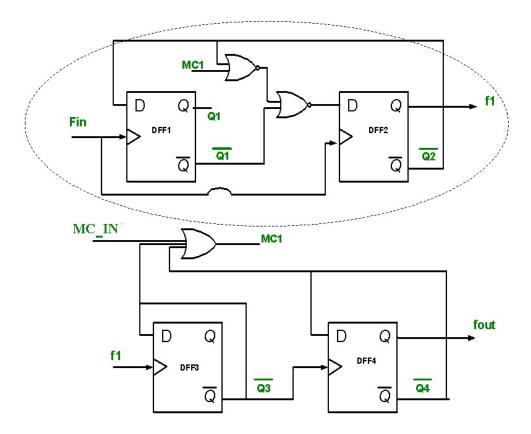

### c. Dual Modulus Division

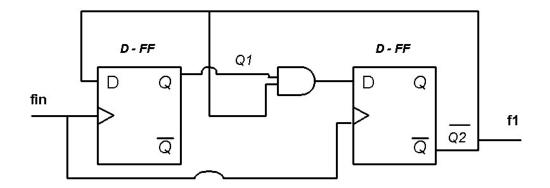

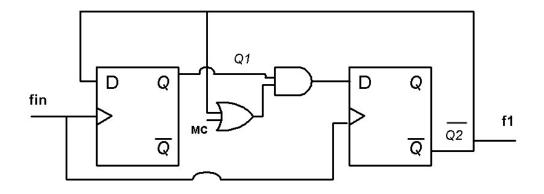

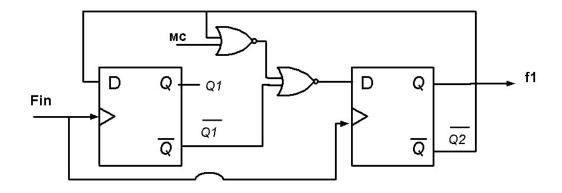

Dual modulus division, often noted as divide-by-M/(M+1) is very commonly used in frequency synthesizers. A commonly used dual modulus divider, that implements the core of larger ratio dual modulus dividers, is the divide-by-3/4 circuit that is shown in Fig. 8. When the modulus control (MC) is low, the output of the OR gate becomes  $\overline{Q2}$ and therefore the circuit reduces to a divide-by-3. When MC is high, the input of the second flip-flop is equal to the output of the first flip-flop. Then, the divider acts as the synchronous cascade of two divide-by-2 circuits, therefore becomes a divide-by-4 circuit.

Fig. 8. Block diagram of a dual modulus divide-by-3/4 frequency divider

Due to the reduced number of inverter stages, NAND and NOR circuits are preferred over AND, OR circuits in implementation. To convert the divide-by-3/4 block of Fig. 8 into a NOR-based implementation, we apply De Morgan's law as follows:

$$Q2(n) = \left(MC(n-1) \text{ OR } \overline{Q2}(n-1)\right) \text{ AND } Q1(n-1)$$

$$\overline{Q2(n)} = \overline{\left(MC(n-1) \text{ OR } \overline{Q2}(n-1)\right)} \text{ OR } \overline{Q1}(n-1)$$

$$Q_2(n) = \left(MC(n-1) \text{ NOR } \overline{Q2}\right) \text{ NOR } \overline{Q1}(n-1)$$

(2.14)

the NOR-based implementation of the divide-by-3/4 circuit is shown in Fig. 9. Another core dual modulus divider is a divide-by-2/3 circuit which follows a similar logic with a 3/4 divider. The derivation of a divide-by-2/3 circuit is left to the reader.

Fig. 9. Block diagram of the NOR based divide-by-3/4 circuit

# 2. Programmable Divider

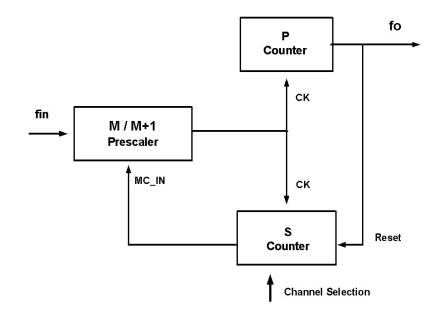

The programmable dividers in the feedback path of the loop should generate the division ratios given by (4.1). Pulse-swallow dividers [14] are commonly used in wireless frequency synthesizers to control the output channel frequency of the PLL. The block diagram of a pulse-swallow divider is shown in Fig. 10.

The input clock of the pulse-swallow divider (in this design, it is the output of the divide-by-2 IQ generation circuit in the forward path) is a dual modulus prescaler (DMP). The DMP runs at the highest frequency in the pulse-swallow divider, and is therefore the most power-critical block. Depending on the value of its control signal  $MC\_IN$ , the DMP divides its input frequency by M (when  $MC\_IN$  is logic 0) or by M + 1 (when  $MC\_IN$  is logic 1).

The output of the DMP controls the program and swallow counters. The program counter can count to a maximum of P cycles where the value of P is constant. The value of S on the other hand, is variable and determined by the channel selection control bits. The operation is as follows. Let's assume that initially the DMP control

Fig. 10. Block diagram of a pulse-swallow programmable divider

$MC\_IN$  is set high and DMP is in divide-by-M mode. In this case, program counter counts and when it reaches S cycles the S counter resets  $MC\_IN$ . The DMP starts dividing-by-(M+1). The P counter continues counting until it reaches its maximum count of P. Then, the S counter sets  $MC\_IN$  to a logic high again and a new division cycle begins. Note that the output Fo of the pulse-swallow divider goes through one period for every N cycles of the input Fin. Based on this discussion, the total division ratio of the pulse-swallow divider is given by:

$$N = (M+1) \times S + M \times (P-S)$$

$$N = M \times P + S$$

(2.15)

Table VII summarizes the values of M,P and S used in this implementation, to achieve the values of N given in (4.1). Note that P is a power of 2. Therefore, the counter will wrap around and start counting from 0 automatically when it reaches its

| Parameter | Value     |  |  |

|-----------|-----------|--|--|

| Р         | 32        |  |  |

| S         | 1,2,3,,16 |  |  |

| M/(M+1)   | 15/16     |  |  |

Table VII. Summary of the pulse-swallow divider parameter values

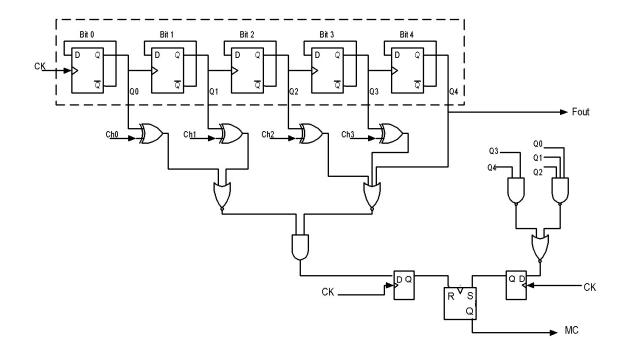

As seen from Table VII, S takes 16 values. Therefore, 4 channel control bits are used in the design. While it is called a counter, in implementation, the function of S described above, can be implemented with digital logic circuitry. The implementation of program counter and the function of S in this synthesizer is shown in Fig. 11. CK is the output of the dual modulus prescaler as shown in Fig. 10. Note that the Set and Reset control signals have one more clock delay due to the additional D-flip-flops. Therefore, these D-flip-flop inputs are high when P counter output is equal to P-1 and to S-1. Then, the channel select bit word is:

$$Ch_3 Ch_2 Ch_1 Ch_0 = S - 1 (2.16)$$

Based on the values of M shown in Table VII, the P and S counters operate at frequencies less than 200MHz. Therefore, the circuit-level implementation of the logic gates shown in Fig. 11 are done by conventional static CMOS logic [28].

Fig. 11. Block diagram of the P counter and S block

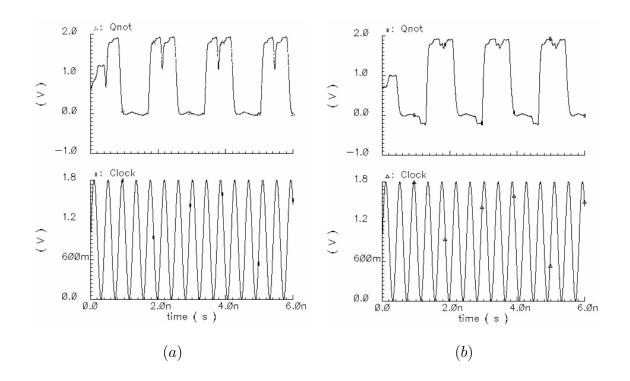

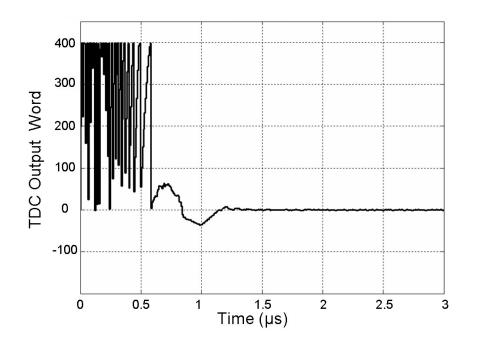

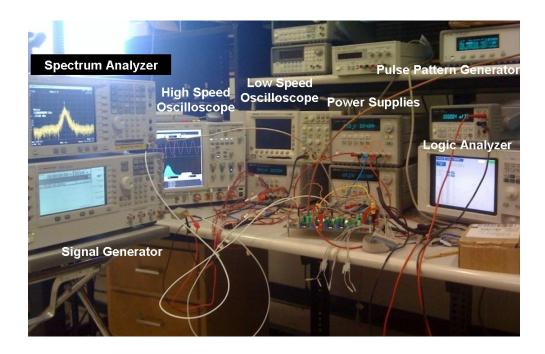

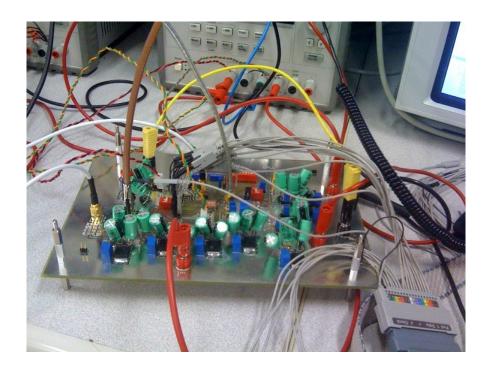

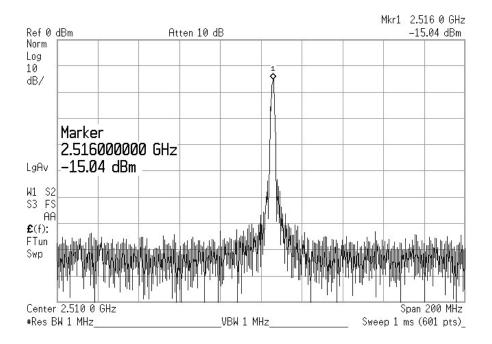

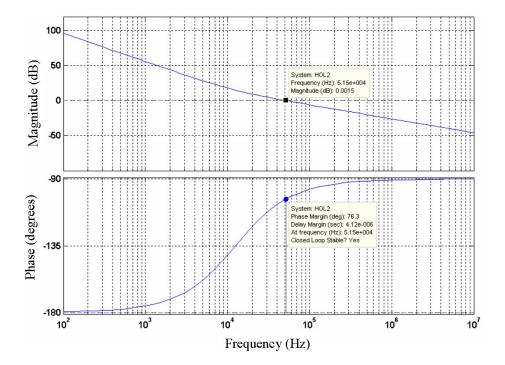

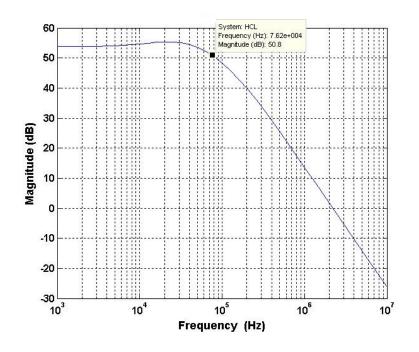

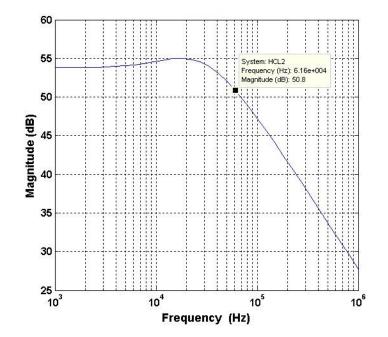

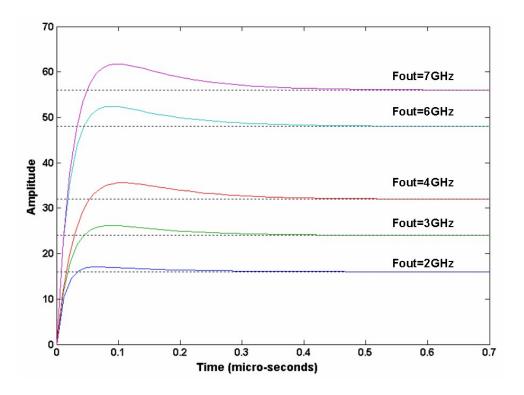

### 3. Dual Modulus Prescaler Implementation