# DESIGN METHODOLOGIES FOR BUILT-IN TESTING OF INTEGRATED RF TRANSCEIVERS WITH THE ON-CHIP LOOPBACK TECHNIQUE

A Thesis

by

## MARVIN OLUFEMI ONABAJO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2007

Major Subject: Electrical Engineering

# DESIGN METHODOLOGIES FOR BUILT-IN TESTING OF INTEGRATED RF TRANSCEIVERS WITH THE ON-CHIP LOOPBACK TECHNIQUE

#### A Thesis

by

## MARVIN OLUFEMI ONABAJO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Approved by:

Chair of Committee, Jose Silva-Martinez

Committee Members, Edgar Sánchez-Sinencio

Sunil Khatri

Duncan M. H. Walker

Head of Department, Costas N. Georghiades

December 2007

Major Subject: Electrical Engineering

#### **ABSTRACT**

Design Methodologies for Built-In Testing of Integrated RF Transceivers with

the On-Chip Loopback Technique. (December 2007)

Marvin Olufemi Onabajo, B.S., The University of Texas at Arlington

Chair of Advisory Committee: Dr. Jose Silva-Martinez

Advances toward increased integration and complexity of radio frequency (RF) and mixed-signal integrated circuits reduce the effectiveness of contemporary test methodologies and result in a rising cost of testing. The focus in this research is on the circuit-level implementation of alternative test strategies for integrated wireless transceivers with the aim to lower test cost by eliminating the need for expensive RF equipment during production testing.

The first circuit proposed in this thesis closes the signal path between the transmitter and receiver sections of integrated transceivers in test mode for bit error rate analysis at low frequencies. Furthermore, the output power of this on-chip loopback block was made variable with the goal to allow gain and 1-dB compression point determination for the RF front-end circuits with on-chip power detectors. The loopback block is intended for transceivers operating in the 1.9-2.4GHz range and it can compensate for transmitter-receiver offset frequency differences from 40MHz to 200MHz. The measured attenuation range of the 0.052mm<sup>2</sup> loopback circuit in 0.13µm CMOS technology was

26-41dB with continuous control, but post-layout simulation results indicate that the attenuation range can be reduced to 11-27dB via optimizations.

Another circuit presented in this thesis is a current generator for built-in testing of impedance-matched RF front-end circuits with current injection. Since this circuit has high output impedance (>1k $\Omega$  up to 2.4GHz), it does not influence the input matching network of the low-noise amplifier (LNA) under test. A major advantage of the current injection method over the typical voltage-mode approach is that the built-in test can expose fabrication defects in components of the matching network in addition to on-chip devices. The current generator was employed together with two power detectors in a realization of a built-in test for a LNA with 14% layout area overhead in 0.13 $\mu$ m CMOS technology (<1.5% for the 0.002mm<sup>2</sup> current generator). The post-layout simulation results showed that the LNA gain (S<sub>21</sub>) estimation with the external matching network was within 3.5% of the actual gain in the presence of process-voltage-temperature variations and power detector imprecision.

#### **ACKNOWLEDGMENTS**

I would like to thank my advisor, Dr. Jose Silva-Martinez, whose support, guidance, and constructive critique made this research possible. I also greatly appreciate Dr. Edgar Sánchez-Sinencio's close mentorship and assistance related to this work as well as to my graduate studies. Having received valuable comments and suggestions from Dr. Sunil Khatri and Dr. Duncan Walker, I want to thank them for serving on my thesis committee.

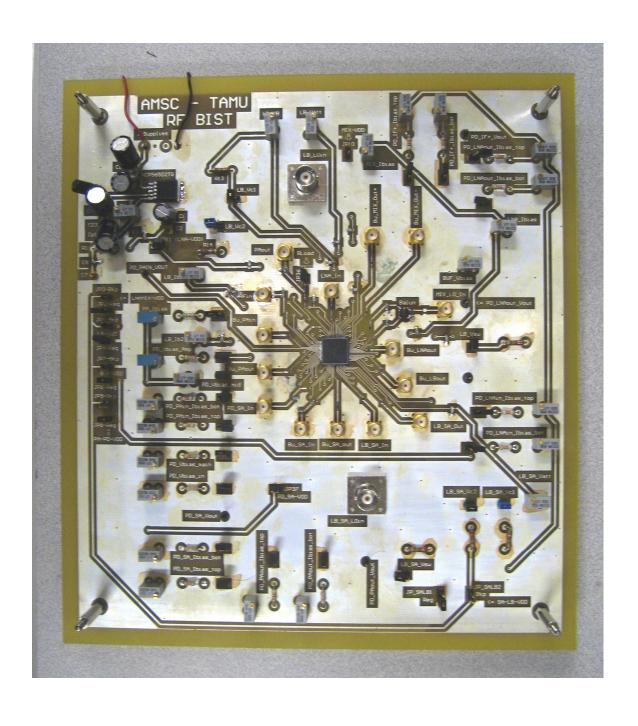

It has been a pleasure and learning experience to collaborate with Xiaohua Fan and Felix Fernandez during the research by merging our test circuitry and circuits-under-test. To be more specific, Felix designed the RMS detectors/PA and Xiaohua the LNAs/down-conversion mixer of the test systems that are discussed in this thesis. In addition, countless ideas originated from discussions and problem solving sessions that I had together with my project partners and advisors.

Many thanks also go out to fellow AMSC group members for helpful conversations regarding research and course projects. Special thanks to Chinmaya Mishra, Sang Wook Park, Manisha Gambhir, Vijay Dhanasekaran, Mohamed Mobarak, Faisal Hussien, Jason Wardlaw, and Didem Turker for their recommendations during the preparations for fabrication and ongoing characterization of the chip. I would like to thank Ella Gallagher for helping to facilitate events and completion of paperwork on a regular basis; it has been nice to have an enthusiastic guide in the bureaucratic jungle.

I would like to express my gratitude to the Department of Electrical & Computer Engineering and Texas Instruments, Inc. for financial support; and acknowledge the sponsorship of the test chip fabrication by United Microelectronics Corporation.

A fortunate aspect of my graduate studies was to go through the experience with Casey Wang, a good friend, cube neighbor, and project partner who made the first two years more enjoyable, especially off-campus and during those necessary breaks - thanks. I also want to thank Bola Onipede for helping me to get acquainted with the town and the university during the first semester.

In retrospect, I would like to thank Dr. Sungyong Jung from The University of Texas at Arlington for introducing me to research in integrated circuit design and continuing to be a mentor.

I am grateful for the love, encouragement, and support from my parents and brother over the years. Their influence and motivation has inspired me in many aspects of life, including education.

## TABLE OF CONTENTS

|                                                                                                                                             | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|

| ABSTRACT                                                                                                                                    | iii  |

| ACKNOWLEDGMENTS                                                                                                                             | v    |

| TABLE OF CONTENTS                                                                                                                           | vii  |

| LIST OF FIGURES                                                                                                                             | ix   |

| LIST OF TABLES                                                                                                                              | xii  |

| I. INTRODUCTION                                                                                                                             | 1    |

| I.1. Economical motivation for built-in testing of wireless integrated circuits .  I.2. Alleviating manufacturing test issues               | 4    |

| I.3. Technical challenges associated with RF transceiver built-in testing  I.4. On-chip measurement circuitry for RF transceiver front-ends |      |

| II. TRANSCEIVER TESTING WITH ON-CHIP LOOPBACK                                                                                               | 9    |

| II.1. Applications                                                                                                                          | 9    |

| II.1.2. On-chip calibration                                                                                                                 |      |

| II.2. The loopback testing method and related works                                                                                         |      |

| II.2.1. Test coverage and accuracy limitations                                                                                              |      |

| II.3. System-level overview to investigate on-chip loopback                                                                                 |      |

| II.5. Implementation overview of the loopback block                                                                                         |      |

| II.5.1. Switches                                                                                                                            |      |

| II.5.2. Attenuation                                                                                                                         |      |

| II.5.3. Frequency translation                                                                                                               |      |

| II.5.4. Design challenges                                                                                                                   |      |

| III. ATTENUATOR AND OFFSET MIXER FOR TRANSCEIVER BIT                                                                                        | 25   |

| III.1. RF attenuator design                                                                                                                 |      |

| III.1.1. Background                                                                                                                         |      |

| III.1.2. Input switch/attenuator: proposed implementation                                                                                   |      |

| III.1.3. Component dimensions and layout                                                                                                    |      |

| III.1.4. Post-layout simulation results                                                                                                     |      |

| III.2. Offset mixer with variable gain for loopback testing                                                                                 |      |

| III.2.1. Background and application-specific constraints                                                                                    |      |

| III.2.2. Proposed mixer topology                                                                                                            | 41   |

| III.2.3. Component dimensions and layout                                                                                                    | 48   |

|                                                                             | Page |

|-----------------------------------------------------------------------------|------|

| III.2.4. LO input buffer                                                    | 50   |

| III.2.5. Post-layout simulation results                                     | 52   |

| III.3. Loopback block consisting of attenuator and offset mixer             |      |

| III.3.1. Prototype chip with RF front-end circuits and loopback test option |      |

| III.3.2. Post-layout simulation results                                     |      |

| III.3.3. Measurement results                                                |      |

| III.3.4. Discussion                                                         | 70   |

| IV. RF BIT WITH ON-CHIP CURRENT INJECTION                                   | 72   |

| IV.1. Background and Motivation                                             |      |

| IV.2. BIT extension to components of the impedance matching network         |      |

| IV.2.1. Example test scenario: impedance-matched low-noise amplifier        |      |

| IV.2.2. Voltage-mode testing                                                |      |

| IV.2.3. Current-mode testing: proposed approach                             |      |

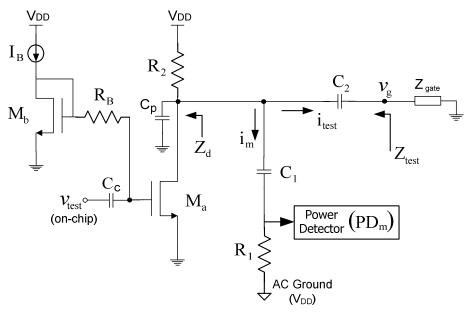

| IV.3. Test current signal generation circuit                                |      |

| IV.3.1. Proposed topology and design considerations                         |      |

| IV.3.2. Component dimensions and layout                                     |      |

| V. SUMMARY AND CONCLUSIONS                                                  |      |

| V.1. On-chip loopback test method for integrated transceivers               |      |

| V.2. RF front-end testing with current injection                            |      |

| V.3. Opportunities for further research                                     | 97   |

| REFERENCES                                                                  | 99   |

| APPENDIX A                                                                  | 104  |

| APPENDIX B                                                                  | 110  |

| APPENDIX C                                                                  | 113  |

| APPENDIX D                                                                  | 115  |

| APPENDIX E                                                                  | 117  |

| APPENDIX F                                                                  | 118  |

|                                                                             |      |

| APPENDIX G                                                                  |      |

| VITA                                                                        | 121  |

# LIST OF FIGURES

|           | Page                                                                                                         |

|-----------|--------------------------------------------------------------------------------------------------------------|

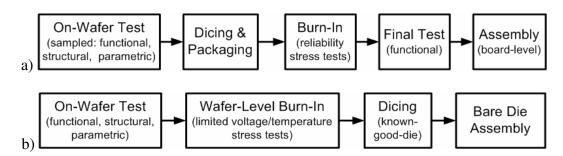

| Figure 1  | Production test flows: (a) traditional (b) known-good-die                                                    |

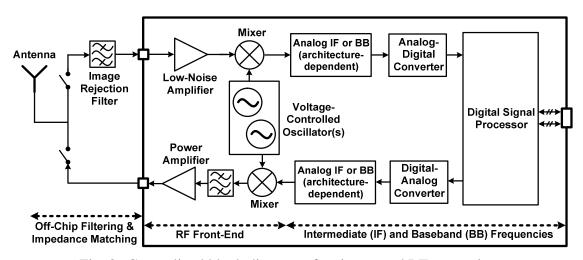

| Figure 2  | Generalized block diagram of an integrated RF transceiver                                                    |

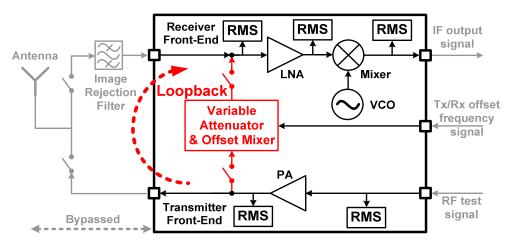

| Figure 3  | Transceiver front-end test system with on-chip loopback                                                      |

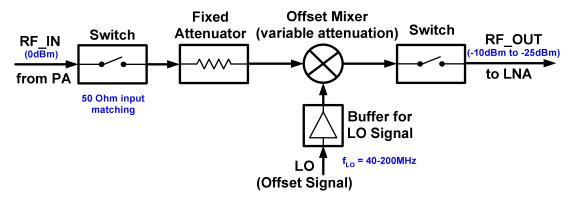

| Figure 4  | Block-level loopback representation                                                                          |

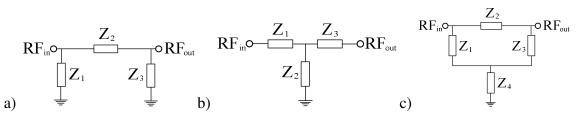

| Figure 5  | RF attenuator topologies: (a) $\pi$ -type (b) T-type (c) bridge-T-type26                                     |

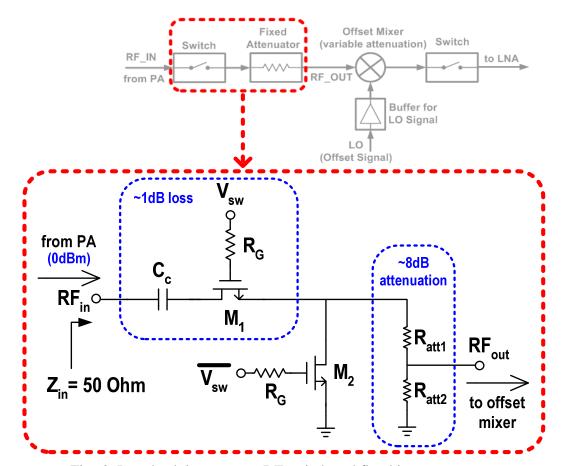

| Figure 6  | Loopback input stage: RF switch and fixed input attenuator28                                                 |

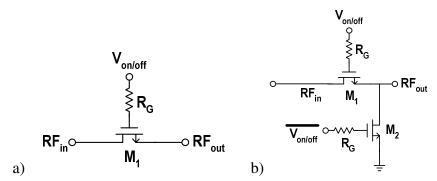

| Figure 7  | (a) Simple RF switch (b) switch with shunt transistor29                                                      |

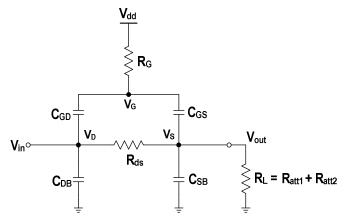

| Figure 8  | Equivalent model of simple switch with gate resistance (triode region)30                                     |

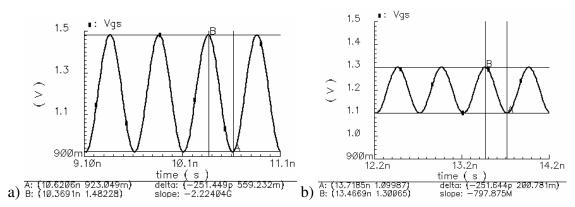

| Figure 9  | RF switch: $V_{gs(t)}$ (a) $R_G$ =0 [ $V_{gs\_p-p}$ =0.56V] (b) $R_G$ =2k $\Omega$ [ $V_{gs\_p-p}$ =0.20V]32 |

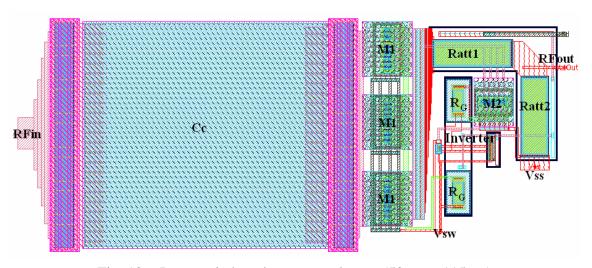

| Figure 10 | Input switch and attenuator layout $(50\mu\text{m} \times 115\mu\text{m})$                                   |

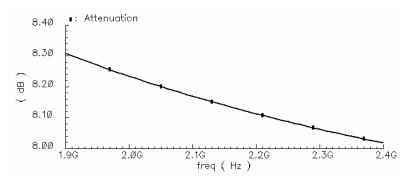

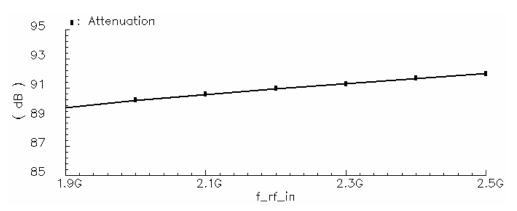

| Figure 11 | Input switch and attenuator: attenuation vs. frequency                                                       |

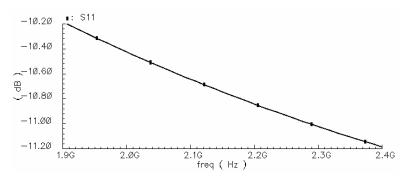

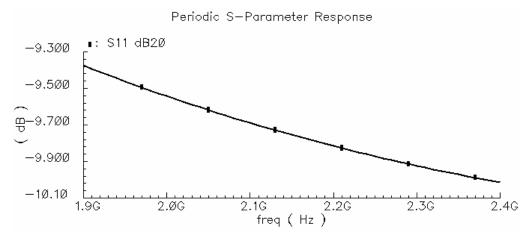

| Figure 12 | Input switch and attenuator: S <sub>11</sub> vs. frequency36                                                 |

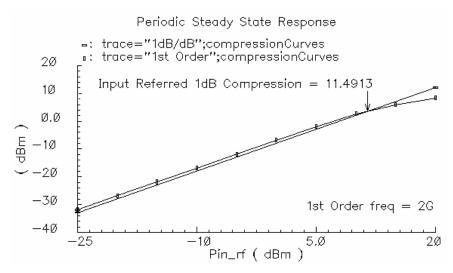

| Figure 13 | Input switch and attenuator: input 1-dB compression point                                                    |

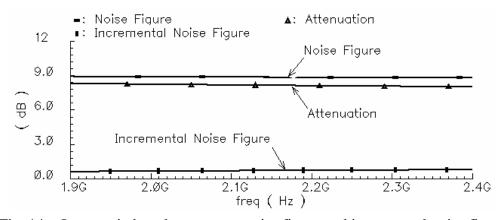

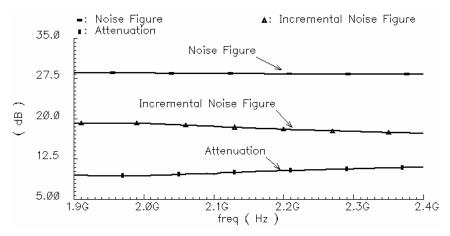

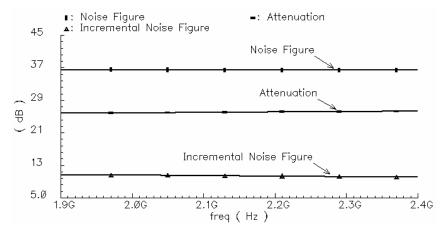

| Figure 14 | Input switch and attenuator: noise figure and incremental noise figure37                                     |

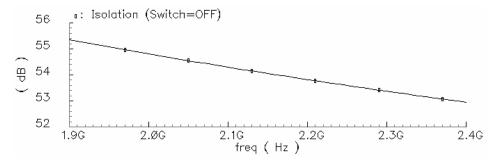

| Figure 15 | Input switch and attenuator: isolation in off-state                                                          |

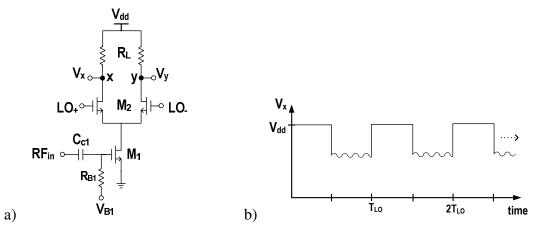

| Figure 16 | (a) Simple single-balanced mixer (b) transient V <sub>x</sub>                                                |

| Figure 17 | (a) Single-balanced mixer with DC voltage stabilization (b) transient $V_x$ 43                               |

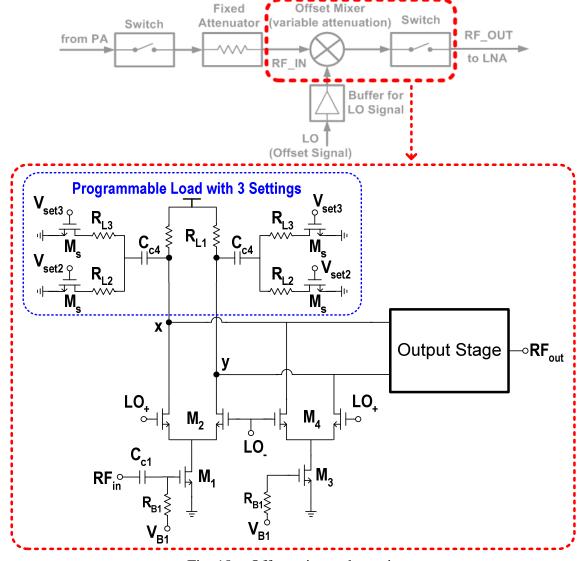

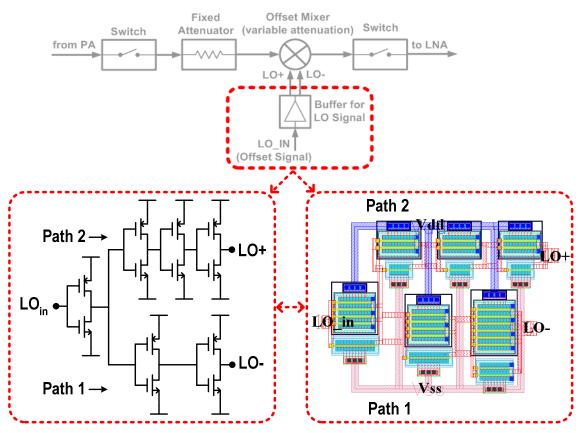

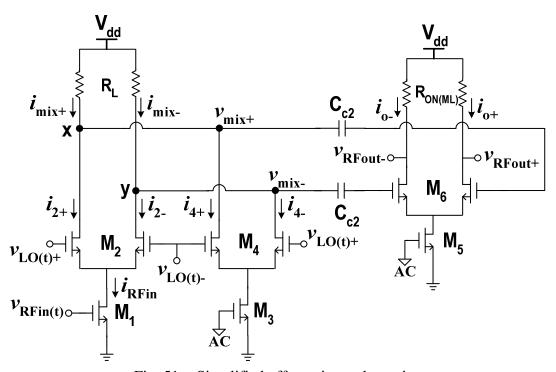

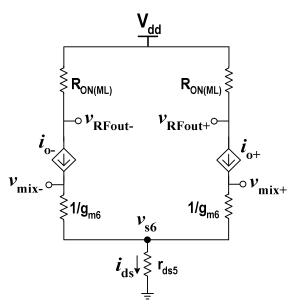

| Figure 18 | Offset mixer schematic                                                                                       |

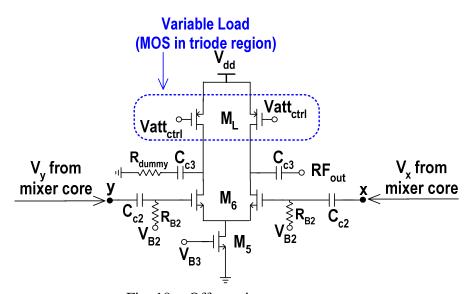

| Figure 19 | Offset mixer output stage                                                                                    |

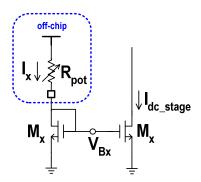

| Figure 20 | Biasing scheme for M <sub>1</sub> , M <sub>3</sub> , and M <sub>5</sub> in the offset mixer48                |

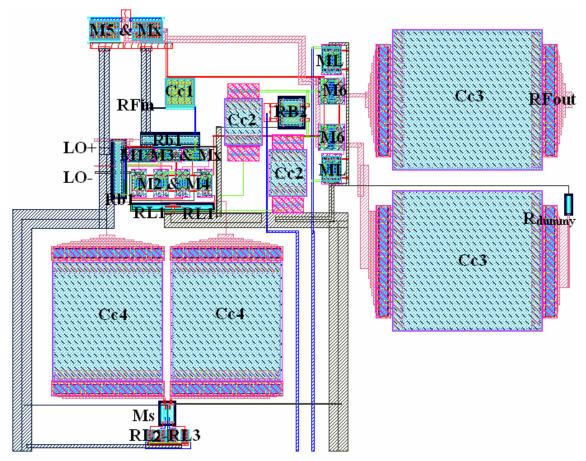

| Figure 21 | Offset mixer layout $(185 \mu m \times 230 \mu m)$                                                           |

| Figure 22 | LO input buffer schematic and layout $(15\mu m \times 20\mu m)$                                              |

|           | Pa                                                                                    | ge |

|-----------|---------------------------------------------------------------------------------------|----|

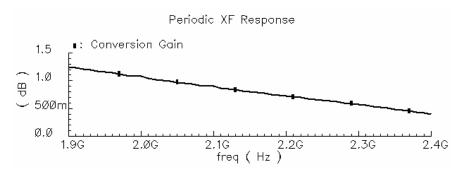

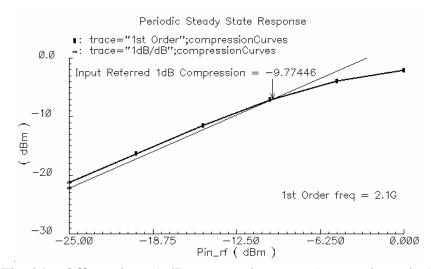

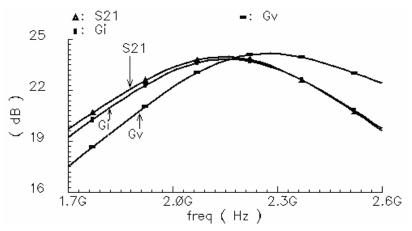

| Figure 23 | Offset mixer: max. voltage conversion gain vs. RF frequency                           | 53 |

| Figure 24 | Offset mixer: 1-dB compression curve (max. gain setting)                              | 53 |

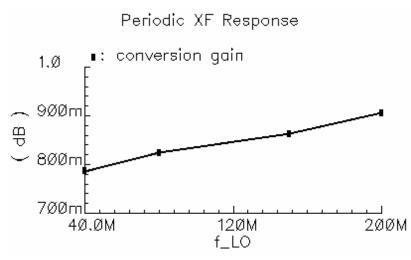

| Figure 25 | Offset mixer: max. conversion gain vs. LO frequency ( $f_{RFout} = 2.1 GHz$ )         | 53 |

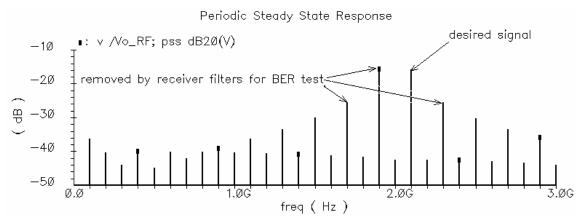

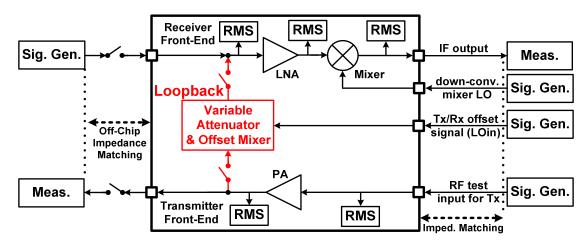

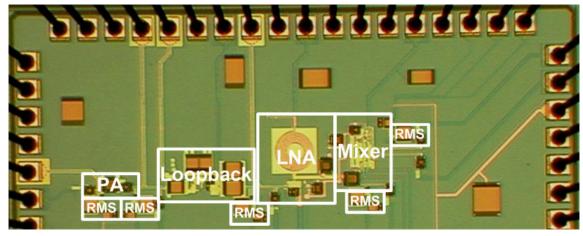

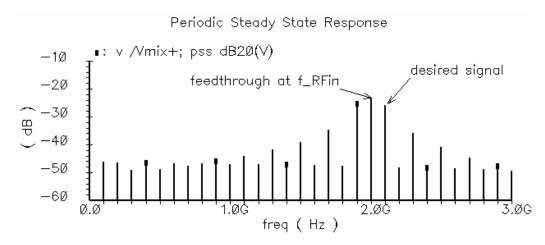

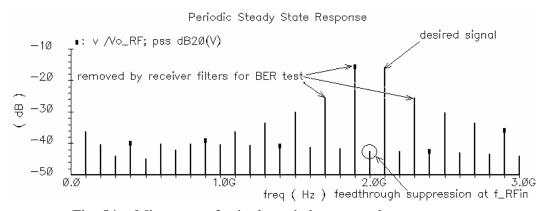

| Figure 26 | Offset mixer output voltage spectrum                                                  | 54 |

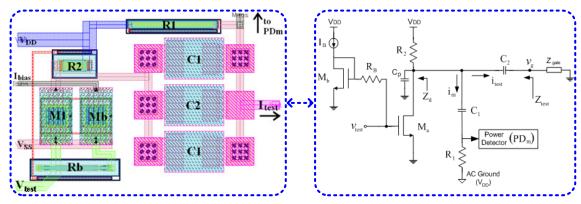

| Figure 27 | Test chip block diagram                                                               | 57 |

| Figure 28 | Test chip micrograph                                                                  | 57 |

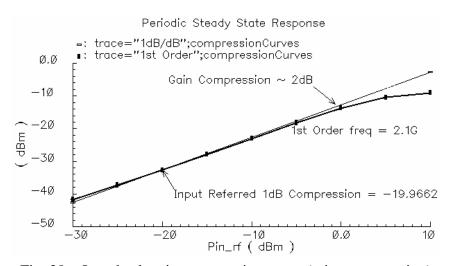

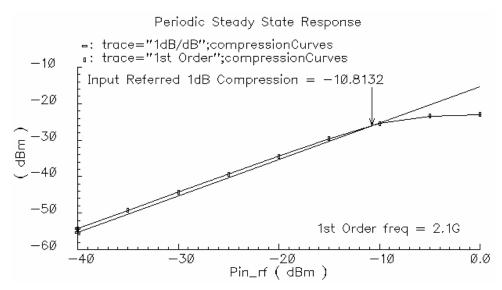

| Figure 29 | Loopback gain compression curve (min. atten. setting)                                 | 60 |

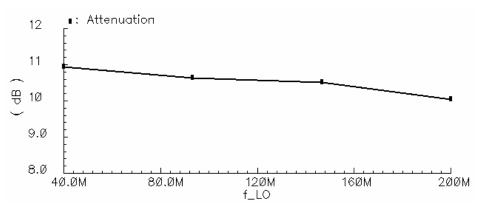

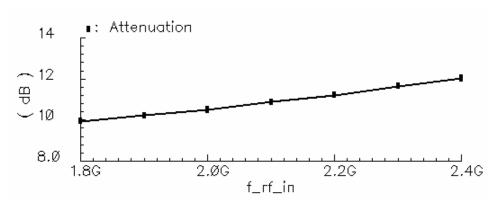

| Figure 30 | Loopback min. attenuation vs. LO frequency ( $f_{RFin} = 2GHz$ )                      | 61 |

| Figure 31 | Loopback min. attenuation vs. input frequency ( $f_{LO} = 100MHz$ )                   | 61 |

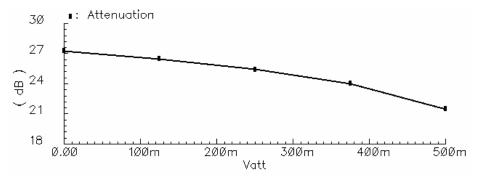

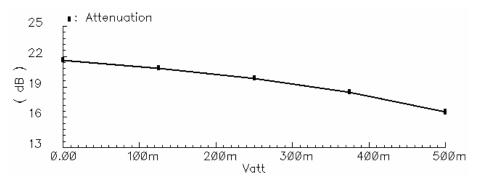

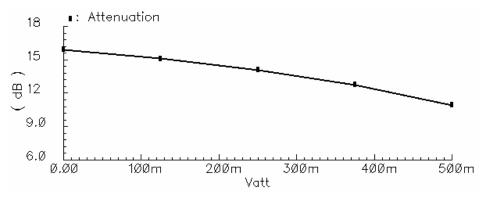

| Figure 32 | Loopback attenuation vs. control voltage, Vatt <sub>ctrl</sub> in Fig. 18 (setting 1) | 62 |

| Figure 33 | Loopback attenuation vs. control voltage, Vatt <sub>ctrl</sub> in Fig. 18 (setting 2) | 62 |

| Figure 34 | Loopback attenuation vs. control voltage, Vatt <sub>ctrl</sub> in Fig. 18 (setting 3) | 62 |

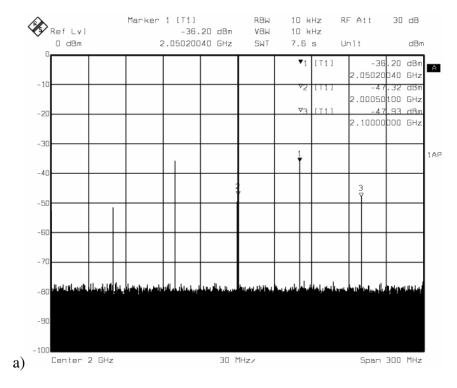

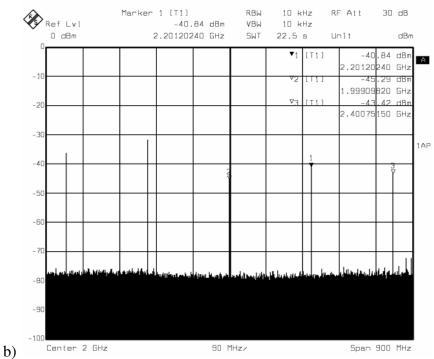

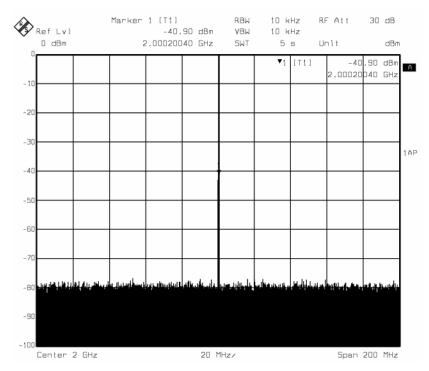

| Figure 35 | Measured loopback output spectrum ( $RF_{in} = -4.9dBm$ at $2GHz$ )                   | 66 |

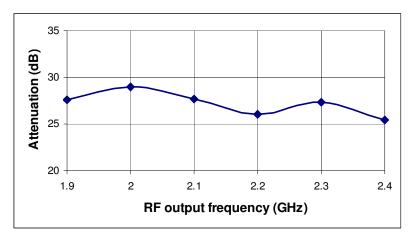

| Figure 36 | Loopback attenuation vs. RF output frequency                                          | 67 |

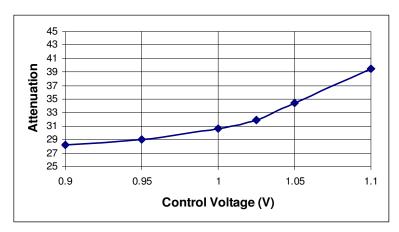

| Figure 37 | Continuous attenuation range with the loopback control voltage                        | 68 |

| Figure 38 | Input-output isolation when the loopback block is deactivated                         | 69 |

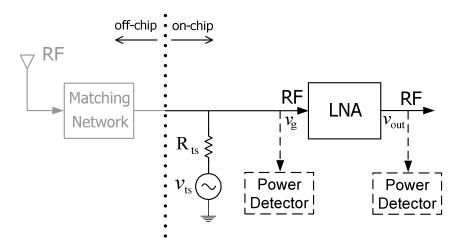

| Figure 39 | Conventional voltage-mode on-chip testing scheme                                      | 73 |

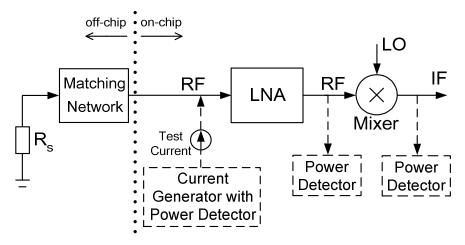

| Figure 40 | Current injection testing scheme.                                                     | 74 |

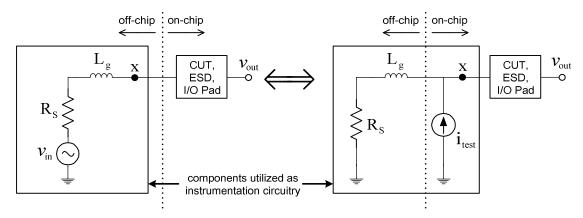

| Figure 41 | Equivalence of voltage and current domain test input signals                          | 75 |

| Figure 42 | LNA testing: (a) normal operation (b) voltage-mode on-chip testing                    | 77 |

| Figure 43 | Current injection BIT configuration                                                   | 78 |

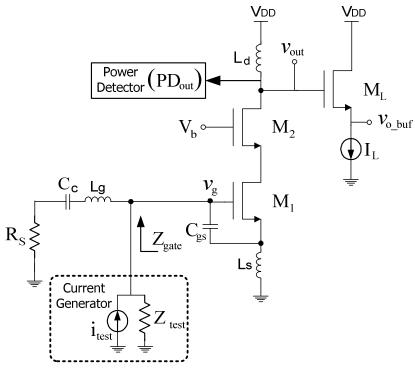

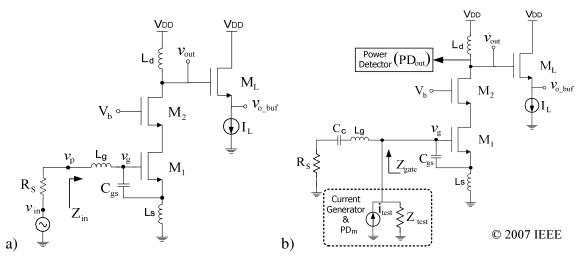

| Figure 44 | RF test current generator                                                             | 81 |

| Figure 45 | Current generator layout (40um × 50um)                                                | 86 |

|           | ı                                                                                   | Page |

|-----------|-------------------------------------------------------------------------------------|------|

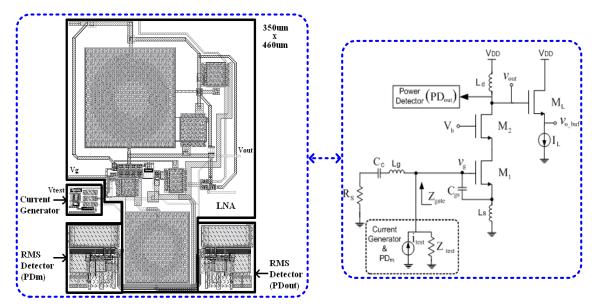

| Figure 46 | Layout of LNA BIT with current injection                                            | 87   |

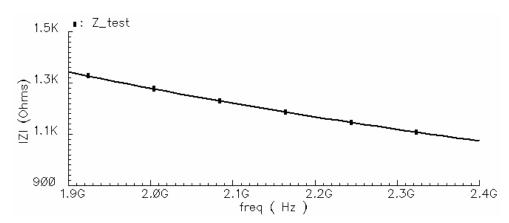

| Figure 47 | Current generator output impedance (Z <sub>test</sub> ) vs. frequency               | 89   |

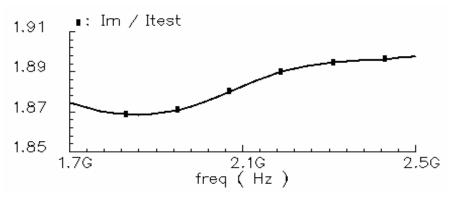

| Figure 48 | Ratio of measured current $(i_m)$ and test current $(i_{test})$ vs. frequency       | 90   |

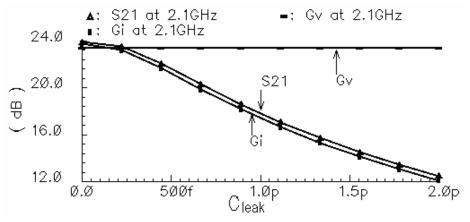

| Figure 49 | Current-mode $(G_I)$ and voltage-mode $(G_V)$ estimation of $S_{21}$                | 92   |

| Figure 50 | $S_{21}$ estimation with ESD protection diodes and leakage due to defects           | 93   |

| Figure 51 | Simplified offset mixer schematic                                                   | .104 |

| Figure 52 | Mixer core output voltage spectrum                                                  | .108 |

| Figure 53 | Simplified small-signal equiv. circuit for the offset mixer output stage            | .110 |

| Figure 54 | Mixer stage 2: single-ended output voltage spectrum                                 | .112 |

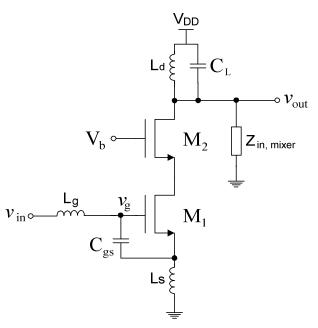

| Figure 55 | LNA schematic (UMC 0.13µm techn./1.2V supply)                                       | .113 |

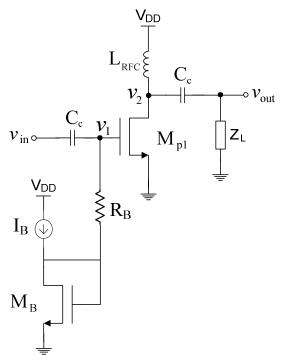

| Figure 56 | PA schematic (class A, UMC 0.13μm techn./1.2V supply)                               | .114 |

| Figure 57 | Loopback block: S <sub>11</sub> vs. frequency                                       | .115 |

| Figure 58 | Loopback block: Tx/Rx isolation (attenuation in off-state)                          | .115 |

| Figure 59 | Loopback block: noise figure vs. frequency (min. atten. setting)                    | .116 |

| Figure 60 | Loopback block: noise figure vs. frequency (max. atten. setting)                    | .116 |

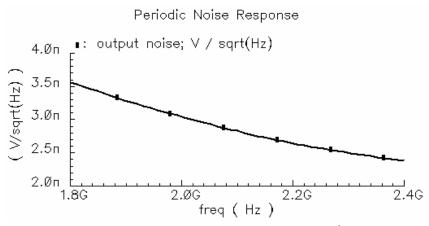

| Figure 61 | Loopback block: worst-case output noise (V/\sqrt{Hz}) vs. frequency                 | .116 |

| Figure 62 | LNA & output buffer (M <sub>L</sub> ): (a) normal config. (b) current injection BIT | .118 |

| Figure 63 | Current generator: 1dB compression curve                                            | .119 |

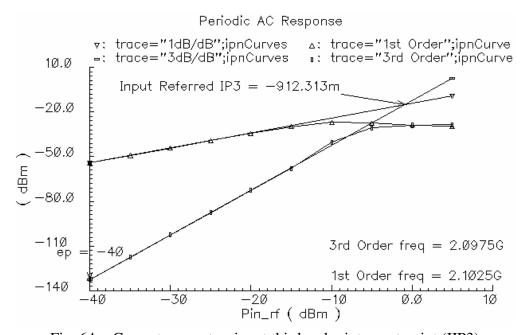

| Figure 64 | Current generator: input third-order intercept point (IIP3)                         | .119 |

| Figure 65 | Current generator: output noise (V <sup>2</sup> /Hz) vs. frequency                  | .120 |

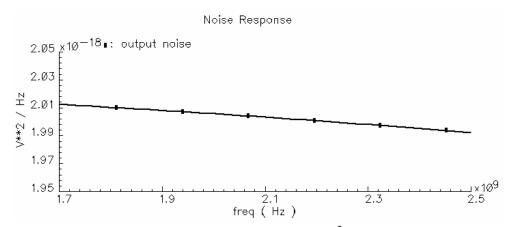

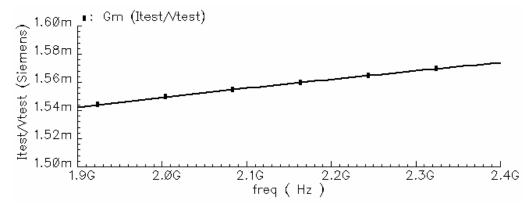

| Figure 66 | Current generator: $g_{test}$ ( $i_{test}$ / $v_{test}$ ) vs. frequency             | .120 |

# LIST OF TABLES

|             | Page                                                                    |

|-------------|-------------------------------------------------------------------------|

| Table I     | Alternative strategies for test cost reduction                          |

| Table II    | Conventional transceiver tests vs. coverage with BIT11                  |

| Table III   | Proof-of-concept RF front-end parameters                                |

| Table IV    | High-level loopback block specification targets                         |

| Table V     | Comparison of RF attenuators                                            |

| Table VI    | RF switch preliminary simulations at 2GHz                               |

| Table VII   | Input attenuator component sizes (UMC 0.13μm CMOS technology)34         |

| Table VIII  | Input switch and attenuator simulation results                          |

| Table IX    | Comparison of relevant mixer performance specifications                 |

| Table X     | Offset mixer component sizes (UMC 0.13µm CMOS technology)49             |

| Table XI    | Offset mixer simulation results                                         |

| Table XII   | Loopback block simulation results                                       |

| Table XIII  | Loopback block: comparison of post-layout and measurement results64     |

| Table XIV   | Loopback attenuation (measured at f <sub>RFout</sub> =2.1GHz)68         |

| Table XV    | Current generator component dimensions                                  |

| Table XVI   | Current generator simulation results89                                  |

| Table XVII  | LNA S <sub>21</sub> estimation error with current injection at 2.1GHz91 |

| Table XVIII | LNA performance comparison                                              |

| Table XIX   | Transmitter buffer (PA) performance comparison                          |

| Table XX    | LNA performance comparison – current injection BIT118                   |

### I. INTRODUCTION\*

Most semiconductor product improvements over the past decades are direct or indirect consequences of the perpetual shrinking of devices and circuits, allowing performance enhancements at lower fabrication cost. Yet, in the particular case of wireless mixed-signal integrated systems, the trend towards increasing integration and complexity has been paralleled by technical challenges and rising cost of testing, which can amount up to 40-50% of the total manufacturing cost [1], [2]. In recent years, built-in self-test (BIST) and design-for-test (DFT) methods for analog and mixed-signal circuits have received growing attention as part of a cost reduction effort that will allow more people globally to benefit from access to cellular communication.

The concepts of using BIST and DFT methods to facilitate the manufacturing test of digital integrated circuits are not new, and their development has led to widespread utilization and standardization in the industry over the years. In contrast, analog/RF BIST techniques are significantly less mature because failure mechanisms are more complicated and specification-based test of analog circuits requires more instrumentation resources. Another problematic aspect during the test of analog circuits is that they are more sensitive to crosstalk as well as process, voltage, and temperature (PVT) variations

This thesis follows the style and format of the IEEE Journal of Solid-State Circuits.

<sup>\*© 2006</sup> IEEE. Excerpts from sections I.1-I.2 are in part reprinted, with permission, from "Strategic test cost reduction with on-chip measurement circuitry for RF transceiver front-ends – an overview," M. Onabajo, F. Fernandez, J. Silva-Martinez, and E. Sánchez-Sinencio, in *Proc.* 49<sup>th</sup> IEEE International Midwest Symposium on Circuits and Systems, vol. 2, pp. 643-647, August 2006.

than their digital counterparts; which entails that verification of individual blocks may not be sufficient to guarantee the desired performance when the whole system is operating [3]. With the existing challenges, current research efforts in the analog BIST field are focused on both, the improvement of fault models to enable more effective defect-oriented/structural testing as well as the development of novel specification-based/functional test approaches to verify system-level performance.

In this work, the system under investigation with respect to testability is the integrated RF transceiver, which is an essential component in wireless communication devices. It will be discussed how the proposed on-chip circuitry can be employed to route the test signal from the transmitter to the receiver sections of the transceiver. This on-chip loopback approach has the benefits of allowing built-in test (BIT) of analog blocks with integrated power detectors in combination with simultaneous system-level functional verification during production test.

## I.1. Economical motivation for built-in testing of wireless integrated circuits

Comprehensive but time-consuming characterization testing is currently conducted during design debug and prior to high-volume production in order to ensure product compliance to specifications. However, the purpose of production testing is to quickly screen out substandard parts due to processing defects and variations; a more detailed discussion about the impact of test time on cost in the production phase is provided in [4], [5]. Fig. 1 shows high-level charts of the traditional post-fabrication test flow and the test flow for known-good-die testing, which is in rising demand due to the emergence of multi-die assemblies and increasing packaging cost. The needs for

continued development of DFT/BIST methods for analog cores and wafer-level burn-in tests have both been emphasized in the 2005 International Technology Roadmap for Semiconductors [6]. Regarding the flow charts in Fig. 1, test cost reduction efforts typically fall into three categories [7]:

- "Test faster" increased equipment throughput, operational efficiency (technicians, management, process engineers), test program improvements

- "Test earlier" early identification of faulty devices to prevent incurrence of packaging and additional test cost from further processing

- "Test less" removal of redundant or non-critical tests based on statistical data correlations (i.e. final vs. wafer test), selection of less parts for sampled testing.

Fig. 1. Production test flows: (a) traditional (b) known-good-die (© 2006 IEEE)

With the advent of more complex and costly system-in-a-package (SIP) and multichip module (MCM) technologies, there is an increased incentive for known-good-die testing at wafer sort to avoid the rising cost of subsequent packaging and final test. But, on-wafer verification at RF frequencies requires high performance and costly hardware for high-volume production testing with automatic test equipment (ATE) [8]. Replacement of conventional tests with BISTs is typically conducted with the goal to reduce test interface hardware and ATE requirements.

## I.2. Alleviating manufacturing test issues

A key prerequisite to reduce RF test cost with on-chip circuitry is that the test input and output signals are limited to low frequencies in order to allow the replacement of expensive RF ATE with low-cost digital ATE. Based on the definition in [9], complete BIST requires the on-chip generation of test stimuli, analysis of the signal at the output of the circuit under test (CUT), and generation of the pass/fail result. Due to the analog nature of the signals, a full BIST of RF circuits requires long test times and significant die area overhead for on-chip signal processing [9]. Alternatively, substantial measurement circuitry and signal processing can be realized on-chip, while some remaining post-processing is still left to the external ATE. In this thesis, the latter approach will be referred to as built-in test (BIT), which is a more appropriate description since it is not a true built-in self-test because of the need for off-chip resources. The term BIT is also becoming more popular in the literature to distinguish between BIT and BIST. The objective of BIT is to make the use of low-cost ATE possible by simplifying the external processing to tasks such as DC output measurements or comparisons of low-frequency digital output bitstreams with stored reference vectors.

Off-chip generation of RF test input signals for a BIT should be avoided because it requires more expensive test hardware for signal generation and the use of impedance matching networks. Efficient ATE hardware development for RF test involves additional

cost considerations [8], [10] that need to be taken into account during conception of BIT methodologies. Table I provides a summary of key factors and their technical impact in the development of alternative test strategies with on-chip analog BIT circuitry.

Table I. Alternative strategies for test cost reduction

| Table 1. Atternative strategies for test cost reduction |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Cost Factor                                             | Technical Implications for<br>Alternative On-Chip Built-In Test Approaches                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Test time                                               | - Develop circuitry for on-chip measurements in the analog domain to avoid long signal paths to ATE and long computation time with DSP-based algorithms.                                                                                                                                                                                                                                                                                                                            |  |  |

| Number of inputs/outputs                                | <ul> <li>Minimize test pins as they drive up the die size and package cost.</li> <li>Design on-chip circuitry to maximize coverage of internal nodes.</li> <li>→ Multiplex test output signals.</li> </ul>                                                                                                                                                                                                                                                                          |  |  |

| Batch-mode testing                                      | <ul> <li>Avoid test stimuli that are difficult to generate with low-cost/low-frequency (preferably below 100MHz) digital ATE signals on multiple channels. Use robust resources that are available such as clock signals.</li> <li>Design for parallel testing of multiple parts (on-wafer test offers more cost-saving opportunities in batch-mode via multi-site testing; mechanical handling time at final test is longer because individual packages are processed).</li> </ul> |  |  |

| Test fixture<br>design                                  | <ul> <li>Use robust on-chip circuitry to generate high frequency test signals or to up-convert signals (impedance matching and RF ports require costly test fixture designs and more expensive RF measurement equipment).</li> <li>Implement communication schemes between on-chip circuitry and testers that are compatible with low-speed digital ATE.</li> </ul>                                                                                                                 |  |  |

## I.3. Technical challenges associated with RF transceiver built-in testing

Consistent progress has been made towards integrating the analog and digital portions of RF transceivers using CMOS technology, which allows cost, component

count, and power consumption reduction for mobile phones and other wireless products. Single-chip transceivers have become available on the market, but the high level of integration currently presents significant test challenges due to limited access to internal analog signals and an increasing number of functions that have to be verified [5], [11]. A simplified block diagram of a system-on-chip (SOC) transceiver is shown in Fig. 2. It includes the RF front-end, analog baseband, and mixed-signal data conversion circuits at the interface between the antenna and the digital signal processor.

Fig. 2. Generalized block diagram of an integrated RF transceiver

Conventional on-wafer or chip-package tests of SOC transceivers similar to the one in Fig. 2 involve the generation of a RF test signal that is applied at the low-noise amplifier (LNA) input pin in order to verify the functionality of the receiver path by monitoring the baseband output of the digital signal processor (DSP). In a separate transmitter test, an input bitstream is provided to the DSP, and the corresponding output of the power amplifier or pre-power amplifier (PA) is measured and processed by the

external ATE. One issue with this method is the need for external RF signals at the LNA and PA, which mandates the technically challenging tasks of developing a test setup with impedance-matched interface hardware and expensive RF signal generation/ measurement equipment. Parallelization of tests is also problematic because the RF signal generation and measurement require dedicated ATE equipment resources as well as time-consuming digital signal processing and test synchronization [5].

## I.4. On-chip measurement circuitry for RF transceiver front-ends

Another concern during production testing of transceiver SOCs is the limited availability of block-level data. Increased integration leads to more interference between blocks in addition to manufacturing process variation. For this reason, the improvement of power detectors has received growing research attention in order to perform characterization of individual blocks rather than just monitoring a few nodes with received signal strength indicators (RSSIs). Several power and signal amplitude detector topologies have been presented [12]-[15] that demonstrated promising results to provide gain and linearity estimates for pass/fail decisions in production test scenarios. Key attributes of these detectors are minimized die area, robustness to process variations, and small parasitic input capacitance to avoid degradation of the RF signal path. More extensive block-level BITs have also been proposed to extend on-chip test coverage to noise figure, input matching, and other parameters [16]-[18]. With ongoing efforts, the on-chip measurement techniques show vast potential for gaining access to internal nodes and block-level parameters, which offers more on-chip fault coverage and information for debugging designs as well as decision-making during the product ramp phase.

The first problem addressed in this thesis is a circuit-level realization of an on-chip loopback block in complementary metal-oxide-semiconductor (CMOS) technology with the capabilities of programmable attenuation and frequency translation between transmitter and receiver. System-level concepts and design constraints related to this BIT approach are discussed in section II, which also contains an elaboration why the two aforementioned features are necessary to ensure power-level compatibility and to compensate for the frequency difference between transmitter and receiver sections of transceivers that have separate uplink and downlink specifications, such as in the W-CDMA and CDMA2000 standards. The development of the proposed circuit topologies, design details, and a discussion of the post-layout simulation as well as measurement results for the loopback block can be found in section III. Another problem under investigation is the design of a test current generation circuit for built-in testing of RF transceiver front-ends, which is the focus of section IV. The target application is a novel current injection BIT technique for impedance-matched RF front-ends that permits an extension of the fault detection capability to off-chip components in the matching network. A resulting benefit is that the current injection BIT can be utilized at final package or board-level test stages in addition to wafer test. Finally, concluding remarks and opportunities for further research concerning the on-chip loopback and current injection BIT techniques are presented in section V.

#### II. TRANSCEIVER TESTING WITH ON-CHIP LOOPBACK

## II.1. Applications

#### *II.1.1. Functional testing*

An advantage of the high integration levels in modern transceiver chips comparable to the one in Fig. 2 is that comprehensive system-level functional tests can be performed to simultaneously verify multiple blocks. It is possible to employ higherlevel tests involving bit error rate (BER) or error vector magnitude (EVM) analysis instead of block-level measurements. These system-level functional tests can replace several lower-level tests, thus reducing test time and cost [4], [5], [19]. When all transceiver components are integrated on a single die, on-chip resources can be used to perform modulation, up-/down-conversion, and some digital signal processing. For specified test conditions, all blocks in the signal path must work properly to guarantee passing BER/EVM results. Since modulated signals are processed in the RF front-end, these tests also allow to detect amplitude, phase, and thermal noise problems as well as synchronization and frequency deviations of on-chip frequency synthesizers [5]. It is common practice to perform BER-based tests separately for the transmitter and receiver [5], which means that high-frequency signals still have to be generated, captured, and analyzed in the discrete time domain with large data sets due to the short sampling time requirement for high-frequency signals. With on-chip loopback, the transmitter and receiver tests could be conducted concurrently without the need for external highfrequency signals. When the modulator and demodulator are implemented on the transceiver SOC, on-chip loopback offers the opportunity for more widespread use of EVM-based test approaches because the ATE does not require digital modulation or RF resources. EVM-based testing is not heavily used yet in the production phase [5] and the main factors that currently drive up the cost are the RF/modulation ATE requirements and prolonged test time unless alternative algorithms are used as proposed in [19].

#### II.1.2. On-chip calibration

If the on-chip loopback scheme is achieved without any external RF signal generation or capture, then a periodic transceiver self-check could be performed during in-field operation. With on-chip generation of the RF test signal, such a self-check creates the opportunity to utilize self-calibration schemes ([20], [21]) for compensation of manufacturing process variations, different thermal conditions, and optimization of impedance matching to external components [18]. A realization of such a true BIST (based on the definition in section I.2) would require that the digital signal processing tasks in the last column of Table II have to be executed on-chip. If the SOC does not already include sufficient resources that can be used for these tasks, then the cost of adding digital circuitry and an analog-to-digital converter to measure the DC output voltages of the power detectors must be weighted against the need for the autonomous self-check. In this thesis, the primary goal is the utilization of the loopback to reduce the technical requirements and cost associated with the ATE resources by limiting the external processing to low-frequency digital signal generation and measurements as elaborated in the following section. This approach still leaves room for one-time calibration during production testing.

Table II. Conventional transceiver tests vs. coverage with BIT  $(\mathbf{R}\mathbf{x} = \text{receiver}, \mathbf{T}\mathbf{x} = \text{transmitter}, \mathbf{LO} = \text{local oscillator}, \mathbf{LB} = \text{loopback block in sect. III},$

**CI** = current injection method in sect. IV, **PD** = on-chip power detector)

| CI – current m                                                | jection method in sect. IV, I                                                                                                                                                                                                                                                                  |                                                      | p po wer detector)                                                                                                                                                                            |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Typical Test                                                  | Typical ATE Resource<br>Requirements                                                                                                                                                                                                                                                           | Coverage with BIT Circuitry                          | ATE Resource<br>Requirements with BIT                                                                                                                                                         |

| Rx BER                                                        | - RF source to generate modulated test signal - digital output capture & comparison with stored reference                                                                                                                                                                                      | Yes<br>(LB)                                          | <ul> <li>digital signal generation<br/>(&lt;200MHz)</li> <li>digital output capture &amp;<br/>comparison with stored<br/>reference</li> </ul>                                                 |

| Tx/Rx EVM                                                     | <ul> <li>vector signal analyzer (phase &amp; symbol info) or digitizers for I/Q paths (then Fast Fourier transform)</li> <li>ATE host computer for intensive EVM calculations</li> <li>Rx: RF source to generate the modulated test signal</li> <li>Tx: RF capture and demodulation</li> </ul> | Yes<br>(LB)                                          | <ul> <li>vector signal analyzer<br/>(baseband frequency)</li> <li>ATE host computer for<br/>intensive EVM<br/>calculations</li> </ul>                                                         |

| Tx output power                                               | - RF capture, spectrum<br>analysis with Fast Fourier<br>transform (or spectrum<br>analyzer)                                                                                                                                                                                                    | in-band<br>power: Yes<br>(LB, PD)<br>spectrum:<br>No | - DC voltage measurement                                                                                                                                                                      |

| Rx VSWR,<br>Rx/Tx return loss (RL),<br>Rx insertion loss (IL) | - RF network analyzer                                                                                                                                                                                                                                                                          | Yes,<br>indirect<br>verification<br>(CI)             | - DC voltage measurement<br>- arithmetic with complex<br>numbers to calculate $S_{21}$<br>(section IV.2.1), which<br>depends on $S_{11}$ (VSWR,<br>RL, IL $\rightarrow$ calc. from $S_{11}$ ) |

| Rx/Tx gain                                                    | <ul> <li>Separate tests for Rx &amp; Tx</li> <li>Rx: RF source, digital baseband capture</li> <li>Tx: digital baseband input signal generation, RF output capture</li> </ul>                                                                                                                   | Yes<br>(LB, PD)                                      | <ul> <li>digital baseband signal<br/>generation</li> <li>DC voltage measurement</li> <li>Simultaneous Tx &amp; Rx<br/>verification</li> </ul>                                                 |

| Rx noise figure (NF)                                          | - direct method at room<br>temp.: digital output<br>capture; NF calc. from<br>measured gain, bandwidth<br>- or Y-factor method:<br>requires a noise source and<br>tests at two temperatures                                                                                                    | Yes<br>(LB, PD)                                      | - direct method at room<br>temp.: digital output<br>capture; NF calc. from<br>measured gain, bandwidth<br>- or indirectly: high NF<br>degrades BER result                                     |

Table II. continued

| Typical Test                                    | Typical ATE Resource Requirements                                                                                                                                           | Coverage with BIT Circuitry                  | ATE Resource<br>Requirements with BIT                                                                                                                                                                               |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rx dynamic range                                | - same as for BER (using min./max. power settings)                                                                                                                          | Yes<br>(LB, PD)                              | - same as for BER (using min./max. power settings)                                                                                                                                                                  |

| Rx/Tx 1-dB<br>compression points                | - same as for BER (several power settings)                                                                                                                                  | Yes<br>(LB, PD)                              | - same as for BER (several power settings)                                                                                                                                                                          |

| Rx/Tx third-order intermodulation product (IP3) | - same as for BER, but with<br>two tone input signal<br>(several power settings)                                                                                            | Yes,<br>indirect<br>verification<br>(LB, PD) | <ul> <li>- same as for BER (several power levels)</li> <li>- IP3 extrapolation from 1-dB comp. point with arithmetic</li> </ul>                                                                                     |

| Rx harmonic distortion                          | - Fast Fourier transform and digital signal processing of digital baseband output                                                                                           | Yes<br>(LB, PD)                              | - Fast Fourier transform and digital signal processing of digital baseband output                                                                                                                                   |

| Rx/Tx bandwidth                                 | - same as for BER (several RF frequency settings)                                                                                                                           | Yes<br>(LB, PD)                              | - same as for BER (several on-chip LO frequency settings)                                                                                                                                                           |

| Rx RF-LO rejection                              | <ul> <li>- same as for Tx output<br/>power spectrum</li> <li>- calculation of RF-LO<br/>rejection from spectral<br/>components</li> </ul>                                   | No,<br>but LO<br>leakage<br>degrades<br>BER  | - indirect verification: same as for BER                                                                                                                                                                            |

| Tx adjacent channel power ratio (ACPR)          | - same as Tx output power                                                                                                                                                   | No                                           |                                                                                                                                                                                                                     |

| Rx I/Q offset,<br>amplitude/phase match         | - same as Rx harmonic distortion (if processing is performed on outputs of the analog-to-digital converters in the I/Q paths) - or: fault detection via BER/EVM degradation | Yes,<br>indirect<br>verification<br>(LB, PD) | <ul> <li>same as for BER</li> <li>(I/Q offset &amp; mismatches degrade BER)</li> <li>or: directly if I/Q digital output can be accessed prior to demodulation (same resources as Rx harmonic distortion)</li> </ul> |

| Tx/Rx phase noise<br>& carrier suppression      | - same as Tx/Rx EVM - separate for Tx and Rx                                                                                                                                | Yes,<br>indirectly<br>(LB, PD)               | <ul> <li>same as for Rx I/Q amplitude/phase match</li> <li>only for Tx/Rx loopback combination</li> <li>I/Q baseband output of Rx must be processed by ATE</li> </ul>                                               |

## II.2. The loopback testing method and related works

The system-level concept of loopback self-testing of transceivers has been introduced in the mid-nineties [22], [23]. It involves generation of the test signal in the digital baseband processor, analog-to-digital conversion, and up-conversion to the RF frequency in the transmitter section. The output of the transmitter is then routed back to the input of the receiver where it is amplified, down-converted to the baseband frequency, converted back to the digital domain, and analyzed for functionality verification of the complete transceiver. In this decade, algorithms have been demonstrated with system-level validations to improve test coverage and fault identification based on BER results [24] and spectral analysis of the receiver output [25]. With behavioral models and novel algorithms, recent works have also addressed test time reduction by using optimized bitstreams for the loopback test [26], statistical sampling circuits along the RF path [27], and demonstration of a feasible method for wafer-level production testing [28].

The aforementioned works were conducted with behavioral simulations, implementation of the transceiver system with discrete components, or off-chip realization of the loopback using on-board or ATE resources. An on-chip loopback would entail further benefits of avoiding any off-chip high-frequency interfaces and allowing post-production transceiver self-checks without measurement equipment. Moving towards this goal, on-chip block-level characterization of critical loopback components (switches, attenuator) was performed in [29].

## II.2.1. Test coverage and accuracy limitations

The selection of tests that are conducted during production testing of a transceiver depend on the communication standard in use, pre-production characterization results, fabrication yield, and customer requirements among other manufacturer-specific factors. Table II provides an overview of the test coverage with the proposed BIT techniques in comparison to the common system-level RF SOC tests given in [5]. ATE resource requirements are also listed for each test, and in contrast, the BITs would allow almost identical coverage without necessitating RF equipment and off-chip high-frequency impedance matching. The exceptions are the local oscillator-RF (LO-RF) rejection and transmitter adjacent channel power ratio (ACPR), which may or may not be required in the high-volume manufacturing phase, depending on the manufacturer's test plan and initial product characterization results.

Table II lists the common tests at the final (in-package) test stage assuming proper impedance terminations. In general, cost-saving initiatives with BIT do not necessarily imply the complete replacement of testers with RF resources by low-cost digital testers during final test. At the present time, the accuracy of on-chip measurement circuits is too low to rely on them exclusively. Instead, the reduced tester resource requirements offer improved opportunities to conduct the tests in batch-mode at the wafer test stage to prevent the cost of further processing and lengthier device handling time at final test. In the high-volume production phase, test data correlations between the on-wafer and final test could then be used to screen out faulty devices early or to cautiously reduce the coverage at final test for test time reduction. The inherently lower accuracy of the BIT

can be taken into account by widening the guardbands of the pass/fail limits according to statistical correlations of the BIT data with the conventional measurement results. Such an action does not necessarily imply lower yield, especially when the measurement error with the BIT is small (e.g. 5%). The fraction of devices whose test results fall within the guardbands of the specification limits could be re-tested with conventional off-chip equipment at final test. Only a small percentage of parts should be within a guardband of 5% or less around the pass/fail limits because the measurement data typically has a Gaussian distribution and the pass/fail limits are often three standard deviations or more away from the mean. Thus, the majority of the devices could receive a pass/fail classification based on the BIT, which still reduces the overall utilization of the more expensive ATE and avoids longer device handling times at final test.

## II.3. System-level overview to investigate on-chip loopback

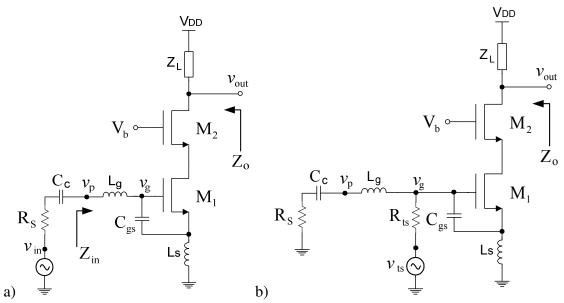

Further evidence for the feasibility of the loopback technique can be obtained by designing the test system displayed in Fig. 3, which contains the front-end blocks of the generalized transceiver from Fig. 2. While the focus in this thesis is on the development of a loopback block, the verification was conducted together with front-end circuits designed by colleagues for a realistic proof-of-concept that takes practical concerns such as impedance-matching, parasitic loading by the test circuitry, and layout issues into account. The system was designed to target the general requirements of transceiver standards that make use of frequency bands in the 1.9GHz to 2.4GHz range.

Fig. 3. Transceiver front-end test system with on-chip loopback

As shown in Fig. 3, a variable attenuator and an offset mixer are required for closing the signal path between the transmitter and receiver subsystems to simultaneously test all blocks of the transceiver at the customary power levels and

different transmit/receive frequencies mandated by standards. Strategic placement of root-mean-square (RMS) power detectors along the high frequency signal path improves the test coverage and identification of fault locations by permitting to measure output power levels, gains, and 1-dB compression points of the RF blocks [13]. In the future, an extension of the RMS detector utilization may include the self-correction of blocks with soft faults by adjusting DC bias conditions based on the measured power levels. From a system-level perspective, the gains in the RF transmitter and receiver chains are important performance indicators with respect to the achievable signal-to-noise ratio. The 1-dB compression point measurements give insights into the linearity of the analog blocks, which directly relates to the integrity of the signal and the associated bit error rate after the demodulation process.

## II.4. Generalized block-level requirements for the front-end test system

As a proof-of-concept, the RF front-end circuits in Fig. 3 were realized with typical topologies and parameters for transceivers operating around 2GHz (Table III).

Table III. Proof-of-concept RF front-end parameters

| Parameter       | Value  |

|-----------------|--------|

| Tx frequency    | 2GHz   |

| PA output power | 0dBm   |

| Rx frequency    | 2.1GHz |

| LNA gain        | 21dB   |

| Mixer gain      | 6.9dB  |

In addition to operating under the boundary conditions in Table III, the loopback block should be able to cover 40-200MHz frequency offset between transmitter (Tx) and receiver (Rx) as well as to operate up to 2.4GHz for compatibility with modern standards in this range. Table IV lists the general requirements for the proposed on-chip loopback testing approach. Besides meeting the targets in the tables, it is essential that the BIT circuits do not significantly affect the performance of the front-end blocks during normal operation. Also, the goal in this loopback implementation is to enable gain and 1-dB compression point characterization of the front-end blocks with RMS detectors, which is done at relatively high power levels. On-chip attenuators similar to those in [29] or [31] could be inserted after the loopback block to achieve lower power levels at the LNA input in case more attenuation is desired to perform BER testing closer to the sensitivity level of the receiver.

Table IV. High-level loopback block specification targets

| Parameter                              | Value                             |

|----------------------------------------|-----------------------------------|

| Input impedance                        | 50Ω (matched to PA)               |

| Tx/Rx offset frequency range           | 40-200MHz                         |

| Attenuation range (continuous)         | 10-25dB                           |

| Operating frequency                    | < 2.4GHz                          |

| Tx/Rx isolation (loopback deactivated) | > 80dB                            |

| Output noise                           | communication standard-dependent* |

<sup>\*</sup> Integrated noise specification over the channel bandwidth must be met at the LNA input. The W-CDMA standard is used as reference in this thesis to assess noise performance because of its stringent noise requirement due to the wideband nature, which mandates a SNR of -7.3dB over the 3.84MHz channel BW [30].

## II.5. Implementation overview of the loopback block

An on-chip loopback circuit without frequency shifting between transmitter and receiver has been reported in [29]. It consists of RF switches and a fixed passive attenuator. The switches were optimized for compactness and insertion loss with slightly reduced isolation compared to traditional RF switches. The  $\pi$ -type attenuator in [29] has high linearity because it consists of polysilicon resistors; but multiple attenuators would have to be connected in cascade or in parallel with additional switches to implement discrete attenuation settings. Adding frequency translation and continuously variable attenuation capabilities in the loopback block would accommodate to the requirements of more communication standards as well as gain and 1-dB compression testing with power detectors. As an alternative, the loopback block shown in Fig. 4 is proposed in this work to meet the requirements outlined in the previous subsection. It consists of switches with high isolation to activate the loopback in test mode and to disconnect it during normal operation. The input of the loopback is impedance-matched to the PA output and the output stage designed to drive the low-impedance node at the LNA input gate. A fixed attenuator at the loopback input reduces the power level of the test signal to ensure linear operation in the offset mixer stage. Finally, the programmable attenuation is achieved in the mixer using continuously variable loads.

Fig. 4. Block-level loopback representation

#### II.5.1. Switches

Low insertion loss is a key requirement when the switches are closed. The onresistance of the switch should be small enough to avoid degradation of the matching

between the PA and the attenuator. Additionally, the switch at the PA output must have

sufficient linearity to be placed at that node, which has relatively large voltage swings

due to the high power level of the signal. In the off-state, high isolation is desired to

avoid power leakage from the transmitter to the receiver during normal operation.

#### II.5.2. Attenuation

The characterization of the transceiver front-end circuitry will have to be performed at a power level well below the 1-dB compression points of all blocks for uncompressed gain measurements as well as at higher levels to determine the 1-dB compression points from the RMS detector outputs. Assuming 0dBm as output power level for the PA in an integrated transceiver to drive the off-chip load, which could be another high-power PA on a separate chip, the attenuation requirement of 10-25dB was selected to guarantee the necessary range at the LNA input for the gain and 1-dB compression point tests. Most

transceivers have multiple gain settings in various transmitter/receiver stages, which would add more flexibility and extend the attenuation range beyond the minimum requirement.

#### *II.5.3. Frequency translation*

Depending on the communication standard, the loopback block might have to provide 40-200MHz frequency shifting between the transmitter and receiver sections, which requires an offset mixer. In a production test environment, the offset signal for the mixer can be supplied by the ATE or an on-chip local oscillator (if available). Due to the relatively low frequency of the offset signal, it can be supplied to the offset mixer in the form of a digital square wave, which is easy to generate and also allows to relax the design requirements when a switching mixer is used (section III.2).

#### II.5.4. Design challenges

Several design challenges and constraints are associated with the loopback target specifications outlined in section II.4:

## **Linearity**

Due to the high power levels of the PA output and the goal to test around the 1-dB compression point of the LNA, the 1-dB compression points of the circuits within the loopback block must be high enough to accommodate the test conditions. This linearity must be achieved with a low supply voltage (1.2V with 0.13µm technology). In general, BIT circuitry must be realized with minimum area overhead to be cost efficient and with minimum complexity to reduce the probability of false fails due to fabrication defects in

the BIT circuits themselves. For this reason, linearization schemes are undesirable, especially those that require additional input pins for bias circuitry or tuning. Thus, meeting the linearity requirement becomes an intricate circuit design task under the constraints.

## Input impedance matching

Effective test of the on-chip power/pre-power amplifier requires that the loopback input impedance is matched to the PA output, which is  $50\Omega$  in the following design example. Resonant networks with inductors cannot be used for that purpose because they would make the loopback block too area expensive. Consequently, resistive impedance matching is a better solution because of its simplicity; but it has the trade-off of higher noise.

## <u>Transmitter-receiver isolation and loading effects</u>

High isolation of the transmitter and receiver section is critical during normal operation to avoid SNR degradation on the receiver side due to signal leakage from the transmitter. It must also be assured that the parasitic capacitances of the switches at the loopback terminals are small enough to avoid significant influence on the equivalent impedances at these nodes at the operating frequency. Therefore, it is beneficial to add multiple switches in the signal path as well as to ground critical nodes within the loopback during normal operation in order to disconnect it with high isolation. A problem associated with the switches is that they introduce losses, which are unwanted when minimum attenuation is needed to perform block-level 1-dB compression tests. Losses due to switches are especially high when they are designed with smaller

dimensions to limit the parasitic capacitances at the loopback terminals, since smaller transistor sizes (W/L ratios) also increase the on-resistances of the switches.

## Design reconfigurability

Due to the multitude of communication standards in the 1.9-2.4GHz range, an ideal loopback topology should be compatible with a large number of them and also cover a high offset frequency range. Variable attenuation should be implemented without feedback loops that are often used for dB-linear attenuators to maintain matched terminal impedances as discussed in section III. In addition, the loopback output signal should be available for single-ended or differential processing in the receiver front-end.

## Noise

Another concern is adherence to the noise specifications. Being a wideband standard with a stringent noise requirement, W-CDMA will be brought into the picture as a reference to check that the noise integrated over the bandwidth is generally acceptable. At the downlink receiver, W-CDMA requires a signal-to-noise (SNR) ratio of -7.3dB over the 3.84MHz channel bandwidth [30]. Under the assumption of an approximately flat noise level over the bandwidth, the spot noise at the operating frequency will be used to estimate this integrated SNR according to:

$$SNR_{\text{integrated (dB)}} \approx SNR_{\text{spot(dB)}} - 10\log(BW_{\text{channel}})$$

(1)

At the W-CDMA sensitivity specification of -106.7 dBm/3.84 MHz, the allowable integrated noise power is -99.4 dBm/3.84 MHz, which translates to an allowable spot noise of  $1.2 nV/\sqrt{Hz}$  at the receiver frequency. If, for example, the loopback BIT is conducted with a power level of approximately -30 dBm at the LNA input, the

permissible integrated noise power is -22.7dBm/3.84MHz, which corresponds to  $8.4\mu\text{V}/\sqrt{\text{Hz}}$  allowable spot noise. This demonstrates that the output noise requirement for the loopback block mainly depends on the power level at which the transceiver is tested and the allowable noise specified in the standard.

In this section, the loopback testing method for transceivers was discussed from a system-level perspective to show how the application-specific constraints give rise to the specifications for the loopback block. The proposed implementation was introduced together with a high-level description of the design challenges, which will be revisited in the discussion of the circuit-level performance considerations in next section.

#### III. ATTENUATOR AND OFFSET MIXER FOR TRANSCEIVER BIT

### III.1. RF attenuator design

#### III.1.1. Background

Fig. 5 displays generalizations of typical RF attenuator realizations. Attenuation is achieved by selecting the proper impedances  $(Z_x)$ , which also have to meet input/output matching requirements. Both, active and passive devices can be utilized as impedances, but active elements are usually preferred in applications that require continuous variation of the attenuation or multiple attenuation steps with minimal die area. Resistors are normally used if the application demands high linearity, low power consumption, or precise attenuation ratios. The T-attenuator in Fig. 5b is a good choice to match the input and output terminals to high source and load impedances, which is not the case in the loopback application. Matching to low terminal impedances is simplified with the bridge-T attenuator (Fig. 5c), but high attenuation ratios are impractical because Z<sub>1</sub> and Z<sub>3</sub> are the low-impedance elements used for the matching, creating a low-impedance connection between the input and output ports. The  $\pi$ -type attenuator in Fig. 5a was selected as basis for the loopback block because it is suitable for low-impedance matching with sufficient attenuation range. Furthermore, high-frequency performance of the  $\pi$ -attenuator is excellent since short RC time constants are formed with the parasitic capacitances due to the low-impedance nodes.

Fig. 5. RF attenuator topologies: (a)  $\pi$ -type (b) T-type (c) bridge-T-type

Table V. Comparison of RF attenuators

| Ref. | Type                                    | Techn.           | Freq.         | Atten.         | NF*   | 1-dB<br>Comp. Pt. | Area                               | Power |

|------|-----------------------------------------|------------------|---------------|----------------|-------|-------------------|------------------------------------|-------|

| [31] | MOS:<br>dB-linear                       | 0.13μm<br>CMOS   | DC<br>-10GHz  | 0.8dB<br>-35dB | 1dB   | 5dBm              | 0.29mm <sup>2</sup>                | 1.8mW |

| [32] | MOS:<br>dB-linear                       | 0.8μm<br>CMOS    | DC<br>-900MHz | 3.3dB<br>-28dB | 1dB   | 5dBm              | 1.57mm <sup>2</sup>                | 12mW  |

| [33] | MOS:<br>dB-linear                       | 0.35μm<br>CMOS   | DC-1GHz       | 3.4dB<br>-23dB | 0.1dB | n/a               | 0.21mm <sup>2</sup>                | 15mW  |

| [29] | poly<br>resistors:<br>discrete<br>steps | 0.25μm<br>BiCMOS | <5GHz         | <40dB          | n/a   | n/a<br>(>>0dBm)   | 9×10 <sup>-4</sup> mm <sup>2</sup> | 0     |

| [34] | poly resistors: 5dB steps               | 0.18μm<br>CMOS   | 2.45GHz       | 0dB<br>-30dB   | n/a   | n/a<br>(>>0dBm)   | n/a                                | 0     |

<sup>\*</sup> Incremental noise figure = NF - attenuation.

An overview of integrated RF attenuator performance results relevant to the loopback application is presented in Table V. Several attenuators have been reported that utilize MOS transistors to obtain linearly variable attenuation at RF frequencies [31]-[33]. These circuits allow up to 35dB attenuation range that can be adjusted linearly-indB. But, one issue associated with that approach is that MOS transistors in triode region are employed to vary the impedances in the attenuators (typically  $\pi$ -type), which results

in changes of the terminal impedances that degrade the  $50\Omega$  matching dynamically. For this reason, control circuitry was added in [31]-[33] to preserve impedance matching as the attenuation is varied. In [31], for example, the control scheme for impedance matching and control voltage linearization requires a replica attenuator and an operational amplifier in a feedback loop. Similarly, two attenuators and a reliable  $50\Omega$  reference resistor are needed in [32] and [33]. With such a high complexity and associated risk increase for failure in the test circuitry as well as large area overhead (>0.2mm<sup>2</sup>), these attenuators are not good candidates for the loopback BIT application.

# III.1.2. Input switch/attenuator: proposed implementation

The proposed loopback input stage (Fig. 6) comprises the switch/fixed attenuator and has two purposes: to terminate the PA output with  $50\Omega$  as during normal operation and to reduce the signal power at the input of the offset mixer, which relaxes the linearity requirement for the mixer. Impedance matching and attenuation is carried out in broadband fashion based on the resistive divider formed by  $R_{att1}$  /  $R_{att2}$  and the switch transistor's on-resistance [ $R_{ON(M1)}$ ] in triode region. Based on the voltage division principle and the assumption that the impedance contribution of  $C_c$  is negligible, the resulting attenuation is:

$$Atten_{fixed(dB)} = -10\log(\frac{R_{att2}}{R_{att1} + R_{att2} + R_{ON(M1)}}) = -10\log(\frac{R_{att1}}{R_{att1} + R_{att2} + [\mu_n C_{ox}(W/L)_{M1} \times (V_{sw} - V_{TH} - V_{ds(M1)})]^{-1}})$$

(2)

where  $\mu_n$  is the electron mobility,  $C_{ox}$  is the gate oxide capacitance per unit area, W is the gate width,  $V_{TH}$  is the threshold voltage, and L is the effective channel length of the device.

Fig. 6. Loopback input stage: RF switch and fixed input attenuator

Transistors  $M_1$  and  $M_2$  of the input stage compose a standard RF switch, in which  $M_2$  increases the isolation in off-state, and the gate bootstrap resistors ( $R_G$ ) enhance the linearity by lowering the variation of the channel resistance in response to the large voltage swing at the attenuator input [35]. These merits were assessed with an analysis based on preliminary simulations of the switches in Fig. 7 and the equivalent model for a single switch transistor with gate resistor  $R_G$  shown in Fig. 8. First, the parasitic

capacitances and their equivalent impedances at 2GHz were obtained with a simulation in Cadence using UMC 0.13µm technology with a 1.2V supply voltage:

$$\begin{split} &C_{gd}\approx C_{gs}\approx 40 fF \ \rightarrow \ |Z_{eq}\{C_{gd}\}| \ \approx 2 k\Omega \text{ at } 2GHz \\ \\ &C_{db}\approx C_{sb}\approx \ 2 fF \ \rightarrow \ |Z_{eq}\{C_{gd}\}| \ \approx 40 k\Omega \text{ at } 2GHz \end{split}$$

The simulated on-resistance of the switch in triode region ( $R_{ds}$ ) was approximately  $5\Omega$ , and the time-dependency of the channel resistance is clear from the simplified MOS model equation for the transistor operating in triode region:

$$r_{ds(t)} = \frac{1}{(W/L) \times \mu_n C_{ox} \times (V_{G(t)} - V_{S(t)} - V_{TH} - [V_{D(t)} - V_{S(t)}])} = \frac{1}{(W/L) \times \mu_n C_{ox} \times (V_{G(t)} - V_{D(t)} - V_{TH})}$$

(3)

Based on the impedances of the elements in Fig. 8 and the resulting voltage divisions, it can be observed that the following conditions are desired to reduce variations of  $V_{gs(t)} = V_{G(t)} - V_{S(t)}$  and  $V_{ds(t)} = V_{D(t)} - V_{S(t)}$ , which improves linearity: