### COMMUNICATION SYNTHESIS OF NETWORKS-ON-CHIP (NoC)

A Dissertation

by

#### PRAVEEN SUNDER BHOJWANI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

December 2007

Major Subject: Computer Engineering

### COMMUNICATION SYNTHESIS OF NETWORKS-ON-CHIP (NoC)

A Dissertation

by

PRAVEEN SUNDER BHOJWANI

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Rabi N. Mahapatra |  |

|---------------------|-------------------|--|

| Committee Members,  | Duncan M. Walker  |  |

|                     | Eun J. Kim        |  |

|                     | Gwan Choi         |  |

| Head of Department, | Valerie E. Taylor |  |

December 2007

Major Subject: Computer Engineering

#### ABSTRACT

Communication Synthesis of Networks-on-Chip (NoC). (December 2007)

Praveen Sunder Bhojwani, B.Tech.(H), Indian Institute of Technology (IIT),

Kharagpur;

M.S., Texas A&M University;

Chair of Advisory Committee: Rabi N. Mahapatra

The emergence of networks-on-chip (NoC) as the communication infrastructure solution for complex multi-core SoCs presents communication synthesis challenges. This dissertation addresses the design and run-time management aspects of communication synthesis. Design reuse and the infeasibility of Intellectual Property (IP) core interface redesign, requires the development of a Core-Network Interface (CNI) which allows them to communicate over the on-chip network. The absence of intelligence amongst the NoC components, entails the introduction of a CNI capable of not only providing basic packetization and depacketization, but also other essential services such as reliability, power management, reconfiguration and test support. A generic CNI architecture providing these services for NoCs is proposed and evaluated in this dissertation.

Rising on-chip communication power costs and reliability concerns due to these, motivate the development of a peak power management technique that is both scalable to different NoCs and adaptable to varying traffic configurations. A scalable and adaptable peak power management technique - SAPP - is proposed and demonstrated. Latency and throughput improvements observed with SAPP demonstrate its superiority over existing techniques.

Increasing design complexity make prediction of design lifetimes difficult. Post

SoC deployment, an on-line health monitoring scheme, is essential to maintain confidence in the correct operation of on-chip cores. The rising design complexity and IP core test costs makes non-concurrent testing of the IP cores infeasible. An on-line scheme capable of managing IP core test in the presence of executing applications is essential. Such a scheme ensures application performance and system power budgets are efficiently managed. This dissertation proposes Concurrent On-Line Test (COLT) for NoC-based systems and demonstrates how a robust implementation of COLT using a Test Infrastructure-IP (TI-IP) can be used to maintain confidence in the correct operation of the SoC. To my family

#### ACKNOWLEDGMENTS

I would like to thank Dr. Mahapatra for his direction and support over the last six years. His faith in my abilities helped mould my transition from a graduate student into a researcher. I would also like to thank Drs. Walker, Kim and Choi for serving on my committee and being excellent teachers.

Over the last six years, a number of colleagues and friends have made my stay in College Station bearable. I would like to thank Sunil, Pramod, Sid, Kiran, Junyi, Anand, Kabi, Purna, Nitesh, Tae Sung, Di, Rupak, Veera, Rohit, Waqar, Prasenjit, Sarabjyot, Anuja, Upali, Jason, Suman, Nikhil, Amar, Nari, Vivek, Pandi, Praveen, Abhijit, Narayanan, Binoy and my wing-mates.

The support of my family over the last six years has been instrumental in the compilation of this dissertation.

## TABLE OF CONTENTS

# CHAPTER

| Ι   | INTRODUCTION                                                       | 1  |

|-----|--------------------------------------------------------------------|----|

| II  | CORE-NETWORK INTERFACE DESIGN                                      | 7  |

|     | A. Related Work                                                    | 8  |

|     | B. Proposed CNI Design                                             | 8  |

|     | 1. CNI Services                                                    | 8  |

|     | a. End-to-end Reliable Communication                               | 9  |

|     | b. Communication Scheduling                                        | 9  |

|     | c. Peak Power Management and Network Recon-                        |    |

|     | figurability                                                       | 10 |

|     | d. IP Core Test Support                                            | 10 |

|     | 2. CNI Architectural Sub-components                                | 11 |

|     | C. Latency Constrained On-chip Communication                       | 15 |

|     | 1. Factors Affecting End-to-end Latency                            | 15 |

|     | 2. Proposed VC Allocation Scheme                                   | 16 |

|     | 3. VCA Architecture                                                | 17 |

|     | 4. NoC Support                                                     | 17 |

|     | 5. Setting the Class_id Field                                      | 18 |

|     | 0                                                                  | 19 |

|     | D. CNI Evaluation                                                  | 20 |

|     | E. Unconsidered Design Issues                                      | 22 |

| III | PEAK POWER AWARE NOCS                                              | 23 |

|     | A. Related Work                                                    | 24 |

|     | 1. Energy/Power Model                                              | 24 |

|     | 2. PowerHerd $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 25 |

|     | 3. Peak Power Control (PC)                                         | 27 |

|     | B. Static Peak Power Aware Design                                  | 27 |

|     | 1. Problem Formulation                                             | 28 |

|     | 2. Definitions and Operations                                      | 30 |

|     | 3. Heuristic                                                       | 31 |

|     | 4. Off-line Peak Power Control                                     | 33 |

|     | 5. Evaluation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 34 |

| C. SAPP: Scalable and Adaptable Peak Power Manage- |            |

|----------------------------------------------------|------------|

| ment in NoCs $\ldots$ 3                            | 87         |

| 1. SAPP                                            | 88         |

| a. Flit Injection Control                          | 88         |

| b. Peak Power Budget Re-allocation                 | <b>3</b> 9 |

| c. Budget Re-allocation Check-pointing 4           | 1          |

| 2. Feature Comparison with Other Schemes           | 2          |

| 3. Experimental Setup and Results                  | 13         |

| a. Test Cases                                      | 13         |

| b. Performance Evaluation                          | 4          |

| IV CONCURRENT ON-LINE TESTING                      | 50         |

| A. Related Work                                    | 51         |

|                                                    | 61         |

| 0                                                  | 52         |

| 0                                                  | 52         |

|                                                    | 53         |

|                                                    | 55         |

| -                                                  | 66         |

|                                                    | 60         |

|                                                    | 52         |

|                                                    | 52         |

| -                                                  | 6          |

|                                                    | 58         |

|                                                    | 70         |

|                                                    | 70         |

|                                                    | 70         |

|                                                    | 71         |

| * *                                                | 71         |

|                                                    | 73         |

| a. SoC Configuration 1                             | 73         |

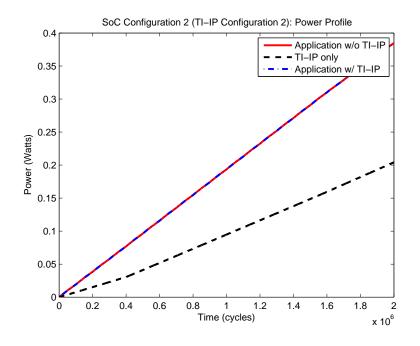

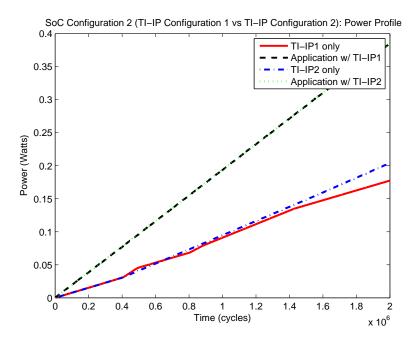

| b. SoC Configuration 2                             | 76         |

|                                                    | 78         |

| 7. Synthesis Results                               | 78         |

| V SUMMARY 8                                        | 31         |

| A. Conclusions                                     | 31         |

|                                                    | 32         |

Page

# Page

| REFERENCES                                     | 84  |

|------------------------------------------------|-----|

| APPENDIX A FORWARD ERROR CORRECTION IN NOCS    | 93  |

| A. Introduction                                | 93  |

| B. Related Work                                | 95  |

| 1. FEC Basics                                  | 95  |

| 2. Energy Model                                | 96  |

| C. Motivation                                  | 97  |

| D. On-chip Communication Reliability           | 100 |

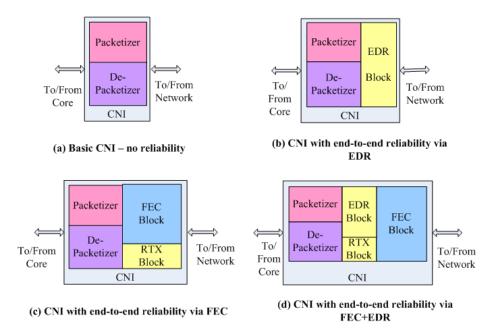

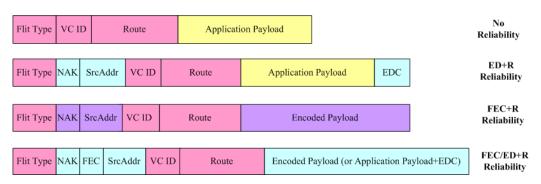

| 1. Error Detection and Retransmission $(ED+R)$ | 100 |

| a. End-to-end Retransmission                   | 101 |

| b. Hop-to-hop Retransmission                   | 102 |

| 2. Forward Error Correction (FEC+R)            | 104 |

| 3. Hybrid Scheme (FEC/ED+R)                    | 105 |

| E. Conclusions                                 | 108 |

| APPENDIX B NOCSIM                              | 109 |

| VITA                                           | 110 |

### LIST OF TABLES

| TABLE |                                                                                                                                                                      | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Ι     | Gate count breakdown for CNI modules                                                                                                                                 | 21   |

| II    | Test case 1 and 2 specification summary                                                                                                                              | 35   |

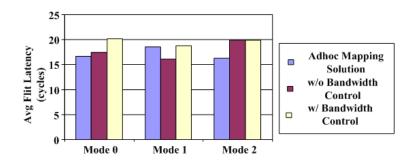

| III   | Latency and throughput improvement of SAPP over PC $\ . \ . \ . \ .$                                                                                                 | 46   |

| IV    | Power budget migration latency when sufficient power budget is<br>unavailable along the path to the destination (for PowerHerd) and<br>at injection point (for SAPP) | 48   |

| V     | System snapshot table fields                                                                                                                                         | 58   |

| VI    | TI-IP configuration table fields                                                                                                                                     | 61   |

| VII   | NoCSim features                                                                                                                                                      | 109  |

### LIST OF FIGURES

| FIGURI | E                                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------------------------|------|

| 1      | NoC architecture                                                                                       | 2    |

| 2      | NoC design process illustrating off-line and on-line steps $\ . \ . \ . \ .$                           | 4    |

| 3      | Core-Network Interface architecture                                                                    | 11   |

| 4      | Application data is sent over the NoC in the form of packets, which are further broken up into flits   | 13   |

| 5      | On-chip router internals                                                                               | 16   |

| 6      | Simplified architecture for class-based VCA                                                            | 18   |

| 7      | Latency vs hop distance for varying classes                                                            | 19   |

| 8      | Effective MIPS for processor for different cache miss rates $\ldots$ .                                 | 20   |

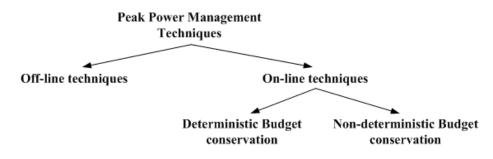

| 9      | Taxonomy of peak power management techniques for NoCs $\ . \ . \ .$ .                                  | 24   |

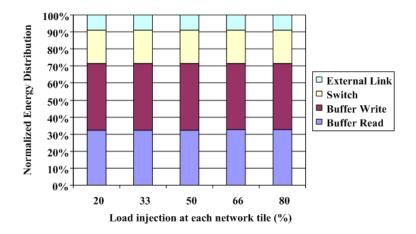

| 10     | Energy distribution profile for different loads                                                        | 26   |

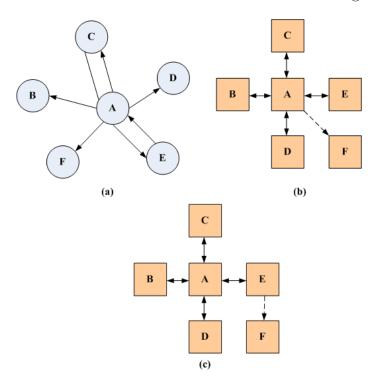

| 11     | (a) MCG, (b) NCG, (c) NCG after merge operation                                                        | 29   |

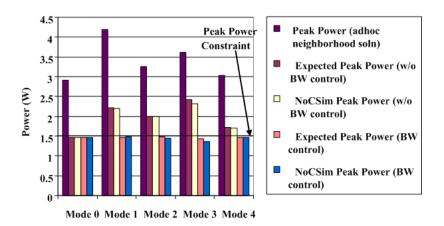

| 12     | Test case 1: Peak power results for different NoC configurations<br>(Peak power constraint = $1.5W$ )  | 35   |

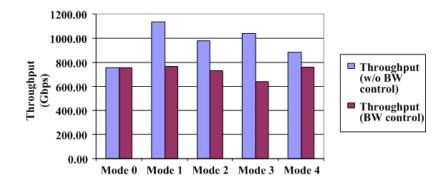

| 13     | Test case 1: Effect of peak power control on NoC throughput $\ . \ . \ .$                              | 36   |

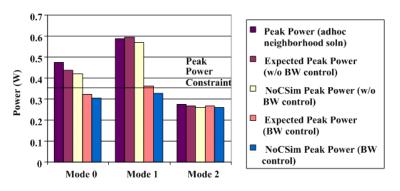

| 14     | Test case 2: Peak power results for different NoC configurations<br>(Peak power constraint = $0.35W$ ) | 36   |

| 15     | Test case 2: Average flit latency                                                                      | 37   |

| 16     | Two snapshots of peak power budget re-allocation in NoC $\ . \ . \ .$ .                                | 40   |

| 17     | Non-uniform test configurations                                                                        | 45   |

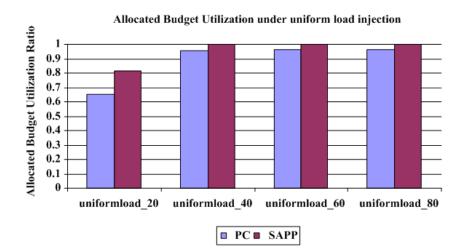

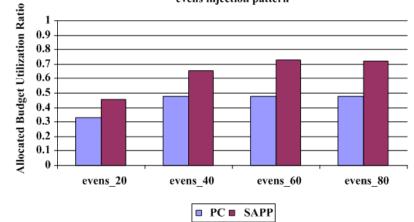

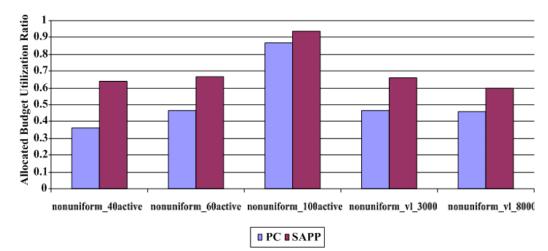

| 18 | Allocated budget utilization comparison between SAPP and PC for different load injection configurations                                                                                                                   | 47 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

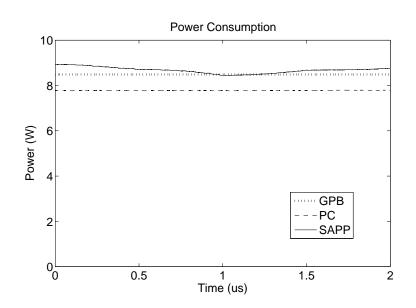

| 19 | Power profile variation demonstrating peak power budget viola-<br>tion due to non-deterministic peak power budget prediction. This<br>violation is bounded to 5% with the current prediction function<br>characterization | 49 |

| 20 | Conceptual NoC-based test infrastructure. TI-IP manages test of<br>on-chip cores                                                                                                                                          | 54 |

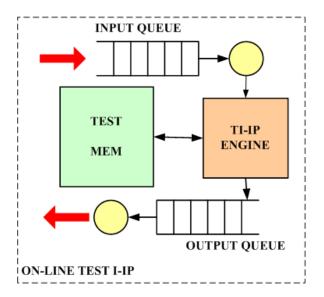

| 21 | On-line test I-IP architecture                                                                                                                                                                                            | 55 |

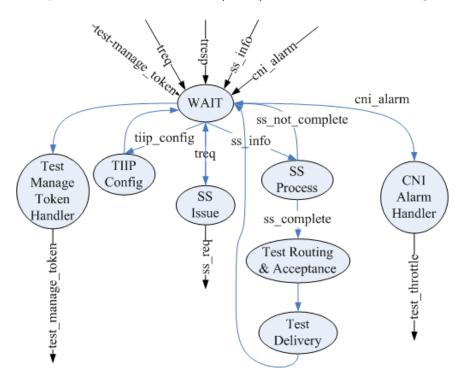

| 22 | TI-IP FSM                                                                                                                                                                                                                 | 57 |

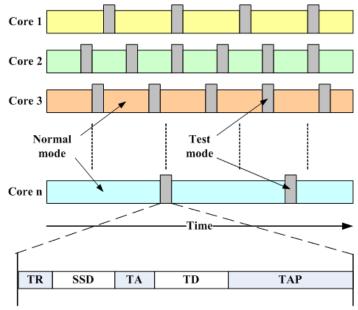

| 23 | SoC operation timeline with integrated COLT                                                                                                                                                                               | 58 |

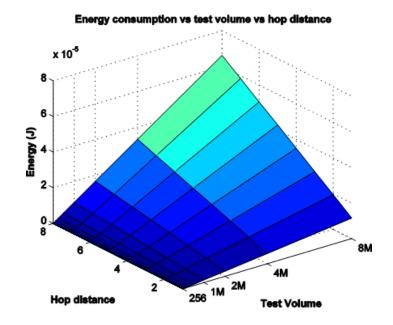

| 24 | Proximity effect on test vector delivery energy consumption                                                                                                                                                               | 62 |

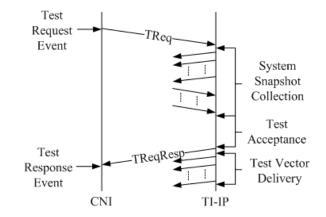

| 25 | Test request protocol step                                                                                                                                                                                                | 63 |

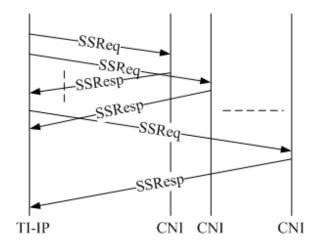

| 26 | System snapshot collection protocol step                                                                                                                                                                                  | 64 |

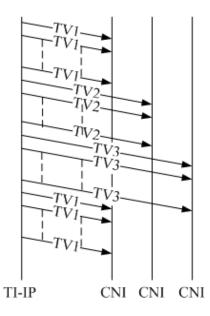

| 27 | Test vector delivery protocol step                                                                                                                                                                                        | 64 |

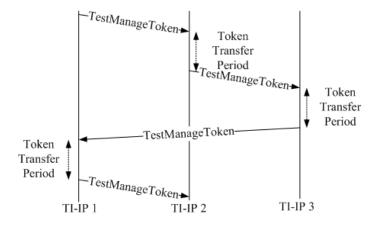

| 28 | Test management token transfer protocol step                                                                                                                                                                              | 65 |

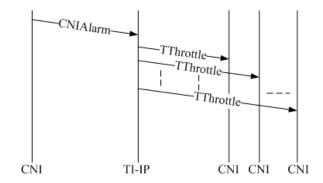

| 29 | Test throttle protocol step                                                                                                                                                                                               | 66 |

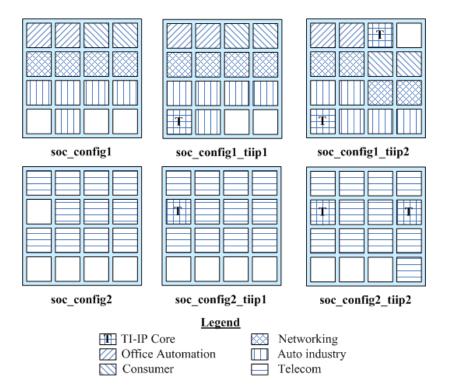

| 30 | Experimental SoC configurations                                                                                                                                                                                           | 72 |

| 31 | ITC'02 SoC test benchmark mapping to experimental configurations                                                                                                                                                          | 73 |

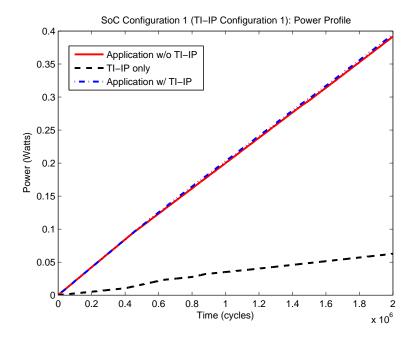

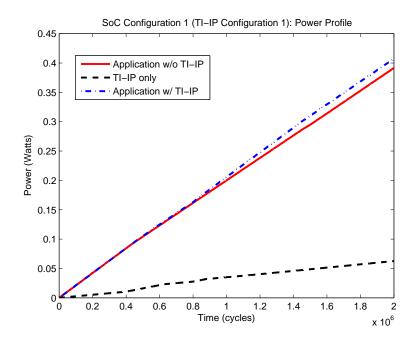

| 32 | SoC configuration 1 power profile, 1 IP core tested                                                                                                                                                                       | 74 |

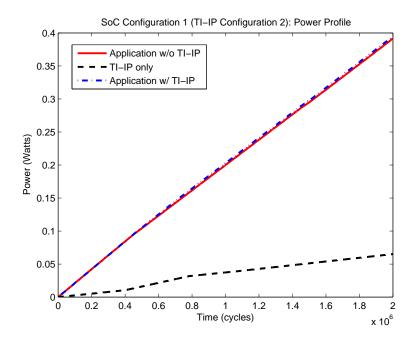

| 33 | SoC configuration 1 power profile, 3 IP cores tested                                                                                                                                                                      | 74 |

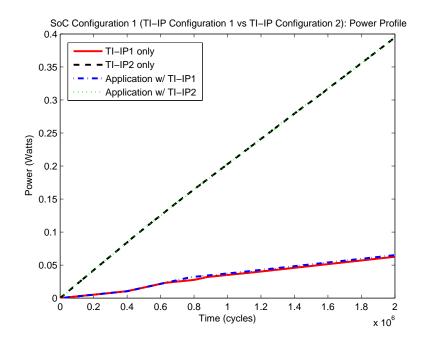

| 34 | SoC configuration 1 power profile, multi TI-IP setup                                                                                                                                                                      | 75 |

| 35 | SoC configuration 1 comparing single TI-IP with multi TI-IP setup power profiles                                                                                                                                          | 76 |

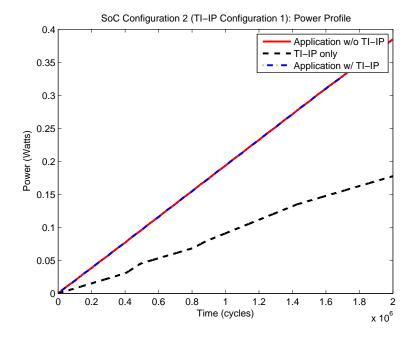

Page

| 36 | SoC configuration 2 power profile, single TI-IP setup                                                             | 77  |

|----|-------------------------------------------------------------------------------------------------------------------|-----|

| 37 | SoC configuration 2 multi TI-IP setup power profile                                                               | 78  |

| 38 | SoC configuration 2 single TI-IP vs multi TI-IP power profile $\ldots$                                            | 78  |

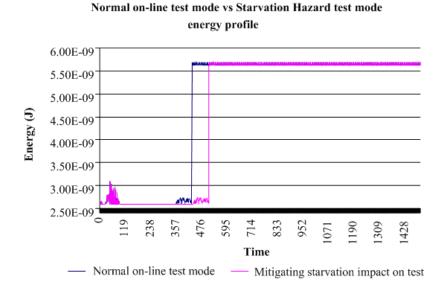

| 39 | Energy profile demonstrating starvation hazard mitigation $\ldots$ .                                              | 79  |

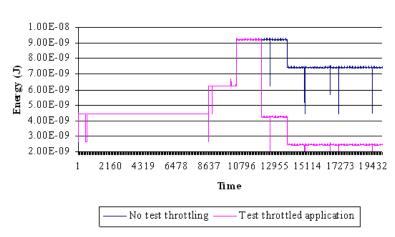

| 40 | Energy profile demonstrating TI-IP test throttling effect on mis-<br>behaving application                         | 79  |

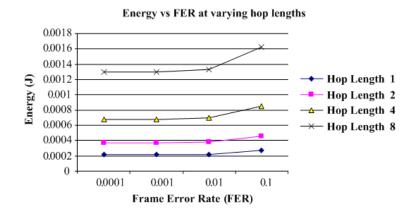

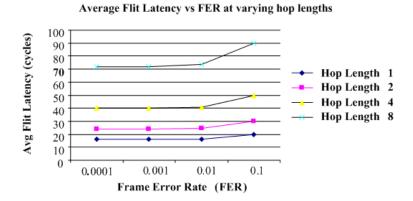

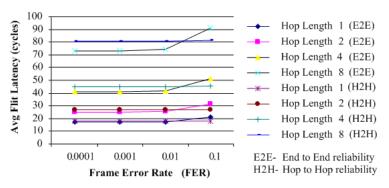

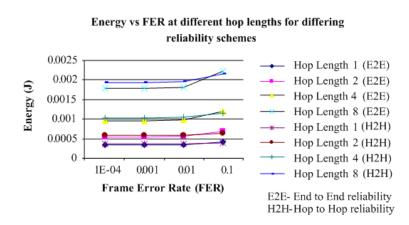

| 41 | Motivation behind selecting target FER for FEC module: Energy<br>vs FER at varying hop lengths                    | 98  |

| 42 | Motivation behind selecting target FER for FEC module: Average<br>Flit latency vs FER at varying hop lengths      | 98  |

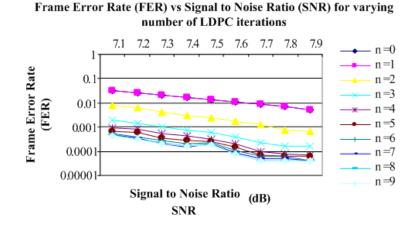

| 43 | Error rate vs signal to noise ratio for varying LDPC iterations                                                   | 99  |

| 44 | CNI structure                                                                                                     | 101 |

| 45 | Average flit latency for end-to-end vs hop-to-hop reliability (CRC) $% \left( \left( {\rm CRC} \right) \right)$ . | 103 |

| 46 | Energy for hop-to-hop vs end-to-end reliability                                                                   | 103 |

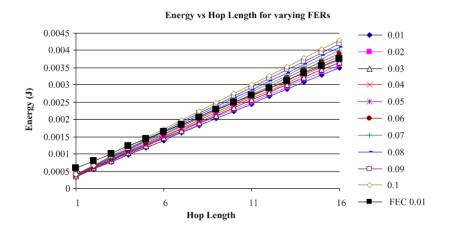

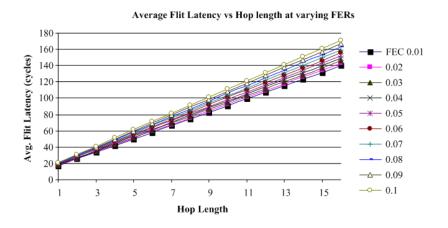

| 47 | Energy of ED+R and FEC+R vs hop length for varying FERs                                                           | 106 |

| 48 | Average flit latency for ED+R and FEC+R vs hop length at vary-<br>ing FERs                                        | 106 |

| 49 | Flit fields/overheads for different schemes                                                                       | 107 |

# Page

#### CHAPTER I

#### INTRODUCTION

In 1965, Gordon E. Moore predicted that the number of transistors on a chip would double every two years [1]. Technology improvements have allowed for this prediction to hold true for over four decades, allowing for density to almost double every 18 months. The International Technology Roadmap for Semiconductors (ITRS) indicates that these trends will continue till atleast the end of the decade, allowing for more than a billion transistors on a chip [2].

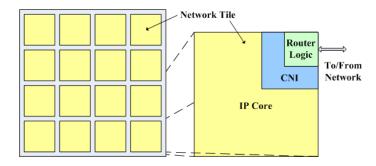

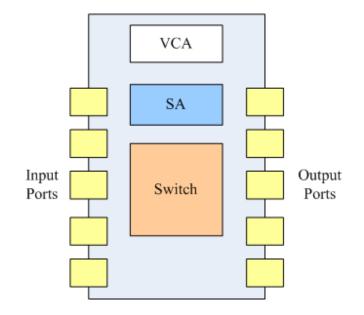

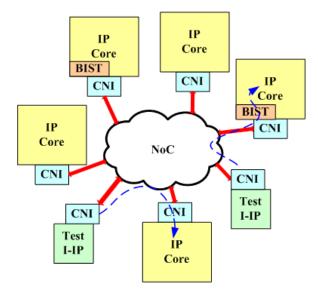

This technology scaling trend allows for the design of complex multi-core systemson-a-chip (SoC). These SoCs will be capable of executing multiple applications providing a wide variety of features. Early SoC designs utilized bus-based communication infrastructures for interactions between the Intellectual Property (IP) cores. In 2000, Guerrier and Greiner identified that as designs got more complex and applications became communication intensive, bus-based infrastructures would no longer be sufficient [3]. They proposed the use of on-chip packet-switched networks to address contention, scalability and availability concerns. This idea was also reiterated by Towles and Dally, in the form of an abstract design of a SoC utilizing a folded 2D torus packet-switched network and a regular IP core layout [4]. In research literature, these on-chip networks are referred to as Networks-on-Chip (NoC). Figure 1 illustrates an architecture considered by most NoC researchers. This architecture consists of a regular layout of *network tiles*. These tiles consist of IP cores interfaced with NoCs via core-network interfaces (CNI). On-chip routers route communication between the source and destination network tiles, over links between them. A pro-

The journal model is IEEE Transactions on Automatic Control.

tocol stack similar to the one used in wide-area networks has also been proposed for the on-chip network environment [5].

Fig. 1. NoC architecture

*Communication synthesis* of NoCs involves the design of components required for on-chip communication and the necessary support for its run-time management. Design aspects for NoCs cover challenges such as application mapping, topology selection and NoC synthesis. Application mapping determines mapping of application task graphs to processing elements in the SoC. This mapping is typically constrained by execution time budgets and deadlines. This idea is pretty similar to the traditional hardware/software partitioning [6], with the exception that communication between the IP cores is no longer trivial. In [7], the authors proposed energy constrained mapping of task graphs to processors, setting communication routes based on bandwidth constraints. An energy aware mapping and routing technique was also proposed in [8]. To improve on algorithm run-time, the research in [9] proposed a heuristic to determine the neighborhood for communicating cores in a regular NoC, while scheduling communication on the network links to ensure performance constraints are met. Topology exploration and selection techniques were proposed in [10, 11, 12]. A number of NoC sythesis techniques using heuristics and optimization algorithms have been proposed in [12, 13, 14, 15], allowing for the design of application specific NoCs.

Run-time management of NoCs considers issues such as peak power control,

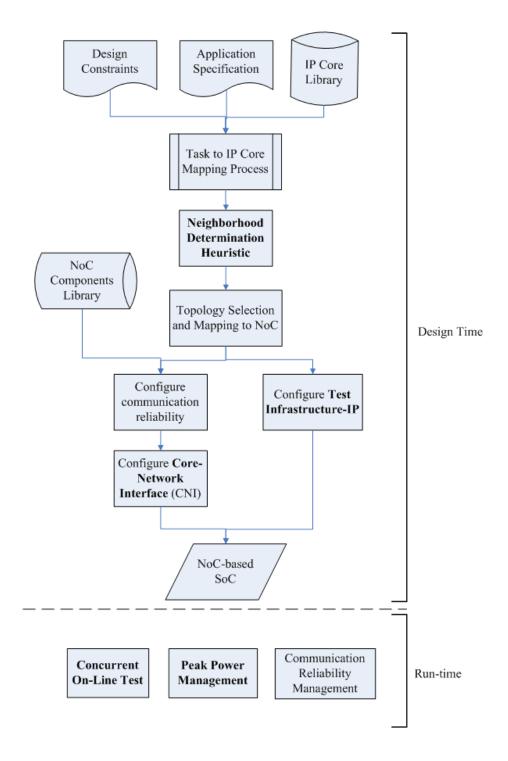

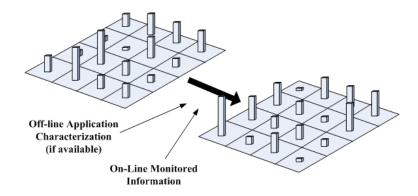

hotspot avoidance, communication reliability and on-chip core health. These present critical challenges to the reliable operation of the SoC. Peak power management has an impact on design reliability and the cooling costs associated with the system. Techniques to address this challenge have been proposed in [16, 17]. By controlling communication flow in the NoC, these techniques manage power consumption. Providing reliability in on-chip networks were explored in [18, 19, 20]. The first efforts at looking into the on-line health management for SoCs have been addressed in this dissertation [21, 22]. Figure 2 illustrates how these design challenges fit into a NoCbased system complete design process, identifying challenges to be addressed design time and run-time. The steps in bold have been researched in this dissertation.

This dissertation makes three novel contributions in both aspects of communication synthesis for NoC-based systems. The primary contribution is in the domain of *Core-Network Interfacing*. In the IP reuse design space, providing for an interface to NoCs is an essential design step. Apart from allowing the IP core to talk the *language* of the network, this dissertation identifies other services that may be provided by the Core-Network Interface (CNI) - reliable communication, peak power management, IP core test support and NoC reconfiguration. A generic architecture that can be customized to varying IP core interfaces and NoC configurations is also proposed. An evaluation of the costs associated with the CNI is reported, demonstrating the feasibility of the proposed design.

*Peak power management* in NoCs is a design concern that can be addressed in different ways. This dissertation examines peak power management at (i) design time (static) and (ii) run-time (dynamic). Design time approaches lead to pesimisstic solutions that impact performance. Dynamic approaches allow for adaptive solutions to address these performance concerns, but are limited by available compute resources to aid in the peak power management for NoCs. A Scalable, Adaptable Peak Power

Fig. 2. NoC design process illustrating off-line and on-line steps

(SAPP) management technique is proposed in this dissertation to address scalability and adaptability limitations of previously proposed techniques.

Lifetime reliability challenges presented by complex multi-core SoCs require the deployment of an on-line health monitoring technique to track the health of the onchip cores. Post SoC deployment, confidence in the health of on-chip cores can be obtained by performing IP core test using existing test support. This would typically be performed non-concurrently, i.e. by turning off executing applications. But with rising design complexity and test costs - test time and test power - non-concurrent testing is not feasible. Concurrent test of IP cores in presence of executing applications in the system is essential. NoC components can facilitate this process, with the help of an infrastructure-IP (I-IP). This dissertation proposes the deployment of a Test (COLT) support for the on-chip components. The challenges to COLT are identified and addressed by the proposed TI-IP design. A robust protocol of operation is also documented along with implementation costs.

This dissertation is organized as follows: Chapter II discusses the Core-Network Interfacing issues and proposes the essential CNI service set and support architecture required for efficient and reliable operation of NoCs. Performance support from on-chip routers in the form of class-based virtual channel allocation is also discussed with results demonstrating their effectiveness. Chapter III proposes a novel peak power management techniques for NoCs, while addressing the scalability and adaptability limitations of prior research attempts. Evaluation highlighting the observed improvements are also reported. Chapter IV motivates the need for a concurrent online health monitoring system for SoCs. Challenges to the proposed technique COLT are documented and solutions are deployed using a a robust TI-IP implementation. Performance on different SoC configuration prepared using academic benchmarks are reported to establish the feasibility of deploying COLT. Finally, the dissertation is summarized in the last chapter, and a few concluding remarks on future work are presented.

**Note:** Since this dissertation does not investigate design exploration strategies for NoC-based system designs, a single baseline NoC configuration is assumed and configured into the evaluation platform *NoCSim*. This platform is configured for a 2D folded torus 4x4 layout of IP cores in an SoC. Source routing is used to route communication between network tiles, while virtual channel based flow control is utilized to avoid communication blocking.

Concepts proposed in this dissertation are implemented into *NoCSim* for functional validation. Appendix B lists the features of this evaluation platform.

#### CHAPTER II

#### CORE-NETWORK INTERFACE DESIGN

In light of rising shorter time-to-market (TTM) pressures and design reuse, interfacing pre-existing IP cores to formulate complex multi-core SoCs presents a critical design challenge. When designing NoC-based systems, modifying core interfaces to communicate over a NoC is not feasible and sometimes impossible. The interface protocols and specifications are extensively pre-verified and validated, and may not have been designed with the intent for deployment in NoCs.

These interfaces can broadly be classified into two categories: (i) standard interfaces and (ii) non-standard (or in-house) interfaces. Standard interfaces like the Open Core Protocol - International Partnership (OCP-IP) [23], VSI Alliance (VSIA) [24] and Advanced Microcontroller Bus Architecture (AMBA) family of interfaces [25] are widely used in present day system designs. Their interface specifications are welldefined and widely available in the public domain or by membership. Non-standard interfaces are usually propietary to a corporation and used to design SoCs with IP cores from a single library or vendor.

To integrate IP cores with this variety of possible interfaces, an adapter is required to translate signals from the IP core domain into signals in the NoC domain and back again. This translation would be provided in the form of a *packetization* and *depacketization* functionality, thus allowing for communication over the NoC. Besides these services, this dissertation proposes a set of essential services to be provided by the CNI to manage the NoC operation. The following sections discuss related research and present the proposed services and a *generic CNI architecture* that can be applied to any IP core interface and NoC configuration, by configuring specific blocks of the design, thus avoiding complete redesign of the CNI.

#### A. Related Work

The first research [9, 26] addressing the interfacing aspects in NoCs, compared costs (area and performance) of providing packetization in software, hardware and with a co-processor attached to a Xtensa core [27]. The software implementation provided an API for the programmer to send data over the IP core interface in a packetized form. The hardware implementation utilized a hardware adapter that packetized interface signals. The co-processor based implementation added a special instruction to the Xtensa processor Instruction Set Architecture (ISA) using the Tensilica Instruction Extension (TIE) language. Other NoC research limit interface service to packetization and de-packetization. This dissertation proposes a generic, enhanced CNI architecture design that provides services required for the reliable and efficient operation of NoCs. Concurrent research efforts documented in [28] identified a similiar service set essential for NoCs.

#### B. Proposed CNI Design

The CNI design is specified in terms of its services and architecture. The following subsections detail the proposed service set and generic CNI architecture.

#### 1. CNI Services

The purpose of the CNI is to provide an interface for the IP cores to the NoC. Apart from packetization and de-packetization functionality, it would also provide: *end-toend reliability, communication scheduling, NoC reconfigurability, power management* and *testing of IP cores.*

#### a. End-to-end Reliable Communication

With reducing noise margins in current and future SoC designs, data communication in on-chip networks are susceptible to errors and schemes to recover from these need to be incorporated into the NoC. In a multi-hop NoC, these schemes can either be used in a hop-to-hop or end-to-end fashion. Deciding between these will depend on the error rates of the design. If reliability concerns warrant the use of end-to-end reliability, these schemes would be implemented within the CNI. Appendix A reports on some of the studies performed in this regard. Error detecting codes such as CRC and hamming have been previously suggested to detect errors and request retransmissions [20, 29]. Forward error correction (FEC) can also be used to reduce the number of retransmissions, especially if the power and latency costs associated with them are unacceptable. Previous research have examined the feasibility of using a scaled down low density parity check coders (LDPC) [30] for use in on-chip networks [19].

#### b. Communication Scheduling

With SoCs being proposed for use in real-time (RT) systems, it places timing constraints on all operational aspects of the system. These not only apply to the computational components of the system, but also the communication infrastructure. Providing latency constraints to on-chip communications will be essential for correct operation of the system. Since the CNIs control the communication entering the NoC, they are in the ideal position to provide for communication scheduling. Schemes previously used in distributed embedded systems may not be feasible for use in cost constrained NoCs where a simple, yet effective scheme is needed. Support for such a scheme would also be needed from the NoC. We utilize the proposed class-based VC allocation scheme which is supported by the router discussed in Section C.

#### c. Peak Power Management and Network Reconfigurability

Network reconfigurability is essential in dynamic systems. With changing communication requirements, certain aspects, such as flit routes and stream bandwidth allocation may need to be modified at runtime. In the NoC configuration considered, we use source routing, which requires a route table to provide the flit with the route to the destination. Routes within a dynamic system may need to be changed to accommodate avoidance of hotspots that may lead to system failure and latency violations. In [31], the authors used a static bandwidth allocation scheme when VC based communication was used. Since the power consumption in the NoC is directly proportional to the bandwidth of the communication on-chip, the bandwidth allocation may need to be scaled to manage power and control propagation latency to the destination. Scaling of bandwidth is implemented in the CNI itself and may be implemented in the routers, but this will lead to buffering issues at the intermediate nodes in the NoC. This dissertation also proposes a dynamic peak power management technique to address any limitations of off-line techniques. Chapter III details the proposed schemes for peak power management in NoCs and compares them to existing techniques.

The CNI can also be reconfigured based on events monitored in the NoC. [32] introduced the monitoring service for NoCs. Events monitored can be provided to the relevant CNIs in the system to allow for reconfiguration.

#### d. IP Core Test Support

Another functionality for the CNI is that of testing of the IP cores attached to it. Prior research [33] has indicated the possibility of reusing the NoC as a Test Access Mechanism (TAM). Since test requests and responses need to be properly interfaced, by providing a test controller, we believe that the testability of the SoC can be managed more effectively. The Concurrent On-Line Test technique proposed in this dissertation (see Chapter IV) utilizes the test controller to interface test with the IP core.

#### 2. CNI Architectural Sub-components

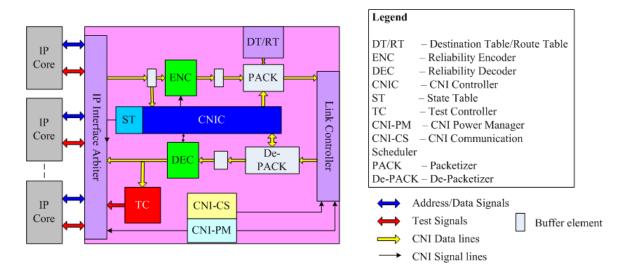

An architectural sketch of the proposed CNI is shown in Figure 3 below. It highlights the major components. To provide the essential CNI services, the following

Fig. 3. Core-Network Interface architecture

sub-components are integrated into the proposed architecture.

**IP Interface Arbiter**: The arbiter behaves as a proxy for communication between the IP cores attached to the NoC. It accepts (delivers) communication requests (responses) to the various IP cores. It replays the communication protocols associated with the core interface standard. A FSM representing the protocol is be used to configure the arbiter. For this research we have considered the OCP-IP 2.0 interface specification and have developed an arbiter capable of interfacing with the basic signal set of the OCP interface. Actual implementations and protocols cannot be specified here due to privacy considerations. The arbiter tracks communication requests from multiple cores attached to it via the state table.

**Encoder/Decoder**: The coders are used to provide for end-to-end reliability. Data to be transmitted is encoded at the sender CNI, transmitted over the NoC to the receiver CNI where it is decoded. The decoder either detects or corrects errors in the transmitted data based on the selected coding scheme. The "strength" of the coding scheme depends on the desired level of reliability and the acceptable cost of implementation in terms of silicon area, power and latency. In the presence of multiple coders in the CNI, varying levels of strengths maybe supported based on the detected error rates in the system. The CNIC would be responsible for the selection amongst multiple schemes based on observed error rates.

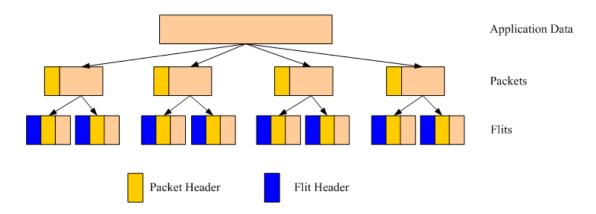

**Packetizer/De-packetizer**: Data to be sent over the NoC is sent in the form of packets. These packets are further broken up into flits (flow digits), which are the smallest atomic data chunks sent over the NoCs. The flits are limited by their size, hence a single packet of data is made up of multiple flits. Each packet larger than a single flit in size, contains a HEAD flit and TAIL flit. Packets larger than two flits in size also have DATA flits, which contain application data. Figure4 illustrates the data fragmentation.

As mentioned in [26], the main functionality of the packetizer is to prepare the flits to be sent out over the NoC. It packetizes the encoded data and sets all the fields of the flit. The de-packetizer accepts flits from the NoC and forwards them to the decoder before delivery to the target IP core. The NoC parameters that affect the packetizer configuration are: topology, routing, flow control policy, VC allocation scheme, etc.

Route Table (RT): The RT provides for address translation between the IP core

Fig. 4. Application data is sent over the NoC in the form of packets, which are further broken up into flits

and the NoC addressing. It maps addresses issued by the IP cores into routes to the intended destinations (i.e. host intelligent routing). When responses are to be returned, the query is made in the form of network addresses. The network address consists of the network tile ID and the IP core ID that will be assigned at design time. When requests are packetized, the **source\_id** field of the flit is set with the network address of the sending CNI.

When router intelligent routing is used in the NoC, the DT/RT will provide the network address of the destination IP core. This address will be looked up in the RT at the intermediate hops in the NoC.

**CNI Controller (CNIC)**: The CNIC manages the operation of the CNI and controls its sub-components. Since the CNI is pipelined (5 stages), CNIC manages control signals for each of the pipelined stages. When reconfigurability is supported by the CNI, the CNIC will be responsible for updating the sub-components like CNI-CS and DT/RT. Connected to the ST, the CNIC assigns and records stream IDs to communications originating from the network tile. When issuing responses, it provides the packetizer with stream ID from the received request flit. On the receipt of a response, the stream ID entry is removed from the ST, allowing it to be reused on future outgoing requests.

**CNI** Communication Scheduler (CNI-CS): The CNICS provides initial VC allocation to the flit emerging from the CNI. It does so based on the requested VC allocation class. Details on class-based VC allocation scheme, its benefits and setting of the class id field of the flit are discussed in Section C. When supporting dynamic bandwidth scaling, the CNICS is responsible for modifying the bandwidth allocated to the communication streams originating from this CNI. The bandwidth allocations are modified by the CNIC.

Link Controller (LC): It provides an interface for the CNI to the NoC. Its purpose is to match CNI operation parameters like clock rate to that of the NoC. In cases where clock rates do not match, additional buffers may be needed to match the arrival and service rates of the CNI and NoC.

**Power Manager (CNI-PM)**: Most IP cores are capable of operating in low power modes. When determination of the operating mode is dependent on the communication characteristics, the CNI-PM will be used to manage the states of operation. The CNI-PM also manage NoC power. Since power consumption in the NoC is dependent on the volume of traffic, managing traffic injection into the NoC control power consumption. Chapter III details the investigation performed on this aspect.

**Test Controller (TC)**: The TC handles testing of the IP cores through available IP test interfaces. It may either receive test vectors from remote network tiles or obtain them from a local test memory. Results from the TC can be utilized in reconfiguring the NoC too. In the current implementation of the CNI, we do not include the CNI-PM and TC since these are dependent on the IP core characteristics.

Some sub-components of the CNI are IP core specific, while others are NoC specific. The interface arbiter is IP core interface specific and is configured to replay the interface protocol. The packetizer, depacketizer, link controller, DT/RT and

CNIC are NoC specific. The encoder and decoder are technology specific as they are dependent on error rates present in the design.

To provide communication scheduling support in the NoC, the on-chip router needs to be modified to provide for latency constrained on-chip communication. The following section describes the motivation and approach taken towards providing this service.

#### C. Latency Constrained On-chip Communication

VC allocation in on-chip networks can yield unwanted jitter in end-to-end communication. This dissertation proposes a *class-based VC allocation scheme* to bound end-to-end jitter. It is important to note that even in the absence of the proposed scheme, the worst case (WC) jitter is bounded. The proposed scheme would only be useful when WC exceeds desired latency bounds. VC allocation could easily be setup to provide best case jitter results. But this may not always be desirable in RT environments where latency constraint budgets are critical to only part of the communication set.

#### 1. Factors Affecting End-to-end Latency

The end-to-end latency is the sum of delays incurred by a flit at each on-chip router enroute to the destination. The delay (in the absence of congestion) at each network tile is constituted of VC configuration dependent delay and VC configuration independent delay. The VC configuration properties include number of VCs and VC service policy. For our experiments, we consider a simple round-robin service policy.

The on-chip router is constituted of input ports, output ports, switch, switch allocator and a virtual channel allocator. The *input ports* receive flits from neighboring network tiles. The *output ports* forward flits to the neighboring tiles. The *switch* interconnects input and output ports. The *switch allocator* decides on which input and output ports are connected at any given time. The *VC allocator* allocates virtual channels over the next communication hop. Figure 5 illustrates these components.

Fig. 5. On-chip router internals

#### 2. Proposed VC Allocation Scheme

We propose a class-based VC allocation scheme for the VC Allocator (VCA) of the router, which provides next VC allocations for the requested class of communication. The VCA receives requests from the input ports. These requests specify the target output port and the desired class of communication. The VCA responds with a VC id and class id for the next hop - this is needed to support class migration.

One of the situations that may arise is that of the unavailability of VCs for the desired class of communication. In such a case, a VC at a lower priority communication class is provided. Over the next hop, an attempt is made to restore communication to its original classification. We term this as *class migration*, that is restricted between certain levels of classes to prevent any drastic degradation in performance. In certain cases, where communications have stringent deadlines, class migration may be unacceptable. The current configuration of the design does not have a provision for selective class migration, i.e. allow migration for certain communication streams when allowed. Support for such a scheme can be achieved by incorporating additional fields in the flit headers to provide the VCA with additional information that can be used to make VC allocation. We now present the architectural modifications made to the VCA to support the proposed scheme.

#### 3. VCA Architecture

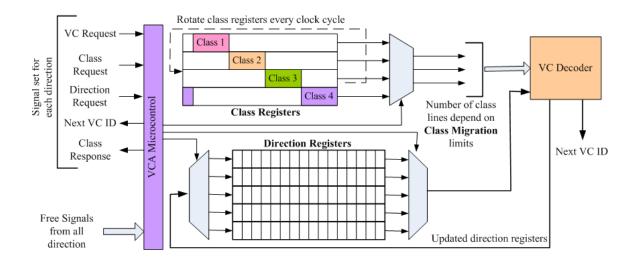

The traditional VCA consisted of direction registers that indicated the availability of free VCs in the output directions. To restrict the allocate-able VCs, class registers are introduced. The number of VCs assigned to each class is identical. Since these change every clock cycle, they are rotated at every clock edge. Based on the requested output port and requested class, the VC decoder determines the next VC id and the class to which it belongs to. The VCA micro-control manages the credit updates for the neighboring network tiles (Figure 6). To support low latency class migration, the VC decoder simultaneously determines next VC ids for a window of classes. The highest available class next VC id is returned to the requesting input port.

#### 4. NoC Support

To support the class-based VC allocation, the NoC flit headers have additional fields, class id and original class id. The original class id field is used to restore the class of communication to its original class after it has migrated to a lower class. The proposed scheme has a very low overhead when compared to the original design,

Fig. 6. Simplified architecture for class-based VCA

since the additional components are the class registers and utilizes a slightly more complex VC Decoder. This was one of the original design goals. A better scheme may be achieved but with a much larger overhead.

#### 5. Setting the Class\_id Field

We have shown how the class\_id field of the flit can be used to provide end-to-end latency jitter bounding. Setting the class of communication is an important aspect. We believe that the class can be set in two ways: (i) by application: The application will stipulate desired class for every communication stream via the available ports of the interface. One implementation we considered provided the class via the address port of the IP core. This information is then used to set the class id field of the flits and (ii) by CNI configuration: The DT/RT can be pre-programmed with a class for each communication stream originating from the CNI and intended for a particular destination. This would require the addition of a single port and an additional field to the DT/RT. The packetizer would obtain the class id from the DT/RT and sets it in the flits.

#### 6. Evaluating Class-based VCA

*NoCSim* was used to evaluate the effectiveness of our proposed scheme. Two versions of the NoC router - *classless VC allocation* and *class-based VC allocation* - were tested.

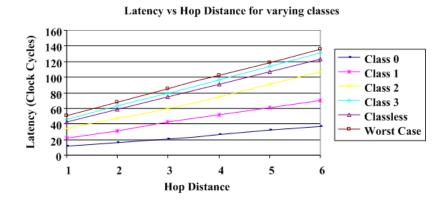

The first experiment analyzed the end-to-end latency bound for the different classes of communications over different hop distances. We set up the class-based VCA with support for 4 classes (0-3). Random traffic sources were used to determine the average flit latency to the destinations. We observe that the performance of the classless VC allocation is not the same as the WC - in fact it is better than the latency observed for class 3. The absence of class-based VC allocation leads to unpredictability and a latency variation of up to 400% (see Figure 7).

Fig. 7. Latency vs hop distance for varying classes

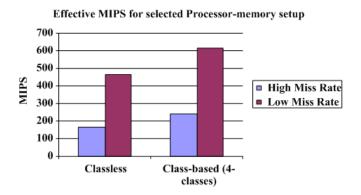

We considered a processor-memory setup [34] with the following characteristics: Processor: 1GHz, Assumed CPI = 1.0, Instruction Mix: 25% Load/Stores, 4:1 = Load:Store, Cache miss rates considered: 5% and 25%, Memory miss penalty: 35 cycles. The layout considered is shown in Figure 8. For the two cache miss rates, the generated NoC traffic leads to varied throughput in the processor. To keep communication latency at a minimum, class 0 was assigned to the communication stream. Using the communication characteristics from the previous experiment, we estimated the effective throughput in terms of MIPS. This experiment clearly shows a 25% improvement in throughput in the low miss rate scenario, while in the case of a high miss rate, there is a 22% improvement when using a class-based VC allocation scheme.

Fig. 8. Effective MIPS for processor for different cache miss rates

#### D. CNI Evaluation

The proposed CNI architecture is implemented for a OCP-IP compliant IP core interface and a 4x4 2D folded torus NoC providing the communication infrastructure for 16 cores. Functional validation of the proposed CNI is achieved in two steps. A SystemC model of the CNI is developed and integrated with *NoCSim*. Using trace-based and task-graph based traffic generation, CNI functionality is validated.

A Verilog HDL implementation of the CNI was synthesized with Synopsys Design Compiler [35] using the Virginia Tech VLSI for Telecommunications TSMC-0.25um, 2.5V standard cell library [36, 37], the gate count for the CNI was estimated at 21,283.Table I lists the breakdown of gates between design modules.

The Verilog design was also synthesized on a FPGA using using the Xilinx ISE.

| Module                      | Gate Count |

|-----------------------------|------------|

| Interface Arbiter           | 3478       |

| Encoder                     | 1208       |

| Packetizer                  | 2212       |

| Route Table                 | 205        |

| Link Controller             | 6022       |

| Depacketizer                | 944        |

| Decoder                     | 2995       |

| CNI Power Manager           | 808        |

| CNI Communication Scheduler | 2154       |

| CNI Controller              | 1257       |

| Total                       | $21,\!283$ |

Table I. Gate count breakdown for CNI modules

The design utilized 1,467 slices of the FPGA. The equivalent gate count was estimated at 24,154.

#### E. Unconsidered Design Issues

Two interface design aspects have not been considered in this dissertation. The first is the *clock domain mismatch*. The clocking domains of the IP cores and NoCs maybe different, leading to different arrival and service rates in the CNI. These issues are also found in present day systems and can be addressed with additional buffers to handle the different rates of operation. In the proposed CNI architecture, the interface arbiter would operate at the IP core interface rate, while the link controller would operate on the NoC clock. Buffers between the arbiter and encoder/decoder can be used to address the mismatch. The selected buffer depth would impact the number of outstanding requests managed by the CNI.

Transaction ordering in traditional bus-based systems are ordered. This is possible with low overheads due to the presence of a direct link between the components. Transaction re-ordering tends to take place on split buses and is addressed by advanced modes of bus protocols. In NoCs, ordering becomes more difficult. Global ordering required a central arbitration mechanism. Local ordering between sourcedestination pairs is achievable with costly overheads in the form of sequence numbers and additional buffering to allow for reordered delivery.

#### CHAPTER III

#### PEAK POWER AWARE NOCS

The emergence of complex SoC designs with increased communication requirements have led to the deployment of NoCs. They address scalability challenges presented by traditional bus-based communication infrastructures. However, these also present power related cooling and reliability challenges making the peak power consumption a critical design time constraint. As identified in [17, 38], 50% of the electronic failures are temperature related, since circuit reliability is exponentially dependent on operation temperature. The increasing dominance of the power consumption of on-chip networks in present day systems poses critical challenges that need to be addressed lest they become a bottleneck in the development of high performance systems [39]. The power consumption in routers and links of the Alpha 21364 microprocessor were found to be about 20% of the total power consumption [40]. In the MIT Raw on-chip network, network components constitute 36% of the total power consumption [41]. These numbers indicate the significance of managing the interconnect power consumption.

Peak power of NoCs can be managed at design time or dynamically at run-time. Dynamic peak power management can be further classfied into (i) deterministic and (ii) non-deterministic budget conservation techniques. Figure 9 illustrates the taxonomy of peak power management techniques. At design time, peak power budget for on-chip communication is ensured by setting communication parameters like maximum bandwidth and communication routing [31]. However, design time peak power management lacks adaptability which can lead to performance degradation. Dynamic peak power management schemes are essential to meet varying run-time performance requirements. PowerHerd [17] is a dynamic peak power management scheme proposed for on-chip networks. It manages peak power budgets across the NoC and attempts to meet peak power requirements by sharing power budget between neighboring on-chip routers. Jin et al. [16] proposed a QoS-aware peak power management scheme (PC) that controls flit injection into the NoC while providing an improvement in average latency when considering best effort and real time traffic. These schemes perform suitably for well-behaved and predictable traffic in smaller NoCs. However, they cannot meet adaptability and scalability needs for unpredictable traffic and larger multi-core NoC designs. A comparison of the key requirements of a peak power management scheme is discussed later.

Fig. 9. Taxonomy of peak power management techniques for NoCs

A. Related Work

# 1. Energy/Power Model

Bit-level power models for on-chip networks have been utilized by various researchers [42, 43]. In this research, the power consumption of the NoC has been estimated at the per-flit level. Using the thermal time constant (TTC), we determine the number of flits that are present in the network during this time window and the consequent energy consumption of each of these flits. Flit traversal in the network can be broken down into a sequence of operations (1) *buffer read*, (2) *switch traversal*, (3) *external*

*link traversal* and (4) *buffer write* [17]. The energy consumption of the flit can be estimated with equation 3.1:

$$E_{flit} = (n+1)[E_{BR} + E_{BW} + E_S] + nE_L$$

(3.1)

where,  $E_{flit}$  - energy consumption of flit,  $E_{BR}$  - buffer read energy,  $E_{BW}$  - buffer write energy,  $E_S$  - switch traversal energy,  $E_L$  - external link traversal energy, and n number of hops to destination. Hence the power consumption during TTC for t flits can be determined with equation 3.2

$$P = \frac{\sum_{t \in flits} E_{flit}(t)}{TTC}$$

(3.2)

where, P - power consumption, and  $E_{flit}(t)$  - energy consumption for flit t.

Using energy/power values from the IBM 90nm workbook, we experiment to determine the effect of varying traffic loads on the energy distribution amongst the network tile components (buffer, switch and links). The energy distribution profile in Figure 10 emphasizes the contribution of the buffer operation energy to the total flit energy for the varying loads. With over 60% of the total energy contribution being made by the buffers, it stands in sharp contrast to the chip-to-chip link scenario, where the buffer contributes about 10% and the link contributes over 80%.

# 2. PowerHerd

PowerHerd was proposed for the dynamic monitoring and management of peak power consumption in NoCs. The technique ensures that the total energy consumed over the thermal time constant duration is bounded by the global peak power budget -  $P_{GPB}$ . PowerHerd is deployed in on-chip routers and consists of power estimation, prediction, sharing, routing and regulation. The router *estimates* is power consumption based on

Fig. 10. Energy distribution profile for different loads

observed activity. This is then used to *predict* future budget requirements. This information is used to determine the amount of budget to be *shared* with the neighboring routers. *Regulation* is achieved by throttling switch allocation. *Route decisions* are made based on power budgets in the neighboring routers. These operations take place dynamically and are used for peak power management.

The observed limitations of PowerHerd are:

- 1. Delay in budget migration from one end of the chip to the other. Since budget is exchanged with neighbors only, the response of this approach to rapidly changing budget requirements in the system will be slow. This leads to scalability and adaptability limitations.

- 2. The budget sharing method can lead to formation of islands which would localize power budgets, reducing the effectiveness of the budget sharing.

- 3. Peak power budget management at routers involves additional buffer requirements in the routers.

## 3. Peak Power Control (PC)

In [16], a peak power control technique (PC) involved deploying an injection throttle logic at the injection point into the network. The injection is bound by power budgets. Using a QoS aware on-chip router, performance improvement over PowerHerd was reported. This approach is similar to that proposed in this dissertation.

The observed limitations of PC are:

- 1. There is no budget re-allocation amongst the injection throttle logic. This limits the adaptability of the PC to varying peak power budget requirements.

- 2. Using a uniform distribution of the peak power budget amongst the injection throttle logic does not scale well with increasing NoC sizes, especially when there is no re-allocation between them.

The following section discusses the design time peak power management explored as a part of this dissertation.

### B. Static Peak Power Aware Design

When designing SoCs, predictable communication parameters allow for off-line peak power constraining. This research exploits this idea, and provides a bandwidth controlled peak power constraining scheme. The effect of the scheme in terms of cost and benefit is also presented.

This research utilizes a mode-based communication model that allows for the abstraction of the multimode communication within the system. The information provided by the model aids in reducing the design space explored and yields a solution that conforms to the communication restrictions set by the design specifications. A design heuristic to aid in determining the immediate neighbors of a resource in a regular NoC topology and the routing of the communication within the system is presented here.

The solution obtained does not provide the exact mapping of resources onto the NoC. It only determines immediate neighbors of the resources in the SoC and routes taken by all communications in the system. This flexible solution provided can then be mapped onto the NoC template, depending on placement constraints that the system designer may have. A scenario where such flexibility may be essential is when a particular resource may need to be placed along the chip boundary for I/O operations. The solution obtained is verified through *NoCSim*.

A crucial step in the design methodology, the *neighborhood determination stage* facilitates the determination of immediate neighbors of resources within the NoC topology and the communication routing between them. Power cost associated with the solution obtained is evaluated and depending on the Peak Power Budget, the communication bandwidth is throttled to constrain the peak power consumption.

#### 1. Problem Formulation

The Mode Characterization Graph, MCG(N,C), shown in Figure 11(a), characterizes the communication characteristics of the target multimode system. The node set (N) enumerates the set of communicating resources and the edge set (C) specifies the communications in all modes. Communication edges are characterized by:

- 1. *mode*: mode of operation,

- 2. bandwidth required: performance constraint,

- 3. data volume: amount of data to be transferred in each iteration, and

- 4. injection load: indicates the amount of load injected into the network by this

communication pattern.

It belongs to the range (0,1]. These communication edges are also referred to as secondary edges.

The Network Graph, NG(T,L), shown in Figure 11(b), provides the neighborhood characteristics of the network tile set(T). If a network edge  $ne \in L$ , has an edge between t1 and t2 (t1, t2  $\in$  T), then t1 and t2 are immediate neighbors in the NoC. The network edge ne, highlights the secondary edges that flow through it, and the link bandwidth that has been allocated to that communication edge.

Fig. 11. (a) MCG, (b) NCG, (c) NCG after merge operation

The neighborhood determination problem is framed as a transformation of the arbitrary cardinality MCG into the fixed cardinality NG. The constraint applied during transformation is bandwidth reservation from source to destination for each of the secondary edges.

# 2. Definitions and Operations

**Definition 1**: A *candidate* for transformation is a node in the MCG that has cardinality greater than the constraint set by the target topology.

**Definition 2**: A *critical edge* is a secondary edge that is selected by the heuristic to merge with one of the network edges.

**Operation 1**: The merge operation - merge(se, ne) - adds a secondary edge se to a network edge ne. During the merge operation, the heuristic attempts to allocate bandwidth to the secondary edge. If enough bandwidth is not available, the heuristic redistributes the link bandwidth amongst the secondary edges flowing through it. When the bandwidth of a secondary edge on ne is modified, its bandwidth is updated from source to the destination along all network edges it flows in.

**Operation 2**: The *rank* operation ranks the network edges with which a secondary edge would be merged. The ranking is based on three criteria:

- network edge already visited: This helps keep check on the cyclic propagation of secondary edges amongst the resources.

- network edge backtracked from: prevent wasted effort

- number of secondary edges at the resource pointed to by the network edge whose communication clashes with the mode of the candidate secondary edge.

Example: In the example in Figure 11, consider the given MCG. The target NoC topology is a 2D torus. We need to reduce the cardinality of resource A to 4 and route the extra edge through the other resources. The heuristic selects the four most critical outgoing edges of resource A and assigns them to the four vacant outgoing network edges. In this case, it has selected the edges to B, C, D and E to be the critical edges and hence places B, C, D and E as the immediate neighbors of A. The

edge to F will be routed through the four outgoing edges, i.e. we need to merge the communication of A to F through B, C, D or E. From Figure 11(c) we notice that the heuristic selects resource D to be the candidate through which this connection is to be routed. This selection is done based on the results obtained by the ranking operation.

### 3. Heuristic

The heuristic (see Algorithm 1) that has been shown here is iterative in nature. In each of the iterations we consider a resource (candidate) and attempt to make decisions on its immediate neighbors in the NoC. The objective of the heuristic is to merge these secondary edges with the network edges. These network edges are the network links between tiles in the NoC network.

When we attempt to merge a secondary edge with a network edge, there are three possible scenarios. In *scenario 1*, when the network edge has no destination specified yet, the merge operation will set the destination resource of the secondary edge as an immediate neighbor of the candidate. In *scenario 2*, the network edge has the same destination as that of the secondary edge. Here we just merge the communication and update the bandwidth for the different modes of communication on this network edge. In *scenario 3*, the destination of the network edge is not the same as that of the secondary edge to the destination with the network edge. Aside from that we also add a secondary edge to the destination resource pointed too by the network edge. This new secondary edge would have the same destination as that of the critical secondary edge being merged. These steps are performed for each un-merged secondary edge of each resource in the system.

Algorithm 1 Neighborhood Determination Heuristic

```

while n \in N : n is a candidate do

SE_n = \text{set of secondary edges of } n

NE_n = \text{set of network edges of } n

while |SE_n| \neq \Phi do

se = getCriticalSE()

if \exists ne \in NE_n : ne.dest = se.dest then

merge(se, ne) \\ SE_n = SE_n - se

UpdateRoute(se)

else if \exists ne \in NE_n : ne.dest = \Phi then

if N(ne.dest) supports a return edge to n then

merge(se, ne)

SE_n = SE_n - se_1

UpdateRoute(se)

setNetworkEdge(ne.dest, n)

setNetworkEdge(n, ne.dest)

else

getMultihopReturnPath()

end if

else

rank ne \in NE_n

select best candidate for merge

merge(se, ne)

SE_n = SE_n - se

SE_{ne.dest} = SE_{n.dest} + se

UpdateRoute(se)

if merge not possible then

Backtrack2Predecessor()

end if

end if

end while

```

```

end while

```

### 4. Off-line Peak Power Control

Another aspect that needs to be addressed in SoC design is that of peak power management. The peak power is the maximum power consumed during a TTC and is directly proportional to the number of flits traversing the on-chip network. It can be controlled in two ways: (i) *dynamically*, and (ii) *statically*. Dynamic peak power control would require the deployment of an on-line power control/management strategy. Some techniques that have been proposed are link voltage scaling [44], link on/off technique [45], and Powerherd [17]. But these techniques are mostly for off-chip networks. The cost associated with implementing such techniques on-chip might be too. For the off-line (static) peak power control, there are essentially two schemes: (1) *admission control*, and (2) *communication scaling*.

When designing SoCs, admission control cannot be used to reject communication since it is not a viable design option. So the appropriate solution would be to use the communication scaling scheme where the communication would be accepted, but the bandwidth allocated to it may not be equivalent to its demand.

The network model in [4], utilizes virtual channels and in this scenario, the link bandwidth is divided equally amongst them. So by modifying the number of virtual channels allocated to a communication, we can modify the bandwidth allocated to it and thereby its power consumption. In the peak power constraining phase of the design, the bandwidth allocated to the communications is scaled down in the modes in which there is a peak power violation. The bandwidth allocation is reduced by scaling down the number of virtual channels that are allocated to the communications. Performance degradation in terms of throughput reduction is expected. We provide results to demonstrate the effect of the bandwidth control

# 5. Evaluation

For our experiments, we used two test cases. For each test case we examine the peak power results for:

- Adhoc mapping solution: This solution is a random mapping of resources in the NoC. It is not the worst possible configuration.

- Expected peak power without bandwidth control: These peak power results are obtained from the neighborhood determination heuristic.

- Actual peak power without bandwidth control: These peak power results are obtained through *NoCSim* simulations.

- Expected peak power with bandwidth control: These peak power results are the expected peak power results due to the effect of the offline peak power control through bandwidth control.

- Actual peak power with bandwidth control: These peak power results are obtained through *NoCSim* simulations.

We also examine the effect of the peak power control on the throughput of the NoC. The first test case was a synthetic case. Table II summarizes the specifications of the test case. Figure 12 shows the peak power consumption for each of the modes of operation. The adhoc mapping solutions consume a considerable amount of power (upto 2x). The neighborhood determination heuristic inherently constrains the amount of power consumed. Through bandwidth control we were able to reduce the peak power consumption to the 1.5W limit. Figure 13 shows the consequent degradation in throughput. An example of how performance degrades with peak power control can be seen in the case of mode 3 for test case 1. For a 40% reduction in peak power, there is a 40% reduction in throughput.

| Classification           | Synthetic test case                        | Multimedia System                        |

|--------------------------|--------------------------------------------|------------------------------------------|

|                          |                                            | (MP3, MPEG, JPEG,                        |

|                          |                                            | ADPCM)                                   |

| No. of resource          | 16                                         | 4                                        |

| No. of modes             | 5                                          | 3                                        |

| Total no. of comm. edges | 39                                         | 21                                       |

| Mode::No. of comm. edges | 0::6, 1::9, 2::8, 3::9, 4::7               | 0::8, 1::7, 2::6                         |

| Target Topology          | 2D  torus  (4x4)                           | 2D  torus  (2x2)                         |

| Network link Properties  | 128 bit wide,                              | 128 bit wide,                            |

|                          | $1 \text{Ghz} \Rightarrow 128 \text{Gbps}$ | $1\text{Ghz}{\Rightarrow}128\text{Gbps}$ |

| Number of VCs/           | 4/32Gbps                                   | 4/32Gbps                                 |

| Bandwidth per VC         |                                            |                                          |

| Peak Power Budget        | 1.5W                                       | 0.35W                                    |

Table II. Test case 1 and 2 specification summary

Fig. 12. Test case 1: Peak power results for different NoC configurations (Peak power constraint = 1.5W)

Fig. 13. Test case 1: Effect of peak power control on NoC throughput

The second test case was a conglomeration of MP3 encoder-decoder, MPEG encoder, JPEG compression and ADPCM encoder-decoder. The system was configured to operate in three modes and the traffic loads have been scaled up to get results of interest. Table II summarizes the test case specification of this test case. Figure 14 illustrates the peak power consumption in the different modes. In mode 1, we observe that the peak power consumption for the adhoc solution is actually lower than that expected by the heuristic. But as mentioned earlier, this adhoc solution was not setup to be the worst case scenario, hence it turned out to be a suitable configuration for mode 1 (but not for mode 0 and 2, else the heuristic would have determined it). The latency degradation for peak power control for test case 2 is shown in Figure 15.

Fig. 14. Test case 2: Peak power results for different NoC configurations (Peak power constraint = 0.35W)

Fig. 15. Test case 2: Average flit latency

To address this performance degradation due to the pessimistic design decision, a dynamic peak power management scheme is essential. The following section proposes a novel peak power management scheme that is both scalable and adaptable.

# C. SAPP: Scalable and Adaptable Peak Power Management in NoCs

This research proposes SAPP, a scalable and adaptable peak power management technique for NoCs. Using a non-deterministic, independent and dynamic budget re-allocation approach, this technique autonomously manages peak power budgets in NoCs, making it suitable to multi-core processors and MPSoC designs where communication characteristics are not available. *Scalability* is provided by independent peak power budget re-allocation that avoids the need for budget sharing amongst immediate neighbors. *Adaptability* is granted by the non-deterministic budget re-allocation approach proposed here. The non-deterministic peak power budget variation is observed to be within 5% of the global peak power budget and is guaranteed by periodic check-pointing of allocated peak power. Evaluation of SAPP on uniform, non-uniform and non-uniform with varying injection loads demonstrates average flit latency improvements averaging 47% and effective throughput improvements averaging 36%.

### 1. SAPP

A peak power management scheme has two functions:

- Peak power constrained communication and

- Peak power budget management.

Peak power constrained communication ensures that communication being injected into the NoC is constrained by the peak power budget allocated at the injection point (the CNI). Peak power budget management re-allocates the power budget amongst the network tiles, while ensuring that global peak power budgets are not violated.

This research proposes a scalable and adaptable peak power management technique. Scalability is provided by independent peak power budget re-allocation that avoids the need for budget sharing amongst immediate neighbors. Adaptability is granted by the non-deterministic budget re-allocation approach proposed here.

SAPP is deployed in the CNI-PM module of the CNI. All CNI-PMs in the NoC manage power consumption in a distributed and independent manner. The three SAPP operations that provide the aforementioned functions are:

- Flit Injection Control into the NoC,

- Peak Power Budget Re-allocation,

- Peak Power Budget Check-pointing

- a. Flit Injection Control

Power consumed in the NoC is directly proportional to the number of flits traversing the NoC links. Flit injection control ensures peak power consumed by communication emerging from a network tile is constrained by the budget allocated to it. This budget can either be distributed uniformly through the NoC or custom allocated based on the type of applications executing in the SoC. Let  $AllocPPB^i$  be the peak power budget allocated to network tile *i*. This peak power budget is represented in the form of energy credits; we assume credits to be represented with integers allowing for low overhead hardware implementation. Prior to egress of flit from the source CNI, the link controller checks with CNI-PM to ensure presence of sufficient power budget. If unavailable, injection at this network tile is throttled, else it is injected into the NoC and the appropriate amount of energy credits are debited from the budget. Flit Injection Control operation is specified in Algorithm 2.

# Algorithm 2 Flit Injection Control

| Calculate $hd \{hd - hop distance to destination\}$                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calculate $hd \{hd - hop \text{ distance to destination}\}$<br>Calculate $\#$ of energy credits $E_{flit}$ needed by flit from source to destination |

| if $E_{flit} \leq Alloc_PPB^i$ then                                                                                                                  |

| $Alloc\_PPB^i = Alloc\_PPB^i - E_{flit}$                                                                                                             |

| Send <i>ready_to_send</i> signal to Link Controller                                                                                                  |