# DEVELOPMENT OF ROBUST ANALOG AND MIXED-SIGNAL CIRCUITS IN THE PRESENCE OF PROCESS-VOLTAGE-TEMPERATURE VARIATIONS

A Dissertation

by

# MARVIN OLUFEMI ONABAJO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2011

Major Subject: Electrical Engineering

# DEVELOPMENT OF ROBUST ANALOG AND MIXED-SIGNAL CIRCUITS IN THE PRESENCE OF PROCESS-VOLTAGE-TEMPERATURE VARIATIONS

## A Dissertation

by

## MARVIN OLUFEMI ONABAJO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Jose Silva-Martinez

Committee Members, Edgar Sánchez-Sinencio

Sunil Khatri

Duncan M. H. Walker

Head of Department, Costas N. Georghiades

May 2011

Major Subject: Electrical Engineering

### **ABSTRACT**

Development of Robust Analog and Mixed-Signal Circuits in the Presence of Process-

Voltage-Temperature Variations. (May 2011)

Marvin Olufemi Onabajo,

B.S., The University of Texas at Arlington;

M.S., Texas A&M University

Chair of Advisory Committee: Dr. Jose Silva-Martinez

Continued improvements of transceiver systems-on-a-chip play a key role in the advancement of mobile telecommunication products as well as wireless systems in biomedical and remote sensing applications. This dissertation addresses the problems of escalating CMOS process variability and system complexity that diminish the reliability and testability of integrated systems, especially relating to the analog and mixed-signal blocks. The proposed design techniques and circuit-level attributes are aligned with current built-in testing and self-calibration trends for integrated transceivers. In this work, the main focus is on enhancing the performances of analog and mixed-signal blocks with digitally adjustable elements as well as with automatic analog tuning circuits, which are experimentally applied to conventional blocks in the receiver path in order to demonstrate the concepts.

The use of digitally controllable elements to compensate for variations is exemplified with two circuits. First, a distortion cancellation method for baseband

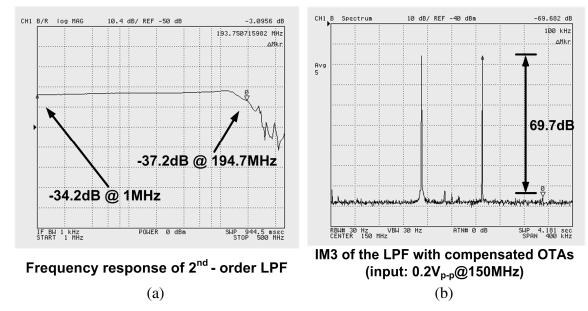

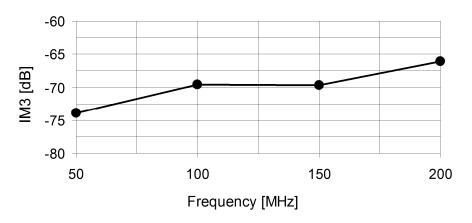

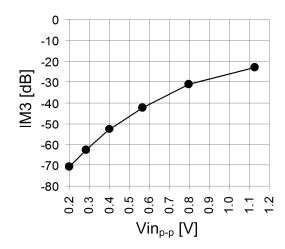

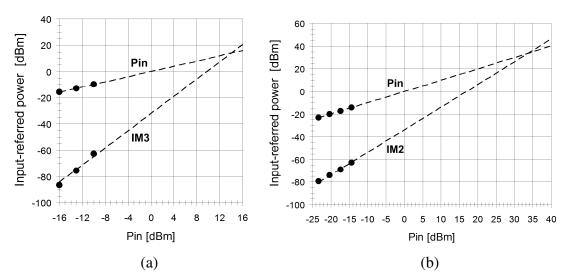

operational transconductance amplifiers is proposed that enables a third-order intermodulation (IM3) improvement of up to 22dB. Fabricated in a 0.13 $\mu$ m CMOS process with 1.2V supply, a transconductance-capacitor lowpass filter with the linearized amplifiers has a measured IM3 below -70dB (with 0.2V peak-to-peak input signal) and 54.5dB dynamic range over its 195MHz bandwidth. The second circuit is a 3-bit two-step quantizer with adjustable reference levels, which was designed and fabricated in 0.18 $\mu$ m CMOS technology as part of a continuous-time  $\Sigma\Delta$  analog-to-digital converter system. With 5mV resolution at a 400MHz sampling frequency, the quantizer's static power dissipation is 24mW and its die area is 0.4mm<sup>2</sup>.

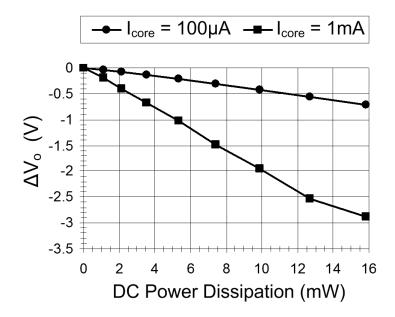

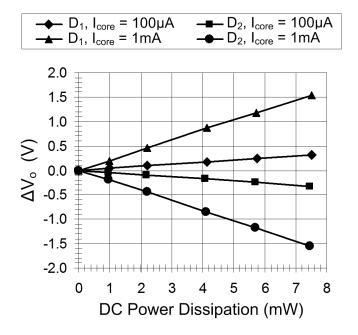

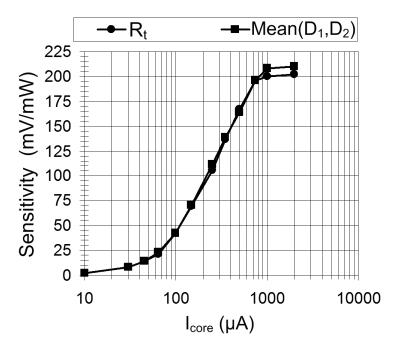

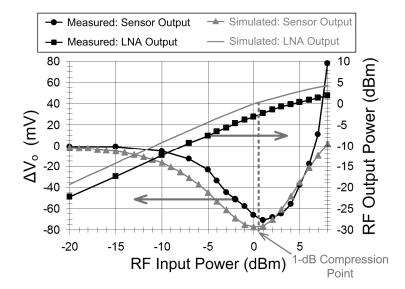

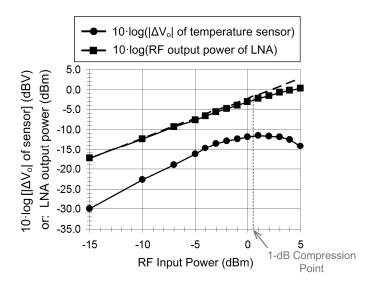

An alternative to electrical power detectors is introduced by outlining a strategy for built-in testing of analog circuits with on-chip temperature sensors. Comparisons of an amplifier's measurement results at 1GHz with the measured DC voltage output of an on-chip temperature sensor show that the amplifier's power dissipation can be monitored and its 1-dB compression point can be estimated with less than 1dB error. The sensor has a tunable sensitivity up to 200mV/mW, a power detection range measured up to 16mW, and it occupies a die area of 0.012mm<sup>2</sup> in standard 0.18µm CMOS technology.

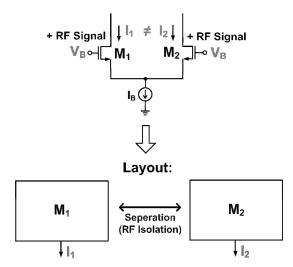

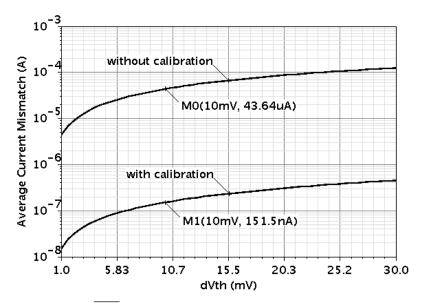

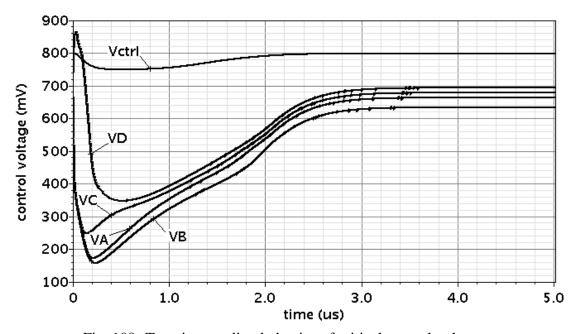

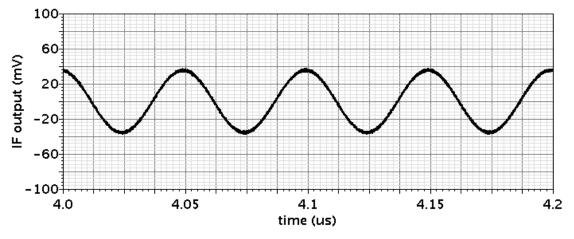

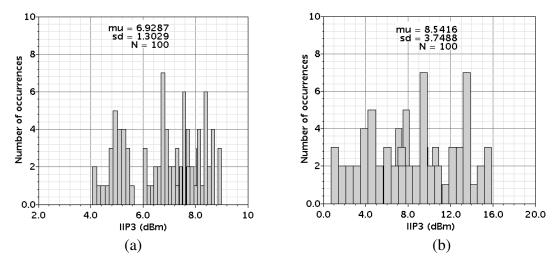

Finally, an analog calibration technique is discussed to lessen the mismatch between transistors in the differential high-frequency signal path of analog CMOS circuits. The proposed methodology involves auxiliary transistors that sense the existing mismatch as part of a feedback loop for error minimization. It was assessed by performing statistical Monte Carlo simulations of a differential amplifier and a double-balanced mixer designed in CMOS technologies.

### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor Dr. Jose Silva-Martinez for his support, guidance, and constructive critique over the past years. I also greatly appreciate Dr. Edgar Sánchez-Sinencio's mentorship and assistance related to several research projects and to my graduate studies. Having received valuable advice from Dr. Sunil Khatri and Dr. Duncan Walker, I want to thank them for serving on my dissertation committee.

Various funding sources have made this work possible. I thank the Department of Electrical and Computer Engineering, Texas Instruments, and Broadcom for financial support. I would like to acknowledge the sponsorship of the chip fabrications by Jazz Semiconductor and United Microelectronics Corporation, as well as partial funding of the test cost by grants from TAMU-CONACYT and the National Science Foundation.

It has been a pleasure and great learning experience to collaborate on research projects with several other graduate students at Texas A&M University; namely Xiaohua Fan, Felix Fernandez, Mohamed Mobarak, Cho-Ying Lu, Venkata Gadde, Yung-Chung Lo, Vijay Periasamy, Fabian Silva-Rivas, Hsien-Pu Chen, Hemasundar Mohan Geddada, Chang Joon Park, and Aravind Kumar Padyana.

Many thanks also go out to fellow department members for helpful conversations regarding research and course projects; especially to Raghavendra Kulkarni, Jason Wardlaw, Mohamed El-Nozahi, Heng Zhang, Jusung Kim, John Mincey, Alfredo Perez, Mandar Kulkarni, Nicolas Frank, Casey Wang, Joselyn Torres, Erik Pankratz, Mohammed Mohsen Abdul-Latif, Ramy Saad, Chadi Geha, Sang Wook Park, Chinmaya

Mishra, Manisha Gambhir, Younghoon Song, and Vijay Dhanasekaran. Furthermore, I would like to thank Ella Gallagher for helping to facilitate events and completion of paperwork on many occasions.

I appreciate having had the opportunity to work together with Dr. Josep Altet from the Universitat Politècnica de Catalunya (UPC) in Barcelona, Spain; and thank him for sharing his experience related to on-chip temperature sensing during his stay at Texas A&M University. I also thank Dr. Eduardo Aldrete-Vidrio, Dr. Diego Mateo, and Didac Gómez from UPC for the collaboration related to thermal testing strategies.

In closing the acknowledgments, I am grateful for the encouragement, understanding, as well as support from my parents and brother. They have inspired me in many aspects of life, including education.

# TABLE OF CONTENTS

| P                                                                               | age   |

|---------------------------------------------------------------------------------|-------|

| ABSTRACT                                                                        | . iii |

| ACKNOWLEDGMENTS                                                                 | V     |

| TABLE OF CONTENTS                                                               | .vii  |

| LIST OF FIGURES                                                                 | X     |

| LIST OF TABLES                                                                  | xvi   |

| I. INTRODUCTION                                                                 | 1     |

| I.1. Background and Motivation                                                  | 1     |

| I.2. Research Focus and Dissertation Organization                               |       |

| I.2.1. Linearization scheme for transconductance amplifiers                     |       |

| I.2.2. Process variation-aware quantization                                     |       |

| I.2.3. Non-invasive on-chip measurement of thermal gradients and RF power       |       |

| I.2.4. Analog calibration for transistor mismatch reduction                     |       |

| II.1. Current Trends                                                            |       |

| II.1.1. The impact of rising process variations                                 |       |

| II.1.2. Circuit and system design tendencies                                    |       |

| II.2. A System Perspective on Transceiver Built-In Testing and Self-Calibration |       |

| II.2.1. Digital correction and calibration                                      | 19    |

| II.2.2. Analog measurements and tuning                                          |       |

| II.2.3. Loopback testing                                                        |       |

| II.2.4. Digital performance monitoring with analog compensation                 | 28    |

| II.2.5. Combined digital monitoring, analog measurements, and tuning            | 30    |

| II.2.6. High-volume manufacturing testing                                       | 31    |

| III. HIGH-LINEARITY TRANSCONDUCTANCE AMPLIFIERS WITH DIGITAL                    |       |

| CORRECTION CAPABILITY                                                           |       |

| III.1. Background                                                               | 34    |

| III.2. Attenuation-Predistortion Linearization Methodology                      | 37    |

| III.2.1. Single-ended circuits                                                  | 38    |

| III.2.2. Fully-differential circuits                                            |       |

| III.2.3. Scaling of attenuation ratios                                          |       |

| III.2.4. Volterra series analysis                                               | 44    |

|                                                                                       | Page |

|---------------------------------------------------------------------------------------|------|

| III.3. Circuit-Level Design Considerations                                            | 45   |

| III.3.1. Fully-differential OTA with floating-gate FETs                               |      |

| III.3.2. Proof-of-concept filter realization and application considerations           |      |

| III.4. Compensation for PVT Variations and High-Frequency Effects                     |      |

| III.5. Prototype Measurement Results                                                  |      |

| III.5.1. Standalone OTA                                                               |      |

| III.5.2. Second-order lowpass filter                                                  |      |

| III.6. Summarizing Remarks                                                            |      |

| IV. QUANTIZER DESIGN FOR A CONTINUOUS-TIME SIGMA-DELTA ADO                            | 1    |

| WITH REDUCED DEVICE MATCHING REQUIREMENTS                                             |      |

| IV.1. Background                                                                      | 69   |

| IV.1.1. State of the art continuous-time $\Sigma\Delta$ ADCs                          | 70   |

| IV.1.2. Quantizer design trends                                                       | 72   |

| IV.1.3. Quantizer design considerations for the $\Sigma\Delta$ modulator architecture | 77   |

| IV.2. 3-Bit Two-Step Current-Mode Quantizer Architecture                              | 83   |

| IV.2.1. Quantizer design                                                              |      |

| IV.2.2. Process variations                                                            | 91   |

| IV.2.3. Simulation results and technology scaling                                     | 97   |

| IV.2.4. ADC chip measurements with embedded quantizer                                 | 102  |

| IV.3. Summarizing Remarks                                                             | 107  |

| V. AN ON-CHIP TEMPERATURE SENSOR TO MEASURE RF POWER                                  |      |

| DISSIPATION AND THERMAL GRADIENTS                                                     | 109  |

| V.1. Background                                                                       | 109  |

| V.2. Temperature Sensing Approach                                                     |      |

| V.2.1. Integration with transceiver calibration techniques                            |      |

| V.2.2. Modeling of the thermal coupling                                               |      |

| V.2.3. Electro-thermal analysis example: low-noise amplifier                          | 117  |

| V.3. CMOS Differential Temperature Sensor Design                                      | 122  |

| V.3.1. Previous sensors                                                               | 122  |

| V.3.2. Design of the proposed sensor topology                                         | 123  |

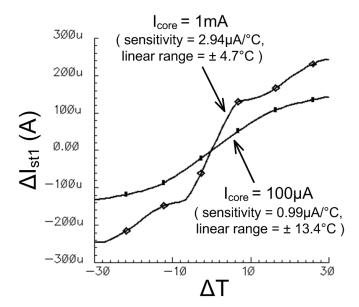

| V.3.3. Adjustment of the sensor's sensitivity                                         | 130  |

| V.3.4. Sensor design optimization procedure                                           |      |

| V.4. Measurement Results                                                              |      |

| V.4.1. Temperature sensor characterization                                            |      |

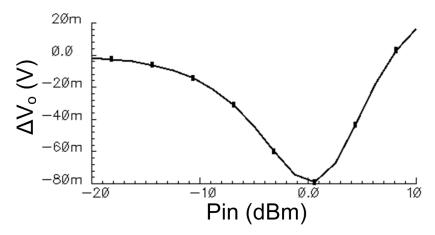

| V.4.2. RF testing with the on-chip DC temperature sensor                              |      |

| V.5. Summarizing Remarks                                                              | 146  |

| P                                                                      | age |

|------------------------------------------------------------------------|-----|

| VI. MISMATCH REDUCTION FOR TRANSISTORS IN HIGH-FREQUENCY               |     |

| DIFFERENTIAL ANALOG SIGNAL PATHS                                       | 147 |

|                                                                        |     |

| VI.1. Background                                                       |     |

| VI.2. A Mismatch Reduction Technique for Differential Pair Transistors |     |

| VI.2.1. Approach                                                       |     |

| VI.2.2. Simulation results                                             |     |

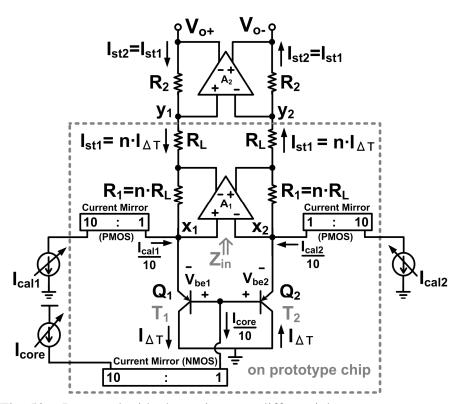

| VI.3. Second-Order Nonlinearity Enhancement for Double-Balanced Mixers |     |

| VI.3.1. Introduction                                                   |     |

| VI.3.2. Proposed mixer calibration                                     |     |

| VI.3.3. Double-balanced mixer design                                   |     |

| VI.3.4. Simulation results                                             |     |

| VI.4. Summarizing Remarks                                              | 195 |

| VII. SUMMARY AND CONCLUSIONS                                           | 197 |

| VII.1. Overall Perspective                                             | 197 |

| VII.2. Dissertation Projects                                           |     |

| ·                                                                      |     |

| REFERENCES                                                             | 202 |

|                                                                        |     |

| APPENDIX A                                                             | 217 |

| APPENDIX B                                                             | 222 |

|                                                                        |     |

| APPENDIX C                                                             | 229 |

| APPENDIX D                                                             | 231 |

| VITA                                                                   | 235 |

# LIST OF FIGURES

|          | Page                                                                               |

|----------|------------------------------------------------------------------------------------|

| Fig. 1.  | Smartphone market trend.                                                           |

| Fig. 2.  | Single-chip transceiver in a cell phone.                                           |

| Fig. 3.  | Specification variation impact on the fraction of discarded chips13                |

| Fig. 4.  | Process corner-based vs. 3σ design approaches                                      |

| Fig. 5.  | Receiver with digital I/Q mismatch compensation ([14])20                           |

| Fig. 6.  | Analog I/Q calibration for image-rejection receivers                               |

| Fig. 7.  | BIT with analog instrumentation along the signal path25                            |

| Fig. 8.  | Generalized transceiver block diagram with loopback27                              |

| Fig. 9.  | Transceiver with digital monitoring and tuning of analog blocks29                  |

| Fig. 10. | Transceiver with digital monitoring, analog measurements, and tuning30             |

| Fig. 11. | Attenuation-predistortion linearization for single-ended circuits39                |

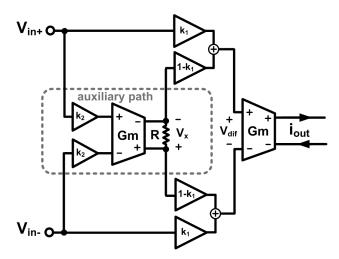

| Fig. 12. | Attenuation-predistortion linearization for fully-differential circuits4           |

| Fig. 13. | Low-frequency model for the attenuation-predistortion scheme43                     |

| Fig. 14. | Folded-cascode OTA (implements $G_{m}$ in the main and auxiliary paths)46          |

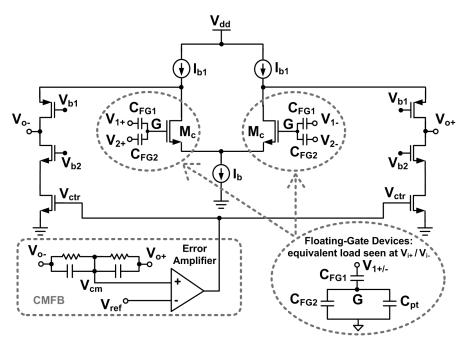

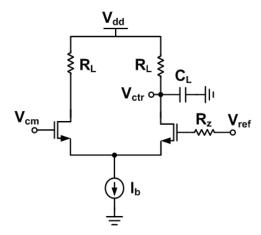

| Fig. 15. | Error amplifier circuit in the CMFB loop                                           |

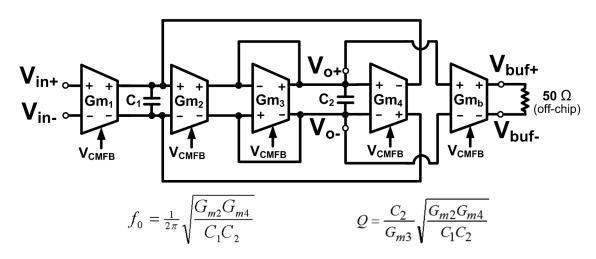

| Fig. 16. | 2 <sup>nd</sup> -order lowpass filter diagram and design parameters                |

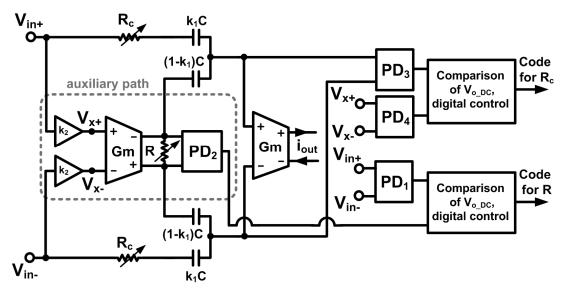

| Fig. 17. | Block diagram of the proposed automatic linearity tuning scheme5                   |

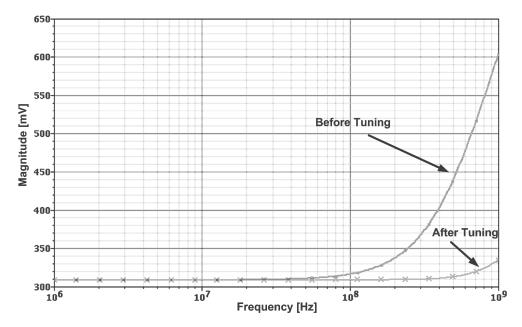

| Fig. 18. | Simulated AC amplitude at the input of the main OTA (PD <sub>3</sub> in Fig. 17)53 |

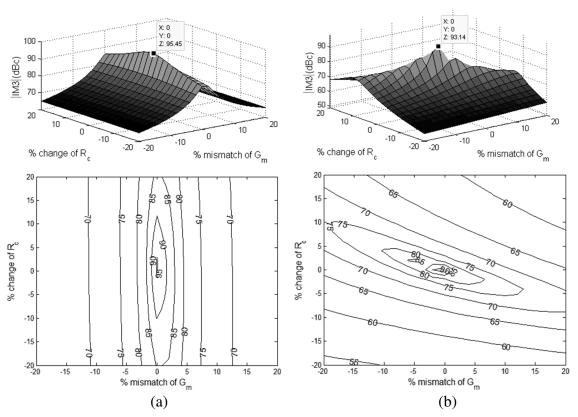

| Fig. 19. | Sensitivity of IIM3l (in dBc) to component mismatches54                            |

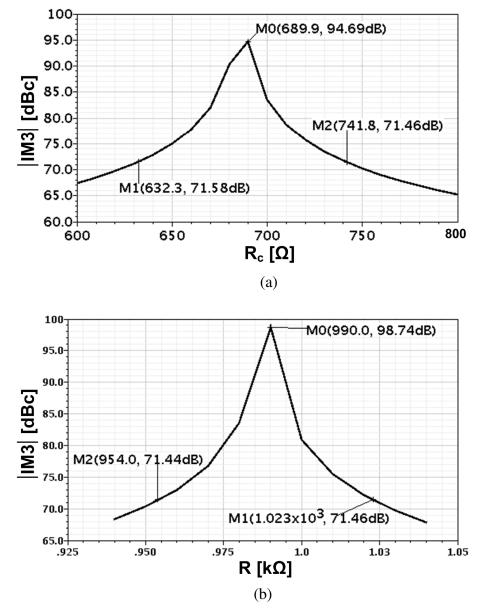

| Fig. 20. | Simulated sensitivity to critical component variations and mismatches56            |

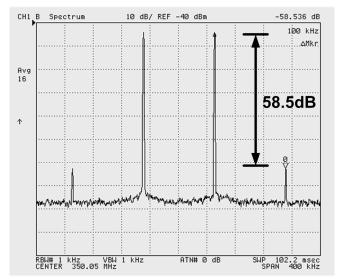

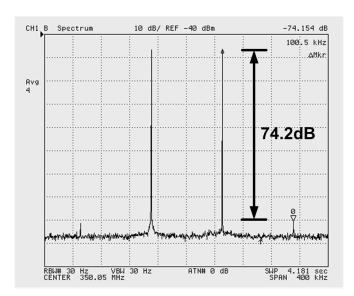

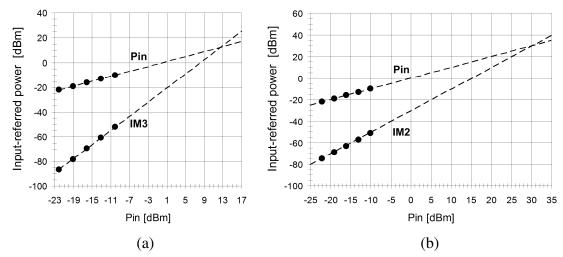

| Fig. 21. | Measured linearity with 0.2V <sub>p-p</sub> input swing from two tones58           |

| Page                                                                             |

|----------------------------------------------------------------------------------|

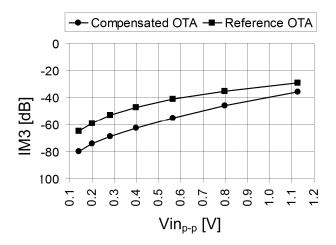

| Fig. 22. IM3 vs. input voltage swing for reference OTA and compensated OTA60     |

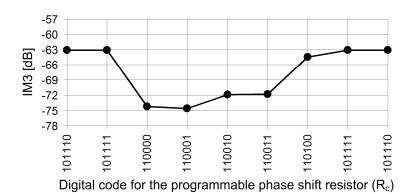

| Fig. 23. Measured IM3 dependence of the compensated OTA on phase shift60         |

| Fig. 24. Measured filter frequency response and linearity                        |

| Fig. 25. Filter IM3 vs. frequency measured with two tones spaced by 100KHz63     |

| Fig. 26. IM3 vs. input peak-peak voltage for the linearized filter64             |

| Fig. 27. Measured in-band intercept point curves for the filter                  |

| Fig. 28. Measured out-of-band intercept point curves for the filter66            |

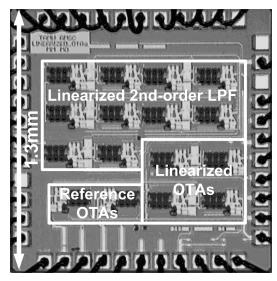

| Fig. 29. Die micrograph of the OTAs and filter in 0.13μm CMOS technology68       |

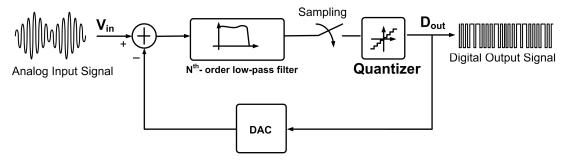

| Fig. 30. Simplified diagram of a continuous-time $\Sigma\Delta$ modulator70      |

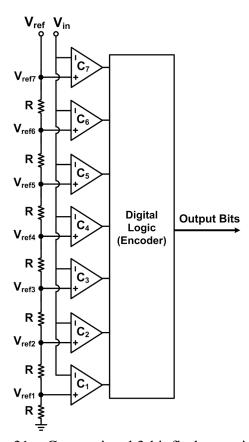

| Fig. 31. Conventional 3-bit flash quantizer                                      |

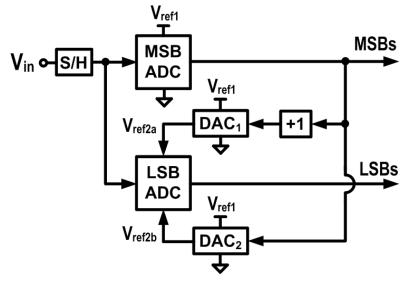

| Fig. 32. The two-step ADC principle                                              |

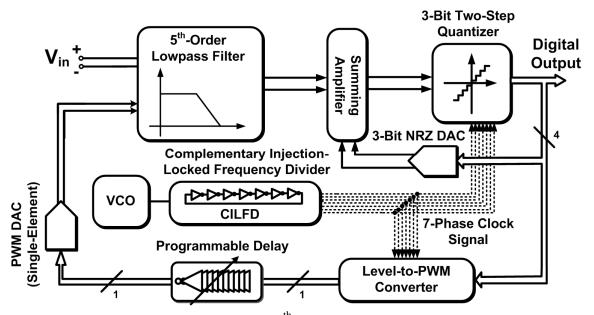

| Fig. 33. Block diagram of the 5 <sup>th</sup> -order continuous-time modulator78 |

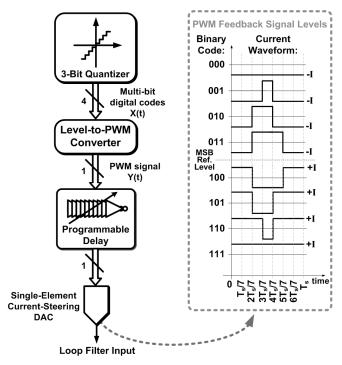

| Fig. 34. Feedback path with 3-bit quantizer and PWM DAC                          |

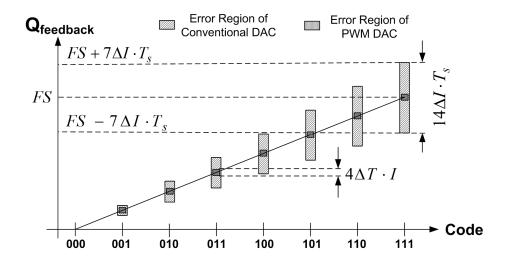

| Fig. 35. Relative 3-bit DAC linearity error comparison: conventional vs. PWM83   |

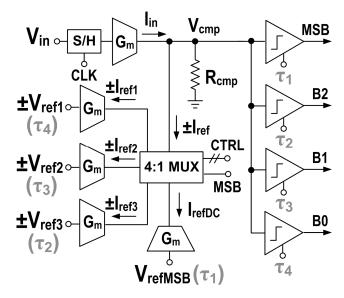

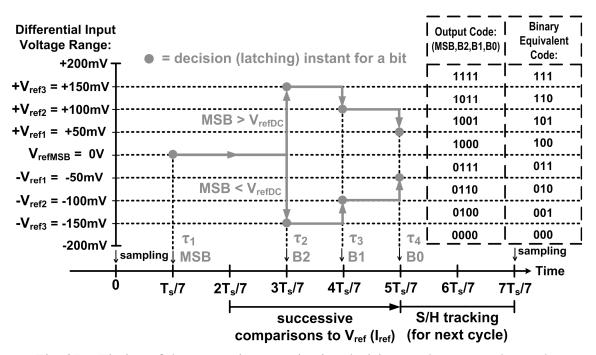

| Fig. 36. Single-ended equivalent block diagram of the quantizer84                |

| Fig. 37. Timing of the successive quantization decisions and output code words84 |

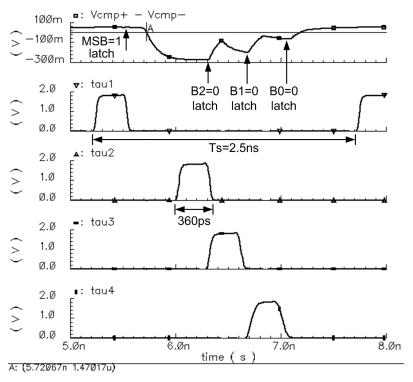

| Fig. 38. Simplified schematic of the current-mode quantizer core circuitry86     |

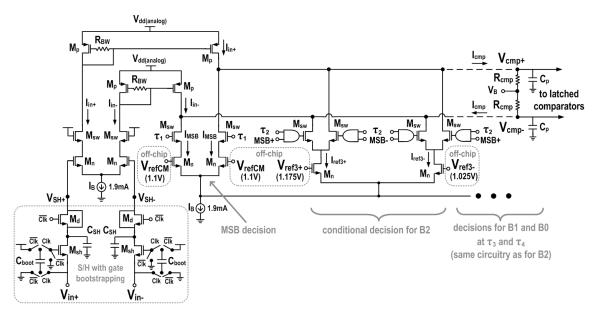

| Fig. 39. Simulated example of the quantization timing                            |

| Fig. 40. Schematic of the latched comparator90                                   |

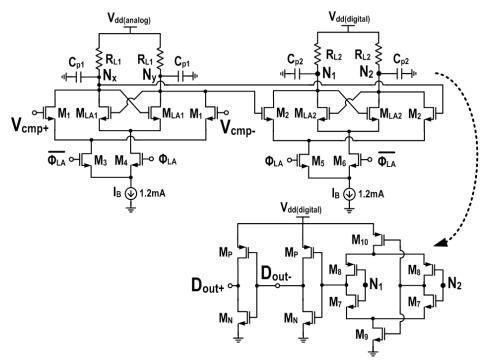

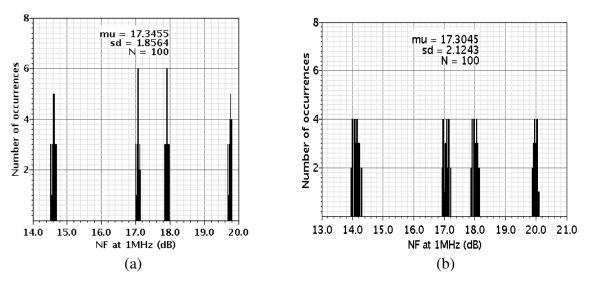

| Fig. 41. Latched comparator Monte Carlo simulation without device matching93     |

| Fig. 42. Latched comparator Monte Carlo simulation with device matching95        |

| Pag                                                                                                  | ıge |

|------------------------------------------------------------------------------------------------------|-----|

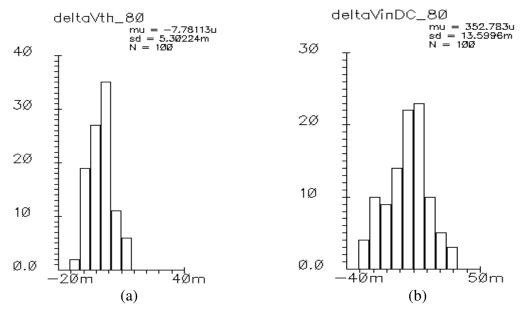

| 3. Quantizer core Monte Carlo simulation with device matching                                        | 96  |

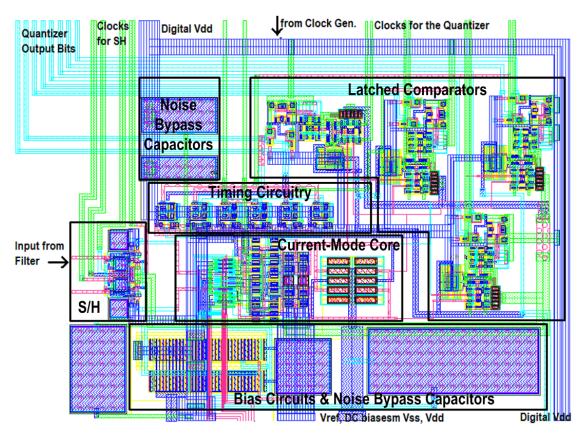

| 4. Quantizer layout (0.18μm CMOS technology)                                                         | 97  |

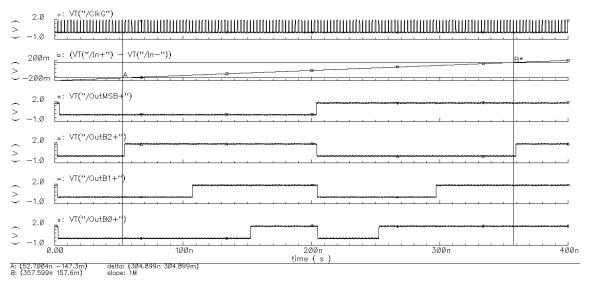

| 5. Output bit transitions with an input ramp from -200mV to 200mV                                    | 98  |

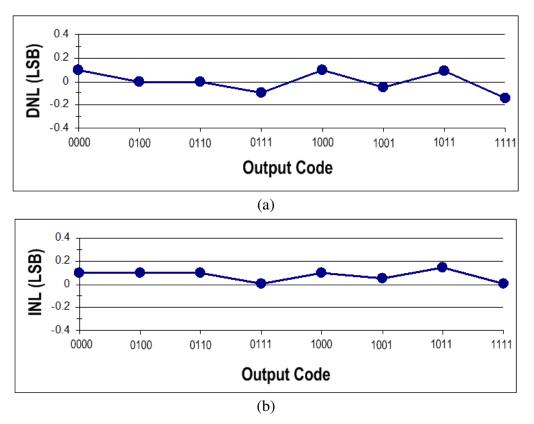

| 6. Quantizer post-layout simulations: (a) DNL (b) INL                                                | 99  |

| 7. Tuning range of the -150mV transition level (schematic simulations)10                             | 00  |

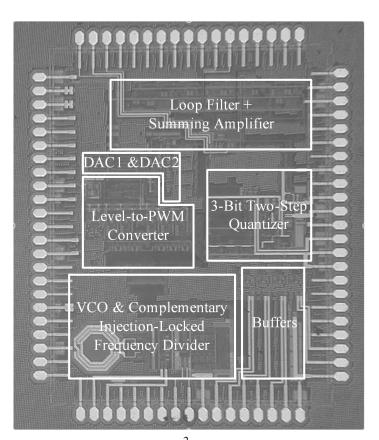

| 8. Die microphotograph (2.6mm² area excluding pads and ESD circuitry)10                              | 03  |

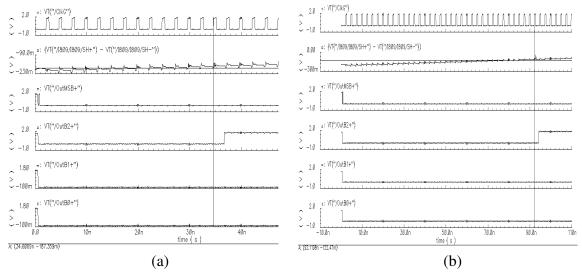

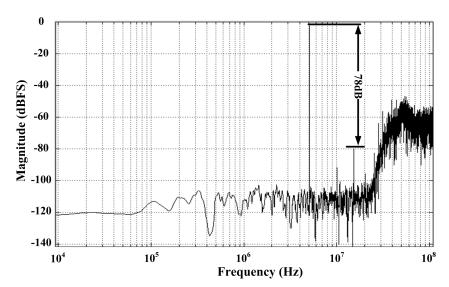

| 9. Measured output spectrum of the $\Sigma\Delta$ modulator                                          | 04  |

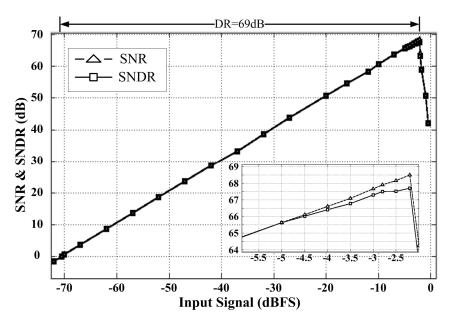

| 0. Measured SNR and SNDR vs. input signal power                                                      | 05  |

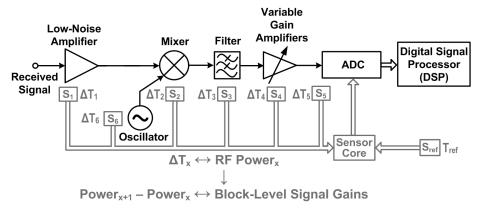

| 1. Generalized receiver diagram with on-chip thermal sensing                                         | 12  |

| 2. RC network model for electro-thermal coupling                                                     | 14  |

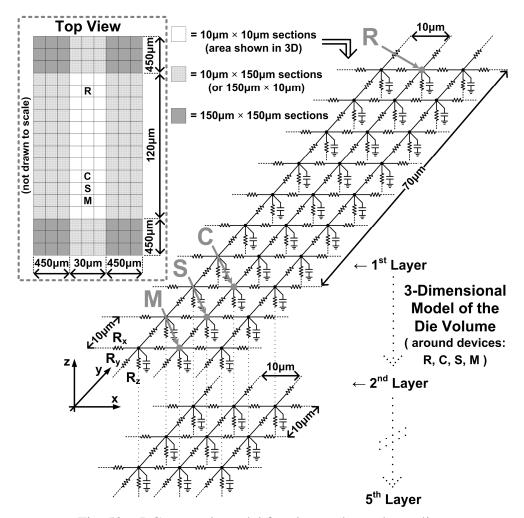

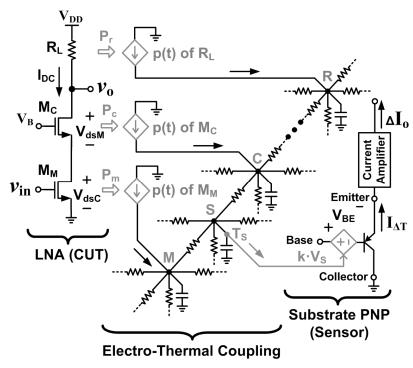

| 3. Electro-thermal coupling between CUT and sensing device                                           | 16  |

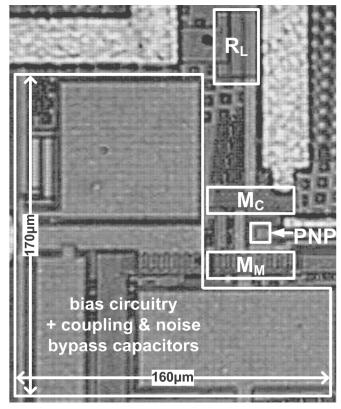

| 4. Area of the die with CUT (LNA) and temperature-sensing PNP device1                                | 19  |

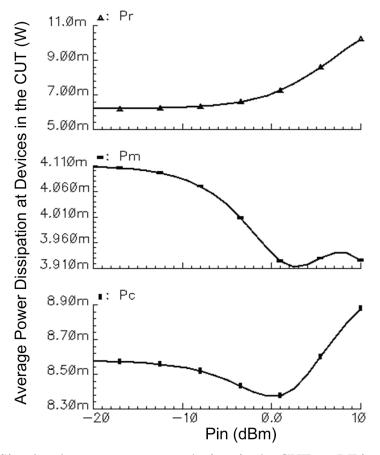

| 5. Simulated average powers at devices in the CUT vs. RF input power12                               | 20  |

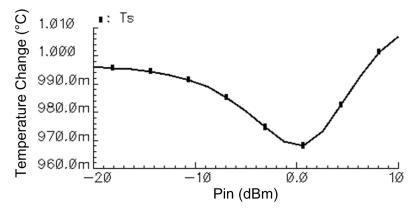

| 6. Temperature change T <sub>s</sub> at the sensing device vs. RF input power                        | 21  |

| 7. Transient behavior of T <sub>s</sub> with -5dBm input power                                       | 22  |

| 8. A differential CMOS temperature sensor with lateral PNP devices12                                 | 23  |

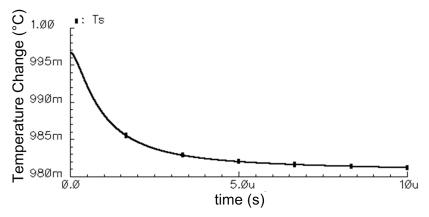

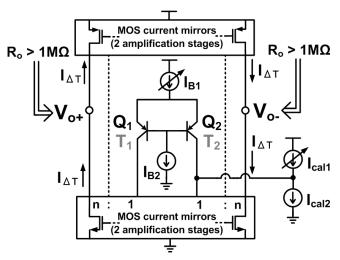

| 9. Proposed wide dynamic range differential temperature sensor                                       | 24  |

| 0. Simplified small-signal equivalent circuit of the sensor core                                     | 26  |

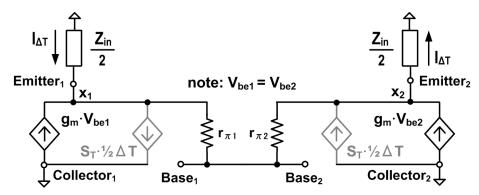

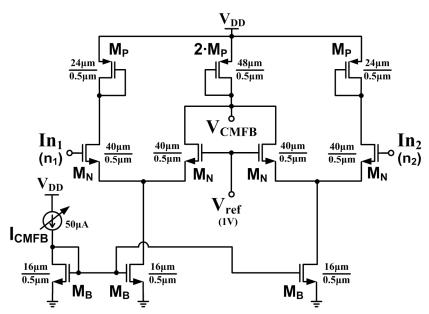

| Simulated sensor sensitivity ( $\Delta I_{stl}/\Delta T$ ) vs. gain ( $A_v$ ) for amplifier $A_1$ 12 | 27  |

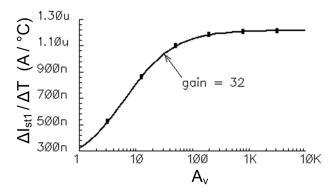

| 2. Amplifier $(A_1)$ schematic with annotated width/length dimensions                                | 28  |

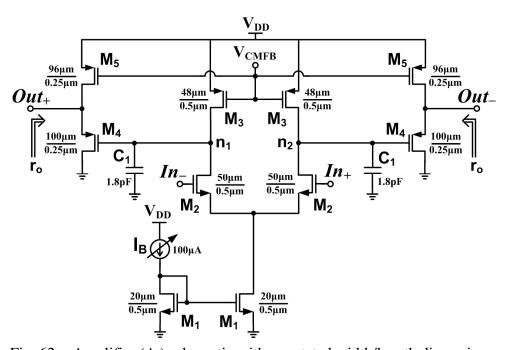

| 3. Common-mode feedback (CMFB) circuit schematic                                                     | 29  |

|          | Page                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------|

| Fig. 64. | Simulated dynamic range of the sensor core                                                               |

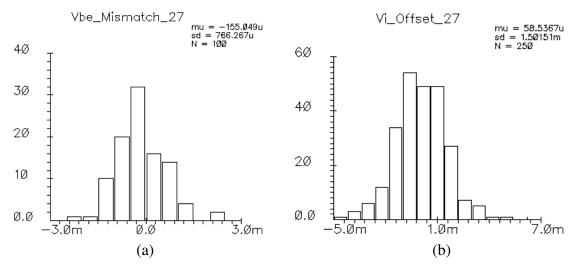

| Fig. 65. | Assessment of offsets in the sensor core with Monte Carlo simulations131                                 |

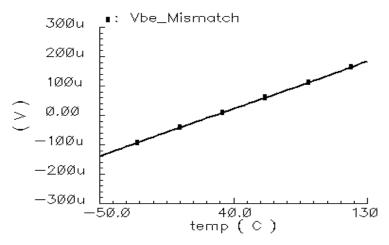

| Fig. 66. | Simulated $V_{be}$ mismatch of $Q_1/Q_2$ vs. ambient temperature                                         |

| Fig. 67. | Combined CUT and sensor simulation                                                                       |

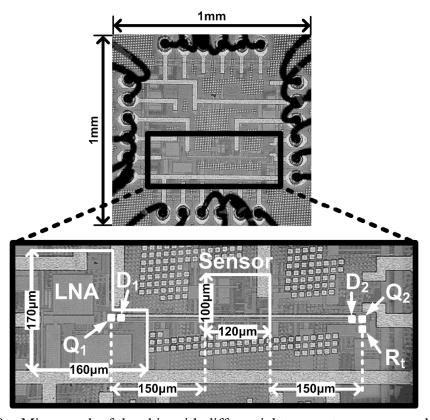

| Fig. 68. | Micrograph of the chip with differential temperature sensor and LNA 135                                  |

| Fig. 69. | Sensor output vs. power dissipation at resistor R <sub>t</sub>                                           |

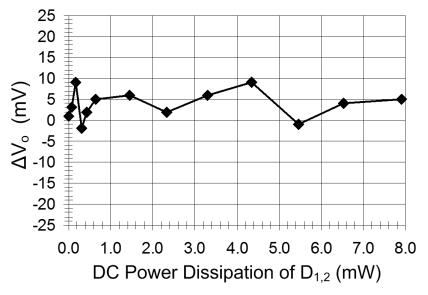

| Fig. 70. | Sensor output vs. power of diode-connected MOS transistors D <sub>1,2</sub> 137                          |

| Fig. 71. | Sensitivity control to power in R <sub>t</sub> and D <sub>1,2</sub> via I <sub>core</sub> adjustments138 |

| Fig. 72. | Common-mode sensitivity of the temperature sensor                                                        |

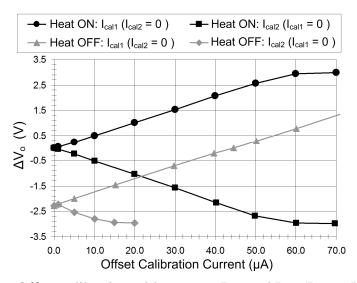

| Fig. 73. | Offset calibration with currents $I_{cal1}$ and $I_{cal2}$ ( $I_{core} = 500 \mu A$ )                    |

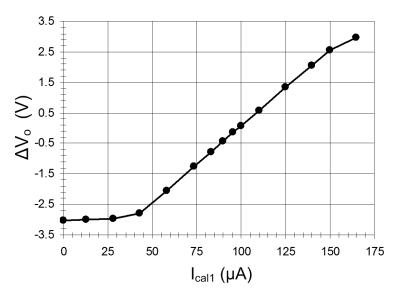

| Fig. 74. | Offset calibration range with $I_{cal1}$ ( $I_{cal2} = 0$ , $I_{core} = 500\mu A$ )                      |

| Fig. 75. | Measurement vs. simulation comparison for the CUT characterization143                                    |

| Fig. 76. | LNA output power and log-magnitude of the sensor output voltage144                                       |

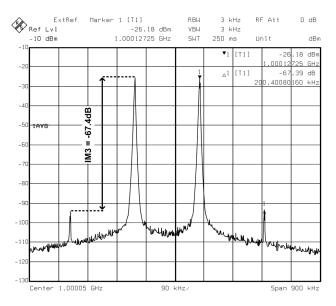

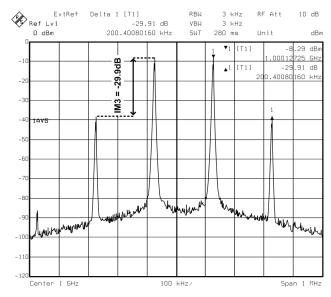

| Fig. 77. | The CUT's output spectrum from a two-tone test around 1GHz (case 1)145                                   |

| Fig. 78. | The CUT's output spectrum from a two-tone test around 1GHz (case 2)145                                   |

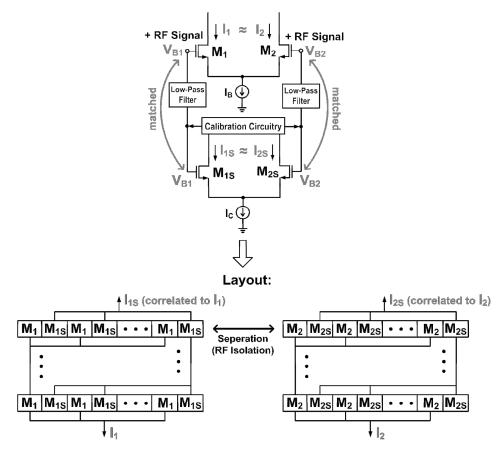

| Fig. 79. | An unmatched RF transistor pair                                                                          |

| Fig. 80. | An RF transistor pair with DC mismatch reduction loop                                                    |

| Fig. 81. | Differential amplifier with transistor mismatch reduction loop152                                        |

| Fig. 82. | Operational transconductance amplifier (A) in the calibration loop152                                    |

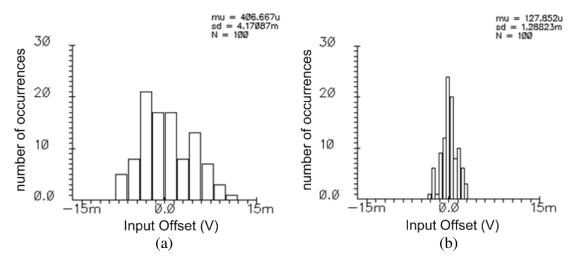

| Fig. 83. | Monte Carlo simulation results (100 runs at 30°C)                                                        |

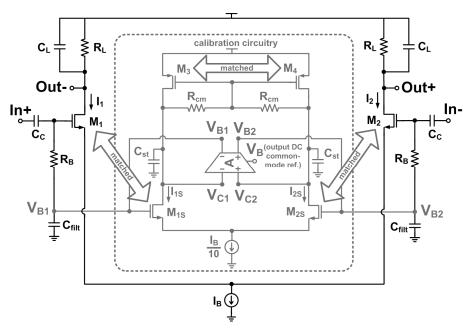

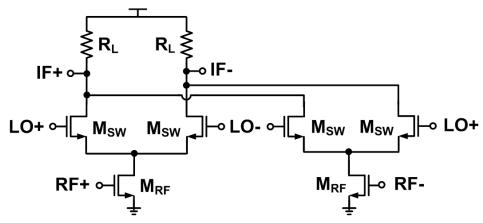

| Fig 84   | Double-balanced mixer 158                                                                                |

|           |                                                                                | Page |

|-----------|--------------------------------------------------------------------------------|------|

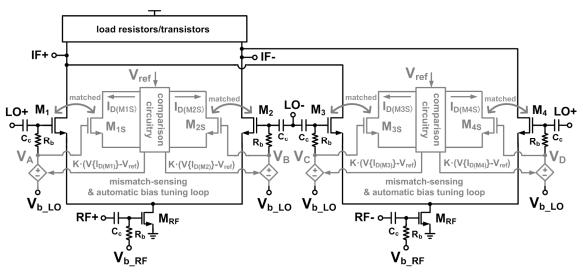

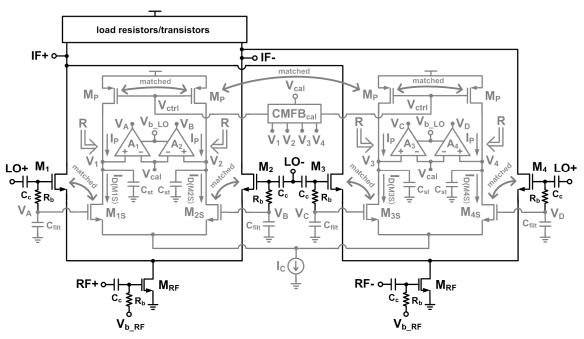

| Fig. 85.  | Mixer with conceptual mismatch reduction for the LO transistors                | 164  |

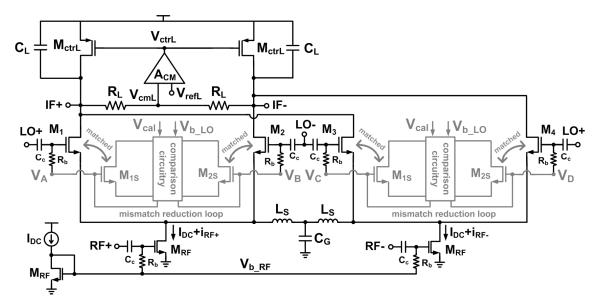

| Fig. 86.  | Mixer with calibration loop components.                                        | 166  |

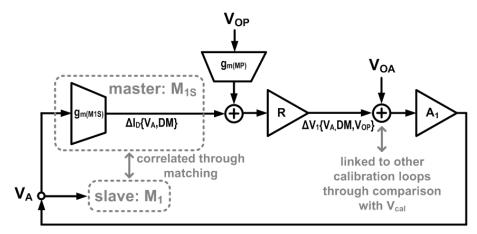

| Fig. 87.  | DC signal flow diagram for one calibration loop with offsets                   | 167  |

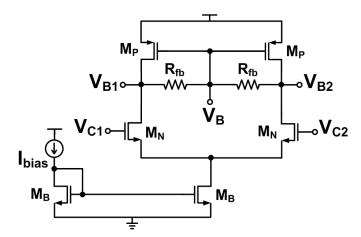

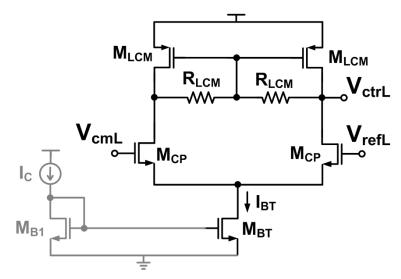

| Fig. 88.  | Common-mode feedback circuit for the main calibration loop                     | 169  |

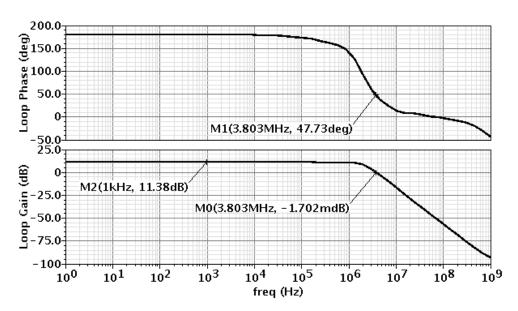

| Fig. 89.  | Frequency response of the main CMFB circuit.                                   | 170  |

| Fig. 90.  | Schematic of amplifiers A <sub>1</sub> -A <sub>4</sub> in the calibration loop | 171  |

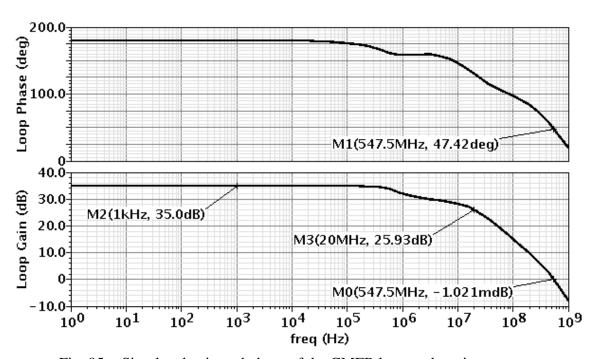

| Fig. 91.  | Frequency response of the amplifiers in the calibration loop                   | 172  |

| Fig. 92.  | Open-loop frequency response of the calibration circuit                        | 174  |

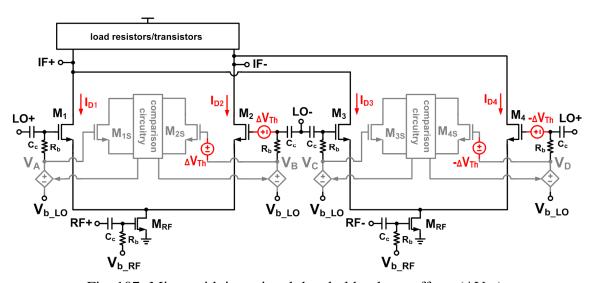

| Fig. 93.  | Detailed double-balanced mixer schematic.                                      | 177  |

| Fig. 94.  | Common-mode feedback amplifier at the mixer output                             | 178  |

| Fig. 95.  | Simulated gain and phase of the CMFB loop at the mixer output                  | 178  |

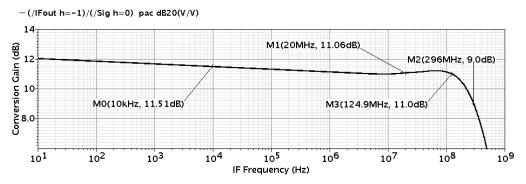

| Fig. 96.  | Conversion gain vs. frequency                                                  | 180  |

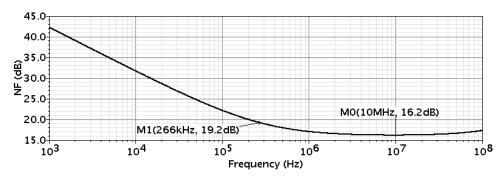

| Fig. 97.  | SSB noise figure vs. frequency.                                                | 181  |

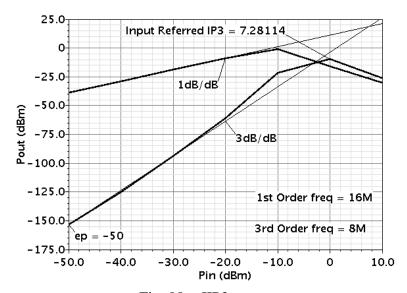

| Fig. 98.  | IIP3 curve.                                                                    | 181  |

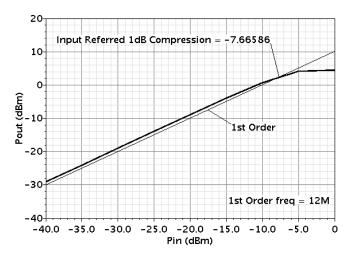

| Fig. 99.  | 1-dB compression curve.                                                        | 182  |

| Fig. 100. | IIP2 curve with $0.5\%$ mismatch between the load resistors ( $R_L$ )          | 182  |

| Fig. 101. | Feedthrough between mixer ports.                                               | 183  |

| Fig. 102. | Transient simulation with a 20MHz IF output signal                             | 184  |

| Fig. 103. | Conversion gain vs. LO signal power.                                           | 185  |

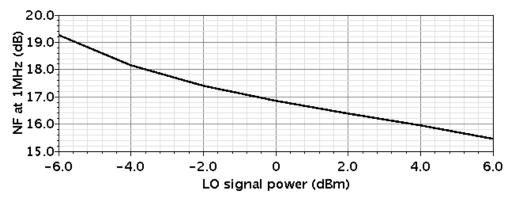

| Fig. 104. | SSB Noise figure at IF = 1MHz vs. LO signal power                              | 185  |

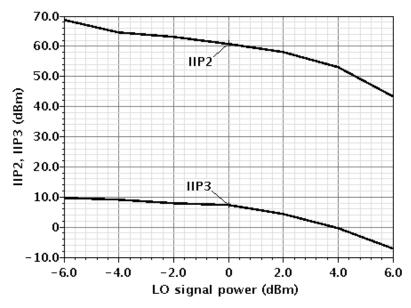

| Fig. 105. | IIP2 (with 0.5% R <sub>I</sub> mismatch) and IIP3 vs. LO signal power          | 186  |

|           |                                                                                          | Page |

|-----------|------------------------------------------------------------------------------------------|------|

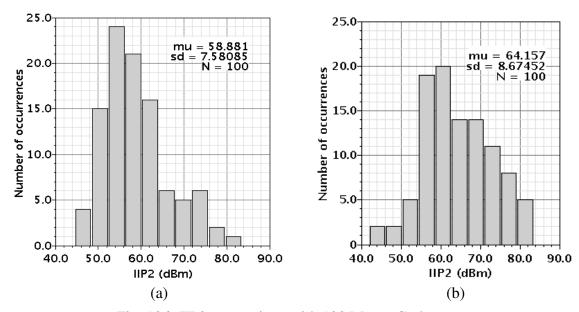

| Fig. 106. | IIP2 comparison with 100 Monte Carlo runs                                                | 188  |

| Fig. 107. | Mixer with intentional threshold voltage offsets ( $\Delta V_{Th}$ )                     | 189  |

| Fig. 108. | $\overline{\Delta I_{D}}$ (average mismatch of $I_{D1}$ - $I_{D4}$ ) vs. $\Delta V_{Th}$ | 190  |

| Fig. 109. | Transient settling behavior of critical control voltages                                 | 191  |

| Fig. 110. | Transient IF output after settling of the calibration control voltages                   | 191  |

| Fig. 111. | Conversion gain comparison with 100 Monte Carlo runs.                                    | 192  |

| Fig. 112. | IIP3 comparison with 100 Monte Carlo runs                                                | 193  |

| Fig. 113. | Comparison of the SSB NF at 1MHz with 100 Monte Carlo runs                               | 193  |

| Fig. 114. | Nonlinear model for differential attenuation-predistortion cancellation.                 | 217  |

| Fig. 115. | OTA model with additional nonidealities                                                  | 222  |

| Fig. 116. | Single-ended equivalent block diagram of a bandpass biquad                               | 224  |

| Fig. 117. | Single-ended diagram of a bandpass biquad with phase compensation.                       | 227  |

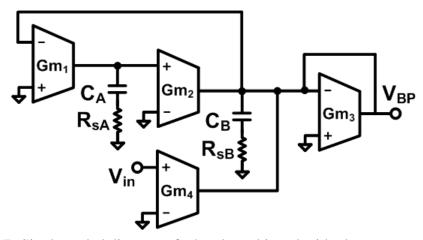

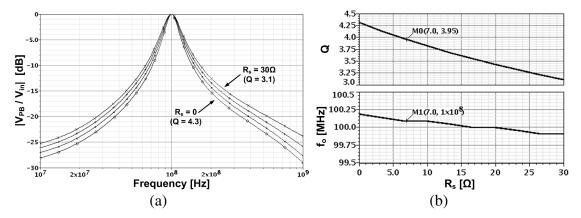

| Fig. 118. | BP filter simulations with different R <sub>s</sub> values for phase compensation        | 228  |

# LIST OF TABLES

|             | Page                                                                    |

|-------------|-------------------------------------------------------------------------|

| Table I.    | Intra-die variability (with min. dimensions) vs. CMOS technology node12 |

| Table II.   | Comparison of transceiver built-in testing and calibration techniques33 |

| Table III.  | Measured main parameters of the reference folded-cascode OTA57          |

| Table IV.   | Comparison of OTA linearity and noise measurements61                    |

| Table V.    | OTA comparison with prior works                                         |

| Table VI.   | Comparison of wideband G <sub>m</sub> -C lowpass filters67              |

| Table VII.  | Component parameters in the quantizer core (Fig. 38)101                 |

| Table VIII. | Key quantizer performance parameters                                    |

| Table IX.   | Measured $\Sigma\Delta$ ADC performance                                 |

| Table X.    | Comparison with previously reported lowpass $\Sigma\Delta$ ADCs106      |

| Table XI.   | CUT design parameters and simulation results                            |

| Table XII.  | Simulated amplifier (A <sub>1</sub> ) specifications                    |

| Table XIII. | Measured CUT* performance parameters                                    |

| Table XIV.  | Differential amplifier and calibration loop components                  |

| Table XV.   | Calibration circuitry components                                        |

| Table XVI.  | Subthreshold mixer components                                           |

| Table XVII. | Simulated mixer specifications with and without calibration187          |

| Table XVIII | I. Down-conversion mixer performance comparison                         |

| Table XIX.  | Simulated comparison: OTA linearization without power increase230       |

### I. INTRODUCTION

## I.1. Background and Motivation

As rapid progress encompasses the integration of voice, video, and internet connectivity functions into small low-power integrated circuits, portable wireless devices continue to become more prevalent in our lives to the point that many vital situations depend on the reliable operation of the integrated circuits. Consequently, there is an increasing incentive to incorporate self-test and correction features for improved reliability of wireless devices, especially in medical and military applications in which life-saving information is transmitted and received. Even though new technologies allow the design of smaller chips with more functionality, manufacturing process variability and post-production aging effects pose growing challenges for the design, fabrication, and reliability of single-chip mixed-signal systems that are realized with complementary metal-oxide-semiconductor (CMOS) technology in the modern nanometer regime. Consequently, many current research efforts are concentrated on the development of more robust analog and mixed-signal circuits by devising built-in test methodologies that enable digitally-assisted performance tuning.

On the analog circuit level, rising parameter variability is a fundamental contributor to yield and reliability problems. As a result, designing for optimum performance specifications alone is not sufficient anymore. In parallel, it has become critical to improve the on-chip measurement and self-calibration capabilities as well as the

This dissertation follows the style and format of the IEEE Journal of Solid-State Circuits.

testability of single-chip systems during high volume production testing, all in order to increase product yields and to lower the cost of testing. Both yield and cost improvement have been identified as needs in the International Technology Roadmap for Semiconductors [1], giving the incentive for novel built-in test features and alternative test strategies. Additionally, progressive on-chip self-calibration of wireless devices will help to enhance their reliability and allow full utilization of future CMOS technologies with smaller feature sizes despite of increased parameter variations.

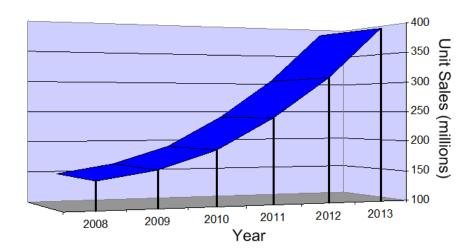

Fig. 1. Smartphone market trend.

Due to high manufacturing volumes, consumer products are a key driving force behind the development of highly integrated chips for wireless communication. For example, the projected global sales of Smartphones is plotted in Fig. 1, which is based on the data provided in [2]. The push towards mobile internet and multimedia features has led to ongoing efforts to incorporate additional functionality. At the same time,

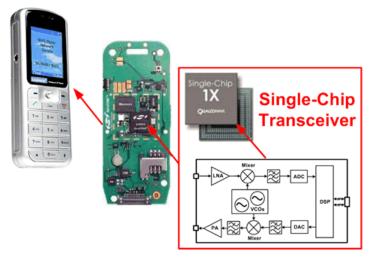

single-chip transceivers have emerged to perform the analog signal reception and transmission operations, as well as much digital signal processing on the same chip as possible. This approach has allowed to reduce product dimensions and production cost. Nowadays, cell phones have fewer chips on the printed circuit board (Fig. 2), but the complexity of those chips causes significant design complications. In the case of integrated transceivers, the demand to support multiple communication standards has created design issues related to more stringent linearity requirements for the broadband radio frequency (RF) front-end circuits, reconfigurability of many blocks along the transmit/receive chains, interference avoidance among circuits, minimization of total power consumption, and other aspects. Within the scope this dissertation is that RF system performance monitoring is becoming significantly more important and difficult with the trend towards increasing integration and power densities in single-chip systems fabricated with modern CMOS technologies. On-chip electrical power detectors are commonly used to monitor and optimize the dynamic range of RF systems through measurements and controlled amplifications in RF front-ends. However, the adverse effects from parasitic input capacitances of electrical detectors become more detrimental at higher frequencies. Non-invasive temperature sensors for RF power detection offer an attractive alternative to conventional power detectors, as shown by the investigations presented in this dissertation.

Fig. 2. Single-chip transceiver in a cell phone.

# I.2. Research Focus and Dissertation Organization

Contemporary CMOS technologies have offered progress with respect to circuit properties such as smaller device dimensions, better high-frequency operation, and power efficiency. But, analog designers in particular face various technology-related drawbacks associated with newer technologies, for example signal swing limitations due to decreased supply voltage and gain reduction due to lower transistor output resistance. Other major disadvantages, which are elaborated in Section II, are worsening process variations and intra-die device mismatches. These have a strong impact on the product yield and reliability, translating into manufacturing cost and risk factors in critical medical or military applications. Variations and circuit sensitivity to environmental conditions such as temperature changes and interference from other nearby circuits are becoming more problematic as the complexity of integrated systems increases. In this dissertation, special attention is given to augmentations of analog and mixed-signal

circuits in response to the emerging variability problems and system-level calibration approaches concerning current and future CMOS technologies.

An intricate issue is the high number of possible failure causes for analog circuits as a result of the random nature of process variation, ambient temperature changes, and interference signals. Typically, it is insufficient to monitor a single quantity and extract the necessary information to determine the severity of faults or the actions to be taken for their correction. For instance, measurement of an RF circuit's quiescent current can be helpful to identify gross defects, but has very limited usefulness when the goal is to tune RF metrics such as gain or linearity parameters. This creates a need for continuous expansion of on-chip measurement capabilities, especially because the acceptability of an analog circuit's performance normally depends on many parameters that can take on a continuous range of values. Moreover, the integration of more functionality and transistors into integrated systems leads to higher power densities on the chips, which leads to more pronounced temperature gradients and interference between circuits due to thermal coupling. A temperature sensing strategy is introduced in Section V to provide alternative means for on-chip measurements of RF characteristics and to increase the observability of temperature gradients. The section also contains descriptions of the proposed temperature sensor topology for built-in testing of analog circuits and the simulation methodology for its design.

A digital circuit whose functionality has been verified during the characterization test phase will predominantly be affected by process variation of the transition frequency and threshold voltage, which will have main effects on the maximum speed of operation and power consumption. This eases the determination of performance limits for digital circuits by verifying their logic outputs or the output of test structures at the mandated speed. As alternative for test cost reductions or performance optimizations, local process monitors can be embedded in the layout design to measure the transition frequency or threshold voltages (as representatives for areas of a partitioned die), and to compensate for variations by adjusting nearby digital circuits through features such as adaptive body bias or supply voltage. Such systematic approaches have become increasingly popular to deal with variability in digital circuits, but they are less effective for analog circuits because their performance depends on more parameters and each analog block has a different dependence on a given parameter. For that reason, the design strategies for robust analog circuits tend to be tailored to the circuit type or even its specific topology.

The approach taken in this dissertation is to present examples of circuits and their features that alleviate the effects of process variations. With adaptations, the presented methodologies can be extended to similar analog circuits. In particular, the use of digitally programmable circuit elements or bias conditions will be emphasized and related to the compatibility of individual blocks with emerging system-level self-calibration strategies. The first example to be discussed in Section III is the linearization of transconductance amplifiers in broadband filter applications. Section IV describes another case study, which is a 3-bit quantizer that was designed for continuous-time  $\Sigma\Delta$  analog-to-digital converters. Section V introduces a strategy to utilize differential temperature sensors as on-chip RF power detectors for built-in testing. Next, a general technique to reduce the mismatch between transistors is proposed in Section VI, in

which it is applied to differential pair transistors of a wide bandwidth amplifier and the switching transistors of a double-balanced mixer. To finish, Section VII summarizes the contributions of this work. The following subsections give a more detailed overview of the focal points in this dissertation.

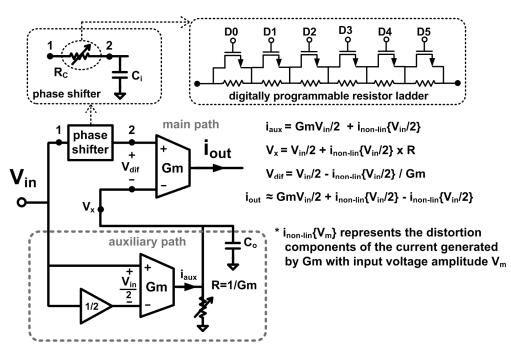

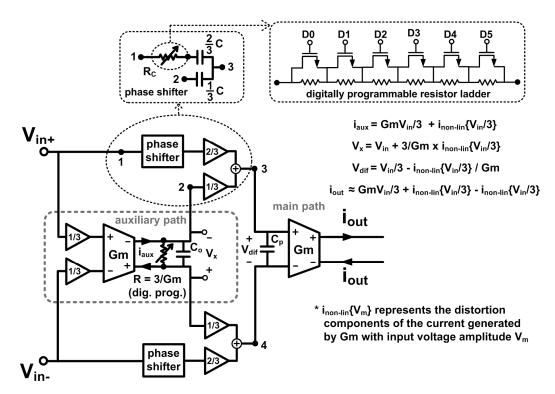

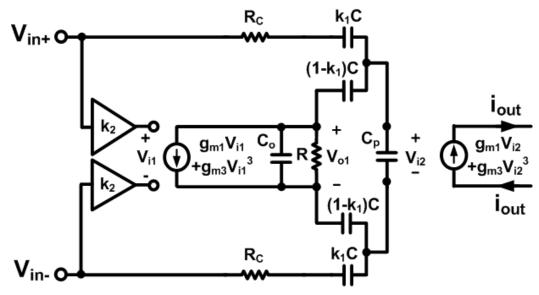

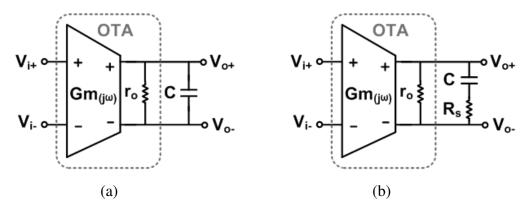

# I.2.1. Linearization scheme for transconductance amplifiers

Operational transconductance amplifiers (OTAs) are elements of transconductance-capacitor ( $G_m$ -C) filters in many wireless receivers and continuous-time  $\Sigma\Delta$  analog-to-digital converters. Thus, OTA performance and dependability improvements manifest themselves in system-level enhancements of communication circuits and sensor signal conditioning circuits. The push towards wider bandwidths in these applications mandates OTA designs with progressively better linearity at higher frequencies. Towards this end, an architectural solution is presented in Section III that can be applied to diverse circuit-level OTA configurations. Effective linearization over a wide frequency range demands a mechanism to correct for high-frequency effects and process variations. Accordingly, digital programmability was realized to ensure high linearity and compatibility with modern CMOS technologies.

The linearization technique utilizes two matched OTAs to cancel output harmonic distortion components, creating a robust architecture. Compensation for process variations and frequency-dependent distortion based on Volterra series analysis is achieved by employing a delay equalization scheme with on-chip programmable resistors. An OTA design with the proposed broadband linearization method has third-order inter-modulation (IM3) distortion better than -74dB up to 350MHz with  $0.2V_{p-p}$

input, 70dB signal-to-noise ratio (SNR) in 1MHz bandwidth, and 5.2mW power consumption. The distortion-cancellation technique enables an IM3 improvement of up to 22dB compared to a commensurate OTA without linearization. A proof-of-concept lowpass filter with the linearized OTAs has a measured IM3 < -70dB and 54.5dB dynamic range over its 195MHz bandwidth. The standalone OTAs and the filter were fabricated on a 0.13 $\mu$ m CMOS test chip with 1.2V supply.

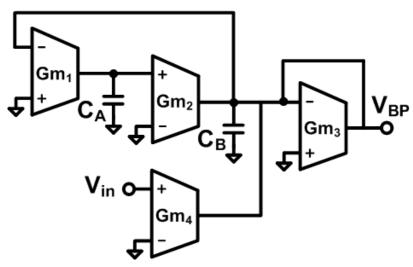

## *I.2.2. Process variation-aware quantization*

Future wireless devices will require extensive connectivity to accommodate several services, which means that the receivers must cover broader frequency bands. Therefore, on-chip analog-to-digital converters (ADCs) in multi-standard receivers not only demand increased signal-to-quantization-noise-ratio, but also more bandwidth for the conversion of the analog signal into the digital domain. Our research group developed a lowpass continuous-time  $\Sigma\Delta$  ADC for next generation broadband receiver applications using a 0.18µm CMOS process. Rather than using multiple signal levels, a multi-bit digital-to-analog converter (DAC) realization based on a feedback signal with timevarying pulse duration was employed. This approach alleviates nonlinearity problems associated with typical multi-bit DACs. Section IV of this dissertation describes the corresponding 3-bit quantizer architecture with multi-phase clocking. The reference levels for the quantizer are adjustable to compensate for process variations after fabrication if the application necessitates fine resolution. Designed with 5mV resolution at a 400MHz sampling frequency, the quantizer power dissipation is 24mW and its die area with auxiliary logic circuitry and routing is 0.4mm<sup>2</sup>. With embedded quantizer, the  $5^{th}$ -order  $\Sigma\Delta$  ADC achieves a measured peak SNDR of 67.7dB in 25MHz bandwidth, consumes a total of 48mW with a 1.8V supply, and occupies 2.6mm<sup>2</sup> die area.

# I.2.3. Non-invasive on-chip measurement of thermal gradients and RF power

One aspect of designing robust analog and mixed-signal circuits in wireless products is the inclusion of on-chip monitors that can determine whether device performance parameters are within an acceptable range or whether a detrimental shift has occurred due to effects from aging, temperature variations, interfering signals, or other conditions. This information can then be incorporated into self-calibration schemes that tune circuit blocks to restore satisfactory functionality. A part of this dissertation work is directed towards the conception of a practical monitoring strategy employing differential temperature sensors with high sensitivity and accuracy for measuring on-chip temperature gradients over the range of interest. Due to thermal coupling, the temperature in the vicinity of a device depends on its power dissipation, and this relation can be exploited for testing purposes [3].

In Section V, a design methodology is presented which aims at the extraction of RF circuit performance characteristics from the DC output of an on-chip temperature sensor. Any RF input signal can be applied to excite the circuit under examination because only dissipated power levels are measured, which makes this approach attractive for online thermal monitoring and built-in test scenarios. A fully-differential sensor topology is introduced that has been specifically designed for the proposed method by constructing it with a wide dynamic range, programmable sensitivity to DC and RF power dissipation, as well as compatibility with CMOS technology. Furthermore, a procedure

is outlined to model the local electro-thermal coupling between heat sources and the sensor, which is used to define the temperature sensor's specifications as well as to predict the thermal signature of the circuit under test.

A prototype chip with an RF amplifier and temperature sensor was fabricated in a conventional 0.18 $\mu$ m CMOS technology. The proposed concepts were validated by correlating RF measurements at 1GHz with the measured DC voltage output of the onchip sensor and the simulation results, demonstrating that the RF power dissipation can be monitored and the 1-dB compression point can be estimated with less than 1dB error. The sensor circuitry occupies a die area of 0.012mm², which can be shared when several on-chip locations are observed by placement of multiple 11 $\mu$ m × 11 $\mu$ m temperature-sensing devices.

## *I.2.4.* Analog calibration for transistor mismatch reduction

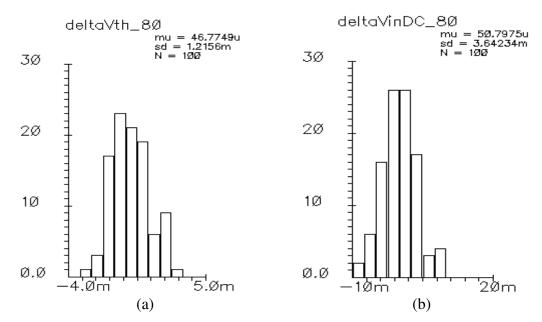

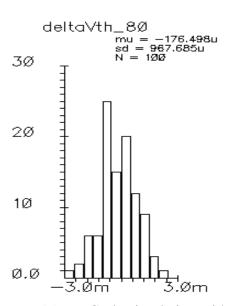

An analog calibration technique is presented to lessen the mismatch between transistors in the differential high-frequency signal path of analog CMOS circuits. It can be applied for offset reduction in high-speed amplifiers and comparators in which short-channel devices are utilized to minimize bandwidth reduction from parasitic capacitances. In general, this approach is suitable for RF applications in which direct matching of the transistors is undesired because sophisticated layout practices would increase the coupling between the high-frequency paths. The proposed methodology involves auxiliary devices that sense the existing mismatch as part of a feedback loop for error minimization. This technique is demonstrated in Section VI with a differential amplifier having a loaded gain and -3dB frequency of 13dB and 2.14GHz. It was

designed in 90nm CMOS technology with a 1.2V supply. Monte Carlo simulations indicate that the 4.17mV standard deviation of the amplifier's anticipated input-referred offset voltage improves to 0.76mV-1.29mV with the mismatch reduction loop, which is contingent on the layout configuration of the mismatch-sensing transistors.

Section VI also provides a second application example for the analog mismatch reduction loop, which is to enhance the matching between the switching transistors in a double-balanced CMOS mixer. Simulation results show that this scheme improves the mixer's IIP2 by 5dB while having negligible impact on other performance parameters with the exception of 30% higher power due to the dissipation in the calibration circuitry. The calibration method helps to compensate for the large process variations of the mixer transistors that are biased with small currents in the subthreshold region. As a result, the power consumption of the presented mixer is still more than six times lower than that of conventional down-conversion mixers using saturation region bias, whereas its specifications are similar to the state of the art.

### II. PROCESS VARIATION CHALLENGES AND SOLUTIONS APPROACHES

## **II.1. Current Trends**

# II.1.1. The impact of rising process variations

Most semiconductor product improvements over the past decades are direct or indirect consequences of the perpetual shrinking of devices and circuits, allowing performance enhancements at lower fabrication cost. A paralleling trend is that process variations and intra-die variability increase with each technology node. Since most highperformance analog circuits depend on matched devices and differential signal paths, this trend has begun to diminish yields and reliabilities of chip designs. Fundamentally, the problem is that parameters of devices on the same die show increasing intra-die variations, thereby exhibiting different characteristics. For example, Table I displays the evolution of the typical transistor threshold voltage standard deviation  $\sigma\{V_{Th}\}$ normalized by the threshold voltage (V<sub>Th</sub>) for several technologies, as reported in [4]. Also notice that V<sub>Th</sub> exhibits further dependence on gate length variations through the drain-induced-barrier-lowering (DIBL) effect under large drain-source voltage bias conditions, as demonstrated by the characterization in [5] using 65nm technology. Since DIBL worsens as the channel is scaled down, this additional impact on V<sub>Th</sub> variations can be assumed to be even stronger beyond the 65nm technology node.

Table I. Intra-die variability (with min. dimensions) vs. CMOS technology node

| Technology Node            | 250nm | 180nm | 130nm | 90nm | 65nm  | 45nm |

|----------------------------|-------|-------|-------|------|-------|------|

| $\sigma \{V_{Th}\}/V_{Th}$ | 4.7%  | 5.8%  | 8.2%  | 9.3% | 10.7% | 16%  |

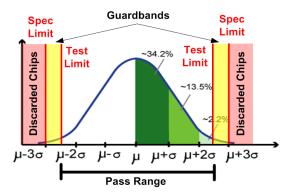

A direct consequence of device parameter variations is a decrease in production yields because block-level and system-level parameters will show a corresponding increase in variations. This relationship between variations and yield can be inferred from the visualization in Fig. 3, where the Gaussian distribution of a specification with a standard deviation  $\sigma$  around the mean value  $\mu$  is shown together with the specification limits ( $\pm 3\sigma$  in this example). For standalone analog circuits, parameters such as gain may have an upper and/or lower specification limit, and the samples that exceed the limit(s) during production testing must be discarded. Guardbands are often defined to account for measurement uncertainties by following procedures such as repeating the same test or performing other more comprehensive tests to determine whether the part can be sold to customers, which incurs additional test cost in a manufacturing environment.

Fig. 3. Specification variation impact on the fraction of discarded chips.

An important observation from Fig. 3 is that an increase of variation  $(\sigma)$  widens the Gaussian distribution, which leads to a higher percentage of parts that fall within the highlighted ranges that require them to be scrapped or retested. Clearly, there is a direct

relationship between the amount of process variations and production cost due to low yields. In the case of wireless mixed-signal integrated systems, the trend towards increasing integration and complexity has also been paralleled by technical challenges and rising cost of testing, which can amount up to 40-50% of the total manufacturing cost [6], [7]. As a consequence, built-in self-test, design-for-test, and design-formanufacturability methods for analog and mixed-signal circuits have received growing attention over the past years.

## *II.1.2. Circuit and system design tendencies*

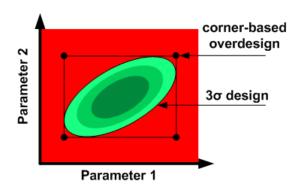

System complexities and process variations raise the importance of considering testability early in the design phase to avoid technical complications and time-to-market delays in the pre-production phase as well as test cost reduction during the production phase. Worst-case process corner models have been used extensively to account for variations during the design of analog circuits. But more recently, a paradigm shift towards the use of statistical models and Monte Carlo simulations has occurred. One of the main reasons for this development is that corner-based design easily results in too pessimistic designs [8], which is evident in Fig. 4. In this figure, the x-axis and y-axis represent the ranges over which two parameters can vary, and the area inside the ellipse indicates the combined range in which the  $3\sigma$  limits are met. This region can be predicted with statistical Monte Carlo simulations for yield estimation. On the other hand, the area outside of the elliptical design space corresponds to design implementations that meet the specifications, but are overdesigned. This means that "investments" of area, power, or trade-offs with other parameters are made in order to

allow acceptable performance despite of increased deviations of the two parameters from their nominal values. The rectangular region between the combination of the four worst corner cases of the two parameters includes overdesign space, implying that it involves costly performance or parameter trade-offs. This economic reason and the availability of more efficient computational tools have created a trend towards statistical yield optimizations rather than corner-based design [8].

Fig. 4. Process corner-based vs. 3σ design approaches.

Defect densities on wafers become worse in newer technologies and production yields decrease with increased chip size [9]. Self-test and self-repair schemes for digital circuits have been routinely incorporated into products for a long time, especially since on-chip verification of logic blocks and repair with redundant circuitry do not require analog instrumentation resources. The inclusion of scan chains gives easy access to internal digital circuitry through a minimal number of pins during production testing. Similarly, the standardized mixed-signal test bus (IEEE Std. 1149.4) has been developed to improve the testability of analog blocks by allowing better observation of internal

nodes. Nowadays, the use of analog test buses within single-chip systems is feasible in the industry, but significant design considerations are required to avoid that the interface circuitry does not affect the integrity of the analog signals or measurements [10].

In addition to the underlying variation and defect issues on the device level, several system-level and technology trends impair the testability and manufacturability of integrated circuits for mobile applications:

# Support of multiple communication standards and more features on low-power chips

The wireless communication industry has experienced phenomenal growth in the past decade that resulted in low-power handheld devices with multi-purpose functionality such as video, voice, pictures, and internet access. The wireless local-area networks for laptops, desktops, and personal digital assistants (PDAs) include standards like Bluetooth, WiFi, IEEE 802.16, WiMAX, Ultra-Wideband (UWB), and GPS. Most relevant services for handheld devices range from 470 MHz to almost 11GHz. The main technical challenge is the co-existence of wireless devices, which results in signal interference. This can be solved if more linear high-performance analog receiver frontends are available to tolerate and filter out high-power interfering signals without saturation of the analog blocks due to excessive signal power levels. Further filtering and channel selection can be performed in the digital domain when the signal integrity is maintained by the processing through unsaturated highly-linear analog blocks. Support of multiple communication standards requires chips with more circuitry and complexity, which makes them less testable in the production stage because of limited access to internal nodes, interactions between blocks, and a higher number of test cases to verify functionality. Systems with more channels are more likely to fail, which is another reason why yields of integrated receivers, transmitters, and transceivers are on the decline. Simultaneously, the processing of broadband signals in their front-ends mandates high-performance analog circuits, which in many cases requires continued circuit-level innovations for on-chip self-calibration to tune for optimum performance.

# Process technology optimizations for digital circuits create analog design challenges

The main advantages of device scaling with CMOS technology are improved performance at higher frequencies, reduced power consumption, and increased levels of integration. Those benefits are particularly aiding the development of digital circuits and systems. With regards to analog circuits, deep-submicron technology scaling progress comes together with adverse effects such as reduced gains from lower transistor output impedances, design with limited voltage headroom, higher flicker noise levels, and reduced transistor linearity. Larger variability of parameters is caused by physical and fabrication limitations such as under-etching uncertainties, variations of effective transistor dimensions, severe channel length modulation due to higher electric fields, and channel dopant fluctuations. Interestingly, the random dopant fluctuations have reached a severity that can lead to threshold voltage mismatch in neighboring devices at the 65nm node [11]. Additional reliability concerns arise from the restricted power that transistors can supply to the load without exceeding the low breakdown voltage of the deep submicron devices. Furthermore, digital CMOS processes often do not provide high-quality passive devices required for conventional high-performance analog designs. For example, metal-insulator-metal (MIM) capacitors, high-resistivity polysilicon resistors, or well-characterized inductor models might not be available in a digital process, forcing analog designers to get by with metal-oxide-semiconductor (MOS) capacitors and standard polysilicon resistors. Both of these have higher parasitic capacitance to the substrate than the equal-valued MIM capacitors or high-resistivity polysilicon resistors. Scaling down transistors permits more digital functionality and memory on a single chip, but with less reliability especially for analog signal processing.

## II.2. A System Perspective on Transceiver Built-In Testing and Self-Calibration

The concepts and examples presented in this dissertation are all involving circuit blocks which are found in conventional transceivers within mobile wireless devices. While equipping the circuit blocks with built-in test (BIT) and self-calibration features to compensate for variations, it is important to keep their role as part of the system in mind because of the interaction between blocks and the overall goal to optimize system-level performance specifications such as bit error rate (BER) or error vector magnitude (EVM). In general, the self-calibration challenge can be divided into two parts: one is to add tunability and controllability capabilities in the individual blocks, and the other one is to devise comprehensive system-level calibration algorithms in a digital signal processing unit. The former task is the focus of this dissertation, but the existing approaches for the latter task will be briefly discussed in the remainder of this section and when applicable throughout the dissertation.

BIT strategies for transceivers vary tremendously depending on the transceiver architecture, communication standard, available on-chip measurement and computation resources, the production volume, and whether the BIT is designed for production

testing (quality control) or on-line self-calibration (reliability) during the life time of the chip. Consequently, most BITs involve a mix of analog and digital blocks, on-chip and off-chip measurement devices, long calibration routines at start-up, and shorter periodic or on-line calibration. Generally, a trend has emerged to combine techniques for verification of complex mixed-signal transceivers implemented as single chips. Nevertheless, the BIT approaches can be grouped into a few rough high-level categories that represent the different design philosophies in academia and the industry. In the following overview, a few example cases will be discussed to highlight the distinctive characteristics of methods that can be broadly classified into these categories:

- Digital correction and calibration

- Analog measurements and tuning

- Loopback testing

- Combined digital performance monitoring and analog compensation

- Combined digital monitoring, analog measurements, and analog compensation

## II.2.1. Digital correction and calibration

Digital BIT approaches involve measurements and compensation techniques that are realized in the digital baseband processor of the transceiver. They are suitable for parameters that are observable and traceable in the digital domain, such as slowly drifting DC offsets or mismatch between the in-phase (I) and quadrature-phase (Q) paths in the front-end. Generally, digital methods have the advantage of high precision when sufficient computational resources are available. They are also very attractive for on-line calibration schemes that run in the background.

Digital I/Q mismatch compensation is a widely used method that involves digital measurement and compensation of the I/Q gain and phase mismatches in the analog front-end circuitry. For example, the work in [12] presents a scheme that runs during start-up or in a dedicated calibration mode to ensure acceptable performance of a low-IF receiver even with up to 10% gain and 10° phase imbalance in the analog front-end. Online digital I/Q compensation techniques have also been reported, such as [13], in which the training symbols that are standard in orthogonal frequency-division multiplexing (OFDM) transmissions are exploited for background I/Q calibration. It was also demonstrated in [13] how digital I/Q compensation relaxes the overall signal-to-noise ratio (SNR) requirements in the receiver chain because I/Q imbalance directly affects the SNR and thereby degrades the bit error rate (BER). In the OFDM receiver example presented in [13], the digital calibration allowed to improve the tolerance to I/Q imbalances from 1%-gain/1°-phase to 10%-gain/10°-phase.

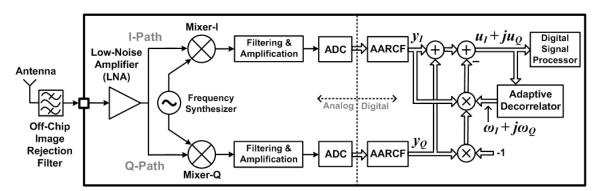

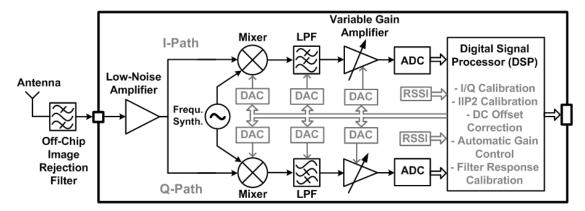

Fig. 5. Receiver with digital I/Q mismatch compensation ([14]).

Digital I/Q calibration is widely used in the industry. An example is the work from Texas Instruments describing a low-IF GSM receiver in 90nm CMOS technology [14]. This receiver utilizes an adaptive filter that obtains the mismatch information from online I/Q correlations, for which the modified block diagram from [14] is displayed in Fig. 5. The interesting part of the block diagram is the adaptive decorrelator after the analog-to-digital converter (ADC) and anti-aliasing rate change filter (AARCF). In the digital domain, gain mismatch appears as difference in the auto-correlation between I and Q paths, while phase mismatch appears as nonzero cross-correlation between I and Q. The authors use an algorithm that takes advantage of the aforementioned relationships by implementing an adaptive decorrelator which attempts to minimize the auto-correlation and the cross-correlation between I and Q outputs  $(y_I, y_Q)$ . This is done by adjusting the correction coefficients:

$$\omega_{I(n+1)} = \omega_{I(n)} + \mu \cdot [u_{I(n)} \cdot u_{I(n)} - u_{Q(n)} \cdot u_{Q(n)}] \text{ and } \omega_{Q(n+1)} = \omega_{Q(n)} + 2\mu \cdot u_{I(n)} \cdot u_{Q(n)}, \quad (1)$$

where  $\mu$  is the adaptation step size which is inversely proportional to the signal energy. Thus, periodic training sequences are required with this scheme. Depending on process-voltage-temperature (PVT) variations, 15-30dB image rejection ratio (IRR) improvement has been demonstrated in practice with phase mismatch < 1° and amplitude mismatch < 10% in [14] with a settling time in the range of 3-4 milliseconds. This settling time is lengthy compared to analog tuning approaches that can be as short as a few microseconds [15], which becomes important in production testing situations because any adjustments for different test conditions in the front-end (different gain settings, channel, etc.) would require 3-4ms idle time for digital I/Q calibration before

the BER test can begin. On the other hand, settling times of analog tuning schemes depend on the loop bandwidth, which can be designed in the megahertz range to achieve settling times in the microseconds regime. Hence, analog I/Q tuning approaches would fill the niche of situations that require fast convergence.

The incentive for using a digital BIT technique is high when the circuit under test itself has digital features. An example is the BIT of a transmitter in [16] that includes an all-digital phase-locked loop (ADPLL). In that case, the error signal of the ADPLL is already in the digital domain, allowing to monitor failures and the center frequency drift of the digitally controlled oscillator. Furthermore, the authors of [16] state that digital filtering and spectral estimation can be used to monitor and adjust the phase noise transfer function.

#### II.2.2. Analog measurements and tuning

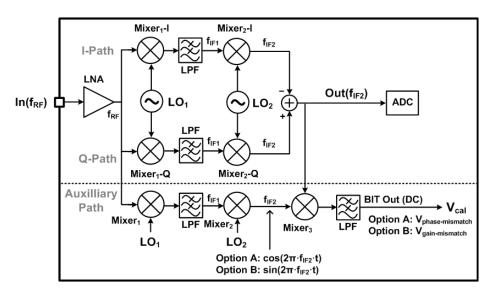

The analog equivalent to the digital I/Q imbalance calibration scheme has been proposed and demonstrated for image-reject receiver (IRRX) architectures [17]. A simplified block diagram of such a BIT is displayed in Fig. 6, which is representing the work from [17]. In an IRRX, the down-conversion scheme with two mixing stages and lowpass filters suppresses the image signal at the second intermediate frequency output  $Out(f_{IF2})$ , which avoids the need for an external image-rejection filter. The quality of the image-rejection is typically expressed with the image-rejection ratio (IRR) that depends on the I/Q amplitude mismatch ( $\Delta A$ ) and phase mismatch ( $\Delta \theta$ ):

$$IRR_{(dB)} \approx 10 \cdot \log \left( (1/4) \cdot \left[ (\Delta \theta)^2 + (\Delta A/A)^2 \right] \right). \tag{2}$$

In practice, the IRR is normally limited to 25dB-40dB due to mismatches, even though almost 60dB are required for acceptable BER performance. In [17], a purely analog calibration scheme was implemented with the auxiliary path shown in Fig. 6. This path contains the duplicate mixing operations as in the main path with the exception that the output signal at the second intermediate frequency ( $f_{IF2}$ ) can be of the form  $\cos(2\pi \cdot f_{IF2} \cdot t)$  or  $\sin(2\pi \cdot f_{IF2} \cdot t)$ , depending on which phases of the two local oscillators (LO<sub>1</sub>, LO<sub>2</sub>) are routed to the auxiliary mixers. Finally, mixer<sub>3</sub> correlates the signals from the two paths to extract the I/Q mismatch information contained in the DC component after the lowpass filter (LPF). This analog DC voltage ( $V_{cal}$ ) can be directly used to tune the bias voltages of analog circuits for mismatch compensation, resulting in high IRR (e.g. 57dB in [17]). A similar automatic IRR calibration with analog mixers, variable phase shifter, and gain tuning has been realized in [18], achieving an IRR of 59dB.

Fig. 6. Analog I/Q calibration for image-rejection receivers.

A benefit with local analog tuning is that the bias conditions of the analog blocks under calibration are controlled and less affected by PVT variations due to the correcting action of the local loops, thereby allowing higher yields as a result of automatic correction in the analog front-end. However, the power and area consumption of the BIT circuitry is the main trade-off. Furthermore, the BIT circuits themselves have to be designed robustly to avoid failures, making the implementation more challenging and invasive than digital schemes. Efforts for the analog approach are generally more justified in transceivers that have limited on-chip digital resources and in scenarios that require fast automatic correction. For example, the IRR calibration in [18] can be used on-line with a settling time that depends on the bandwidth of the analog control loops rather than convergence of digital algorithms that take several milliseconds as in [14]. Another fast analog calibration method with a convergence time in the microseconds regime is described in [15].

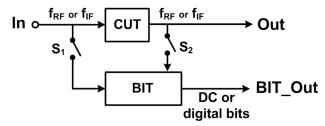

Instead of using a system-level test strategy, it has been very popular to extract information from each block in the analog front-end for characterization or tuning of the block, which is visualized in Fig. 7. The circuit under test (CUT) represents a block in the RF front-end or analog baseband that can be connected to a BIT circuit in test mode by closing the two switches S<sub>1</sub> and S<sub>2</sub>. In [19] for instance, a low-noise amplifier (LNA) was tested with a BIT block containing a test amplifier and two power detectors to measure input impedance, gain, noise figure, input return loss, and output SNR. This approach has the advantage that the fault location/cause can be identified clearly and that the DC or digital outputs of the BIT circuits can be used to recover from certain failure

modes. High-frequency RF front-ends have been targeted in particular with dedicated design of BIT circuits because gain, impedance matching, and linearity performances are very sensitive to variations. Also, direct signal digitization is not feasible at high frequencies, eliminating many digital compensation schemes. Hence, several RF block-level measurement approaches involve power or amplitude detectors along the signal path [20]-[23].

Fig. 7. BIT with analog instrumentation along the signal path.

Self-calibration of impedance matching for an LNA at the input of the receiver chain as done in [24] also requires on-chip analog sensing circuitry, especially to achieve a short calibration time such as the 30µs reported in [24]. An alternative proposition to monitor individual blocks in the signal path was made in [25], in which the transient supply currents of the CUTs are monitored with the BIT circuitry by placing small series resistors in the power supply lines. However, a clear disadvantage with any block-level measurement is that the BIT circuitry is connected to the CUT and therefore must be designed carefully to avoid impact on block or system performance. But, some degradation due to loading effects from BIT circuitry must usually be tolerated.

Furthermore, switches in or along the signal path are undesired due to their losses and signal feedthrough due to finite isolation, particularly at RF frequencies.

Though with less accuracy than off-chip measurement equipment, efforts have also been made to mimic conventional instrumentation such as spectrum analyzers ([26], [27]) on the chip with sufficient accuracy for BIT applications. In [26] for example, the analyzer with a frequency range of 33MHz to 3GHz could cover the entire signal paths of many wireless transceivers in handheld consumer products. A multiplexor could be used to selectively route a test input at a time to one spectrum analyzer, but the on-chip measurement circuitry still takes up large area and significant power that might not be permissible in certain applications. For example the analyzer in [26] consumes 0.384mm<sup>2</sup> and more than 20mW.

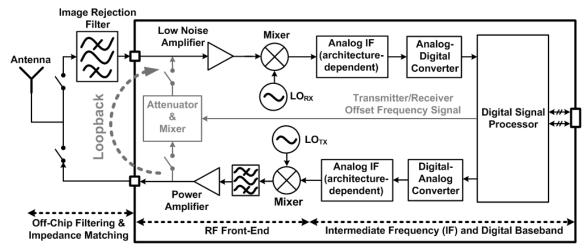

#### II.2.3. Loopback testing

Loopback testing is a system-level BIT technique in which the BER is monitored in the digital baseband [28]. It allows simultaneous verification of the analog and digital transceiver blocks (Fig. 8) with a low-frequency digital input signal applied to the baseband subsection of the transmitter. This up-converted signal is routed from the transmitter (TX) output to the receiver (RX) input via a loopback connection [29]. After down-conversion and digitization in the RX, the received bitstream is analyzed in the digital baseband processor to determine the BER. Attenuation and frequency translation with a mixer are required in the loopback block to maintain signal integrity and to ensure that the power levels during testing are comparable to normal operation. If the communication standard does not require frequency translation between TX and RX,

then only the RF attenuator is required. In any case, the overhead of the BIT circuitry is below 10% of the complete transceiver, which is efficient. However, the loopback BIT cannot be executed on-line; it requires a dedicated test mode during production testing or self-checks during times when the transceiver is idle.

Fig. 8. Generalized transceiver block diagram with loopback.

The main benefit of the loopback technique is that a BER test is the most important metric, which is only low when all components function properly. This property makes loopback very attractive for fast pass/fail production testing and quick self-checks during in-field use, especially when few or no off-chip test resources are available. For example, a loopback test for the on-wafer production test stage was presented in [30].

A drawback of early loopback implementations is the lack of information regarding failure causes and fault locations. In response, one proposed variant [31] involves more computations in the digital baseband processor to determine the spectral content of the received bits and to use the data for estimation of receiver/transmitter nonlinearity

specifications. Alternatively, power detectors could be placed at critical nodes to extract block-level gain and 1dB-compression point measurements. Or, similarly, statistical sampling blocks were placed along the signal path in [32]. These blocks produce digital bitstreams for analysis of fault locations. In general, inclusion of auxiliary circuitry during a loopback test increases the observability of faults, but with the associated trade-offs that have been discussed for on-chip measurement circuitry in Section II.2.2.

## II.2.4. Digital performance monitoring with analog compensation

A BIT approach for complex transceiver chips that has become increasingly popular in recent years is depicted in Fig. 9. It incorporates accurate digital monitoring and I/Q mismatch correction in the baseband processors as well as a few analog observables such as outputs from received signal strength indicators (RSSIs) or DC control voltages of blocks that give some insights into their operating conditions. A significant aspect is that many analog bias voltages for RF front-end and baseband circuits are generated with digital-to-analog converters (DACs). These DACs are utilized for coarse adjustments at start-up in order to compensate for PVT variations. They also reduce DC offsets in the analog circuits to prevent saturation of internal nodes due to large gains in the receiver. Thus, more mismatches can be tolerated because of the capability to counteract them.

Fig. 9. Transceiver with digital monitoring and tuning of analog blocks.

Combined digital monitoring/calibration with analog compensation DACs has been reported in publications describing industrial transceivers. Some examples are:

- Single-chip GSM/WCDMA transceiver in 90nm CMOS [33], (Freescale, 2009)

- DC offset, I/Q gain & phase, IIP2 calibration in the digital signal processor

- 6-bit DACs for analog compensation

- 2.4GHz Bluetooth Radio in 0.35µm CMOS [34], (Broadcom, 2005)

- Bias networks with digital settings for LNA, mixer, filter

- Tuning patent (US 7,149,488 B2); RSSIs & digital block-level bias trimming

- 5.15-5.825GHz WLAN transceiver in 0.18µm CMOS [35], (Athena, 2003)

- Digital I/Q mismatch correction

- Multiple internal loopback switches for self-calibration in test mode

- 8-bit DACs for DC offset minimization after mixers and filters

- 2.4GHz WLAN transceiver in 0.25µm CMOS [36], (MuChip, 2005)

- Baseband I/Q gain and phase calibration

- Extra analog mixer & peak detector

# II.2.5. Combined digital monitoring, analog measurements, and tuning

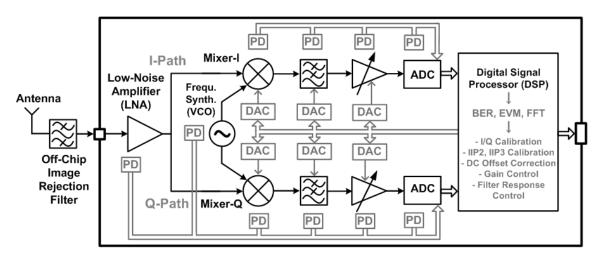

The circuit-level research projects discussed in the following sections are based on the hybrid analog/digital approach outlined in the previous subsection. One goal is to improve fault observability and calibration effectiveness by adding more measurement circuitry in the analog segments to provide data that can become part of the system-level calibration routine. Information from measurements can be used for block-level tuning prioritizations and optimizations, leading to shorter start-up routines and convergence times of algorithms. Fig. 10 portrays the envisioned transceiver with enhanced analog measurements, where power detectors (PD) measure gains along the analog chain [20]-[23]. Power gain and linearity measurements through temperature sensing are explored in Section V. In contrast to conventional power detectors, temperature sensors do not physically come in contact with the CUT and thus avoid loading effects.

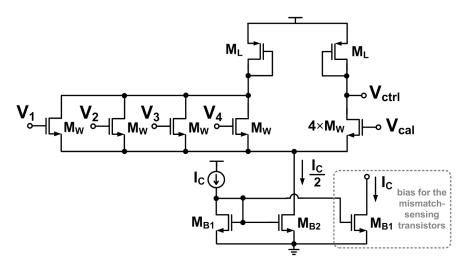

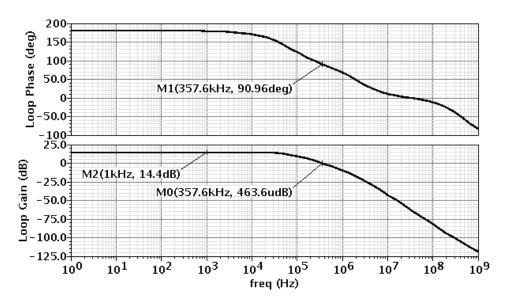

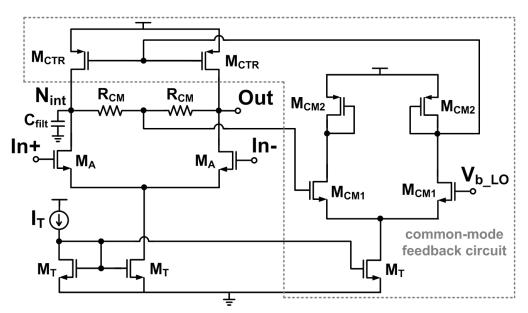

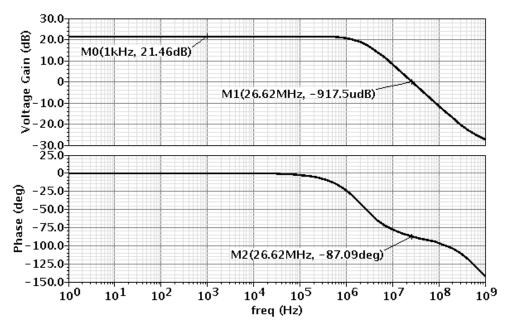

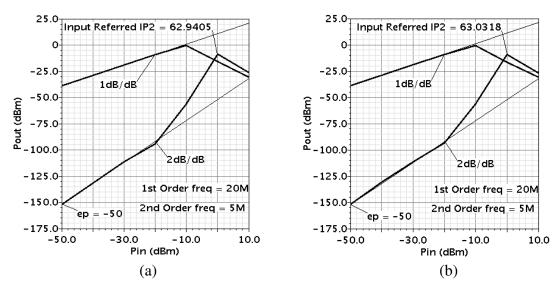

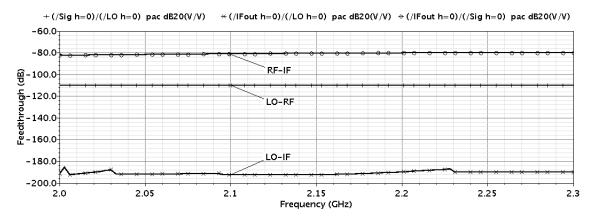

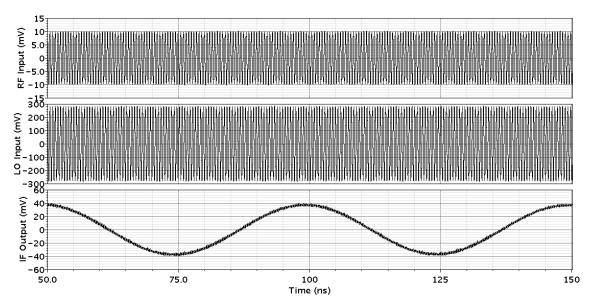

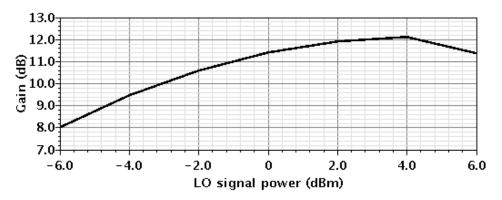

Fig. 10. Transceiver with digital monitoring, analog measurements, and tuning.