# PARALLEL VLSI CIRCUIT ANALYSIS AND OPTIMIZATION

A Dissertation

by

XIAOJI YE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2010

Major Subject: Computer Engineering

# PARALLEL VLSI CIRCUIT ANALYSIS AND OPTIMIZATION

A Dissertation

by

# XIAOJI YE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Peng Li Committee Members, Weiping Shi

Weiping Shi Aydin I. Karsilayan

Vivek Sarin

Head of Department, Costas N. Georghiades

December 2010

Major Subject: Computer Engineering

## ABSTRACT

Parallel VLSI Circuit Analysis and Optimization. (December 2010)

Xiaoji Ye, B.E., Wuhan University;

M.S., Texas A&M University

Chair of Advisory Committee: Dr. Peng Li

The prevalence of multi-core processors in recent years has introduced new opportunities and challenges to Electronic Design Automation (EDA) research and development. In this dissertation, a few parallel Very Large Scale Integration (VLSI) circuit analysis and optimization methods which utilize the multi-core computing platform to tackle some of the most difficult contemporary Computer-Aided Design (CAD) problems are presented. The first CAD application that is addressed in this dissertation is analyzing and optimizing mesh-based clock distribution network. Mesh-based clock distribution network (also known as clock mesh) is used in high-performance microprocessor designs as a reliable way of distributing clock signals to the entire chip. The second CAD application addressed in this dissertation is the Simulation Program with Integrated Circuit Emphasis (SPICE) like circuit simulation. SPICE simulation is often regarded as the bottleneck of the design flow. Recently, parallel circuit simulation has attracted a lot of attention.

The first part of the dissertation discusses circuit analysis techniques. First, a combination of clock network specific model order reduction algorithm and a port sliding scheme is presented to tackle the challenges in analyzing large clock meshes with a large number of clock drivers. Our techniques run much faster than the standard SPICE simulation and existing model order reduction techniques. They also provide a basis for the clock mesh optimization. Then, a hierarchical multi-algorithm parallel circuit simulation (HMAPS) framework is presented as an novel technique of parallel

circuit simulation. The inter-algorithm parallelism approach in HMAPS is completely different from the existing intra-algorithm parallel circuit simulation techniques and achieves superlinear speedup in practice. The second part of the dissertation talks about parallel circuit optimization. A modified asynchronous parallel pattern search (APPS) based method which utilizes the efficient clock mesh simulation techniques for the clock driver size optimization problem is presented. Our modified APPS method runs much faster than a continuous optimization method and effectively reduces the clock skew for all test circuits. The third part of the dissertation describes parallel performance modeling and optimization of the HMAPS framework. The performance models and runtime optimization scheme improve the speed of HMAPS further more. The dynamically adapted HMAPS becomes a complete solution for parallel circuit simulation.

To my family

#### ACKNOWLEDGMENTS

First and foremost I thank my advisor, Dr. Peng Li. Throughout the course of my graduate studies, he was always willing to make himself accessible to me for technical discussions. He consistently challenged me to be a better student and researcher. His dedication to excellence, encouragement and support to students, and enthusiasm for research and innovations, will leave a lasting imprint on me. He is not only a great academic advisor, but also a mentor for life.

I also want to thank my committee members, Drs. Weiping Shi, Aydin Karsilayan, and Vive Sarin, for spending time to become familiar with my research, giving valuable suggestions to me, and for reviewing my dissertation.

I am grateful to the fellow students in the computer engineering group. I learned a lot from them. They also made my stay in College Station enjoyable and memorable.

Finally, I want to thank my wife Biwei, my parents, and other family members. They are the source of my confidence and happiness. Without their support, this dissertation would not have been possible.

# TABLE OF CONTENTS

| CHAPTER |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| I       | INTRODUCTION AND BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                      |

|         | A. Emergence of Multi-Core CPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                      |

| II      | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6                                                                                      |

|         | A. Clock Mesh Analysis and Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11                                                                                     |

| III     | CIRCUIT ANALYSIS TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                                     |

|         | A. Analysis of Clock Mesh  1. Overview of the Approach  2. Harmonic-Weighted Model Order Reduction  3. Port Sliding  4. Implementation Issues  5. Experimental Results  6. Summary  B. HMAPS: Hierarchical Multi-Algorithm Parallel Simulation  1. Background  2. Overview of the Approach  3. HMAPS: Diversity in Numerical Integration Methods  4. HMAPS: Diversity in Nonlinear Iterative Methods  5. Construction of Simulation Algorithms  6. Intra-Algorithm Parallelism  7. Communications in HMAPS  8. Experimental Results  9. Summary | 18<br>21<br>28<br>33<br>34<br>41<br>41<br>41<br>44<br>51<br>57<br>60<br>62<br>65<br>69 |

| IV      | CIRCUIT OPTIMIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82                                                                                     |

|         | A. Basic Description of APPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87                                                                                     |

| CHAPTER  | P                                                                                                          | <b>'</b> age                                  |

|----------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|          | 2. Harmonic Weighted Model Order Reduction C. Additional Directions                                        | 90<br>93<br>95<br>100                         |

| V        | PARALLEL PERFORMANCE MODELING AND OPTI-MIZATION                                                            | 104                                           |

|          | 1. Overview                                                                                                | 104<br>105<br>107                             |

|          | <ul><li>4. Performance Modeling of Inter-Algorithm Collaboration</li><li>5. Experimental Results</li></ul> | 118                                           |

|          | v                                                                                                          | <ul><li>122</li><li>123</li></ul>             |

|          | <ol> <li>On-the-fly Automatic Adaptation</li></ol>                                                         | 125<br>125<br>126<br>128<br>129<br>129        |

|          | a. Dynamic HMAPS vs Static HMAPS b. Dynamic HMAPS vs Standard Parallel Cir-                                | <ul><li>130</li><li>131</li><li>134</li></ul> |

|          | 3. Summary                                                                                                 | 134                                           |

| VI       | CONCLUSION                                                                                                 | 136                                           |

| REFERENC | ES                                                                                                         | 138                                           |

| VITA     |                                                                                                            | 145                                           |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

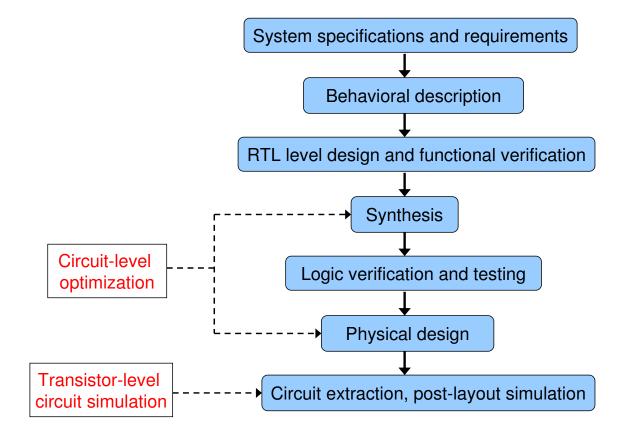

| 1      | Basic VLSI design flow                                                                                                                                                                                                                      | 4    |

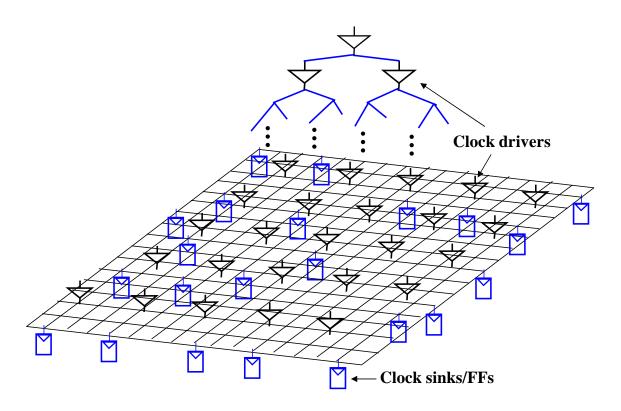

| 2      | Clock distribution using mesh structures                                                                                                                                                                                                    | 7    |

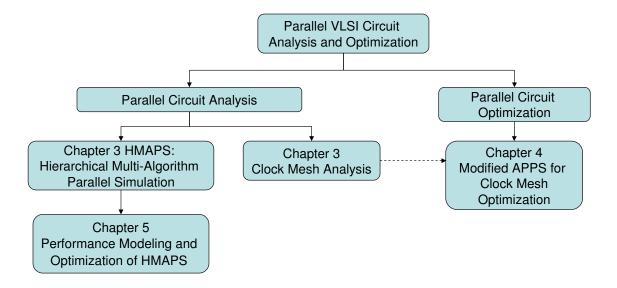

| 3      | Connections between different pieces of research work in this dissertation                                                                                                                                                                  | . 16 |

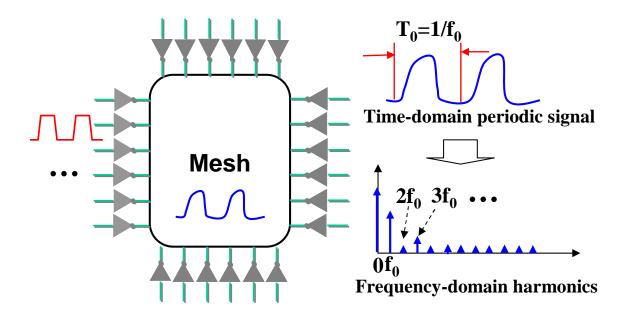

| 4      | Steady-state response of clock networks                                                                                                                                                                                                     | 19   |

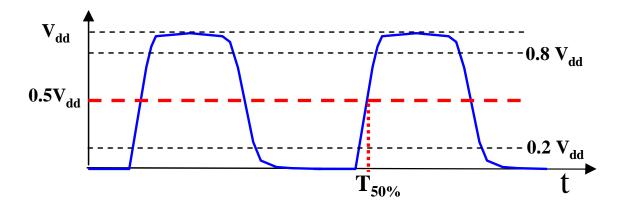

| 5      | Voltage-crossing times of a clock signal                                                                                                                                                                                                    | 23   |

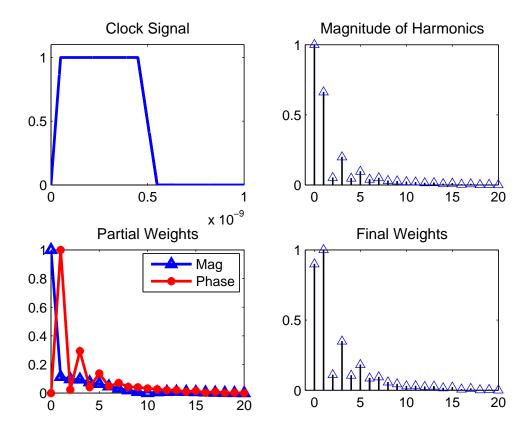

| 6      | Harmonic weighting for a clock signal                                                                                                                                                                                                       | 25   |

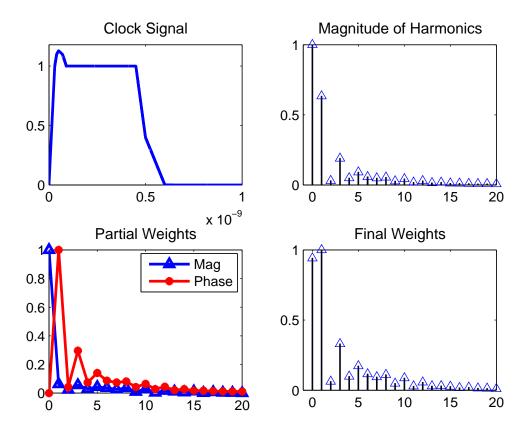

| 7      | Harmonic weighting for a clock signal with overshoot                                                                                                                                                                                        | 26   |

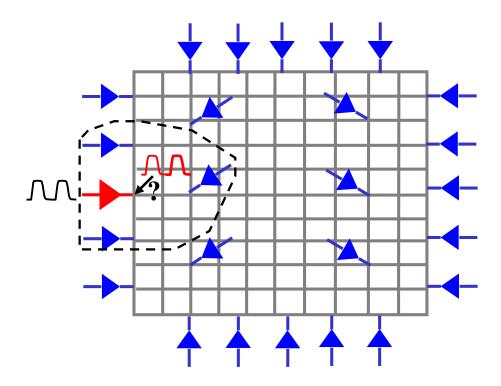

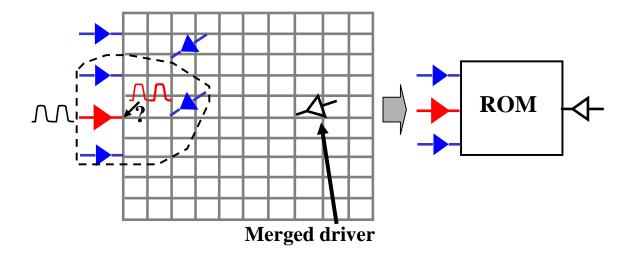

| 8      | Efficient driving point waveform computation using port sliding                                                                                                                                                                             | 30   |

| 9      | Merging of faraway drivers                                                                                                                                                                                                                  | 31   |

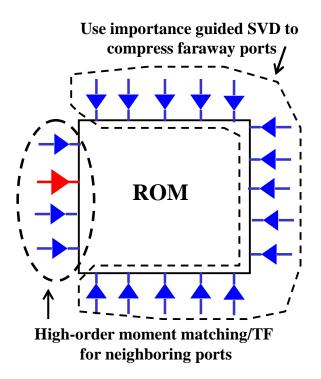

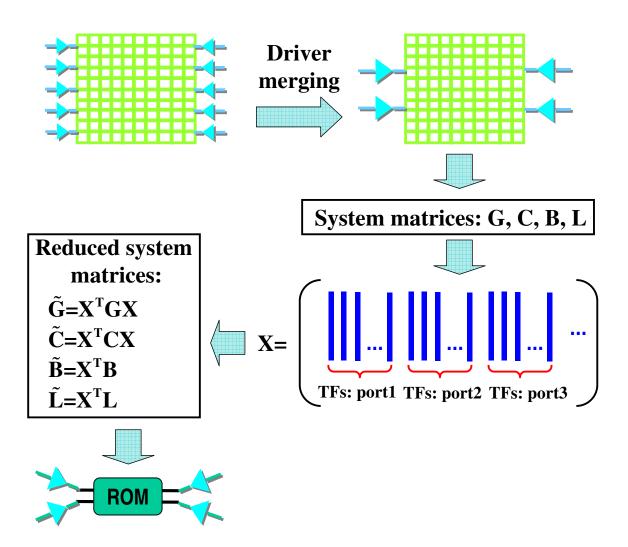

| 10     | Compaction of faraway ports using importance-weighted SVD                                                                                                                                                                                   | 32   |

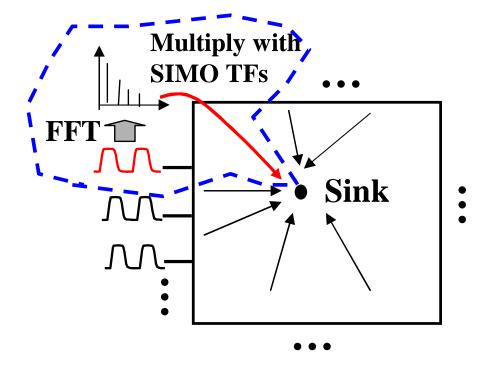

| 11     | Computation of sink node waveforms                                                                                                                                                                                                          | 33   |

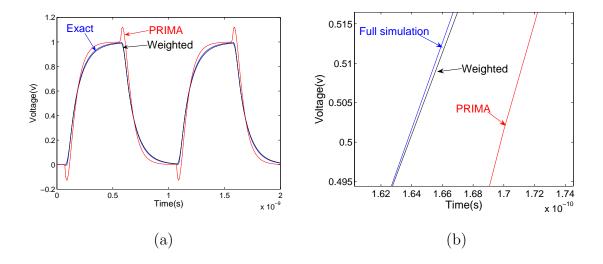

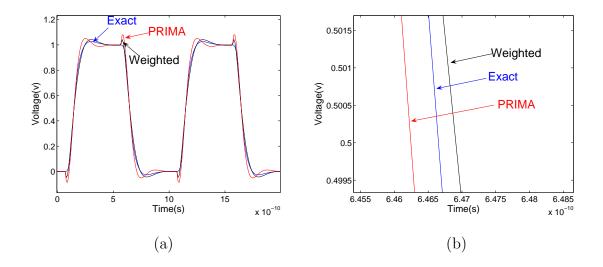

| 12     | (a)Comparison of time domain response between PRIMA and Harmonic-weighted MOR at one sink node of mesh1. (b)Zoomedin view of Fig. 12(a)                                                                                                     | 36   |

| 13     | (a)Comparison of time domain response between PRIMA and Harmonic-weighted MOR at one sink node of mesh2. (b)Zoomedin view of Fig. 13(a)                                                                                                     | 36   |

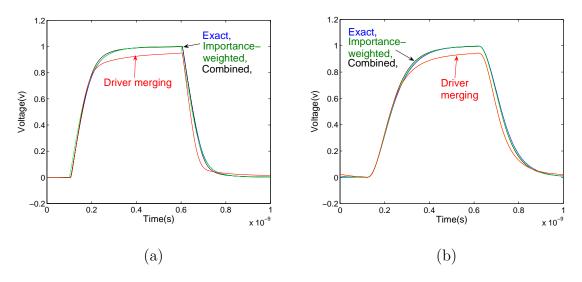

| 14     | (a) Comparison of driving point waveform between full simulation and three different port sliding methods for mesh2. (b) Comparison of the time domain waveform of a clock sink between full simulation and driver merging scheme for mesh2 | 38   |

| FIGURE |                                                                                                               | Page |  |

|--------|---------------------------------------------------------------------------------------------------------------|------|--|

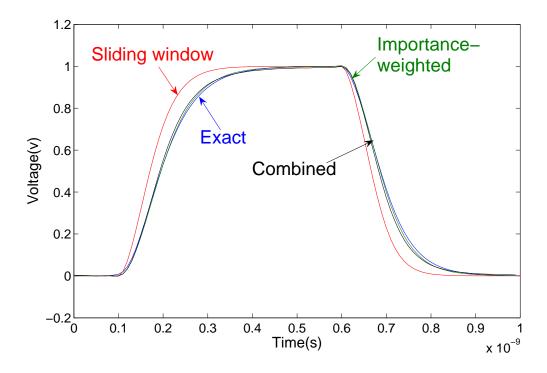

| 15     | Comparison of the time domain waveform of a clock sink between sliding window scheme and port sliding scheme. | 39   |  |

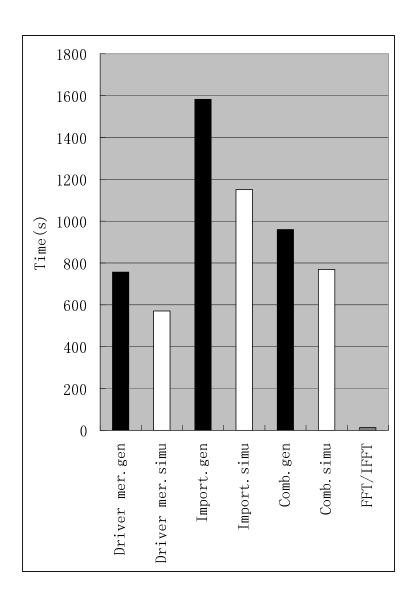

| 16     | Runtime breakdown for mesh3                                                                                   | 40   |  |

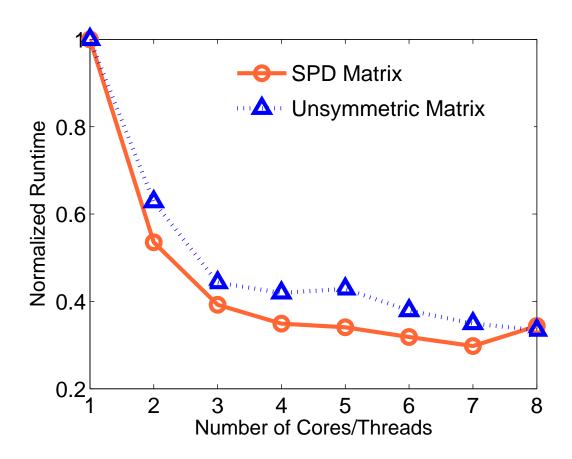

| 17     | Performance evaluation of a parallel matrix solver                                                            | 43   |  |

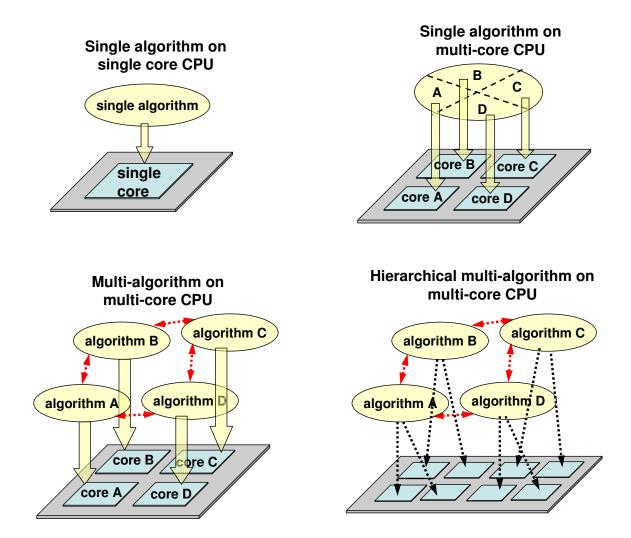

| 18     | Four different computing models of circuit simulation approaches.                                             | 45   |  |

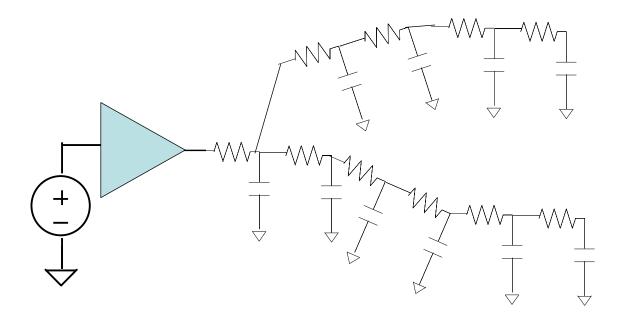

| 19     | An example circuit.                                                                                           | 46   |  |

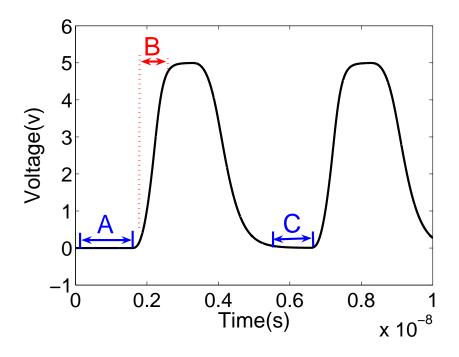

| 20     | Waveform at one node in a nonlinear circuit                                                                   | 47   |  |

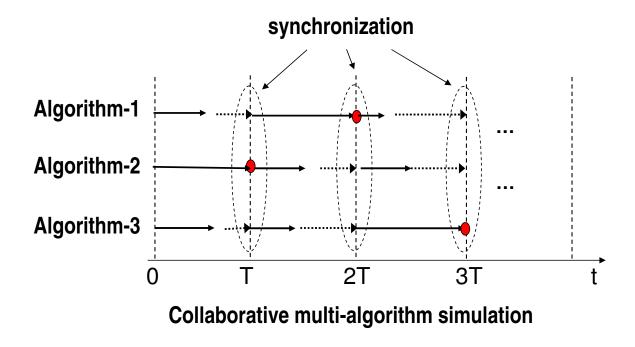

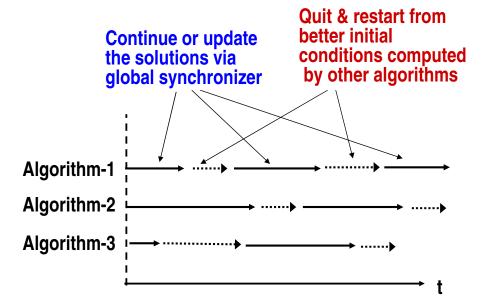

| 21     | Simple multi-algorithm synchronization scheme.                                                                | 47   |  |

| 22     | Synchronization scheme in <i>HMAPS</i>                                                                        | 49   |  |

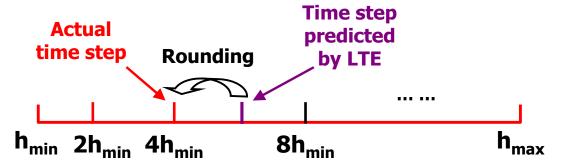

| 23     | Dynamic time step rounding                                                                                    | 62   |  |

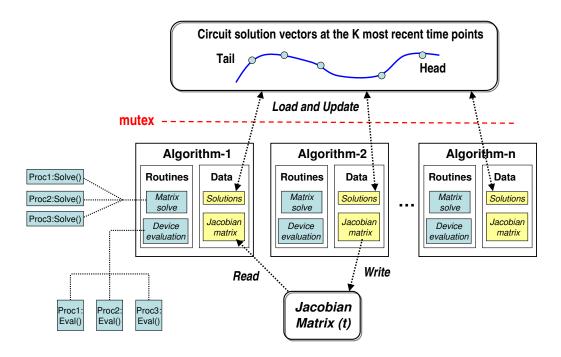

| 24     | Communication scheme in HMAPS                                                                                 | 66   |  |

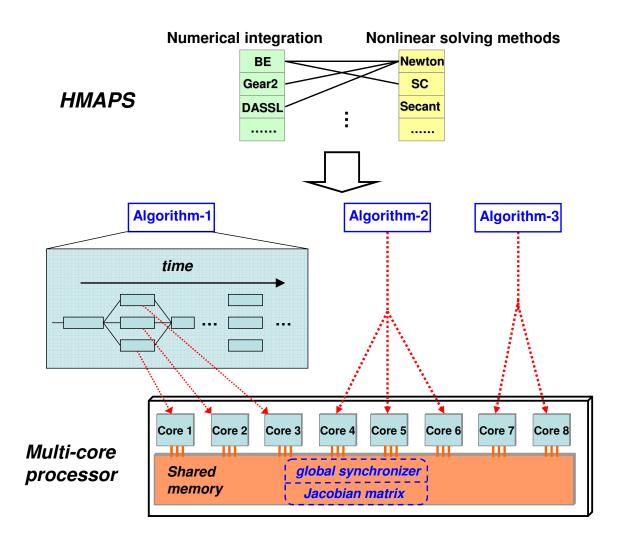

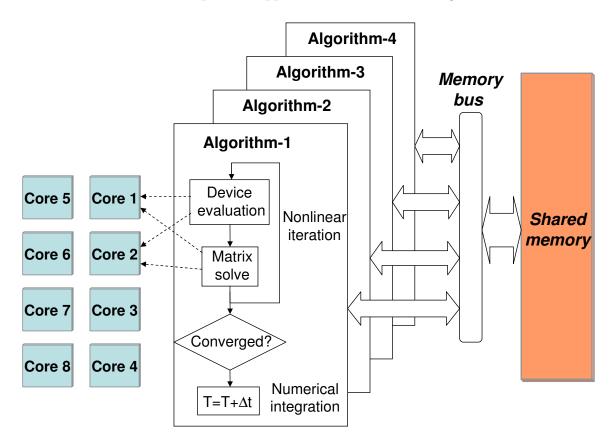

| 25     | Overall structure of HMAPS                                                                                    | 70   |  |

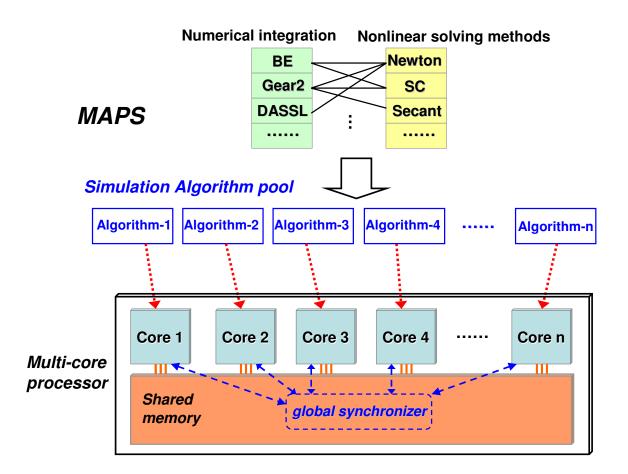

| 26     | Overall structure of MAPS                                                                                     | 71   |  |

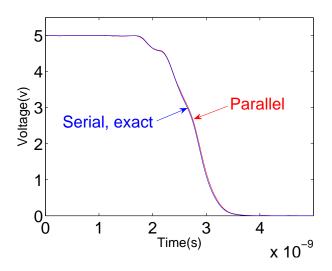

| 27     | Accuracy of HMAPS for a combinational logic circuit                                                           | 76   |  |

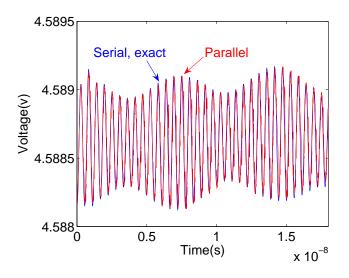

| 28     | Accuracy of HMAPS for a double-balanced mixer                                                                 | 77   |  |

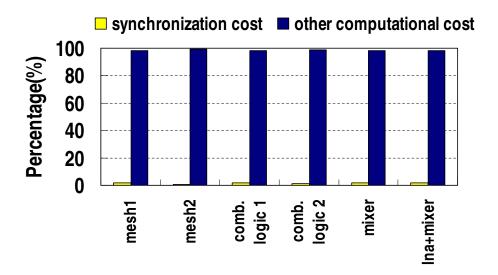

| 29     | Synchronization cost vs. other computational cost                                                             | 77   |  |

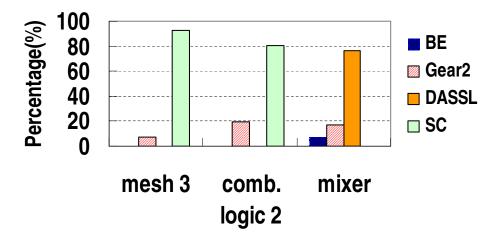

| 30     | Overall global synchronizer update breakdowns                                                                 | 78   |  |

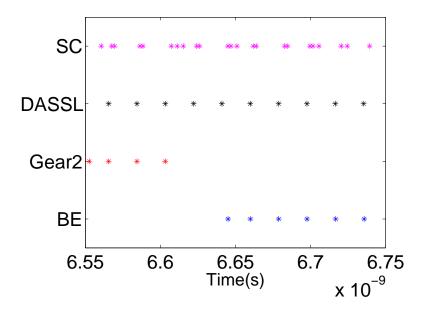

| 31     | Synchronizer updates within a local time window                                                               | 79   |  |

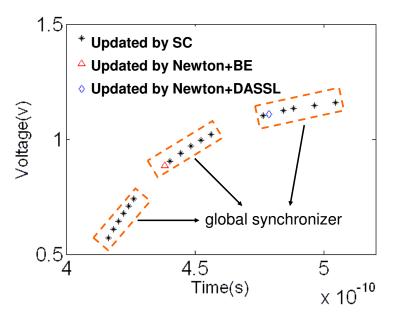

| 32     | Snapshot of the global synchronizer                                                                           | 80   |  |

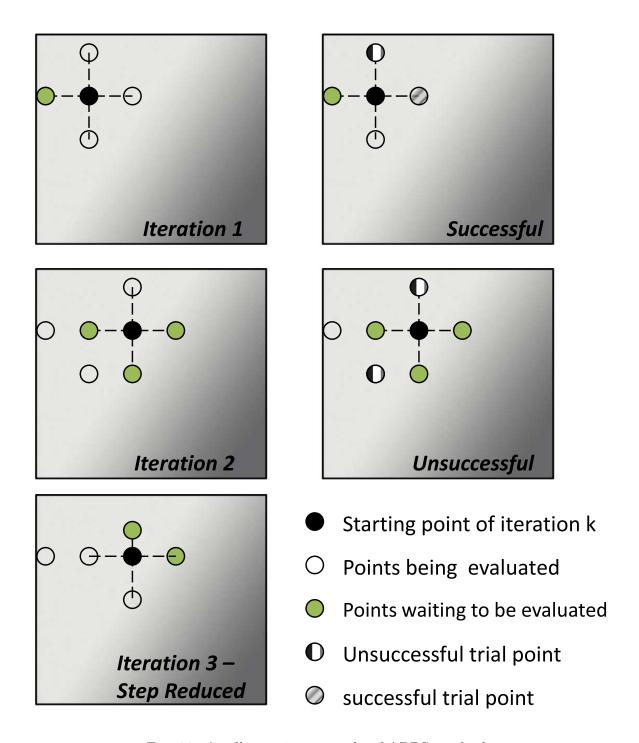

| 33     | An illustrative example of APPS method                                                                        | 86   |  |

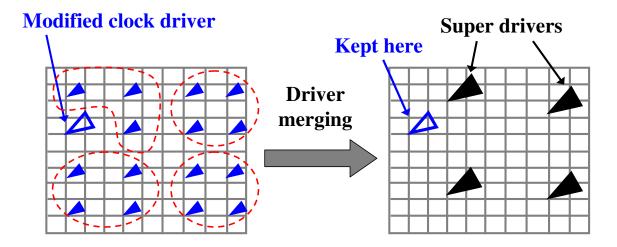

| 34     | Driver merging method where modified clock driver is kept                                                     | 89   |  |

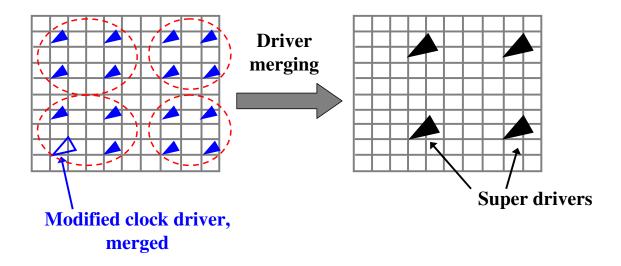

| 35     | Driver merging method where modified clock driver is merged                                                   | 90   |  |

| FIGURE | $\Xi$                                                                                                                                       | Page   |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 36     | The complete quick estimation flow                                                                                                          | 92     |

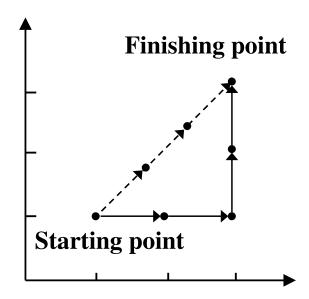

| 37     | Illustration of the benefit of using non-axial search directions                                                                            | 94     |

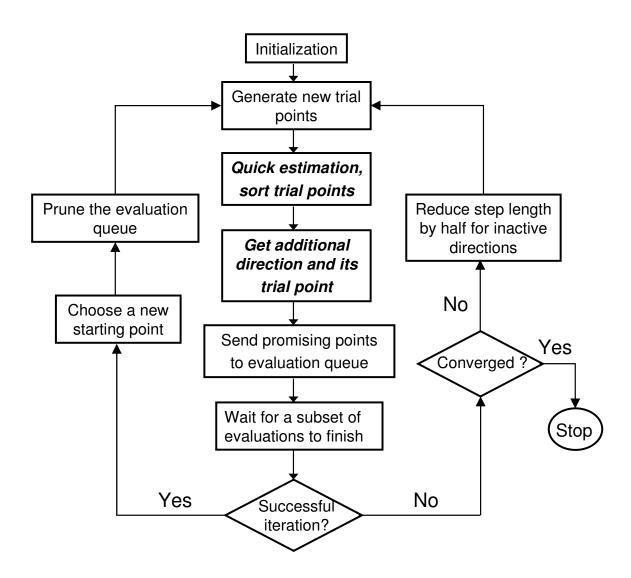

| 38     | Flow of modified APPS method for clock driver sizing problem                                                                                | 96     |

| 39     | Clock arrival time distribution before optimization for smooth load distribution.                                                           | 101    |

| 40     | Clock arrival time distribution after optimization for smooth load distribution                                                             | 102    |

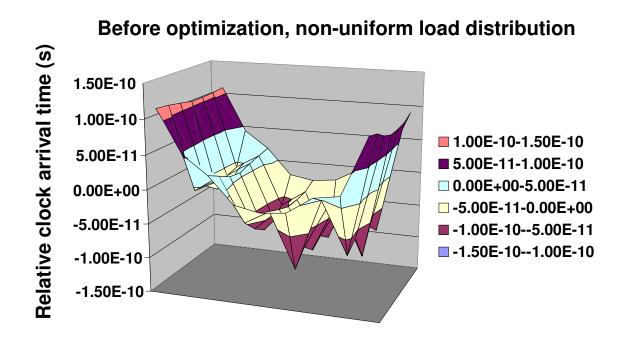

| 41     | Clock arrival time distribution before optimization for non-uniform load distribution.                                                      | 102    |

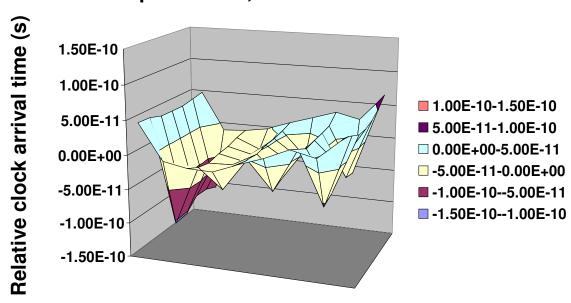

| 42     | Clock arrival time distribution after optimization for non-uniform load distribution.                                                       | 103    |

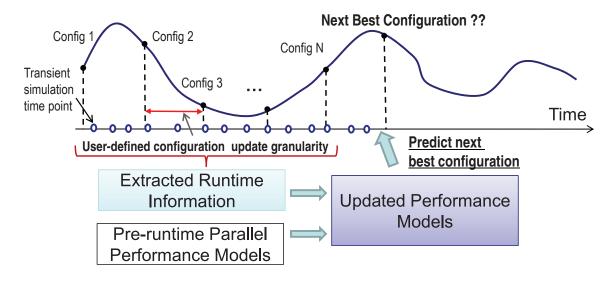

| 43     | Illustration of modeling tasks                                                                                                              | 106    |

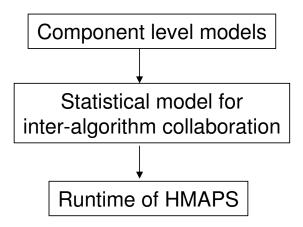

| 44     | Data flow of the performance modeling of HMAPS                                                                                              | 107    |

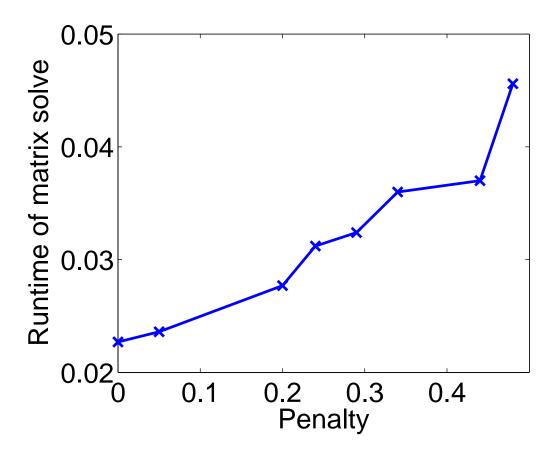

| 45     | Runtime of matrix solve is increasing with the penalty from other active threads                                                            | 111    |

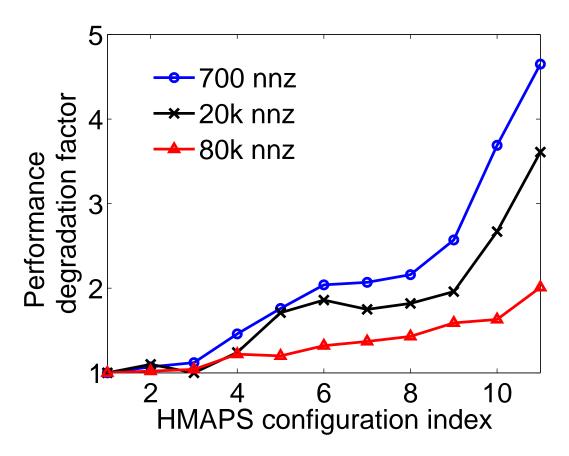

| 46     | The trend of the performance degradation factor changing with HMAPS configurations for different matrices                                   | 112    |

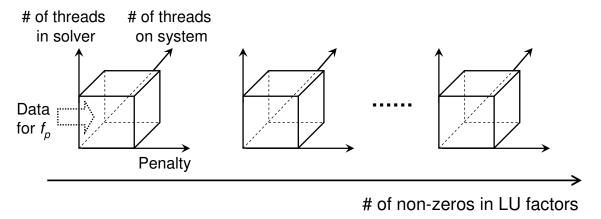

| 47     | Four-dimensional lookup table for the parallel matrix solver                                                                                | 113    |

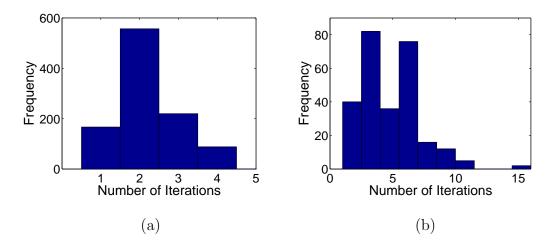

| 48     | (a) Number of iterations distribution for BE method. (b) Number of iterations distribution for Dassl method                                 | 115    |

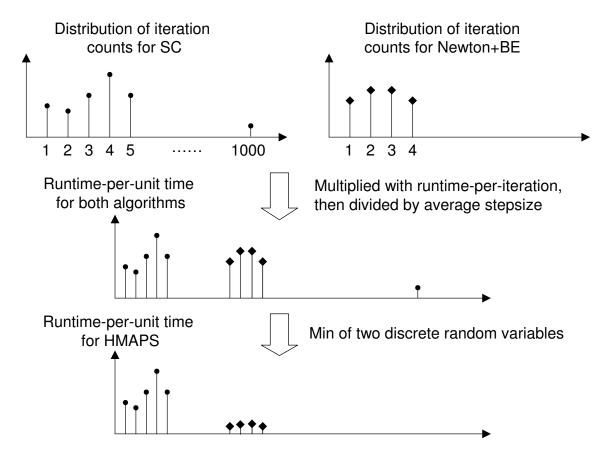

| 49     | Illustration of the statistical model                                                                                                       | 118    |

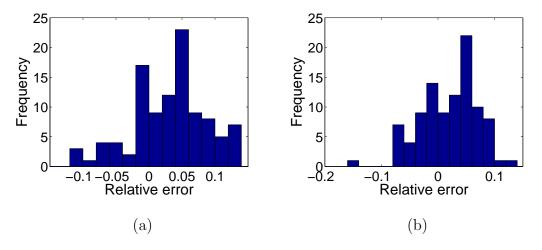

| 50     | (a)Relative error of the predicted matrix solve time for a matrix. (b)Relative error of the predicted matrix solve time for a larger matrix | x. 119 |

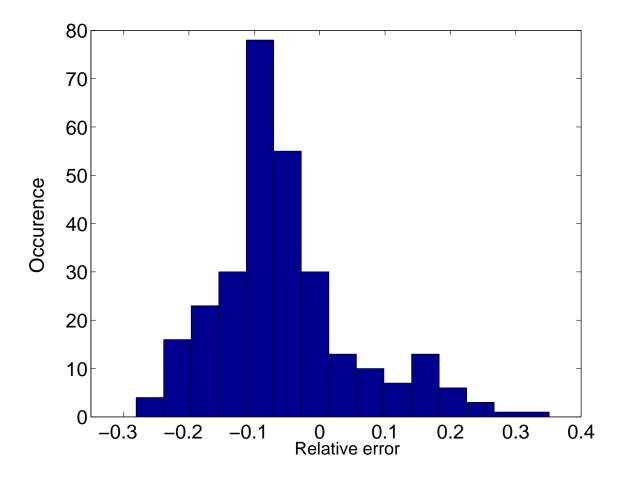

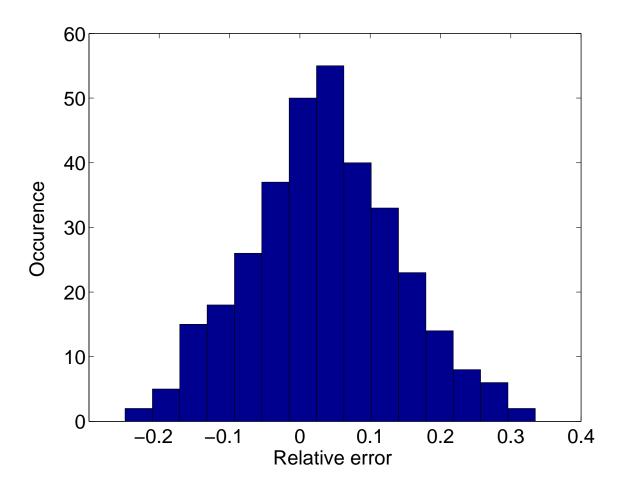

| 51     | Histogram of the relative error for one circuit example                                                                                     | 123    |

| 52     | Histogram of the relative error for another circuit example                                                                                 | 124    |

| FIGURI | ${\mathbb E}$                                    | Page |

|--------|--------------------------------------------------|------|

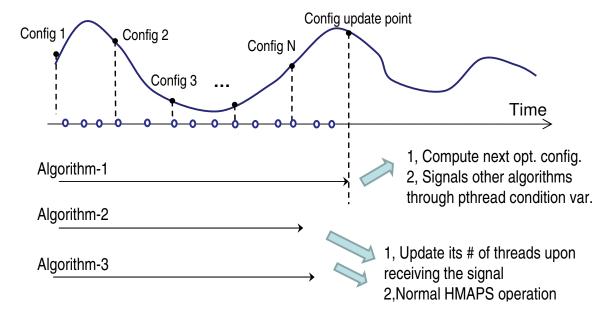

| 53     | Dynamic reconfiguration for runtime optimization | 126  |

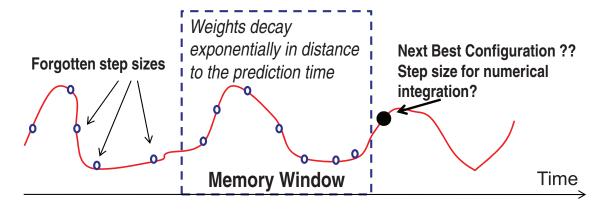

| 54     | Fading memory: dynamic updating of step size     | 127  |

| 55     | Dynamic configuration update in HMAPS            | 130  |

# LIST OF TABLES

| TABLE |                                                                                                                                                                | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Ι     | Runtime(s) comparison for full simulation, PRIMA and Harmonic-weighted MOR                                                                                     | 35   |

| II    | Comparison between three port sliding methods                                                                                                                  | 37   |

| III   | Comparisons of MAPS and HMAPS                                                                                                                                  | 51   |

| IV    | Runtime (in seconds) of four sequential algorithms and HMAPS with inter-algorithm parallelism only (using 4 threads)                                           | 72   |

| V     | HMAPS implementation 1 (Inter-algorithm parallelism only, using 4 threads) vs HMAPS implementation 2 (Inter- and Intra-algorithm parallelism, using 8 threads) | 73   |

| VI    | HMAPS implementation 1 (Inter-algorithm parallelism only, using 4 threads) vs Newton+Gear2                                                                     | 75   |

| VII   | HMAPS implementation 2 (Inter- and Intra-algorithm parallelism, using 8 threads) vs Newton+Gear2                                                               | 75   |

| VIII  | Computational component cost (in seconds) breakdown for each example circuit                                                                                   | 76   |

| IX    | Memory usage for each simulation                                                                                                                               | 80   |

| X     | Verification of the quick estimation routine on three clock mesh examples                                                                                      | 98   |

| XI    | Tradeoff of quick estimation routine: more accuracy and less speedup                                                                                           | 98   |

| XII   | Comparison between the original APPS method and the modified APPS method on seven clock mesh examples                                                          | 98   |

| XIII  | Results of applying DONLP2 on the same set of clock mesh examples as in Table XII                                                                              | 99   |

| TABLE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| XIV   | Algorithm composition for a set of HMAPS configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 120  |

| XV    | Comparison between predicted and real performance for the first combinational circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 121  |

| XVI   | Comparison between predicted and real performance for the second combinational circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 121  |

| XVII  | Comparison between predicted and real performance for the first clock mesh circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 122  |

| XVIII | Comparison between predicted and real performance for the second clock mesh circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 122  |

| XIX   | Comparison between statically predicted and real performance for a clock mesh circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132  |

| XX    | Runtime comparison between static HMAPS and dynamic HMAPS $% \left( 1\right) =\left( 1\right) \left( 1\right) \left($ | 133  |

| XXI   | Profiling of configuration evolution for the dynamic HMAPS run for CKT 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 134  |

| XXII  | Profiling of configuration evolution for the dynamic HMAPS run for CKT 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 134  |

| XXIII | Runtime comparison between dynamic HMAPS and standard parallel circuit simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 135  |

## CHAPTER I

#### INTRODUCTION AND BACKGROUND

# A. Emergence of Multi-Core CPUs

VLSI technology scaling has been the driving force behind Moore's law for several decades. By scaling down the minimum feature size, several benefits can be achieved: gate delays are reduced, operating frequency is increased, transistor density is increased and more functionality can be put in a single chip. However, as technology scaling comes closer and closer to the fundamental limit that is imposed by physics laws, the problems associated with technology and frequency scaling become more and more severe. As the operating frequency keeps increasing, the power dissipation and power density of a chip eventually become too high. Technology and frequency scaling alone can no longer keep up with the demand for better CPU performance. To overcome this obstacle, CPU vendors have introduced a ground-breaking design methodology. By incorporating multiple cores on a single chip and having each core running at a lower frequency than a single-core processor, better power efficiency and performance can be achieved[1].

This change in the hardware industry brings new opportunities and excitement to the software industry. Before the emergence of multi-core processors, parallel computing was only used in limited scope such as supercomputing and distributed computing. Since the hardware platforms were very expensive and not easily accessible to the general public, parallel computing was only studied and utilized by domain experts. Nowadays, since multi-core processors are widely accessible to the general public, there is a strong need in the software industry to develop parallel

The journal model is *IEEE Transactions on Automatic Control*.