# ANALYSIS AND DESIGN OF RESILIENT VLSI CIRCUITS

A Dissertation

by

# **RAJESH GARG**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2009

Major Subject: Computer Engineering

## ANALYSIS AND DESIGN OF RESILIENT VLSI CIRCUITS

## A Dissertation

by

## **RAJESH GARG**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

# Approved by:

Chair of Committee, Sunil P. Khatri

Committee Members, Peng Li

Peng Li Krishna R. Narayanan Duncan M. Walker Kevin Nowka

Head of Department, Costas N. Georghiades

May 2009

Major Subject: Computer Engineering

### **ABSTRACT**

Analysis and Design of Resilient VLSI Circuits. (May 2009)

Rajesh Garg, B. Tech., Indian Institute of Technology-Delhi, India;

M.S.,Texas A&M University,

Chair of Advisory Committee: Dr. Sunil P. Khatri

The reliable operation of Integrated Circuits (ICs) has become increasingly difficult to achieve in the deep sub-micron (DSM) era. With continuously decreasing device feature sizes, combined with lower supply voltages and higher operating frequencies, the noise immunity of VLSI circuits is decreasing alarmingly. Thus, VLSI circuits are becoming more vulnerable to noise effects such as crosstalk, power supply variations and radiation-induced soft errors. Among these noise sources, soft errors (or error caused by radiation particle strikes) have become an increasingly troublesome issue for memory arrays as well as combinational logic circuits. Also, in the DSM era, process variations are increasing at an alarming rate, making it more difficult to design reliable VLSI circuits. Hence, it is important to efficiently design robust VLSI circuits that are resilient to radiation particle strikes and process variations. The work presented in this dissertation presents several analysis and design techniques with the goal of realizing VLSI circuits which are tolerant to radiation particle strikes and process variations.

This dissertation consists of two parts. The first part proposes four analysis and two design approaches to address radiation particle strikes. The analysis techniques for the radiation particle strikes include: an approach to analytically determine the pulse width and the pulse shape of a radiation induced voltage glitch in combinational circuits, a technique to model the dynamic stability of SRAMs, and a 3D device-level analysis of the radiation tolerance of voltage scaled circuits. Experimental results demonstrate that the

proposed techniques for analyzing radiation particle strikes in combinational circuits and SRAMs are fast and accurate compared to SPICE. Therefore, these analysis approaches can be easily integrated in a VLSI design flow to analyze the radiation tolerance of such circuits, and harden them early in the design flow. From 3D device-level analysis of the radiation tolerance of voltage scaled circuits, several non-intuitive observations are made and correspondingly, a set of guidelines are proposed, which are important to consider to realize radiation hardened circuits. Two circuit level hardening approaches are also presented to harden combinational circuits against a radiation particle strike. These hardening approaches significantly improve the tolerance of combinational circuits against low and very high energy radiation particle strikes respectively, with modest area and delay overheads.

The second part of this dissertation addresses process variations. A technique is developed to perform sensitizable statistical timing analysis of a circuit, and thereby improve the accuracy of timing analysis under process variations. Experimental results demonstrate that this technique is able to significantly reduce the pessimism due to two sources of inaccuracy which plague current statistical static timing analysis (SSTA) tools. Two design approaches are also proposed to improve the process variation tolerance of combinational circuits and voltage level shifters (which are used in circuits with multiple interacting power supply domains), respectively. The variation tolerant design approach for combinational circuits significantly improves the resilience of these circuits to random process variations, with a reduction in the worst case delay and low area penalty. The proposed voltage level shifter is faster, requires lower dynamic power and area, has lower leakage currents, and is more tolerant to process variations, compared to the best known previous approach.

In summary, this dissertation presents several analysis and design techniques which significantly augment the existing work in the area of resilient VLSI circuit design.

To my family

### **ACKNOWLEDGMENTS**

I am very grateful to my advisor Dr. Sunil P. Khatri, for giving me this opportunity to work under him. Without his constant guidance, suggestions and encouragement, this work would not have been possible. I owe him my gratitude for showing me this way of research. He has supported and encouraged me whenever I needed him and answered all my questions very openly. The informal talks that I had with him have been a constant source of knowledge and inspiration. I also want to thank him for all the facilities and support he has given to me. Thanks a lot Sunil for everything.

I would also like to thank my committee members, Dr. Peng Li, Dr. Hank Walker, Dr. Kevin Nowka, and Dr. Krishna Narayanan, for giving me their valuable feedbacks and suggestions. Their suggestions have been very helpful in improving my research work.

I would also like to express my sincere acknowledgment to Kanupriya, Karandeep, Charu, Suganth, and Nikhil, for their constant support, valuable comments and guidance. They have also helped me in learning new things, given time to discuss the problems, and has been a source of inspiration all along.

I would also like to thank my parents, brother and sister, who taught me the value of hard work by their own example. I would also like to share my moment of happiness with them. Without their encouragement and confidence in me, I would have never been able to pursue and complete my Doctoral study.

Finally, I would like to thank all my friends, who directly and indirectly supported and helped me in completing this dissertation.

# TABLE OF CONTENTS

| CHAPTER |                                                            | Page     |

|---------|------------------------------------------------------------|----------|

| I       | INTRODUCTION                                               | 1        |

|         | I-A. Background and Motivation                             | 2        |

|         | I-A.1. Radiation Particle Strikes                          |          |

|         | I-A.1.a. Physical Origin of Radiation Particles            |          |

|         | I-A.1.b. Charge Deposition Mechanisms                      |          |

|         | I-A.1.c. Charge Collection Mechanisms                      |          |

|         | I-A.1.d. Circuit Level Modeling of a Radiation             |          |

|         | Particle Strike                                            | 10       |

|         | I-A.1.e. Impact of Technology Scaling on the               |          |

|         | Radiation Tolerance of VLSI Design                         | 11       |

|         | I-A.2. Process Variations                                  |          |

|         | I-A.2.a. Impact of Technology Scaling on Pro-              |          |

|         | cess Variations                                            | 15       |

|         | I-B. Dissertation Overview                                 | 17       |

|         | I-C. Chapter Summary                                       | 22       |

| II      | RADIATION ANALYSIS - ANALYTICAL DETERMINATION              |          |

|         | OF RADIATION-INDUCED PULSE WIDTH IN COMBINA-               |          |

|         | TIONAL CIRCUITS                                            | 23       |

|         | II-A. Introduction                                         | 23       |

|         | II-B. Related Previous Work                                | 26       |

|         | II-C. Proposed Analytical Model for the Pulse Width of     |          |

|         | Radiation-induced Voltage Glitch                           | 28       |

|         | II-C.1. Radiation Particle Strike at the Output of an Inve | erter 29 |

|         | II-C.2. Classification of Radiation Particle Strikes       | 31       |

|         | II-C.3. Overview of the Model for Determining the          |          |

|         | Pulse Width of the Voltage Glitch                          | 32       |

|         | II-C.4. Derivation of the Proposed Model for Deter-        |          |

|         | mining the Pulse Width of the Voltage Glitch .             | 34       |

|         | II-C.4.a. Voltage Glitch Magnitude $V_{GM}$                | 35       |

|         | II-C.4.b. Derivation of the Expression for $t_1$           |          |

|         | II-C.4.c. Derivation of the Expression for $t_2$           |          |

|         | II-D. Experimental Results                                 |          |

|         | II-E Chapter Summary                                       | 45       |

| CHAPTER |                            |                                                                                                | Page         |

|---------|----------------------------|------------------------------------------------------------------------------------------------|--------------|

| III     |                            | ON ANALYSIS - ANALYTICAL DETERMINATION RADIATION-INDUCED PULSE SHAPE                           | . 47         |

|         | III-A.<br>III-B.<br>III-C. | Introduction                                                                                   |              |

|         |                            | induced Voltage Glitch                                                                         |              |

|         | III                        | mining the Pulse Shape of the Voltage Glitch                                                   | . 54         |

|         |                            | III-C.2.a. Voltage Glitch Magnitude $V_{GM}$                                                   | . 60<br>. 61 |

|         | III-D.<br>III-E.           | Experimental Results                                                                           | . 63         |

| IV      | ITY OF S                   | ON ANALYSIS - MODELING DYNAMIC STABIL-<br>SRAMS IN THE PRESENCE OF RADIATION PAR-<br>FRIKES    | . 70         |

|         | IV-A.<br>IV-B.<br>IV-C.    | Introduction                                                                                   | . 70         |

|         |                            | in the Presence of Radiation Particle Strikes                                                  | . 77         |

|         | IV-D.<br>IV-E.             | Experimental Results                                                                           | . 81         |

| V       | SIS OF TI                  | ON ANALYSIS - 3D SIMULATION AND ANALY-<br>HE RADIATION TOLERANCE OF VOLTAGE SCALED<br>CIRCUITS | . 85         |

|         | V-A.<br>V-B.               | Introduction                                                                                   | . 85         |

|         | V-C.                       | Simulation Setup                                                                               | . 88         |

|         | V-<br>V-D.                 | C.1. NMOS Device Modeling and Characterization Experimental Results                            |              |

|         | V-E.                       | Chapter Summary                                                                                |              |

| CHAPTER | ]                                                                                                                                                                                                                                                                                                   | Page                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| VI      | RADIATION HARDENING - CLAMPING DIODE BASED RADIATION TOLERANT CIRCUIT DESIGN APPROACH                                                                                                                                                                                                               | 103                                           |

|         | VI-A. Introduction                                                                                                                                                                                                                                                                                  | 104                                           |

|         | ing Devices  VI-C.1.a. PN Junction Diode  VI-C.1.b. Diode Connected Device  VI-C.2. Critical Depth for a Gate  VI-C.3. Circuit Level Radiation Hardening  VI-C.4. Alternative Circuit Level Radiation Hardening  VI-C.5. Final Circuit Selection  VI-D. Experimental Results  VI-E. Chapter Summary | 108<br>109<br>110<br>112<br>112<br>114<br>114 |

| VII     | RADIATION HARDENING - SPLIT-OUTPUT BASED RADIATION TOLERANT CIRCUIT DESIGN APPROACH                                                                                                                                                                                                                 | 127                                           |

|         | VII-A. Introduction                                                                                                                                                                                                                                                                                 | 128<br>129<br>129<br>135<br>136<br>141<br>144 |

| VIII    | VARIATION ANALYSIS - SENSITIZABLE STATISTICAL TIM-<br>ING ANALYSIS                                                                                                                                                                                                                                  | 150                                           |

|         | VIII-A. Introduction                                                                                                                                                                                                                                                                                | 152<br>n155                                   |

|         | VIII-C.2. Propagating Arrival Times                                                                                                                                                                                                                                                                 |                                               |

| CHAPTER  | Page                                                                                                                                                                                                                                                                                                |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | VIII-D. Experimental Results                                                                                                                                                                                                                                                                        |

| IX       | VARIATION TOLERANT DESIGN - A VARIATION TOLER-<br>ANT COMBINATIONAL CIRCUIT DESIGN APPROACH US-<br>ING PARALLEL GATES                                                                                                                                                                               |

|          | IX-A.Introduction177IX-B.Related Previous Work178IX-C.Process Variation Tolerant Combinational Circuit Design180IX-C.1.Process Variations180IX-C.2.Variation Tolerant Standard Cell Design181IX-C.3.Variation Tolerant Combinational Circuits185IX-D.Experimental Results186IX-E.Chapter Summary198 |

| X        | VARIATION TOLERANT DESIGN - PROCESS VARIATION<br>TOLERANT SINGLE SUPPLY TRUE VOLTAGE LEVEL SHIFTER 200                                                                                                                                                                                              |

|          | <ul> <li>X-A. Introduction</li></ul>                                                                                                                                                                                                                                                                |

|          | rameters Value                                                                                                                                                                                                                                                                                      |

|          | Temperature Variations                                                                                                                                                                                                                                                                              |

| XI       | CONCLUSIONS AND FUTURE DIRECTIONS                                                                                                                                                                                                                                                                   |

| REFERENC | ES                                                                                                                                                                                                                                                                                                  |

|          |                                                                                                                                                                                                                                                                                                     |

# LIST OF TABLES

| TABLE |                                                                                                                          | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------|------|

| II.1  | Pulse Width for INV1 Gate for $Q=150 fC$ , $\tau_{\alpha}=150 ps$ and $\tau_{\beta}=50 ps$                               | 43   |

| II.2  | Pulse Width for NAND2 gate for $\emph{Q}=150\emph{fC},$ $\tau_{\alpha}=150\emph{ps}$ and $\tau_{\beta}=50\emph{ps}$ .    | 43   |

| III.1 | RMSP Error of the Proposed Model for $3\times$ Gates and $Q=150fC$ , $\tau_{\alpha}=150 ps$ and $\tau_{\beta}=50 ps$     | 67   |

| III.2 | RMSP Error of the Proposed Model for Different Gates Sizes and $Q=150fC$ , $\tau_{\alpha}=150ps$ and $\tau_{\beta}=50ps$ | 67   |

| IV.1  | Comparison of Model with HSPICE                                                                                          | 83   |

| V.1   | $Q$ and Area of Voltage Glitch Versus Load Capacitance $(C_{load})$                                                      | 98   |

| VI.1  | Glitch Magnitude of PN Junction Clamping Diode for Rising Pulses (Output at Logic 0)                                     | 115  |

| VI.2  | Glitch Magnitude of PN Junction Clamping Diode for Falling Pulses (Output at Logic 1)                                    | 115  |

| VI.3  | Glitch Magnitude of Diode-connected Clamping Device for Rising Pulses (Output at Logic 0)                                | 116  |

| VI.4  | Glitch Magnitude of Diode-connected Clamping Device for Falling Pulses (Output at Logic 1)                               | 116  |

| VI.5  | Delay, Area and Critical Depth of Cells                                                                                  | 119  |

| VI.6  | Delay Overhead of the Proposed Radiation Hardened Design Approaches .                                                    | 122  |

| VI.7  | Area Overhead of the Proposed Radiation Hardened Design Approaches .                                                     | 123  |

| VI.8  | Total Number of Gates and Number of Hardened Gate in Different Designs                                                   | 123  |

| VI.9  | Delay Overhead of the Improved Circuit Protection Approach                                                               | 124  |

| VI.10 | Area Overhead of the Improved Circuit Protection Approach                                                                | 125  |

| TABLE  |                                                                                                                                                | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| VII.1  | Area Overheads of the Radiation Hardened Design Approach Proposed in This Chapter                                                              | 144  |

| VII.2  | Delay Overheads and $Q_{cri}$ of the Proposed Radiation Hardened Design Approach                                                               | 145  |

| VII.3  | Area and Delay Overheads of the Proposed Radiation Hardened Design Approach for 100% Coverage                                                  | 147  |

| VIII.1 | Transitions for a NAND Gate that Cause Its Output to Switch                                                                                    | 159  |

| VIII.2 | Parameters with Their Variation                                                                                                                | 166  |

| VIII.3 | Comparison of SSTA and StatSense for 75 Input Vector Transitions                                                                               | 171  |

| VIII.4 | Comparison of SSTA and StatSense for 50 and 25 Input Vector Transitions                                                                        | 173  |

| VIII.5 | Comparison of SSTA, StatSense50 and SSTA without False Paths                                                                                   | 175  |

| IX.1   | Comparison of Regular and Parallel Gates                                                                                                       | 191  |

| X.1    | Low to High Level Shifting                                                                                                                     | 212  |

| X.2    | High to Low Level Shifting                                                                                                                     | 213  |

| X.3    | Process Variations Simulation Results for Low to High and High to Low Level Shifting at $T = 27^{\circ} C \dots \dots \dots \dots \dots \dots$ | 214  |

| X.4    | Process Variations Simulation Results for Low to High and High to Low Level Shifting at $T = 60^{\circ}$ C                                     | 214  |

| X.5    | Process Variations Simulation Results for Low to High and High to Low Level Shifting at $T = 90^{\circ} C \dots \dots \dots \dots \dots \dots$ | 215  |

# LIST OF FIGURES

| FIGURE |                                                                                                                              | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------|------|

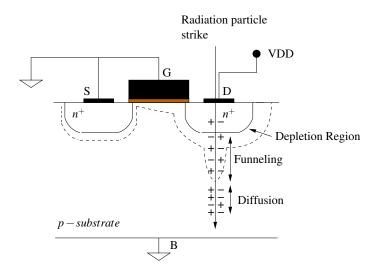

| I.1    | Charge deposition and collection by a radiation particle strike                                                              | 8    |

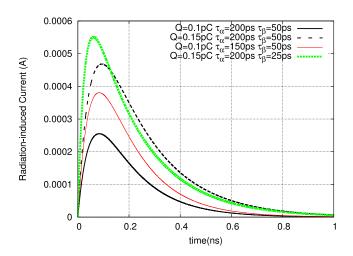

| I.2    | Current pulse model for a radiation particle strike plotted for different values of $Q$ , $\tau_{\alpha}$ and $\tau_{\beta}$ | 10   |

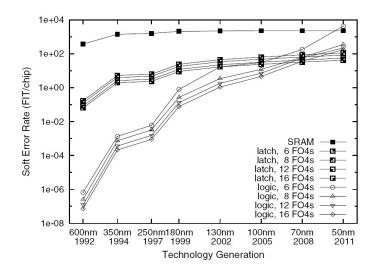

| I.3    | SER of an alpha processor for different technology nodes                                                                     | 14   |

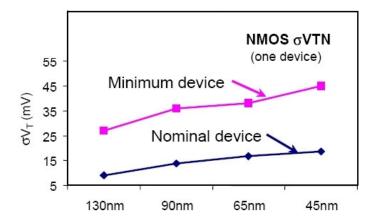

| I.4    | Variation in threshold voltage of devices for different technology nodes                                                     | 16   |

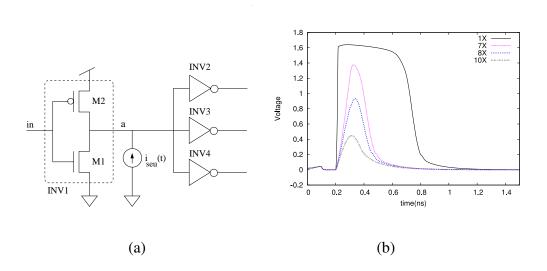

| II.1   | <ul><li>a) Radiation-induced current injected at the output of inverter INV1,</li><li>b) Voltage glitch at node a</li></ul>  | 29   |

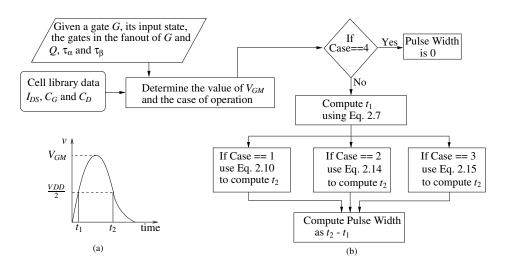

| II.2   | Flowchart of the proposed model for pulse width calculation                                                                  | 33   |

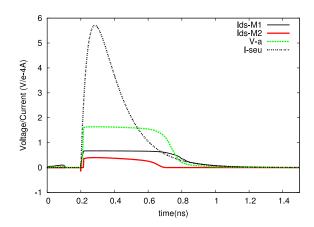

| II.3   | Voltage/Current due to a radiation particle strike at node <i>a</i> of INV1 of Figure II.1 (a)                               | 39   |

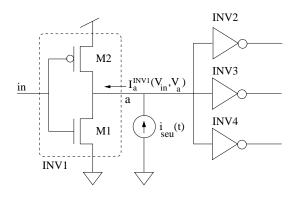

| III.1  | Radiation-induced current injected at the output of inverter INV1                                                            | 51   |

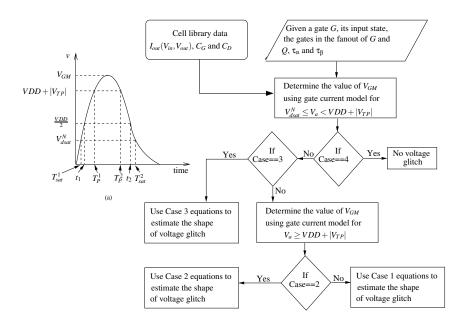

| III.2  | Flowchart of the proposed model for the shape of the radiation-induced voltage glitch                                        | 53   |

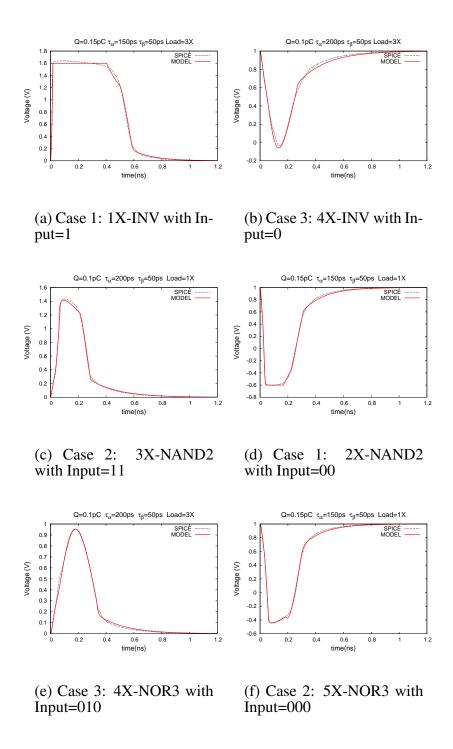

| III.3  | Radiation-induced voltage glitches obtained using the proposed model and SPICE for different gates                           | 65   |

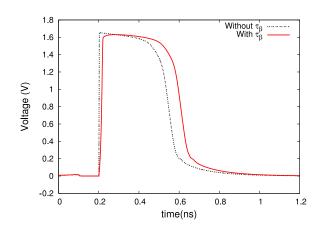

| III.4  | Radiation-induced voltage glitch at 2X-INV1                                                                                  | 68   |

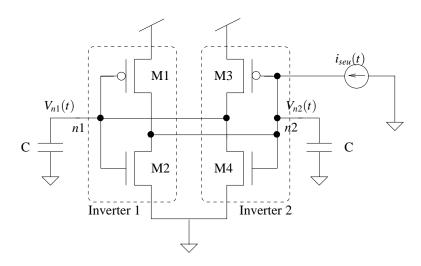

| IV.1   | Schematic of SRAM cell with noise current (access transistors are not shown)                                                 | 74   |

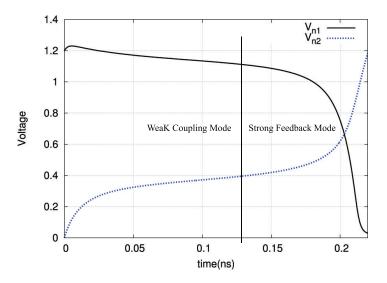

| IV.2   | SRAM node voltages for the noise injected at node $n2 \dots \dots \dots$                                                     | 76   |

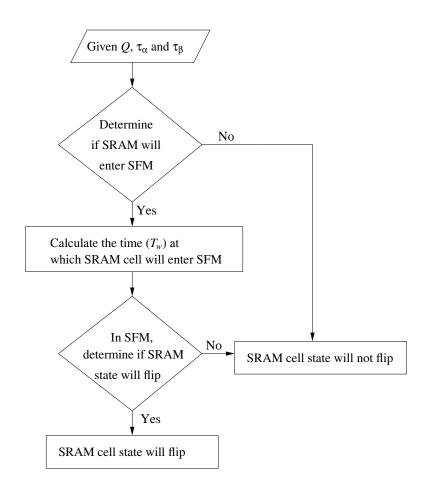

| IV.3   | Flowchart of the proposed model for SRAM cell stability                                                                      | 77   |

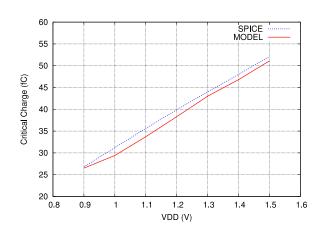

| IV.4   | Comparison of critical charge obtained using HSPICE and the proposed model                                                   | 82   |

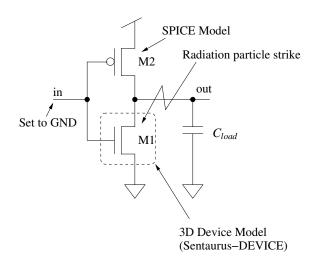

| V.1    | Inverter (INV) under consideration                                                                                           | 90   |

| FIGURE |                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------|------|

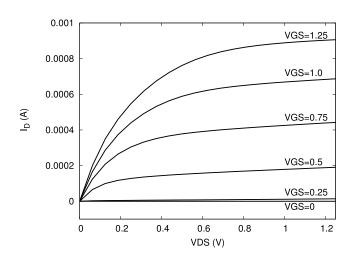

| V.2    | NMOS device: $I_D$ versus VDS plot for different VGS values                                 | 92   |

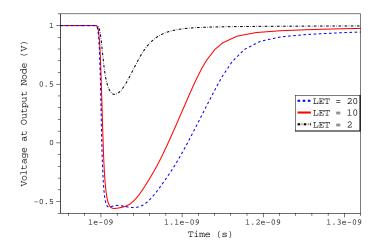

| V.3    | Radiation-induced voltage transient at the output of $4 \times$ INV with VDD=1 V            | . 93 |

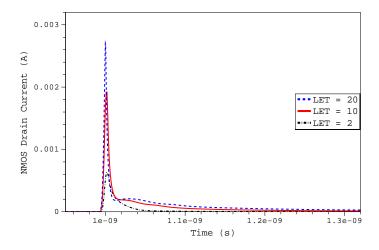

| V.4    | Radiation-induced drain current of the NMOS transistor of $4 \times$ INV with VDD=1 V       | . 93 |

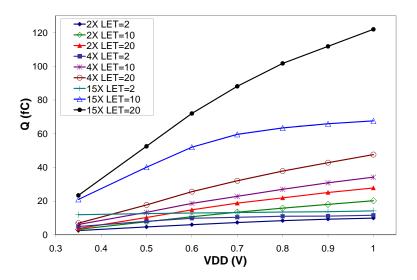

| V.5    | Charge collected at the output of INV for different values                                  | 95   |

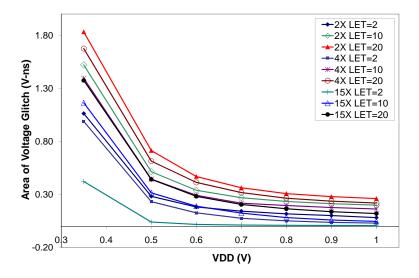

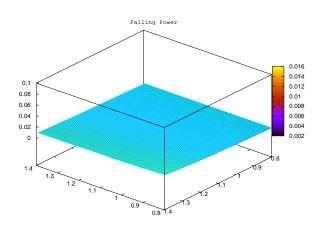

| V.6    | Area of voltage glitch versus VDD                                                           | 96   |

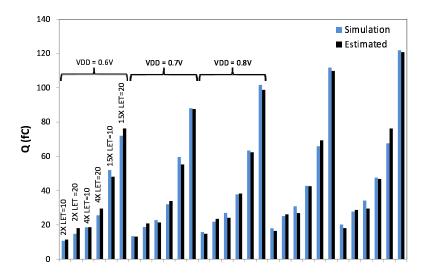

| V.7    | Comparison of charge collected $(Q)$ obtained from the proposed model versus 3D simulations | 102  |

| VI.1   | Diode based radiation-induced voltage glitch clamping circuit                               | 107  |

| VI.2   | Device based radiation-induced voltage glitch clamping circuit                              | 107  |

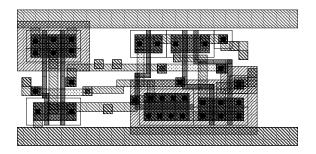

| VI.3   | Layout of radiation-tolerant NAND2 gate (uses device based clamping)                        | 111  |

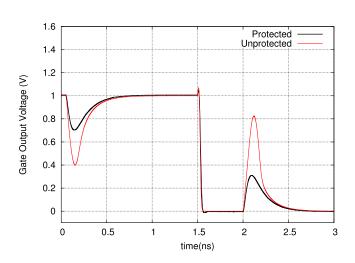

| VI.4   | Output waveform during a radiation event on output                                          | 117  |

| VI.5   | Output waveform during a radiation event on protecting node                                 | 118  |

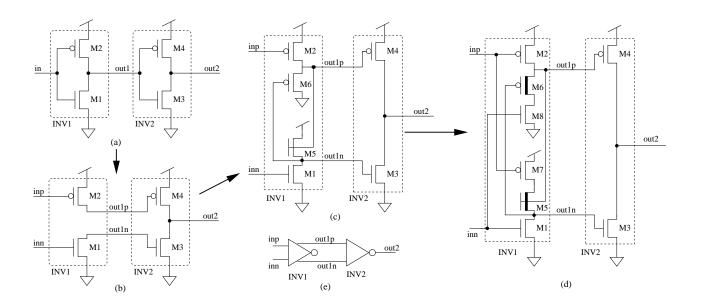

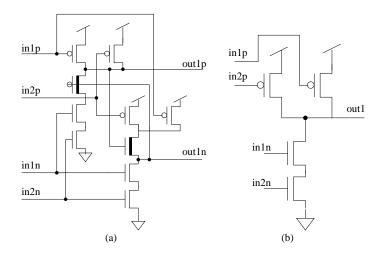

| VII.1  | Design of an radiation tolerant inverter                                                    | 131  |

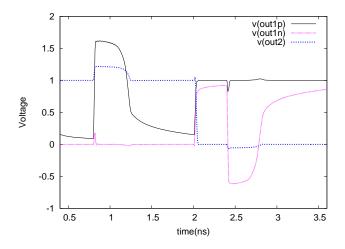

| VII.2  | Radiation particle strike at $out 1p$ and $out 1n$ of INV1 of Figure VII.1d                 | 134  |

| VII.3  | a) Radiation tolerant 2-input NAND gate, b) <i>modified</i> regular 2-input NAND gate       | 136  |

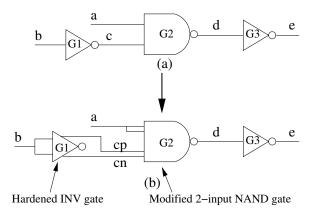

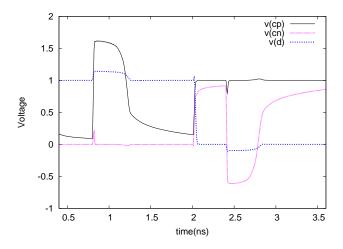

| VII.4  | Part of a circuit                                                                           | 138  |

| VII.5  | Waveforms at nodes $cp$ , $cn$ and $d$ of Figure VII.4 (b)                                  | 139  |

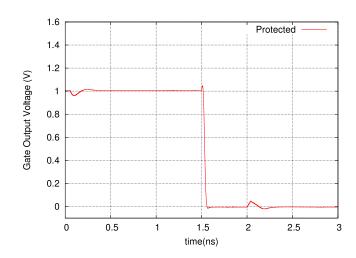

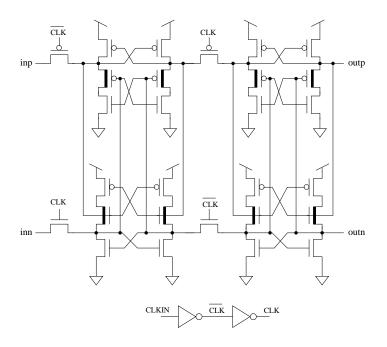

| VII.6  | Radiation tolerant flip-flop                                                                | 140  |

| VII.7  | a) Circuit under consideration b) Waveform at different nodes                               | 143  |

| VII.8  | Area and delay overhead of our radiation hardening design approach for different coverage   | 148  |

| FIGURE | ·<br>·                                                                                                                                                                              | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| VIII.1 | Arrival time propagation using a NAND2 gate                                                                                                                                         | 158  |

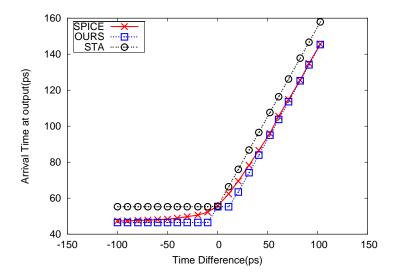

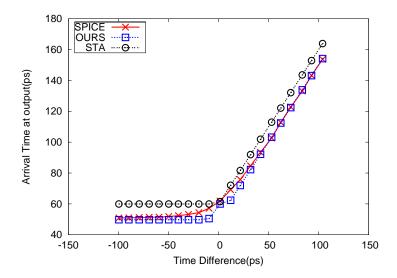

| VIII.2 | Plot of arrival times at output of NAND2 gate calculated through various means for the transition $00 \rightarrow 11 \dots \dots \dots \dots$ .                                     | 162  |

| VIII.3 | Plot of arrival times at output of NAND2 gate calculated through various means for the transition $11 \rightarrow 00 \ldots \ldots \ldots \ldots$                                   | 163  |

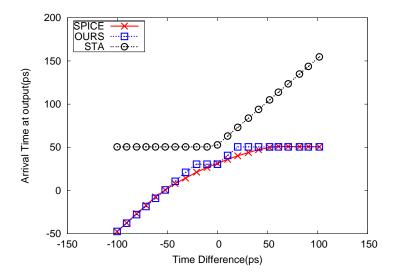

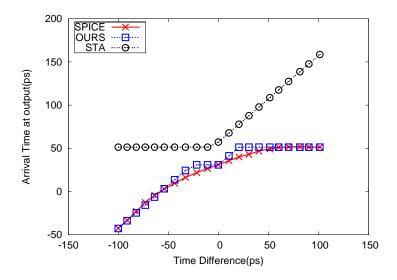

| VIII.4 | Plot of arrival times at output of NOR2 gate calculated through various means for the transition $00 \rightarrow 11 \dots \dots \dots \dots$                                        | 164  |

| VIII.5 | Plot of arrival times at output of NOR2 gate calculated through various means for the transition $11 \rightarrow 00$                                                                | 165  |

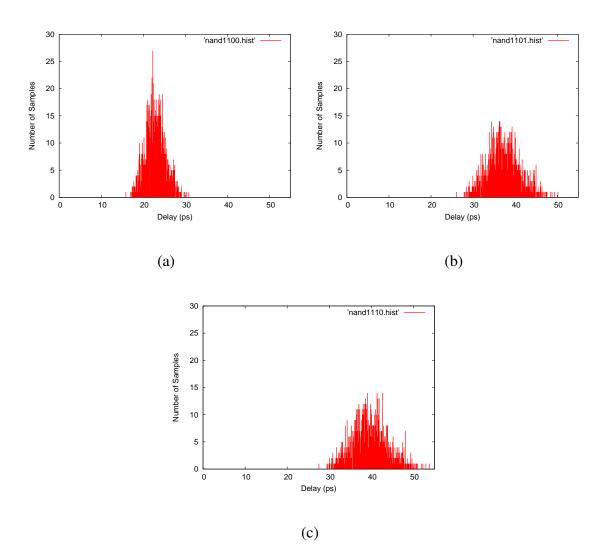

| VIII.6 | Characterization of NAND2 delay for all input transitions which cause a rising output. a) $11 \rightarrow 00$ , b) $11 \rightarrow 01$ and c) $11 \rightarrow 10 \dots \dots \dots$ | 167  |

| VIII.7 | Characterization of NAND2 delay for all input transitions which cause a falling output. a) $00 \rightarrow 11$ , b) $01 \rightarrow 11$ and c) $10 \rightarrow 11$                  | 168  |

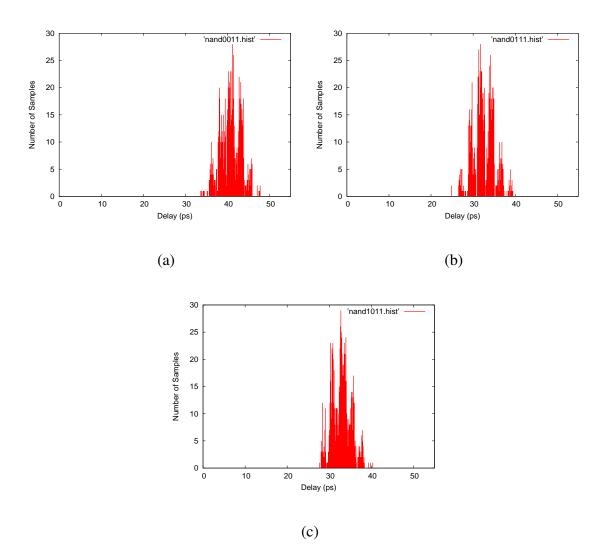

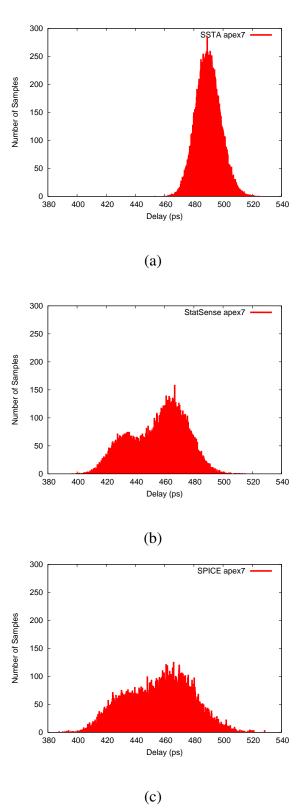

| VIII.8 | Delay histograms for a) SSTA, b) StatSense and c) SPICE (for apex7)                                                                                                                 | 172  |

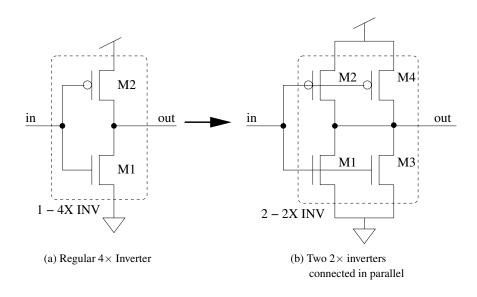

| IX.1   | 4× Inverter implementations                                                                                                                                                         | 182  |

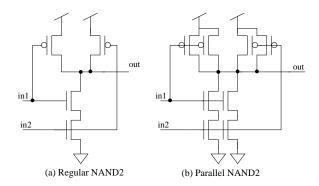

| IX.2   | 2 input NAND gate a) Regular b) Parallel                                                                                                                                            | 183  |

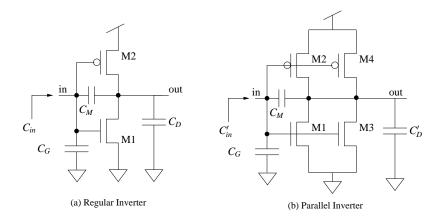

| IX.3   | Capacitance of various nodes a) Regular inverter, b) Parallel inverter                                                                                                              | 185  |

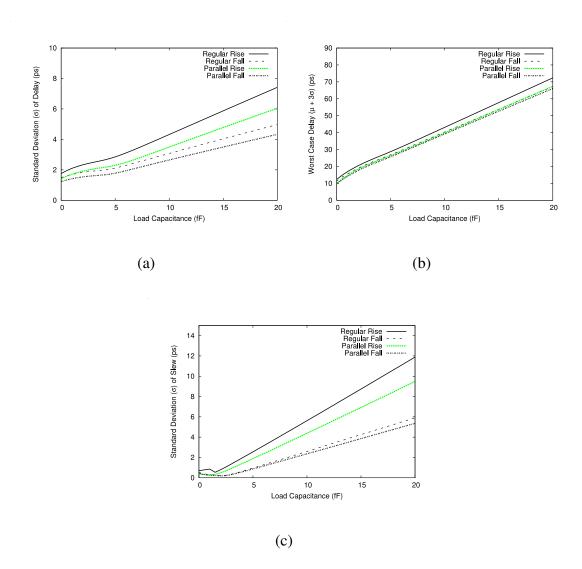

| IX.4   | Results for $4\times$ regular and parallel inverters: a) Standard deviation of delay, b) Worst case delay and c) Standard deviation of output slew                                  | 188  |

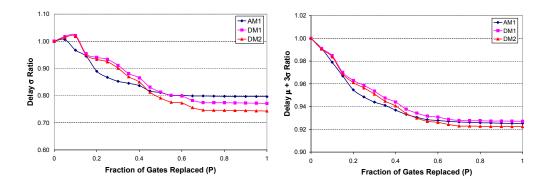

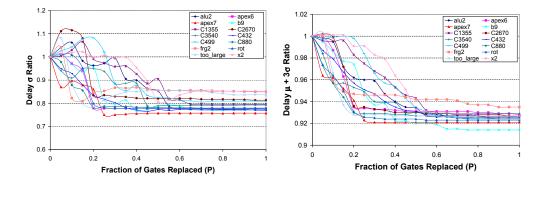

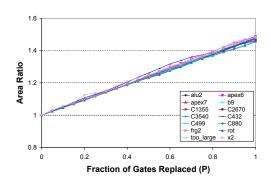

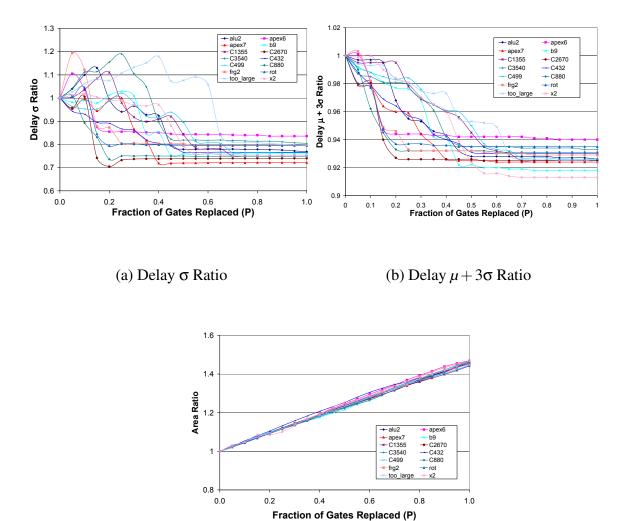

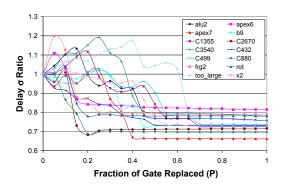

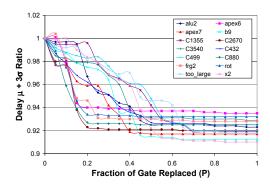

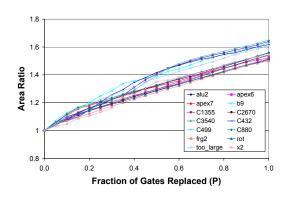

| IX.5   | Ratio of results of the proposed approach compared to regular circuits for different values of $P$                                                                                  | 194  |

| IX.6   | Delay $\sigma$ , $\mu + 3\sigma$ and area ratio of the proposed approach compared to regular circuits for different values of $P$ for area mapped designs                           | 195  |

| IX.7   | Delay $\sigma$ , $\mu + 3\sigma$ and area ratio of the proposed approach compared to regular circuits for different values of <i>P</i> for DM1 designs                              | 196  |

| FIGURE |                                                                                                                                                        | Page  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| IX.8   | Delay $\sigma$ , $\mu + 3\sigma$ and area ratio of the proposed approach compared to regular circuits for different values of <i>P</i> for DM2 designs | . 197 |

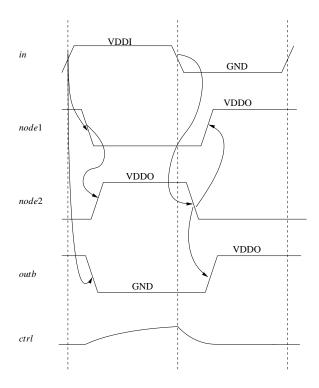

| X.1    | Conventional voltage level shifter                                                                                                                     | 203   |

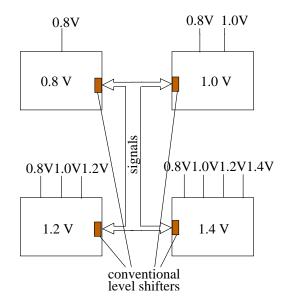

| X.2    | Multi-voltage system using CVLS                                                                                                                        | 204   |

| X.3    | Multi-voltage system using SS-TVLS                                                                                                                     | 205   |

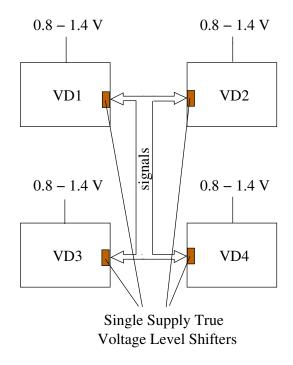

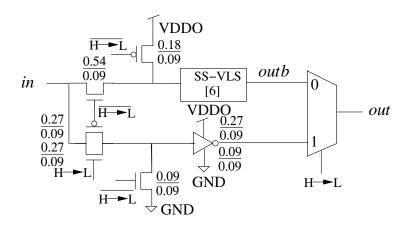

| X.4    | Novel single supply true voltage level shifter                                                                                                         | 208   |

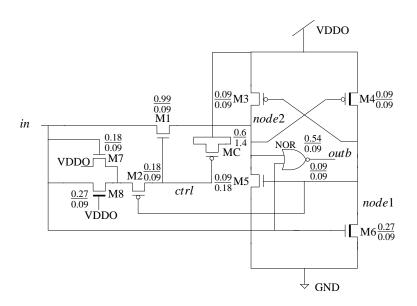

| X.5    | Timing diagram for the proposed SS-TVLS                                                                                                                | 209   |

| X.6    | Combination of an inverter and SS-VLS by Khan et al                                                                                                    | 211   |

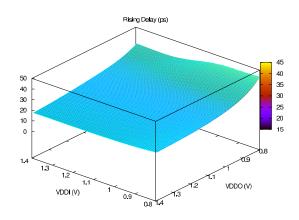

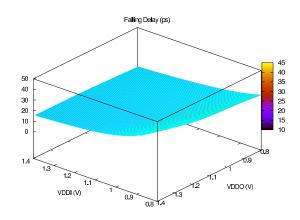

| X.7    | Delay of SS-TVLS a) rising, b) falling                                                                                                                 | 217   |

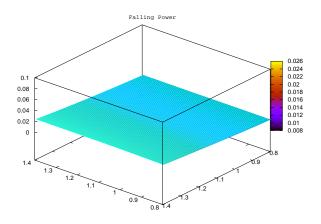

| X.8    | Power of SS-TVLS a) rising, b) falling                                                                                                                 | 218   |

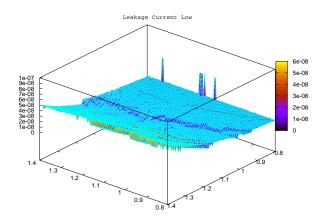

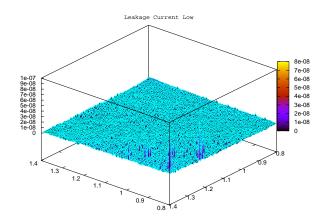

| X.9    | Leakage current of SS-TVLS a) high, b) low                                                                                                             | 219   |

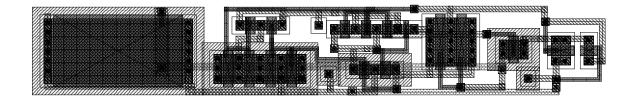

| X.10   | Layout of the proposed SS-TVLS                                                                                                                         | 220   |

#### CHAPTER I

## INTRODUCTION

Reliability of VLSI (Very Large Scale Integration) systems has always been a major concern. Integrated circuits (ICs) have always been subjected to several reliability degrading factors such as manufacturing defects (for example, wire shorts, wire opens, etc), electromigration, noise, etc. To deal with these issues, various forms of fault tolerance have been built into digital systems for the past several decades. Recently, in the deep sub-micron (DSM) era, with continuously decreasing device feature sizes, lowering supply voltages and increasing operating frequencies, the tolerance of VLSI systems against these effects has significantly decreased. In addition to this, several new factors such as process variations, aging, etc now further adversely affect digital VLSI system reliability. Therefore, in the DSM regime, the design of reliable digital VLSI systems has become very challenging.

There are many types of noise effects in VLSI systems, like power and ground noise, capacitive coupling noise, radiation particle strikes or single event effects (SEEs), etc. With technology scaling, ICs have become very sensitive to radiation particle strikes [1, 2, 3, 4, 5, 6, 7]. Radiation particle strikes affect the electrical behavior of a circuit temporarily, and can result in functional errors. Such errors are often referred to as *soft* or *transient errors*. Researchers expect about an 8% increase in soft error rate (SER) per logic state bit each technology generation [6, 7]. Also, the number of logic state bits on a chip double each technology generation. This further increases the sensitivity of ICs to radiation particle strikes with technology scaling. It is expected that the SER for chips implemented in 16 nm technology will be almost 100× of the SER of chips implemented in 180 nm technology [6, 7]. Also, with device scaling, the variations of key device parameters are

The journal model is *IEEE Transactions on Automatic Control*.

increasing at an alarming rate [8, 9, 10], making it difficult to predict the performance of a VLSI design. Thus, both these issues (radiation particle strikes and process variations) result in unpredictable behavior of circuits and hence severely degrade the reliability of VLSI systems. Due to the widespread use of modern VLSI systems, it is necessary to address these issues during the design phase, to improve system reliability and resilience to radiations and process variations. This is the focus of this dissertation.

In the remainder of this chapter, Section I-A provides background information about radiation particle strikes and process variations. It also describes how these issues affect VLSI circuit operation. The goals of the research work presented in this dissertation are stated in Section I-B. Section I-B also provides an outline of the remaining chapters of this dissertation. Finally, a chapter summary is provided in Section I-C.

## I-A. Background and Motivation

This section provide some background information about radiation particle strikes and process variations, to aid in understanding the remainder of this dissertation. It also describes how these issues affect VLSI system operation, and how they are expected to scale in future technologies.

### I-A.1. Radiation Particle Strikes

Single event effects (SEEs) are caused when radiation particles such as protons, neutrons, alpha particles, or heavy ions strike sensitive regions (usually reverse-biased p-n junctions) in VLSI designs. These radiation particles strikes can deposit a charge, resulting in a voltage pulse or glitch at the affected node. This radiation-induced voltage glitch can result in a soft or transient error.

Radiation particle strikes are very problematic for memories (latches, SRAMs and

DRAMs) since they can directly flip the stored state of a memory element, resulting in a *Single Event Upset (SEU)* [1, 2]. Although radiation-induced errors in sequential elements will continue to be problematic for high performance microprocessors, it is expected that soft errors in combinational logic will dominate in future technologies [4, 11, 12], as discussed later. Radiation strikes in combinational circuits are referred to as *Single Event Transients (SETs)*. In a combinational circuit, a voltage glitch due to a radiation particle strike can propagate to the primary output(s) of the circuit, which can result in an incorrect value being latched by the sequential element(s), hence resulting in single or multiple bit upsets. Whether or not a voltage glitch induced by a radiation particle strike at any gate in a combinational circuit propagates to the primary outputs (and results in a failure) depends upon three masking factors. These masking factors are [4, 12]:

- Electrical masking occurs when a voltage glitch at a circuit node, induced by a radiation particle strike attenuates as it propagates through the circuit to the primary

outputs. Electrical masking can reduce the voltage glitch magnitude to a value which

cannot cause any soft errors.

- Logical masking occurs when there is no functionally sensitizable path from the node

in the circuit where a radiation particle strikes, to any primary output of the circuit.

Hence, logical masking properties of a gate can be estimated using logic information

alone.

- *Temporal masking* occurs if a voltage glitch due to a radiation particle strike reaches the primary outputs of a circuit at an instant other than the latching window of the sequential elements of the circuit. Temporal masking only depends upon the frequency of operation of the circuit. Its influence is identical for all gates in the circuit (for a given voltage glitch due to a particle strike). Therefore, it provides a circuit some gratuitous radiation tolerance against soft errors.

Note that all these masking factor reduce the severity of a radiation particle strike in combinational circuits. In other words, if a gate in a circuit is masked to a large extend by any of these masking factors, then it is unlikely (low probability) that a radiation particle strike at the output of that gate will have any effect on the primary outputs of the circuit. Only those gates in a combinational circuit which exhibit a low degree of masking due to these three factors (referred to as *sensitive gates*) contribute significantly to the failure of the circuit due to soft errors.

Until recently, radiation particle strikes were considered troublesome only for military and space electronics. This is mainly due to the abundance of radiation particles in the operating environment of such systems. In fact, the first confirmed radiation-induced upsets in space (four upsets in 17 years of satellite operation) was reported in 1975 [13]. However, just four years later (i.e in 1979), soft errors were also observed in terrestrial microelectronics [1]. Since then, with technology scaling, several cases of soft errors or upsets have been observed in both space as well as terrestrial electronics [11]. Therefore, for applications such as space, military and critical terrestrial (for example biomedical) electronics, which place a stringent demand on reliable circuit operation, it is important to use radiation tolerant circuits. To efficiently design radiation tolerant circuits, it is important to understand the effects of radiation particle strikes on VLSI systems.

The rest of this section is devoted to a discussion on the physical origin of radiation particles, how these particle strikes result in voltage transients, the modeling of a radiation particle strike in circuit level simulations, and the impact of technology scaling on the sensitivity of VLSI designs to radiation particle strikes.

## I-A.1.a. Physical Origin of Radiation Particles

In space, the cosmic rays enter the solar system from the outside which are referred to as galatic cosmic rays. These rays are high-energy charged particles, composed of protons,

electrons, and heavier nuclei [14]. These energy particles are primarily responsible for soft errors in space electronics [11]. Apart from galactic cosmic rays, solar event protons, and protons trapped in the earth's radiation belts are the other sources of protons present in the earth's atmosphere [11]. These are also capable of producing SEEs. Alpha-particles may also originate from radioactive contaminations in IC packages [11]. In fact, the first soft error reported for terrestrial electronics [1] was due to alpha-particles that originated from IC packaging materials. Recently, flip-chip packages have been identified as a source of radiation particles (from the Pb-Sn solder bumps). This aggravates the problem of radiation hardening because a source of radiation particles is present extremely close to the die. Also at the surface of the earth, neutrons induced upsets have found to be very problematic. Several studies have found that the neutrons from cosmic rays are a significant source of soft errors for SRAMs and DRAMs [11] operating at the earth's surface. These atmospheric neutrons result when high energy galactic cosmic rays collide with other particles in the earth's atmosphere. Thus, the neutron flux varies a lot with altitude and latitude [11, 4, 15]. The authors of [4] reported that the neutron flux at an altitude of 10,000 feet in Leadville, CO is approximately 13× greater than that at the sea level. Due to this, a large number of neutron induced upsets were observed in DRAMs at 10,000 feet in Leadville, CO, while no upsets were observed when the DRAM was placed 200m underground in a salt mine [11].

Different radiation particles such as protons, neutrons, alpha-particles and heavy ions have different mechanisms by which they deposit charge in VLSI designs. These mechanisms are explained next.

### I-A.1.b. Charge Deposition Mechanisms

There are two methods by which a radiation particle deposits charge in VLSI designs: direct ionization and indirection ionization.

Direct Ionization: A radiation particle generates electron-hole pairs along its path as it passes through a semiconductor material, as shown in Figure I.1. In this process, the radiation particle loses its energy. After losing all its energy, the particle comes to rest. The energy transferred by the radiation particle is described by its linear energy transfer (LET) value. LET is defined as the energy transferred (for electron-hole pair generation) by the radiation particle per unit length, normalized by the density of the target material (for VLSI designs, this is the density of Silicon). Thus the unit of LET is MeV-cm<sup>2</sup>/mg. The LET of a radiation particle also corresponds to the charge deposited by the radiation particle per unit length. In silicon, the amount of charge deposited ( $Q_D$ ) by a radiation particle per unit length (in microns) is calculated as  $Q_D = 0.01036 \cdot LET$ . For example, a particle with an LET of 97 MeV-cm<sup>2</sup>/mg can deposit  $1pC/\mu m$ . Heavy ions<sup>1</sup> and alpha-particles primarily deposit charge in a semiconductor by direct ionization. Light particles such as protons and neutrons do not deposit enough charge by direct ionization to cause a soft error.

Indirect Ionization: Protons and neutrons typically deposit charge by indirect ionization, which can result in significant numbers of soft errors [11, 4, 16]. When a high-energy light radiation particle (such as a proton or a neutron) passes through a semiconductor material, it can collide with nuclei, resulting in nuclear reactions. These nuclear reactions may produce secondary particles such as alpha-particles or heavy ions. These secondary particles then deposit charge by direction ionization and if the charge is deposited at different locations in a chip then multiple soft errors may occur [11, 16]. Thus, the charge deposited by a light particle through indirect ionization heavily depends upon the location and the angle of incidence of the particle strike.

When charge is deposited a radiation event, this charge is *collected* by different terminals of the devices, resulting in voltage and current transients in the device. The charge

<sup>&</sup>lt;sup>1</sup>Heavy ion are ions whose atomic number is greater than equal to 2 [11].

deposited by a radiation particle strike may get collected through different charge collection mechanisms which are briefly described next.

## I-A.1.c. Charge Collection Mechanisms

There are three charge collection mechanisms as discussed below:

Drift-diffusion: Consider an NMOS transistor shown in Figure I.1. The source, gate and bulk terminals of the NMOS transistor are connected to GND. The drain terminal is connected to VDD. The drain-bulk junction is reverse-based and hence there is a strong electric field in the depletion region this junction from the drain to the bulk. Since radiation particle generated free electron-hole pairs, the electric field present in the depletion region of the drain-bulk junction leads to the collection of electrons at the drain and of holes at the bulk. Thus, the reverse-biased electric field leads to the charge collection at the drain. Therefore, the reverse biased junctions are most sensitive to a radiation particle strike. Assume that a radiation particle strikes this (drain-bulk) junction and generates electron-hole pairs along its path as shown in Figure I.1. Immediately after the generation of this ionized track, the depletion region collapses due to the separation of free electrons and holes by the drift process in the depletion region. As mentioned earlier, charge (electrons and holes) separation occurs due to the presence of a high electric field, which pulls the electrons up (towards the  $n^+$  diffusion) and pushes the holes down (towards the p-substrate). This phenomenon reduces the width of the depletion region of the drain-bulk junction. As a result, the potential drop across the depletion region decreases (before the radiation strike, the potential drop across the depletion region was VDD). As the voltage between the drain and the bulk terminals  $(n^+ \text{ and } p - substrate)$  is still VDD, the decrease in the potential across the depletion region causes a voltage drop in the p-substrate region. This causes the drain-bulk junction electric field to penetrate into the p-substrate region, beyond the original depletion region and hence enhances the flow of electrons from the substrate (these

electrons are generated by the radiation particle strike in the substrate region) to the depletion region. This enhanced electron flow process is referred to as *funneling* as shown in Figure I.1. The electrons present in the depletion region drift to the drain  $(n^+)$  diffusion region and hence get collected. Thus, charge is said to be collected through the *drift* process (or the *funnel-assisted drift process*). The funneling process increases the depth of the region with a strong electric field beyond the original depletion region. Hence it increases the amount of charge collection by the drift process [17, 18, 19, 11].

Fig. I.1. Charge deposition and collection by a radiation particle strike

As the electric field continues to pull electrons up, it also pushes the holes down (away from the depletion region) which allows the drain-bulk depletion region to recover and regain its original width. After the recovery of the depletion region, the electrons which were not collected by the funnel assisted drift process diffuse towards the depletion region (due to their concentration gradient) and then get pulled by the junction electric field towards the  $n^+$  drain diffusion region. Thus the charge is also collected at the  $n^+$  region by the *diffusion* process. It was reported in [18], that in a lightly doped substrate, most of the charge

collection is through drift only whereas, more heavily doped substrates demonstrate charge collection due to both the drift and the diffusion processes [20, 17, 18, 19, 11]. In the DSM technologies, the substrate is heavily doped and hence charge collection at the drain node occurs due to both drift and diffusion processes.

Bipolar Effect: Consider an NMOS transistor (an n-channel transistor located in a p-well) in cut-off state, and with its gate and source terminals at GND and drain terminal at VDD. The electrons generated by a radiation particle strike can be collected at either the drain-well junction or the well-substrate junction. However, the radiation-induced holes are left in the p-well, which reduces the source-well potential barrier (due to the increase in the potential of the p-well). Thus, the source injects electrons into the channel which can be collected at the drain. This increases the total amount of the charge collected at the drain node and hence reduces the tolerance of the device to a radiation particle strike. This effect is called bipolar effect because the source-well-drain of the NMOS (PMOS) transistor act as a n-p-n (p-n-p) bipolar transistor. This effect mimics the "on" state of the parasitic bipolar transistor. With technology scaling, the channel length decreases which in turn reduces the base width (of the n-p-n transistor). Hence, this effect becomes more pronounced in scaled technologies [19, 11, 21].

Alpha-particle Source-drain Penetration (ALPEN): This charge collection mechanism results when a radiation particle strikes a MOS transistor at near-grazing incidence, such that the particle penetrates through both the source and the drain regions of the transistor. A radiation particle penetration through both the source and the drain regions of the MOS transistor (nominally in the off state) perturbs the potential in the channel region. In this case, the charge collection at the drain of the MOS transistor happens in three phases: an initial funneling phase while there is no source/drain barrier, a bipolar phase as the source/channel barrier recovers, and subsequent diffusion phase (after the device potentials have recovered). This process also mimics the "on" state of the transistor. It is reported

Fig. I.2. Current pulse model for a radiation particle strike plotted for different values of Q,  $\tau_{\alpha}$  and  $\tau_{\beta}$

that the charge collection due to the ALPEN mechanism increases rapidly for effective gate lengths below about  $0.5\mu m$  [19, 11]. This mechanism may increase the radiation susceptibility of DSM devices.

The charge collected (through any mechanism) at the drain node of a device results in voltage transients at that node. These voltage transients in turn may result in soft errors.

## I-A.1.d. Circuit Level Modeling of a Radiation Particle Strike

A radiation particle strike in a device induces current flow from the n type diffusion to the p type diffusion. Traditionally, the radiation-induced current at circuit level is modeled by a double-exponential current pulse [20] for circuit level simulations. The expression for this pulse is

$$i_{seu}(t) = \frac{Q}{(\tau_{\alpha} - \tau_{\beta})} (e^{-t/\tau_{\alpha}} - e^{-t/\tau_{\beta}})$$

(1.1)

Here Q is the amount of charge collected as a result of the ion strike, while  $\tau_{\alpha}$  is the

collection time constant for the junction and  $\tau_{\beta}$  is the ion track establishment constant. This current pulse is injected at any node in a circuit, to simulate a radiation particle strike in SPICE at that node. Typically  $\tau_{\alpha}$  is of the order of 100 ps and  $\tau_{\beta}$  is of the order of tens of picoseconds [12, 11]. Figure I.2 shows  $i_{seu}(t)$  for several values of Q,  $\tau_{\alpha}$  and  $\tau_{\beta}$ . The minimum amount of charge required to result in an error is referred to as critical charge  $(Q_{cri})$ .

Note that in DSM devices, the radiation-induced current may be very different from this double exponential pulse [19, 22]. This is because, in DSM devices, the substrate is more heavily doped compared to older technologies. As mentioned earlier, heavily doped substrate demonstrate charge collection due to both the drift and the diffusion processes [20, 17, 18, 19, 11]. Therefore, a significant amount of charge is collected in DSM devices, due to both the drift and the diffusion processes. Whereas, in older technologies, the charge was mainly collected by the drift process. Since, the double exponential current pulse of Equation 1.1 was derived for an older technology by using the fact the charge is mainly collected by the drift process [20], the radiation-induced current pulse can be different from this double exponential current pulse in DSM devices. Therefore, for an accurate analysis, device-level simulations of radiation particle strikes in transistors need to be performed. However, for circuit level analysis and design, it is adequate to use the current model of Equation 1.1 to model the worst case radiation particle strike [11, 12].

## I-A.1.e. Impact of Technology Scaling on the Radiation Tolerance of VLSI Design

In the DSM era, the number of transistors on a chip is still increasing, in accordance with Moore's law [23]. This is facilitated by decreasing device and interconnect dimensions, which have led to a reduction in the node capacitances of VLSI circuits. Hence, in modern VLSI processes, even a small amount of charge deposited by a radiation particle (or low energy particle) is sufficient to cause a significant change in the voltage of a node. In other

words, DSM circuits are susceptible even to low energy radiation particle strikes. This is further aggravated by decreasing supply voltages and increasing operating frequencies in the DSM regime.

Although, these technology scaling trends severely reduce the radiation tolerance of VLSI circuits, there are couple of factors associated with technology scaling which improves the radiation tolerance of VLSI circuits. The area of transistors reduces with technology scaling and hence, the probability with which a device in a circuit experiences a radiation particle strike reduces as well. Also, the decreasing supply voltages reduce the charge collection efficiency. Therefore, the devices implemented in newer technologies (with lower supply voltages) collect less charge compared to the devices implemented in older technologies (with higher supply voltages). A reduction in the amount of charge collected (due to lowering supply voltages) with technology scaling improves the radiation resilience of VLSI circuits.

The soft error rate (SER) is typically measured as failure in time (FIT), where a FIT is defined as the number of failures in 10<sup>9</sup> hours of operation. Figure I.3 shows the SER for an Alpha [24] processor, which was implemented using different technology nodes [4]. Figure I.3 shows the individual contributions of SRAMs, latches (for different pipeline depths) and combinational logic (for different pipeline depths with a fanout factor of 4) to the overall SER of the Alpha processor. Observe from Figure I.3 that the overall chip SER, which is the sum of the contributions of SRAMs, latches and combinational logic, increases with decreasing feature sizes. This verifies that radiation particle strikes are becoming increasingly problematic for the reliability of VLSI systems, as predicted by the theory.

Also, observe from Figure I.3 that in older technologies the contribution of the SRAMs and latches to the overall chip SER was much higher than that of combinational logic. Hence, traditionally, radiation particle strikes were mainly considered problematic for memories (SRAMs, DRAMs and latches) only. However, as the feature size is reduced

below 45 nm, the SER contribution of combinational logic has increased by a large factor (more than 10<sup>9</sup>), whereas the SER contribution of SRAMs (in absolute terms) has stayed relatively constant (as shown in Figure I.3). This is because of the fact that with technology scaling, heavily pipelined circuits are increasingly used, which leads to a reduction in the depth of combinational circuits. Due to this, the effect of the three masking factors (as described earlier) reduces and hence, fewer SET events are masked. Hence, it is expected that radiation particle strikes in combinational logic will be more problematic than in memories in future technologies [4, 11, 12]. Note that the SER of the Alpha processor due to radiation particle strikes in latches also increased slightly with decreasing feature sizes. Therefore, it will be necessary to harden both combinational logic and memories, to improve the radiation resilience of VLSI systems implemented using future DSM processes.

Many critical applications such as space, military and critical terrestrial electronics (for example biomedical circuits and high performance servers) electronics place a stringent demand on reliable circuit operation. Therefore, efficient analysis and design techniques are required to harden VLSI circuits (both combinational logic and memories) against radiation events. Developing these is one of the two goals of this dissertation.

### I-A.2. Process Variations

Another important problem encountered with technology scaling in the DSM era is the increase in process variations. With the continuous scaling of devices and interconnects, variations in key device and interconnect parameters such as channel length (L), threshold voltage  $(V_T)$ , oxide thickness  $(T_{ox})$ , wire width  $(W_M)$ , and wire height (H) are increasing at an alarming rate [8, 9, 10]. Due to this, the performance of different die of the same IC can vary widely, resulting in a significant yield loss, which translates into higher manufacturing costs.

The two major sources of variability in device parameters are a) limited control over

Fig. I.3. SER of an alpha processor for different technology nodes

the manufacturing process (extrinsic causes of variations) and b) fundamental atomic-scale randomness of the device (intrinsic causes of variations) [8]. The variability that arises due to limited control over the manufacturing process is becoming more and more challenging to control. This is because of the inability of the semiconductor industry to improve manufacturing tolerances at the same pace as technology scaling [8]. For example, the light source (with a wavelength of 193 nm) used in lithography in older technologies ( $\geq$  130 nm) is still used in newer technologies (45 nm and below). Therefore, it is becoming increasingly difficult to control the channel length of transistors with technology scaling [8]. The intrinsic causes of variations are also expected to significantly problematic in future technologies because of the fact that device dimensions are approaching the scale of silicon lattice distances. At this scale, quantum physics needs to be used to explain device operation, which is modeled as a stochastic process. Also, at this scale, the precise atomic configuration of the material significantly affects the electrical properties of the device. Therefore, a small variation in the silicon structure has a large impact on the device performance. For

example, the threshold voltage of a transistor heavily depends on the doping density of the channel region. With technology scaling, the number of dopant atoms required to achieve the desired doping density is getting smaller [8]. Since the placement of dopant atoms in the silicon crystal structure is random, the final number of dopant atoms deposited in the channel region of a transistor is a random variable. Therefore, the threshold voltage of transistors also become a random variable. Variations in interconnect parameters are mainly caused by a limited control over the manufacturing process. Processing steps such as chemical mechanical polishing (CMP) and etching induce variations in interconnects or wire dimensions [8].

The process variations due to these sources can be classified as *systematic variations* and *random variations* [8, 9, 25]. The systematic component is the predictable variation trend across a chip, and is caused by spatial dependencies of device processing, such as Chemical and Mechanical Polishing (CMP) variations [26] and optical proximity effects [27]. The random component is caused by effects such as random fluctuations of the number and location of dopants in the MOSFET channel, polysilicon gate line-edge roughness, etc [8, 9, 10].

Note that in terms of delay variability of a circuit, the contribution of variations in device parameters dominates that of interconnect parameter variations [8]. The variation in device parameters contributes close to 90% of the total variability of the delay of a realistic design [8]. In future technologies, it is expected that the variation in device parameters will continue to be the dominant source of delay variability of a circuit.

## I-A.2.a. Impact of Technology Scaling on Process Variations

Figure I.4 shows the standard deviation of the threshold voltage of transistors ( $\sigma_{V_T}$ ) implemented in different technology nodes [28]. As shown in Figure I.4,  $\sigma_{V_T}$  has increased by a factor of  $\sim 2\times$  for a 45 nm technology compared to a 130 nm process. Note that the

Fig. I.4. Variation in threshold voltage of devices for different technology nodes

absolute value of  $V_T$  is higher for 130 nm process ( $\sim 0.35 \text{ V}$ ) compared to a 45 nm process ( $\sim 0.28 \text{ V}$ ). Similarly, the variation in other device (L and  $T_{ox}$ ) and interconnect (W, H, etc.) parameters has also increased with technology scaling, as reported in [29]. Therefore, unless significant advancements are made in process control, the variation in key device and interconnect parameters is expected to further increase in future technologies.

Additionally, as devices are scaled below 45 nm, the random component of the total variations becomes significantly more problematic than the systematic component [30, 8]. Negligible spatial correlation was observed in the L and  $V_T$  of devices in a test chip fabricated using a 65nm SOI process [30]. However, the random component of L and  $V_T$  variation was quite high in comparison (the standard deviation of L and  $V_T$  variations was 5% and 9% of the mean value respectively). Thus, the L [30, 8, 26] and  $V_T$  [30, 8, 31, 10] variations are expected to be mostly random (or independent) in nature for future deep submicron technologies.

With the increasing amount  $(\sigma/\mu)$  of variations in device and interconnect parameters, it becomes difficult to predict the performance of VLSI designs, and hence it becomes a challenging task to design reliable VLSI systems. The second goal of this dissertation is

to develop efficient analysis and design techniques to address the process variation issue, in order to facilitate the implementation of process variation resilient VLSI circuits. These techniques help improve design yield and hence lower manufacturing costs.

### I-B. Dissertation Overview

Section I-A indicates that radiation particle strikes and process variations can significantly degrade the reliability of VLSI systems. Due to the widespread use of modern VLSI circuits, it is necessary to address these issues while designing VLSI systems, so as to improve their reliability. Therefore, there is a critical need for analysis and design techniques to enable the implementation of VLSI systems that are resilient to radiation and process variation effects.

The goal of this dissertation is to develop several analysis and design techniques to achieve circuit resilience against radiation particle strikes and process variations. This dissertation consists of two parts.

In the first part of this dissertation (Chapters II to VII), four analysis approaches for analyzing the effects of radiation particle strikes in combinational circuits, SRAMs and voltage scaled circuits [32, 33, 34] are presented. Two circuit level hardening approaches [35, 36] are also presented, to harden combinational circuits against a radiation particle strike.

In the second part of this dissertation (Chapters VIII to X), a sensitizable statistical timing analysis approach is presented to improve the accuracy of statistical timing analysis of combinational circuits. Two design approaches are also presented to improve the process variation tolerance of combinational circuits and voltage level shifters (which are used in circuits with multiple interacting supply domains), respectively.

This dissertation is organized as follows.

In Chapter II, an analytical approach is developed to analyze radiation-induced transients in combinational circuits. Efficient and accurate models for radiation-induced transients are required to evaluate the radiation tolerance of a circuit. As mentioned earlier, a radiation particle strike at a node may result in a voltage glitch. The pulse width of this voltage glitch is a good measure of radiation robustness of a design. Thus, an analytical model to estimate the pulse width of the radiation-induced voltage glitch in combinational designs is presented in this chapter. In this approach, a piecewise linear transistor  $I_{DS}$  model is used (instead of a linear RC gate model), and the effect of the ion track establishment constant  $(\tau_{\beta})$  of the radiation-induced current pulse is considered. Both these factors improve the accuracy (in comparison with the best existing approach [37]) of the analytical model for the pulse width computation. The model is applicable to any logic gate, with arbitrary gate size and loading, and with different amounts of charge collected due to the radiation strike. The model can be used to quickly ( $1000 \times$  faster than SPICE [38]) determine the susceptible gates in a design (the gates where a radiation particle strike can result in a voltage glitch with a positive pulse width). The most susceptible gates can then be protected using circuit hardening approaches, based on the degree of hardening desired.

In Chapter III, an analytical model is presented, which efficiently estimates the shape of the voltage glitch that results from a radiation particle strike. A model for the load current  $I_{out}^G(V_{in}, V_{out})$  of the output terminal current of the gate G is used. Again, the model is applicable to any general combinational gate with different loading, and for arbitrary values of collected charge (Q). The effect of the ion track establishment constant  $(\tau_{\beta})$  of the radiation particle induced current pulse is accounted for. The voltage glitch estimated by this analytical model can be propagated to the primary outputs of a circuit using existing voltage glitch propagation tools. The properties of the voltage glitch (such as its magnitude, glitch shape and width) at the primary outputs can be used to evaluate the SEE robustness of the circuit. Based on the result of this analysis, circuit hardening approaches can be

implemented to achieve the level of radiation tolerance required.

Chapter IV presents a model for the dynamic stability of an SRAM cell in the presence of a radiation particle strike. Such models are required since SRAM stability analysis is crucial from an economic viewpoint, given the extensive use of memory in modern processors and SoCs. Static noise margin (SNM) based stability analysis often results in pessimistic designs because SNM cannot capture the transient behavior of the noise. Therefore, to improve analysis accuracy, a dynamic stability analysis is required. The model proposed in this chapter utilizes the double exponential current pulse of Equation 1.1 for modeling a radiation particle strike, and is able to predict (more accurately than the most accurate prior approach [39]) whether a radiation particle strike will result in a state flip in a 6T-SRAM cell (for given values of Q,  $\tau_{\alpha}$  and  $\tau_{\beta}$ ). This model enables a designer to quickly (2000× faster than SPICE) and accurately analyze SRAM stability during the design phase.

In Chapter V, an analysis of the effects of voltage scaling on the radiation tolerance of VLSI systems is presented. For this analysis, 3D simulations of radiation particle strikes on the output of an inverter (implemented using DVS and sub-threshold design) were performed. The radiation particle strike on an inverter was simulated using Sentaurus-DEVICE [40] for different inverter sizes, inverter loads, the supply voltage values (VDD) and the energy of the radiation particles. From these 3D simulations, several non-intuitive observations were made, which are important to consider during radiation hardening of such DVS and sub-threshold circuits. Based on these observations, several guidelines are proposed for radiation hardening of such designs. These guidelines suggest that traditional radiation hardening approaches need to be revisited for DVS and sub-threshold designs. A charge collection model for DVS circuits is also proposed, using the results of these 3D simulations. The parameters of this charge collection model can be included in transistor model cards in SPICE, to improve the accuracy of SPICE based simulations of radiation events in DVS circuits.

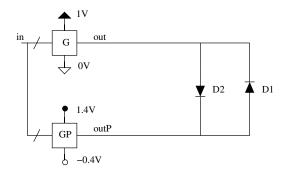

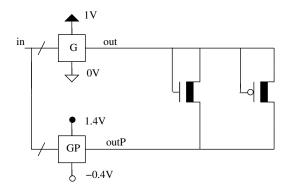

Chapter VI presents a radiation tolerant combinational circuit design approach which is based on diode clamping action. This diode clamping based hardening approach is based on the use of shadow gates, whose task it is to protect the primary gate in case it experiences a radiation strike. The gate to be protected is duplicated locally, and a pair of diode-connected transistors (or diodes) is connected between the outputs of the original and the shadow gate. These diodes turn on when the voltage across the two gate outputs deviates (during a radiation strike). A methodology is also presented to protect specific gates of the circuit based on electrical masking, in a manner that guarantees radiation tolerance for the entire circuit and also keeps the area and delay overhead low. An improved circuit level hardening algorithm is also proposed, to further reduce the delay and area overhead. Note that the diode clamping based approach is suitable for hardening a circuit against low energy particle strikes.

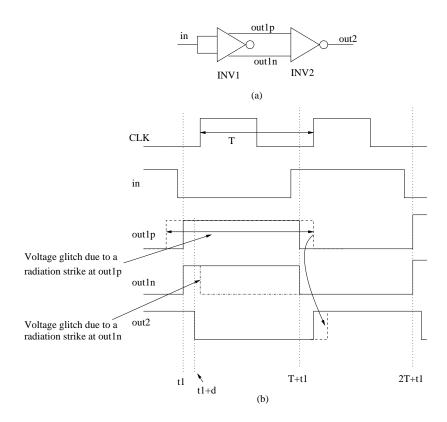

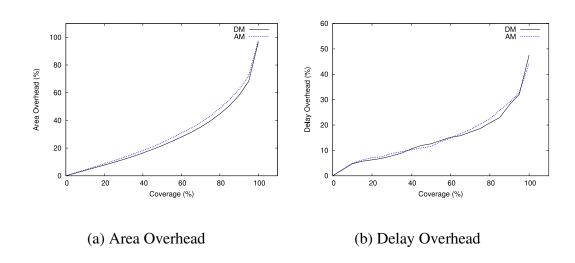

In Chapter VII, another radiation tolerant combinational circuit design approach is presented, which is called the *split-output based hardening approach*. This hardening approach exploits the fact that if a gate is implemented using only PMOS (NMOS) transistors then a radiation particle strike can result only in logic 0 to 1 (1 to 0) transient. Based on this observation, radiation hardened variants of regular static CMOS gates are derived. Split-output based radiation hardened gates exhibit an extremely high degree of radiation tolerance, which is validated at the circuit level. Hence, this approach is suitable for hardening against medium and high energy radiation particles. Using split-output gates, circuit level hardening is performed based on logical masking, to selectively harden those gates in a circuit which contribute maximally to the soft error failure of the circuit. The gates whose outputs have a low probability of being logically masked are replaced by their radiation tolerant counterparts, such that the digital design achieves a soft error rate reduction of a desired amount (typically 90%). The split-output based hardening approach is able to harden combinational circuits with a modest layout area and delay penalty.

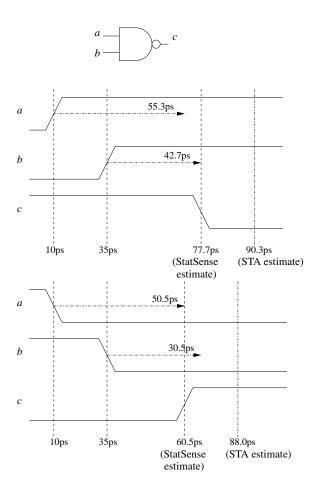

Chapter VIII presents the sensitizable statistical timing analysis (StatSense) methodology, developed to remove the pessimism due to two sources of inaccuracy which plague current statistical static timing analysis (SSTA) tools. Specifically, the StatSense approach implicitly eliminates false paths, and also uses different delay distributions for different input transitions for any gate. StatSense consists of two phases. In the first phase, a set of *N* logically sensitizable vector transitions which result in the largest delays for a circuit, are obtained. In the second phase, these delay-critical sensitizable input vector transitions are propagated using a Monte-Carlo based technique to obtain the delay distribution at the outputs. The specific input transitions at any gate are known after the first phase, and so the gate delay distribution corresponding to these input transitions is utilized in the second phase. The second phase performs Monte Carlo based statistical static timing analysis (SSTA), using the appropriate gate delay distribution corresponding to the particular input transition for each gate. The StatSense approach is able to significantly improve the accuracy of SSTA analysis. The circuit delay distribution obtained using StatSense closely matches that obtained by SPICE based Monte Carlo simulations.

In Chapter IX, a process variation tolerant design approach for combinational circuits is presented, which exploits the fact that random variations can cause a significant mismatch in two identical devices placed next to each other on the die. In this approach, a large gate is implemented using an appropriate number (> 1) of smaller gates, whose inputs and outputs are connected to each other in parallel. This parallel connection of smaller gates to form a larger gate is referred to as a *parallel gate*. Since the L and  $V_T$  variations are largely random and have independent variations in smaller gates, the variation tolerance of the parallel gate is improved. The parallel gates are implemented as single layout cells. By careful diffusion sharing in the layout of the parallel gates, it is possible to reduce the input and output capacitance of the gates, thereby improving the nominal circuit delay as well. An algorithm is also developed to selectively replace critical gates in a circuit by

their parallel counterparts, in order to improve the variation tolerance of the circuit. Monte Carlo simulations demonstrate that this process variation tolerant design approach achieves significant improvements in circuit level variation tolerance.

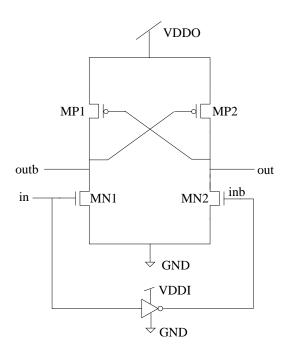

In Chapter X, a novel process variation tolerant single-supply true voltage level shifter (SS-TVLS) design is presented. It is referred to as "true" since it can handle both low to high, or high to low voltage level conversions. The SS-TVLS is the first VLS design which can handle both low-to-high and high-to-low voltage translation without a need for a control signal. The use of a single supply voltage reduces circuit complexity, by eliminating the need for routing both supply voltages. The proposed circuit was extensively simulated in a 90nm technology using SPICE. Simulation results demonstrate that the level shifter is able to perform voltage level shifting with low leakage for both low to high, as well as high to low voltage level translation. The proposed SS-TVLS is also more tolerant to process and temperature variations, compared to a combination of an inverter along with the non-true VLS solution [41].

Finally, in Chapter XI, this dissertation is concluded. This chapter also presents some future directions for research, and a summary of the broader impact of this work.

#### I-C. Chapter Summary