# POWER AND MEMORY EFFICIENT HASHING SCHEMES FOR SOME NETWORK APPLICATIONS

A Dissertation

by

HEEYEOL YU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2009

Major Subject: Computer Science

# POWER AND MEMORY EFFICIENT HASHING SCHEMES FOR SOME NETWORK APPLICATIONS

A Dissertation

by

## HEEYEOL YU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

# Approved by:

Chair of Committee,

Committee Members,

Duncan M. Walker

Riccardo Bettati

Gwan Choi

Head of Department, Valerie E. Taylor

May 2009

Major Subject: Computer Science

#### ABSTRACT

Power and Memory Efficient Hashing Schemes

for Some Network Applications. (May 2009)

Heeyeol Yu, B.S., Korea Advanced Institute of Science and Technology;

M.S., University of California, Los Angeles

Chair of Advisory Committee: Dr. Rabi Mahapatra

Hash tables (HTs) are used to implement various lookup schemes and they need to be efficient in terms of speed, space utilization, and power consumptions. For IP lookup, the hashing schemes are attractive due to their deterministic  $\mathcal{O}(1)$  lookup performance and low power consumptions, in contrast to the TCAM and Trie based As the size of IP lookup table grows exponentially, scalable lookup performance is highly desirable. For next generation high-speed routers, this is a vital requirement when IP lookup remains in the critical data path and demands a predictable throughput. However, recently proposed hash schemes, like a Bloomier filter HT and a Fast HT (FHT) suffer from a number of flaws, including setup failures, update overheads, duplicate keys, and pointer overheads. In this dissertation, four novel hashing schemes and their architectures are proposed to address the above concerns by using pipelined Bloom filters and a Fingerprint filter which are designed for a memory-efficient approximate match. For IP lookups, two new hash schemes such as a Hierarchically Indexed Hash Table (HIHT) and Fingerprint-based Hash Table (FPHT) are introduced to achieve a a perfect match is assured without pointer overhead. Further, two hash mechanisms are also proposed to provide memory and power efficient lookup for packet processing applications.

Among four proposed schemes, the HIHT and the FPHT schemes are evaluated

for their performance and compared with TCAM and Trie based IP lookup schemes. Various sizes of IP lookup tables are considered to demonstrate scalability in terms of speed, memory use, and power consumptions. While an FPHT uses less memory than an HIHT, an FPHT-based IP lookup scheme reduces power consumption by a factor of 51 and requires 1.8 times memory compared to TCAM-based and trie-based IP lookup schemes, respectively. In dissertation, a multi-tiered packet classifier has been proposed that saves at most 3.2 times power compared to the existing parallel packet classifier.

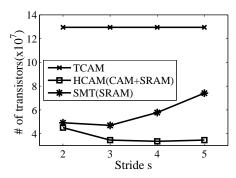

Intrinsic hashing schemes lack of high throughput, unlike partitioned Ternary Content Addressable Memory (TCAM)-based scheme that are capable of parallel lookups despite large power consumption. A hybrid CAM (HCAM) architecture has been introduced. Simulation results indicate HCAM to achieve the same throughput as contemporary schemes while it uses 2.8 times less memory and 3.6 times less power compared to the contemporary schemes.

To my family

#### ACKNOWLEDGMENTS

I would like to thank Dr. Mahapatra for his direction and support over the last 3 years. His faith in my abilities helped mould my transition from a graduate student into a researcher. I would also like to thank Drs. Walker, Bettati, and Choi for serving on my committee and being excellent teachers.

I want to thank my family who support me mentally and financially. In addition, my soccer club, the Korean Aggies Soccer Association (KASA), gave me wonderful joy during my study at Texas A&M University. In particular, I miss Bong Su Koh who always gave me a smile, Sanghyub Kang who was an ex-professional soccer player, Jaewoo Suh who always loves an over-night drink, Won Ju Sung who I just met for one semester, and Hyeongil Kwak who gave spiritual help. Furthermore, I want to give a life-lasting appreciation to Uichin Lee at University of California Los Angeles who helped me in many ways

## NOMENCLATURE

HT Hash Table

LHT Legacy Hash Table

FHT Fast Hash Table

TCAM Ternary Content Addressable Memory

CTCAM Cool TCAM

UTCAM Ultra TCAM

STCAM Selective TCAM

BTCAM Beyond TCAM

ACSM Approximate Concurrent State Machines

SRAM Static Random Access Memory

DRAM Dynamic Random Access Memory

PC Prefix Collapse

CPE Controlled Prefix Expansion

TCP Transport Control Protocol

IP Internet Protocol

SIP Source IP

DIP Destination IP

BF Bloom Filter

MBF Multi-predicate Bloom Filter

FF Fingerprint Filter

SBF Segmented Bloom Filter

SL Successful Lookup

UL Unsuccessful Lookup

SS Successful Search

US Unsuccessful Search

BMF Bloomier Filter

PPC Parallel Packet Classifier

MPC Multi-tiered Packet Classifier

2TPC 2-tiered Packet Classifier

3TPC 3-tiered Packet Classifier

MBHT Multi-predicate Bloom filter Hash Table

HIHT Hierarchically Indexed Hash Table

IT Indexing Tree

HIT Hierarchical Indexing Tree

FPHT Fingerprint-based Hash Table

HCAM Hybrid CAM

SMT Segmented Multibit Trie

# TABLE OF CONTENTS

| CHAPTER |                                                                                                                                                                                                                                                                                                                                     | Page                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| I       | INTRODUCTION                                                                                                                                                                                                                                                                                                                        | . 1                                  |

| II      | RELATED WORKS IN PACKET PROCESSING                                                                                                                                                                                                                                                                                                  | . 9                                  |

|         | A. IP Lookup                                                                                                                                                                                                                                                                                                                        | . 11<br>. 11                         |

| III     | BASICS ON HASH FOR PACKET PROCESSING                                                                                                                                                                                                                                                                                                | . 15                                 |

|         | A. Basic Bloom Filter Theory                                                                                                                                                                                                                                                                                                        | . 18<br>. 20<br>. 20<br>. 21<br>. 22 |

| IV      | A MULTI-TIERED PACKET CLASSIFIER WITH $N$ BFS                                                                                                                                                                                                                                                                                       | . 26                                 |

|         | A. Building a Multi-tiered Packet Classifier  B. Insert Operation in an MPC  C. Query Operation in an MPC  1. False classification in a successful lookup  2. False classification in an unsuccessful lookup  D. Delete Operation in an MPC  E. Simulation Result for an MPC  1. Experiment for Power  2. Experiment for Throughput | . 31<br>. 33<br>. 34<br>. 36<br>. 36 |

| V       | MULTI-PREDICATE BLOOM-FILTERED HASH TABLE                                                                                                                                                                                                                                                                                           | . 41                                 |

|         | A. Index Address to a Key Table in Base-b                                                                                                                                                                                                                                                                                           | . 45<br>. 46                         |

| CHAPTER |                                                                                  | Page                                                                 |

|---------|----------------------------------------------------------------------------------|----------------------------------------------------------------------|

|         | 1. False indexing for an SS in an MBHT                                           | 50<br>52<br>55<br>57<br>58<br>59<br>61                               |

| VI      | A HIERARCHICALLY INDEXED HASH TABLE                                              | 65                                                                   |

|         | A. Building a Conceptual HIT in Stacked SRAMs B. Insert Operation in an HIT      | 65<br>66<br>67<br>69<br>72<br>73<br>76<br>78<br>79<br>79<br>81<br>81 |

| VII     | A. Building a Conceptual IT of a Binary Prefix Tree B. Insert Operation in an IT | 84<br>85<br>87<br>88<br>90<br>91<br>92<br>93<br>95<br>95<br>96<br>97 |

| VIII    | HASH-BASED IP LOOKUP ARCHITECTURE                                                | 100<br>100                                                           |

| CHAPTER  |                                                               | Page                                   |

|----------|---------------------------------------------------------------|----------------------------------------|

|          | B. Simulation Result of HIHT and FPHT-based IP Lookup Schemes | . 102                                  |

| IX       | HYBRID CAMS OF CAM AND SRAM FOR IP LOOKUP                     | . 105                                  |

|          | A. HCAM-based IP Lookup Architecture                          | 107<br>107<br>108<br>110<br>111<br>112 |

| X        | SUMMARY                                                       | . 116                                  |

|          | A. Conclusion                                                 |                                        |

| REFERENC | CES                                                           | . 120                                  |

| VITA     |                                                               | . 131                                  |

# LIST OF TABLES

| TABLE |                                                                                               | Page   |

|-------|-----------------------------------------------------------------------------------------------|--------|

| Ι     | Lookup & update complexities                                                                  | 6      |

| II    | Hardware features of each scheme                                                              | 6      |

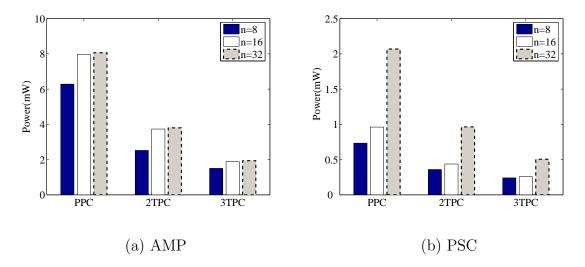

| III   | Power value by CACTI in PPC(31Kx1, 20 ports), 2TPC(29Kx1, 19 ports), and 3TPC(14Kx1,18 ports) | 38     |

| IV    | Complexities of operations to off-chip in four schemes                                        | 61     |

| V     | On-chip memory usage for three traces. The load factor is 0.034, $K=1024.$                    | 64     |

| VI    | AAS in a successful search of NLANR trace for three schemes. $f=2^{-1}$                       | 10. 64 |

# LIST OF FIGURES

| FIGURE | $\Xi$                                                                                                                                                                                                                       | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

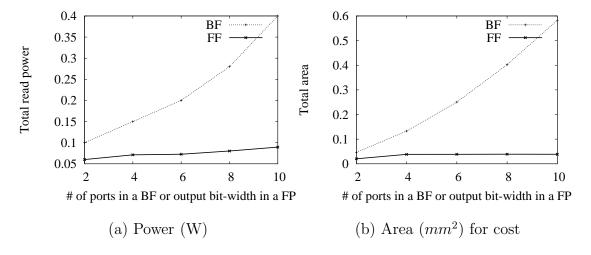

| 1      | Comparison of power and area for a BF and an FF through CACTI.                                                                                                                                                              | 19   |

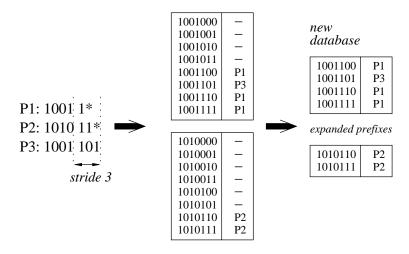

| 2      | Prefix conversion of a CPE with 3 prefixes in stride 3                                                                                                                                                                      | 20   |

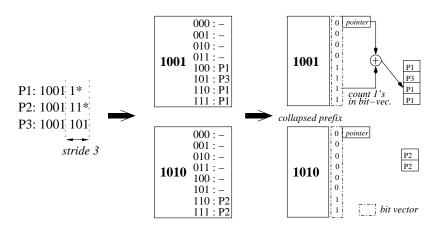

| 3      | Prefix conversion of PC with the same 3 prefixes of Fig. 2                                                                                                                                                                  | 21   |

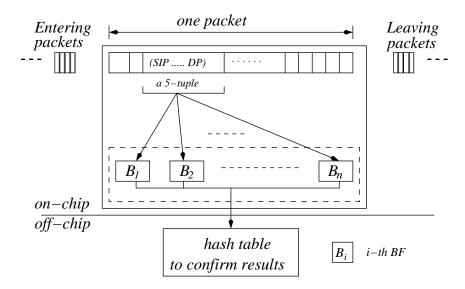

| 4      | Parallel packet classifier engine of $n$ BFs in a given packet                                                                                                                                                              | 23   |

| 5      | Throughput comparison in a different number of BFs, $p_s$ , and $k$                                                                                                                                                         | 25   |

| 6      | Power and area in multi memory read ports for 64K×1-bit memory                                                                                                                                                              | 26   |

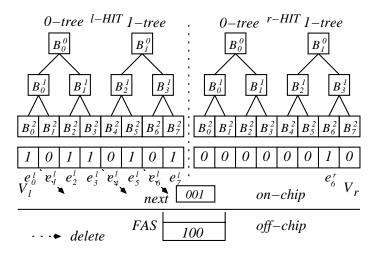

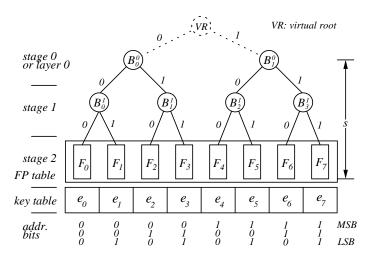

| 7      | Pipeline memory architecture of a 2TPC in a forest. S1 and S2 are pipeline stages. $B_j^i$ means the <i>j</i> -th BF at layer <i>i</i> . $n$ =4. $k$ = $w$ due to Eq. (3.3). $w_2$ =1, $w_1$ = $k$ -1. $b$ is a buffer size | 27   |

| 8      | Memory architecture of a 3TPC in a forest and in pipeline. $B_j^i$ means the j-th BF at layer i. $n=8$ . $k=w$ due to Eq. (3.3)                                                                                             | 28   |

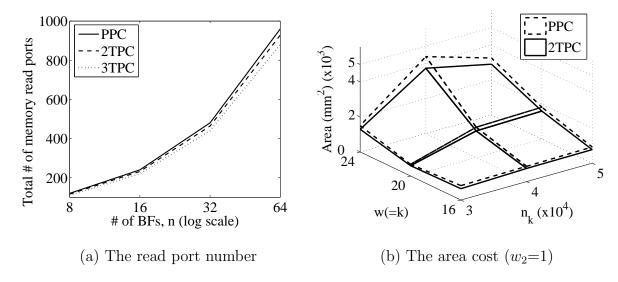

| 9      | (a) The total number of read ports in different number of BFs. $w_3=w_2=1, w_1=13$ for a 3TPC. $w_2=1, w_1=14$ for a 2TPC. $f=2^{-15}$ . (b) 2TPC and PPC area costs with $n=8$ in .13 $\mu m$ process technology.          | 29   |

| 10     | The average packet misclassification for a PPC- $n$ and a 3TPC- $n$ in a different SL rate. $f=2^{-w}=2^{-30}, w_1=28, w_2=w_3=1. n \in \{32,64,128\}$                                                                      | . 35 |

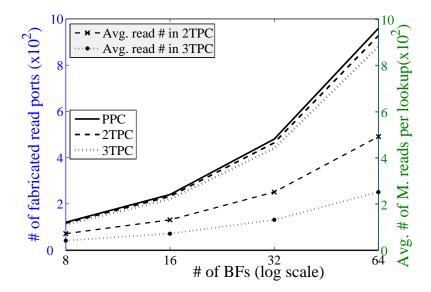

| 11     | The number of read ports and average number of memory reads in different number of BFs. $w_3=w_2=1, w_1=13$ for a 3TPC. $w_2=1, w_1=14$ for a 2TPC. $f=2^{-15}$                                                             | 37   |

| 12     | Power consumption by two traces in PPCs, 2TPCs, and 3TPCs. Also, $n \in \{8, 16, 32\}$                                                                                                                                      | 38   |

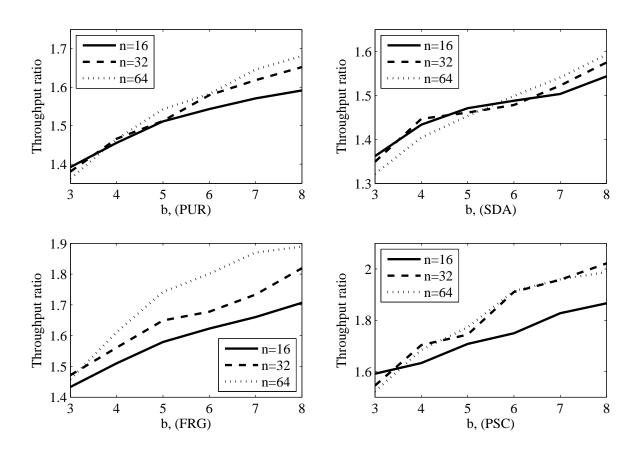

| 13     | Throughput ratios of a 2TPC against a PPC with four traces in different number of buffer size $b$ and $n$ BFs, $w_1=28$ , $w_2=2$                                                                                           | 40   |

| FIGURI | E 1                                                                                                                                                                                                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

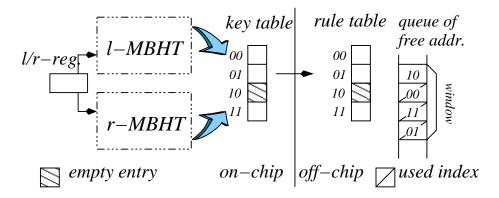

| 14     | Macro view of an MBHT in on/off-chip memory of base-2. $n=2^2$                                                                                                                                                                                                              | 41   |

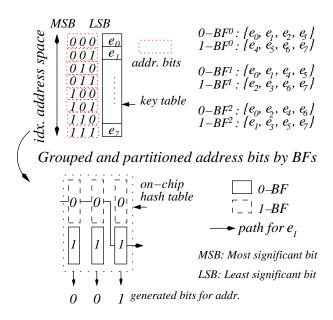

| 15     | Partitioning of 8 elements in base-2 with $0-BF$ s and $1-BF$ s                                                                                                                                                                                                             | 43   |

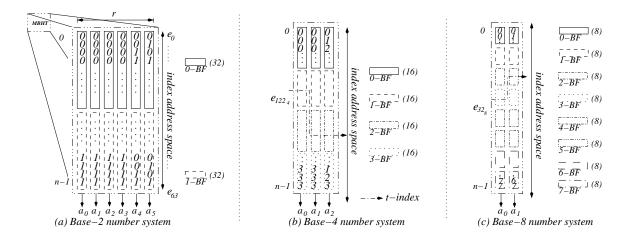

| 16     | Conversion of the base-2 number system to base-4 and base-8 for 64 elements. $n=2^6$ . By (X), X means the number of the same digits in a BF                                                                                                                                | 44   |

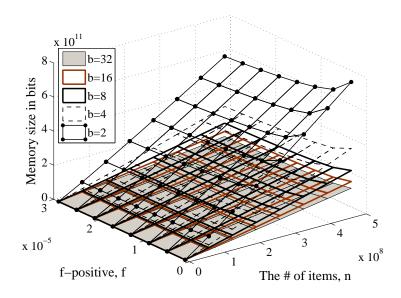

| 17     | Memory size $M_b$ for $b = 2, 4, 8, 16$ , and 32 with $f$ and $n$                                                                                                                                                                                                           | 46   |

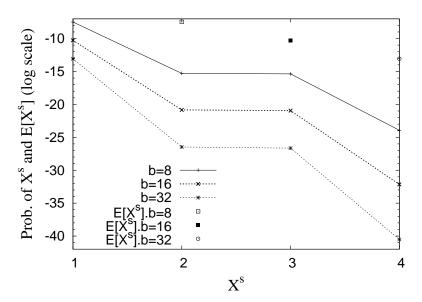

| 18     | Probability of $X^s$ , the number of $f$ -indexes, in an SS. $n=2^{16}$ . Required $f=2^{-10}$ for $b=2$                                                                                                                                                                    | 51   |

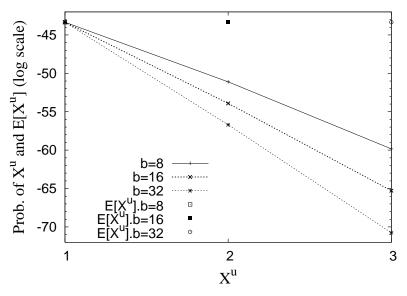

| 19     | Probability of $X^u$ , false memory access, in a US. $n=2^{16}$ . Required $f=2^{-10}$ for $b=2$                                                                                                                                                                            | 54   |

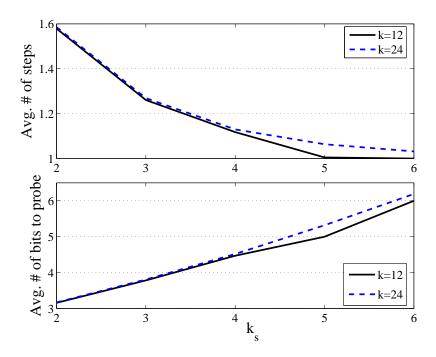

| 20     | The benefit of pipeline in an MBF returning 'no' in a query for two cases of $k=12$ or 24                                                                                                                                                                                   | 56   |

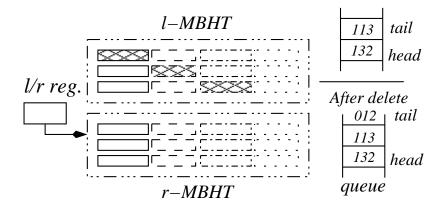

| 21     | An example of delete for item $e$ located at $012_4$ in base-4                                                                                                                                                                                                              | 57   |

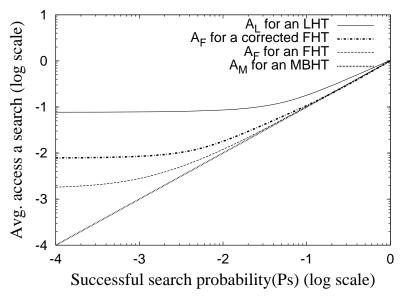

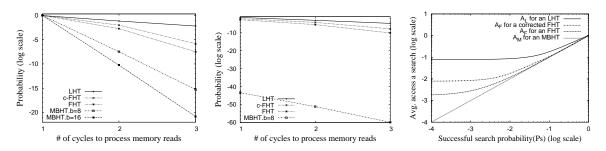

| 22     | Probabilities of memory access in an SS and a US and the average access time to off-chip for an LHT, an FHT, and an MBHT with the same memory $128K\log_2 n$ to fully utilize the saved memory for increase in precisions of base-8 and base-16. $k{=}10$ , and $n{=}64K$ . | 59   |

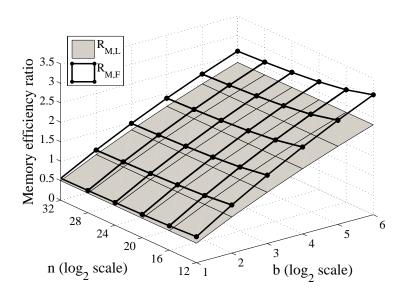

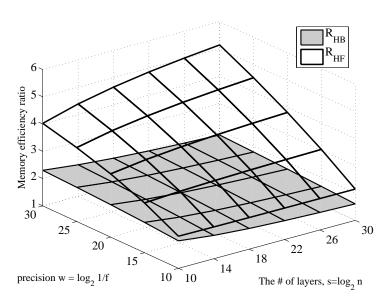

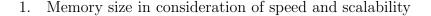

| 23     | Memory efficiency ratios of $R_{M,L}$ and $R_{MF}$ with various $b$ and $n$ . $w_F = w_M = 20$ . Note that although an MBHT is set to have the same average access as others, the actual average access times are different each other as shown in Fig. 22                  | 62   |

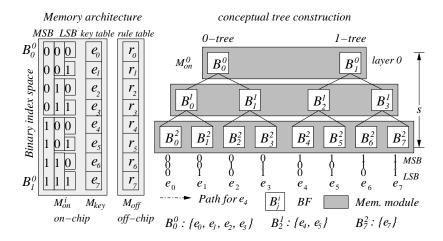

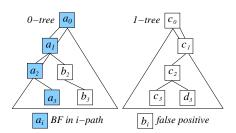

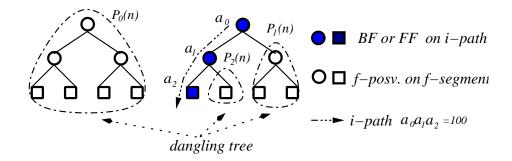

| 24     | Basic configuration of hierarchical indexing tree of 0- and 1-tree                                                                                                                                                                                                          | 65   |

| 25     | Dual configuration of HITs for delete operation                                                                                                                                                                                                                             | 68   |

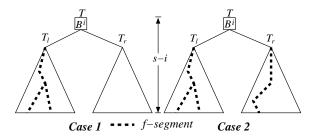

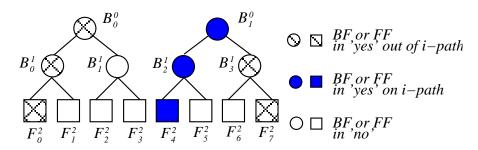

| 26     | Examples of an $i$ -path, $f$ -segments, and $f$ -paths. Probability of $f$ -paths                                                                                                                                                                                          | 71   |

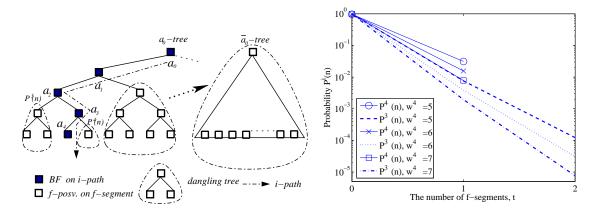

| 27     | An <i>i</i> -path and d-trees in an SS, and $P^i(n)$ of Eq. (7.1) for each d-tree in an HIT                                                                                                                                                                                 | 74   |

| FIGURI | $\Xi$                                                                                                                                                                                 | Page  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 28     | Memory efficiency ratios of $R_{H,B}$ and $R_{H,F}$ with various $s$ and $w$ .<br>Note a corrected-FHT is considered                                                                  | . 79  |

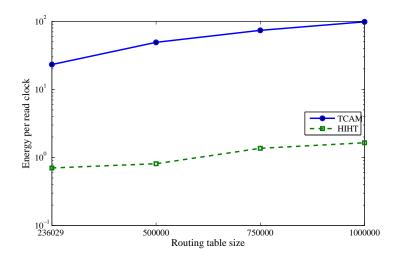

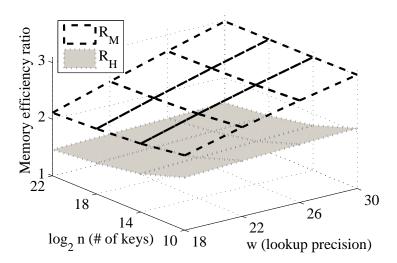

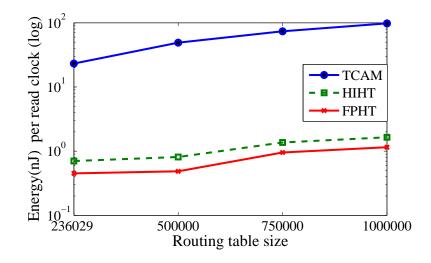

| 29     | Consumed energy per read clock in $0.09 \mu m$ process technology                                                                                                                     | . 82  |

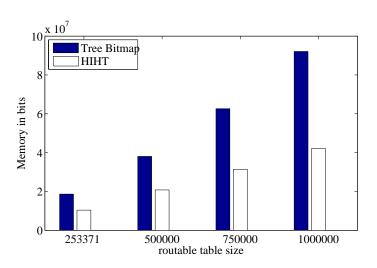

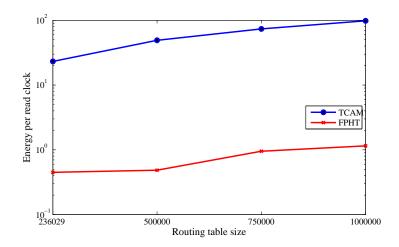

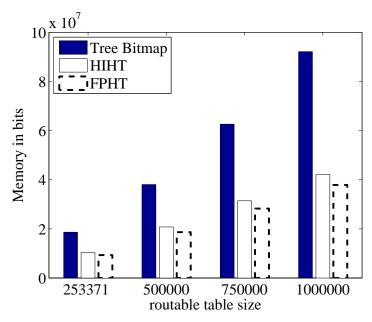

| 30     | Memory comparison of Tree Bitmap and an HIHT in different table sizes                                                                                                                 | . 83  |

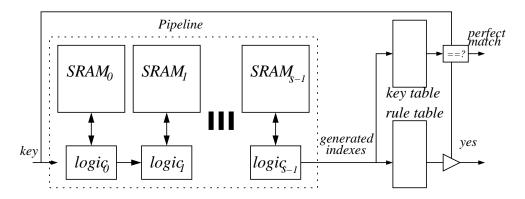

| 31     | An pipelined FPHT architecture with $s$ stages                                                                                                                                        | . 84  |

| 32     | Conceptual IT construction with BFs and tables of FPs and keys                                                                                                                        | . 85  |

| 33     | Examples of an $i$ -path and $f$ -paths for a given query of key $e_4$ in an IT without a virtual root                                                                                | . 89  |

| 34     | An IT of 3 layers (or stages) with an $i$ -path and dangling trees                                                                                                                    | . 92  |

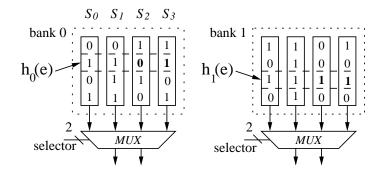

| 35     | A sample configuration of a 4-SBF in $k=2$ banks. A 4-SBF represents $S_0$ through $S_3$ . The memory size is $2\times4\times4$                                                       | . 95  |

| 36     | Memory efficiency ratios of an FPHT over an MBHT and an HIHT at various $n$ and $w$ . In an FPHT, a lookup precision of a CBF is set to 6 for a 16-ary prefix tree                    | . 96  |

| 37     | Consumed energy per read clock in $0.09 \mu m$ process technology                                                                                                                     | . 98  |

| 38     | Memory comparison of Tree Bitmap and an FPHT in different table sizes                                                                                                                 | . 99  |

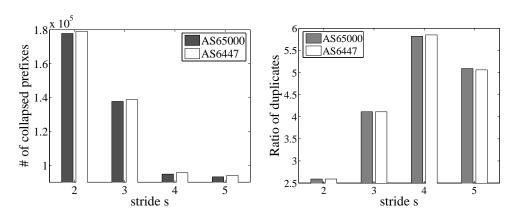

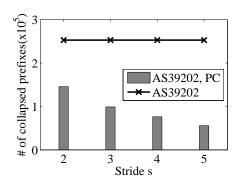

| 39     | The number of collapsed prefixes and the average number of duplicate next-hops at various stride $s$ . The prefix number for AS 65000 and AS 6447 are 233451 and 235307, respectively | . 100 |

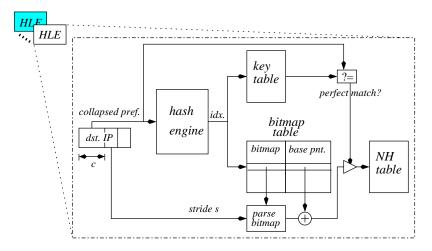

| 40     | IP lookup architecture with parallel Hash Lookup Engines (HLEs) for a wildcard support. Each HLE has different $c$ and $s$ values                                                     | . 101 |

| 41     | Consumed energy per read clock in $0.09 \mu m$ process technology                                                                                                                     | . 103 |

| 42     | Memory size comparison of Tree Bitmap, an HIHT, and an FPHT in different table sizes.                                                                                                 | . 104 |

| FIGURE | $\Xi$                                                                                                                                                                                                                                                                                                                                                                             | Page  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

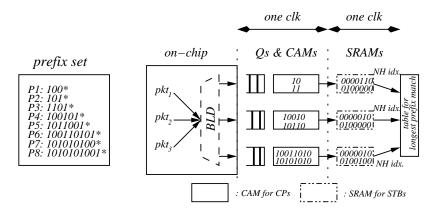

| 43     | HCAM-based IP lookup architecture for a prefix set. Stride $s$ =2. The collapsed prefix lengths, $d_1$ , $d_2$ , $d_3$ , are 2,5, and 8, respectively                                                                                                                                                                                                                             | 105   |

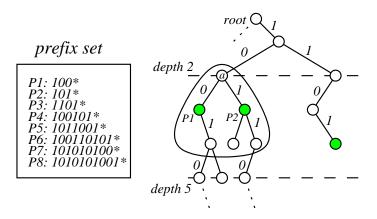

| 44     | A sample prefix set and a subtrie in a uni-bit trie for the set                                                                                                                                                                                                                                                                                                                   | 107   |

| 45     | The number of collapsed prefixes and the number of transistors at various stride $s$                                                                                                                                                                                                                                                                                              | 108   |

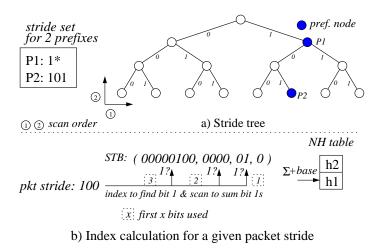

| 46     | A stride tree for 2 prefix strides and an index method to an NH table                                                                                                                                                                                                                                                                                                             | . 109 |

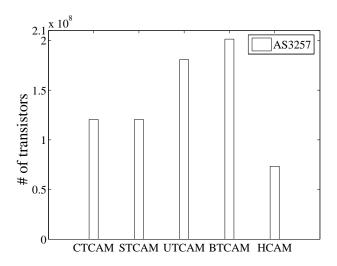

| 47     | The memory comparison of all schemes in terms of a transistor. Lookup precision $w=10$ . Note that 'HCAM' includes all CPs, STBs, and BFs                                                                                                                                                                                                                                         | 111   |

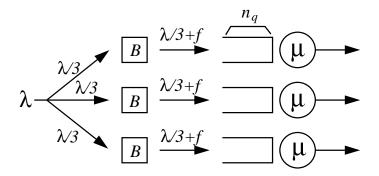

| 48     | Queuing model of $n_c$ pipelines in an HCAM. $n_c$ =3                                                                                                                                                                                                                                                                                                                             | 113   |

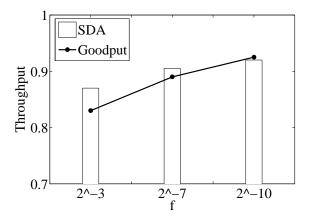

| 49     | Goodput vs. measured throughput of a CAM block in an SDA trace. $\rho$ =0.95                                                                                                                                                                                                                                                                                                      | 114   |

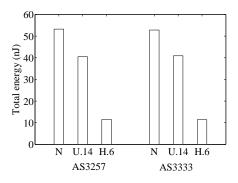

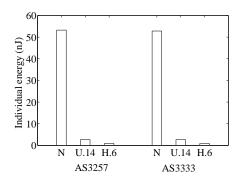

| 50     | a) Total energy consumption in one clock for an NTCAM, a UTCAM, and an HCAM. Symbols 'N', 'U.14', and 'H.6' denote NTCAM with a block of whole prefixes, UTCAM with 16 blocks of 14K prefixes, and HCAM with 16 blocks of 6K prefixes, respectively. $.13\mu m$ process technology is used. b) The energy consumptions for a single lookup operation in a block for three schemes | 115   |

#### CHAPTER I

#### INTRODUCTION

In packet processing, a router fast associates packets with a set of rules for packet forwarding or various network services. Provision of such a fast packet processing like IP lookup and packet classification becomes harder, as the demand for high-speed and large-scale routers continues to surge in networking. It has been reported that the traffic of the Internet is doubling every two years by Moore's law of data traffic [1] and the number of hosts is tripling every two years [2].

These rapidly increased traffic and host numbers lead to two major packet processing related problems for core routers. 1) Speed: a high-speed router needs to look up a rule table at the rate that satisfies its bandwidth requirement. For example, IP lookup at the rate of 160Gbps must process 500M lookups in a second, and this implies that a packet of minimum 40 bytes must be forwarded to a next hop in 2ns in the worst case. 2) Scalability: a fast packet processing must be made in searching an associated rule even with hundreds of thousands of rules. For instance, in packet classification domain the maximum number of rules is up to 2 to 104 due to the 104-bit length of a tuple of source, destination IPs, etc.

Since a fast packet processing is a in the router's critical data path, literature on packet processing has developed numerous fast lookup schemes using three major techniques, Ternary Content Addressable Memory (TCAM) [3–6], trie [7–10], and hashing [11–17]. Although a TCAM provides a deterministic and high-speed packet lookup [5,6], due to its non-commodity nature and brute-force search method, its die area cost and power dissipation tend to become prohibitive for packets with a large

This dissertation follows the style of IEEE Transactions on Networking

number of rules and high line rates. Unlike TCAM, trie-based scheme uses a tree-like data structure to successively classify a packet a few bits at a time [7–10], but it inherently suffers from space to hold pointers from nodes to their children and the sequential memory accesses introduced by these pointers. In addition, an imbalanced memory access hinders the high IP lookup performance due to an irregular prefix distribution in a trie's tree structure. In contrast, the hash-based schemes neither perform brute-force lookups as in TCAM nor suffer from imbalanced memory access, so they can potentially receive an order-of-magnitude power and memory savings, respectively.

Traditionally, a hash table (HT) is popularly used for a fast search and this is due to its  $\mathcal{O}(1)$  average memory access per lookup under reasonable assumptions. Recently, HTs are used in a wide variety of packet processing applications such as intrusion detection systems [18], packet classification [19, 20], TCP/IP system management [21], and IP lookup [12, 16].

In particular, the binary search on prefix lengths algorithm [22] has the best theoretical performance of any sequential algorithm for the longest prefix match in IP lookup by using HTs. In addition, packet classification applications utilize HTs [23, 24], so they first perform a lookup on a single header field and later leverage the results to narrow down the search to a smaller subset of packet classifiers. These use HTs with the expectation of  $\mathcal{O}(1)$  memory access and encompass a more predictable worst-case lookup scheme.

However, as the table occupancy, or load, increases, collision occurs frequently, which in turn reduces the performance by increasing the cost of the primitive operations. Although there are two collision resolutions (i.e. open address and chaining), schemes in open address are not suitable for a fast lookup because of the worst case performance. In addition, a chaining suffers from pointers' overhead as it maintains

a set of linked lists.

While these solutions are designed to maintain a good average performance despite their high loads and increased collisions, their performance nevertheless meets the packet processing needs: high speed and scalability. To satisfy such needs, an onchip Bloom filter (BF) is widely used because the BF of an m-bit vector can provide both the memory efficiency and the high throughput using an approximate membership testing. Packet processing applications using such a BF include IP lookup in [12], an intrusion detection system in [13], or packet classifications [19,20]. Also, in trading off space, computation, and the impact of false positive lookup, an efficient lookup using a fingerprint filter (FF) or d-left hashing has been considered preferable in the literature on networking [21,25,26]. The reason is that even though a BF provides memory-efficient approximate lookup, an FF is found more efficient in power and memory usages for set representation than its counterpart.

However, such an approximate match is not suitable for all packet processing applications; the exception includes IP lookup, where its packets are required strictly to be forwarded to a next hop according to a prefix table. For instance, the recently-proposed IP lookup approaches [12,16] have the following design flaws that are not suitable for a high-speed and large-scale router: 1) A Bloomier filter-based hash table (BFHT) [16] utilizes a Bloomier filter [27]. However, it inherits two disadvantages of a Bloomier filter: a setup failure in saving n keys and  $\mathcal{O}(n \log n)$  setup complexity for n keys. 2) Authors in [12] propose a memory-efficient IP lookup by using BFs, each assigned to a set of the same-length prefixes. Although this scheme provides fast approximate matches in on-chip, the perfect prefix match is achieved in an off-chip HT due to the BFs' false positive match. Thus, the lookup time is bounded in a slow off-chip memory access.

A supportive scheme to [12]'s scheme is made to provide a fast off-chip HT

access in [15]. However, this scheme suffers from duplicate keys saved in off-chip memory, and the number of duplicates is depending on k which is the number of hash functions and it controls the lookup precision. Also, the *insert* and *delete* operations take approximately k times. Such a depending fact k of a large value is not suitable for performing fast lookups and key updates in high speed routers. Other Peacock and multilevel hash schemes for packet processing [28, 29] suffer from setup failures as well.

To address these flaws, such as key duplicates, complicated key updates, and setup failures, we propose scalable hash schemes for maintaining a fast packet processing by using BFs and an FF in pipeline. The four hash schemes in this dissertation are 1) a multi-tiered packet classifier (MPC), 2) a multi-predicate Bloom-filter HT (MBHT), 3) a hierarchically indexed HT (HIHT), and 4) a fingerprint-based HT (FPHT). The first two schemes are designed for general packet processing applications while the last 2 schemes are designed for IP lookup application due to a memory-efficient perfect match. These four schemes' overviews are the following:

A multi-tiered packet classifier (MPC) with n BFs provides a lookup distribution for higher power and throughput efficiencies, compared to a parallel packet classifier (PPC) of n parallel BFs [12–14,17]. A PPC accesses n BFs for one lookup every cycle while an MPC accesses n BFs for several lookups every cycle with the same BFs' memory amount as that of a PPC. To build 2-tiered BFs, for an example of an MPC, the total PPC memory is split between a pre-stage of small-sized BFs with one read port and a post-stage of large-sized BFs with k-1 read ports. Then, a small-sized BF is logically connected to two large-sized BFs, so that a forest of binary trees is built [30].

Secondly, a multi-predicate Bloom-filtered HT (MBHT) with a set of multipredicate BFs (MBFs) generates index addresses which have different base number systems to a key table. The generated indexes are geared to in parallel access to a key table on-chip with simple switching circuitry, so that for a successful query at most one off-chip memory access is guaranteed for bandwidth requirement of a router. There are two benefits of an MBHT as regards to both on-chip and off-chip memory. For the on-chip memory, an MBF reduces the memory size in the base- $2^x$  number system by x times compared to that of the base- $2^1$  number system with a binary predicate BF, where x is a positive integer larger than 1 [31].

Thirdly, a hierarchically indexed hash table (HIHT) is proposed and is used for approximate testing on keys' index paths in trees. Once the BFs of the last step of pipelining complete their index addresses to entries in a table, a *perfect* match is made by comparing the saved keys in the indexed entries with a given key, so that at the most one off-chip access is made to a known associated rule with the given key [32].

Finally, a finger**p**rint-based HT (FPHT) generates indexes to a key table with the help of both memory-efficient BFs which are approximate membership testers and an FF which is the most memory-efficient set representation. Specifically, in an FPHT with no pointers, BFs play a role in key searching in a b-ary prefix tree,  $b \in \{2, 4, 8, \dots\}$ , and an FF ensures a fewer number of false indexes to a key table in the worst lookup case [33].

In addition to hash-based approaches in packet processing, the TCAMs have become the defacto industrial standard solution for a high-speed IP lookup. More than 6 million TCAM devices were deployed worldwide in 2004 [34], and TCAMs are projected to be increasingly used as the next generation network search engines. Part of the TCAMs success is that they are developed with the abilities to store a "don't care" state for a prefix and to compare an input key against every TCAM entry, thereby enabling them to retain a single clock cycle lookup.

Table I. Lookup & update complexities.

| schemes |                            |

|---------|----------------------------|

| Trie    | $\mathcal{O}(W)^{\dagger}$ |

| Hash    | $\mathcal{O}(1)$           |

| TCAM    | 1                          |

$^{\dagger}W$ : # of IP address bits

Table II. Hardware features of each scheme.

|                          | TCAM | CAM | SRAM |

|--------------------------|------|-----|------|

| $\mathrm{clock}^\dagger$ | 266  | 333 | 400  |

| Power ‡                  | ≈15  | ≈1  | ≈0.1 |

| Cell°                    | 16   | 8   | 6    |

<sup>\*</sup> MHz unit \* Watts unit \* # of transistors per bit

Despite TCAMs' popularity and simplicity, TCAMs have their own limitations with respect to IP lookup. 1) Throughput: parallel searches in all prefixes are made in one clock cycle for a single lookup, so that the throughput is simply 1 as shown in Table I. 2) Power: although a TCAM provides an one-cycle lookup, such an one-cycle lookup, which is made in parallel searches on all prefixes, requires at most 150 times more in power consumption than any SRAM-based scheme does. Table II shows such power consumption difference measured by CACTI [35]. Thus, reducing TCAM power usage is a paramount goal for a deterministic TCAM lookup.

A high TCAM throughput has been achieved through a partitioning technique [36,37]. Its principle with pipelining depends on a parallel architecture that fulfills multiple lookups per clock cycle. Likewise, a SRAM-based parallel scheme [38] partitions a trie and maps subtries to pipelines using a solution of a *NP-complete* problem for a high throughput. However, these kinds of approaches suffer from a high power consumption and a complicated mapping algorithm complexity, respectively.

In dissertation we proposes a hybrid CAM (HCAM) IP lookup architecture for maintaining a high throughput and power efficiency. Our approach adopts prefix collapse and partitioning schemes with Bloom filters (BFs). A prefix collapse (PC) reduces the number of prefixes as opposed to the prefixes expansion. In such prefix collapse, the collapsed prefixes can be put in a deterministic lookup-capable CAM

to demonstrate further hardware efficiencies for power and the number of transistors per cell than a TCAM can as shown in Table II. A complete prefix match beyond the collapsed prefix match is made through a stride tree bitmap (STB) saved in SRAM. Also, the CAM for the same-length collapsed prefixes can be partitioned into CAM blocks to provide multiple lookups on the collapsed prefixes per clock cycle.

This dissertation has the following contributions of the four hash schemes.

- An MPC hashing scheme with n BFs is proposed in a multi-tiered configuration of BFs with the same memory capacity as that of a PPC.

- An MBHT scheme is proposed using a contiguous memory space in off-chip memory without using pointers to conduct a perfect match and a fast search.

- An HIHT scheme for fast and memory-efficient packet processing is introduced.

It provides per-key information lookup to be used as an index to a key table in on-chip memory without pointer operation.

- An FPHT scheme provides indexes to a key table using BFs and an FF without incurring pointer operations.

- For each of the above schemes, new algorithms on insert, query, and delete

operations are proposed, and they are as easy to implement as those of a BF or

an LHT.

- In an MPC evaluation, it has been shown that the proposed MPC scheme has 4.2 and 2 times power and throughput efficiencies against a PPC, respectively.

- In comparison for scalability and speed, analyses on memory efficiency for an MBHT, an HIHT, and an FPHT are made and multi-fold times memory efficiency is achieved over other contemporary schemes.

- In IP lookup application of the proposed hash schemes, the HIHT and the FPHT, memory and power comparisons with TCAM-based and trie-based IP lookups are made. The proposed hash-based IP lookup schemes show at least 51 times power efficiency and 1.8 times memory efficiency, compared to TCAM-and tried-based schemes.

- In addition, the proposed HCAM-based IP lookup scheme achieves the same throughput as contemporary schemes while it uses 2.8 times less memory and 3.6 times less power compared to contemporary schemes

The rest of the paper is organized as follows. Sec. II presents several hash-based schemes for packet processing, such as an FHT, a BFHT, and the Peacock hashing. Sec. III discusses the basics of a BF and an FF in terms of their memory size and power consumption. Also, this section shows two applications of an HT to IP lookup and packet classification. Then, a detailed MPC build with n BFs for a packet classification is shown in Sec. IV. In the following Sec. V, the detail of an MBHT for a perfect match is discussed. In Sec. VI, the detail of an HIHT for a perfect match is explained. A detailed FPHT build in a binary prefix tree for a perfect match is illustrated in Sec. VII. As the last scheme, an HCAM is proposed for a high throughput and power saving in Sec. IX. In each of Secs. IV, V, VI, VII, and IX, the analysis on memory, power, or throughput efficiencies in comparison to other contemporary schemes is made. A conclusion and future work are presented in the following Sec. X.

#### CHAPTER II

#### RELATED WORKS IN PACKET PROCESSING

Packet processing has different objectives in each networking layer. For instance, in layer 2 a router needs to forward a packet to a corresponding port in a limited time with a large-scale routing table. In layer 3 a packet is classified into a flow for various purposes like firewall or qualify of service. In this chapter, related major research works on packet processings like IP lookup and packet classification are enumerated.

#### A. IP Lookup

Song et al. [15] claimed that for a perfect match an FHT with help of a BF improves the performance over an LHT by reducing the number of off-chip memory accesses needed for the most time-consuming lookups. This benefit is possible by combining hashed linked lists with k hash functions so that only the shortest linked list is used in the search. Although chaining in a linked list for resolving a collision is one solution, accessing a key in a linked list costs the same memory accesses as the number of keys in the linked list because of pointer operation. Beyond the generic limitation of linked list implementation, overlapping k linked lists in an FHT suffers from several others described here. First of all, due to merging k linked lists there is a chance that duplicate keys are saved in off-chip memory, depending on k. In that case, k is reversely proportional to collision rate, a need of very low collision rate for a high-speed router makes a number of copies of a key, proportional to k, in off-chip. Although searching for a key is expedited by choosing the shortest linked list, the insert and delete operations take at least k times memory accesses due to the kshared linked lists. These operations are not suitable for a dynamically changing set because any change in the set needs 2k times of off-chip memory access. Besides

time complexities of *insert* and *delete* operations, to obtain better performance over an LHT in terms of reduced collisions, an FHT needs a plethora of buckets used as pointers to off-chip memory and it holds a large wasted portion of buckets in on-chip memory. Also, perfect match is made in off-chip memory, so that every query needs at least one access to off-chip memory. Furthermore, due to the inherent drawback of a BF, the *delete* operation was designed by introducing a 4-bit counter in each bucket [39]. Yet, they did not consider the memory size of the counters, but just the number of buckets.

There is a fundamental limitation in a HT using a linked list: a sequential access to a key along the linked list. For example, to access key e located at the end of a linked list of t keys, t sequential accesses are necessary in t cycles, because memory address of key e is known after a previous key e' with a pointer to the next key e is obtained in the previous cycle. However, accessing a few entries with known indexes in a table can be processed in one cycle with a simple switching circuitry. To provide collision-free lookup with a key table, a BFHT [16] utilizes a Bloomier filter [27] capable of per-key information lookup. Per-key information by a Bloomier filer is considered as an index address of a key table given a packet, so that a BFHT performs perfect match to make a deterministic IP lookup with a key table. Although a BFHT contributes prefix collapsing as well, it also inherits two disadvantages of a Blooimer filter: first, there is a setup failure in saving per-key informations of n keys in a BFHT, so that another lookup mechanism is used for the failed keys in the setup. Thus the number of hash functions gets increased to reduce setup failure rate, leading to more memory need. Second, the setup complexity of n keys is  $\mathcal{O}(n \log n)$ , implying that a copy of a BFHT works for update of a new key in the rear of the BFHT for seamless lookups of other keys.

#### B. Packet Classification

The packet classification goal is to identify a flow characterized with a 5-tuple of source IP (SIP), destination IP (DIP), protocol, source port (SP), destination port (DP) and to forward the flow to a corresponding output port. Several types of packet classifiers like TCAM-based and SRAM-based ones are suggested [6, 20, 40-42]. In a hash-based approach, a packet classifier in [14] uses BFs in parallel, so that in a given packet lookup all BFs need to be checked to find the packet-associated flow and the packet is forwarded to a corresponding port where a BF returns 'yes'. However, in a high-speed lookup to a BF, the number of memory read ports in the BF is considerably large. Also, the number of BFs to be probed is as large as the number of a high-speed router's ports. Unlike the above schemes of the  $\Theta(n)$  BF access complexity among n BFs, our MPC needs probabilistically less complexity than  $\Theta(n)$  for a lookup

### C. Other Packet Processing Applications

Besides BF applications for packet processing in the previous section, applications of other domains have utilized the benefit of BFs, such as dynamic BF for data management [17], wide-area web caching [39], content delivery across overlay networks [43], IP traceback [11], query routing in peer-to-peer networks [44]. Even in a wire-less sensor networks where power saving is a paramount issue, a coordinated packet traceback mechanism in [45] is introduced with the concept of dimensions in hash algorithms in which a dimension can expand by the number of either hash functions, hash tables, or both.

A legacy BF does not support deletion operation because a bit-location in a bit-vector indexed by hash functions can be overlapped by more than one key. To avoid this problem, Fan *et al.* [39] introduced the idea of a counting BF in which

each entry in the BF is not a single bit, but rather a small counter in a couple of bits. Bonomi et al. [21] introduced Approximate Concurrent State Machines (ACSM). While similar in spirit to BFs, the scheme is based on a combination of hashing and fingerprints, using d-left hashing to obtain a near-perfect hash function in a dynamic setting. Although it is found that its data structure takes much less space than a comparable counting BF, the fundamental problem in their approach is that in an f-positive there is no way to verify a result given by a ACSM. In contrast, our three schemes (MBHT, HIHT, FPHT) provide a perfect match mechanism without a pointer. Cohen and Mattias [46] introduce Spectral Bloom Filter (SBF), an extension of the original BF to multi-sets, allowing the filtering of elements whose multiplicities are below a threshold given at query time. However, SBF does not support a function of relationship between a key and arbitrary per-key information.

Unlike previous BF approaches for approximate membership testing, for the first time, Bloomier filter in [27] provides storage and retrieval of arbitrary per-key information. It guarantees perfect-hashing for a constant-time lookup in the worst case. However, a disadvantage lies in static support of membership. Also, there is setup failure probability of encoding all keys depending on k, the number of hash functions.

In an application of overlay networks, continuous reconfiguration of virtual topology by overlay management strives to establish paths with the most desirable end-to-end characteristics. The approximate reconciliation tree for overlay networks by Byers et al. [43] uses BFs on top of a tree structure to minimize the amount of data transmitted for verification.

## D. Parallel IP Lookup Using TCAM or SRAM

Except a parallel SRAM scheme in [38], most parallel IP lookup engines for high throughput are TCAM-based due to benefit of employing parallel searches on TCAM prefixes [36, 37]. They partition the full routing table into several TCAM blocks and make parallel lookups on different blocks. This parallelism obtains power efficiency and throughput improvement.

Cool TCAM (CTCAM) was proposed in two separate schemes: bit-selection and trie-based schemes [47]. In the former, selected bits are used to index different TCAM blocks directly. The latter scheme splits the trie by carving subtries out of the full trie. However, the prefix distribution imbalance among the TCAM blocks can be noticeably high, resulting in low worst case performance.

Ultra TCAM (UTCAM) in [36] increases the throughput 4.0 times with a 25% TCAM entry redundancy. It uses distributed and parallel TCAM blocks aided by having an index logic to choose the destination TCAM block for a given packet. Likewise, Selective TCAM (STCAM) in [37] uses the multiple TCAM-block selectors with prefix TCAM caches. A collision among TCAM-block selection attributes a STCAM's need to resolve TCAM block contentions with arbiters, and these arbiters prevent from receiving a new lookup request. Thus, the STCAM throughput gain was reported to be at most 1.5 times even with multiple TCAM blocks without caches.

Unlike TCAM partitioning, beyond TCAM (BTCAM) scheme in [38, 48] is introduced for trie-partitioning using SRAMs where subtries were mapped to SRAM blocks with consideration of memory balance. However, such a mapping is proved to be *NP-complete*, so that remapping for prefix update during lookup operation is not feasible. Furthermore, leaf-pushing causes the increase number of trie nodes resulting in memory overhead.

Trie- and hash-based schemes shown in the above subsections are lack of high lookup performance. In contrast, a TCAM's lookup complexity is 1 and a TCAM has been considered as a natural choice of multi lookups due to its parallel searches through partitioning [36, 37]. The same characteristic is preserved in a CAM except the prefix match. After discussing an issue in prefix match by prefix collapse or expansion in Sec. C, a hybrid CAM (HCAM) scheme using CAM blocks is presented for high throughput in Sec. D.

#### CHAPTER III

#### BASICS ON HASH FOR PACKET PROCESSING

This chapter introduces the basics of a BF and an FF as well as their applications to packet processings, IP lookup and packet classification.

## A. Basic Bloom Filter Theory

To understand the fundamental relationship among the number of buckets, m; the number of items, n; and the number of hash functions, k, the mathematics about a BF and a false positive, or f-positive are presented.

A legacy BF for representing set  $S=\{e_0, e_1, ..., e_{n-1}\}$  of n elements is described by an array of m bits with each initially set to 0. A BF uses set H of k independent hash functions  $h_0, h_1, ..., h_{k-1}$  with range [0:m-1], implying that in hardware implementation a memory module for a BF needs k ports for memory read. For mathematical convenience, a natural assumption is made that these hash functions map each item in the universe to a random number uniform over the range. For each element  $e_{j'} \in S$ , the bits indexed by  $h_{k'}(e_{j'})$  are set to 1 for  $0 \le k' \le k-1$ ,  $0 \le j' \le n-1$ . To verify that item e' is in S, it is checked whether k bits in a BF indicated by  $h_{k'}(e')$  are 1. If not, then clearly e' is not a member of S. Even if chosen bits indexed by  $h_{k'}(y)$  have a value 1, there may be a probability called f-positive that item y is falsely believed to belong to set S due to the random gathering of k bits of value 1 set by independent items.

The above probability f of f-positive can be formulated in a straightforward way, given our assumption that hash functions are perfectly random. Among m bits, the chance of a bit being value 0 by one  $h_k$  is 1/m. After all n elements of S are hashed k times into the BF, i.e. totaling  $k \cdot n$  times, the probability that a specific bit is still 0 is asymptotically  $p = (1-1/m)^{kn} \approx e^{-kn/m}$ . Then, the probability of an f-positive by

randomly choosing k bits among m bits is

$$f \ge \{1 - (1 - 1/m)^{kn}\}^k \approx (1 - p)^k \ge (1/2)^{m \ln 2/n}$$

(3.1)

because k bits with probability of becoming 0, or p, could independently become more than 0 when a membership test is requested. This probability is bounded and the optimal k, the number of hash functions, that minimizes f is easily found  $k=\ln 2(m/n)$  according to the results of Broder and Mitzenmacher [49]. After some algebraic manipulation, Broder and Mitzenmacher [49] claimed that the requirement of  $f \le \epsilon = 2^{-w}$  suggests

$$m \ge n \frac{\log_2(1/\epsilon)}{\ln 2} \approx 1.44n \log_2(1/\epsilon) = 1.44nw,$$

(3.2)

where w is a precision in query operation. Furthermore, in an optimal configuration, k becomes w according to the following derivation:

$$k = \ln 2 \frac{m}{n_i} = \ln 2 \left( n_i \frac{\log_2(1/f)}{\ln 2} \right) / n_i = w.$$

(3.3)

Also, k needs to be at least 29 (  $\approx \log_2 1/500M$ ) to be a scheme of a deterministic  $\mathcal{O}(1)$  lookup processing 500M packets a second for a 160Gbps router.

Two important lemmas can be derived from Eq. (3.2), described as follows

LEMMA 1 (LINEAR PROPERTY) Linear property between m and n exists in Eq. (3.2) because given f requires that variable n is linearly proportionate to variable m. Therefore, if n is reduced by half or decreased by constant  $\alpha$ , the desired m for a given f is reduced by half or decreased by the constant of  $\alpha \cdot 1.44 \log_2(1/\epsilon)$ , respectively.

**Proof:** Suppose function  $F_m(n, f)$  of Eq. (3.2) has domain variables n and f. Once f is set to a constant  $\epsilon$  as requirement, this function becomes a polynomial of variable n,  $F'_m(n)=a\cdot n$ , with degree one, where  $a=1.44\cdot\log_2(1/\epsilon)$ . Therefore,

$$F_m'(n/2)=a\cdot (n/2)=an\cdot 1/2=F_m'(n)/2 \text{ and }$$

$$F_m'(n-\alpha)=a\cdot (n-\alpha)=an-a\alpha=F_m'(n)-a\alpha,$$

proving Linear Property.

LEMMA 2 (REVERSE EXPONENTIAL PROPERTY) The change of m has an exponential effect on f for a given n from Eq. (3.2). That is, if m is increased by constant  $\alpha$  or multiplied x times, f is exponentially divided on base-2 by the power of constant  $\alpha/c$  or powered by x times where x>1, constant c=1.44n.

**Proof:** Suppose function  $F_f(n, m)$  is derived from Eq. (3.2) and rearranged in  $2^{-m/c}$ , where c=1.44.n. Once n is set to a constant, this function becomes a exponential function of m,  $F'_f(m)$ . Therefore,

$$\begin{split} F_f'(m+\alpha) &= 2^{-(m+\alpha)/c} = 2^{-m/c-\alpha/c} = F_f'(m)/2^{\alpha/c} \text{ and } \\ F_f'(xm) &= 2^{-xm/c} = (2^{-m/c})^x = F_f'(m)^x, \end{split}$$

proving Reverse Exponential Property. These Linear and Reverse Exponential Properties are used in introducing an MBF, so that an MBHT has the benefit of memory saving in on-chip memory by the Linear Property, and, thereinafter the saved memory is designed to decrease f exponentially by the Reverse Exponential Property.

We have linked the theoretical relationships between k, m, n for the required f-positive,  $\epsilon$ , in a query. If a BF is to be used for IP lookup despite producing an approximate query result, a lookup precision w should be at least 29 ( $\approx -\log_2 1/500M$ ) for 160Gbps routers because a collision in 500M lookups in a second is not tolerable in bandwidth requirement satisfaction. Also, Eq. (3.3) suggests that a BF memory implementation for 160Gbps routers needs 29 read ports for the same number of hash functions, but this is not feasible in terms of cost and power concerns. To lessen these overheads, we adopt a segmented BF (SBF) [14] with memory banking. Using this scheme with commodity memory is more practical since IDT currently produces high-speed bank-switchable memory organized into a 64-bank memory array.

In an SBF, an m-bit vector is divided into k m'(=m/k)-bit subvectors, each put in an independent memory bank. k hash functions with the range [0:m'-1] are assigned to their corresponding subvectors, and an one-clock query in an SBF is based on k indexed values in k subvectors (or banks) together as in a legacy BF. Although a SBF's memory banking scheme removes the multiport overhead, the SBF's false positive probability, f', becomes the same BF's f as follows:

$$f = \left(1 - (1 - 1/m)^{kn}\right)^k = \left(1 - \left(1 - 1/km'\right)^{kn}\right)^k$$

$$= \left(1 - \left(1 - k/km' + o(1)\right)^n\right)^k \approx \left(1 - \left(1 - 1/m'\right)^n\right)^k = f'$$

(3.4)

where a small o function is negligible at a large m' value.

#### B. A Memory- and Power-Efficient Fingerprint Filter

Authors in [49, 50] claim that an FF is the most memory-efficient set representation scheme. In this section, beyond the theoretical FF benefit, it will be claimed that an FF is the power-efficient data structure in hardware implementation as well.

One method to determine the efficiency of a set representation scheme is to consider how many bits, m, are necessary for a set of n keys from a universe. An efficient scheme must not allow any false negative but can at most allow an f-positive of a fraction  $\epsilon$  of the universe. As claimed in [49], the following inequality of m for a given required  $\epsilon$  is made:

$$m \ge n \log_2(1/\epsilon) = nw = w + \dots + w = \sum_{i=1}^n w.$$

(3.5)

Thus, an FF can be regarded as an array of n fingerprints (FPs) of  $\log_2(1/\epsilon)$  bits for the approximate set representation. Since an FF does not have a constant time indexing mechanism like hash functions in a BF, knowing an index to a key's FP is other complicated search. However, once an index to the key's FP is known, the same

index can be used in a key table for a perfect match. Also, an FF needs 1.44 times less memory than a BF for required  $\epsilon$ , based on Eq. (3.2) and Eq. (3.5).

In addition to the theoretical benefit, in terms of memory architecture using an FF SRAM requires a simpler memory read port design than an SBF SRAM does, so that area and power benefits in memory architecture are gained. Suppose there are two SRAMs for an SBF and an FF and the required false positive  $\epsilon$  is  $2^{-29}$  for 160Gbps. The SBF requires 29 read ports to query a key as a result of its simultaneous accesses while the FF needs only one read port to an FP of 29 bits. That is, an SBF SRAM with n keys is designed as a  $w \times 1.44n \times 1$ -bit memory array with w read ports of 1-bit output width while an FF SRAM is made of an  $1 \times n \times w$ -bit memory array with one read port of w-bit output width.

Fig. 1. Comparison of power and area for a BF and an FF through CACTI.

Fig. 1 shows the power and area comparisons for an 11520-bit SBF and an 8000-bit FF in different ports or output bit widths.  $.09\mu m$  process technology in CACTI 4.2 [35] is used. In Fig. 1 a) and b), gaps between the SBF and the FF are significant as w get larger. or example, an FF memory consumes 9.5 times less power, compared to an SBF while the former needs 76 times less area. Thus, for a

perfect match query, utilizing few-port SBFs in a binary search for a key's fingerprint in an FF and accessing a key table through the indexed fingerprint is a memory- and power-efficient hash scheme, and this scheme is introduced in the following section.

## C. IP Lookup Using Hashing

Hash function maps a value in domain to a specific value in range uniformly. Thus, hash-based schemes, like a BFHT and an FHT, do not address the issue of supporting wildcard bits in prefixes. In this section, we present two kinds of schemes to support prefix match in a hash-based IP lookup: Controlled Prefix Expansion (CPE) and Prefix Collapse (PC).

#### 1. Controlled Prefix Expansion

Fig. 2. Prefix conversion of a CPE with 3 prefixes in stride 3.

A CPE in [7, 16] is to transform a set of prefixes by combining prefix expansion and prefix capture to reduce any set of arbitrary length prefixes into an expanded set of prefixes in optimized sequence of length. With dynamic programming, it was applied to tries where the worst-case IP lookup time is  $\mathcal{O}(W)$ , where W is the length of IP address. For a hash-based scheme, CPE was used in [16] to support wildcards in prefixes.

Fig. 2 shows a CPE mechanism with prefix database of 3 prefixes as a running example. In expanding bits and wildcard of 3 prefixes, prefix 1001101 is overlapped with prefix 10011\*, so that the total number of expanded prefixes is 6. The 6 expanded prefixes in a new database are keyed to a hash function in hash-based IP lookup schemes. Although a CPE removes wildcards in prefixes for the hashing mechanism, the number of expanded prefixes along with the same number of next hops can become 2 times larger compared to the original prefix set. In general, the expansion is made in multi-fold and by simulation work on BGP tables, AS65000 and AS6447 [51, 52]. We found that the number of expanded prefixes increases as the stride size gets larger and that the number is about 5 times larger in stride 5. The reason is that a given prefix of stride l can be expanded to  $2^{l}$  prefixes if there is no overlapping with other prefix, unlike prefix  $10011^*$  and 1001101.

#### 2. Prefix Collapse

Fig. 3. Prefix conversion of PC with the same 3 prefixes of Fig. 2.

Unlike inflating the number of expanded prefixes and the next-hop informations

in a CPE, a PC converts a prefix of length x into a single prefix of shorter length x-l by replacing its l least significant bits with a wildcard [16]. The truncated prefix of length x-l is collapsed with others of the same x-l bits, so that the number of collapsed prefixes is reduced. Fig. 3 shows the prefix collapse mechanism with the same set of prefixes as in Fig. 2 for a CPE. Although the first conversion expands wildcards of the prefixes in stride 3 like a CPE, the second conversion adopts a bit vector indicating the relative index to a next-hop table. In addition, after expansion of the wildcard, the first and the third prefixes are same among 3 truncated prefixes of length 4. Thus, the final collapsed prefixes are prefix 1001 and 1010 with bit vectors (00001111) and (00000011). Compared to the example in Fig. 2, the number of collapsed prefixes is reduced, while the number of next-hops maintains the same as that for a CPE but yet it still increased 2 times than the original set.

# 3. IPv6 IP Lookup

The addressing architecture for IPv6 is detailed in RFC 3513. In terms of the number of prefix lengths in forwarding tables, the important address type is the global unicast address which many be aggregated. RFC 3513 states that IPv6 unicast addresses may be aggregated with arbitrary prefix lengths like IPv4 address under classless interdomain routing. While this provides extensive flexibility, it is not foreseen that this flexibility necessarily results in an explosion of unique prefix lengths. The global unicast address format has three fields: a global routing prefix, a subnet ID, and an interface ID. All global unicast addresses, other than those that begin with 000, must have a 64-bit interface ID in the Modifed EUI-64 format. These identifiers may be of global or local scope; however, we are only interested in the structure they impose on routing databases. In such cases, the global routing prefix and subnet ID fields must consume a total of 64 bits. If these policies are followed, it could be anticipated that

IPv6 routing tables will not contain a significant difference from the current IPv4 tables except a prefix length distribution. Thus, hash-based IP lookup schemes can play a major role in saving memory and power for IPv6 as for IPv4, compared to TCAM- and trie-based IP lookup schemes.

# D. Packet Classification Using Hashing

The issue of how to reduce the number of used BFs in processing a packet with n BFs is a paramount power concern in any packet processing [12, 14, 53] as well as network application including wireless sensor network [45]. However, in this section we formalize and restrict the issue to packet classification domain.

Fig. 4. Parallel packet classifier engine of n BFs in a given packet.

A parallel lookup with n BFs is a common configuration in packet classification [14] as shown in Fig. 4 where a 5-tuple of SIP, DIP, protocol, SP, and DP is extracted from a packet and a lookup of the 5-tuple is made among n BFs. Fast on-chip packet processing with n BFs is beneficial because it reduces the number of off-chip hash probes [12, 22]. Due to f-positives from the BFs, all positives are required to

be confirmed by a hash table of recorded flows. Due to QoS and security concern, providing a perfect match is necessary in packet classification. Thus, there is BFs' access contention to the hash table. BFs can be fabricated in on-chip due to memory efficiency while the hash table is located in off-chip due to its large size as in other schemes [12, 13, 20]. Thus, the packet lookup throughput is bounded to the processing time in the off-chip hash table.

The worst case throughput can be calculated in the following way: given a lookup of a minimum 40-byte packet, there are two kinds of lookups, an unsuccessful lookup (UL) in which a key is relentlessly searched although it does not exist in BFs, and a successful but time-consuming lookup (SL) in which a key is to be searched in BFs. Let  $t_s$  and  $t_u$  denote processing times in an off-chip hash table (HT) for an SL and a UL, respectively. Then, the packet lookup throughput in n BFs is calculated as

$$T = \frac{40 \cdot 8}{p_s\{t_s + t_u \cdot (n-1)f\} + (1-p_s)\{t_u \cdot nf\}} bits/sec.,$$

(3.6)

where  $p_s$  is an SL rate and the nf and (n-1)f terms explain the expected numbers of f-positives which is based on the binomial distribution of identical and independent BFs in an SL and a UL, respectively.

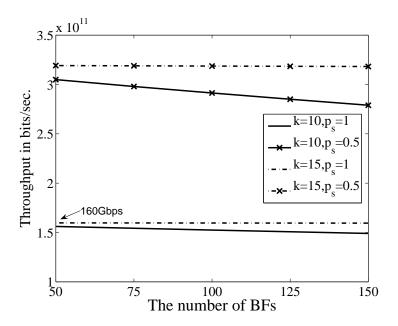

Based on Eq. (3.6), Fig. 5 shows the throughput where HT's processing time in an SL,  $t_s$ , is 1.001 times of 2ns in a modern T-RAM [54] and  $t_u$  is set to 0.5 times of 2ns. In the worst case of  $p_s=1$ , the lookup throughput with BFs of k=10 read ports can barely keep up with 160Gbps while BFs of k=15 read ports can meet the bandwidth. Thus, a large number of read ports in a BF memory are required for a high throughput, and avoiding irrelevant BFs of such a large number of ports for a lookup is preferable. In the following section, such an avoidance is made by a PPC which distributes lookups through small-sized BFs of a few ports, so that a subset of the lookups are processed in large-sized BFs in one clock cycle for a higher power

Fig. 5. Throughput comparison in a different number of BFs,  $p_s$ , and k. and throughput efficiencies.

# CHAPTER IV

## A MULTI-TIERED PACKET CLASSIFIER WITH N BFS

This chapter introduces how to build an MPC and implement insert, query, and delete operations in an MPC for better lookup performance.

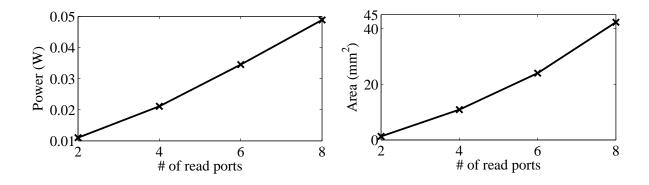

Fig. 6. Power and area in multi memory read ports for 64K×1-bit memory.

Each hash function corresponds to one random lookup in an m-bit BF. Thus, a BF having k hash functions for high throughput needs the exact same k of memory read ports in an m-bit memory module. Although state-of-the-art VLSI technology can fabricate memory with multiple ports, supporting more than 10 ports is tremendously hard as noted in a concise summary of the recent embedded memory technologies [55]. Fig. 6 shows such a difficulty in terms of the power and area costs measured by CACTI [35], according to the number of read ports in a single memory module. The conclusion from the figure is that the power and area costs is superlinear to the number of read ports. Thus, a BF is considered as a high computation element due to the large value of k for the high-speed router, and thereby reconfiguring such BFs for a power- and throughput-efficient lookup is necessary.

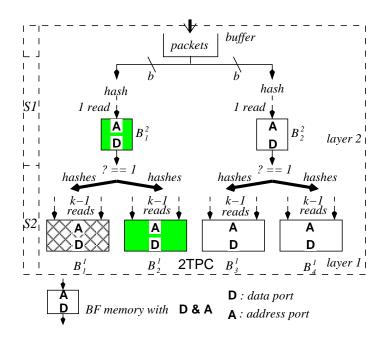

Fig. 7. Pipeline memory architecture of a 2TPC in a forest. S1 and S2 are pipeline stages.  $B_j^i$  means the j-th BF at layer i. n=4. k=w due to Eq. (3.3).  $w_2=1$ ,  $w_1=k-1$ . b is a buffer size.

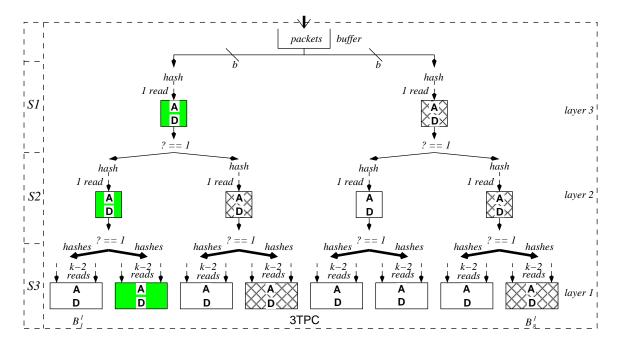

# A. Building a Multi-tiered Packet Classifier

In this section, we derive mathematical proof that an MPC uses the same memory size as that of a PPC while the detailed insertion and query are mentioned in Secs. B and C. Fig. 7 shows a configuration example of an MPC, a 2-tiered PC (2TPC) on top of 4 BFs, in place of a PPC used in a dashed box of Fig. 4. Also, Fig. 8 shows a 3-tiered PC (3TPC) on top of 8 BFs. Given desired f-positive  $f=2^{-w}$ , the total PPC memory in bits with n BFs is  $n \cdot m$ , where m is a BF's memory based on Eq. (3.2). However, with linear property between m and  $n_i$  and an additive operation on memory size  $m_t$ , we can reconfigure BFs in a (r+1)-tiered way, r>0, while the same memory size,  $m_M$ , for an MPC is used as follows:

Fig. 8. Memory architecture of a 3TPC in a forest and in pipeline.  $B_j^i$  means the j-th BF at layer i. n=8. k=w due to Eq. (3.3).

$$n \times m = n \times \{1.44 \cdot n_i \cdot \log_2(1/f)\}\$$

$$= n \times \{1.44 \cdot n_i \cdot w\} = n \times \{1.44 \cdot n_i \cdot (w - r + r)\}\$$

$$= n \cdot 1.44 \cdot n_i \cdot (w - r) + \sum_{t=1}^r \{n \cdot 1.44 \cdot n_i \cdot 1\}\$$

$$= \sum_{i=1}^n (1.44 \cdot n_i \cdot (w - r)) + \sum_{t=1}^r \sum_{i=1}^{n/2^t} (1.44 \cdot (2^t n_i) \cdot 1)$$

$$= m_1 + \sum_{t=1}^r m_{t+1} = m_M,$$

$$(4.1)$$

where  $m_t$  is the total memory of BFs on layer t, r+1 is the number of tiers,  $2^t n_i$  is the number of keys in  $B_i^t$ , and the lookup precisions of a BF on layer 1 and t,  $w_1$  and  $w_t$ , are w-r and 1, respectively. Based on Eq. (3.2), the f-positives of BFs on layer 1 and 2 in a 3TPC are expected to be  $2^{-(w-2)}$  and  $2^{-1}$ , respectively, and the second term,  $\sum_{t=1}^r \sum_{i=1}^{n/2^t} (1.44 \cdot (2^t n_i) \cdot 1)$ , in Eq. (4.1) is the sum of small-sized BFs from

Fig. 9. (a) The total number of read ports in different number of BFs.  $w_3=w_2=1$ ,  $w_1=13$  for a 3TPC.  $w_2=1$ ,  $w_1=14$  for a 2TPC.  $f=2^{-15}$ . (b) 2TPC and PPC area costs with n=8 in .13 $\mu m$  process technology.

layer 2 to layer r+1. Also, a BF from layer 1 covers  $n_i$  elements, and a BF from layer 2 covers  $2n_i$  keys. Generally,  $B_i^j$  covers all keys from  $B_{2i}^{j-1}$  and  $B_{2i+1}^{j-1}$ ,  $1 \le i \le n/2$ ,  $1 < j \le r$  in an MPC.

In this multi-tiered and pipelined configuration with b=1, power in accessing memory (or probing BFs) can be saved. For example,  $B_2^1$  has a key and there is a lookup for the key. By preprocessing the lookup in stage S1 with  $B_1^2$  and  $B_2^2$ , if  $B_2^2$  returns 'no' in the lookup there is no need to probe  $B_3^1$  and  $B_4^1$ . Thus, a power used to probe them can be saved.

In addition to the power concern, simply setting b to more than 1 does not achieve a higher throughput efficiency. Although Eq. (4.1)'s derivation shows that an MPC has the same memory size as a PPC, processing a lookup in small-sized BFs of one read port does not provide a higher throughput in large-sized BFs on a lower layer. For instance, even if b in Fig. 7 with  $w_2=1$  is set to 2, a one-read-port BF on layer 2 cannot process 2 lookups in one cycle. Thus, the number of read ports in the small-

sized BF needs to be the same as b. In general, the number needs to be  $b \cdot w_2$  for a throughput-efficient MPC. As suggested in [12], using mini-BFs with few read ports is the solution without degrading lookup accuracy. However, even if a BF is broken into several mini-BFs, the total number of read ports in the mini-BFs is the same as that of a PPC. Thus, breaking a BF into mini-BFs only gives the possibility of fabricating BFs for packet processing, not the benefit of high throughput. However, a proposed MPC has two benefits of few number of read ports and an area cost which can lead to fabricate small-sized BFs of multi read ports for a high throughput without area overhead.

Figs. 9(a) and 9(b) show such two benefits: the smaller number of fabricated read ports and the smaller area for a 2TPC. Fig. 9(a) shows the required numbers of read ports in fabricating a different number of BFs for a PPC, a 2TPC, and a 3TPC, respectively. In fabricating, a 2TPC and a 3TPC use 4% and 10% less number of read ports than a PPC in all cases. Fig. 9(b) shows 2TPC and PPC area costs in a different number of w and  $n_i$ , and in each case the area costs of using 4 mini-BFs for a BF are measured by using CACTI model [35].

Now, we show how to fabricate multi-ports in a small-sized BF without hardware overhead. There is a noticeable gap between dotted and solid meshes in Fig. 9(b), and the reason is that fabricating multi-ports in a small-sized memory does not need area as much as in a large-sized memory. Due to page limit, we did not plot the area costs for 2 through 5 read ports in a small-sized BF memory on layer 2. However, there is a small area increase for the multi-port memory, compared to a PPC's area. Thus, it is clear that the buffer size b can amount to 5 at the most. Also, utilizing dual reads on falling and rising edges in a clock [56] can double the memory read capacity and a lookup throughput (i.e. double data rate scheme does in DRAM and AMD Athlon64). Thus, the buffer size becomes twice and the maximum b is 10 without

memory overhead in an MPC.

## B. Insert Operation in an MPC

Insert operation of a key in a BF on layer 1 is as simple as the key's insertion in a legacy BF. Similarly, on layer j, if a key to hash is assigned to  $B_i^j$ , the key is given to  $B_{\lfloor i/2 \rfloor}^{j+1}$  for insert operation,  $1 < j \le s$ . The detailed procedure is shown in **Procedure insert** which does  $k_j$  times memory write on layer j. Therefore, the memory write complexity of one key insertion is  $\sum_{t=1}^{s} k_t = w = k_P$  which is the same as a PPC, where  $k_P$  is based on Eq. (3.3). Also, note that the first vertically lined for can be in pipeline because BF memories on a layer are independent ones from other layers. Thus, in every cycle one key insertion is performed on the condition that  $B_i^1$  on layer 1,  $1 \le i \le n$ , supports multiports.

# C. Query Operation in an MPC

Unlike insert operation where only the involved BFs are accessed, query operation needs to access all BFs to find which BFs return 'yes'. Because except one involved BF the rest of irrelevant BFs give f-positives leading to packet misclassification, the irrelevant BFs in an MPC are not considered for probing, so that the BF access complexity in processing a lookup with n BFs is far less than n. To provide such a