# HYBRID ANALYSIS OF MEMORY REFERENCES AND ITS APPLICATION TO AUTOMATIC PARALLELIZATION

A Dissertation

by

## SILVIUS VASILE RUS

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2006

Major Subject: Computer Science

# HYBRID ANALYSIS OF MEMORY REFERENCES AND ITS APPLICATION TO AUTOMATIC PARALLELIZATION

## A Dissertation

by

## SILVIUS VASILE RUS

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee,

Lawrence Rauchwerger

Committee Members,

Nancy Amato

Narasimha Reddy

Vivek Sarin

Head of Department,

Valerie Taylor

December 2006

Major Subject: Computer Science

## ABSTRACT

Hybrid Analysis of Memory References

and Its Application to Automatic Parallelization. (December 2006)

Silvius Vasile Rus, B.S., Babes-Bolyai University

Chair of Advisory Committee: Dr. Lawrence Rauchwerger

Executing sequential code in parallel on a multithreaded machine has been an elusive goal of the academic and industrial research communities for many years. It has recently become more important due to the widespread introduction of multicores in PCs. Automatic multithreading has not been achieved because classic, static compiler analysis was not powerful enough and program behavior was found to be, in many cases, input dependent. Speculative thread level parallelization was a welcome avenue for advancing parallelization coverage but its performance was not always optimal due to the sometimes unnecessary overhead of checking every dynamic memory reference.

In this dissertation we introduce a novel analysis technique, Hybrid Analysis, which unifies static and dynamic memory reference techniques into a seamless compiler framework which extracts almost maximum available parallelism from scientific codes and incurs close to the minimum necessary run time overhead. We present how to extract maximum information from the quantities that could not be sufficiently analyzed through static compiler methods, and how to generate sufficient conditions which, when evaluated dynamically, can validate optimizations.

Our techniques have been fully implemented in the Polaris compiler and resulted in whole program speedups on a large number of industry standard benchmark applications. To Ixel, Ileana and Vasile

#### ACKNOWLEDGMENTS

First, I would like to thank Lawrence Rauchwerger, my academic advisor for teaching me how to be a researcher. He taught me how to read scientific papers, how to extract the essence from a free roaming idea, and how to design, run and understand scientific experiments. I owe Lawrence for never having to worry a single day about funding throughout my entire Ph.D. student life. Above all, he did well what any good advisor should do: give good advice. Perhaps not all was taken, but all was heard, listened to and learned from.

I want to thank Nancy Amato for her advice, but even more so for making time to read my papers even when she had her own close deadlines. She is a model to follow regardless where I go from here. I would like to thank my committee members Narasimha Reddy and Vivek Sarin for taking the time to advise me on my research.

I am grateful to Jay Hoeflinger for his collaboration on my first paper. A part of my experimental setup was built on top of code written by him. I thank Marvin Adams for giving me the opportunity to work on an important nuclear engineering project and for teaching me some of the reasons why physicists want more computing power. Francis Dang helped me run experiments as a colleague and later as the administrator of the on-site supercomputer. Hao Yu helped me understand some more difficult parts of my research topic. Guobin He, Dongmin Zhang and Marinus (Maikel) Pennings helped me with compiler development and also helped me validate my ideas before putting them into practice. I benefited much from talking to, listening to, and being around other students in my group: Alin Jula, Julio Antonio Carvallo de Ochoa, Nathan Thomas, Tim Smith, Gabriel Tănase, Steven Saunders, William McLendon and Antoniu Pop.

I would like to thank the people I worked with at IBM Research, Gheorghe Almási, José Moreira and Manish Gupta, for giving me the opportunity to be a small part of the BlueGene/L project. I learned to be a better person from their attitude, professionalism and dedication.

I thank the Computer Science Department and the GAANN program at the Department of Education for supporting me through a teaching assistantship and a fellowship respectively. I would like to thank the administrative staff at the Computer Science Department, and especially Kay Jones, Sandra Morse and Elena Rodriguez, for making complicated procedures seem easy.

Long before I became a Ph.D. student, several great people shaped my mind. My first teacher, Raveca Găurean, cultivated the values seeded by my parents: respect, correctness and common sense. My math teachers, Gheorghe Simionaş, Nicolae Sanda, Petru Ivănescu, and Csaba Varga, made me understand that memorizing a formula makes you its slave, while knowing how to create it makes you its master.

My close friend, Merrill, made my stay in Bryan/College Station better, lighter on the heart. He is not only a friend, but also a fellow scientist, my landlord for the last two years and a surrogate parent. Ben Krieger was my first host in College Station and helped me learn the ways of Texas and Aggieland. Deborah Lord and Alin Jula were my good friends from the beginning.

My mother and father deserve the credit for making me into who I am. They have supported me wholeheartedly throughout my life. They have believed in me and have inspired me with their successful and happy lives. I am forever thankful to them, as well as to my brother, Marius, my uncle Tudor and aunt Maria for their continuous support.

To my wife, Ixel, I owe the magic of being able to smile every day. She has given me strength and hope. Her vision of life opened my eyes and changed my life forever.

## TABLE OF CONTENTS

| CHAPT | ΓER                                                                            | Page |

|-------|--------------------------------------------------------------------------------|------|

| I     | INTRODUCTION                                                                   | 1    |

|       | A. Parallel Computers                                                          | 1 2  |

|       | C. Hybrid Analysis                                                             | 4    |

|       | D. Contribution                                                                | 6    |

|       | E. Organization                                                                | 7    |

| II    | FUNDAMENTALS AND PREVIOUS WORK                                                 | 8    |

|       | A. Fundamentals of Automatic Parallelization                                   | 8    |

|       | 1. Scalar Data Flow and Data Dependence                                        | 8    |

|       | 2. Array Data Flow and Data Dependence                                         | 10   |

|       | B. Current State of the Art in Automatic Parallelization                       | 12   |

|       | 1. Compiler Analysis                                                           | 12   |

|       | a. Data Flow Analysis                                                          | 12   |

|       | b. Data Dependence Analysis                                                    | 15   |

|       | c. Analysis of Array References                                                | 18   |

|       | 2. Compiler Transformations                                                    | 20   |

|       | a. Removing Flow Dependences                                                   | 20   |

|       | b. Removing Storage Related Dependences                                        | 21   |

|       | c. Results in Automatic Parallelization                                        | 21   |

|       | 3. Run Time Parallelization Techniques                                         | 22   |

|       | a. Instrumentation of Memory References                                        | 22   |

|       | b. Optimization Predicate Extraction                                           | 24   |

|       | c. Partially Parallel Loops and Communication                                  |      |

|       | Schedules                                                                      | 25   |

|       | $\operatorname{d.}\nolimits$ Inspector Executor vs. Speculative Optimization . | 26   |

| III   | HYBRID MEMORY REFERENCE ANALYSIS                                               | 27   |

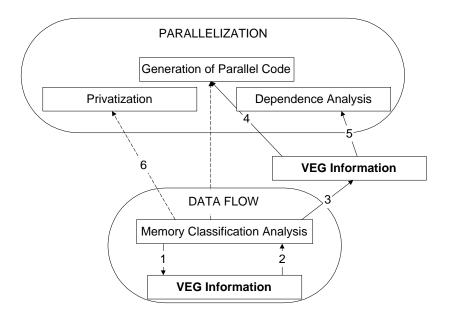

|       | A. An Overview of Hybrid Analysis Applied to Parallelization                   | 28   |

|       | B. Proposed Memory Reference Representation: USR                               | 30   |

|       | 1. Program Model                                                               | 33   |

|       | 2. Background: the Linear Memory Access Descriptor                             | 33   |

|       | 3. Abstraction of Set Operations                                               | 35   |

35

# CHAPTER

| b. Set Difference                                         | 36 |

|-----------------------------------------------------------|----|

| c. Set Union                                              | 37 |

| 4. Abstraction of Loops                                   | 38 |

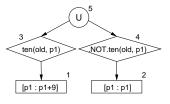

| 5. Abstraction of Control                                 | 40 |

| 6. Abstraction of Subprograms                             | 40 |

| 7. Formal Definition                                      | 42 |

| C. Hybrid Memory Reference Analysis using USRs            | 43 |

| 1. Memory Classification Analysis                         | 44 |

| a. Classification of References in Straight Line Code     | 45 |

| b. Classification of References in Conditional Blocks     | 46 |

| c. Classification of References in Loops                  | 47 |

| d. Interprocedural Classification of References           | 50 |

| 2. Dependence Testing as Verification of USR Identities . | 51 |

| D. Hybrid Dependence Analysis                             | 52 |

| 1. Symbolic Representation: the PDAG                      | 53 |

| 2. Symbolic Analysis Algorithms                           | 54 |

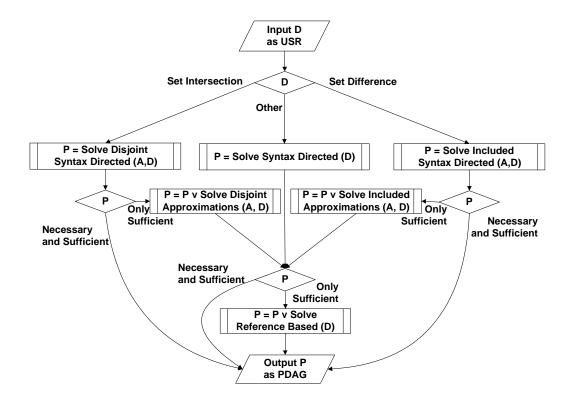

| a. Syntax Directed Predicate Extraction                   | 54 |

| b. Extracting PDAGs from USR Approximations               | 57 |

| c. Predicate Extraction from Finite Valued USRs           | 59 |

| d. Extracting PDAGs from LMAD Equations                   | 60 |

| 3. Testing Monotonicity and Disjoint Intervals            | 60 |

| 4. Reference Pattern Library: Extensible Compiler         | 61 |

| 5. Fallback: Reference-based Dependence Tests             | 62 |

| 6. Case Study                                             | 62 |

| E. Other Applications of Memory Reference Analysis        | 65 |

| 1. Array Data Flow Analysis                               | 65 |

| a. Region Array SSA                                       | 66 |

| b. Transformations Based on Data Flow Analysis            | 68 |

| 2. Efficient Recompilation                                | 68 |

| 3. Program Verification and Symbolic Debugging            | 70 |

| F. Related Work                                           | 71 |

| G. Conclusions                                            | 73 |

| IV SYMBOLIC VALUE ANALYSIS                                | 75 |

| A. Motivation                                             | 75 |

| 1. Background and a Motivating Example                    | 77 |

| 2. Our Solution: The Value Evolution Graph                | 78 |

| •                                                         |    |

# CHAPTER

| В.    | The Value Evolution Graph (VEG)                       | 80  |

|-------|-------------------------------------------------------|-----|

|       | 1. Formal Definition                                  | 81  |

|       | 2. Value Evolution Graph Construction                 | 83  |

|       | 3. Queries on Value Evolution Graphs                  | 85  |

|       | 4. VEG Conditional Pruning                            | 86  |

| С.    | VEG-based Memory Reference Analysis                   | 87  |

|       | 1. Using the VEG in Memory Classification Analysis    | 89  |

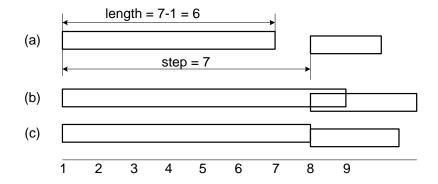

|       | 2. Memory Reference Sequence Classification           | 90  |

|       | 3. VEG Applications to Classic Compiler Optimizations | 92  |

|       | a. Dataflow Analysis                                  | 92  |

|       | b. Privatization                                      | 93  |

|       | c. Dependence Analysis                                | 93  |

|       | 4. Recognition of Pushbacks and                       |     |

|       | Other Parallelizable Prefix Computations              | 94  |

|       | a. Pushback Sequences                                 | 95  |

|       | b. Other Parallelizable Sequences                     | 96  |

| D.    | Case Studies                                          | 97  |

|       | 1. ADM/DKZMH_do60                                     | 100 |

|       | 2. TRACK/EXTEND_do400                                 | 100 |

| E.    | Related Work                                          | 102 |

|       | 1. Recurrence Recognition, Classification, and Paral- |     |

|       | lelization                                            | 102 |

|       | 2. Analysis of Memory Referenced by Recurrences with- |     |

|       | out Closed Forms                                      | 103 |

| F.    | Conclusions and Future Work                           | 105 |

| V ENG | SINEERING A HYBRID AUTOMATIC PARALLELIZER .           | 106 |

| A.    | Automatic Parallelizer Overview                       | 106 |

| В.    | Static vs. Dynamic Parallelization                    | 107 |

| С.    | Dynamic Optimization Strategy                         | 109 |

|       | 1. Inspector/Executor                                 | 109 |

|       | 2. Speculation                                        | 110 |

|       | a. Checkpointing                                      | 110 |

|       | 3. Inspector/Executor vs. Speculative Execution       | 111 |

| D.    | Transformations to Remove Dependences                 | 112 |

|       | 1. Hybrid Privatization                               | 114 |

|       | a. Hybrid Copy In                                     | 116 |

|       | b. Hybrid Copy Out and Last Value Assignment          | 116 |

|       |                                                       |     |

## CHAPTER

|     | 2. Hydrid Reduction Parallelization                      |

|-----|----------------------------------------------------------|

|     | 3. Pushback Sequence Parallelization                     |

|     | E. Automatic Detection of Array Bounds                   |

|     | F. Case Study: DYFESM/MXMULT_do10 120                    |

|     | 1. Discussion                                            |

| VI  | COMPILER DESIGN AND IMPLEMENTATION                       |

|     | A. Making General Applications Fit our Program Model 133 |

|     | 1. Bringing Programs to Block Structured Form 132        |

|     | 2. Alias Disambiguation                                  |

|     | a. Commons                                               |

|     | b. Equivalence                                           |

|     | c. Type Mismatches across Subprograms 136                |

|     | 3. Language and Programming Style Issues 137             |

|     | a. Array Bound Declarations                              |

|     | b. Multiple Subprogram Entries                           |

|     | c. Data Statements                                       |

|     | d. Lazy Initialization Code                              |

|     | B. USR Design and Implementation                         |

|     | 1. USR Optimization                                      |

|     | a. Optimization Based on Minimal Evaluation              |

|     | Cost Form                                                |

|     | b. Partial Invariants                                    |

|     | c. Approximation with LMAD Lists 144                     |

|     | d. Language Specific Optimization 145                    |

|     | C. PDAG Design and Implementation                        |

|     | D. Complexity of Hybrid Analysis                         |

|     | 1. Compile Time Complexity                               |

|     | a. Memory Classification Analysis 149                    |

|     | b. PDAG Extraction                                       |

|     | 2. Run Time Complexity                                   |

|     | a. USR Evaluation                                        |

|     | b. PDAG Evaluation                                       |

| VII | EMPIRICAL EVALUATION                                     |

|     | A. Methodology                                           |

|     | 1. Hardware and Software Environment                     |

|     | 2. Input Data Sets                                       |

# CHAPTER

| APPENDIX A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3. Performance Metrics                                  | 161 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|

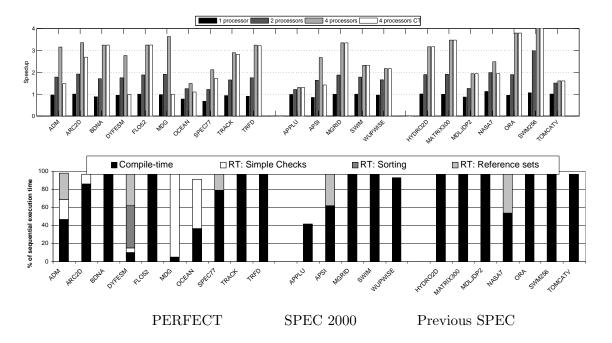

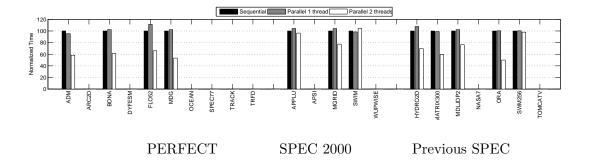

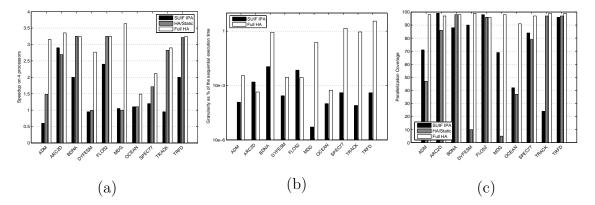

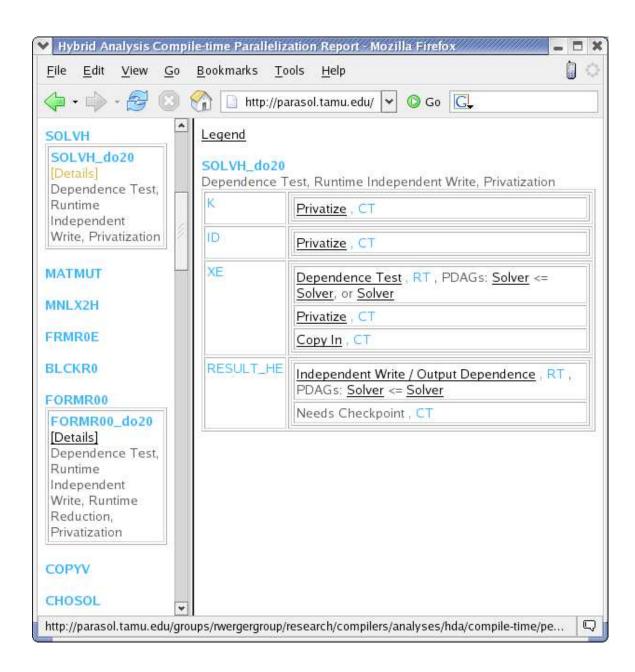

| D. Comparison to Other Parallelizing Compilers       165         1. The Intel® Compiler       165         2. The IBM Toronto Lab Parallelizing Compiler       167         3. The SUIF Research Compiler       168         E. Discussion of Important Loops       170         1. Value Evolution Graph       173         2. USR Based Memory Reference Analysis       173         3. PDAG Based Efficient Run Time Tests       174         a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         d. Dynamic Parallelization, Privatization and Reduction       176         VIII       CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         3. Extending Hybrid Analysis       179         1. Extending Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183 | B. Hybrid Analysis Automatic Parallelization Results    | 162 |

| 1. The Intel® Compiler       165         2. The IBM Toronto Lab Parallelizing Compiler       167         3. The SUIF Research Compiler       168         E. Discussion of Important Loops       170         1. Value Evolution Graph       173         2. USR Based Memory Reference Analysis       173         3. PDAG Based Efficient Run Time Tests       174         a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         4. Dynamic Parallelization, Privatization and Reduction       176         VIII       CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       179         a. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       <             | C. Evaluation of Run Time Tests                         | 164 |

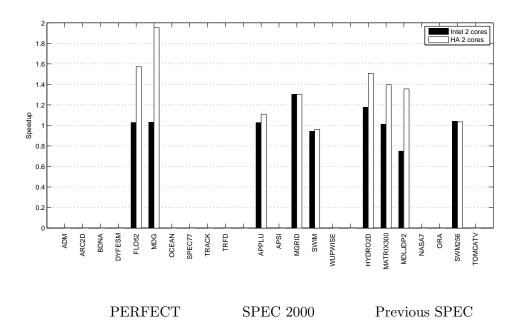

| 2. The IBM Toronto Lab Parallelizing Compiler       167         3. The SUIF Research Compiler       168         E. Discussion of Important Loops       170         1. Value Evolution Graph       173         2. USR Based Memory Reference Analysis       173         3. PDAG Based Efficient Run Time Tests       174         a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         d. OCEAN       175         4. Dynamic Parallelization, Privatization and Reduction       176         VIII       CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       180         b. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183                         | D. Comparison to Other Parallelizing Compilers          | 165 |

| 3. The SUIF Research Compiler       168         E. Discussion of Important Loops       170         1. Value Evolution Graph       173         2. USR Based Memory Reference Analysis       173         3. PDAG Based Efficient Run Time Tests       174         a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         d. Dynamic Parallelization, Privatization and Reduction       176         VIII CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         APPENDIX A       218                                                                      |                                                         | 165 |

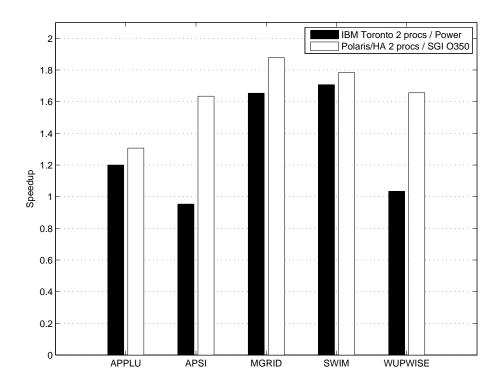

| E. Discussion of Important Loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2. The <i>IBM Toronto Lab</i> Parallelizing Compiler    | 167 |

| 1. Value Evolution Graph       173         2. USR Based Memory Reference Analysis       173         3. PDAG Based Efficient Run Time Tests       174         a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         4. Dynamic Parallelization, Privatization and Reduction       176         VIII CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         APPENDIX A       218          APPENDIX B       224                                                                                                                                           |                                                         | 168 |

| 2. USR Based Memory Reference Analysis       173         3. PDAG Based Efficient Run Time Tests       174         a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         4. Dynamic Parallelization, Privatization and Reduction       176         VIII CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       180         b. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         APPENDIX A       218         APPENDIX B       224                                                                                                                                          | E. Discussion of Important Loops                        | 170 |

| 2. USR Based Memory Reference Analysis       173         3. PDAG Based Efficient Run Time Tests       174         a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         4. Dynamic Parallelization, Privatization and Reduction       176         VIII CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       180         b. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         APPENDIX A       218         APPENDIX B       224                                                                                                                                          | 1. Value Evolution Graph                                | 173 |

| a. ADM/APSI       174         b. MDG       175         c. DYFESM       175         d. OCEAN       175         4. Dynamic Parallelization, Privatization and Reduction       176         VIII CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       180         b. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218                                                                                                                                                                                                                                                            |                                                         | 173 |

| b. MDG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3. PDAG Based Efficient Run Time Tests                  | 174 |

| c. DYFESM       175         d. OCEAN       175         4. Dynamic Parallelization, Privatization and Reduction       176         VIII CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       179         a. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218         APPENDIX B       224                                                                                                                                                                                                                                                                                      | a. ADM/APSI                                             | 174 |

| d. OCEAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | b. MDG                                                  | 175 |

| 4. Dynamic Parallelization, Privatization and Reduction  VIII CONCLUSIONS AND FUTURE WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | c. DYFESM                                               | 175 |

| VIII       CONCLUSIONS AND FUTURE WORK       177         A. Contributions       178         1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       180         b. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218                                                                                                                                                                                                                                                                                                                                                                                                                                              | d. OCEAN                                                | 175 |

| A. Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4. Dynamic Parallelization, Privatization and Reduction | 176 |

| 1. Program Representation       178         2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       179         a. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218         APPENDIX B       224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VIII CONCLUSIONS AND FUTURE WORK                        | 177 |

| 2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       179         a. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218         APPENDIX B       224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A. Contributions                                        | 178 |

| 2. Program Analysis       179         B. Future Work       179         1. Extending Hybrid Analysis       179         a. Hybrid Pointer Analysis       180         b. Hybrid Optimization for High Level Languages       181         2. Applications of Hybrid Dataflow Analysis       182         a. Generation of Communication Schedules       182         b. Compiler-based Cache Coherence       182         c. Symbolic Debugging and Verification       183         d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218         APPENDIX B       224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1. Program Representation                               | 178 |

| B. Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         | 179 |

| a. Hybrid Pointer Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B. Future Work                                          | 179 |

| b. Hybrid Optimization for High Level Languages . 181 2. Applications of Hybrid Dataflow Analysis 182 a. Generation of Communication Schedules 182 b. Compiler-based Cache Coherence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1. Extending Hybrid Analysis                            | 179 |

| b. Hybrid Optimization for High Level Languages . 181 2. Applications of Hybrid Dataflow Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · · · · · · · · · · · · · · · · · · ·                   | 180 |

| 2. Applications of Hybrid Dataflow Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | b. Hybrid Optimization for High Level Languages .       | 181 |

| b. Compiler-based Cache Coherence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2. Applications of Hybrid Dataflow Analysis             | 182 |

| b. Compiler-based Cache Coherence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | a. Generation of Communication Schedules                | 182 |

| d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218         APPENDIX B       224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         | 182 |

| d. Other Uses       183         3. Dynamic Compilation Based on Input Sensitivity       184         REFERENCES       185         APPENDIX A       218         APPENDIX B       224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | c. Symbolic Debugging and Verification                  | 183 |

| REFERENCES       185         APPENDIX A       218         APPENDIX B       224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         | 183 |

| APPENDIX A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3. Dynamic Compilation Based on Input Sensitivity       | 184 |

| APPENDIX B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REFERENCES                                              | 185 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | APPENDIX A                                              | 218 |

| VITA 237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | APPENDIX B                                              | 224 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VITA                                                    | 237 |

## LIST OF TABLES

|      | TABLE                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι    | Static dependence tests                                                                                                                                                                                                    |

| II   | MCA partitions for the privatization problem on array $A$ in Fig. 11(a). 4-                                                                                                                                                |

| III  | Extracting evolutions from the program                                                                                                                                                                                     |

| IV   | Uses of memory reference sequence classification for the parallelization of the outer loop of a doubly nested loop                                                                                                         |

| V    | Loops parallelized. $CP = Conditional Pushback, SL(U) = Stack$<br>Lookup (and Update), $P-CW = Privatization based on Contiguous Writes, P-VEG = Privatization using the VEG directly 98$                                  |

| VI   | Comparison to recent work on memory referenced through recurrences without closed forms                                                                                                                                    |

| VII  | Comparison of parallel code generation strategies                                                                                                                                                                          |

| VIII | Comparison of run time privatization strategies                                                                                                                                                                            |

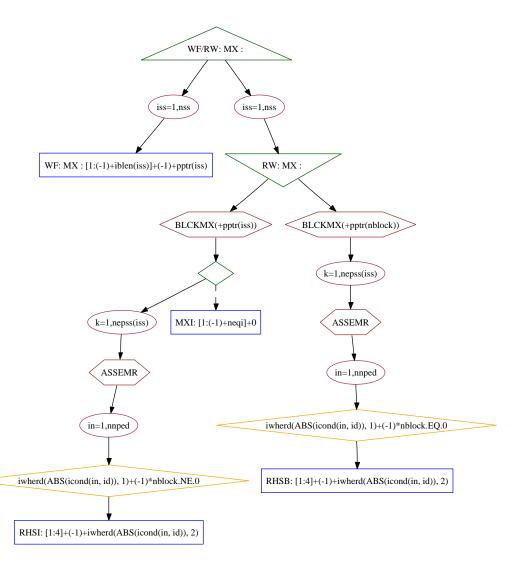

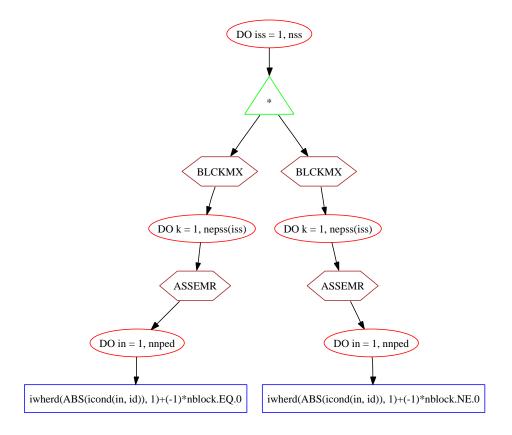

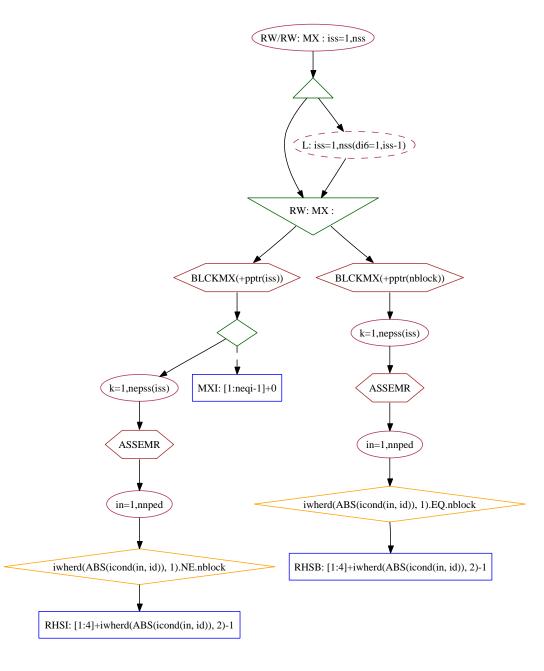

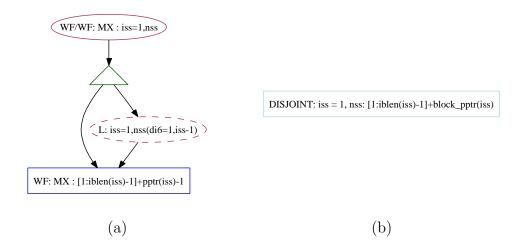

| IX   | Run time tests actually executed to decide whether the dependence structure on array $MX$ prohibits or allows parallelization.  %S represents the time spent in the test as a percentage of the execution time of the loop |

| X    | Attribute grammar for generating Fortran code for USRs 140                                                                                                                                                                 |

| XI   | USR evaluation cost model                                                                                                                                                                                                  |

| XII  | USR approximation using LMAD lists                                                                                                                                                                                         |

| XIII | Compile-time analysis statistics in seconds for both MCA and PDAG extraction for parallelization. Column 4 and 5 show the total number of USR and PDAG nodes created (operator or leaves) 153                              |

# TABLE

| XIV  | Run time test dynamic overhead reduction through HDA: ratio between the number of actual memory references and the number of PDAG operations performed at run time. Only the applications with run time tests are shown.                                                                                                                                                                                                                                                                                                                                                                                                           | 153 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

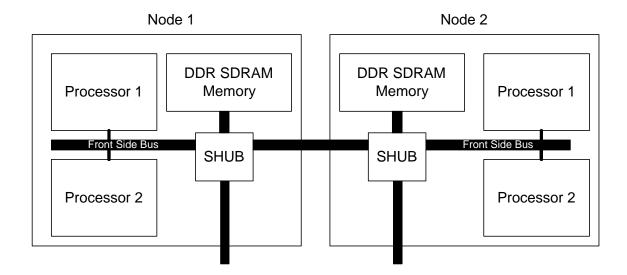

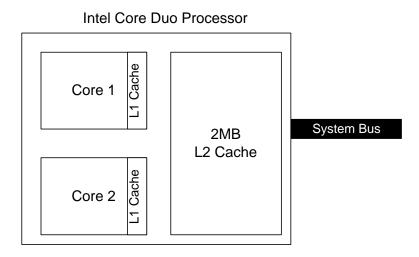

| XV   | Experiment environments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 160 |

| XVI  | Loop parallelization in PERFECT codes. % = percentage of total application execution time. DD Test = type of data dependence test required (CT = compile time, RT = run time, SE = simple logical expressions, IT = interval trees, UE = USR evaluation, LRPD = LRPD run time test) Priv = type of privatization required (A = array privatization). Red = type of reduction required. PB = pushback required. IP = loop contains subprogram calls. EX = execution type (IE = inspector/executor, SP = speculative execution). Intel = parallelized automatically by the Intel Compiler (version 9.0, -parallel -par_threshold100) | 171 |

| XVII | Loop parallelization in SPEC codes. (Legend in Table XVI.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 172 |

## LIST OF FIGURES

|   | FIGURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

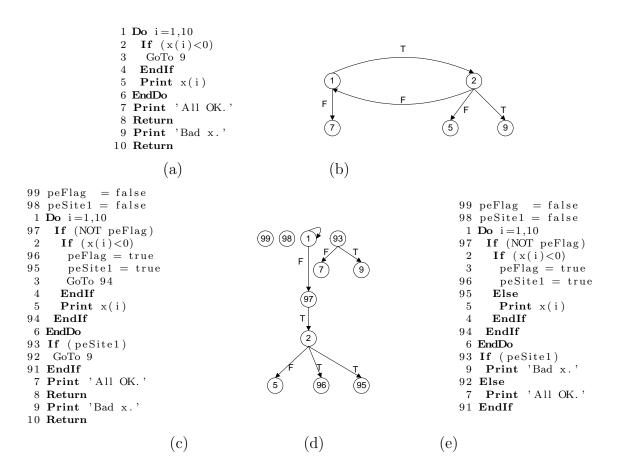

| 1 | Example of an input-sensitive memory reference pattern and corresponding code after parallelization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5    |

| 2 | Data dependences prevent parallelization. Privatization can eliminate storage related dependences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9    |

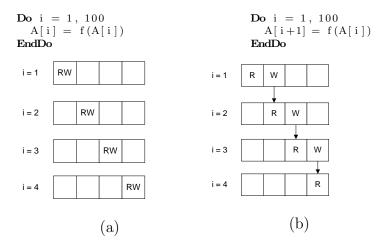

| 3 | Generic memory references through arrays. (a) different locations are referenced in each iteration respectively; no data flow is possible. (b) there is a data flow from each iteration $i$ to iteration $i+1$ on array element $i+1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11   |

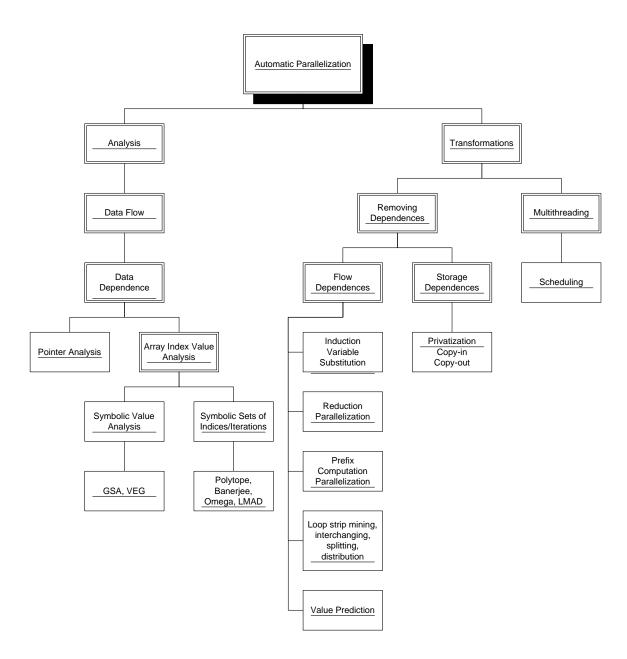

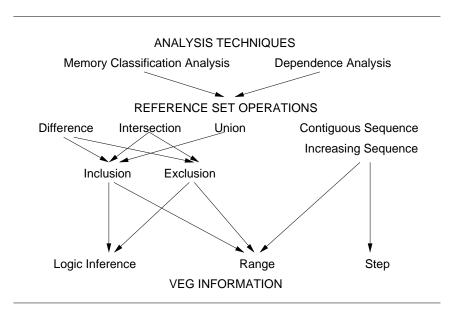

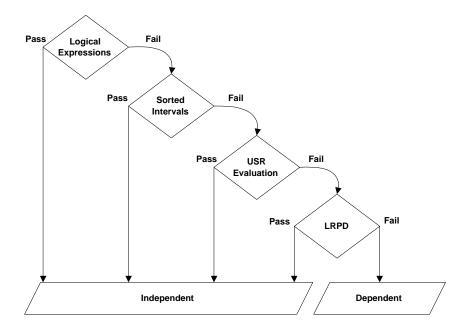

| 4 | Organization of the compiler techniques needed for the automatic parallelization of loops for shared memory machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13   |

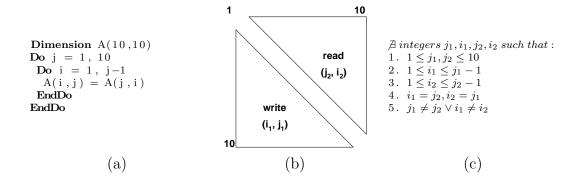

| 5 | (a) Kernel to make matrix symmetric. (b) Geometric and (c) algebraic interpretations of the data dependence test for the <i>write</i> vs. <i>read</i> operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15   |

| 6 | Run time parallelization based on instrumenting every memory reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23   |

| 7 | Inspector / executor vs. speculative execution. (a) original code, (b) inspector/executor parallelization and (c) speculative parallelization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24   |

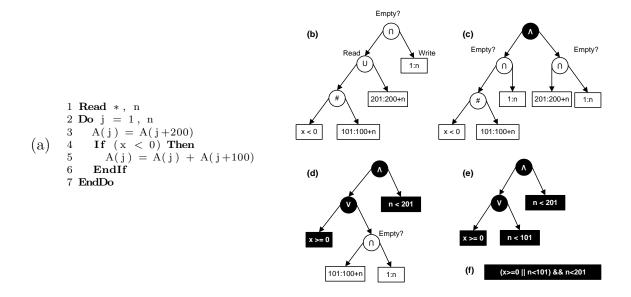

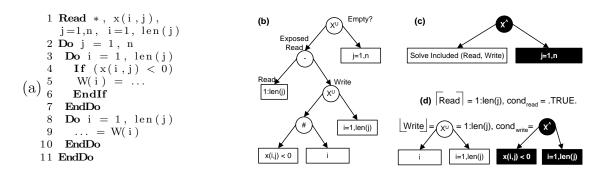

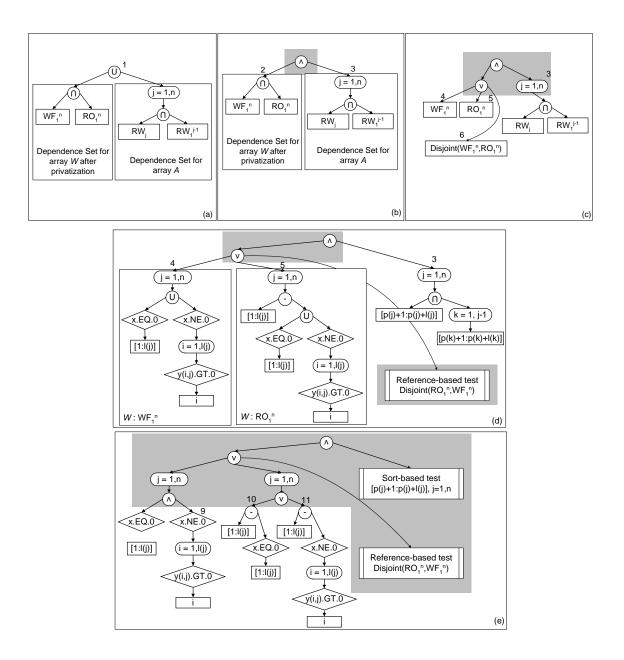

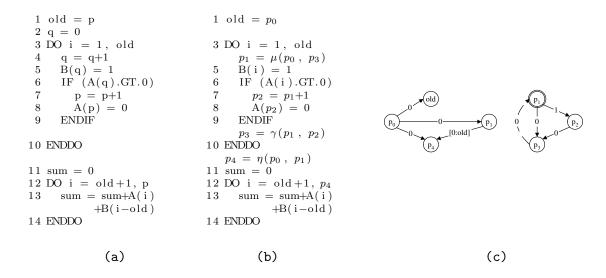

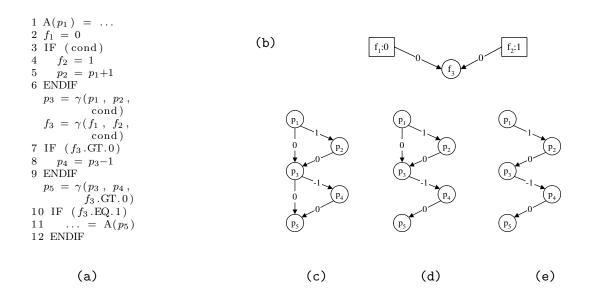

| 8 | Extraction of an independence predicate from an independence equation. The black nodes represent simple conditions and logical operations that are easier to evaluate at run time than it is to solve the original independence problem. (a) Original code. (b) Independence equation as intersection of read and write reference sets. $\cap$ and $\cup$ stand for set intersection and union respectively and $\#$ means predication. (c) The original problem was divided into two subproblems. $\wedge$ and $\vee$ stand for logical and and or respectively. (d) Intermediate result. (e) The final result is an accurate independence predicate which is inserted in the generated code (f) and that will be evaluated efficiently at run | 20   |

|   | $\qquad \qquad {\rm time.} \qquad \ldots $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29   |

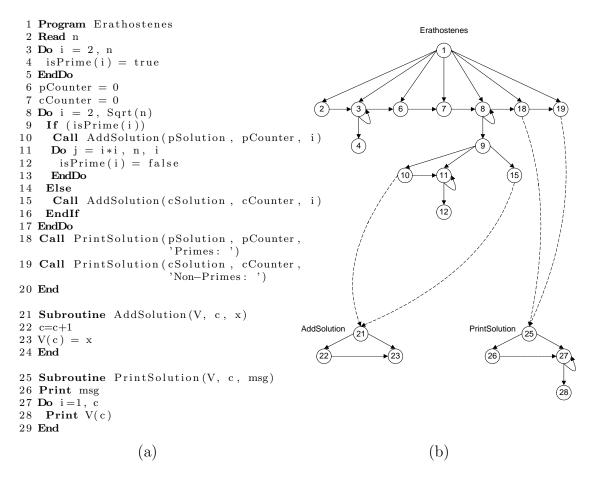

| 9  | Graph and Control Dependence Graphs (CD edges shown as solid lines). CD siblings are connected by dotted lines given by the post-dominance relation in the original Control Flow Graph. Subprogram call relations are shown as dashed lines                                                                                                                                                                                                           | 32 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10 | USR intersection ( $\cap$ ): (a) when the result is an LMAD and (b) when the result cannot be represented as an LMAD                                                                                                                                                                                                                                                                                                                                  | 35 |

| 11 | USR difference (-): (a) when the result is an LMAD and (b) when the result cannot be represented as an LMAD                                                                                                                                                                                                                                                                                                                                           | 36 |

| 12 | USR union ( $\cup$ ): (a) when the result is an LMAD and (b) when the result cannot be represented as an LMAD                                                                                                                                                                                                                                                                                                                                         | 37 |

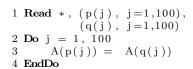

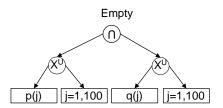

| 13 | USR expansion ( $\otimes^{\cup}$ ): (a) when the result is an LMAD and (b) when the result cannot be represented as an LMAD                                                                                                                                                                                                                                                                                                                           | 38 |

| 14 | USR gate (#): (a) when the result is an LMAD and (b) when the result cannot be represented as an LMAD                                                                                                                                                                                                                                                                                                                                                 | 39 |