## VOLTAGE SENSING BASED BUILT-IN CURRENT SENSOR FOR $I_{\text{DDQ}}$ TEST

A Dissertation

by

### BIN XUE

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

December 2005

Major Subject: Computer Engineering

## VOLTAGE SENSING BASED BUILT-IN CURRENT SENSOR FOR $I_{\text{DDQ}}$ TEST

A Dissertation

by

## BIN XUE

## Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Duncan M. Walker      |  |

|---------------------|-----------------------|--|

| Committee Members,  | Jyh-Charn Liu         |  |

|                     | Rabinarayan Mahapatra |  |

|                     | Henry F. Taylor       |  |

| Head of Department, | Valerie E. Taylor     |  |

December 2005

Major Subject: Computer Engineering

### ABSTRACT

Voltage Sensing Based Built-In Current Sensor for IDDO Test.

(December 2005)

Bin Xue, B.S., Xiamen University, China;

M.S., National University of Singapore

Chair of Advisory Committee: Dr. Duncan M. Walker

Quiescent current leakage test of the  $V_{DD}$  supply ( $I_{DDQ}$  Test) has been proven an effective way to screen out defective chips in manufacturing of Integrated Circuits (IC). As technology advances, the traditional  $I_{DDQ}$  test is facing more and more challenges. In this research, a practical built-in current sensor (BICS) is proposed and the design is verified by three generations of test chips. The BICS detects the signal by sensing the voltage drop on supply lines of the circuit under test (CUT). Then the sensor performs analog-to-digital conversion of the input signal using a stochastic process with scan chain readout. Self-calibration and digital chopping are used to minimize offset and low frequency noise and drift. This non-invasive procedure avoids any performance degradation of the CUT. The measurement results of test chips are presented. The sensor achieves a high  $I_{DDQ}$  resolution with small chip area overhead. This will enable  $I_{DDQ}$  of future technology generations.

## DEDICATION

To my wife, my parents and my sister: without their support this wouldn't have been possible. And to my little sweetheart, Rochelle, who just turned 10 months old.

#### ACKNOWLEDGMENTS

First I would like to express my thankfulness to my advisor, Dr. Duncan M. (Hank) Walker, to whom I owe a lot. His insights in this particular research area, his technical guidance and spiritual support were invaluable to this work. Like other students under his guidance, I am also thankful to his patience and care for me and my family.

I would like to thank Dr. Rabi Mahapatra, Dr. Steve Liu and Dr. Henry Taylor for serving on my committee and for their careful review and constructive comments.

I am grateful for the support from Dr. Mahapatra and his student, Lin Junyi, for helping me with the FPGA test fixture setup. Dr. Liu helped me access laboratory facilities and test equipment. I also want to thank my friend, Xiaohua Fan, with whom I held many valuable discussions on the research topic. My thankfulness also goes to Tianwei Li, who helped take die photos and who provided useful suggestions regarding Cadence tools.

I gratefully acknowledge the sponsorship from Semiconductor Research Corporation (SRC) and National Science Foundation (NSF).

I would like to thank my colleagues and friends, Zoran, Sagar, Wangqi, Abhijit, Jing, and Lei, and others, who made my time in this little Texas town of College Station enjoyable.

I feel deeply indebted to my parents and sister for their love and moral support throughout my life. I sincerely thank my wife, Hui, for her love, care and support, without which this work would not have been possible. My little sweetheart, Rochelle, brings me endless joy. You are a consistent source of inspiration.

## **TABLE OF CONTENTS**

| 1. | INT              | RODUCTION                                           | 1  |

|----|------------------|-----------------------------------------------------|----|

|    | 1.1              | Introduction                                        |    |

|    | 1.2              | Testing Terminologies                               |    |

|    | 1.3              | Motivation                                          |    |

|    | 1.4              | Objectives of the Research                          | 8  |

|    | 1.5              | Structure of the Dissertation                       | 8  |

| 2. | BAC              | CKGROUND                                            | 10 |

|    | 2.1              | Introduction                                        | 10 |

|    | 2.2              | IC Manufacturing Process Flow                       | 10 |

|    | 2.3              | IC Manufacturing Defects                            | 11 |

|    | 2.4              | Principles of I <sub>DDQ</sub> Testing              | 16 |

|    | 2.5              | Advantages of I <sub>DDQ</sub> Test                 |    |

|    | 2.6              | I <sub>DDQ</sub> Test Challenges                    | 21 |

|    | 2.7              | I <sub>DDQ</sub> Test for Future Technologies       |    |

| 3. | REV              | VIEW OF BUILT-IN CURRENT SENSOR METHODS             | 28 |

|    | 3.1              | Introduction                                        | 28 |

|    | 3.2              | BICS Challenges                                     | 28 |

|    | 3.3              | Prior BICS Designs                                  |    |

|    | 3.4              | The BICS Design Strategy of This Research           | 37 |

| 4. | MA               | GFET SENSOR SENSITIVITY                             | 42 |

|    | 4.1              | Introduction                                        | 42 |

|    | 4.2              | MAGFET Sensor                                       | 42 |

|    | 4.3              | Modeling of Non-Uniform Magnetic Field              | 45 |

|    | 4.4              | Experimental Results of MAGFET Sensitivity          | 50 |

|    | 4.5              | Which Way to Go: MAGFET or Direct Sensing?          | 56 |

| 5. | I <sub>DDQ</sub> | BICS SYSTEM DESIGN AND SIMULATION                   | 58 |

|    | 5.1              | Introduction                                        |    |

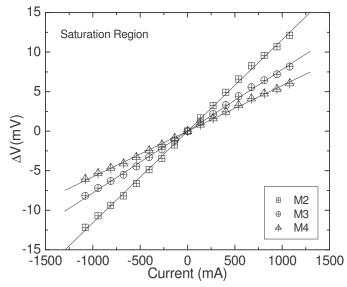

|    | 5.2              | Overview of Proposed Built-In Current Sensor System |    |

|    | 5.3              | Transmission Circuit                                |    |

|    | 5.4              | Flip-Flop Stochastic Sensor                         |    |

|    | 5.5              | Data Detector Circuit                               |    |

|    | 5.6              | Calibration Circuit                                 |    |

|    | 5.7              | Counter and Scan Chain                              | 83 |

|      | 5.8   | Chip Partitioning and BICS Operation          | 6  |

|------|-------|-----------------------------------------------|----|

|      | 5.9   | BICS On-Chip Controller and Usage Methodology | 8  |

|      | 5.10  | BICS Area Overhead Reduction                  | 0  |

|      | 5.11  | Conclusions                                   | 2  |

| 6.   | TEST  | C CHIP RESULTS AND DISCUSSION                 | 4  |

|      | 6.1   | Introduction                                  | 4  |

|      | 6.2   | AMIS 1.5 µm Test Chip9                        |    |

|      | 6.3   | TSMC 350 nm Test Chip10                       |    |

|      |       | TSMC 180 nm Test Chip                         |    |

| 7.   | CON   | CLUSIONS AND FUTURE WORK13                    | 1  |

|      | 7.1   | Summary                                       | 1  |

|      | 7.2   | Future Work                                   | 3  |

| REFE | ERENO | CES13                                         | 5  |

| APPE | ENDIX | X A14                                         | .9 |

| VITA |       |                                               | 0  |

## **LIST OF FIGURES**

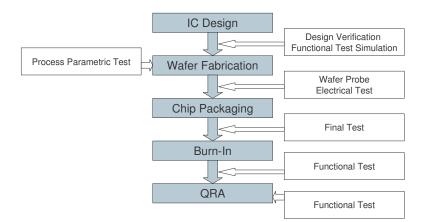

| Fig. 1. Semiconductor IC test at each stage during fabrication2                            |

|--------------------------------------------------------------------------------------------|

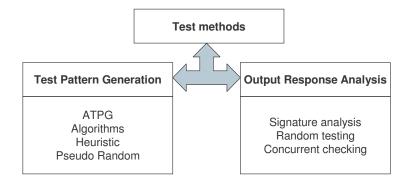

| Fig. 2. Test method divisions                                                              |

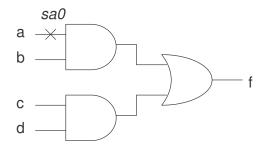

| Fig. 3. Single stuck at fault example                                                      |

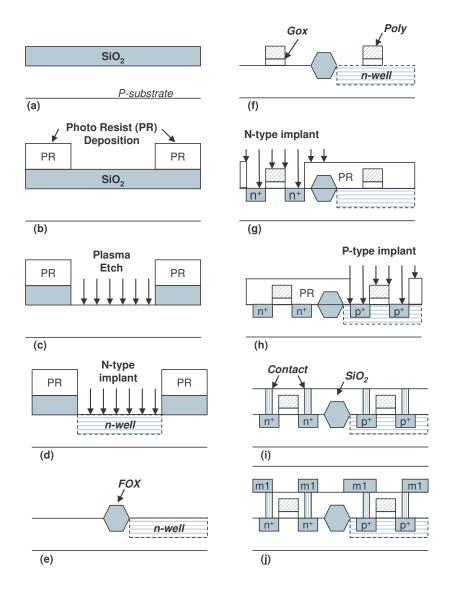

| Fig. 4. Typical CMOS IC fabrication flow12                                                 |

| Fig. 5. A spot defect causing metal shorts                                                 |

| Fig. 6. Abnormal etch or deformation causing resistive open and short                      |

| Fig. 7. CMOS inverter circuit and faulty/fault-free waveforms and current levels           |

| Fig. 8. Conceptual defect-free and defective chip I <sub>DDQ</sub> distribution            |

| Fig. 9. Summary of leakage current mechanisms of deep submicron                            |

| Fig. 10. Overlapping defect-free and defective I <sub>DDQ</sub> values in deep submicron24 |

| Fig. 11. Variation of Max/Min I <sub>DDQ</sub> across a typical production wafer25         |

| Fig. 12. Block diagram of a typical I <sub>DDQ</sub> BICS                                  |

| Fig. 13. BICS using BJT as sensing device                                                  |

| Fig. 14. BICS using diode as bypassing device                                              |

| Fig. 15. Current mirror based BICS                                                         |

| Fig. 16. The OPA based BICS scheme                                                         |

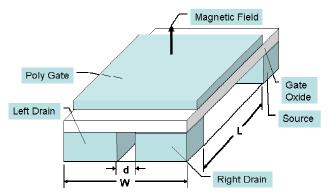

| Fig. 17. Structure of a dual-drain magnetic field-effect sensor (MAGFET)43                 |

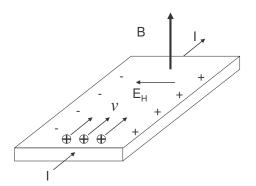

| Fig. 18. The Hall effect on bulk silicon                                                   |

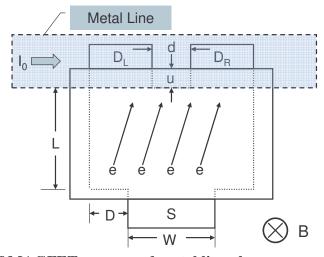

| Fig. 19. Top view of MAGFET sensor and metal line above                                    |

| Fig. 20. Side view of the MAGFET sensor and metal line above                               |

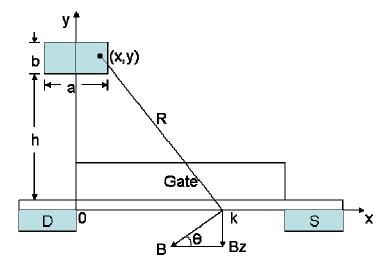

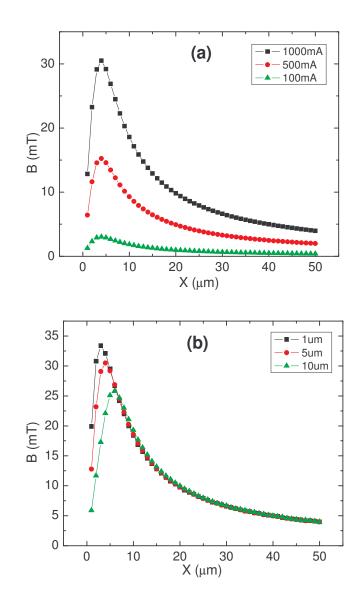

| Fig. 21. | <ul><li>(a) Magnetic field as a function of metal 2 line current and channel location.</li><li>(b) Magnetic field as a function of metal 2 line width and channel location (current: 1000 mA)</li></ul> | .49  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 22. | Magnetic field for different metal layers for a current of 1000 mA.                                                                                                                                     |      |

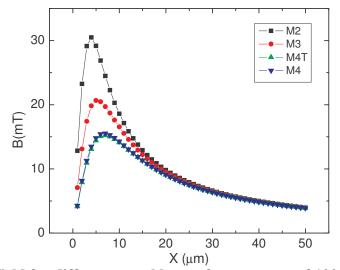

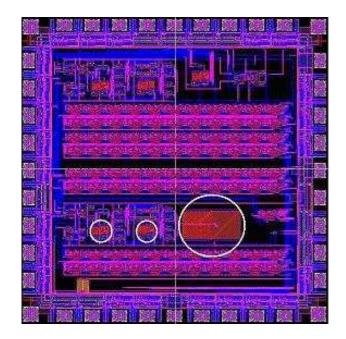

| -        | The 350 nm test chip layout with 6 N-channel MAGFETs of different geometries (shown in circled area).                                                                                                   |      |

| Fig. 24. | Measurement circuit configuration for the MAGFET.                                                                                                                                                       | . 52 |

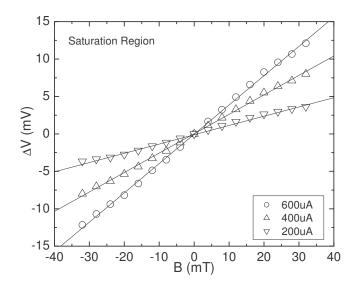

| Fig. 25. | MAGFET sensitivity (N1) at saturation region (R=100 K $\Omega$ )                                                                                                                                        | . 53 |

| Fig. 26. | MAGFET sensitivity (N1) at linear region (R=100 KΩ)                                                                                                                                                     | . 54 |

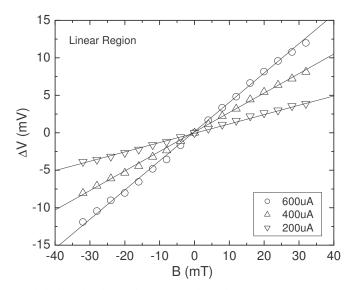

| Fig. 27. | MAGFET sensitivity (N1) under magnetic field generated by M2, M3 and M4.                                                                                                                                | . 54 |

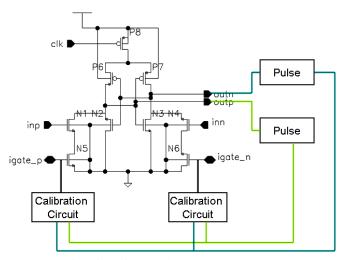

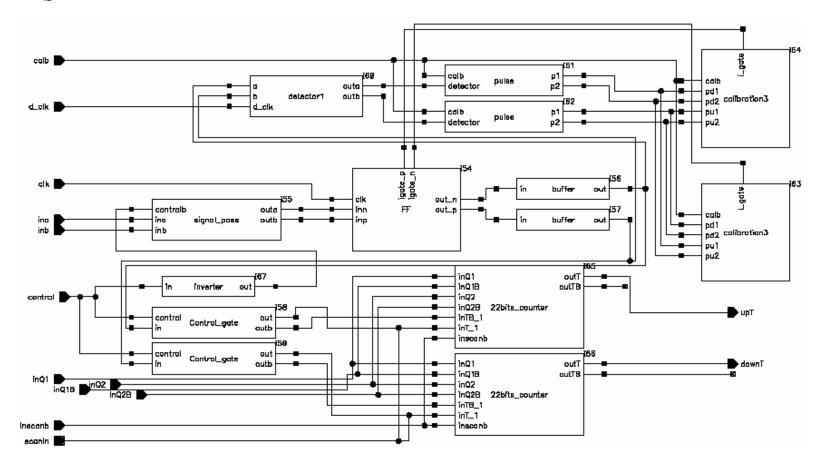

| Fig. 28. | Block diagram of the I <sub>DDQ</sub> Built-In Current Sensor (BICS).                                                                                                                                   | . 59 |

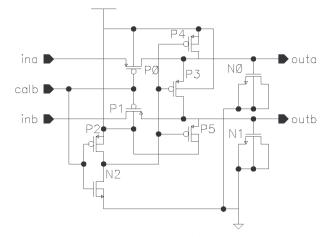

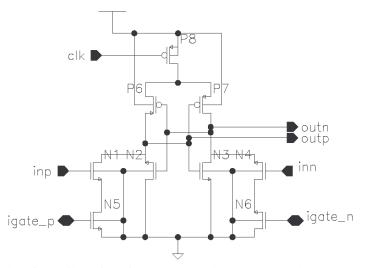

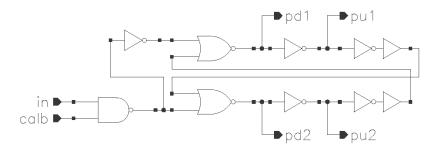

| Fig. 29. | I <sub>DDQ</sub> BICS system component: Transmission circuit                                                                                                                                            | . 62 |

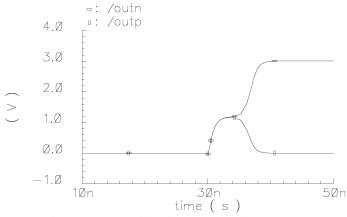

| Fig. 30. | Simulation waveform of the transmission circuit.                                                                                                                                                        | . 63 |

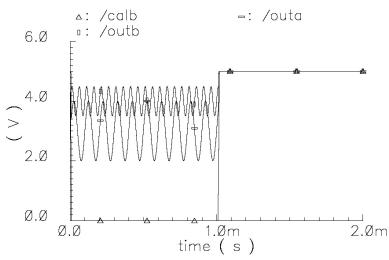

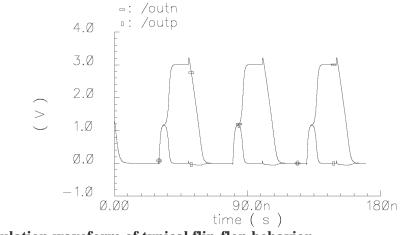

| Fig. 31. | Schematic of the first flip-flop stochastic sensor design                                                                                                                                               | . 65 |

| Fig. 32. | Simulation waveform of typical flip-flop behavior.                                                                                                                                                      | . 66 |

| Fig. 33. | Simulation waveform during flip-flop resolution.                                                                                                                                                        | . 66 |

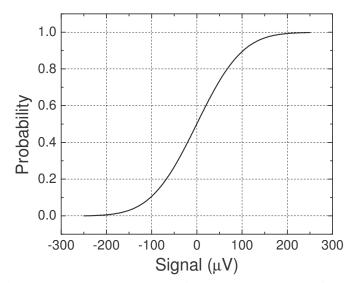

| Fig. 34. | Stochastic sensor conceptual transfer curve. The transfer curve can be<br>approximated as linear in the center region when the signal is much smaller<br>than the noise.                                | . 68 |

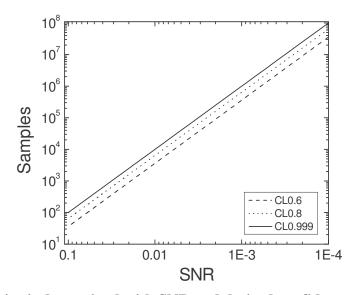

| Fig. 35. | Sample size is determined with SNR and desired confidence level.                                                                                                                                        | .70  |

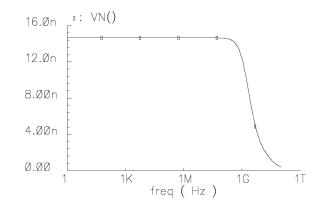

| Fig. 36. | Flip-flop noise simulation. Flicker noise is not included since only frequencies higher than 40 MHz are of interest.                                                                                    | .71  |

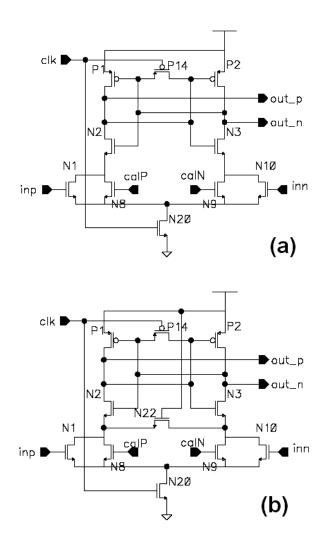

| Fig. 37. | Revised flip-flop stochastic sensor with (a) and without (b) shunting NMOS transistor N22.                                                                                                              | .73  |

| Fig. 38. | Simulated waveform of the second flip-flop sensor design, including a close-up view of one switching event                                                                                              | .74  |

Х

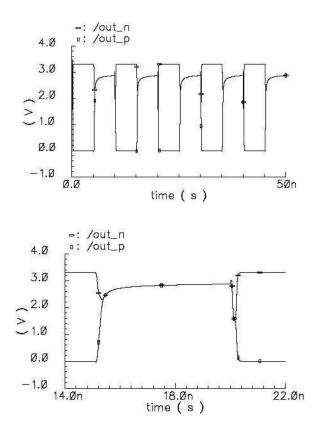

| Fig. 39. Data detector can generate non-overlapping charge pump clock pulses                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 40. Simulated non-overlapping pump down pulses (a) and pump up pulses (b)76                                                         |

| Fig. 41. Revised data detector with additional buffers to increase the non<br>-overlapping interval77                                    |

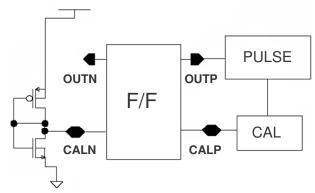

| Fig. 42. Calibration scheme for flip-flop mismatch compensation78                                                                        |

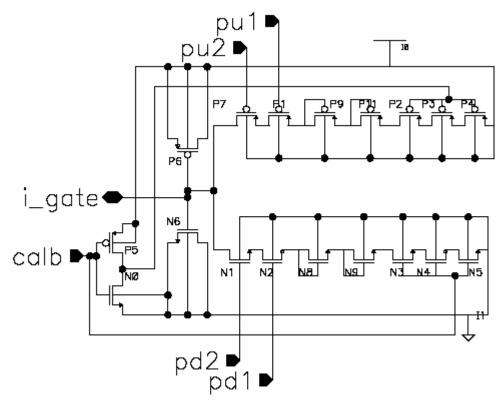

| Fig. 43. Charge pump based calibration circuit79                                                                                         |

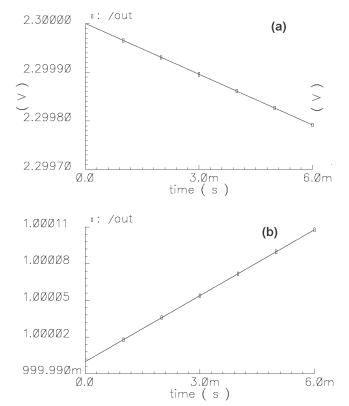

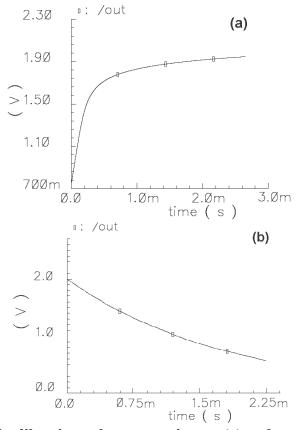

| Fig. 44. Circuit simulation of calibration drift at room temperature with 2.3 V initial voltage (a) and 1.0 V (b), for 350 nm technology |

| Fig. 45. Simulation of calibration voltage pumping up (a) and pumping down (b)                                                           |

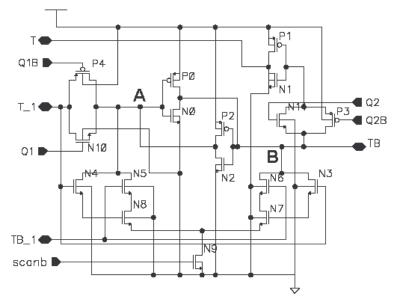

| Fig. 46. Schematics of counter/scan chain cell                                                                                           |

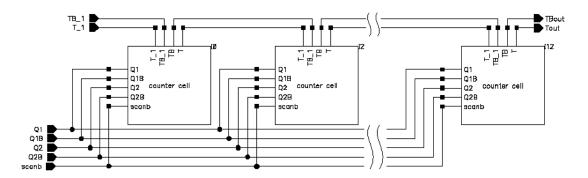

| Fig. 47. Counter/scan chain cells form N bits counter                                                                                    |

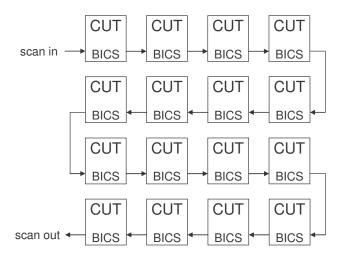

| Fig. 48. Conceptual chip partition with BICS sensor network                                                                              |

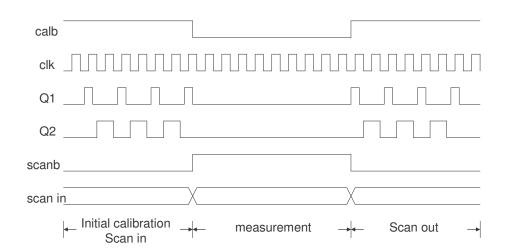

| Fig. 49. Timing diagram of BICS sensor system operating modes                                                                            |

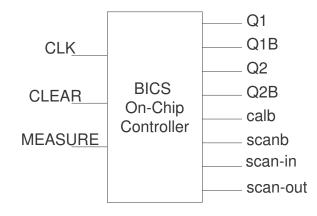

| Fig. 50. BICS on-chip controller                                                                                                         |

| Fig. 51. BICS with single side calibration                                                                                               |

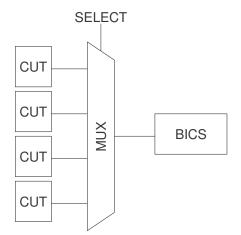

| Fig. 52. Multiplex inputs enable several partitions to share one BICS                                                                    |

| Fig. 53. Chip layout with reservoir capacitors circled                                                                                   |

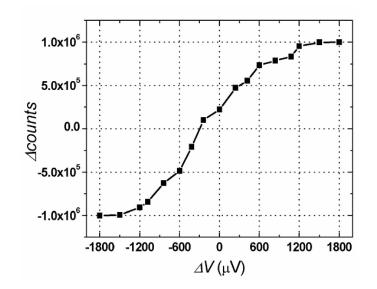

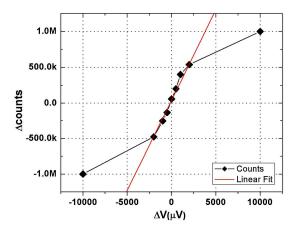

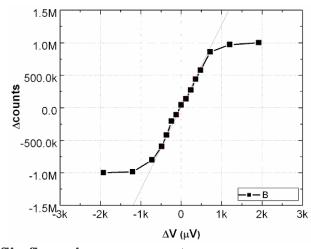

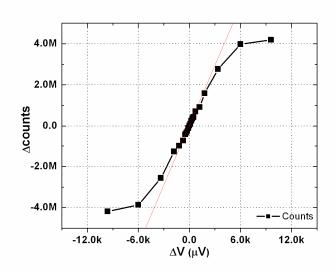

| Fig. 54. Measured stochastic sensor transfer curve                                                                                       |

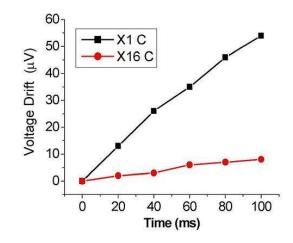

| Fig. 55. Calibration circuit drift rate100                                                                                               |

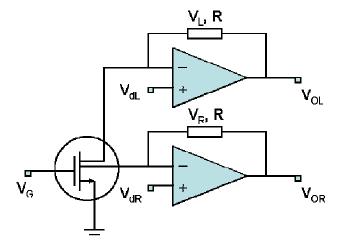

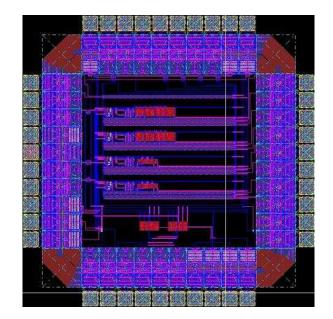

| Fig. 56. TSMC 350 nm test chip layout                                                                                                    |

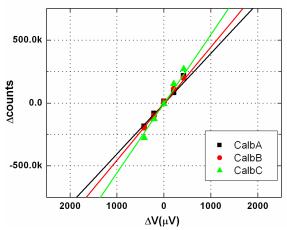

| Fig. 57. Measured calibration drift rate with different initial conditions. The y-axis is the amount of drift103                         |

| Fig. 58. | Calibration voltage gain in terms of differential counter value vs. change in calibration voltage away from the flip-flop balance point. The flip-flop inputs were shorted to $V_{DD}$ , and a total of 1M (2 <sup>20</sup> ) measurement cycles were used for each measurement |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 59. | Standalone flip-flop gain under different calibration bias                                                                                                                                                                                                                      |

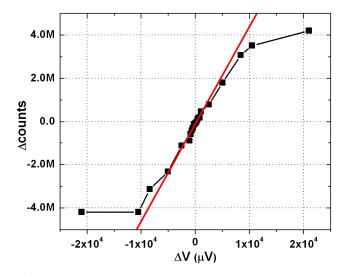

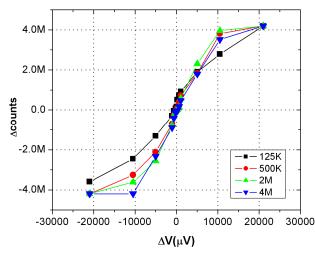

| Fig. 60. | BICS transfer curve using 4M measurement cycles, with 200 calibration cycles interleaved with 500 measurement cycles per period (mode B)110                                                                                                                                     |

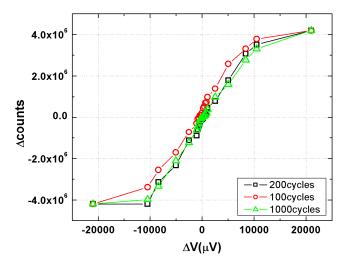

| Fig. 61. | Comparison of three chopping modes with 100, 200 and 1000 calibration cycles, respectively. A total of 4M measurement cycles were used, with 500 measurement cycles per measurement period                                                                                      |

| Fig. 62. | Flip-flop transfer curves for different total measurement cycles, normalized to 4M counts                                                                                                                                                                                       |

| Fig. 63. | Flip-flop transfer curve for different number of measurement cycles per<br>measurement period, for 4M total measurement cycles. Fewer cycles per<br>measurement period means more calibration periods. 200 calibration cycles<br>were used per calibration period               |

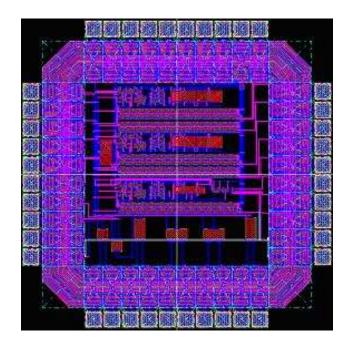

| Fig. 64. | TSMC 180 nm test chip layout                                                                                                                                                                                                                                                    |

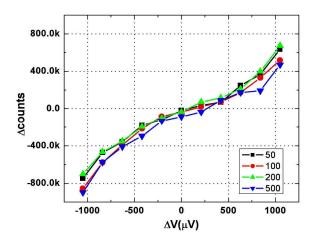

| Fig. 65. | Standalone flip-flop gain measurement                                                                                                                                                                                                                                           |

| Fig. 66. | Sensor gain measurement                                                                                                                                                                                                                                                         |

## LIST OF TABLES

| Table I.    | Defect level examples                                                                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table II.   | ITRS projections for I <sub>DDQ</sub> of high-performance ICs26                                                                                                                                                    |

| Table III.  | Requirements on supply network partitioning                                                                                                                                                                        |

| Table IV.   | Geometry parameters of test chip MAGFETs                                                                                                                                                                           |

| Table V.    | Experimental results of MAGFET sensitivity for all devices under linear (SL) and saturation (SS) regions                                                                                                           |

| Table VI.   | Counter average and standard deviation vs. input voltage                                                                                                                                                           |

| Table VII.  | Mismatch compensation under different calibration voltages107                                                                                                                                                      |

| Table VIII. | Flip-flop gain for different calibration bias108                                                                                                                                                                   |

| Table IX.   | Counter difference and standard deviation under different measurement modes                                                                                                                                        |

| Table X.    | Counter difference and std. dev. for different total measurement cycles.<br>All data was collected with 200 calibration cycles interleaved with 500 measurement cycles. Ten measurements were taken for each value |

| Table XI.   | Scaled counter differences                                                                                                                                                                                         |

| Table XII.  | Counter difference and std. dev. with different measurement cycles<br>per measurement period for 4M total measurement cycles and 200<br>calibration cycles per calibration period                                  |

| Table XIII. | Four calibration circuits                                                                                                                                                                                          |

| Table XIV.  | Drift rate and step size of four calibration circuits                                                                                                                                                              |

| Table XV.   | Mismatch measurement of flip-flop circuit                                                                                                                                                                          |

| Table XVI.  | Standalone flip-flop gain measurement                                                                                                                                                                              |

| Table XVII. | Sensor gain measurement                                                                                                                                                                                            |

#### 1. INTRODUCTION

### 1.1 Introduction

The evaluation of the reliability and quality of a digital integrated circuit (IC) is commonly called "testing." As technology advances, the testing of integrated circuits is gaining in importance. Technology is so advanced that billions of transistors have been integrated into a chip. Moore's Law [1], which projects that the number of transistors per unit area doubles approximately every 18 months, has proven correct for the past few decades, and will continue to hold for at least a decade or more. The International Technology Roadmap for Semiconductors (ITRS) [2] has outlined the projections for future developments in the semiconductor industry and these projections are frequently updated to keep up with development.

At the present time, testing constitutes a large portion (~30%) of the total chip cost and the trend is that test cost will continue to rise. Decreasing silicon costs together with increasing complexity of integrated circuits are two of the most important elements of this trend [3]. The increasing complexity of ICs requires more efficient and effective test methodologies and techniques, otherwise the percentage of test cost is expected to increase even further. In addition, conventional fault models have their inherent limitations, which may lead to poor test quality and cause a significant increase in the

This dissertation follows the style and format of *IEEE Transactions on Very Large Scale Integration (VLSI) Systems.*

overall cost of ICs. So it is becoming more evident that novel test techniques must be developed to keep up with technology advances, while keeping the total test cost at a reasonable level.

In order to ship only products of high quality and reliability to customers, IC manufacturers must ensure that fabricated chips conform to a series of strict specifications. This is accomplished by performing various tests at different stages of chip manufacturing, as shown in Fig. 1.

Fig. 1. Semiconductor IC test at each stage during fabrication.

The very first "test" is performed at the design phase and is called verification. The prototype design is "tested" to ensure that it matches its functional objectives, in other words, to verify the correctness of the design. Verification checks that all layout design rules are obeyed. Verification also checks the circuit to ensure the circuit performs the

intended functionality through circuit simulation with actual process electrical parameters.

The rest of the tests fall into two broad categories: *Boolean tests* and *parametric tests*. Boolean tests are straightforward in that failure (*hard fault*) conclusively detects chip malfunction. So it is a go/no-go type of test, which includes functional [4] and stuck-at tests [5]. For Boolean test, the test cost and test time associated with it are the main challenges. The Boolean test relies on test vectors and automatic test equipment (ATE) to conduct the test. The time to generation test vectors is one major factor of testing cost, because most Boolean test problems have NP-complete time complexity, which means that in the worst case, the CPU time grows exponentially with the size of the IC [6][7][8]. Even if the generation of a large number of test vectors is possible, the time it takes to apply them on the ATE would be enormously expensive, since the state-of-theart ATE cost up to several million dollars. The ATE test time assigned to each chip is very limited due to the high cost of ATE and the volume of chips that must be tested. Therefore the IC test time is another critical factor of testing cost.

In contrast to Boolean tests, parametric tests, as the name implies, measure certain parameters of the circuit under test (CUT). The CUT is considered have a soft fault when the measurement falls outside of its specification range. Power supply quiescent leakage current ( $I_{DDQ}$ ) test, voltage operating range test and speed test are good examples of parametric tests. Although different approaches probe different parameters, all parametric tests have one thing in common, which is the failure of a parametric test does not necessarily declare the chip faulty. The chip may still be able to perform its intended function [9]. As an example a chip may function correctly even though it has abovenormal leakage, so it consumes above-normal power or operates at below-normal clock frequency.

The cost of testing is not only confined to test vector generation and application. It also includes the cost of diagnosis, repair and scrap needed at higher levels of assembly due to poor test quality at lower levels. As indicated by Williams et al. [10], the cost to detect a defect at a higher level of assembly is 10 times as much as the cost to detect the same defect at a lower level. So it is imperative for testing techniques to detect a very high percentage of manufacturing defects.

### 1.2 Testing Terminologies

This subsection covers some of the common methods and terminologies concerning digital testing techniques. As we discussed, the primary purpose of testing is to screen out defects that occur in manufacturing, to ensure that only defect-free chips are packaged and shipped to customers. This requires the test methods to have the following properties: (1) the test speed must be fast enough to handle the large volume of chips during production; and (2) the test must have high defect coverage. In general, chips are subjected to two types of tests: *Functional tests* consist of input vectors and the corresponding responses. They check for proper operation of a verified design by testing the internal chip nodes. Functional tests cover a very high percentage of (logic and delay type) faults in logic circuits. *Parametric tests* checks for physical defects and ensure the product meet design specifications such as clock frequency, operating voltage range, and

maximum power dissipation.

There are many different approaches used in functional test algorithms. As shown in Fig. 2, McCluskey suggested the general division for testing algorithms into test pattern generation and output response analysis [11]. *Test pattern generation* refers to the work in generating an appropriate subset of all input combinations, such that a desired percentage of potential defects is activated and observed at the outputs. *Automatic test pattern generation* (ATPG) tools are based on various algorithms and their heuristics.

Fig. 2. Test method divisions.

*Output response analysis* encompasses methods which capture only the output stream and apply appropriate transformations, with the assumption that the circuit is stimulated by either an exhaustive or a random set of input combinations. Since the output stream is huge, data compaction is usually performed on the output stream prior to analysis.

Testing can also be divided into *on-line* and *off-line* methods:

• *On-line:* each output word from the circuit is tested during normal operation.

• *Off-line:* the circuit must suspend normal operation and enter a "test mode," at which time the appropriate test method is applied.

Usually off-line test can be executed either through external testing with ATE or through the use of *Built-In Self-Test* (BIST) structures. In contrast, on-line testing (also called *concurrent checking*) usually implies that the circuit contains some coding scheme which has been previously embedded in the circuit design.

Because of the enormous number of different defects that could be present in manufacturing, the resulting failures are grouped together based on their logical *fault* effect on the circuit functionality, and this leads to the construction of logical fault models as the basis for testing algorithms [12]. The most commonly used fault model is the *stuck-at fault*, in which a net is stuck at logic 0 or 1 (stuck-at-1 or stuck-at-0).

Fig. 3. Single stuck at fault example.

An example of stuck at fault is given in Fig. 3. Under fault free condition the logic function of the circuit is f=ab+cd. Assume there is a stuck at 0 (*sa0*) fault at input *a*, then the logic function would be transformed to f=cd. In order to catch this fault, a test

vector set must be able to activate the fault and the faulty result must be propagated to the primary output to be observed. In this example, a test vector set of  $\{1,1,0,0\}$  would detect the fault. Many of the physical defects can cause a stuck at 0 fault. For example, the input line of *a* is shorted to ground by a spot defect. The most common physical defects are:

- *Bridging Faults*: they occur when two or more lines are shorted together.

- *Stuck-Open Fault*: they occur when the signal net has an open circuit, usually due to an open via.

### 1.3 Motivation

An effective and efficient testing strategy should be evaluated by taking into consideration the capability of defect detection as well as the cost associated with it. Therefore ideal test methods should be able to catch as many defects as possible while keep the cost as low as possible. BIST is one such candidate because it has the potential to reduce the overall test cost. As transistor costs fall relative to ATE costs, and on-chip bandwidth and timing accuracy rises relative to off-chip bandwidth and timing accuracy, the cost of BIST falls relative to external testing with ATE. BIST can also be used to test chips at the package and board level, and in the field [13][14]. The primary costs of BIST are the chip area and design time associated with it, and the speed penalty of inserting BIST into on-chip logic paths. A good BIST approach should be able to detect a very high percentage of manufacturing defects and at the same time have modest area overhead and delay impact. It should be able to support fault diagnosis and in addition,

any necessary supporting ATE should be kept as simple and cheap as possible. This research is devoted to developing a BIST scheme for quiescent current testing, which can be widely used in current and future semiconductor technologies.

### 1.4 Objectives of the Research

The main goal of this research is to develop and evaluate a novel quiescent current sensing scheme for static Complementary Metal Oxide Silicon (CMOS) circuits. Integrated circuits using static CMOS technology are currently the dominant technology, because it offers reduced power consumption, design simplicity, and high circuit density. This research is therefore specifically targeted at testing digital CMOS ICs. We classify this research as a BIST approach because the technique utilizes Built-In Current Sensors (BICS) [15]. In addition to the standard advantages of BIST, the BICS approach allows the power grid to be virtually partitioned by multiple BICSs, so that the current measured by any one sensor remains small, even as total chip current rises in future technologies. Thus this research will extend  $I_{DDQ}$  test to future technologies while maintain the  $I_{DDQ}$  test efficiency and effectiveness.

#### 1.5 Structure of the Dissertation

The dissertation gives a general testing overview in Section 2, which covers some basic concepts of test, including  $I_{DDQ}$  test. Section 3 covers the background on prior BICS approaches and requirements for a practical BICS design. Section 4 is devoted to evaluation of a magnetic field-effect transistor (MAGFET) as a sensing element in a

BICS. The proposed BICS design and analysis is described in Section 5. The principles of operation and the function of each module are described. This section also covers the evolution of the design over the three generations of test chips. Section 6 presents the experimental results of the three test chips, along with discussions of the measurement results. Section 7 concludes the dissertation and gives directions for future work.

#### 2. BACKGROUND

### 2.1 Introduction

In this section we will provide a general overview of very large scale integrated circuit (VLSI) testing and then focus on  $I_{DDQ}$  test in detail, including its challenges in future technologies. The description will form the background for the later discussion on BICS test methodology. A short review of the IC manufacturing process flow is given first. Then failure modes and the underneath physical causes will be discussed and the models to represent these failures will be established. Classification of the various test methodologies and related key terminologies will be covered next. Then a detailed discussion of  $I_{DDQ}$  test.

### 2.2 IC Manufacturing Process Flow

Before discussing IC testing, we first briefly describe how an integrated circuit is fabricated. The IC chip manufacturing process consists of a series of steps of thin film deposition, photolithography, etching, implant/doping, and supporting processes. A greatly simplified description of a CMOS fabrication process flow is shown in Fig. 4. In step (a) the wafer is cleaned and laser scribed, then followed by silicon dioxide (SiO<sub>2</sub>) growth. In step (b), photoresist is deposited and developed with openings for the n-well areas. Anisotropic plasma etch is applied at step (c) to open the n-well window on SiO<sub>2</sub>. The n-well is then formed by implant of n-type dopants (phosphorus or arsenic or its compound). After the n-well is formed, the photoresist and SiO<sub>2</sub> are stripped and another

mask is applied to form the window for field oxide (FOX) at step (e). Usually before growing the field oxide, an implant step forms a channel stop layer beneath the field oxide, to prevent unwanted parasitic transistors. After field oxide growth, a thin gate oxide layer and a polysilicon layer are deposited. Then the cycle of masking, and etching is performed again to define the transistor gate in step (f). In step (g) the NMOS source and drain is formed by n-type implant while other areas are covered with photo resist to shield away the dopants. A similar procedure is repeated in step (h) to form the PMOS source and drain. Steps (a) to (h) are termed "front end" processing, since they form the transistors. The "back end" steps are then carried out to form interconnect between the transistors. In step (i), a SiO<sub>2</sub> dielectric layer is deposited and contact mask and etch is performed followed by the deposition of the contact layer. After that metal layer, via and inter-metal dielectric is applied alternately to conclude the remaining processing steps [16].

### 2.3 IC Manufacturing Defects

The manufacturing process is subject to contamination and variation. Given the small geometries and tight product tolerances, any tiny contamination or process fluctuation can cause product malfunction. Disturbances are usually classified into two categories, global and local [17]. Fluctuations of process or environment parameters that affect large areas of the wafer are termed *global disturbances*. For example, polysilicon underetching on part of a wafer will increase transistor gate length and threshold voltage, reducing drive current and circuit speed. In contrast, particle contamination causes *local*  *disturbances* (or spot defects) that only affect small areas of the chip. Spot defects manifest themselves as shorts and opens in the circuit structure.

Fig. 4. Typical CMOS IC fabrication flow.

Fig. 5 depicts a typical spot defect causing metal shorts, in which three metal lines are

connected by the defect. The metal shorts caused by this defect are low resistance and change the circuit function.

Fig. 5. A spot defect causing metal shorts.

Fig. 6 shows a resistive short caused by over-etching or photolithography distortion. The resistive nature of the defect may produce a delay increase, rather than functional failure. In other words, some defects may cause change in IC functional behavior while others change its performance. If the defect in Fig. 6 causes only a small delay increase, the circuit performance may not be affected, but the "almost" failure may reduce chip reliability. Defects combined with technology, layout and process may cause a wide variety of abnormality circuit behavior. There are many fault models constructed to emulate the behavior of defective ICs. The purpose of fault models is to simplify the test generation problem and to abstract away many process details.

Fig. 6. Abnormal etch or deformation causing resistive open and short.

As the manufacturing process is disturbed by many types of defects, the manufacturing yield is lowered, and testing becomes of increased importance to maintain outgoing product quality. An estimate of the relationship between manufacturing yield, effectiveness of testing and outgoing product defect level is given in equation (2.1) [18]:

$$DL = \left(1 - Y^{(1-FC)}\right) \tag{2.1}$$

In (2.1), *Y* is the manufacturing yield, ranging from 1 (defect-free production) to 0 (all circuits are faulty). Typical yield values are low at the start of production and reach about 90% at maturity. Fault coverage (*FC*) is calculated as the percentage of faults detected over the total number of detectable faults. The value of *FC* ranges from 1 (all possible faults detected) to 0 (no faults detected). Our ultimate concern is the final defect level (*DL*). *DL* is defined as the probability of shipping a defective product after test and

is usually given in defects per million (DPM) or defective parts per million (DPPM). Competitive defect levels are in the range of 100-1000 DPM. It has been shown that tests with high fault coverage also have high defect coverage. Associating data to this equation gives interesting and practical results. Table I shows examples for some practical values of *Y* and *FC*. The main conclusion to be drawn is that for typical yield values, very high fault coverage must be achieved to obtain an acceptable defect level.

| TABLE I. DEFECT LEVEL EXAMPLES. |                     |                   |  |

|---------------------------------|---------------------|-------------------|--|

| Yield (Y)                       | Fault Coverage (FC) | Defect Level (DL) |  |

| 0.1                             | 0.9                 | 200,000 DPM       |  |

| 0.9                             | 0.99                | 1,000 DPM         |  |

| 0.9                             | 0.9                 | 10,000 DPM        |  |

| 0.5                             | 0.99                | 7,000 DPM         |  |

| 0.5                             | 0.999               | 700 DPM           |  |

Given the defect susceptibility of IC manufacturing, the fabrication of an IC chip includes a series of stringent tests to ensure the IC is defect-free and conforms to product specifications. In-line measurement data are collected throughout the wafer manufacturing process to ensure that critical process control parameters (e.g. gate oxide breakdown voltage) meet their specifications. At the end of the wafer processing, electrical test structures (usually located in the scribe lanes) are measured to provide process information and check for potential defects. An example test structure is the metal comb and serpentine to check for metal shorts and opens. After wafer fabrication, each chip on the wafer will go through a thorough functional and parametric test. As discussed earlier, test vectors will be applied to the inputs of the IC and the outputs will be compared with predetermined values. If a discrepancy is detected, the chip is declared faulty and scraped. Parametric tests check a number of parameters to verify that they fall into the specification range. Only those chips passed all the above tests will be packaged. After packaging, functional test and parametric tests will be carried out again. Some defects do not cause chip failure, but can reduce reliability. These defects may cause chips to fail after a short operating life, termed infant mortality. Reduction of such failures can be achieved by subjecting chips to stress conditions before they are shipped. A burn-in (BI) test can be performed in which chips are subjected to high temperature and voltage for an extended time to force those potential defects to manifest themselves. The drawback of burn-in test is that it is quite expensive, so electrical tests that can detect reliability hazards are highly desirable. One test that has proven successful at screening out reliability hazards is I<sub>DDQ</sub> test, which is described in more detail in the following section.

### 2.4 Principles of I<sub>DDQ</sub> Testing

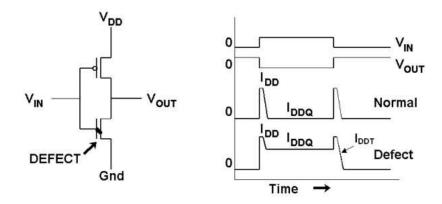

A unique characteristic of static CMOS integrated circuits is that there is no direct current flow when the circuit is in quiescent state, i.e. there is no transistor switching. Under ideal conditions, no current path exists from  $V_{DD}$  to GND so the current flow should be zero. In practice, the quiescent current ( $I_{DDQ}$ ) is small since the only sources of current are transistor sub-threshold, gate oxide and junction leakage. An example of  $I_{DDQ}$  test is shown in Fig. 7. A typical static CMOS inverter is shown with a PMOS and NMOS transistor connected in series. When the input  $V_{IN}$  is low (logic zero) the PMOS transistor is ON while the NMOS transistor is OFF. Thus the output  $V_{OUT}$  is high (logic one). The opposite conditions occur when  $V_{IN}$  is high (logic one). The right side of the figure shows the voltage and current waveforms. The input V<sub>IN</sub> has a rising transition followed by a falling transition, which causes  $V_{OUT}$  to have a falling transition and then a rising transition. Spikes of current occur during the output transitions, when the load capacitance is being charged or discharged. The current flow is at its quiescent level the remainder of the time. Assume there is a spot defect in the gate oxide of the NMOS transistor that causes a resistive gate to source short. The circuit function remains unchanged, but when  $V_{IN}$  is high, current flows from  $V_{DD}$  through  $V_{IN}$  and the spot defect to GND. If a measurement of  $I_{DDQ}$  is taken at this moment, the elevated current will detect the defect. Some early work on the use of IDDQ test and the associated fault models for defect screening can be found in [19][20]. In the example, I<sub>DDQ</sub> is elevated only when the  $V_{IN}$  is high, because under this circumstance the defect is excited. We define a defect that only causes elevated current under some conditions as a patterndependent or active defect. In contrast, a passive defect [21] is the one that is patternindependent. An example is a spot defect causing a short between V<sub>DD</sub> and GND.

Fig. 7. CMOS inverter circuit and faulty/fault-free waveforms and current levels.

### 2.5 Advantages of I<sub>DDQ</sub> Test

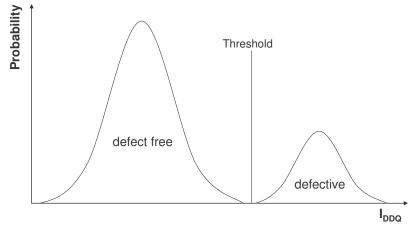

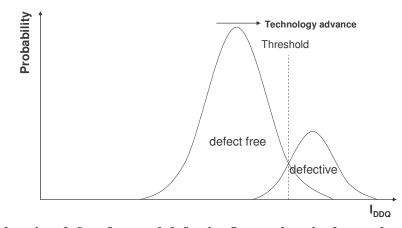

As discussed in the previous section, if the defective circuit  $I_{DDQ}$  is significantly higher than that of the defect-free circuit, we can readily group chips into defective and non-defective populations, as shown in Fig. 8. Under ideal conditions, both populations have a normal distribution (due to process variations) and are well separated from each other. Therefore a threshold  $I_{DDQ}$  can be specified in the gap to differentiate the two groups. Any chips with  $I_{DDQ}$  below the threshold are considered defect-free, while chips with their  $I_{DDQ}$  level higher than the threshold are classified at defective. Threshold setting is of particular importance in that an improper threshold may result in either too many good chips declared defective (overkill), which leads to lower yield and profit, or defective chips declared good (test escape), which increases defect levels.

Fig. 8. Conceptual defect-free and defective chip I<sub>DDO</sub> distribution.

Once a proper  $I_{DDQ}$  threshold is determined, the  $I_{DDQ}$  test becomes an effective and efficient method for defect screening [22]. It has been shown that  $I_{DDQ}$  test achieves good coverage of physical defects that are not very well represented by classical fault models [23][24] and detects defects undetectable by conventional functional tests [25][26][27]. These defects include bridging defects, gate oxide shorts, floating gates and even some delay faults [28]. Unlike other test methodologies, power supply current is always observable, so  $I_{DDQ}$  test does not have the fault propagation requirements of stuck-at test. Because of these unique characteristics, especially the high fault coverage and cost effectiveness inherited from its simplicity,  $I_{DDQ}$  test has been widely utilized in industry [29][30][31].

$I_{DDQ}$  test aids in localizing defects, particularly short circuits. If two nets have different voltages, but elevated  $I_{DDQ}$  is not observed, this means there is no short between these nets. This also makes it easier to debug the design and improve the process and yield. With an effective diagnosis method in hand, the product development

cost can be reduced and the overall time to market can be improved.

Some test solutions which combine  $I_{DDQ}$  with other test techniques have the potential to reduce or even eliminate burn-in (BI) test [32][33][34]. As we discussed earlier, burn-in test is used to screen out reliability hazards that cause infant mortality failure. A more accurate description of BI test is using the Arrhenius equation (2.2) and (2.3) to normalize failure rate predictions as a function of system operation temperature and/or voltage [35]. The elevated temperature and voltage in BI test accelerates the defect degradation [36], which also means that BI test is destructive [37]. One key challenge is that the fastest chips also have the highest power dissipation. During BI these chips can get so hot they go into thermal runaway and burn up, causing a large profit loss. Avoiding this overkill requires increasingly expensive temperature and voltage controls in the burn-in test fixture.

$$A_{T} = e^{\frac{E_{a}}{k}(\frac{1}{T_{use}} - \frac{1}{T_{stress}})}$$

(2.2)

$$A_{V} = e^{\frac{E_{a}}{k}(\frac{1}{V_{use}} - \frac{1}{V_{stress}})}$$

(2.3)

V and T are voltage and temperature respectively. Subscript 'use' represents the nominal condition while 'stress' refers to the stress condition.  $E_a$  is the defect activation energy, and k is Boltzmann's constant. The model is built on the assumption that the performance parameter degradation is linear with respect to time. The probability of occurrence is an exponential function of temperature. As supply voltages scale down

with technology,  $\Delta V (V_{stress} - V_{use})$  keeps falling. Increased power consumption raises the operating temperature, so that  $\Delta T (T_{stress} - T_{use})$  also reduced. The combined reduction in  $\Delta V$  and  $\Delta T$  reduce the effectiveness of BI test or increase its cost. In contrast,  $I_{DDQ}$  test takes much less time and has lower cost. The non-destructive nature of  $I_{DDQ}$  test also avoids the overkill of BI test.

The advantages of  $I_{DDQ}$  test can be summarized as follows: simplicity; cost effectiveness; high fault coverage; capability of detect faults that escape other test methods; defect diagnosis and burn-in test alternative.

### 2.6 I<sub>DDQ</sub> Test Challenges

As discussed above, the effectiveness of  $I_{DDQ}$  relies on the proper setting of the threshold value. A chip with  $I_{DDQ}$  higher than the threshold for some test vector is considered defective. The common practice for estimating the maximum defect-free  $I_{DDQ}$  is through model-based circuit simulations [38][39][40][41] or analytical methods [42]. The threshold value can also be determined by simulation [43][44][45] or empirical methods [46] using production data. The validity of this single  $I_{DDQ}$  threshold is based on the assumption that there is no ambiguity between the  $I_{DDQ}$  level of defect-free chips and defective chips. However, as technology advanced to the deep submicron era, the ambiguity of  $I_{DDQ}$  of defect-free chips and defective chips emerged. Reduced transistor threshold voltage, increased doping concentration levels, and more pronounced short channel effect [47] cause increased mean and variance in defect-free  $I_{DDQ}$  values, posing a great challenge for  $I_{DDQ}$  test.

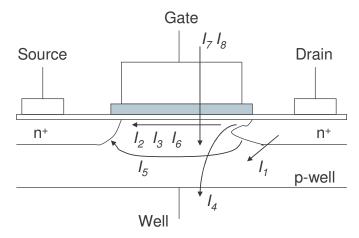

Fig. 9. Summary of leakage current mechanisms of deep submicron.

As shown in Fig. 9, the direct impact on the effectiveness of  $I_{DDQ}$  is the elevated offstate leakage current ( $I_{OFF}$ ), which consists of the following components [48]:

- *pn* junction reverse bias current and gated diode leakage (I<sub>1</sub>) which arises from two main components: minority carrier diffusion/drift near the edge of the depletion region and electron-hole pair generation in the depletion region of the reverse bias junction.

- Weak inversion or sub-threshold conduction current (I<sub>2</sub>) between source and drain in a MOS transistor occurs when the gate voltage is below the threshold voltage V<sub>TH</sub>.

- Drain-Induced Barrier Lowering (DIBL) (I<sub>3</sub>) occurs when the depletion region of the drain interacts with the source near the channel surface to lower the source potential barrier. The source then injects carriers into the channel

surface without the gate playing a role. DIBL is enhanced at higher drain voltage and shorter gate length  $L_{eff}$ .

- Gate-Induced Drain Leakage (GIDL) (I<sub>4</sub>) arises in the high electric field under the gate/drain overlap region causing deep depletion and effectively making the depletion width of drain to well *pn* junction thinner.

- Punchthrough (I<sub>5</sub>) occurs when the drain and source depletion regions approach each other and electrically "touch" deep in the channel. It is a space-charge condition that allows channel current to exist deep in the subgate region causing the gate to lose control of the subgate channel region.

- Narrow width effect (I<sub>6</sub>): Transistor  $V_{TH}$  in the nontrench isolated technologies increases for geometric gate widths on the order of  $\leq 0.5 \mu m$ . And an opposite and more complex effect is seen for trench isolated technologies that show decrease in  $V_{TH}$  for effective channel widths on the order of  $\leq 0.5 \mu m$ .

- Gate oxide tunneling (I<sub>7</sub>) includes direct tunneling through the gate or Fowler-Nordheim tunneling through the oxide bands.

- Hot carrier injection (I<sub>8</sub>): Short channel transistors are more susceptible to injection of hot carriers (holes and electrons) into the oxide. These charges are a reliability risk and are measurable as gate and substrate currents. It increases in amplitude as  $L_{eff}$  is reduced unless  $V_{DD}$  is scaled accordingly.

The dominating leakage component includes DIBL and weak inversion. As transistor geometries get smaller and smaller, the supply voltage and the threshold voltage ( $V_{TH}$ )

keep dropping as well to limit electric fields. The sub-threshold leakage current significantly increases with reduced  $V_{TH}$ , since sub-threshold leakage is exponential in  $V_{TH}$  [49]. The combination of these factors is that  $I_{OFF}$  is rising rapidly with each technology generation. This makes it harder to differentiate good chips from bad chips, due to the two groups of chips overlapping with each other, as shown in Fig. 10 [50].

Fig. 10. Overlapping defect-free and defective I<sub>DDQ</sub> values in deep submicron.

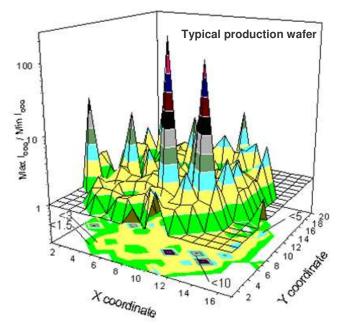

Another issue is the increasing variation of defect-free  $I_{DDQ}$  due to the variation in effective channel length and threshold voltage. This  $I_{DDQ}$  variation can be as high as an order of magnitude [45]. Fig. 11 illustrates the spatial variation of  $I_{DDQ}$  across a typical production wafer. This huge variation coupled with the high background leakage makes it difficult to set a threshold to distinguish defective chips from defect-free chips [50]. As shown in Table II, the International Technology Roadmap for Semiconductors (ITRS) projections for  $I_{DDQ}$  of high-performance microprocessor circuits indicate  $I_{DDQ}$  will keep rising rapidly [47][50]. There has been much prior work devoted to the threshold setting problem, mainly focused on two directions. The first is to reduce the leakage current while the second is to reduce the effective signal variation. Substrate back-biasing [51], chip cooling for low temperature measurement and low supply voltage [52][53], dual threshold voltage technique [54], reduction of process variation [55] and internal or external chip supply grid partitioning have been proposed to help counter the problem of leakage and facilitate the  $I_{DDQ}$  threshold setting. Techniques targeting reduced signal variation include delta  $I_{DDQ}$  [56][57][58], current ratio (CR) [59][60][61], neighborhood current ratio (NCR) [62] and current signature [63][64][65]. These approaches have extended  $I_{DDQ}$  test to newer technologies, but alone are insufficient for the future.

Fig. 11. Variation of Max/Min I<sub>DDQ</sub> across a typical production wafer.

| Year | Maximum I <sub>DDQ</sub> |

|------|--------------------------|

| 2003 | 70-150 mA                |

| 2005 | 150- 400 mA              |

| 2008 | 400 mA-1.6 A             |

| 2011 | 1.6 - 8 A                |

| 2014 | 8-20 A                   |

TABLE II. ITRS PROJECTIONS FOR IDDQ OF HIGH-PERFORMANCE ICS.

## 2.7 I<sub>DDQ</sub> Test for Future Technologies

In spite of the difficulties  $I_{DDQ}$  test is facing, its unparalleled benefits necessitate that it continue to be used in future technologies. Researchers are exploiting every possible solution to extend this simple yet effective test method. As the chip size and complexity advances with technologies, functional test still needs to partner with  $I_{DDQ}$ , as well as other test methods, to form a test suite to achieve the required fault coverage. With critical path delay test to check timing issues, stuck-at test to achieve fault coverage, and burn-in test to ensure reliability, the  $I_{DDQ}$  test will continue to play an important role in catching process-related defects such as bridging faults, gate shorts or delay faults which often escape other test methods. This unique characteristic of  $I_{DDQ}$  test becomes more useful as feature sizes shrink and chips become more vulnerable to smaller defects. Many benign defects of today will become fatal defects in future technologies. For an inherently low leakage process such as silicon-on-insulator (SOI) [66][67],  $I_{DDQ}$  test naturally becomes part of the test suite. In the next section, we will focus on internal partitioning of the power supply grid using built-in current sensors (BICS). We will review prior BICS work and develop the requirements for our BICS. We will later examine and evaluate our BICS design according to these requirements.

#### **3. REVIEW OF BUILT-IN CURRENT SENSOR METHODS**

# 3.1 Introduction

$I_{DDQ}$  test can be performed with external (off-chip) current monitors, or with internal (on-chip) monitors. External testing measures power supply current through the power pins of the integrated circuit, such as with a precision measuring unit of an ATE, or a load board sensor on the test head. Internal testing measures power supply current using a built-in current sensor (BICS) inserted in series with the power or ground grid of the CUT. External testing faces rapidly rising leakage currents, and transient currents. The larger transient currents require more decoupling capacitance, reducing  $I_{DDQ}$  test speeds. Internal testing has the advantage that multiple BICSs can be placed within a chip, reducing the background leakage seen by each sensor, permitting the extension of  $I_{DDQ}$  test to future technologies. Prior work on BICSs will be reviewed in the following sections.

#### 3.2 BICS Challenges

At the present time,  $I_{DDQ}$  is measured off-chip. Although many BICS designs have been proposed, they have not been applied in practice. The major problems of these BICSs can be summarized as follows:

Circuit under Test (CUT) performance degradation: A voltage drop across the sampling device will occur when sampling the I<sub>DDQ</sub> directly, which causes CUT performance degradation, typically 10-30% [68].

- Pass/fail and I<sub>DDQ</sub> level: Most BICSs were designed to compare with a reference current/voltage and make a pass/fail decision. However even with BICSs, the increased variance in I<sub>DDQ</sub> makes pass/fail decision making obsolete. A BICS that can quantitatively measure the I<sub>DDQ</sub> level would be more useful in that the results can be used in I<sub>DDX</sub> algorithms.

- 3. Fabrication process compatibility: Some BICS designs need to use analog components such as resistors and capacitors that are not available in a digital CMOS process. Furthermore, some designs require accurate device matching and thus impose a great fabrication difficulty.

- 4. *External reference*: Most approaches require an external current or voltage reference. This increases the hardware requirement of the ATE.

- Adaptability: Once implemented, most designs are difficult to adjust for different current resolution requirements.

- 6. *Area overhead*: Many BICS designs take too much chip area (especially to achieve a low delay penalty), so that they are impractical for use in industry.

### 3.3 Prior BICS Designs

A BICS consist of two primary parts: a sensing device and signal processing unit, such as an amplifier or comparator. The sensing strategy often determines the selection of the amplifier. The amplifier can be either voltage mode or current mode, depending on the signal produced by the sensing device.

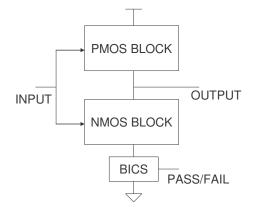

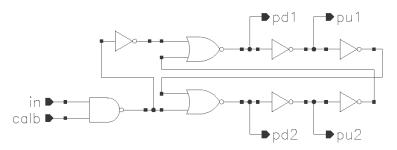

Fig. 12. Block diagram of a typical I<sub>DDQ</sub> BICS.

Sensing devices include bipolar junction transistor (BJT) [69], *pn* junction diode [70][71][72][73][74][75], resistance of metal line [76], current mirror [77] or the load device of the voltage regulator [78][79]. Since sensing devices cannot be removed or turned off after testing, they will be present during normal circuit operation. Fig. 12 shows a general location of the BICS for  $I_{DDQ}$  testing, where the BICS is inserted between the CUT and GND. The BICS embedded in the circuit checks whether the quiescent current is below or above a threshold level, or produces a value. The voltage drop through the BICS sensing device indicates the existence of defects. The voltage must minimize these effects. There have been several attempts to solve this problem: using dual (or even multiple) power supplies [80][81], bypass device [82] or bypass pad [83], Hall sensor [84][85], MAGFET sensor [86] or associating BICS with the voltage regulator.

We will review several typical BICS designs to get a better understanding of the

different approaches that have been proposed to date. We will first review a BICS using a BJT sensing device [73], as shown in Fig. 13. The incentive for using a BJT as a sensing device is that it can handle a large range of current, and the voltage drop is small under defect-free conditions, but large enough for a voltage comparator under defective conditions.

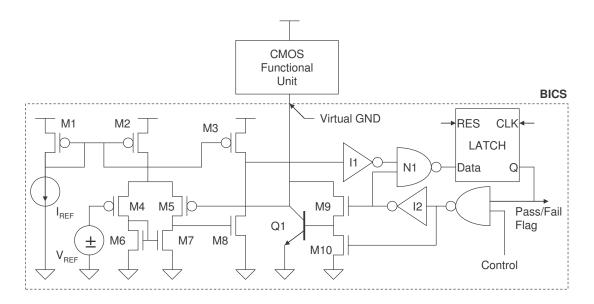

Fig. 13. BICS using BJT as sensing device.

The proposed BICS consists of the a voltage drop BJT device Q1, a comparator (M1-M7), a two-stage amplifier (M3, M8, I1), a bistable, edge-sensitive latch generating a flag signal (F), a circuit breaker (M9, M10, I2), a reference voltage source ( $V_{ref}$ ) and a current source ( $I_{ref}$ ). One can see that this circuit sets the pass/fail flag to ONE and disconnects the CMOS functional unit from ground when  $V_{CE}$  of Q1 is higher than  $V_{ref}$ . The essential elements of this BICS implementation are the low offset comparator and

an adequate  $V_{ref}$  voltage source. The exponential characteristic of the BJT voltage drop device is critical in minimizing the performance degradation of the CUT. While the design benefits from the unique BJT voltage and current handling characteristics, it also brings the difficulty of manufacturing process compatibility issue. The application of the BICS means a migration from a digital logic process to a bipolar process, which is much more complicated and expensive. Further, the diode drop across the BJT does not scale with technology, and so becomes an increasing fraction of total supply voltage in future technologies.

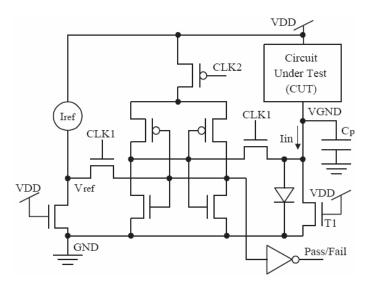

Fig. 14 depicts a BICS design using a diode to bypass the transient current and a transistor *T1* to function as the  $I_{DDQ}$  sensing device [74]. As with the BJT design, the diode has a 0.65V volt drop, which causes approximately a 14% CUT performance degradation, and does not scale with technology. The principle of the BICS design is simple, the  $I_{DDQ}$  will be converted to a voltage signal via *T1*, the signal is then compared with  $V_{ref}$  and resolved into a pass/fail decision through the flip-flop and a inverter.

Fig. 14. BICS using diode as bypassing device.

In order to measure the  $I_{DDQ}$  correctly, parasitic capacitor Cp must be allowed to discharge completely. The settling time is determined by the time constant of  $Cp \cdot R$ , where R is the TI on resistance. The time constant indicates there is trade-off between test speed and resolution. To increase test speed, R needs to be reduced, but this also reduces resolution. Or we can increase test speed by reducing Cp, which will result in an increased CUT delay penalty, or require more CUT partitions and more BICS area. The optimum size of T1 is determined by the threshold voltage value ( $V_{ref}$ ). This type of design tests only one CUT at a time. The reference current is still needed and is fed to the opposite side of the CUT currently being tested. A modification of the design makes a small change and uses a differential scheme, in which the  $I_{ref}$  is replaced by another CUT so the circuit is symmetric with two CUT connected to the two current input terminals of the BICS. The benefit of this modification is that if both CUT has similar *Cp* associated with them, then the BICS can run faster since the charging up effect is canceled.

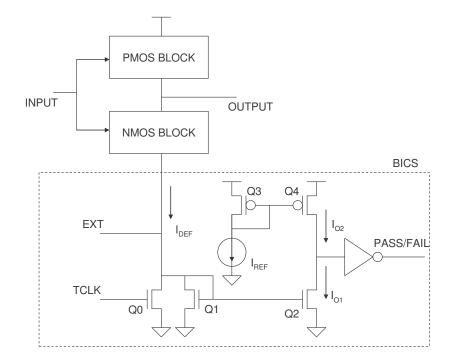

A typical current mirror based BICS is shown in Fig. 15 [81]. The proposed BICS consists of a current mirror, a constant current source for reference and an inverter. NMOS transistor  $Q_0$  is operated to switch either isolating or connecting the BICS, which enable the BICS to work in two modes: the normal mode or the test mode. In normal mode (TCLK is one) CUT current flows through  $Q_0$ . The speed degradation and area depend on the size of  $Q_0$ . The EXT pin can be used as an external connection to avoid the bypass transistor after testing is complete. In test mode, the BICS compares the quiescent current consumed by the CUT with the reference current. When the quiescent state current is greater than the reference current, the output signal PASS/FAIL is set to 1, which indicates the existence of a defect. Otherwise the signal is set to 0.

In the quiescent state  $Q_0$  is turned off and the current mirror pair replicates the defective current  $I_{DEF}$ . The reference current source,  $I_{REF}$ , has a constant current value. The PMOS current mirror pairs,  $Q_3$  and  $Q_4$ , replicates this reference current. Drains of the PMOS replicating transistor  $Q_4$  and the NMOS replicating transistor  $Q_2$  are connected to the input of the inverter to generate the PASS/FAIL signal, based on a comparison of  $I_{REF}$  to  $I_{DEF}$ .

Fig. 15. Current mirror based BICS.

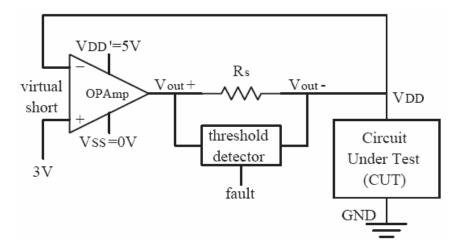

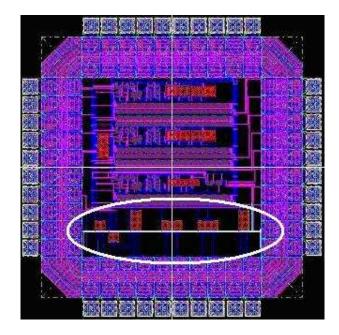

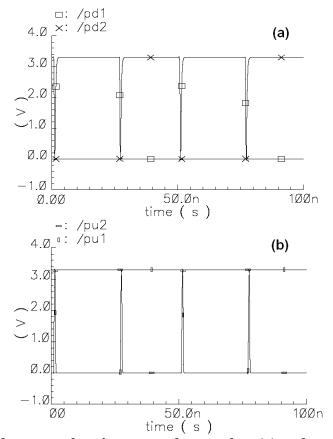

The operational amplifier (OP-AMP) is also used in some BICS designs. One of the OP-AMP BICS designs is depicted in Fig. 16 [82]. The BICS is integrated with a voltage regulator to provide on-chip low voltage source for low voltage circuits and to provide power bus stability. Since the BICS is not in series with the CUT after the  $V_{DD}$  power supply, the performance degradation can be neglected.

Fig. 16. The OPA based BICS scheme.

Because of the virtual short property of an OP-AMP, the voltage at the noninverting node V<sup>+</sup> is equal to the voltage of the inverting node V<sup>-</sup> and no current flow into or out of either V<sup>+</sup> or V<sup>-</sup> (high input impedance property of OP-AMP). The V<sup>+</sup> of the OP-AMP is connected to the original power supply and the V<sup>-</sup> is connected to the V<sub>DD</sub> node of the CUT. The OP-AMP is powered by an additional pair of power supplies V<sub>DD</sub>' and V<sub>SS</sub>, where V<sub>DD</sub>' must be higher than V<sub>DD</sub> and V<sub>SS</sub> is common-grounded with other BICS modules. This scheme is typically used for relatively low power CUTs, due to the limited current sourcing abilities of practical power amplifiers. Between the output node of the OP-AMP and the V<sub>DD</sub> node, there is a series resistor  $R_S$ . The two terminals of  $V_{OUT}^+$  and  $V_{OUT}^-$  of  $R_S$  are connected with the inputs of a threshold detector. The detail of the threshold detector is not shown here. It consists of a differential amplifier, a sample and hold circuit and an output buffer. The  $R_S$  converts the I<sub>DDQ</sub> to a voltage drop of V<sub>OUT</sub>. This voltage drop is then used by the threshold detector to make a decision of whether the CUT is fault free or not. When the reference current is set at 140  $\mu$ A, the threshold voltage used by the threshold detector is only 50 mV. If a lower reference current level is used, an extremely sensitive power amplifier is needed, making this approach difficult to implement. A larger  $R_S$  can be used to enhance the sensitivity of the BICS, but the OP-AMP will only work properly when  $R_S$  is small. A variation of this design utilizes a long existing power wire in the CUT to function as the  $R_S$ . However, this type of sensing device produces a very weak signal, and thus requires a very sensitive amplifier.

## 3.4 The BICS Design Strategy of This Research

By reviewing the prior work on BICSs and analyzing the BICS challenges and benefits, we have conceived a practical BICS design. In this section we will discuss the design strategy. The key drawback of most prior BICS approaches is CUT performance degradation. The performance degradation is usually caused by the impedance of the sensing device. The requirements for the sensing device are that a small voltage drop can handle a larger range of current flow during transient operation and at the same time a small current increase in the quiescent state caused by defects should generate an appreciable voltage/current that can be measured and read out. A bypass device or bypass pad solves the problem, but at a price of extra area or extra pins, both of which are unacceptable. The proposed BICS uses a small section of the existing  $V_{DD}$  line (a small metal strip) as the sensing device, so it introduces no additional series impedance and so no performance degradation. The challenge is that the small defect current through the low-resistance metal line will produce only a small voltage signal. For example, 10 squares of 100 m $\Omega$  metal will produce a 1  $\mu$ V signal for a 10  $\mu$ A defect current. The amplifier stage (stochastic sensor) must have correspondingly high gain.

BICS implemented by sensing the power line has the potential to speed up  $I_{DDQ}$  test since a large decoupling capacitor is not needed to bypass the sensing element. Fast  $I_{DDQ}$  test is desirable for use in a traditional BIST environment or for concurrent fault detection [75] [87].

Even with BICS, leakage currents are rising so rapidly that it is likely that  $I_{DDX}$  techniques must be used to achieve adequate resolution. This requires that the BICS provide the current level, rather than just a pass/fail value. When inserted into a power mesh, current flow on a given branch could change directions based on process variations, so the sensor should also supply current direction. This is also very useful in localizing a defect. BICS area overhead can also be reduced by using multiplexers [88] or ratioed logic [89].

The partition size (amount of circuitry sensed by one BICS) is variable depending on the technology and  $I_{DDQ}$  resolution. In addition, chip area overhead should also be taken into account. As technology advances, the leakage current rises drastically, causing background current to become the most dominant factor in determine the partition size. The partition size should be determined so that the background current of each partition does not overlap with faulty  $I_{DDQ}$  [90]. As shown in Table III, projections have been made on the requirements for partitioning the supply network to maintain a 10  $\mu$ A background current within each partition [94]. The maximum allowable BICS area is for a 1% area overhead. Since the proposed BICS design is larger than the allowable area for most technologies, the allowable background current must be relaxed to 100-1000  $\mu$ A, and resolution enhancement techniques such as current ratios or delta I<sub>DDQ</sub> can be used to achieve the desired defect detection. As the proposed BICS is capable of measure the current level, then a simple on-chip controller can be implemented to realize some of the enhancement algorithms, simplifying the ATE interface.

| TADLE III, REQUIREMENTS ON SUFFLY NET WORK FARTITIONING. |        |        |        |       |       |  |

|----------------------------------------------------------|--------|--------|--------|-------|-------|--|

| Year                                                     | 2002   | 2005   | 2008   | 2011  | 2014  |  |

| Technology                                               | 130 nm | 100 nm | 100 nm | 50 nm | 35 nm |  |

| I <sub>DDQ</sub> /transistor (nA) high perf              | 2.55   | 3.9    | 5.4    | 7.68  | 10.56 |  |

| I <sub>DDQ</sub> /transistor (pA) low power              | 2.55   | 3.9    | 5.4    | 7.68  | 10.56 |  |

| Partition size (transistors) high perf                   | 15686  | 10256  | 7408   | 5208  | 1894  |  |

| Partition size (transistors) cost perf                   | 15686  | 10256  | 7408   | 5208  | 1894  |  |

| Partition size (transistors) low power                   | 15686  | 10256  | 7408   | 5208  | 1894  |  |

| Partition/chip MPU high perf                             | 21.1K  | 86K    | 337K   | 1.35M | 10.5M |  |

| Partition/chip MPU cost perf                             | 4526   | 18.5K  | 72.8K  | 292K  | 2.3M  |  |

| Partition/chip MPU low power                             | 5      | 19     | 73     | 292   | 2275  |  |

| Max BICS Area (transistors) high perf                    | 157    | 103    | 74     | 52    | 19    |  |

| Max BICS Area (transistors) cost perf                    | 157    | 103    | 74     | 52    | 19    |  |

| Max BICS Area (transistors) low power                    | 157K   | 103K   | 74K    | 52K   | 19K   |  |

TABLE III. REQUIREMENTS ON SUPPLY NETWORK PARTITIONING.

Based on the above analysis, in order to keep up with technology and maintain the efficiency and effectiveness  $I_{DDQ}$  test, a built-in current sensor should satisfy the following requirements:

• If the random intra-die  $I_{DDQ}$  variation is up to 20% and the transistor conduction current is up to 50  $\mu$ A (based on ITRS for 35 nm technology), then

the background  $I_{DDQ}$  level should be kept to no more than 10  $\mu$ A in order for the maximum random variation to equal the target defect current.

- The BICS should measure I<sub>DDQ</sub> level and direction. I<sub>DDQ</sub> spatial variations across the wafer calls for measurement of I<sub>DDQ</sub> value instead of just pass/fail. The capability of measuring I<sub>DDQ</sub> value will assist the spatial analysis. Measuring current direction is required if the BICS will be inserted into branches of a power mesh.

- The test should achieve a speed of 1 ms/vector in order to be competitive with the best current I<sub>DDQ</sub> test techniques.

- There should be no CUT performance loss. The BICS should not introduce any significant series impedance into the power grid. In addition, the BICS should be able to completely power off when testing is completed.

- There should be no special technology requirements, so the BICS can be fabricated in a standard digital logic manufacturing process.

- I<sub>DDQ</sub> test used to be a pass/fail test with a single threshold. This method can also be expanded to execute I<sub>DDX</sub> based simple algorithms with an on-chip controller, in which delta I<sub>DDQ</sub>, current ratios, min/max I<sub>DDQ</sub>, current signature can be calculated.

- Our objective of the chip area overhead is that the total area taken by the BICS system should be less than one percent of the total chip area. As far as how the test is to be conducted, the BICS is designed to be usable at both wafer level and package level test.

So to summarize, our approach of BICS is focused on the abilities of high  $I_{DDQ}$  resolution with current level measurement capability, defect identification, localization and diagnosis, and at the meantime causing no CUT performance degradation.

## 4. MAGFET SENSOR SENSITIVITY

## 4.1 Introduction