# INTEGRATED CIRCUIT OUTLIER IDENTIFICATION BY MULTIPLE PARAMETER CORRELATION

A Dissertation

by

SAGAR SURESH SABADE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2004

Major Subject: Computer Engineering

# INTEGRATED CIRCUIT OUTLIER IDENTIFICATION BY MULTIPLE PARAMETER CORRELATION

A Dissertation

by

SAGAR SURESH SABADE

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| proved as to style and content by: |                      |

|------------------------------------|----------------------|

| Duncan Walker                      | Donald Friesen       |

| (Chair of Committee)               | (Member)             |

| Vivek Sarin                        | Henry Taylor         |

| (Member)                           | (Member)             |

|                                    |                      |

|                                    | Valerie Taylor       |

|                                    | (Head of Department) |

May 2004

Major Subject: Computer Engineering

#### **ABSTRACT**

Integrated Circuit Outlier Identification by Multiple Parameter Correlation.

(May 2004)

Sagar Suresh Sabade, B.E., Pune University, India;

M. Tech., Indian Institute of Science, Bangalore, India

Chair of Advisory Committee: Dr. Duncan Walker

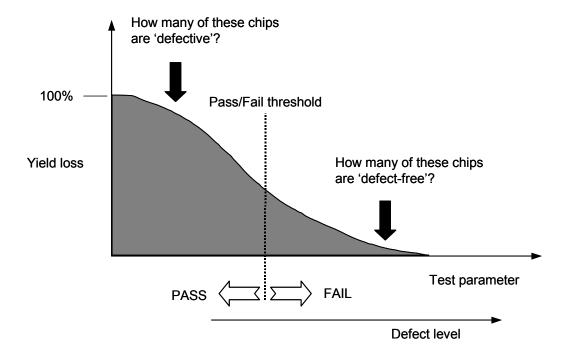

Semiconductor manufacturers must ensure that chips conform to their specifications before they are shipped to customers. This is achieved by testing various parameters of a chip to determine whether it is defective or not. Separating defective chips from fault-free ones is relatively straightforward for functional or other Boolean tests that produce a go/no-go type of result. However, making this distinction is extremely challenging for parametric tests. Owing to continuous distributions of parameters, any pass/fail threshold results in yield loss and/or test escapes. The continuous advances in process technology, increased process variations and inaccurate fault models all make this even worse. The pass/fail thresholds for such tests are usually set using prior experience or by a combination of visual inspection and engineering judgment.

Many chips have parameters that exceed certain thresholds but pass Boolean tests. Owing to the imperfect nature of tests, to determine whether these chips (called "outliers") are indeed defective is nontrivial. To avoid wasted investment in packaging or further testing it is important to screen defective chips early in a test flow. Moreover, if seemingly strange behavior of outlier chips can be explained with the help of certain process parameters or by correlating additional test data, such chips can be retained in the test flow before they are proved to be fatally flawed.

In this research, we investigate several methods to identify *true* outliers (defective chips, or chips that lead to functional failure) from *apparent* outliers (seemingly defective, but fault-free chips). The outlier identification methods in this research primarily rely on wafer-level spatial correlation, but also use additional test parameters. These methods are evaluated and validated using industrial test data. The potential of these methods to reduce burn-in is discussed.

#### **DEDICATION**

To my grandmother and my parents, whom I owe everything.

Without their unflagging support this wouldn't have been possible.

The following poem that I composed during one of my study breaks, expresses the general theme of my research.

VLSI Testing – A Poetic Perspective

There's an open or there is a short

These are defects that cause a fault

Current may rise or current may halt

Depends on where and what caused the fault

Technology today is called CMOS

Takes a tiny current, has small power loss

Current would increase for a defect gross

But if it's subtle, you are at a loss

Is chip good or faulty: who can say?

One has to find a better way

Throwing good chips means loss of yield

But shipping a bad one, can fail on field

Fail on field means customer return

That can hamper your reputation

"Poor quality" customers will say

Reducing defect level is the only way

#### **ACKNOWLEDGMENTS**

I arrived on the campus of Texas A&M University in August 1999 with rather a vague notion of doing a Ph.D. As I reflect upon this academic journey so far, I realize I owe a lot to many people who supported me throughout this process. I am deeply indebted to Dr. Hank Walker for his financial, academic and moral support throughout my years at TAMU. He encouraged me, like his other students, to explore a research direction on my own in order to hone my research skills and independent thinking. He shared his insights to help me understand where my research fits in the long-term. I would like to thank my committee members Dr. Donald Friesen, Dr. Vivek Sarin and Dr. Henry Taylor for agreeing to serve on my committee and for their helpful comments and constructive criticism. I would like to express my thanks to my Graduate Committee Representative (GCR) Dr. Sharon Braunagel for completing the paperwork promptly. Thanks to Wanda Allen, Elena Catalena, Dr. Bart Childs, Margaret Dunaway, Glenda Elledge, Leah Lewis, and Sandy Morse for cooperating in the administrative tasks.

I gratefully acknowledge the financial support I received from the National Science Foundation (NSF), Texas Advanced Research Program/Advanced Technology Program (ARP/ATP) and Semiconductor Research Corporation (SRC).

Several people from industry and academia were helpful in shaping my views about the VLSI testing area in general and defect-based testing in specific. In particular, I would like to thank Dr. Anne Gattiker (IBM), my SRC Industrial Liaison, for sharing her views on some topics and for answering my queries. I would like to thank Dr. Phil Nigh (IBM) for providing SEMATECH data, a copy of his dissertation and for answering my numerous questions.

I was a summer intern at Texas Instruments, Inc. (Dallas) in 2000 and 2001. Working in industry while being in a graduate school was indeed a valuable experience as I got an opportunity to see some of the "real-world" issues. I would like to thank Hari Balachandran, Dr. Ken Butler, David Colby, Craig Force, Shri Jandhyala, Dr. Theo Powell, Ron Richmond, Dr. Jayashree Saxena, and Neil Simpson for discussions that gave me useful information. I am thankful to Bob Madge and Manu Rehani of LSI Logic for providing valuable data and Kevin Cota for useful discussions. Thanks to Dr. Peter Maxwell of Agilent Technologies for sharing his knowledge and allowing reproduction of figures from his papers. Thanks to David Bergman (NIST), Dr. Ali Keshavarzi (Intel), Thomas Vogel (CMU) for allowing reproduction of figures from their publications.

I would also like to thank Dr. Jim Plusquellic of University of Maryland Baltimore County for

his insightful comments. My friend Dr. Subashish Mitra of Intel extended all the help he could and I am thankful to him for the same. I wish to thank Wayne Needham who answered my questions in spite of having officially retired from the testing field!

I would like to thank my undergraduate advisors Dr. C. P. Gadgil (College of Engineering, Pune) and Dr. K. Gopakumar (Indian Institute of Science, Bangalore) who motivated me for further studies. Thanks to Prof. N. J. Rao and Dr. L. Umanand for encouraging me for further studies and for writing recommendation letters.

I would like to express my sincere thanks to my friends and colleagues Hoki Kim, Chul Lee, Abhijit Prasad, Ajay Thadhlani, Zoran Stanojevic, Wangqi Qiu, Ms. Jing Wang and Bin Xue. Several discussions with Wangqi Qiu during study breaks kept me enthused about my research.

Several friends helped me during graduate school directly or indirectly. Thanks to Prabha Acharya, Rajmohan Bharadwaj, Rajendra and Deepali Bhamare, Yogen Deshpande, Anagha Phadke, Supriya Phadke, Ramesh Setigam and Shailesh Waikar. I am especially grateful to my friends Jayesh Kulkarni and Sachin Upadhye for their encouragement and unfading friendship.

My cousin Sonalee and brother-in-law Himanshu were helpful in every possible way. Sonalee's phone calls provided some sort of refreshment in my studies. I am thankful to both of them. Mrunal, my wife, made the last phase of my Ph.D. sustainable and more manageable by taking care of several minute details. I am thankful to her.

My decision to join the Ph.D. program was supported by my grandmother, parents and other family members. I certainly believe that I have come this far only due to their guidance and best wishes. I am deeply indebted to them for their love and moral support throughout my life. I earnestly hope this moderate achievement brings some happiness to their lives. As I finish my graduate studies and know there are still many challenges to solve the problem I embarked upon, I realize that true wisdom comes not from knowing all the answers but by knowing how many questions remain. I have often thought that a Ph.D. is more than a degree – it is an attitude to solve problems. Having gone through the process myself, now I know, that it is really so and it imposes more responsibility than privilege. I am glad to have had the opportunity to experience it.

# TABLE OF CONTENTS

|    |      |                                                              | Page |

|----|------|--------------------------------------------------------------|------|

| 1. | INTR | ODUCTION                                                     | 1    |

|    | 1.1  | Introduction                                                 | 1    |

|    | 1.2  | Motivation                                                   | 2    |

|    | 1.3  | Objectives of the Research                                   | 7    |

|    | 1.4  | Contributions of the Dissertation                            | 8    |

|    | 1.5  | Structure of the Dissertation                                | 8    |

| 2. | BAC  | KGROUND                                                      | 10   |

|    | 2.1  | Introduction                                                 | 10   |

|    | 2.2  | IC Manufacturing Flow                                        | 10   |

|    | 2.3  | Need for Testing.                                            | 10   |

|    | 2.4  | Contamination, Defects, Faults and Degradation               |      |

|    | 2.5  | Test Quality                                                 | 16   |

|    | 2.6  | Test Method Classification                                   | 17   |

|    | 2.7  | Principle of I <sub>DDQ</sub> Testing                        | 18   |

|    | 2.8  | I <sub>DDQ</sub> Testing Benefits                            | 19   |

|    | 2.9  | I <sub>DDQ</sub> Test in Practice                            | 21   |

|    | 2.10 | Components of I <sub>DDQ</sub>                               | 21   |

|    | 2.11 | Impact of Technology on I <sub>DDQ</sub> Test                | 22   |

| 3. | REV  | IEW OF I <sub>DDX</sub> –BASED TEST METHODS                  | 27   |

|    | 3.1  | Introduction                                                 | 27   |

|    | 3.2  | I <sub>DDQ</sub> Reduction Techniques                        | 28   |

|    | 3.3  | Reverse Body Biasing (RBB) Technique                         | 28   |

|    | 3.4  | Stack Effect                                                 | 29   |

|    | 3.5  | Multiple-V <sub>TH</sub> CMOS Transistors                    | 30   |

|    | 3.6  | Use of Alternative Technology                                | 31   |

|    | 3.7  | Partitioning of Power Supply Network                         | 32   |

|    | 3.8  | I <sub>DDQ</sub> Variance Reduction/Data Analysis Techniques | 32   |

|    | 3.9  | Current Signature                                            | 32   |

|    | 3.10 | Delta I <sub>DDQ</sub>                                       | 34   |

|    | 3.11 | Statistical Clustering                                       | 35   |

|    | 3.12 | Current Ratio                                                | 36   |

|    |      |                                                            | Page |

|----|------|------------------------------------------------------------|------|

|    | 3.13 | Eigen Signatures                                           | 39   |

|    | 3.14 | I <sub>DDQ</sub> versus Temperature                        | 41   |

|    | 3.15 | I <sub>DDQ</sub> versus F <sub>max</sub>                   | 43   |

|    | 3.16 | I <sub>DDQ</sub> versus Voltage                            | 45   |

|    | 3.17 | Principal Component Analysis-Based Linear Prediction       | 46   |

|    | 3.18 | Transient Current (I <sub>DDT</sub> )-Based Test Methods   | 47   |

|    | 3.19 | I <sub>DD</sub> Pulse Response Testing (PRT)               | 47   |

|    | 3.20 | Dynamic Power Consumption Current-Based Testing            | 48   |

|    | 3.21 | Transient Signal Analysis (TSA)                            | 49   |

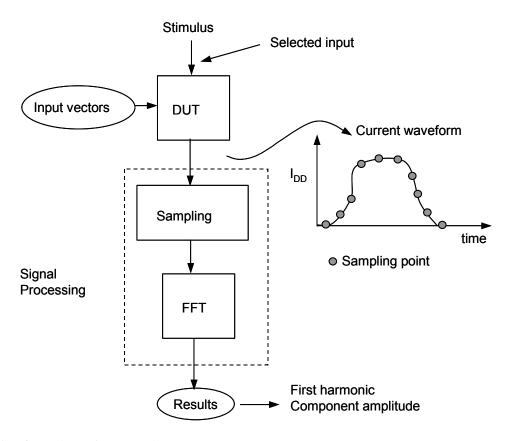

|    | 3.22 | Frequency Spectrum Analysis of Dynamic Current             | 49   |

|    | 3.23 | On the Fly Depowering                                      | 49   |

|    | 3.24 | Energy Consumption Ratio (ECR)                             | 50   |

|    | 3.25 | Fault-Free Parameter Value                                 | 51   |

| 4. | OUT  | LIER IDENTIFICATION AND PARAMETRIC TEST DATA               | 55   |

|    | 4.1  | Introduction                                               | 55   |

|    | 4.2  | What Are Outliers?                                         | 55   |

|    | 4.3  | Outlier Identification, Detection and Rejection            | 55   |

|    | 4.4  | Why Do Outliers Exist?                                     | 57   |

|    | 4.5  | Challenges in Outlier Rejection                            | 58   |

|    | 4.6  | Outlier Detection Methods                                  | 64   |

|    | 4.7  | Resistant Outlier Detection                                | 65   |

|    | 4.8  | Philosophy Behind Outlier Rejection                        | 65   |

|    | 4.9  | Chauvenet's Criterion                                      | 65   |

|    | 4.10 | Tukey Method                                               | 66   |

|    | 4.11 | Median of Absolute Deviations (MAD) About Medians          | 67   |

|    | 4.12 | Applicability of Outlier Rejection Methods to VLSI Testing | 68   |

|    | 4.13 | Measuring Outlier Screening Effectiveness                  | 70   |

| 5. | MUL  | TIPLE PARAMETER CORRELATION                                | 72   |

|    | 5.1  | What Is Parameter Correlation?                             | 72   |

|    | 5.2  | Why Correlate Multiple Parameters?                         | 72   |

|    | 5.3  | Correlating Multiple Factors                               | 73   |

|    | 5.4  | Multiple Test Parameter Correlation                        | 87   |

|     |        |                                                             | Page |

|-----|--------|-------------------------------------------------------------|------|

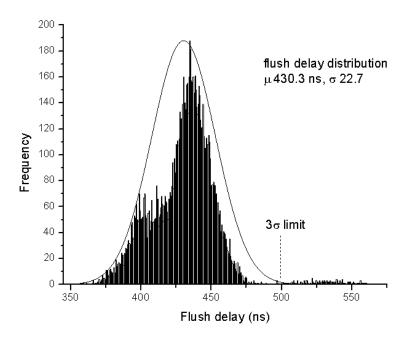

|     | 5.5    | Use of Multiple Test Metrics                                | 92   |

|     | 5.6    | CR-NCR Combination                                          | 92   |

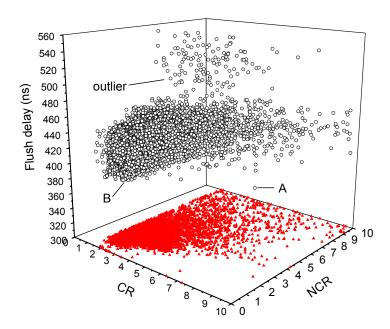

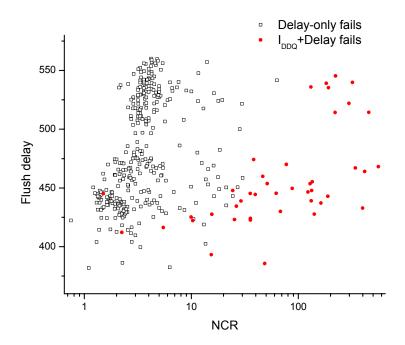

|     | 5.7    | Combination of CR, NCR and Delay Data                       | 93   |

|     | 5.8    | Conclusion                                                  | 97   |

| 6.  | ANA    | ALYSIS OF INDUSTRIAL TEST DATA                              | 98   |

|     | 6.1    | Introduction                                                | 98   |

|     | 6.2    | Analysis Using Spatial Fit Method                           | 99   |

|     | 6.3    | Evaluation of Statistical Outlier Rejection Methods         | 107  |

|     | 6.4    | Correlating Two Test Parameters                             | 110  |

|     | 6.5    | Exploiting Wafer Spatial Correlation Using NCR              | 115  |

|     | 6.6    | Immediate Neighbor Difference I <sub>DDQ</sub> Test (INDIT) | 120  |

|     | 6.7    | Combination of CR and NCR                                   | 124  |

|     | 6.8    | Combination of CR, NCR and Delay Data                       | 136  |

|     | 6.9    | Conclusion                                                  | 141  |

| 7.  | APP    | LICATION TO BURN-IN REDUCTION                               | 144  |

|     | 7.1    | Introduction                                                | 144  |

|     | 7.2    | Methodology                                                 | 144  |

|     | 7.3    | Burn-in Pass/Fail Decision                                  | 147  |

|     | 7.4    | Experimental Results                                        | 148  |

|     | 7.5    | Discussion of Results                                       | 149  |

|     | 7.6    | Conclusion                                                  | 149  |

| 8.  | CON    | ICLUSIONS AND FUTURE WORK                                   | 150  |

|     | 8.1    | Summary                                                     | 150  |

|     | 8.2    | Future Directions for Research                              |      |

|     | 8.3    | Conclusion                                                  | 157  |

| REF | FEREN  | CES                                                         | 158  |

| APF | PENDIX | X A SEMATECH EXPERIMENT S-121                               | 176  |

| APF | PENDIX | K B LSI DATA                                                | 180  |

| APF | PENDIX | C TI DATA                                                   | 181  |

| APF | PENDIX | X D 3-D LINEAR REGRESSION                                   | 182  |

| APF | PENDIX | X E CHAUVENET'S CRITERION                                   | 184  |

| APF | PENDIX | X F MAD SCORE COMPUTATION                                   | 185  |

|                                                          | Page      |

|----------------------------------------------------------|-----------|

| APPENDIX G COST MODEL FOR OUTLIER REJECTION BENEFIT EVAL | UATION186 |

| VITA                                                     | 188       |

# LIST OF FIGURES

|                                                                                      | Page |

|--------------------------------------------------------------------------------------|------|

| Fig. 1. Basic manufacturing test flow for semiconductor chips                        | 2    |

| Fig. 2. Illustration of IC parameter variation at various levels.                    | 4    |

| Fig. 3. Reliability bathtub curve and reliability screen using burn-in               | 5    |

| Fig. 4. IC parameters show a continuous distribution.                                | 6    |

| Fig. 5. Conflicting goals of yield loss and defect level.                            | 7    |

| Fig. 6. Typical CMOS IC fabrication flow.                                            | 11   |

| Fig. 7. (a) Original mask pattern and (b) actual silicon.                            | 12   |

| Fig. 8. Process variation induces inter-layer variation in metal thickness.          | 13   |

| Fig. 9. Global and local defects and associated yield loss.                          | 14   |

| Fig. 10. Yield loss due to parametric, systematic and random defects.                | 15   |

| Fig. 11. Subtle and gross defects.                                                   | 16   |

| Fig. 12. Shmoo plot showing relationship between supply voltage and chip speed       | 18   |

| Fig. 13. (a) CMOS inverter circuit and (b) faulty and fault-free waveforms.          | 19   |

| Fig. 14. Leakage current mechanisms for DSM transistors.                             | 22   |

| Fig. 15. Reduction in threshold voltage increases leakage current exponentially      | 23   |

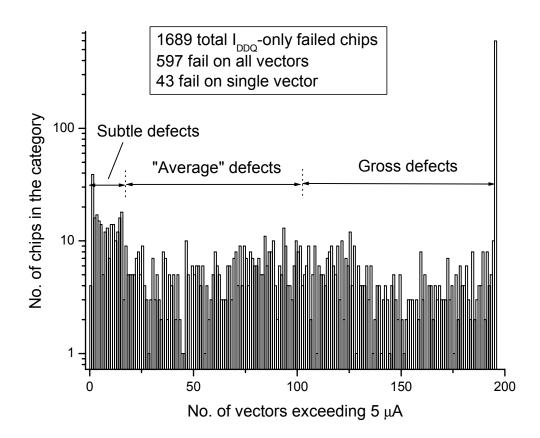

| Fig. 16. Defect detection using I <sub>DDQ</sub> test depends on defect severity.    | 24   |

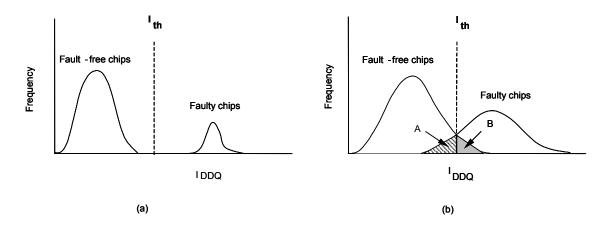

| Fig. 17. (a) Single threshold test for older and (b) for DSM technologies.           | 25   |

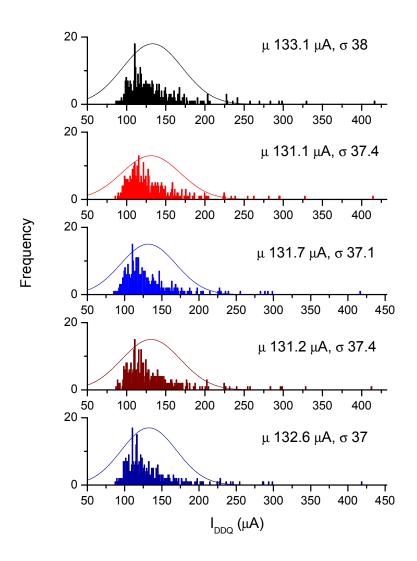

| Fig. 18. Chip-to-chip I <sub>DDQ</sub> variation for a vector for five wafers.       | 26   |

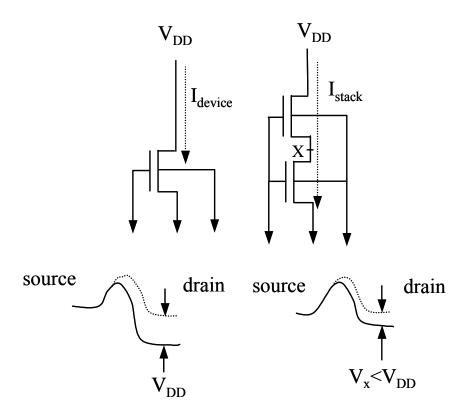

| Fig. 19. Leakage current reduction by stacking of transistors.                       | 29   |

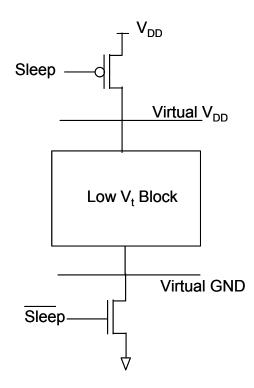

| Fig. 20. Basic principle of MTCMOS circuits showing sleep control transistors.       | 30   |

| Fig. 21. Cross section of SOI transistor and leakage components.                     | 31   |

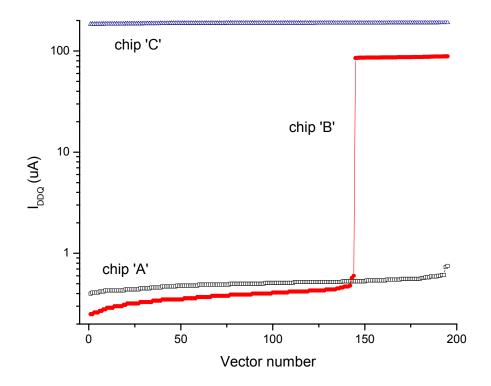

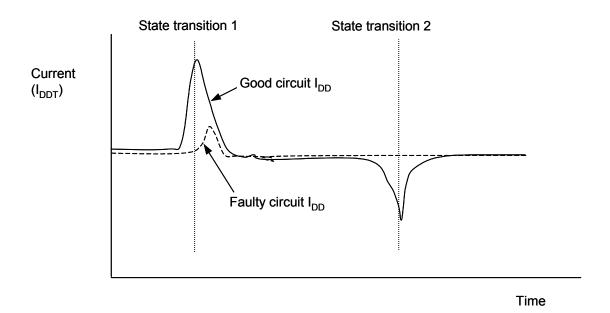

| Fig. 22. Current signatures for fault-free and faulty chips.                         | 33   |

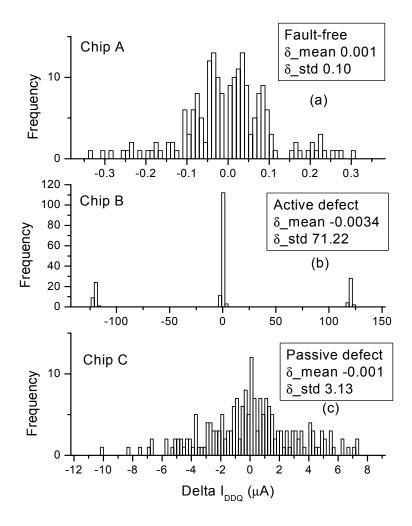

| Fig. 23. Histograms of delta-I <sub>DDQ</sub> for fault-free and faulty chips        | 35   |

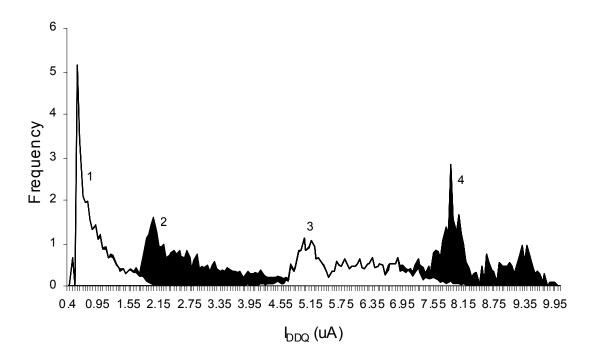

| Fig. 24. Normalized histogram for four clusters of I <sub>DDQ</sub> test data.       | 36   |

| Fig. 25. Two chips having different I <sub>DDQ</sub> magnitude but similar CR        | 37   |

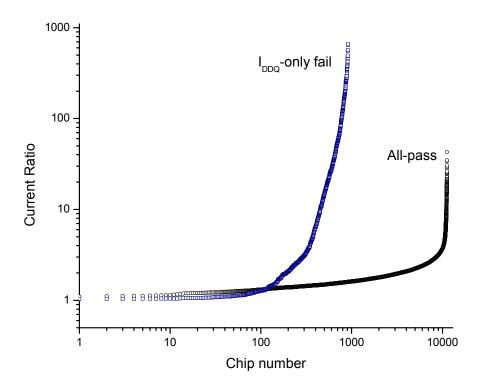

| Fig. 26. Current ratios of fault-free and faulty chips from a wafer.                 | 38   |

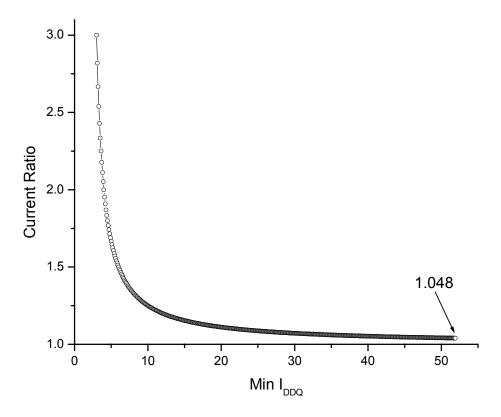

| Fig. 27. Reduction in CR with increasing background leakage.                         | 39   |

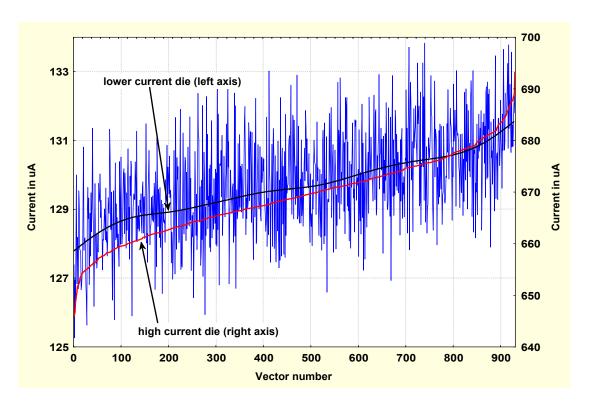

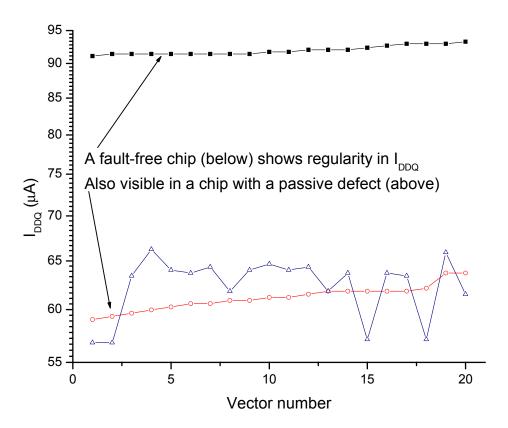

| Fig. 28. Fault-free chips show regular variation in I <sub>DDQ</sub> .               | 40   |

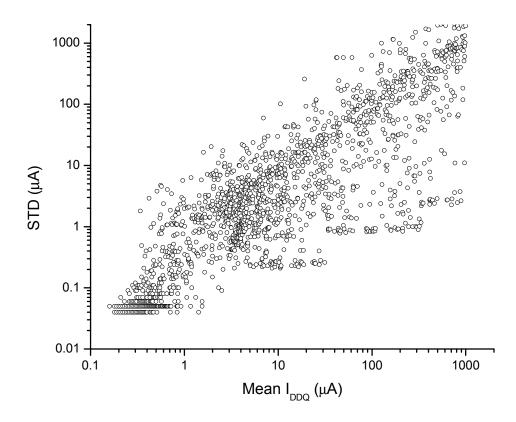

| Fig. 29. Scatter plot of mean and standard deviation of $I_{DDQ}$ for SEMATECH data  | 41   |

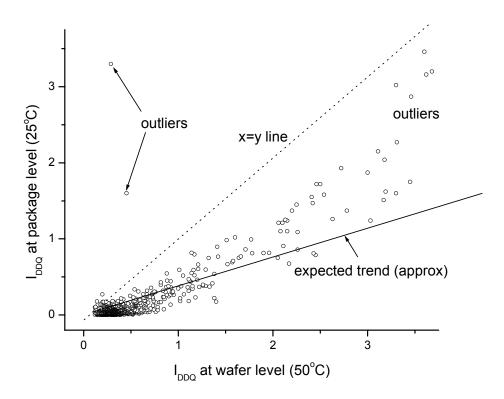

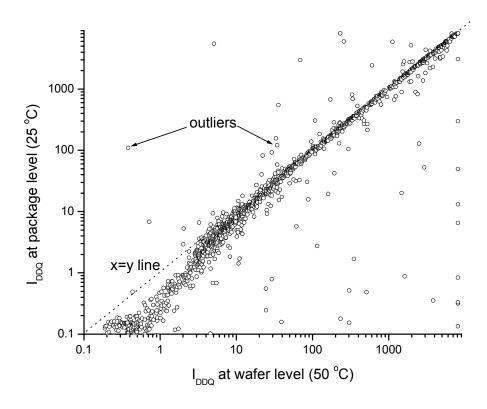

| Fig. 30. I <sub>DDQ</sub> values at two different temperatures for outlier screening | 42   |

| Fig. 31. Temperature-based outlier screening.                                        | 43   |

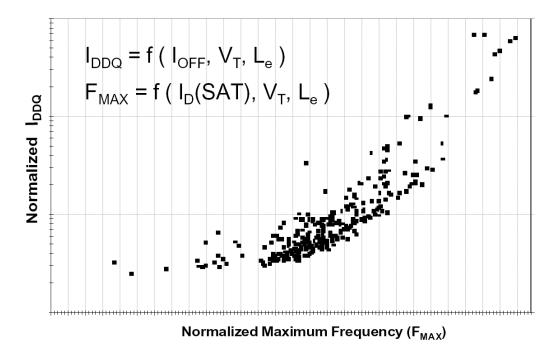

| Fig. 32. Relationship between I <sub>DDO</sub> and Fmax.                             | 44   |

|                                                                                                           | Page |

|-----------------------------------------------------------------------------------------------------------|------|

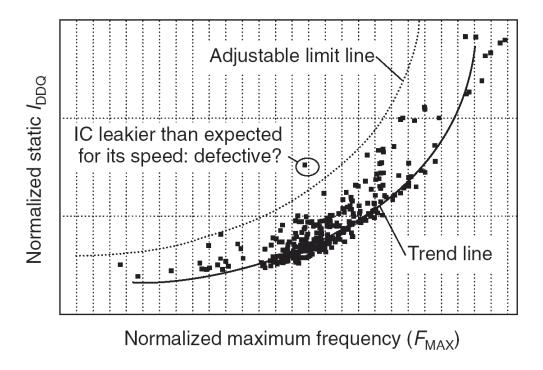

| Fig. 33. Adjustable limit setting for leakier and faster chips.                                           | 45   |

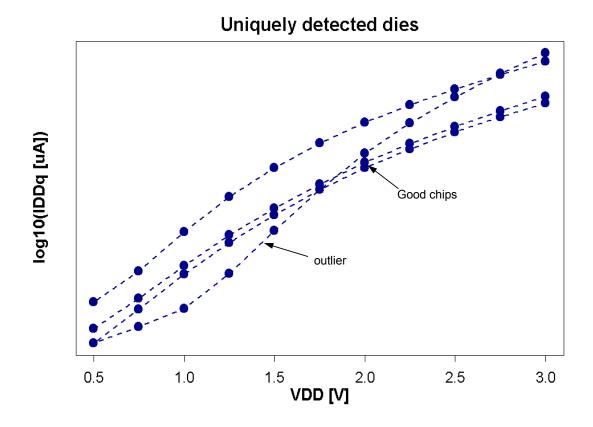

| Fig. 34. I-V curve for some uniquely detected defective chips.                                            | 46   |

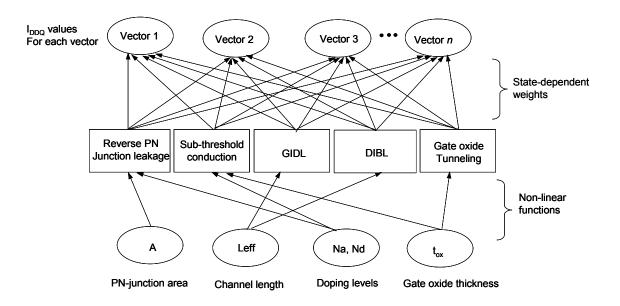

| Fig. 35. Test vector to fabrication process correlation.                                                  | 47   |

| Fig. 36. Comparison of good circuit I <sub>DDT</sub> response to faulty circuit I <sub>DDT</sub> response | 48   |

| Fig. 37. Overview of I <sub>DDF</sub> testing method.                                                     | 50   |

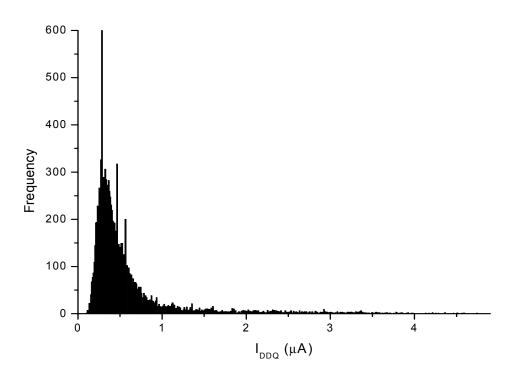

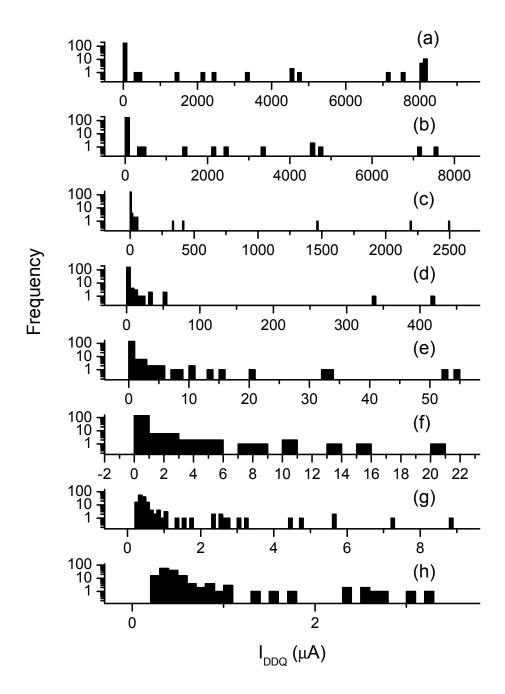

| Fig. 38. Distribution of I <sub>DDQ</sub> values from different chips shows a long tail                   | 51   |

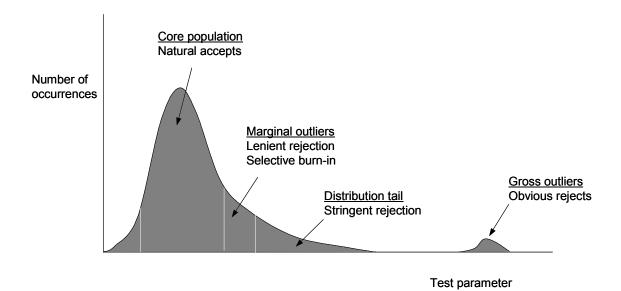

| Fig. 39. Test strategy can be modified depending on "outlier-ness".                                       | 57   |

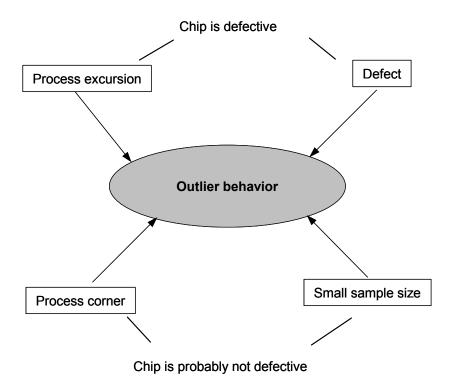

| Fig. 40. Outlier behavior can stem from different reasons.                                                | 58   |

| Fig. 41. (a) A symmetrical distribution gets skewed (b) due to outliers                                   | 59   |

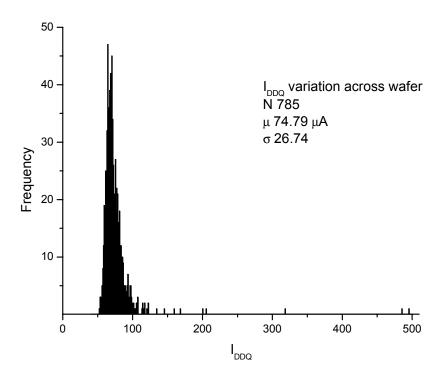

| Fig. 42. I <sub>DDQ</sub> variation across a wafer.                                                       | 60   |

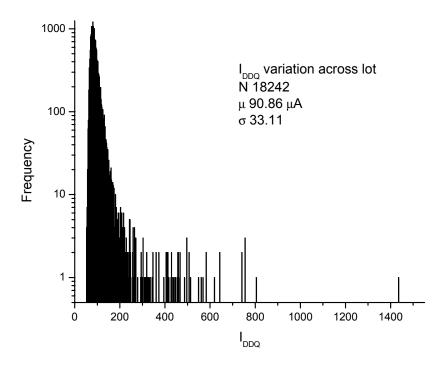

| Fig. 43. I <sub>DDQ</sub> variation across a lot.                                                         | 61   |

| Fig. 44. Successive outlier rejection can nibble away data                                                | 62   |

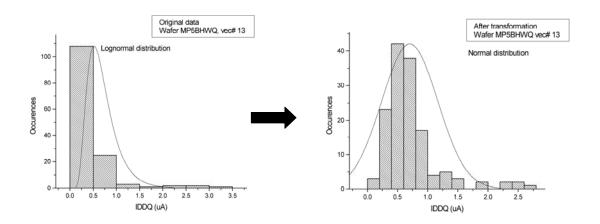

| Fig. 45. Transformation of Lognormal data to Normal distribution.                                         | 64   |

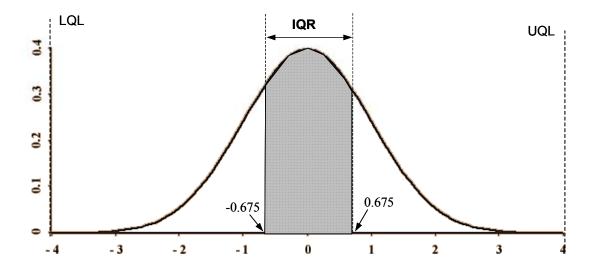

| Fig. 46. Parameter definition for Tukey method.                                                           | 67   |

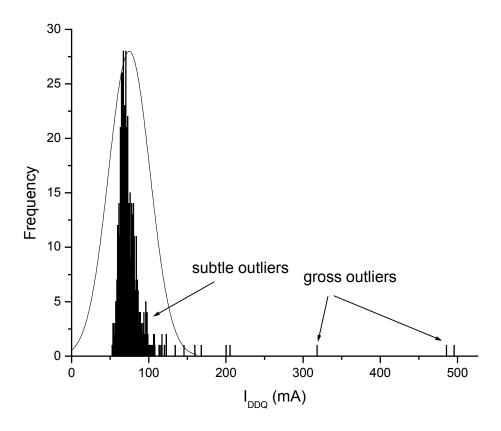

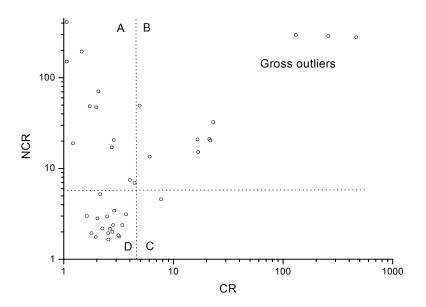

| Fig. 47. Outliers can be subtle or gross. Gross outliers hide the subtle outliers                         | 69   |

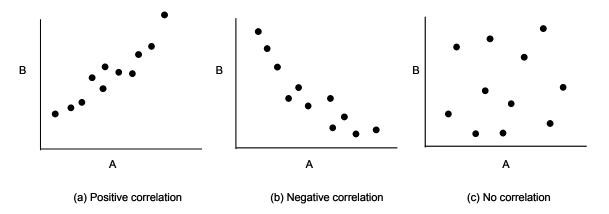

| Fig. 48. Illustrations for positive (a), negative (b) and no (c) correlation                              | 72   |

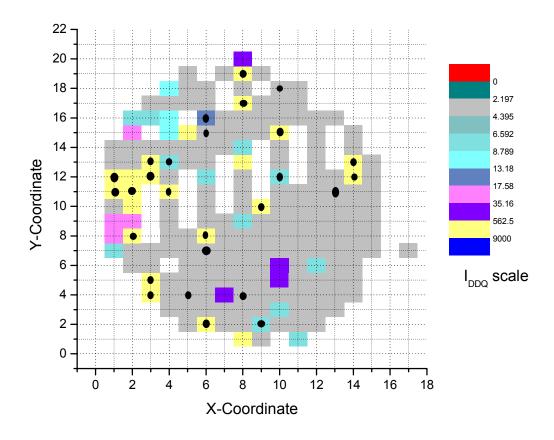

| Fig. 49. Two dimensional grayscale map for I <sub>DDQ</sub> across a wafer                                | 74   |

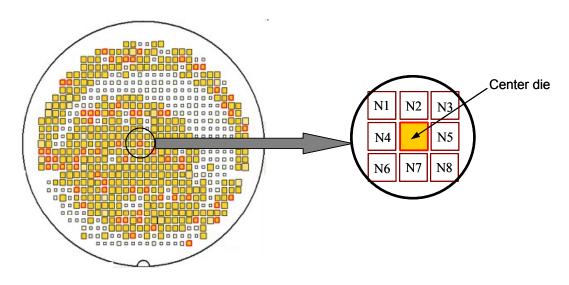

| Fig. 50. Neighborhood die definition.                                                                     | 75   |

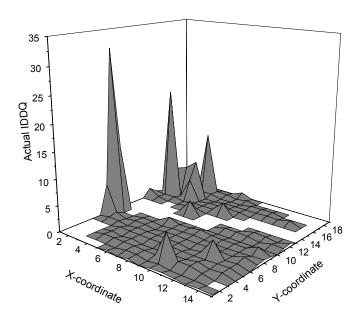

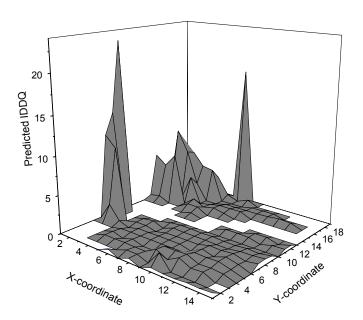

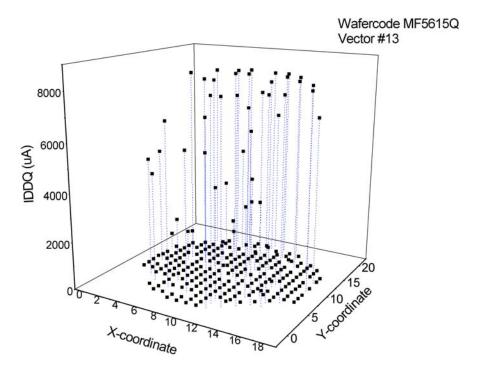

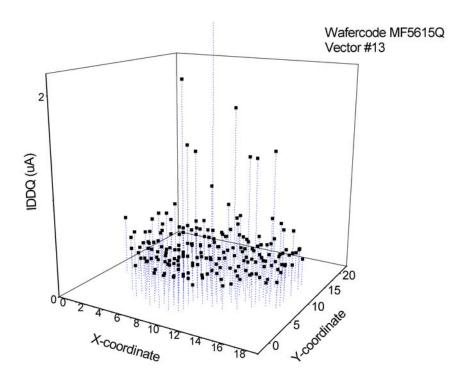

| Fig. 51. Wafer surface plot for a single I <sub>DDQ</sub> vector                                          | 76   |

| Fig. 52. Wafer surface plot for estimated I <sub>DDQ</sub> values.                                        | 76   |

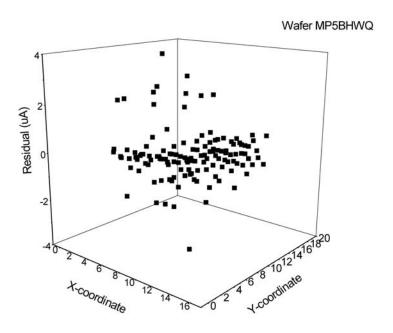

| Fig. 53. Wafer surface plot for residual values for a vector.                                             | 77   |

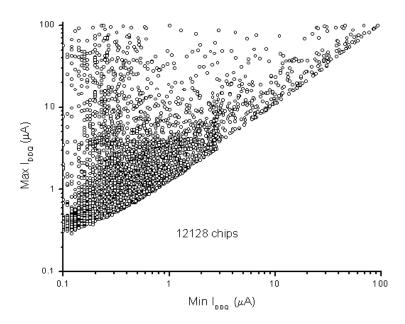

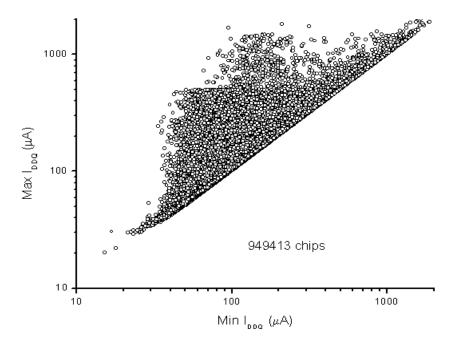

| Fig. 54. Variation in minimum and maximum I <sub>DDQ</sub> for SEMATECH chips.                            | 78   |

| Fig. 55. Variation in minimum and maximum I <sub>DDQ</sub> for LSI chips                                  | 79   |

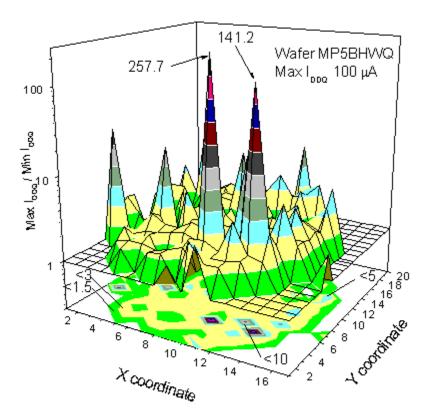

| Fig. 56. Variation in CRs across a wafer.                                                                 | 81   |

| Fig. 57. Variation in NCRs across a wafer.                                                                | 82   |

| Fig. 58. INDIT algorithm.                                                                                 | 83   |

| Fig. 59. Wafer surface plot of maximum self-deltas for a wafer                                            | 83   |

| Fig. 60. Wafer surface plot of maximum neighbor-deltas for a wafer                                        | 84   |

| Fig. 61. Wafer signatures for two wafers for two vectors                                                  | 85   |

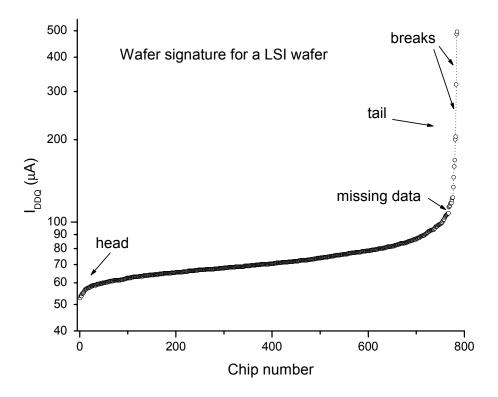

| Fig. 62. Wafer signature for a wafer from LSI data                                                        | 86   |

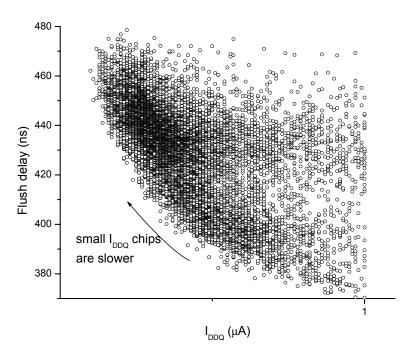

| Fig. 63. Flush delay and $I_{DDQ}$ correlation for SEMATECH data ( $R^2 = 0.40$ )                         | 88   |

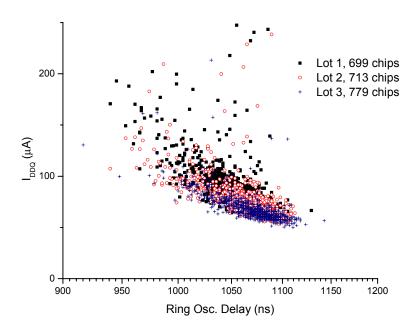

| Fig. 64. Correlation between ring oscillator frequency and $I_{DDQ}$ for LSI data ( $R^2 = 0.48$ )        |      |

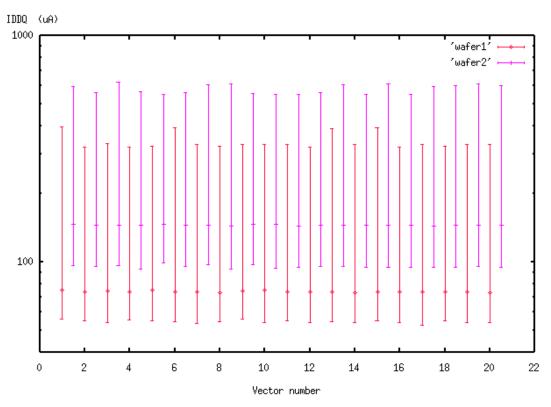

| Fig. 65. Leakage current variation for 20 vectors for two wafers                                          | 89   |

|                                                                                                         | Page  |

|---------------------------------------------------------------------------------------------------------|-------|

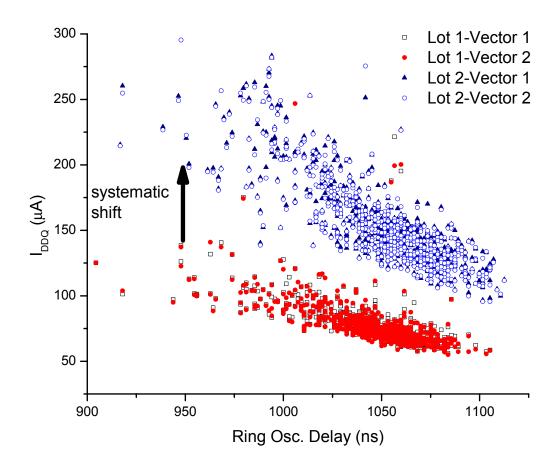

| Fig. 66. Systematic shift in I <sub>DDQ</sub> across lots.                                              | 90    |

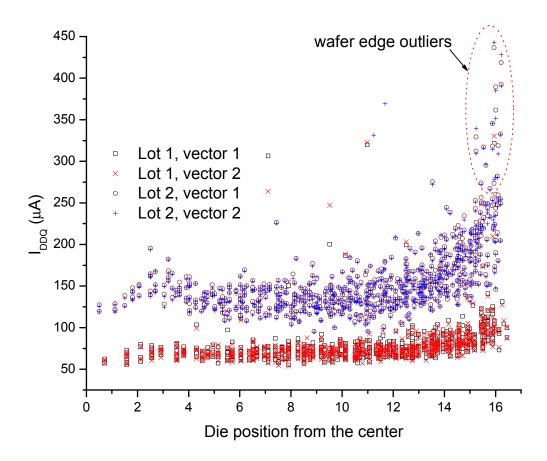

| Fig. 67. Radial variation in I <sub>DDQ</sub> .                                                         | 91    |

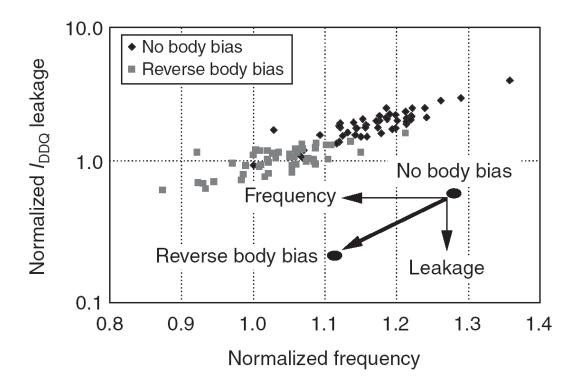

| Fig. 68. IC leakage with and without RBB of 0.5 V at room temperature.                                  | 92    |

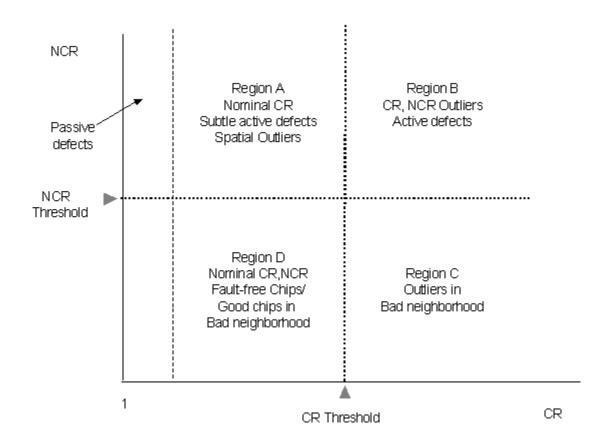

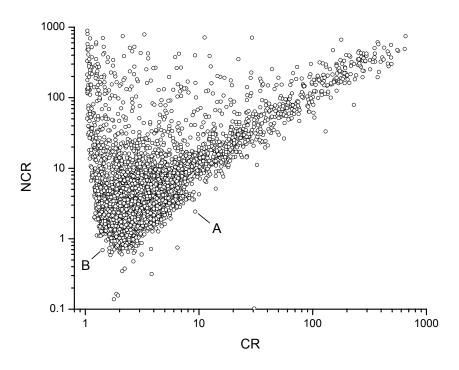

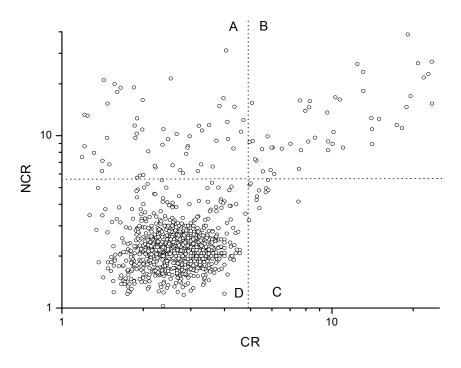

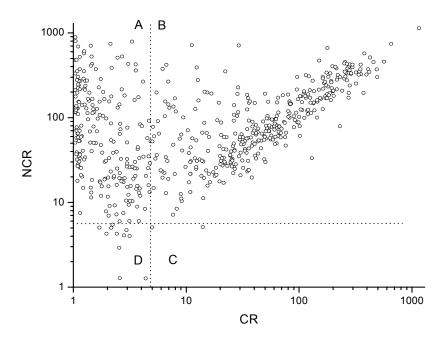

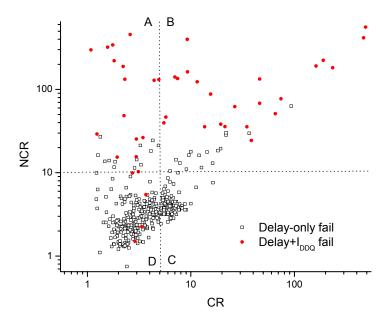

| Fig. 69. Categorization of chips based on CR and NCR.                                                   | 93    |

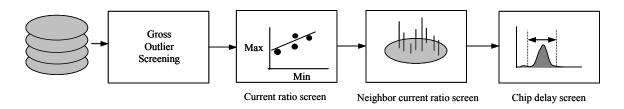

| Fig. 70. Typical analysis flow for multiple test metric screening.                                      | 94    |

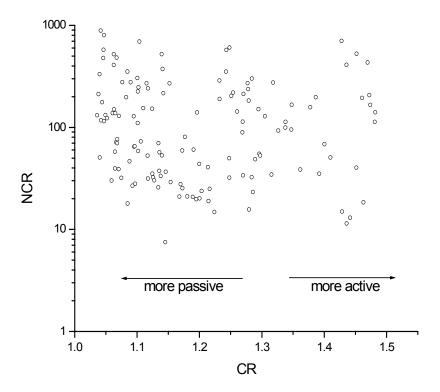

| Fig. 71. CR-NCR scatter plot for chips that passed all wafer tests or failed only $I_{\text{DDQ}}$ test | 96    |

| Fig. 72. CR, NCR and flush delay scatter plot for chips having CR≤10 and NCR≤10                         | 96    |

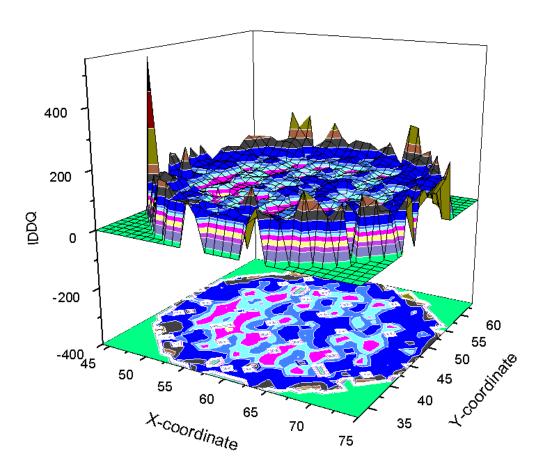

| Fig. 73. I <sub>DDQ</sub> projections on wafer XY plane.                                                | 100   |

| Fig. 74. I <sub>DDQ</sub> projections on wafer XY plane after outlier removal.                          | 101   |

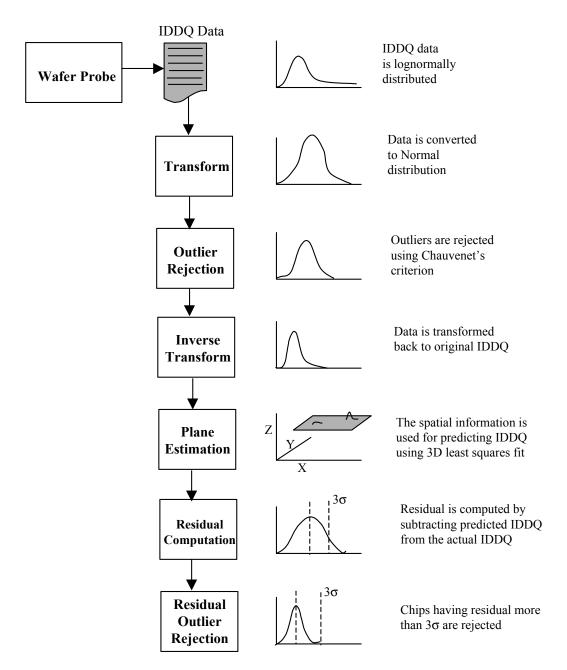

| Fig. 75. Execution flow for outlier screening in spatial fit method.                                    | 102   |

| Fig. 76. Distribution of residuals for spatial fit approach for a vector across wafer                   | 104   |

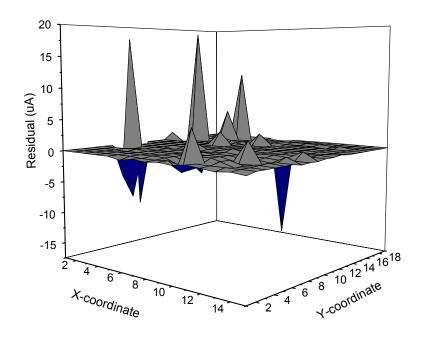

| Fig. 77. A three-dimensional view of residual variation for a vector across a wafer                     | 104   |

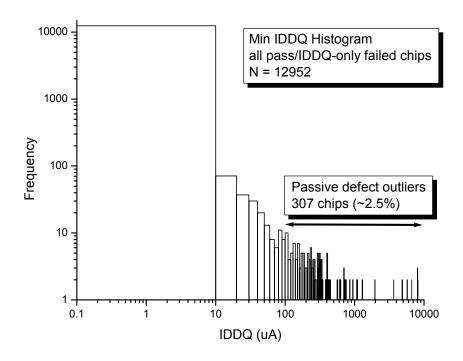

| Fig. 78. Wafer-level minimum I <sub>DDQ</sub> distribution for SEMATECH chips                           | 111   |

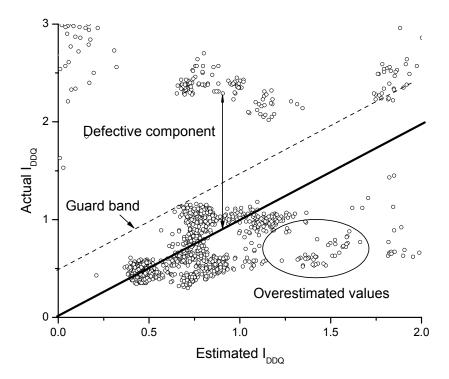

| Fig. 79. Correlating actual and estimated I <sub>DDQ</sub> values.                                      | 112   |

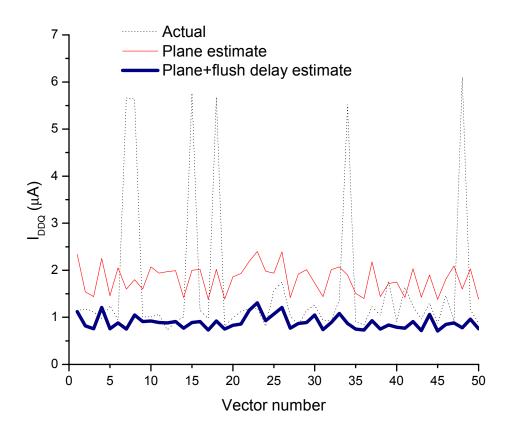

| Fig. 80. Actual and estimated I <sub>DDQ</sub> values for a chip.                                       | 113   |

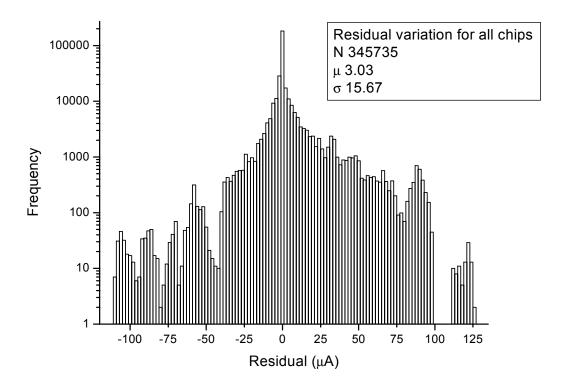

| Fig. 81. Residual distribution for all chips.                                                           | 114   |

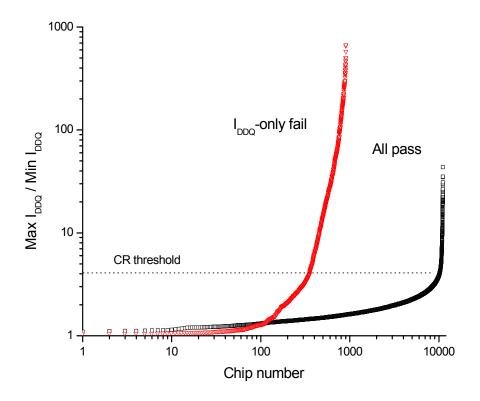

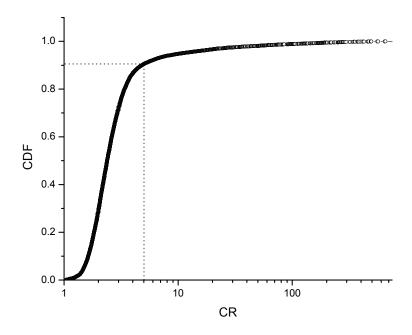

| Fig. 82. Current Ratios for IBM/SEMATECH chips in the dataset.                                          | 117   |

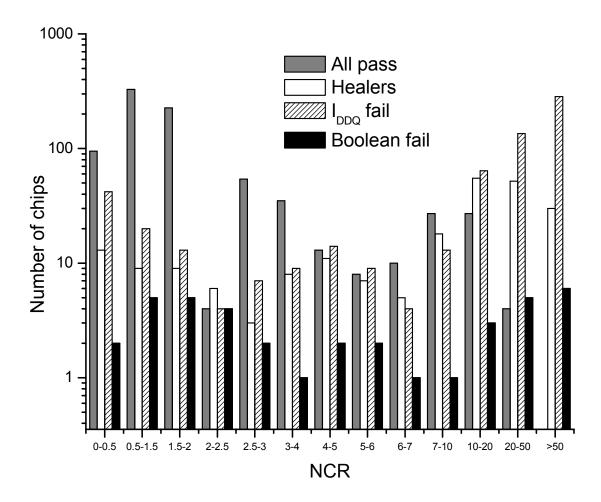

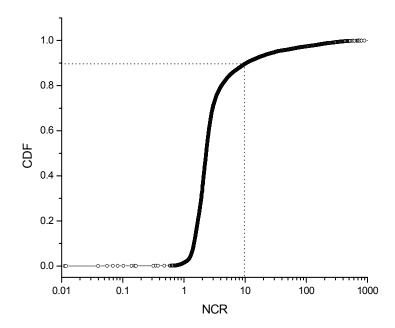

| Fig. 83. Distribution of post-BI results of chips for different maximum NCR values                      | 120   |

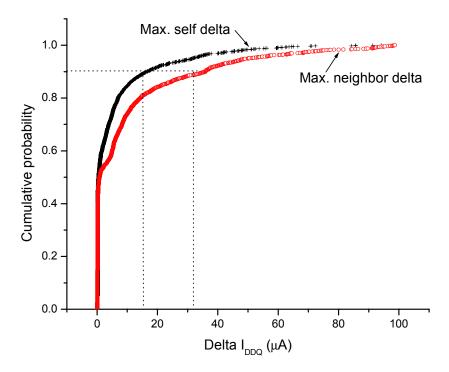

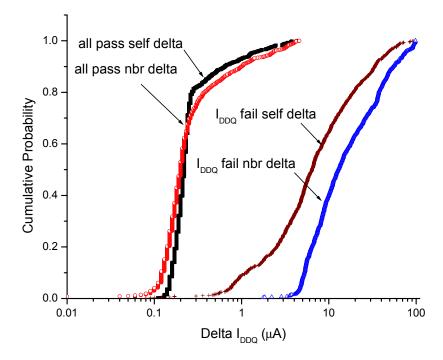

| Fig. 84. CDFs for self and neighbor deltas.                                                             | 122   |

| Fig. 85. CDFs for chips with different wafer probe test results.                                        | 122   |

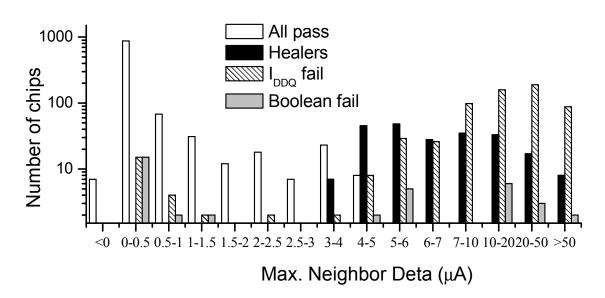

| Fig. 86. Distribution of post-BI results of chips for different maximum neighbor-delta value            | s 124 |

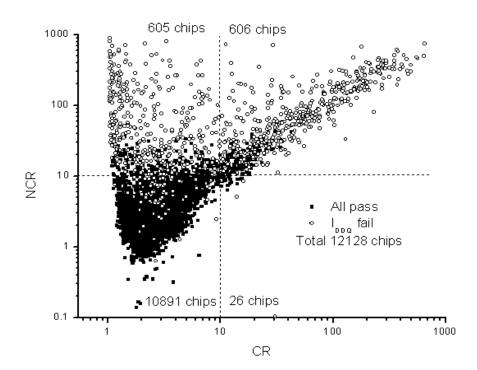

| Fig. 87. Scatter plot of CR/NCR values for all pass or $I_{DDQ}$ -only fail SEMATECH chips              | 125   |

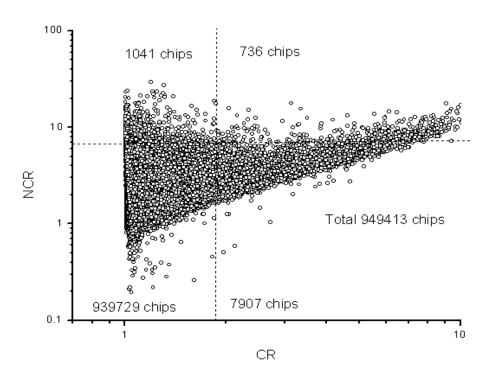

| Fig. 88. CR/NCR scatter plot for LSI data showing number of chips in each region                        | 126   |

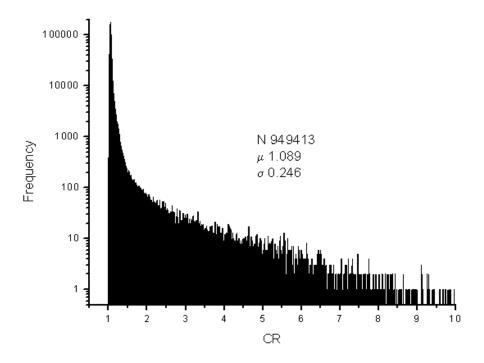

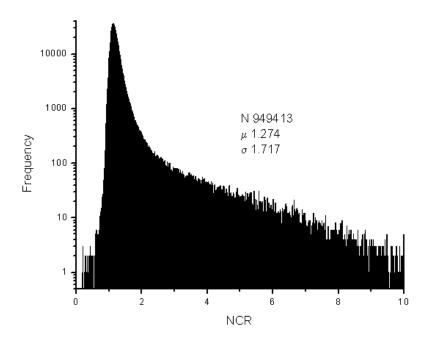

| Fig. 89. Distribution of CR values for LSI data.                                                        | 127   |

| Fig. 90. Distribution of NCR values for LSI data.                                                       | 127   |

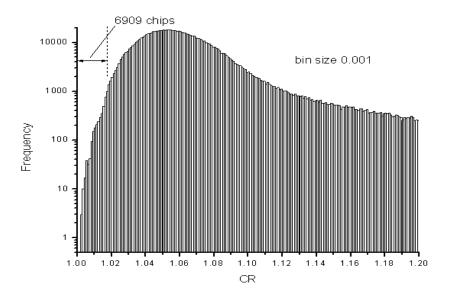

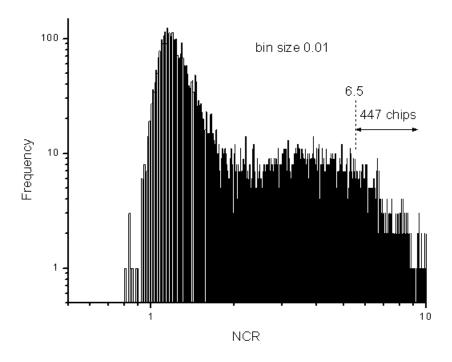

| Fig. 91. Distribution of CRs in the range 1-1.02 for LSI data.                                          | 129   |

| Fig. 92. Distribution of NCRs for LSI chips having CR less than 1.02.                                   | 130   |

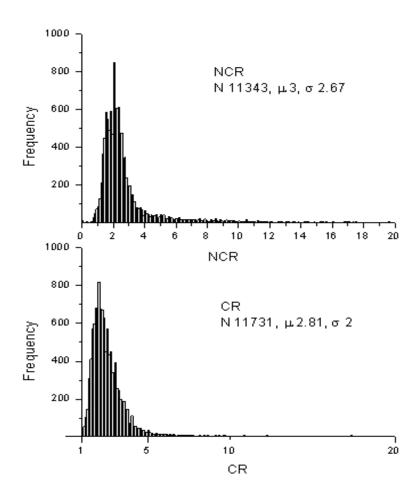

| Fig. 93. Distributions of CR and NCR values less than 20.                                               | 131   |

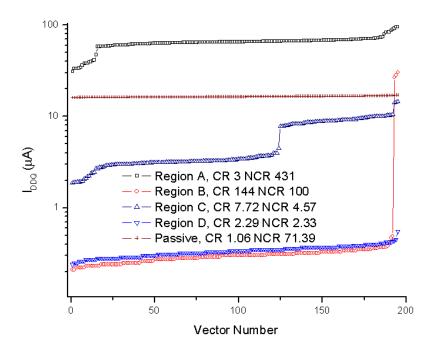

| Fig. 94. Current signatures for die from regions shown in Fig. 69.                                      | 132   |

| Fig. 95. CR/NCR scatter plot for SEMATECH chips that passed all tests                                   | 134   |

| Fig. 96. CR/NCR scatter plot for chips that failed only $I_{DDQ}$ test before and after BI              | 135   |

| Fig. 97. CR/NCR scatter plot for chips that failed Boolean test after BI                                | 136   |

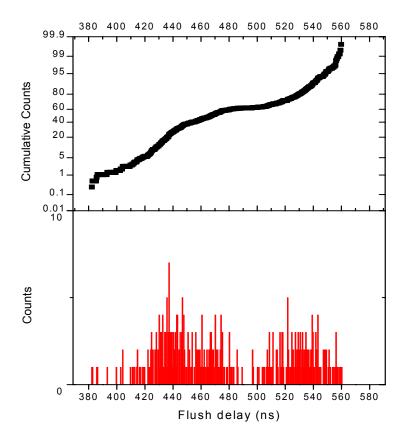

| Fig. 98. Flush delay distribution for the SEMATECH sample.                                              | 137   |

|                                                                                                                                                                                             | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 99. Cumulative distribution for CR values for the SEMATECH sample                                                                                                                      | 138  |

| Fig. 100. Cumulative distribution of NCR values for the SEMATECH sample.                                                                                                                    | 138  |

| Fig. 101. CR-NCR scatter plot for CROWNE chips.                                                                                                                                             | 140  |

| Fig. 102. Distribution of flush delays for delay failed chips.                                                                                                                              | 142  |

| Fig. 103. CR-NCR scatter plot for delay fail and/or I <sub>DDQ</sub> fail chips.                                                                                                            | 142  |

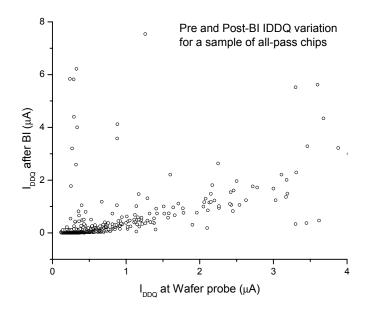

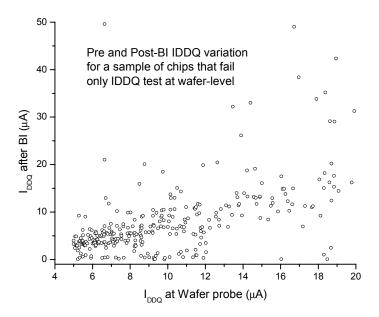

| Fig. 104. NCR and flush delay scatter plot for delay fail and/or I <sub>DDQ</sub> fail chips                                                                                                | 143  |

| Fig. 105. $I_{DDQ}$ before and after burn-in for a sample of chips that passed all tests at wafer probe; chips for which post burn-in $I_{DDQ}$ < 8 $\mu A$ are shown                       | 146  |

| Fig. 106. $I_{DDQ}$ before and after burn-in for a sample of chips that failed only $I_{DDQ}$ test at wafer probe; chips for which post burn-in $I_{DDQ}$ is less than 50 $\mu A$ are shown | 146  |

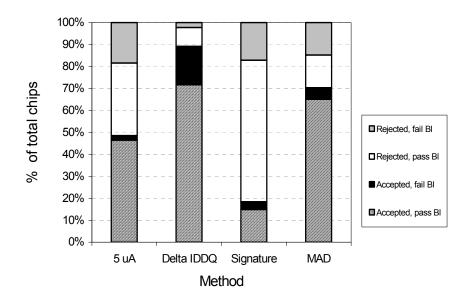

| Fig. 107. Comparison of effectiveness of various methods.                                                                                                                                   | 148  |

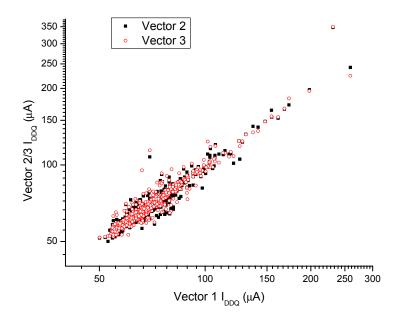

| Fig. 108. Vector-to-vector correlation between different chips.                                                                                                                             | 152  |

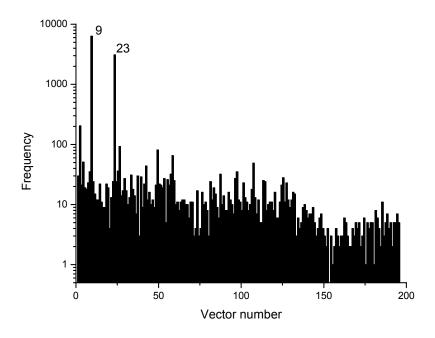

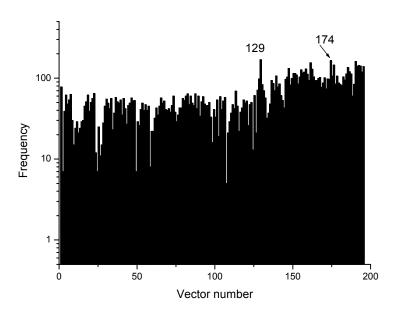

| Fig. 109. Histograms of vectors resulting in minimum I <sub>DDQ</sub> .                                                                                                                     | 153  |

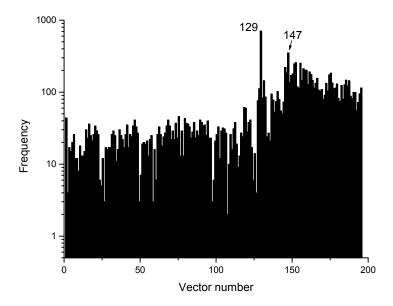

| Fig. 110. Histogram of vectors resulting in maximum I <sub>DDQ</sub> .                                                                                                                      | 154  |

| Fig. 111. Histogram of vectors resulting in max NCR.                                                                                                                                        | 154  |

| Fig. 112. I <sub>DDQ</sub> surface plot for a wafer showing outlier behavior of wafer edge dice                                                                                             | 155  |

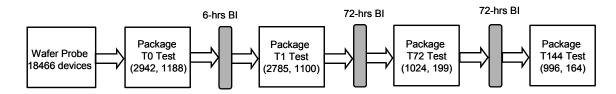

| Fig. 113. Test flow for SEMATECH experiment S-121.                                                                                                                                          | 176  |

|                                                                                                                                                                                             |      |

# LIST OF TABLES

|                                                                                                                    | Page |

|--------------------------------------------------------------------------------------------------------------------|------|

| Table I. ITRS projections for I <sub>DDQ</sub> of high-performance ICs.                                            | 24   |

| Table II. Summary I <sub>DDQ</sub> -based test methods.                                                            | 52   |

| Table III. Summary of I <sub>DDT</sub> -based test methods.                                                        | 54   |

| Table IV. Properties of distributions shown in Fig. 44.                                                            | 63   |

| Table V. Various possibilities as implied by NCR.                                                                  | 80   |

| Table VI. Test strategy when test metrics disagree.                                                                | 94   |

| Table VII. Combination of CR, NCR and delay data.                                                                  | 95   |

| Table VIII. Comparison of predicted and actual I <sub>DDQ</sub>                                                    | 103  |

| Table IX. Comparison of different limit setting schemes Considering post-BI I <sub>DDQ</sub> fails                 | 105  |

| Table X. Comparison of different limit setting schemes ignoring post-BI I <sub>DDQ</sub> fails                     | 106  |

| Table XI. Results for Chauvenet's criterion                                                                        | 109  |

| Table XII. Results for Tukey test                                                                                  | 109  |

| Table XIII. Results for static threshold method                                                                    | 109  |

| Table XIV. Distribution of chips for two methods                                                                   | 115  |

| Table XV: Distribution of dice in the original dataset                                                             | 116  |

| Table XVI. Distribution of chips for different test methods                                                        | 118  |

| Table XVII. Overkill and DL for different test methods                                                             | 119  |

| Table XVIII. Distribution of wafer test and post BI results of chips in the dataset                                | 121  |

| Table XIX. Distribution of chips according to SEMATECH test results for self-delta and neighbor-delta test methods | 123  |

| Table XX. DL and OveRkill comparison of two methods                                                                | 124  |

| Table XXI. Distribution of SEMATECH chips.                                                                         | 132  |

| Table XXII . DL and YL for various categories.                                                                     | 134  |

| Table XXIII. Distribution of sample according to chip test results (12521 chips)                                   | 139  |

| Table XXIV. Comparison of DL and YL for various methods.                                                           | 148  |

| Table XXV. Description of SEMATECH test methods.                                                                   | 177  |

| Table XXVI. Distribution of chips at different test levels.                                                        | 178  |

| Table XXVII. Distribution of BI sample based on test results.                                                      | 179  |

| Table XXVIII. MAD-based rejection example.                                                                         | 185  |

| Table XXIX. List of variables used in cost model                                                                   | 186  |

#### 1. INTRODUCTION

#### 1.1 Introduction

Continuous advances in semiconductor manufacturing technology permit reduction in transistor geometries. This allows higher levels of integration of transistors on a chip. The number of transistors per unit area doubles approximately every 18 months [1]. The International Technology Roadmap for Semiconductors (ITRS) outlines the projections for the future improvements in Very Large Scale Integration (VLSI) semiconductor technology [2]. The recent projections indicate that this progress will continue at least for a decade or more. Of course, several challenges exist for the development to occur. One of these is testing of these chips, an area this dissertation will elaborate on.

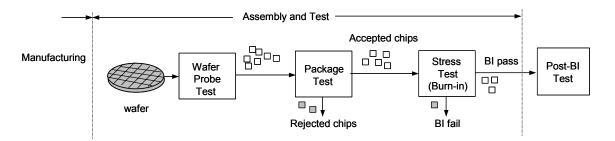

Semiconductor manufacturers must ensure that chips shipped to customers conform to their specifications. This is achieved by testing them for various parameters at different stages of chip manufacturing as shown in Fig. 1. These tests can be classified into two broad categories: Boolean tests and parametric tests. We consider Boolean tests as those tests whose failure clearly means device malfunction. These tests have a pass/fail type decision. Since failure of this type of test means the circuit under test (CUT) has a *hard fault* and cannot perform its desired function, it is rejected. Examples of this type of test include functional [3] and stuck-at tests [4]. On the other hand, parametric tests measure a certain parameter of the CUT. If the parameter falls outside the acceptable range, the CUT has a *soft fault* (parametric fault). Examples of parametric test include quiescent leakage current (I<sub>DDQ</sub>) test and speed (F<sub>max</sub>) test. The failure of a parametric test does not necessarily imply that the device cannot perform its intended function. However, it does not meet its specifications completely [5]. For example, a chip may function correctly but consume more power or operate at a slower speed.

Generally, parametric tests are not part of specification tests. The threshold for a parametric test is always a subjective decision. Too stringent a threshold rejects many fault-free chips; resulting in lost revenue and too loose a threshold accepts many faulty chips, resulting in

This dissertation follows the style and format of *IEEE Transactions on VLSI Systems*.

shipment of defective chips. Because parametric failed chips are functional, the distinction between "fault-free" and "faulty" chips is not straightforward, which makes deciding the pass/fail threshold for a parametric test challenging.

Fig. 1. Basic manufacturing test flow for semiconductor chips.

Apart from screening faulty chips, testing also provides a way to monitor the semiconductor manufacturing process. As semiconductor wafers are processed through the production line in batches called 'lots' (each containing 25-50 wafers) they undergo hundreds of processing steps. Detailed data is collected following many of the process steps and monitored using Statistical Process Control (SPC) [6]. The purpose of SPC is to maintain and insure or improve process quality [7]. Test data is analyzed to understand process variation and determine process corners. It is crucial for semiconductor manufacturers to set reasonable thresholds for SPC as it has direct impact on the outgoing quality and parametric yield.

#### 1.2 Motivation

Testing is one of the final stages in the production cycle and is of fundamental importance to assure that customers will get working units. No product can be manufactured without an efficient test strategy that guarantees the percentage of defective products passing undetected (measured as *defective parts per million* or *DPM*) is sufficiently low to be acceptable. The test strategy that simplifies the production test results in lower test costs and products that are more reliable. Thus, in the long run it influences customer satisfaction. The value of a test can be defined as the ratio of improvement in quality (quantified as reduction in DPM) to the cost of the test. It is possible to reduce DPM by adding more tests but that increases test cost and reduces its value. Screening all defects is unnecessarily expensive. Manufacturers wish to maximize the value of test by balancing outgoing quality and the associated test costs.

Testing is a complex task. The growing complexity of semiconductor chips makes it even more challenging. The cost of testing does not fall as fast as the cost of manufacturing transistors. This results in increased overall percentage of manufacturing cost attributed to testing. To remain competitive in the market semiconductor manufacturers need to be able to keep test cost as low as possible. Tests themselves are not perfect and therefore cannot catch all defects [8]. Although testing does give some confidence to manufacturers about the quality of the shipped lot, it is always an overhead cost. As illustrated in Fig. 1, testing is carried out at different processing steps. Typically the first tests applied to a chip after continuity test check the integrity of the chip structure [9]. Chips with gross defects usually fail this initial screening. As a rule of thumb, test cost increases by an order of magnitude with each integration level (wafer, package, board and system level) [10]. If defective chips are identified earlier in the test cycle, investment in the later steps can be saved. By detecting defects at the wafer level, the cost of manufacturing is kept the lowest as investment in packaging and further testing a defective part is saved. The packaging costs vary greatly depending on the package type. For example, a 16-pin ceramic DIP (dual-in-line package) is about 2 cents while a 400-pin ceramic PGA can cost as much as \$50 [11]. Therefore, identifying defective chips earlier in the manufacturing cycle becomes even more important as the relative percentage of packaging cost increases [12]. This forms the basic motivation for semiconductor manufacturers to screen defective chips at the wafer level test called wafer sort.

Transistor geometries are shrunk with each technology node to obtain higher performance and density. However, controlling transistor geometries precisely becomes harder as transistors are scaled down. Thus, the impact of process variations on integrated circuit (IC) performance increases for deep sub-micron (DSM) technologies [13]. This is further exacerbated by the increasing number of process steps, complex transistor geometries and introduction of new materials. The process variations occur due to variations in physical and environmental conditions such as impurity concentrations, oxide thickness, diffusion of impurities and the imperfect spatial uniformity of the processing steps such as gas flows, etching and deposition of

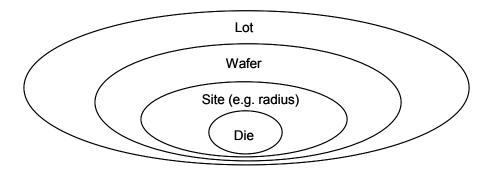

materials, ion implantation, and chemical mechanical polishing (CMP). Variations in the dimensions occur due to limited resolution of the photolithographic process. This gives rise to variation in the chip performances between lots, wafers, across a wafer (*inter-die*<sup>1</sup>) and within a chip (*intra-die*) as shown in Fig. 2. The impact of these variations on chip performance can be as high as 30-35% [14]. Parametric tests or guard bands are used to compensate for discrepancies due to possible test equipment variations within their specified limits. The purpose of guard bands is to minimize the number of devices that fall out due to marginality [3]. Parametric tests must determine which variations are acceptable and which are not. Chips having unacceptable variation in parameter(s) are *outliers*. Empirical evidence suggests that outlier chips have low reliability [15]. Thus to improve or insure quality it is important to screen outliers.

Fig. 2. Illustration of IC parameter variation at various levels.

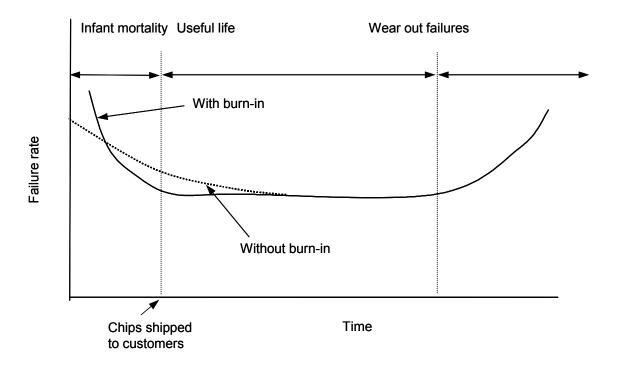

The traditional test method to screen low-reliability chips is burn-in (BI) test. The basis for the concept of BI test is that a chip will most likely fail in the early hours of its life, if it is going to fail at all [16]. BI involves subjecting chips to high temperature and voltage stress to accelerate defects. Chip failure rate is most severe during the infancy of a device as shown in the bathtub curve in Fig. 3. Chips that fail BI test earlier are called *infant mortality*. BI accelerates

\_

<sup>&</sup>lt;sup>1</sup> We use the words 'die' and 'chip' synonymously in this dissertation.

the aging of the device or compresses the time scale so that infant mortality can be screened. Since chips are aged beyond their infant-mortality life stage, the chips that survive BI are expected to be more reliable and have very low and steady failure rates.

Fig. 3. Reliability bathtub curve and reliability screen using burn-in.

The effectiveness of BI depends on the stress exerted on a chip, which is a function of the difference between nominal voltage (temperature) and elevated voltage (temperature). As supply voltages are reduced with each technology node and operating temperatures are increased, the effective stress is reduced, thus making BI less effective. Secondly, BI is getting prohibitively expensive. This has fueled research to seek alternatives to BI. Chips having higher leakage current are observed to have low reliability and, therefore, the use of quiescent leakage current (I<sub>DDQ</sub>) test has been investigated as an alternative to BI [17]. However, increasing fault-free leakage current and current variation due to technology advances makes distinction between faulty and fault-free leakage difficult and hence this option less viable for state-of-the-art technologies. One line of research is to screen chips based on the comparison of their behavior with the population. If a chip is an outlier, semiconductor manufacturers would rather accept the

yield loss incurred by rejecting it than risk shipping it. Due to higher cost of a customer return and long-term likely impact on customer-perceived quality, test economics is complicated. Statistical post-processing (SPP) of wafer-level test data has been shown to be a powerful alternative to BI in the production flow [15].

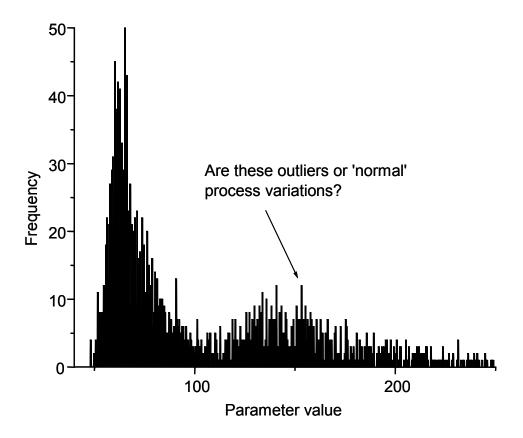

Fig. 4. IC parameters show a continuous distribution.

To determine whether a chip is an outlier it is necessary to define the "normal" behavior of a chip. Fig. 4 shows the distribution of a parameter for all chips from a wafer. Note that due to continuous parameter distribution many chips appear to be outliers. However, their seemingly strange behavior may be explained by understanding underlying process variations or by comparison with some parameters of other fault-free chips. Hence, outlier identification is a difficult challenge. This becomes even more challenging as subtle defects become crucially important for advanced technologies [18]. Differentiating between "true outliers" (defective chips) and "apparent outliers" is the primary goal of this research. Here further we use the word "outlier" to mean a defective chip.

#### 1.3 Objectives of the Research

The main goal of this research is to evaluate outlier-screening capability of different data analysis methods for measured IC parameters. Ideally, outlier screening should result in a reduced number of defective parts shipped to customers (i.e. lower DPM) as well as reduced number of good parts getting rejected (i.e. yield loss). Due to continuous parameter distributions, these are conflicting goals as shown in Fig. 5. Therefore, semiconductor manufacturers need to balance these goals.

Fig. 5. Conflicting goals of yield loss and defect level.

In this dissertation, we evaluate some methods to determine their effectiveness in identifying outlier chips. These methods are evaluated using industrial test data from IBM (SEMATECH experiment), LSI Logic and Texas Instruments (TI). The information about the data is included in Appendices A, B and C.

The quiescent leakage current ( $I_{DDQ}$ ) forms our basic parameter for outlier identification. However, as will be shown later,  $I_{DDQ}$  data alone may not be sufficient to screen outliers. We therefore define additional test metrics and use a combination of multiple test parameters (e.g. delay and leakage current) for screening outliers with higher resolution. We primarily use wafer-

level test data for outlier identification and supplement it with wafer-level spatial data. If additional tests are conducted after packaging, we use them to evaluate the effectiveness of the outlier detection methods. While extensive BI and other test data is available for the SEMATECH research experiment, our evaluation is limited for the LSI Logic and TI data since further testing is not carried out when a chip fails in the test flow ("stop on first fail" test flow) and no BI stress test is performed.

#### 1.4 Contributions of the Dissertation

The focus of this dissertation is to evaluate different techniques to screen defective chips using parametric test data and statistical outlier rejection methods. To achieve it, this dissertation exploits wafer-level spatial correlation. The methods evaluated, metrics proposed or examined primarily revolve around this basic theme.

The contributions of this dissertation can be summarized as follows:

- Evaluation of applicability of statistical outlier rejection methods to VLSI testing using parametric data

- Exploitation of wafer-level spatial correlation for outlier screening

- Evaluation of a novel self-scaling test metric called Neighbor Current Ratio (NCR)

- Evaluation of two new methods, Immediate Neighbor Difference I<sub>DDQ</sub> Test (INDIT) and Wafer Signature, for outlier identification

- Combination of multiple test metrics for obtaining some insights into defect type

- Evaluation of applicability of outlier rejection using Median of Absolute Deviation (MAD) resistant estimator for BI reduction

#### 1.5 Structure of the Dissertation

The dissertation discusses the background in Section 2. We define the VLSI testing problem in general and describe different test methods used. This section should prepare the reader with the background necessary to understand the material covered in the later sections.

The focus of this research work is outlier identification. The outlier identification methods are applicable to any parametric test data. We use  $I_{DDQ}$  test data extensively to illustrate the basic concepts in outlier analysis. The prior work reported in the literature for  $I_{DDQ}$  data analysis is reviewed in Section 3. This section also discusses how these methods lose their effectiveness in screening defective chips (outliers) for new semiconductor technologies. This motivates the use of multiple test metrics.

Outliers are defined by knowing the distribution of nominal measured parameters. However, the distribution is affected by the presence of outliers. This is equivalent to the chicken and egg problem. Section 4 describes this difficulty in screening outliers. Some outlier identification criteria and different metrics are proposed in this section. Since outlier detection depends on resistant estimators, they are also discussed. Outlier detection itself is a separate topic in statistics and a wealth of literature is available [19]. Our goal here is just to provide a glimpse of this area and evaluate its applicability to VLSI testing.

Section 5 discusses multiple-parameter correlation and its effectiveness in screening outlier chips. Some discussion on why two parameters should exhibit correlation is provided. We also show how a combination of multiple test metrics is useful for increasing confidence in outlier detection.

We use the test data from IBM/SEMATECH, LSI Logic and TI for the experimental validation of our methods. Results of the analyses are presented in Section 6. The conclusions drawn are our own and do not necessarily represent views of these companies.

Section 7 presents our preliminary analysis of using an outlier screening method to reduce burn-in. The results of analysis of IBM/SEMATECH data are presented in this section.

Finally, Section 8 presents conclusions and contributions of this work. It also outlines the direction of future research and comments on impact of technology and usefulness of this research.

#### 2. BACKGROUND

#### 2.1 Introduction

This section provides an overview of VLSI testing. The information presented here should help the reader understand the key terms used in the later sections and gain an appreciation for the complexity and challenges involved in testing semiconductor chips. We use quiescent leakage current measurement data extensively in this dissertation. Therefore, we discuss  $I_{DDQ}$  test in detail in this section.

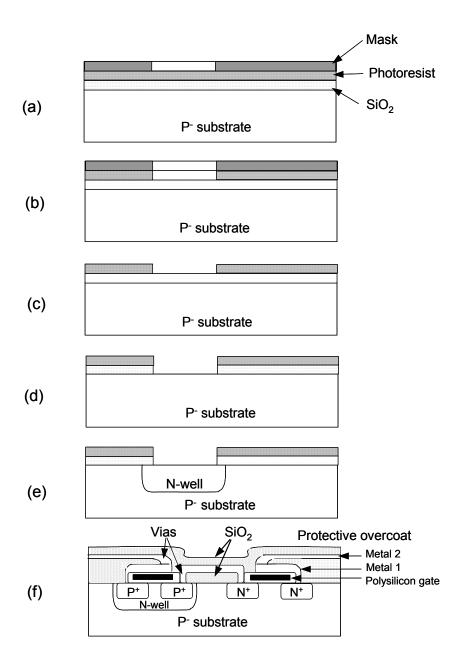

## 2.2 IC Manufacturing Flow

The Integrated Circuit (IC) manufacturing process consists of a series of photolithographic printing, etching, and doping (impurity addition) steps. A typical fabrication process for manufacturing a CMOS (Complementary Metal Oxide Semiconductor) transistor pair is illustrated in Fig 6. A layer of silicon dioxide (SiO<sub>2</sub>) is grown on the surface of a P<sup>-</sup> wafer. Photoresist is laid down on top of SiO<sub>2</sub> layer. Using ultraviolet (UV) light a pattern is projected onto the photoresist through a photographic mask. The area of photoresist exposed to UV light gets hardened. Using an organic solvent the nonexposed portion of the photoresist is washed away. After baking the remaining photoresist, exposed areas of oxide are removed using an etching process. The exposed areas of silicon are doped to form an N-well using either diffusion or ion implantation. Through a series of hundreds of steps of printing, masking, etching, implanting, and chemical vapor deposition (CVD), a complex IC is fabricated [20].

### 2.3 Need for Testing

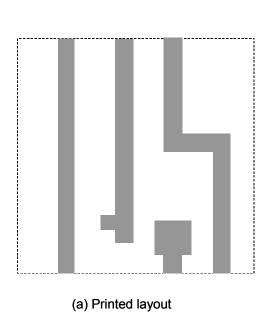

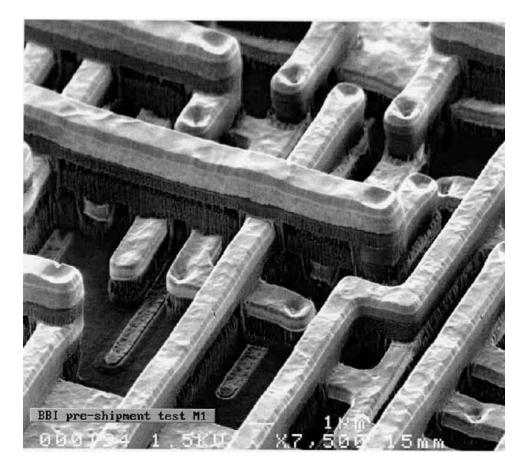

What is illustrated in Fig. 6 is an idealized approximation of actual fabricated circuit. In today's state of the art technology, the transistor geometries, metal pitch, and depositions are extremely small. For example, the state of the art microprocessor uses 130 nm technology. At such small geometries, even a tiny dust particle, metallic sliver, or even a piece of human hair can lead to shorting of two wires. The wire patterns are not exactly rectangular when printed. Fig. 7 (a) is the intended wiring pattern while Fig. 7(b) is the actual fabrication as observed through a Scanning Electron Microscope (SEM). The SEM photo shows that wires have non-uniform width as well as a particle that shorts two wires (called a *bridging defect*).

Fig. 6. Typical CMOS IC fabrication flow.

Variations in process conditions, physical deformations in the processing material and contaminations can cause a chip to malfunction [21]. Fig. 8 shows an example of interconnections on multiple metal layers. This clearly illustrates the nonuniformity caused in wires due to different processing conditions.

(b) Manufactured silicon

Fig. 7. (a) Original mask pattern and (b) actual silicon.

To ensure that all transistors and interconnect work in tandem to achieve the desired circuit functionality is a challenging task. To verify that a chip conforms to specifications, manufacturers need to test chips. However, from a manufacturer's perspective, the purpose of testing is not only to ensure conformance to specifications, but also to reduce the long-term cost involved in handling a customer return. Seen from this perspective, testing is an investment made in a "cost-avoidance" strategy [10]. In other words, testing is an investment made by the manufacturer to ensure customer satisfaction. Naturally, a semiconductor manufacturer wishes to maximize the return on investment (ROI), that is, minimize test cost while improving outgoing quality. Obviously, if test costs more than the manufacturing cost, it would be cheaper to replace the returned (defective) parts. In a nutshell, the role of testing is to screen chips that do not function and also chips that are likely to fail early in the customer system (reliability risk). Testing is also used for understanding, controlling and diagnosing process excursions to improve yield in the so-called *yield learning* phase.

Fig. 8. Process variation induces inter-layer variation in metal thickness.

# 2.4 Contamination, Defects, Faults and Degradation

The purpose of test is detection of a malfunction in the operation of an IC. A distinction is made between defects, faults and degradation [22]. Contamination is a foreign material on a wafer surface. It can be from human skin, dirt, dust particle, residual chemicals, etc. A *defect* is a physical deformation that leads to device malfunction. A defect may be extra material (e.g. a short between two nodes called *bridge*) on a layer or between layers or missing material (e.g. discontinuity in metal or polysilicon line called *open defect*)

Different types of defects lead to similar IC abnormalities called *faults*. A fault is thus a higher-level abstraction of a defect. It is a hypothesis of how a logic gate would malfunction without assigning any specific attributes to the defect that can cause it [22]. A fault is said to occur only if a test to detect it exists (i. e. it is detectable) and it is detected. Obviously, if a fault

does not cause any change in the chip behavior then faulty and fault-free chips cannot be distinguished. These faults, called *redundant faults*, are of no consequence to the functional behavior of the circuit, although they may affect the reliability of the circuit.

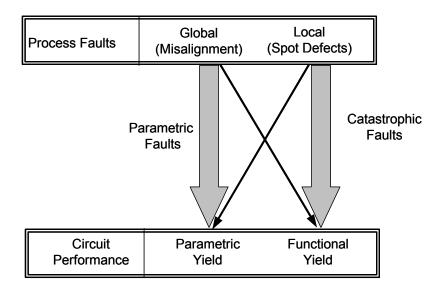

Fig. 9. Global and local defects and associated yield loss.

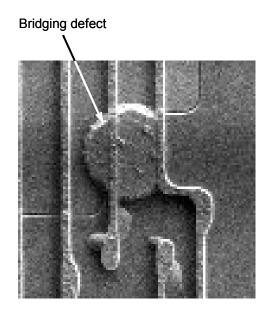

Many defects cause degradation (a weakness in the physical construction of the circuit) that does not lead to logical malfunction but only degrades system performance (e.g. propagation delay or noise margin). For example, a thinner metal line will result in higher resistance and increased delay. The circuit still functions but at a reduced speed. Such a chip, even if it passes all functional tests, is a reliability risk. CMOS chips are more prone to degradation faults [23]. In general, there are two types of faults than can occur: local process faults and global process faults [24]. Examples of global process faults include mask misalignment and line width variations. Local process faults include spot defects like oxide pinholes or bridges. As shown in Fig. 9, global process faults primarily affect parametric yield as they cause variation in speed or power consumption. This gives rise to *parametric faults*. Parametric faults are often the consequence of bad design, but they may also be an indication of a defect [25]. Local process faults primarily affect circuit topology, cause a chip to fail functionally, and affect functional yield. They are also called *catastrophic faults*. However, as thin arrows in Fig. 9 indicate, global faults can affect functional yield and local faults can affect parametric yield as well. Note that

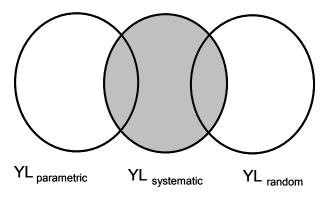

whether a fault leads to structural or performance failure depends on the overall disturbance caused by the process deformation [26]. There is an overlap between yield loss caused by parametric, systematic and random defects as shown in Fig. 10. Recent studies indicate that systematic variation (e.g. via alignment, optical proximity correction (OPC) based defects, etc.) is a more dominant cause of failures for new technologies [27].

Fig. 10. Yield loss due to parametric, systematic and random defects.

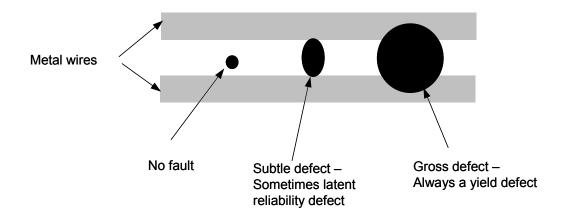

It must be emphasized that not all defects lead to faults or functional failure. This can be conceptually illustrated with the help of Fig. 11. It shows a particle defect between two metal lines. Depending on the size of the particle and its location relative to the wires, it may or may not short the wires. If the particle barely touches the wires (subtle defect), it may not cause functional failure but remain latent until the chip is shipped. In some cases, it may cause delay fault [28].

Although there are infinite numbers of possible defects, many have a similar effect on the electrical (logical) behavior of a chip, and, therefore, a finite number of fault models are sufficient. Fault models enable us to quantify the quality of test suites and compare them. This is done using a *fault coverage* or *test coverage* metric, which is the percentage of faults detected by a test out of the total detectable faults in the circuit. Under the same fault model a test with higher fault coverage is better than one with lower fault coverage as it has a higher probability of detecting a defect. The most popular fault model is the stuck-at fault model that assumes that all circuit failures occur in such a way that a logic gate node (input/output) behaves as if it is clamped to logic 1 or 0. Since stuck-at fault model is not accurate for many actual defect

behaviors [29], other fault models like pseudo stuck-at, bridging, open, transistor stuck-on/off, etc. have been used [28], [30]. To model delay faults (which become more important as chip frequencies increase) path delay, gate delay and transition delay fault models have been suggested [31]. These models have their own merit and are successful in varying degrees, however, the single stuck-at fault model continues to be the most popular fault model owing to its simplicity and effectiveness [32] and investment in tools [33].

Fig. 11. Subtle and gross defects.

Once a chip is manufactured, there is no direct access to its internal nodes. Hence, for fault detection, a test pattern must excite the fault as well propagate its effect to an output. These conditions, called *excitation* (or *sensitization*) and *propagation* of the fault, form the basis of test generation [34], [35]. All *automatic test pattern generator* (ATPG) tools essentially try to generate a test vector (or a pair of test vectors) that excites a fault and makes its presence detectable at an output [36], [37].

## 2.5 Test Quality

Tests themselves are not perfect and cannot catch all defects. Since test cost increases roughly by an order of magnitude with each integration level [10], there is a strong motivation to screen defective chips at the wafer-level before they are packaged. This becomes increasingly important as packaging costs escalate. Finding a defective chip at the customer site is expensive as it can result in a customer return. Moreover, it damages the manufacturer's reputation about quality. Today's microprocessors demand quality levels on the order of 100 DPM [38]. To achieve these

quality targets given tests are not perfect, manufacturers need to use a combination of different test methods.

#### 2.6 Test Method Classification

A simple method to test a chip is to verify that it performs its intended operation. This is what is called a *functional* test. Obviously, to guarantee a chip is indeed fault-free one must exercise all possible input conditions and verify outputs for correctness. As the number of inputs increases, this results in an exponential growth of test patterns (test vectors) and long test time. Therefore, such *exhaustive testing* is prohibitively expensive and impractical. Moreover, generation of functional test vectors requires thorough understanding of the design and hence long development time. For these reasons, complete functional testing is impractical. The alternative approaches use knowledge of circuit structure for testing. One way to achieve this is to ensure that all internal circuit nodes can assume both binary values and propagate them to (at least) an output. This so-called *structural* test gives some confidence about the integrity of a chip. To ensure ease of structural test requires certain design modifications that enhance controllability and observability of a circuit's internal nodes [39]. These modifications need to have little, if any, impact on the design. Such design modifications are termed *design for testability* (DFT) [40] and are a topic of great importance for VLSI chips [41][42].

Another class of test methods is *parametric tests* which measures various parameters like supply current or chip speed.  $F_{max}$  test is a type of parametric test.  $F_{max}$  is the maximum frequency a chip is capable of operating at. Microprocessor companies often speed bin their products to optimize revenues (a faster chip has a higher price). Die-to-die and within-die fluctuations in IC parameters significantly impact the result of the  $F_{max}$  test [43].

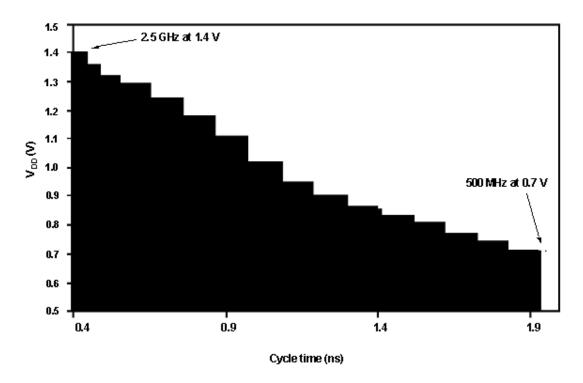

A popular parametric test method is to plot two test parameters and measure their variation across wafers/lots. Such plots, called *shmoo plots*, represent how a particular test passes or fails when parameters like frequency, voltage, or temperature are varied and the test is executed repeatedly [44]. It is a method to visualize how the performance of an IC changes with changes in external environment like temperature or voltage, as well as process parameters. A shmoo plot for power supply and chip speed for an Intel Pentium® 4 processor is shown in Fig. 12. It shows that at a lower supply voltage chips operate at a lower frequency.

The impracticality of functional test and inadequacy of structural test to detect all defects led to *defect based test* (DBT) [45]. In this type of test, a chip is tested for the presence of defects by

comparing the chip's behavior if a defect were present to its defect-free behavior. Examples of this type of test include stuck-at test, pseudo stuck-at ( $I_{DDQ}$ ) test, bridge fault test, etc. It is observed that the addition of DBT is useful for achieving high quality goals [46].

Fig. 12. Shmoo plot showing relationship between supply voltage and chip speed.

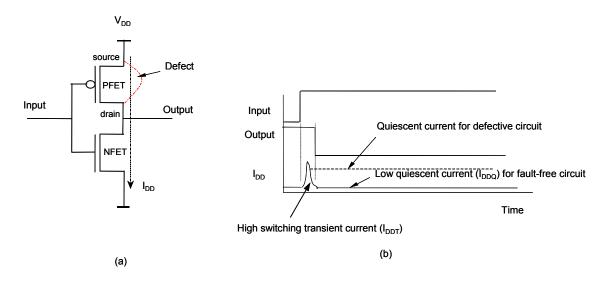

# 2.7 Principle of I<sub>DDQ</sub> Testing

When the inputs of CMOS circuits are static, there is no direct conduction path from  $V_{DD}$  to  $V_{SS}$  (ground/GND). Thus, ideally no current flows through the circuit. Fig. 13(a) shows a static CMOS inverter circuit having PMOS and NMOS transistors in series. When the input is at logic zero (one) the PMOS (NMOS) transistor is ON, NMOS (PMOS) transistor is OFF and the output is at logic one (zero). Ideally, current flows from  $V_{DD}$  to GND only for a brief period of time during switching when both transistors are partially ON as shown in Fig. 13(b). However, in practice, a small amount of leakage or quiescent current ( $I_{DDQ}$ ) flows even when inputs are stable. In the presence of a defect, (e.g. source-to-drain short as shown in Fig. 13(a)), the current flows through the direct path from  $V_{DD}$  to GND comprised of the defect (short) and ON transistor. This current is much higher than the leakage current as shown in Fig. 13(b). Thus by

measuring the leakage current flowing through the chip for different input vectors, defective circuits can be identified. This observation has been used for screening defective chips and a corresponding fault model is proposed [47][48]. Note that  $I_{DDQ}$  is large only when the defect shown in Fig. 13(a) is excited, when the input is high (i.e. PMOS transistor is OFF). Such a defect is called a pattern-dependent or *active* defect. If the defect current is independent of the input pattern, it is referred to as a pattern-independent or *passive* defect. An example of a passive defect is a bridge between  $V_{DD}$  and GND [49].

Fig. 13. (a) CMOS inverter circuit and (b) faulty and fault-free waveforms.

# 2.8 I<sub>DDQ</sub> Testing Benefits

I<sub>DDQ</sub> testing is attractive to semiconductor manufacturers due to its simplicity as well as many other benefits it offers [50]. Since power supply current can always be observed, I<sub>DDQ</sub> test does not have fault propagation requirements like stuck-at test. This is equivalent to saying that I<sub>DDQ</sub> test has 100% observability. Several studies have shown that I<sub>DDQ</sub> test detects certain defects not detected by any other test method [51–53] thus improving outgoing quality [54]. Examples of these defects include gate-oxide short (GOS), bridging defects, some stuck-open faults and certain delay faults [55]. As achieving very high stuck-at fault coverage becomes difficult, I<sub>DDQ</sub> testing has been used to improve coverage with non-observable test locations and relatively few measurements [56].

Some defects do not cause functional failure, but can result in low reliability of the chip. Such chips fail after they are put in the system. Reduction in the number of such failures (called *infant mortality*) can be achieved by subjecting chips to stress conditions before they are shipped. Semiconductor manufacturers have employed *burn-in* (BI) test<sup>2</sup> in which chips are subjected to higher temperature and voltage. The Arrhenius equation is used to normalize failure rate predictions at a system operation temperature (voltage) [57]. This model assumes the degradation of the performance parameter is linear with time. The temperature dependence is taken to be an exponential function that defines the probability of occurrence. The acceleration of defects due to increased temperature (A<sub>T</sub>) and voltage (A<sub>V</sub>) are given by the Arrhenius equation as follows [58]:

$$A_T = e^{\frac{E_a}{k}} \left( \frac{1}{T_{use}} - \frac{1}{T_{stress}} \right)$$

(2.1)

$$A_{V} = e^{\frac{E_{a}}{k}} \left( \frac{1}{V_{use}} - \frac{1}{V_{stress}} \right)$$

(2.2)

where  $T_{use}$  ( $V_{use}$ ) is the normal operating temperature (voltage),  $T_{stress}$  ( $V_{stress}$ ) is the stress temperature (voltage),  $E_a$  is the activation energy, and k is Boltzmann's constant (1.38 × 10<sup>-23</sup> J/K). Due to reduced operating voltage in newer technologies, the maximum  $\Delta V$  ( $V_{stress} - V_{use}$ ) that can be achieved without destroying the part is reduced. In addition, increased power levels cause high operating temperature, thus reducing the  $\Delta T$  ( $T_{stress} - T_{use}$ ) that can be obtained. This makes BI less effective for advanced process technologies or requires economically prohibitive BI time. Below 90 nm, BI may become economically infeasible. Moreover, it is a destructive test [59] and components failing BI represent lost revenues. The motivation for reduction in DPM due to BI is becoming outweighed by unacceptable (apparent) yield loss. Thermal runaway due

<sup>&</sup>lt;sup>2</sup> BI is used for high-performance and high-reliability chips and is not part of the normal test flow.

to inadequate temperature control can destroy some fast chips. More cost-effective alternatives to BI are sought. It has been shown that  $I_{DDQ}$  testing is useful for detecting many defects that lead to reliability hazards [60–64]. These include gate-oxide shorts, punchthrough and leaky transistors [65]. An independent study from SEMATECH showed that the chips having higher leakage have higher BI failure rate [66]. As  $I_{DDQ}$  testing takes a fraction of the time it would take for BI, assembly and test cycle time can be reduced.

# 2.9 I<sub>DDQ</sub> Test in Practice

$I_{DDQ}$  test essentially involves setting a pass/fail threshold value for leakage current. A chip whose leakage exceeds the threshold is considered defective. The maximum  $I_{DDQ}$  is estimated by circuit simulations [67–70] or by developing analytical models [71]. The pass/fail threshold value can be decided by simulation [72–74] or empirical analysis of data [75]. Transistor-level simulation of the circuit is performed for deciding the threshold through simulation. To account for vector-to-vector variation in  $I_{DDQ}$  that results from which paths are turned ON/OFF, simulation is carried out for different vectors and maximum  $I_{DDQ}$  is estimated. Empirical analysis involves plotting histograms of  $I_{DDQ}$  for chips from different wafers and lots. Faulty chips having high leakage current appear in the tail of the distribution. Typically, the threshold is decided by using a value a few standard deviations above the mean. Characterization data is used to estimate maximum fault-free leakage. A sample of chips may be examined to ensure outgoing defect level is within the acceptable limit. Research indicates that a majority of chips that fail only  $I_{DDQ}$  test contain defects that go undetected by other test methods [76].

The parametric measurement unit (PMU) is used to measure I<sub>DDQ</sub>. However, it is slow and often inflexible. Other methods for high-speed I<sub>DDQ</sub> measurement include use of load board sensors [77], QuiC-Mon [78][79], Built-In Current Sensors (BICS) [80] or other proprietary methods.

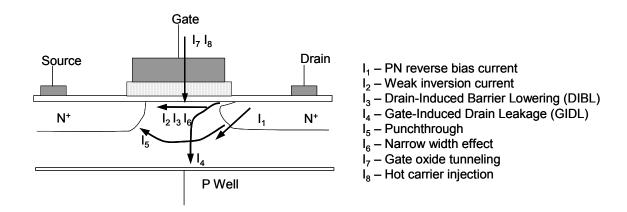

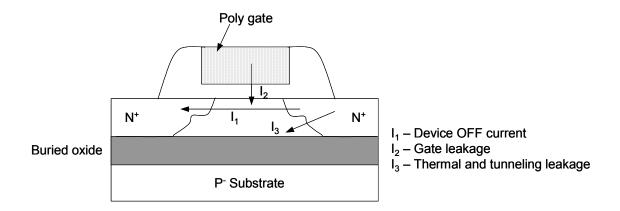

# 2.10 Components of I<sub>DDQ</sub>

Fig. 14 shows various components of the leakage current for DSM transistors as suggested by Keshavarzi et al. [81]. PN junction reverse bias current (I<sub>1</sub>) is the result of minority carrier diffusion/drift near the edge of the depletion region and due to electron-hole pair generation in the depletion region of the reverse bias junction. Weak inversion or sub-threshold leakage (I<sub>2</sub>) occurs when the gate voltage is below the threshold voltage and is the result of carrier movement along the channel surface. Drain-Induced Barrier Lowering or DIBL (I<sub>3</sub>) is due to the interaction

between the depletion region of the drain with the source that results in lower source potential barrier. Gate-Induced Drain Leakage or GIDL ( $I_4$ ) is the result of high electric field under the gate/drain overlap region that causes deep depletion and results in thin depletion width of the drain-to-well PN junction. Punchthrough ( $I_5$ ) occurs when the drain and source depletion regions electrically "touch" deep in the channel. This is a space-charge condition that causes the gate to lose control of the channel region. The narrow width effect ( $I_6$ ) is seen for transistor geometric gate widths of the order of  $\leq 0.5 \ \mu m$ . Gate oxide tunneling ( $I_7$ ) is the result of Fowler-Nordheim (FN) tunneling through the oxide. This becomes an important issue for very thin gate oxides. Hot carrier injection ( $I_8$ ) is due to injection of hot carriers into the oxide. This increases in amplitude as  $L_{eff}$  is reduced unless  $V_{DD}$  is scaled accordingly.

Fig. 14. Leakage current mechanisms for DSM transistors.

The dominating leakage current components for advanced bulk CMOS technologies include DIBL and sub-threshold weak inversion current. GIDL dominates for elevated voltages during BI. For higher reliability and lower power consumption, it is necessary to keep leakage current as low as possible. Leakage reduction, as will be explained later, helps I<sub>DDQ</sub> test to a certain extent, but does not completely solve the outlier identification issue.

# 2.11 Impact of Technology on I<sub>DDQ</sub> Test

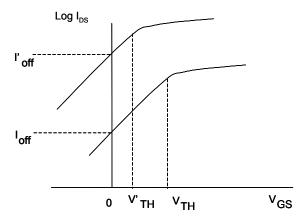

As transistor geometries are reduced, it is necessary to reduce the supply voltage to avoid electrical breakdown of the gate oxide. However, to retain or improve the performance it is necessary to reduce the threshold voltage  $(V_{TH})$  as well to maintain the gate overdrive. The sub-

threshold leakage current is given by

$$I_{sub} = \mu . C_{ox} . \frac{W}{L} V_t^2 e^{V_{GS} - V_{TH} / \eta V_t} . (1 - e^{-V_{DS} / V_t})$$

(2.3)

where  $\mu$  is the carrier mobility,  $C_{OX}$  is the gate capacitance per unit area, W is the channel width, L is the channel length,  $V_{GS}$  is the gate-to-source voltage,  $V_{TH}$  is the threshold voltage and  $\eta$  is the technology dependent parameter [82]. The thermal voltage  $V_t$  is given by kT/q where k is Boltzmann's constant, T is the absolute temperature and q is the electron charge  $(1.6 \times 10^{-19} \text{ C})$ . Thus, the reduction in threshold voltage  $(V_{TH})$  causes an exponential increase in the subthreshold leakage current [83] as illustrated in Fig. 15.

Fig. 15. Reduction in threshold voltage increases leakage current exponentially.

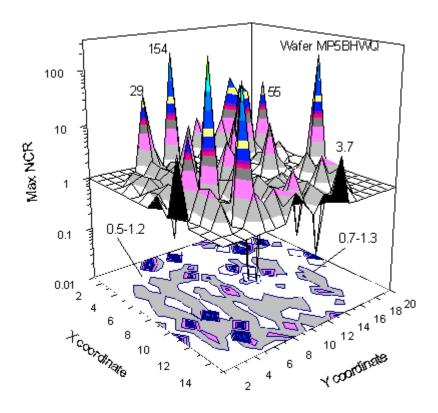

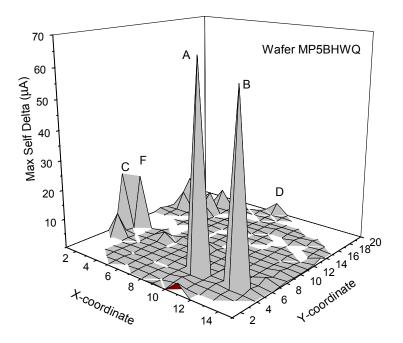

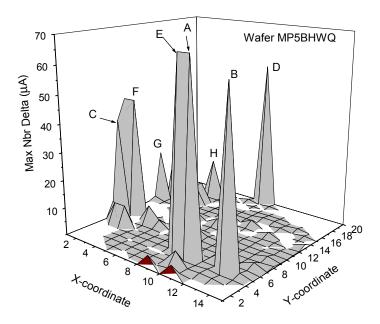

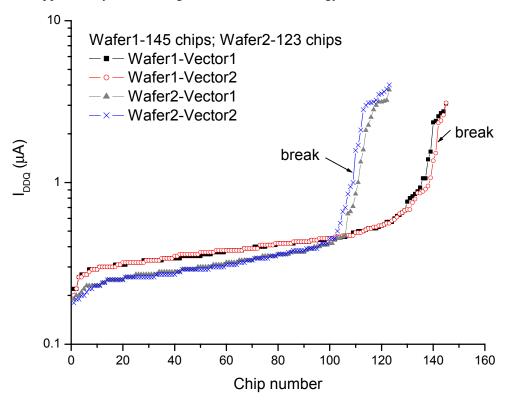

DSM technology chips are characterized by what is known as the *short channel effect* (SCE) [84]. As the distance between source and drain is reduced, the gate begins to lose control over the charge in the channel. Thus, even with no bias a large number of charge carriers are able to cross the channel resulting in appreciable leakage current. The International Technology Roadmap for Semiconductors (ITRS) projections for I<sub>DDQ</sub> of high-performance microprocessor circuits shown in Table I indicate that this trend will continue in the future due to pronounced SCE [2][85][86].