# IN SITU AUTOMATIC ANALOG CIRCUIT CALIBRATION AND OPTIMIZATION

# A Dissertation

by

# SANGHOON LEE

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Chair of Committee, Edgar Sánchez-Sinencio

Committee Members, Sebastian Hoyos

Jiang Hu

Erick Moreno-Centeno

Head of Department, Miroslav M. Begovic

December 2020

Major Subject: Electrical Engineering

Copyright 2020 Sanghoon Lee

#### **ABSTRACT**

As semiconductor technology scales down, the variations of active/passive device characteristics after fabrication are getting more and more significant. As a result, many circuits need more accuracy margin to meet minimum accuracy specifications over huge process-voltage-temperature (PVT) variations. Although, overdesigning a circuit is sometimes not a feasible option because of excessive accuracy margin that requires high power consumption and large area. Consequently, calibration/tuning circuits that can automatically detect and compensate the variations have been researched for analog circuits to make better trade-offs among accuracy, power consumption, and area.

The first part of this research shows that a newly proposed in situ calibration circuit for a current reference can relax the sharp trade-off between the temperature coefficient accuracy and the power consumption of the current reference. Prototype chips fabricated in a 180 nm CMOS technology generate 1 nA and achieve an average temperature coefficient of 289 ppm/°C and an average line sensitivity of 1.4 %/V with no help from a multiple-temperature trimming. Compared with other state-of-the-art current references that do not need a multiple-temperature trimming, the proposed circuit consumes at least 74% less power, while maintaining similar or higher accuracy.

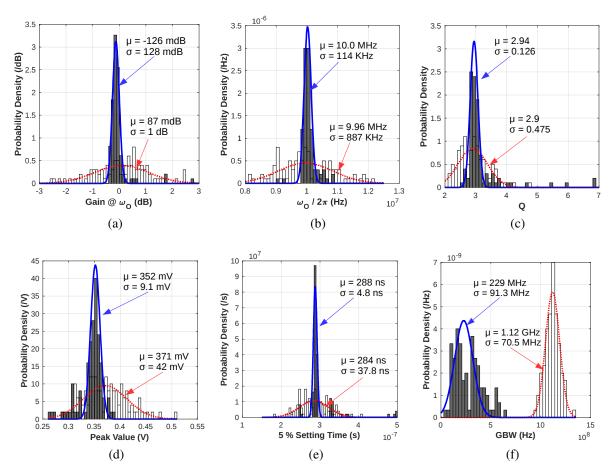

The second part of this research proves that a newly proposed multidimensional in situ analog circuit optimization platform can optimize a Tow-Thomas bandpass biquad. Unlike conventional calibration/tuning approaches, which only handle one or two frequency-domain characteristics, the proposed platform optimizes the power consumption, frequency-, and time-domain characteristics of the biquad to make a better trade-off between the accuracy and the power consumption of the biquad. Simulation results show that this platform reduces the gain-bandwidth product of opamps in the biquad by 80% while reducing the standard deviations of frequency- and time-domain characteristics by 82%. Measurement results of a prototype chip fabricated in a 180 nm CMOS technology also show that this platform can save maximum 71% of the power consumption of the biquad while the biquad maintains its frequency-domain characteristics: Q,  $\omega_O$ , and the gain at

$\omega_O$ .

# **DEDICATION**

To my parents, who have encouraged me in pursuing my dream since I was a kid.

To my wife, Narae Yoon, who is always next to me with love.

To my daughter, Julia Taehee Lee, who makes me smile.

#### **ACKNOWLEDGMENTS**

During the time I worked on my Ph.D. degree, I learned a lot more than I had expected thanks to my advisor, Dr. Edgar Sánchez-Sinencio, and my friends. Especially, Dr. Sánchez gave me an opportunity to have leadership in my research and taught me how to make an innovation with a strong initiative. Two projects I led were enjoyable journeys thanks to his support and patience. I believe that having a good attitude is as important as having an in-depth knowledge for my future career. Dr. Sánchez showed me what a good attitude is as a researcher and a teacher. I would like to appreciate it.

I also would like to thank my committee members: Dr. Sebastian Hoyos, Dr. Jiang Hu, and Dr. Erick Moreno-Centeno. Especially, Dr. Hu gave me many valuable comments while we were working together for an NSF project. In addition, I thank Ms. Ella Gallagher, who was always willing to help me with Dr. Sánchez.

Many people contributed to two projects in this dissertation. Stephen Heinrich-Barna and Keith Kunz initiated the current reference calibration project. Kyoohyun Noh thoroughly reviewed my manuscript for the current reference project. All circuit optimization team members (Congyin Shi, Jiafan Wang, Adriana Sanabria Borbon, and Hatem Osman) did not hesitate giving me good comments while we were working together as a team. Especially, Congyin Shi provided a die photograph and measurement results for our manuscript. I am grateful to all of them.

My life in College Station would have been less delightful without my good friends: Alfredo Costilla Reyes, Chulhyun Park, Haewoong Yang, Hyun-Myung Woo, Johan Estrada Lopez, Joseph Samy Riad, Kyoohyun Noh, Myung Seok Shim, Sangjin Han, Sangmin Kim, and Sungjoon Yoon. I will never forget the coffee chats and happy hours with you.

Last but not least, I would like to express my sincere gratitude to my family. From elementary school years to high school years, my parents gave me countless opportunities to learn more about science and engineering. Thanks to the support, my curiosity could grow, leading to my Ph.D. degree. My parents-in-law, who have a full amount of positive energy, always encouraged me with

the energy. My wife, Narae Yoon, was the biggest supporter of my Ph.D. degree. She is always in my heart. My precious daughter, Julia Taehee Lee, has been and always will be the joy of my life.

## CONTRIBUTORS AND FUNDING SOURCES

## **Contributors**

This work was supported by a dissertation committee consisting of Professors Dr. Edgar Sánchez-Sinencio, Dr. Sebastian Hoyos, and Dr. Jiang Hu of the Department of Electrical and Computer Engineering and Professor Dr. Erick Moreno-Centeno of the Department of Industrial and Systems Engineering.

Congyin Shi provided the die photograph and the silicon measurement results in Chapter 5. All other work conducted for the dissertation was completed by the student independently.

# **Funding Sources**

Graduate study was supported by multiple fellowships from Texas Instruments and Microtune. Research projects were funded in part by Texas Instruments, in part by Silicon Labs, in part by Qualcomm, and in part by NSF (CCF-1815583).

# NOMENCLATURE

%RMSE Percent Root-Mean-Square Error

ADC Analog-to-Digital Converter

ALU Arithmetic Logic Unit

ATE Automatic Test Equipment

BIST Built-In Self-Test

BJT Bipolar Junction Transistor

CTAT Complementary to Absolute Temperature

CUO Circuit Under Optimization

CUT Circuit Under Test

DNL Differential Nonlinearity

ESG Excitation Signal Generator

FPGA Field Programmable Gate Array

GA Genetic Algorithm

GBW Gain Bandwidth Product

HVRVT High-Voltage Regular-Threshold

IC Integrated Circuit

IDAC Current Digital-to-Analog Converter

INL Integral Non-Linearity

IoT Internet of Things

LSB Least Significant Bit

LTI Linear Time-Invariant

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MSB Most Significant Bit

MVT Medium-Threshold

NM Nelder-Mead Method

NMOS N-type Metal-Oxide-Semiconductor

ORA Output Response Analyzer

PDF Probability Density Function

PMOS P-type Metal-Oxide-Semiconductor

PS Pattern Search

PTAT Propotional To Absolute Temperature

PVT Process-Voltage-Temperature

RVT Regular-Threshold

SA Simulated Annealing

SNR Signal-to-Noise Ratio

SS Sensitivity Search

THD Total Harmonic Distortion

ZTC Zero Temperature Coefficient

# TABLE OF CONTENTS

|     |       |            | P                                                                 | age  |

|-----|-------|------------|-------------------------------------------------------------------|------|

| ΑĒ  | BSTR. | ACT        |                                                                   | ii   |

| DE  | EDICA | ATION      |                                                                   | iv   |

| Δ(  | 'KNO  | WI FDGM    | ENTS                                                              | v    |

|     |       |            |                                                                   |      |

| CC  | ONTR  | IBUTORS A  | AND FUNDING SOURCES                                               | vii  |

| NO  | OMEN  | ICLATURE   | <u> </u>                                                          | viii |

| TA  | BLE   | OF CONTE   | ENTS                                                              | X    |

| LIS | ST OF | F FIGURES  |                                                                   | xiii |

| LIS | ST OF | F TABLES.  |                                                                   | xv   |

| 1.  | INTI  | RODUCTIC   | DN                                                                | 1    |

| 2.  | A SU  | JRVEY ON   | CURRENT REFERENCE CIRCUITS                                        | 4    |

|     | 2.1   | Backgroun  | nd                                                                | 4    |

|     |       | _          | mperature-Dependent Physical Quantities                           |      |

|     |       |            | 70 Types of Computations to Get a Temperature-Independent Current | 5    |

|     | 2.2   |            | s of Current Reference Circuits                                   | 7    |

|     |       | • •        | V <sub>BE</sub> -based Current References                         |      |

|     |       | 2.2.2 Be   | ta-multiplier-based Current References                            | 10   |

|     |       | 2.2.3 Sm   | nartly Biased Current References                                  | 15   |

|     |       | 2.2.4 Dir  | vision-based Current References                                   | 16   |

|     | 2.3   | Performan  | ce Comparison Among Current Reference Types                       | 17   |

|     | 2.4   | Conclusion | n                                                                 | 19   |

| 3.  |       |            | W-POWER HIGH-ACCURACY CURRENT REFERENCE USING AU-                 | • •  |

|     | TOM   | IATIC CAL  | IBRATION                                                          | 20   |

|     | 3.1   | Motivation | 1                                                                 | 20   |

|     | 3.2   |            | evel Architecture                                                 | 21   |

|     | 3.3   | •          | Blocks                                                            | 24   |

|     |       | _          | akage-Based IDAC                                                  | 24   |

|     |       | 3.3.2 Cu   | rrent-to-Time Converters                                          | 26   |

|     |       | 3.3.3 Ot   | her Building Blocks                                               | 32   |

|    | 3.4  | Accuracy Analysis                                               | 32 |

|----|------|-----------------------------------------------------------------|----|

|    | 3.5  | Calibration Algorithm and Time Frame                            | 36 |

|    | 3.6  | Current-Providing Mechanism                                     | 39 |

|    | 3.7  | Measurement Results                                             | 40 |

|    |      | 3.7.1 Static Accuracy                                           | 40 |

|    |      | 3.7.2 Dynamic Accuracy                                          | 44 |

|    |      | 3.7.3 Power Consumption                                         | 48 |

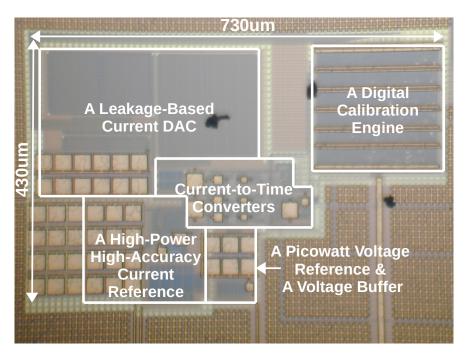

|    |      | 3.7.4 Die Photograph and Comparison Chart                       | 50 |

|    |      | 3.7.5 Range and One-Step Current Accuracy of IDAC               |    |

|    | 3.8  | Conclusion                                                      |    |

|    |      |                                                                 |    |

| 4. | A SU | URVEY ON IN SITU ANALOG CIRCUIT OPTIMIZATION                    | 53 |

|    | 4 1  | Desire Contains                                                 | 50 |

|    | 4.1  | Design Centering.                                               |    |

|    | 4.2  | Tuning/Calibration Methodologies and Their Limitations          |    |

|    | 4.3  | Motivation for In Situ Analog Circuit Optimization              |    |

|    | 4.4  | Previous Works on In Situ Analog Circuit Optimization           | 56 |

| 5. | ΛRI  | UILT-IN SELF-TEST AND IN SITU ANALOG CIRCUIT OPTIMIZATION PLAT- |    |

| ۶. |      |                                                                 | 58 |

|    | TON  |                                                                 | 50 |

|    | 5.1  | Introduction                                                    | 58 |

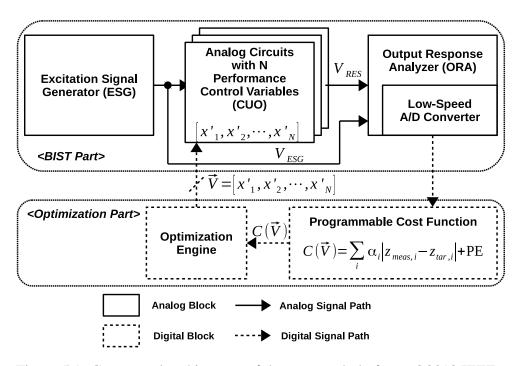

|    | 5.2  | The Proposed Platform Architecture                              |    |

|    |      | 5.2.1 Optimization With BIST                                    |    |

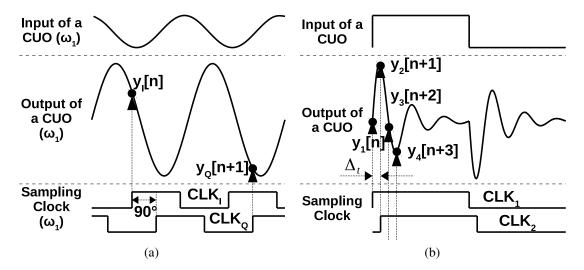

|    |      | 5.2.2 Frequency-Domain Characterization of a CUO                |    |

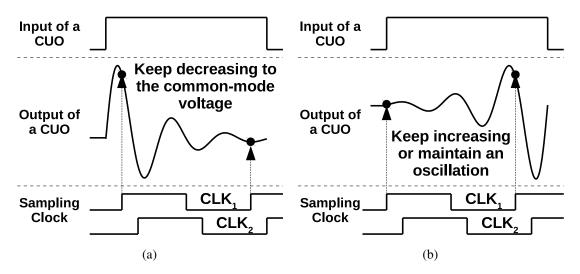

|    |      | 5.2.3 Time-Domain Characterization of a CUO                     |    |

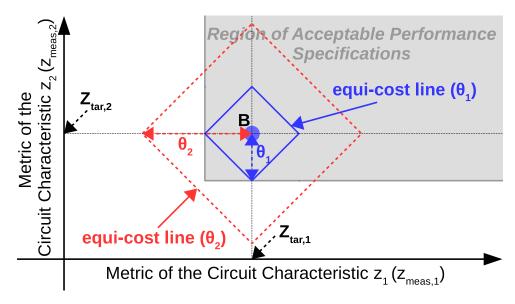

|    | 5.3  | Cost Function                                                   |    |

|    | 5.4  | Optimization Engine                                             |    |

|    | 5.5  | Analysis of Required Accuracies for Platform Building Blocks    |    |

|    |      | 5.5.1 Definitions                                               |    |

|    |      | 5.5.1.1 Control vector                                          |    |

|    |      | 5.5.1.2 Euclidean distance                                      |    |

|    |      | 5.5.1.3 Percent root-mean-square error (%RMSE)                  |    |

|    |      | 5.5.2 Design of the Cost Function                               |    |

|    |      | <u>e</u>                                                        | 75 |

|    |      | 5.5.4 Analysis of the Effect of Noise                           |    |

|    |      | 5.5.5 Analysis of Bit Widths for Digital Computation Blocks     |    |

|    |      |                                                                 | 86 |

|    | 5.6  |                                                                 | 87 |

|    | 5.0  | ·                                                               | 87 |

|    |      |                                                                 | 89 |

|    |      |                                                                 | 91 |

|    | 5.7  | č                                                               | 91 |

|    | 5.1  | Conclusion                                                      | 71 |

| ~  | CON  | ICITICION                                                       | 02 |

| REFERENCES |

|------------|

|------------|

# LIST OF FIGURES

| IGURE Pa                                                                                                             | age |

|----------------------------------------------------------------------------------------------------------------------|-----|

| 1.1 Design point with margins.                                                                                       | 2   |

| 1.2 New design point when a 1-dimension calibration/tuning or a N-dimension optimization is employed.                | 2   |

| 2.1 An example of $\Delta V_{\rm BE}$ -based current references                                                      | 7   |

| 2.2 $\Delta V_{\rm BE}$ -based current references that can provide a design flexibility                              | 9   |

| 2.3 An example of beta-multiplier-based current references                                                           | 11  |

| 2.4 An example of beta-multiplier-based current references that do not use a resistor                                | 12  |

| 2.5 An example of division-based current references                                                                  | 17  |

| 2.6 Performance of five current reference types.                                                                     | 18  |

| 3.1 Performance of various current references.                                                                       | 21  |

| 3.2 System-level architecture.                                                                                       | 22  |

| 3.3 Schematic of the leakage-based IDAC.                                                                             | 24  |

| 3.4 Current-to-time converter for <i>I</i> <sub>REF1</sub>                                                           | 27  |

| 3.5 Current-to-time converter for $I_{REF2}$ .                                                                       | 31  |

| 3.6 Operation of the automatic calibration.                                                                          | 37  |

| 3.7 Current-providing mechanism for always-on load circuits                                                          | 39  |

| 3.8 Effect of the automatic calibration on the generated reference current                                           | 41  |

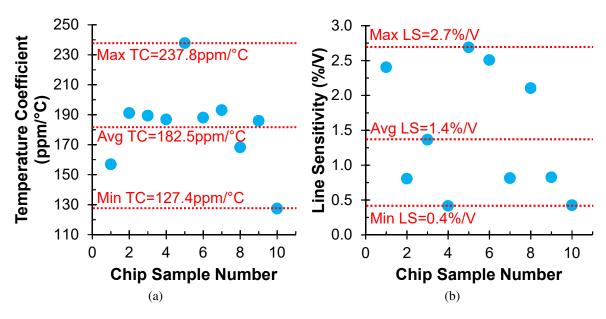

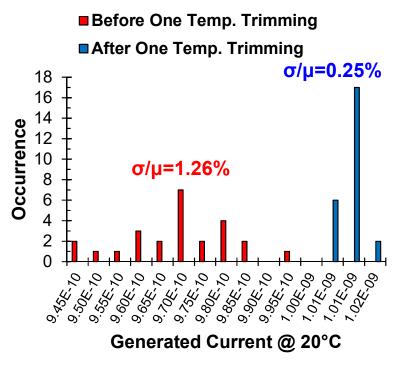

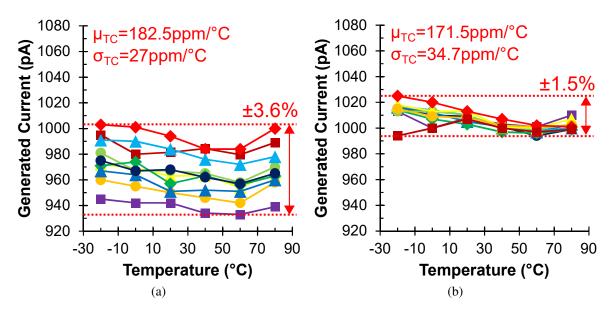

| 3.9 Accuracy of the generated reference current after the automatic calibration when <i>N</i> =86                    | 42  |

| 3.10 Auto-calibrated reference current spread of 25 sample chips at 20 °C before and after room-temperature trimming | 43  |

| 3.11 Auto-calibrated reference current before and after room-temperature trimming                                    | 44  |

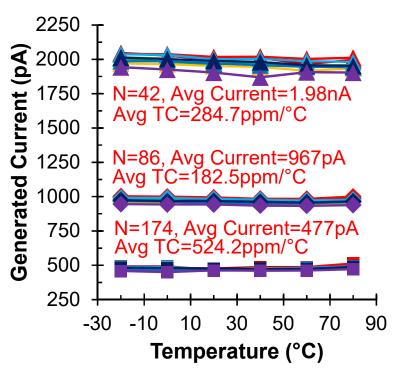

| 3.12 | Generated reference current for various <i>N</i>                                                                                                                                | 45 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

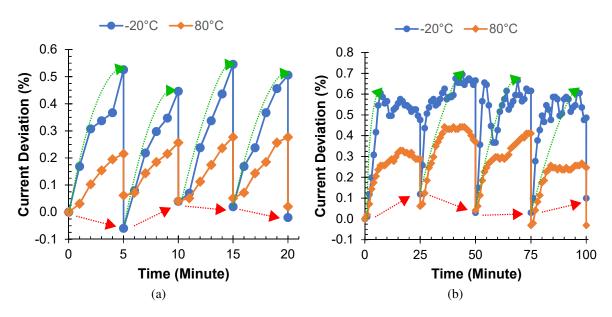

| 3.13 | Accuracy of the current reference when there are ambient temperature variations                                                                                                 | 46 |

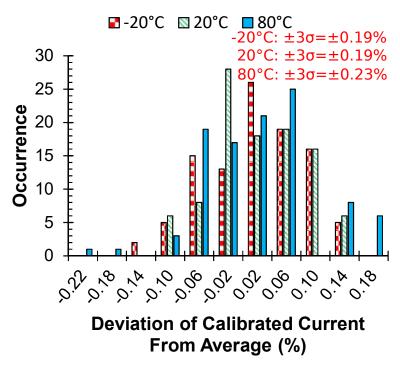

| 3.14 | Deviation of the reference currents generated by 101 calibration trials at three different temperatures.                                                                        | 47 |

| 3.15 | Die photograph.                                                                                                                                                                 | 50 |

| 4.1  | Comparison between a conventional 1-dimensional tuning/calibration and an N-dimensional optimization.                                                                           | 54 |

| 5.1  | Conceptual architecture of the proposed platform                                                                                                                                | 59 |

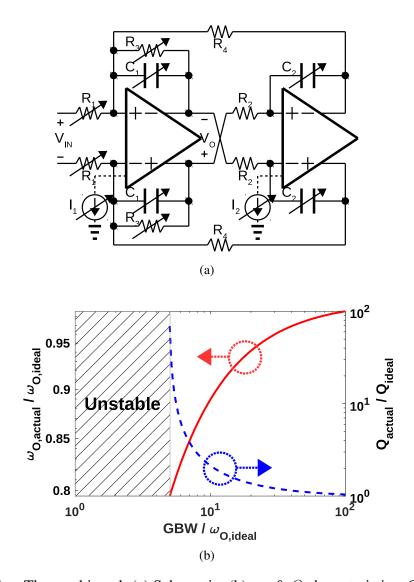

| 5.2  | Frequency- and time-domain characterizations                                                                                                                                    | 61 |

| 5.3  | Stability test.                                                                                                                                                                 | 62 |

| 5.4  | Magnified view around the design point $B$ in Fig. 4.1, and equi-cost lines when $M=2,\alpha_1=\alpha_2=1,$ and PE = 0 in (5.3)                                                 | 64 |

| 5.5  | Tow-Thomas biquad                                                                                                                                                               | 66 |

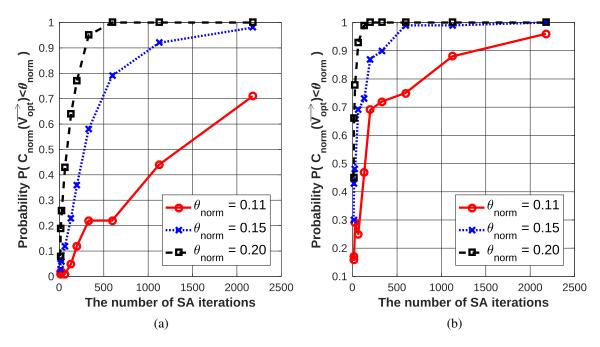

| 5.6  | Relation between the number of SA/SS iterations, the normalized cost criterion, and the probability of having a cost smaller than the criterion after the number of iterations. | 70 |

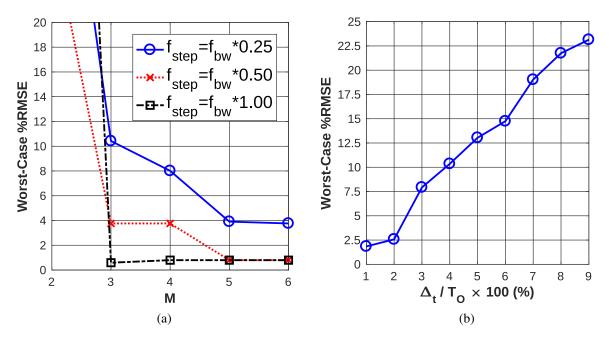

| 5.7  | Relation between the %RMSE and the design parameters of the cost functions                                                                                                      | 74 |

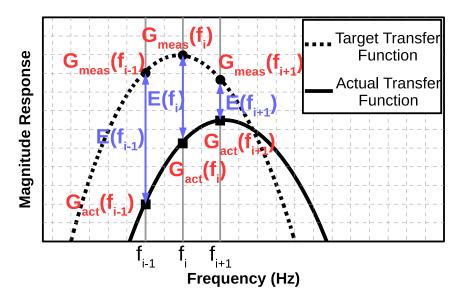

| 5.8  | Effect of distortions in the frequency-domain characterization.                                                                                                                 | 76 |

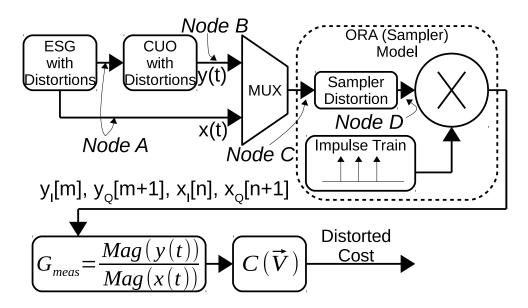

| 5.9  | Block diagram for the distortion analysis.                                                                                                                                      | 77 |

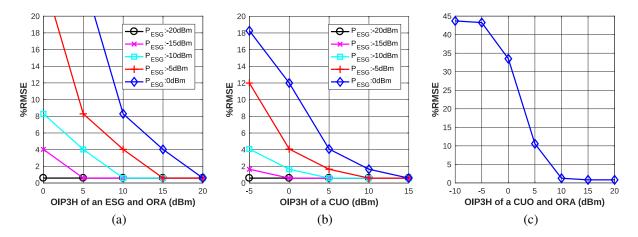

| 5.10 | Simulation results showing the relation between the %RMSE and OIP3H of each block.                                                                                              | 78 |

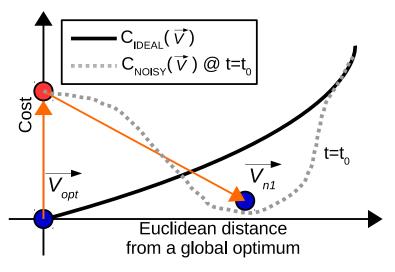

| 5.11 | Effect of noise in sensitivity-search optimization                                                                                                                              | 80 |

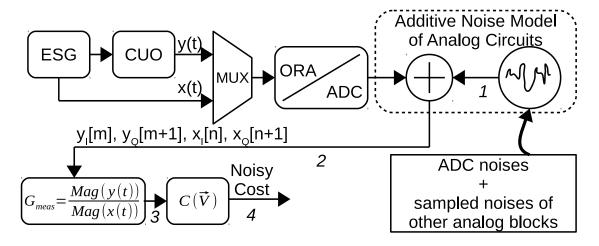

| 5.12 | Block diagram for the noise analysis                                                                                                                                            | 81 |

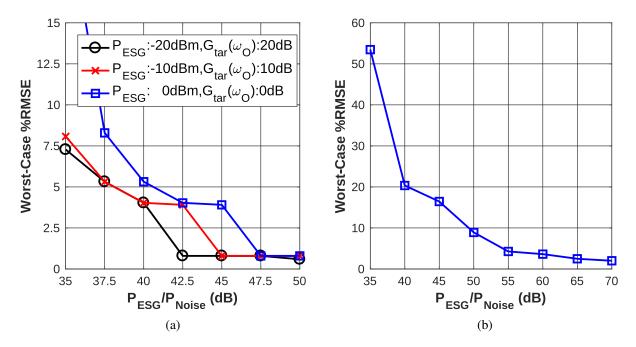

| 5.13 | Simulation results that represent the relation between the %RMSE and $P_{ESG}/P_{Noise}$ .                                                                                      | 82 |

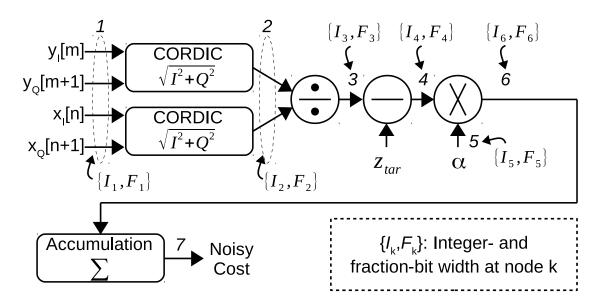

| 5.14 | Digital computation flow and bit width at each node                                                                                                                             | 84 |

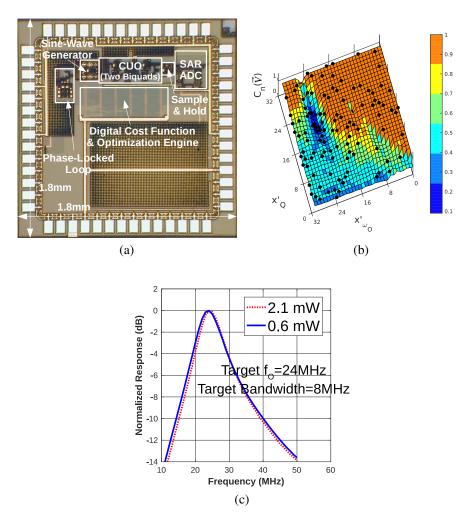

| 5.15 | Integrated circuit prototype and measurement results.                                                                                                                           | 89 |

| 5.16 | Reduction of power consumption and standard deviations of multiple characteristics of a biquad                                                                                  | 90 |

# LIST OF TABLES

| TABLE | P                                                                                  | age |

|-------|------------------------------------------------------------------------------------|-----|

| 3.1   | Ranges of Errors From the Circuit Nonidealities.                                   | 34  |

| 3.2   | Temperature Coefficient Ranges of the Circuit Nonidealities                        | 35  |

| 3.3   | Power Consumption of the Current Reference at Three Temperatures                   | 48  |

| 3.4   | Comparision Chart.                                                                 | 51  |

| 5.1   | Remarks and Simulation Results of the Bit-Width Analysis for Digital Computations. | 85  |

| 5.2   | Summary of Noise and Linearity Requirements                                        | 86  |

| 5.3   | Comparison of Tuning/Calibration Platforms That Utilize Optimization Algorithms.   | 91  |

#### 1. INTRODUCTION

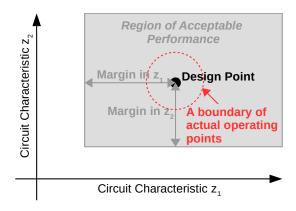

As semiconductor technology scales down, the variations of circuit characteristics are getting more and more significant [1,2]. To have both of a high yield and enough performance better than required specifications given by customers, the most intuitive approach is designing a circuit that has much better performance than the minimum requirement as Fig. 1.1 shows. In Fig. 1.1, larger  $z_1$  and  $z_2$  mean better performance. The location of an actual operating point of the designed circuit can be anywhere enclosed by the dotted line in Fig. 1.1 when there are process-voltage-temperature (PVT) variations. Since the design point has enough margins for  $z_1$  and  $z_2$  circuit characteristics, an actual operating point of the designed circuit can always be in the region of acceptable performance regardless of PVT variations. However, the overdesigned circuit normally requires sacrificing other circuit characteristics that are less important for a certain application. For example, the most important circuit characteristics of a high-precision voltage or current reference circuit are the temperature coefficient and the line sensitivity of the circuit. Consequently, a circuit designer sometimes sacrifices the area and the power consumption of the reference circuit to achieve a low temperature coefficient and a small line sensitivity regardless of PVT variations.

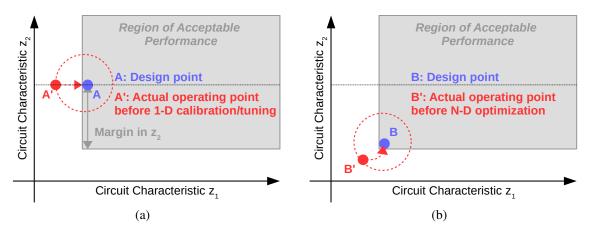

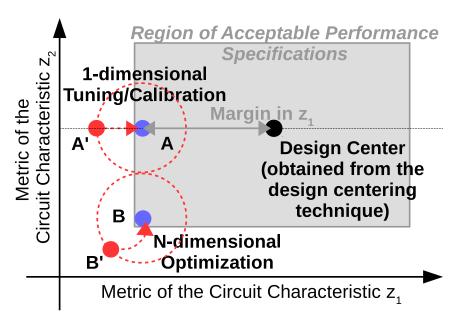

Since achieving excessive performance that has a huge margin is sometimes not feasible, many research have been conducted to make a better trade-off among circuit characteristics. One common approach for the purpose is utilizing an in situ automatic calibration/tuning circuit. Fig. 1.2(a) shows the benefit of the approach. When we place our design point at A, an actual operating point of the designed circuit (A') can be located outside of the region of acceptable performance due to PVT variations. However, the actual operating point can move to A thanks to the calibration/tuning circuit that evaluates the circuit characteristic  $z_1$  and compensates the difference between the required  $z_1$  value and the actual  $z_1$  value. Therefore, we do not need to excessively sacrifice other circuit characteristics that are less important for a certain application because the large margin for  $z_1$  is not needed anymore. This approach generally makes a better trade-off among circuit characteristics when the area and the power consumption overheads of the calibration/tuning circuit are

Figure 1.1: Design point with margins.

Figure 1.2: New design point when a 1-dimension calibration/tuning or a N-dimension optimization is employed. (a) 1-dimension calibration/tuning case. (b) N-dimension optimization case.

#### minimized.

Even though researchers have researched various calibration/tuning circuits for many analog circuits for a long time, the previous research have two limitations. First, there are still several analog circuits that have not been calibrated/tuned by an in situ automatic calibration/tuning circuit. For example, an in situ automatic calibration circuit for a current reference, to the best of the author's knowledge, has not been reported. Second, in many cases, calibration/tuning techniques that have been researched so far deal with only one circuit characteristic, leading to a suboptimal circuit. Fig. 1.2(a) shows the limitation clearly. The design point A still needs a large margin for

$z_2$  since the calibration/tuning circuit in the example only compensates the deviation of  $z_1$ . As a result, we still need to sacrifice less important circuit characteristics to some extent.

This dissertation investigates two approaches that overcome the aforementioned limitations. The first research [3] proposes an in situ automatic calibration circuit for an ultralow-power current reference. Since the calibration circuit detects a current generated from the ultralow-power current reference and compensates its deviations over PVT variations, the generated current can be accurate. The power consumption overhead of the calibration circuit is small because unnecessary circuits are powered off after each calibration. Therefore, the calibration circuit can relax the tight trade-off between the accuracy and the power consumption of the current reference.

The second research [4] proposes a built-in self-test and in situ analog circuit optimization platform. Since the platform optimizes multiple competing circuit characteristics simultaneously unlike conventional calibration/tuning circuits, margins for the multiple circuit characteristics can be greatly reduced. Consequently, a designer can choose the design point at the bottom left corner of the region of acceptable performance (*B*) in Fig. 1.2(b), resulting in a better trade-off among circuit characteristics. Turning on the platform only when it is needed can relax the power consumption overhead of the platform. We can mitigate the area overhead as well by utilizing the platform for multiple linear time-invariant (LTI) analog circuits on the same chip.

The rest of this dissertation is structured as follows. Chapter 2 introduces previous research on current reference circuits. Chapter 3 discusses the newly proposed in situ automatic calibration circuit for a current reference in detail. Previous research on in situ analog circuit optimization are summarized in Chapter 4. Chapter 5 elaborates the newly proposed built-in self-test and in situ analog circuit optimization platform. Finally, future works are discussed in Chapter 6.

#### 2. A SURVEY ON CURRENT REFERENCE CIRCUITS

# 2.1 Background

## 2.1.1 Temperature-Dependent Physical Quantities

Since current generated from a current reference circuit is a function of physical quantities, understanding the temperature dependence of the physical quantities is essential to evaluate the temperature dependence of the generated current. There are five physical quantities that are widely used in current reference circuits to generate a stable current: the thermal voltage  $(V_T)$ , the base-emitter voltage of a bipolar junction transistor  $(V_{BE})$ , the threshold voltage of a metal-oxide-semiconductor field-effect transistor  $(V_{TH})$ , the electron/hole mobility  $(\mu)$ , and the resistances of various resistors (R).

At room temperature, the thermal voltage, which equals to kT/q, is approximately 26 mV. The following equation shows the temperature coefficient of  $V_T$ .

$$V_{T,TC} = \frac{1}{V_T} \frac{\partial V_T}{\partial T} = \frac{1}{T}.$$

(2.1)

As (2.1) shows, the thermal voltage is a proportional-to-absolute-temperature (PTAT) quantity and has a temperature coefficient of 3333 ppm/°C at room temperature.

According to [5], the temperature variation of  $V_{\rm BE}$  is given by

$$\frac{\partial V_{BE}}{\partial T} = \frac{V_{BE} - 2.5V_T - 1.12}{T}.$$

(2.2)

When  $V_{BE}$  equals to 600 mV, the temperature variation of  $V_{BE}$  is -2 mV/°C at room temperature, leading to a temperature coefficient of -3333 ppm/°C. Note that  $V_{BE}$  cannot be arbitrary small. If  $V_{BE}$  equals to 170 mV, the temperature variation of  $V_{BE}$  is -3.38 mV/°C at room temperature. If we ignore the temperature dependency of the temperature variation,  $V_{BE}$  will be close to 0 mV at 77 °C, which is not acceptable for many circuits.

The temperature variation of  $V_{\rm TH}$  is also approximately -2 mV/°C [6]. Consequently, the temperature coefficient of  $V_{\rm TH}$  is -6667 ppm/°C when  $V_{\rm TH}$  equals to 300 mV at room temperature.

The temperature dependency of the electron/hole mobility can be expressed as

$$\mu = \mu_0 (T_0 / T)^n. \tag{2.3}$$

In (2.3),  $T_0$  is a reference temperature, and  $\mu_0$  is the mobility at the reference temperature, and n equals to 1.5. The temperature coefficient of the mobility can be written as

$$\mu_{TC} = -1.5/T. \tag{2.4}$$

As a result,  $\mu_{TC}$  is -5000 ppm/°C at room temperature.

The temperature coefficient of the resistance of a resistor can be positive or negative depending on the type of the resistor. The temperature coefficient also depends on a process technology. In many cases, a resistor has a temperature coefficient of several hundreds or thousands ppm/°C.

#### 2.1.2 Two Types of Computations to Get a Temperature-Independent Current

The physical quantities discussed in Section 2.1.1 have temperature coefficients much higher than 100 ppm/°C. Accordingly, it is hard to generate a stable current that has a temperature coefficient comparable to 100 ppm/°C by relying on only one physical quantity. More viable way is utilizing multiple physical quantities and allowing their temperature coefficients to cancel each other.

Two types of computations can cancel the temperature coefficients of physical quantities. The first type is addition/subtraction. If we assume that there are two physical quantities, A and B, then the generated current (*I*) from a current reference circuit can be

$$I = c_1 A \pm c_2 B. \tag{2.5}$$

In (2.5),  $c_1$  and  $c_2$  are temperature-independent constants. The temperature coefficient of I is given

by

$$I_{TC} = \frac{1}{I} \frac{\partial I}{\partial T} = \frac{c_1 A}{c_1 A \pm c_2 B} A_{TC} \pm \frac{c_2 B}{c_1 A \pm c_2 B} B_{TC}.$$

(2.6)

Here  $A_{TC}$  and  $B_{TC}$  are the temperature coefficients of A and B, respectively. As (2.6) shows,  $I_{TC}$  can be zero when we select an appropriate ratio between  $c_1A$  and  $c_2B$ . However,  $I_{TC}$  in (2.6) can be sensitive over process variation when  $c_1A$  and  $c_2B$  do not have a correlation over the process variation, which is generally true for many circuits. Consequently, a multiple temperature trimming is required to obtain a small  $I_{TC}$  over process variation even when  $A_{TC}$  and  $B_{TC}$  are less sensitive for the process variation.

The second type of computation to cancel the temperature coefficients of physical quantities is multiplication/division. When we use a multiplication, I can be expressed as

$$I = cAB, (2.7)$$

where c is a temperature-independent constant. (2.7) results in

$$I_{TC} = A_{TC} + B_{TC}.$$

(2.8)

On the contrary, a division (I = cA/B) leads to

$$I_{TC} = A_{TC} - B_{TC}. (2.9)$$

(2.8) and (2.9) show that  $I_{TC}$  can be zero when the absolute values of  $A_{TC}$  and  $B_{TC}$  are the same. If  $A_{TC}$  and  $B_{TC}$  are less sensitive over process variation, we can obtain a stable  $I_{TC}$  with no help from a multiple temperature trimming. However, when  $A_{TC}$  is different from  $B_{TC}$ , there is no design flexibility to compensate the difference because c cannot make any change for  $I_{TC}$ .

In summary, the two types of computations show the trade-off between design flexibility and robustness. Although an addition/subtraction gives us a design flexibility to make  $I_{\rm TC}$  small,  $I_{\rm TC}$  is less robust over process variation. A multiplication/subtraction can guarantee a stable  $I_{\rm TC}$  while it

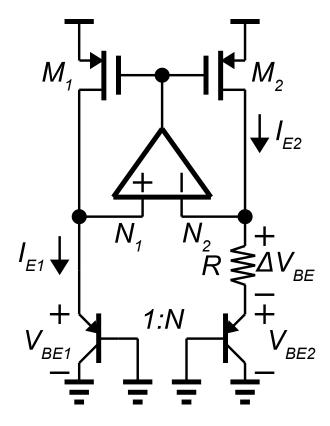

Figure 2.1: An example of  $\Delta V_{\rm BE}$ -based current references.

provides less design freedom.

# 2.2 Four Types of Current Reference Circuits

# 2.2.1 $\Delta V_{\mathrm{BE}}$ -based Current References

One of the conventional approaches to generate a stable current is utilizing the difference between two  $V_{\rm BE}$  as Fig. 2.1 shows [7]. The collector current of a bipolar junction transistor ( $I_{\rm C}$ ) is

$$I_C = I_S e^{V_{BE}/V_T}. (2.10)$$

Thus,

$$V_{BE} = V_T \ln \left( I_C / I_S \right). \tag{2.11}$$

When we assume that the base current of each bipolar junction transistor (BJT) is negligible,  $V_{\rm BEI}$  in Fig. 2.1 is

$$V_{BE1} = V_T \ln \left( I_{E1} / I_S \right). \tag{2.12}$$

Here,  $I_{E1}$  is the emitter current of the left BJT. Since the emitter area of the right BJT is N times larger than that of the left BJT,  $V_{BE2}$  is

$$V_{BE2} = V_T \ln \left( I_{E2} / (NI_S) \right). \tag{2.13}$$

If we assume that there is no mismatch between  $M_1$  and  $M_2$ ,  $I_{E1}$  equals to  $I_{E2}$ , considering that the op-amp  $(A_1)$  matches the voltage of node  $N_1$  with the voltage of  $N_2$ . Consequently, the voltage difference between the two terminals of the resistor is

$$\Delta V_{BE} = V_T \ln N. \tag{2.14}$$

Therefore, the current flowing through the resistor is

$$I = \frac{V_T \ln N}{R}.\tag{2.15}$$

The temperature coefficient of I is

$$I_{TC} = V_{T,TC} - R_{TC}. (2.16)$$

Even though a designer can choose a resistor that has a temperature coefficient close to  $V_{T,TC}$ , the circuit in Fig. 2.1 cannot provide a design flexibility to make  $I_{TC}$  zero. This is a natural consequence because (2.15) uses a division.

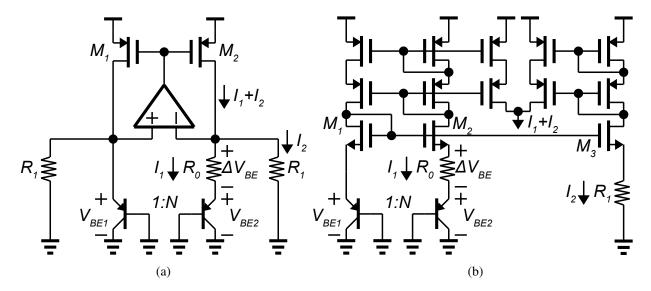

Modified versions of the circuit in Fig. 2.1 have been proposed to provide more design freedom [8–10]. Fig. 2.2(a) and Fig. 2.2(b) show the circuits proposed in [8] and [9], respectively. In

Figure 2.2:  $\Delta V_{\rm BE}$ -based current references that can provide a design flexibility. (a) utilizes an op-amp to generate  $\Delta V_{\rm BE}$ , whereas (b) uses a self-biased current mirror for the same purpose.

Fig. 2.2(a), the generated current is

$$I = I_1 + I_2 = \frac{V_T \ln N}{R_0} + \frac{V_{BE1}}{R_1}.$$

(2.17)

Thus,  $I_{TC}$  is

$$I_{TC} = \frac{I_1}{I_1 + I_2} I_{1,TC} + \frac{I_2}{I_1 + I_2} I_{2,TC}$$

$$= \frac{I_1}{I_1 + I_2} (V_{T,TC} - R_{0,TC}) + \frac{I_2}{I_1 + I_2} (V_{BE1,TC} - R_{1,TC}). \tag{2.18}$$

$I_{\rm TC}$  can be zero only when  $I_{\rm 1,TC}$  and  $I_{\rm 2,TC}$  have opposite polarities. At a certain temperature, we can choose an appropriate ratio between  $I_{\rm 1}$  and  $I_{\rm 2}$  by using design parameters  $(N, R_0, \text{ and } R_1)$  to obtain zero  $I_{\rm TC}$ . However, the ratio cannot be maintained for a wide temperature range because of the opposite polarities of  $I_{\rm 1,TC}$  and  $I_{\rm 2,TC}$ . As a result,  $I_{\rm TC}$  can be zero only at a specific temperature. In addition, the ratio cannot be maintained over process variation as well due to the fact that  $\Delta V_{\rm BE}$  is not sensitive over process variation unlike  $V_{\rm BE}$ . Therefore, process variation can significantly

change both of I and  $I_{TC}$ .

The circuit in Fig. 2.2(b) has the same design equation with the circuit in Fig. 2.2(a). Accordingly, the circuit has the same limitations we discussed in the previous paragraph. The difference between the two circuits comes from the two circuit implementations of the same design equation. The circuit in Fig. 2.2(b) utilizes a self-biased current mirror instead of an op-amp to generate  $\Delta V_{\rm BE}$ , resulting in the reduced power consumption of the circuit. In addition,  $M_2$  and  $M_3$  generate  $I_2$  in (2.17) by assigning  $V_{\rm BE}$  to  $R_1$ .

$\Delta V_{\rm BE}$ -based current references are not widely used for generating a current smaller than 1  $\mu$ A because of two reasons. First, as discussed in Section 2.1.1,  $V_{\rm BE}$  should be higher than 170 mV at room temperature. This means that  $R_1$  in Fig. 2.2(a) and Fig. 2.2(b) should be larger than 170 M $\Omega$  to generate a current smaller than 1 nA, leading to an excessively large area. Second,  $V_{\rm BE,TC}$  is large and sensitive to  $V_{\rm BE}$  variation when  $V_{\rm BE}$  is small as (2.2) shows. Due to the large  $V_{\rm BE,TC}$ ,  $I_2$  in (2.18) should be much smaller than  $I_1$ , resulting in an even larger  $R_1$ .

Note that when  $I_C$  is small, the ratio between  $I_C$  and  $I_B$  ( $\beta_F$ ) is not constant anymore and decreases significantly [6]. Accordingly, we cannot approximate  $I_E$  to  $I_C$ , and the temperature variation of  $\beta_F$  should be considered in (2.16) and (2.18).

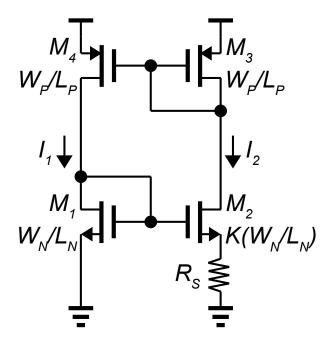

#### 2.2.2 Beta-multiplier-based Current References

Another type of conventional current references is based on a beta multiplier. Fig. 2.3 shows one of beta-multiplier-based current references. When the circuit starts its operation, the source voltage of  $M_2$  is close to 0 V. Consequently, the drain current ratio between  $M_2$  and  $M_1$  is approximately K. Since the current mirror that consists of  $M_3$  and  $M_4$  matches  $I_1$  with  $I_2$ , the drain currents of  $M_1$  and  $M_2$  keep increasing until the source voltage of  $M_2$  reaches the voltage that sets the drain current ratio between  $M_1$  and  $M_2$  as 1. At the operating point,  $I_1$  equals to  $I_2$ .

When all MOSFETs are in the saturation region,  $I_1$  and  $I_2$  can be expressed as below.

$$I = I_1 = I_2 = \frac{2}{\mu_n C_{ox} W_N / L_N} \frac{1}{R_S^2} \left( 1 - \frac{1}{\sqrt{K}} \right). \tag{2.19}$$

Figure 2.3: An example of beta-multiplier-based current references.

Thus,  $I_{TC}$  is

$$I_{TC} = -\mu_{n,TC} - 2R_{S,TC}. (2.20)$$

(2.19) and (2.20) show two limitations of the circuit in Fig. 2.3. First, the circuit is not appropriate for generating a nA-range current. Let  $K' = 1 - 1/\sqrt{K}$ . Since  $\mu_n C_{ox} W_N/L_N = 2I/V_{OV1}^2$ , we can rewrite (2.19) as

$$R_S = \frac{V_{OV1}}{I} \sqrt{K'}.$$

(2.21)

Here,  $V_{\rm OV1}$  means the overdrive voltage of  $M_1$ . When  $V_{\rm OV1}$  equals to 100 mV, K equals to 2, and I equals to 1 nA,  $R_{\rm S}$  will be 54 M $\Omega$ , which takes a huge area. Additionally, channel lengths of  $M_1 \sim M_4$  should be long enough to guarantee that all MOSFETS are in the saturation region while generating a nA-range current, resulting in a large area as well. The second limitation is that there is no design flexibility that can set  $I_{\rm TC}$  as zero. This is because  $\mu_{\rm n}$  and  $R_{\rm S}$  are multiplied in (2.19).

Various circuits have been proposed to overcome the first limitation by improving the circuit shown in Fig. 2.3 [11–13]. Instead of using  $R_S$ , [11] utilizes a PTAT floating voltage source inserted between the gates of  $M_1$  and  $M_2$  as Fig. 2.4(a) shows. In Fig. 2.4(a), if we assume that there is no

Figure 2.4: An example of beta-multiplier-based current references that do not use a resistor. (a) Schematic of the current reference. (b) Schematic of the PTAT voltage source.

threshold voltage mismatch between  $M_1$  and  $M_2$ ,  $I_2$  is

$$I_2 = \mu_n C_{ox} K_1 \frac{W_N}{L_N} \frac{V_{PTAT}^2}{(1 - \sqrt{m})^2},$$

(2.22)

where m equals to  $K_1K_2$ , and  $V_{PTAT}$  is the voltage of the PTAT voltage source. Since  $I_2$  is proportional to  $V_{PTAT}^2$ , a small  $V_{PTAT}$  results in a small  $I_2$  while all MOSFETs in Fig. 2.4(a) are in the saturation region. Fig. 2.4(b) represents the circuit implementation of the PTAT floating voltage source. The following equation relates the input voltage  $(V_I)$  and the output voltage  $(V_O)$  of the floating voltage source by assuming that the MOSFETs in Fig. 2.4(b) are in the subthreshold region.

$$V_O = V_I + nV_T ln(\frac{W_6/L_6}{W_5/L_5}). (2.23)$$

Consequently,

$$V_{PTAT} = nV_T ln(\frac{W_6/L_6}{W_5/L_5}). (2.24)$$

From (2.22) and (2.24),  $I_{2,TC}$  is

$$I_{2,TC} = \mu_{n,TC} + 2V_{T,TC}. (2.25)$$

Even though the circuit in Fig. 2.4 can generate a nA-range current while consuming small area, it still does not have a design flexibility for  $I_{2,TC}$ .

Unlike [11], [12] employs a high-voltage MOSFET to remove  $R_S$ . On the other hand, [13] uses two different body biases for a current mirror in a beta multiplier for the same purpose with [12]. Since the circuits proposed in [12] and [13] generate a  $\mu$ A-range current, it is hard to justify that the circuits are better than the circuit in Fig. 2.3.

Circuits proposed in [14, 15] improve the design freedom of the circuit in Fig. 2.3 to obtain the better temperature coefficient of the generated current. [14] replaces  $R_S$  with a linear-region MOSFET and assigns a PTAT voltage to the drain of the linear-region MOSFET. Since a bandgap voltage reference generates the PTAT voltage, the temperature coefficient of the PTAT voltage can be designed to minimize the temperature coefficient of the generated current. [15] improves the design flexibility by adding one more diode-connected MOSFET to the source of  $M_1$  in Fig. 2.3. Unfortunately, both of [14] and [15] do not provide measurement results.

If  $M_1$  and  $M_2$  in Fig. 2.3 are in the subthreshold region and if we ignore nonideal effects such as the finite resistance seen at the drain, the drain-induced barrier lowering, and the body effect of the MOSFETs, the generated current is given by

$$I = I_1 = I_2 = \frac{nV_T ln(K)}{R_S},$$

(2.26)

where n is the slope factor. Thus,

$$I_{TC} = V_{T,TC} - R_{S,TC}.$$

(2.27)

The numerator in (2.26) is 27 mV at room temperature when n and K equal to 1.5 and 2, respectively. As a result, to generate a 1 nA current,  $R_S$  should be 27 M $\Omega$ , which is 50% smaller than the resistance calculated from (2.21). However, when  $M_1$  and  $M_2$  are in the subthreshold region, the beta multiplier is more sensitive to mismatch variations. If we assume that there is a threshold voltage mismatch between  $M_1$  and  $M_2$  ( $\Delta V_{TH}$ ), (2.26) can be rewritten as

$$I = \frac{\Delta V_{TH} + nV_T ln(K)}{R_S}. (2.28)$$

If  $nV_Tln(K)$  is 27 mV,  $\Delta V_{TH}$  and  $nV_Tln(K)$  can be comparable, resulting in decreased accuracy for I and  $I_{TC}$ . On the other hand, when  $M_1$  and  $M_2$  are in the saturation region,  $\Delta V_{TH}$  can be negligible if  $\Delta V_{TH}$  is much smaller than  $V_{GS2}$ , which is generally true since  $M_2$  is in the saturation region. Therefore, in many cases,  $nV_Tln(K)$  in (2.28) should be as large as 100 mV as [16] shows, leading to an excessively large area for  $R_S$ .

[17–22] replace  $R_S$  with a MOSFET in the triode or the saturation region. The currents generated from the circuits in [17, 19–21] all have the following relation.

$$I \propto \mu V_T^2. \tag{2.29}$$

Thus,

$$I_{TC} = \mu_{TC} + 2V_{TTC}. (2.30)$$

Since (2.30) does not have any design freedom, [22] exploits a threshold voltage difference between two transistors that have different sizes to add more design freedom in (2.30). However, if the threshold voltage difference (17 mV) is comparable to the mismatch variations of the threshold voltages, the temperature coefficient of the generated current from the circuit proposed in [22] can be several hundreds ppm/°C as the measurement results in [22] show.

## 2.2.3 Smartly Biased Current References

When a MOSFET is in the saturation region, there is a  $V_{\rm GS}$  bias voltage that sets the temperature coefficient of the MOSFET drain current as zero [23]. The bias voltage is called "zero temperature coefficient (ZTC) bias voltage" and can be derived from the square law shown below.

$$I = \frac{1}{2}\mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{TH} \right)^2. \tag{2.31}$$

The temperature coefficient of I is

$$I_{TC} = \mu_{TC} - \frac{2V_{TH}}{V_{GS} - V_{TH}} V_{TH,TC}.$$

(2.32)

Since  $\mu_{TC}$  and  $V_{TH,TC}$  are negative values,  $I_{TC}$  can be zero when the following equation holds.

$$V_{GS} = \left(\frac{2V_{TH,TC}}{\mu_{TC}} + 1\right)V_{TH}.$$

(2.33)

When  $V_{\rm TH}$  is given by

$$V_{TH} = V_{TH0} - \gamma T, \tag{2.34}$$

the temperature coefficient of  $V_{\rm TH}$  is

$$V_{TH,TC} = \frac{-\gamma}{V_{TH}}. (2.35)$$

From (2.4), (2.34), and (2.35), we have

$$V_{GS} = V_{TH0} + \frac{1}{3}\gamma T. {(2.36)}$$

As (2.36) shows, ideally  $V_{\rm GS}$  should be a PTAT voltage to set  $I_{\rm TC}$  as zero at all temperature. Smartly biased current references generate the ZTC bias voltage and assign the bias voltage to an NMOS or a PMOS current generator. [24] utilizes a bandgap voltage reference to generate a ZTC voltage.

On the other hand, [25] uses a nanowatt PTAT voltage generator for the same purpose.

One drawback of this approach is that ZTC bias voltages are sensitive to process variation. In other words, the generated  $V_{\rm GS}$  should have the same process variation with  $V_{\rm TH}$  as (2.33) shows. [25] proposes an all-PMOS PTAT voltage generator to generate a ZTC bias voltage that tracks the  $V_{\rm TH}$  variation of a PMOS current generator. [26] utilizes a threshold voltage monitoring circuit that outputs  $V_{\rm TH0}$  of a MOSFET as a ZTC bias voltage generator. If the threshold voltage of a current generator is the same with the threshold voltage of a MOSFET monitored, the current generator can always have an appropriate bias voltage regardless of process variation.

The other drawback of this approach is that a MOSFET that is biased to generate a stable current should be in the saturation region. As a result, generating a current smaller than 1 nA is challenging when we consider the following equation.

$$V_{OV} = V_{GS} - V_{TH} = \sqrt{\frac{2I}{\mu C_{OX} W/L}}.$$

(2.37)

As (2.37) shows, W/L for generating 1 nA should be 1000 times smaller than W/L for 1  $\mu$ A when both cases have the same  $V_{\rm OV}$ . To avoid this issue, the circuit proposed in [27] uses a subthreshold MOSFET as a current generator and produces a gate bias voltage for the current generator. Even though the circuit generates a pA-range current with a small area, it has relatively low accuracy because of the exponential relationship between  $V_{\rm GS}$  and the generated current.

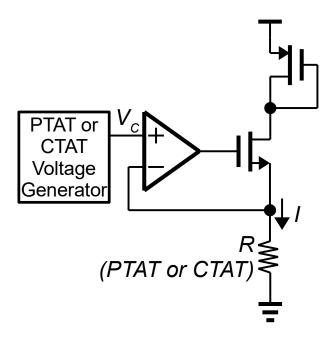

#### 2.2.4 Division-based Current References

Division-based current references generate a stable current by assigning a voltage to a resistor. Fig. 2.5 shows one example of division-based current references [28, 29]. [28] utilizes a PTAT voltage generator that consists of four subthreshold MOSFETs to generate  $V_{\rm C}$ . On the other hand, [29] uses floating gates to generate a temperature-independent  $V_{\rm C}$  and a temperature-insensitive resistance for R in Fig. 2.5. I can be written as

$$I = \frac{V_C}{R}. (2.38)$$

Figure 2.5: An example of division-based current references.

Thus,

$$I_{TC} = V_{C,TC} - R_{TC}. (2.39)$$

Even though (2.38) includes only a division, division-based current references have enough design freedom because a designer can choose  $V_{C,TC}$  while designing the compensation voltage generator in Fig. 2.5. One drawback of the circuits in [28,29] is that R should be very large when the circuits generate a small current. For example, if  $V_C$  is 100 mV, R should be 100 M $\Omega$  to generate 1 nA, resulting in an excessively large area.

The circuit proposed in [30] reduces R to minimize the area of the circuit by generating a small temperature-independent voltage. Since  $V_{C,TC}$  is close to zero,  $I_{TC}$  cannot be zero anymore. [31,32] utilize MOSFET gate leakages to obtain large resistance with small area.

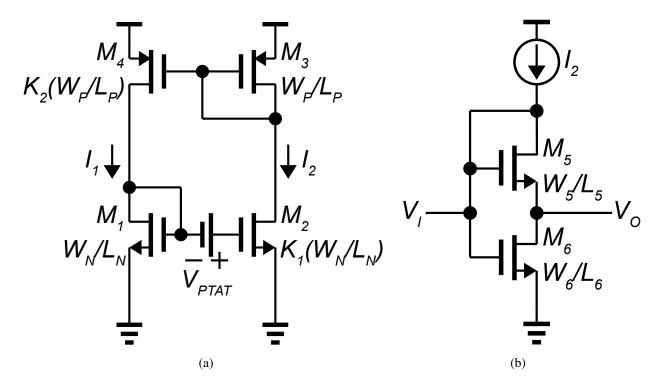

# 2.3 Performance Comparison Among Current Reference Types

Fig. 2.6 shows the measured performance of various current references and their types. In Fig. 2.6, " $\Delta$ VBE" means  $\Delta V_{BE}$ -based current references. "BM-Sat" and "BM-Sub" indicate beta-multiplier-based current references in the saturation region and in the subthreshold region, respec-

Figure 2.6: Performance of five current reference types. (a) Generated reference current versus total power consumption. (b) Generated reference current versus temperature coefficient.

tively. "SB" and "Div" stand for smartly biased current references and division-based current references, respectively. Note that the number of current references shown in Fig. 2.6(a) is smaller than the number of current references shown in Fig. 2.6(b). The reason for the difference is that some articles do not report the power consumption of the current reference each article proposes.

The  $\Delta V_{\rm BE}$ -based current references and the beta-multiplier-based current references in the saturation region generate currents comparable to or higher than 1  $\mu$ A. On the other hand, the beta-multiplier-based current references in the subthreshold region, the smartly biased current ref-

erences, and the division-based current references can generate nA-range or pA-range currents. Especially, the smartly biased current references and the division-based current references have better temperature coefficient than others in many cases as Fig. 2.6(b) shows when we compare the references with other types of current references that provide comparable amounts of current. In addition, if a current reference provides a small amount of current, the reference tends to consume less power as Fig. 2.6(a) indicates. Therefore, circuit techniques that utilize smart biasing or division are better choices than others to generate a small and accurate current over temperature variations with low power consumption.

#### 2.4 Conclusion

This chapter categorizes current reference circuits into four types and discusses the characteristics of each type. This chapter also summarizes recent research on each type of current references and shows a research trend. Smart biasing circuit techniques and division-based circuit techniques are more promising than other circuit techniques since the two techniques can generate a smaller and more accurate current over temperature variations with lower power consumption than others.

# 3. AN ULTRALOW-POWER HIGH-ACCURACY CURRENT REFERENCE USING AUTOMATIC CALIBRATION\*

#### 3.1 Motivation

A current reference circuit provides a stable bias current for many analog and mixed-signal circuits despite process-voltage-temperature (PVT) variations. As a result, on-chip fully-integrated current references have been researched to reduce a bill of materials and a form factor. Recently, researchers pay attention to on-chip fully-integrated current references that can generate a small current in a range of pA or nA because the Internet of Things (IoT) applications commonly require a small bias current for ultralow-power circuits.

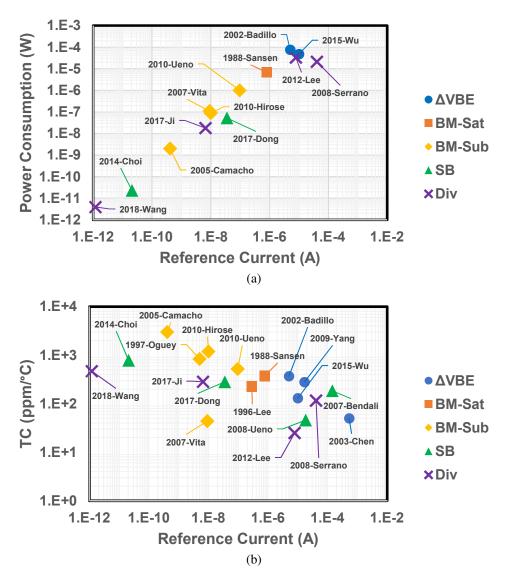

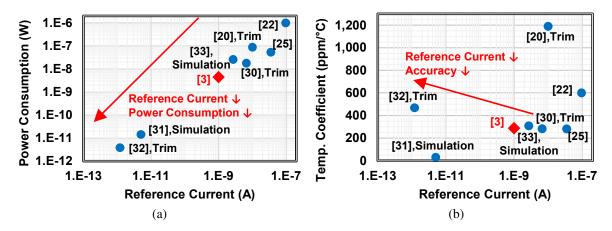

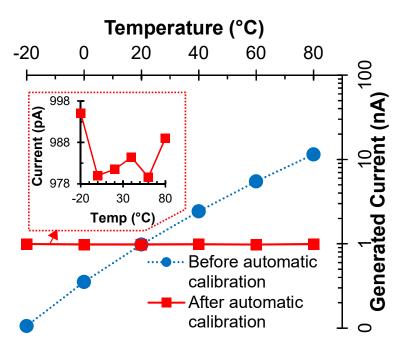

One challenge that makes designing the current references hard is a trade-off between the power consumption and the accuracy of a current reference. Fig. 3.1 clearly demonstrates the trade-off, using selected low-power current references that generate currents smaller than 1 µA [20, 22, 25, 30–33]. Each axis of Fig. 3.1 represents one of three key characteristics of a current reference: the amount of a generated current from a current reference, the temperature coefficient of the generated current, and the total power consumption of the current reference. In Fig. 3.1(a), the power consumption for generating a reference current tends to decrease as the reference current decreases. However, a lower-power current reference results in a larger temperature coefficient as Fig. 3.1(b) shows. In short, low power consumption compromises the accuracy of a current reference. One way to relax the trade-off is utilizing a multiple-temperature trimming as [32] and [30] show. However, a multiple-temperature trimming requires an additional post-fabrication test setup, leading to an increased cost and a decreased production throughput.

[3] proposes a current reference that relaxes the tight trade-off with no help from a multipletemperature trimming. In the current reference, an automatic calibration circuit periodically corrects the current generated from an ultralow-power current generator. After the calibration is fin-

<sup>\*©2020</sup> IEEE. Parts of this chapter are reprinted, with permission, from "A 1-nA 4.5-nW 289-ppm/°C Current Reference Using Automatic Calibration", by Sanghoon Lee, Stephen Heinrich-Barna, Kyoohyun Noh, Keith Kunz, and Edgar Sánchez-Sinencio, *IEEE Journal of Solid-State Circuits*.

Figure 3.1: Performance of various current references. (a) Generated reference current versus total power consumption. (b) Generated reference current versus its accuracy over temperature variation. ©2020 IEEE.

ished, all circuit blocks for the calibration are powered off. If the temperature and the supply voltage of the ultralow-power current generator change slowly, the calibration process does not need to be activated frequently. Therefore, the proposed circuit can provide an accurate current while consuming low average power.

This chapter discusses in detail about the current reference proposed in [3]. Section 3.2 introduces the system-level architecture of the proposed current reference. Section 3.3 elaborates the building blocks of the current reference. The accuracy of the proposed current reference is analyzed in Section 3.4. A calibration algorithm and a calibration time frame are discussed in Section 3.5. Current-providing mechanisms for load circuits are given in Section 3.6. Section 3.7 presents the measurement results of prototype chips. Finally, Section 3.8 makes a conclusion.

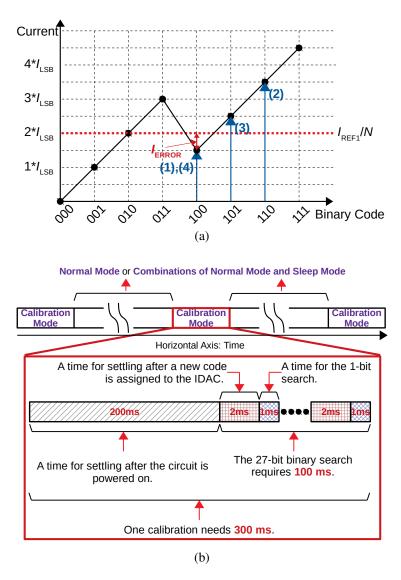

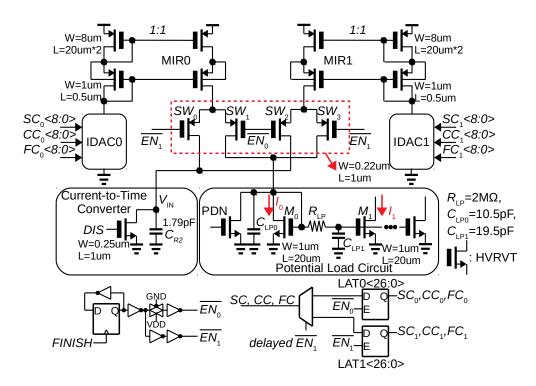

# 3.2 System-Level Architecture

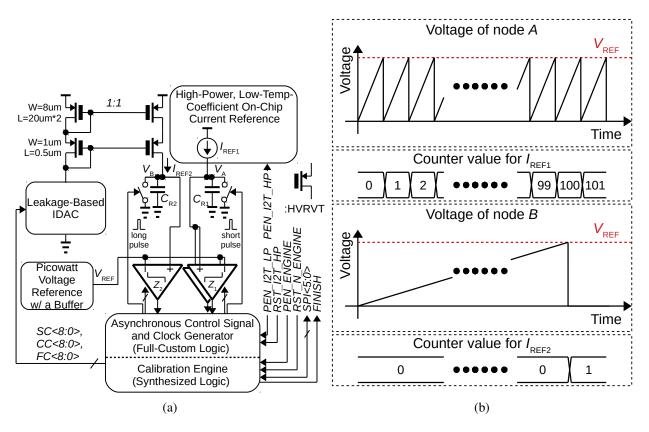

The proposed current reference has three modes of operation: calibration mode, normal mode, and sleep mode. In the calibration mode, the proposed circuit calibrates a small and inaccurate current ( $I_{REF2}$ ) using a relatively large and accurate current ( $I_{REF1}$ ). In Fig. 3.2(a), the leakage-based current digital-to-analog converter (IDAC) generates  $I_{REF2}$ , while the high-power low-temperature-coefficient on-chip current reference provides  $I_{REF1}$ . The calibration mode is activated when fol-

Figure 3.2: System-level architecture. (a) Block diagram. (b) Example waveforms of selected signals when  $I_{REF1}$ : $I_{REF2}$ =100.5:1. ©2020 IEEE.

lowing conditions are met: the active-high power-enable signals ( $PEN_I2T_HP$ ,  $PEN_I2T_LP$ , and  $PEN_ENGINE$ ) are high,  $RST_I2T_HP$  is low, and  $RST_N_ENGINE$  is high. In these signal names,  $I2T_HP$  means a current-to-time converter for the high-power current reference providing  $I_{REF1}$ , whereas  $I2T_LP$  means a current-to-time converter for the low-power current generator (IDAC) supplying  $I_{REF2}$ . Additionally, ENGINE means the calibration engine in Fig. 3.2(a). In the calibration mode, the proposed circuit first converts the two currents to time signals by charging two capacitors:  $C_{R1}$  and  $C_{R2}$ , where  $C_{R1}=C_{R2}=1.79$  pF. Since  $I_{REF1}$  is larger than  $I_{REF2}$ , the node voltage at  $A(V_A)$  rises more quickly than the node voltage at  $B(V_B)$  as Fig. 3.2(b) shows. When  $V_A$  crosses  $V_{REF}$ , a rising edge appears at the output of an auto-zeroed comparator  $Z_1$ . The full-custom logic detects the rising edge and subsequently produces various digital signals asynchronously: a pulse signal to discharge  $C_{R1}$ , a clock signal for the calibration engine, and other necessary signals

to control  $Z_1$ . The calibration engine counts the rising and the falling edges of the clock signal derived from  $I_{REF1}$ . Once  $C_{R1}$  is reset,  $I_{REF1}$  charges the capacitor again, and the proposed circuit repeats the charging and discharging process until  $V_{\rm B}$  crosses  $V_{\rm REF}$ . A counter in the full-custom logic counts the rising edge that appears at the output of the left-side comparator  $Z_2$ , and the fullcustom logic resets  $C_{R2}$ . Since the engine operates based on the clock generated from  $I_{REF1}$ , the engine detects the change in the counter value for  $I_{REF2}$  when the next rising edge of  $Z_1$  comes. Therefore, in the case of Fig. 3.2(b), the engine calculates the measured current ratio between  $I_{REF1}$ and  $I_{REF2}$  as 101:1 by comparing the two counter values. The ratio can be considered the outcome of a rounding-up because the actual ratio between the two currents is 100.5:1. When the engine obtains the measured current ratio, it assigns to the IDAC a better input code that makes  $I_{REF2}$  closer to  $I_{REF1}/N$  based on its algorithm by changing the inputs of the IDAC (SC<8:0>, CC<8:0>, and FC < 8:0 >). Since the IDAC consists of three separate arrays of binary-weighted leakage sources, the three inputs control the leakage sources of each array in the IDAC. Afterwards, the engine releases the reset signal for  $C_{R2}$ . After trying multiple input code values for the IDAC, the engine assigns 1'b1 to FINISH to indicate that the calibration process is complete. Additionally, it fixes a final code value for IDAC. Through SPI<5:0>, the code value can be read or be written for testing purposes. Furthermore, SPI < 5:0 > can set the target integer ratio between  $I_{REF1}$  and  $I_{REF2}$  (N).

After the calibration ends, the proposed circuit enters the normal mode. In the normal mode, all circuits are powered off, except the IDAC, the current mirror, and the picowatt voltage reference in Fig. 3.2(a), by assigning 1'b0 to  $PEN_I2T_IP$ ,  $PEN_I2T_IP$ , and  $PEN_ENGINE$ . Since retention flops [34] can maintain the input digital code for the IDAC, the IDAC can provide  $I_{REF2}$  through the current mirror for other analog circuits as a reference/bias current, which equals to  $I_{REF1}/N$ . Also, the normal mode has significantly lower power consumption than the calibration mode thanks to small  $I_{REF2}$  around 1 nA and a power gating technique [34] that minimizes leakages of digital logics. If the other circuits do not need the reference/bias current anymore, the proposed circuit moves to the sleep mode when all the PEN signals and  $RST_N_DIGENGINE$  are 1'b0, which sets the input of IDAC as 27'b0. In the sleep mode, the entire circuit consumes the lowest energy.

Figure 3.3: Schematic of the leakage-based IDAC. ©2020 IEEE.

The calibration mode is turned on periodically to compensate IDAC's output current deviation caused by temperature and supply voltage variations. However, the proposed circuit remains energy efficient, since it spends most of its time in the normal mode or in the sleep mode with low power consumption, whereas the calibration mode lasts for only a short time. In summary, the proposed circuit creates a small and accurate current by relaxing the trade-off between the accuracy and the power consumption of a current reference.

### 3.3 Building Blocks

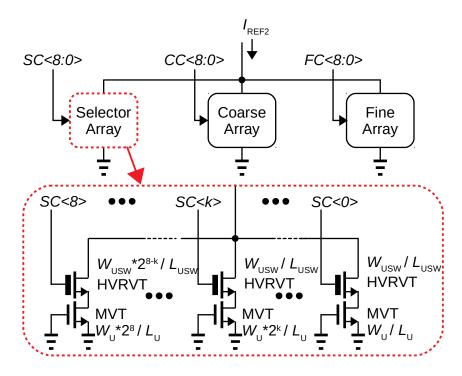

## 3.3.1 Leakage-Based IDAC

The leakage-based IDAC in Fig. 3.3 consists of three arrays: a selector array, a coarse array, and a fine array. Each array has a 9-bit digital input and produces a current as an output. The selector array generates a wide-range current, whereas the coarse and the fine arrays provide sufficient granularity in the range. Accordingly, the selector array has the largest one-least-significant-bit current ( $I_{LSB}$ ). The  $I_{LSB}$  of the coarse array is the second largest, and the  $I_{LSB}$  of the fine array is the

smallest. In the wide-range selector array, each medium-threshold (MVT) NMOS transistor that has zero voltage difference between its gate and source supplies a large leakage current. A high-votlage regular-threshold (HVRVT) NMOS transistor is selected as a switch above each MVT NMOS transistor because its high threshold voltage allows only a small leakage when it is off. Since the k-th MVT NMOS transistor from the right has a  $2^k$  times larger width than the width of the rightmost transistor, the current controlled by SC < k > 1 is  $2^k$  times larger than the current handled by SC < k > 1. Consequently, the input to each array should be a binary-coded decimal to get ideally-constant  $I_{LSB}$  from the minimum input to the maximum. Unlike the leakage current suppliers, the switches have a constant width up to the k-th switch from the right, whereas the p-th switch from the right has a width equals to  $W_{USW} \times 2^{p-k}$ , where p>k. Thanks to the constant width, the area of the selector array can be reduced. The other arrays have the same structure as the selector array. Meanwhile, to generate leakage currents that have various scales, they use different types of NMOS transistors as leakage sources: regular-threshold (RVT) NMOS transistors for the coarse array and HVRVT NMOS transistors for the fine array.

The sizes of the leakage sources in the three arrays are determined based on four requirements. First, the maximum current of the selector array should be larger than the current that the IDAC provides ( $I_{REF1}/N$ ). Second, the  $I_{LSB}$  of the selector array should be smaller than the maximum current of the coarse array. Third, the  $I_{LSB}$  of the coarse array should be smaller than the maximum current of the fine array. Lastly, the  $I_{LSB}$  of the fine array should be smaller than 0.1 % of  $I_{REF1}/N$  to minimize a quantization error. The second and the third requirements are intended for calibration accuracy through current redundancies between the arrays. When 1-LSB increase in the input code affects more than two arrays simultaneously, the IDAC has negative differential nonlinearity (DNL) smaller than -1 due to the redundancies. For example, the current generated from a setting, SC < 8:0 >= 9'h000 and CC < 8:0 >= FC < 8:0 >= 9'h1FF, is larger than the current produced from a setting, SC < 8:0 >= 9'h001 and SC < 8:0 >= FC < 8:0 >= 9'h000. The redundancy prevents calibration accuracy degradation by canceling positive DNL that might occur from current mismatches between the arrays. Mismatches between the leakage sources in an array can be alleviated by

utilizing large area for the sources.

Two factors determine the k value and the sizes of the HVRVT switches. If k=0 for an array and there is no mismatch between transistors in the array,  $V_{\rm DS}$  of on-state switches are uniform because the resistance of an on-state switch is scaled in inverse proportion to the amount of the current flowing through the switch. As a result, the array has small DNL due to the uniform drain voltage of its leakage sources. In other words, k can be increased to reduce area as long as the value does not harm the second, the third, and the forth design criteria for leakage sources. Additionally, the sizes of the switches are decided to have a total leakage current of an array smaller than the 1-LSB current of the array when all switches in the array are off. The transistor sizes are shown as follows:  $W_{\rm U}$ =4 um,  $L_{\rm U}$ =5 um,  $W_{\rm USW}$ =3 um,  $L_{\rm USW}$ =0.35 um, and k=5 for the selector array;  $W_{\rm U}$ =0.6 um,  $L_{\rm U}$ =19.9 um,  $W_{\rm USW}$ =0.22 um,  $L_{\rm USW}$ =5 um, and k=6 for the coarse array;  $W_{\rm U}$ =4 um,  $L_{\rm USW}$ =20 um, and k=6 for the fine array.

#### 3.3.2 Current-to-Time Converters

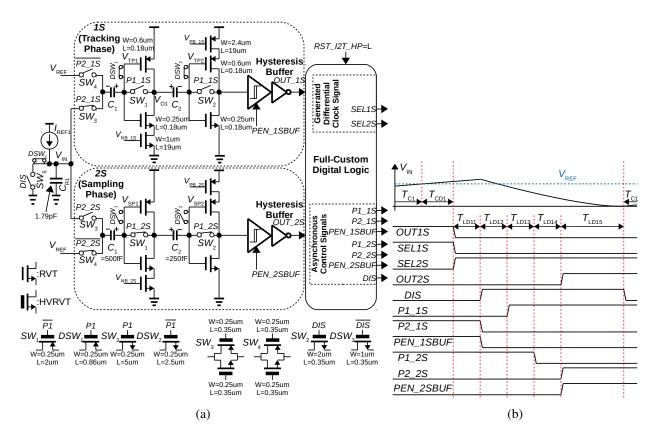

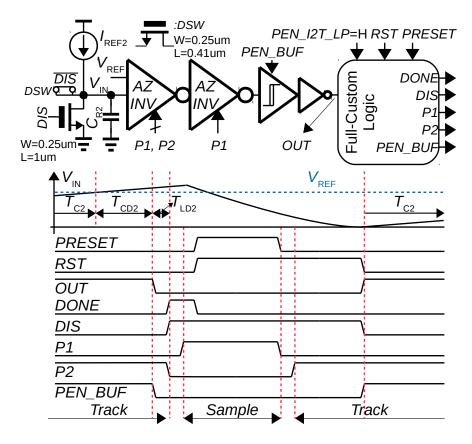

The same two auto-zeroed [35] unbalanced-current-starved-inverter-based comparators convert  $I_{\text{REF1}}$  in Fig. 3.2(a) to a time signal. Fig. 3.4(a) shows the two comparators. Each comparator has two operation phases: a sampling phase and a tracking phase. In the sampling phase, the comparator samples the switching threshold voltages [36] of the two unbalanced current-starved inverters  $(V_{\text{ST1}}, V_{\text{ST2}})$ .  $C_1$  stores the voltage difference between the reference  $(V_{\text{REF}})$  and the switching threshold of the first inverter because  $V_{\text{SP1}} = V_{\text{ST1}}$ . In addition,  $C_2$  keeps  $V_{\text{SP1}} - V_{\text{SP2}}$ , where  $V_{\text{SP2}} = V_{\text{ST2}}$ . In the tracking phase, the comparator acts as an offset-canceled comparator. When  $V_{\text{IN}}$  reaches  $V_{\text{REF}}$ , the input (and the output) voltage of the first inverter ideally equals to  $V_{\text{ST1}}$  regardless of PVT variations because of the voltage sampled in  $C_1$ . Likewise, the input (and the output) voltage of the second inverter is ideally  $V_{\text{ST2}}$  when  $V_{\text{IN}}$  reaches  $V_{\text{REF}}$ . Therefore, the switching threshold of the comparator is  $V_{\text{REF}}$  regardless of  $V_{\text{ST1}}$  and  $V_{\text{ST2}}$ . Each inverter in the comparator consumes 400 nA and has a 32-dB DC gain (27 °C, TT) at its switching threshold. Two current mirrors generate the bias voltages for each comparator. The high-power accurate current reference in Fig. 3.2(a) provides a bias current for the current mirrors. The hysteresis buffer [36] in the

Figure 3.4: Current-to-time converter for  $I_{REF1}$ . (a) Schematic. (b) Timing diagram. ©2020 IEEE.

comparator suppresses possible glitches caused by noise.

Each current-starved inverter in Fig. 3.4(a) has only one NMOS (or PMOS) current source. Accordingly,  $V_{\rm ST1}$  is higher than  $V_{\rm REF}$ , whereas  $V_{\rm ST2}$  is lower than  $V_{\rm ST1}$ . These high and low switching thresholds ensure that  $V_{\rm TP1}$  is always higher than the ground and  $V_{\rm TP2}$  is always lower than the supply voltage in the tracking phase, although  $V_{\rm IN}$  and  $V_{\rm O1}$  start from the ground and near the supply voltage respectively. For example, a balanced current-starved inverter that has a PMOS current source (W=2.4  $\mu$ m, L=19  $\mu$ m) and an NMOS current source (W=1  $\mu$ m, L=19  $\mu$ m) can have a switching threshold ranging from 515 mV to 863 mV at 80 °C in the FF corner case when the supply voltage is 1.5 V and when there are bias current mismatches smaller than  $\pm 10$  % between the two current sources. With the same temperature, corner case, supply voltage, and bias current mismatch conditions, the unbalanced current-starved inverter has a switching threshold ranging from 1.12 V to 1.13 V. Since  $V_{\rm REF}$  is 610 mV in the FF corner case, the balanced current-starved

inverter samples -95 mV on  $C_1$  in the sampling phase when the switching threshold of the inverter is the minimum. On the other hands, the unbalanced current-starved inverter stores 510 mV on  $C_1$ . Accordingly, the maximum voltage differences between the two nodes of  $SW_1$  in the tracking phase are 1.60 V and 0.99 V for the balanced and unbalanced current-starved inverters respectively. Although the unbalanced current-starved inverter uses a PMOS-only switch for  $SW_1$ , the balanced inverter cannot use the same switch because of its high on-resistance when the switching threshold of the inverter is the lowest. Instead, a transmission gate (W=0.25 µm, L=0.5 µm for both of transistors) is utilized considering that the switching threshold of the inverter has high variability. The length of the transmission gate is selected to closely match the on-resistance of the transmission gate (1.81 M $\Omega$ ) with that of the PMOS-only switch (1.74 M $\Omega$ ) when both of the inverters are in the sampling phase at 27 °C in the TT corner case. Both switches have the minimum width to minimize the capacitance seen at the drain or source of each transistor. Unlike the unbalanced current-starved inverter, the balanced inverter does not have dummy switches ( $DSW_1$  and  $DSW_2$ ) because a PMOS in the transmission gate can cancel the charge injection of an NMOS in the transmission gate without dummy switches. Under this circumstance, the unbalanced current-starved inverter has 65.6 fA leakage through  $SW_1$  when the tracking phase starts, whereas the balanced inverter has 26.8 pA leakage.

Due to the small leakage, the unbalanced-starved-inverter-based comparator can have a small offset after the auto zeroing. The offset can be quantified by measuring the difference between two voltages: sampled voltage on  $C_1$  (and  $C_2$ ) in the sampling phase; actual voltage on  $C_1$  (and  $C_2$ ) in the tracking phase when the input of the frist (and the second) inverter in the comparator reaches the switching threshold of the inverter. The comparator based on the unbalanced inverters in the current-to-time converter for  $I_{REF1}$  has 67  $\mu$ V and -10  $\mu$ V offsets on  $C_1$  and  $C_2$  respectively (30 °C, FF). However, the comparator based on the balanced inverters has a -462  $\mu$ V offset on  $C_1$  and a 496  $\mu$ V offset on  $C_2$ . The total input-referred offsets of the comparators are 67  $\mu$ V and -450  $\mu$ V respectively considering that the offset on  $C_2$  is divided by the gain of the first inverter. Temperature variations of the offsets are 111  $\mu$ V and 94  $\mu$ V respectively from -20 °C to 80 °C.

If the current-to-time converter for  $I_{REF2}$  utilizes the same comparators, the effect of the leakage on the comparator offset can be more prominent because the comparators stay in the tracking phase longer than the comparators in the current-to-time converter for  $I_{REF1}$ . The balanced-starved-inverter-based comparator in the converter for  $I_{REF2}$  has a -2.9 mV offset (80 °C, FF). Since the temperature variation of the offset is 2.9 mV and  $V_{REF}$  is 610 mV, the temperature-dependent offset can increase the temperature coefficient of  $I_{REF2}$  by at most 47.5 ppm/°C. However, the unbalanced-starved-inverter-based comparator has a 290  $\mu$ V offset (80 °C, FF). The temperature variation of the offset is 102  $\mu$ V, resulting in at most 1.7 ppm/°C temperature coefficient degradation of  $I_{REF2}$ .

Another benefit of employing the unbalanced current-starved inverter is to provide a large bandwidth with a fixed current budget. When the unbalanced inverter is loaded with a replica inverter, it has a 2.7-MHz 3-dB bandwidth at its switching threshold (27 °C, TT, 1.8 V), whereas the balanced inverter has a 17-KHz bandwidth with the same current budget (400 nA). This is because the balanced inverter has a large output resistance due to the cascoded transistors. When the supply voltage is 1.8 V and there is no bias current mismatch, the worst delay of the balancedstarved-inverter-based comparator is 4.24 µs (80 °C, FF), whereas that of the unbalanced-starvedinverter-based comparator is 225 ns (-20 °C, SS). Due to the long delay of the balanced-starvedinverter-based comparator, moving to the sampling phase from the tracking phase is delayed after  $V_{\rm IN}$  exceeds  $V_{\rm REF}$ . As a result, the input and the output voltages of each inverter deviate largely from the switching threshold of the inverter, resulting in huge settling errors on  $C_1$  and  $C_2$  in the sampling phase. When the current-to-time converter for  $I_{REF1}$  utilizes the two types of inverters, the worst settling error of the unbalanced inverter is 25.2  $\mu$ V on  $C_1$  (80 °C, SF). The temperature variation of the settling error is 21.5 μV, resulting in at most 0.35 ppm/°C temperature coefficient degradation of  $I_{REF1}$ . However, the balanced inverter shows a 40.5 mV settling error on  $C_1$  in the worst case (-20 °C, FF), and its temperature variation is 11.3 mV, leading to at most 185 ppm/°C temperature coefficient degradation of  $I_{REF1}$ .

The full-custom digital logic in Fig. 3.4(a) generates a differential clock signal from the outputs of the comparators and provides asynchronous control signals for the comparators. Fig. 3.4(b)

represents the timing diagram of the asynchronous control signals. When  $SW_5$  is disconnected,  $I_{\text{REF1}}$  charges  $C_{\text{R1}}$ , and  $V_{\text{IN}}$  rises from the ground. After a charging time  $(T_{\text{C1}})$ ,  $V_{\text{IN}}$  crosses  $V_{\text{REF}}$ , and the upper-side comparator (1S) flips its output after the delay of the comparator ( $T_{\rm CD1}$ ). A 1-bit counter in the full-custom logic detects the falling edge of OUT\_1S and changes the polarities of its outputs, SEL1S and SEL2S. After a short logic delay  $T_{\rm LD11}$ , SW<sub>5</sub> starts discharging  $C_{\rm R1}$ , and  $SW_3$  in 1S breaks the connection between  $C_{R1}$  and  $C_1$ . Additionally, the full-custom logic sets PEN\_ISBUF as 1'b0 to power off the hysteresis buffer in 1S. 1S is in the sampling phase after an additional delay  $T_{\rm LD12}$  because  $SW_1$  and  $SW_2$  are enabled. A non-overlapping signal generator produces two signals,  $P1_2S$  and  $P2_2S$ , with delays  $T_{LD13}$  and  $T_{LD14}$ . As a result, 2S is in the tracking phase after  $T_{\rm LD13}$ + $T_{\rm LD14}$ . At the same time, the full-custom logic enables the hysteresis buffer in 2S. In short, the full-custom logic completes the process that interchanges the phases of operation between IS and 2S in  $T_{\rm LD11} + T_{\rm LD12} + T_{\rm LD13} + T_{\rm LD14}$ . However, the full-custom logic needs a long delay  $(T_{\rm LD15})$  before charging  $C_{\rm R1}$  again because discharging  $C_{\rm R1}$  takes longer than  $T_{\rm LD12} + T_{\rm LD13} + T_{\rm LD14}$ . Unlike the other delays, which static logic gates generate, a dynamic logic provides  $T_{\rm LD15}$  by discharging its MOS capacitor with a constant rate using a current from the high-power accurate current reference in Fig. 3.2(a). Once the full-custom logic disconnects  $SW_5$ , the same process is repeated. The only difference is that 1S and 2S start from the sampling phase and the tracking phase respectively. Accordingly, the 1-bit counter in the full-custom logic detects the falling edge of  $OUT_2S$  when  $V_{IN}$  goes across  $V_{REF}$ . Afterwards, the full-custom logic first changes the control signals for 2S to move 2S to the sampling phase. 1S enters the tracking phase later.

The current-to-time converter for  $I_{REF2}$  shown in Fig. 3.5 utilizes the same type of the comparator used for  $I_{REF1}$ . All devices in the comparator for  $I_{REF2}$  have the same sizes with the devices in the comparator for  $I_{REF1}$  except the sizes of the dummy switches ( $DSW_1$  and  $DSW_2$ ) in Fig. 3.4(a). There are two major differences between the two converters. First, the comparator in the converter for  $I_{REF2}$  is controlled by PRESET and RST from the calibration engine in Fig. 3.2(a). Second, the converter for  $I_{REF2}$  uses only one comparator because it does not need to generate a clock signal.

Figure 3.5: Current-to-time converter for  $I_{REF2}$ . ©2020 IEEE.

The operation of the converter is synchronized with the clock generated from the converter for  $I_{\text{REF1}}$ . When  $V_{\text{IN}}$  crosses  $V_{\text{REF}}$ , the comparator drives OUT to 1'b0 after  $T_{\text{CD2}}$ . A 1-bit counter activated by the falling edge of OUT assigns 1'b1 to its output, DONE after  $T_{\text{LD2}}$ . In addition, the full-custom logic in the converter generates control signals to discharge  $C_{\text{R2}}$  and to move the comparator to the sampling phase. In the next clock cycle, the calibration engine receives the DONE signal and changes PRESET and RST to 1'b1, which resets DONE. After the calibration engine computes the ratio between the two currents ( $I_{\text{REF1}}$  and  $I_{\text{REF2}}$ ) and assigns a better input code to the IDAC, the engine changes PRESET to 1'b0, which moves the comparator to the tracking phase. In the next clock cycle, the engine sets RST as 1'b0, and  $I_{\text{REF2}}$  starts charging  $C_{\text{R2}}$  again.

## 3.3.3 Other Building Blocks