# ANALYSIS OF LIGHTNING ARRESTER OVERLOADING IN FUTURE DISTRIBUTION SYSTEMS WITH DISTRIBUTED GENERATION

## A Thesis

by

## JONATHAN MICHAEL SNODGRASS

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Chair of Committee, Le Xie

Committee Members, Miroslav M. Begovic

Scott Miller

Erick Moreno-Centeno

Head of Department, Miroslav M. Begovic

August 2016

Major Subject: Electrical Engineering

Copyright 2016 Jonathan Snodgrass

#### **ABSTRACT**

The objective of this thesis is to address an issue that arises from the increasing penetration of distributed energy resources in future power systems: the design and analysis of protective devices with more complex topology and power flow patterns. In particular, this thesis investigates lightning arrester overloading and failure from fault-induced overvoltages. Currently, in existing literature and industry practice, there does not exist a readily practical and sufficiently accurate method to determine the magnitude of a fault-induced overvoltage. Thus, the length of time from the fault inception until the lightning arresters fail is unknown, forcing utility companies to assume the worst case scenario and install more costly and complex protection schemes than otherwise needed.

In this thesis, the Thevenin Equivalent Impedance method is proposed to analyze a distributed generation (DG) source's effect on the transformer high side voltage. After examining the voltage transients and determining the magnitude of the overvoltage, an optimal and cost-effective protective relaying strategy is developed and implemented. To complete this study, various types of DG sources were modeled and simulated using two test systems. Finally, the implementation of the suggested solution of intentional islanding operation of the distribution system is discussed. This solution allows the DG source to continue to supply a portion of the distribution system's load, thereby increasing the reliability of the system.

## ACKNOWLEDGEMENTS

I would like to thank my academic committee, for their time and input into my research. I would especially like to thank Dr. Le Xie, my academic advisor, for his invaluable help, without which this work would not have been possible. His guidance and direction have helped me substantially, and allowed me to flourish in my research. Also, I would like to thank Dr. Henry Zmuda from the University of Florida for allowing me to utilize his course notes on symmetrical components for my detailed explanation in Appendix A. Finally, I would also like to thank my family, friends, and fiancée, since their emotional and spiritual support helped tremendously in the research and writing of this thesis.

## NOMENCLATURE

ATP Alternative Transients Program

EMTP Electromagnetic Transient Program

DG Distributed Generation

MCOV Maximum Continuous Operating Voltage

POI Point of Interconnection

PQ Bus Bus Real Power (P), Reactive Power (Q) specified

PV Bus Bus Power and Voltage specified

TOV Temporary Overvoltage

VT Voltage Transformer

# TABLE OF CONTENTS

|     |                                                                                    | Page |

|-----|------------------------------------------------------------------------------------|------|

| ABS | STRACT                                                                             | ii   |

| AC  | KNOWLEDGEMENTS                                                                     | iii  |

| NO  | MENCLATURE                                                                         | iv   |

| TAI | BLE OF CONTENTS                                                                    | v    |

| LIS | ST OF FIGURES                                                                      | viii |

| LIS | ST OF TABLES                                                                       | xi   |

| 1   | INTRODUCTION                                                                       | 1    |

|     | 1.1 Contributions from this Thesis                                                 | 2    |

| 2   | PROBLEM OVERVIEW                                                                   | 4    |

| 3   | CURRENT INDUSTRY PRACTICE                                                          | 8    |

| 4   | LITERATURE REVIEW                                                                  | 11   |

|     | 4.1 Currently Suggested Solutions in Literature                                    |      |

| 5   | ALTERNATE ANALYSIS METHODS                                                         | 13   |

|     | <ul><li>5.1 Distribution Load Flow</li><li>5.2 Sequence Network Approach</li></ul> |      |

| 6   | OVERVOLTAGE CONDITIONS                                                             | 18   |

| 7   | LIGHTNING ARRESTER OVERVIEW                                                        | 22   |

|     | 7.1 Temporary Overvoltages                                                         | 24   |

| 8   | SOLUTION METHODOLOGY                                                               | 26   |

|     | 8.1 Equivalent System Impedance                                                    | 26   |

|     |       | 8.1.1    | Test Current Injection                          | 26 |

|-----|-------|----------|-------------------------------------------------|----|

|     |       | 8.1.2    | Voc/Isc                                         | 27 |

|     | 8.2   | Voltage  | Computation                                     | 27 |

| 9   | TES   | T SYSTE  | EMS                                             | 28 |

|     | 9.1   | IEEE 4   | Node Test Feeder                                | 28 |

|     | 9.2   |          | 3 Node Test Feeder                              |    |

|     | 9.3   | Solar ar | nd Wind SG Source Models                        | 31 |

|     | 9.4   |          | nedding Simulations                             |    |

| 10  | RES   | ULTS     |                                                 | 34 |

|     | 10.1  | Voltage  | Transients                                      | 34 |

|     |       |          | IEEE 4 Node Test Feeder                         |    |

|     |       | 10.1.2   | Simulink Verification                           | 36 |

|     |       | 10.1.3   | IEEE 13 Node Test Feeder                        |    |

|     | 10.2  | Theven   | in's Equivalent Circuit                         | 38 |

|     |       | 10.2.1   | Test Current Injection: Simulink Approach       |    |

|     |       | 10.2.2   | Voc/Isc: Simulink Simulations                   |    |

|     |       | 10.2.3   | Assumptions and Simplifications                 |    |

|     | 10.3  | Substati | ion Voltages                                    |    |

|     |       | 10.3.1   | Original IEEE 13 Node System Configuration      |    |

|     |       | 10.3.2   | Expanded IEEE 13 Node System Configurations     |    |

|     |       | 10.3.3   | Error vs. Imbalance                             |    |

| 11  | PRO   | BLEM S   | OLUTIONS                                        | 61 |

|     | 11.1  | Protecti | ve Relaying Strategies                          | 61 |

|     |       | 11.1.1   | • •                                             |    |

|     |       | 11.1.2   | · · · · · · · · · · · · · · · · · · ·           |    |

|     |       | 11.1.3   | Fault Detection at the Point of Interconnection | 64 |

|     | 11.2  | Islandin | ng Strategies                                   |    |

|     |       | 11.2.1   | Load Shedding                                   | 69 |

|     |       | 11.2.2   | Frequency-Droop Control                         |    |

| 12  | FUR   | THER R   | ESEARCH                                         | 74 |

| 13  | SUM   | IMARY.   |                                                 | 75 |

| REF | FEREN | NCES     |                                                 | 77 |

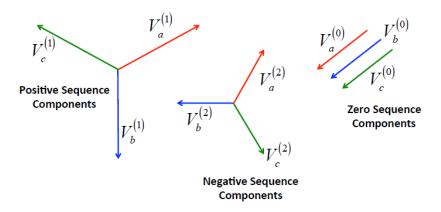

| APF | PEND  | IX A OV  | ERVIEW OF SYMMETRICAL COMPONENTS                | 82 |

| APF | PENDI | IX B AD  | DITIONAL IEEE 4 NODE RESULTS                    | 90 |

| APPENDIX C ADDITIONAL IEEE 13 NODE RESULTS       | 93 |

|--------------------------------------------------|----|

| APPENDIX D UNDER FREQUENCY LOAD SHEDDING RESULTS | 99 |

# LIST OF FIGURES

|                                                                                                                                       | Page |

|---------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1: Distribution System One-Line with DG                                                                                      | 4    |

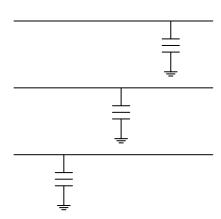

| Figure 2.2: Lightning Arrester Connections to Transmission Lines                                                                      | 5    |

| Figure 2.3: System One-Line after Line-End Breakers Opened                                                                            | 6    |

| Figure 5.1: Network Bus Voltages                                                                                                      | 13   |

| Figure 5.2: Phase and Sequence Impedance Matrices for Load at Node 675                                                                | 16   |

| Figure 5.3: Phase and Sequence Impedance Matrices for Line from Node 675 to Node 692                                                  | 16   |

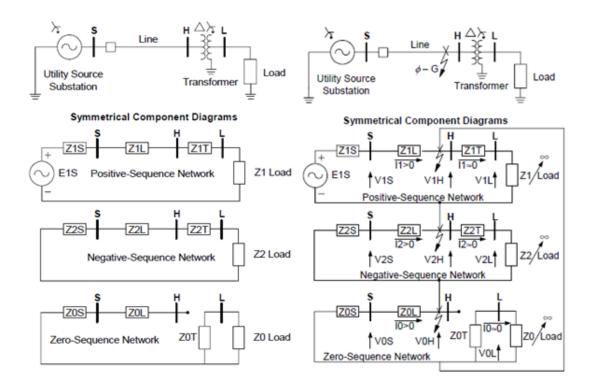

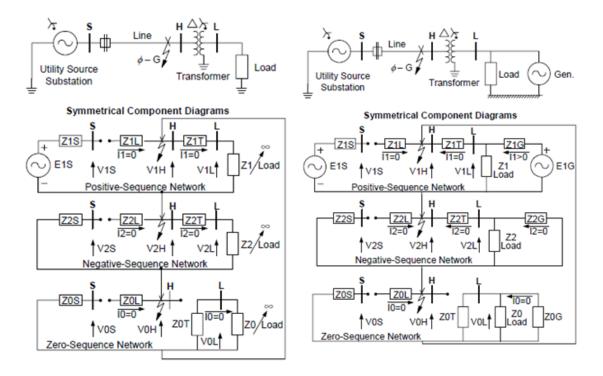

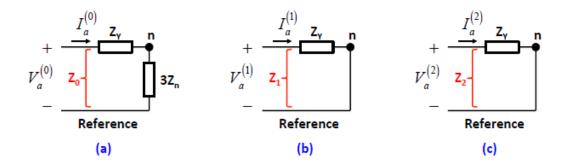

| Figure 6.1: Sequence Network Connections Pre-Fault and for Single Line to Ground Fault (Reprinted with Permission from [2])           | 19   |

| Figure 6.2: Sequence Network Connections After Utility Breaker Opens, Without and With DG Source (Reprinted with Permission from [2]) | 20   |

| Figure 6.3: (a) Normal Phasor diagram, (b) Line-to-Line Fault, (c) Apparent Neutral Shift (Reprinted with Permission from [2])        | 21   |

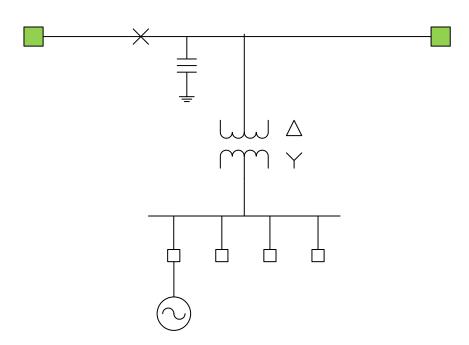

| Figure 9.1: ATP Simulation of IEEE 4 Node System Model                                                                                | 29   |

| Figure 9.2: Simulink Simulation of the IEEE 13 Node Feeder System                                                                     | 30   |

| Figure 9.3: Simulink Constant Power Model of Power Electronically Interfaced Generation                                               | 32   |

| Figure 9.4: Under Frequency Load Shedding Simulation in Simulink                                                                      | 33   |

| Figure 10.1: Voltage Transients for Single Line to Ground Fault                                                                       | 35   |

| Figure 10.2: Simulink Model of IEEE 4 Node System                                                                                     | 36   |

| Figure 10.3: Simulink Voltage Transients for Single Line to Ground Fault, IEEE 13 Node System                                         | 38   |

| Figure 10.4: System Impedance Measurements of IEEE 13 Node System                                                                     | 39   |

| Figure 10.5: Voc/Isc Equivalent Network Measurement Model                                                | 41 |

|----------------------------------------------------------------------------------------------------------|----|

| Figure 10.6: IEEE 13 Node System, Series Configuration                                                   | 44 |

| Figure 10.7: Thevenin Equivalent Network Model                                                           | 46 |

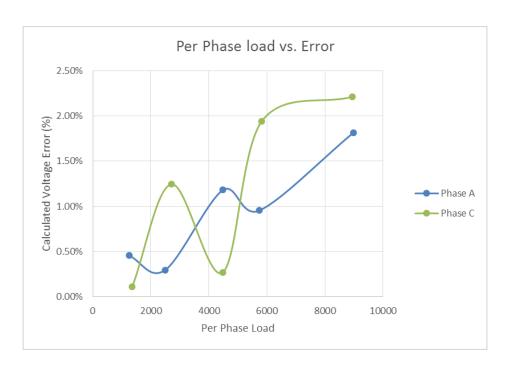

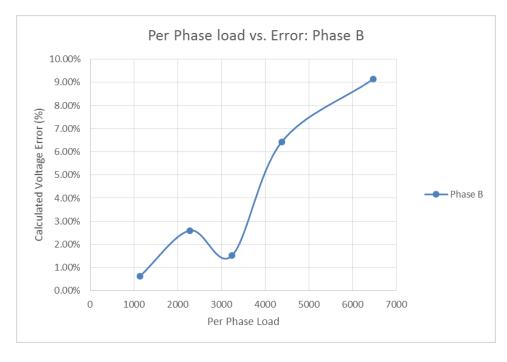

| Figure 10.8: Per Phase Load vs. Error % for Phases A and C                                               | 58 |

| Figure 10.9: Per Phase Load vs. Error % for Phase B                                                      | 58 |

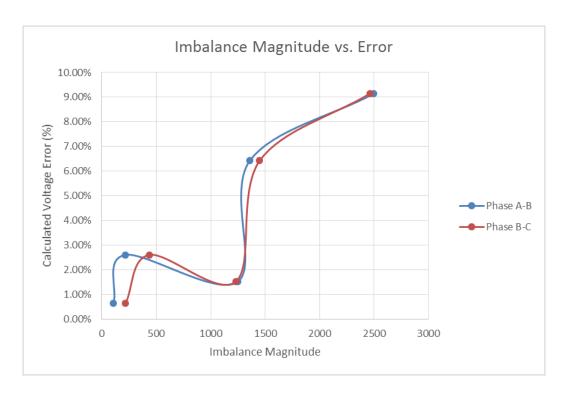

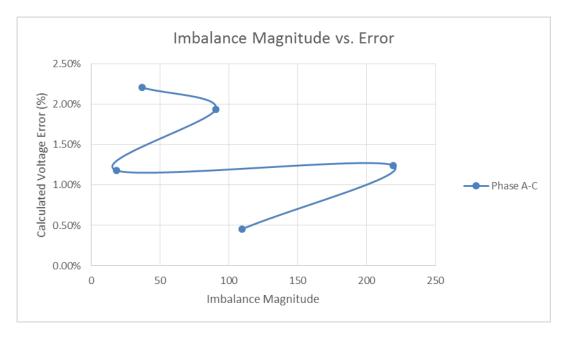

| Figure 10.10: Imbalanced Magnitude vs. Error % for Phases A-B and B-C                                    | 59 |

| Figure 10.11: Imbalanced Magnitude vs. Error % for Phase A-C                                             | 59 |

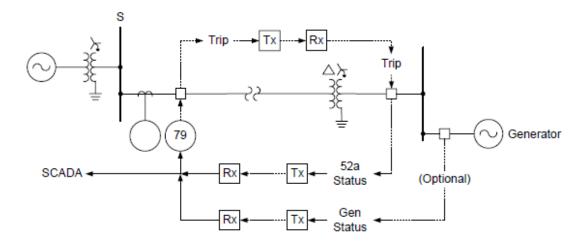

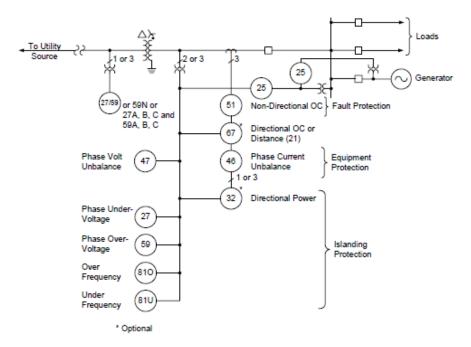

| Figure 11.1: Tripping DG Using Communication Channel (Reprinted with Permission from [2])                | 63 |

| Figure 11.2: Fault Detection Relaying One-Line (Reprinted with Permission from [2])                      | 64 |

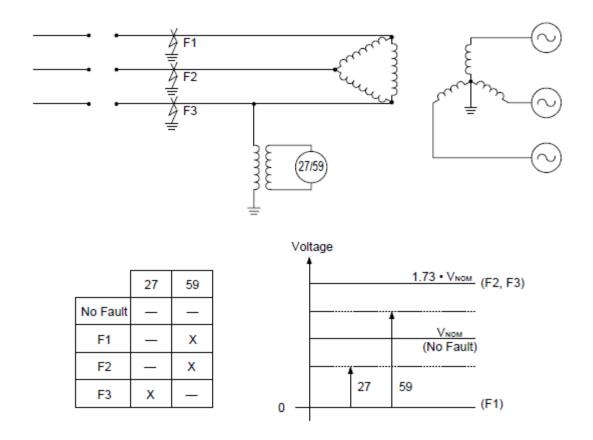

| Figure 11.3: Fault Detection Using a Single Voltage Relay (Reprinted with Permission from [2])           | 66 |

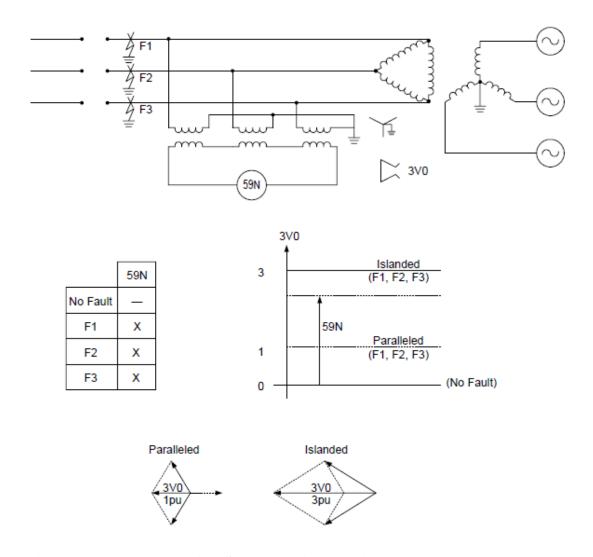

| Figure 11.4: Fault Detection Strategy Using Multiple Voltage Relays (Reprinted with Permission from [2]) | 68 |

| Figure A.1: Sequence Phasor Diagram (Reprinted with Permission from [10])                                | 82 |

| Figure A.2: Sequnce to Phase Conversion (Reprinted with Permission from [10])                            | 83 |

| Figure A.3: Derivation of Sequence Conversion (Reprinted with Permission from [10])                      | 84 |

| Figure A.4: Sequnce Impedance Calcuations (Reprinted with Permission from [10])                          | 84 |

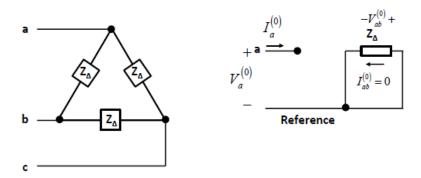

| Figure A.5: Zero Sequence Network Connection for Delta Circuit (Reprinted with Permission from [10])     | 85 |

| Figure A.6: Derivation of Zero Sequence Delta Connections (Reprinted with Permission from [10])          | 86 |

| Figure A.7: Ungrounded Y-Connected Load (Reprinted with Permission from [10])                            | 86 |

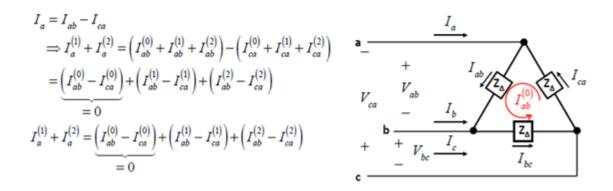

| Figure A.8: Neutral Current derivation (Reprinted with Permission from [10])                             | 87 |

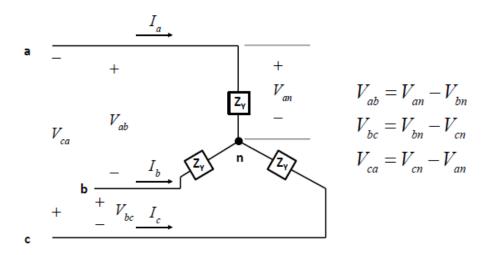

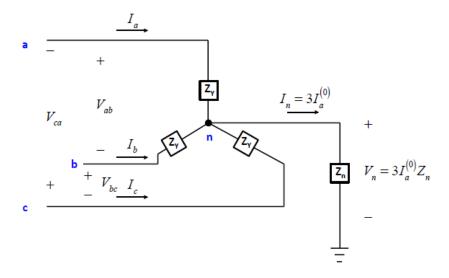

| Figure A.9: Voltage Computations (Reprinted with Permission from [10])                                             | 88  |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Figure A.10: Unbalanced Voltage Operation (Reprinted with Permission from [10])                                    | 88  |

| Figure A.11: Sequence Impedances (Reprinted with Permission from [10])                                             | 89  |

| Figure A.12: Zero Sequence Connections for Delta and Ungrounded Wye Circuits (Reprinted with Permission from [10]) | 89  |

| Figure B.1: IEEE 4 Node Network, Modified                                                                          | 90  |

| Figure B.2: Voltage Results From Modified IEEE 4 Node System                                                       | 91  |

| Figure B.3: Voltage Results with Load Trippled                                                                     | 92  |

| Figure D.1: Graph of System Frequency (Hz) vs. Time (s)                                                            | 100 |

| Figure D.2: Electrical Power and Rotor Angle vs. Time                                                              | 101 |

| Figure D.3: Breaker Status (open/closed) vs. Time (s)                                                              | 101 |

# LIST OF TABLES

|                                                                                                                                  | Page |

|----------------------------------------------------------------------------------------------------------------------------------|------|

| Table 5.1: IEEE 13 Node System Load for Node 675                                                                                 | 15   |

| Table 10.1: IEEE 13 Node System Equivalent Impedances                                                                            | 45   |

| Table 10.2: IEEE 13 Node System Load Levels for Various Configurations                                                           | 47   |

| Table 10.3: DG Source Connected to Node 633                                                                                      | 49   |

| Table 10.4: DG Source Connected to Node 675                                                                                      | 49   |

| Table 10.5: DG Source Connected to node 680                                                                                      | 50   |

| Table 10.6: Parallel 1 Configuration, DG Connected to Node 675                                                                   | 52   |

| Table 10.7: Series System Configuration, no Test Load                                                                            | 53   |

| Table 10.8: Series System Configuration, with Test Load                                                                          | 53   |

| Table 10.9: Series Parallel 1 System, Using Measured Impedance of the Series System                                              | 54   |

| Table 10.10: Series Parallel 2 Configuration, Using Measured Impedance of the Series System                                      | 54   |

| Table 10.11: Series Parallel 2 Configuration, Using Measured Impedance of the Series Parallel 2 System                           | 55   |

| Table 10.12: Results of the Load Reduction Method                                                                                | 56   |

| Table C.1: Measured System Impedances with the DG Source Connected to the Given Node, with and without the Connected System Load | 93   |

| Table C.2: Impedances of the Series and Parallel Configurations of the IEEE 13  Node System                                      | 93   |

| Table C.3: Voc/Isc Measured Impedances of Various System Configurations                                                          | 93   |

| Table C.4: Substation Voltages with DG Connected to Node 633, Voc/Isc Calculated Impedance                                       | 94   |

| Calculated Impedance                                                                                      | 94 |

|-----------------------------------------------------------------------------------------------------------|----|

| Table C.6: Substation Voltages with DG Connected to Node 680, Voc/Isc Calculated Impedance                | 95 |

| Table C.7: Substation Voltages of Series System Configuration, no Test Load, Voc/Isc Calculated Impedance | 95 |

| Table C.8: Substation Voltages of Series System Configuration, Test Load, Voc/Isc Calculated Impedance    | 96 |

| Table C.9: Substation Voltages of Parallel 1 System Configuration, Voc/Isc Calculated Impedance           | 96 |

| Table C.10: Equivalent Loads for Parallel 1 Configurations                                                | 97 |

| Table C.11: Equivalent Loads for Series Configurations, Part 1                                            | 97 |

| Table C.12: Equivalent Loads for Series Configurations, Part 2                                            | 97 |

| Table C.13: Equivalent Loads for Series Parallel 1 Configurations                                         | 98 |

| Table C.14: Equivalent Loads for Series Parallel 2 Configurations                                         | 98 |

#### 1 INTRODUCTION

One of the major challenges facing the world today is that of global climate change and the resulting effects on the environment. In response, there have been efforts to decrease greenhouse gas emissions by installing new renewable energy sources to eventually replace fossil-fuel based generation [1]. Many distributed generation (DG) resources, such as photovoltaic panels or wind turbines, are integrated directly into distribution systems. DG resources pose fundamental challenges in today's control and protection framework of distribution systems, since the traditional design philosophy is based on the premise of unidirectional power flow from transmission down to the distribution systems. While there are numerous challenges to overcome when integrating DG into future or existing energy systems, the focus of this thesis is to model, analyze, and design a coordinated protection scheme for a class of protection devices: the lightning arresters.

If a distribution system with adequate distributed generation is connected to the transmission grid through a delta-wye substation transformer, a permanent line-to-ground fault that causes the distribution grid to inadvertently island will cause at worst a line-to-line voltage drop across the lightning arresters, thus quickly overloading the arresters. Without an analysis method to determine the possibility and severity of these overvoltages, utility companies are forced to assume the worst case scenario, and must implement a protection scheme that is potentially much more complex and costly than

otherwise required. Thus, a simpler method to analyze the voltage profile of a distribution system with integrated DG is of great need.

## 1.1 Contributions from this Thesis

This project was motivated by a summer project by the author with a Texas utility that was facing the aforementioned problem. In response to this issue, research was conducted on using a simple, but sufficiently accurate model of the distribution system to determine the overvoltage that results from the installation of a given DG source in to a distribution grid. By determining the severity of the overvoltage, a more proper protective relaying scheme may be utilized, preventing a utility company from implementing an overly conservative and costly scheme. Utilizing the Thevenin Equivalent Method suggested in this paper could potentially save utility companies numerous hours in conducting a more complicated and detailed system study. Also, implementing the protective relaying schemes suggested in this thesis can potentially save tens to hundreds of thousands of dollars on costly protection equipment.

Additionally, if islanding schemes are utilized, the DG source can continue to operate during a transmission-level fault, increasing reliability of the distribution grid by supplying a portion of the distribution system load.

The outline of this thesis is as follows: Sections 2 and 3 present an overview of the lightning arrester overvoltage problem, as well as the current solutions used by utility companies. Sections 4 and 5 give an overview of the existing academic literature on lightning arrester overloading, and lists the shortcomings of the current analysis and solutions presented. The cause of the overvoltage conditions is more fully examined in

section 6, and the impact on lightning arresters is discussed in section 7, along with additional background information on lightning arresters. The Thevenin Equivalent solution method is explained in section 8, and test systems are introduced in section 9. The results of the transient voltage analysis as well as the steady state voltage levels are given in section 10. In section 11, protective relaying strategies are presented and successful islanding operation of the distribution grid is discussed. Finally, sections 12 and 13 present areas for future research, as well as summarize the research in this thesis.

## 2 PROBLEM OVERVIEW

An increasing amount of distributed generation, such as wind and solar, is being integrated into distributions systems. Though there are many problems that such installations pose, one such issue is the risk of a transformer high-side overvoltage contingency when a substation is connected at a single point to a high-voltage transmission line via delta-wye step-up transformer, as shown in Figure 2.1

Figure 2.1: Distribution System One-Line with DG

The lightning arrestors are connected to the transmission line directly from each conductor to ground, as shown in Figure 2.2, thus nominally experiencing line-to-ground voltages.

Figure 2.2: Lightning Arrester Connections to Transmission Lines

However, for normal transmission lines, voltages are given in line-to-line quantities, thus a 138kV transmission line would have a line to neutral voltage of approximately 80kV (precisely 79.67kV). Thus, for normal operation, a lightning arrestor would experience a line to neutral (or ground) voltage drop.

In the case of a line to ground fault (shown in Figure 2.3), the transmission level line-end breakers will open (near) instantaneously, assuming there is a communication scheme between the line-end relays. Once the line-end breakers have opened, the DG source will be connected to the transmission grid via an ungrounded delta transformer, until the DG or distribution substation breaker trips. During this period (10-20 cycles, or

longer), the lightning arrestors on the non-faulted phases will experience a line-to-line voltage drop instead of the customary line-to-neutral voltage drop, as explained in further sections. If the overvoltage is severe enough, and the DG source isn't tripped within 2-3 cycles, then this overvoltage condition will cause the semiconductor-based lightning arrestors to fail. However, as explained later in this thesis, the delta transformer creates a break in the zero-sequence transformer impedance, thus no fault current flows, making fault detection much more difficult since traditional overcurrent relays cannot be used.

Figure 2.3: System One-Line after Line-End Breakers Opened

Currently, protection engineers mitigate this risk by installing a transmissionlevel undervoltage relaying scheme with a direct transfer trip signal to the DG source's main breaker. This transfer trip command could initiate from the remote substation relays, or a relay on the high side of the local substation transformer. While this approach is robust and reliable, it causes over-tripping of the DG source for every transmission line fault, including temporary faults. This means the DG source must wait a set amount of time before reconnecting to the transmission grid, and must go through the resynchronization process before connecting to the grid. This results in lost revenue for the DG, and increased wear and tear on the DG interconnection breaker. Also, there is currently no analysis process to determine if the DG source is sufficient to cause overvoltages capable of damaging the lightning arresters, or if the distribution system load causes sufficient voltage drop to mitigate the problem. Therefore, the worst case scenario is assumed, and the undervoltage relaying with direct transfer trip is implemented for all cases of distribution level interconnected DG. Thus, a simple, but sufficiently accurate method of determining the overvoltage conditions resulting from the line-to-ground fault needs to be developed, as will be explained in subsequent sections.

#### 3 CURRENT INDUSTRY PRACTICE

In the Electric Reliability Council of Texas (ERCOT) grid, due to deregulation, there is a limited amount of information that can be shared between generation companies, transmission/distribution companies, and the retail electric providers. Thus, if a generation company, or an independent power producer, wants to connect a new power source to the distribution or transmission grid, the system operator or transmission company needs to conduct a feasibility study to make sure that the new generation can be safely and properly connected [2].

For both cases, the generation company must supply the needed information to the transmission company regarding the details and capacity of the generation to be connected, the point of interconnection, and any other information required to complete the study. Thus, the generation company supplies only one proposed location, and this location is used for the interconnection study, regardless of whether this is the optimal interconnection location or not. However, this results in an easier feasibility study, since the generation capacity and interconnection location are already known.

Since the DG source to be integrated is only proposed and not actually installed, this is a worst-case analysis study. Thus, the worst-case DG source levels and system loading conditions are used to determine the highest possible voltage across the lightning arresters. This occurs when the DG source is producing its rated power output (e.g. at noon on a sunny day for a solar photovoltaic installation), and the load is at its lightest (e.g. a mild spring day where little air conditioning is running). Thus, the generation and

load quantities are conservative estimates and create factors of safety in the system.

Also, in typical utility distribution voltage studies of this type, unbalanced operation is not considered, however, for the purpose of this paper, unbalanced load and asymmetrical distribution lines are considered.

Currently, there is no good method of determining if the proposed DG capacity will result in lightning arrester overload conditions. Consequently, utility protection engineers assume the worst-case scenario and design the protection schemes such that they trip the DG source for any transmission-level fault. However, this results in unnecessary tripping of the DG for temporary faults, as well as interconnections where the DG source capacity isn't high enough to cause lightning arrester overloads.

One method that has been proposed is the sequence network analysis method, but as discussed later in this paper, the asymmetrical distribution lines and unbalanced distribution loads substantially complicate the symmetrical component analysis by making the sequence networks no longer decoupled and independent. Thus, a simpler analysis method must be developed to determine if the proposed DG will operate safely, or if additional and more complicated analysis methods are required.

The conclusion is that using the Thevenin impedance method results in a first-order approximation of the transformer high-side voltages. If these calculated voltages are below the threshold where the lightning arresters will be overloaded, then simpler protective relaying strategies may be used, saving time and money. If the calculated voltages are above the threshold voltage range, then islanding schemes may be implemented, depending on the DG capacity.

For a more robust solution, adaptive relaying strategies may be implemented that take the current load and DG source capacities into account when determining whether to island the system, trip the DG, or allow existing protection schemes to work.

#### 4 LITERATURE REVIEW

Several other sources have theorized about the line-to-line overvoltage across the lightning arresters and documented the potential problems that this overvoltage condition would create. In [3], it is shown that an ungrounded wye system could experience up to a 1.73 per unit overvoltage on the unfaulted phases for a single-line to ground fault. [4] indicates that a 1.73 overvoltage can also occur from an open phase fault. [5] introduces the idea of cogeneration (DG) connected to a distribution system, and presents the same problem as addressed in this paper: a distribution-level DG source is interconnected to the transmission grid through a delta-wye transformer. According to [5], during a ground fault, the line-end breakers will open, but the DG breaker will not open due to the delta connection preventing fault current from flowing. Until the DG breaker trips on underfrequency or undervoltage, the line section between the transformer and the line-end breakers will operate at as a 3-wire system, and the unfaulted phases "may reach 1.73 P.U. This overvoltage may have no effect on gapped arresters, but the metal oxide arresters on this feeder will conduct current on the overvoltage. If the overvoltage is high, the metal oxide arresters will fail unless the duration of the overvoltage is short." [5]

While all of these papers explain that the neutral shift overvoltages can occur in theory, none of them ran any simulations to illustrate or prove this point. Additionally, none of the sources mention islanding the distribution grid as a possible solution for the overloads. However, later in this paper, the line-to-ground fault on an ungrounded

(delta) system cause of the neutral shift overvoltage will be examined, and simulations will verify that this condition does indeed result in an overvoltage of approximately 1.73 pu voltage on the unfaulted phases.

## 4.1 Currently Suggested Solutions in Literature

One solution described by [3] is to make the lightning arresters less sensitive to overvoltages, and if an arrester does overload, making sure that the arrester fails in an acceptable manner. According to [4], this can be accomplished by placing a disconnector in series after the lightning arrester, which disconnects after the arrester has failed to remove the short circuit from the transmission line.

## 4.1.1 Gapped Lightning Arresters

According to [4] and [6], an efficient way to prevent the lightning arresters from being overloaded is to introduce gapped silicon-carbide arresters in series with the MOV arresters. The withstand voltage of the gapped arresters is approximately 2.34 pu, which is above the maximum overvoltage experienced by the arresters [4]. The problem is that most proposed DG integrations are into existing distribution networks with existing transmission infrastructure already in place. Thus, all of the lightning arresters on the connected transmission lines would need to be replaced, at great cost to the DG owner or transmission grid operator. Another problem is that the higher withstand voltage of a gapped arrester also means that the arrester has a higher flashover voltage, thus offering less protection to connected equipment in the event of transient overvoltages and switching surges [3]. Thus, a method that allows the current system configuration to remain unchanged is needed.

#### 5 ALTERNATE ANALYSIS METHODS

Next, two existing methods of voltage analysis, load flow and sequence network analysis, are explored. It is shown that both of these methods have disadvantages, and a simpler, first step approach is needed to determine the substation voltage levels for the proposed DG installation.

#### **5.1** Distribution Load Flow

Load flow is a method that uses the network impedance matrix and three different types of busses to determine the voltage magnitudes and phase angles at each bus, as well as the real and reactive power flows along each line connecting the busses. As detailed by [7], load flow calculations use the voltage equations shown below in Figure 5.1. There is one bus, the slack or reference bus, where the voltage magnitude and phase angle is known. All other busses on the system are either load (PQ busses where the real and reactive power injection is specified) or generator (PV busses where the real power and voltage magnitude are specified) busses.

$$\mathbf{V}_{k} = \frac{1}{\mathbf{Y}_{kk}} \left( \frac{P_{k} - jQ_{k}}{\mathbf{V}_{k}^{*}} - \sum_{j \neq k} \mathbf{Y}_{jk} \mathbf{V}_{j} \right)$$

Figure 5.1: Network Bus Voltages

As detailed by [8], distribution load flow takes into account asymmetrical distribution lines and unbalanced loading conditions. The method presented in [8] utilizes the Zbus Gauss solution approach which takes advantage of the sparse bifactored Ybus matrix, and treats unbalanced loads as current injections into or from the network. Another paper, [9] uses the Newton-Raphson method and calculates the effect of distributed generation in the distribution network by modeling the generators as PV busses.

The limitation with using distribution load flow is that there must be a slack bus to establish the voltage phase angle reference, as well as meet any power mismatch not supplied by the generation busses. However, islanded distribution systems inherently do not meet this criteria, since the utility grid can no longer be considered the slack bus. Also, as in the cases explored later in this thesis, the DG generation capacity is below the load levels, and the substation voltage must be computed to examine the effect on lightning arrester overloading. This short time scale voltage profile is present before the load shedding relays will operate, thus removing the possibility of using distribution level load flow for this analysis.

Finally, distribution load flow requires a full system model of the distribution system with precise load locations, and as detailed in section 3, the load levels and locations are not precisely known for the purpose of determining if lightning arresters will overload. Thus, an analysis method that allows for mismatch between generation and load, as well as accommodates uncertainty in the load placement and levels, is needed.

## **5.2** Sequence Network Approach

As detailed in Appendix A [10], symmetrical components is a method that is utilized to change an unbalanced set of voltage or current phasors into three sets of balanced phasors: positive, negative and zero sequence. This analysis method is utilized to compute voltages and currents for inherently unbalanced systems, such as line-to-ground fault conditions.

However, as shown later in this paper, distribution systems have unbalanced loads and asymmetrical distribution lines by nature, thus significantly complicating the sequence network analysis. For example, the load at node 675 on the IEEE 13 node feeder test case is shown in Table 5.1 below.

| Node | Load  | Ph-1          | Ph-1 | Ph-2 | Ph-2 | Ph-3 | Ph-3 |

|------|-------|---------------|------|------|------|------|------|

|      | Model | $\mathbf{kW}$ | kVAr | kW   | kVAr | kW   | kVAr |

| 675  | Y-PQ  | 485           | 190  | 68   | 60   | 290  | 212  |

Table 5.1: IEEE 13 Node System Load for Node 675

The phase impedance matrix,  $Z_{abc}$  is given below. Then, the impedance is transformed to the sequence domain using the transformation described in Appendix A, and the result,  $Z_{012}$  is given below in Figure 5.2. Notice that the sequence matrix is far from diagonal, with significant cross coupling existing between most of the sequence networks.

| Zabc =  |   |         |           |   |         |         |   |         |

|---------|---|---------|-----------|---|---------|---------|---|---------|

| 30.934  | - | 12.119i | 0 +       | + | 0i      | 0       | + | 0i      |

| 0       | + | 0i      | 143.09 -  | _ | 126.26i | 0       | + | 0i      |

| 0       | + | 0i      | 0 +       | + | 0i      | 38.891  | - | 28.431i |

| Z012 =  |   |         |           |   |         |         |   |         |

| 57.559  | - | 3.704i  | -73.613 + | + | 84.607i | 6.749   | + | 62.672i |

| -32.506 | - | 2.1161i | 98.414 -  | _ | 142.95i | -32.758 | - | 54.64i  |

| 5.8812  | _ | 6.2984i | 6.1332    | + | 46.225i | 56.943  | - | 20.151i |

Figure 5.2: Phase and Sequence Impedance Matrices for Load at Node 675

Also, the line impedance between node 675 and the adjacent node 692 is shown below. Notice that since the line is more symmetrical than the load above, the sequence matrix is closer to being diagonal, with the exception of the cross coupling shown in the first row of the matrix.

| ZLineabc = |   |             |           |   |           |           |   |           |

|------------|---|-------------|-----------|---|-----------|-----------|---|-----------|

| 0.7982     | + | 0.4463i     | 0.3192    | + | 0.0328i   | 0.2849    | - | 0.0143i   |

| 0.3192     | + | 0.0328i     | 0.7891    | + | 0.4041i   | 0.3192    | + | 0.0328i   |

| 0.2849     | - | 0.0143i     | 0.3192    | + | 0.0328i   | 0.7982    | + | 0.44631   |

| ZLine012 = |   |             |           |   |           |           |   |           |

| 1.4033     | + | 0.46872i    | -0.074081 | + | 1.7557i   | 0.12942   | + | 1.7271i   |

| -0.0028137 | - | 0.0045366i  | 0.47616   | + | 0.37439i  | 0.0031053 | + | 0.027711i |

| 0.0018292  | + | 0.00061591i | 0.03021   | + | 0.015469i | 0.50605   | + | 0.45359i  |

Figure 5.3: Phase and Sequence Impedance Matrices for Line from Node 675 to Node 692

Thus, when unbalanced loads are considered in a distribution system, sequence matrix analysis is not the best method to pursue when a simplified approach is desired. Thus, the Thevenin equivalent network method will be considered. Although this

method makes certain assumptions and simplifications, the results can be shown to be accurate within a desired tolerance, and will provide an excellent first-order approximation to determine whether additional studies are needed.

#### 6 OVERVOLTAGE CONDITIONS

As more distributed generation is integrated into distribution systems, the issue of lightning arrester overloading will become more significant and important. Thus, a simple analysis method to determine a range of voltages that the DG source can create on the distribution system is an excellent method to determine if the proposed DG will operate safely, or if an additional in-depth study or special protection scheme is needed.

To illustrate the problem, the examples explained in [2] will be summarized. First, the example of a simple, 3-bus power system is given below. The utility source (S), is connected to a distribution load bus (L) through a line connected to a delta-wye transformer (T). The sequence networks are given below in Figure 6.1 (left side). Notice that as explained in the symmetrical components overview in Appendix A, there is an open circuit in the zero-sequence network at the delta connection of the transformer. In the event of a single-line to ground fault as shown in Figure 6.1 (right side), the sequence networks become connected in series. Since the load is significantly higher resistance than the source and transmission line impedance, the vast majority of the fault current flows through the source and line, and thus the current through the load can be neglected, as is typical in fault most fault analysis studies.

Figure 6.1: Sequence Network Connections Pre-Fault and for Single Line to Ground Fault (Reprinted with Permission from [2])

Thus, when the utility source breaker opens, the fault path becomes interrupted, thus no current can flow, as shown in Figure 6.2 (left side). However, when a DG source is introduced into the distribution system, as shown in Figure 6.2 (right side), there is still a source connected to the fault, even when the utility breaker (S) opens. However, even though the DG is still connected to the fault, no fault current flows, since the zero sequence network impedance has an open circuit from the delta winding in the transformer. However, positive sequence current still flows through the load, since it still has a return path to the source through the load grounding.

Figure 6.2: Sequence Network Connections after Utility Breaker Opens, Without and With DG Source (Reprinted with Permission from [2])

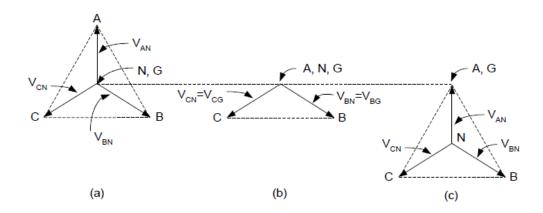

What is not shown in the figures above is the voltages on the unfaulted phases. During normal operation, the generator and y-grounded winding of the transformer provide a reference to ground for the system. Thus, the neutral point of the delta winding is in the center of the delta voltage triangle, as shown in Figure 6.3 (a). When there is a solidly-bolted fault on the system, the voltage of the faulted phase (in this case phase A), collapses to 0, and the utility grid holds the voltage of the unfaulted phases near the nominal unfaulted voltage values, as shown in Figure 6.3 (b). Once the utility breaker opens, the fault current ceases to flow, as explained above. If the fault is an arcing fault, the fault will clear, and the line will remain energized. However, if the fault

is permanent, with the worst case being a bolted fault, the apparent neutral shifts, as shown in Figure 6.3 (c). In this case, phase A is directly connected to ground, becoming the new ground reference point for the system. However, since no fault current is flowing, the phase-to-phase voltages are still maintained, so  $V_{ab}$ ,  $V_{bc}$ , and  $V_{ca}$  are still their nominal values. Since phase A is the new neutral reference point, phase B and C now have line-to-line voltages across any line-to-ground connected equipment, such as arresters, or single-phase transformers. In the case of a solidly connected fault, this voltage can rise to approximately 1.73 times the normal phase-to-ground voltage, causing damage to equipment such as lightning arresters [2].

Figure 6.3: (a) Normal Phasor diagram, (b) Line-to-Line Fault, (c) Apparent Neutral Shift (Reprinted with Permission from [2])

#### 7 LIGHTNING ARRESTER OVERVIEW

In order to protect against transient voltage spikes and surges, lightning or surge arresters are installed in numerous locations around power systems, such as on transformers, near critical loads, and on transmission towers. The lightning arresters that are of primary concern in the analysis presented in this paper are the arresters on the high side of the substation transformer, as well as the arresters on the transmission towers that are between the substation breaker and transmission line-end breakers. In particular, the arresters closer to the substation will experience higher voltage if there are additional loads tapped off the transmission line before the line-end breakers. The worst case scenario is considered: analyzing the high-side voltage assuming little to no current is flowing in the transmission line, resulting in little to no voltage drop across the transformer. Thus, the low side voltages can be used, and scaled to line-to-line voltages by multiplying by  $\frac{\sqrt{3}}{2}$ .

There are two main types of surge arresters installed in power systems, gapped and gapless types. Gapless, the most common arresters, are typically MOV, or Metal Oxide Varistors. These are typically made of a bulk semiconductor, such as zinc oxide, that can conduct significant current when the voltage across the arrester is above its rated voltage [11]. Unfortunately, most MOVs fail closed, i.e. when they break, they create a permanent fault on the system. MOVs can be protected by installing a series thermal fuse to prevent thermal runaway and catastrophic failure of the MOV.

Gapped arresters are the simplest and oldest overvoltage protective device, and are still found in telephone circuits today. The size of the gap determines the flashover voltage. However, since the ambient air is the dielectric material, the performance and spark voltage varies with atmospheric conditions, such as humidity. Also due to the physical presence of a spark or arc on the transmission line, gapped arresters are not used as commonly as MOV arresters.

Surge arresters are designed to protect against surge voltages associated with: lightning strikes as well as switching capacitor and equipment insulation failure. When lightning first strikes a transmission line, it quickly travels away from the point of stroke origin in both directions. The voltage magnitude of a lightning surge is typically very high, but the surge has a short duration, with typical durations of 1 to 20 microseconds, and the crest of the wave can be from 5 to 20 times the normal system voltage [12].

The rating of a piece of electrical equipment or surge protective device is call the Basic Insulation Level, or BIL. The BIL is determined by applying an impulse test and determining the crest value of the voltage wave.

The current industry practice is to select the surge arrester with the lowest conduction voltage to protect the desired equipment, while still having a satisfactory service life when connected to the power system [12]. For example, by examining Table 1 in [12], a design engineer could select a 108 kV or 120 kV MCOV (Maximum Continuous Operating Voltage) rated surge arrester for a 138kV transmission system, which would be 1.36 pu and 1.50pu, respectively, of line-to-neutral voltage.

Thus, an obvious solution to the lightning arrester overvoltage problem is to select lightning arresters that have an MCOV of 1.73pu or higher. This is the current industry practice for high impedance grounded or ungrounded systems, as shown in [12]. For example, the 138kV circuit examined before has the options of a 132kV and 144kV arrester, which is near or above the rated line-to-line voltage. If such an arrester were selected for a substation design, an islanded distribution system with DG would not overload these arresters. The drawbacks to this method is that this leaves the protected equipment more vulnerable to switching surges. Additionally, for existing distribution systems the surge arresters are already installed, and upgrading the arresters to higher MCOV ratings would be expensive and time consuming [3].

Thus, a better approach must be developed that allows the current industry arrester selection process to be continued, but still allows DG integration into distribution systems without incurring the significant additional cost of specialty protection systems for cases in which islanding is not needed or desired.

## 7.1 Temporary Overvoltages

Temporary overvoltages (TOV) are caused by numerous sources, but for the sake of this paper, distribution systems with connected DG sources are examined to be the cause of the temporary overvoltage. As discussed previously, a permanent line to ground fault on the high side of a delta-wye distribution transformer can cause a TOV of up to 1.73 pu of line-to-neutral voltage, corresponding to nominal line-to-line voltage.

As detailed in [13] and [14], a lightning arrester has four voltage transient stages that it must withstand: impulse or fast-front overvoltages, switching surges or slow-front

overvoltages, temporary overvoltages, and the highest system operating voltage. Industry practice is to clear a transmission-level fault within 20 cycles, with a backup clearing time of 30 to 60 cycles [15]. Thus, a TOV withstand of 1 second is used for the analysis in this paper. According to [12], the maximum withstand rating for a 1 second TOV event is 1.43 to 1.57 per unit of MCOV, depending on the type of lightning arrester. Thus, a distribution system voltage drop of 16% to 30% from nominal in needed to ensure that the lightning arresters are not overloaded. This voltage is taken at the high side of the distribution transformer when just the DG source is supplying the load, and the DG must be disconnected within 1 second to avoid damaging the lightning arresters. However, if the voltage drop on the distribution system is higher when the distribution grid is inadvertently islanded, then the distribution system can remain connected to the transmission system for a longer duration without damaging the lightning arresters. However, it is still advantageous to disconnect the distribution system from the faulted transmission system to avoid other damage to the grid, as well as prevent injury to line workers who may try and repair or remove the cause of the fault.

#### 8 SOLUTION METHODOLOGY

Given the drawbacks to the current methods available to analyze the high-side transformer voltage to determine if the transmission line lightning arresters will be overloaded, a simpler, first-level approach must be developed and tested. After discussion and deliberation, it was decided to create an equivalent network model with the substation as the output node. This allows for a simple calculation of the substation voltages using ohm's law and doesn't require the use of sequence networks, load flow calculations, or differential equations.

The benefits of using the Thevenin's Equivalent Circuit approach is that it is less dependent on the exact load placement locations in the system. Since the exact system load placement is unknown, as explained in section 3, the Thevenin equivalent method is a better choice for the analysis of this problem.

### **8.1** Equivalent System Impedance

Two methods were used to calculate Thevenin's Equivalent Impedance of the distribution circuit.

### 8.1.1 Test Current Injection

The first and primary method used to measure the equivalent circuit impedance was injecting a test current and measuring the resultant voltage [16]. The method is as follows: first deactivate the sources by setting their values to zero. This results in a short (zero voltage) for voltage sources, and an open circuit (zero current) for current sources. Then, a test current source is connected to the output node, and the voltage drop from

node one to node two of the current source is measured. Using ohm's law, the system impedance is calculated by dividing the measured voltage by the test injected current.

#### 8.1.2 *Voc/Isc*

As an alternative method, the open circuit voltage and short circuit current method was used to calculate the system impedance. Instead of deactivating the system sources, they were left connected and set to their nominal values. First, the steady-state system voltage was measured at the output node (the substation). Then, the output node was connected to ground, and the short circuit current was measured. Finally, ohm's law was again used to calculate the system impedance by dividing the open circuit voltage by the short circuit current.

## **8.2** Voltage Computation

Once the system impedance is calculated, the source voltage and a test load is used to compute the voltage at the output node, i.e. the substation. As shown in later in this thesis, several factors complicate the analysis and prevent an exact implementation of the methods described above. However, modifications are made as described in subsequent sections, and these changes allow for successful implementation and testing of the substation voltage using Thevenin's equivalent circuit method.

### 9 TEST SYSTEMS

### 9.1 IEEE 4 Node Test Feeder

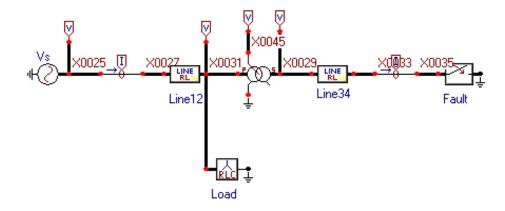

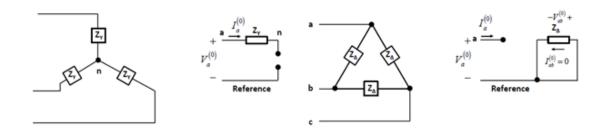

The first step in testing the validity of the Thevenin equivalent circuit approach was to examine the transient voltage waveforms to determine if they had significant impact on the voltages seen across the lightning arresters. To verify this, the IEEE 4 node test feeder [17] was modeled and tested in the EMTP transient program, ATP. This model is shown in Figure 9.1 The IEEE 4 node case is a small distribution system consisting of an infinite bus representing the transmission grid, a delta-wye transformer, and two short, nearly symmetrical distribution lines. The main purpose of this distribution system is to test simulation models of transformers when there is an unbalanced load on the distribution system. However, this system worked well to examine the transient voltages caused by a line-to-ground fault on the high side of a delta-wye transformer, as well validate the line-to-line overvoltage on the lightning arresters, as described in section 6.

Figure 9.1: ATP Simulation of IEEE 4 Node System Model

Several modifications were made to the system to make it compatible with the desired outcome. First, a DG source was connected on the low side of the distribution transformer and the load was connected to the low side of the transformer, as shown in Figure 9.1. As mentioned in Appendix B, the DG source was first simulated using an ideal voltage source with no source impedance to establish a worst-case post fault transformer high side voltage. During later simulations as summarized in, the ideal voltage source was replaced by a synchronous generator that used all of the default ATP parameter settings, except the voltage was changed to 12.47 kV (line-to-line) and the power rating to 6 MVA to match the power rating of the transformer. The results from these simulations are summarized in section 10.1.1 and detailed in Appendix B.

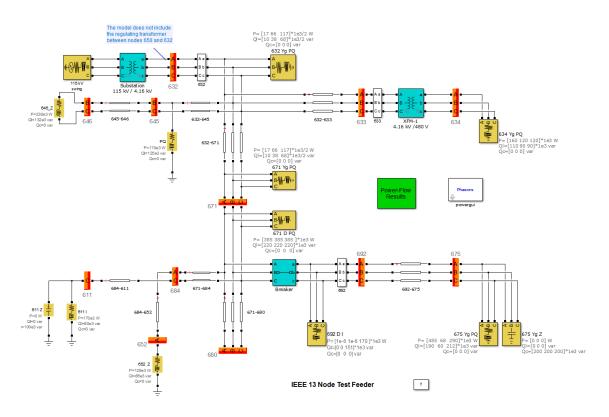

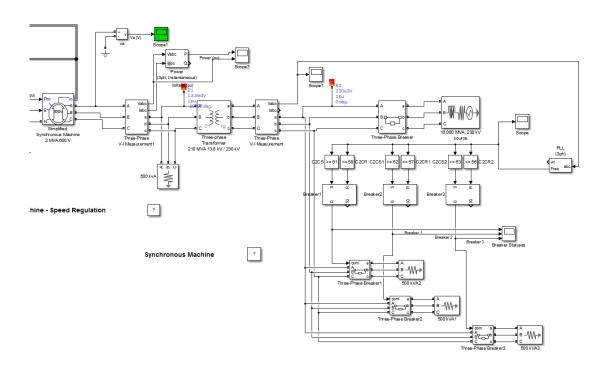

### 9.2 IEEE 13 Node Test Feeder

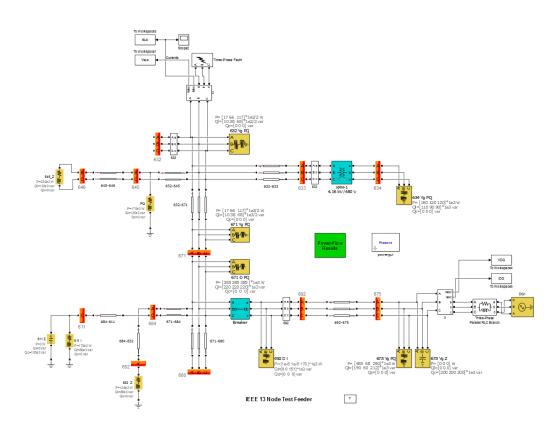

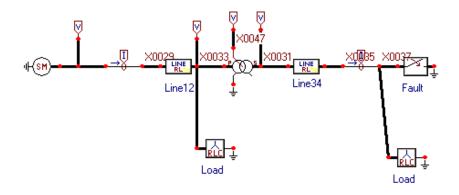

After the transient and steady state voltages were examined using the IEEE 4 node feeder, a larger system, the IEEE 13 node test feeder, was utilized to examine the

effect of DG placement and load values on the substation voltage. The characteristics of the IEEE 13 node feeder [18] are that the system is operated at 4.16kV, the lines are short and relatively highly loaded, and the system has unbalanced loads and shunt capacitor banks. A Simulink model of the IEEE 13 node test feeder is shown in Figure 9.2.

Figure 9.2: Simulink Simulation of the IEEE 13 Node Feeder System

### 9.3 Solar and Wind SG Source Models

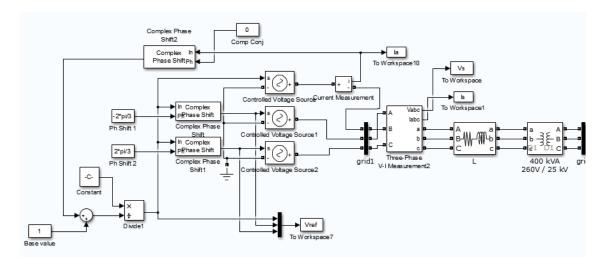

Once the test systems were established, a simple model of power electronic interfaced DG sources was developed. Current industry practice is to model such sources as current-limited (to 1.5 pu) voltage sources to reflect the regulating effect of the power electronics. Thus, a simple model of these sources is a constant power source, since the power electronic interfaces can only supply a maximum amount of power to the system.

Since the distribution system loads in Simulink are modeled as constant impedance loads, a constant power source is created using the following approach:

Using the measured current as feedback, a Simulink controlled voltage source is varied to supply constant power to the system. A Simulink model of the proposed system is shown below in Figure 9.3. Since two quantities are fixed, the load impedance Z and the power output of the source, there need to be two degrees of freedom to satisfy Ohm's law and the electrical power equation. Thus, these two equations, P=IV and V=IZ are used to calculate the voltage and current produced by the power-limited DG source.

Then, these voltages and currents can be used to determine the voltage drop across the network and thus the voltage at the substation.

Figure 9.3: Simulink Constant Power Model of Power Electronically Interfaced Generation

## 9.4 Load Shedding Simulations

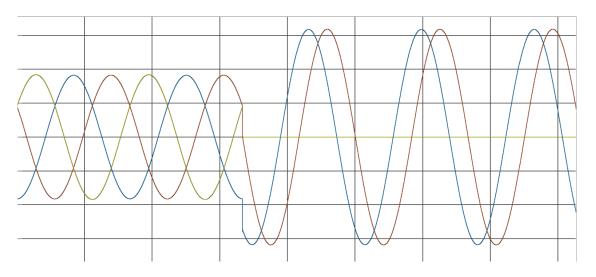

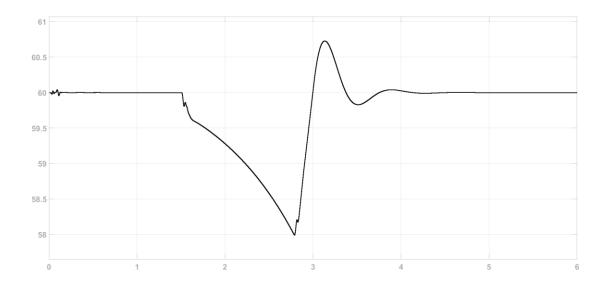

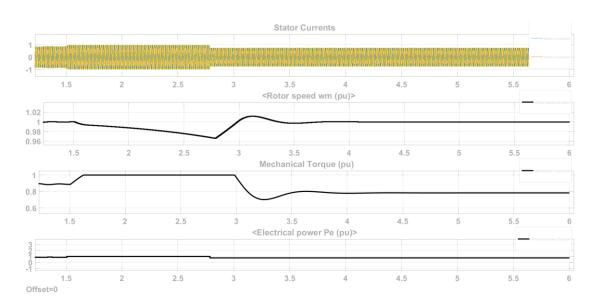

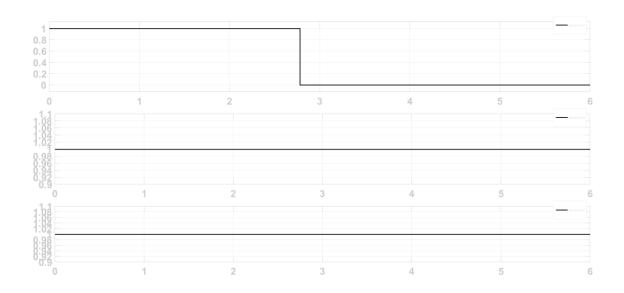

Once the substation voltage has been determined for the worst-case scenario of DG generation levels and load levels, the proper protective relaying scheme is selected to properly island the distribution system. This is further discussed in section 11.1. If the load levels are greater than the current DG maximum capacity, load shedding must be utilized to properly match generation and load. This is done using simulated power-frequency droop control for power electronic interfaced generation, and underfrequency relays for loads as further detailed in 11.2.1. Since power electronic interfaced generation has a very fast response time compared to traditional rotating machine based generation [19], a modified load-shedding simulation needed to be created, with a reduced equivalent "inertia" to properly simulate the implemented droop control. Thus, a small synchronous machine example in Simulink was used that has a low inertia, as

shown in Figure 9.4. A phase locked loop was used to determine the system frequency, and once it dropped below a pre-established threshold, the feeder breakers were tripped one at a time until the system frequency stabilized. The results of this simulation are shown in Appendix D.

Figure 9.4: Under Frequency Load Shedding Simulation in Simulink

#### 10 RESULTS

First, the voltage transients were examined to determine if they were insignificant enough for a steady-state analysis to fully characterize the system. Then, the Thevenin's equivalent circuit method was used to calculate the substation voltages, and the results are tabulated in this section.

### **10.1 Voltage Transients**

#### 10.1.1 IEEE 4 Node Test Feeder

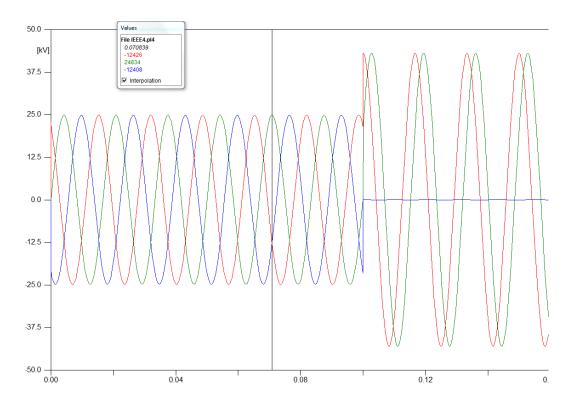

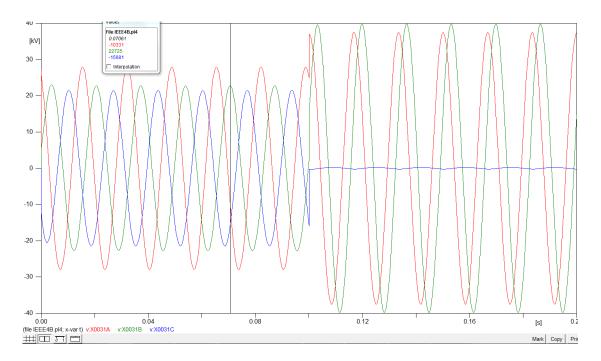

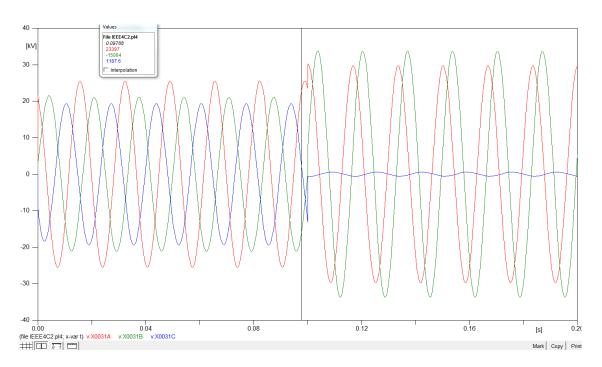

As discussed in section 9.1, the IEEE 4 node test feeder was used to verify the transient and steady state voltage levels. First, a base case was established for the balanced load specified in [17] by simulating a single-phase to ground fault on the high side of the transformer. The voltage at the high side of the transformer is shown below in Figure 10.1. To aid in viewing the results, I set the peak voltage value of the DG source to be the nominal line-to-line voltage. Thus, the pre-fault voltage seen across the lightning arresters (connected line to neutral) is 24.83 kV, and the post fault voltage is 43 kV, corresponding to the line-to-line voltage of the pre-fault condition. This validates the assertions from [3], [4] that a bolted line to ground fault on an ungrounded (delta) system results in an approximately 1.73 pu (line-to-line voltage) overvoltage to be seen on the non-faulted phases.

Also, the transient voltage spikes in Figure 10.1 are noticeably insignificant, thus showing that a steady-state post fault voltage fully characterizes the behavior of the system. As seen below, there is no overshoot or significant ramping from the pre-fault

to post-fault voltage levels on the system. This is most likely because no fault current flows in the system, as explained in section 6.

Figure 10.1: Voltage Transients for Single Line to Ground Fault

After this base case was established, several additional simulations were run with varying levels of unbalanced load. As detailed in Appendix A, adding additional load to the system reduced the high side voltage by causing a voltage drop across the distribution lines and the transformer, thus validating that there exists a certain load level or DG source amount that reduces the high side voltage so that the lightning arresters are

no longer overloaded in under 1 second, thus allowing time for the substation breaker to trip and the distribution system to be islanded.

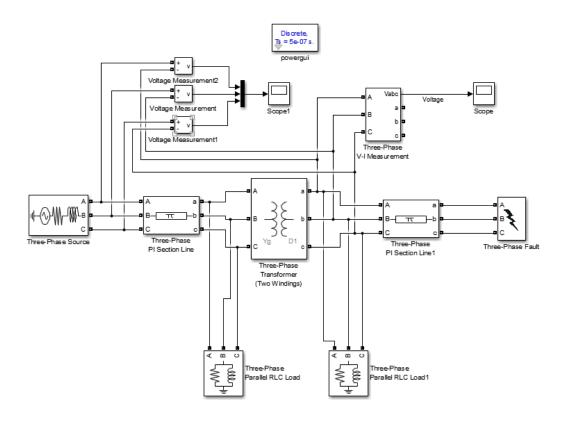

# 10.1.2 Simulink Verification

The IEEE 4 node feeder was also modeled and simulated in Simulink's Simscape Power Systems. Figure 10.2 below shows the system along with the voltage measurements. The duplicated load configuration from Appendix A was utilized, and a single-line to ground fault was simulated on the high side of the transformer.

Figure 10.2: Simulink Model of IEEE 4 Node System

#### 10.1.3 IEEE 13 Node Test Feeder

The IEEE 13 node test feeder was utilized to determine the voltage levels at the substation when different types of DG (solar, wind, microturbine) were placed at different locations on the distribution grid. The results for several case studies were tabulated below, however, the application is that a utility company can successfully create a simple model of their distribution systems and analyze the voltage impact of a proposed DG interconnection.

The following observations were made: for a system such as the IEEE 13 node case where the line impedance is several of orders of magnitude below the load impedance, the exact placement of the load on the system is less important than accurately estimating the worst case load levels and amount of imbalance. Also, the asymmetrical distribution lines along with the mutual coupling create problems for the Thevenin equivalent network analysis, but this can be remedied by techniques explained later.

First, the transient voltage waveforms were observed as in the IEEE 4 node system. A single-line to ground fault was simulated on the high side of the substation transformer, and the voltage waveforms for are shown below in Figure 10.3. This verified that the transient voltage spikes are negligible, and established that the steady state voltage values can be utilized to determine the highest voltage seen across the lightning arresters.

Figure 10.3: Simulink Voltage Transients for Single Line to Ground Fault, IEEE 13

Node System

## 10.2 Thevenin's Equivalent Circuit

After it was determined that the voltage transients were negligible, the equivalent circuit impedance was determined for the distribution system, and the substation voltages were calculated to determine if the Thevenin Equivalent would produce sufficiently accurate voltages for a first-order approximation of the distribution system voltages. The transformer low-side voltage was calculated, which can be multiplied by  $\sqrt{3}$  to get the high side voltage in the case of a high side single line-to-ground fault. This is further explained in section 6.

## 10.2.1 Test Current Injection: Simulink Approach

To implement the test current injection method described in section 8.1.1, Simulink's Simscape Power Systems impedance measurement block was used. It uses a two-input block with current source Iz connected internally between the two inputs. The

terminals of the impedance to be measured were externally connected between the two inputs, and a 60 Hz test current was injected into the impedance network. When calculating the impedance, the impedance measurement block automatically deactivates the sources as described in section 8.1.1, then divides the voltage measured across the impedance network.

For the IEEE 13 node distribution system, one terminal of the impedance measurement block was connected to the output node (the substation, node 632), and the other terminal was connected to ground, thus measuring the impedance of the distribution system from the reference output node of the substation, "looking into" the distribution network, as shown in Figure 10.4.

Figure 10.4: System Impedance Measurements of IEEE 13 Node System

However, the impedance measurement block doesn't properly take mutual coupling into account. This was seen when the impedance of only A-phase of the distribution network was measured independently, then three impedance measurement blocks were connected simultaneously to the system. In both cases, the impedance was the same to 13 digits, i.e. when the DG source was connected to node 675, the system impedance in both cases was 0.2352606557 + 0.4431160283i. When there was a substantial imbalanced between the phase load levels, this resulted in inaccuracies in the voltage levels as calculated using the equivalent circuit impedances, which can be remedied, as shown later in the paper.

### 10.2.2 Voc/Isc: Simulink Simulations

To implement the Voc/Isc method as described in section 8.1.2, a Simulink model was constructed with an example shown in Figure 10.5. The DG source (in this case, a simple model of a microturbine) was left connected to a distribution node, and a 3-phase to ground fault with negligible fault resistance was triggered on the substation node at t= 3 cycles. The Simulink powergui simulation block was set to run in phasor mode, and voltage and current measurement blocks were connected at the substation. The open circuit voltage was recorded from the pre-fault values, and the short circuit current values were measured during the fault period. Because in some cases the current and voltage values had an angle difference of more than 90 degrees, the calculated resistance was negative, i.e. had an angle of more than 90 degrees. As shown later in the results section, this resulted in higher voltage values calculated using the equivalent network approach.

For example, the Simulink model of the IEEE 4 node feeder in section 9.1 gave a calculated impedance of -4.1 + j12.24 ohms. This was because the open circuit voltage was  $24.825 \angle -0.149$  kV, and the short circuit current was  $1924 \angle -108.5475$  amps, yielding an impedance angle of 108.39 degrees.

Figure 10.5: Voc/Isc Equivalent Network Measurement Model

## 10.2.3 Assumptions and Simplifications

The benefit of using the Thevenin's Equivalent method is that it created 3 simple, single-phase, decoupled systems that could be analyzed separately. However, the mutual coupling between distribution lines was computed at one particular instant, and the result was lumped into the phase impedances of each line. For the test current injection method, this resulted in a lower system impedance, as verified by the results later in this paper. This is because the test current method didn't take the mutual coupling into account, as shown in section 10.2.1. Also, for the Voc/Isc method, the mutual coupling was computed for one instant during the 3-phase to ground fault, and thus was not properly considered. However, as shown later in this paper, variations in the load are used to correct for these assumptions and create a more accurate voltage profile.

### **10.3 Substation Voltages**

The IEEE 13 node system is used to test and measure the low-side substation voltages. For the simulations, a 5 kVA microturbine is used as the DG source to match the power rating of the transformer. Based on typical values from [20], the reactance X was set to be 0.17 pu and the X/R ratio is 25. This DG source was connected to nodes 675, 680 and 633, respectively, and the substation voltages are listed in following subsections. Since the sum of the 3 phase total system load, (real load and reactive load minus shunt capacitors) was only 3.74 kVA, the substation voltages are fairly close to 1 pu.

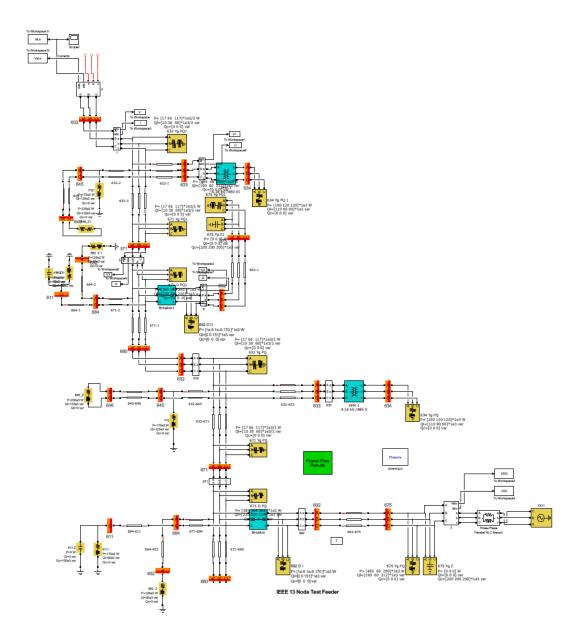

Thus, to further test the effect of the system load being greater than the DG source capacity, the IEEE 13 system was duplicated in both series and parallel to approximate a larger system. For the series duplication, the substation (node 632) of a copy of the IEEE 13 node system was connected to node 680 of the original system, as shown in Figure 10.6.

Figure 10.6: IEEE 13 Node System, Series Configuration

The parallel duplication took a copy of the IEEE 13 node system and connected the two substations (node 632) together, thus creating two parallel systems. Since the DG was only connected to the original distribution system, the second parallel system

was treated as a parallel adjacent feeder. For the Thevenin equivalent calculations, the impedance of the parallel system (feeder) was measured using the Simulink impedance measurement tool, and is recorded below in Table 10.1. Also, if such an impedance were connected to the original system's substation, the equivalent power value of the corresponding constant impedance load is also given. Notice the substantial imbalanced between the equivalent powers of phases A and C, and phase B, as will be discussed later in this paper.

| IEEE 13 node system     | Phase A        | Phase B        | Phase C        |

|-------------------------|----------------|----------------|----------------|

| Impedance Without DG    | 5.0095+1.8523i | 7.7655+2.7371i | 5.2413+1.8498i |

| <b>Equivalent Power</b> | 3039+1124i     | 1982+699i      | 2936+1036i     |

**Table 10.1: IEEE 13 Node System Equivalent Impedances**

Another interesting result from the equivalent network approach is the nearly negligible impact of the load location on the feeder with DG on the calculated substation voltage, as detailed later in this paper. This is because the total load per phase is on the order of 12 ohms (magnitude), whereas the phase impedance of the distribution network (with the DG source connected to node 675) is on the order of 0.5 ohms magnitude. The effect of the system load on the measured network impedances can be further observed in Table C.1 in Appendix C. However, this effect is very beneficial and desirable, because the exact locations of the worst-case loads for the actual distribution system to

be simulated are difficult to determine, and thus approximations and combined loads must be used.

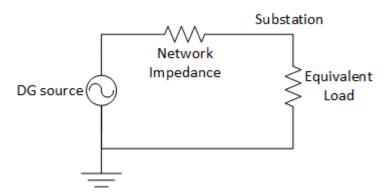

To verify the Thevenin equivalent method, an excel spreadsheet was created to calculate the substation voltages for several different DG placement locations, system configurations and load levels. Thevenin's equivalent circuit, shown in Figure 10.7, was simulated, and Ohm's law was utilized to calculate the voltages at the substation. The network impedance was calculated using the methods described in section 8.1, and an equivalent load for the different system configurations was calculated as described below.

Figure 10.7: Thevenin Equivalent Network Model

For the first 3 test cases, the normal IEEE 13 node system configuration was utilized (Figure 9.2), with the DG source connected to three different nodes, 633, 675

and 680, respectively. The results are shown in the tables of results below. Several values for the equivalent load were used, as summarized in Table 10.2 below.

To compare the accuracy of the Thevenin's equivalent circuit voltages, a complete voltage simulation of the IEEE 13 node system was conducted in Matlab's Simscape Power Systems. The phasor analysis was utilized with the default solver parameters set from the IEEE 13 node system. The results from these simulations are listed in the Measured Voltage columns of the tables of results below.

| Equivalent      | Base Load      | Base Load     | Base + Test | Test Load |

|-----------------|----------------|---------------|-------------|-----------|

| Load values for | Configuration  | Configuratio  | Load        | only      |

| first 3 cases   | (without caps) | n (with caps) |             |           |

| A-Phase         | 1175+606i      | 1175+416i     | 2675-1016i  | 1500+600i |

| B-Phase         | 1039+627i      | 1039+465i     | 2539-1065i  | 1500+600i |

| C-Phase         | 1252+753i      | 1252+521i     | 2752-1121i  | 1500+600i |

**Table 10.2: IEEE 13 Node System Load Levels for Various Configurations**

## 10.3.1 Original IEEE 13 Node System Configuration

For the first 3 tables (Table 10.3, Table 10.4 and Table 10.5), the first three columns are the calculated voltages when only an equivalent lumped system load was used as the equivalent load in Figure 10.7. The base load configuration was computed by taking the sum of the IEEE 13 node system loads as specified in [18] and connecting them directly to the substation node as part of the Equivalent Load in Figure 10.7. Two different configurations were used: one subtracting the connected shunt capacitor values

from the total reactive power load (with caps), and the other load configuration did not consider the effects of the connected capacitors on the system (without caps).

Then, a balanced test load (last column of Table 10.2) was connected to the substation and added to the equivalent load, and the measured network impedance was used as the network impedance. The results are listed in the last 3 columns of the tables of results.

The results were inconclusive as to whether the system load with or without the connected capacitors yielded a more accurate result, as seen from the error percentages in the first 3 tables. However, since the total system load (3.74 kVA) was below the DG maximum capacity (5 kVA) and the total including the test load (8.59 kVA) was only 1.72 pu of the DG capacity, the substation voltage for the most extreme scenario experience a 5% maximum drop. These results indicate that the lightning arrestors would be overloaded in less than 1 second, so more advanced protective relaying strategies would be needed to ensure the distribution system is islanded quickly to avoid overloading the lightning arresters, as detailed in section 11.1.

Also, there exists a slight imbalance in the system loads as seen in Table 10.2. However, since the maximum imbalance is between phases B and C, and is only 250 VA (18%), the voltage difference between the three phases is fairly small. However, once the load imbalance becomes more pronounced, the discrepancies between the measured and calculated voltages become greater.

Thus, for a system without a large magnitude of load imbalances such as the IEEE 13 node system with load impedances much greater than line impedances, the

Thevenin equivalent method is an excellent approximation for determining the substation voltages. This saves time and resources since a full sequence network model or transient model doesn't need to be constructed.

| Calculated | Base Load | Base      | Measured    | Base + | Test  | Meas-   |

|------------|-----------|-----------|-------------|--------|-------|---------|

| Substation | Config-   | Load      | Voltage (no | Test   | Load  | ured    |

| Voltage    | uration   | Config-   | test load)  | Load   | only  | Voltage |

|            | (without  | uration   |             |        |       |         |

|            | caps)     | (w/ caps) |             |        |       |         |

| A-Phase    | 0.990     | 0.991     | 0.981       | 0.982  | 0.988 | 0.972   |

| B-Phase    | 0.991     | 0.992     | 0.989       | 0.983  | 0.989 | 0.980   |

| C-Phase    | 0.988     | 0.990     | 0.974       | 0.977  | 0.988 | 0.964   |

| Error      |           |           |             |        |       |         |

| A-Phase    | 0.85%     | 0.98%     |             | 0.96%  | 1.57% |         |

| B-Phase    | 0.22%     | 0.32%     |             | 0.28%  | 0.87% |         |

| C-Phase    | 1.44%     | 1.60%     |             | 1.32%  | 2.44% |         |

Table 10.3: DG Source Connected to Node 633

| Calculated<br>Substation<br>Voltage | Base Load<br>Config-<br>uration | Base<br>Load<br>Config- | Measured<br>Voltage (no<br>test load) | Base +<br>Test<br>Load | Test<br>Load<br>only | Measured<br>Voltage<br>(test load) |

|-------------------------------------|---------------------------------|-------------------------|---------------------------------------|------------------------|----------------------|------------------------------------|

| Voltage                             | (without                        | uration                 | test load)                            | Load                   | omy                  | (test load)                        |

|                                     | caps)                           | (w/ caps)               |                                       |                        |                      |                                    |

| A-Phase                             | 0.969                           | 0.974                   | 0.978                                 | 0.940                  | 0.965                | 0.956                              |

| B-Phase                             | 0.972                           | 0.976                   | 0.969                                 | 0.943                  | 0.967                | 0.952                              |

| C-Phase                             | 0.966                           | 0.972                   | 0.973                                 | 0.940                  | 0.967                | 0.951                              |

| Error                               |                                 |                         |                                       |                        |                      |                                    |

| A-Phase                             | 0.92%                           | 0.46%                   |                                       | 1.62%                  | 1.00%                |                                    |

| B-Phase                             | 0.25%                           | 0.63%                   |                                       | 0.91%                  | 1.54%                |                                    |