# ULTRA-LOW POWER TRANSMITTER AND POWER MANAGEMENT FOR INTERNET-OF-THINGS DEVICES

#### A Dissertation

by

## JORGE EDGAR ZARATE ROLDAN

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Edgar Sánchez-Sinencio

Committee Members, Kamran Entesari

Aniruddha Datta Duncan M. Walker

Head of Department, Miroslav M. Begovic

May 2016

Major Subject: Electrical Engineering

Copyright 2016 Jorge Edgar Zarate Roldan

#### **ABSTRACT**

Two of the most critical components in an Internet-of-Things (IoT) sensing and transmitting node are the power management unit (PMU) and the wireless transmitter (Tx). The desire for longer intervals between battery replacements or a completely self-contained, battery-less operation via energy harvesting transducers and circuits in IoT nodes demands highly efficient integrated circuits. This dissertation addresses the challenge of designing and implementing power management and Tx circuits with ultra-low power consumption to enable such efficient operation.

The first part of the dissertation focuses on the study and design of power management circuits for IoT nodes. This opening portion elaborates on two different areas of the power management field: Firstly, a low-complexity, SPICE-based model for general low dropout (LDO) regulators is demonstrated. The model aims to reduce the stress and computation times in the final stages of simulation and verification of Systems-on-Chip (SoC), including IoT nodes, that employ large numbers of LDOs. Secondly, the implementation of an efficient PMU for an energy harvesting system based on a thermoelectric generator transducer is discussed. The PMU includes a first-in-its-class LDO with programmable supply noise rejection for localized improvement in the suppression.

The second part of the dissertation addresses the challenge of designing an ultralow power wireless FSK Tx in the 900 MHz ISM band. To reduce the power consumption and boost the Tx energy efficiency, a novel delay cell exploiting current reuse is used in a ring-oscillator employed as the local oscillator generator scheme. In combination with an edge-combiner PA, the Tx showed a measured energy efficiency of 0.2 nJ/bit and a normalized energy efficiency of 3.1 nJ/(bit·mW) when operating at output power levels up to -10 dBm and data rates of 3 Mbps. To close this dissertation, the implementation of a supply-noise tolerant BiCMOS ring-oscillator is discussed. The combination of a passive, high-pass feedforward path from the supply to critical nodes in the selected delay cell and a low cost LDO allow the oscillator to exhibit power supply noise rejection levels better than –33 dB in experimental results.

# **DEDICATION**

Para Mariana, que creyó en mi, caminó a mi lado y me levantó en cada caída durante esta aventura sin pedirme nada a cambio.

Para Jacobo, que me quitó todos mis miedos cuando me sonrió.

Para mis padres, Jorge y Silvia, quiénes me enseñaron con su ejemplo que nada es inalcanzable.

#### **ACKNOWLEDGEMENTS**

I want to express my sincere gratitude to my advisor Dr. Edgar Sánchez-Sinencio, his guidance and vision were instrumental in my growth as a person and as a professional. His contagious enthusiasm, willingness to teach and learn from every possible topic are a source of inspiration. I thank him for believing in my ideas and for seeing something in me that at the time I couldn't see.

I would like to thank Dr. Kamran Entesari, Dr. Aniruddha Datta, and Dr. Duncan Walker for serving as my committee members. Special thanks to academic advisors and staff of the Electrical and Computer Engineering Department: Tammy Carda, Jeanie Marshall, Melissa Sheldon, and Ella Gallagher. I can't even remember how many times they helped me during my stay at Texas A&M, the ECEN department would not be the same without all of them.

I am grateful to the Intel Radio Integration Labs members and former members: Manuel Guzman, Arturo Veloz, Sergio Solis, Yorgos Palaskas, Stefano Pellerano, Ashoke Ravi, Paolo Madoglio, and Kailash Chandrashekar for their friendship, mentorship, and for believing that a small town kid from Mexico could design integrated circuits.

During my studies at the Analog and Mixed Signal Center, I was truly blessed to become friends with some of the best and smartest persons I have met. My deepest gratitude goes to Miguel Rojas, Salvador Carreon, and Joselyn Torres with whom I shared highs and lows but were always there for me. I also thank the many friends and colleagues

with whom I worked in the multiple research projects during my doctoral studies: Mengde Wang, Adrian Colli, Carlos Briseño, Fernando Lavalle, Jyaji Jin, Congyin Shi, Omar ElSayed, Didem Turker, Xiaosen Lui, Amr Abuellil, Mo'men Mansour, Alfredo Perez, and Alfredo Costilla.

I also want to thank the National Council for Science and Technology of Mexico, Intel Corporation, and Silicon Laboratories for economic support throughout my studies.

Finally and most importantly, I would like to thank my family, if not for the example and upbringing full of unconditional love, support and understanding from my parents Jorge and Silvia, I would never have come to Texas A&M. To my sister Fanny, for always making me feel the greatest even when I had lost my way. Thanks to my son Jacobo, who reminds me every day what the important things in life are. Lastly, thanks to my wife Mariana. Her love, constant support, and positive attitude got me through the toughest times. Thank you for being my rock, the truth is that every time you thought I was holding your hand, it was really you holding mine.

# TABLE OF CONTENTS

|                                                                                    | Page     |

|------------------------------------------------------------------------------------|----------|

| ABSTRACT                                                                           | ii       |

| DEDICATION                                                                         | iv       |

| ACKNOWLEDGEMENTS                                                                   | v        |

| TABLE OF CONTENTS                                                                  |          |

|                                                                                    |          |

| LIST OF FIGURES                                                                    | ,X       |

| LIST OF TABLES                                                                     | XV       |

| CHAPTER I INTRODUCTION                                                             | 1        |

| 1.1 The Internet-of-Things (IoT)                                                   | 1        |

| <ul><li>1.2 Inside an IoT node</li><li>1.3 Research scope and motivation</li></ul> |          |

| CHAPTER II A COMPREHENSIVE MODEL FOR CMOS LOW DROPOUT VOLTAGE REGULATORS           | 15       |

| 2.1 Introduction                                                                   |          |

| 2.1.1 Low dropout regulators: Basics                                               |          |

| 2.1.2 Transfer-function-based LDO model                                            |          |

| 2.2 Proposed LDO model                                                             |          |

| 2.3 LDO model implementation                                                       | 30<br>20 |

| 2.3.2 EA model                                                                     |          |

| 2.3.3 Frequency compensation scheme (FCS) and β                                    |          |

| 2.3.4 Special considerations for PSR modeling                                      |          |

| 2.4 Model simulation results for different LDO structures                          |          |

| 2.4.1 Model for the general LDO structure                                          |          |

| 2.4.2 Model for a high PSR LDO                                                     |          |

| 2.4.3 Model for a fast transient LDO                                               |          |

| 2.5 Simulation time comparison.                                                    |          |

| 2.6 Conclusion.                                                                    |          |

| CHAPTER   | III A POWER MANAGEMENT UNIT WITH 40 dB SWITCHING-                 |     |

|-----------|-------------------------------------------------------------------|-----|

| NOISE-SU  | PPRESSION FOR A THERMAL HARVESTING ARRAY                          | 48  |

| 3.1 Ir    | ntroduction                                                       | 49  |

|           | nergy harvesting power management unit                            |     |

|           | nergy harvesting power management unit front-end                  |     |

| 3.3.1     | Input resistance matching                                         |     |

| 3.3.2     | =                                                                 |     |

| 3.3.3     | Zero current switching scheme                                     |     |

| 3.4 E     | nergy harvesting power management unit back-end                   |     |

|           | Basic CL-LDO                                                      |     |

| 3.4.2     | Proposed CL-LDO                                                   | 65  |

| 3.4.3     | CL-LDO stability                                                  | 68  |

| 3.4.4     | CL-LDO PSR                                                        | 72  |

| 3.5 S     | ense-and-control loop                                             | 78  |

| 3.5.1     | Look-up table contents optimization                               | 79  |

| 3.6 N     | leasurements                                                      | 82  |

| 3.7 C     | onclusion                                                         | 87  |

| CHADTED   | WANTIETH LOW DOWED BY LIEGG WIDELEGG                              |     |

|           | IV AN ULTRA-LOW POWER PLL-LESS WIRELESS ITER FOR IOT APPLICATIONS | 90  |

| INANSIVII | TER FOR IOT AFFLICATIONS                                          | 09  |

| 4.1 Ir    | ntroduction                                                       | 90  |

|           | roposed Tx architecture                                           |     |

| 4.2.1     | •                                                                 |     |

|           | RO analysis and design                                            |     |

|           | ower amplifier and frequency correction scheme                    |     |

| 4.4.1     | Pre-amplifiers and edge-combiner power amplifier                  |     |

| 4.4.2     | Digital calibration scheme for LO frequency correction            |     |

| 4.5 E     | xperimental results                                               |     |

|           | onclusions                                                        |     |

| CHA DEED  | WAR BOOMER BRIC COOK LATER WITH EFFRORWARD                        |     |

|           | V A BICMOS RING OSCILLATOR WITH FEEDFORWARD                       | 105 |

| PATHFOR   | IMPROVED POWER SUPPLY REJECTION                                   | 127 |

| 5.1 T     | he problem of supply noise in ring oscillators                    | 128 |

|           | BiCMOS delay cell for ring oscillators                            |     |

|           | ow cost feedforward path                                          |     |

|           | leasurement results.                                              |     |

|           | onclusions                                                        |     |

|           | VI CONCLUSIONS AND FUTURE WORK                                    |     |

|           |                                                                   |     |

|           | ummary of research.                                               |     |

| 6.2 A     | reas for future work                                              | 152 |

| REFERENCES | 5 | 4 |

|------------|---|---|

|            |   |   |

# LIST OF FIGURES

| Fig. 1. Internet-of-Things network diagram example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                          | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 3. Examples of energy transducer and a transformer-rectifier for AC-DC voltage conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fig. 1. Internet-of-Things network diagram example.                                                                                                                                                                                                                                      | 2    |

| voltage conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Fig. 2. Wireless sensor network/IoT node description.                                                                                                                                                                                                                                    | 3    |

| Fig. 5. Conceptual diagram of the energy extraction and conditioning chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                          | 4    |

| Fig. 6. Typical circuit blocks used in the analog front-end for sensor signal readout and acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fig. 4. Examples of circuits for efficient energy extraction from the transducer                                                                                                                                                                                                         | 5    |

| readout and acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fig. 5. Conceptual diagram of the energy extraction and conditioning chain                                                                                                                                                                                                               | 6    |

| Fig. 8. Building blocks of an IoT node addressed in the dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          | 7    |

| Fig. 9. Examples of LDOs use in Systems-on-Chip: a) Increase isolation between analog and digital circuitry, b) Generate multiple power domains, and c) Improve point-of-load regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Fig. 7. Snapdragon's conceptual block diagram [8]                                                                                                                                                                                                                                        | 8    |

| analog and digital circuitry, b) Generate multiple power domains, and c) Improve point-of-load regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fig. 8. Building blocks of an IoT node addressed in the dissertation.                                                                                                                                                                                                                    | 10   |

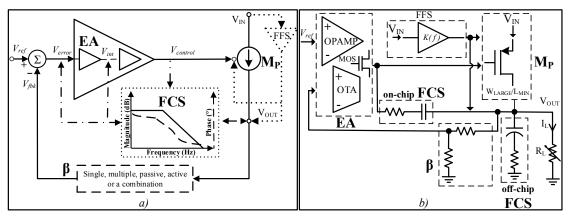

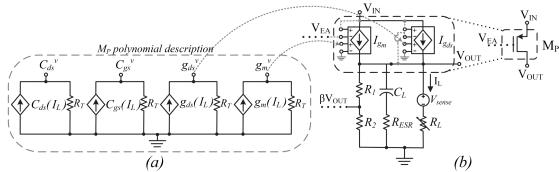

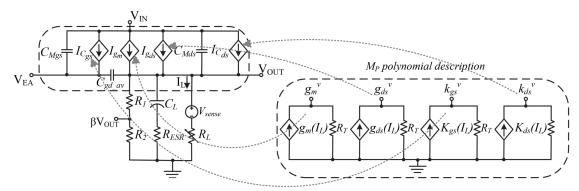

| <ul> <li>Fig. 11. TF-based model of an LDO using a two-stage EA.</li> <li>Fig. 12. Implementation of the g<sub>m</sub>-parameter to model M<sub>P</sub>.</li> <li>Fig. 13. M<sub>P</sub> characterization results: (a) M<sub>P</sub>'s g<sub>m</sub> and g<sub>ds</sub> in function of I<sub>L</sub> during a I<sub>Lmin</sub> to I<sub>Lmax</sub> DC sweep; (b) M<sub>P</sub>'s C<sub>gs</sub>, C<sub>gd</sub>, C<sub>gb</sub> and C<sub>ds</sub> in function of I<sub>L</sub> during a I<sub>Lmin</sub> to I<sub>Lmax</sub> DC sweep; (c) I<sub>L</sub> transient event (step) with different t<sub>rise</sub> for M<sub>P</sub> transient characterization, and (d) M<sub>P</sub> static and dynamic g<sub>m</sub> comparison.</li> <li>Fig. 14. a) LDO conceptual sub-block identification for modeling; b) Typical devices and circuits implementing the sub-blocks.</li> <li>Fig. 15. M<sub>P</sub> model and partial (g<sub>m</sub> and g<sub>ds</sub>) implementation: a) M<sub>P</sub> polynomial description using PCCS (Step 1 in Fig. 12); b) g<sub>m</sub><sup>v</sup> and g<sub>ds</sub><sup>v</sup> weighting and contributions towards I<sub>L</sub> (I<sub>gm</sub> and I<sub>gds</sub>) using two 2-port PVCCS</li> </ul> | analog and digital circuitry, b) Generate multiple power domains, and c)                                                                                                                                                                                                                 | 17   |

| <ul> <li>Fig. 12. Implementation of the g<sub>m</sub>-parameter to model M<sub>P</sub>.</li> <li>Fig. 13. M<sub>P</sub> characterization results: (a) M<sub>P</sub>'s g<sub>m</sub> and g<sub>ds</sub> in function of I<sub>L</sub> during a I<sub>Lmin</sub> to I<sub>Lmax</sub> DC sweep; (b) M<sub>P</sub>'s C<sub>gs</sub>, C<sub>gd</sub>, C<sub>gb</sub> and C<sub>ds</sub> in function of I<sub>L</sub> during a I<sub>Lmin</sub> to I<sub>Lmax</sub> DC sweep; (c) I<sub>L</sub> transient event (step) with different t<sub>rise</sub> for M<sub>P</sub> transient characterization, and (d) M<sub>P</sub> static and dynamic g<sub>m</sub> comparison.</li> <li>Fig. 14. a) LDO conceptual sub-block identification for modeling; b) Typical devices and circuits implementing the sub-blocks.</li> <li>Fig. 15. M<sub>P</sub> model and partial (g<sub>m</sub> and g<sub>ds</sub>) implementation: a) M<sub>P</sub> polynomial description using PCCS (Step 1 in Fig. 12); b) g<sub>m</sub><sup>v</sup> and g<sub>ds</sub><sup>v</sup> weighting and contributions towards I<sub>L</sub> (I<sub>gm</sub> and I<sub>gds</sub>) using two 2-port PVCCS</li> </ul>                                                                  | Fig. 10. General CMOS LDO structure.                                                                                                                                                                                                                                                     | 20   |

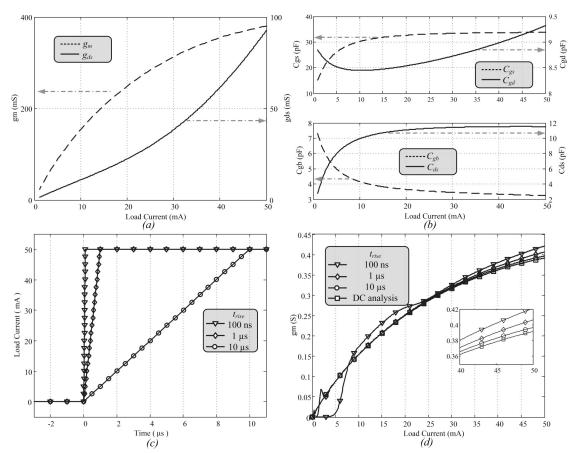

| <ul> <li>Fig. 13. M<sub>P</sub> characterization results: (a) M<sub>P</sub>'s g<sub>m</sub> and g<sub>ds</sub> in function of I<sub>L</sub> during a I<sub>Lmin</sub> to I<sub>Lmax</sub> DC sweep; (b) M<sub>P</sub>'s C<sub>gs</sub>, C<sub>gd</sub>, C<sub>gb</sub> and C<sub>ds</sub> in function of I<sub>L</sub> during a I<sub>Lmin</sub> to I<sub>Lmax</sub> DC sweep; (c) I<sub>L</sub> transient event (step) with different t<sub>rise</sub> for M<sub>P</sub> transient characterization, and (d) M<sub>P</sub> static and dynamic g<sub>m</sub> comparison.</li> <li>Fig. 14. a) LDO conceptual sub-block identification for modeling; b) Typical devices and circuits implementing the sub-blocks.</li> <li>Fig. 15. M<sub>P</sub> model and partial (g<sub>m</sub> and g<sub>ds</sub>) implementation: a) M<sub>P</sub> polynomial description using PCCS (Step 1 in Fig. 12); b) g<sub>m</sub><sup>v</sup> and g<sub>ds</sub><sup>v</sup> weighting and contributions towards I<sub>L</sub> (I<sub>gm</sub> and I<sub>gds</sub>) using two 2-port PVCCS</li> </ul>                                                                                                                                                          | Fig. 11. TF-based model of an LDO using a two-stage EA.                                                                                                                                                                                                                                  | 22   |

| a I <sub>Lmin</sub> to I <sub>Lmax</sub> DC sweep; (b) M <sub>P</sub> 's C <sub>gs</sub> , C <sub>gd</sub> , C <sub>gb</sub> and C <sub>ds</sub> in function of I <sub>L</sub> during a I <sub>Lmin</sub> to I <sub>Lmax</sub> DC sweep; (c) I <sub>L</sub> transient event (step) with different t <sub>rise</sub> for M <sub>P</sub> transient characterization, and (d) M <sub>P</sub> static and dynamic g <sub>m</sub> comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Fig. 12. Implementation of the g <sub>m</sub> -parameter to model M <sub>P</sub> .                                                                                                                                                                                                       | 23   |

| devices and circuits implementing the sub-blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | a $I_{Lmin}$ to $I_{Lmax}$ DC sweep; (b) $M_P$ 's $C_{gs}$ , $C_{gd}$ , $C_{gb}$ and $C_{ds}$ in function of $I_L$ during a $I_{Lmin}$ to $I_{Lmax}$ DC sweep; (c) $I_L$ transient event (step) with different $t_{rise}$ for $M_P$ transient characterization, and (d) $M_P$ static and | 26   |

| description using PCCS (Step 1 in Fig. 12); b) $g_m^v$ and $g_{ds}^v$ weighting and contributions towards $I_L$ ( $I_{gm}$ and $I_{gds}$ ) using two 2-port PVCCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                          | 30   |

| ( \times \tau \tau \tau \tau \tau \tau \tau \tau                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | description using PCCS (Step 1 in Fig. 12); b) $g_m^v$ and $g_{ds}^v$ weighting                                                                                                                                                                                                          | 31   |

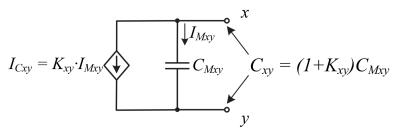

| Fig. 16  | . Model for the variable C <sub>xy</sub> of M <sub>P</sub> .                                                                                                                                                                                                                                    | 32 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 17. | . Complete $M_P$ model. $C_L$ and $\beta$ included to show the connections                                                                                                                                                                                                                      | 33 |

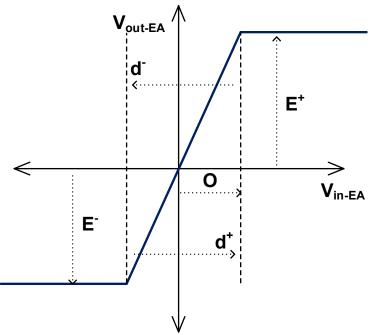

| Fig. 18  | . Threshold values for the EA model obtained from the EA I/O transfer characteristics                                                                                                                                                                                                           | 34 |

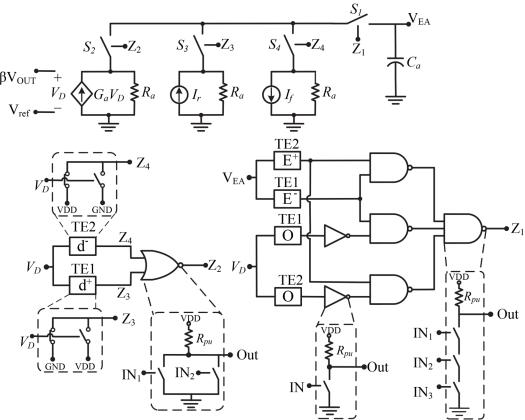

| Fig. 19  | . EA model. Modified and adapted from [42]                                                                                                                                                                                                                                                      | 35 |

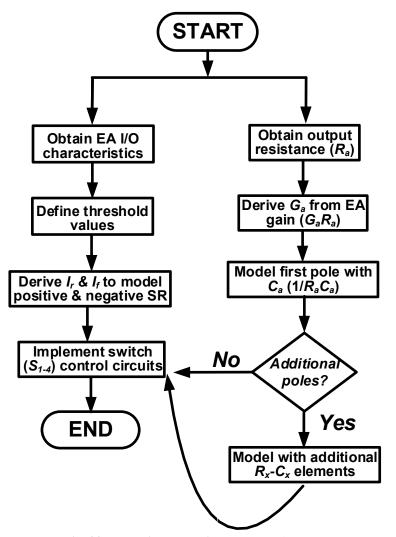

| Fig. 20  | . Flow diagram to implement EA model                                                                                                                                                                                                                                                            | 36 |

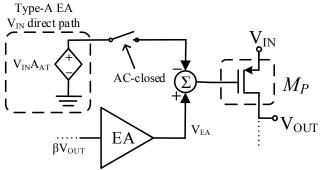

| Fig. 21. | . Modification to model's PSR path when a Type-A EA is present                                                                                                                                                                                                                                  | 37 |

| Fig. 22  | LDOs modeled as case studies: a) High PSR LDO [25]; b) Fast transient LDO with on-chip, active FCS [27]                                                                                                                                                                                         | 39 |

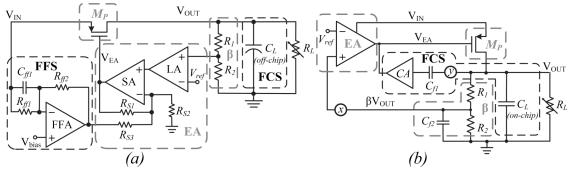

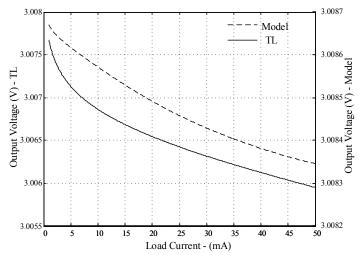

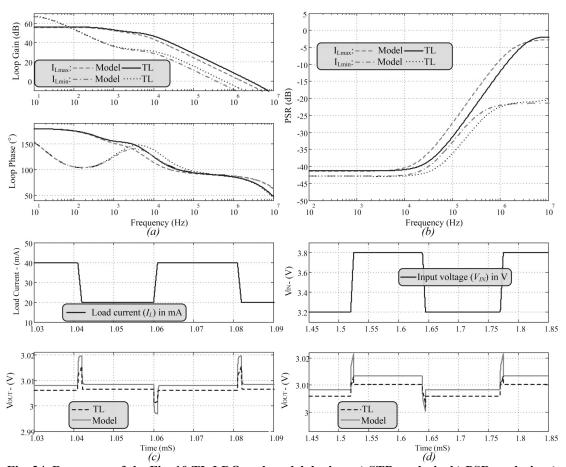

| Fig. 23  | DC analysis simulation results for the TL LDO of Fig. 10 and its generated model.                                                                                                                                                                                                               | 40 |

| Fig. 24  | . Responses of the Fig. 10 TL LDO and model during: a) STB analysis; b) PSR analysis; c) Load transient analysis: 20-40 mA I <sub>L</sub> step: and d) Line transient analysis: 3.2-3.8 V V <sub>IN</sub> step.                                                                                 | 40 |

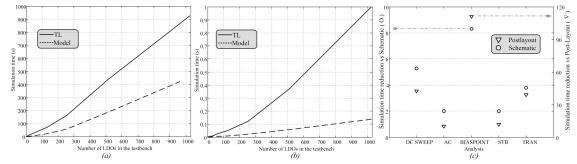

| Fig. 25  | Simulation time comparison for: a) TL and model for the Fig. 10 LDO during a transient analysis; b) TL and model for the Fig. 10 LDO during a bias point analysis; c) Simulation time reduction factor per analysis for the Fig. 22a LDO model versus its schematic and postlayout counterparts | 46 |

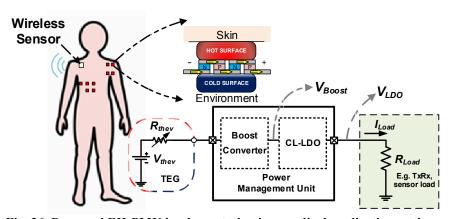

| Fig. 26  | . Proposed EH-PMU implementation in a medical application setting                                                                                                                                                                                                                               | 50 |

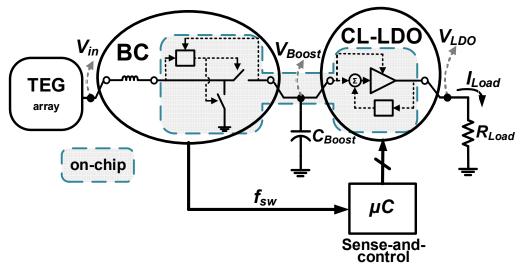

| Fig. 27  | . EH-PMU for a TEG array using a boost converter and a CL-LDO.                                                                                                                                                                                                                                  | 52 |

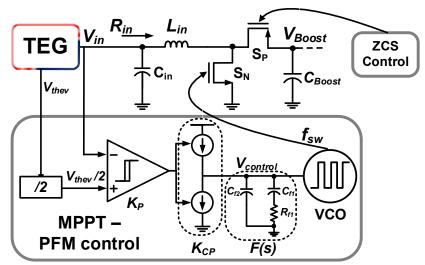

| Fig. 28  | . Implemented Boost Converter with MPPT and ZCS schemes.                                                                                                                                                                                                                                        | 54 |

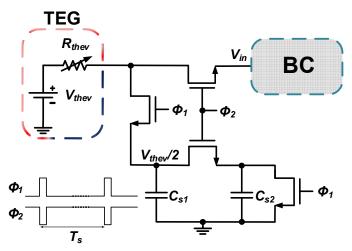

| Fig. 29  | . Capacitive divider for V <sub>thev</sub> /2 extraction [4].                                                                                                                                                                                                                                   | 56 |

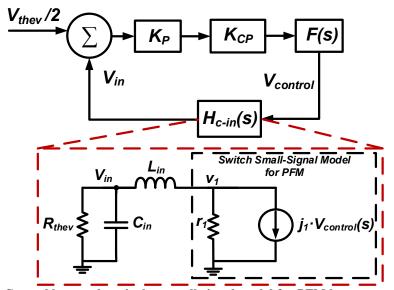

| Fig. 30  | . Control loop and equivalent small-signal model for PFM boost converter                                                                                                                                                                                                                        | 58 |

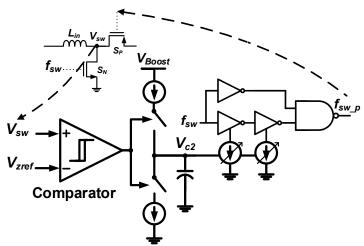

| Fig. 31. | . Zero Current Switching Tracking loop implementation [66].                                                                                                                                                                                                                                     | 60 |

| Fig. 32  | . Simple CL-LDO structure.                                                                                                                                                                                                                                                                      | 62 |

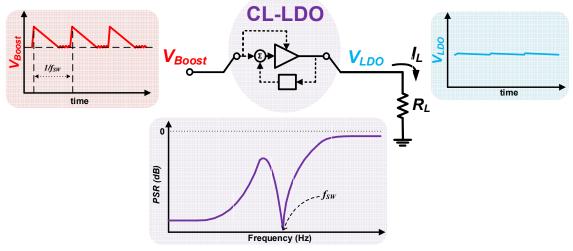

| Fig. 33  | . Conceptual CL-LDO operation                                                                                                                                                                                                                                                                   | 66 |

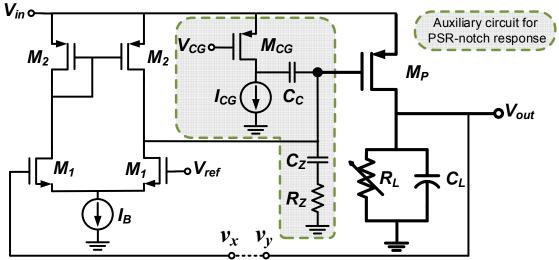

| Fig. 34  | . Transistor-level implementation of the proposed CL-LDO                                                                                                                                                                                                                                        | 68 |

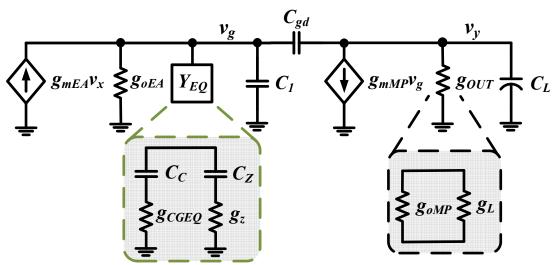

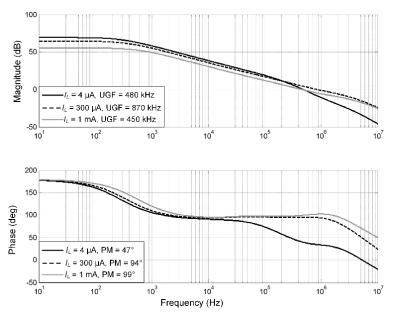

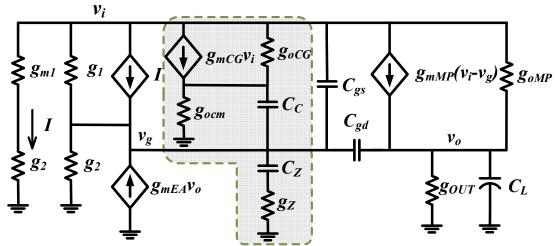

| Fig. 35. | Small signal open loop model to analyze stability in the proposed CL-LDO.                                                                                                                                                                        | 69   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 36  | CL-LDO loop gain for different I <sub>L</sub> values (postlayout simulation)                                                                                                                                                                     | 72   |

| Fig. 37. | Small signal model to analyze PSR in the proposed CL-LDO.                                                                                                                                                                                        | 73   |

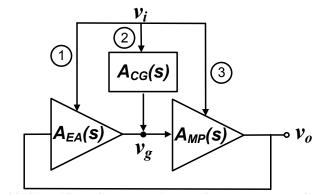

| Fig. 38  | Simplified PSR block diagram for the proposed CL-LDO                                                                                                                                                                                             | 77   |

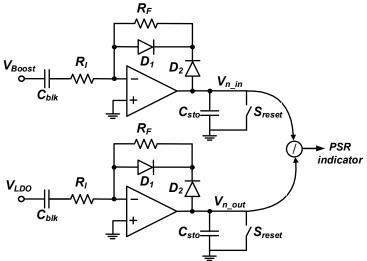

| Fig. 39  | PSR measurement circuit.                                                                                                                                                                                                                         | 80   |

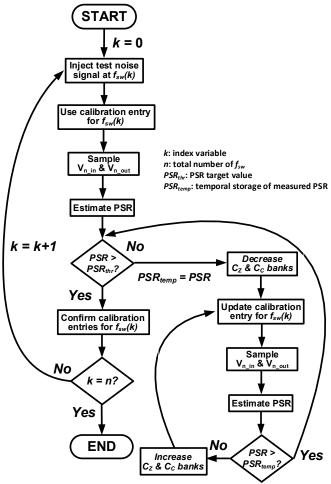

| Fig. 40  | LUT optimization algorithm.                                                                                                                                                                                                                      | 81   |

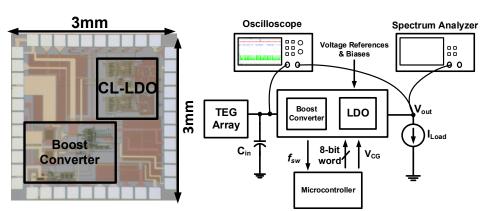

| Fig. 41  | Die microphotograph and testbench setup.                                                                                                                                                                                                         | 82   |

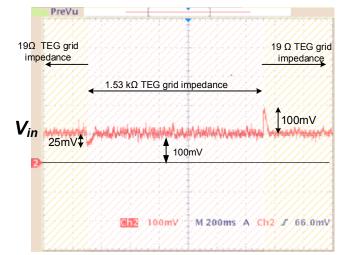

| Fig. 42  | Correct MPPT is achieved through PFM control loop.                                                                                                                                                                                               | 83   |

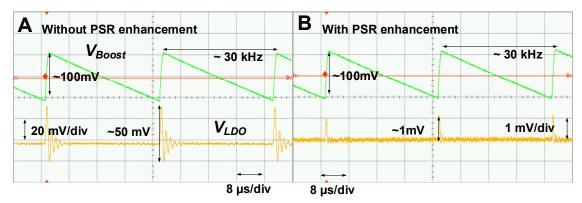

| Fig. 43  | Switching noise suppression from CL-LDO                                                                                                                                                                                                          | 84   |

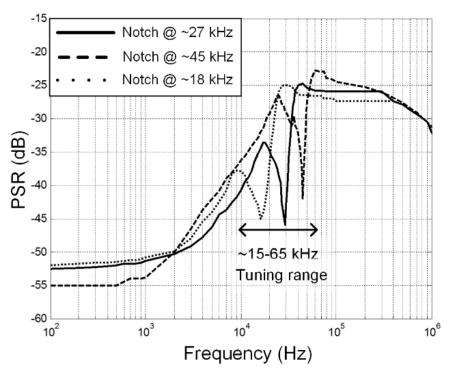

| Fig. 44  | . CL-LDO measured PSR with notch tuning range of 15-65 kHz.                                                                                                                                                                                      | 85   |

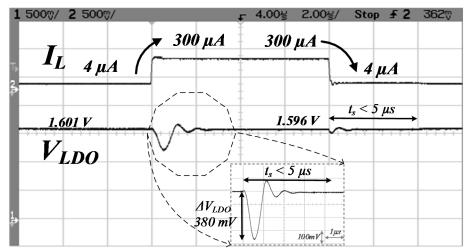

| Fig. 45  | . CL-LDO load transient response to a 4 $\mu A$ to 300 $\mu A$ $I_L$ step                                                                                                                                                                        | 86   |

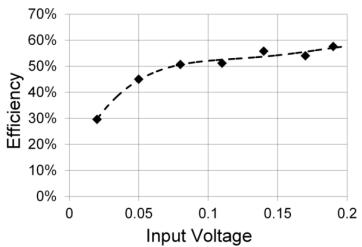

| Fig. 46  | End-to-end system efficiency.                                                                                                                                                                                                                    | 87   |

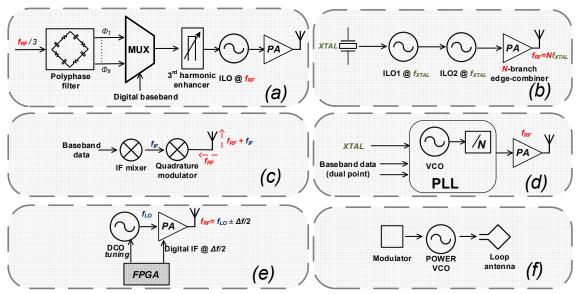

| Fig. 47  | Some state-of-the-art approaches for low power Tx, a) Subharmonic IL oscillator, b) Edge-combiner PA, c) IF backscattering technique, d) Multi-point modulation in a polar Tx, e) Two-tone RF signal transmission, f) Power VCO.                 | 92   |

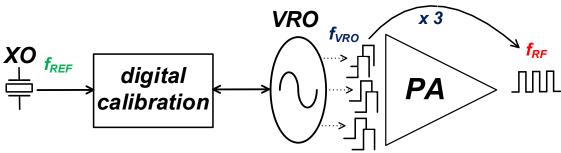

| Fig. 48  | Conceptual diagram of the proposed Tx.                                                                                                                                                                                                           | 93   |

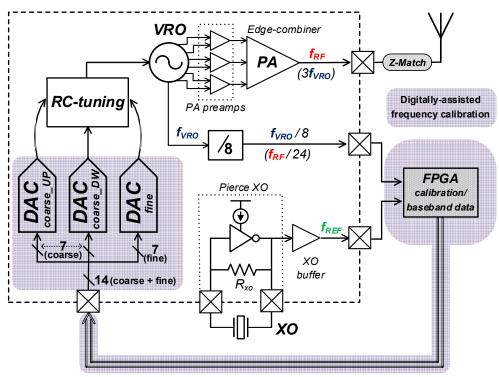

| Fig. 49  | Top-level Tx block diagram.                                                                                                                                                                                                                      | 95   |

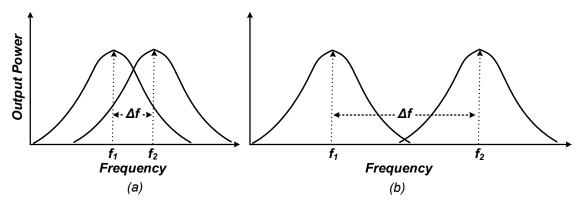

| Fig. 50  | BFSK modulation with a) small Δf (LO phase noise buries f <sub>1</sub> and f <sub>2</sub> );<br>b) large Δf (negligible LO phase noise effect)                                                                                                   | 97   |

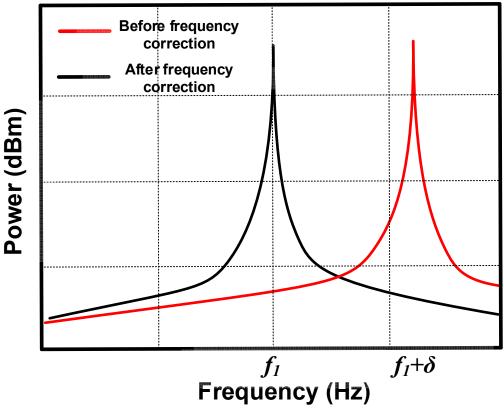

| Fig. 51. | Conceptual description of the frequency correction scheme effect in the VRO output frequency for the correct transmission of a mark state $(f_1)$                                                                                                | 98   |

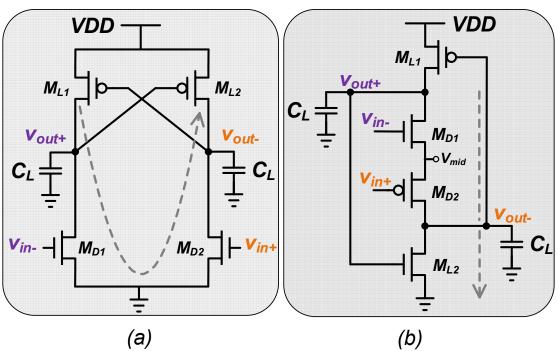

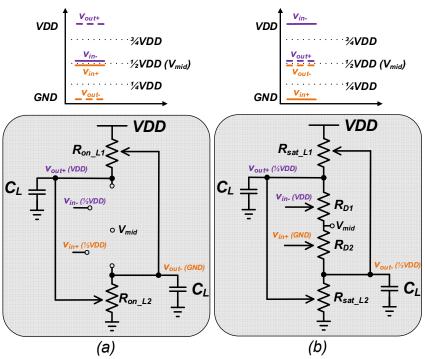

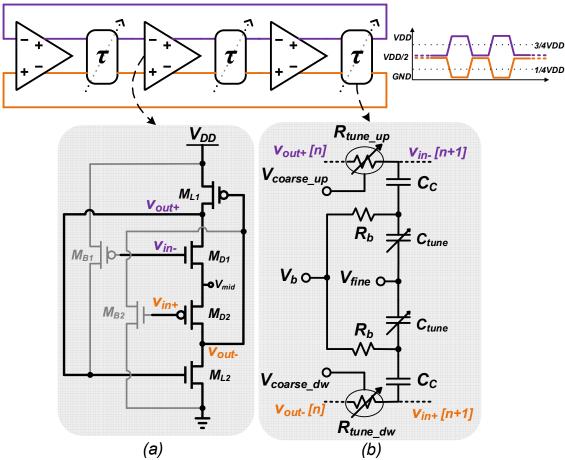

| Fig. 52  | a) Typical DCVSL delay cell, and b) Proposed vertical delay cell                                                                                                                                                                                 | 99   |

| Fig. 53  | Equivalent models for the vertical delay cell during its two possible states showing the corresponding common-mode levels: a) Logic high (low) at $v_{out+}(v_{out+})$ , and b) Its complementary logic high (low) state at $v_{out-}(v_{out+})$ | .101 |

| Fig. 54 | Output levels comparison of a) DCVSL cell, and b) Proposed vertical delay cell.                                                            | 102 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

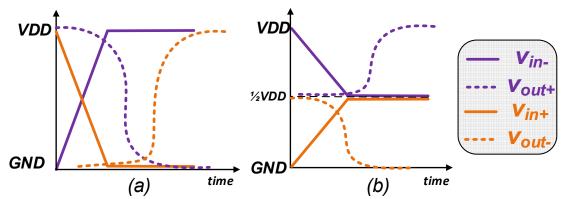

| Fig. 55 | . Vertical delay cell waveforms and signal transitions details for a) $\tau_{pHL}$ , and b) $\tau_{pLH}$ in the $v_{out^+}$ (upper) output | 107 |

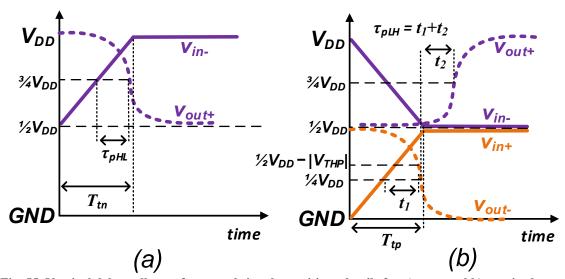

| Fig. 56 | . VRO and its building blocks: a) vertical delay cell, and b) RC delay tuning cell.                                                        | 108 |

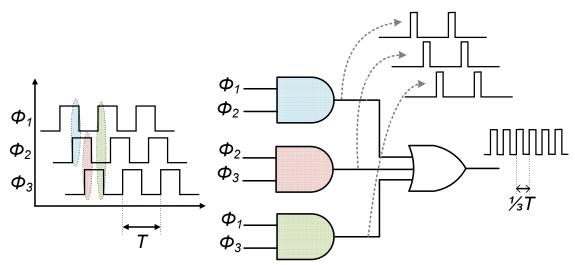

| Fig. 57 | . Conceptual description of the operation of the edge-combiner as a logic gate array                                                       | 110 |

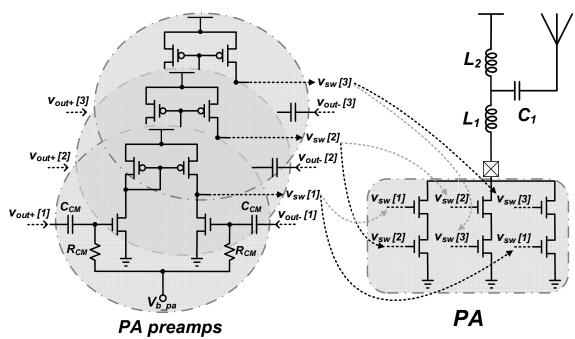

| Fig. 58 | . Edge-combiner PA and the pre-amplifiers used to interface with the VRO                                                                   | 111 |

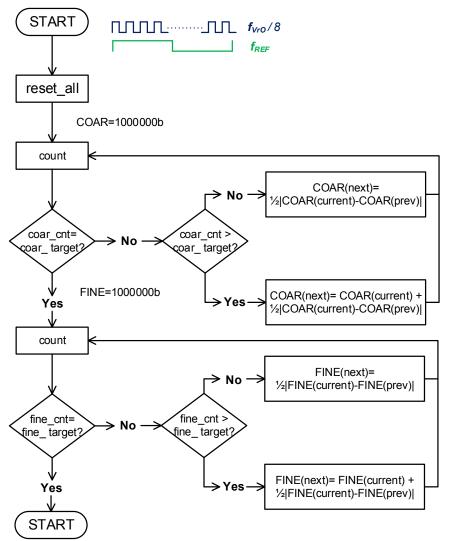

| Fig. 59 | . Binary search algorithm used to calibrate the VRO frequency                                                                              | 114 |

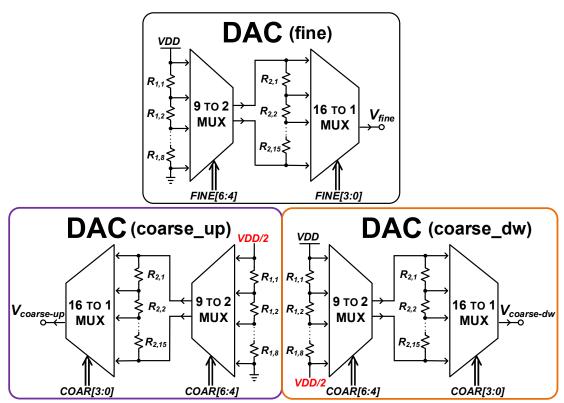

| Fig. 60 | . Resistive-string-based DACs used to generate the tuning voltages for the RC delay tuning cell.                                           | 115 |

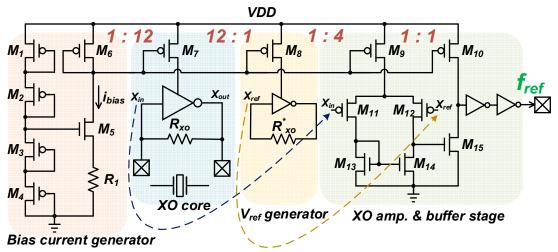

| Fig. 61 | . Crystal oscillator schematic including bias current generation and buffering stage.                                                      | 117 |

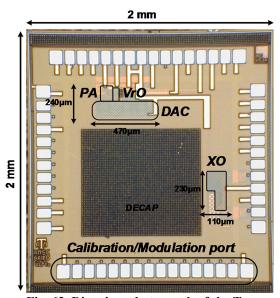

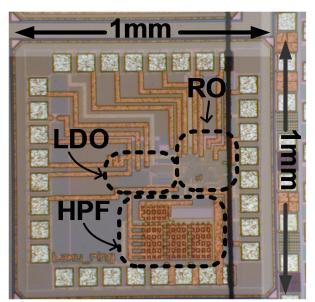

| Fig. 62 | . Die microphotograph of the Tx                                                                                                            | 118 |

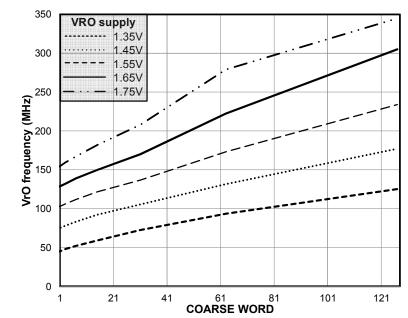

| Fig. 63 | . VRO measured tuning range 50–350 MHz translates into a PA RF range of 0.15–1.05 GHz.                                                     | 119 |

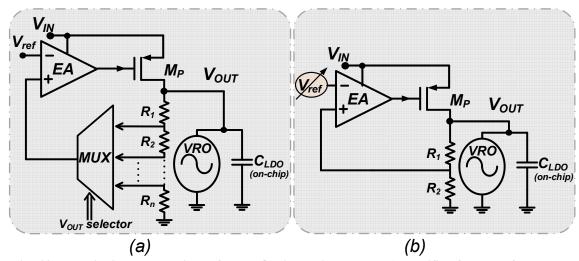

| Fig. 64 | . Potential implementations of an LDO with variable $V_{\text{OUT}}$ : a) Modified feedback factor, and b) Variable reference voltage.     | 120 |

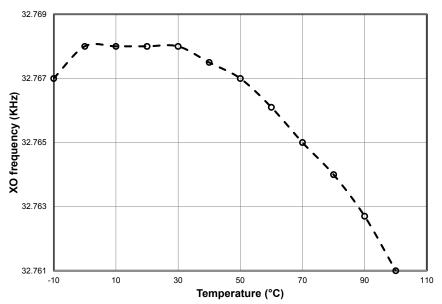

| Fig. 65 | . XO frequency stability against temperature                                                                                               | 121 |

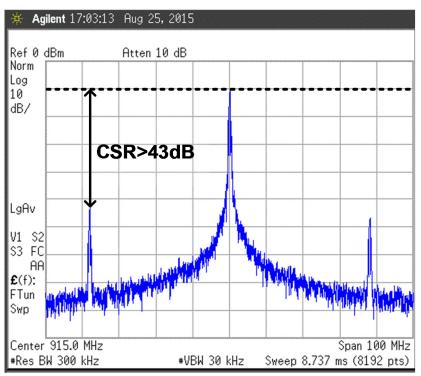

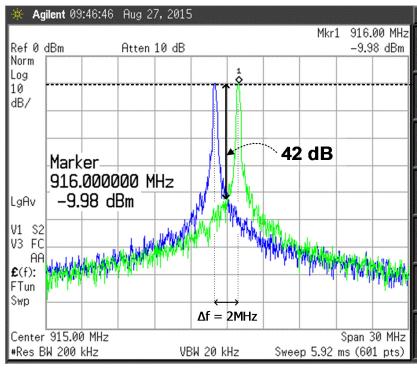

| Fig. 66 | . PA maximum output power showing a 43 dB carrier-to-spur ratio (CSR)                                                                      | 122 |

| Fig. 67 | BFSK modulated signal at the PA output for the 2 MHz frequency deviation case.                                                             | 122 |

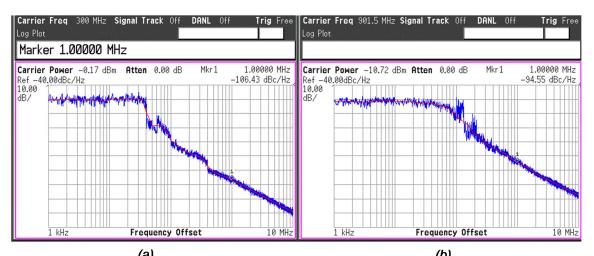

| Fig. 68 | . Phase noise of a) VRO with $f_{VRO}$ of 300 MHz for -106 dBc/Hz @ 1 MHz, and b) Tx carrier at 900 MHz with -94 dBc/Hz @ 1 MHz            | 123 |

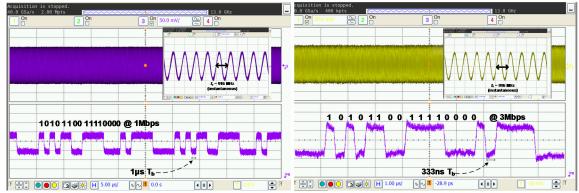

| Fig. 69 | . Transmitted bit pattern (1010110011110000) at 1 and 3 Mbps received in a signal analyzer.                                                | 124 |

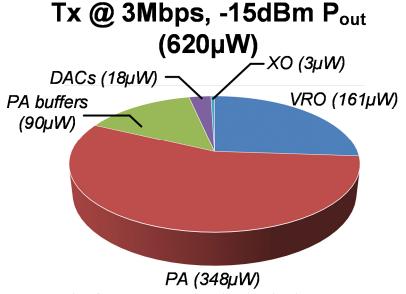

| Fig. 70 | Tx power consumption per circuit block.                                                                                                    | 124 |

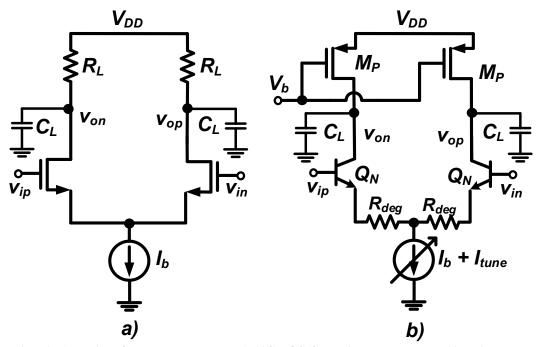

| Fig. 71. | a) Typical CML delay cell, and b) BiCMOS CML-like delay cell used in this work.                                | 131 |

|----------|----------------------------------------------------------------------------------------------------------------|-----|

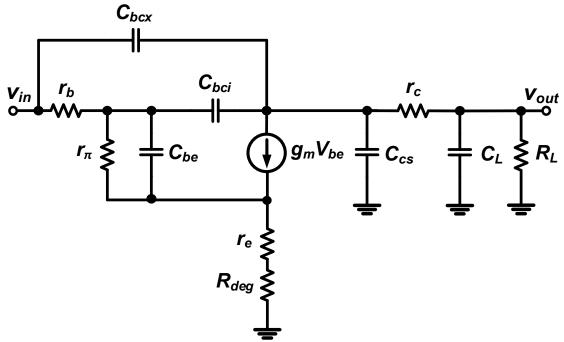

| Fig. 72. | Small signal model to analyze the BiCMOS CML-like delay cell [122]                                             | 133 |

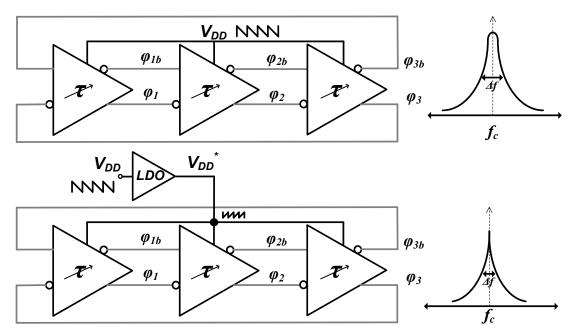

| Fig. 73. | Effect of supply noise in the RO frequency spectrum.                                                           | 136 |

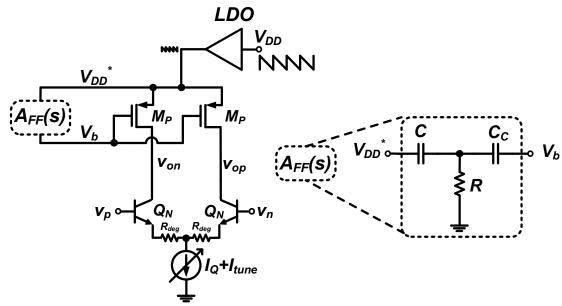

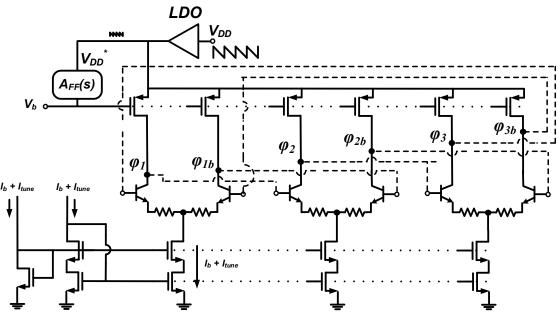

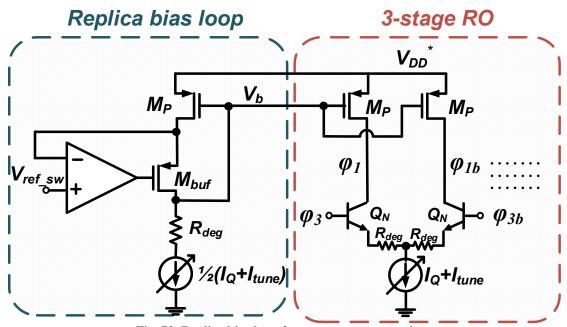

| Fig. 74. | Composite solution to the power supply-noise problem in a BiCMOS delay cell.                                   | 138 |

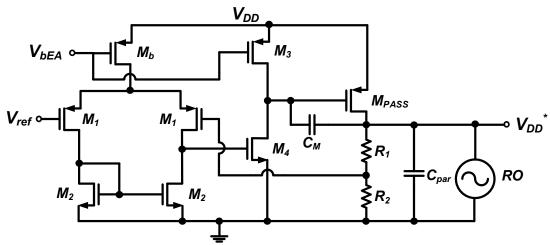

| Fig. 75. | Simple LDO for low frequency supply noise rejection.                                                           | 139 |

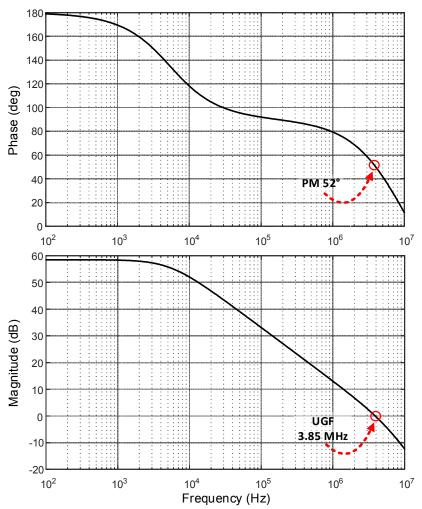

| Fig. 76. | Simulated LDO loop magnitude and phase.                                                                        | 140 |

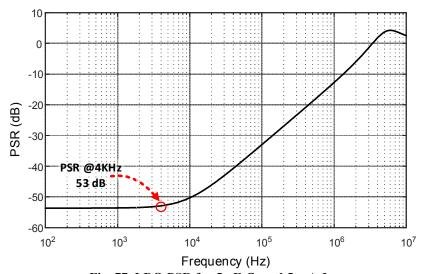

| Fig. 77. | LDO PSR for 5 pF C <sub>L</sub> and 5 mA I <sub>L</sub> .                                                      | 141 |

| Fig. 78. | Detailed schematic of the RO including the frequency tuning scheme via the tail current.                       | 143 |

| Fig. 79. | Replica bias loop for constant output swing.                                                                   | 143 |

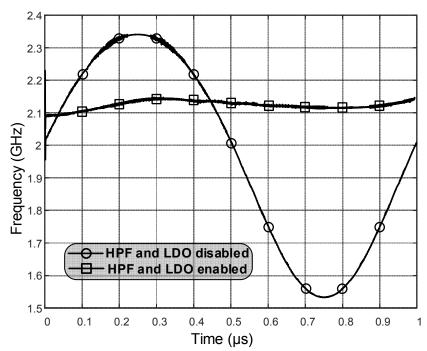

| Fig. 80. | RO frequency stability in the presence of a 200 mV $_{PP}$ , 1 MHz aggressor in the supply.                    | 144 |

| Fig. 81. | Die microphotograph of the RO + PSNR solution.                                                                 | 145 |

| Fig. 82. | Setup for RO frequency stability measurement under supply noise aggressors                                     | 146 |

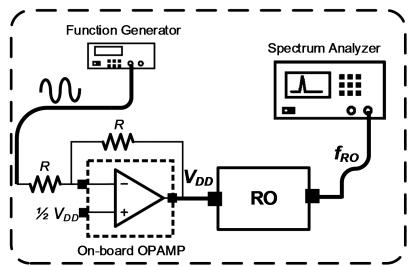

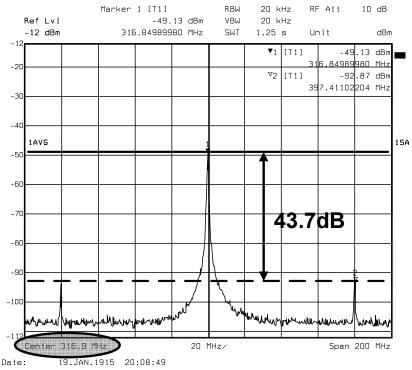

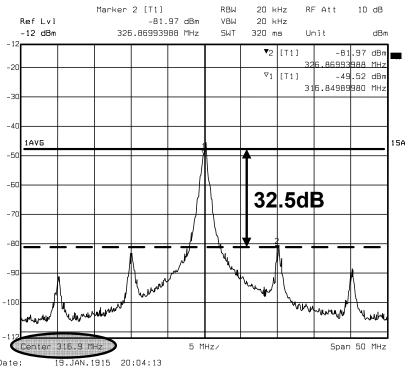

| Fig. 83. | RO spectrum for 317 MHz $f_{RO}$ under the presence of a 0.2 $V_{PP}$ , 80 MHz supply aggressor.               | 147 |

| Fig. 84. | RO spectrum for 317 MHz $f_{RO}$ under the presence of a 0.2 $V_{PP}$ , 10 MHz supply aggressor.               | 147 |

| Fig. 85. | RO spectrum for 947 MHz f <sub>RO</sub> under the presence of a 0.2 V <sub>PP</sub> , 80 MHz supply aggressor. | 148 |

# LIST OF TABLES

|                                                                                                  | Page |

|--------------------------------------------------------------------------------------------------|------|

| Table 1. Polynomial coefficients for a 5 <sup>th</sup> order fitting.                            | 31   |

| Table 2. Comparison between TL and LDO model for the general LDO structure (Fig. 10)             |      |

| Table 3. Comparison between TL and model for an LDO with FF-stage [25]                           | 42   |

| Table 4. Comparison between post-layout, model and measurements for an LDC with active FCS [27]. |      |

| Table 5. Qualitative comparison for the features of several LDO models                           | 46   |

| Table 6. Proposed CL-LDO loop poles and zeros.                                                   | 71   |

| Table 7. Proposed CL-LDO PSR poles and zeros.                                                    | 74   |

| Table 8. Proposed CL-LDO PSR poles and zeros numerical value for a notch @ 65 kHz.               | 76   |

| Table 9. Proposed CL-LDO design parameters summary.                                              | 78   |

| Table 10. Performance summary and comparison for the proposed PMU                                | 87   |

| Table 11. Design and empirical parameters values for delay calculation in 0.18 μm CMOS process.  | 106  |

| Table 12. Performance summary and comparison for the proposed Tx                                 | 125  |

| Table 13. Comparison between LC-based and ring oscillator (RO)                                   | 127  |

| Table 14. Measurement results summary and performance comparison                                 | 149  |

#### CHAPTER I

#### INTRODUCTION

## 1.1 The Internet-of-Things (IoT)

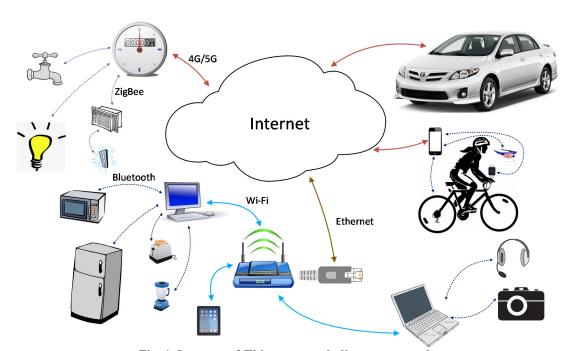

The origins of the Internet-of-Things (IoT) can be traced back to 1999 when the Auto-ID research group in the Massachusetts Institute of Technology (MIT) was exploring the application of networked radio identification (RFID) systems to the then emerging sensing technologies [1, 2]. However, accepting the definition of the IoT conception as "the point in time when more things or objects were connected to the Internet than people" [1], the Cisco Internet Business Solutions Group (IBSG) concluded that the IoT emerged between 2008 and 2009. A massive IoT network, expected to accommodate more than 50 billion devices by 2020 [1], will (and to some extent, already is) enable the exchange of information and communication of all the things and individuals connected [3], which when coupled with efficient sensing technologies, offers an endless pool of possibilities. As such, the IoT platform has already triggered the development of multiple and diverse applications in a variety of fields such as: healthcare, wearable technology, logistics, smart homes and buildings, and smart infrastructure for smart cities, to mention a few. Illustrated in Fig. 1 is an example of the potential communications links established by all the "things" part of the IoT. Multiple wireline and wireless network standards such as Bluetooth, ZigBee, Ethernet, and of course cellular technology (4G/5G), can be used to ultimately reach the Internet cloud where the bulk of the data storage is done.

Because of the variety of technologies converging into the IoT, the characteristics and requirements of every node and gateway are vastly different. However, there are similarities in the sense that most of the nodes require some sort of sensing but particular levels of processing power; also, every node needs to be able to transmit information but an embedded receiver might be optional in some cases. Furthermore, every node and gateway share the fundamental requirement of a local power supply, which might be in the form of an AC power outlet, a battery, or an energy harvesting system. A collection of such nodes forms what is known as wireless sensor networks (WSN). A WSN might expand over different spaces, at the personal or body-area levels. Fig. 1 also shows small examples of the so-called PAN (personal area network) and BAN (body area network) within the IoT network context.

Fig. 1. Internet-of-Things network diagram example.

#### 1.2 Inside an IoT node

A general, conceptual description of the blocks typically incorporated in a WSN/IoT node is shown in Fig. 2. The node can have a single or multiple energy sources, which might include: an AC outlet for stationary nodes located in areas with utility services; a rechargeable or disposable battery; a naturally available resource in the environment such as sun light, temperature gradients, and electromagnetic waves; an induced source such as vibrational energy; or alternative energy sources such as methanol.

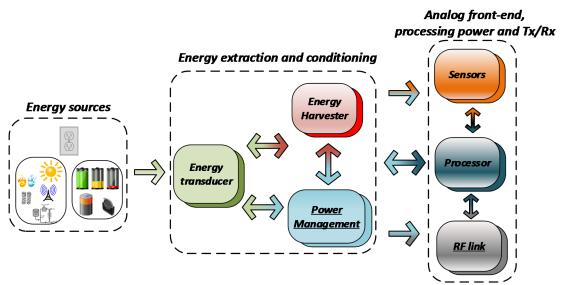

Fig. 2. Wireless sensor network/IoT node description.

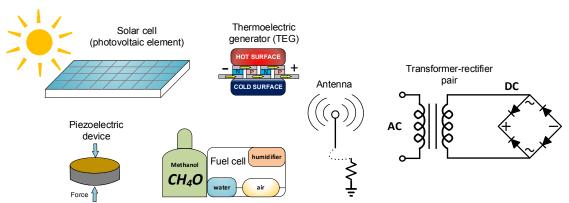

For the electronic circuits in the node to operate using energy from whatever source is available, this energy must be in the form of an electric potential (voltage). An energy transducer is used to transform from one type of energy to another. Some examples

of commonly used transducers are shown in Fig. 3, and include: a solar cell that converts incident sun light into a voltage; a thermoelectric generator that uses a temperature gradient between its plates to produce electrical energy; a piezoelectric device that generates a voltage when deformed (stressed) by external forces; a resistively-terminated antenna that converts electromagnetic waves at radio frequencies (RF) into an AC voltage; and a methanol fuel cell, where a chemical reaction generates a voltage between anode and cathode of the fuel cell. Although strictly speaking transformer-rectifier pair is not an energy transducer, these elements are required for AC-to-DC conversion when power is directly obtained from the power mains. On the other hand, while a battery is a transducer in itself (stacked electrochemical cells transforming chemical into electrical energy), when batteries are the primary energy source, some power conditioning is still required before the battery voltage reaches the circuits that perform the actual sensing, processing and transmitting/receiving tasks.

Fig. 3. Examples of energy transducer and a transformer-rectifier for AC-DC voltage conversion.

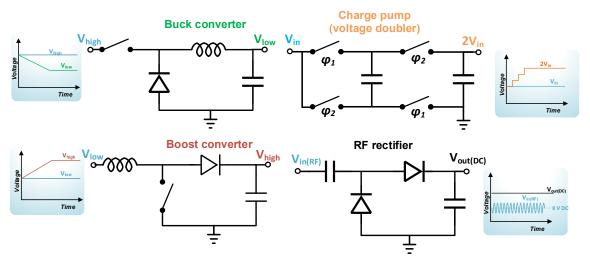

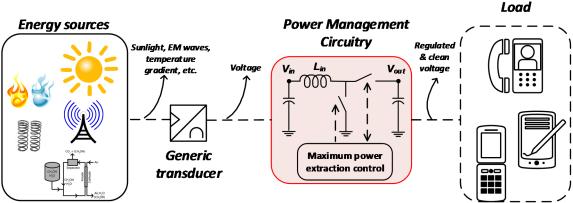

After the energy has been converter to the required –voltage– form, an energy harvester circuit is employed to extract the maximum amount of power (energy per unit time) from the energy transducer in the most efficient way. Simple circuits such as inductor-based DC-DC converters, RF rectifiers, and charge pumps are commonly used for this purpose [4-6]. Some examples of these type of circuits are shown in Fig. 4. After maximum energy extraction is guaranteed, additional power management and conditioning is required to properly scale the voltage levels, minimize supply noise, and regulate the provided output voltage. Additional switching converters or linear regulators are employed for this last step before delivering a clean supply for the sensitive circuits that form the IoT node. A conceptual block diagram of the energy extraction and conditioning chain is shown in Fig. 5.

Fig. 4. Examples of circuits for efficient energy extraction from the transducer.

Fig. 5. Conceptual diagram of the energy extraction and conditioning chain.

The bulk of the work performed in an IoT node, as perceived by the end-user, is carried in the section that implements the sensing activities, provides the processing power and enables the communication link with the network gateway or with peer nodes. The sensors block primarily determines the application in which the node will be used. Temperature and humidity sensors embedded in the node enable climate monitoring and control; similarly, heart rate and bioimpedance sensors combined with accelerometers are the foundation of fitness monitors. The plethora of available sensors with different accuracies and sensitivities is part of the reason for the limitless potential of WSN.

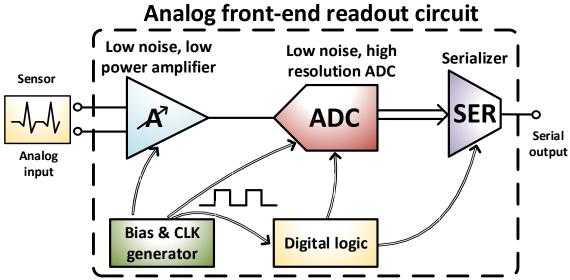

An analog readout front-end used to acquire sensor's signals is shown in Fig. 6 [7]. It consists of a low noise, low power amplifier with variable gain (A); a low speed, low noise, and high resolution analog-to-digital converter (ADC) frequently based on the successive approximation architecture (SAR); bias and clock generators; a digital logic block; and a serializer output block.

Fig. 6. Typical circuit blocks used in the analog front-end for sensor signal readout and acquisition.

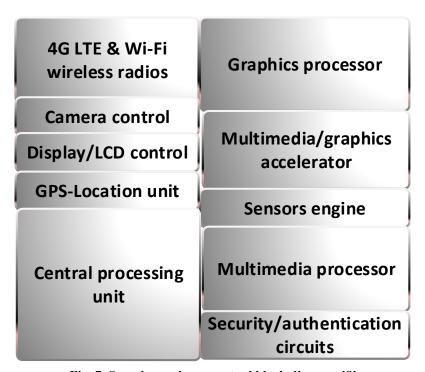

Equally important for a pleasant user experience is the processor that executes, oversees, and coordinates the operation of the IoT node. The amount of processing power required per node greatly varies according to the application. For instance, nodes exclusively dedicated to monitor certain variable (water flow, energy consumption, etc.) and transmit its value at regular time intervals require a minimum of processing power which might be addressed with a simple finite state machine (FSM). Conversely, nodes that *i*) handle larger volumes of information, *ii*) perform complex operations on the acquired measurement before transmitting it, or *iii*) need to display it on a screen in a user-friendly mode, rely heavier on fast and powerful integrated processor. An easily identifiable node falling in the latter category is a smartphone. Furthermore, processors for mobile applications not only strive for high performance but also compete to achieve the lowest power consumption for long battery life. Examples include families of multi-

core processors such as Samsung's Exynos, Qualcomm's Snapdragon, Apple's A4-9, some of which (Samsung & Qualcomm) already integrate the wireless radios. Based on the manufacturer's features description of the Snapdragon processor [8], a top level block diagram is depicted in Fig. 7.

Fig. 7. Snapdragon's conceptual block diagram [8].

The last block element illustrated in Fig. 2 is the one in charge of the RF communication link. As illustrated in Fig. 1, there are several standards which can be used to establish a wireless channel. While LTE (cellular), Wi-Fi (IEEE 802.11b/g/n), Bluetooth (and its Low-Energy version –BLE–), ZigBee (IEEE 802.15.4) are amongst the most used standards, some other recently released standards focused on power

optimization like IEEE 802.15.6 for wireless body area networks (WBAN), 6LoWPAN (IPv6 over low power personal area networks), and proprietary protocols in the sub-1 GHz ISM (industrial, scientific, and medical) frequency bands are gaining important traction to achieve the lowest possible power consumption on the IoT node during data transmission and reception.

## 1.3 Research scope and motivation

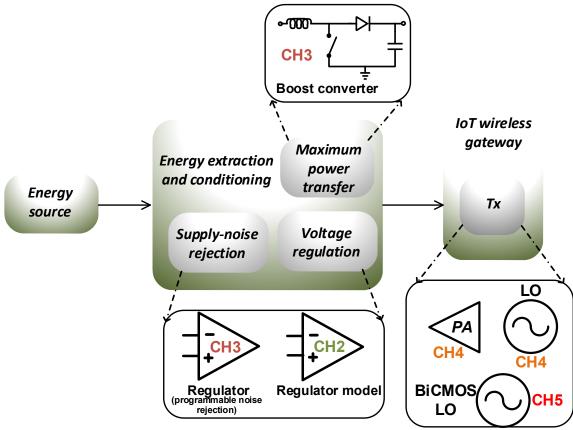

This dissertation focuses on low and ultra-low power integrated circuits for IoT nodes targeting sensing and monitoring tasks for immediate transmission of raw (unprocessed) data results. In particular, the design and implementation of models and integrated circuits for the two underlined blocks in Fig. 2 are addressed. The next few chapters present and discuss in detail novel models, circuits and techniques for the power management and the RF (up)-link sections in IoT nodes. In order to provide context and understand the importance, motivation, and driving factors of this research, the rest of this chapter briefly touches on the problems that the integrated circuits here proposed aim to solve. The different building blocks that will be discussed throughout the dissertation are highlighted in Fig. 8 as key elements in the performance of an IoT node. The design and implementation of critical circuits such as switching and linear voltage regulators for power management (chapter 3), and its modeling (chapter 2); as well as local oscillators (LO) and power amplifiers for the wireless gateway part (chapter 4 and 5) are thoroughly discussed.

Fig. 8. Building blocks of an IoT node addressed in the dissertation.

An important part of every power management unit (PMU) used to provide supply voltage(s) for the operation of the brain (processor) of every System-on-Chip (SoC) like an IoT node, are the low dropout (LDO) regulators used to develop and deliver clean and regulated output voltages for the rest of the circuitry. However, as the number of LDOs per SoC increases, so does the complexity and time required to perform a reliable verification for the complete SoC at the transistor-level. To reduce the burden imposed on the simulators, chapter II describes a methodology to generate an LDO model that can be used to replace its transistor-level counterpart in top level SoC final simulations and verification. The proposed model is exclusively based on SPICE primitive components

which provides the required flexibility when dealing with excessively long top level netlists. Using the LDO model, it is demonstrated via simulation that important time reductions are achieved without significant loss in accuracy.

Chapter III digs further into the complete PMU circuitry. In this case, an integrated circuit is designed, fabricated and tested to demonstrate an end-to-end energy harvesting concept using a thermoelectric generator array as energy transducer. The proposed solution tackles several important problems in PMU: a) achieve high efficiency and continuous maximum power extraction, b) adapt to diverse conditions presented at the transducer output such as array reconfigurations triggered by different needs of the load circuit or by a varying temperature gradient within the target range, c) provide a wellregulated output voltage, and d) maintain a), b) and c) while providing high supply noise rejection, particularly at the PMU switching frequency. Although it might be argued that conditions a)-d) are typically expected from a high performance PMU, building a PMU targeted for an energy-harvest-powered IoT node poses tough challenges both at the architectural and circuit-levels to accomplish the PMU specifications under severe power consumption restrictions. In the presented scenario, the PMU must operate with extremely low power levels to avoid an important efficiency degradation. The proposed PMU was fabricated in 0.5 µm CMOS, experimental results showed overall system efficiency better than 57% @ 1.6 V output voltage, and a switching noise suppression in the supply of 40dB at the switching frequency. Furthermore, the PMU includes a first-of-its-kind, capacitorless LDO with adaptive power supply transfer function that places a notch at the average switching frequency, allowing for the PMU to operate within a wide range of switching frequencies in response to the varying conditions of the thermoelectric transducer while providing high supply noise rejection.

Chapter IV takes on a different challenge than previous chapters, this chapter discusses the details of an integrated circuit design implementing an ultra-low power transmitter (Tx) for IoT nodes. The fundamental goal of the proposed Tx is to reduce its power consumption and maximize its energy efficiency per transmitted bit. It follows that reducing the power required in the communication link section of the IoT node can significantly decrease the total node consumption. Between the analog front-end, the processor, and the wireless radio, it is the power consumption of the latter which dominates over that of the rest of the node components.

Reaching ultra-low power consumption levels in a wireless Tx requires a comprehensive approach that includes a system-level Tx design that anticipates and considers potential (new) circuit architectures that are of low power nature by themselves. Following this convention, chapter IV discusses the design strategy that lead to the proposed Tx, which operates in the 900 MHz ISM band using a wideband frequency-shift keying modulation. Taking advantage of these system level considerations, it is possible to use an open-loop, free-running ring-oscillator as the local oscillator (LO) generator in the proposed Tx. Moreover, a novel type of ultra-low power delay cell termed as vertical delay cell is introduced and employed to build the ring-oscillator. This oscillator architecture and the synthesizer-less approach further reduce the Tx power consumption. However, proposing a new, low power LO stage is only half of the way toward the ultimate goal of high energy efficiency in the Tx. An edge-combiner power amplifier (PA) stage is

used for implicit frequency multiplication of the LO at the PA output port. This PA structure allows the oscillator to operate at only  $\frac{1}{3}$  of the RF frequency. The Tx was fabricated in 0.18  $\mu$ m CMOS technology and experimental results showed an oscillator tuning range large enough to provide an RF carrier tunability of 0.15 GHz–1.05 GHz. The maximum output power is -10 dBm, and the normalized energy efficiency is 3.1 nJ/(bit-mW) while transmitting with a 3 Mbps data rate.

Continuing the research in ring-oscillators, chapter V presents a BiCMOS ringoscillator with high tolerance to supply-noise. To grant the ring-oscillator with this feature, a feedforward path from the supply to strategic nodes in the delay cells forming the oscillator is used in combination with a low-cost LDO. From a black-box point of view, the proposed solution reduces the supply sensitivity of the oscillator, which in turn relaxes the specifications of a global LDO in the PMU driving the oscillator in an IoT node. To avoid a simple transference of the requirements and power consumption from the global to the local LDO and feedforward path, the approach described in chapter V uses only passive components to build a high-frequency feedforward path with cut-off frequency as low as allowed by the allocated area. Due to its implementation and connection points, this feedforward filter essentially shields the delay cell against supply noise with frequencies higher than its cut-off frequency. To complement the solution, a low-cost LDO with bandwidth equal or larger than the cut-off frequency of the feedforward filter is used. In this way, the supply rejection provided by the LDO protects the oscillator against supply noise with frequencies below the cut-off of the feedforward filter. The composite solution provides superior supply noise tolerance without strongly increasing the overall power consumption.

Finally, chapter VI presents this dissertation's conclusions, summarizes its contributions and sheds light into related opportunities for future work.

#### CHAPTER II

# A COMPREHENSIVE MODEL FOR CMOS LOW DROPOUT VOLTAGE REGULATORS

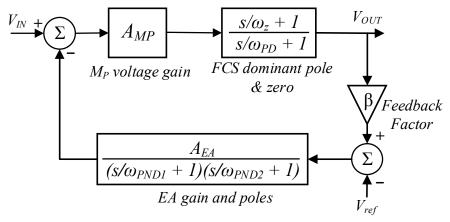

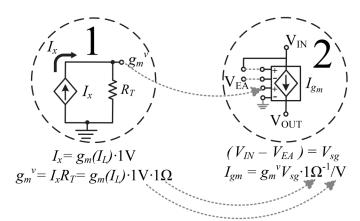

A comprehensive, yet simple and of fast simulation time SPICE-oriented model for CMOS Low-Dropout (LDO) voltage regulators is presented in dissertation. The selfcontained model tracks the instantaneous LDO output current to continuously describe the LDO operation. A set of nonlinear polynomials obtained from simulation data describes the pass transistor in the LDO loop context and constitutes the cornerstone of the model. Additional but key to the accurate modelling of the small and large signal LDO characteristics is the inclusion of individual models for the error amplification path, feedback stage and frequency compensation. The topology-independent LDO model is portable and useful in the design, analysis and verification of integrated systems that use LDOs. Altogether, the computational and assembling efforts are minimized by using only SPICE elements in the model. To fully verify the model validity, three modelling case studies for different LDO structures are presented, one of which includes comparison versus experimental results. The generated models demonstrate the versatility of the approach and expose the model as an agile tool to examine the LDO effects at the system level. The models exhibit analysis-dependent simulation time reduction factors up to 10x and 110x when compared with circuit schematic-level and extracted-level simulations, respectively.

#### 2.1 Introduction

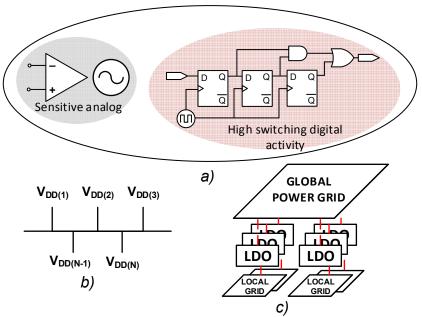

It is the coexistence and interaction of analogue and digital circuits that enable the high performance of the state-of-the art integrated circuits. The high level of integration displayed in such systems is part of the reason for the widespread use of the low-dropout voltage regulator (LDO) [9-12]. Whether the LDO is used to increase the isolation between analog and digital circuits (Fig. 9a), generate multiple on-chip supply domains (Fig. 9b), or improve the point-of-load regulation in power delivery networks (Fig. 9c), high performance LDOs seem to be present in almost every integrated circuit. While in some applications the LDO is still considered an ancillary circuit able to provide clean supply voltages to noise-sensitive circuits, the LDO has turned into a central piece in certain systems due to its extensive use [11, 13, 14]. Due to the recurrent use of LDOs, there is a pressing need for an LDO model able to provide fast evaluation of LDO structures within the main system's context. Furthermore, an accurate LDO model is key to reduce computing and simulation time of integrated systems using multiple LDOs. Replacing the LDO with its model counterpart allows to focus the design and debugging efforts on the main system.

Fig. 9. Examples of LDOs use in Systems-on-Chip: a) Increase isolation between analog and digital circuitry, b) Generate multiple power domains, and c) Improve point-of-load regulation.

Contrary to the case of switched-mode power supplies where different models have been developed in the last 30 years [15-17], the available options for LDO models are limited and far from a self-contained solution. The models in [18-20] use an actual transistor to model the pass device, with [18] providing a full characterization for only one regulator topology; [19] and [21] limited to small-signal AC analyses; and [20] using Verilog-A to complement the model. The model in [22] elegantly describes the LDO for electromagnetic compatibility purposes but does not evaluate other fundamental LDO specifications of interest for integrated circuit design. While the LDO synthesis framework in [23] demonstrated an efficient specification-to-silicon design flow, this methodology is complex and only applicable to LDOs using particular types of error amplifiers and compensation methods.

This chapter presents a comprehensive, SPICE-compatible LDO model that captures the frequency and time-domain LDO characteristics. The model is able to describe different LDO structures for all the load current values of interest. By exclusively employing SPICE elements, the model can be used in the multiple circuit simulation tools based on a SPICE engine, facilitating the model's adoption during the design stage by providing a readily available and low complexity model for integrated LDOs with suitable accuracy.

## 2.1.1 Low dropout regulators: Basics

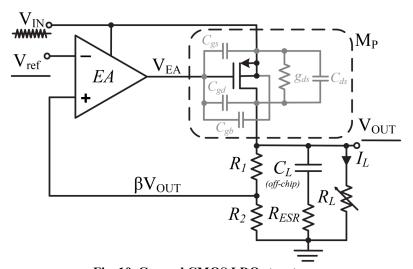

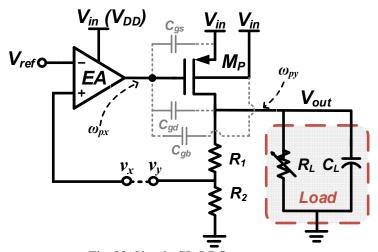

In the general LDO (Fig. 10), the output voltage ( $V_{OUT}$ ) is ideally a clean, scaled and regulated version of a noisy, unregulated input voltage ( $V_{IN}$ ). Four major sub-blocks constitute the LDO in Fig. 10:

• Pass transistor (M<sub>P</sub>). This device provides the current (I<sub>L</sub>) demanded by the load (R<sub>L</sub>). While an NMOS transistor can be used, a PMOS reduces the  $V_{IN}$  to  $V_{OUT}$  voltage drop. In Fig. 10,  $g_{ds}$ ,  $C_{gd}$ ,  $C_{gs}$ ,  $C_{gb}$  and  $C_{ds}$  are M<sub>P</sub>'s drain-to-source conductance, gate-to-drain, gate-to-source, gate-to-bulk and drain-to-source capacitances, respectively. Since the performance of the LDO is tightly related to the  $I_L$ , M<sub>P</sub> should be carefully sized accordingly to the  $I_L$  and dropout voltage ( $V_{DO} = V_{IN} - V_{OUT}$ ) requirements. For a first order approximation, (1) can be used to determine the required width (W) of M<sub>P</sub> (the length L is typically chosen based on the minimum

allowable per the process technology  $L_{min}$ ). In (1)  $\mu_p$  is the hole mobility and  $C_{ox}$  is the oxide capacitance.

$$W = \frac{2I_L}{\mu_p C_{ox} V_{DO}^2} L_{min} \tag{1}$$

- Feedback stage ( $\beta$ ).  $\beta$  feeds a scaled version of  $V_{OUT}$  ( $\beta V_{OUT}$ ) to the error amplifier. It is typically implemented with a resistor divider. In Fig. 10,  $\beta = R_2/(R_1 + R_2)$ .