# INTEGRATION OF NON-VOLATILE MEMORY INTO STORAGE HIERARCHY

A Dissertation

by

## SHENG QIU

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | A.L.Narasimha Reddy |  |  |  |

|---------------------|---------------------|--|--|--|

| Committee Members,  | Riccardo Bettati    |  |  |  |

|                     | Krishna Narayanan   |  |  |  |

|                     | Paul Gratz          |  |  |  |

| Head of Department, | Chanan Singh        |  |  |  |

December 2013

Major Subject: Computer Engineering

Copyright 2013 Sheng Qiu

#### ABSTRACT

In this dissertation, we present novel approaches for integrating non-volatile memory devices into storage hierarchy of a computer system. There are several types of nonvolatile memory devices, such as flash memory, Phase Change Memory (PCM), Spintransfer torque memory (STT-RAM). These devices have many appealing features for applications, however, they also offer several challenges. This dissertation is focused on how to efficiently integrate these non-volatile memories into existing memory and disk storage systems. This work is composed of two major parts.

The first part investigates a main-memory system employing Phase Change Memory instead of traditional DRAM. Compared to DRAM, PCM has higher density and no static power consumption, which are very important factors for building large capacity memory systems. However, PCM has higher write latency and power consumption compared to read operations. Moreover, PCM has limited write endurance. To efficiently integrate PCM into a memory system, we have to solve the challenges brought by its expensive write operations. We propose new replacement policies and cache organizations for the last-level CPU cache, which can effectively reduce the write traffic to the PCM main memory. We evaluated our design with multiple workloads and configurations. The results show that the proposed approaches improve the lifetime and energy consumption of PCM significantly.

The second part of the dissertation considers the design of a data/disk storage using non-volatile memories, e.g. flash memory, PCM and nonvolatile DIMMs. We consider multiple design options for utilizing the nonvolatile memories in the storage hierarchy. First, we consider a system that employs nonvolatile memories such as PCM or nonvolatile DIMMs on memory bus along with flash-based SSDs. We propose a hybrid file system, NVMFS, that manages both these devices. NVMFS exploits the nonvolatile memory to improve the characteristics of the write workload at the SSD. We satisfy most small random write requests on the fast nonvolatile DIMM and only do large and optimized writes on SSD. We also group data of similar update patterns together before writing to flash-SSD, as a result, we can effectively reduce the garbage collection overhead. We implemented a prototype of NVMFS in Linux and evaluated its performance through multiple benchmarks.

Secondly, we consider the problem of using flash memory as a cache for a disk drive based storage system. Since SSDs are expensive, a few SSDs are designed to serve as a cache for a large number of disk drives. SSD cache space can be used for both read and write requests. In our design, we managed multiple flash-SSD devices directly at the cache layer without the help of RAID software. To ensure data reliability and cache space efficiency, we only duplicated dirty data on flash-SSDs. We also balanced the write endurance of different flash-SSDs. As a result, no single SSD will fail much earlier than the others.

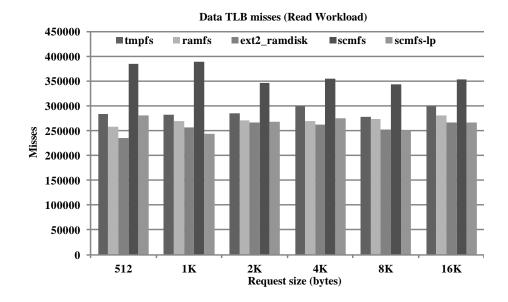

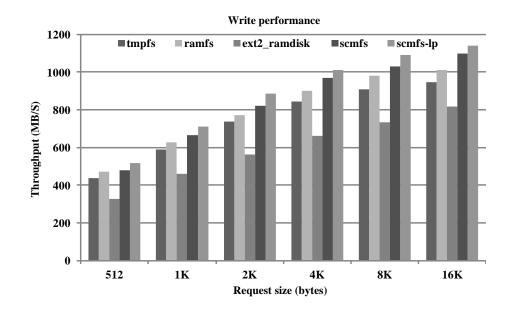

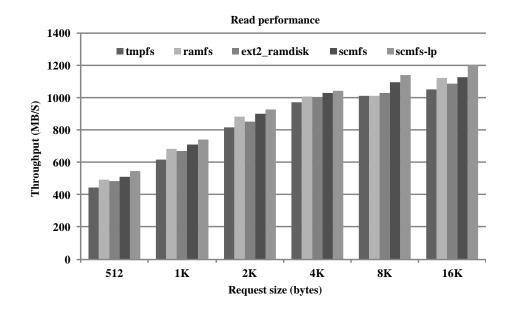

Thirdly, when using PCM-like devices only as data storage, it's possible to exploit memory management hardware resources to improve file system performance. However, in this case, PCM may share critical system resources such as the TLB, page table with DRAM which can potentially impact PCM's performance. To solve this problem, we proposed to employ superpages to reduce the pressure on memory management resources. As a result, the file system performance is further improved.

#### ACKNOWLEDGEMENTS

I am sincerely thankful to my advisor, Dr. Reddy, for his patience on guiding and helping me in my research, as well as my life. I would like to thank my committee members, Dr. Bettati, Dr. Gratz and Dr. Narayanan, for their precious time to review my dissertation and gave me valuable feedback. I would like to thank all my friends, without their help I might not solve some challenges while studying and living abroad. Finally, I would like to thank my parents for their love throughout my whole life. Without their support, it would have been impossible for me to finish my Ph.D. degree.

# TABLE OF CONTENTS

|     |              | P                                                                                                                              | age                  |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------|

| AF  | BSTR         | ACT                                                                                                                            | ii                   |

| AC  | CKNC         | OWLEDGEMENTS                                                                                                                   | iv                   |

| TA  | BLE          | OF CONTENTS                                                                                                                    | v                    |

| LIS | ST O         | F FIGURES                                                                                                                      | vii                  |

| LIS | ST O         | F TABLES                                                                                                                       | х                    |

| 1.  | INT          | RODUCTION                                                                                                                      | 1                    |

|     | $1.1 \\ 1.2$ | Main memory technologyDisk storage technology                                                                                  | $\frac{2}{5}$        |

| 2.  |              | CESSOR CACHE DESIGN TO IMPROVE LIFETIME AND EN-<br>GY IN PCM-BASED MAIN MEMORY                                                 | 9                    |

|     | 2.1          | Background                                                                                                                     | 9<br>9               |

|     | 2.2          | 2.1.2Last-level cache based writeback reductionDesign and implementation2.2.1Cache replacement policy                          | 11<br>12<br>13       |

|     | 2.3          | 2.2.2 Cache organization                                                                                                       | 16<br>18             |

|     |              | 2.3.1Methodology2.3.2Single-threaded simulation2.3.3Multi-threaded simulation                                                  | 19<br>20             |

|     | 2.4          | Analysis                                                                                                                       | 24<br>25<br>27       |

|     | 2.5          | 2.4.2Behavior of the partitioned-cacheRelated work2.5.1Phase change memory based memory systems2.5.2Cache replacement policies | 28<br>29<br>30<br>31 |

|     |              | 2.5.3 Cache organization                                                                                                       | 31                   |

| 3.  |              | MFS: A HYBRID FILE SYSTEM FOR IMPROVING RANDOM WRITENAND-FLASH SSD                                                             | 33                   |

|     | $3.1 \\ 3.2$ | Background                                                                                                                     | 33<br>37             |

|       | 3.2.1 Hybrid storage architecture                                                                         | 37 |

|-------|-----------------------------------------------------------------------------------------------------------|----|

|       | 3.2.2 File system layout $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 39 |

|       | 3.2.3 Data distribution and write reorganization                                                          | 41 |

|       | 3.2.4 Non-overwrite on solid state drive                                                                  | 44 |

|       | 3.2.5 File system consistency                                                                             | 46 |

| 3.3   |                                                                                                           | 48 |

|       | $3.3.1$ Methodology $\ldots$                                                                              | 48 |

|       | 3.3.2 Reduced i/o traffic to solid state drive                                                            | 49 |

|       | 3.3.3 Reduced erase operations and overhead on solid state drive                                          | 51 |

|       | 3.3.4 Improved i/o throughput                                                                             | 54 |

| 3.4   | Related work                                                                                              | 60 |

| 4. SP | ACE MANAGEMENT OF SSD BASED SECONDARY DISK CACHES                                                         | 63 |

| 4.1   | Background                                                                                                | 63 |

| 4.2   | 8                                                                                                         | 68 |

|       | 4.2.1 Multi-device aware caching                                                                          | 68 |

|       | 4.2.2 Flexible data redundancy                                                                            | 70 |

|       | 4.2.3 Balance the writes among solid state drives                                                         | 70 |

| 4.3   | ő                                                                                                         | 71 |

|       | $4.3.1$ Methodology $\ldots$                                                                              | 72 |

|       | 4.3.2 Results                                                                                             | 72 |

| 5. EX | PLOITING SUPERPAGES IN A NONVOLATILE MEMORY FILE                                                          |    |

|       | STEM                                                                                                      | 76 |

|       |                                                                                                           |    |

| 5.1   | 0                                                                                                         | 76 |

| 5.2   | 0 1                                                                                                       | 78 |

|       | 5.2.1 Preservation for superpage                                                                          | 78 |

|       | 5.2.2 Space utilization                                                                                   | 79 |

|       | 5.2.3 Modifications to kernel                                                                             | 80 |

| 5.3   |                                                                                                           | 81 |

|       | 5.3.1 Methodology $\ldots$                                                                                | 81 |

|       | 5.3.2 Iozone results                                                                                      | 83 |

|       | 5.3.3 Postmark results                                                                                    | 87 |

| 5.4   | Related work                                                                                              | 87 |

| 6. CC | ONCLUSION                                                                                                 | 89 |

| REFE  | RENCES                                                                                                    | 91 |

|       |                                                                                                           | 51 |

# LIST OF FIGURES

# FIGURE

# Page

| 1.1  | Main memory and disk storage of a computer system                                                                               | 1  |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | PCM device and circuit. [18]                                                                                                    | 3  |

| 1.3  | Hard disk drive VS. solid state drive                                                                                           | 5  |

| 2.1  | Number of total evictions per unique dirty line from a typical, 16-way, 2MB, last-level cache (LLC) for SPEC CPU2006 benchmarks | 10 |

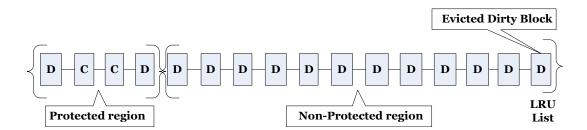

| 2.2  | MRU-LRU list for one set in a cache using the Protect-0 replacement algorithm.                                                  | 13 |

| 2.3  | MRU-LRU list for one set in a cache using the Protect-N replacement algorithm (N=4).                                            | 15 |

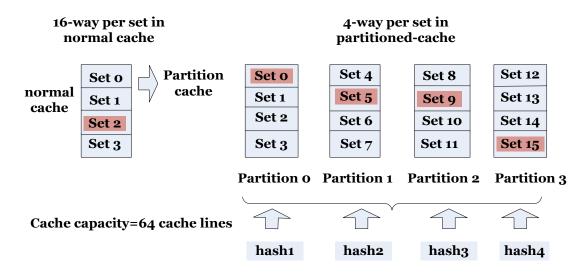

| 2.4  | The organization of partitioned-cache.                                                                                          | 16 |

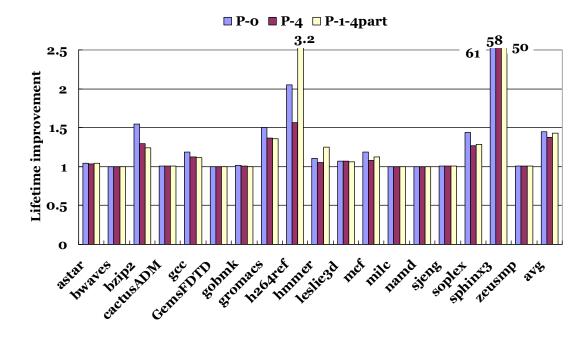

| 2.5  | Lifetime improvement of SPEC2006 benchmarks on randomized wear-<br>leveling PCM system                                          | 21 |

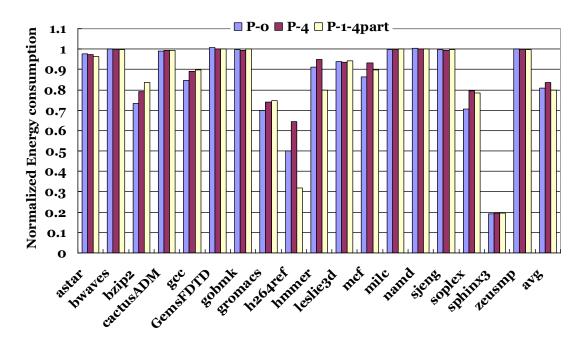

| 2.6  | Normalized energy consumption for SPEC2006 benchmarks                                                                           | 22 |

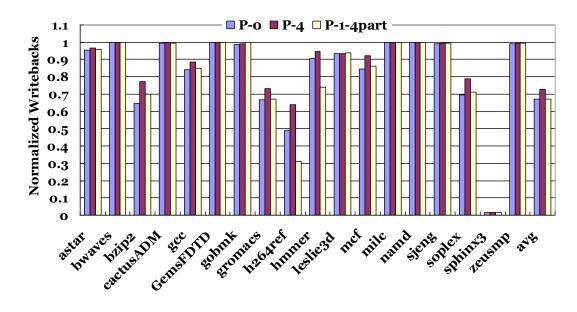

| 2.7  | Normalized last-level cache writebacks for SPEC2006 benchmarks                                                                  | 23 |

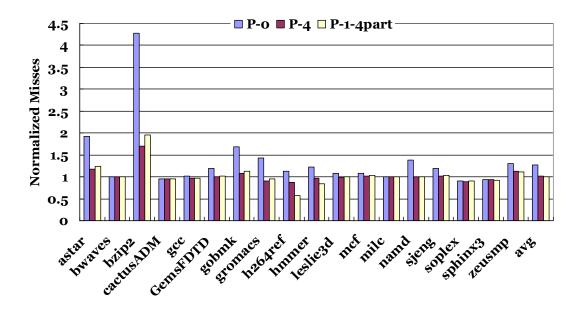

| 2.8  | Normalized last-level cache misses for SPEC2006 benchmarks                                                                      | 24 |

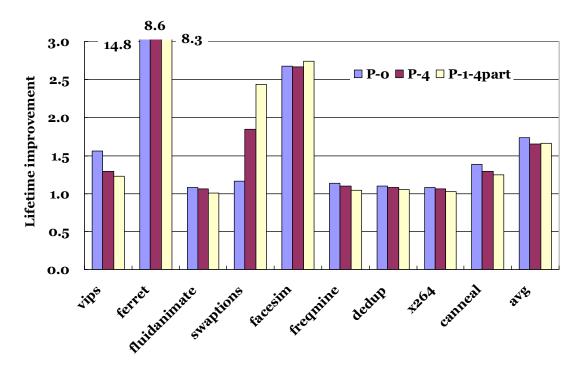

| 2.9  | Lifetime improvement of PARSEC benchmarks on randomized wear-<br>leveling PCM system                                            | 25 |

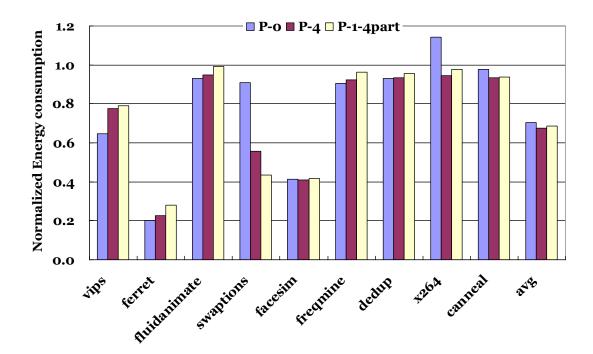

| 2.10 | Normalized energy consumption for PARSEC benchmarks                                                                             | 26 |

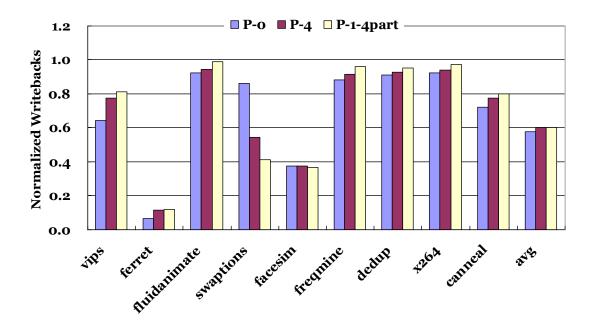

| 2.11 | Normalized last-level cache writebacks for PARSEC benchmarks                                                                    | 26 |

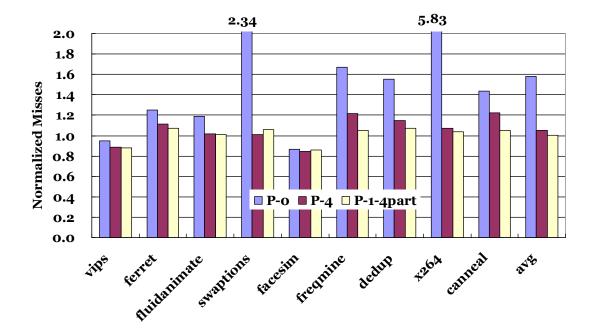

| 2.12 | Normalized last-level cache misses for PARSEC benchmarks                                                                        | 27 |

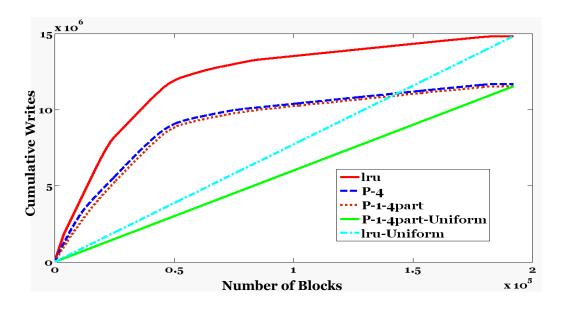

| 2.13 | Write distribution of soplex                                                                                                    | 28 |

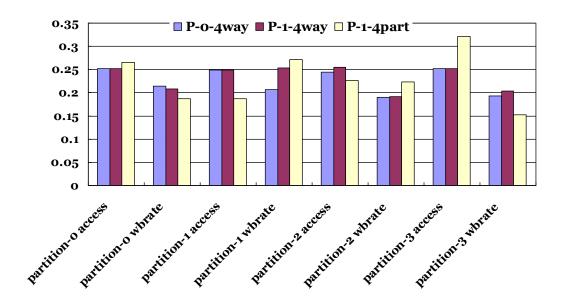

| 2.14 | Accesses, writeback rate of each partition under hmmer application                                                              | 29 |

| 3.1  | Non-volatile DIMMs                                                                                                              | 34 |

| 3.2  | Hybrid storage architecture                                                                 | 38 |

|------|---------------------------------------------------------------------------------------------|----|

| 3.3  | Storage space layout                                                                        | 40 |

| 3.4  | Dirty and clean LRU lists                                                                   | 42 |

| 3.5  | Migrate dirty NVRAM pages to SSD                                                            | 43 |

| 3.6  | Space management on SSD                                                                     | 45 |

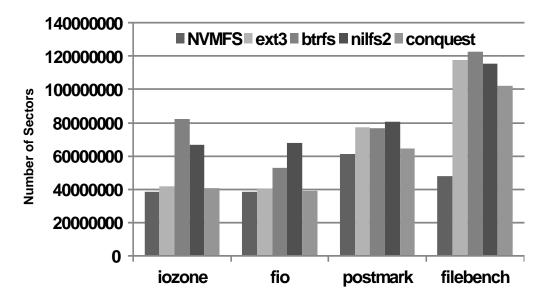

| 3.7  | Write traffic to SSD under different workloads and file systems                             | 50 |

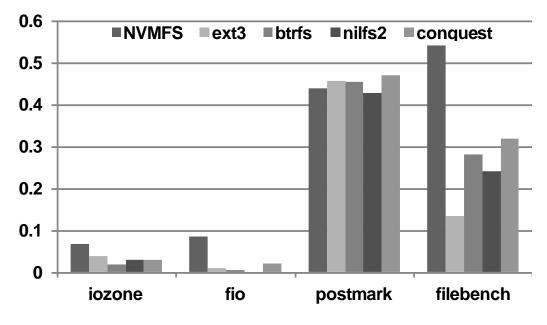

| 3.8  | Hit ratio on memory                                                                         | 51 |

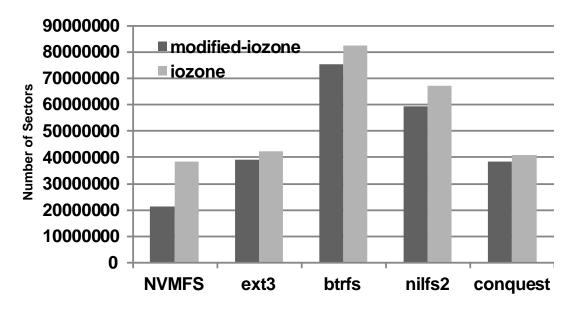

| 3.9  | Write traffic to SSD under modified iozone                                                  | 52 |

| 3.10 | Average I/O request size issued to SSD under different workloads and file systems           | 52 |

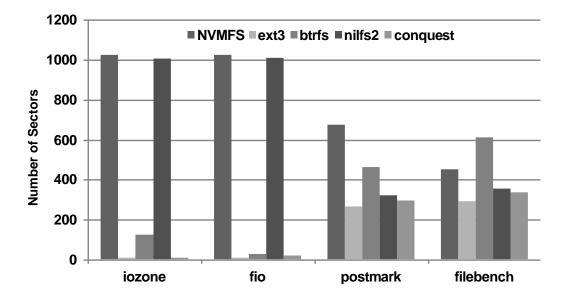

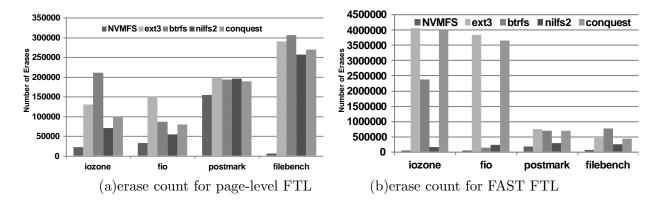

| 3.11 | Erase count for page-level and FAST FTL                                                     | 53 |

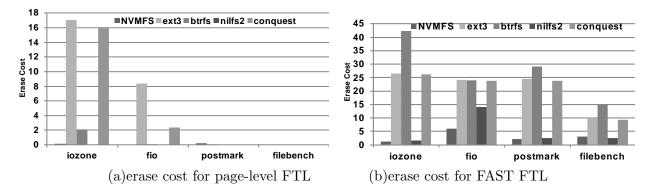

| 3.12 | Erase cost for page-level and FAST FTL                                                      | 53 |

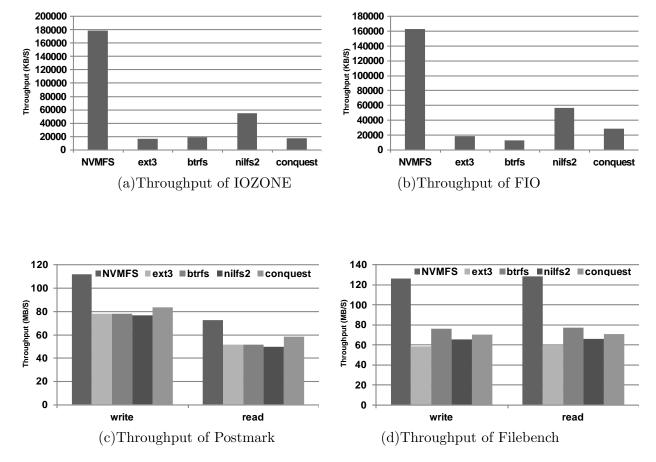

| 3.13 | I/O throughput under different workloads for $50\%$ - $70\%$ disk utilization               | 55 |

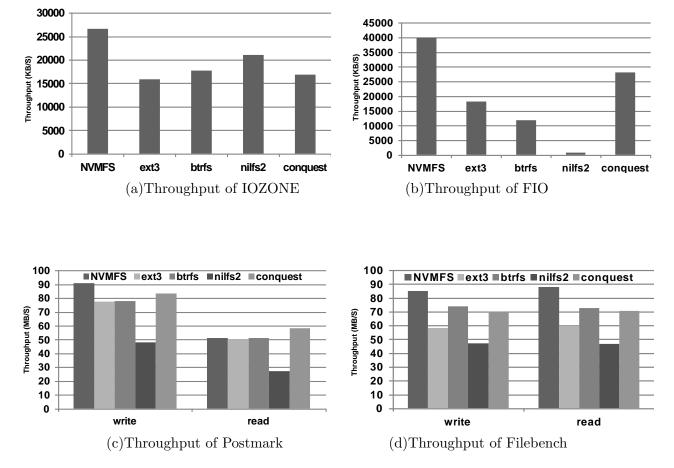

| 3.14 | I/O throughput under different workloads for over $85\%$ disk utilization                   | 56 |

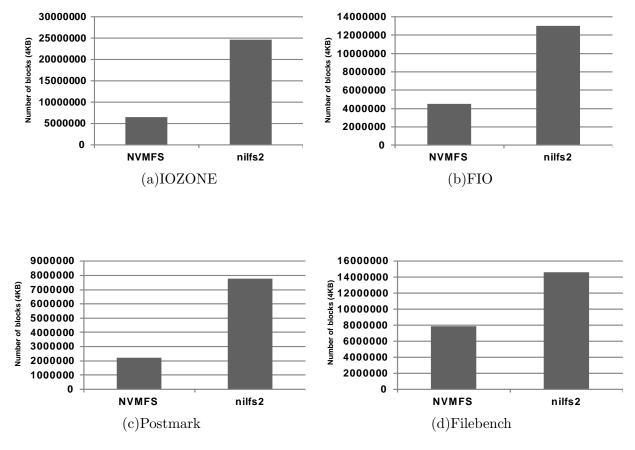

| 3.15 | Total number of recycled blocks while running different workloads<br>under NVMFS and nilfs2 | 57 |

| 3.16 | Cleaning efficiency while running different workloads under NVMFS and nilfs2                | 58 |

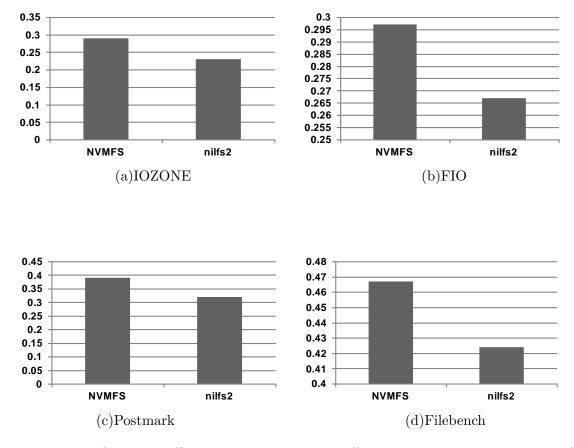

| 4.1  | SSD cache based disk storage system                                                         | 64 |

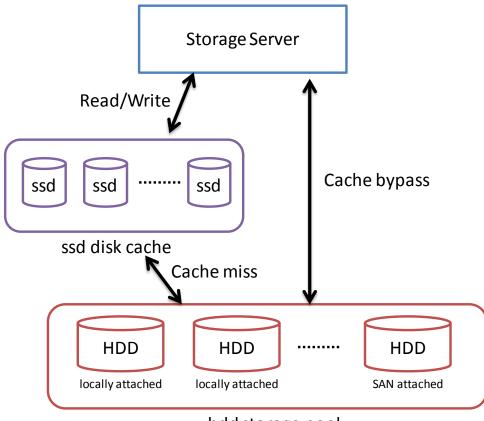

| 4.2  | Bcache based on RAID in a multi-device environment. $\ldots$ $\ldots$ $\ldots$              | 66 |

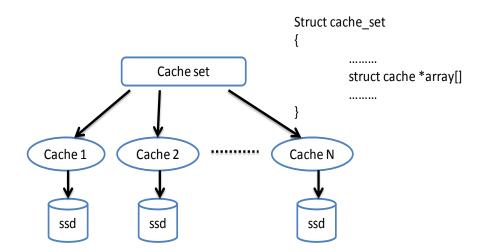

| 4.3  | Extensions made to the cache set structure of bcache                                        | 69 |

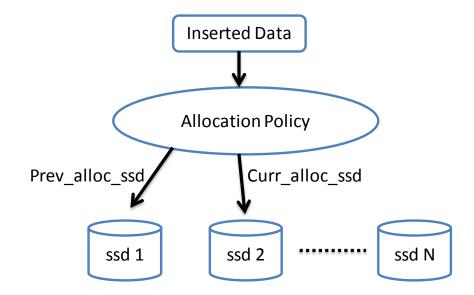

| 4.4  | Insert data to SSDs based on round-robin style                                              | 71 |

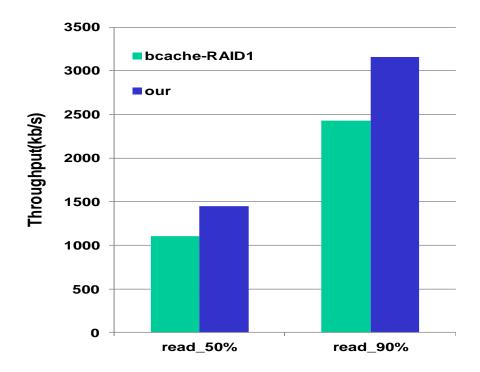

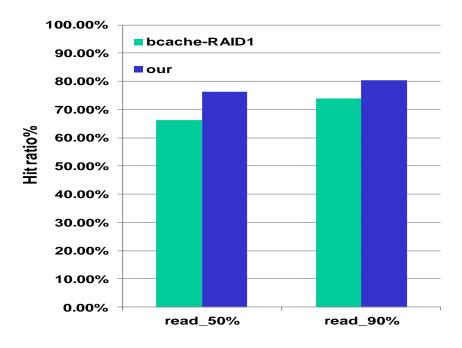

| 4.5  | The throughput of the storage system while running different workloads.                     | 73 |

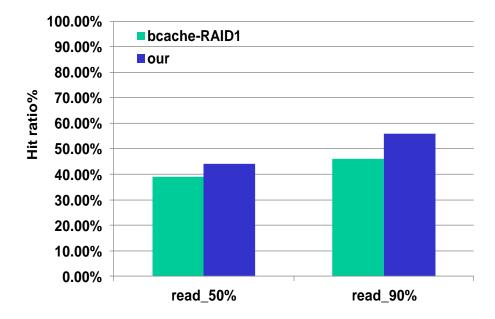

| 4.6  | The hit ratio of SSD caches while running different workloads                               | 73 |

| 4.7  | The hit ratio of SSD caches after reducing the cache size                                   | 74 |

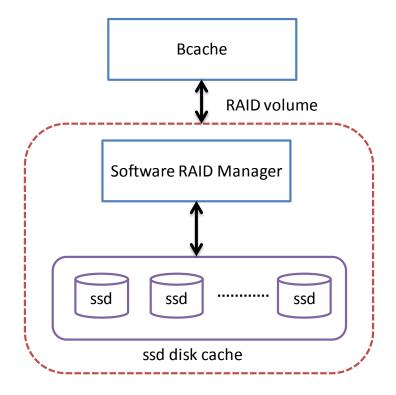

| 5.1  | Storage class memory                                                                        | 77 |

| 5.2  | Physical space of SCM                                                                       | 79 |

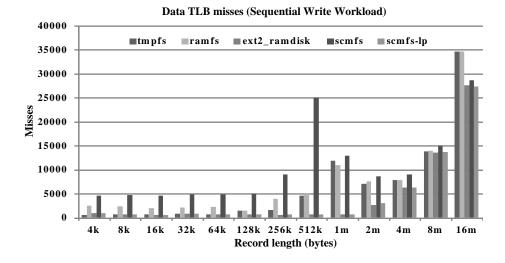

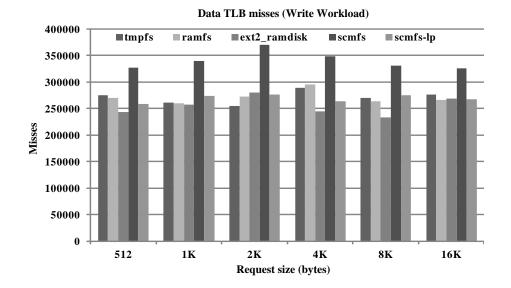

| 5.3  | TLB misses – iozone sequential write workload                                      | 82 |

|------|------------------------------------------------------------------------------------|----|

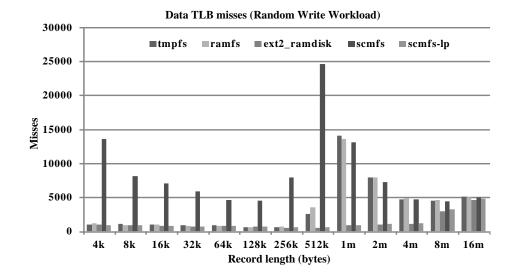

| 5.4  | TLB misses – iozone random write workload $\hdots$                                 | 82 |

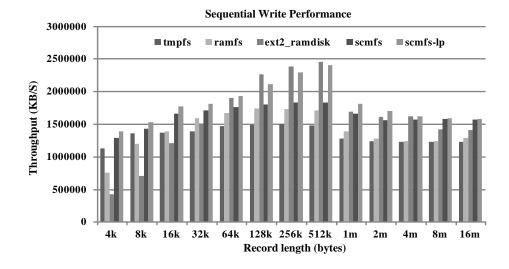

| 5.5  | Throughput – iozone sequential write workload $\ldots \ldots \ldots \ldots \ldots$ | 84 |

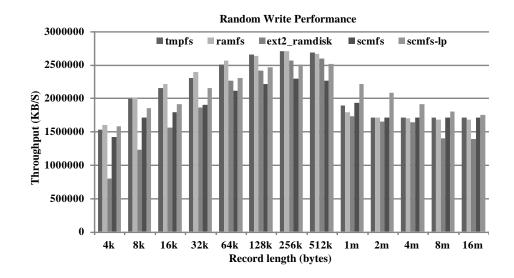

| 5.6  | Throughput – iozone random write workload                                          | 84 |

| 5.7  | TLB misses – postmark's write workload                                             | 85 |

| 5.8  | TLB misses – postmark's read workload                                              | 85 |

| 5.9  | Throughput of postmark's write workload                                            | 86 |

| 5.10 | Throughput of postmark's read workload                                             | 86 |

# LIST OF TABLES

| TABLI | Page                             |

|-------|----------------------------------|

| 1.1   | PCM vs DRAM characteristics [18] |

| 2.1   | Baseline cache configurations    |

#### 1. INTRODUCTION

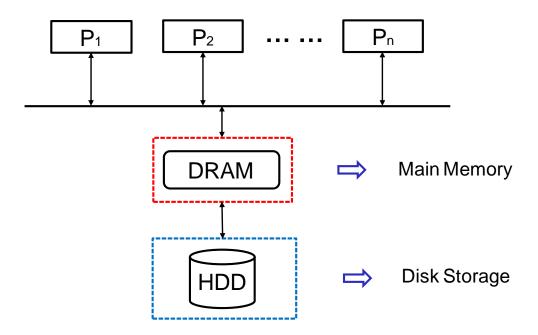

Within existing storage hierarchy of a computer system, main memory and disk storage are two important components as shown in figure 1.1. The main memory is normally composed of Dynamic Random Access Memory (DRAM) which is volatile and supports fast random read and write accesses. For personal desktop or laptop, it's sufficient to have several GBs' memory, while large computing servers usually require much larger capacity memory systems. However, DRAM technology is now hitting hard power and capacity constraints that will limit its future process technology scaling [30]. The technology scaling constraints for DRAM memory recently led to the emergence of Phase Change Memory as an alternative form of main memory in future processor designs [67]. We will introduce this in section 1.1.

Figure 1.1: Main memory and disk storage of a computer system.

Another important component is the data/disk storage. When data are not in memory, we need to first fetch them from disk storage. Moreover, to ensure data endurance, existing memory systems need to write data updates to the disk storage within a short time since DRAM is volatile and cannot sustain power failure. Therefore, the read and write speed of the disk storage can directly affect the overall performance of the whole system. Traditional hard disk has low performance for random operations, which led to the emergence of solid state disk (SSD) and other emerging nonvolatile memories as an alternative or a complementary building block for storage. We will describe it in section 1.2.

#### 1.1 Main memory technology

Dynamic random access memory (DRAM) is the predominant technology for main memory in current processor systems. DRAM technology, however, is now hitting hard power and capacity constraints that will limit its future process technology scaling [30]. Phase-Change Memory (PCM) has been proposed as an alternate technology for processor memory systems [45, 63, 88, 61, 65].

PCM technology utilizes a class of materials known as chalcogenides. An alloy of Germanium, Antimony and Tellurium  $(Ge_2Sb_2Te_5)$  is one such alloy used by some manufacturers [57, 3]. These materials can exist in two different states, either crystalline or amorphous. By heating the chalcogenides, the phase (or the state) can be changed or reversed between amorphous and crystalline states. The material exhibits high resistivity in amorphous state and low resistivity in crystalline state allowing binary states of 0/1 to be represented. While DRAM, is volatile and must be refreshed, leading to a constant power consumption even when idle, PCM is nonvolatile and retains the state even when the power is off.

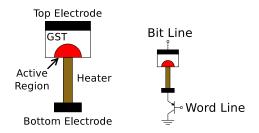

Figure 1.2 [18] shows a diagram of a single PCM device cell and the circuit used

Figure 1.2: PCM device and circuit. [18]

to construct a memory cell from a PCM device. A PCM cell consists of two electrodes with a layer of chalcogenide in between. As shown in Figure 1.2, a resistive heating element extends from the bottom electrode to the layer of chalcogenide. Current injected through the heating element changes the state of the chalcogenide through local heating. The density of PCM arrays is expected to scale with process technology better than the capacitance used in a DRAM cell as the semiconductor technology progresses for two reasons: 1) As the access transistor in capacitive DRAM cells shrink, their sub-threshold leakage increases, eventually making further shrinks impractical. Resistive PCM cells do not rely upon capacitive charge to determine state [45]. 2) Future PCM cells promise the capacity of storing more than one bit per cell further increasing their density versus DRAM cells [3].

Since writing a PCM cell involves thermal energy, writes take higher energy. Table 1.1 details the read and write power for PCM versus DRAM in 78nm technology. A write to PCM typically requires more power compared to an equivalent write to DRAM. On the other hand, reads to PCM are less expensive in power consumption than a DRAM. As this data shows, while PCM is 2.5x more efficient than DRAM for reads, writes are 4x more expensive for PCM. The table also shows, while DRAM row read latency can be about 15ns, the read latency of PCM can range from 15-28ns. Similarly a DRAM row write latency can be about 20ns, the write latency in PCM is about 150ns [18].

As Table 1.1 shows, both the power consumption and latency characteristics of read/write operations, PCM exhibits asymmetric performance characteristics, with reads being much more efficient than writes. These characteristics require attention when designing a memory system using PCM. The asymmetry of read/write characteristics require that read/write accesses be differently optimized.

|                             | PCM   | DRAM              |

|-----------------------------|-------|-------------------|

| Row read power              | 78mW  | $210 \mathrm{mW}$ |

| Row write power             | 773mW | $200 \mathrm{mW}$ |

| Initial row read latency    | 28ns  | 15 ns             |

| Row write latency           | 150ns | 20ns              |

| Same row read/write latency | 15ns  | 15ns              |

Table 1.1: PCM vs DRAM characteristics [18]

As introduced above, PCM has different characteristics than DRAM. PCM is expected to be available in higher densities than DRAM in the future; PCM memory is also non-volatile. These characteristics of PCM have spurred novel memory hierarchy designs. Relative to DRAM, PCM memory, however, introduces some new design constraints. PCM memory's read and write access characteristics are asymmetric. Reads are more efficient in access time and power consumption than writes. PCM memory cells also have a limited number of write cycles before they wearout. Hence, a memory system employing PCM needs to address this asymmetry in its design.

In Chapter 2, we present our design for employing PCM in memory system considering the impact of this asymmetry. We propose low-complexity techniques, utilizing existing cache memory systems, to substantially improve the lifetime durability and energy consumption of PCM main memory.

#### 1.2 Disk storage technology

Traditional data/disk storage is built using hard disks. Hard disk stores data on rapidly rotating disks (platters) coated with magnetic material. Hard disks, shown in Figure 1.3a, can retain data even when powered off. The sequential read and write operations are much faster than the random ones due to the so called seek latency. The factors that limit the time to access the data on an HDD (Hard Disk Drive) are mostly related to the mechanical nature of the rotating disks and moving heads. Seek time is a measure of how long it takes the head assembly to travel to the track of the disk that contains data. For random read or write requests, we might need to frequently change the head assembly to different disk tracks which results in much worse performance than sequential accesses.

(a)Hard Disk Drive of Laptop

(b)Solid State Drive

Figure 1.3: Hard disk drive VS. solid state drive

New disk devices based on NAND-flash memory are becoming available with different performance characteristics from traditional magnetic hard disks. Figure

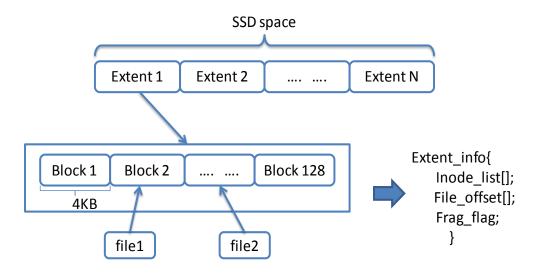

1.3b shows a NAND-flash based Solid State Drive (SSD). SSDs have no moving mechanical components, therefore there is no seek latency. They have good random performance, especially for read operations. However, NAND-flash cannot support in-place updates and has limited write endurance. When we update existing data, SSDs will write them to new places and mark the original data as invalid. To recycle the invalid pages, we need to erase a whole SSD block which normally contains 64-128 pages. The erase operation is very expensive which limits the write performance of SSDs. There are different types of SSDs, namely SLC, MLC and TLC according to the number of bits can be programmed per single cell. For SLC SSD, each cell can only represent one bit '0' or '1', while the cell of MLC and TLC SSD can represent more than one bit. Therefore, the capacity of SLC SSD is smaller than the corresponding MLC and TLC devices, however, the performance of SLC SSD is better than the MLC and TLC devices. The SSDs reuse the standard hard disk interfaces. To achieve out-of-place updates, there is a layer called Flash Translation Layer (FTL) inside SSD that manages the address mapping. It maps a logical block address (LBA) seen by the operating system to the actual physical block address (PBA) of a flash page. Moreover, to facilitate the space allocation and balance the flash cell's wear-out, FTL also controls the wear leveling and garbage collection. When the available empty blocks of the SSD are not sufficient, the garbage collection process will recycle those used blocks. To recycle a used block, the garbage collection process has to first migrate all the valid pages to a new block, then erase the old block.

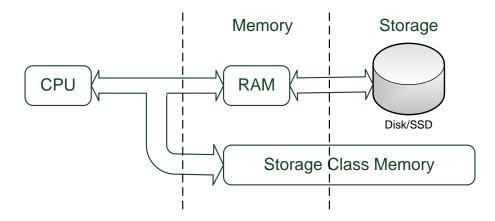

Moreover, emerging nonvolatile memory technologies (sometimes referred as Storage Class Memory (SCM)), are poised to close the enormous performance gap between persistent storage and main memory. They can provide better performance than flash-based SSDs. The SCM devices can be attached directly to memory bus and accessed like normal DRAM. It becomes then possible to exploit memory management hardware resources to improve file system performance. However, in this case, SCM may share critical system resources such as the TLB, page table with DRAM which can potentially impact SCM's performance.

Our research work in this part focuses on building efficient and high performance data storage utilizing flash-based SSDs and the emerging nonvolatile memories.

In chapter 3, we integrate nonvolatile DIMMs and flash SSD as a hybrid storage, instead of building disk storage on SSD directly. The nonvolatile DIMMs combine traditional DRAM, Flash, an intelligent system controller, and an ultracapacitor power source to provide a highly reliable memory subsystem that runs with the latency and endurance of the fastest DRAM, while also having the persistence of Flash (data on DRAM will be automatically backed up to flash memory on power failure). We utilize nonvolatile DIMMs to further improve SSD's performance. We know that SSD has good random read performance, however, small random writes bring down its performance and lifetime. We design a hybrid storage system managed by our proposed file system, NVMFS, which utilizes nonvolatile DIMMs to absorb the small random write requests. When the space of nonvolatile DIMMs is not sufficient, we begin to flush data to SSD in large and optimized write units. As a result, our design effectively improves the performance of SSD while improving the garbage collection overhead.

In chapter 4, we design a secondary disk cache utilizing multiple SSDs, which can be shared by a number of hard disk drives. Instead of managing the SSD devices as a traditional RAID volume, we manage them directly at the cache layer. To improve the cache space utilization, we only duplicate dirty data that are cached in SSDs. This ensures that we won't lose any data for single SSD failure at the cache layer. As a result, our design significantly improved the hit ratio of the SSD caches and the throughput of the storage system.

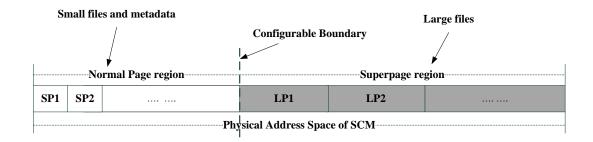

In chapter 5, we analyze the problem of increased TLB misses while employing the emerging nonvolatile memories as data storage. We propose to solve this problem by employing superpages to reduce the pressure on memory management resources such as the TLB. As a result, the file system performance is further improved. We also analyze the space utilization efficiency of superpages. We improve space efficiency of the file system by allocating normal pages (4KB) for small files while allocating super pages (2MB on x86) for large files. We show that it is possible to achieve better performance without loss of space utilization efficiency of nonvolatile memory.

# 2. PROCESSOR CACHE DESIGN TO IMPROVE LIFETIME AND ENERGY IN PCM-BASED MAIN MEMORY

While process technology scaling continues providing ever greater numbers of transistors, current and future process technologies constrain the transistor performance and power gains that traditionally accompanied process scaling [30]. Recently this trend led to the emergence of chip-multiprocessor (CMP) designs as a means to leverage increasing transistor counts to achieve greater application performance more with more power efficiency than traditional monolithic processors. Similar technology scaling constraints for DRAM memory recently led to the emergence of Phase Change Memory (PCM) as an alternative form of main memory in future processor designs [67]. While PCM memory provides better power and density scaling in future process technologies, it introduces new design challenges with respect to lifetime durability and wear-out. In this chapter, we propose low-complexity techniques, utilizing existing cache memory systems, to substantially improve the lifetime durability and energy consumption of PCM main memory.

#### 2.1 Background

#### 2.1.1 Processor cache hierarchies

Current applications are placing greater pressure on their memory systems to maintain data and instruction stream needs. To this end, current chips employ memory system hierarchies with three levels of cache prior to main memory [51]. Multi-level cache hierarchies provide an approximation of a unified, fast, large memory space, through the low latency access times of small, private, first-level caches and the large capacities of shared, last-level caches. As the design of the last-level cache is optimized towards capacity rather than speed, these caches are often highly associative.

In all associative caches, when a cache miss occurs a decision must be made regarding which block will be evicted and replaced. Current caches typically employ Least Recently Used (LRU) or approximations of LRU policies in deciding on which victim block to evict from cache in order to make room for a missing block. If the victim block is clean, it is simply discarded, however, if the current victim block is dirty, it must be written to memory before the new block may be written to cache. While many variations of LRU and other policies such as Least Frequently Used (LFU) [47] have been studied, much of the focus of this research has been on minimizing overall miss ratio at the caches.

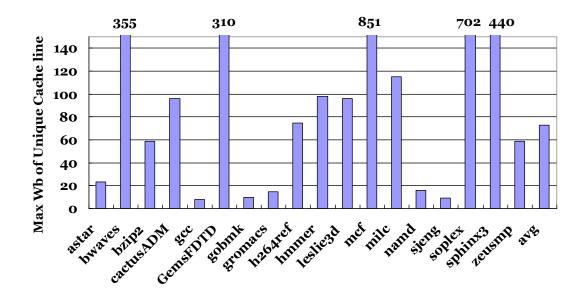

Figure 2.1: Number of total evictions per unique dirty line from a typical, 16-way, 2MB, last-level cache (LLC) for SPEC CPU2006 benchmarks.

As a result of this miss ratio focus, LRU and it's variants often lead to frequent re-writebacks of dirty cache lines to main memory, as illustrated in Figure 2.1. The figure shows the total number of dirty evictions from a processor's LLC divided by the total number unique dirty lines, giving the average number of times each dirty line is re-written to the main memory for applications in the SPEC CPU2006 benchmark suite. As the figure shows, more than half the benchmarks re-evict the same dirty lines more than 10 times *on average*, two benchmarks re-evict cache lines hundreds of times on average. Given the PCM cell's high write cost in terms of energy, latency and wearout, re-writing the same cache lines repeatedly is highly undesirable. We propose to shift the focus of LLC design to account for the costs of writes to PCM based main memory, while maintaining low miss rates.

#### 2.1.2 Last-level cache based writeback reduction

In this Chapter, we introduce new cache replacement policies and cache organizations that reduce the writeback data volume while minimizing the impact of cache miss rates. Figure 2.1 shows that many dirty cache lines written back to main memory will later be modified again, effectively ping-ponging from memory to cache and back many times during the course of the application. This Chapter examines techniques to favor retention of frequently re-written dirty lines, over lines which are clean. We observe that modern LLCs are both large relative to application footprints and highly associative, yielding an opportunity to reduce writebacks while minimally increasing misses to the LLC. Furthermore, as the techniques developed only imply changes to the LLC, the effect on the total memory system access latency is very small. The primary contributions of our design are as follows:

- We proposes a set of new cache replacement policies which favor eviction of clean data over dirty data. These policies are simple to implement and imply very low hardware overhead.

- We proposes a new cache organization which partitions sets to further favor

the retention of frequently re-written dirty lines. This cache organization is a natural fit for the banking typically found in LLCs, implying very little extra hardware overhead.

- We show these replacement policies and the new cache organization improve PCM lifetime by 49%-66% over a memory system employing randomized wear-leveling techniques [63].

- We also show our design reduce PCM energy consumption by 21%-31% on average over traditional LLC cache design.

#### 2.2 Design and implementation

Based upon the observation that dirty blocks are often re-written to main-memory many times during a program's execution, we propose low-complexity, low-overhead techniques to modify the LLC with the goal of retaining dirty blocks which will be re-written frequently while maintaining low miss-rates. Our techniques address two aspects of cache design: cache replacement policies and cache organization. The proposed cache replacement policies favor replacement of clean blocks, keeping dirty blocks in the LLC longer, effectively reducing redundant writebacks. Moreover, we propose a new cache organization—the *partitioned-cache*, which aims to further bias replacement to favor those particular dirty blocks in a set which are re-written most frequently. The partitioned-cache accomplishes this by sub-dividing cache sets into partitions and adaptively determining which partition to select blocks to evict from depending on the relative writeback performance of those partitions. These techniques not only prolong the lifetime of PCM-based main memory, but also save the power and energy since PCM device has much higher power consumption and latency for write relative to read. This section discusses cache replacement policy based writeback reduction as well as cache organization based writeback reduction.

#### 2.2.1 Cache replacement policy

PCM-based main memory has limited write endurance and different read and write cost in terms of time and energy. As a result, the cache replacement algorithm of the LLC used with PCM-based main memory should consider not only the miss-rate but also the cost, in terms of energy and lifetime, for replacing dirty blocks. Therefore, we propose two cache replacement policies for the last-level of cache which extend conventional LRU by integrating write costs to PCM main memory with cache locality. Our policies reduce the write traffic of last-level cache to PCM main memory, while maintaining a low miss rate. The first policy, *Protect-0* maximally reduces the writeback of last-level cache. The other policy, *Protect-N*, seeks to balance write traffic reduction and the last-level cache's misses.

#### 2.2.1.1 Protect-0

There are two costs for cache replacement on the last-level cache. One is the read cost of fetching a requested cache block from main memory. The read cost may be minimized through cache locality, and is the focus of the LRU replacement algorithm. PCM-based main memory introduces a second, write cost, when evicting a dirty cache block from the last-level cache. PCM-based main memory has higher write access latency relative to read, and limited write endurance; we therefore propose the *Protect-0* cache replacement algorithm to maximally reduce the writeback cost.

Figure 2.2: MRU-LRU list for one set in a cache using the Protect-0 replacement algorithm.

Protect-0, shown in Figure 2.2, is a modified form of the LRU algorithm. When a replacement is required in the last-level cache, Protect-0 searches the LRU list to find an LRU clean block to replace. In the figure, the LRU clean block is the block next to the LRU block, so it is chosen for the next eviction by Protect-0. If there's no clean block in the LRU chain, Protect-0 replaces the dirty LRU block.

Protect-0 attempts to maximally reduce write traffic to PCM main memory. As long as there are clean blocks in LRU chain, Protect-0 will always select a clean block for replacement and no additional writes to PCM main memory are generated. Protect-0 fosters the retention of dirty cache blocks in the cache longer than clean blocks. The longer dirty blocks remain in the cache, the more likely they are to receive subsequent writes, reducing the total number of write-backs over the course of the program by reducing the frequency with which dirty blocks ping-pong between the main memory and the cache. The disadvantage of Protect-0 is it violates the principle of temporal locality for clean blocks and therefore, may increase misses in the LLC in the event that the replaced clean block is referenced again in the near future and the preserved dirty block is not.

## 2.2.1.2 Protect-N

To minimize the increased misses caused by Protect-0, we propose another policy called *Protect-N*. Protect-N balances dirty replacements against increased misses. Previous studies have shown, in highly associative caches when sets are sorted in most recently used (MRU) to LRU order, the vast majority of hits typically occur in the first few MRU ways of the cache and the remaining ways provide only marginal decreases in miss rate. Protect-N leverages this observation by dividing the LRU list into two parts: the protected region and the non-protected region. The protected region contains the N MRU blocks for which temporal locality is preserved regardless

of clean/dirty status. The non-protected region includes the rest of the cache blocks (W-N for W-way cache) in the LRU list. Protect-N only applies clean-first policy to the non-protected cache blocks of the LRU chain. By protecting the N MRU blocks, it is expected that locality will be preserved while reducing the writebacks by evicting clean blocks from the remaining (LRU) blocks.

Determining the window size of N is very important to minimize misses while preserving dirty data. A large protected window size will reduce the possibility of finding a clean block for replacement, leading to more dirty replacements in PCMbased main memory. A small protected window size increases the chances of replacing a clean block that is likely to be referenced soon, leading to an increased miss rate of last-level cache. Considering both two kinds of replacement cost of last-level cache, we experimentally determined the best value of N to be 4 for 16-way, 2 for 8-way and 1 for 4-way caches.

Figure 2.3: MRU-LRU list for one set in a cache using the Protect-N replacement algorithm (N=4).

The Protect-N algorithm always protects the first N MRU blocks regardless of their clean/dirty status and only applies the clean-first policy to the non-protected blocks. As shown in Figure 2.3, if Protect-N fails to find a clean block from the non-protected region of LRU list, it will simply replace the LRU block. In the figure, there are no clean blocks in the non-protected region, therefore Protect-N (N=4 in this case) will choose the LRU block for replacement. Since the LRU block is dirty, a writeback request must be generated to the lower-level PCM-based main memory. Protect-N may not perform as well as Protect-0 at reducing write traffic, however attempts to balance the miss rate of last-level cache against writebacks to the main memory.

#### 2.2.2 Cache organization

We observe that dirty cache blocks which are evicted and re-fetched repeatedly over the course of a program's execution often will have significant intervening references between consecutive writes. This is often the case in applications which stream clean data through the cache. It also can occur in applications which frequently allocate and free temporary data space on the heap and stack. In these instances Protect-N is unable to retain critical dirty blocks in the cache until their subsequent reuse.

Figure 2.4: The organization of partitioned-cache.

To address the applications where Protect-N is insufficient to reduce re-writes of dirty data, we propose a new adaptive form of cache organization—*partitioned-cache*, which aims to preserve dirty cache blocks longer than Protect-N while introducing fewer misses than Protect-0. Figure 2.4 shows the difference between a normal cache and the partitioned-cache. As the figure shows, the partitioned-cache divides a Protect-N W-way cache into M partitions, each maintaining a smaller (N/M) protected region. In the figure, the partitioned-cache separates the original 16-way set into four 4-way sets, and applies Protect-1 within each of them.

As in a typical cache, the referenced block address in the partitioned-cache is divided into three components: the tag, the set index, and the offset, however in the partitioned-cache the least significant bits of the tag are used as a partition index. Upon receiving a reference, the set index determines which set and the tag is used to match the block within the set. All partitions of the set are searched in parallel. If the reference is a hit, the LRU list of the corresponding set of partition is updated. In the event of a miss, the partition index indicates a preferred partition within the set, to search for a clean block for eviction. In operation this is similar to Protect-N operating only within the preferred partition within the set. In the event that no unprotected clean block is found in the preferred partition of the set, the partition within the cache which has the most clean blocks is adaptively chosen to receive the miss. If no partitions have unprotected clean blocks then the preferred partition's LRU dirty block is evicted.

For the address shown in Figure 2.4, set 2 of Partition 1 will be considered first. If Protect-1 fails to find a proper clean block in set 2 of Partition 1, it will further search other partitions. Finally, if we cannot replace a proper clean block among all the partitions, the LRU block of mapped set within the preferred partition, set 2 of Partition 1, is evicted. The benefit of the partitioned-cache lies in its longer term preservation of dirty blocks in the set partitions which contain the most dirty blocks. The partition cache steers replacement traffic away from those partitions which receive the most dirty blocks, allowing them to stay in the cache longer than the partitions which contain some clean blocks. As a result, the cache access traffic is shifted to the partition that has a lower writeback rate (writebacks per cache access), further reducing the writeback traffic to PCM-based main memory.

We note that, in comparison with the Protect-N cache, the partitioned-cache has little additional design complexity and latency overhead. Initial tag matching is done in parallel among a set's partitions as in a traditional cache of the same associativity, and hence incurs no extra latency on hits. The logic overhead of adaptive partition selection upon a miss may be placed in the cache's pipeline after the missing block's fetch from main memory has been initiated and prior to it's return, hence off the critical path. We also note that our policies are only imposed on the LLC and not the rest of the cache hierarchy and the resultant LLC does not retain the inclusion property.

#### 2.3 Evaluation

The primary goal of this work is to improve PCM main memory lifetime, and energy through a reduction in the number of writebacks to main memory from the LLC while maintaining a low impact on system performance. To this end, in this section we evaluate our modified cache replacement algorithm and cache organization in their direct impact on PCM lifetime and energy consumption. We then examine the cache performance in terms of writebacks and misses, which cause the corresponding changes on PCM memory lifetime and energy. We note that the techniques which require substantial changes to the main memory system and do not focus on the

| System             | One core      |        |      | Eight cores   |         |        |      |

|--------------------|---------------|--------|------|---------------|---------|--------|------|

| L1 cache (Private) | 64KB,         | 2-way, | LRU, | 64KB          | L1, 2-  | way, L | LRU, |

|                    | 64Bytes block |        |      | 64Bytes block |         |        |      |

| L2 cache (Shared)  |               |        | LRU, | 8MB,          | 16-way, |        | LRU, |

|                    | 64Bytes block |        |      | 64Bytes block |         |        |      |

Table 2.1: Baseline cache configurations

LLC [61, 65, 63], are orthogonal and complimentary to our techniques. As such they are not evaluated in this work for the sake of brevity.

## 2.3.1 Methodology

The proposed cache replacement policy and cache organization were evaluated with both single- and multi-core configurations. Our baseline processor configurations for an 8-core CMP and a single core system are shown in Table 2.1. In both models, each core has its own private L1 caches, each 64KB. In the CMP model, a shared 8MB, 16-way L2 cache forms the last-level cache (LLC), upon which our modified cache replacement policies and cache organization are used. The L1 and L2 caches in both models have the same block size of 64Bytes.

For single core simulation, we use 18 applications from SPEC CPU2006 benchmark suite [74] and collected the memory system reference traces as the input of our simulator. The memory system traces were run through an in-house cache simulator to simplify and speed LLC cache organization development and evaluation.

For multi-core simulation, we use the M5 architecture simulator [5] to generate the simulation results and evaluate our modified cache replacement policies and cache organization. We chose PARSEC 2.1 benchmark suite [21, 4] as workloads which contains a suite of multi-threaded, CMP oriented applications, thus is suitable for

the evaluation of a CMP machine.

For the partitioned-cache, we always ensure the way-complexity is equal with normal cache organization (i.e. partitioned-cache with 4-way, 4-part is compared with 16-way normal cache). Except where otherwise noted, in the following experiments we vary both the L2 cache's replacement policy (Protect-0, Protect-N) and cache organization (traditional cache, partitioned-cache). For simplicity, in all figures, P-0, P-4, P-1-4part represent our designs of Protect-0, Protect-4, Protect-1-4partition respectively. Our design only impacts the L2 cache, the LLC of the system, the L1 still uses the traditional LRU replacement algorithm and normal cache organization. Dirty cache blocks at the end of simulation are included in all the writeback counts.

## 2.3.2 Single-threaded simulation

In this section we present the results from a single-core, single-threaded evaluation of our proposed cache replacement policies and cache organization.

## 2.3.2.1 Lifetime

The effective lifetime of PCM is ultimately limited by the maximum number of writes to a given cell. In this section we evaluate the improvement in lifetime by examining the relative reduction in re-writes to the cell which has the maximum number of writes for each of our techniques versus LRU. We show the impact of our design on a memory system that employs randomized wear-leveling similar to that proposed in [71, 63, 52].

As we see in figure 2.5, our design provides a 49% gain (on average) over LRU when both applying on a randomized wear-leveling PCM system. This is because wear-leveling techniques can only distribute the writes to PCM more evenly, while the number of total writebacks can't be reduced at all. As our design effectively reduces writesbacks from LLC to PCM main memory, it's natural to achieve better

Figure 2.5: Lifetime improvement of SPEC2006 benchmarks on randomized wear-leveling PCM system

performance when combined with other wear-leveling techniques. Importantly, our design accomplishes the writeback reduction without the additional complexity of a DRAM cache in front of PCM.

#### 2.3.2.2 Energy consumption

Unlike previously proposed randomized wear-leveling techniques, our designs also reduce the energy consumption relative to conventional LRU cache. From Table 1.1, we see write-power is approximately 10x read-power and the write-latency is approximately 6x read-latency for PCM devices. We calculate the energy consumption using the formula: Energy = Misses\*R\_power\*R\_latency + Writebacks\*W\_power\*W\_latency. As our design can effectively reduce write traffic to PCM, we expect them to reduce energy consumption as well. Figure 2.6 shows the normalized energy consumption of our designs against LRU baseline cache. On average, our Protect-0, Protect-4 and Protect-1-4partition reduce the energy consumption by 19.2%, 16.3% and 21% respectively.

Figure 2.6: Normalized energy consumption for SPEC2006 benchmarks.

## 2.3.2.3 Write traffic

In this section, we explore how our design achieves improvement on lifetime and energy of PCM memory system. Figure 2.7 shows the impact on writebacks of the LLC cache when applying Protect-0, Protect-4 and Protect-1-4part versus traditional LRU cache for all the benchmarks. In Figure 2.7, we see all designs significantly reduce the write traffic to PCM-based main memory. Our design greatly reduces the total number of writes performed on the PCM device, so that its lifetime is improved effectively.

Generally, Protect-1-4 partition performs better than Protect-4 and slightly worse

than Protect-0. It is, however, interesting to note that in several instances, for example h264ref, Protect-1-4partition actually outperforms Protect-0. In these cases Protect-1-4partition is adaptively retaining critical dirty blocks longer than even Protect-0 would allow.

Figure 2.7: Normalized last-level cache writebacks for SPEC2006 benchmarks.

## 2.3.2.4 Misses

Figure 2.8 shows the corresponding miss impact of our design against traditional LRU baseline. As expected, Protect-0 has the worst effect on misses. Generally, Protect-4 and Protect-1-4partition have a lower impact on misses than Protect-0, and the overall increase is quite small compared with conventional LRU. Therefore, Protect-4 and Protect-1-4partition effectively reduce the additional cost of increasing LLC's misses and achieve a good trade-off between reducing write traffic and preserving locality. Moreover, Protect-1-4partition generates the fewest misses, approaching

LRU. Generally, the partitioned-cache scheme outperforms the corresponding normal cache organization in terms of both writebacks and misses, which demonstrates the benefit of partitioned-cache organization.

Figure 2.8: Normalized last-level cache misses for SPEC2006 benchmarks.

#### 2.3.3 Multi-threaded simulation

In this section we examine the impact of our proposed cache replacement policies and cache organization on multi-threaded applications on multi-core processors.

Figure 2.9 and 2.10 show the lifetime and energy improvement for our proposed design relative to the baseline randomized wear-leveling system. We see our design also has impressive improvement on lifetime and energy for multi-threaded applications. These improvement come from efficient writeback reduction while at the same time keeping misses comparable to the tradition LRU. Figure 2.11 and 2.12

show the corresponding writeback and misses performance under our design relative to LRU for PARSEC benchmarks. We can see that our design reduces the writeback by 40% while only increases misses by less than 1%. Energy consumption is also reduced greatly because of much less expensive-write performed. Generally, our cache replacement policies and cache organization have similar performance on multi-threaded applications as that of single-threaded ones, both improve lifetime and energy of PCM effectively.

Figure 2.9: Lifetime improvement of PARSEC benchmarks on randomized wear-leveling PCM system

#### 2.4 Analysis

In this section, we analyze the performance of the proposed cache design with respect to wear leveling. We also provide some intuition behind what makes the

Figure 2.10: Normalized energy consumption for PARSEC benchmarks.

Figure 2.11: Normalized last-level cache writebacks for PARSEC benchmarks.

Figure 2.12: Normalized last-level cache misses for PARSEC benchmarks.

partitioned-cache work.

# 2.4.1 Wear leveling

Wear-leveling is very important for PCM-based main memory, if writes occur more frequently on certain PCM cells the write endurance of those cells is soon hit, potentially leading to the breakdown of the device as a whole. Therefore, a uniform write distribution can effectively prolong the overall life time of a PCM device. To further explore our design's effect on wear-leveling, we apply our design and LRU on a baseline PCM system (without wear-leveling). Figure 2.13 shows a sorted cumulative distribution graph of main memory write addresses versus write counts for systems in which the LLC cache uses the LRU baseline, Protect-4, Protect-1-4partition on the *soplex* benchmark (other benchmarks have similar pattern). The two linear traces representing an ideal uniform write distribution for lru baseline and our technique respectively. In the figure the x-axis represents the written address tags, sorted according to the number of writes per tag, and the y-axis represents the number of total writes for each tag. As the figure shows, our designs produce a much lower and flatter distribution than the 16-way baseline LRU cache. Moreover, the uniform lines show that our design will perform much better than LRU baseline when combined with wear-leveling algorithms [71, 63, 52]. These results indicate not only do our designs produce fewer writes than baseline LRU cache on this workload, they also produce a much more uniform wear than LRU for its number of writes.

Figure 2.13: Write distribution of soplex

#### 2.4.2 Behavior of the partitioned-cache

To further analyze the behavior of the partitioned-cache, we examine the relationship between writeback rate and access traffic. For the sake of comparison with the partitioned-cache organization, we apply Protect-0 and Protect-1 both on a traditional 4-way cache, which is manually divided into four partitions according to the most two significant bits of the set index. As shown in Figure 2.14, the accesses are normalized to traditional LRU baseline, and the wbrate is the writeback rate. We observe that Protect-0-4way and Protect-1-4way have comparable accesses among all partitions, while Protect-1-4partition preserves a much higher access rate to the partition with lower writeback rate. Generally, the partitioned-cache holds on to the lines that have higher writeback rate by reducing the number of times they are replaced.

Figure 2.14: Accesses, writeback rate of each partition under hmmer application.

### 2.5 Related work

This section describes related work in PCM based memory systems, cache replacement policies and cache organization.

#### 2.5.1 Phase change memory based memory systems

Recently a handful of works have explored the design space of alternative main memory technologies. Li et al. and Dhiman et al. have investigated hybrid DRAM and PCM memory architectures [86, 18], while Sun et al. explored hybrid PCM and Solid State Disk (SSD) storage architectures [77]. In both cases, the authors sought to use one technology to provide buffers for frequently written data, offsetting some of the penalties of the other technology. These works are largely orthogonal and possibly complementary to the work presented here, as we focus upon reducing writebacks from the lower levels in the memory system.

Qureshi et al. propose two techniques called write cancellation and write pausing for improving the read performance of PCM memories [61]. These techniques give preference to reads at PCM and help mitigate the long write times in order to improve read performance. Separately, Qureshi et al. propose sub-block cache writebacks to reduce the writeback volume to PCM [65]. This work has a similar motivation as our work here, but proposes a different solution. While their work incorporates sub-block level dirty bits and only writes dirty words to PCM instead of full cache blocks, our work modifies the cache replacement policy to reduce the number of writebacks.

Lee et al. propose three techniques to improve PCM lifetime [45, 46]. These include elimination of redundant bit writes, row shifting, and segment swapping, all of which are aimed at either reducing the number of writes or leveling wear across the arrays. These techniques should be complimentary with the work presented here, although the benefit of combining them will not be strictly additive as our technique also will level wear somewhat across the arrays.

#### 2.5.2 Cache replacement policies

Cache replacement policies have been studied extensively since caches came into wide use in the early 1980's [28, 27, 35, 2, 47]. These works focused primarily upon achieving the fewest misses, as cache miss rate has the most direct effect on processor performance. These works largely disregard the effect of writebacks on the DRAM because, from the processor's point of view, writebacks occur in the background and do not directly affect miss latency. Furthermore, in DRAM technology, writes are not much more expensive than reads so there was less need to favor them.

In a seminal paper introducing the "Snoopy" cache coherence protocol, Goodman discussed the impact of writebacks on memory system bandwidth [23]. This work focused on shared memory induced writebacks and write-through caches. Mattson's stack algorithm is a useful tool to study associativity and replacement algorithms in caches [22]. Several recent works use Mattson's stack algorithm to improve cache utilization [9], sharing between processors [64, 37], or to improve DRAM utilization [75].

Clean First LRU (CFLRU) policy was proposed for page cache management in solid-state disks (SSDs) for similar reasons of reducing expensive writes to SSDs [58]. While the page replacement policies they propose have some similarities with our *Protect-N* policy, our focus here is on appropriate last-level, on-die cache, block replacement policies for PCM main memory. As such our proposed policies must be hardware implementable with low latency overheads and limited logical complexity.

# 2.5.3 Cache organization

Cache organization has also been extensively studied. Seznec proposed skew associative caches employing different hash functions enabling different sets to map to different parts (or partitions) of the cache [72, 6]. Powell et al. examined techniques to adaptively change the associativity and parallel search requirements of highly associative caches to reduce power and energy in the cache [60]. The set balancing cache allowed the associativity of a set in the cache to double based on observed miss behavior of that set [68]. A miss saturation counter is used to guide the expansion of a set into another location in the cache and these locations are serially searched to find a data item. The V-way cache employed a larger number of tag entries (compared to data entries) to allow variable associativity per set [62]. These alternative cache organizations were motivated by an aim of maintaining uniform accesses across the different sets or ways of the cache to approximate higher associativity and fewer misses. We propose an organization of the cache that intentionally skews the traffic (makes it less uniformly spread across the sets) to reduce the writebacks from the last level cache.

# 3. NVMFS: A HYBRID FILE SYSTEM FOR IMPROVING RANDOM WRITE IN NAND-FLASH SSD\*

In this chapter, we propose a hybrid storage system employing non-volatile DIMMs and solid state disks. The hybrid storage system is managed by our file system, NVMFS, which leverages both devices' advantages and compensates their disadvantages. Our design utilizes non-volatile DIMMs to absorb small random write requests and optimizes the write operations on flash SSD. We show that such a hybrid storage system can improve write throughput and garbage collection efficiency of SSD.

#### 3.1 Background

For many years, the performance of persistent storage (such as hard disk drives) has remained far behind that of microprocessors. Although the disk density has improved from GBs to TBs, data access latency has increased by only 9X [17, 16]. Compared with HDDs, SSDs have several benefits. An SSD is a purely electronic device with no mechanical parts, and thus can provide lower access latencies, lower power consumption, lack of noise and shock resistance. However, SSDs also have two serious problems: limited lifetime and relatively poor random write performance. In SSDs, the smallest write unit is one page (such as 4KB) and can only be performed out-of-place, since data blocks have to be erased before new data can be written. Random writes can cause internal fragmentation of SSDs and thus lead to higher frequency of expensive erase operations [11, 7]. Besides performance degradation, the lifetime of SSDs can also be dramatically reduced by random writes.

Flash memory is now being used in other contexts, for example in designing

<sup>\*</sup>Reprinted with permission from "NVMFS: A hybrid file system for improving random write in NAND-flash SSD" by Sheng Qiu and A.L.Narasimha Reddy, 2013. IEEE 29th Symposium on Mass Storage Systems and Technologies (MSST), Copyright 2013 by IEEE

Figure 3.1: Non-volatile DIMMs.

nonvolatile DIMMs [1, 79] as shown in Figure 3.1. These designs combine traditional DRAM, Flash, an intelligent system controller, and an ultracapacitor power source to provide a highly reliable memory subsystem that runs with the latency and endurance of the fastest DRAM, while also having the persistence of Flash (data on DRAM will be automatically backed up to flash memory on power failure). The availability of these nonvolatile DIMMs can simplify and enhance file system design, a topic we explore in this chapter.

In this chapter, we consider a storage system consisting of Nonvolatile DIMMs (as NVRAM) and SSDs. We expect a combination of NVRAM and SSD will provide the higher performance of NVRAM while providing the higher capacity of SSD in one system. We propose a file system NVMFS for such a system that employs both NVRAM and SSD. Our file system exploits the unique characteristics of these devices to simplify and speed up file system operations.

Traditionally, when devices of different performance are used together in a system, two techniques are employed for managing space across the devices. When caching is employed, the higher performance device improves performance transparently to the layers above, with data movement across the devices taken care of at lower layers. When migration is alternately employed, the space of both slower and faster devices becomes visible to the higher layers. Both have their advantages and disadvantages. In our file system proposed here, we employ both caching and migration at the same time to improve file system operations. When data is migrated, the address of the data is typically updated to reflect the new location whereas in caching, the permanent location of the data remains the same, while the data resides in higher performance memory. For example, in current file systems, when data is brought into the page cache, the permanent location of the file data remains on the disk even though access and updates may be satisfied in the page cache. Data eventually has to be moved to its permanent location, in caching systems. In systems that employ migration, data location is typically updated as data moves from one location to another location to reflect its current location. When clean data needs to be moved to slower devices, data cannot be simply discarded as in caching systems (since data always resides in the slower devices in caching systems), but has to be copied to the slower devices and the metadata has to be updated to reflect the new location of the data. Otherwise, capacity of the devices together cannot be reported to the higher layers as the capacity of the system.

In our system, we employ both these techniques simultaneously, exploiting the nonvolatile nature of the NVRAM to effectively reduce many operations that would be otherwise necessary. We use the higher performance NVRAM as both a cache and permanent space for data. Hot data and metadata can permanently reside in the NVRAM while not-so-hot, but recently accessed data can be cached in the NVRAM at the same time. This flexibility allows us to eliminate many data operations that would be needed in systems that employ either technique alone.

When data is accessed from SSD, initially that data is cached in the NVRAM, and the file system retains pointers to both locations. If this data becomes a candidate for eviction from NVRAM and it hasn't been updated since it is brought into NVRAM, we discard the data from NVRAM and update the metadata to reflect the fact that data resides now only on the SSD. If the data gets updated after it is brought into NVRAM, we update the metadata to reflect that the data location is the NVRAM and the data on the SSD is no longer valid. Since NVRAM is nonvolatile, we can retain the data in NVRAM much longer and get forced to flush or write this data back to SSD to protect against failures. This allows us to group the dirty data together and write the dirty data together to SSD at a convenient time. Second, this allows us to group data with similar hot-cold behavior into one block while moving it to SSD. We expect this will improve the garbage collection process at SSD in the longer term.

In order to allow this flexibility that we described above, where data can be cached or permanently stored on the NVRAM, we employ two potential addresses for a data block in our file system. The details of this will be described later in section 3.2.

The primary contributions of our design are as following:

- We proposes a new file system NVMFS, which integrates Nonvolatile DIMMs (as NVRAM) and a commercial SSD as the storage infrastructure.

- NVMFS exploits the strengths of NVRAM and SSD to improve file system performance. In our design, we utilize SSD's larger capacity to hold the majority of file data while absorbing random writes on NVRAM. We explore different write policies on NVRAM and SSD: in-place updates on NVRAM and non-overwrite on SSD. As a result, random writes at file system level are transformed to sequential ones at device level when completed on SSD.

- NVMFS distributes metadata and relatively hot file data on NVRAM while storing other file data on SSD. Unlike normal caching or migration scheme, our design can permanently store hot data on NVRAM while also temporar-

ily caching the recently accessed data. To track the hotness of file data, we implement two LRU lists for dirty and clean file data respectively. Our file system will dynamically adapt the number of pages distributed between dirty and clean LRU lists. When the dirty file data are not hot enough we will collectively flush them (grouped into SSD blocks) to SSD and put them to the end of clean LRU list which may be quickly replaced whenever the space of NVRAM is not enough (we always replace LRU clean pages).

- We show that NVMFS improves IO throughput by an average of 98.9% when segment cleaning is not active, while improving IO throughput by an average of 19.6% when segment cleaning is activated, compared to several existing file systems.

- We also show that the erase operations and erase overhead at SSD are both effectively reduced.

### 3.2 Design and implementation

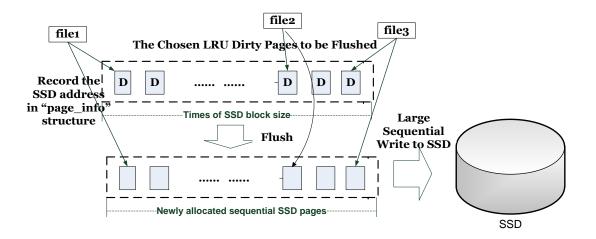

NVMFS improves SSD's random write performance by absorbing small random IOs on NVRAM and only performing large sequential writes on SSD. To reduce the overhead of SSD's erase operations, NVMFS groups data with similar update likelihood into the same SSD blocks. The benefits of our design resides on three aspects: (1)reduce write traffic to SSD; (2)transform random writes at file system level to sequential ones at SSD level; (3)group data with similar update likelihood into the same SSD blocks.

# 3.2.1 Hybrid storage architecture

In NVMFS, the memory system is composed of two parts, one is the traditional DRAM, the other is the Nonvolatile DIMMs. Figure 3.2 shows the hardware archi-

Figure 3.2: Hybrid storage architecture

tecture of our system. We utilize Nonvolatile DIMMs attached to the memory bus, and accessed through virtual addresses as NVRAM. The actual physical addresses to access NVRAM are available through the page mapping table, leveraging the operating system infrastructure. All the page mapping information of NVRAM will be stored on a fixed part of NVRAM. We will detail this later in section 3.2.2. If the requested file data is on NVRAM, we can directly access it through load/store instructions. While if the requested file data is on SSD, we need to first fetch it to NVRAM. It's noted that we bypass page cache in our file system, since CPU can directly access NVRAM which can provide the same performance as DRAM based page cache. To access the file data on SSD, we use logical block addresses (LBAs), which will be translated to the physical block addresses (PBAs) through FTL component of SSD. Therefore, NVMFS has two types of data addresses at file system level – virtual addresses for NVRAM and logical block addresses for SSD. In our design, we can store two valid versions for hot data on NVRAM and SSD respectively. Whenever the data become dirty, we keep the recent data on NVRAM and invalidate the corresponding version on SSD. We will introduce how we manage the data addresses of our file system in section 3.2.2.

The benefit of building such a hybrid storage is that we can exploit each device's advantages while offsetting their disadvantages. Since SSD has poor random write performance and limited write cycles, we absorb random writes on NVRAM and only perform large sequential writes on SSD. For metadata and frequently accessed file data, we permanently store them on NVRAM, while distributing other relatively cold, clean data on SSD. We will detail how NVMFS distributes the file data between NVRAM and SSD in section 3.2.3.

# 3.2.2 File system layout

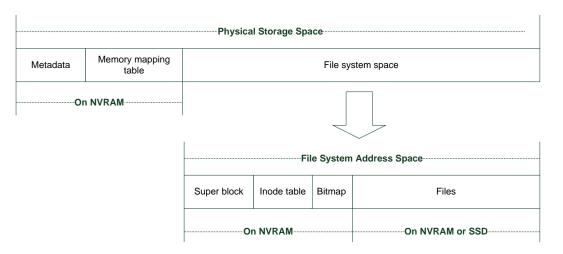

The space layout of NVMFS is shown in figure 3.3. The metadata and memory mapping table are stored on NVRAM. The metadata contains the information such as size of NVRAM and SSD, size of page mapping table, etc. The memory mapping table is used to build some in-memory data structures when mounting our file system and is maintained by memory management module during runtime. All the updates to the memory mapping table will be flushed immediately to NVRAM.

Figure 3.3: Storage space layout

In NVMFS, the directory files are stored as ordinary files, while their contents are lists of inode numbers. To address the inode table, we store the pointer to the starting address of the inode table in the super block. Within the inode table, we use a fixed size entry of 128 bytes for each inode, and it is simple to get a file's metadata through its inode number and the start address of the inode table. The inode will store several pieces of information including checksum, owner uid, group id, file mode, blocks count of NVRAM, blocks count of SSD, size of data in bytes, access time, block pointer array and so on. The block pointer array is similar as the direct/indirect block pointers used in EXT2. The difference is that we always allocate indirect blocks on NVRAM so that it is fast to index the requested file data even when the file is large which requires retrieving indirect blocks. The block address is 64 bits and the NVRAM addresses are distinct from the SSD block addresses. To build our file system, we can use the command like "mount -t NVMFS -o init=4G /dev/sdb1 /mnt/NVMFS". In the example, we attached 4GB Nonvolatile DIMMs as the NVRAM, and inform NVMFS the path of the SSD device, finally mount it to the specified mount point.

#### 3.2.3 Data distribution and write reorganization

The key design of NVMFS relies on two aspects: (a)how to distribute file system data between the two types of devices – NVRAM and SSD; (b)how to group and reorganize data before writing to SSD so that we can always perform large sequential writes on SSD.

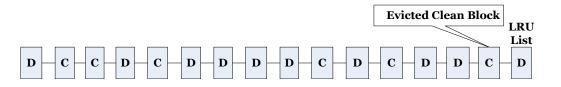

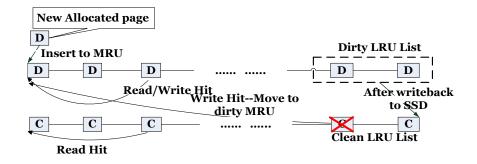

File system metadata are small and will be updated frequently, thus it's natural to store them on NVRAM. To efficiently distribute file data, we track the hotness of both clean and dirty file data. We implemented two LRU (Least Recently Used) lists dirty and clean LRU lists, which are stored as metadata on NVRAM. Considering the expensive write operations of SSD, we prefer to store more dirty data on NVRAM, expecting them to absorb more update/write operations. Whenever the space of NVRAM is not sufficient, we replace file data from clean LRU list. However, we also do not want to hurt the locality of clean data. We balance this by dynamically adjusting the length of dirty and clean LRU lists. For example, if the hit ratio of clean data is 2X more than that of dirty data, we increase the NVRAM pages that are allocated for clean data. In other words, we increase the length of clean LRU list. To achieve this, we maintain two performance counters which keep track of the hits on clean and dirty data (on NVRAM) respectively. We periodically measure and reset the counters. The total number of pages within clean and dirty LRU lists is fixed, equalling to the number of NVRAM pages.

Figure 3.4: Dirty and clean LRU lists

Figure 3.4 shows the clean and dirty LRU lists as well as the related operations. When writing new file data, we allocate space on NVRAM and mark them as dirty, then insert to the MRU (Most Recently Used) position of dirty LRU list. Read/write operations on dirty data will update their position to MRU within dirty LRU list. For clean data, read operations update their position to MRU of clean LRU list, while write operations are a little different since the related data become dirty afterward. As shown in figure 3.4, writes on clean data will migrate the corresponding NVRAM pages from clean LRU list to the MRU of dirty LRU list.