# INTERNSHIP EXPERIENCE AT TEXAS INSTRUMENTS

The Internship Report

bу

KERRY CLOYCE GLOVER

Submitted to the College of Engineering of Texas A&M University in partial fulfillment for the degree of

DOCTOR OF ENGINEERING

May 1982

Major Subject: Electrical Engineering

## INTERNSHIP EXPERIENCE AT TEXAS INSTRUMENTS

The Internship Report

bу

KERRY CLOYCE GLOVER

Approved as to style and content by:

Dr. V. T. Rhyne (Chairman of Committee)

Dr. W. B. Jones (Head of Department)

Noel R Strader

Dr. N. R. Strader

(Committee Member)

Dr. T. A. Parish

(D.E. College Rep.)

Dr. C. A. Rodenberger (Committee Member)

Dr. W. C. Griswold (D.E. Coordinator)

Dr. R. Ohlendorf

(Internship Supervisor)

Dr. J. R. Boone (Graduate College Rep.)

#### ABSTRACT

Internship Experience with Texas Instruments

Kerry Cloyce Glover, B.S., Texas A&M University

M.S., Texas A&M University

Chairman of Advisory Committee: Dr. V.T. Rhyne

survey of the author's This report presents a experience with Texas Instruments internship November 1980 to November 1981. The internship was spent in the Advanced Research and Development Division οf Digital Systems Group. The report's intent is this experience fulfills tο demonstrate that requirements of the Doctor of Engineering internship.

author's internship activities involved the design of a special purpose processor. The internship divided into two parts during which different was versions of the processor were developed. The design was of a slow processor which was to be simple to build and debug. The second design was performance, and therefore complex, processor. of expertise were gained during the internship areas including simulation, caching techniques developed pipelining. Communication skills were because of the interaction with software designers.

## TABLE OF CONTENTS

| D | Δ | C  | ਸ਼ |

|---|---|----|----|

| r | _ | 17 | C  |

| INTERNSHIP REPORT1                  |

|-------------------------------------|

| Introduction1                       |

| PROJECT OVERVIEW4                   |

| GENERAL PURPOSE PROCESSOR16         |

| Software Defined Architecture16     |

| Architectural Implications20        |

| Processor Evolution23               |

| Microcode27                         |

| ALL Field29                         |

| Specialized Fields31                |

| Detailed Design34                   |

| Arithmetic and Logical Unit (ALU)34 |

| Large Register File (LRF)           |

| Sequencer (SEQ)41                   |

| Testability and Debug Features43    |

| Simulation                          |

| BASIC Simulation47                  |

| HDL Simulation50                    |

| Communications53                    |

| Change in Direction                 |

| FAST PR     | OCESS     | OR.     | • • • • | • • • •           | • • • • | • • •   | • • • • | • • • • • | • • • • •   | • • • • • 56 | 1 |

|-------------|-----------|---------|---------|-------------------|---------|---------|---------|-----------|-------------|--------------|---|

| 0ъј         | ectiv     | es.     |         | • • • •           |         | • • •   | • • • • | • • • • • | • • • • •   | 56           | 1 |

| Con         | venti     | onal    | Cac     | ching             | g Me    | tho     | ds      | • • • • • | • • • • •   | • • • • • 57 |   |

| Cac         | he Ev     | olut    | ion.    | • • • •           |         | • • •   | • • • • | • • • • • | • • • • •   | 61           |   |

| Pip         | eline     | Evo     | luti    | ion.              | • • •   | • • •   | • • • • | • • • • • |             | 65           |   |

| Per         | forma     | nce     | Impi    | cover             | nent    | S       | • • • • | • • • • • | • • • • •   | 68           |   |

| Det         | ailed     | Des     | ign.    | • • • •           | • • •   | • • •   | • • • • | • • • • • | • • • • •   | 72           |   |

| •           | Fif       | o Bu    | ıffer   |                   | •••     | • • •   | • • • • | • • • • • | • • • • •   | 73           |   |

|             | 0 p e     | rand    | l Spe   | ecifi             | ler     | Dec     | der.    | • • • • • | • • • • • • | 76           |   |

|             | Add       | ress    | Dev     | relo <sub>l</sub> | er.     | • • • • | • • • • |           |             | 80           | l |

|             | End       | of      | the     | Pipe              | · • •   | • • •   | • • • • | • • • • • | • • • • •   | 81           |   |

| Sim         | ulati     | on      | • • • • | • • • •           |         | • • • • | • • • • | • • • • • |             | 86           |   |

| Pro         | ject      | Term    | inat    | ion               |         | • • •   | • • • • | • • • • • |             | 89           |   |

| SUMMARY     | • • • • • | • • • • | • • • • | • • • •           | • • •   | • • • • | • • • • | • • • • • | • • • • •   | ••••91       |   |

| BIBLIOG     | RAPHY     | •••     | • • • • | • • • •           |         | • • • • | • • • • | • • • • • |             | ••••95       |   |

| APPENDI     | CES       | • • • • | • • • • | • • • •           | • • •   | • • • • |         | • • • • • | • • • • •   | 96           |   |

| <b>ΥΤΤΔ</b> |           |         |         |                   |         |         |         |           |             | 161          |   |

•

.

### LIST OF FIGURES

| FIGURES | PAGE |

|---------|------|

|---------|------|

| 1   | Hardware Speed-Cost Curve               |

|-----|-----------------------------------------|

| 2   | System Configuration4                   |

| 3 A | Long Narrow/Slow Machine6               |

| 3 B | Short Wide/Fast Machine6                |

| 4   | Project Schedule                        |

| 5   | Microcode Processor W/Test Features8    |

| 6   | Debug Configuration9                    |

| 7   | HDL Block Orientation11                 |

| 8   | Slow Processor Block Diagram            |

| 9   | Fast Processor Block Diagram            |

| 10  | Software/Hardware Interface             |

| 11  | Software/Hardware Cost Vs Time Curve18  |

| 12  | Instruction Stream                      |

| 13  | Hardware Implemented Operating System22 |

| 1 4 | Von Neumann Architecture23              |

| 15  | Combined Address/Data Buss24            |

| 16  | Slow Processor Block Diagram26          |

| 17  | Microcode Word Bit Field29              |

| 18  | Arithmetic and Logical Unit35           |

| 19  | Byte Rotater/Selector37                 |

| 20  | Large Register File40                   |

FIGURE

| 2 1 | Sequencer42                    |

|-----|--------------------------------|

| 2 2 | Test and Debug Data Paths44    |

| 23  | Sample Screen Display48        |

| 2 4 | Hardware Speed-Cost Curve56    |

| 25  | Workspace Cache58              |

| 26  | Content Addressable Memory59   |

| 27  | Associative Cache60            |

| 28  | Cache Evolution I              |

| 29  | Cache Evolution II62           |

| 30  | Cache Evolution III63          |

| 31  | Final Cache Configuration64    |

| 32  | Address Translation65          |

| 33  | Pipeline67                     |

| 3 4 | Pipeline Improvements/Calls70  |

| 35  | Pipeline Improvements/Jumps72  |

| 36  | FIFO73                         |

| 37  | Address Decoder76              |

| 38  | Displacement Length Decoding79 |

| 39  | Address Developer80            |

| 40  | Fast ALU82                     |

| 41  | Memory Data Paths84            |

| 42  | Processor Block Diagram        |

PAGE

### LIST OF APPEDICES

APPENDIX

L

M

| A | The Internship Objectives97      |

|---|----------------------------------|

| В | Definition of Microcode          |

| С | Sample Microcode Routine114      |

| D | Processor/Sequencer Interface118 |

| E | Debug Interface Signals          |

| F | Software Debug Routines125       |

| G | PASCAL Emulator127               |

| Н | HDL Simulation of MEM141         |

| J | Cache Placement Study149         |

| K | Pipeline Data Flow Study         |

#### INTERNSHIP REPORT

#### Introduction

Working on a team effort to design and develop a new computer system is an exciting and challenging opportunity. Such has been my intern experience with Texas Instruments for the past year. My assignment was to design the Central Processing Unit (CPU) of an experimental computer system. This required close work with the research group which was defining the architecture. The successful implemention of the system would require a full understanding of computer hardware, software and system architecture.

The initial objectives of the project are listed in Appendix A. Since this list of objectives was submitted, many things have changed on the project. Many of the objectives were not attainable, however, additional goals were achieved.

Throughout the internship project, the major goal has been to design a processor. During that time, performance requirements for the processor have been changed. The first processor was a low-end implementation of the architecture. This had several

attributes as discussed in the objectives. These were to develop rapidly a machine which had built-in debug and test features, allowing it to be easily microcoded. The goals changed half-way through the project. The new goal was to develop a high performance/high speed version of the processor.

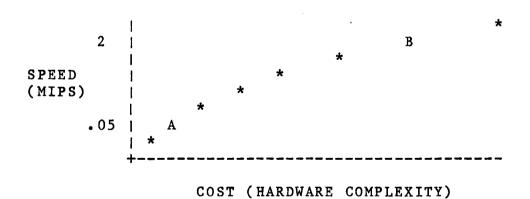

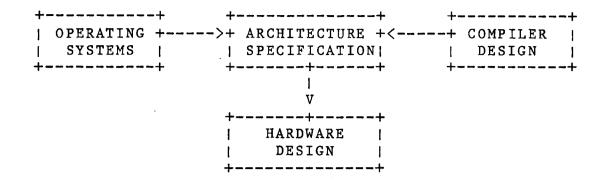

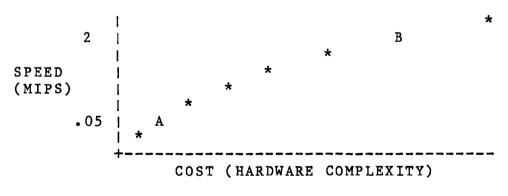

The two versions of the processor were οf two speed/performance ranges. A relationship exists between hardware complexity and speed. This project started at one point on that curve (A) and latter was redirected to another point on that curve (B). the speed of the processor increased the complexity also increased.

FIGURE 1 - HARDWARE SPEED-COST CURVE

This report will be divided into three sections. The first section will be a short overview of the entire project. This is a condensed form of the report which will familiarize the reader with the project and the various areas which were investigated. The second section will discuss a slow machine. It explains details about the data paths, microcode, and debug features which were designed. The third section will describe several aspects of high performance design of computers and how it applies to this project in developing a fast machine.

#### PROJECT OVERVIEW

The first several months on the project were spent studying a research oriented computer architecture. This architecture required that several tasks traditionally done in software to be implemented in hardware. Understanding and envisioning an implementation for this experimental machine proved to be a learning experience.

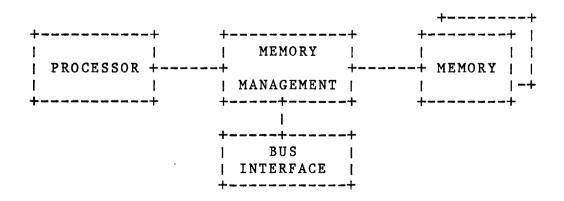

The project had been divided into several different hardware implementation areas. These were the processor, memory management and bus interface. The processor section was developed during the internship. The processor interfaced directly to the memory manager which then interfaced to other parts of the system.

FIGURE 2 - SYSTEM CONFIGURATION

The first step in the design of the machine was to define the data paths. This involved the study of flow inside of the machine data would manipulated to perform the functions needed. Severa1 implementing the architecture methods of envisioned and each new revision allowed different functions to bе implemented at various speeds and efficiencies.

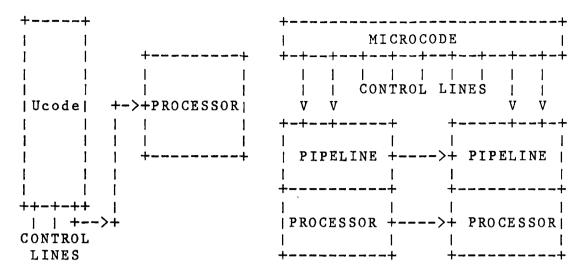

first The architecture was very basic а Neumann architecture with separate address and data This proved to be very inefficient and design went through several variations. found that the hardware needed to implement version of the architecture would take a long time to hard to microcode (Ucode) design and would be debug. The final implementation decision was between a slow vertically microcoded machine and a horizontal fast machine. Figure 3A shows a rough representation the vertical slow machine and Figure 3B shows the horizontal fast machine.

LONG NARROW/SLOW MACHINE SHORT WIDE/FAST MACHINE

FIGURE 3A FIGURE 3B

It was decided that a general purpose breadboard needed. The major reason for the general purpose aspect was the variability of the design. The architecture was changing as various aspects of the system were developed. Therefore the breadboard was to be very flexible, easily changed, and quickly implemented. Data collection was also important in determining how to increase the performance. requirements resulted in the selection of the slow vertically microcoded machine to be implemented (Figure 3A).

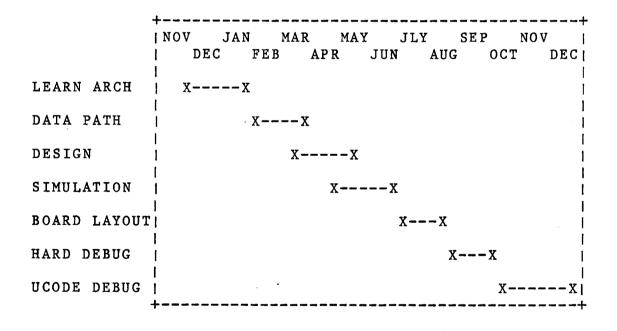

project schedule was made to reflect the different phases of the design and to estimate the amount of time each phase would require. These steps included studying and understanding the architecture, defining the data paths, doing the detailed design, the simulation, board layout, hardware and microcode debug. The schedule from initial design to implementation would require approximately one year to complete. This is how the initial schedule appeared at the beginning of the project.

FIGURE 4 - PROJECT SCHEDULE

TIME

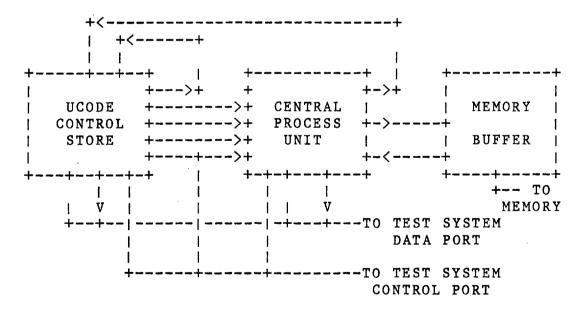

The requirement for a general purpose machine led to the decision that no special purpose hardware would be added to speed the processor. This would allow a prototype to be available very rapidly. Proper data paths were needed to implement the architecture around a standard bit-slice CPU. A vertically microcoded machine would reduce the hardware needed, make the machine easier and quicker to implement and debug, make the microcode easier to write, and allow the microcode to control the collection of data. Figure 5 shows the initial view of how the processor would be organized, controlled and tested.

FIGURE 5 - MICROCODE PROCESSOR W/TEST FEATURES

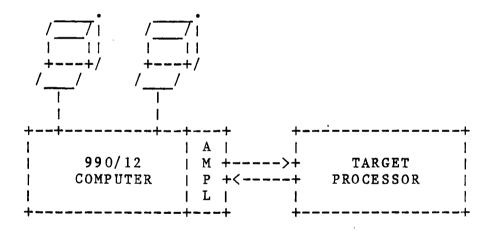

One important point stressed at this time was ease in debugging and microcoding. If not done correctly, microcode software development could be very difficult and time consuming. Therefore an elaborate interface with a debugging system was made. This required that the data paths allow proper tracing of information and downloading of data into the writable microcode store (Figure 5). Several I/O modules and AMPL trace modules in a 990 system were to be used to down-load microcode and trace its execution (Figure 6).

FIGURE 6 - DEBUG CONFIGURATION

detailed design was built on top of the data paths. In traditional system design, schematics would drawn from which data bases would be created for computerized layout of PC or wirewrap boards. design was to be fully simulated in software using a Description Language (HDL) Hardware internally Simulation is radically different available in TI. from traditional schematic drawing. The hardware described in a special computer language where each signal is described as a variable. These variables are programmed to change in the same manner as the hardware signals would change.

One simulation consisted of a register-to-register transfer program written in BASIC to simulate flow of data along the data paths. This was used to exercise the machine to insure the data paths were adequate. It would also be used as a debug tool by microcode writers before an actual machine was available. After this, the detailed design was simulated using HDL.

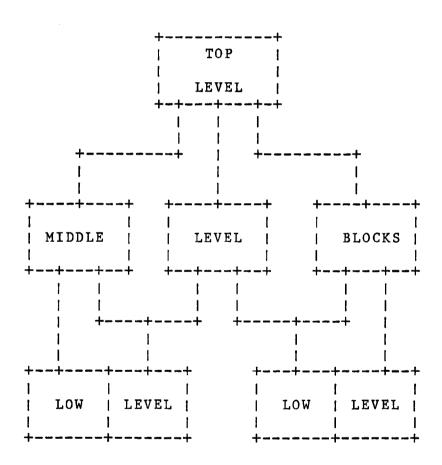

HDL hardware simulation is written in "blocks". The lowest levels of design represent the lowest levels of hardware. These low levels are then put together to form higher level descriptions. This block orientation was very versatile and allowed rapid programming of many hardware functions which were linked together to form a high level description of the hardware.

FIGURE 7 - HDL BLOCK ORIENTATION

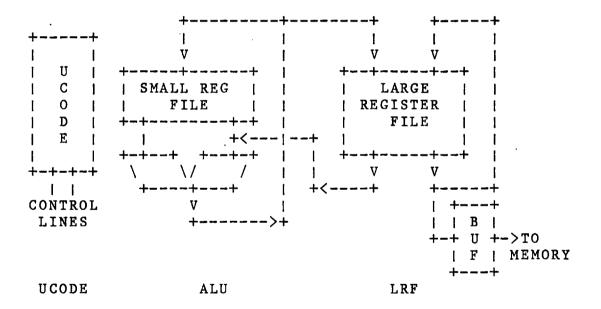

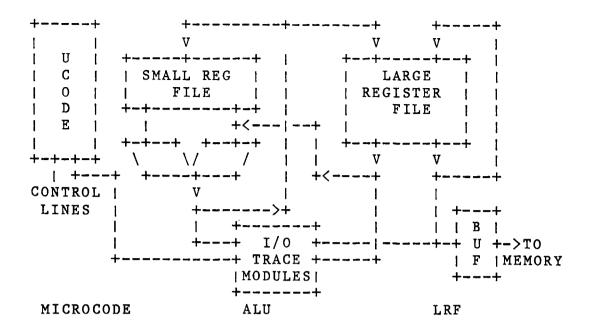

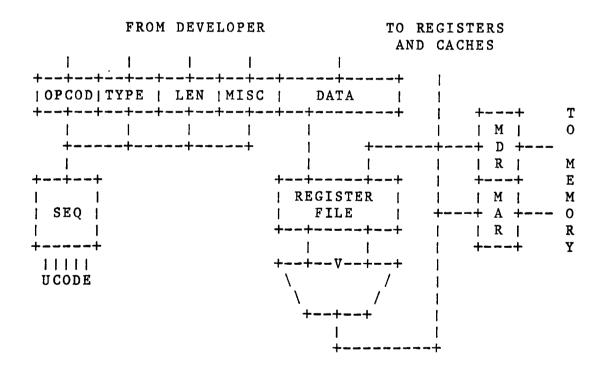

The actual processor contains three major parts; the Large Register File (LRF), the Arithmetic and Logical Unit (ALU), and the Sequencer (SEQ). The LRF contains a large number of registers used by the ALU and provides an interface with the memory mapper. The ALU is the workhorse of the processor and does all data manipulation. The SEQ controls the system. The microcode is stored in Writable Control Store (WCS) in this portion of the processor.

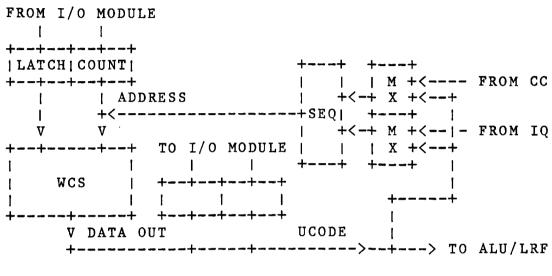

FIGURE 8 - SLOW PROCESSOR BLOCK DIAGRAM

The LRF and ALU were simulated separately using HDL. The design was first described in terms of low level blocks consisting of registers, counters and memory elements. These blocks were then linked together to form a high level representation of the design. The high level blocks of the ALU and LRF were then interconnected to form an overall simulation.

About halfway through the slow processor design, a decision was made to change the implementation to a high performance version. Since this was to Ъe experimental processor intended for a learning tool, it decided that the hardware implementation should be designed to learn as much as possible. The major necessary to investigate was performance. which was Therefore the second version would have its main emphasis on speed.

The new machine would be fast and utilize advanced techniques for improving performance. This included using various caches and pipelining the architecture. This added complexity would result in a longer design period.

Several types of caches were used in the machine. Workspace caches, Content Addressable Memory (CAM), and associative caches were all used in various places. These caches were mandatory to increase the performance to the levels needed.

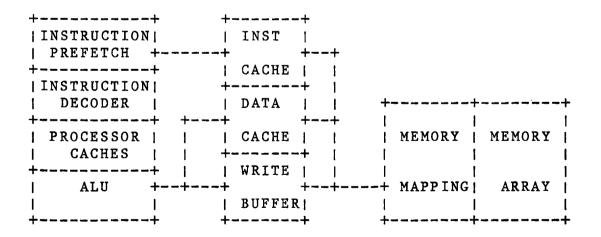

The fast machine was also pipelined. Five levels of pipelining were used to simplify and speed the machine.

- 1. Instruction Prefetch

- 2. Operand Specifier Decode

- 3. Register Prefetch and Address Development

- 4. Arithmetic and Logical Unit

- 5. Buffered Memory Write

| ++          | ++        | ++       | ++     |

|-------------|-----------|----------|--------|

| INSTRUCTION | INST      | 1 1      | 1 1    |

| PREFETCH +  | +ASSOC    | 1 1      | 1      |

| "FIFO"      | CACHE     | 1 1      | 1 1    |

| ++          | ++        | MEMORY   | MEMORY |

| OP SPEC     | DATA      | ++       | 1 1    |

| "DECODER"   | ++ASSOC + | +   CAM+ | +      |

| PROCESSOR & | CACHE     | ++       | ARRAY  |

| WS CACHE    | ++        | MAPPER   | 1 1    |

| ++          | WRITE!    | 1 1      | 1      |

| ALU +       | -++BUFFER | 1 1      | 1      |

| ++          | ++        | ++       | ++     |

FIGURE 9 - FAST PROCESSOR BLOCK DIAGRAM

The fast processor was simulated using a top down approach to HDL. Top down programming means the high level blocks are simulated before the low level ones. Blocks such as caches, levels of the pipeline or the ALU are simulated before low levels. These high levels are later broken down into registers, latches, counters, etc. Care was taken to reflect how the lower blocks of the design would be connected in the actual hardware.

The first block to be simulated was the First In First Out buffer (FIFO). This part was very straight forward to simulate since the major elements were registers. The "Decoder" was different from the FIFO since it consisted of Programmable Logic Arrays (PLAs) and Read Only Memorys (ROMs). A deliberate effort had to be made to insure the high level code represented the actual hardware. It would be very easy to build a system which could never be implemented.

The FIFO and Decoder were simulated before the internship's termination. Many things were learned and the overall experience was very educational.

# GENERAL PURPOSE PROCESSOR Software Defined Architecture

Upon arrival at the job site, I was introduced to the group and given a document describing the architecture to be implemented. Many advanced concepts were being implemented in hardware rather than software and it took some time to understand their benefit.

Architecture has been defined as what one sees when he looks at something. This could be a building or a computer. The architecture of the internal workings of a computer system depends upon what level is being addressed. The programmer looks at a computer from a different perspective than a hardware designer. There is a difficult task in designing hardware to match the view from the software perspective.

The architecture was based on requirements of both operating systems and programming languages. Data structures, memory management requirements, time sharing functions, and the instruction set were specified and the hardware designer's job was to use this information to develop a system that would reflect this structure.

FIGURE 10 - SOFTWARE/HARDWARE INTERFACE

The software designer and the hardware designer are similar to the artist and the builder. The artist sketch a grand building that looks beautiful. builder in turn must take the sketch and construct the artist does not fully understand building. Ιf building principles he could sketch an impossible design to construct; the same is true of computer design. The artist or software designer developing the architecture must understand the constraints builder hardware designer who will implement the or final structure.

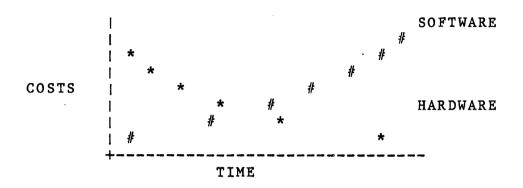

A major effort was being made in this architecture to put a large amount of the software complexity into the hardware. Software is becoming more expensive to develop while hardware is declining in cost. Therefore

it seems reasonable that one solution to the problem would be to increase the amount of hardware complexity in a manner which would reduce the software development cost.

FIGURE 11 - SOFTWARE/HARDWARE COST VS TIME CURVE

Changing the software/hardware boundary leads to the problem of cost/efficiency trade-offs. The typical software programmer has little feeling for the cost of the hardware and cannot make tradeoffs based upon that cost. Therefore it is necessary to identify the most costly aspects of the architecture and make sure that the appropriate tradeoffs is made.

Interfacing with software groups provides a very challenging opportunity to learn many new things. Understanding why a new feature is needed and at the same time analyzing the cost is very difficult. To

communicate the problems to the software designer introduces a distinct communications problem. This requires knowing most members of the group, knowing which person to talk to and approaching them at the right time. If you approach them on a part of the architecture they have designed, you must be careful and not criticize them while evaluating whether it is actually needed or not.

An example of a difficult instruction to argue against is the Reverse Bit instruction. This instruction would take the operand and reverse the most significant and least significant bits in a criss-cross pattern. This is very difficult to do in software yet only takes one data path in hardware. The cost of that hardware finite and it is questionable as to how is much the instruction will be used. It was decided that the architecture would support any needed software feature and therefore the instruction would be implemented.

### Architectural Implications

Many features of the architecture had various implications upon the hardware. These areas were investigated in more detail as different parts of the architecture were understood. The areas under investigation included the instruction opcodes, the operand specifiers, the processor data structures and memory management.

Conventional architectures have machine specific instructions which are a length. On e objective of this architecture was to frequency encode the instructions. The most often used instructions would take the smallest amount of room in the code stream. Less frequently used instructions would This accomplished by encoding more room. is instruction to be a variable number of bytes in length.

In the instruction, a distinct division is made between the operation code and the operand specifiers. The operation code is normally one byte long, but escape codes are allowed for expansion of the instruction set. The operand specifiers vary from one to seven bytes in length and there can be from one to

five operand specifiers per operation code. This provides two levels of frequency encoding; operation code and operand specifiers.

| OP CODE | OP SPEC | OP SPEC | . . ! OP SPEC | +-----+

FIGURE 12 - INSTRUCTION STREAM

The instruction fetch was not precise as in most machines. The instructions could be from one byte to many bytes in length depending on the addressing mode. This meant the whole instruction could not be fetched from memory at one time. Rather, blocks of code would be fetched and instructions decoded from these blocks.

operand specifiers were divided into various lengths and types. The type of operand specifier had to be checked with the opcode to insure that it was valid for that operation. The address of the operand specifier had to be developed from the information This given in the instruction. included the many addressing modes the processor had to support. this was done, the data was fetched from memory and stored into the processor. After all operand specifiers were fetched, the execution could begin.

There were other data structures in the architecture which the processor must understand. These were time-slicing, page faulting and complex message primitive instructions. The processor had to time-slice between many different tasks being run the machine. The processor also had to support a paging system and must handle page faults in the middle of an instruction. The processor also had to deal with very complex message primitive instructions. three things, page fault, time slicing and messages are the complex OS primitives being implemented in the hardware.

|             | * | * | *   | *   | * | * | *   | *   | *   | *   | *  | *  | *   | *   | *   | *          |

|-------------|---|---|-----|-----|---|---|-----|-----|-----|-----|----|----|-----|-----|-----|------------|

| HARDWARE    | * |   |     |     |   | * |     |     |     |     | *  |    |     |     |     | *          |

| OS          | * | ] | ?A( | GΕ  |   | * | •   | ri  | ΜE  |     | *  | MI | ESS | SAG | GES | 5 <b>*</b> |

|             | * | ] | A   | JL' | Γ | * | S   | LI  | CII | NG. | *  |    |     |     |     | *          |

|             | * | * | *   | *   | * | * | *   | *   | *   | *   | *  | *  | *   | *   | *   | *          |

| TRADITIONAL | * |   |     |     |   |   |     |     |     |     |    |    |     |     |     | *          |

| HARDWARE    | * |   |     |     |   | I | NS: | rRI | JC: | ri  | NC |    |     |     |     | *          |

|             | * |   |     |     |   |   |     | SI  | ΞΤ  |     |    |    |     |     |     | *          |

|             | * | * | *   | *   | * | * | *   | *   | *   | *   | *  | *  | *   | *   | *   | *          |

FIGURE 13 - HARDWARE IMPLEMENTED OPERATING SYSTEM

#### Processor Evolution

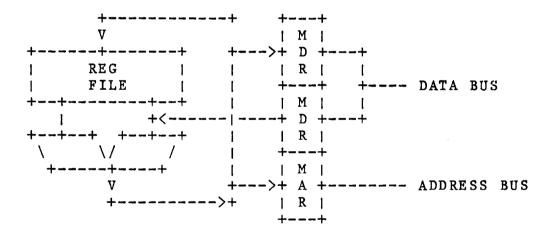

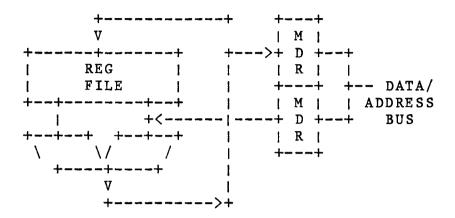

The initial design was a basic Von Neumann architecture with one data/instruction space and separate address and data lines. This was not effective because it was communicating with the memory management board and not with memory. The memory management board in turn manipulated the data in such a way that it could access actual memory and return a value to the processor.

FIGURE 14 - VON NEUMANN ARCHITECTURE

The next type of architecture had a combined data and address bus. This was efficient since the memory management board had to manipulate the address before he received the data. Other data paths were added to speed various operations such as a barrel byte shifter

to do byte manipulation easily. Even with these modifications the machine was very slow, yet it would still be easy to implement and debug.

FIGURE 15 - COMBINED ADDRESS/DATA BUS

Another severe problem was that the architecture was not firm. Specific speed improvements would be useless if the architecture changed underneath them. This particular implementation had to be flexible enough to be changed as the architecture changed. This proved to be the most difficult challenge and dictated that the functionality be in the microcode.

Because of the flexibility problem and the complexity of a fast machine, a slow microcoded machine was chosen to be implemented. This machine would have all obvious data paths but would not include complex

hardware to speed the execution. Rather than more hardware, there would be more microcode written. This would have the added benefit of hardware being available to the the software group sooner.

With so much functionality being put into microcode, it was imperative that the microcode be easily written. Past experience with microcoded machines shows that a large amount of time is spent writing and debugging the microcode. Therefore the machine must have the necessary support to help write, modify and debug the microcode.

Since the machine would be used extensively to develop the system software, there was a need to make the machine easily testable and maintainable. There should be no hidden data paths or registers that could not be directly tested. This design attitude would allow diagnostics to be written to support the machine during software checkout.

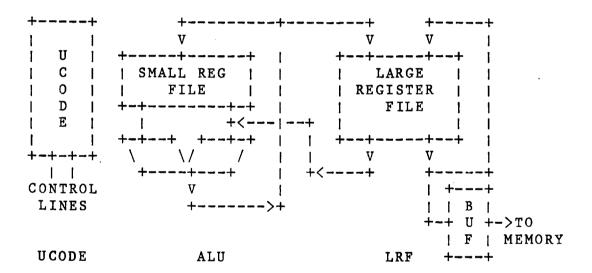

The data paths of the final machine provided a maximum of efficiency with a minimum of complexity. The final data paths were broken down into three parts. The microcode was the heart of the machine and in

absolute control of all parts of the processor. It must also be specially designed to interface with an external computer to allow downloading of the microcode. The second part was the Arithmetic and Logical Unit (ALU). This part was the workhorse of the processor and did all data manipulations. The last part was a Large Register File (LRF). This was a twoport file through which the processor and memory management communicated.

FIGURE 16 - SLOW PROCESSOR BLOCK DIAGRAM

#### Microcode

The microcode of the machine evolved as different functions were added or deleted. The first microcode control word allowed control of all fields in parallel. This word had several fields or distinct groups of bits. These fields are as follows:

- 1. Arithmetic and Logic Unit (ALU)

- 2. CONstant field low or high (CON)

- 3. SHift control (SHF)

- 4. Condition Code and Carry (CCC)

- 5. MEMory field (MEM)

- 6. Memory MAP request field (MAP)

- 7. SEQuencer field (SEQ)

This microcode word was very wide but contained many independent fields. Each field controlled a separate part of the hardware. This wide word could control every state of the machine during each microcode state.

The major problem with the wide microcode word was the size of the microcode control store memory. Additional hardware could be added to reduce the width but this would take some versatility out of the microcode. In most scenarios, not all fields in the microcode could be utilized during each machine state,

yet the functionality of the wide field and all the bits still needed to be controlled.

The best solution to the problem was to reduce the number of bits affected during each cycle. The microcode still controlled the full width, but only one section could be affected at a time. This would be done by loading only a portion of the wide microcode latch. Each of the eight sections of the wide microcode would still be controlled, one section at a time. Appendix B details the definition of the microcode.

The microcode was vertically oriented and narrow such that each machine cycle executed one microcode instruction. These instructions were very similar to assembly language instructions. Appendix C lists a sample add instruction. It can be seen from this example how similar this is to assembly language.

The microinstructions were assigned assembly language memonics such as INC, MOV, ADD and JMP. A microcode assembler was then used to translate this microcode into machine level ones and zeros. There were several people helping write the microcode. They

were familiar with assembly language and could begin programming microcode very easily.

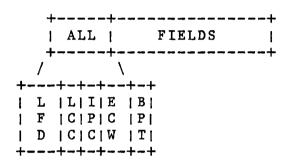

The 32-bit microcode field is subdivided into two sections, a eight bit field and 24-bit field. The eight bit "ALL" field is subdivided into five other control fields. The control field acts as a mode control for the other 24 bits.

FIGURE 17 - MICROCODE WORD BIT FIELD

## ALL Field

The first eight bits are referred to as the ALL field. The first subdivision of this field is into the Load FielD (LFD). The LFD is used to determine which portion of the machine the lower 24 bits will control. The other portions of this field controls signals

affected during all modes of operation. These are things such as Load Condition Code (LCC), Increment Program Counter (IPC), Enable Constant Word (ECW), and BreakPoinT (BPT).

The LFD field has three bits which mode select between eight different fields. The bit assignments are shown below:

- 001 LCON LOAD CON UCODE REG LOW OR HIGH

- 010 LSHF LOAD SHIFT/CONTROL

- 011 LCCC LOAD COND CODE AND CARRY

- 100 LALU LOAD ALU UCODE REG

- 101 LMEM LOAD MEM UCODE REG

- 110 LMAP LOAD MAP UCODE REG

- 111 LSEQ LOAD SEQ UCODE REG

These portions of the wide microcode field have been restructured in the vertical microcoded machine. The details of each will be discussed later.

The Load Condition Code (LCC) is used by several fields which have status inputs to the condition code register. The condition code register is wide enough to test the many status condition. The IPC field is used to advance the program counter at any time. The ECW is used to select a portion of the microcode from

the normal WCS or from a special constant register. This is needed if an internal address is calculated, then used by the microcode. The BPT was a bit used to signal external hardware that a breakpoint is to occur. This could be used to stop the machine, sample some data or increment a loop counter. This would be very useful in data collection.

1

### Specialized Fields

The ALU field controls the functions of the ALU. The control fields include two source register addresses, a destination address, the shift controls, logic and arithmetic function selection. Also there is the ability to read and write special purpose registers such as the Constant, timer, byte pipe, program counter and the LRF.

The CONstant (CON) fields are needed when the microcode uses a constant in some operation or on a computed branch. The Constant In (CI) field allows the microcode to contain constants needed in the execution of an instruction. Another Constant Out (CO) field exists and is the destination of the ALU field and used

by the ALL field. There are many applications for this such as the table branch into the microcode.

The SHift control (SHF) field sets the direction and parameters of a shift operation. Care must be taken to set this field to a known value before an ALU operation is performed.

The next field is the CCC field. This sets the condition code parameters. This field is used to select the proper output from the condition code and status multiplexer. This is then used by the sequencer to control conditional branches in the microcode.

The MEM field controls the reading from and writing to the LRF. This includes writing into one of several address counters, incrementing these counters then reading and writing to the data registers. There is an additional pointer into the register file used by the memory mapper. The MAP section will describe this in detail.

The MAP section controls when the memory system is to read and write data into the LRF. The interface is a request system, that is where address and data are

written as a group. In this system a pointer read or is set to the LRF which points to the address of data followed by a tag word which defines whether it is read/write and the length number or words. field tells the memory to run and it then reads address and tag, does the operation, then reads or writes the results in the locations following the address the LRF but can memory cannot sequentially access the data to which the pointer, set up by the MEM field, is pointing to. pointer is automatically incremented after every memory mapper initiated LRF read.

The SEQuencer controls the flow of microcode The next microcode word microcode subroutine calls. executed could be the old address plus one, a address given by the microcode, or the address on the Call stack. The Call stack is a push pop stack which enables the microcode to do subroutine calls. allows efficient use of the microcode with common The sequencer is relatively independent subroutines. of the other parts of the system although a jump to computed address is possible through the CO field.

#### Detailed Design

the microcode and the data paths had been developed, the detailed design of the hardware could The detailed design consisted of determining chips needed and interconnecting the actual In addition to interconnecting these parts, the chips. system would be simulated to insure the system was designed correctly. This would be done before any hardware existed and all debugging could be done during the simulation.

#### Arithmetic and Logical Unit

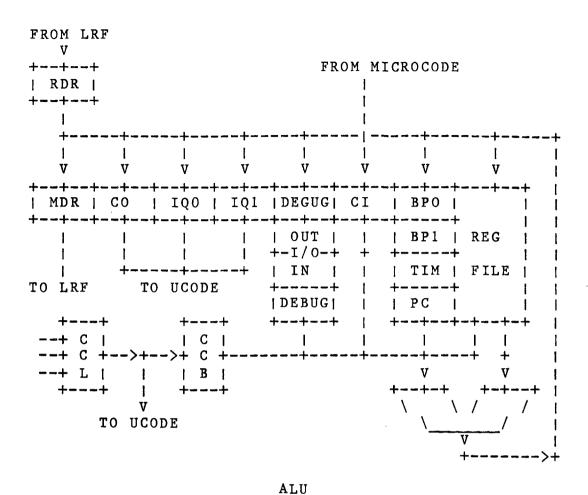

The ALU manipulated data within the machine. This is the workhorse of the processor and executed the guts of the instructions. This includes a 2900 bit slice machine, a "Byte Pipe" (BP), a Program Counter (PC) and a Condition Code register (CC), a TIMer (TIM), and a Instruction Queue (IQ).

FIGURE 18 - ARITHMETIC AND LOGICAL UNIT

The 2900 series are standard devices used extensively in bit-slice design. The chip family contains several parts including the ALU, register file, condition code select and shift control. The ALU can have inputs from the register file or an external data path. This external data path busses the output of the IQ, PC, TIM, CI and BP. The ALU has the standard arithmetic and logical functions needed. The

shift controller has the needed functions to accomplish arithmetic and logical shifts. The CC has the necessary functions to set overflow, underflow and carry bits.

The PC, and ΙQ are related special purpose registers. The PC is the program counter and incremented when a byte from the IQ is used. Whenever the PC counts over a word boundary, the processor fetches the next word in the code stream. The IQ feeds the sequencer to select where the microcode will execute. This is in the form of a table branch where lower 8 bits of the branch address comes from the instruction stream and the upper bits from microcode.

There can be some pipelining done in the processor. When code is fetched from memory it is stored in the LRF. This could be one word or several. When the ALU uses the last word from this cache, it starts a memory request. This memory request is then executed in parallel with the execution within the processor.

The TIM is a simple counter and is incremented every tick of the system clock. This counter is used to allocate time slices to different tasks. An overflow latch must be polled at the end of each instruction to check for the end of a time slice.

The BP is a byte rotater/selector. It has two words as inputs and one word as the output. The output word contains consecutive bytes of the two input words pointed to by the rotate select. This allows many versatile applications. One very useful application is to align words not on word boundaries. Another would be to speed a bit shift operation.

FIGURE 19 - BYTE ROTATER/SELECTOR

The CI and CO are the Constant In and Constant Out registers. The CI latches output from the microcode to ALU and the CO latches output from the ALU to the microcode. The CI register is controlled by the CON field in the microcode. This field load the can register with a constant value of data. The ALU can load the CO register as a destination of the ALU. This register is then enabled to the microcode by the ECW field.

The SHF field is used to set up parameters of the ALU shifter. This function is not often used but takes many bits of microcode because of the many various options allowed. The shifting is accomplished using the AMD 2900 series parts including the 2904 status and shift control unit. This is a very versatile unit but difficult to control.

The CCC field is used to select a status bit or condition code bit. This selected bit is then used by the SEQ field in a conditional branch. If a branch is taken the condition was true, otherwise sequential execution continues. There are 32 bits of status and condition codes but only one of them can be tested. All of the error condition codes are ORed together and

tested at the end of each instruction. If an error exists, the microcode branches to a routine which resolve the error condition. This reduced the number of tests to check for interrupts and errors.

# Large Register File (LRF)

The LRF is a two-port memory accessed by both the memory map and the processor. There are pointers into the LRF. One counters used as is switched between the memory map and the processor. This limits the memory map to accesses only in the area where the processor has pointed. A memory fetch accomplished by setting up a group of words in the LRF, pointing a counter to the group and telling the memory map that a memory cycle is to be done. The mapper then access the data in the LFR to determine what to fetch.

| FROM MICROCODE |           |           |          |

|----------------|-----------|-----------|----------|

| -++            |           |           |          |

| ++             | ++        | ++        |          |

|                | 1 1       | M         |          |

| ++ C ++        | LARGE     | +->+ 0 +> | TO MEM   |

| +              | -+ 1      |           |          |

| ++   +-+ M     | REGISTER+ | ++        |          |

| 1   B   ++ U   | ++        | 1   R     |          |

| ++ C ++ X      | FILE      | +->+ D +> | TO ALU   |

| ! ! ! +-+      | (4K)      | R         |          |

| ++   +         | -+ ++     | ++        |          |

| M   +-+-+      | 1         | M         |          |

| ++ C ++ M      | Ì         | +<+ I +<  | FROM MEM |

| 1 1 1 1 0 1    | MAP       | 1 1 1     |          |

| ++ +-+ X   A   | DDRESS +  | -+ ++     | .*       |

| M     ++       |           | M         |          |

| ++ C +-+       |           | +<+ D +<  | FROM ALU |

| 1 1            |           | R         |          |

| ++             |           | ++        |          |

FIGURE 20 - LARGE REGISTER FILE

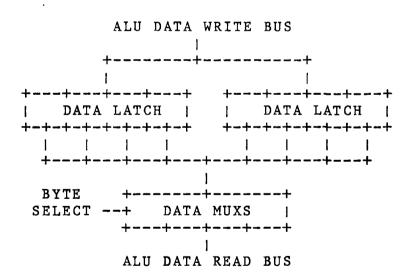

The LRF is 4k words of very fast (45 ns) memory. The memory is double cycled to form a two-port memory. An address multiplexer selects either the MAP address or the processor address. The processor can address the LRF either directly or through two counters, the AC and BC. Another counter can be swapped with the MAP address counter, the MC and MC' counter. In this way the processor can store data into the LRF, an address into the MC and then swap registers MC and MC'. This will indicate to the memory mapper that a memory cycle is to be started.

ALU reads and writes the LRF through two registers called the MDR and RDR. Reading and writing in the LRF mode. The MDR is a buffer of when occur data from the ALU to the LRF. The MEM specifies write operation and an address in the microcode field. The data in the MDR is then written into the LRF that address. Reading data is somewhat different. LFR read data through the RDR and directly into one of the ALU registers. This way a second cycle is needed to transfer data to an ALU register.

## Sequencer (SEQ)

The SEQuencer consists of another chip from the 2900 family. This has the controls for subroutine calls, a micro-program counter, a pipelining register and a direct input. Additional hardware was added for conditional branches, table jumps and downloading of microcode.

The table branch hardware is a simple masking operation. In normal operation, the microcode can branch to any location in the microcode memory. The table branch allows part of the branch address to come

from the microcode and part from the IQ register. The upper bits of the address are concatenated to the eight bits from the IQ and this address passed to the sequencer.

FIGURE 21 - SEQUENCER

A conditional branch uses the condition bit to select the next address in the microcode sequence. First the proper condition code must be selected. If the condition is not true, the next sequential address is selected. If the condition is true, then a branch to another location is executed. This can be a table branch or an absolute branch.

The microcode is stored in fast memory. This is called a Writable Control Store (WCS). Data paths have

been designed into the system to allow simple microcoding of the machine. This is done with parallel I/O ports and control lines. These are used to write, read and test the WCS.

The WCS was to be implemented on a separate board from the rest of the processor. Therefore an interface between the two parts of the processor had to be defined. Appendix D shows a memo defining the interface between the two boards. This division point was selected such that only 32 microcode lines and a few control lines were needed to be passed between the two boards.

#### Testability and Debug Features

There are several data paths in the processor to increase the ease of testing and debugging the machine. The testing and debugging is done over several I/O ports and through the use of a Trace module. Connectors have been designed into the system to allow ease in connecting trace modules to all important data paths and I/O modules connected to the necessary control points.

FIGURE 22 - TEST AND DEBUG DATA PATHS

The major concern is the ease of microcoding and debugging. Therefore special data paths have been added to the microcode sequencer to allow ease in downloading the microcode. The address and data lines into the microcode have an interface to several I/O modules and the sequencer output enables are controlled by the I/O modules. Appendix E is a memo describing the debug interface signal assignment and the functions of those signals.

The first I/O module is a control module. It selects the enabling onto control busses from either

the debug module or the microcode. The second I/O module outputs only data. The first module selects the destination for the second and strobes the data into the proper latches. The first module has other various control signals which allow the microcode to be written into, read from, single stepped, multiple stepped, and several other features. This allows full control over the execution of the microcode.

The I/O modules are controlled by AMPL which is a software package TI uses to control the trace modules. AMPL is used to setup and control the trace modules and to read and write the I/O modules.

Connections to the trace module from data busses in the ALU and LRF allow information to be gathered I/O during execution of the microcode. An module connected to the ALU section allows testing of ALU's registers and the LRF. In addition to the I/Omodules, several seven-segment LEDs mounted on processor board are used during initial self test. This would allow a user to visually check for any error condition with a simple go/no go indication.

A microcode bit was allocated to enhance the tracing of information. This bit could be used to trigger the trace of a sequence, trace a state or stop the machine and wait for a single step. This versatile bit, coupled with the trace module, would provide for an easily debugged system.

Several software interface routines were to be written to provide a simple interface to the debug data. A memo describing showing the definition of these signals is shown in Appendix F. These routines by two software be written diagnostic to They would do things from engineers. simple complex. For example one routine would simply reset the processor. Another would allow the processor to be single stepped. These routines were defined in AMPL as subroutines. This would allow more complex programs to be written. These would do complex functions such the processor, download a new set of microcode, reset execute until a specific point and then begin single stepping and tracing data at that point.

#### Simulation

Two different types of simulation were utilized in the development of this machine. First a register level simulator was written to define, test and debug the data paths and microcode. The next simulation effort was in conjunction with the detailed design and analyzed detailed delay through all parts of the system.

#### BASIC Simulation

The initial simulation was written in the BASIC language. This simulator can be described as a register-to-register transfer program. Figure 23 shows how the display looked to the user. This showed the important internal registers and data paths.

|        |          | +              | +       | - AC  | 0000   |       | 0000   |

|--------|----------|----------------|---------|-------|--------|-------|--------|

| +-RDR  | - 0000   | )   M          | EMORY   | BC    | 0000   |       | 0000   |

| +-MDR- | - 0000   | )              | Į       | MC    | 0000   | STK   | 0000   |

|        |          | +              | +       | - DI  | R 0000 |       | 0000   |

| +      | +-       |                | +       |       | +      | RE    | 0000   |

| 1      | I        |                | 1       |       | ļ      | ISB   | 0000   |

| R(     | )0000    | ) R(           | )000    |       | 0000   |       | 1      |

| IQO    | - 0000   | ) BP 0         | 000     | 00    | 1      | SA    | 0000   |

| IQ1    | - 0000   | $\mathbf{BP1}$ | 000     | 0     | +      | -+    | 1      |

| DEB    | UG 0000  | MIT (          | 000     | 00    | l      | 1     | ++     |

| 1      | 1        | PC             | 000     | )0 CI | 0000   | SB    | 100001 |

| 1      | 1        |                | !       |       | l      | 1     | ++     |

| 1      | +        |                | +       |       | +      | I     | 1 .    |

| 1      | 0000     | 0000//0        | 0000    |       | 1      | ALU   | 0000   |

| l      | Al       | rn- o -        |         | +CC   | 0000   | MEM   | 0000   |

| 1      | (        | 0000           | j       |       |        | l CCC | 0000   |

| 1      |          | +              | -+QR+-+ | -     |        | MAP   | 0000   |

| 1      | <i>'</i> | 0000           | 0000    |       |        | SEQ   | 0000   |

| 1      |          | 1              | 1 1     |       |        | I     | 1      |

| +      |          | +              | +       | +     |        | +     | +      |

FIGURE 23 - SAMPLE SCREEN DISPLAY

The main purpose of this simulator was to be an interactive tool used to assist in the detailing of the data paths, writing and debugging of the microcode. The register-to-register transfer allowed the data paths to be exercised with several sample programs. The actual microcode controlled the register transfer and data manipulation. These bits were assigned and developed during the writing of the simulator.

After the simulator was finished, it was used to test and debug microcode routines. This proved to be a great benefit since the execution could be visualized

the CRT screen. No detailed on hardware considerations other than machine clock cycles were into account. Each loop through the program is state in the microcode. This would instruction timing to be accurately defined. Writing and debugging of microcode could be done before hardware existed.

The user interface was the most important aspect of the simulator. The data paths were graphically displayed upon the screen. As variables changed in various parts of the system, the changes were displayed. The microcoder could actually see what the microcode was doing and visually trace the execution of his program.

One problem with the simulator was it was BASIC is inherently a slow language and therefore the program was rewritten in PASCAL. This version ran much faster but the I/O was much more difficult and harder modify. Yet both the BASIC and PASCAL versions proved to be beneficial to the microcoders. A listing οf Pascal version of the emulator is shown in Appendix G.

#### HDL Simulation

The detailed design was initially done in the traditional sense of drawing schematics. The several pages of schematics were drawn fast and rough to be a visual reference during the simulation.

The first step in the simulation was to learn HDL. HDL is a Hardware Description Language written for use in simulating a chip design. No had used one this language to simulate a complete design from the gate level to chip level then to board level and finally complete system level. Since the project was complex, it was believed that simulation would reduce the time it takes to debug the breadboard. The debug would be done during simulation before hardware existed.

HDL is a block description language. The design is divided into many different blocks and each of simulated. The low level blocks were then blocks connected by upper level blocks to form a tree structure. Each higher level reflected the functioning of larger pieces of hardware. For example a latch chip could be simulated at the lowest level with gates.

Several latches could be put together at a higher level form а register. Several registers could combined form a register file. The register file to could be combined at a higher level with the form the CPU. This type of simulation is very flexible since the lowest level is only written once for a latch and duplicated whenever a latch is used by a higher level. This is similar to subroutines in software design.

is also easy to modify. Errors are found by tracing the program execution. This is similar hardware signals with a logic analyzer. Once an error is found a change is made and the hardware resimulated. Once a lower level is fully simulated and debugged it can be used over and over with a high level of confidence. This is better than with schematics which must be redrawn when an error is found.

Before simulation of the processor could begin, low level blocks of memory, counters, latches and multiplexers were simulated. Another engineer had the responsibility of writing these low level blocks and debugging them. I took these low level blocks and made a macro-library out of them. The macro-library

consisted of registers, a memory file, wide multiplexers and large counters.

The macro-library was then used to simulate the LRF, ALU and SEQ portions of the design. The LRF used several of the macro-blocks and combined them together form this upper level block. This was simulated with selected data being input and internal then be compared traced. This would against expected results. The ALU was also simulated in similar way but the SEQ was handed off to another engineer to simulate. This could be done since sequencer was on another board and the interface between the boards was well defined. The data path and block level design had been done and only the detailing of the blocks was left.

The simulation for the LRF can be found in Appendix H. The first portion of the block defines all input and output signals to that block. Next the structure of the sub-blocks is defined. This is done by simply defining the block's type then its inputs and outputs. All blocks are connected in this way until the lowest level is reached.

#### Communications

During this project, communication with other engineers was very important. There were many key portions of the system which were developed through close communication of ideas and possible solutions.

The architectural specifications was constantly changing while the hardware was being designed. While the data path were general purpose, it was still critical that all changes be fully understood to insure they could be implemented. All changes were to be taken into account by modifying the microcode and not the hardware. For the most part, additional data paths were not needed although some microcode sequences became rather long to perform.

The debugging of the system was done with AMPL. Other software engineers were to write the procedures to accomplish the needed tasks. This again involved communications problems since I had to convey how the hardware would work to people who did not fully understand hardware. Yet with several memos and many informal meetings they were able to understand and write the procedures which were needed.

#### Change in Direction

Because of the slow speed of the breadboard, it was decided that the development of a slow breadboard be halted and a high performance version be built. It was deemed that a higher risk should be taken at a earlier date so that more could be learned from this experimental design.

The project was then redirected from building a slow vertical machine to a parallel fast machine. This posed many new problems and changed the view of the architecture drastically. Many things which were taken for granted in the slow machine and being done through many cycles must now be done in one. Therefore every data path and every microcode state had to be changed. This change in direction was very frustrating since several months of work was thrown away.

Simulation was the most important thing which was learned from the breadboard. This was one area where what was learned on the slow machine could be applied to the fast processor. A bottom up approach was used on the breadboard in writing the blocks and hooking them together. A top down method could have also been

used and in retrospect would have been the best way to go. The fast machine would be much more difficult to simulate and therefore the top down approach would be more important to use.

With this decision, all work on the slow breadboard was stopped and the new direction towards a faster, improved model was begun.

# FAST PROCESSOR Objectives

Performance is the sole objective of the fast version of the processor. While Millions of Instructions Per Second (MIPS) is not a good measure of performance, the speed goal of the machine was 2 MIPS.

The slow breadboard was at the low-speed/low-cost end of the speed/cost curve (A). This machine is high performance and therefore a high cost implementation. This puts the second processor at the other end of the curve previously discussed (B).

FIGURE 24 - HARDWARE SPEED-COST CURVE

The first problem facing the hardware designer is to sort out the software architecture. This results in defining what will require extensive hardware versus

what remains in software. A good understanding of this was gained from the first breadboard. Architectural implications of caching and pipelining also must be studied. Successful cache placement is very important yet architecturally dependent. Pipelining requires an understanding of data flows and how that flow could be layered in this architecture.

paths for the fast processor will be broken Data down into several areas. First, existing methods processor will be discussed including speeding а Next, specific caching and pipelining. hardware developed to speed this processor will be described. This will include a decoder for the operand specifiers and · a method of speeding the jump and call instructions.

#### Conventional Caching Methods

One method commonly used to speed execution is through the use of caches. In this report, caches are defined as any fast memory added to the system to improve performance. There are several types of caches and many methods and positions for the caches to be

placed.

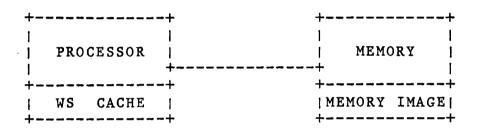

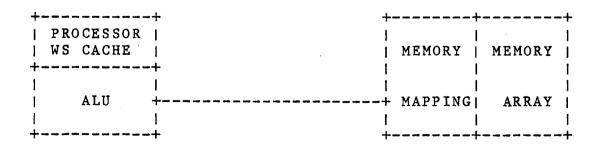

The workspace is an area of memory which contains the most frequently used variables. This would be similar to the 990 workspace and is used like a register file. A workspace cache can be used to store the data in the processor such that access to this area do not actually go to memory. This cache is bulk stored and loaded whenever a context switch occurs.

FIGURE 25 - WORKSPACE CACHE

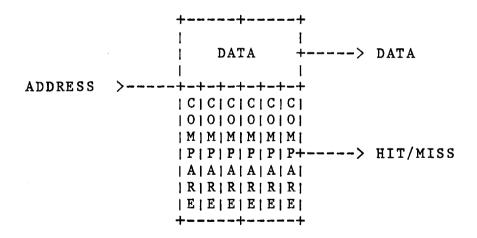

Another type of cache is a Content Addressable Memory (CAM). This cache stores both data and the full address of that data. An address is presented to the cache and it is compared in parallel with every address in the cache. If the compare is true, a cache "hit" occurs and the data corresponding with that address is presented on the output. A large amount of dedicated hardware can make this cache very fast.

is used frequently to speed CAM translation. This is important in various memory mapping schemes where an address is mapped from address space to another. Most mapping schemes require the logical address output by the processor to be translated into a virtual or physical address. This address would be the input to the cache. If the address had been previously mapped and stored in CAM, data read out of the cache would be the translated While being very fast, this cache is also address. very expensive and usually only has four to eight entries.

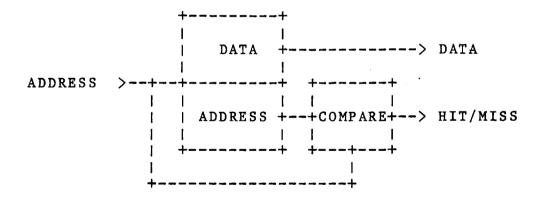

FIGURE 26 - CONTENT ADDRESSABLE MEMORY

Another type of cache is the Associative Cache which stores both data and the group associative address of that data. When a memory address is presented to the cache, data and address are read from the cache. After the read, the address stored in the cache is compared to the associative portion of the memory address presented to the cache which determines if the cache contains valid data. This is slower than a CAM since the compare occurs serially after the data is read but can results in a less expensive and larger cache. This cache is typically between 2k and 16k in length.

FIGURE 27 - ASSOCIATIVE CACHE

#### Caching Evolution

Data cache placement is very important to system performance and must be studied carefully. Appendix J shows various cache placements and the resultant speed of the processor. These are estimates based upon the number of memory accesses and the percentage of those accesses which hit the cache. From this study, it was determined that the processor should contain several types of data caches at various locations.

The workspace is an architectural feature which is preferred by software designers. The workspace is an area of memory used simular to a register file. When a subroutine call is made, the workspace pointer is changed. This results in the processor writing the current contents of the cache cache into memory and loading data from the new workspace.

FIGURE 28 - CACHE EVOLUTION I

Another general data cache is needed for frequently accessed data not found in the workspace. This is an associative type cache which is demand loaded with "write through". Demand loading occurs on memory reads when a cache does not contain the correct data. This is referred to as a cache miss and when this happens a full memory cycle is started. When valid data is retrieved from the memory system, the data along with the proper address would be written back into the cache. A "write through" occurs every cache write also results in a memory write. This causes the memory to always contain the current data thereby avoiding the need to ever "flush" the cache into memory.

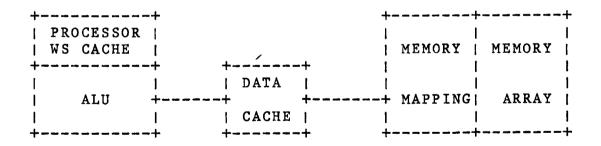

FIGURE 29 - CACHE EVOLUTION II

An instruction cache is in parallel with the data cache and is very similar. In fact, the same cache subsystem could be duplicated for both. This cache is also demand loaded but never written into. Since the data cache and instruction cache are in parallel, both accesses can occur in parallel. This allows for a higher memory bandwidth. The back side of the data and instruction caches are interfaced to the memory system and must arbitrate for the memory accesses.

| ++          | +            | +          |        |

|-------------|--------------|------------|--------|

| INSTRUCTION | INST         | 1          |        |

| PREFETCH +- | +            | ++         |        |

| ++          | CACHE        | 1 1 +      | +      |

| PROCESSOR   | +            | +          | 1      |

| WS CACHE    |              | ++ MEMORY  | MEMORY |

| ++          | +            | +          | 1      |

|             | DATA         | 1          | 1      |

| ALU +-      | <del>+</del> | ++ MAPPING | ARRAY  |

| ·<br>       | CACHE        | 1          | i i    |

| ++          | +            | + +        | ·+     |

FIGURE 30 - CACHE EVOLUTION III

When a write occurs to the memory system, it is immediately written into the data cache and presented to the memory mapping. The write buffer will queue the write request and the memory mapper will write the data when it is not busy. This allows the processor to continue to execute from the data cache while the memory system is completing the write.

| +           | -+ -  | <b>+</b> | -+  |           |        |

|-------------|-------|----------|-----|-----------|--------|

| INSTRUCTION | 11    | INST     | 1   |           |        |

| PREFETCH    | +     | - CACHE  | ++  |           |        |

| +           | -+    | i        | 1 1 | +         | +      |

| PROCESSOR   | -     | +        | -+  | 1         | 1      |

| WS CACHE    | 1     | DATA     | 1 1 | MEMORY    | MEMORY |

| +           | -+ +  | F CACHE  | ++  | 1         | 1      |

| 1           | 1 1 - | +        | -+  | 1         | 1      |

| ALU         | ++    | + WRITE  | ++  | + MAPPING | ARRAY  |

| 1           | 1     | BUFFE    | R į | 1         | I .    |

| +           | -+ -  | +        | -+  | +         | +      |

FIGURE 31 - FINAL CACHE CONFIGURATION

There are two address translation in the system.

A logical-to-virtual and virtual-to-physical. Address caches are mandatory in this system. The logical-to-virtual translation occurs in the processor while the virtual-to-physical occurs in the memory mapper.

The address register file is a defined set of base addresses which must be used when addressing memory. When a base address register is loaded into the processor, the address is resolved from a logical address to a virtual address and this virtual address is cached in the address register file. When a base register is specified, the previously translated virtual address is then used in address development.

The virtual-to-physical translation occurs in the memory mapping portion of the system. This address translation utilizes a CAM to improve speed.

| ++          | +      | -+ +- | +      | ++     |

|-------------|--------|-------|--------|--------|

| INSTRUCT    | 1      | 1 1   | 1      | 1 1    |

| PREFETCH +- | -+     | ++    | MEMORY |        |

| ++          | DATA   | 1     | ++     | MEMORY |

| LOGICAL/    |        | ++    | CAM+-  | +      |

| VIRTUAL     | 1      | 1 1   | ++     | 1 1    |

| ++          | CACHES | ++    | MAP    | ARRAY  |

| ALU +-      | -+     | 1 1   | I      | 1 1    |

| ++          | +      | -+ +- | +      | ++     |

FIGURE 32 - ADDRESS TRANSLATION

# Pipelining Evolution

Pipelining is another widely used method of speeding the execution of a machine. Pipelining is a method of paralleling various portions of the instructon cycle such as the fetch, decode and execution phases.

Several studies were made of data flowing through the pipeline. Appendix K shows an example of one study. An instruction is traced through the pipeline and the diagram keeps track of how the data flows. The pipeline needs to be balanced such that each level stays equally busy. This diagram can show holes in the pipeline when one level waits on another. This is a useful tool in developing the appropriate division in the pipeline and the hardware to put into each level.

The processor is pipelined in several layers. The first is the instruction prefetch. The second is the operand specifier decoding. The third level fetchs data from internal registers and develops the addresses. The fourth level contained the ALU which does data fetches and manipulation. The last portion of the pipeline was a memory write buffer.

The instruction prefetch is the first level of the pipeline. It looks ahead of the current program counter and retrieves the addition words of code from the instruction cache. This is fed into a FIFO which buffers several code words and performs code alignment and extraction.

The speed of the instruction execution is dependent upon the bandwidth to memory. With small data paths, the instruction fetches occur more often than data fetches. As the paths get wider more and

more of the instruction stream is fetched on each memory access. This will improve performance of data manipulation by speeding the handling of larger data types with a major benefit coming from not making as many instruction fetches. This is very important especially when instruction prefetch is heavily used.

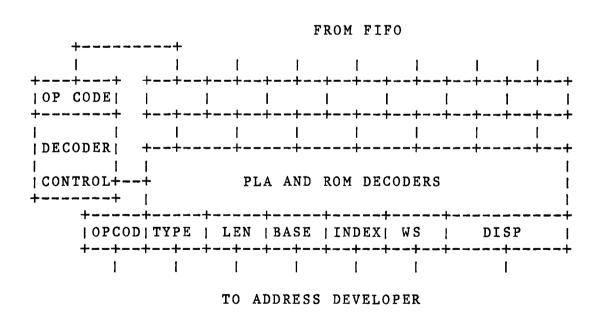

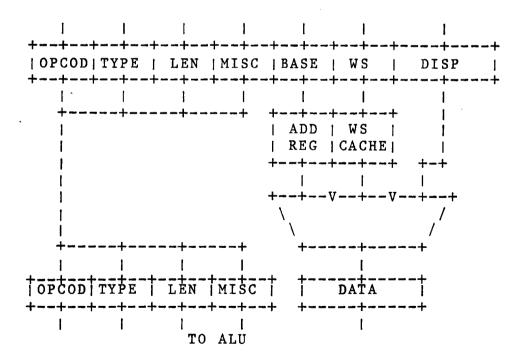

The next level of the pipeline is the operand specifier DECODER. Instructions are aligned on byte boundaries and can be many bytes in length. This section takes these instructions and decodes their operand specifiers. The DECODER extracts the base register designator, workspace register designator, displacement and/or an immediate value then passes the pointers and data to the next level of the pipeline.

FIGURE 33 - PIPELINE

The register fetch and address development is the next level of the pipeline. At this level the base address, limits, and access privileges are read from the internal address register file and the index is read from the workspace cache. The base in then added to the index and displacement and compared to the bound. The results of this stage are then passed to the ALU.

The ALU does all memory fetches, data manipulation and writes into memory. After all address, register or immediate data has been developed, this leaves a relatively small amount of work for the ALU. The ALU can do a memory fetch during every cycle. There is no delay when the cache is "hit" or contains the correct data. If there is a cache "miss" a longer memory cycle is started. Once the ALU has all the data needed for the operation, it proceeds with the calculation.

# Performance Improvements

One factor which is of key importance to software implementers is the speed and functionality of the CALL

instruction. In high level languages, the CALL instruction occurs frequently. Yet most architectures do not have any assemble language instructions which resembles the high level language CALL. In order to accomplish a CALL, many assemble language instructions branch to must be executed to the routine, parameters and save the current context. In this machine one single instruction does all of this. saves the current context, loads the new context, gives the branch address and sets up parameters to be passed.

Fast execution of the CALL instruction requires special purpose hardware. The context changes when a CALL instruction is executed. This means the old context must be stored into memory and a new context read into the processor. Addresses must be developed from this old context and data fetched. One method of speeding the Call is to cache the last context in the processor. This is done by simply saving a copy of the old context within the processor so that the last context is not fetched from memory on a return.

In Figure 34 the internal processor cache #1 could contain the old context. The #2 bank contains the current task. When a return is executed, the old

context is is still in the processor and a switch is simply made from bank #2 to bank #1. This also improves speed when task #2 wants to get a parameter from the old context. All registers are still in the processor and it is simple to calculate the passed operand specifiers address from the old context.

FIGURE 34 - PIPELINE IMPROVEMENTS/CALLS

There are problems which arise from this structure. If more that one call is made, the first Call's context must be destroyed. This results in only the last context being saved. It is believed that most programs execute CALLs and RETURNs in groups which are only one level deep. If this proved false, several levels of context caching could be added to speed the CALL.

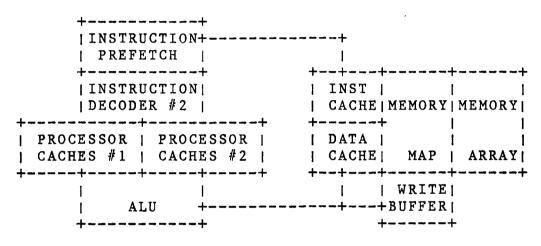

problem Another speed arises from JUMP instructions. Since the machine is pipelined, a JUMP instruction causes the pipeline to be flushed and the new instruction stream fetched from the branch address. One way to speed this is to have a dual prefetch decode system such that both branches of the JUMP instruction are prefetched and decoded ahead of This way both directions of the branch execute at the same speed assuming that the prefetch can keep queues full.

This same method can be used to speed the CALL. If the old prefetched instruction stream were kept in the processor, the old context would be preserved along with the old instruction stream, and no penalty would be paid upon a return. This requires three parallel paths within the machine from instruction prefetch through decoding and register prefetching. Instruction decoder #2 and #3 would now hold the current context. #3 would contain the instruction stream if a jump were taken while #2 would have the currently executing instruction stream.

| ++                        |                         |

|---------------------------|-------------------------|

| INSTRUCTION +             | +                       |

| PREFETCH                  | 1                       |

| ++                        | ++                      |

| INST   INST   INST        | INST                    |

| DECODE#1 DECOD#2  DECOD#3 | CACHE   MEMORY   MEMORY |

| ++                        | ++                      |

| PROCESSOR   PROCESSOR     | DATA                    |

| CACHES #1   CACHES #2     | CACHE   MAP   ARRAY     |

| ++                        | ++                      |

| 1 1                       | WRITE!                  |

| ALU +                     | +BUFFER                 |

| ++                        | ++                      |

FIGURE 35 - PIPELINE IMPROVEMENTS/JUMPS

The CALL, Jump and current context portions of the pipeline are all dynamic. The assignment depends upon where the processor is currently executing and which bank is an available prefetch queue.

# Detailed Design

The operand specifier decoder was the first part of the machine to be detailed. This includes the FIFO buffer and the operand specifier DECODER. It is assumed that an instruction prefetch feeds code into this portion of the processor and the output is the base register addresses, cache register addresses,

displacements and literals.

# FIFO Buffer

The first part of the detailed design consisted of a FIFO buffer. This buffer is a queue for the prefetched instructions and a code stream aligner for the decoder. The aligner extracts any eight sequential bytes from the FIFO. The select input determines which byte is the first position on the output.

seven bytes of the code stream are needed Uр for decoding the operand specifier. Therefore is decided that each level of the FIFO would be eight bytes wide. The number of levels or depth of the far ahead of the current program upon how counter the FIFO needs to buffer the code stream. levels, each eight bytes wide, are mandatory to be able properly utilize the FIFO. Four to levels were selected as the number of total levels in the FIFO.

# INSTRUCTION PREFETCH INPUTS

|                | 1  | 1         | <u> </u> |                    |           |           |             |            |          |

|----------------|----|-----------|----------|--------------------|-----------|-----------|-------------|------------|----------|

| <br>           |    | <br> <br> | <br>     | <br> <br>          | <br> <br> | <br> <br> | <br> <br>   | <br> <br>  | F        |

| !<br>+-        |    | <br>+     | <br>+    | <br>               | <br>+     | <br>      | <br>        | <br> +     | F        |

| <u> </u><br>+- |    | !<br>+    | !<br>+   | <br>               | <br>+     | <br>      | <br>+       | <br>       | - C      |

| <br>+-         | -+ | 1<br>++   | !<br>++  | <br> +             | !<br>++   | <br> +    | <br>        | <br> +     | - N I    |

|                |    |           | INTERMI  | I<br>EDIATE        | OUTPU'    | rs        |             |            | T  <br>R |

| +-             |    | +         | •        | <br> <br>  BYTE R( | <br> <br> | <br>      | <br>        | <br> +<br> | - L      |

| +-             | -+ | ++        |          |                    | )         |           | <del></del> | ۱<br>+++   | o        |

|                | ļ  | ı         | i        | ı                  | ı         | ı         | I           | ı          |          |

DATA OUTPUTS

# FIGURE 36 - FIFO

The FIFO is constructed from byte-wide register latches, eight per row with four rows. The outputs of the four rows are tied together and the controller determines which output is enabled. Following this intermediate output is a byte rotater.

The FIFO read is a two step process. First, the byte pointed to by the select input and the next eight consecutive bytes of code stream are enabled, one per column. Secondly, these eight intermediate bytes are

rotated until they were properly aligned.

The FIFO controller has an internal counter which keeps track of the next write location. From the next write location and the select input, the controller can determine when a level in the FIFO becomes empty. When this happens, a handshaking signal with the instruction prefetch is toggled to begin the next code word prefetch.